20. Universal synchronous asynchronous receiver transmitter (USART)

20.1 USART introduction

The universal synchronous asynchronous receiver transmitter (USART) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The USART offers a very wide range of baud rates using a fractional baud rate generator.

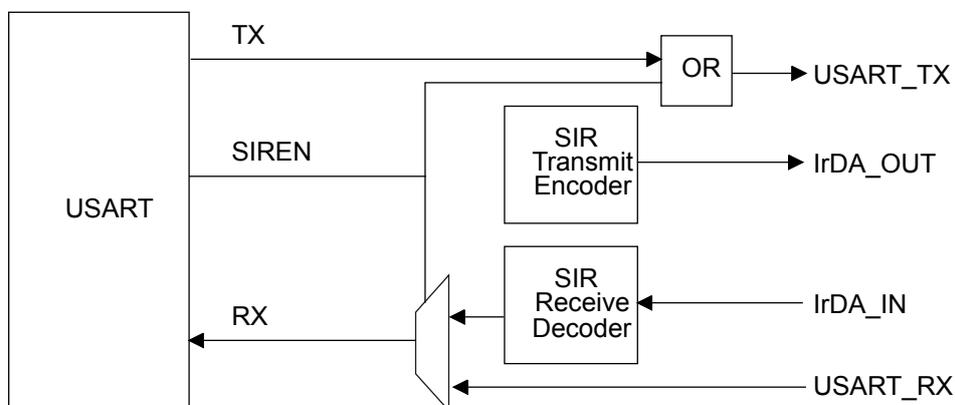

It supports synchronous one-way communication and half-duplex single-wire communication. It also supports the LIN (local interconnection network), smartcard protocol and IrDA (infrared data association) SIR ENDEC specifications, and modem operations (CTS/RTS). It also supports multiprocessor communications.

High speed data communication is possible by using the DMA (direct memory access) for multi-buffer configuration.

20.2 USART main features

- • Full-duplex asynchronous communication

- • NRZ standard format (mark/space)

- • Configurable oversampling method by 16 or 8 to give flexibility between speed and clock tolerance

- • Baud rate generator systems

- • Two internal FIFOs for transmit and receive data, that can be enabled/disabled by software. FIFOs come with status flags for FIFOs states

- • A common programmable transmit and receive baud rate of up to 2 Mbit/s with the clock frequency at 16 MHz and oversampling is by 8

- • Dual clock domain with a dedicated kernel clock allowing baud rate programming independent from the PCLK reprogramming

- • Auto baud rate detection

- • Programmable data word length (7 or 8 or 9 bits)

- • Programmable data order with MSB-first or LSB-first shifting

- • Configurable stop bits (1 or 2 stop bits)

- • Synchronous master/slave mode and clock output/input for synchronous communications

- • SPI slave transmission underrun error flag

- • Single-wire half-duplex communications

- • Continuous communications using DMA

- • Received/transmitted bytes are buffered in reserved SRAM using centralized DMA

- • Separate enable bits for transmitter and receiver

- • Separate signal polarity control for transmission and reception

- • Swappable Tx/Rx pin configuration

- • Hardware flow control for modem and RS-485 transceiver

- • Communication control/error detection flags

- • Parity control:

- – Transmits parity bit

- – Checks parity of received data byte

- • Interrupt sources with flags

- • Multi processor communications

- • Wakeup from mute mode (by idle line detection or address mark detection)

20.3 USART extended features

- • LIN master synchronous break send capability and LIN slave break detection capability

- – 13-bit break generation and 10/11 bit break detection when USART is hardware configured for LIN

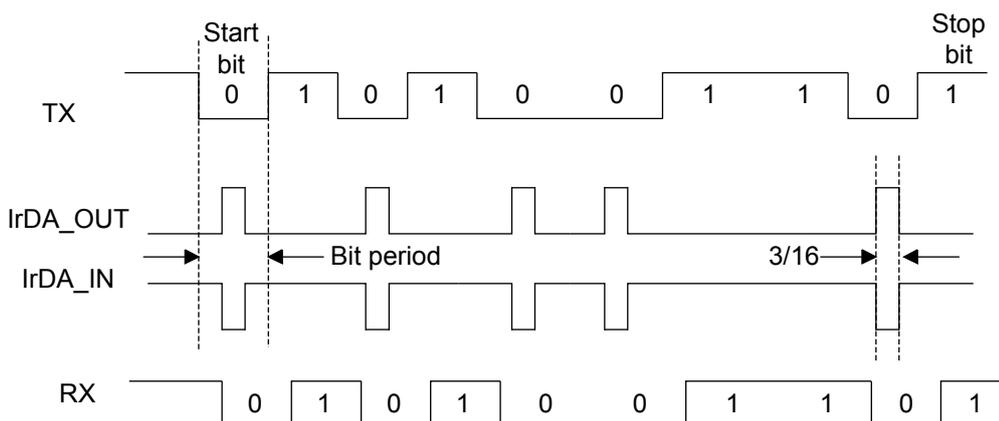

- • IrDA SIR encoder decoder supporting 3/16 bit duration for normal mode

- • Smartcard mode

- – Supports the T=0 and T=1 asynchronous protocols for smartcards as defined in the ISO/IEC 7816-3 standard

- – 0.5 and 1.5 stop bits for smartcard operation

- • Support for Modbus communication

- – Timeout feature

- – CR/LF character recognition

20.4 USART implementation

Table 60. USART/LPUART features describes the USART and LPUART implementation on the STM32WB07xC and STM32WB06xC devices.

Table 60. USART/LPUART features

| USART modes/features (1) | USART | LPUART |

|---|---|---|

| Hardware flow control for modem | X | X |

| Continuous communication using DMA | X | X |

| Multiprocessor communication | X | X |

| Synchronous mode (master/slave) | X | - |

| Smartcard mode | X | - |

| Single-wire half-duplex communication | X | X |

| IrDA SIR ENDEC block | X | - |

| LIN mode | X | - |

| Dual clock domain | X | X |

| Receiver timeout interrupt | X | - |

| Modbus communication | X | - |

| Auto baud rate detection | X | - |

| Driver enable | X | X |

| USART data length | 7, 8 and 9 bits | |

| Tx/Rx FIFO | X | X |

| Tx/Rx FIFO size | 8 | |

1. X=supported.

20.5 USART functional description

Any USART bidirectional communication requires a minimum of two pins: receive data in (RX) and transmit data out (TX):

- •

RX:

receive data input

This is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise. - •

TX:

Transmit data output

When the transmitter is disabled, the output pin returns to its I/O port configuration. When the transmitter is enabled and nothing is to be transmitted, the TX pin is at high level. In single-wire and smartcard modes, this I/O is used to transmit and receive the data.

Serial data are transmitted and received through these pins in normal USART mode. The frames are comprised of:

- • An Idle Line prior to transmission or reception

- • A start bit

- • A data word (7, 8 or 9 bits) least significant bit first

- • 0.5, 1, 1.5, 2 stop bits indicating that the frame is complete

- • The USART interface uses a baud rate generator

- • A status register(USART_ISR)

- • Receive and transmit data registers (USART_RDR, USART_TDR). When FIFO mode is enabled, writing into USART_TDR adds one data to the transmit FIFO; and reading from USART_RDR removes one data from the receive FIFO

- • A baud rate register(USART_BRR)

- • A guardtime register (USART_GTPR) in case of smartcard mode.

Refer to Section 20.7: USART registers for the definitions of each bit.

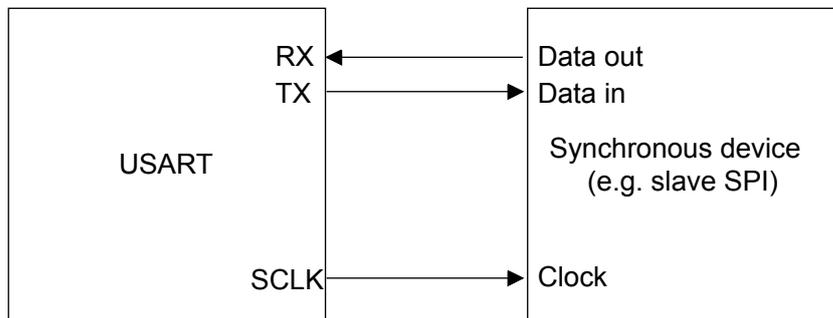

The following pin is required to interface in synchronous mode and smartcard mode:

- • SCLK: This pin acts as clock output in synchronous master and smartcard modes. It acts as clock input in synchronous slave mode. In synchronous master mode, this pin outputs the transmitter data clock for synchronous transmission corresponding to SPI master mode (no clock pulses on start bit and stop bit, and a software option to send a clock pulse on the last data bit). In parallel, data can be received synchronously on RX. This can be used to control peripherals that have shift registers (e.g. LCD drivers). The clock phase and polarity are software programmable.

In smartcard mode, SCLK output can provide the clock to the smartcard.

- • NSS: This pin acts as slave select input in synchronous slave mode.

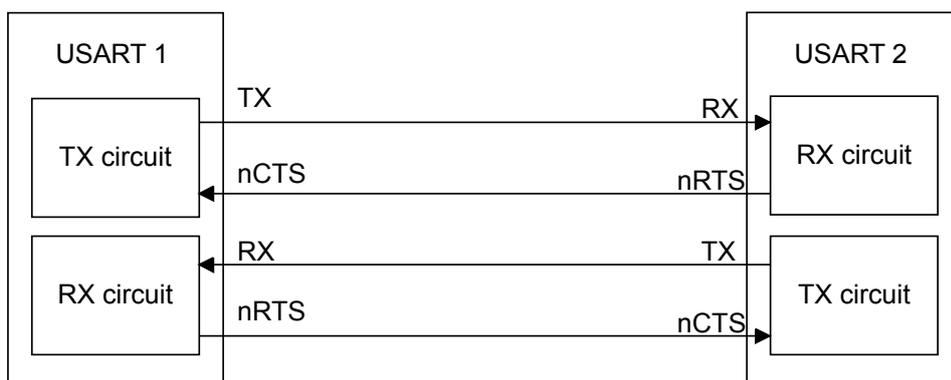

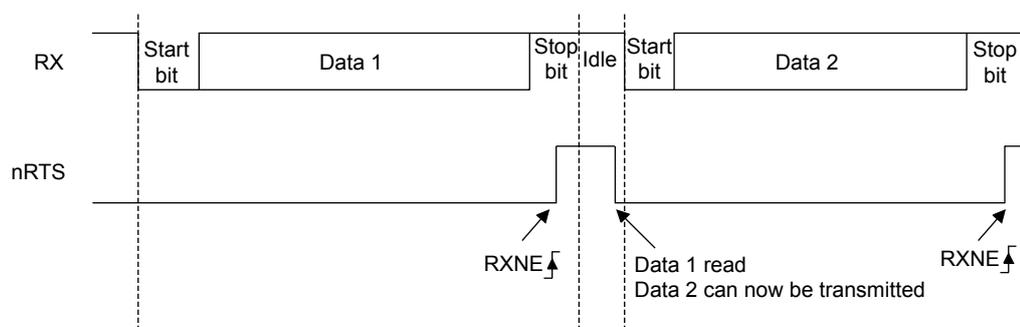

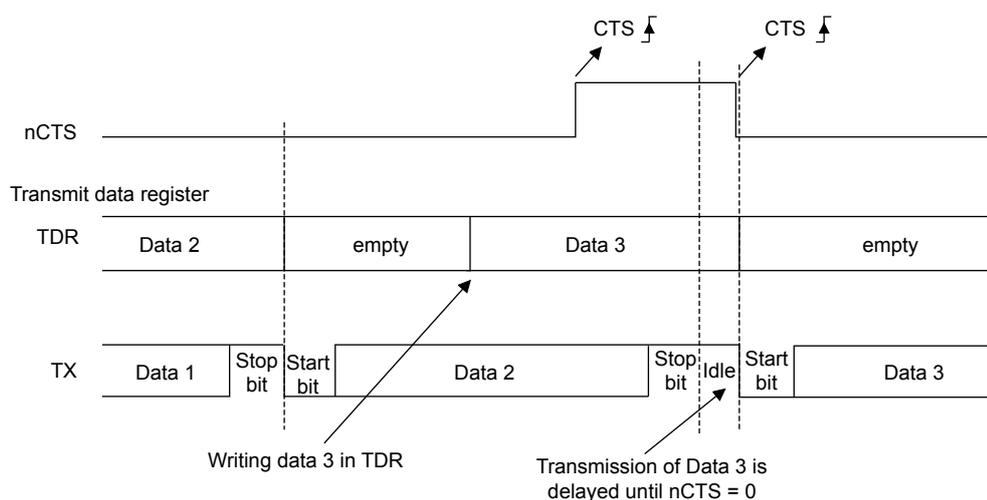

The following pins are required in RS232 hardware flow control mode:

- • nCTS: Clear to send blocks the data transmission at the end of the current transfer when high

- • nRTS: Request to send indicates that the USART is ready to receive data (when low).

The following pin is required in RS485 hardware control mode:

- • DE: driver enable activates the transmission mode of the external transceiver.

Note: DE and nRTS share the same pin.

Note: NSS and nCTS share the same pin.

Figure 113. USART block diagram![Figure 113. USART block diagram. This is a complex block diagram of the USART peripheral. At the top, there are two data registers: 'Transmit data register (TDR/TXFIFO)' and 'Receive data register (RDR/RXFIFO)'. Data is written to the TDR and read from the RDR. Below these are 'Transmit shift register' and 'Receive shift register'. To the left is an 'IrDA SIR ENDEC block' connected to TX and RX pins. On the right is an 'SCKL control' block connected to the SCLK pin. Below the shift registers are control and configuration registers: 'USART_CR1 register', 'USART_CR2 register', 'USART_CR3 register', and 'USART_GTPR register' (containing GT and PSC). A 'Hardware flow controller' is connected to nRTS, /DE, and nCTS pins. Below the registers are 'Transmit control', 'Wake-up unit', and 'Receiver control' blocks. These are connected to 'USART_ISR register' and 'USART interrupt control'. At the bottom is a 'Conventional baud rate generator' containing 'USART_BRR register', 'Transmitter rate controller', 'Receiver rate controller', and 'BRR[15:0]'. It is connected to a clock divider block labeled '/USARTDIV or 2/USARTDIV (depending on the oversampling mode) (Note 1)'. The input clock is fCK (Note 2).](/RM0530-STM32WB07xC-06xC/5a7ef674d3d47e22615920f270a52b5a_img.jpg)

Note: For details on coding USARTDIV in the USARTx_BRR register, refer to Section 20.5.5: Baud rate generation .

Note: \( f_{CK} \) is 16 MHz.

20.5.1 USART character description

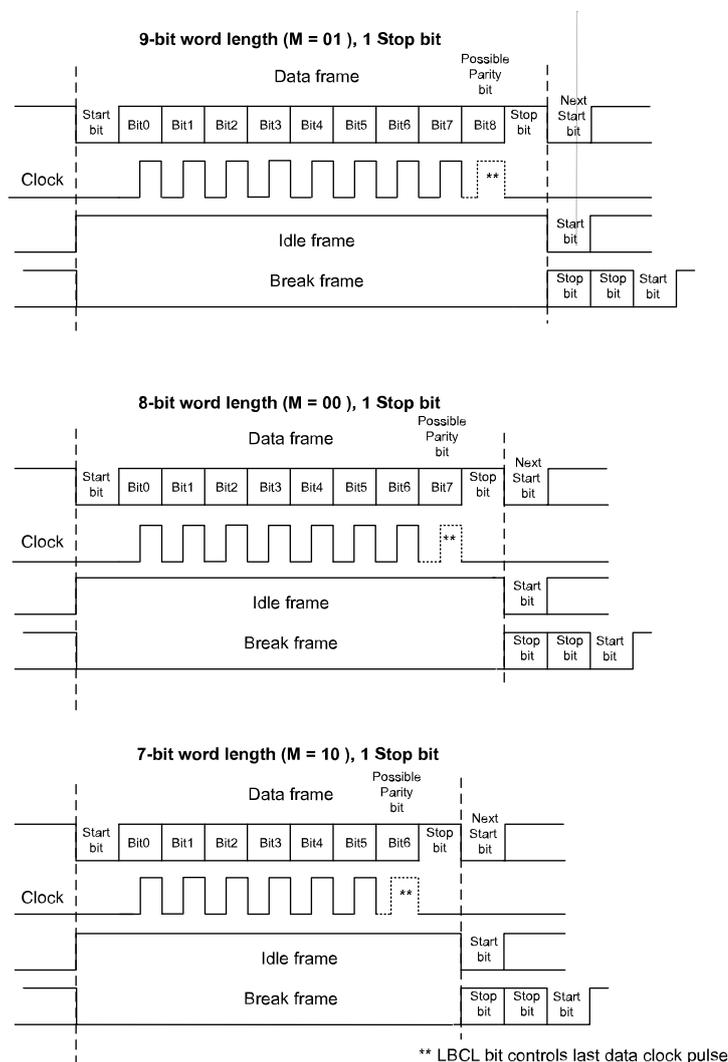

The word length can be selected as being either 7 or 8 or 9 bits by programming the M bits (M0: bit 12 and M1: bit 28) in the USART_CR1 register (see Figure 114. Word length programming ).

- • 7-bit character length: M [1:0] = 10

- • 8-bit character length: M [1:0] = 00

- • 9-bit character length: M [1:0] = 01

Note: In 7-bits data length mode, the smartcard mode, LIN master mode and auto baud rate (0x7F and 0x55 frames detection) are not supported.

In default configuration, the signal (TX or RX) is in low state during the start bit. It is in high state during the stop bit.

These values can be inverted, separately for each signal, through polarity configuration control.

An Idle character is interpreted as an entire frame of “1”s. (The number of “1”s includes the number of stop bits).

A Break character is interpreted on receiving “0”s for a frame period. At the end of the break frame, the transmitter inserts 2 stop bits.

Transmission and reception are driven by a common baud rate generator, the clock for each is generated when the enable bit is set respectively for the transmitter and receiver.

The details of each block is given below.

Figure 114. Word length programming

The diagram illustrates three word length configurations for the USART:

- 9-bit word length (M = 01), 1 Stop bit:

- Data frame: Start bit, Bit0 through Bit8, Possible Parity bit, Stop bit, followed by the Next Start bit.

- Clock: A square wave with a note that the last data clock pulse is controlled by the LBCL bit (**).

- Idle frame: A continuous high level followed by a Start bit.

- Break frame: A continuous low level followed by two Stop bits and a Start bit.

- 8-bit word length (M = 00), 1 Stop bit:

- Data frame: Start bit, Bit0 through Bit7, Possible Parity bit, Stop bit, followed by the Next Start bit.

- Clock: Similar to the 9-bit configuration with the LBCL bit note (**).

- Idle frame: Continuous high level followed by a Start bit.

- Break frame: Continuous low level followed by two Stop bits and a Start bit.

- 7-bit word length (M = 10), 1 Stop bit:

- Data frame: Start bit, Bit0 through Bit6, Possible Parity bit, Stop bit, followed by the Next Start bit.

- Clock: Similar to the other configurations with the LBCL bit note (**).

- Idle frame: Continuous high level followed by a Start bit.

- Break frame: Continuous low level followed by two Stop bits and a Start bit.

** LBCL bit controls last data clock pulse

20.5.2 FIFOs and thresholds

The USART can operate in FIFO mode, with the FIFO buffers having a depth of 16 bytes (8 bytes TX, 8 bytes RX).

The USART comes with a transmit FIFO (TXFIFO) and a receive FIFO (RXFIFO). The FIFO mode is enabled by setting the bit 29 FIFOEN in the USARTx_CR1 register.

The FIFO mode is supported only on UART, SPI and smartcard modes.

Being 9 bits the maximum data word length, the TXFIFO is 9-bits wide. However the RXFIFO is by default 12-bits wide. This is due to the fact that the receiver does not only put the data in the FIFO, but also the error flags associated to each character (Parity error, Noise error and Framing error flags).

Note: The received data is stored in the RXFIFO with its flags. But If you read RDR, you read just the data. The status flags are available in the USART_ISR register.

It is possible to define the TXFIFO and RXFIFO levels at which the Tx and RX interrupt are triggered. These thresholds are programmed through bit fields RXFTCFG and TXFTCFG in USARTx_CR3 control register.

In this case:

- • The receive interrupt is generated when the number of received data in the RXFIFO reaches the threshold programmed in the RXFTCFG bits fields

- • The transmit interrupt is generated when the number of empty locations in the TXFIFO reaches the threshold programmed in the TXFTCFG bit fields.

RXFIFO threshold

The RXFIFO threshold is configured using the RXFTCFG bits fields in the USARTx_CR3 register.

When the number of received data is equal to the programmed RXFTCFG, the flag RXFT in the USART_ISR register is set.

Having RXFT flag set means that there are RXFTCFG data received: 1 data in USARTx_RDR and (RXFTCFG - 1) data in the RXFIFO. So, when the RXFTCFG is programmed to «101», the RXFT flag is set when 8 data are received: 7 data in the RXFIFO and 1 data in the USARTx_RDR. Consequently, the 9 th received data do not set the overrun flag.

20.5.3 Transmitter

The transmitter can send data words of either 7 or 8 or 9 bits depending on the M bit status. The transmit enable bit (TE) must be set in order to activate the transmitter function. The data in the transmit shift register is output on the TX pin and the corresponding clock pulses are output on the SCLK pin.

Character transmission

During an USART transmission, data shifts out least significant bit first (default configuration) on the TX pin. In this mode, the USARTx_TDR register consists of a buffer (TDR) between the internal bus and the transmit shift register.

When FIFO mode is enabled, data written to the transmit data register USART_TDR, is queued in the TXFIFO.

Every character is preceded by a start bit which is a logic level low for one bit period. The character is terminated by a configurable number of stop bits.

The following stop bits are supported by USART: 0.5, 1, 1.5 and 2 stop bits.

Note: The TE bit must be set before writing the data to be transmitted to the USART_TDR. The TE bit should not be reset during transmission of data. Resetting the TE bit during the transmission corrupts the data on the TX pin as the baud rate counters get frozen. The current data being transmitted are lost. An idle frame is sent after the TE bit is enabled.

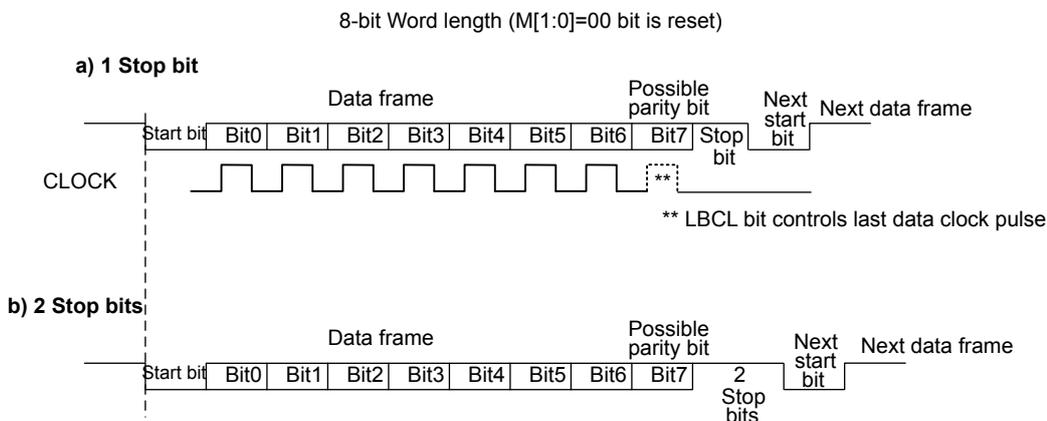

Configurable stop bits

The number of stop bits to be transmitted with every character can be programmed in control register 2, bits 13,12.

- • 1 stop bit: this is the default value of number of stop bits

- • 2 stop bits: this is supported by normal USART, single-wire and modem modes

- • 1.5 stop bits: to be used in smartcard mode.

An idle frame transmission includes the stop bits.

A break transmission is 10 low bits (when M[1:0] = 00) or 11 low bits (when M[1:0] = 01) or 9 low bits (when M[1:0] = 10) followed by 2 stop bits (see Figure 115. Configurable stop bits ). It is not possible to transmit long breaks (break of length greater than 9/10/11 low bits).

Figure 115. Configurable stop bits

8-bit Word length (M[1:0]=00 bit is reset)

a) 1 Stop bit

The diagram shows the sequence of bits for a data frame: Start bit, Bit0, Bit1, Bit2, Bit3, Bit4, Bit5, Bit6, Bit7, Possible parity bit, Stop bit, and the start bit of the next data frame. A CLOCK signal is shown with pulses corresponding to each bit. A note indicates that the LBCL bit controls the last data clock pulse.

b) 2 Stop bits

The diagram shows the sequence of bits for a data frame: Start bit, Bit0, Bit1, Bit2, Bit3, Bit4, Bit5, Bit6, Bit7, Possible parity bit, 2 Stop bits, and the start bit of the next data frame. A CLOCK signal is shown with pulses corresponding to each bit.

Character transmission procedure

- 1. Program the M bits in USART_CR1 to define the word length.

- 2. Select the desired baud rate using the USART_BRR register.

- 3. Program the number of stop bits in USART_CR2.

- 4. Enable the USART by writing the UE bit in USART_CR1 register to 1.

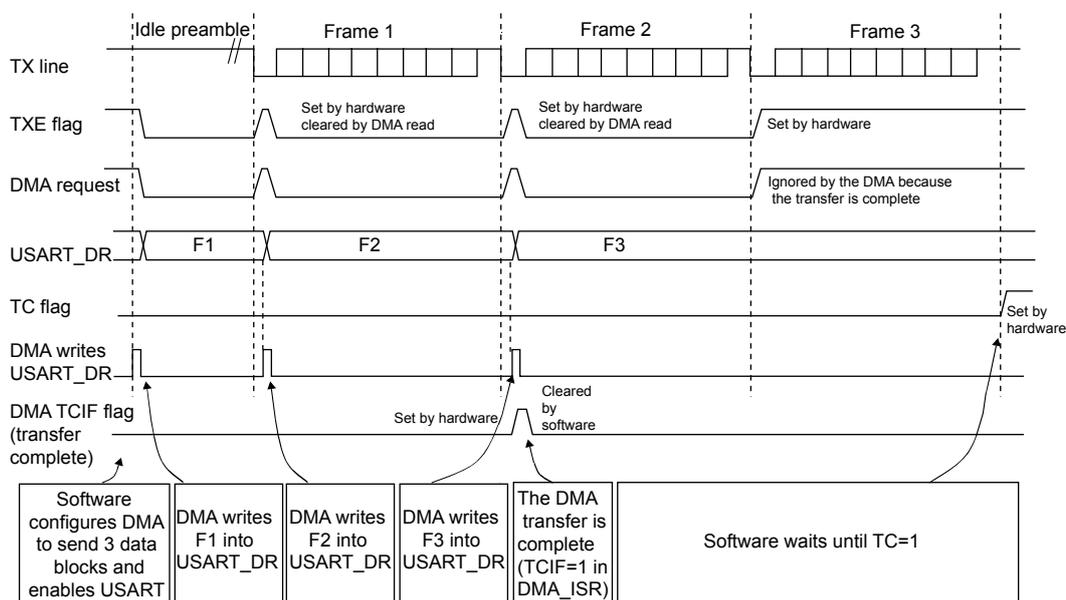

- 5. Select DMA enable (DMAT) in USART_CR3 if multi-buffer communication is to take place. Configure the DMA register as explained in multi-buffer communication.

- 6. Set the TE bit in USART_CR1 to send an idle frame as first transmission.

- 7. Write the data to send in the USART_TDR register. Repeat this for each data to be transmitted in case of single buffer.

- a. When FIFO mode is disabled, writing a data in the USART_TDR clears the TXE flag.

- b. When FIFO mode is enabled, writing a data in the USART_TDR adds one data to the TXFIFO and write operations in the USART_TDR are made when TXFNF flag is set. This flag remains set until the TXFIFO is full.

- 8. After writing the last data into the USART_TDR register, wait until TC=1.

- – When FIFO mode is disabled, this indicates that the transmission of the last frame is complete.

- – When FIFO mode is enabled, this indicates that both TXFIFO and shift register are empty.

Single byte communication

- • When FIFO mode is disabled:

clearing the TXE flag is always performed by a write to the transmit data register. The TXE flag is set by hardware and it indicates:

- • the data has been moved from the USARTx_TDR register to the shift register and the data transmission has started

- • the USARTx_TDR register is empty

- • the next data can be written in the USARTx_TDR register without overwriting the previous data.

This flag generates an interrupt if the TXEIE bit is set.

When a transmission is taking place, a write instruction to the USARTx_TDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the USARTx_TDR register places the data in the shift register, the data transmission starts, and the TXE bit is set.

- • When FIFO mode is enabled, the TXFNF (TXFIFO not full) flag is set by hardware and it indicates:

- – the TXFIFO is not full

- – the USART_TDR register is empty

- – the next data can be written in the USART_TDR register without overwriting the previous data. When a transmission is taking place, a write operation to the USART_TDR register stores the data in the TXFIFO. Data are copied from the TXFIFO into the shift register at the end of the current transmission.

When the TXFIFO is not full, the TXFNF flag stays at 1 even after a write in USART_TDR . It is cleared when the TXFIFO is full.

This flag generates an interrupt if the TXFNFIE bit is set.

Alternatively, interrupts can be generated and data can be written into FIFO when the TXFIFO threshold is reached. In this case, the CPU can write a block of data defined by the programmed trigger level.

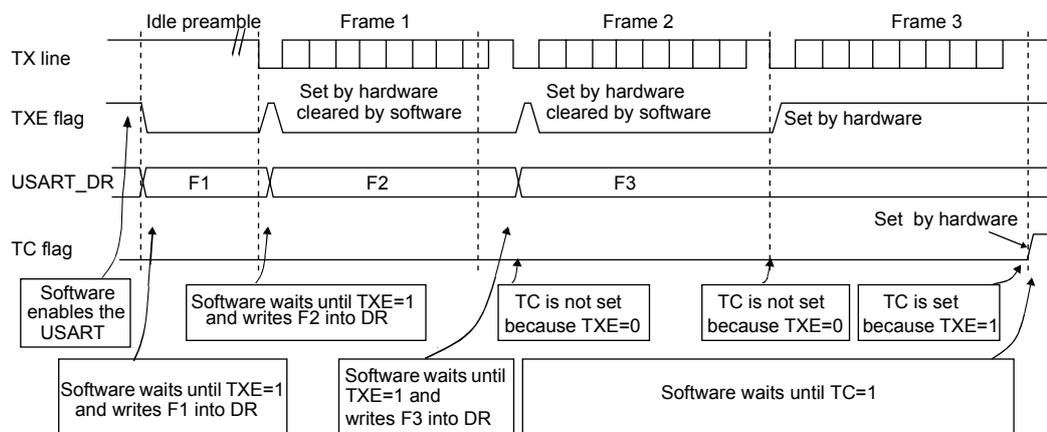

If a frame is transmitted (after the stop bit) and the TXE flag (TXFE in case of FIFO mode) is set, the TC flag goes high. An interrupt is generated if the TCIE bit is set in the USART_CR1 register.

After writing the last data in the USART_TDR register, it is mandatory to wait for TC=1 before disabling the USART or causing the microcontroller to enter the low-power mode (see Figure 116. TC/TXE behavior when transmitting ).

Figure 116. TC/TXE behavior when transmitting

The diagram illustrates the timing and control signals for transmitting three frames (Frame 1, Frame 2, Frame 3) after an idle preamble. The signals shown are:

- TX line: Shows the idle preamble followed by the transmission of Frame 1, Frame 2, and Frame 3.

- TXE flag:

- Initially set by hardware.

- After writing F1 to USART_DR, it is set by hardware and cleared by software.

- After writing F2 to USART_DR, it is set by hardware and cleared by software.

- After writing F3 to USART_DR, it is set by hardware and remains set until the transmission is complete.

- USART_DR: Shows the data words F1, F2, and F3 being written into the data register.

- TC flag:

- Initially set by hardware.

- After writing F1, it is not set because TXE=0.

- After writing F2, it is not set because TXE=0.

- After writing F3, it is set by hardware because TXE=1.

Software control flow:

- Software enables the USART.

- Software waits until TXE=1 and writes F1 into DR.

- Software waits until TXE=1 and writes F2 into DR.

- Software waits until TXE=1 and writes F3 into DR.

- Software waits until TC=1.

Note: When FIFO management is enabled, the TXFNF flag is used for data transmission.

Break characters

Setting the SBKRQ bit transmits a break character. The break frame length depends on the M bit (see Figure 114. Word length programming).

If a '1' is written to the SBKRQ bit, a break character is sent on the TX line after completing the current character transmission. The SBKF bit is set by the write operation and it is reset by hardware when the break character is completed (during the stop bits after the break character). The USART inserts a logic 1 signal (STOP) for the duration of 2 bits at the end of the break frame to guarantee the recognition of the start bit of the next frame.

When the SBKRQ bit is set, the break character is sent at the end of the current transmission.

When FIFO mode is enabled, sending the break character has priority on sending data even if the TXFIFO is full.

Idle characters

Setting the TE bit drives the USART to send an idle frame before the first data frame.

20.5.4 Receiver

The USART can receive data words of either 7 or 8 or 9 bits depending on the M bits in the USART_CR1 register.

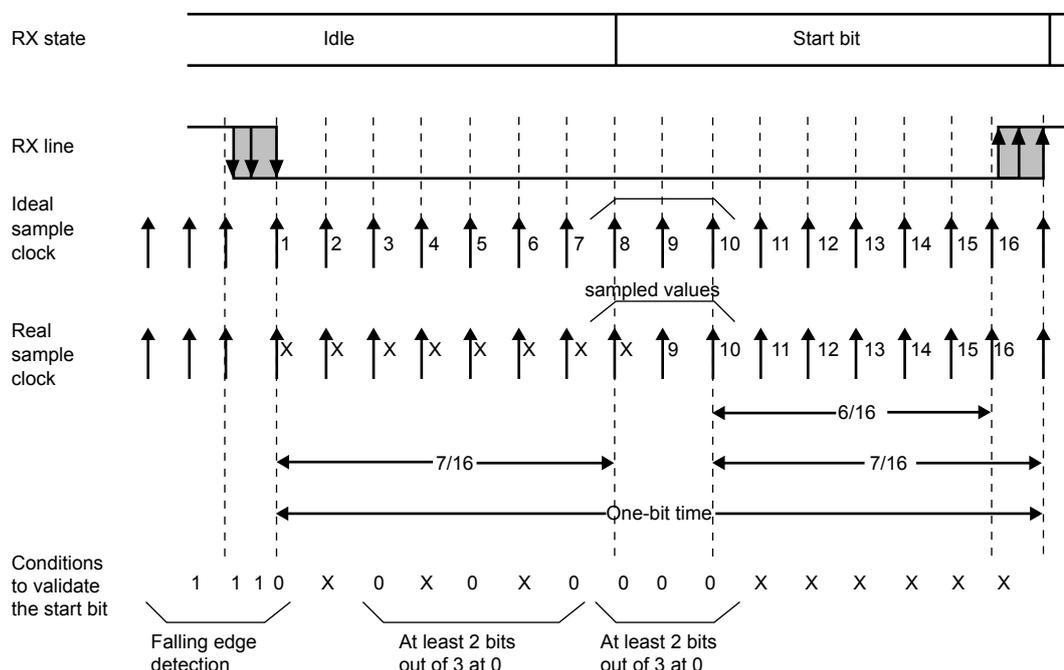

Start bit detection

The start bit detection sequence is the same when oversampling by 16 or by 8. In the USART, the start bit is detected when a specific sequence of samples is recognized. This sequence is: 1 1 1 0 X 0 X 0X 0X 0 X 0X 0.

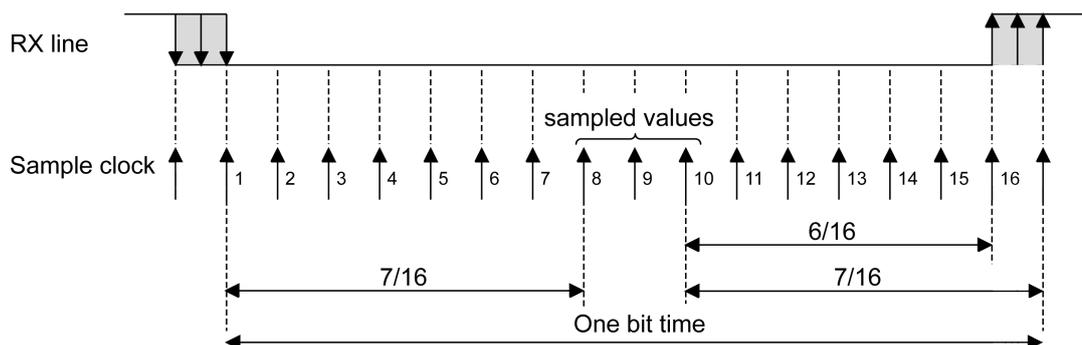

Figure 117. Start bit detection when oversampling by 16 or 8

The diagram illustrates the start bit detection process. The RX line transitions from Idle (high) to Start bit (low). Ideal sample clock has 16 pulses per bit period. Real sample clock has pulses at 1/16 intervals. Sampling points are marked at 3rd, 5th, 7th, 8th, 9th, and 10th pulses. Conditions to validate the start bit are shown as a sequence of 1s and 0s with annotations for falling edge detection and 'At least 2 bits out of 3 at 0'.

| Conditions to validate the start bit | 1 | 1 | 1 | 0 | X | 0 | X | 0 | X | 0 | 0 | 0 | X | X | X | X | X | X | |

| Falling edge detection | At least 2 bits out of 3 at 0 | At least 2 bits out of 3 at 0 | |||||||||||||||||

Note: If the sequence is not complete, the start bit detection aborts and the receiver returns to the idle state (no flag is set), where it waits for a falling edge.

The start bit is confirmed (RXNE flag set, interrupt generated if RXNEIE=1 (RXFNE flag set, interrupt generated if RXFNEIE=1 if FIFO mode is enabled) if the 3 sampled bits are at 0 (first sampling on the 3rd, 5th and 7th bits finds the 3 bits at 0 and second sampling on the 8th, 9th and 10th bits also finds the 3 bits at 0).

The start bit is validated but the NF noise flag is set if,

- 1. for both samplings, 2 out of the 3 sampled bits are at 0 (sampling on the 3rd, 5th and 7th bits and sampling on the 8th, 9th and 10th bits)

or - 2. for one of the samplings (sampling on the 3rd, 5th and 7th bits or sampling on the 8th, 9th and 10th bits), 2 out of the 3 bits are found at 0.

If neither conditions, 1 or 2, are met, the start detection aborts and the receiver returns to the idle state (no flag is set).

Character reception

During a USART reception, data shifts in least significant bit first (default configuration) through the RX pin.

Character reception procedure

- 1. Program the M bits in USART_CR1 to define the word length

- 2. Select the desired baud rate using the baud rate register USART_BRR

- 3. Program the number of stop bits in USART_CR2

- 4. Enable the USART by writing the UE bit in USART_CR1 register to 1

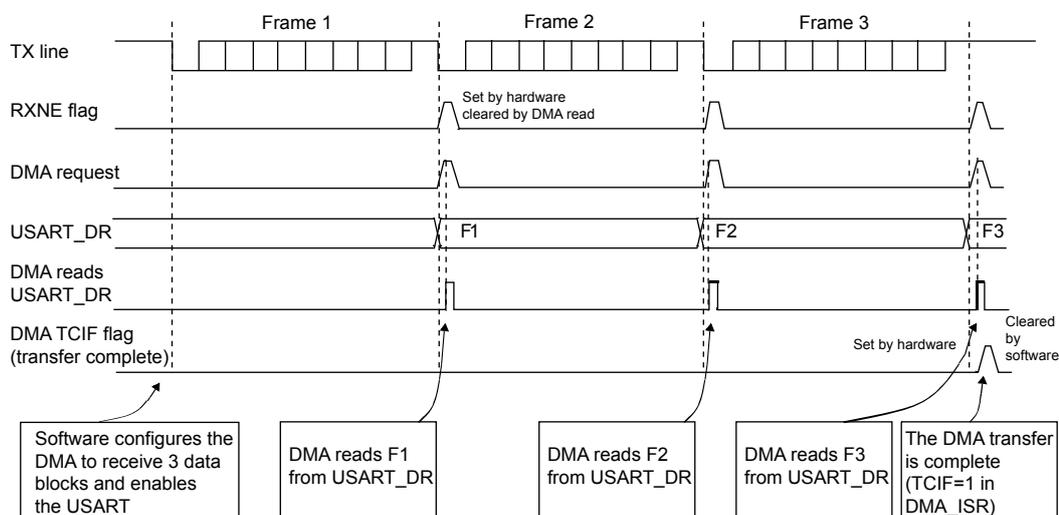

- 5. Select DMA enable (DMAR) in USART_CR3 if multi-buffer communication is to take place. Configure the DMA register as explained in multi-buffer communication

- 6. Set the RE bit USART_CR1. This enables the receiver which begins searching for a start bit.

When a character is received

- • When FIFO mode is disabled, the RXNE bit is set indicating that the content of the shift register is transferred to the RDR. In other words, data has been received and can be read (as well as its associated error flags)

- • When FIFO is enabled, the RXFNE bit is set indicating that the RXFIFO is not empty. A read of the USART_RDR gets the oldest entry in the RXFIFO. When a data is received, it is stored in the RXFIFO, with error bits associated with that data

- • An interrupt is generated if the RXNEIE (RXFNEIE in case of FIFO mode) bit is set

- • The error flags can be set if a frame error, noise, parity or an overrun error has been detected during reception

- • In multi-buffer communication:

- – When FIFO mode is disabled, the RXNE is set after every byte received and is cleared by the DMA read of the receive data register.

- – When FIFO mode is enabled, the RXFNE is set when the RXFIFO is not empty. After every DMA request, a data is retrieved from the RXFIFO. DMA request is triggered by RXFIFO if not empty, i.e. there is data in the RXFIFO to be read.

- • In single buffer mode,

- – When FIFO mode is disabled: clearing the RXNE flag is performed by a software read to the USARTx_RDR register. The RXNE flag can also be cleared by writing 1 to the RXFRQ in the USARTx_RQR register. The RXNE flag must be cleared before the end of the reception of the next character to avoid an overrun error.

- – When FIFO mode is enabled, the RXFNE is set when the RXFIFO is not empty. After every read of the USART_RDR, a data is retrieved from the RXFIFO. When the RXFIFO is empty, the RXFNE flag is cleared. The RXFNE flag can also be cleared by writing 1 to the RXFRQ in the USART_RQR register. When the RXFIFO is full, the first entry in the RXFIFO must be read before the end of the reception of the next character to avoid an overrun error. The RXFNE flag generates an interrupt if the RXFNEIE bit is set. Alternatively, interrupts can be generated and data can be read from RXFIFO when the RXFIFO threshold is reached. In this case, the CPU can read a block of data defined by the programmed threshold.

Break character

When a break character is received, the USART handles it as a framing error.

Idle character

When an idle frame is detected, there is the same procedure as for a received data character plus an interrupt if the IDLEIE bit is set.

Overrun error

- • FIFO mode disabled:

An overrun error occurs when a character is received when RXNE has not been reset. Data cannot be transferred from the shift register to the RDR register until the RXNE bit is cleared. The RXNE flag is set after every byte received. An overrun error occurs if RXNE flag is set when the next data is received or the previous DMA request has not been serviced. When an overrun error occurs:

- 1. The ORE bit is set.

- 2. The RDR content is not lost. The previous data is available when a read to USARTx_RDR is performed.

- 3. The shift register is overwritten. After that point, any data received during overrun is lost.

- 4. An interrupt is generated if either the RXNEIE bit is set or EIE bit is set.

- • FIFO mode enabled

An overrun error occurs when the shift register is ready to be transferred when the receive FIFO is full. Data can not be transferred from the shift register to the USARTx_RDR register until there is one free location in the RXFIFO. The RXFNE flag is set when the RXFIFO is not empty. An overrun error occurs if the RXFIFO is full and the shift register is ready to be transferred. When an overrun error occurs:

- 1. The ORE bit is set.

- 2. The first entry in the RXFIFO is not lost. It is available when a read to USART_RDR is performed.

- 3. The shift register is overwritten. After that point, any data received during overrun is lost.

- 4. An interrupt is generated if either the RXFNEIE bit is set or EIE bit is set.

The ORE bit is reset by setting the ORECF bit in the USARTx_ICR register.

Note: The ORE bit, when set, indicates that at least 1 data has been lost. When the FIFO mode is disabled, there are two possibilities

- • if RXNE=1, then the last valid data is stored in the receive register RDR and can be read

- • if RXNE=0, then it means that the last valid data has already been read and thus there is nothing to be read in the RDR. This case can occur when the last valid data is read in the RDR at the same time as the new (and lost) data is received.

Selecting the clock source and the proper oversampling method

The clock source frequency is \( f_{CK} \) (16 MHz).

The \( f_{CK} \) can be divided by a programmable factor in the USARTx_PRESC register.

Figure 118. usart_ker_ck clock divider block diagram

![Block diagram of the usart_ker_ck clock divider. An input signal 'usart_ker_ck' enters a large grey box. Inside the box, the signal first passes through a block labeled 'USARTx_PRESC[3:0]'. The output of this block, labeled 'usart_ker_ck_pres', then enters another block labeled 'USARTx_BRR register and oversampling'.](/RM0530-STM32WB07xC-06xC/1f529e8f3a32cdc238e3dc7e4770d5da_img.jpg)

MSv40855V1

The communication speed range (specially the maximum communication speed) is also determined by the clock source.

The receiver implements different user-configurable oversampling techniques (except in synchronous mode) for data recovery by discriminating between valid incoming data and noise. This allows a trade off between the maximum communication speed and noise/clock inaccuracy immunity.

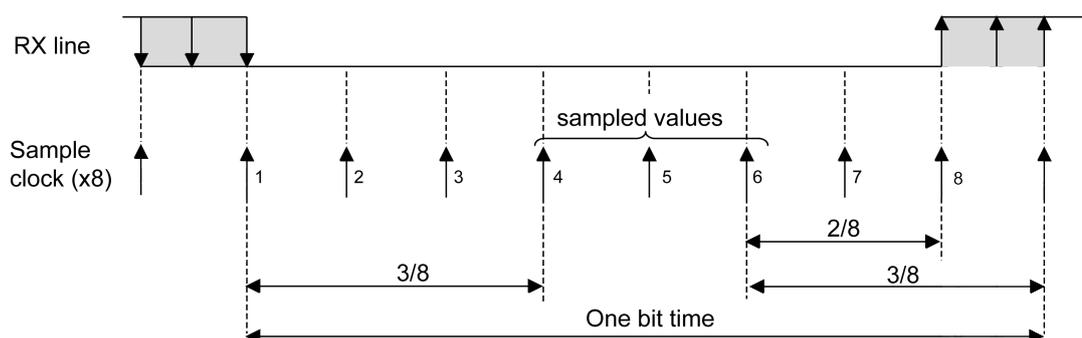

The oversampling method can be selected by programming the OVER8 bit in the USART_CR1 register and can be either 16 or 8 times the baud rate clock (Figure 119. Data sampling when oversampling by 16 and Figure 120. Data sampling when oversampling by 8).

Depending on the application:

- • Select oversampling by 8 (OVER8=1) to achieve higher speed (up to \( f_{CKPRES}/8 \) ). In this case the maximum receiver tolerance to clock deviation is reduced (refer to Section 20.5.6: Tolerance of the USART receiver to clock deviation).

- • Select oversampling by 16 (OVER8=0) to increase the tolerance of the receiver to clock deviations. In this case, the maximum speed is limited to maximum \( f_{CKPRES}/16 \) .

where \( f_{CKPRES} \) is the USART input clock divided by a prescaler.

Programming the ONEBIT bit in the USART_CR3 register selects the method used to evaluate the logic level. There are two options:

- • The majority vote of the three samples in the center of the received bit. In this case, when the 3 samples used for the majority vote are not equal, the NF bit is set

- • A single sample in the center of the received bit

Depending on the application:- – select the three samples' majority vote method (ONEBIT=0) when operating in a noisy environment and reject the data when a noise is detected (refer to Figure 68. Deadtime waveforms with delay greater than the negative pulse because this indicates that a glitch occurred during the sampling).

- – select the single sample method (ONEBIT=1) when the line is noise-free to increase the receiver's tolerance to clock deviations (see Section 20.5.6: Tolerance of the USART receiver to clock deviation). In this case the NF bit is never set.

When noise is detected in a frame:

- • The NF bit is set at the rising edge of the RXNE bit (RXFNE in case of FIFO mode enabled)

- • The invalid data is transferred from the Shift register to the USART_RDR register

- No interrupt is generated in case of single byte communication. However this bit rises at the same time as the RXNE bit (RXFNE in case of FIFO mode enabled) which itself generates an interrupt. In case of multi-buffer communication an interrupt is issued if the EIE bit is set in the USART_CR3 register.

The NF bit is reset by setting NFCF bit in the ICR register.

Note: Noise error is not supported in SPI mode.

Note: Oversampling by 8 is not available in the smartcard, IrDA and LIN modes. In those modes, the OVER8 bit is forced to '0' by hardware.

Figure 119. Data sampling when oversampling by 16

Figure 120. Data sampling when oversampling by 8

Table 61. Noise detection from sampled data

| Sampled value | NE status | Received bit value |

|---|---|---|

| 000 | 0 | 0 |

| 001 | 1 | 0 |

| 010 | 1 | 0 |

| 011 | 1 | 1 |

| 100 | 1 | 0 |

| 101 | 1 | 1 |

| 110 | 1 | 1 |

| 111 | 0 | 1 |

Framing error

A framing error is detected when the stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

When the framing error is detected:

- The FE bit is set by hardware

- The invalid data is transferred from the shift register to the USART_RDR register ( RXFIFO in case FIFO mode is enabled)

- • No interrupt is generated in case of single byte communication. However this bit rises at the same time as the RXNE bit (RXFNE in case FIFO mode is enabled) which itself generates an interrupt. In case of multi-buffer communication an interrupt is issued if the EIE bit is set in the USART_CR3 register.

The FE bit is reset by writing 1 to the FECF in the USART_ICR register.

Note: Framing error is not supported in SPI mode.

Configurable stop bits during reception

The number of stop bits to be received can be configured through the control bits of control register 2 - it can be either 1 or 2 in normal mode and 0.5 or 1.5 in smartcard mode.

- • 0.5 stop bit (reception in smartcard mode): No sampling is done for 0.5 stop bit. As a consequence, no framing error and no break frame can be detected when 0.5 stop bit is selected.

- • 1 stop bit: Sampling for 1 stop bit is done on the 8 th , 9 th and 10 th samples.

- • 1.5 stop bits (smartcard mode): When transmitting in smartcard mode, the device must check that the data is correctly sent. Thus the receiver block must be enabled (RE=1 in the USART_CR1 register) and the stop bit is checked to test if the smartcard has detected a parity error. In the event of a parity error, the smartcard forces the data signal low during the sampling - NACK signal -, which is flagged as a framing error. Then, the FE flag is set with the RXNE (RXFNE in case FIFO mode is enabled) at the end of the 1.5 stop bit. Sampling for 1.5 stop bits is done on the 16 th , 17 th and 18 th samples (1 baud clock period after the beginning of the stop bit). The 1.5 stop bit can be decomposed into 2 parts: one 0.5 baud clock period during which nothing happens, followed by 1 normal stop bit period during which sampling occurs halfway through. Refer to Section 20.5.14: Receiver timeout for more details.

- • 2 stop bits: Sampling for 2 stop bits is done on the 8 th , 9 th and 10 th samples of the first stop bit. If a framing error is detected during the first stop bit the framing error flag is set. The second stop bit is not checked for framing error. The RXNE (RXFNE in case FIFO mode is enabled) flag is set at the end of the first stop bit.

20.5.5 Baud rate generation

The baud rate for the receiver and transmitter (Rx and Tx) are both set to the same value as programmed in the USART_BRR register.

The equation below is baud rate for standard USART (SPI mode included) (OVER8= 0 or 1).

In case of oversampling by 16, the equation is:

In case of oversampling by 8, the equation is:

The equation below is baud rate in Smartcard, LIN and IrDA modes (OVER8= 0):

\( f_{CKPRES} \) is the USART clock which is the USART input clock divided by a prescaler configured in the USART_PRES register.

USARTDIV is an unsigned fixed point number that is coded on the USART_BRR register.

- • When OVER8 = 0, BRR = USARTDIV

- • When OVER8 = 1

- – BRR[2:0] = USARTDIV[3:0] shifted 1 bit to the right

- – BRR[3] must be kept cleared

- – BRR[15:4] = USARTDIV[15:4]

Note: The baud counters are updated to the new value in the baud registers after a write operation to USART_BRR. Hence the baud rate register value should not be changed during communication. In case of oversampling by 16 and 8, USARTDIV must be greater than or equal to 16d.

How to derive USARTDIV from USART_BRR register values

Example 1

To obtain 9600 baud with \( f_{CKPRES} = 8 \) MHz.

- • In case of oversampling by 16:

\( USARTDIV = 8\,000\,000/9600 \)

\( BRR = USARTDIV = 833d = 0341h \) - • In case of oversampling by 8:

\( USARTDIV = 2 * 8\,000\,000/9600 \)

\( USARTDIV = 1666,66 \) ( \( 1667d = 683h \) )

\( BRR[3:0] = 3h \gg 1 = 1h \)

\( BRR = 0x681 \)

20.5.6 Tolerance of the USART receiver to clock deviation

The asynchronous receiver of the USART works correctly only if the total clock system deviation is less than the tolerance of the USART receiver. The causes which contribute to the total deviation are:

- • DTRA: Deviation due to the transmitter error (which also includes the deviation of the transmitter's local oscillator)

- • DQUANT: Error due to the baud rate quantization of the receiver

- • DREC: Deviation of the receiver local oscillator

- • DTCL: Deviation due to the transmission line (generally due to the transceivers which can introduce an asymmetry between the low-to-high transition timing and the high-to-low transition timing)

- \( DTRA + DQUANT + DREC + DTCL < USART receiver tolerance. \)

The USART receiver can receive data correctly at up to the maximum tolerated deviation specified in Table 62. Tolerance of the USART receiver when BRR [3:0] = 0000 (high-density devices) and Table 63. Tolerance of the USART receiver when BRR[3:0] is different from 0000 (high-density devices) , depending on the following choices:

- • 9-,10- or 11-bit character length defined by the M bits in the USART_CR1 register

- • Oversampling by 8 or 16 defined by the OVER8 bit in the USART_CR1 register

- • Bits BRR[3:0] of USART_BRR register are equal to or different from 0000

- • Use of 1 bit or 3 bits to sample the data, depending on the value of the ONEBIT bit in the USART_CR3 register.

Table 62. Tolerance of the USART receiver when BRR [3:0] = 0000 (high-density devices)

| M bits | OVER8 bit = 0 | OVER8 bit = 1 | ||

|---|---|---|---|---|

| ONEBIT=0 | ONEBIT=1 | ONEBIT=0 | ONEBIT=1 | |

| 00 | 3.75% | 4.375% | 2.50% | 3.75% |

| 01 | 3.41% | 3.97% | 2.27% | 3.41% |

| 10 | 4.16 | 4.86 | 2.77 | 4.16 |

Table 63. Tolerance of the USART receiver when BRR[3:0] is different from 0000 (high-density devices)

| M bits | OVER8 bit = 0 | OVER8 bit = 1 | ||

|---|---|---|---|---|

| ONEBIT=0 | ONEBIT=1 | ONEBIT=0 | ONEBIT=1 | |

| 00 | 3.33% | 3.88% | 2% | 3% |

| 01 | 3.03% | 3.53% | 1.82% | 2.73% |

| 10 | 3.7 | 4.31 | 2.22 | 3.33 |

Note: The data specified in Table 62. Tolerance of the USART receiver when BRR [3:0] = 0000 (high-density devices) and Table 63. Tolerance of the USART receiver when BRR[3:0] is different from 0000 (high-density devices) may slightly differ in the special case when the received frames contain some Idle frames of exactly 10-bit times when M bits = 00 (11-bit times when M = 01 or 9-bit times when M = 10).

20.5.7 Auto baud rate detection

The USART is able to detect and automatically set the USART_BRR register value based on the reception of one character. Automatic baud rate detection is useful under two circumstances:

- • The communication speed of the system is not known in advance

- • The system is using a relatively low accuracy clock source and this mechanism allows the correct baud rate to be obtained without measuring the clock deviation.

The clock source frequency must be compatible with the expected communication speed (when oversampling by 16, the baud rate is between \( f_{CK}/65535 \) and \( f_{CK}/16 \) . When oversampling by 8, the baud rate is between \( f_{CK}/65535 \) and \( f_{CK}/8 \) .

Before activating the auto baud rate detection, the auto baud rate detection mode must be chosen. There are four modes based on different character patterns.

The modes can be chosen through the ABRMOD[1:0] field in the USART_CR2 register. In these auto baud rate modes, the baud rate is measured several times during the synchronization data reception and each measurement is compared to the previous one.

These modes are:

- •

Mode 0:

Any character starting with a bit at 1.

In this case the USART measures the duration of the start bit (falling edge to rising edge). - •

Mode 1:

Any character starting with a 10xx bit pattern.

In this case, the USART measures the duration of the start and of the 1 st data bit. The measurement is done falling edge to falling edge, ensuring better accuracy in the case of slow signal slopes. - •

Mode 2:

A 0x7F character frame (it may be a 0x7F character in LSB first mode or a 0xFE in MSB first mode).

In this case, the baud rate is updated first at the end of the start bit (BRs), then at the end of bit 6 (based on the measurement done from falling edge to falling edge: BR6). Bit0 to Bit6 are sampled at BRs while further bits of the character are sampled at BR6. - •

Mode 3:

A 0x55 character frame.

In this case, the baud rate is updated first at the end of the start bit (BRs), then at the end of bit0 (based on the measurement done from falling edge to falling edge: BR0), and finally at the end of bit6 (BR6). Bit0 is sampled at BRs, Bit1 to Bit6 are sampled at BR0, and further bits of the character are sampled at BR6. In parallel, another check is performed for each intermediate transition of RX line. An error is generated if the transitions on RX are not sufficiently synchronized with the receiver (the receiver being based on the baud rate calculated on bit 0).

Prior to activating auto baud rate detection, the USART_BRR register must be initialized by writing a non-zero baud rate value.

The automatic baud rate detection is activated by setting the ABREN bit in the USART_CR2 register. The USART then waits for the first character on the RX line. The auto baud rate operation completion is indicated by the setting of the ABRF flag in the USART_ISR register. If the line is noisy, the correct baud rate detection cannot be guaranteed. In this case the BRR value may be corrupted and the ABRE error flag is set. This also happens if the communication speed is not compatible with the automatic baud rate detection range (bit duration not between 16 and 65536 clock periods (oversampling by 16) and not between 8 and 65536 clock periods (oversampling by 8)).

The auto baud rate detection can be re-launched later by resetting the ABRF flag (by writing a 0).

When FIFO management is disabled, in case of auto baud rate error, the ABRE flag is set with RXNE and FE.

When FIFO management is enabled, in case of auto baud rate error, the ABRE flag is set with RXFNE and FE.

In case FIFO mode is enabled, the auto baud rate detection should be made using the data on the first RXFIFO location. So, prior to launching the auto baud rate detection, the user should make sure that the RXFIFO is empty using the RXFNE flag in the USARTx_ISR register.

Note: The BRR value may be corrupted if the USART is disabled (UE=0) during an auto baud rate operation.

20.5.8 Multiprocessor communication

It is possible to perform multiprocessor communication with the USART (with several USARTs connected in a network). For instance one of the USARTs can be the master, its TX output connected to the RX inputs of the other USARTs. The others are slaves, their respective TX outputs are logically ANDed together and connected to the RX input of the master.

In multiprocessor configurations it is often desirable that only the intended message recipients should actively receive the full message contents, thus reducing redundant USART service overhead for all non addressed receivers.

The non addressed devices may be placed in mute mode by means of the muting function. In order to use the mute mode feature, the MME bit must be set in the USARTx_CR1 register.

Note: When FIFO management is enabled and MME is already set, MME bit must not be cleared and then set again quickly (within two UCLK cycles) otherwise mute mode might remain active.

In mute mode:

- • None of the reception status bits can be set

- • All the receive interrupts are inhibited

- • The RWU bit in USART_ISR register is set to 1. RWU can be controlled automatically by hardware or by software, through the MMRQ bit in the USART_RQR register, under certain conditions.

The USART can enter or exit from mute mode using one of two methods, depending on the WAKE bit in the USART_CR1 register:

- • Idle Line detection if the WAKE bit is reset

- • Address Mark detection if the WAKE bit is set.

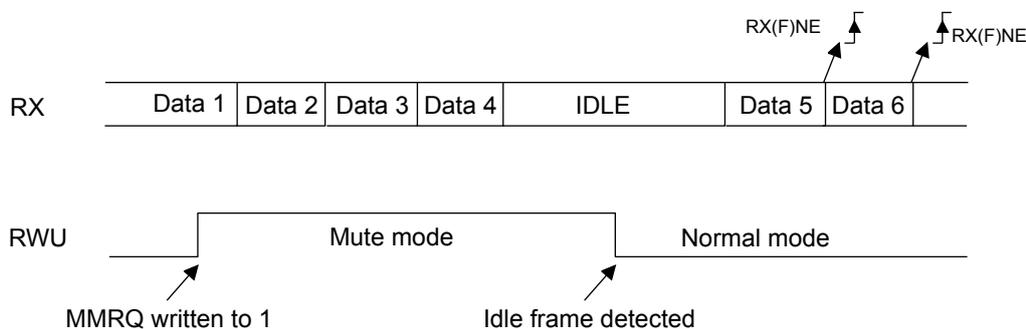

Idle line detection (WAKE=0)

The USART enters mute mode when the MMRQ bit is written to 1 and the RWU is automatically set. It wakes up when an idle frame is detected. Then the RWU bit is cleared by hardware but the IDLE bit is not set in the USART_ISR register. An example of mute mode behavior using Idle line detection is given in Figure 121. Mute mode using Idle line detection.

Figure 121. Mute mode using Idle line detection

The diagram illustrates the relationship between received data and the USART's mute mode. The top part shows a sequence of data frames: Data 1, Data 2, Data 3, Data 4, an IDLE frame, Data 5, and Data 6. The RX(F)NE flag is indicated by upward arrows after the reception of Data 4 and Data 6. The bottom part shows the RWU (Receiver Wake-Up) signal. When 'MMRQ written to 1' occurs, the RWU signal transitions to 'Mute mode' (high). It remains high until an 'Idle frame detected' event occurs, at which point it transitions back to 'Normal mode' (low).

Note: If the MMRQ is set while the IDLE character has already elapsed, mute mode is not entered (RWU is not set).

Note: If the USART is activated while the line is IDLE, the idle state is detected after the duration of one IDLE frame (not only after the reception of one character frame).

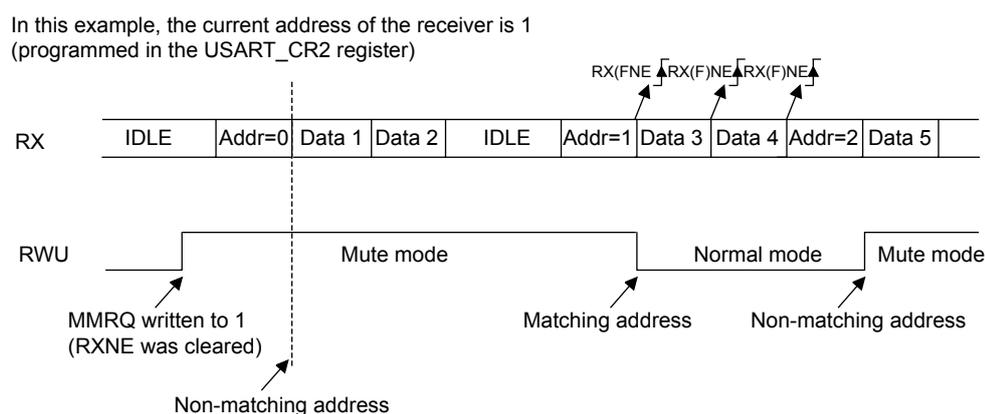

4-bit/7-bit address mark detection (WAKE=1)

In this mode, bytes are recognized as addresses if their MSB is a '1' otherwise they are considered as data. In an address byte, the address of the targeted receiver is put in the 4 or 7 LSBs. The choice of 7 or 4 bit address detection is done using the ADDM7 bit. This 4-bit/7-bit word is compared by the receiver with its own address which is programmed in the ADD bits in the USART_CR2 register.

Note: In 7-bit and 9-bit data modes, address detection is done on 6-bit and 8-bit addresses (ADD[5:0] and ADD[7:0]) respectively.

The USART enters mute mode when an address character is received which does not match its programmed address. In this case, the RWU bit is set by hardware. The RXNE flag is not set for this address byte and no interrupt or DMA request is issued when the USART enters mute mode. When FIFO management is enabled, the software should ensure that there is at least one empty location in the RXFIFO before entering mute mode.

The USART also enters mute mode when the MMRQ bit is written to 1. The RWU bit is also automatically set in this case. The USART exits from mute mode when an address character is received which matches the programmed address. Then the RWU bit is cleared and subsequent bytes are received normally. The RXNE/RXFNE bit is set for the address character since the RWU bit has been cleared.

Note: When FIFO management is enabled, when MMRQ is set while the receiver is sampling the last bit of data, these data maybe be received before entering mute mode.

An example of mute mode behavior using address mark detection is given in Figure 122. Mute mode using address mark detection.

Figure 122. Mute mode using address mark detection

In this example, the current address of the receiver is 1 (programmed in the USART_CR2 register)

The diagram illustrates the RX and RWU signals over time. The RX signal shows a sequence of IDLE, Addr=0, Data 1, Data 2, IDLE, Addr=1, Data 3, Data 4, Addr=2, Data 5. The RWU signal shows Mute mode and Normal mode transitions. Mute mode starts when MMRQ is written to 1 (RXNE was cleared) and ends when a matching address (Addr=1) is received. Normal mode resumes after Addr=1 and ends when a non-matching address (Addr=2) is received, returning to Mute mode. RX(FNE) flags are shown for Addr=1, Data 3, and Data 4.

20.5.9 Modbus communication

The USART offers basic support for the implementation of Modbus/RTU and Modbus/ASCII protocols. Modbus/RTU is a half-duplex, block transfer protocol. The control part of the protocol (address recognition, block integrity control and command interpretation) must be implemented in software.

The USART offers basic support for the end of the block detection, without software overhead or other resources.

Modbus/RTU

In this mode, the end of one block is recognized by a “silence” (idle line) for more than 2 character times. This function is implemented through the programmable timeout function.

The timeout function and interrupt must be activated, through the RTOEN bit in the USART_CR2 register and the RTOIE in the USART_CR1 register. The value corresponding to a timeout of 2 character times (for example 22 x bit time) must be programmed in the RTO register. When the receive line is idle for this duration, after the last stop bit is received, an interrupt is generated, informing the software that the current block reception is completed.

Modbus/ASCII

In this mode, the end of a block is recognized by a specific (CR/LF) character sequence. The USART manages this mechanism using the character match function. By programming the LF ASCII code in the ADD[7:0] field and by activating the character match interrupt (CMIE=1), the software is informed when an LF has been received and can check the CR/LF in the DMA buffer.

20.5.10 Parity control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the USART_CR1 register. Depending on the frame length defined by the M bits, the possible USART frame formats are as listed in Table 64. Frame formats.

Table 64. Frame formats

| M bits | PCE bit | USART frame (1) |

|---|---|---|

| 00 | 0 | | SB | 8-bit data | STB | |

| 00 | 1 | | SB | 7-bit data | PB | STB | |

| 01 | 0 | | SB | 9-bit data | STB | |

| M bits | PCE bit | USART frame (1) |

|---|---|---|

| 01 | 1 | | SB | 8-bit data PB | STB | |

| 10 | 0 | | SB | 7-bit data | STB | |

| 10 | 1 | | SB | 6-bit data | PB | STB | |

1. Legends: SB: start bit, STB: stop bit, PB: parity bit. In the data register, the PB is always taking the MSB position (8 th or 7 th , depending on the M bit value).

Even parity

The parity bit is calculated to obtain an even number of “1s” inside the frame of the 6, 7 or 8 LSB bits (depending on M bit values) and the parity bit.

As an example, if data=00110101, and 4 bits are set, then the parity bit is 0 if even parity is selected (PS bit in USART_CR1 = 0).

Odd parity

The parity bit is calculated to obtain an odd number of “1s” inside the frame made of the 6, 7 or 8 LSB bits (depending on M bit values) and the parity bit.

As an example, if data=00110101 and 4 bits set, then the parity bit is 1 if odd parity is selected (PS bit in USART_CR1 = 1).

Parity checking in reception

If the parity check fails, the PE flag is set in the USART_ISR register and an interrupt is generated if PEIE is set in the USART_CR1 register. The PE flag is cleared by software writing 1 to the PECF in the USART_ICR register.

Parity generation in transmission

If the PCE bit is set in USART_CR1, then the MSB bit of the data written in the data register is transmitted but is changed by the parity bit (even number of “1s” if even parity is selected (PS=0) or an odd number of “1s” if odd parity is selected (PS=1)).

20.5.11 LIN (local interconnection network) mode

This section is relevant only when LIN mode is supported. Refer to Section 20.4: USART implementation .

The LIN mode is selected by setting the LINEN bit in the USART_CR2 register. In LIN mode, the following bits must be kept cleared:

- • CLKEN in the USART_CR2 register

- • STOP[1:0], SCEN, HDSEL and IREN in the USART_CR3 register.

LIN transmission

The procedure explained in Section 20.5.2: FIFOs and thresholds has to be applied for LIN Master transmission. It must be the same as for normal USART transmission with the following differences:

- • Clear the M bit to configure 8-bit word length

- • Set the LINEN bit to enter LIN mode. In this case, setting the SBKRQ bit sends 13'0 bits as a break character. Then 2 bits of value '1' are sent to allow the next start detection.

LIN reception

When LIN mode is enabled, the break detection circuit is activated. The detection is totally independent from the normal USART receiver. A break can be detected whenever it occurs, during idle state or during a frame.

When the receiver is enabled (RE=1 in USART_CR1), the circuit looks at the RX input for a start signal. The method to detect start bits is the same when searching break characters or data. After a start bit has been detected, the circuit samples the next bits exactly like for the data (on the 8 th , 9 th and 10 th samples). If 10 (when the LBDL = 0 in USART_CR2) or 11 (when LBDL=1 in USART_CR2) consecutive bits are detected as '0', and are followed by a delimiter character, the LBDF flag is set in USART_ISR. If the LBDIE bit=1, an interrupt is generated. Before validating the break, the delimiter is checked for as it signifies that the RX line has returned to a high level.

If a '1' is sampled before the 10 or 11 have occurred, the break detection circuit cancels the current detection and searches for a start bit again.

If the LIN mode is disabled (LINEN=0), the receiver continues working as normal USART, without taking into account the break detection.

If the LIN mode is enabled (LINEN=1), as soon as a framing error occurs (i.e. stop bit detected at '0', which is the case for any break frame), the receiver stops until the break detection circuit receives either a '1', if the break word was not complete, or a delimiter character if a break has been detected.

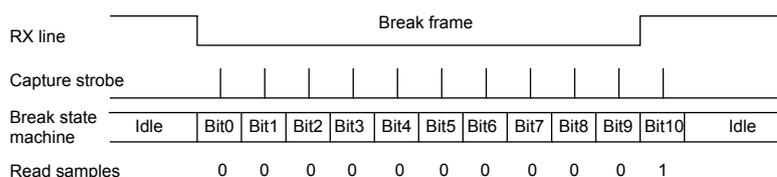

The behavior of the break detector state machine and the break flag is shown in Figure 123. Break detection in LIN mode (11-bit break length - LBDL bit is set).

Examples of break frames are given:

Figure 123. Break detection in LIN mode (11-bit break length - LBDL bit is set)

Case 1: break signal not long enough => break discarded, LBDF is not set

| RX line | Break frame | ||||||||||||

| Capture strobe | | | | | | | | | | | | | | | | | | | | | |||

| Break state machine | Idle | Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 | Bit7 | Bit8 | Bit9 | Bit10 | Idle |

| Read samples | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | ||

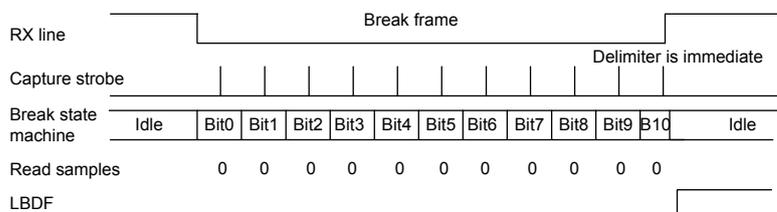

Case 2: break signal just long enough => break detected, LBDF is set

| RX line | Break frame | Delimiter is immediate | |||||||||||

| Capture strobe | | | | | | | | | | | | | | | | | | | | | | | ||

| Break state machine | Idle | Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 | Bit7 | Bit8 | Bit9 | Bit10 | Idle |

| Read samples | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| LBDF | Set (High) | ||||||||||||

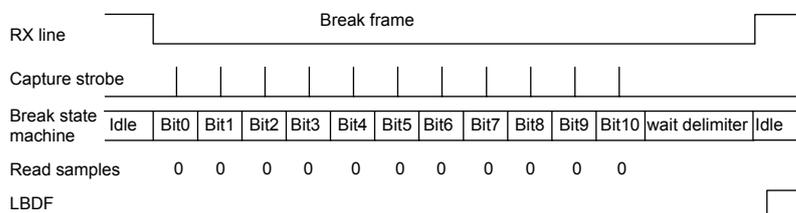

Case 3: break signal long enough => break detected, LBDF is set

| RX line | Break frame | |||||||||||||

| Capture strobe | | | | | | | | | | | | | | | | | | | | | | | | | ||

| Break state machine | Idle | Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 | Bit7 | Bit8 | Bit9 | Bit10 | wait delimiter | Idle |

| Read samples | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| LBDF | Set (High) | |||||||||||||

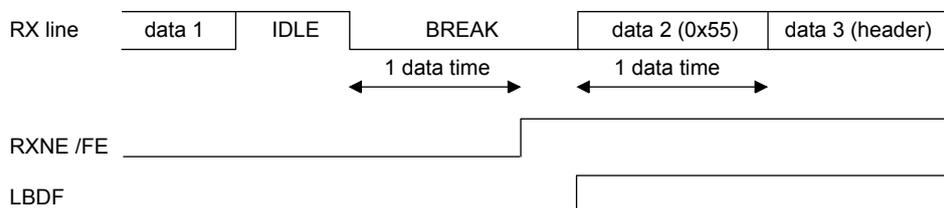

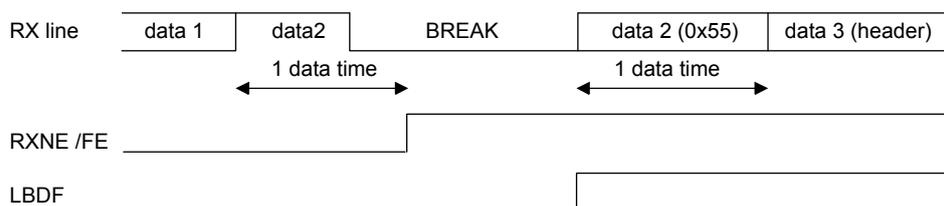

Figure 124. Break detection in LIN mode vs. framing error detection

Case 1: break occurring after an Idle

The diagram shows the RX line, RXNE/FE line, and LBDF line over time. The RX line has segments for 'data 1', 'IDLE', 'BREAK', 'data 2 (0x55)', and 'data 3 (header)'. The 'BREAK' segment is labeled with a double-headed arrow indicating a duration of '1 data time'. The 'IDLE' segment between 'data 1' and 'BREAK' is also labeled with a double-headed arrow indicating a duration of '1 data time'. The RXNE/FE line is high during the 'IDLE' segment and goes low at the start of the 'BREAK' segment. The LBDF line is high during the 'IDLE' segment and goes low at the start of the 'BREAK' segment.

Case 2: break occurring while data is being received

The diagram shows the RX line, RXNE/FE line, and LBDF line over time. The RX line has segments for 'data 1', 'data 2', 'BREAK', 'data 2 (0x55)', and 'data 3 (header)'. The 'BREAK' segment is labeled with a double-headed arrow indicating a duration of '1 data time'. The 'data 2' segment between 'data 1' and 'BREAK' is also labeled with a double-headed arrow indicating a duration of '1 data time'. The RXNE/FE line is high during the 'data 2' segment and goes low at the start of the 'BREAK' segment. The LBDF line is high during the 'data 2' segment and goes low at the start of the 'BREAK' segment.

20.5.12 USART synchronous mode

Master mode

The synchronous master mode is selected by writing the CLKEN bit in the USART_CR2 register to 1. In synchronous mode, the following bits must be kept cleared:

- • LINEN bit in the USART_CR2 register

- • SCEN, HDSEL and IREN bits in the USART_CR3 register.

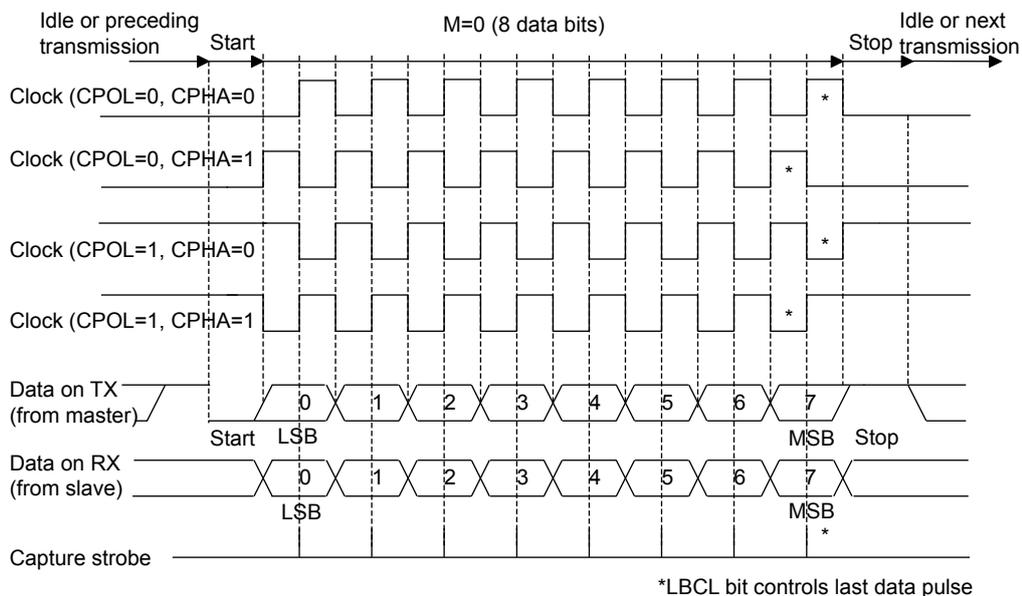

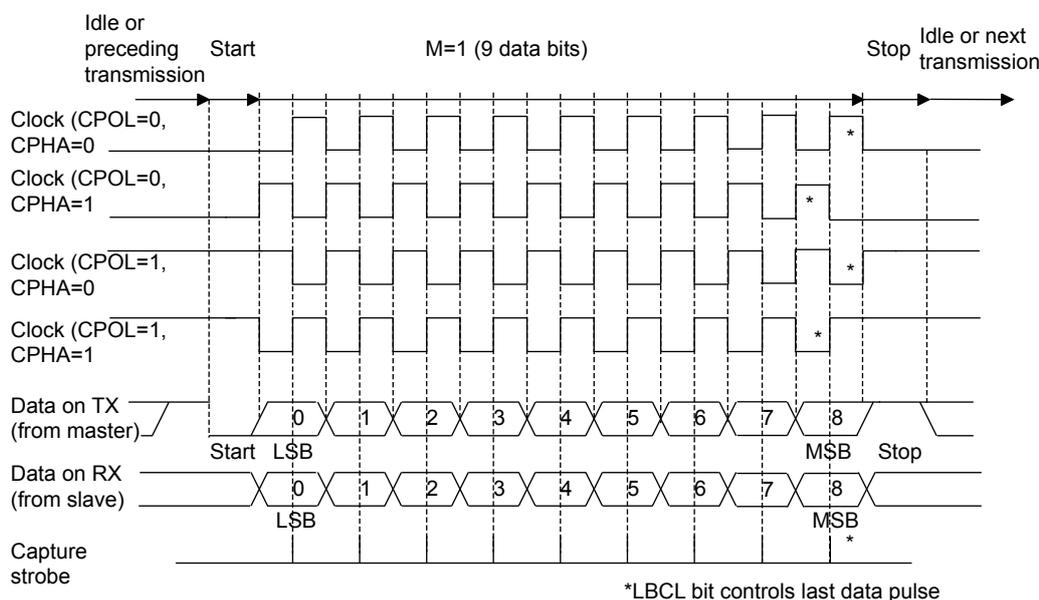

In this mode, the USART can be used to control bidirectional synchronous serial communications in master mode. The SCLK pin is the output of the USART transmitter clock. No clock pulses are sent to the SCLK pin during start bit and stop bit. Depending on the state of the LBCL bit in the USART_CR2 register, clock pulses are, or are not, generated during the last valid data bit (address mark). The CPOL bit in the USART_CR2 register is used to select the clock polarity, and the CPHA bit in the USART_CR2 register is used to select the phase of the external clock (see Figure 125. USART example of synchronous master transmission and Figure 126. USART data clock timing diagram M=0).

During the idle state, preamble and send break, the external SCLK clock is not activated.

In synchronous master mode the USART transmitter works exactly like in asynchronous mode. But as SCLK is synchronized with TX (according to CPOL and CPHA), the data on TX is synchronous.

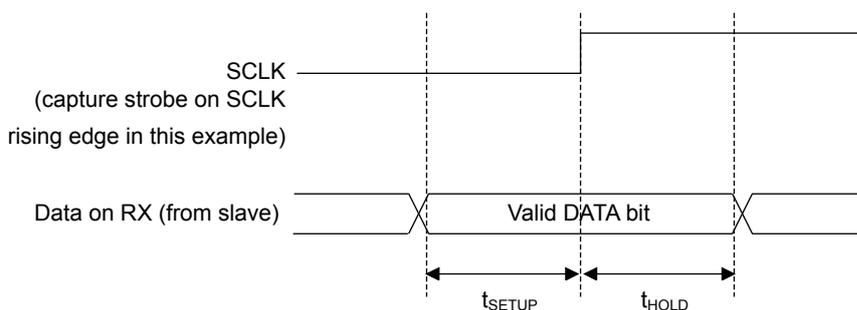

In this mode the USART receiver works in a different manner compared to the asynchronous mode. If RE=1, the data is sampled on SCLK (rising or falling edge, depending on CPOL and CPHA), without any oversampling. A setup and a hold time must be respected (which depends on the baud rate: 1/16 bit time).

Note: In master mode, the SCLK pin works in conjunction with the TX pin. Thus, the clock is provided only if the transmitter is enabled (TE=1) and data is being transmitted (the data register USART_DR written). This means that it is not possible to receive synchronous data without transmitting data.

Figure 125. USART example of synchronous master transmission

Figure 126. USART data clock timing diagram M=0

Idle or preceding transmission Start M=0 (8 data bits) Stop Idle or next transmission

Clock (CPOL=0, CPHA=0)

Clock (CPOL=0, CPHA=1)

Clock (CPOL=1, CPHA=0)

Clock (CPOL=1, CPHA=1)

Data on TX (from master)

Data on RX (from slave)

Capture strobe

*LBCL bit controls last data pulse

Figure 127. USART data clock timing diagram (M bits = 01)

Figure 128. RX data setup/hold time

Slave mode

The synchronous slave mode is selected by writing the SLVEN bit in the USART_CR2 register to 1. In synchronous slave mode, the following bits must be kept cleared:

- • LINEN and CLKEN bits in the USART_CR2 register,

- • SCEN, HDSEL and IREN bits in the USART_CR3 register.

In this mode, the USART can be used to control bidirectional synchronous serial communications in slave mode. The SCLK pin is the input of the USART in slave mode.

Note: When the peripheral is used in SPI slave mode, the peripheral clock source (fck_pres) must be greater than 3xSCLK input clock.

The CPOL bit in the USART_CR2 register is used to select the clock polarity, and the CPHA bit in the USART_CR2 register is used to select the phase of the external clock (see Figure 125. USART example of synchronous master transmission, Figure 126. USART data clock timing diagram M=0 and Figure 127. USART data clock timing diagram (M bits = 01)).

In slave transmission mode, an underun error flag is available. This flag is set when the first clock for data transmission appears while the software has not yet loaded any value into USARTx_TDR.

The slave supports the hardware and software NSS management.

Slave select (NSS) pin management

Hardware or software slave select management can be set using the DIS_NSS bit in the USART_CR2 register.

- • Software NSS management (DIS_NSS =1)

SPI slave is always selected and NSS input pin is ignored. The external NSS pin remains free for other application uses. - • Hardware NSS management (DIS_NSS =0)

The SPI slave selection depends on NSS input pin. The slave is selected when NSS is low and deselected when NSS high.

Note: The LBCL (used only on SPI master mode), CPOL and CPHA bits have to be selected when the USART is disabled (UE=0) to ensure that the clock pulses function correctly.

Note: When in SPI slave mode, the USART must be enabled before the master starts communication (or between frames while the clock is stable). Otherwise, if the USART slave is enabled while the master is in the middle of a frame, it becomes desynchronized with the master. The data register of the slave needs to be ready before the first edge of the communication clock or before the end of the on-going communication, otherwise SPI slave transmits zeros.

SPI slave underrun error

When an underrun error occurs, the SPI slave sends the last data until the underrun error flag is cleared in software.

The underrun flag is set at the beginning of the frame.

The underrun error flag is cleared by setting bit UDRCF in the USART_ICR register.

In underrun condition, it is allowed to write the TDR register. Clearing the underrun error would allow sending the new data.

If an underrun error occurred and there is no new data written in TDR, then the TC flag is set at the end of the frame.

Note: An underrun error may occur if the data is written in the USARTx_TDR too close to the first SCLK transmission edge. To avoid this underrun error, the USART_TDR should be written 3 UCLK cycles before the first SCLK edge.

20.5.13 Single-wire half-duplex communication

Single-wire half-duplex mode is selected by setting the HDSEL bit in the USART_CR3 register. In this mode, the following bits must be kept cleared:

- • LINEN and CLKEN bits in the USART_CR2 register

- • SCEN and IREN bits in the USART_CR3 register.

The USART can be configured to follow a single-wire half-duplex protocol where the TX and RX lines are internally connected. The selection between half- and full-duplex communication is made with a control bit HDSEL in USART_CR3.

As soon as HDSEL is written to 1:

- • The TX and RX lines are internally connected

- • The RX pin is no longer used

- • The TX pin is always released when no data is transmitted. Thus, it acts as a standard I/O in idle or in reception. It means that the I/O must be configured so that TX is configured as alternate function open-drain with an external pull-up.

Apart from this, the communication protocol is similar to normal USART mode. Any conflicts on the line must be managed by software (by the use of a centralized arbiter, for instance). In particular, the transmission is never blocked by hardware and continues as soon as data are written in the data register while the TE bit is set.

Note: As the TX line and the RX lines are connected together, all the transmitted data are stored in the RX FIFO as the data received from an external device. The software has to take care to discard its “own” information after a transmit phase. In half-duplex mode, it is always wise to read back the transmitted data to check if they are correct as there is no hardware protection against possible collision between nodes. If the software does not want to have the RX FIFO storing the transmitted value then it has to disable the receiver part while transmitting (by clearing the RE bit in USART_CR1 register).

20.5.14 Receiver timeout

The receiver timeout feature is enabled by setting the RTOEN bit in the USART_CR2 control register.

The timeout duration is programmed using the RTO bit fields in the USARTx_RTOR register.

The receiver timeout counter starts counting

- • From the end of the stop bit in case STOP = 00 and STOP = 11

- • From the end of the second stop bit in case STOP = 10

- • From the beginning of the stop bit in case STOP = 01.

When the timeout duration has elapsed, the RTOF flag in the USARTx_ISR register is set and a timeout is generated if RTOIE bit in USARTx_CR1 register is set.

20.5.15 Smartcard mode

This section is relevant only when smartcard mode is supported. Refer to Section 20.4: USART implementation .

Smartcard mode is selected by setting the SCEN bit in the USART_CR3 register. In Smartcard mode, the following bits must be kept cleared:

- • LINEN bit in the USART_CR2 register

- • HDSEL and IREN bits in the USART_CR3 register.

The CLKEN bit may be set in order to provide a clock to the Smartcard.

The Smartcard interface is designed to support asynchronous protocol Smartcards as defined in the ISO 7816-3 standard. Both T=0 (character mode) and T=1 (block mode) are supported.

The USART should be configured as:

- • 8-bit plus parity: where M=1 and PCE=1 in the USART_CR1 register

- • 1.5 stop bits when transmitting and receiving data: where STOP=11 in the USART_CR2 register. It is also possible to choose the 0.5 stop bit for receiving.

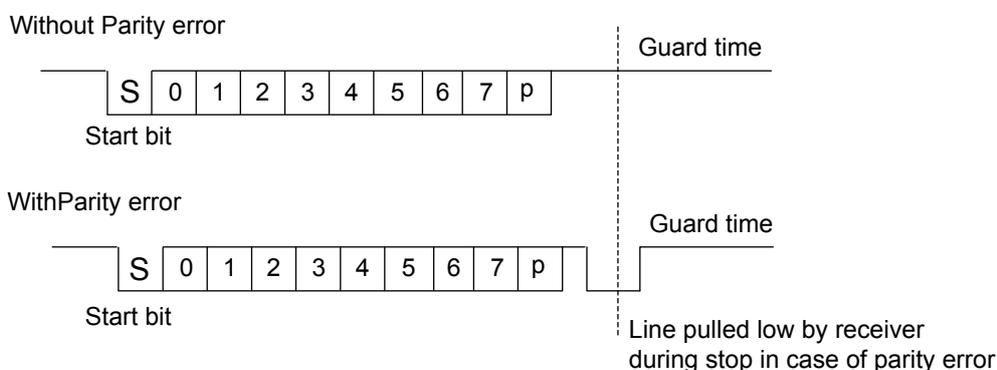

In T=0 (character) mode, the parity error is indicated at the end of each character during the Guard Time period.

Figure 129. ISO 7816-3 asynchronous protocol shows examples of what can be seen on the data line with and without parity error.

Figure 129. ISO 7816-3 asynchronous protocol

When connected to a Smartcard, the TX output of the USART drives a bidirectional line that is also driven by the Smartcard. The TX pin must be configured as open drain.

Smartcard mode implements a single-wire half-duplex communication protocol.

- • Transmission of data from the transmit shift register is guaranteed to be delayed by a minimum of 1/2 baud clock. In a normal operation a full transmit shift register starts shifting on the next baud clock edge. In Smartcard mode this transmission is further delayed by a guaranteed 1/2 baud clock.

- • In transmission, if the Smartcard detects a parity error, it signals this condition to the USART by driving the line low (NACK). This NACK signal (pulling transmit line low for 1 baud clock) causes a framing error on the transmitter side (configured with 1.5 stop bits). The USART can handle automatic re-sending of data according to the protocol. The number of retries is programmed in the SCARCNT bit field. If the USART continues receiving the NACK after the programmed number of retries, it stops transmitting and signals the error as a framing error. The TXE bit (TXFNF bit in case FIFO mode is enabled) may be set using the TXFRQ bit in the USART_RQR register.

- • Smartcard auto-retry in transmission: a delay of 2.5 baud periods is inserted between the NACK detection by the USART and the start bit of the repeated character. The TC bit is set immediately at the end of reception of the last repeated character (no Guard Time). If the software wants to repeat it again, it must ensure the minimum 2 baud periods required by the standard.

- • If a parity error is detected during reception of a frame programmed with a 1.5 stop bit period, the transmit line is pulled low for a baud clock period after the completion of the receive frame. This is to indicate to the Smartcard that the data transmitted to the USART has not been correctly received. A parity error is NACKed by the receiver if the NACK control bit is set, otherwise a NACK is not transmitted (to be used in T=1 mode). If the received character is erroneous, the RXNE (RXFNE in case FIFO mode is enabled)/receive DMA request is not activated. According to the protocol specification, the Smartcard must resend the same character. If the received character is still erroneous after the maximum number of retries specified in the SCARCNT bit field, the USART stops transmitting the NACK and signals the error as a parity error.

- • Smartcard auto-retry in reception: the BUSY flag remains set if the USART NACKs the card but the card does not repeat the character.

- • In transmission, the USART inserts the Guard Time (as programmed in the Guard Time register) between two successive characters. As the Guard Time is measured after the stop bit of the previous character, the GT[7:0] register must be programmed to the desired CGT (Character Guard Time, as defined by the 7816-3 specification) minus 12 (the duration of one character).

- • The assertion of the TC flag can be delayed by programming the Guard Time register. In normal operation, TC is asserted when the transmit shift register is empty and no further transmit requests are outstanding. In Smartcard mode an empty transmit shift register triggers the Guard Time counter to count up to the programmed value in the Guard Time register. TC is forced low during this time. When the Guard Time counter reaches the programmed value TC is asserted high. The TCBGT flag can be used to detect the end of data transfer without waiting for Guard Time completion. This flag is set just after the end of frame transmission and if no NACK has been received from the card.

- • The de-assertion of TC flag is unaffected by Smart card mode.

- • If a framing error is detected on the transmitter end (due to a NACK from the receiver), the NACK is not detected as a start bit by the receive block of the transmitter. According to the ISO protocol, the duration of the received NACK can be 1 or 2 baud clock periods.

- • On the receiver side, if a parity error is detected and a NACK is transmitted the receiver does not detect the NACK as a start bit.

Note: A break character is not significant in smartcard mode. A 0x00 data with a framing error is treated as data and not as a break.

Note: No Idle frame is transmitted when toggling the TE bit. The Idle frame (as defined for the other configurations) is not defined by the ISO protocol.

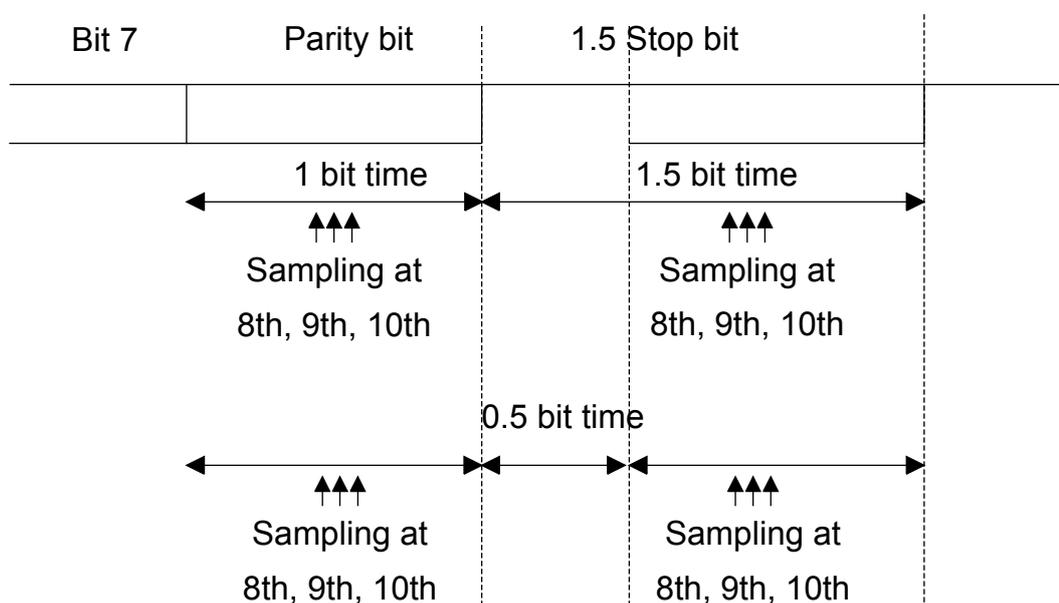

Figure 130. Parity error detection using 1.5 stop bits details how the NACK signal is sampled by the USART. In this example the USART is transmitting data and is configured with 1.5 stop bits. The receiver part of the USART is enabled in order to check the integrity of the data and the NACK signal.

Figure 130. Parity error detection using 1.5 stop bits

The diagram illustrates the timing for parity error detection. It shows a sequence of bits: Bit 7, followed by a Parity bit, and then a 1.5 Stop bit.

- The Parity bit has a duration of '1 bit time'. Sampling occurs at the 8th, 9th, and 10th clock cycles within this bit time.

- The 1.5 Stop bit has a duration of '1.5 bit time'. Sampling also occurs at the 8th, 9th, and 10th clock cycles of the first bit time of the stop bit period.

- A second row shows a '0.5 bit time' offset, followed by another '1.5 bit time' segment for the stop bit, with sampling again at the 8th, 9th, and 10th clock cycles.

The USART can provide a clock to the Smartcard through the SCLK output. In Smartcard mode, SCLK is not associated to the communication but is simply derived from the internal peripheral input clock through a 5-bit prescaler. The division ratio is configured in the prescaler register USART_GTPR. SCLK frequency can be programmed from \( f_{CKPRES}/2 \) to \( f_{CKPRES}/62 \) , where \( f_{CKPRES} \) is the peripheral input clock divided by a programmed prescaler.

Block mode (T=1)

In T=1 (block) mode, the parity error transmission can be deactivated by clearing the NACK bit in the UART_CR3 register.

When requesting a read from the Smartcard, in block mode, the software must program the RTOR register to the BWT (block wait time) - 11 value. If no answer is received from the card before the expiration of this period, a timeout interrupt is generated. If the first character is received before the expiration of the period, it is signaled by the RXNE/RXFNE interrupt.

Note: The RXNE/RXFNE interrupt must be enabled even when using the USART in DMA mode to read from the Smartcard in block mode. In parallel, the DMA must be enabled only after the first received byte.

After the reception of the first character (RXNE/RXFNE interrupt), the RTO register must be programmed to the CWT (character wait time) - 11 value, in order to allow the automatic check of the maximum wait time between two consecutive characters. This time is expressed in baudtime units. If the Smartcard does not send a new character in less than the CWT period after the end of the previous character, the USART signals this to the software through the RTOF flag and interrupt (when RTOIE bit is set).

Note: As in the Smartcard protocol definition, the BWT/CWT values should be defined from the beginning (start bit) of the last character. The RTO register must be programmed to BWT - 11 or CWT - 11, respectively, taking into account the length of the last character itself.

A block length counter is used to count all the characters received by the USART. This counter is reset when the USART is transmitting. The length of the block is communicated by the Smartcard in the third byte of the block (prologue field). This value must be programmed to the BLEN field in the USART_RTOR register. When using DMA mode, before the start of the block, this register field must be programmed to the minimum value (0x0). With this value, an interrupt is generated after the 4th received character. The software must read the LEN field (third byte), its value must be read from the receive buffer.

In interrupt driven receive mode, the length of the block may be checked by software or by programming the BLEN value. However, before the start of the block, the maximum value of BLEN (0xFF) may be programmed. The real value is programmed after the reception of the third character.

If the block is using the LRC longitudinal redundancy check (1 epilogue byte), the BLEN=LEN. If the block is using the CRC mechanism (2 epilog bytes), BLEN=LEN+1 must be programmed. The total block length (including prologue, epilogue and information fields) equals BLEN+4. The end of the block is signaled to the software through the EOBF flag and interrupt (when EOBI bit is set). In case of an error in the block length, the end of the block is signaled by the RTO interrupt (character wait time overflow).

Note: The error checking code (LRC/CRC) must be computed/verified by software.

Direct and inverse convention

The Smartcard protocol defines two conventions: direct and inverse.

The direct convention is defined as: LSB first, logical bit value of 1 corresponds to a H state of the line and parity is even. In order to use this convention, the following control bits must be programmed: MSBFIRST=0, DATAINV=0 (default values).

The inverse convention is defined as: MSB first, logical bit value 1 corresponds to an L state on the signal line and parity is even. In order to use this convention, the following control bits must be programmed: MSBFIRST=1, DATAINV=1.

Note: When logical data values are inverted (0=H, 1=L), the parity bit is also inverted in the same way.

In order to recognize the card convention, the card sends the initial character, TS, as the first character of the ATR (answer to reset) frame. The two possible patterns for the TS are: LHHL LLL LLH and LHHL HHH LLH.

- • (H) LHHL LLL LLH sets up the inverse convention: state L encodes value 1 and moment 2 conveys the most significant bit (MSB first). When decoded by inverse convention, the conveyed byte is equal to '3F'.

- • (H)LHHL HHH LLH sets up the direct convention: state H encodes value 1 and moment 2 conveys the least significant bit (LSB first). When decoded by direct convention, the conveyed byte is equal to '3B'.

Character parity is correct when there is an even number of bits set to 1 in the nine moments 2 to 10.

As the USART does not know which convention is used by the card, it needs to be able to recognize either pattern and act accordingly. The pattern recognition is not done in hardware, but through a software sequence. Moreover, supposing that the USART is configured in direct convention (default) and the card answers with the inverse convention, TS = LHHL LLL LLH => the USART received character is '03' and the parity is odd.

Therefore, two methods are available for TS pattern recognition:

Method 1

The USART is programmed in standard Smartcard mode/direct convention. In this case, the TS pattern reception generates a parity error interrupt and error signal to the card.

- • The parity error interrupt informs the software that the card did not answer correctly in direct convention. Software then reprograms the USART for inverse convention

- • In response to the error signal, the card retries the same TS character, and it is correctly received this time, by the reprogrammed USART.

Alternatively, in answer to the parity error interrupt, the software may decide to reprogram the USART and also to generate a new reset command to the card, then wait again for the TS.

Method 2

The USART is programmed in 9-bit/no-parity mode, no bit inversion. In this mode it receives either of the two TS patterns as: