18. Infrared interface (IRTIM)

An infrared interface (IRTIM) for remote control is available on the device. It can be used with an infrared LED to perform remote control functions.

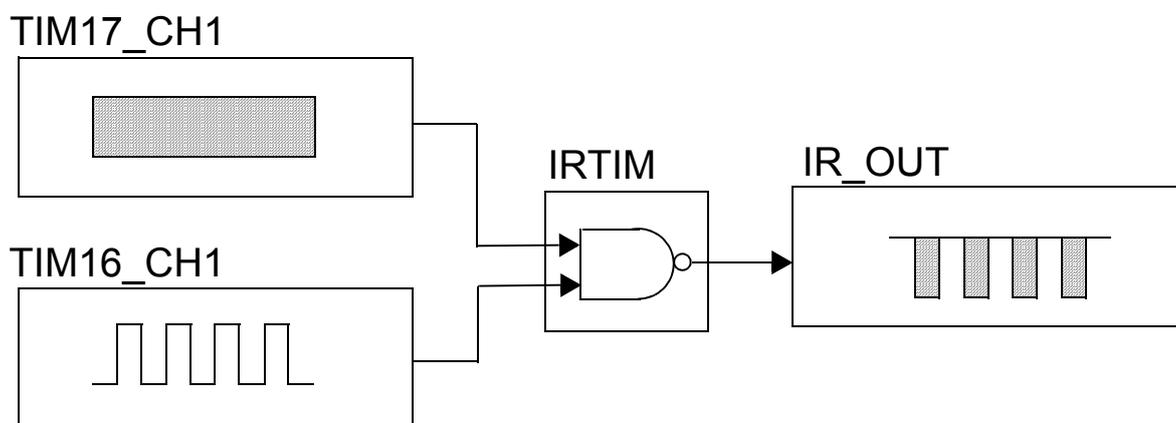

It uses internal connections with TIM16 and TIM17 as shown in Figure 91. IR internal hardware connections with TIM16 and TIM17 .

To generate the infrared remote control signals, the IR interface must be enabled and TIM16 channel 1 (TIM16_OC1) and TIM17 channel 1 (TIM17_OC1) must be properly configured to generate correct waveforms.

The infrared receiver can be implemented easily through a basic input capture mode.

Figure 91. IR internal hardware connections with TIM16 and TIM17

All standard IR pulse modulation modes can be obtained by programming the two timer output compare channels. TIM17 is used to generate the high frequency carrier signal, while TIM16 generates the modulation envelope.

The infrared function is output on the IR_OUT pin. The activation of this function is done through the Section 7.4.17: GPIOA alternate function low register (GPIOA_AFRL) or Section 7.4.19: GPIOA alternate function high register (GPIOA_AFRH) register by enabling the related alternate function.

The high sink LED driver capability (only available on the PA0, PA1 pin) can be activated through the I2C1_PA0_FMP or I2C1_PA1_FMP bit in the Section 8.2.3: I2C Fast-Mode Plus pin capability control register (I2C_FMP_CTRL) register and used to sink the high current needed to directly control an infrared LED.