9. Radio system

9.1 Introduction

The 2.4 GHz RADIO is ultra-low power, operating in the 2.4 GHz ISM band. It provides Bluetooth® LE 1 Mbps coded, 1 Mbps, and 2 Mbps non-coded GFSK, and IEEE802.15.4 chip rate 2 Mchip/s, spreading mode DSSS, data rate 125 and 250 kbps O-QPSK-C modulation.

The 2.4 GHz RADIO is compliant with the Bluetooth® LE, Thread and Zigbee® specifications, and radio regulations including ETSI EN 300 328, EN 300 440, EN 301 489-17, ARIB STD-T66, FCC CFR47 part 15 section 15.205, 15.209, 15.247, and 15.249, IC RSS-139 and RSS-210.

9.2 Main features

- • Radio protocol:

- – Bluetooth® LE

- – IEEE802.15.4

- – Concurrent mode

- – External PA support

- – Packet traffic arbitration

- • Bluetooth® LE features:

- – Device privacy and network privacy modes

- – Anonymous device address types

- – Advertising extension PDUs

- – Advertising channel index

- – Periodic advertising synchronous transfer

- – High duty cycle, nonconnectable advertising

- – Channel selection algorithm #2

- – Angle of arrival (AoA), angle of departure (AoD)

- – Up to 20 connections in any role in addition to advertiser and scanner roles

- – Audio connected isochronous streams

- – Audio broadcast isochronous streams

- – Core specification v6.0

- • IEEE 802.15.4 features:

- – Beacon management

- – 16-bit short and 64-bit IEEE addressing modes

- – PAN formation along with association and disassociation

- – Full handshake protocol for transfer reliability, frame validation, and acknowledgment frame delivery

- – IEEE802.15.4 2020 MAC for non-beaconed PANs

9.3 2.4 GHz RADIO implementation

Table 76. 2.4 GHz RADIO implementation

| Feature (1) | STM32WBA65xx | STM32WBA64xx | STM32WBA63xx | STM32WBA62xx |

|---|---|---|---|---|

| Bluetooth AoA/AoD | X | X | X | - |

| External PA | X | X | X | - |

| Packet traffic arbitration | X | X | X | X |

| IEEE802.15.4 | X | X | X | - |

1. X = supported

9.4 Functional description

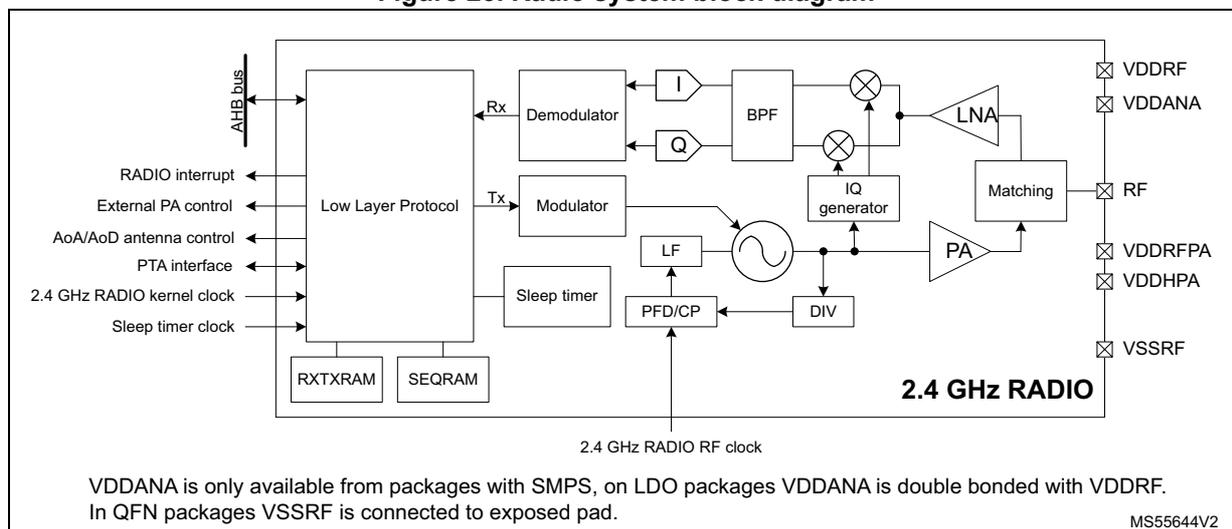

9.4.1 Block diagram

Figure 23. Radio system block diagram

VDDANA is only available from packages with SMPS, on LDO packages VDDANA is double bonded with VDDRF.

In QFN packages VSSRF is connected to exposed pad.

MS55644V2

9.4.2 Pins and internal signals

Table 77. Input/output pins

| Pin name | Signal type | Description |

|---|---|---|

| RF | RF | 2.4 GHz RF input output |

| RADIO interrupt | Output | 2.4 GHz RADIO interrupt to the CPU |

| External PA control | Output | External PA control |

| AoA/AoD antenna control | Output | Angle of arrival/departure antenna area control |

| PTA interface | Input/Output | Packet traffic arbitration control |

| RF_IO[7:6] | Output | General purpose interrupt to EXTI[20:19] |

9.4.3 Transmit output power

The 2.4 GHz RADIO includes an internal PA. The transmit output power can be increased using an additional external PA. External PA control signal BYPASS can be selected on GPIOs (see the datasheet), and the signal ENABLE can be mapped on any free GPIO by application software.

Figure 24 shows the transmit path and output power control.

Figure 24. Transmit path and output power control

![Figure 24: Transmit path and output power control diagram. The diagram shows the internal components of a 2.4 GHz radio system. At the top, a switch selects between VDDRFP_A and VDD11^(1) for the VDDHPA supply. Below this is a REG VDDHPA block controlled by PWR_RADIOSCR.REGPASEL and PWR_RADIOSCR.REGPABYPEN. The 2.4 GHz RADIO block contains a 'Transmit output power dBm' input, a 'PA output power table', and a 'TX' block. The 'PA output power table' provides 'VDDHPA level', 'PA code', and 'RF_EXTABYP' signals. The 'TX' block connects to an 'int PA' (internal PA). The 'int PA' output is connected to an 'RF' block, which then connects to an 'External PA (optional)' block. The 'External PA' has 'TX/RX', 'BYPASS', and 'ENABLE' inputs. The 'BYPASS' input is connected to 'GPIO[n] (optional)' and the 'ENABLE' input is connected to 'GPIOx[y] (optional)'. Both GPIO signals are controlled by a 'GPIO AF mapping' block. The 'External PA' output is connected to an 'Antenna'.](/RM0515-STM32WBA6/e9b47415a14efe87ccac5a1781be3a67_img.jpg)

- 1. VDD11 must be selected only when supplied from device SMPS.

The transmit output power (in dBm) is dependent upon the \( V_{DDHPA} \) voltage level and the PA code, and, when the application supports an external PA, an external PA bypass indication. The values for these parameters are defined in a PA output power table available to the link layer software.

Table 78. PA output power table format

| \( V_{DDHPA} \) level | PA code | BYPASS |

|---|---|---|

| 0x0 = 0.90 V 0x1 = 0.95 V 0x2 = 1.0 V 0x3 = 1.1 V ... 0xE = 2.2 V 0xF = 2.3 V | 0 to 25 dec. | 0 or 1 |

The internal PA maximum transmit output power depends upon the \( V_{DDHPA} \) voltage level and the PA code. The maximum \( V_{DDHPA} \) voltage level depends upon the application (VDDRFP_A pin) supply scheme, see Table 79 for details.

Note that the 2.4 GHz RADIO internal \( V_{CCRF} \) regulated supply level also depends upon the VDDRFP_A pin supply scheme:

- • when \( V_{DDRFP_A} < 1.4 \) V the \( V_{CCRF} \) regulated supply level must be 1.0 V

- • when \( V_{DDRFP_A} \geq 1.4 \) V the \( V_{CCRF} \) regulated supply level must be 1.2 V

The REG VDDHPA regulator input voltage can be controlled through REGPASEL and REGPABYPEN.

Table 79. 2.4 GHz RADIO supply configuration

| V DDHPA level | Minimum V DDRPA | Internal PA max transmit output power |

|---|---|---|

| 1.0 V | 1.2 V (1) | + 3 dBm |

| 1.2 V | 1.71 V | + 6 dBm |

| 1.5 V | 1.8 V | + 8 dBm |

| 2.3 V | 2.6 V | + 10 dBm |

1. Only on STM32WBA63/65xx devices when SMPS is used.

9.4.4 Bluetooth AoA and AoD

Up to eight antennas are supported by means of the coded RF_ANTSW[2:0] signal bus available through GPIO alternate function for Bluetooth AoA when receiving the constant tone extension of a packet, or for AoD while transmitting the constant tone extension of a packet.

Figure 25. Bluetooth AoA/AoD antennas control

![Figure 25. Bluetooth AoA/AoD antennas control diagram. The diagram shows the internal architecture of the 2.4 GHz RADIO block. It includes a TX path with an internal PA (int PA) and a matching network, and an RX path with an LNA and a matching network. The RF_ANTSW[2:0] signal bus is connected to the matching networks. The RF output is connected to an antenna matrix (optional) via a TX/RX switch. The antenna matrix is controlled by a Control block with inputs V1, V2, and V3. The V1, V2, and V3 inputs are connected to GPIOx, GPIOy, and GPIOz pins through a GPIO AF mapping block. The antenna matrix outputs are labeled Antenna1 through Antenna8.](/RM0515-STM32WBA6/fe3c62db1fe118bc628a0ea3045618f9_img.jpg)

9.4.5 RXTX data SRAM access

The link layer software must put the 2.4 GHz RADIO in Sleep mode to let the host application access the 2.4 GHz RADIO RXTXRAM. When the access is no longer needed, the host application must request the link layer software to put the 2.4 GHz RADIO in deep sleep mode.

To access the RXTX data SRAM, both the 2.4 GHz RADIO bus clock and the kernel clock must be active and ready.

The 2.4 GHz RADIO modes depend upon the host application request, and upon the link layer scheduled radio activity.

9.5 Low-power modes

The 2.4 GHz RADIO supports autonomous operation down to Stop 0 mode with voltage scaling range 1. Additionally, the 2.4 GHz RADIO configuration and sleep timer remain functional down to Standby retention mode.

In autonomous (Active) mode, the 2.4 GHz RADIO can transmit and receive packets over the air to maintain radio connections.

The 2.4 GHz RADIO configuration SRAMs and sleep timer enable the radio to maintain connections while in low-power modes such as Sleep and deep sleep, for example, between Bluetooth® LE connection events.

The device may enter Standby retention mode only when the 2.4 GHz RADIO is in deep sleep mode.

Before entering Standby mode, the 2.4 GHz RADIO must be disabled.

Table 80. Effect of low-power modes on the 2.4 GHz RADIO

| Mode | Description |

|---|---|

| Sleep | No effect. The 2.4 GHz RADIO (only in voltage scaling range 1) and the 2.4 GHz RADIO sleep timer interrupts cause the device to exit Sleep mode. Radio connections are maintained and may transmit and receive packets. |

| Stop 0 (voltage scaling range 1) | The 2.4 GHz RADIO autonomously transmits and receives packets. The 2.4 GHz RADIO and sleep timer interrupts cause the device to exit Stop 0 mode. Radio connections are maintained and may transmit and receive packets. |

| Stop 0 (voltage range 2), Stop 1, and Stop 2 | The 2.4 GHz RADIO configuration is retained but it is no longer capable of transmitting or receiving packets. The 2.4 GHz RADIO sleep timer interrupt causes the device to exit Stop mode. Radio connections are maintained during Bluetooth® LE connection intervals. |

| Standby retention | The 2.4 GHz RADIO configuration is retained but it is no longer capable of transmitting or receiving packets. The 2.4 GHz RADIO sleep timer interrupt causes the device to exit Standby retention mode. Radio connections are maintained during Bluetooth® LE connection intervals. |

| Standby | The 2.4 GHz RADIO and 2.4 GHz RADIO sleep timer are powered down. Radio connections are not maintained. |