2. Memory and bus architecture

2.1 System architecture

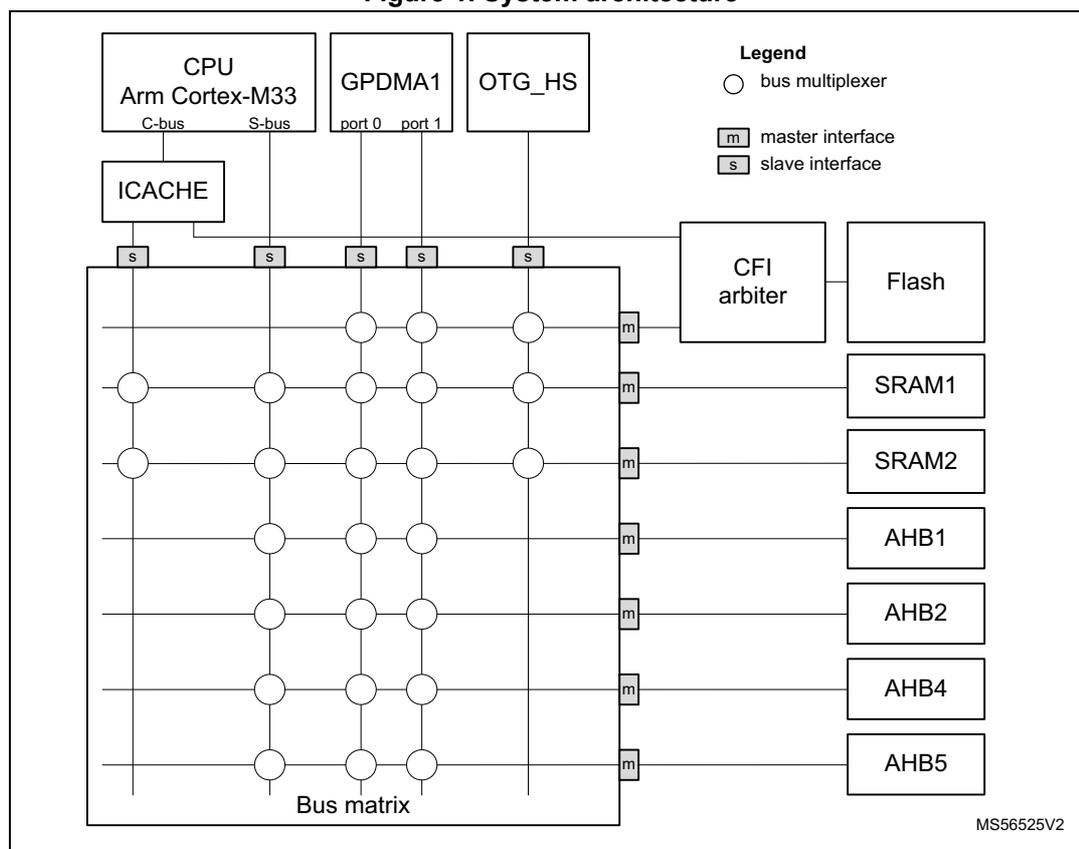

The device architecture relies on an Arm ® Cortex ® -M33 core optimized for execution, thanks to an instruction cache with a direct access to the embedded flash memory.

The architecture features a 32-bit multilayer AHB bus matrix interconnecting masters and slaves:

- • Masters:

- – CPU core C-bus through 128-bit wide ICACHE connecting to flash memory

- – CPU core C-bus through 32-bit wide ICACHE connecting to SRAM

- – CPU core S-bus

- – GPDMA1 port 0

- – GPDMA1 port 1

- – USB OTG_HS

- • Slaves:

- – Internal flash memory on the CPU core C-bus

- – Internal flash memory on the GPDMA1 bus

- – Internal SRAM1

- – Internal SRAM2

- – AHB1 peripherals including AHB to APB bridges and APB peripherals (connected to APB1 and APB2)

- – AHB2 peripherals

- – AHB4 peripherals including AHB to APB bridges and APB peripherals (connected to APB7)

- – AHB5 with the 2.4 GHz RADIO peripheral

The bus matrix provides access from a master to a slave, enabling concurrent access and efficient operation even when several high-speed peripherals work simultaneously. The architecture is shown in Figure 1 .

Figure 1. System architecture

The diagram illustrates the system architecture of the STM32 microcontroller. At the top, three main components are shown: CPU Arm Cortex-M33 (with C-bus and S-bus), GPDMA1 (with port 0 and port 1), and OTG_HS. Below the CPU, the ICACHE is connected to the C-bus. The S-bus connects to a central 'Bus matrix'. The GPDMA1 ports connect to the bus matrix via slave interfaces. The bus matrix is a grid of bus multiplexers (circles). On the right side, master interfaces (labeled 'm') connect the bus matrix to the CFI arbiter, Flash, SRAM1, SRAM2, AHB1, AHB2, AHB4, and AHB5. Slave interfaces (labeled 's') are shown on the left side of the bus matrix, connecting to the ICACHE and the CPU's S-bus. A legend indicates: circle = bus multiplexer, 'm' = master interface, 's' = slave interface. The identifier MS56525V2 is in the bottom right corner.

2.1.1 CPU C-bus

This bus connects the C-bus of the CPU to the internal flash memory and to the bus matrix via the instruction cache. This bus is used for instruction fetch and data access to the internal memories mapped in code region. This bus targets the internal flash memory and the internal SRAM (SRAM1 and SRAM2) via the ICACHE address remap function.

2.1.2 CPU S-bus

This bus connects the system bus of the CPU to the bus matrix, and it is used by the core to access data located in a peripheral or SRAM area. This bus targets the internal SRAM (SRAM1 and SRAM2), the AHB1 peripherals including the APB1 and APB2 peripherals, AHB2, AHB4 peripherals including the APB7, and AHB5 peripherals.

2.1.3 GPDMA1-bus

The buses connect the two AHB master interfaces of the GPDMA1 to the bus matrix. This targets the internal flash memory, the internal SRAMs (SRAM1, SRAM2), the AHB1 peripherals including the APB1 and APB2 peripherals, the AHB2 peripherals, AHB4 peripherals including the APB7, and AHB5 peripherals.

2.1.4 USB OTG_HS-bus

The bus connects the AHB master interfaces of the USB OTG_HS to the bus matrix. This bus is used by the USB OTG_HS to load and store data in memory. This targets the internal flash memory and the internal SRAMs (SRAM1, SRAM2).

2.1.5 Bus matrix

The bus matrix manages the access arbitration (based on fixed priority) between masters, and features a bus multiplexer used to connect each master to a given slave without latency.

Table 1. Bus matrix access arbitration

| Master | Priority |

|---|---|

| CPU core S-bus | 1 - highest |

| ICACHE slow port | 2 |

| GPDMA1 port 0 | 3 |

| GPDMA1 port 1 | 4 |

| USB OTG_HS | 5 - lowest |

2.1.6 AHB/APB bridges

The three bridges (AHB1 to APB1, AHB1 to APB2, and AHB4 to APB7) provide full synchronous connections between the AHB and the APB buses, resulting in flexible selection of the peripheral frequency.

Refer to Section 2.3.2: Memory map and register boundary addresses for the address mapping of the peripherals connected to these bridges.

After each device reset, the clock of peripherals having an xxEN bit in the RCC is disabled. Before using a peripheral, its clock must be enabled in the RCC_AHBxENR and RCC_APBxENR registers.

Note: When a 16- or 8-bit access is performed on an APB register, the access is transformed into a 32-bit access: the bridge duplicates the 16- or 8-bit data to feed the 32-bit vector.

AHB5 is a semisynchronous bus, connected through a bridge to the bus matrix.

2.2 TrustZone ® security architecture

The security architecture is based on Arm ® TrustZone with the Armv8-M mainline extension.

The TZEN option bit in the FLASH_OPTR register activates TrustZone security.

When the TrustZone is enabled, the SAU (security-attribution unit) and IDAU (implementation-defined-attribution unit) defines the access permissions based on secure and nonsecure states.

- • SAU: up to eight SAU configurable regions are available for security attribution.

- • IDAU: provides a first memory partition as nonsecure or nonsecure callable attributes. The IDAU memory map partition is not configurable and fixed by hardware

implementation (refer to Figure 2: Memory map ). It is then combined with the results from the SAU security attribution, and the higher security state is selected.

Based on IDAU security attribution, the flash memory, system SRAMs and peripherals memory space are aliased twice for secure and nonsecure states. However, the external memories space is not aliased.

Table 2 shows a typical example of eight SAU regions mapping, based on IDAU regions. The user can split and choose the secure, nonsecure or NSC regions for external memories according to application needs.

Table 2. Memory map security attribution example vs. SAU configuration regions (1)

| Region description | Address range | IDAU security attribution | SAU security attribution typical configuration | Final security attribution |

|---|---|---|---|---|

| Reserved | 0x0000 0000 to 0x07FF FFFF | Nonsecure | Secure, nonsecure or NSC | |

| Code Flash and SRAM | 0x0800 0000 to 0x0BFF FFFF | Nonsecure | Nonsecure | |

| 0x0C00 0000 to 0x0FFF FFFF | NSC | Secure or NSC | ||

| Reserved | 0x1000 0000 to 0x17FF FFFF | Nonsecure | ||

| 0x1800 0000 to 0x1FFF FFFF | ||||

| SRAM | 0x2000 0000 to 0x2FFF FFFF | Nonsecure | ||

| 0x3000 0000 to 0x3FFF FFFF | NSC | Secure or NSC | ||

| Peripherals | 0x4000 0000 to 0x4FFF FFFF | Nonsecure | Nonsecure | |

| 0x5000 0000 to 0x5FFF FFFF | NSC | Secure or NSC | ||

| Reserved | 0x6000 0000 to 0xDFFF FFFF | Nonsecure | Secure, nonsecure or NSC | |

1. NSC = nonsecure callable

2.2.1 Default TrustZone security state

When the TrustZone security is activated by the TZEN option bit in the FLASH_OPTR, the default system security state is detailed below:

- • CPU:

- – CPU1 Cortex-M33 is in secure state after reset. The boot address must point to a secure area.

- • Memory map:

- – SAU is fully secure after reset. Consequently, all memory map is fully secure. Up to height SAU configurable regions are available for security attribution.

- • Flash memory:

- – The flash memory security area is defined by watermark user options.

- – Flash block-based security attributions are nonsecure after reset.

- • SRAMs:

- – All SRAMs are secure after reset. MPCBBx (block-based memory protection controller) are secure.

- • Peripherals (see

Table 3

and

Table 4

for a list of securable and TrustZone-aware peripherals)

- – Securable peripherals are nonsecure after reset.

- – TrustZone-aware peripherals are nonsecure after reset. Their secure configuration registers are secure.

- • All GPIOs are secure after reset.

- • Interrupts:

- – NVIC: All interrupts are secure after reset. NVIC is banked for secure and nonsecure state.

- – TZIC: All illegal access interrupts are disabled after reset (see Section 5.5: GTZC interrupts ).

2.2.2 TrustZone peripheral classification

When the TrustZone security is active, a peripheral can be either securable or TrustZone-aware type as follows:

- • Securable: peripheral protected by an AHB/APB firewall gate controlled from TZSC controller to define security properties

- • TrustZone-aware: peripheral connected directly to AHB or APB bus and implementing a specific TrustZone behavior such as a subset of registers being secure.

Refer to Section 5: Global TrustZone controller (GTZC) for more details.

Table 3 and Table 4 list the securable and TrustZone-aware peripherals within the system.

Table 3. Securables peripherals by TZSC

| Bus | Peripheral |

|---|---|

| AHB5 | 2.4 GHz RADIO + SEQRAM |

| PTACONV | |

| AHB4 | ADC4 |

Table 3. Securable peripherals by TZSC (continued)

| Bus | Peripheral |

|---|---|

| AHB2 | SAES |

| PKA | |

| RNG | |

| HASH | |

| AES | |

| USB_OTG_HS (1) | |

| AHB1 | ICACHE registers |

| TSC | |

| CRC | |

| RAMCFG | |

| APB7 | LPTIM1 |

| I2C3 | |

| VREFBUF (2) | |

| COMP | |

| LPUART1 | |

| SPI3 | |

| APB2 | TIM17 |

| TIM16 | |

| SAI1 | |

| USART1 | |

| SPI1 | |

| TIM1 | |

| APB1 | LPTIM2 |

| I2C4 (1) | |

| I2C2 (1) | |

| I2C1 | |

| USART3 (1) | |

| USART2 | |

| SPI2 (1) | |

| IWDG | |

| WWDG | |

| TIM4 (1) | |

| TIM3 | |

| TIM2 |

1. Available only on STM32WBA62/64/65xx devices

- 2. Available only on STM32WBA62/65xx devices

| Bus | Peripheral |

|---|---|

| AHB4 | EXTI |

| RCC | |

| PWR | |

| AHB2 | HSEM |

| GPIOH | |

| GPIOG (1) | |

| GPIOE (1) | |

| GPIO (2) | |

| GPIOC | |

| GPIOB | |

| GPIOA | |

| AHB1 | GTZC-MCPBB6 |

| GTZC-MCPBB2 | |

| GTZC-MCPBB1 | |

| GTZC-TZSC | |

| GTZC-TZIC | |

| FLASH interface | |

| GPDMA1 | |

| APB7 | TAMP |

| RTC | |

| SYSCFG |

- 1. Available only on STM32WBA62/65xx devices.

2. Available only on STM32WBA62/64/65xx devices.

2.3 Memory organization

2.3.1 Introduction

Program memory, data memory, registers and I/O ports are organized within the same linear address space.

The bytes are coded in memory in Little Endian format. The lowest numbered byte in a word is considered the word's least significant byte and the highest numbered byte the most significant.

2.3.2 Memory map and register boundary addresses

Figure 2. Memory map

Legend:

- NS = aliased nonsecure (white box)

- S = aliased secure – nonsecure callable (green box)

| Address Range | Memory Region / Alias | Security Status |

|---|---|---|

| 0x0000 0000 – 0x00800 0000 | Reserved | NS |

| 0x00800 0000 – 0x00820 0000 | Flash-NS | NS |

| 0x00820 0000 – 0x00BF8 0000 | Reserved | NS |

| 0x00BF8 0000 – 0x00BF8 C000 | System Flash- NS | NS |

| 0x00BF8 C000 – 0x00C00 0000 | Reserved | NS |

| 0x00C00 0000 – 0x00C20 0000 | Flash-S | S |

| 0x00C20 0000 – 0x00FF8 0000 | Reserved | NS |

| 0x00FF8 0000 – 0x00FF8 C000 | System Flash- S | S |

| 0x00FF8 C000 – 0x01000 0000 | Reserved | NS |

| 0x01000 0000 – 0x02000 0000 | Reserved | NS |

| 0x02000 0000 – 0x02007 0000 | SRAM1-NS | NS |

| 0x02007 0000 – 0x02008 0000 | SRAM2-NS | NS |

| 0x02008 0000 – 0x03000 0000 | Reserved | NS |

| 0x03000 0000 – 0x03007 0000 | SRAM1-S | S |

| 0x03007 0000 – 0x03008 0000 | SRAM2-S | S |

| 0x03008 0000 – 0x03FFF FFFF | Reserved | NS |

| 0x04000 0000 – 0x04001 0000 | APB1-NS | NS |

| 0x04001 0000 – 0x04002 0000 | APB2-NS | NS |

| 0x04002 0000 – 0x04200 0000 | Reserved | NS |

| 0x04200 0000 – 0x04202 0000 | AHB1-NS | NS |

| 0x04202 0000 – 0x04400 0000 | Reserved | NS |

| 0x04400 0000 – 0x04600 0000 | APB7-NS | NS |

| 0x04600 0000 – 0x04601 0000 | Reserved | NS |

| 0x04601 0000 – 0x04602 0000 | AHB4-NS | NS |

| 0x04602 0000 – 0x04800 0000 | Reserved | NS |

| 0x04800 0000 – 0x04802 0000 | AHB5-NS | NS |

| 0x04802 0000 – 0x04A00 0000 | Reserved | NS |

| 0x04A00 0000 – 0x05000 0000 | APB1-S | S |

| 0x05000 0000 – 0x05001 0000 | APB2-S | S |

| 0x05001 0000 – 0x05002 0000 | Reserved | NS |

| 0x05002 0000 – 0x05200 0000 | Reserved | NS |

| 0x05200 0000 – 0x05202 0000 | Reserved | NS |

| 0x05202 0000 – 0x05400 0000 | Reserved | NS |

| 0x05400 0000 – 0x05600 0000 | Reserved | NS |

| 0x05600 0000 – 0x05601 0000 | APB7-S | S |

| 0x05601 0000 – 0x05602 0000 | Reserved | NS |

| 0x05602 0000 – 0x05800 0000 | Reserved | NS |

| 0x05800 0000 – 0x05802 0000 | Reserved | NS |

| 0x05802 0000 – 0x059FF FFFF | Reserved | NS |

| 0x059FF FFFF – 0x059FF FFFF | AHB5-S | S |

Left side memory map:

- 0x0000 0000 – 0x00C00 0000: CODE nonsecure

- 0x00C00 0000 – 0x01000 0000: CODE nonsecure

- 0x01000 0000 – 0x02000 0000: CODE nonsecure

- 0x02000 0000 – 0x03000 0000: SRAM nonsecure

- 0x03000 0000 – 0x04000 0000: SRAM nonsecure

- 0x04000 0000 – 0x05000 0000: Peripheral nonsecure

- 0x05000 0000 – 0x06000 0000: Peripherals nonsecure callable

- 0x06000 0000 – 0x0E000 0000: Reserved

- 0x0E000 0000 – 0x0FFFF FFFF: CPU internal peripherals

Right side memory map (aliases):

- 0x0000 0000 – 0x00800 0000: Reserved

- 0x00800 0000 – 0x00820 0000: Flash-NS

- 0x00820 0000 – 0x00BF8 0000: Reserved

- 0x00BF8 0000 – 0x00BF8 C000: System Flash- NS

- 0x00BF8 C000 – 0x00C00 0000: Reserved

- 0x00C00 0000 – 0x00C20 0000: Flash-S

- 0x00C20 0000 – 0x00FF8 0000: Reserved

- 0x00FF8 0000 – 0x00FF8 C000: System Flash- S

- 0x00FF8 C000 – 0x01000 0000: Reserved

- 0x01000 0000 – 0x02000 0000: Reserved

- 0x02000 0000 – 0x02007 0000: SRAM1-NS

- 0x02007 0000 – 0x02008 0000: SRAM2-NS

- 0x02008 0000 – 0x03000 0000: Reserved

- 0x03000 0000 – 0x03007 0000: SRAM1-S

- 0x03007 0000 – 0x03008 0000: SRAM2-S

- 0x03008 0000 – 0x03FFF FFFF: Reserved

STM32WBA6xxl devices contain a 2-Mbyte flash memory from address offset 0x00 0000 to 0x1F FFFF, and SRAM1 448-Kbyte from address offset 0x0 0000 to 0x6 FFFF, (continuous SRAM space with SRAM2).

STM32WBA6xxG devices contain a 1-Mbyte flash memory from address offset 0x00 0000 to 0x0F FFFF, and SRAM1 192-Kbyte from address offset 0x0 0000 to 0x2 FFFF, (noncontinuous SRAM space with SRAM2).

Any memory area not allocated to on-chip memories and peripherals is considered “Reserved”.

Table 5 gives the boundary addresses of the peripherals available in the device.

Table 5. Memory map and peripheral register boundary addresses

| Bus | Nonsecure callable boundary address (1) | Nonsecure boundary address (1) | Size (bytes) | Peripheral | Peripheral register map |

|---|---|---|---|---|---|

| - | 0x5A00 0000 - 0xDFFF FFFF | 0x4A00 0000 - 0x4FFF FFFF | - | Reserved | - |

| AHB5 | 0x5803 8400 - 0x59FF FFFF | 0x4803 8400 - 0x49FF FFFF | - | Reserved | - |

| 0x5803 8000 - 0x5803 83FF | 0x4803 8000 - 0x4803 83FF | 1 K | PTACONV | PTACONV register map | |

| 0x5802 C000 - 0x5803 7FFF | 0x4802 C00 - 0x4803 7FFF | - | Reserved | - | |

| 0x5802 8000 - 0x5802 BFFF | 0x4802 8000 - 0x4802 BFFF | 16 K | RXTXRAM | - | |

| 0x5802 1200 - 0x5802 7FFF | 0x4802 1200 - 0x4802 7FFF | - | Reserved | - | |

| 0x5802 1000 - 0x5802 11FF | 0x4802 1000 - 0x4802 11FF | 0.5 K | SEQRAM | - | |

| 0x5802 0000 - 0x5802 0FFF | 0x4802 0000 - 0x4802 0FFF | 4 K | 2.4 GHz RADIO | - | |

| - | 0x5800 0000 - 0x5801 FFFF | 0x4800 0000 - 0x4801 FFFF | - | Reserved | - |

| AHB4 | 0x5602 2400 - 0x57FF FFFF | 0x4602 2400 - 0x47FF FFFF | - | Reserved | - |

| 0x5602 2000 - 0x5602 23FF | 0x4602 2000 - 0x4602 23FF | 1 K | EXTI | EXTI register map | |

| 0x5602 1400 - 0x5602 1FFF | 0x4602 1400 - 0x4602 1FFF | - | Reserved | - | |

| 0x5602 1000 - 0x5602 13FF | 0x4602 1000 - 0x4602 13FF | 1 K | ADC4 | ADC register map | |

| 0x5602 0C00 - 0x5602 0FFF | 0x4602 0C00 - 0x4602 0FFF | 1 K | RCC | RCC register map | |

| 0x5602 0800 - 0x5602 0BFF | 0x4602 0800 - 0x4602 0BFF | 1 K | PWR | PWR register map | |

| 0x5602 0000 - 0x5602 07FF | 0x4602 0000 - 0x4602 07FF | - | Reserved | - | |

| - | 0x5601 0000 - 0x5601 FFFF | 0x4601 0000 - 0x4601 FFFF | - | Reserved | - |

| APB7 | 0x5600 8000 - 0x5600 FFFF | 0x4600 8000 - 0x4600 FFFF | - | Reserved | - |

| 0x5600 7C00 - 0x5600 7FFF | 0x4600 7C00 - 0x4600 7FFF | 1 K | TAMP | TAMP register map | |

| 0x5600 7800 - 0x5600 7BFF | 0x4600 7800 - 0x4600 7BFF | 1 K | RTC | RTC register map | |

| 0x5600 7400 - 0x5600 77FF | 0x4600 7400 - 0x4600 77FF | 1 K | VREFBUF (2) | VREFBUF register map | |

| 0x5600 5800 - 0x5600 73FF | 0x4600 5800 - 0x4600 73FF | - | Reserved | - | |

| 0x5600 5400 - 0x5600 57FF | 0x4600 5400 - 0x4600 57FF | 1 K | COMP | COMP register map | |

| 0x5600 4800 - 0x5600 53FF | 0x4600 4800 - 0x4600 53FF | - | Reserved | - | |

| 0x5600 4400 - 0x5600 47FF | 0x4600 4400 - 0x4600 47FF | 1 K | LPTIM1 | LPTIM register map | |

| 0x5600 2C00 - 0x5600 43FF | 0x4600 2C00 - 0x4600 43FF | - | Reserved | - | |

| 0x5600 2800 - 0x5600 2BFF | 0x4600 2800 - 0x4600 2BFF | 1 K | I2C3 | I2C register map | |

| 0x5600 2400 - 0x5600 27FF | 0x4600 2400 - 0x4600 27FF | 1 K | LPUART1 | LPUART register map |

Table 5. Memory map and peripheral register boundary addresses (continued)

| Bus | Nonsecure callable boundary address (1) | Nonsecure boundary address (1) | Size (bytes) | Peripheral | Peripheral register map |

|---|---|---|---|---|---|

| APB7 (cont'd) | 0x5600 2000 - 0x5600 23FF | 0x4600 2000 - 0x4600 23FF | 1 K | SPI3 | SPI register map |

| 0x5600 0800 - 0x5600 1FFF | 0x4600 0800 - 0x4600 1FFF | - | Reserved | - | |

| 0x5600 0400 - 0x5600 07FF | 0x4600 0400 - 0x4600 07FF | 1 K | SYSCFG | SYSCFG register map | |

| 0x5600 0000 - 0x5600 03FF | 0x4600 0000 - 0x4600 03FF | - | Reserved | - | |

| - | 0x5400 0000 - 0x55FF FFFF | 0x4400 0000 - 0x45FF FFFF | - | Reserved | - |

| AHB2 | 0x520C 4000 - 0x53FF FFFF | 0x420C 4000 - 0x43FF FFFF | - | Reserved | - |

| 0x520C 3400 - 0x520C 3FFF | 0x420C 3400 - 0x420C 3FFF | 8 K | PKA continue | PKA register map | |

| 0x520C 2400 - 0x520C 33FF | 0x420C 2400 - 0x420C 33FF | PKA RAM | |||

| 0x520C 2000 - 0x520C 23FF | 0x420C 2000 - 0x420C 23FF | PKA | |||

| 0x520C 1C00 - 0x520C 1FFF | 0x420C 1C00 - 0x420C 1FFF | 1 K | HSEM | HSEM register map | |

| 0x520C 1000 - 0x520C 1BFF | 0x420C 1000 - 0x420C 1BFF | - | Reserved | - | |

| 0x520C 0C00 - 0x520C 0FFF | 0x420C 0C00 - 0x420C 0FFF | 1 K | SAES | SAES register map | |

| 0x520C 0800 - 0x520C 0BFF | 0x420C 0800 - 0x420C 0BFF | 1 K | RNG | RNG register map | |

| 0x520C 0400 - 0x520C 07FF | 0x420C 0400 - 0x420C 07FF | 1 K | HASH | HASH register map | |

| 0x520C 0000 - 0x520C 03FF | 0x420C 0000 - 0x420C 03FF | 1 K | AES | AES register map | |

| 0x5206 0000 - 0x520B FFFF | 0x4206 0000 - 0x420B FFFF | - | Reserved | - | |

| 0x5204 0000 - 0x5205 FFFF | 0x4204 0000 - 0x4205 FFFF | 128 K | USB OTG (3) | OTG register map | |

| 0x5202 2000 - 0x5203 FFFF | 0x4202 2000 - 0x4203 FFFF | - | Reserved | - | |

| 0x5202 1C00 - 0x5202 1FFF | 0x4202 1C00 - 0x4202 1FFF | 1 K | GPIOH | GPIOH register map | |

| 0x5202 1800 - 0x5202 1BFF | 0x4202 1800 - 0x4202 1BFF | 1 K | GPIOG (2) | GPIOG register map | |

| 0x5202 1400 - 0x5202 1BFF | 0x4202 1400 - 0x4202 1BFF | - | Reserved | - | |

| 0x5202 1000 - 0x5202 13FF | 0x4202 1000 - 0x4202 13FF | 1 K | GPIOE (2) | GPIOE register map | |

| 0x5202 0C00 - 0x5202 0FFF | 0x4202 0C00 - 0x4202 0FFF | 1 K | GPIOF (3) | GPIOF register map | |

| 0x5202 0800 - 0x5202 0BFF | 0x4202 0800 - 0x4202 0BFF | 1 K | GPIOC | GPIOC register map | |

| 0x5202 0400 - 0x5202 07FF | 0x4202 0400 - 0x4202 07FF | 1 K | GPIOB | GPIOA to B register map | |

| 0x5202 0000 - 0x5202 03FF | 0x4202 0000 - 0x4202 03FF | 1 K | GPIOA | GPIOA to B register map | |

| - | 0x5200 0000 - 0x5201 FFFF | 0x4200 0000 - 0x4201 FFFF | - | Reserved | - |

| AHB1 | 0x5003 4400 - 0x51FF FFFF | 0x4003 4400 - 0x41FF FFFF | - | Reserved | - |

| 0x5003 4000 - 0x5003 43FF | 0x4003 4000 - 0x4003 43FF | 1 K | GTZC_MPCBB6 | GTZC1 MPCBB6 register map | |

| 0x5003 3400 - 0x5003 3FFF | 0x4003 3400 - 0x4003 3FFF | - | Reserved | - | |

| 0x5003 3000 - 0x5003 33FF | 0x4003 3000 - 0x4003 33FF | 1 K | GTZC_MPCBB2 | GTZC1 MPCBB1 and MPCBB2 register map | |

| 0x5003 2C00 - 0x5003 2FFF | 0x4003 2C00 - 0x4003 2FFF | 1 K | GTZC_MPCBB1 | ||

| 0x5003 2800 - 0x5003 2BFF | 0x4003 2800 - 0x4003 2BFF | 1 K | GTZC_TZIC | GTZC1 TZIC register map | |

| 0x5003 2400 - 0x5003 27FF | 0x4003 2400 - 0x4003 27FF | 1 K | GTZC_TZSC | GTZC1 TZSC register map |

Table 5. Memory map and peripheral register boundary addresses (continued)

| Bus | Nonsecure callable boundary address (1) | Nonsecure boundary address (1) | Size (bytes) | Peripheral | Peripheral register map |

|---|---|---|---|---|---|

| AHB1 (cont'd) | 0x5003 0800 - 0x5003 23FF | 0x4003 0800 - 0x4003 23FF | - | Reserved | - |

| 0x5003 0400 - 0x5003 07FF | 0x4003 0400 - 0x4003 07FF | 1 K | ICACHE | ICACHE register map | |

| 0x5002 7000 - 0x5003 03FF | 0x4002 7000 - 0x4003 03FF | - | Reserved | - | |

| 0x5002 6000 - 0x5002 6FFF | 0x4002 6000 - 0x4002 6FFF | 4 K | RAMCFG | RAMCFG register map | |

| 0x5002 4400 - 0x5002 5FFF | 0x4002 4400 - 0x4002 5FFF | - | Reserved | - | |

| 0x5002 4000 - 0x5002 43FF | 0x4002 4000 - 0x4002 43FF | 1 K | TSC | TSC register map | |

| 0x5002 3400 - 0x5002 3FFF | 0x4002 3400 - 0x4002 3FFF | - | Reserved | - | |

| 0x5002 3000 - 0x5002 33FF | 0x4002 3000 - 0x4002 33FF | 1 K | CRC | CRC register map | |

| 0x5002 2400 - 0x5002 2FFF | 0x4002 2400 - 0x4002 2FFF | - | Reserved | - | |

| 0x5002 2000 - 0x5002 23FF | 0x4002 2000 - 0x4002 23FF | 1 K | FLASH interface | FLASH register map | |

| 0x5002 1000 - 0x5002 1FFF | 0x4002 1000 - 0x4002 1FFF | - | Reserved | - | |

| APB2 | 0x5002 0000 - 0x5002 0FFF | 0x4002 0000 - 0x4002 0FFF | 4 K | GPDMA1 | GPDMA register map |

| 0x5001 5800 - 0x5001 FFFF | 0x4001 5800 - 0x4001 FFFF | - | Reserved | - | |

| 0x5001 5400 - 0x5001 57FF | 0x4001 5400 - 0x4001 57FF | 1 K | SAI1 | SAI register map | |

| 0x5001 4C00 - 0x5001 53FF | 0x4001 4C00 - 0x4001 53FF | - | Reserved | - | |

| 0x5001 4800 - 0x5001 4BFF | 0x4001 4800 - 0x4001 4BFF | 1 K | TIM17 | TIM16/TIM17 register map | |

| 0x5001 4400 - 0x5001 47FF | 0x4001 4400 - 0x4001 47FF | 1 K | TIM16 | ||

| 0x5001 3C00 - 0x5001 3FFF | 0x4001 3C00 - 0x4001 3FFF | - | Reserved | - | |

| 0x5001 3800 - 0x5001 3BFF | 0x4001 3800 - 0x4001 3BFF | 1 K | USART1 | USART register map | |

| 0x5001 3400 - 0x5001 37FF | 0x4001 3400 - 0x4001 37FF | - | Reserved | - | |

| 0x5001 3000 - 0x5001 33FF | 0x4001 3000 - 0x4001 33FF | 1 K | SPI1 | SPI register map | |

| 0x5001 2C00 - 0x5001 2FFF | 0x4001 2C00 - 0x4001 2FFF | 1 K | TIM1 | TIM1 register map | |

| APB1 | 0x5001 0000 - 0x5001 2BFF | 0x4001 0000 - 0x4001 2BFF | - | Reserved | - |

| 0x5000 9800 - 0x5000 FFFF | 0x4000 9800 - 0x4000 FFFF | - | Reserved | - | |

| 0x5000 9400 - 0x5000 97FF | 0x4000 9400 - 0x4000 97FF | 1 K | LPTIM2 | LPTIM register map | |

| 0x5000 8800 - 0x5000 93FF | 0x4000 8800 - 0x4000 93FF | - | Reserved | - | |

| 0x5000 8400 - 0x5000 87FF | 0x4000 8400 - 0x4000 87FF | 1 K | I2C4 (3) | I2C register map | |

| 0x5000 5C00 - 0x5000 83FF | 0x4000 5C00 - 0x4000 83FF | - | Reserved | - | |

| 0x5000 5800 - 0x5000 5BFF | 0x4000 5800 - 0x4000 5BFF | 1 K | I2C2 (3) | I2C register map | |

| 0x5000 5400 - 0x5000 57FF | 0x4000 5400 - 0x4000 57FF | 1 K | I2C1 | I2C register map | |

| 0x5000 4C00 - 0x5000 53FF | 0x4000 4C00 - 0x4000 53FF | - | Reserved | - | |

| 0x5000 4800 - 0x5000 4BFF | 0x4000 4800 - 0x4000 4BFF | 1 K | USART3 (3) | USART register map | |

| 0x5000 4400 - 0x5000 47FF | 0x4000 4400 - 0x4000 47FF | 1 K | USART2 | USART register map |

Table 5. Memory map and peripheral register boundary addresses (continued)

| Bus | Nonsecure callable boundary address (1) | Nonsecure boundary address (1) | Size (bytes) | Peripheral | Peripheral register map |

|---|---|---|---|---|---|

| APB1 (cont'd) | 0x5000 3C00 - 0x5000 43FF | 0x4000 3C00 - 0x4000 43FF | - | Reserved | - |

| 0x5000 3800 - 0x5000 3BFF | 0x4000 3800 - 0x4000 3BFF | 1 K | SPI2 (3) | SPI register map | |

| 0x5000 3400 - 0x5000 37FF | 0x4000 3400 - 0x4000 37FF | - | Reserved | - | |

| 0x5000 3000 - 0x5000 33FF | 0x4000 3000 - 0x4000 33FF | 1 K | IWDG | IWDG register map | |

| 0x5000 2C00 - 0x5000 2FFF | 0x4000 2C00 - 0x4000 2FFF | 1 K | WWDG | WWDG register map | |

| 0x5000 0C00 - 0x5000 2BFF | 0x4000 0C00 - 0x4000 2BFF | - | Reserved | - | |

| 0x5000 0800 - 0x5000 0BFF | 0x4000 0800 - 0x4000 0BFF | 1 K | TIM4 (3) | TIMx register map | |

| 0x5000 0400 - 0x5000 07FF | 0x4000 0400 - 0x4000 07FF | 1 K | TIM3 | ||

| 0x5000 0000 - 0x5000 03FF | 0x4000 0000 - 0x4000 03FF | 1 K | TIM2 | ||

| AHB | 0x3008 0000 - 0x4FFF FFFF | 0x2008 0000 - 0x3FFF FFFF | - | Reserved | - |

| 0x3007 0000 - 0x3007 FFFF | 0x2007 0000 - 0x2007 FFFF | 64 K | SRAM2 | - | |

| 0x3000 0000 - 0x3006 FFFF | 0x2000 0000 - 0x2006 FFFF | 448 K (4) | SRAM1 | - | |

| 0x0FFA C000 - 0x2FFF FFFF | 0x0FFA C000 - 0x1FFF FFFF | - | Reserved | - | |

| 0x0FFA 8000 - 0x0FFA BFFF | 0x0BFA 8000 - 0x0BFB 7FFF | 16 K | Flash user options | Option bytes description | |

| 0x0FFA 4000 - 0x0FFA 7FFF | 0x0BFA 4000 - 0x0BFA 7FFF | - | Reserved | - | |

| 0x0FFA 0500 - 0x0FFA 3FFF | 0x0BFA 0500 - 0x0BFA 3FFF | 14.75 K | DESIG | DESIG register map | |

| 0x0FFA 0200 - 0x0FFA 04FF | 0x0BFA 0200 - 0x0BFA 04FF | - | Reserved | - | |

| 0x0FFA 0000 - 0x0FFA 01FF | 0x0BFA 0000 - 0x0BFA 01FF | 512 | OTP | - | |

| 0x0FF9 8000 - 0x0FF9 FFFF | 0x0BF9 8000 - 0x0BF9 FFFF | - | Reserved | - | |

| 0x0FF9 0000 - 0x0FF9 7FFF | 0x0BF9 0000 - 0x0BF9 7FFF | 32 K | Bootloader | - | |

| 0x0FF8 6000 - 0x0FF8 FFFF | 0x0BF8 6000 - 0x0BF8 FFFF | 40 K | RSS-Lib | - | |

| 0x0FF8 0000 - 0x0FF8 5FFF | 0x0BF8 0000 - 0x0BF8 5FFF | 24 K | RSS-Boot | - | |

| 0x0C20 0000 - 0x0FF7 FFFF | 0x0820 0000 - 0x0BF7 FFFF | - | Reserved | - | |

| 0x0C00 0000 - 0x0C1F FFFF | 0x0800 0000 - 0x081F FFFF | 2 M (5) | User Flash | - | |

| 0x0000 0000 - 0x0BFF FFFF | 0x0000 0000 - 0x07FF FFFF | - | Reserved | - |

1. Gray shaded fields are reserved.

2. Available only on STM32WBA62/65xx devices.

3. Available only on STM32WBA62/64/65xx devices.

4. Device-dependent (STM32WBA6xxI 448-Kbyte SRAM1 offset 0x0 0000 - 0x6 FFFF, STM32WBA6xxG 192-Kbyte SRAM1 offset 0x0 0000 - 0x2 FFFF where 0x3 0000 - 0x6 FFFF is reserved).

5. Device-dependent (STM32WBA6xxI 2-Mbyte flash offset 0x00 0000 - 0x1F FFFF, STM32WBA6xxG 1-Mbyte flash offset 0x00 0000 - 0x0F FFFF where 0x10 0000 - 0x1F FFFF is reserved).

2.3.3 Embedded SRAM

The devices feature 512 Kbytes of SRAM:

- • SRAM1: up to 448 Kbytes (192 Kbytes on STM32WBA6xxG, 448 Kbytes on STM32WBA6xxI)

- • SRAM2: 64 Kbytes

These SRAMs can be accessed as bytes, half-words (16 bits) or full words (32 bits). These memories can be addressed both by CPU and DMA.

The CPU can access the SRAM1, and SRAM2 through the system bus or, when remapped in the I-CACHE, through the C-bus, depending on the selected address.

When TrustZone security is enabled, all SRAMs are secure after reset. The SRAM can be programmed as nonsecure with a block granularity. For more details, refer to Section 5: Global TrustZone controller (GTZC) .

SRAM features are detailed in Section 6.3.1: Internal SRAMs features .

2.3.4 Flash memory overview

The flash memory is composed of two distinct physical areas:

- • The main flash memory block contains the application program and user data.

- • The information block, composed of the following parts:

- – option bytes for hardware and memory protection user configuration

- – system memory, which contains ST proprietary code

- – OTP (one-time programmable) area

The flash interface implements instruction access and data access based on the AHB protocol. It also implements the logic necessary to carry out the flash memory operations (program/erase) controlled through the flash registers plus security access control features. Refer to Section 7: Embedded flash memory (FLASH) for more details.