44. Device electronic signature (DESIG)

The device electronic signature is stored in the System memory area of the flash memory module, and can be read using the debug interface or by the CPU. It contains factory-programmed identification and calibration data that allow the user firmware or other external devices to automatically match the characteristics of the microcontroller.

44.1 Device electronic signature registers

44.1.1 DESIG package data register (DESIG_PKGR)

Address offset: 0x000

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PKG[4:0] | ||||

| r | r | r | r | r | |||||||||||

Bits 31:5 Reserved, must be kept at reset value.

Bits 4:0 PKG[4:0] : Package type

- 00000: UFQFPN32

- 00010: UFQFPN48

- 01001: WLCSP41 SMPS

- 01010: UFQFPN48 SMPS

- 01011: UFBGA59 SMPS

- Others: reserved

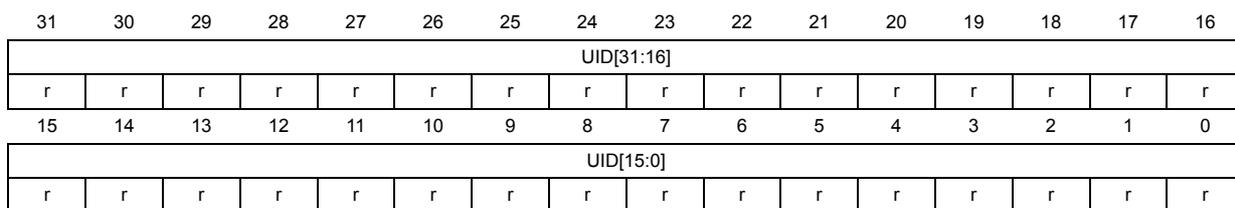

44.1.2 DESIG 96-bit unique device ID register 1 (DESIG_UIDR1)

Address offset: 0x200

Reset value: 0xXXXX XXXX (X is factory-programmed)

The 96-bit unique device identifier is ideally suited:

- • for use as serial number (USB string serial number or other end applications)

- • for use as part of the security keys to increase the code security in the flash memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the memory

- • during processes such as secure boot

This unique device identifier provides a reference number, unique for a given device and in any context. These bits cannot be altered by the user.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| UID[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| UID[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 UID[31:0] : X and Y coordinates on the wafer expressed in BCD format

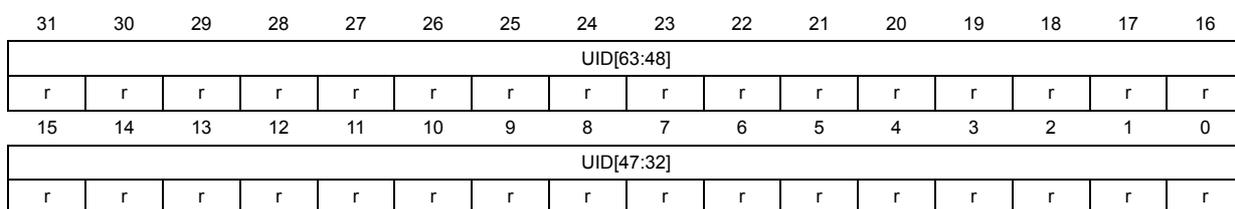

44.1.3 DESIG 96-bit unique device ID register 2 (DESIG_UIDR2)

Address offset: 0x204

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| UID[63:48] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| UID[47:32] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 UID[63:32] : Lot and wafer number

UID[63:40] = LOT_NUM[23:0], lot number lower part (ASCII encoded)

UID[39:32] = WAF_NUM[7:0], wafer number (8-bit unsigned number)

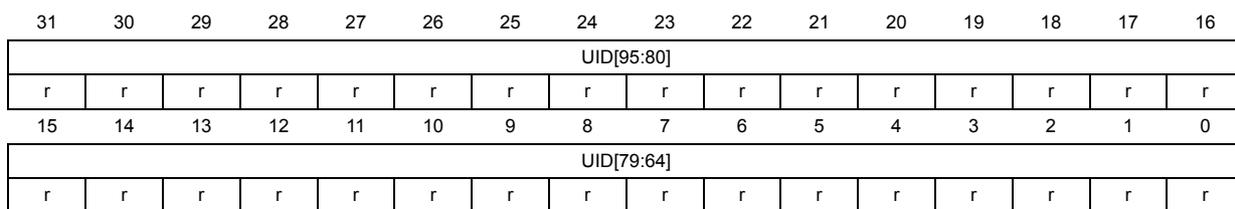

44.1.4 DESIG 96-bit unique device ID register 3 (DESIG_UIDR3)

Address offset: 0x208

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| UID[95:80] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| UID[79:64] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 UID[95:64] : LOT_NUM[55:24], lot number higher part (ASCII encoded)

44.1.5 DESIG temperature calibration 1 register (DESIG_TSCAL1R)

Address offset: 0x210

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | TS_CAL1[11:0] | |||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | ||||

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 TS_CAL1[11:0] : Factory temperature sensor calibration 1 value for ADC4

44.1.6 DESIG temperature calibration 2 register (DESIG_TSCAL2R)

Address offset: 0x240

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | TS_CAL2[11:0] | |||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:16 TS_CAL2[11:0] : Factory temperature sensor calibration 2 value for ADC4

Bits 15:0 Reserved, must be kept at reset value.

44.1.7 DESIG FLASH size data register (DESIG_FLASHSIZER)

Address offset: 0x2A0

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| RAM_SIZE[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| FLASH_SIZE[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:16 RAM_SIZE[15:0] : RAM memory size

These bits indicates the size of the device total system RAM memory in Kbytes.

As an example, 0x0040 corresponds to 64 Kbytes.

Bits 15:0 FLASH_SIZE[15:0] : Flash memory size

These bits indicates the size of the device flash memory in Kbytes.

As an example, 0x0040 corresponds to 64 Kbytes.

44.1.8 DESIG internal voltage reference calibration register (DESIG_VREFINTCALR)

Address offset: 0x2A4

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | VREFINT_CAL[11:8] | |||

| r | r | r | r | ||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| VREFINT_CAL[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:8 VREFINT_CAL[11:0] : Factory internal voltage reference calibration value for ADC4

Bits 7:0 Reserved, must be kept at reset value.

44.1.9 DESIG resistor calibration register (DESIG_RCALR)

Address offset: 0x2F0

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | R_CAL[7:0] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 R_CAL[7:0] : Resistor calibration value

44.1.10 DESIG radio gain calibration register (DESIG_RFGAINCALR)

Address offset: 0x2F4

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| GAIN4_CAL[7:0] | GAIN3_CAL[7:0] | ||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| GAIN2_CAL[7:0] | GAIN1_CAL[7:0] | ||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:24 GAIN4_CAL[7:0] : Radio gain 4 calibration value

Bits 23:16 GAIN3_CAL[7:0] : Radio gain 3 calibration value

Bits 15:8 GAIN2_CAL[7:0] : Radio gain 2 calibration value

Bits 7:0 GAIN1_CAL[7:0] : Radio gain 1 calibration value

44.1.11 DESIG IEEE 64-bit unique device ID register 1 (DESIG_UID64R1)

Address offset: 0x500

Reset value: 0xXXXX XXXX (X is factory-programmed)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| DEVNUM[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DEVNUM[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 DEVNUM[31:0] : device number

The 32-bit unique device number is a sequential number, different for each individual device.

44.1.12 DESIG IEEE 64-bit unique device ID register 2 (DESIG_UID64R2)

Address offset: 0x504

Reset value: 0x0080 E12A

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| STID[23:8] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| STID[7:0] | DEVID[7:0] | ||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:8 STID[23:0] : company ID

0x0080E1 for STMicroelectronics

Bits 7:0 DEVID[7:0] : device ID

0x2A: STM32WBA5xxx

44.1.13 DESIG register map

Table 442. DESIG register map and reset values

| Offset | Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x000 | DESIG_ PKGR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PKG[4:0] | ||||

| Reset value | x | x | x | x | x | ||||||||||||||||||||||||||||

| 0x004- 0x1FF | Reserved | ||||||||||||||||||||||||||||||||

| 0x200 | DESIG_ UIDR1 | UID[31:0] | |||||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| 0x204 | DESIG_ UIDR2 | UID[63:32] | |||||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| 0x208 | DESIG_ UIDR3 | UID[95:64] | |||||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| 0x210 | DESIG_ TSCAL1R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TS_CAL1[11:0] | |||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | |||||||||||||||||||||

| 0x214- 0x23F | Reserved | ||||||||||||||||||||||||||||||||

| 0x240 | DESIG_ TSCAL2R | Res. | Res. | Res. | Res. | TS_CAL2[11:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | |||||||||||||||||||||

| 0x248- 0x2EC | Reserved | ||||||||||||||||||||||||||||||||

| 0x2F0 | DESIG_ RCALR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | R_CAL[7:0] | |||||||

| Reset value | x | x | x | x | x | x | x | x | |||||||||||||||||||||||||

| 0x2F4 | DESIG_ RFGAINCALR | GAIN4_CAL[7:0] | GAIN3_CAL[7:0] | GAIN2_CAL[7:0] | GAIN1_CAL[7:0] | ||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| 0x2F8- 0x29F | Reserved | ||||||||||||||||||||||||||||||||

| 0x2A0 | DESIG_ FLASHSIZER | RAM_SIZE[15:0] | FLASH_SIZE[15:0] | ||||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| 0x2A4 | DESIG_ VREFINT CALR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | VREFINT_CAL[11:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | |||||||||||||||||||||

| 0x2A8- 0x4FF | Reserved | ||||||||||||||||||||||||||||||||

| 0x500 | DESIG_ UID64R1 | DEVNUM[31:0] | |||||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

| 0x504 | DESIG_ UID64R2 | STID[23:0] | DEVID[7:0] | ||||||||||||||||||||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | |

Refer to Section 2.3 for the register boundary addresses.