11. Power control (PWR)

11.1 Introduction

The power controller manages the device power supplies and power modes transitions.

11.2 PWR main features

The power controller (PWR) main features are:

- • Power supplies and supply domains

- – Core domain ( \( V_{CORE} \) )

- – \( V_{DD} \) domain

- – Analog domain ( \( V_{DDA} \) )

- – Supply for the SMPS power stage (available only on STM32WBA55xx devices)

- – Supply for the 2.4 GHz RADIO

- • System supply voltage regulation

- – SMPS step-down converter

- – Linear voltage regulator (LDO)

- • Power supply supervision

- – BOR monitor (including Power-on reset)

- – PVD monitor

- • Power management

- – Operating modes

- – Voltage scaling control

- – Low-power modes

- • GPIO retention in Standby

- • TrustZone® security and privileged protection

11.3 PWR pins and internal signals

Table 85. PWR input/output pins

| Pin name | Signal type | Description |

|---|---|---|

| VDD | Supply | Main and Backup domain supply |

| GND | Supply | Main ground |

| VDDA | Supply | Analog peripherals supply |

| VDDRF | Supply | 2.4 GHz RADIO RF supply |

| VDDRFPA | Supply | 2.4 GHz RADIO PA regulator supply |

| VDDANA (1) | Supply | 2.4 GHz RADIO analog supply |

| VDDHPA | Output | 2.4 GHz RADIO PA regulator output |

| VSS | Supply | Ground |

| VSSA (1) | Supply | Analog peripherals ground |

| VSSRF (1) | Supply | 2.4 GHz RADIO ground |

| VDD11 (1) | Input/Output | Logic supply ( \( V_{CORE} \) ) |

| VCAP (2) | Output | Logic supply ( \( V_{CORE} \) ) |

| VDDSMPS (1) | Supply | SMPS supply |

| VSSSMPS (1) | Supply | SMPS ground |

| VLXSMPS (1) | Supply | SMPS output |

1. Available only on STM32WBA55xx devices.

2. Available only on STM32WBA50/52/54xx devices.

Table 86. PWR internal input/output signals

| Internal signal name | Signal type | Description |

|---|---|---|

| WKUPx_y (x = 1 to 8, y = 1 to 4) | Input | Wake-up event source selection |

| WKUP interrupt | Output | Global WKUP pin interrupt |

| WKUP_S interrupt | Output | Global WKUP_S pin secure interrupt |

| PWR_CSLEEP | Output | CPU in Sleep mode, Sleep |

| PWR_CSTOP | Output | MCU in Stop mode, Stop |

Each of the wake-up event WKUPx can be generated from device pins or internal events, selected by WUSELx[1:0] in the PWR_WUCR3 register (x = 1 to 8). A WKUP interrupt is generated only when WKUPx is generated from a device pin. WKUPx generated from internal events are associated with an internal event interrupt.

Table 87. PWR wake-up source selection

| Wake-up event | Internal signal source (x = 1 to 8) | |||

|---|---|---|---|---|

| WKUPx_0 (WUSELx = 00) | WKUPx_1 (WUSELx = 01) | WKUPx_2 (WUSELx = 10) | WKUPx_3 (WUSELx = 11) | |

| WKUP1 | PA0 | PB2 | Reserved | Reserved |

| WKUP2 | PA4 (1) | PC13 | Reserved | Reserved |

| WKUP3 | Reserved | PA1 | PB6 | Reserved |

| WKUP4 | PA2 | PB1 | Reserved | Reserved |

| WKUP5 | Reserved | PA3 | PB7 | Reserved |

| WKUP6 | PA12 | PA5 | Reserved | rtc_alara_s or rtc_alrb_s or rtc_wut_s or RTC_TS_S (2) |

| WKUP7 | PB14 | PA6 | Reserved | rtc_alra or rtc_alrb or rtc_wut or RTC_TS (2) |

| WKUP8 | Reserved | PA7 | PB9 | tamp or tamp_s (3) |

1. Available only on STM32WBA55xx devices.

2. As enabled in the RTC interrupt and according the RTC interrupt security setting.

3. As enabled in the TAMP mask.

11.4 PWR power supplies and supply domains

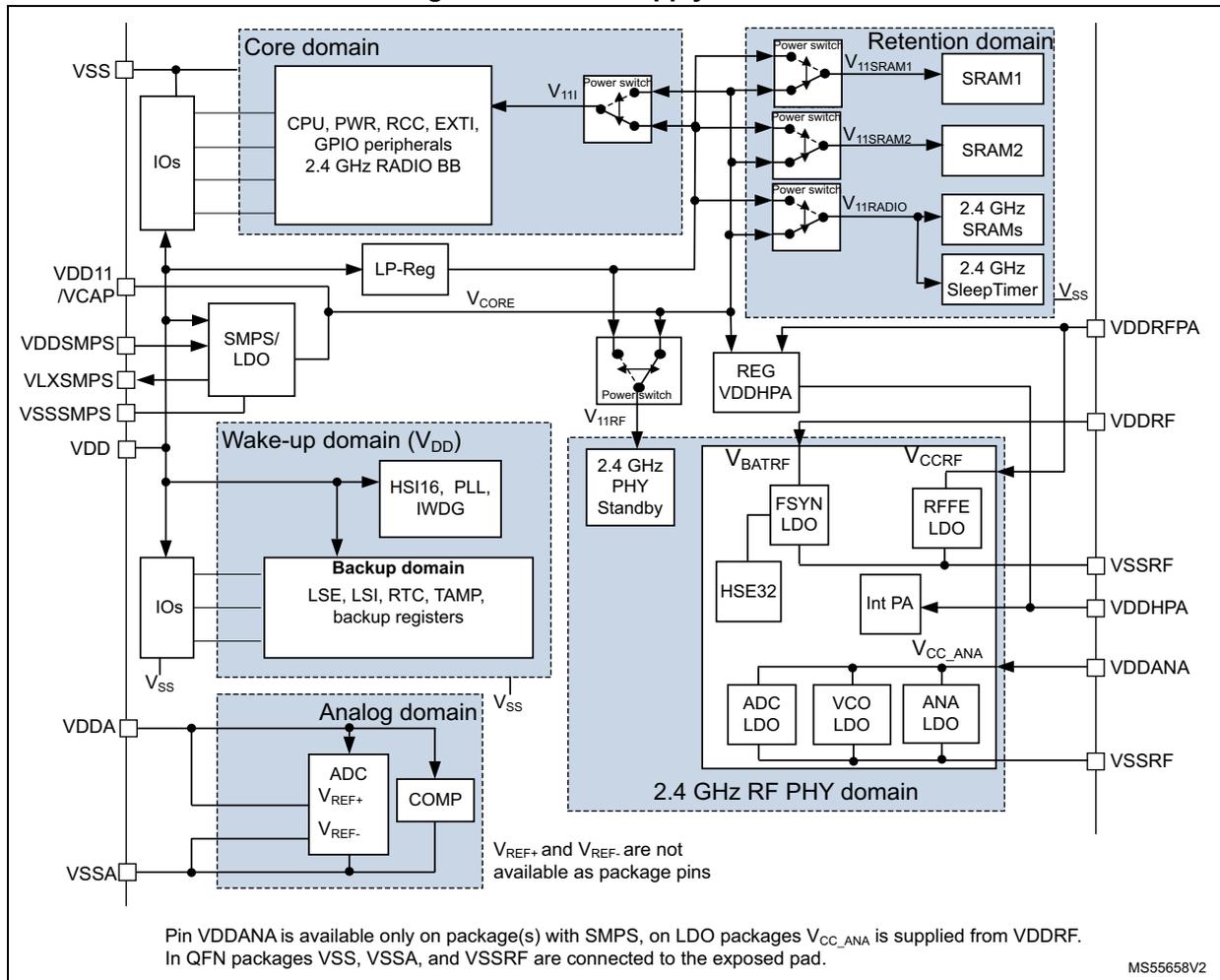

Figure 28. Power supply overview

The diagram illustrates the power supply architecture for the device, organized into several functional domains:

- Core domain: Contains CPU, PWR, RCC, EXTI, GPIO peripherals, and 2.4 GHz RADIO BB. It is powered by V CORE from the LP-Reg and connects to V 111 via a power switch.

- Retention domain: Contains SRAM1, SRAM2, 2.4 GHz SRAMs, and 2.4 GHz SleepTimer. It receives power through switches as V 11SRAM1 , V 11SRAM2 , and V 11RADIO .

- Wake-up domain (V DD ): Contains HSI16, PLL, and IWDG.

- Backup domain: Contains LSE, LSI, RTC, TAMP, and backup registers.

- Analog domain: Contains ADC (with V REF+ and V REF- ) and COMP.

- 2.4 GHz RF PHY domain: Contains 2.4 GHz PHY Standby, HSE32, Int PA, and various LDOs (FSYN, RFFE, ADC, VCO, ANA).

Key power components include:

- LP-Reg: Low-power regulator providing V CORE .

- SMPS/LDO: Main supply regulator.

- REG VDDHPA: Regulator for high power amplifier.

- Power switches: Control power distribution to SRAMs and radio components.

External pins shown include: VSS, VDD11/VCAP, VDDSMPS, VLXSMPS, VSSSMPS, VDD, VDDA, VSSA on the left; VDDRFPA, VDDRF, VSSRF, VDDHPA, VDDANA, VSSRF on the right.

V REF+ and V REF- are not available as package pins

Pin VDDANA is available only on package(s) with SMPS, on LDO packages V

CC_ANA

is supplied from VDDRF.

In QFN packages VSS, VSSA, and VSSRF are connected to the exposed pad.

MS55658V2

11.4.1 External power supplies

The devices require a 1.71 to 3.6 V \( V_{DD} \) operating voltage supply. Several independent supplies can be provided for specific peripherals. Those supplies must be provided with a valid operating supply on the \( V_{DD} \) pin:

- •

\(

V_{DD} = 1.71 \text{ V to } 3.6 \text{ V}

\)

\( V_{DD} \) is the external power supply for the I/Os, the internal regulator, and the system analog such as reset, power management, and internal clocks. It is provided externally through the \( V_{DD} \) pins. - •

\(

V_{DDA} = 1.62 \text{ to } 3.6 \text{ V}

\)

\( V_{DDA} \) is the external analog power supply for ADC and comparators. The \( V_{DDA} \) voltage level is independent from the \( V_{DD} \) voltage and must preferably be connected to \( V_{DD} \) when these peripherals are not used. - •

\(

V_{DDSMPS} = 1.71 \text{ V to } 3.6 \text{ V}

\)

(available only on STM32WBA55xx devices)

\( V_{DDSMPS} \) is the external power supply for the SMPS step-down converter. It is provided externally through \( V_{DDSMPS} \) supply pin, and must be connected to the same supply as \( V_{DD} \) pin. - • \( V_{LXSMPS} \) is the switched SMPS step-down converter output. (available only on STM32WBA55xx devices)

Note: The SMPS power supply pins are available only on specific package with SMPS step-down converter option.

- •

\(

V_{DD11}/V_{CAP} = 0.9 \text{ V to } 1.2 \text{ V}

\)

\( V_{CORE} \) is the internal power supply for the digital logic. - •

\(

V_{DDRFP A} = 0 \text{ V to } 3.6 \text{ V}

\)

(must be above 1.2 V for 2.4 GHz RADIO operation).

\( V_{DDRFP A} \) must be equal to or lower than \( V_{DDRF} \) .

\( V_{DDRFP A} \) is the external power supply for the 2.4 GHz RADIO front-end part and PA.- – \( V_{DDRFP A} \) when connected to \( V_{DD11} \) supports a transmit maximum low output power

- – \( V_{DDRFP A} \) when connected to \( V_{DD} \) supports a transmit maximum high output power

- •

\(

V_{DDANA} = 0 \text{ V to } 3.6 \text{ V}

\)

(must be above 1.2 V for 2.4 GHz RADIO operation), available only on STM32WBA55xx devices).

\( V_{DDANA} \) must be equal to or lower than \( V_{DDRF} \) .

\( V_{DDANA} \) is the external power supply for the 2.4 GHz RADIO part, can be connected to \( V_{DD11} \) .

Note: The VDDANA supply pin is available only on specific packages with SMPS step-down converter option. In packages with only LDO support, VDDANA is double bonded with VDDRF.

- •

\(

V_{DDRF} = 1.71 \text{ V to } 3.6 \text{ V}

\)

\( V_{DDRF} \) is the external power supply for the 2.4 GHz RADIO IF part. \( V_{DDRF} \) must always be connected to the supply used for \( V_{DD} \) . - •

\(

V_{DDHPA} = 0.9 \text{ V to } 2.3 \text{ V}

\)

\( V_{DDHPA} \) is the internal power supply for the 2.4 GHz RADIO power amplifier.

11.4.2 Application RADIO power supply schemes

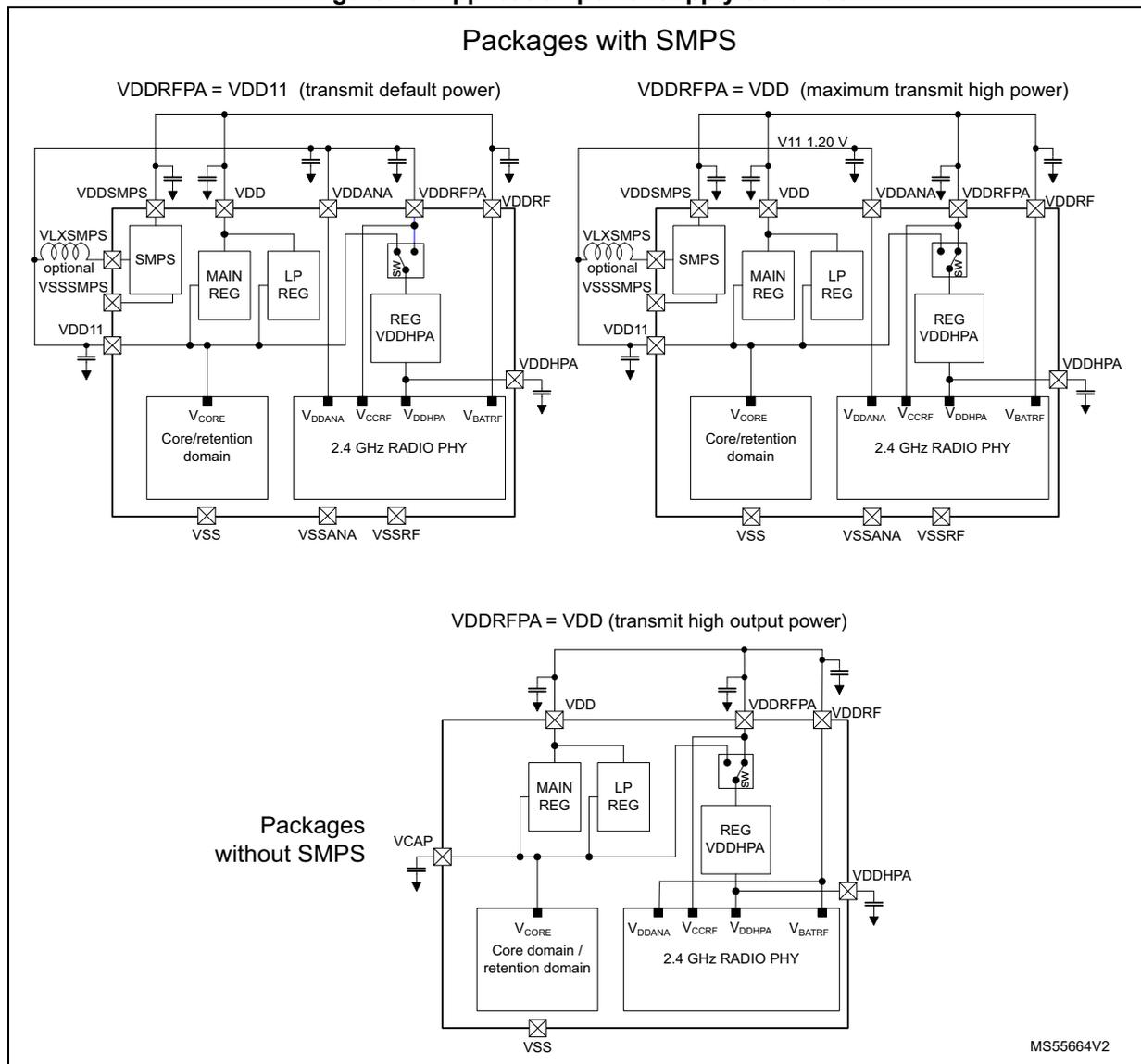

The device supports different supply schemes, as shown in Figure 29 . The maximum achievable transmit output power from the 2.4 GHz RADIO internal PA is linked to the supply scheme.

- • In packages supporting an SMPS, a maximum transmit low output power can be reached with lowest power consumption. In this power scheme \( V_{DDRFA} \) is connected to \( V_{DD11} \) , and REGVDDHPA is connected to V11 internal selected by REGPASEL register bit.

- • In all other power schemes \( V_{DDRFA} \) is connected to \( V_{DD} \) , allowing maximum transmit high output power.

Figure 29. Application power supply schemes

Packages with SMPS

VDDRFA = VDD11 (transmit default power)

VDDRFA = VDD (maximum transmit high power)

Packages without SMPS

VDDRFA = VDD (transmit high output power)

MS55664V2

11.4.3 Power-up and power-down power sequences

During power-up and power-down phases, respect the following requirements:

- • When \( V_{DD} \) is below 1 V, other power supplies ( \( V_{DDA} \) , \( V_{DDRF} \) ) must remain below \( V_{DD} + 300 \) mV.

- • When \( V_{DD} \) is above 1 V, all power supplies are independent.

During the power-down phase, \( V_{DD} \) can temporarily become lower than other supplies only if the energy provided to the MCU remains below 1 mJ; this allows external decoupling capacitors discharge with different time constants during the power-down transient phase.

11.4.4 Independent analog peripherals supply

To improve A/D conversion accuracy and 2.4 GHz RADIO performance, and to extend the supply flexibility, the analog and 2.4 GHz RADIO peripherals have independent power supplies that can be separately filtered and shielded from noise on the PCB:

- • the analog peripherals voltage supply input is available on a separate \( V_{DDA} \) pin

- • the 2.4 GHz RADIO peripheral voltage supply input is available on separate \( V_{DDRF} \) , \( V_{DDANA} \) , and \( V_{DDRFP} \) pins.

The \( V_{DDA} \) supply voltage can be different from \( V_{DD} \) . The \( V_{DDA} \) must be present before enabling any of the analog peripherals supplied by \( V_{DDA} \) (ADC4 and COMP).

When a single supply is used, \( V_{DDA} \) can be externally connected to \( V_{DD} \) through the external filtering circuit to ensure a noise-free \( V_{DDA} \) voltage.

11.4.5 Radio peripherals supply

The 2.4 GHz RADIO \( V_{DDRF} \) , \( V_{DDANA} \) , and \( V_{DDRFP} \) supply voltages can be different from \( V_{DD} \) . The supplies must be present before enabling the 2.4 GHz RADIO.

When a single supply is used, \( V_{DDRF} \) , \( V_{DDANA} \) , and \( V_{DDRFP} \) supplies can be externally connected to \( V_{DD} \) through external filtering circuitry to ensure noise-free supply voltage.

In devices with SMPS, \( V_{DDANA} \) can be externally connected to \( V_{DD11} \) through external filtering circuitry to ensure noise-free supply voltage.

In devices with SMPS, for low transmit output power applications \( V_{DDRFP} \) can be externally connected to \( V_{DD11} \) through external filtering circuitry to ensure noise-free supply voltage.

11.4.6 Backup domain

The backup domain contains the RTC, TAMP, backup registers, LSE and LSI oscillators, and is directly supplied from \( V_{DD} \) pin.

Backup domain access

After a system reset, the Backup domain (RCC Backup domain control register

RCC_BDCR1

, RTC registers, TAMP registers, backup registers) is protected against possible unwanted write accesses. To enable access to the Backup domain, proceed as follows:

- 1. Enable the power interface clock by setting the PWREN bits in the Section 12.8.22: RCC AHB4 peripheral clock enable register (RCC_AHB4ENR) .

- 2. Set the DBP bit in the PWR disable Backup domain register (PWR_DBPR) to enable access to the Backup domain.

11.4.7 Internal regulators

The devices embed two regulators: one LDO and one SMPS in parallel to provide the \( V_{CORE} \) (for digital peripherals, SRAM and embedded flash memory). Both regulators generate this voltage on VDD11/VCAP pins. The SMPS is available only on STM32WBA55xx devices.

Both regulators can provide two different voltage ranges (voltage scaling) and can operate in Run and Stop modes.

It is possible to switch from SMPS to LDO and from LDO to SMPS and change range on the fly (when the 2.4 GHz RADIO is not active).

Other internal supplies for the 2.4 GHz RADIO are generated for the dedicated regulator.

11.5 PWR system supply voltage regulation

11.5.1 SMPS and LDO embedded regulators

All devices embed an internal linear voltage regulator (LDO). STM32WBA55xx devices embed also an internal SMPS step-down converter, which can be selected when the application runs, depending upon application requirements.

The SMPS allows the power consumption to be reduced. Some peripherals can be perturbed by the noise generated by the SMPS, requiring the application to switch to LDO when running this peripheral, to reach the best performances.

The LDO and the SMPS regulators have two modes, namely Main regulator mode (used when performance is needed), and Low-power regulator mode. LDO or SMPS can be used in all voltage scaling ranges, and in all Stop modes and Standby with retention mode.

11.5.2 LDO and SMPS versus reset, voltage scaling, and low-power modes

After BOR0 power-on reset and system reset, the LDO regulator is enabled, in range 2. Switching to the SMPS regulator provides lower consumption in particular for high \( V_{DD} \) voltages. It is possible to switch from LDO to SMPS, or from SMPS to LDO in any range, by configuring the REGSEL register bit.

When exiting from Stop or Standby retention modes, the regulator is the same used to enter the low-power mode. When exiting from Standby modes, the LDO regulator is always used to startup. When Standby has been entered from the SMPS regulator, after exiting Standby with the LDO, the regulator is switched automatically to SMPS regulator.

When exiting from Stop 0 modes the voltage range is the same as on entering Stop 0 mode. When exiting from Stop 1 and Standby modes the voltage range 2 is used.

When the 2.4 GHz RADIO is active, the regulator and range cannot be changed. Any requested regulator or range change while the 2.4 GHz RADIO is active is suspended and takes effect only after the 2.4 GHz RADIO and PHY have entered Sleep or Deepsleep mode.

11.5.3 LDO and SMPS step-down converter fast startup

After BOR0 power-on reset, the LDO regulator starts in high-power mode and in slow-startup mode. The slow-startup feature is selected to limit the inrush current after power-on reset. This increases the wake-up time also when exiting Standby modes.

It is possible to configure fast-startup on the fly and it is applied for next startup either after a system reset or wake-up from Standby mode. The fast-startup is selected by setting the FSTEN bit in the PWR_CR3 register. Fast-startup selection applies to both LDO and SMPS regulators.

11.5.4 Dynamic voltage scaling management

The dynamic voltage scaling is a power management technique that consists in increasing or decreasing the voltage used for the digital peripherals ( \( V_{CORE} \) ), according to the application performance and power consumption needs.

Dynamic voltage scaling to increase \( V_{CORE} \) is known as overvolting. This is used to improve device performance.

Dynamic voltage scaling to decrease \( V_{CORE} \) is known as undervolting. It is performed to save power, particularly in devices where the energy comes from a battery and is thus limited.

The regulator operates in the following ranges:

- • Range 1: high performance

It allows a system clock frequency up to 100 MHz, and is required for any 2.4 GHz RADIO transmit and receive operation.

When the 2.4 GHz RADIO is active the range cannot be changed. Any requested range change while the 2.4 GHz RADIO is active is suspended and only takes effect after the 2.4 GHz RADIO and PHY have entered Sleep or DeepSleep mode.

- • Range 2: low-power range

The system clock frequency can be up to 16 MHz. The 2.4 GHz RADIO cannot transmit nor receive.

Voltage scaling is selected through the VOS bit in the PWR_VOSR register.

The sequence to switch the voltage scaling from range 2 to range 1 is the following:

- 1. Program the VOS to range 1 in the PWR_VOSR

- 2. Wait until the VOSRDY flag is set in the PWR_VOSR

- 3. If target SYSCLK > 50 MHz

- a) Switch on the PLL1 oscillator source

- b) Select the PLL1 clock source in PLL1SRC in the RCC_PLL1CFGR

- 4. Adjust number of wait states according to the new target SYSCLK frequency. Flash LATENCY in the FLASH_ACR, and SRAM WSC in the RAMCFG_MxCR.

- 5. Configure and enable the PLL1 is needed

- 6. Switch to the new SYSCLK frequency.

The sequence to switch the voltage scaling from range 1 to range 2 is the following:

- 1. Switch to the SYSCLK frequency \( \leq 16 \) MHz

- 2. Adjust number of wait states according to the new target SYSCLK frequency. Flash LATENCY in the FLASH_ACR, and SRAM WSC in the RAMCFG_MxCR.

- 3. Disable the PLL1

- 4. Program the VOS to range 2 in the PWR_VOSR

- 5. Optionally wait until the ACTVOS in the PWR_SVMSR = VOS in the PWR_VOSR and ACTVOSRDY flag is set in PWR_SVMSR

Note: When switching the voltage scaling, the sequence must be completed (VOS = ACTVOS and ACTVOSRDY = 1) before entering Stop or Standby modes. When the 2.4 GHz RADIO is active (PWR_RADIOSCR.MODE = active) the system does not enter low-power mode and the CPU can enter Deepsleep mode independently from VOS, ACTVOS and ACTVOSRDY.

11.5.5 2.4 GHz RADIO PA regulator

The PA regulator REG VDDHPA is used to supply the 2.4 GHz RADIO internal PA with the correct voltage level \( V_{DDHPA} \) for a given transmit output power. This regulator output voltage \( V_{DDHPA} \) is controlled from the 2.4 GHz RADIO link layer software. \( V_{DDHPA} \) maximum supply level and associated maximum transmit output power is depended on the application supply scheme. See Section 11.4.2: Application RADIO power supply schemes .

The application software can control the REG VDDHPA regulator input voltage.

- • Force the input voltage selection of the REG VDDHPA regulator to be from VDDRFPA pin by setting the REGPASEL register bit.

- – When the REG VDDHPA regulator input voltage is forced to VDDRFPA, power consumption at low transmit output power is higher. Lowering noise in the RADIO which may improve the transmit spectrum and receiver sensitivity.

- • Allow the 1.2 V

\(

V_{DDHPA}

\)

voltage level to be generated directly from the VDD11 supply via the REGPABYPEN register bit. This can be selected only when VDD11 is supplied from the device SMPS. This is available only when the input voltage of the REG VDDHPA regulator is not forced to VDDRFPA.

- – When the SMPS is used, allowing the 1.2 V \( V_{DDHPA} \) voltage level to be generated directly from the VDD11 lowers power consumption at the transmit output levels using this supply level at the cost of introducing more noise in the RADIO which may impact the transmit spectrum and receiver sensitivity.

The required REG VDDHPA regulator supply source configuration in REGPASEL and REGPABYPEN must be set before using the regulator. When the REG VDDHPA regulator is used, REGPASEL and REGPABYPEN must not be changed.

The REG VDDHPA is forced off, discharging the external capacitor, in all Standby modes.

For more information on the 2.4 GHz RADIO transmit output power and REG VDDHPA regulator control see Section 9.4.3: Transmit output power .

11.6 PWR power supply supervision

11.6.1 Brownout reset (BOR)

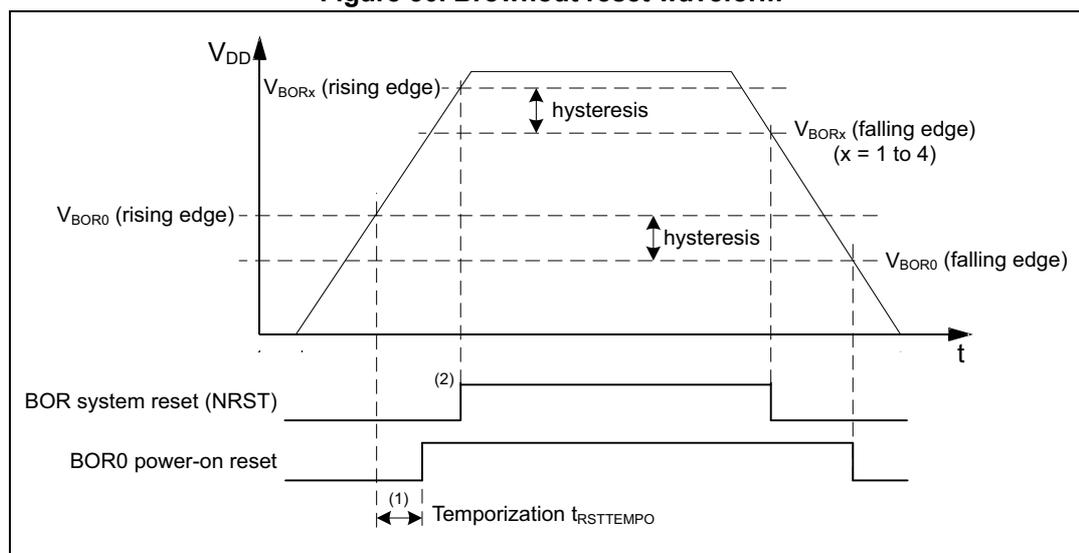

The device has an integrated BOR (brownout reset) circuitry. The BOR is active in all power modes, and cannot be disabled. The BOR reset also generates a system reset on pin NRST.

Five BOR thresholds can be selected through option bytes. A power-on reset is always generated at the \( V_{BOR0} \) thresholds.

The Backup domain is supplied by \( V_{DD} \) and is reset by the \( V_{BOR0} \) thresholds.

The other \( V_{BORx} \) ( \( x = 1 \) to \( 4 \) ) thresholds keep most of the device under system reset until the supply voltage \( V_{DD} \) reaches the specified threshold. When \( V_{DD} \) drops below the selected threshold, a system reset on pin NRST is generated. When \( V_{DD} \) is above the \( V_{BORx} \) upper limit, the system reset on pin NRST is released and the system can start.

For more details on the brownout reset thresholds, refer to the electrical characteristics section in the datasheet.

During Stop 1 and Standby modes, it is possible to set the BOR0 in Ultra-low power (discontinuous) mode to further reduce the current consumption by setting the ULPMEN bit in PWR control register 1 (PWR_CR1) .

Warning: In Ultra-low power mode, the supply monitoring is discontinuous and may not detect fast drops in supply, hence it must not be used together with autonomous peripherals using HSI16 as kernel clock.

Figure 30. Brownout reset waveform

- 1. The reset temporization \( t_{RSTTEMPO} \) is present only for the BOR0 lowest threshold ( \( V_{BOR0} \) ).

- 2. The rising edge of the system reset NRST can be driven from the \( V_{BOR0} \) power-on reset or \( V_{BORx} \) ( \( x = 1 \) to \( 4 \) ) rising threshold depend on the \( V_{DD} \) rising slope.

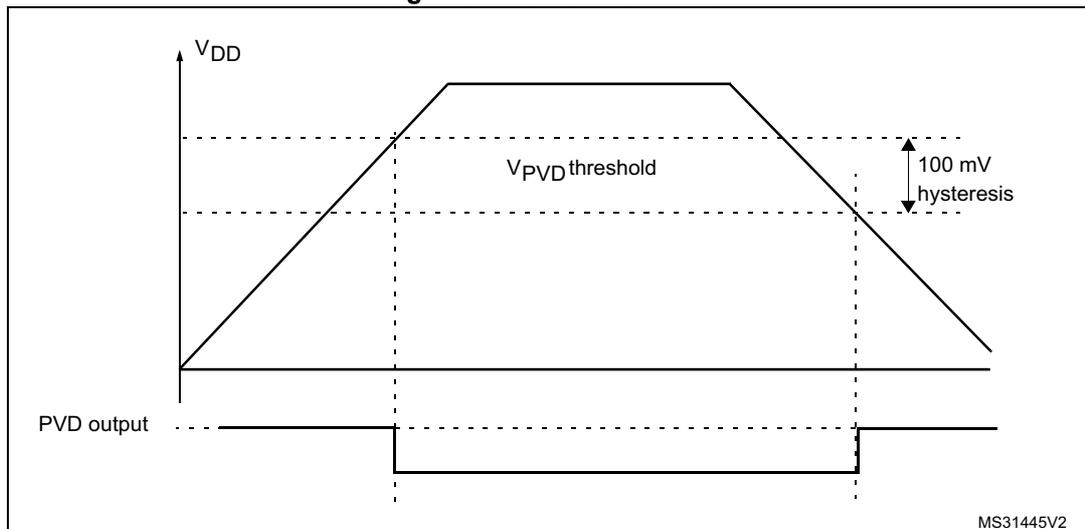

11.6.2 Programmable voltage detector (PVD)

The PVD can be used to monitor the \( V_{DD} \) power supply by comparing it to a threshold selected by the PVDLS[2:0] bits in the PWR supply voltage monitoring control register (PWR_SVMCR) . Also the PVD can be used to monitor an analog signal on the PVD_IN I/O by comparing it to the \( V_{REFINT} \) threshold. The PVD is enabled by setting the PVDE bit.

A PVDO flag is available in the PWR supply voltage monitoring status register (PWR_SVMR) to indicate if \( V_{DD} \) is higher or lower than the PVD threshold. This event is internally connected to the EXTI and can generate an interrupt if enabled through the EXTI registers (refer to Table 97 ).

The rising/falling edge sensitivity of the EXTI line must be configured according to PVD output behavior. For example, if the EXTI line is configured to rising edge sensitivity, the interrupt is generated when \( V_{DD} \) drops below the PVD threshold. As an example the service routine can perform emergency shutdown tasks.

The PVD can remain active in Stop 0, Stop 1 modes, and the PVD interrupt can wake up the system from the Stop modes. The PVD is not functional in Standby mode.

Figure 31. PVD thresholds

The figure illustrates the relationship between the supply voltage \( V_{DD} \) and the PVD output. The top graph shows \( V_{DD} \) rising from a low value to a peak and then falling. Two horizontal dashed lines represent the threshold levels. The upper dashed line is the rising threshold, and the lower dashed line is the falling threshold, with a 100 mV hysteresis between them. The label \( V_{PVD} \) threshold is placed between these lines. Vertical dashed lines indicate the points where \( V_{DD} \) crosses these thresholds. The bottom graph shows the PVD output signal. It is high when \( V_{DD} \) is below the threshold and transitions to low when \( V_{DD} \) rises above the upper threshold. Conversely, it transitions from low to high when \( V_{DD} \) falls below the lower threshold.

11.7 PWR power management

11.7.1 PWR power modes

By default, the microcontroller is in Run mode range 2 and the 2.4 GHz RADIO in DeepSleep after a system or a power reset. Several low-power modes are available to save power when the CPU or peripherals do not need to be kept running, for example when waiting for an external event. It is up to the user to select the mode that gives the best compromise between low-power consumption, short startup time and available wake-up sources.

The device features these low-power modes:

- • Run mode:

The CPU is running. The power consumption can be reduced by slowing down the system clocks and configuring voltage scaling to lower-power range, and/or gating the clocks to the APB and AHB peripherals when they are not used. - • Sleep mode:

CPU clock off, all peripherals including Cortex-M33 core such as NVIC and SysTick can run and wake up the CPU when an interrupt or an event occurs. Refer to Section 11.7.5 . - • Stop 0, Stop 1 modes:

Stop modes achieve the lowest power consumption while retaining the registers content. The SRAM content can be selected to be retained or not. All clocks (except some autonomous peripherals bus and kernel clocks) in the Core domain are stopped. The PLL and HSE32 crystal oscillator are disabled. The HSI16 RC oscillator is disabled when not activated as autonomous peripheral bus or kernel clock. The LSE or LSI can still run.

Some peripherals are autonomous and can operate in Stop modes by requesting their kernel clock, and in Stop 0 mode also when requesting their bus clock when needed. When a peripheral requests its (APB or AHB) bus clock, for example to transfer data with GPDMA1, the device transitions from Stop 1 to Stop 0 mode.

The I2C, USART, LPUART, SPI, LPTIM, ADC, RTC can remain active in Stop modes when kernel clock is LSE, LSI, or HSI16. The 2.4 GHz RADIO can remain active in Stop 0 mode on its kernel clock HSE32. In Stop 0 mode the autonomous peripherals bus clock can remain active using HSI16.

The brownout reset (BOR) remains always active, and the PVD can be kept active in Stop modes. In Stop 1 mode the BOR0 can be configured in ultra-low power mode to further reduce power consumption.

Warning: Ultra-low power mode must not be used together with autonomous peripherals using HSI16 as kernel clock.

In Stop 0 mode, the regulator remains in main regulator mode, allowing a very fast wake-up time but with higher consumption compared with Stop 1.

The system clock when exiting from Stop mode is HSI16 at 16 MHz.

Refer to Section 11.7.6 , and Section 11.7.7 .

- • Standby mode:

The Standby mode is used to achieve the lowest power consumption. The internal regulator is switched off so that the Core domain is powered off. The PLL, the HSI16 RC, and the HSE32 crystal oscillators are also switched off. The LSE or LSI can still run. The RTC and TAMPER can remain active in Standby modes when kernel clock is LSE or LSI.

The BOR always remains active in Standby mode. The BOR can be configured in ultra-low power mode to further reduce power consumption during standby mode.

The state of each I/O during Standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

When entering Standby mode register contents are lost except for registers in the Backup domain and Standby circuitry.

Optionally, the full SRAM1 and/or SRAM2 can be retained in Standby mode, supplied by the low-power regulator (Standby with retention mode).

Optionally, the 2.4 GHz RADIO sleep Timer, RXTXRAM, and sequence SRAM can be retained in Standby mode, supplied by the low-power regulator (Standby with retention mode).

The device exits Standby mode when an NRST pin external reset, an IWDG early interrupt or reset, WKUP pin event (configurable rising or falling edge), an RTC event occurs (alarm, periodic wake-up, timestamp), a TAMP tamper detection, or a 2.4 GHz RADIO sleep timer event (available only in Standby with retention mode). The tamper detection can be raised either due to external pins or due to an internal failure detection.

The system clock after wake-up is HSI16 16 MHz.

Refer to Section 11.7.8 .

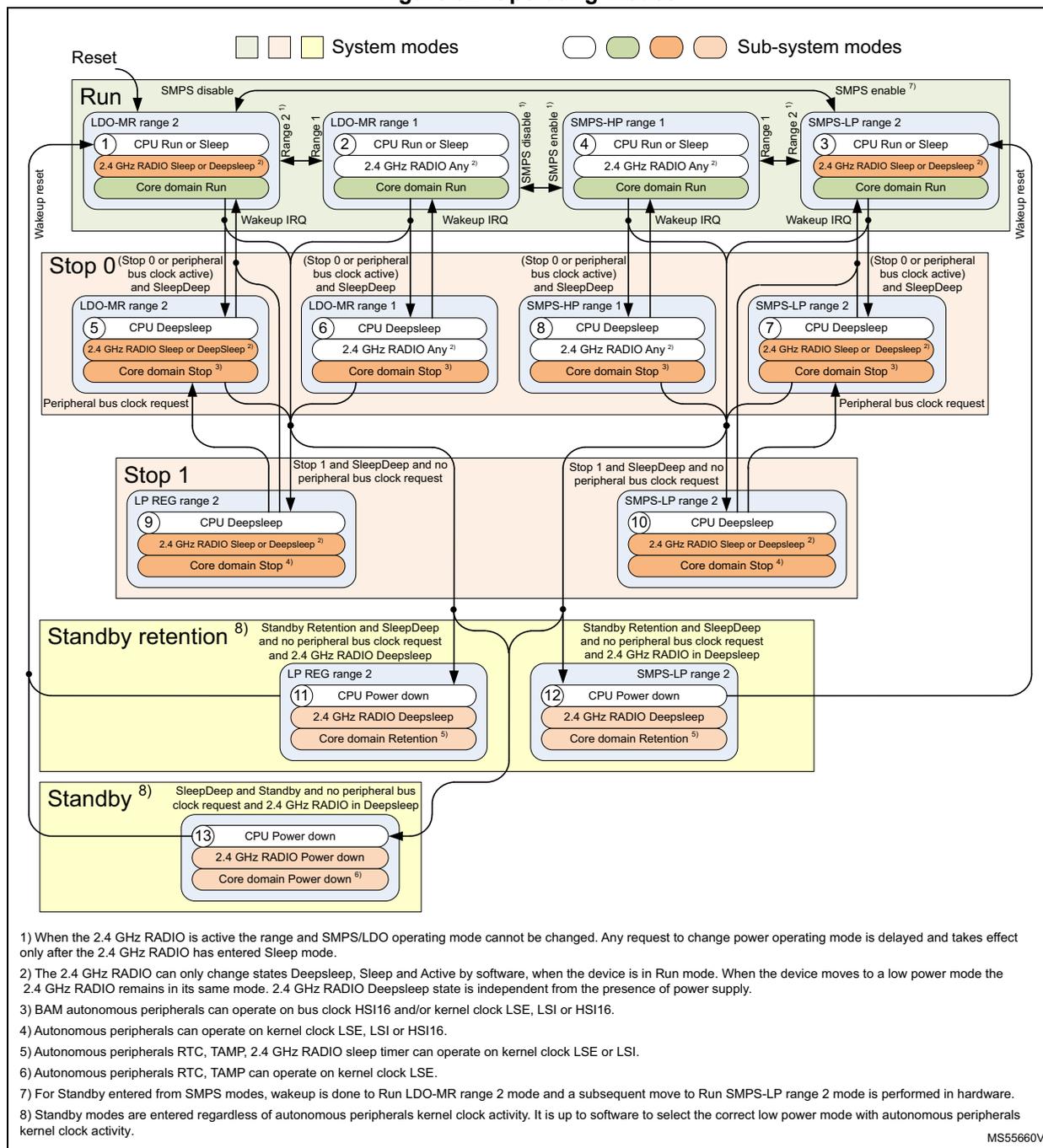

The operating modes and transitions are shown in Figure 32 .

Figure 32. Operating modes

Legend:

- System modes: Run (Green), Stop 0 (Light Orange), Stop 1 (Orange), Standby retention (Yellow), Standby (Yellow)

- Sub-system modes: (White, Light Green, Orange, Light Orange)

Transitions:

- Run to Stop 0: Triggered by 'Stop 0 or peripheral bus clock active) and SleepDeep'.

- Stop 0 to Run: Triggered by 'Wakeup IRQ' or 'Peripheral bus clock request'.

- Stop 0 to Stop 1: Triggered by 'Stop 1 and SleepDeep and no peripheral bus clock request'.

- Stop 1 to Stop 0: Triggered by 'Peripheral bus clock request'.

- Stop 1 to Standby retention: Triggered by 'Standby Retention and SleepDeep and no peripheral bus clock request and 2.4 GHz RADIO in DeepSleep'.

- Standby retention to Stop 1: Triggered by 'Stop 1 and SleepDeep and no peripheral bus clock request'.

- Standby retention to Standby: Triggered by 'SleepDeep and Standby and no peripheral bus clock request and 2.4 GHz RADIO in DeepSleep'.

- Standby to Standby retention: Triggered by 'Standby Retention and SleepDeep and no peripheral bus clock request and 2.4 GHz RADIO in DeepSleep'.

- Standby to Run: Triggered by 'Wakeup reset'.

- Run internal transitions: Between LDO-MR and SMPS ranges, controlled by 'SMPS disable', 'SMPS enable', 'Range 1', and 'Range 2'.

System modes details:

- Run:

- LDO-MR range 2: CPU Run or Sleep, 2.4 GHz RADIO Sleep or DeepSleep 2 , Core domain Run.

- LDO-MR range 1: CPU Run or Sleep, 2.4 GHz RADIO Any 2 , Core domain Run.

- SMPS-HP range 1: CPU Run or Sleep, 2.4 GHz RADIO Any 2 , Core domain Run.

- SMPS-LP range 2: CPU Run or Sleep, 2.4 GHz RADIO Sleep or DeepSleep 2 , Core domain Run.

- Stop 0:

- LDO-MR range 2: CPU DeepSleep, 2.4 GHz RADIO Sleep or DeepSleep 2 , Core domain Stop 3 .

- LDO-MR range 1: CPU DeepSleep, 2.4 GHz RADIO Any 2 , Core domain Stop 3 .

- SMPS-HP range 1: CPU DeepSleep, 2.4 GHz RADIO Any 2 , Core domain Stop 3 .

- SMPS-LP range 2: CPU DeepSleep, 2.4 GHz RADIO Sleep or DeepSleep 2 , Core domain Stop 3 .

- Stop 1:

- LP REG range 2: CPU DeepSleep, 2.4 GHz RADIO Sleep or DeepSleep 2 , Core domain Stop 4 .

- SMPS-LP range 2: CPU DeepSleep, 2.4 GHz RADIO Sleep or DeepSleep 2 , Core domain Stop 4 .

- Standby retention:

- LP REG range 2: CPU Power down, 2.4 GHz RADIO DeepSleep, Core domain Retention 5 .

- SMPS-LP range 2: CPU Power down, 2.4 GHz RADIO DeepSleep, Core domain Retention 5 .

- Standby:

- LP REG range 2: CPU Power down, 2.4 GHz RADIO Power down, Core domain Power down 6 .

Notes:

- When the 2.4 GHz RADIO is active the range and SMPS/LDO operating mode cannot be changed. Any request to change power operating mode is delayed and takes effect only after the 2.4 GHz RADIO has entered Sleep mode.

- The 2.4 GHz RADIO can only change states DeepSleep, Sleep and Active by software, when the device is in Run mode. When the device moves to a low power mode the 2.4 GHz RADIO remains in its same mode. 2.4 GHz RADIO DeepSleep state is independent from the presence of power supply.

- BAM autonomous peripherals can operate on bus clock HSI16 and/or kernel clock LSE, LSI or HSI16.

- Autonomous peripherals can operate on kernel clock LSE, LSI or HSI16.

- Autonomous peripherals RTC, TAMP, 2.4 GHz RADIO sleep timer can operate on kernel clock LSE or LSI.

- Autonomous peripherals RTC, TAMP can operate on kernel clock LSE.

- For Standby entered from SMPS modes, wakeup is done to Run LDO-MR range 2 mode and a subsequent move to Run SMPS-LP range 2 mode is performed in hardware.

- Standby modes are entered regardless of autonomous peripherals kernel clock activity. It is up to software to select the correct low power mode with autonomous peripherals kernel clock activity.

MS55660V4

Table 88 shows the power modes overview.

Table 88. Low-power mode summary

| Name | Entry | Wake-up source (1) | Wake-up system clock | Effect on clocks | Voltage regulator (2) |

|---|---|---|---|---|---|

| Sleep | WFI or Return from ISR | Any interrupt | Same as before entering Sleep mode | CPU clock OFF No effect on other clocks or analog clock sources | Main regulator range 1, 2 (SMPS or LDO) |

| WFE SEVONPEDND = 0 | Wake-up event | ||||

| WFE SEVONPEDND = 1 | Any interrupt, wake-up event | ||||

| Stop 0 | (LPMS = Stop 0 or autonomous peripheral bus clock request active) + SLEEPDEEP bit + WFI or Return from ISR or WFE | Any EXTI line, autonomous peripherals, 2.4 GHz RADIO sleep timer event, IWDG event, RTC event, TAMP event, WKUP event, NRST external reset, BOR reset (only in Stop 0 range 1. HSECSS event) | HSI16 at 16 MHz | All clocks OFF except LSE, LSI and HSI16 or HSE32 when requested as autonomous peripheral kernel or bus clock | Low-power regulator (SMPS or LDO) |

| Stop 1 | (LPMS = Stop 1 and no autonomous peripheral bus clock request) + SLEEPDEEP bit + WFI or Return from ISR or WFE | All clocks OFF except LSE, LSI and HSI16 when requested as autonomous peripheral kernel clock. | |||

| Standby with retention | (LPMS = Standby + (R[2:1]RSB or RADIORSB != 0) and no autonomous peripheral bus clock request and 2.4 GHz RADIO mode = Deepsleep) + SLEEPDEEP bit + WFI or Return from ISR or WFE | 2.4 GHz RADIO sleep timer event, IWDG event, RTC event, TAMP event, WKUP event, NRST external reset, BOR reset | All clocks OFF except LSI and LSE | OFF | |

| Standby | (LPMS = Standby + (R[2:1]RSB and RADIORSB = 0) and no autonomous peripheral bus clock request and 2.4 GHz RADIO mode = Deepsleep) + SLEEPDEEP bit + WFI or Return from ISR or WFE | IWDG event, RTC event, TAMP event, WKUP event, NRST external reset, BOR reset |

1. Refer to Table 89 .

2. SMPS is available only on STM32WBA55xx devices.

Table 89. Functionalities depending on the working mode (1)| Peripheral | Run/Sleep | Stop 0 | Stop 1 | Standby retention | Standby | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Range 1 | Range 2 | Range 1 | Range 2 | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | |

| CPU | A | R | - | R | - | - | - | - | |||

| ICACHE | O | R | - | R | - | - | - | - | |||

| Flash memory | O (2) | R | - | R | R | - | R | - | |||

| SRAM1 | A | O | - | O | O | - | - | - | |||

| SRAM2 | A | O | Y | O | O | - | - | - | |||

| Backup registers | A | R | - | R | R | - | R | - | |||

| 2.4 GHz RADIO | O | R | O | R | Y | R | - | - | - | - | - |

| 2.4 GHz RADIO SRAM | O | R | O | R | - | R | - | O | - | - | - |

| 2.4 GHz RADIO Sleep timer | O | O | O | O | Y | O | Y | O | Y | - | - |

| BOR | A | A | Y | A | A | Y | A | Y | |||

| PVD | O | O | O | O | - | - | - | - | |||

| HSI16 clock | O | O (3) | - | O (3) | - | - | - | - | |||

| HSE32 clock | O | O (4) | - | - | - | - | - | - | - | - | |

| LSI clock | O | O | - | O | O | - | O | - | |||

| LSE clock | O | O | - | O | O | - | O | - | |||

| CSSHSE clock security | O | O | - | Y | - | - | - | - | - | - | |

| CSSLSE clock security | O | O | Y | O | O | Y | O | Y | |||

| RTC | O | O | Y | O | O | Y | O | Y | |||

| TAMP | O | O | Y | O | O | Y | O | Y | |||

| GPIO | O | R (5) | Y (6) | - | R (5) | Y (6) | R (7) | Y (8) | R (7) | Y (8) | |

| IWDG | O | O | Y | O | O | Y | O | Y | |||

| GPDMA1 | O | O | Y | R (9) | - | - | - | - | - | ||

| USARTx (x = 1, 2 (10) ) | O | O | Y | O | - | - | - | - | |||

| LPUART1 | O | O | Y | O | - | - | - | - | |||

| I2Cx (x = 1 (10) , 3) | O | O | Y | O | - | - | - | - | |||

| SPIx (x= 1 (10) , 3) | O | O | Y | O | - | - | - | - | |||

| ADC4 | O | O | Y | O | - | - | - | - | |||

| COMPx (11) (x = 1, 2) | O | O | Y | O | - | - | - | - | |||

| Temperature sensor | O | O (12) | Y (12) | - | O (12) | Y (12) | - | - | - | - | |

| Peripheral | Run/Sleep | Stop 0 | Stop 1 | Standby retention | Standby | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Range 1 | Range 2 | Range 1 | Range 2 | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | |

| LPTIMx (x = 1, 2 (10) ) | O | O | Y | O | Y | - | - | - | - | ||

| TIMx (x = 1, 2, 3 (10) , 16, 17 (10) ) | O | R | - | R | - | - | - | - | - | ||

| SAI1 (11) | O | R | - | R | - | - | - | - | - | ||

| TSC | O | R | - | R | - | - | - | - | - | ||

| RNG | O | R | - | R | - | - | - | - | - | ||

| AES | O | R | - | R | - | - | - | - | - | ||

| SAES (10) | O | R | - | R | - | - | - | - | - | ||

| HSEM | O | R | - | R | - | - | - | - | - | ||

| PKA | O | R | - | R | - | - | - | - | - | ||

| HASH | O | R | - | R | - | - | - | - | - | ||

| CRC | O | R | - | R | - | - | - | - | - | ||

| WWDG | O | R | - | R | - | - | - | - | - | ||

| GTZC_TZSC (10) | O | R | - | R | - | - | - | - | - | ||

| GTZC_TZIC (10) | O | R | - | R | - | - | - | - | - | ||

| GTZC_MPCBB1 (10) | O | R | - | R | - | - | - | - | - | ||

| GTZC_MPCBB2 (10) | O | R | - | R | - | - | - | - | - | ||

| GTZC_MPCBB6 (10) | O | R | - | R | - | - | - | - | - | ||

| SysTick timer | O | R | - | R | - | - | - | - | - | ||

| Debug | O | O (13) | - | O (13) | - | O (14) | - | O (14) | - | ||

- 1. A = Active, Y = yes. O = optional (can be enabled/disabled by software). R = Retained, - = not available. Gray cells highlight the wake-up capability in each mode.

- 2. The flash memory can be configured in power-down mode.

- 3. Some peripherals with autonomous mode and wake-up from Stop capability can request HSI16 to be enabled. In this case, the oscillator is woken up by the peripheral, and is automatically put off when no peripheral needs it.

- 4. For the autonomous 2.4 GHz RADIO the HSE32 can be kept running.

- 5. GPIO pins from peripherals supporting autonomous mode are still operational.

- 6. Only GPIOs with enabled wake-up functionality in the EXTI or WKUP are able to wake up the system.

- 7. GPIO level retention in Standby modes can be enabled.

- 8. Only GPIOs with WKUP functionality are able to wake up the system.

- 9. BAM autonomous peripherals can wake up the GPDMA to perform data transfers.

- 10. Available only on STM32WBA52/4/5xx devices.

- 11. Available only on STM32WBA54/5xx devices.

- 12. Functional through ADC4 in autonomous mode.

- 13. DBGMCU remains accessible through AP0.

- 14. DBGMCU remains accessible through AP0 when CDBGPWURUPREQ is set.

Debug mode

By default, the debug connection is lost if the application puts the MCU in Stop and Standby modes while the debug features are used. This is because the Cortex-M33 core is no longer clocked or powered.

However, by setting some configuration bits in the DBGMCU control registers, the software can be debugged even when using the low-power modes extensively. For more details, refer to Section 45.2.5: DBG low-power modes .

11.7.2 PWR background autonomous mode (BAM)

The devices support a background autonomous mode (BAM). This allows autonomous peripherals to be functional on its bus and kernel clock in Stop 0 mode and on its kernel clock in Stop 0 and Stop 1 modes (when the CPU is in DeepSleep, not running any software). In Stop 1 mode, whenever an autonomous peripheral request its bus clock, Stop 0 mode is entered while the CPU remains in DeepSleep.

Stop 0 and Stop 1 modes

In Stop 0 and Stop 1 modes, the autonomous peripherals are ADC, LPTIM, USART, LPUART, SPI, I2C:

- • Peripherals are autonomous only with LSE, LSI or HSI16 used as kernel clock, or HSI16 used as bus clock

- • When an autonomous peripheral request its bus clock Stop 0 mode is entered while keeping the CPU in Sleepdeep.

In Stop 0 mode the 2.4 GHz RADIO can operate autonomously on HSI16 used as bus clock and HSE32 used as kernel clock. The 2.4 GHz RADIO cannot be autonomous in Stop 1 mode.

When entering low-power modes Stop and Standby from Run and an autonomous peripheral bus clock request is active, Stop 0 mode is entered, regardless of the low-power mode selection in LPMS bits. Entering in the LPMS selected low-power mode (Stop 1 and Standby) is delayed until the autonomous peripheral bus clock request is released.

When in Stop 1 mode and an autonomous peripheral request its bus clock, Stop 0 mode is entered.

When in Stop 0 mode and all autonomous peripheral bus clock request are deactivated, the low-power mode selected in the LPMS bits is entered. Note that Standby modes can be entered only when the 2.4 GHz RADIO is in DeepSleep.

Note: As soon as the CPU enters Sleepdeep, the system enters Stop mode and the BAM operation autonomous peripheral bus clock and SYSCLK is switched to HSI16 at 16 MHz. If autonomous peripheral operation with higher bus clock frequencies is needed, the CPU must enter Sleep and keep the system in Run with the configured Run mode SYSCLK clock frequency.

BAM in Stop mode

BAM is supported by the autonomous peripherals with the following features:

- • Functionality in Stop mode thanks to the peripheral kernel clock request capability: the peripheral kernel clock is automatically switched on when requested by a peripheral, and automatically switched off when no peripheral requests it. For the peripheral kernel clock to be switched on, both the peripheralEN and peripheralSMEN bits in the RCC registers must be set.

- • DMA transfers supported in Stop 0 mode, thanks to the peripheral bus clock request capability: the system clock (HSI16) is automatically switched on when requested by a peripheral, and automatically switched off when no peripheral requests it. When the system clock is requested by an autonomous peripheral and both peripheralEN and peripheralSMEN bits in the RCC registers are set, the system clock is woken up and distributed to all peripherals for which the RCC peripheralEN and peripheralSMEN bits are set. This makes possible DMA transfers between peripherals and SRAMs. The 2.4 GHz RADIO bus clock is requested independently from the RADIOEN and RADIOSMEN.

- • Automatic start of the peripheral thanks to the hardware synchronous or asynchronous triggers (such as I/Os edge detection and low-power timer events)

- • Wake up the CPU from Sleepdeep mode through a peripheral interrupt.

The GPDMA1 is fully functional and the linked-list is updated in Stop 0 mode, allowing the different DMA transfers to be linked without any CPU intervention. This can be used to chain transfers between different peripherals, or to write peripheral registers, to change their configuration while in Stop 0 mode.

The DMA transfers from memory to memory can be started by hardware synchronous or asynchronous triggers, and the DMA transfers between peripherals and memories can also be gated by those triggers. In BAM in Stop mode only SRAM transfers are supported (flash memory transfers are not).

Here below some use-cases that can be done while remaining in Stop mode:

- • A/D conversion triggered by a low-power timer (or any other trigger)

- – Wake-up from Stop mode on analog watchdog if the A/D conversion result is out of the programmed thresholds

- – Wake-up from Stop mode on DMA buffer event

- • I

2

C slave reception or transmission, SPI reception, UART/LPUART reception

- – Wake-up at the end of peripheral transfer or on DMA buffer event

- • I

2

C master transfer, SPI transmission, UART/LPUART transmission, triggered by a low-power timer (or any other trigger)

- – Example: Sensor periodic read

- – Wake-up at the end of peripheral transfer or on DMA buffer event

- • Bridges between peripherals

- – Example: A/D converted data transferred by communication peripherals

- • Data transfer from/to GPIO to/from SRAM for:

- – Controlling external components

- – Implementing data transmission and reception protocols

- • Data transfer from one SRAM to another one.

Here below some 2.4 GHz RADIO use-cases that can be done while remaining in Stop 0 mode range 1:

- • Transmit and receive data packets.

- – Wake-up at the end of the scheduled event.

11.7.3 PWR Run mode

Slowing down system clocks

In Run mode, the speed of the system clocks (SYSCLK, hclk, pclk) can be reduced by programming the prescaler registers. These prescalers can also be used to slow down the peripherals before entering the Sleep mode.

For more details, refer to Section 12: Reset and clock control (RCC) .

In addition to slowing down the system clocks, the voltage range can be changed. When the system clocks frequency is low enough range 2 may be entered.

Peripheral clock gating

In Run mode, the hclk and pclk for individual peripherals and memories can be stopped at any time to reduce the power consumption. The peripheral clock gating is controlled by the RCC_AHBxENR and RCC_APBxENR registers.

In Sleep and Stop modes, the hclk and pclk for individual peripherals and memories can be stopped automatically. The Sleep and Stop mode peripheral clock gating is controlled by the RCC_AHBxSMENR and RCC_APBxSMENR registers. For autonomous peripherals to be able to request their clocks the peripheral bus clock in Sleep and Stop mode must be enabled. Except for the 2.4 GHz RADIO, which requests its bus clock independently from the setting in the RADIOEN and RADIOSMEN register bits.

For the 2.4 GHz RADIO the bus clock is running only in Sleep and Stop modes when the STRADIOCLKON is set, or when the 2.4 GHz RADIO is active and RADIOEN and RADIOSMEN are set.

11.7.4 PWR low-power modes

Entering into a low-power mode

The MCU enters in low-power modes by

- • The CPU executing the WFI (wait for interrupt), or WFE (wait for event) instructions, or when the SLEEPONEXIT bit in the Cortex-M33 system control register is set on Return from ISR .

Entering into a low-power mode through WFI or WFE is executed only if no interrupt is pending or no event is pending.

Software must enter Low-power Stop and Standby modes only when voltage scaling is ready (ACTVOSRDY = 1).

When an autonomous peripheral bus clock request is active only Stop 0 is entered, regardless of the low-power mode set in LPMS register bits.

Standby modes are entered only when the 2.4 GHz RADIO is in Deep sleep mode.

Exiting a low-power mode

The way the CPU exits the Sleep or Stop mode depends on the way the low-power mode was entered:

- • If the WFI instruction or Return from ISR was used to enter the low-power mode, any peripheral interrupt acknowledged by the NVIC can wake up the device.

- • If the WFE instruction is used to enter the low-power mode, the CPU exits the low-power mode as soon as an event occurs. The wake-up event can be generated by:

- – an NVIC IRQ interrupt:

When SEVONPEND = 0 in the Cortex-M33 system control register

By enabling an interrupt in the peripheral control register and in the NVIC. When the CPU resumes from WFE, the peripheral interrupt pending bit and the NVIC peripheral IRQ channel pending bit (in the NVIC interrupt clear pending register) must be cleared. Only NVIC interrupts with high enough priority wake up and interrupt the CPU.

When SEVONPEND = 1 in the Cortex-M33 system control register

By enabling an interrupt in the peripheral control register and optionally in the NVIC. When the CPU resumes from WFE, the peripheral interrupt pending bit and when enabled the NVIC peripheral IRQ channel pending bit (in the NVIC interrupt clear pending register) must be cleared. All NVIC interrupts wake up the MCU, even the disabled ones. Only enabled NVIC interrupts with high enough priority wake up and interrupt the CPU.

- – an event:

Configuring an EXTI line in event mode. When the CPU resumes from WFE, it is not necessary to clear the EXTI peripheral interrupt pending bit or the NVIC IRQ channel pending bit as the pending bits corresponding to the event line is not set. It may be necessary to clear the interrupt flag in the peripheral.

The CPU exits Standby mode through a reset. After waking up from Standby mode, the program execution restarts in the same way as after a reset (boot pin sampling, option bytes loading, reset vector is fetched).

Caution: When the device is in Stop mode, a peripheral interrupt powers on an internal oscillator. The corresponding NVIC interrupt channel must be enabled to allow the interrupt to wake up the CPU from Stop mode. It is not allowed to disable a peripheral interrupt by disabling only the NVIC channel while keeping the peripheral interrupt enable, as the device could remain in Stop mode with clock ON.

The peripherals with autonomous mode feature are able to generate an AHB or APB clock request when the device is in Stop mode, depending on their internal events. The software must ensure that either DMA transfer or interrupt is served, by configuring properly and in a consistent way the RCC, the autonomous peripherals, the DMA channels, and NVIC. Note that when an autonomous peripheral requests the bus clock in Stop mode, the AHB, and APB clocks are distributed to all enabled peripherals on the same AHB or APB bus. Consequently, enabled peripherals, even without autonomous mode capability, are temporarily clocked and can also generate an interrupt during this time. These interrupts also wake up the device from Stop mode.

11.7.5 PWR Sleep mode

I/O states in Sleep mode

In Sleep mode, all I/O pins keep the same state as in Run mode. In addition I/O pins can be toggled through DMA or other active communication peripherals.

To further reduce the power consumption in Sleep mode, disabling the peripherals clocks in Sleep mode can be performed automatically by resetting the corresponding bit in the RCC_AHBxSMENR and RCC_APBxSMENR registers.

Entering the Sleep mode

The MCU enters the Sleep mode as described in Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is clear (see the table below for details on how to enter the Sleep mode).

Exiting the Sleep mode

The MCU exits the Sleep mode as described in Exiting a low-power mode (see the table below for details on how to exit the Sleep mode).

Table 90. Sleep mode

| Sleep mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On return from ISR while:

|

| Mode exit | If WFI or Return from ISR was used for entry Interrupt (see Table 135: Vector table ) If WFE was used for entry and SEVONPEND = 0: Wake-up event (see Section 19.3: EXTI functional description ) If WFE was used for entry and SEVONPEND = 1: Interrupt even when disabled in NVIC (see Table 135: Vector table ) or wake-up event (see Section 19.3: EXTI functional description ) |

| Wake-up latency | None |

11.7.6 PWR Stop 0 mode

The Stop mode is based on the CPU1 Cortex ® -M33 Sleepdeep mode combined with peripheral clock gating. The voltage regulator configuration as used in Run mode remains the same in Stop 0 mode. In Stop mode, all clocks in the Core domain are stopped. The PLL, HSI16 and HSE32 oscillators are disabled.

Some peripherals with autonomous capability can switch on HSI16 or HSE32 for transferring data (see Section 11.7.2 for details). Autonomous capable peripherals using HSE32 require the use of Stop 0 mode range 1.

To reduce the power consumption in Stop mode, disabling the peripherals clocks can be performed automatically by resetting the corresponding bit in the RCC_AHBxSMENR and RCC_APBxSMENR registers. This bit must be set for the autonomous peripherals requesting clocks in Stop mode.

All register contents are preserved, SRAM1 and/or SRAM2 can totally or not be retained to further reduce consumption.

I/O states in Stop 0 mode

In the Stop 0 mode, all I/O pins keep the same state as in the Run mode. In addition, I/O pins can be toggled through DMA or other autonomous communication peripherals.

Entering the Stop 0 mode

The MCU enters the Stop 0 mode as described in Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is set. The regulator is kept in the same regulation mode and voltage scaling range as used in Run mode. (see the table below for details on how to enter the Stop 0 mode).

If the flash memory programming is ongoing, the Stop 0 mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, the Stop 0 mode entry is delayed until the APB access is finished.

In Stop 0 mode, the following features can be selected by programming the individual control bits:

- • The independent watchdog (IWDG) is started by writing to its key register or by hardware option. Once started, it cannot be stopped except by a reset (see Section 34.4: IWDG functional description ).

- • The real-time clock (RTC) is configured by the RTCSEL bit in the RCC Backup domain control register (RCC_BDCR1) .

- • The internal RC oscillator LSI or LSI1 clock divided by 128, is configured by the LSION and LSI1PREDIV bits in the RCC_BDCR1 register.

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in RCC_BDCR1.

- • The 2.4 GHz RADIO sleep timer configured through the link layer software.

- • SRAM1 retention configured by the SRAM1PDS1 bit in PWR control register 2 (PWR_CR2) .

- • SRAM2 retention configured by the SRAM2PDS1 bit in PWR control register 2 (PWR_CR2) .

Several peripherals can be autonomous in Stop 0 mode, increasing power consumption if enabled (see Section 11.7.2 for more details).

The COMPs and the PVD can be used in Stop mode. If not needed, they must be disabled by software to reduce power consumption.

The ADC4 and the temperature sensor can consume power during the Stop 0 mode, unless they are disabled before entering the mode.

Entering Stop 1 and Standby modes from Stop 0

When entering low-power with Stop 1 or Standby selected in LPMS and an autonomous peripheral bus clock request is active, Stop 0 mode is entered instead. Only when all autonomous peripheral bus clock requests are de-asserted the LPMS selected low-power mode is subsequently entered.

Exiting the Stop 0 mode

The MCU exits the Stop 0 mode as described in Exiting a low-power mode (see Table 91 ).

When exiting Stop 0 mode by issuing an interrupt or a wake-up event, HSI16 is selected as system clock.

Several peripherals are autonomous in Stop mode, and can generate interrupts with wake-up from Stop capability. All peripheral clocks must be enabled to allow a wake-up from Stop interrupt (see Peripheral clock gating ).

When exiting the Stop 0 mode, the MCU is in Run mode same range as before entering Stop 0 mode.

The MCU can enter another low-power mode, as selected in LPMS, from the Stop 0 mode when all autonomous peripheral bus clocks requests are de-asserted.

Table 91. Stop 0 mode

| Stop 0 mode | Description |

|---|---|

| Mode entry from Run | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

– LPMS = Stop 0 in PWR_CR1 or autonomous peripheral bus clock request is active Note: To enter Stop 0 mode, all EXTI line pending bits (in the EXTI rising edge pending register (EXTI_RPR1) and EXTI falling edge pending register (EXTI_FPR1) ), and the peripheral flags generating wake-up interrupts must be cleared. Otherwise, the Stop 0 mode entry procedure is ignored and the program execution continues. |

| Mode entry from Stop 1 | Autonomous peripheral bus clock request active |

Table 91. Stop 0 mode (continued)

| Stop 0 mode | Description |

|---|---|

| Mode exit to Run | If WFI or Return from ISR was used for entry:

If WFE was used for entry and SEVONPEND = 0:

If WFE was used for entry and SEVONPEND = 1:

Note: All peripheral clocks must be enabled to allow this peripheral to generate a wake-up from Stop interrupt (peripheralEN, and peripheralSMEN bits must be set in the RCC, and a functional independent clock must be selected). |

| Mode exit to low-power modes | All autonomous peripheral bus clock requests de-asserted. |

| Wake-up latency | HSI16 wake-up time when applicable and flash wake-up time from Stop 0 mode. |

11.7.7 PWR Stop 1 mode

The Stop 1 mode is the same as Stop 0 mode except that the regulator is in low-power mode and voltage scaling is set to range 2. (see the table below for details on how to enter and exit Stop 1 mode).

The BOR is always available in Stop 1 mode. When not using autonomous peripherals operation with HSI16 as kernel clock, the BOR0 can be forced in ultra-low power mode by the ULPMEN bit in the PWR_CR1 to reach the lowest power consumption.

Entering the Stop 1 mode

The MCU enters the Stop 1 mode in the same way as entering Stop 0. Whenever an autonomous peripheral bus clock request is active, Stop 1 mode is not entered and Stop 0 mode is entered instead.

Entering the Stop 0 mode from Stop 1

When in low-power Stop 1 mode an autonomous peripheral bus clock request is activated, Stop 0 mode range 2 is entered, with HSI16 as system clock and HDIV5 is set to divide by 2 by hardware.

Exiting the Stop 1 mode

The MCU exits the Stop 1 mode as described in Exiting a low-power mode (see Table 92 ).

When exiting Stop 1 mode by issuing an interrupt or a wake-up event, Run range 2 with HSI16 selected as system clock and HDIV5 is set to divide by 2 by hardware. Before entering Stop 1 mode software must configure adequate FLASH wait states latency to at least 1 in FLASH_ACR register and SRAM1 and SRAM2 wait states to at least 1 in RAMCFG_MxCR.

Table 92. Stop 1 mode

| Stop 1 mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

– LPMS = Stop 1 in PWR_CR1 and all autonomous peripheral bus clock requests de-asserted. – LPMS = Standby in PWR_CR1 and all autonomous peripheral bus clock requests de-asserted and 2.4 GHz RADIO not in DeepSleep. Note: To enter Stop 1 mode, all EXTI line pending bits (in the EXTI rising edge pending register (EXTI_RPR1) and EXTI falling edge pending register (EXTI_FPR1) ), and the peripheral flags generating wake-up interrupts must be cleared. Otherwise, the Stop 1 mode entry procedure is ignored and the program execution continues. |

Table 92. Stop 1 mode (continued)

| Stop 1 mode | Description |

|---|---|

| Mode exit to Run | If WFI or Return from ISR was used for entry

If WFE was used for entry and SEVONPEND = 0:

If WFE was used for entry and SEVONPEND = 1:

Note: All peripheral clocks must be enabled to allow this peripheral to generate a wake-up from Stop interrupt (peripheralEN and peripheralSMEN bits must be set in the RCC, and a functional independent clock must be selected). |

| Mode exit to Stop 0 | Autonomous peripheral bus clock request active. |

| Wake-up latency | HSI16 wake-up time and regulator wake-up time from low-power mode + Flash wake-up time from Stop 1 mode. |

11.7.8 PWR Standby mode

It is based on the Cortex-M33 Sleepdeep mode, with the voltage regulators disabled (except when SRAM1, SRAM2, 2.4 GHz RADIO RAMs or sleep timer are retained). The PLL, HSI16 and HSE32 oscillators are also switched off.

The register contents are lost except for SRAMs and registers in the retention domain when enabled and the Backup domain and Standby circuitry (see Figure 28 ). SRAM1, SRAM2 content can fully be preserved depending on R1RSB1 and R2RSB1 bit configuration in PWR_CR1. In this case, the low-power regulator is ON and provides the supply to SRAM1 and/or SRAM2. Also the 2.4 GHz RADIO SRAMs can be retained, and the sleep timer kept operational depending on RADIORSB bit configuration in PWR_CR1.

The BOR is always available in Standby mode. The ULPMEN bit in the PWR_CR1 register must be configured to 1 to reach the lowest power consumption by forcing the BOR0 in ultra-low power mode.

I/O states in Standby mode

In the Standby mode, the GPIOs are by default in floating state. If Standby GPIO retention is enabled in the PWR_IORETENRx register, the GPIO retains the pull or output level. When entering Standby mode, GPIOs that are enabled for Standby mode retention keep their pull or level during and after exiting from Standby mode until the PWR_IORETRx bit is cleared by software. When entering Standby mode the PWR_IORETRx bit is set by hardware for the GPIOs with Standby retention enabled. The PWR_IORETRx only controls the pulls, it does not affect the GPIO analog, input and output states. When exiting from Standby and before re-enabling a GPIO as output, the output level must be restored to the one retained. To do this, first enable the GPIO as input and copy the input data from GPIOx_IDR to the GPIOx_ODR, before setting the GPIO as output. Once the GPIO is reconfigured, disable the retained pulls in PWR_IORETRx.

The GPIO standby retention enable information in PWR_IORETENRx and PWR_IORETRx are retained in Standby mode.

Note: The Standby GPIO retention level cannot be guaranteed when the GPIO port pin is connected to a low impedance destination.

Table 93. GPIO retention pin with pull-up and pull-down

| PWR_IORETEN | GPIO port pin configuration before entering Standby | GPIO port pin configuration in Standby |

|---|---|---|

| 0 | Any | High-Z |

| 1 | Input no pulls | High-Z |

| Input or output with pull-up | Pull-up | |

| Input or output with pull-down | Pull-down | |

| Output no pulls driving level high | Pull-up | |

| Output no pulls driving level low | Pull-down |

For GPIO port pins enabled to be functional in Standby modes, the Standby GPIO retention can also be controlled in the PWR_IORETENRx register. The following GPIO functions are available in Standby modes:

- • RTC outputs on PC13 and/or PB2 (standby GPIO retention must be disabled)

- • TAMP tamper pins

- • WKUPx_y wake-up pins

- • LSE pins on PC14 and/or PC15 (Standby GPIO retention must be disabled)

- • JTDO/TRACE SWO on PB3 when debugger is connected and CDBGPWRUPREQ is set (Standby GPIO retention must be disabled)

When waking up from Standby with a system reset (NRST) GPIO retention is removed before software can reconfigure the GPIO port pins in the GPIO peripheral.

Entering Standby mode

The MCU enters the Standby mode as described in Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 System Control register is set (see Table 94 ).

Whenever an autonomous peripheral bus clock request is active, Standby mode is not entered and Stop 0 mode is entered instead.

Standby mode is entered only when the 2.4 GHz RADIO is in DeepSleep mode. Whenever the 2.4 GHz RADIO is in Active or Sleep modes, Stop 0 mode is entered instead.

In Standby mode, the following features can be selected by programming individual control bits:

- • The independent watchdog (IWDG) is started by writing to its Key register or by hardware option. Once started, it cannot be stopped, except by a reset (see Section 34.4: IWDG functional description ).

- • The real-time clock (RTC) is configured by the RTCSEL bit in RCC Backup domain control register (RCC_BDCR1) .

- • The internal RC oscillator LSI or LSI1 clock divided by 128 is configured by the LSION and LSI1PREDIV bits in RCC_BDCR1 .

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in RCC_BDCR1 .

- • The 2.4 GHz RADIO SRAMs and sleep timer configured by the RADIORSB bit in PWR control register 1 (PWR_CR1) . Available in Standby retention mode.

- • SRAM1 retention configured by the R1RSB1 bit in PWR control register 1 (PWR_CR1) . Available in Standby retention mode.

- • SRAM2 retention configured by the R2RSB1 bit in PWR control register 1 (PWR_CR1) . Available in Standby retention mode.

Exiting Standby mode

The MCU exits the Standby mode as described in Exiting a low-power mode . The SBF status flag in the PWR status register (PWR_SR) indicates that the MCU was in Standby mode (see Table 94 for more details on how to exit Standby mode).

Table 94. Standby mode

| Standby mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

– LPMS = Standby in PWR_CR1 and all autonomous peripheral bus clock requests de-asserted and the 2.4 GHz RADIO in DeepSleep. – WUFx bits cleared in PWR_WUSR – RTC and TAMP flags corresponding to the chosen wake-up source cleared – 2.4 GHz RADIO sleep timer wake-up source cleared. Note: To enter Standby mode, all EXTI line pending bits (in the EXTI rising edge pending register (EXTI_RPR1) and EXTI falling edge pending register (EXTI_FPR1) ), and the peripheral flags generating wake-up interrupts must be cleared. Otherwise, the Standby mode entry procedure is ignored and the program execution continues. |

Table 94. Standby mode

| Standby mode | Description |

|---|---|

| Mode exit | WKUPx event, RTC event, TAMP event, IWDG event, NRST external reset, BOR reset In addition only from Standby retention 2.4 GHz RADIO sleep timer event. |

| Wake-up latency | Reset phase |

11.7.9 Power modes output pins

To help the debug, two signals are available as device pins alternate functions:

- • PWR_CSLEEP

When set, indicates that the CPU is in Sleep mode:

- – WFI or WFE has been executed, and CPU stops execution CPU hclk1 stopped

When cleared, indicates that the CPU is in Run mode.

- • PWR_CSTOP

When set, indicates that the device is in Stop mode, meaning that the following conditions are true:

- – WFI or WFE has been executed with CPU SLEEPDEEP = 1

- – No AHB/APB clock is running, except for BAM autonomous peripherals

When cleared, indicates that the device is in Run or Sleep mode with AHB/APB clocked.

Note: After WFI or WFE has been executed the SYSCLK clock is kept running in Stop 0 mode when an autonomous peripheral requests its bus clock. The peripherals bus clock request can prevent the device to enter the selected low-power mode, which enters Stop 0 mode instead. (refer to Section 11.7.2 and Section 11.7.4 ).

Table 95 explains the MCU power mode depending on these signals states.

Table 95. Power modes output states versus MCU power modes

| PWR_CSLEEP | PWR_CSTOP | MCU power modes (1) |

|---|---|---|

| 0 | 0 | Run mode (CPU executing) |

| 1 | 0 | Sleep mode (CPU Sleep) |

| X | 1 | Stop mode (MCU in Stop mode) |

- 1. PWR_CSLEEP and PWR_CSTOP are generated in the Core domain, consequently they are not driven in Standby mode.

11.8 PWR security and privileged protection

11.8.1 PWR security protection

TrustZone security is activated by the TZEN user option bit in the FLASH_OPTR. Some PWR register fields can be secured against non-secure access.

The PWR TrustZone security allows the following features to be secured through the PWR_SECCFGR register:

- • Low-power mode

- • Wake-up (WKUP) pins

- • Voltage detection

- • Backup domain control

Other PWR configuration bits are secure when:

- • The system clock selection is secure in RCC: the voltage scaling (VOS) configuration is secure.

- • The I/O Standby mode retention configuration is secure when the corresponding GPIO is secure.

If SPRIV is set in the PWR privilege control register (PWR_PRIVCFGR) , the PWR_SECCFGR register can be written only by secure and privileged access. If SPRIV is cleared, PWR_SECCFGR can be written only by secure access, privileged, or unprivileged.

PWR_SECCFGR can be read by secure, non-secure, privileged, and unprivileged access.

A non-secure write access to PWR_SECCFGR is WI and generates an illegal access event and an interrupt if enabled in the GTZC.

When the TrustZone security is disabled (TZEN = 0), PWR_SECCFGR is RAZ/WI and all other registers are non-secure.

When a peripheral is configured as secure, its related PWR feature control bits, are also secure in the associated registers. PWR_PUCRx, PWR_PDCRx, PWR_RADIOSCR, and PWR_VOSR.

A peripheral is secure when:

- • For securable peripherals by GTZC-TZSC (TrustZone security controller), by the SEC security bit in the secure configuration registers corresponding to this peripheral.

- • For TrustZone-aware peripherals, a security feature of this peripheral is enabled through its dedicated bits.

Table 96 gives a summary of the PWR secured bits following the security configuration bit in PWR_SECCFGR.

A non-secure access to a secure-protected register bit is denied:

- • The secured bits are not written (WI) with a non-secure write access.

- • The secured bits are read as 0 (RAZ) with a non-secure read access.

Table 96. PWR security configuration summary

| Secure configuration register | Security configuration bit | Register name | Secured bits | Non-secure access on secure bits |

|---|---|---|---|---|

| PWR_SECCFGR | Not applicable (1) | PWR_SECCFGR | All bits | Read OK. WI and illegal access event |

| PWR_SECCFGR | Not applicable (2) | PWR_PRIVCFGR | SPRIV | Read OK. WI |

| PWR_SECCFGR | LPMSEC | PWR_CR1 | All bits | RAZ/WI |

| PWR_CR2 | All bits | |||

| PWR_SR | CSSF | WI |

Table 96. PWR security configuration summary (continued)

| Secure configuration register | Security configuration bit | Register name | Secured bits | Non-secure access on secure bits |

|---|---|---|---|---|

| PWR_SECCFGR | VDMSEC | PWR_CR3 | All bits | RAZ/WI |

| PWR_SVMCR | All bits | RAZ/WI | ||

| PWR_SECCFGR | VBSEC | PWR_DBPR | All bits | RAZ/WI |

| PWR_SECCFGR | WUPxSEC (x = 1 to 8) | PWR_WUCR1 | WUPENx | RAZ/WI |

| PWR_WUCR2 | WUPPx | RAZ/WI | ||

| PWR_WUCR3 | WUSELx | RAZ/WI | ||

| PWR_WUSCR | CWUFX | WI | ||

| GTZC_TZSC_ SECCFGR | RADIOSEC | PWR_RADIOSCR | REGPABYPEN | RAZ/WI |

| REGPASEL | RAZ/WI | |||

| RCC_SECCFGR | SYSCLKSEC | PWR_VOSR | VOS | RAZ/WI |

| GPIOx_SECCFGR (x = A to C and H) | SECy (y = 0 to 15) | PWR_IORETENRx | ENy | RAZ/WI |

| PWR_IORETRx | RETy | RAZ/WI |

- 1. PWR_SECCFGR is always secure.

- 2. PWR_PRIVCFGR.SPRIV is always secure.

11.8.2 PWR privileged protection

By default, after a reset, all PWR registers can be read or written with both privileged and unprivileged accesses, except PWR_PRIVCFGR that can be written with privileged access only. PWR_PRIVCFGR can be read by secure and non secure, privileged, and unprivileged accesses.

The SPRIV bit in PWR_PRIVCFGR can be written with secure privileged access only. This bit configures the privileged access of all PWR secure functions (defined by PWR_SECCFGR, GTZC, RCC, or GPIO as shown in Table 96 ).

When the SPRIV bit is set in PWR_PRIVCFGR:

- • The PWR secure bits can be written only with privileged access, including PWR_SECCFGR.

- • The PWR secure bits can be read only with privileged access except PWR_SECCFGR and PWR_PRIVCFGR that can be read by privileged or unprivileged access.

- • An unprivileged access to a privileged PWR bit or register is discarded: the bits are read as zero and the write to these bits is ignored (RAZ/WI).

The NSPRIV bit of PWR_PRIVCFGR can be written with privileged access only, secure or non-secure. This bit configures the privileged access of all PWR securable functions that are configured as non-secure (defined by PWR_SECCFGR, GTZC, RCC, or GPIO as shown in Table 96 ).

When the NSPRIV bit is set in PWR_PRIVCFG:

- • The PWR securable bits that are configured as non-secure, can be written only with privileged access.

- • The PWR securable bits that are configured as non-secure, can be read only with privileged access except PWR_PRIVCFG that can be read by privileged or unprivileged accesses.

- • The VOSRDY bit in PWR_VOSR and the registers PWR_SR, PWR_SVMSR, PWR_BDSR and PWR_WUSR, can be read with privileged or unprivileged accesses.

- • An unprivileged access to a privileged PWR bit or register is discarded: the bits are read as zero and the write to these bits is ignored (RAZ/WI).

11.9 PWR interrupts

Table 97 gives a summary of the interrupt sources, and how to control them.

Table 97. PWR interrupt requests

| Interrupt vector | Interrupt event | Event flag | Enable control bit | Interrupt clear method | Exit Sleep, Stop 0, 1 modes | Exit Standby retention mode | Exit Standby modes |

|---|---|---|---|---|---|---|---|

| WKUP | External WKUP | WUFx | WUPENx | CWUFx | Yes | Yes | Yes |

| WKUP_S (1) | External secure WKUP | WUFx | WUPENx | CWUFx | |||

| PVD | Programmable voltage detector through EXTI line 16 | PVDO | EXTI line 16 enabled | EXTI PIF16 | Yes | No | No |

- 1. The WKUP_S secure interrupt is used only when trustZone is enabled.

11.10 PWR registers

11.10.1 PWR control register 1 (PWR_CR1)

Address offset: 0x000

Reset value: 0x0000 0000 (reset value not affected by exit Standby mode)

Access: 14 AHB clock cycles added compared to a standard AHB access

Access to this register can be protected by bits LPMSEC and SPRIV or NSPRIV.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | R1RSB1 | Res. | Res. | RADIOSB | Res. | ULPMEN | Res. | R2RSB1 | Res. | Res. | LPMS[2:0] | ||

| rw | rw | rw | rw | rw | rw | rw | |||||||||

Bits 31:13 Reserved, must be kept at reset value.

Bit 12 R1RSB1 : SRAM1 retention in Standby mode

This bit is used to keep the SRAM1 content in Standby retention mode.

0: SRAM1 content not retained in Standby mode

1: SRAM1 content retained in Standby mode

Bits 11:10 Reserved, must be kept at reset value.

Bit 9 RADIOSB : 2.4 GHz RADIO SRAMs (RXTXRAM and Sequence RAM) and Sleep clock retention in Standby mode.

This bit is used to keep the 2.4 GHz RADIO SRAMs content in Standby retention mode and the 2.4 GHz RADIO sleep timer counter operational.

0: 2.4 GHz RADIO SRAMs and sleep timer content not retained in Standby mode

1: 2.4 GHz RADIO SRAMs and sleep timer content retained in Standby mode

Bit 8 Reserved, must be kept at reset value.

Bit 7 ULPMEN : BOR0 ultra-low power mode.

This bit is used to reduce the consumption by configuring the BOR0 in discontinuous mode for Stop 1 and Standby modes. Discontinuous mode is available only when BOR levels 1 to 4 and PVD are disabled.

0: BOR0 operating in continuous (normal) mode in all operating modes

1: BOR0 operating in discontinuous (ultra-low power) mode in Stop 1 and Standby modes.

Note: This bit must be set to reach the lowest power consumption in the low-power modes, and not set together with autonomous peripherals using HSI16 as kernel clock.

Note: When BOR level 1 to 4 or PVD is enabled continuous mode applies independently from ULPMEN.

Bit 6 Reserved, must be kept at reset value.

Bit 5 R2RSB1 : SRAM2 retention in Standby mode

This bit is used to keep the SRAM2 content in Standby retention mode.

0: SRAM2 content not retained in Standby mode

1: SRAM2 content retained in Standby mode

Bits 4:3 Reserved, must be kept at reset value.

Bits 2:0 LPMS[2:0] : Low-power mode selection

These bits select the low-power mode entered when the CPU enters the SleepDeep mode.

000: Stop 0 mode

001: Stop 1 mode

10x: Standby mode

Others: reserved

11.10.2 PWR control register 2 (PWR_CR2)

Address offset: 0x004

Reset value: 0x0000 0000

Access to this register can be protected by bits LPMSEC and SPRIV or NSPRIV.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | FLASHF WU | Res. | Res. | Res. | Res. | Res. | ICRAM PDS | Res. | Res. | Res. | SRAM2 PDS1 | Res. | Res. | Res. | SRAM1 PDS1 |

| rw | rw | rw | rw |

Bits 31:15 Reserved, must be kept at reset value.

Bit 14 FLASHFWU : Flash memory fast wake-up from Stop modes (Stop 0, 1)

This bit is used to obtain the best trade-off between low-power consumption and wake-up time when exiting the Stop 0 or Stop 1 modes.

When this bit is set, the flash memory remains in normal mode in Stop 0 and Stop 1 modes, which offers a faster startup time with higher consumption.

0: Flash memory enters low-power mode in Stop 0 and Stop 1 modes (lower power consumption).

1: Flash memory remains in normal mode in Stop 0 and Stop 1 modes (faster wake-up time).

Bits 13:9 Reserved, must be kept at reset value.

Bit 8 ICRAMPDS : ICACHE SRAM power-down in Stop modes (Stop 0, 1)

0: ICACHE SRAM content retained in Stop modes

1: ICACHE SRAM content lost in Stop modes

Bits 7:5 Reserved, must be kept at reset value.

Bit 4 SRAM2PDS1 : SRAM2 power-down in Stop modes (Stop 0, 1)

0: SRAM2 content retained in Stop modes

1: SRAM2 content lost in Stop modes

Note: The SRAM2 retention in Standby mode is controlled by R2RSB1 bit in PWR_CR1.

Bits 3:1 Reserved, must be kept at reset value.

Bit 0 SRAM1PDS1 : SRAM1 power-down in Stop modes (Stop 0, 1)

0: SRAM1 content retained in Stop modes

1: SRAM1 content lost in Stop modes

Note: The SRAM1 retention in Standby mode is controlled by R1RSB1 bit in PWR_CR1.

11.10.3 PWR control register 3 (PWR_CR3)

Address offset: 0x008

Power-on reset value: 0x0000 0000 (reset value not affected by exit Standby mode, not affected by system reset, except REGSEL)

Access: 14 AHB clock cycles added compared to a standard AHB access

Access to this register can be protected by bits VDMSEC and SPRIV or NSPRIV.