57. Debug support (DBG)

57.1 Introduction

A comprehensive set of debug features is provided to support software development and system integration:

- • Breakpoint debugging of the CPU core

- • Code execution tracing

- • Software instrumentation

- • Cross-triggering

The debug features can be controlled via a JTAG/Serial-wire debug access port, using industry standard debugging tools. A trace port allows data to be captured for logging and analysis.

The debug features are based on Arm CoreSight components.

- • SWJ-DP: JTAG/Serial-wire debug port

- • AHB-AP: AHB access port

- • ROM table

- • System control space (SCS)

- • Breakpoint unit (BPU)

- • Data watchpoint and trace unit (DWT)

- • Instrumentation trace macrocell (ITM)

- • Embedded Trace Macrocell™ (ETM)

- • Cross trigger interface (CTI)

- • Trace port interface unit (TPU)

The debug features are accessible by the debugger via the AHB-AP.

Additional information can be found in the Arm documents referenced in Section 57.13: References .

57.2 DBG functional description

57.2.1 DBG block diagram

Figure 804. Block diagram of debug support infrastructure

![Block diagram of debug support infrastructure for CPU Cortex-M33. It shows the internal components: SWJ-DP, AHB-AP, Core, DWT, BPU, ITM, TPIU, ETM, CTI, ROM table, and DBG_MCU. The SWJ-DP is connected to JTAG/Serial-wire port pins (JTMS/SWDIO, JTDI, JTDO, JTCK/SWCLK, nJTRST). The AHB-AP connects the SWJ-DP to the Core and other debug components. The Core is connected to the AHB-AP, DWT, BPU, ITM, ETM, CTI, and ROM table. The TPIU is connected to the ITM, ETM, and DBG_MCU. The DBG_MCU is connected to the TPIU and the ROM table. The Trace port pins (TRACECK, TRACED[3:0], TRACESWO) are connected to the TPIU. The diagram is labeled MSv49702V1.](/RM0487-STM32U3/8dab21fa49970c322d5f45b3667ed6d1_img.jpg)

57.2.2 DBG pins and internal signals

Table 629. JTAG/Serial-wire debug port pins

| Pin name | JTAG debug port | SW debug port | Pin assignment | ||

|---|---|---|---|---|---|

| Type | Description | Type | Description | ||

| JTMS/SWDIO | I | JTAG test mode select | IO | Serial-wire data in/out | PA13 |

| JTCK/SWCLK | I | JTAG test clock | I | Serial-wire clock | PA14 |

| JTDI (1) | I | JTAG test data input | - | - | PA15 |

| JTDO | O | JTAG test data output | - | - | PB3 |

| nJTRST | I | JTAG test reset | - | - | PB4 |

1. TDI is hosted on the same IO as a USBPD-CC line. To avoid pull-up/down conflict, a user option can help to decide whether the pad is used as TDI or as CC.

Table 630. Trace port pins

| Pin name | Type | Description | Pin assignment |

|---|---|---|---|

| TRACED0 | O | Trace synchronous data out 0 | Refer to the datasheet |

| TRACED1 | Trace synchronous data out 1 | ||

| TRACED2 | Trace synchronous data out 2 | ||

| TRACED3 | Trace synchronous data out 3 | ||

| TRACECK | Trace clock |

| Pin name | Type | Description | Pin assignment |

|---|---|---|---|

| TRACESWO | O | Single-wire trace asynchronous data out | PB3 (1) |

- 1. TRACESWO is multiplexed with JTDO. This means that single-wire trace is only available when using the serial-wire debug interface, and not when using JTAG.

57.2.3 DBG reset and clocks

The debug port (SWJ-DP) is reset by a power-on reset and when waking up from Standby mode.

The debugger supplies the clock for the debug port via the debug interface pin JTCK/SWCLK. This clock is used to register the serial input data in both serial-wire and JTAG modes, as well as to operate the state machines and internal logic of the debug port. This clock must therefore continue to toggle for several cycles after the end of an access, to ensure that the debug port returns to the idle state.

The SWJ-DP contains an asynchronous interface to the DCLK domain, that covers the rest of the SWJ-DP and the access port.

The DCLK is a gated version of the system clock.

The DCLK domain is enabled by the debugger using the CDBGPWRUPREQ bit in the DP_CTRL_STAT. The clock must be enabled before the debugger can access any of the debug features on the device. The availability of the clock is reflected in the CDBGPWRUPACK bit in DP_CTRLSTAT. The DCLK is disabled at power-up, and must be disabled when the debugger is disconnected, to avoid wasting energy.

The debug and trace components included in the processor are clocked with the processor clock.

57.2.4 DBG power domains

The debug components are located in the core power domain. This means that the debugger connection is not possible in Shutdown or Standby low-power mode. To avoid losing the connection when the device enters Standby mode, the power can be maintained to the core by setting a bit in DBGMCU_CR. This also keeps the processor clocks active and holds off the reset, so that the debug session is maintained.

57.2.5 Debug and low-power modes

The devices include power saving features that allow the core power domain to be switched off or stopped when not required. If the power is switched off or if the core is not clocked, all debug components are inaccessible to the debugger. To avoid this, power-saving mode emulation is implemented. If the emulation is enabled for a domain, the domain still enters power-saving mode, but its clock and power are maintained. In other words, the domain behaves as if it is in power-saving mode, but the debugger does not lose the connection.

The emulation mode is programmed in the microcontroller debug (DBGMCU) unit. For more information, refer to Section 57.12: Microcontroller debug unit (DBGMCU) .

57.2.6 Security

The trace and debug components allow a high degree of access to the processor and system during product development. In order to protect user code and ensure that the debug features can not be used to alter or compromise the normal operation of the finished product, these features can be disabled or limited in scope. For example, secure software debug and trace can be disabled without preventing the debug of nonsecure code.

The following authentication signals are used by the system to determine which debug features are enabled or disabled:

- •

dbgen

: global enable for all debug features

- 0: All debug features are disabled.

- 1: Debug features in nonsecure state are enabled. Debug features in secure state are dependent on the state of the spiden signal.

- •

spiden

: enables debug in secure state when

dbgen

= 1.

- 0: Debug features are disabled in secure state.

- 1: Debug features are enabled in secure state.

- •

niden

: enables trace and performance monitoring (non-invasive debug).

- 0: Trace generation is disabled.

- 1: Trace generation in nonsecure state is enabled. Trace generation in secure state is dependent on the state of the spniden signal.

- •

spniden

: enables trace and performance monitoring in secure state when

niden

= 1.

- 0: Trace generation is disabled in secure state.

- 1: Trace generation is enabled in secure state.

For detailed information on the behavior of each component according to the state of the authentication signals, refer to the relevant component chapter or to the relevant Arm technical documentation.

The state of the signals are set according to the readout protection (RDP) level (see Section 3.11.1: Debug protection with readout protection (RDP) ), as shown in the table below:

Table 632. Authentication signal states

| RDP level | Authentication signal state | Description |

|---|---|---|

| 0 | dbgen = 1, spiden = 1 niden = 1, spniden = 1 | Debug and trace is enabled whatever the state of the processor. The debugger access to secure memory is permitted. |

| 0.5 | dbgen = 1, spiden = 0 niden = 1, spniden = 0 | Debug and trace is enabled when the processor is in nonsecure state. The debugger access to secure memory is disabled. |

| 1 | dbgen = 1, spiden = 0 niden = 1, spniden = 0 | Debug and trace is enabled when the processor is in nonsecure state. The debugger access to secure memory is disabled, as well as to the following areas: flash memory, SRAM2, backup registers, ICACHE, on-the-fly decryption region (OCTOSPI). |

| 2 | dbgen = 0, spiden = 0 niden = 0, spniden = 0 | Debug and trace is disabled. |

Note: Security features are only relevant when the option bit TZEN = 1. If security features are disabled, the authentication signals are still set according to the RDP level, but since the processor and all memories are nonsecure, spniden and spiden are redundant.

The state of the authentication signals can be read from DAUTHSTATUS register in the system control space (SCS) of the Cortex-M33.

The debugger access to secure memory (when permitted) must be performed using secure transactions on the debug AHB, that is, with PROT[6] set in AP_CSW.

The debugger access is disabled while the processor is booting from system flash memory (RSS), whatever the RDP level, if security features are enabled (TZEN = 1).

57.3 Serial-wire and JTAG debug port (SWJ-DP)

The SWJ-DP is a CoreSight component that implements an external access port for connecting debugging equipment.

Two types of interface can be configured:

- • a 5-pin standard JTAG interface (JTAG-DP)

- • a 2-pin (clock + data) serial-wire debug port (SW-DP)

These two modes are mutually exclusive, since they share the same IO pins.

By default, the JTAG-DP is selected after a system or a power-on reset. The five IO pins are configured by hardware in debug alternative function mode. The SWJ-DP incorporates pull-up resistors on JTDI, JTMS/SWDIO, and nJTRST, as well as a pull-down resistor on JTCK/SWCLK.

A debugger can select the SW-DP by transmitting the following serial data sequence on JTMS/SWDIO:

... (50 or more ones) ..., 0, 1, 1, 1, 1, 0, 0, 1, 1, 1, 1, 0, 0, 1, 1, 1, ... (50 or more ones) ...

JTCK/SWCLK must be cycled for each data bit.

In SW-DP mode, the unused JTAG pins JTDI, JTDO and nJTRST can be used for other functions.

Note: All SWJ port I/Os can be reconfigured to other functions by software, but debugging is no longer possible.

57.3.1 JTAG debug port

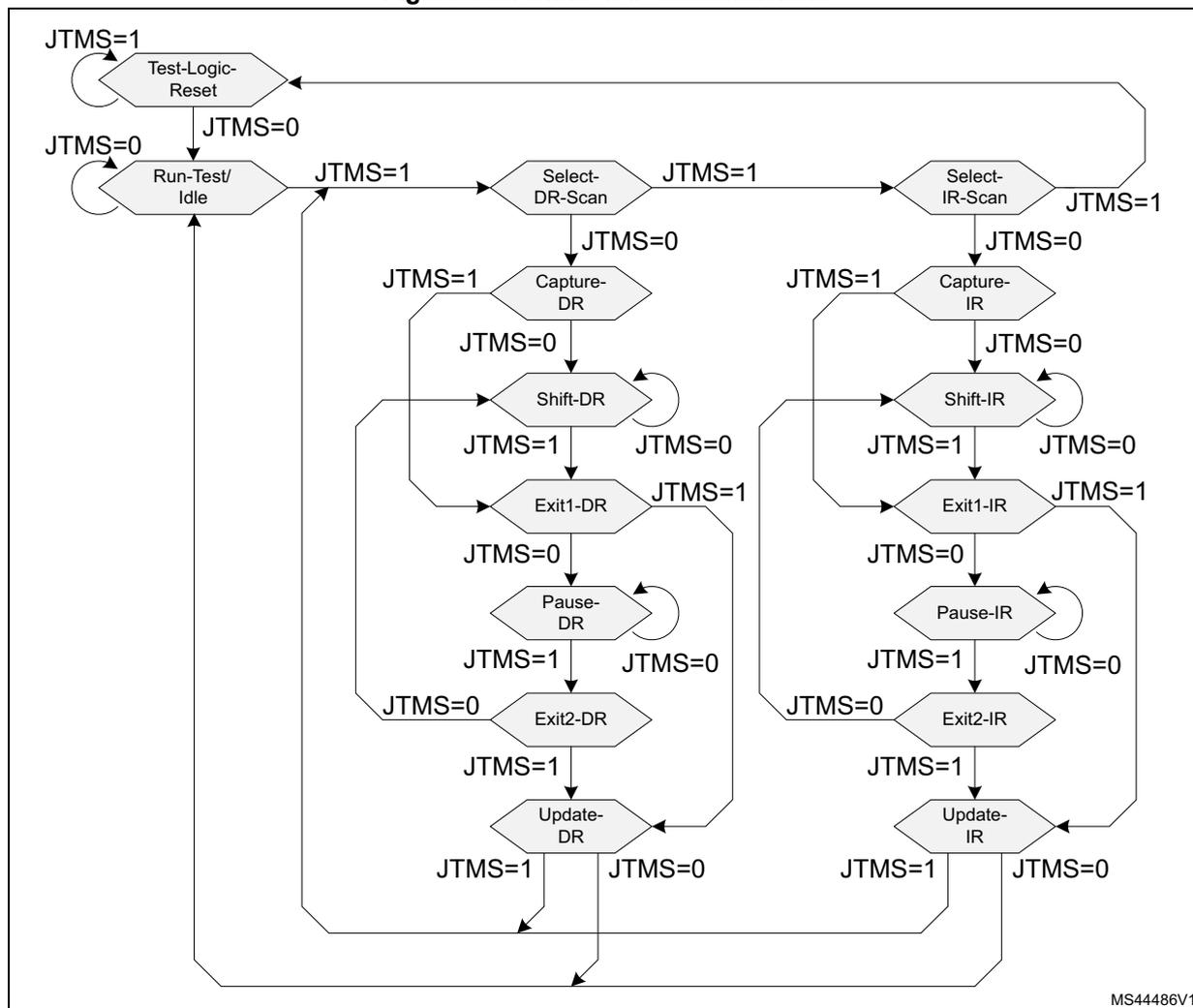

The JTAG-DP implements a TAP state machine (TAPSM), shown in the figure below, based on IEEE Std 1149.1-1990. The state machine controls two scan chains, one associated with an instruction register (IR) and the other one with a number of data registers (DR).

Figure 805. JTAG TAP state machine

stateDiagram-v2

[*] --> Test-Logic-Reset: JTMS=1

Test-Logic-Reset --> Test-Logic-Reset: JTMS=1

Test-Logic-Reset --> Run-Test/Idle: JTMS=0

Run-Test/Idle --> Run-Test/Idle: JTMS=0

Run-Test/Idle --> Select-DR-Scan: JTMS=1

Run-Test/Idle --> Select-IR-Scan: JTMS=1

Select-DR-Scan --> Select-DR-Scan: JTMS=1

Select-DR-Scan --> Capture-DR: JTMS=0

Select-IR-Scan --> Select-IR-Scan: JTMS=1

Select-IR-Scan --> Capture-IR: JTMS=0

Capture-DR --> Capture-DR: JTMS=1

Capture-DR --> Shift-DR: JTMS=0

Capture-IR --> Capture-IR: JTMS=1

Capture-IR --> Shift-IR: JTMS=0

Shift-DR --> Shift-DR: JTMS=0

Shift-DR --> Exit1-DR: JTMS=1

Shift-IR --> Shift-IR: JTMS=0

Shift-IR --> Exit1-IR: JTMS=1

Exit1-DR --> Exit1-DR: JTMS=1

Exit1-DR --> Pause-DR: JTMS=0

Exit1-IR --> Exit1-IR: JTMS=1

Exit1-IR --> Pause-IR: JTMS=0

Pause-DR --> Pause-DR: JTMS=0

Pause-DR --> Exit2-DR: JTMS=1

Pause-IR --> Pause-IR: JTMS=0

Pause-IR --> Exit2-IR: JTMS=1

Exit2-DR --> Exit2-DR: JTMS=0

Exit2-DR --> Update-DR: JTMS=1

Exit2-IR --> Exit2-IR: JTMS=0

Exit2-IR --> Update-IR: JTMS=1

Update-DR --> Update-DR: JTMS=0

Update-DR --> Run-Test/Idle: JTMS=1

Update-IR --> Update-IR: JTMS=0

Update-IR --> Run-Test/Idle: JTMS=1

The operation of the JTAG-DP is as follows:

- 1. When the TAPSM goes through the Capture-IR state, 0b0001 is transferred to the instruction register (IR) scan chain. The IR scan chain is connected between JTDI and JTDO.

- 2. While the TAPSM is in the Shift-IR state, the IR scan chain shifts one bit for each rising edge of JTCK. This means that on the first tick:

- – The LSB of the IR scan chain is output on JTDO.

- – Bit[n] of the IR scan chain is transferred to bit[n-1].

- – The value on JTDI is transferred to the MSB of the IR scan chain.

- 3. When the TAPSM goes through the Update-IR state, the value scanned into the IR scan chain is transferred to the instruction register.

- 4. When the TAPSM goes through the Capture-DR state, a value is transferred from one of the data registers to one of the DR scan chains, connected between JTDI and JTDO.

- 5. The value held in the instruction register determines which data register, and associated DR scan chain, are selected.

- 6. This data is then shifted while the TAPSM is in the Shift-DR state, in the same manner as the IR shifts in the Shift-IR state.

- 7. When the TAPSM goes through the Update-DR state, the value scanned into the DR scan chain is transferred to the selected data register.

- 8. When the TAPSM is in the Run-Test/Idle state, no special actions occurs. The IDCODE instruction is loaded in IR.

When active, the nJTRST signal resets the state machine asynchronously to the test-logic-reset state.

The data registers corresponding to the 4-bit IR instructions are listed in the table below.

Table 633. JTAG-DP data registers

| IR instruction | DR register | Scan chain length | Description |

|---|---|---|---|

| 0000 to 0111 | (BYPASS) | 1 | Not implemented: BYPASS selected |

| 1000 | ABORT | 35 | ABORT register – bits 31:1 = reserved – bit 0 = APABORT: write 1 to generate an AP abort. |

| 1001 | (BYPASS) | 1 | Reserved: BYPASS selected |

| 1010 | DPACC | 35 | Debug port access register Initiates the debug port and gives access to a debug port register. – When transferring data IN: bits 34:3 = DATA[31:0] = 32-bit data to transfer for a write request bits 2:1 = A[3:2] = 2-bit address of a debug port register bit 0 = RnW = read request (1) or write request (0) – When transferring data OUT: bits 34:3 = DATA[31:0] = 32-bit data read following a read request bits 2:0 = ACK[2:0] = 3-bit acknowledge: – 010 = OK/FAULT – 001 = WAIT – others = reserved |

Table 633. JTAG-DP data registers (continued)

| IR instruction | DR register | Scan chain length | Description |

|---|---|---|---|

| 1011 | APACC | 35 | Access port access register Initiates an access port and gives access to an access port register. – When transferring data IN: bits 34:3 = DATA[31:0] = 32-bit data to shift in for a write request bits 2:1 = A[3:2] = 2-bit sub-address of an access port register bit 0 = RnW= Read request (1) or write request (0) – When transferring data OUT: bits 34:3 = DATA[31:0] = 32-bit data read following a read request bits 2:0 = ACK[2:0] = 3-bit Acknowledge: – 010 = OK/FAULT – 001 = WAIT – others= reserved |

| 1100 | (BYPASS) | 1 | Reserved: BYPASS selected |

| 1101 | (BYPASS) | 1 | Reserved: BYPASS selected |

| 1110 | IDCODE | 32 | Identification code 0x0BA0 4477: Cortex-M33 JTAG debug port ID code |

| 1111 | BYPASS | 1 | Bypass: A single JTAG cycle delay is inserted between JTDI and JTDO. |

The DR registers are detailed in the Arm Debug Interface Architecture Specification (see Section 57.13: References ).

57.3.2 Serial-wire debug port

The serial-wire debug protocol uses the following pins:

- • SWCLK: clock from host to target

- • SWDIO: bi-directional serial data

Serial data is transferred LSB first, synchronously with the clock.

A transfer comprises three phases:

- 1. packet request (8 bits) transmitted by the host (see Table 634 )

- 2. acknowledge response (3 bits) transmitted by the target (see Table 635 )

- 3. data transfer (33 bits) transmitted by the host (in case of a write) or target (in case of a read) (see Table 636 )

The data transfer only occurs if the acknowledge response is OK.

Between each phase, if the direction of the data is reversed, a single clock cycle turn-around time is inserted.

Table 634. Packet request

| Bit field | Name | Description |

|---|---|---|

| 0 | Start | Must be 1. |

| 1 | APnDP | – 0: DP register access - see

Section 57.3.3: Debug port registers – 1: AP register access - see Section 57.4: Access ports |

| Bit field | Name | Description |

|---|---|---|

| 2 | RnW | – 0: write request – 1: read request |

| 4:3 | A(3:2) | Address field of the DP or AP register (refer to Table 637 or Table 638 ) |

| 5 | Parity | Single bit parity of preceding bits |

| 6 | Stop | 0 |

| 7 | Park | Not driven by host, must be read as 1 by target. |

| Bit field | Name | Description |

|---|---|---|

| 2:0 | ACK | – 000: FAULT – 010: WAIT – 100: OK |

| Bit field | Name | Description |

|---|---|---|

| 31:0 | WDATA or RDATA | Write or read data |

| 32 | Parity | Single bit parity of 32 data bits |

In the case of a FAULT or WAIT ACK response from the target, the data transfer phase is canceled, unless overrun detection is enabled: in this case, the data is ignored by the target (in the case of a write), or not driven (in the case of a read).

A line reset must be generated by the host when it is first connected, or following a protocol error. The line reset consists in 50 or more SWCLK cycles with SWDIO high, followed by two SWCLK cycles with SWDIO low.

For more details on the serial-wire debug protocol, refer to the Arm Debug Interface Architecture Specification [ 1 ].

Note: The SWJ-DP implements SWD protocol version 2.

57.3.3 Debug port registers

Both SW-DP and JTAG-DP access the debug port (DP) registers listed in Table 637 .

The debugger can access the DP registers as follows:

- 1. Program the A(3:2) field in the DPACC register, if using JTAG, with the register address within the bank. Program the RnW bit to select a read or write. In the case of a write, program the data field with the write data. If using SWD, the A(3:2) and RnW fields are part of the packet request word sent to the SW-DP with the APnDP bit reset (see Table 634 ). The write data are sent in the data phase.

- 2. To access one of the banked DP registers at address 0x4, the register number must first be written to the DP_SELECTR register at address 0x8. Any subsequent read or

write to address 0x4 access the register corresponding to the contents of DP_SELECTR.

DP debug port identification register (DP_PIDR)

Address offset: 0x0

Reset value: 0x0BE0 2477 (SW DP)

For JTAG_DP, reset value is 0x0BE0 1477

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| REVISION[3:0] | PARTNO[7:0] | Res. | Res. | Res. | MIN | ||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | |||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| VERSION[3:0] | DESIGNER[10:0] | Res. | |||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | |

Bits 31:28 REVISION[3:0] : Revision code

0x0: r0p0 (for JTAG_DP and SW_DP)

Bits 27:20 PARTNO[7:0] : Part number for the debug port

0xBE

Bits 19:17 Reserved, must be kept at reset value.

Bit 16 MIN : Minimal debug port (MINDP) implementation

0x1: MINDP implemented (transaction counter and pushed operations are not supported)

Bits 15:12 VERSION[3:0] : Debug port architecture version

0x1: DPv1 (JTAG_DP)

0x1: DPv2 (SW_DP)

Bits 11:1 DESIGNER[10:0] : JEDEC designer identity code

0x23B: Arm JEDEC code

Bit 0 Reserved, must be kept at reset value.

DP abort register (DP_ABORT)

Address offset: 0x0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ORUN ERRCLR R | WDER RCLR | STKER RCLR | Res. | DAPAB ORT |

| w | w | w | w |

Bits 31:5 Reserved, must be kept at reset value.

Bit 4 ORUNERRCLR : Overrun error clear

0: No effect

1: STICKYORUN bit cleared in DP_CTRL_STAT register

Bit 3 WDERRCLR : Write data error clear

0: No effect

1: WDATAERR bit cleared in DP_CTRL_STAT register

Bit 2 STKERRCLR : Sticky error clear

0: No effect

1: STICKYERR bit cleared in DP_CTRL_STAT register

Bit 1 Reserved, must be kept at reset value.

Bit 0 DAPABORT : Current AP transaction aborted if excessive number of WAIT responses returned

This bit indicates that the transaction is stalled.

0: No effect

1: Transaction aborted

DP control and status register (DP_CTRL_STAT)

Address offset: 0x4

Reset value: 0x0000 0000

This register is accessible when DP_SELECT.DPBANKSEL[3:0] = 0x0.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | CDBG PWRU PACK | CDBG PWRU PREQ | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| r | r | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | WDATA ERR | READ OK | STICK YERR | Res. | Res. | Res. | STICK YORUN | ORUN DETECT |

| r | r | r | r | r |

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 CDBGPWRUPACK : Debug power-up acknowledge

See description in Section 57.2.5: Debug and low-power modes .

0: DCLK gated

1: DCLK enabled

Bit 28 CDBGPWRUPREQ : Debug power-up request

This bit controls the DCLK enable request signal.

0: Requests DCLK gating

1: Requests DCLK enable

Bits 27:8 Reserved, must be kept at reset value.

Bit 7 WDATAERR : Write data error (read-only) in SW-DP

This bit indicates that there is a parity or framing error on the data phase of a write, or a write accepted by the DP is then discarded without being submitted to the AP.

This bit is reset by writing 1 to DP_ABORT.WDERRCLR.

0: No error

1: An error occurred

Note: This bit is reserved in JTAG-DP.

Bit 6 READOK : AP read response (read-only) in SW-DP

This bit indicates the response to the last AP read access.

0: Read not OK

1: Read OK

Note: This bit is reserved in JTAG-DP.

Bit 5 STICKYERR : Transaction error (read-only in SW-DP, read/write in JTAG-DP)

This bit indicates that an error occurred in an AP transaction. It is reset by writing 1 to DP_ABORT.STKERRCLR (in SW-DP and JTAG-DP)

0: No error

1: An error occurred

Bits 4:2 Reserved, must be kept at reset value.

Bit 1 STICKYORUN : Overrun (read-only in SW-DP, read/write in JTAG-DP)

This bit indicates that an overrun occurred (new transaction received before previous transaction completed). This bit is only set if the ORUNDETECT bit is set. It is reset by writing 1 to DP_ABORT.ORUNERRCLR (in SW-DP and JTAG-DP).

0: No overrun

1: An overrun occurred

Bit 0 ORUNDETECT : Overrun detection mode enable

0: Disabled

1: Enabled. In the event of an overrun, the STICKYORUN bit is set, and subsequent transactions are blocked until the STICKYORUN bit is cleared.

DP data link control register (DP_DLCR)

Address offset: 0x4

Reset value: 0x0000 0000

This register is accessible when DP_SELECT.DPBANKSEL[3:0] = 0x1.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | TURNROUND[1:0] | WIREMODE[1:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| r | r | r | r |

Bits 31:10 Reserved, must be kept at reset value.

Bits 9:8 TURNROUND[1:0] : Tristate period for SWDIO

0x0: One data bit period

Bits 7:6 WIREMODE[1:0] : SW-DP mode

0x0: Synchronous mode

Bits 5:0 Reserved, must be kept at reset value.

DP target identification register (DP_TARGETID)

Address offset: 0x4

Reset value: 0xXXXX 0041

This register is accessible when DP_SELECT.DPBANKSEL[3:0] = 0x2.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TREVISION[3:0] | TPARTNO[15:4] | ||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TPARTNO[3:0] | TDESIGNER[10:0] | Res. | |||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | |

Bits 31:28 TREVISION[3:0] : Target revision

0x1: For all revisions

Bits 27:12 TPARTNO[15:0] : Target part number

0x42A0: STM32U3B5/3C5

0x42B0: STM32U356/366

0x4540: STM32U375/385

Bits 11:1 TDESIGNER[10:0] : Target designer JEDEC code

0x020: STMicroelectronics

Bit 0 Reserved, must be kept at reset value.

DP data link protocol identification register (DP_DLPIDR)

Address offset: 0x4

Reset value: 0x0000 0001

This register is accessible when DP_SELECT.DPBANKSEL[3:0] = 0x3.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TINSTANCE[3:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |||

| r | r | r | r | ||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PROTSVN[3:0] | |||

| r | r | r | r | ||||||||||||

Bits 31:28 TINSTANCE[3:0] : Target instance number

This bifield defines the instance number for the device in a multi-drop system.

0x0: Instance number 0

Bits 27:4 Reserved, must be kept at reset value.

Bits 3:0

PROTSVN[3:0]

: Serial-wire debug protocol version

0x1: version 2

DP event status register (DP_EVENTSTAT)

Address offset: 0x4

Reset value: 0x0000 0001

This register is accessible when DP_SELECT.DPBANKSEL[3:0] = 0x4.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | EA |

| r |

Bits 31:1 Reserved, must be kept at reset value.

Bit 0

EA

: Event status flag

0: Cortex-M33 processor halted

1: Cortex-M33 processor not halted

DP event status register (DP_RESEND)

Address offset: 0x8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| RESEND[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RESEND[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0

RESEND[31:0]

: Value returned by the last AP read or DP_RDBUFF read

This register is used in the event of a corrupted read transfer.

DP access port select register (DP_SELECT)

Address offset: 0x8

Reset value: 0xXXXX XXXX

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| APSEL[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |||||||

| w | w | w | w | w | w | w | w | ||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | APBANKSEL[3:0] | DPBANKSEL[3:0] | ||||||

| w | w | w | w | w | w | w | w | ||||||||

Bits 31:24 APSEL[7:0] : Access port select

This bitfield selects the access port for the next transaction.

0x0: AP0 - Cortex-M33 debug access port (AHB-AP)

Others: Reserved

Bits 23:8 Reserved, must be kept at reset value.

Bits 7:4 APBANKSEL[3:0] : AP register bank select

This bitfield selects the 4-word register bank on the active AP for the next transaction.

Bits 3:0 DPBANKSEL[3:0] : DP register bank select

This bitfield selects the register at address 0x4 of the debug port.

0x0: DP_CTRL_STAT register

0x1: DP_DLCR register

0x2: DP_TARGETID register

0x3: DP_DLPIDR register

0x4: DP_EVENTSTAT register

Others: Reserved

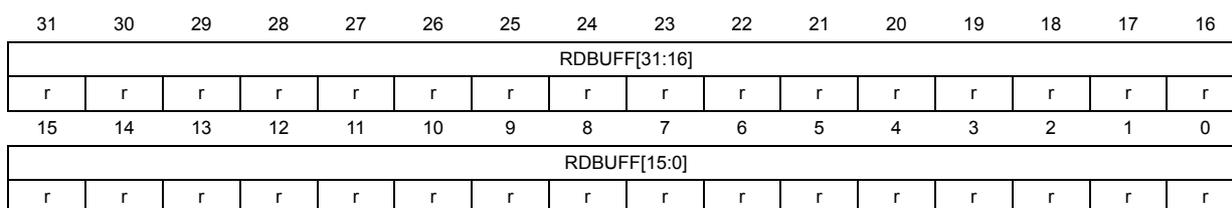

DP read buffer register (DP_RDBUFF)

Address offset: 0xC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| RDBUFF[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RDBUFF[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 RDBUFF[31:0] : Value returned by the last AP read access

The value returned by an AP read access can either be obtained using a second read access to the same address, that initiates a new transaction on the corresponding bus, or else it can be read from this register, in which case no new AP transaction occurs.

57.3.4 Debug port register map

Table 637. Debug port register map and reset values

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x0 | DP_PIDR | REVISION [3:0] | PARTNO[7:0] | Res. | Res. | Res. | MIN | VERSION [3:0] | DESIGNER[10:0] | Res. | |||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | |||||

| 0x0 | DP_ABORT | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ORUNERRCLR | WDERRCLR | STKERRCLR | Res. |

| Reset value | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||||

Table 637. Debug port register map and reset values (continued)

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x4 (1) | DP_CTRL_STAT | Res. | Res. | CDBGPWURUPACK | CDBGPWURUPREQ | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | WDATAERR | READOK | STICKYERR | Res. | Res. | Res. | STICKYORUN | ORUNDETECT |

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||||||||||

| 0x4 (2) | DP_DLCR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TURNROUND [1:0] | WIREMODE [1:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||||

| 0x4 (3) | DP_TARGETID | TREVISON [3:0] | TPARTNO[15:0] | Res. | |||||||||||||||||||||||||||||

| Reset value | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0x4 (4) | DP_DLPIDR | TINSTANCE [3:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PROTSVN [3:0] | Res. | |||

| Reset value | 0 | 0 | 0 | 0 | 0 | 1 | |||||||||||||||||||||||||||

| 0x4 (5) | DP_EVENTSTAT | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | EA |

| Reset value | 1 | ||||||||||||||||||||||||||||||||

| 0x8 | DP_RESEND | RESEND[31:0] | |||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x8 | DP_SELECT | APSEL[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | APBANKSEL [3:0] | DPBANKSEL [3:0] | Res. | ||||||||||||

| Reset value | x | x | x | x | x | x | x | x | x | x | x | x | x | x | x | ||||||||||||||||||

| 0xC | DP_RDBUFF | RDBUFF[31:0] | |||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

- 1. DP_SELECTR.DPBANKSEL[3:0] = 0x0.

- 2. DP_SELECTR.DPBANKSEL[3:0] = 0x1.

- 3. DP_SELECTR.DPBANKSEL[3:0] = 0x2.

- 4. DP_SELECTR.DPBANKSEL[3:0] = 0x3.

- 5. DP_SELECTR.DPBANKSEL[3:0] = 0x4.

57.4 Access ports

There is one access port (AP) attached to the DP. It enables the access to the debug and trace features integrated in the Cortex-M33 processor core via its internal AHB bus.

57.4.1 Access port registers

The access port is of MEM-AP type: the debug and trace component registers are mapped in the address space of the AHB. The AP is seen by the debugger as a set of 32-bit registers organized in banks of four registers each. Some of these registers are used to

configure or monitor the AP itself, while others are used to perform a transfer on the bus. The AP registers are listed in Table 638 .

The address of the AP registers is composed of the following fields:

- • bits [7:4]: content of APBANKSEL[3:0] in DP_SELECT

- • bits [3:2]: content of the A(3:2) field of the APACC data register in the JTAG-DP (see Table 633 ), or of the SW-DP packet request (see Table 634 ), depending on the debug interface used

- • bits [1:0]: always set to 0

The content of DP_SELECT.APSEL[3:0] defines which MEM-AP is being accessed.

The debugger can access the AP registers as follows:

- 1. Program APSEL[3:0] in DP_SELECT to choose the AP, and APBANKSEL[3:0] in DP_SELECT to select the register bank to be accessed.

- 2. Program the A(3:2) field in the APACC data register, if using JTAG, with the register address within the bank. Program the RnW bit to select a read or write. In the case of a write, program the DATA field with the write data. If using SWD, the A(3:2) and RnW fields are part of the packet request word sent to the SW-DP with the APnDP bit set (see Table 634 ). The write data is sent in the data phase.

The debugger can access the memory mapped debug component registers through the AP registers (using the above AP register access procedure) as follows:

- 1. Program the transaction target address in AP_TAR.

- 2. Program AP_CSW, if necessary, with the transfer parameters (AddrInc for example).

- 3. Write to or read from AP_DRW to initiate a bus transaction at the address held in AP_TAR. Alternatively, a read or write to AP_BDn triggers an access to TAR[31:4] + n address, allowing up to four consecutive addresses to be accessed without changing the address in the AP_TAR register.

For more detailed information on the MEM-AP, refer to the Arm Debug Interface Architecture Specification ( Section 57.13: References ).

AP control/status word register (AP_CSW)

Address offset: 0x0

Reset value: 0x0100 00X0

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | PROT[6] | Res. | Res. | PROT[3:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |||

| rw | rw | rw | rw | r | |||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | DBGST ATUS | ADDRINC[1:0] | Res. | SIZE[2:0] | |||

| r | rw | rw | rw | rw | rw | ||||||||||

Bit 31 Reserved, must be kept at reset value.

Bit 30 PROT[6] : Secure transfer request

This bit sets the protection attribute HPROT[6] of the bus transfer.

0: Secure transfer

1: Nonsecure transfer

Bits 29:28 Reserved, must be kept at reset value.

Bits 27:24 PROT[3:0] : Bus transfer protection

This bitfield sets the protection attributes HPROT[3:0] of the bus transfer.

0bXXX1: Data access (bit 24 is read only)

0bXX0X: Unprivilege mode

0bXX1X: Privilege mode

0bX0XX: Nonbufferable

0bX1XX: Bufferable

0b0XXX: Non-shareable, no look-up, non-modifiable

0b1XXX: Shareable, look-up, modifiable

Bits 23:7 Reserved, must be kept at reset value.

Bit 6 DBGSTATUS : Device enable (DEVICEEN) status

0: AHB transfers blocked

1: AHB transfers enabled

Bits 5:4 ADDRINC[1:0] : Auto-increment mode

Defines whether TAR address is automatically incremented after a transaction.

0x0: No auto-increment

0x1: Address incremented by the size in bytes of the transaction (SIZE[2:0])

Other: Reserved

Bit 3 Reserved, must be kept at reset value.

Bits 2:0 SIZE[2:0] : Size of next memory access transaction

0x0: Byte (8-bit)

0x1: Half-word (16-bit)

0x2: Word (32-bit)

Others: Reserved

AP transfer address register (AP_TAR)

Address offset: 0x04

Reset value: 0xXXXX XXXX

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TA[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TA[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 TA[31:0] : Address of current transfer

AP data read/write register (AP_DRWR)Address offset: 0x0C

Reset value: 0xXXXX XXXX

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Address offset: 0x10 + 0x4 * n, (n = 0 to 3)

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TBD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TBD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

The auto address incrementing is not performed on AP_BD0-3. Banked transfers are only supported for word transfers.

AP configuration register (AP_CFG)Address offset: 0xF4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | LD | LA | BE |

| r | r | r |

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 LD : Large data0: Data not larger than 32 bits supported

Bit 1 LA : Long address0: Physical addresses not larger than 32 bits supported

Bit 0

BE

: Big endian

0: Only little-endian supported

AP base address register (AP_BASE)

Address offset: 0xF8

Reset value: 0xE00F E003

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| BASEADDR[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BASEADDR[15:12] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | FORMAT | ENTRYPRESENT | |||

| r | r | r | r | r | r | ||||||||||

Bits 31:12 BASEADDR[31:12] : base address (bits 31 to 12) of the first ROM table

The 12 LSBs are zero since the ROM table must be aligned on a 4-Kbyte boundary.

0xE00FE

Bits 11:2 Reserved, must be kept at reset value.

Bit 1

FORMAT

: base-address register format

1: Arm debug interface v5

Bit 0

ENTRYPRESENT

: debug components presence

Indicates that debug components are present on the access port bus.

1: debug components present

AP identification register (AP_IDR)

Address offset: 0xFC

Reset value: 0x1477 0015

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| REVISION[3:0] | JEDECBANK[3:0] | JEDECCODE[6:0] | CLASS[3] | ||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CLASS[2:0] | Res. | Res. | Res. | Res. | Res. | VARIANT[3:0] | TYPE[3:0] | ||||||||

| r | r | r | r | r | r | r | r | r | r | r | |||||

Bits 31:28

REVISION[3:0]

: Revision number

0x1: r0p1

Bits 27:24

JEDECBANK[3:0]

: JEDEC bank

0x4: Arm

Bits 23:17

JEDECCODE[6:0]

: JEDEC code

0x3B: Arm

0x8: MEM-AP

Bits 12:8 Reserved, must be kept at reset value.

Bits 7:4 VARIANT[3:0] : Variant0x1: Cortex-M33

Bits 3:0 TYPE[3:0] : Type0x5: AHB5

57.4.2 Access port register map

Table 638. Access port register map and reset values

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x00 | AP_CSW | Res | PROT[8] | Res | Res | PROT[3:0] | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | DBGSTATUS | ADDRINC[1:0] | Res | SIZE[2:0] | ||||||

| Reset value | 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 0 | 0 | ||||||||||||||||||||||

| 0x04 | AP_TAR | TA[31:0] | |||||||||||||||||||||||||||||||

| Reset value | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| 0x08 | Reserved | Reserved | |||||||||||||||||||||||||||||||

| 0x0C | AP_DRW | TD[31:0] | |||||||||||||||||||||||||||||||

| Reset value | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | |

| 0x10 + 0x4 * n (n=0 to 3) | AP_BDn | TBD[31:0] | |||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x20 to 0xF0 | Reserved | Reserved | |||||||||||||||||||||||||||||||

| 0xF4 | AP_CFG | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | LD | LA | BE |

| Reset value | 0 | 0 | 0 | ||||||||||||||||||||||||||||||

| 0xF8 | AP_BASE | BASEADDR[31:12] | Res | Res | Res | Res | Res | Res | Res | Res | Res | Res | FORMAT | ENTRYPRESENT | |||||||||||||||||||

| Reset value | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | |||||||||||

| 0xFC | AP_IDR | REVISION[3:0] | JEDECBANK[3:0] | JEDECCODE[6:0] | CLASS[3:0] | Res | Res | Res | Res | Res | VARIANT[3:0] | TYPE[3:0] | |||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | ||||||

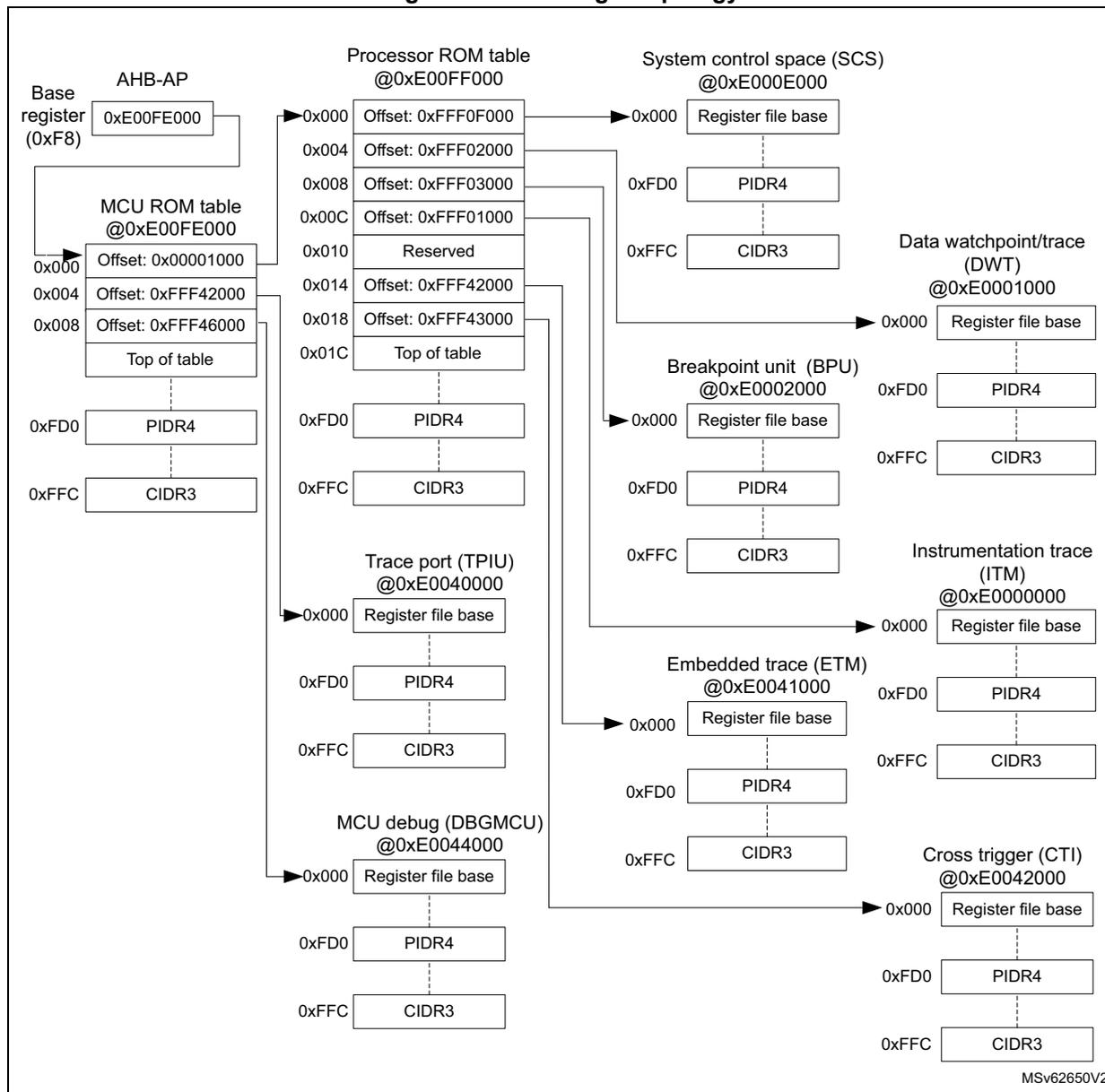

57.5 ROM tables

The ROM table is a CoreSight component that contains the base addresses of all the CoreSight debug components accessible via the AHB-AP. These tables allow a debugger to discover the topology of the CoreSight system automatically.

There are two ROM tables in the CPU sub-system. The MCU ROM table is pointed to by the base register in the AHB-AP. It contains the base-address pointer for the processor ROM table and for the TPIU registers, as well as for the MCU debug unit.

The MCU ROM table (see the table below) occupies a 4-Kbyte, 32-bit wide chunk of address space, from 0xE00F E000 to 0xE00F EFFC.

Table 639. MCU ROM table

| Address in ROM table | Component name | Component base address | Component address offset | Size (Kbytes) | Entry |

|---|---|---|---|---|---|

| 0xE00F E000 | Processor ROM table | 0xE00F F000 | 0x0000 1000 | 4 | 0x0000 1003 |

| 0xE00F E004 | TPIU | 0xE004 0000 | 0xFFF4 2000 | 4 | 0xFFF4 2003 |

| 0xE00F E008 | DBGMCU | 0xE004 4000 | 0xFFF4 6000 | 4 | 0xFFF4 6003 |

| 0xE00F E00C | Reserved | - | - | - | 0x1FF0 2002 |

| 0xE00F E010 | Top of table | - | - | - | 0x0000 0000 |

| 0xE00F E014 to 0xE00F EFC8 | Reserved | - | - | - | 0x0000 0000 |

| 0xE00F EFCC to 0xE00F EFFC | ROM table registers | - | - | - | See Table 641 |

The processor ROM table contains the base-address pointer for the system control space (SCS) registers, that allow the debugger to identify the CPU core, as well as for the BPU, DWT, ITM, ETM and CTI.

The processor ROM table (see the table below) occupies a 4-Kbyte, 32-bit wide chunk of address space, from 0xE00F F000 to 0xE00F FFFC.

Table 640. Processor ROM table

| Address in ROM table | Component name | Component base address | Component address offset | Size (Kbytes) | Entry |

|---|---|---|---|---|---|

| 0xE00F F000 | SCS | 0xE000 E000 | 0xFFF0 F000 | 4 | 0xFFF0 F003 |

| 0xE00F F004 | DWT | 0xE000 1000 | 0xFFF0 2000 | 4 | 0xFFF0 2003 |

| 0xE00F F008 | BPU | 0xE000 2000 | 0xFFF0 3000 | 4 | 0xFFF0 3003 |

| 0xE00F F00C | ITM | 0xE000 0000 | 0xFFF0 1000 | 4 | 0xFFF0 1003 |

| 0xE00F F010 | Reserved | - | - | - | 0xFFF4 1002 |

| 0xE00F F014 | ETM | 0xE004 1000 | 0xFFF4 2000 | 4 | 0xFFF4 2003 |

| 0xE00F F018 | CTI | 0xE004 2000 | 0xFFF4 3000 | 4 | 0xFFF4 3003 |

| 0xE00F F01C | Reserved | - | - | - | 0xFFF4 4002 |

| 0xE00F F020 | Top of table | - | - | - | 0x0000 0000 |

| 0xE00F F024 to 0xE00F FFC8 | Reserved | - | - | - | 0x0000 0000 |

| 0xE00F FFCC to 0xE00F FFFC | ROM table registers | - | - | - | See Table 642 |

The topology for the CoreSight components in the Cortex -M33 is shown in the figure below.

Figure 806. CoreSight topology

The diagram illustrates the CoreSight topology for the Cortex-M33. It shows the following components and their connections:

- Base register (0xF8) : Located at address 0xE00FE000. It contains the MCU ROM table @0xE00FE000 with entries for offsets 0x00001000, 0xFFF42000, and 0xFFF46000. It also includes registers PIDR4 at 0xFD0 and CIDR3 at 0xFFC.

- Processor ROM table @0xE00FF000 : Contains entries for offsets 0xFFF0F000, 0xFFF02000, 0xFFF03000, 0xFFF01000, and 0xFFF42000, plus reserved areas and a 'Top of table' entry at 0x01C. It also includes registers PIDR4 at 0xFD0 and CIDR3 at 0xFFC.

- System control space (SCS) @0xE000E000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- Data watchpoint/trace (DWT) @0xE0001000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- Breakpoint unit (BPU) @0xE0002000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- Trace port (TPIU) @0xE0040000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- MCU debug (DBGMCU) @0xE0044000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- Embedded trace (ETM) @0xE0041000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- Instrumentation trace (ITM) @0xE0000000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

- Cross trigger (CTI) @0xE0042000 : Contains the Register file base at 0x000, PIDR4 at 0xFD0, and CIDR3 at 0xFFC.

Connections are shown via arrows indicating the flow of data and control signals between the base register, ROM tables, and the various CoreSight components. The diagram is labeled with MSV62650V2 at the bottom right.

57.5.1 MCU ROM table registers

MCU ROM memory type register (MCUROM_MEMTYPER)

Address offset: 0xFCC

Reset value: 0x0000 0001

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SYSTM |

| r |

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 SYSTM : System memory

0x1: System memory present on this bus

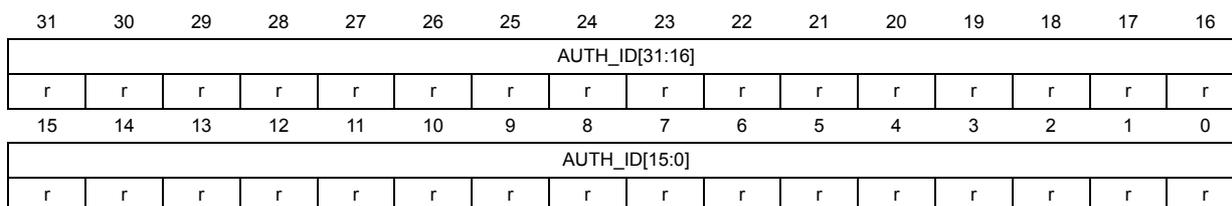

MCU ROM CoreSight peripheral identity register 4 (MCUROM_PIDR4)

Address offset: 0xFD0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SIZE[3:0] | JEP106CON[3:0] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 SIZE[3:0] : Register file size

0x0: The register file occupies a single 4-Kbyte region.

Bits 3:0 JEP106CON[3:0] : JEP106 continuation code

0x0: STMicroelectronics JEDEC continuation code

MCU ROM CoreSight peripheral identity register 0 (MCUROM_PIDR0)

Address offset: 0xFE0

Reset value: 0x0000 0054

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PARTNUM[7:0] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 PARTNUM[7:0] : Part number bits [7:0]

0x2A: STM32U3B5/3C5

0x2B: STM32U356/366

0x54: STM32U375/385

MCU ROM CoreSight peripheral identity register 1(MCUROM_PIDR1)

Address offset: 0xFE4

Reset value: 0x0000 0004

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JEP106ID[3:0] | PARTNUM[11:8] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 JEP106ID[3:0] : JEP106 identity code bits [3:0]

0x0: STMicroelectronics JEDEC code

Bits 3:0 PARTNUM[11:8] : Part number bits [11:8]

0x4: STM32U356/366 or STM32U375/385 or STM32U3B5/3C5

MCU ROM CoreSight peripheral identity register 2 (MCUROM_PIDR2)

Address offset: 0xFE8

Reset value: 0x0000 000A

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVISION[3:0] | JEDEC | JEP106ID[6:4] | |||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 REVISION[3:0] : Component revision number

0x0: rev r0p0

Bit 3 JEDEC : JEDEC assigned value

1: Designer identification specified by JEDEC

Bits 2:0 JEP106ID[6:4] : JEP106 identity code bits [6:4]

0x2: STMicroelectronics JEDEC code

MCU ROM CoreSight peripheral identity register 3 (MCUROM_PIDR3)

Address offset: 0xFEC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVAND[3:0] | CMOD[3:0] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 REVAND[3:0] : Metal fix version

0x0: No metal fix

Bits 3:0 CMOD[3:0] : Customer modified

0x0: No customer modifications

MCU ROM CoreSight component identity register 0 (MCUROM_CIDR0)

Address offset: 0xFF0

Reset value: 0x0000 000D

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[7:0] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 PREAMBLE[7:0] : Component identification bits [7:0]

0x0D: Common identification value

MCU ROM CoreSight peripheral identity register 1 (MCUROM_CIDR1)

Address offset: 0xFF4

Reset value: 0x0000 0010

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CLASS[3:0] | PREAMBLE[11:8] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4

CLASS[3:0]

: Component identification bits [15:12] - component class

0x1: ROM table component

Bits 3:0

PREAMBLE[11:8]

: Component identification bits [11:8]

0x0: Common identification value

MCU ROM CoreSight component identity register 2 (MCUROM_CIDR2)

Address offset: 0xFF8

Reset value: 0x0000 0005

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[19:12] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0

PREAMBLE[19:12]

: Component identification bits [23:16]

0x05: Common identification value

MCU ROM CoreSight component identity register 3 (MCUROM_CIDR3)

Address offset: 0xFFC

Reset value: 0x0000 00B1

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[27:20] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0

PREAMBLE[27:20]

: Component identification bits [31:24]

0xB1: Common identification value

57.5.2 MCU ROM table register map

Table 641. MCU ROM table register map and reset values

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SYSMEM | ||

| 0xFCC | MCUROM_MEMTYPER | ||||||||||||||||||||||||||||||||

| Reset value | 1 |

Table 641. MCU ROM table register map and reset values (continued)

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0xFD0 | MCUROM_PIDR4 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SIZE[3:0] | JEP106CON [3:0] | ||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||

| 0xFD4-0xFDC | Reserved | Reserved | |||||||||||||||||||||||||||||||

| 0xFE0 | MCUROM_PIDR0 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PARTNUM[7:0] | |||||||

| Reset value | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | |||||||||||||||||||||||||

| 0xFE4 | MCUROM_PIDR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JEP106ID [3:0] | PARTNUM [11:8] | ||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |||||||||||||||||||||||||

| 0xFE8 | MCUROM_PIDR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVISION [3:0] | JEDEC | JEP106ID [6:4] | |||||

| Reset value | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | |||||||||||||||||||||||||

| 0xFEC | MCUROM_PIDR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVAND[3:0] | CMOD[3:0] | ||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||

| 0xFF0 | MCUROM_CIDR0 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[7:0] | |||||||

| Reset value | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | |||||||||||||||||||||||||

| 0xFF4 | MCUROM_CIDR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CLASS[3:0] | PREAMBLE [11:8] | ||||||

| Reset value | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||

| 0xFF8 | MCUROM_CIDR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[19:12] | |||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | |||||||||||||||||||||||||

| 0xFFC | MCUROM_CIDR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[27:20] | |||||||

| Reset value | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | |||||||||||||||||||||||||

Refer to Section 2.3 for register boundary addresses.

57.5.3 Processor ROM table registers

CPU ROM memory type register (CPUROM_MEMTYPER)

Address offset: 0xFCC

Reset value: 0x0000 0001

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SYSME M |

| r |

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 SYSTEM : System memory

1: System memory present on this bus

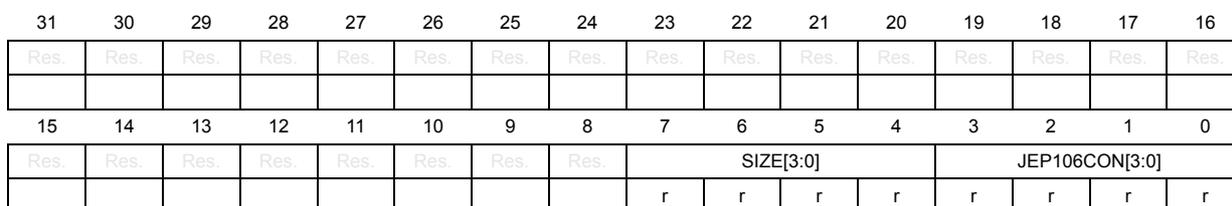

CPU ROM CoreSight peripheral identity register 4 (CPUROM_PIDR4)

Address offset: 0xFD0

Reset value: 0x0000 0004

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SIZE[3:0] | JEP106CON[3:0] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 SIZE[3:0] : Register file size

0x0: The register file occupies a single 4-Kbyte region.

Bits 3:0 JEP106CON[3:0] : JEP106 continuation code

0x4: Arm JEDEC continuation code

CPU ROM CoreSight peripheral identity register 0 (CPUROM_PIDR0)

Address offset: 0xFE0

Reset value: 0x0000 00C9

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PARTNUM[7:0] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 PARTNUM[7:0] : Part number bits [7:0]

0xC9: Cortex-M33

CPU ROM CoreSight peripheral identity register 1 (CPUROM_PIDR1)Address offset: 0xFE4

Reset value: 0x0000 00B4

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JEP106ID[3:0] | PARTNUM[11:8] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 JEP106ID[3:0] : JEP106 identity code bits [3:0]0xB: Arm JEDEC code

Bits 3:0 PARTNUM[11:8] : Part number bits [11:8]0x4: Cortex-M33

CPU ROM CoreSight peripheral identity register 2 (CPUROM_PIDR2)Address offset: 0xFE8

Reset value: 0x0000 000B

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVISION[3:0] | JEDEC | JEP106ID[6:4] | |||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 REVISION[3:0] : Component revision number0x0: rev r0p0

Bit 3 JEDEC : JEDEC assigned value1: Designer ID specified by JEDEC

Bits 2:0 JEP106ID[6:4] : JEP106 identity code bits [6:4]0x3: Arm JEDEC code

CPU ROM CoreSight peripheral identity register 3 (CPUROM_PIDR3)

Address offset: 0xFEC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVAND[3:0] | CMOD[3:0] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 REVAND[3:0] : Metal fix version

0x0: No metal fix

Bits 3:0 CMOD[3:0] : Customer modified

0x0: No customer modifications

CPU ROM CoreSight component identity register 0 (CPUROM_CIDR0)

Address offset: 0xFF0

Reset value: 0x0000 000D

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[7:0] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 PREAMBLE[7:0] : Component identification bits [7:0]

0x0D: Common identification value

CPU ROM CoreSight peripheral identity register 1 (CPUROM_CIDR1)

Address offset: 0xFF4

Reset value: 0x0000 0010

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CLASS[3:0] | PREAMBLE[11:8] | ||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4

CLASS[3:0]

: Component identification bits [15:12] - component class

0x1: ROM table component

Bits 3:0

PREAMBLE[11:8]

: Component identification bits [11:8]

0x0: Common identification value

CPU ROM CoreSight component identity register 2 (CPUROM_CIDR2)

Address offset: 0xFF8

Reset value: 0x0000 0005

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[19:12] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0

PREAMBLE[19:12]

: Component identification bits [23:16]

0x05: Common identification value

CPU ROM CoreSight component identity register 3 (CPUROM_CIDR3)

Address offset: 0xFFC

Reset value: 0x0000 00B1

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[27:20] | |||||||

| r | r | r | r | r | r | r | r | ||||||||

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0

PREAMBLE[27:20]

: Component identification bits [31:24]

0xB1: Common identification value

57.5.4 Processor ROM table register map

Table 642. CPU ROM table register map and reset values

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0xFCC | CPUROM_MEMTYPER | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SYSMEM |

| Reset value | 1 |

Table 642. CPU ROM table register map and reset values (continued)

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0xFD4-0xFDC | Reserved | Reserved | |||||||||||||||||||||||||||||||

| 0xFD0 | CPUROM_PIDR4 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SIZE[3:0] | JEP106CON [3:0] | |||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |||||||||||||||||||||||||

| 0xFE0 | CPUROM_PIDR0 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PARTNUM[7:0] | ||||||||

| Reset value | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | |||||||||||||||||||||||||

| 0xFE4 | CPUROM_PIDR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | JEP106ID [3:0] | PARTNUM [11:8] | |||||||

| Reset value | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | |||||||||||||||||||||||||

| 0xFE8 | CPUROM_PIDR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVISION [3:0] | JEDEC | JEP106ID [6:4] | ||||||

| Reset value | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | |||||||||||||||||||||||||

| 0xFEC | CPUROM_PIDR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | REVAND[3:0] | CMOD[3:0] | |||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||

| 0xFF0 | CPUROM_CIDR0 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[7:0] | ||||||||

| Reset value | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | |||||||||||||||||||||||||

| 0xFF4 | CPUROM_CIDR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CLASS[3:0] | PREAMBLE [11:8] | |||||||

| Reset value | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||

| 0xFF8 | CPUROM_CIDR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[19:12] | ||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | |||||||||||||||||||||||||

| 0xFFC | CPUROM_CIDR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PREAMBLE[27:20] | ||||||||

| Reset value | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | |||||||||||||||||||||||||

Refer to Section 2.3 for register boundary addresses.

57.6 Data watchpoint and trace unit (DWT)

57.6.1 DWT registers

The DWT registers are located at address range 0xE000 1000 to 0xE000 1FFC.

DWT control register (DWT_CTRL)

Address offset: 0x000

Reset value: 0x4000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| NUMCOMP[3:0] | NOTRCPKT | NOEXTTRIG | NOCYCCNT | NOPRFCNT | CYCDISS | CYCEVTENA | FOLDEVTENA | LSUEVTENA | SLEEPEVTENA | EXCEVTENA | CPIEVVTENA | EXCTRCEVENA | |||

| r | r | r | r | r | r | r | r | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | PCSAMPLEN A | SYNCTAP[1:0] | CYCTAP P | POSTINIT[3:0] | POSTRESET[3:0] | CYCCNTENA | |||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||

Bits 31:28 NUMCOMP[3:0] : Number of comparators implemented (read only)

0x4: Four comparators

Bit 27 NOTRCPKT : tTrace sampling and exception tracing support (read only)

0: Supported

Bit 26 NOEXTTRIG : External match signal, CMPMATCH support (read only)

0: Supported

Bit 25 NOCYCCNT : Cycle counter support (read only)

0: Supported

Bit 24 NOPRFCNT : Profiling counter support (read only)

0: Supported

Bit 23 CYCDISS : Cycle counter disabled secure

Controls whether the cycle counter is disabled in secure mode.

0: No effect

1: Disable incrementing of the cycle counter when the processor is in secure state

Bit 22 CYCEVTENA : Enable for POSTCNT underflow event counter packet generation

0: Disabled

1: Enabled

Bit 21 FOLDEVTENA : Enable for folded instruction counter overflow event generation

0: Disabled

1: Enabled

Bit 20 LSUEVTENA : Enable for LSU counter overflow event generation

0: Disabled

1: Enabled

Bit 19 SLEEPEVTENA : Enable for sleep counter overflow event generation

0: Disabled

1: Enabled

Bit 18 EXCEVTENA : Enable for exception overhead counter overflow event generation

0: Disabled

1: Enabled

Bit 17 CPIEVENA : Enable for CPI counter overflow event generation

0: Disabled

1: Enabled

Bit 16 EXCTRCENA : Enable for exception trace generation

0: Disabled

1: Enabled

Bits 15:13 Reserved, must be kept at reset value.

Bit 12 PCSAMPLENA : Enable for POSTCNT counter to be used as a timer for periodic PC sample packet generation

0: Disabled

1: Enabled

Bits 11:10 SYNCTAP[1:0] : Position of the synchronization packet counter tap on the CYCCNT counter

This bitfield determines the synchronization packet rate.

00: Disabled, no synchronization packets

01: Tap at CYCCNT[24]

10: Tap at CYCCNT[26]

11: Tap at CYCCNT[28]

Bit 9 CYCTAP : Selects the position of the POSTCNT tap on the CYCCNT counter

0: Tap at CYCCNT[6]

1: Tap at CYCCNT[10]

Bits 8:5 POSTINIT[3:0] : Initial value of the POSTCNT counter