19. Hardware signal processor (HSP)

This section only applies to STM32U3B5/3C5 devices.

19.1 HSP introduction

The hardware signal processor (HSP) is a dedicated signal processor engine. It can offload and speed up operations initially handled by the CPU. It targets the following application areas:

- • Control loops

- • Metering

- • Small convolutional neural networks

- • General-purpose signal processing

The HSP is built around a dedicated high-performance signal processor engine (SPE) working in 32-bit floating point or 8-bit integer. The SPE runs the HSP microcode (also named firmware).

A part of the microcode (firmware) is embedded in a private ROM. This microcode provides optimized signal processing functions, named “processing functions”.

The HSP can perform sequences of operations autonomously. These sequences are called “processing lists”.

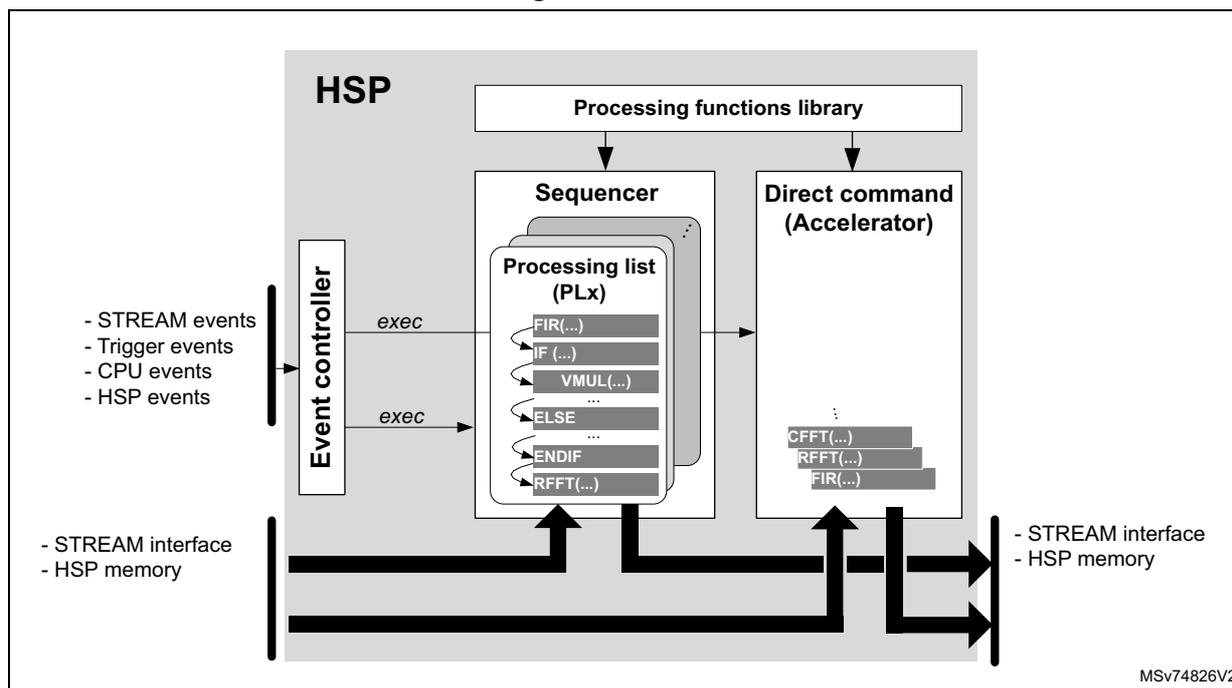

As shown in the figure below, the HSP proposes a sequencer to handle the processing lists, and a direct command interface for the accelerator function.

The peripherals connected to the event controller generate events according to their activity. These events are handled by the event controller, and the event having the highest priority activates a task. This task executes the recorded processing list. If other events are pending, the sequence is repeated when the execution of the current processing list is completed.

Each task can host a single processing list.

Figure 67. HSP functional view

The diagram illustrates the functional view of the HSP. On the left, an 'Event controller' receives inputs: '- STREAM events', '- Trigger events', '- CPU events', and '- HSP events'. It has two 'exec' output lines. The top 'exec' line connects to a 'Sequencer' block, which contains a 'Processing list (PLx)' with instructions: 'FIR(...)', 'IF (...)', 'VMUL(...)', 'ELSE ...', 'ENDIF', and 'RFFT(...)'. The bottom 'exec' line connects to a 'Direct command (Accelerator)' block, which contains instructions: 'CFFT(...)', 'RFFT(...)', and 'FIR(...)'. Above both the 'Sequencer' and 'Direct command' blocks is a 'Processing functions library' block. At the bottom, a thick horizontal bus connects the 'Event controller', 'Sequencer', and 'Direct command' blocks. On the left side of this bus are '- STREAM interface' and '- HSP memory'. On the right side are '- STREAM interface' and '- HSP memory'. The identifier 'MSV74826V2' is in the bottom right corner.

The application can record up to 37 processing lists into the HSP during the runtime. A processing list represents an HSP task. The execution of processing lists is triggered by events. The event sources can be:

- • STREAM interface

- • Trigger signals

- • Software triggers

The HSP offers the following bus interfaces:

- • An AHB slave port interface giving access to the HSP control registers (SP0)

- • An AHB slave port interface giving access to the HSP memories (SP1)

When the data to be processed are 16- or 32-bit integers, the HSP converts them into a 32-bit floating-point format before performing the required processing.

If the data are in 8-bit integer or 32-bit floating-point format, the HSP processes them directly.

Data exchange between the HSP and the application can be done in several ways:

- • Using the BRAM as a shared memory

- • Using data registers via the STREAM interface

After each processing task performed in 32-bit floating-point format, the HSP can provide the data either in floating-point or integer format. Processing performed using an 8-bit integer returns results in 8-bit integer format.

See the user manual HSP processing functions on STM32 MCUs (UM3360) .

Finally, the HSP offers an interrupt interface allowing the application to receive interrupts from a wide variety of events.

19.2 HSP main features

- • AHB slave interface for memories (SP1)

- • AHB slave interface for register control (SP0)

- • Rich set of signal processing commands (such as FFT, FIR, or IIR)

- • Support of 2D convolution for neural networks

- • Operations performed in floating-point single precision compliant with the IEEE-754 standard

The HSP FPU is compliant with the IEEE-754 standard with the following limitations:

- – Denormals are flushed to zero.

- – Only round to the nearest is supported.

- • Supported data formats:

- – Signed/unsigned 16-bit integer format

- – Signed/unsigned 32-bit integer format

- – 32-bit floating-point format

- – 8-bit integer (CNN functions)

- • Trigger inputs

- • Break generation

- • STREAM interface

- • Trigger outputs

- • Interrupt services

Targeted applications:

- • Audio: speech capture

- • Motor control

- • Digital power

- • Metering

19.3 HSP implementation

The table below details the set of features implemented into the product.

Table 143. HSP features (1)

| Feature | Values |

|---|---|

| SRAM instance containing BRAM, CRAM, and DRAM | SRAM4 |

| CRAM size | 20 Kbytes |

| DRAM size | 12 Kbytes |

| BRAM size | 32 Kbytes |

| Global Interrupt (hsp_it) | Yes |

| Error interrupt (hsp_err_it) | - |

| Event interrupt (hsp_evt_it) | - |

| Firmware event interrupt (hsp_fwevt_it) | - |

| HSPDMA and STI function | No |

| Number of DMA channels | - |

| Number of DMA requests, which can be connected to peripherals | - |

| Number of STIAP ports | - |

| Number of STIHP ports | - |

| Number of trigger inputs | 20 |

| Direct ADC interface function | No |

| Number of ADC interfaces | - |

| Maximum number of processing lists | 37 |

1. 'X' = supported, '-' = not supported.

Table 144. HSP memory mapping

| - | CRAM | DRAM | BRAM-A | BRAM-B | BRAM-AB | End of BRAM-AB |

|---|---|---|---|---|---|---|

| Address offset | 0x0000 0000 | 0x0000 5000 | 0x0000 8000 | 0x0000 C000 | 0x0001 0000 | 0x0001 3FFF |

19.4 HSP functional description

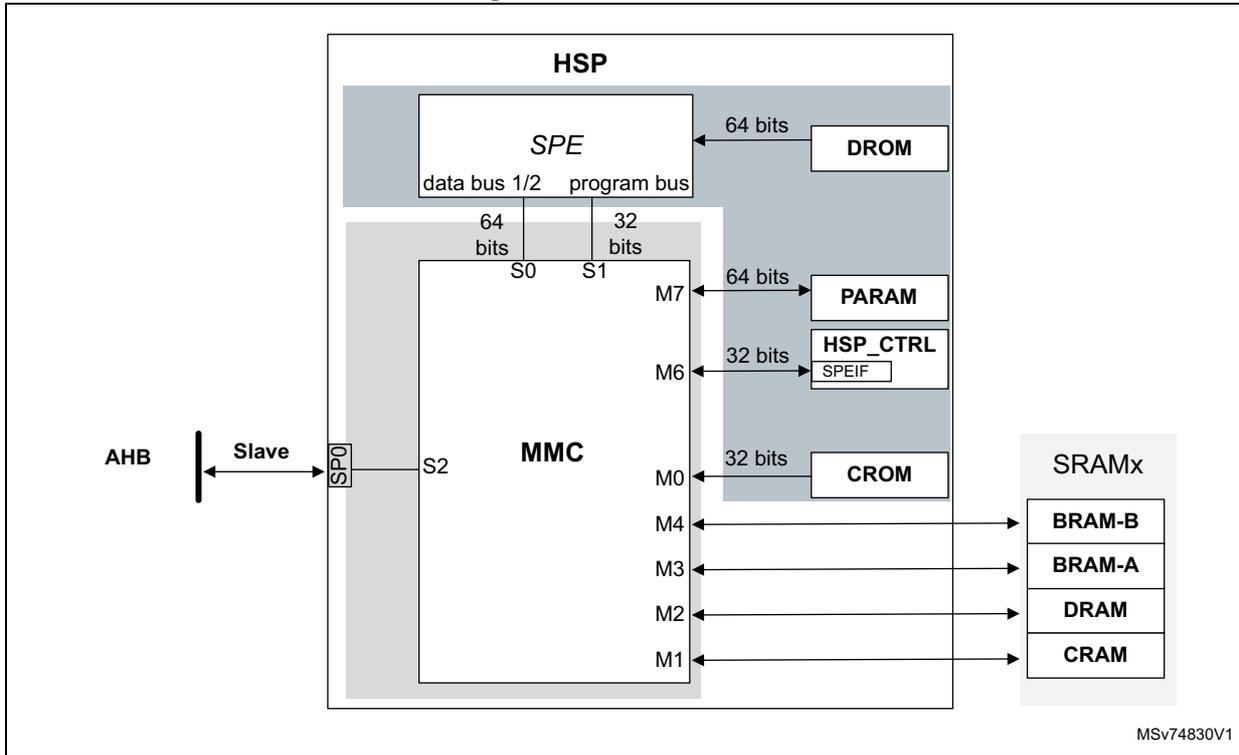

19.4.1 HSP block diagram

Figure 68. HSP block diagram

![HSP block diagram showing internal components like MMC, SPE, SPEIF, STREAM, TRGITF, SEG, EVTC, DCMD, MSGB, PARAM, DITC, HITC, TSC, TRGO, TCU, BKITF, CPUIF, and HSP_CTRL. It also shows external connections to AHB, SRAMx (BRAM-B, BRAM-A, DRAM, CRAM), and various pins like hsp_hclk_mem_ck, hsp_hclk_core_ck, hsp_break_in, hsp_trgi[x:0], hsp_break_out[3:0], hsp_bus_ckreq, hsp_it, hsp_err_it, hsp_fwevt_it, hsp_evt_it, hsp_txev, hsp_trgo[3:0], hsp_gpo[7:0], and HSP_SNP[5:0].](/RM0487-STM32U3/f6a7fb17ff6df278c25da65ef8f1cfa5_img.jpg)

The diagram illustrates the internal architecture of the HSP. At the top, the MMC block is connected to an SP1 interface on the left and to SRAMx (containing BRAM-B , BRAM-A , DRAM , and CRAM ) on the right. Below MMC are DROM and CROM . The SPE block (labeled Quad F32, Quad int8 ) is connected to SP0 on the left and to various output pins on the right. Below SPE is the SPEIF block, which contains STREAM , TRGITF , SEG , and EVTC . Below SPEIF is a grid of blocks: DCMD , MSGB , PARAM , DITC , HITC , TSC , TRGO , TCU , and BKITF . Below this grid is the CPUIF block, which is connected to SP0 on the left and to HSP_SNP[5:0] on the right. The entire lower section is enclosed in the HSP_CTRL block. External inputs include hsp_hclk_mem_ck , hsp_hclk_core_ck , hsp_break_in , and hsp_trgi[x:0] (1) . External outputs include hsp_break_out[3:0] , hsp_bus_ckreq , hsp_it , hsp_err_it , hsp_fwevt_it , hsp_evt_it (grouped by (2) ), hsp_txev , hsp_trgo[3:0] , and hsp_gpo[7:0] . The diagram is labeled MSV74828V2.

- 1. The number of trigger inputs depends on the product, see Section 19.3: HSP implementation .

- 2. These interrupt lines are not always connected, see Section 19.3: HSP implementation .

19.4.2 HSP pins and internal signals

Table 145. HSP external pins

| Pin name | Pin type | Comment |

|---|---|---|

| HSP_SNP[5:0] | Output | HSP outputs for debug and diagnostics |

Table 146. HSP internal signals

| Signal name | Signal type | Comment |

|---|---|---|

| hsp_hclk_mem_ck | Input | Bus clock input for memories |

| hsp_hclk_core_ck | Input | Bus clock input for HSP core |

Table 146. HSP internal signals (continued)

| Signal name | Signal type | Comment |

|---|---|---|

| hsp_bus_ckreq | Output | Bus interface clock request output |

| hsp_break_out[3:0] | Output | HSP break output signals |

| hsp_break_in | Input | HSP break input signal |

| hsp_it | Output | HSP global interrupt |

| hsp_err_it (1) | Output | HSP error interrupt |

| hsp_evt_it (1) | Output | HSP event interrupt |

| hsp_fwevt_it (1) | Output | HSP firmware event interrupt |

| hsp_txev | Output | HSP direct command complete event. |

| hsp_trgi[x:0] (2) | Input | HSP trigger input signals |

| hsp_trgo[3:0] | Output | HSP trigger output signals |

| hsp_gpo[7:0] | Output | HSP general-purpose output signals |

| hsp_dbgmcu_stp | Input | Halt request from DBGMCU (check DBG section to see if the feature is available) |

- 1. This interrupt line is not always connected to the interrupt controller, see Section 19.3: HSP implementation .

- 2. The number of trigger input signals depends on the product, see Section 19.3: HSP implementation .

The table below shows how HSP trigger inputs are connected in the product.

Table 147. HSP trigger input connections

| Input trigger name | Trigger source |

|---|---|

| hsp_trgi1 | gpdma1_chan_tc[0] |

| hsp_trgi1 | gpdma1_chan_tc[1] |

| hsp_trgi2 | gpdma1_chan_tc[2] |

| hsp_trgi3 | gpdma1_chan_tc[3] |

| hsp_trgi4 | EXTI0 |

| hsp_trgi5 | EXTI1 |

| hsp_trgi6 | TIM1 TRGO |

| hsp_trgi7 | TIM1 TRGO2 |

| hsp_trgi8 | TIM2 TRGO |

| hsp_trgi9 | TIM3 TRGO |

| hsp_trgi10 | TIM6_TRGO |

| hsp_trgi11 | TIM7_TRGO |

| hsp_trgi12 | TIM8_TRGO |

| hsp_trgi13 | TIM8_TRGO2 |

| hsp_trgi14 | TIM15_TRGO |

| Input trigger name | Trigger source |

|---|---|

| hsp_trgi15 | LPTIM1_CH1 |

| hsp_trgi16 | LPTIM1_CH2 |

| hsp_trgi17 | LPTIM2_CH1 |

| hsp_trgi18 | LPTIM2_CH2 |

| hsp_trgi19 | ADF_SAD_DET |

The table below shows how HSP trigger outputs are connected in the product.

Table 148. HSP trigger output connections for STM32U3B5/3C5| Output trigger name | Trigger destination |

|---|---|

| hsp_trgo0 | GPDMA1 dma_trig[34] |

| hsp_trgo1 | GPDMA1 dma_trig[35] |

| hsp_trgo2 | GPDMA1 dma_trig[36] |

| hsp_trgo3 | GPDMA1 dma_trig[37] |

| hsp_gpo0 | GPDMA1 dma_trig[38] |

| hsp_gpo1 | GPDMA1 dma_trig[39] |

| hsp_gpo2 | GPDMA1 dma_trig[40] |

| hsp_gpo3 | GPDMA1 dma_trig[41] |

| hsp_gpo[7:4] | - |

The table below shows how HSP break outputs are connected in the product.

Table 149. HSP break connections| Signal name | Trigger source |

|---|---|

| hsp_break_out0 | TIM1_brk1[3] TIM1_brk2[3] TIM8_brk1[3] TIM8_brk2[3] |

| hsp_break_out1 | TIM1_brk1[4] TIM1_brk2[4] TIM8_brk1[4] TIM8_brk2[4] |

| hsp_break_out2 | TIM15_brk1[3] TIM16_brk1[3] TIM17_brk1[3] |

Table 149. HSP break connections (continued)

| Signal name | Trigger source |

|---|---|

| hsp_break_out3 | TIM15_brk1[4] TIM16_brk1[4] TIM17_brk1[4] |

| hsp_break_in | - |

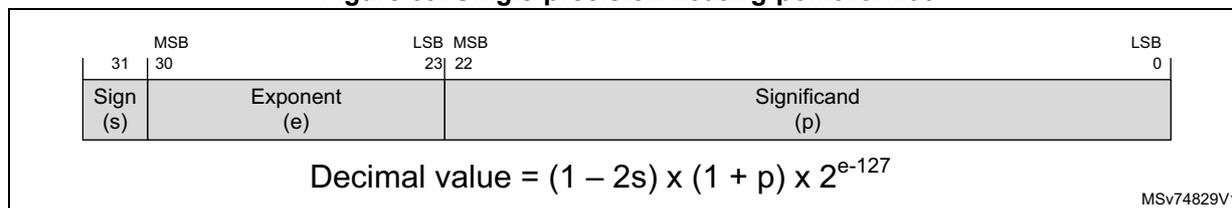

19.4.3 Floating-point format

The HSP is a powerful and flexible signal processing engine, able to perform operations on data located into its shared memory (BRAM).

The HSP can work by processing data blocks (vector) or sample per sample. The latter mode is particularly helpful for closed-loop control.

The HSP supports several kinds of data input formats: 8-, 16-, 32-bit integers, and 32-bit floating points. For simplification, this document refers to 32-bit floating points as “float32”. In the same way, signed 8-bit integers are named “int8”.

The SPE embedded into the HSP performs its computation in single-precision floating points (float32) or 8-bit integers (int8).

As defined by the IEEE-754 standard, the single-precision floating-point numbers are stored into the memory as shown in the figure below.

Figure 69. Single-precision floating-point format

| MSB | LSB | MSB | LSB | ||||

| 31 | 30 | 23 | 22 | 0 | |||

| Sign (s) | Exponent (e) | Significand (p) | |||||

Decimal value = \( (1 - 2s) \times (1 + p) \times 2^{e-127} \)

MSV74829V1

The single precision floating-point number includes:

- • A sign bit

- • A significand part of 23 bits

- • An exponent of 8 bits (-126 to + 127)

The first leading 1 bit of a normalized significand is “hidden”, or “implicit”, extending the significand to 24-bit precision.

Floating point greatly simplifies working with large numbers, up to about \( \pm 3.4e^{38} \) , and small numbers down to about \( \pm 1.17e^{-38} \) .

The HSP embeds the capability of converting integers into float32 and vice versa.

The HSP also supports integer 8-bit operations. They are dedicated to run convolutional neural networks. In this mode, the internal accumulator size is 32 bits to keep the best accuracy.

19.4.4 Memory management

A memory controller (MMC) manages the SRAM shared with the HSP. This SRAM can be used by the application like any other SRAM or dedicated to HSP activity when the HSP is activated (see Section 19.3: HSP implementation to check which SRAM is shared with the HSP on the product). This SRAM is split into five different sections when the application intends to use the HSP. The different sections are listed below:

- • The code RAM (CRAM) section, containing the HSP firmware program, plug-ins, and processing lists

- • The data RAM (DRAM) section, containing SPE sensitive data and processing list parameters

- • The buffer RAM A (BRAM-A), RAM B (BRAM-B), and RAM-AB sections, containing the working data, filter coefficients, and filter states

In addition, the HSP embeds a code ROM and a data ROM:

- • The code ROM (CROM) contains the generic signal processing functions library.

- • The data ROM (DROM) contains constants, such as FFT coefficients.

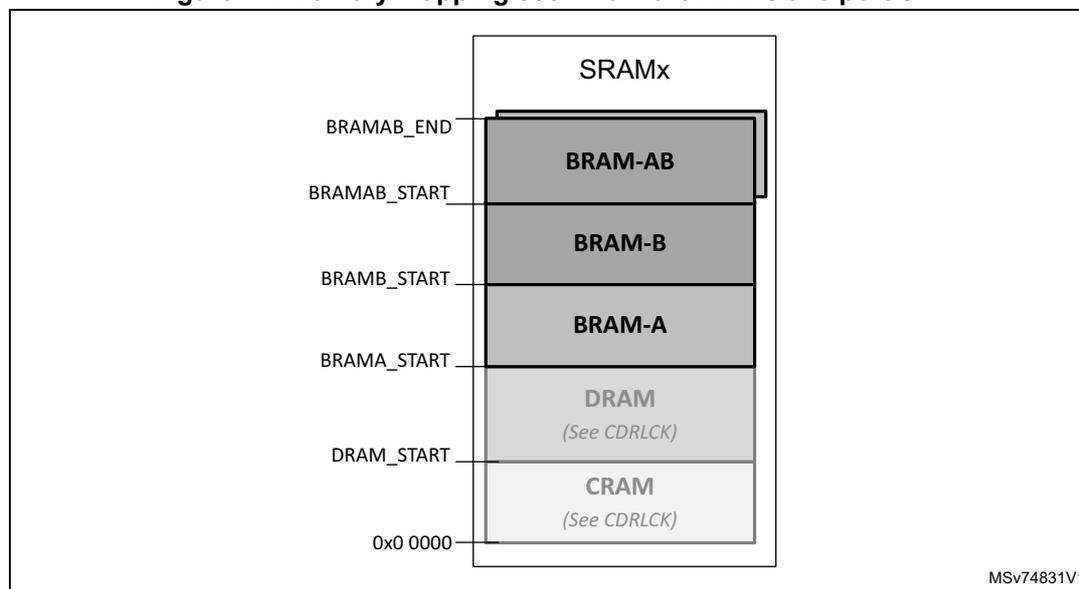

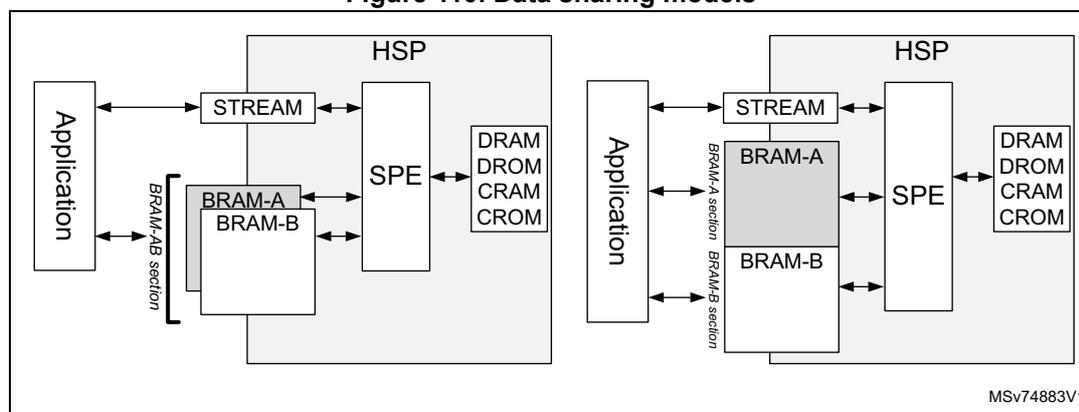

Figure 70. MMC overview

Memory protection and sharing

The access to the memory shared with the HSP is controlled by the MMC (memory controller) block. After a system reset, this SRAM is available for the application, and can be used as a general-purpose SRAM.

Note: This SRAM can be enabled or disabled via an RCC control bit. Make sure it is enabled before using it.

The BRAM-A, BRAM-B, and BRAM-AB sections are always shared with the application and are generally used for data exchanges and working buffers.

The application can restrict the access to CRAM and DRAM sections with the CDRLCK[1:0] bitfield in the HSP control register (HSP_CR) . CRAM and DRAM access filtering works as follows:

- • CDRLCK[1:0] = 0: read and write access through the AHB slave of CRAM and DRAM is allowed.

- • CDRLCK[1:0] = 1: write access to CRAM and DRAM is not allowed. Any read access is allowed. Only an HSP reset can restore write access to these memories.

- • CDRLCK[1:0] = 2 or 3: read and write access to CRAM and DRAM is not allowed. Only an HSP reset can restore read and write access to these memories.

An invalid application read access to a RAM protected by CDRLCK[1:0] returns 0. An invalid application write access to a RAM protected by CDRLCK[1:0] is ignored. In both cases, the ACCERRF and SAHBERR flags are set.

Accessing above BRAMAB_END (see Figure 71 ) also generates a bus error. The ACCERRF and SAHBERR flags are set as well.

See Section 19.4.12: HSP interrupt controller (HITC) .

The access restrictions programmed with CDRLCK[1:0] do not affect the SPE.

Note:

The application must first enable the hsp_hclk_core_ck (via the RCC) to change the value of CDRLCK[1:0]. Once CDRLCK[1:0] is updated, the hsp_hclk_core_ck can be disabled.

If the HSP was previously activated, it is recommended to reset the HSP before reusing the shared SRAM. The HSP reset is handled by the RCC.

Table 150 shows the address offset of each memory section. The BRAM is seen as two single ports, or like a dual port (BRAM-AB). Depending on the operations requested from the HSP, the application must use a dual-port BRAM or single-port BRAMs.

Table 150. Memory mapping seen from MMC AHB slave (1)

| Section start/stop acronym | Generic address offset (bytes) |

|---|---|

| BRAMAB_END | BRAMAB_START + (BRAM_SIZE * 512) - 1 |

| BRAMAB_START | BRAMB_START + BRAM_SIZE * 512 |

| BRAMB_START | BRAMA_START + BRAM_SIZE * 512 |

| BRAMA_START | DRAM_START+ DRAM_SIZE * 1024 |

| DRAM_START | CRAM_SIZE * 1024 |

| CRAM_START | 0 |

- 1. CRAM_SIZE, DRAM_SIZE, and BRAM_SIZE represent the size, in Kbytes, of CRAM, DRAM, and BRAM respectively. Refer to section Section 19.3: HSP implementation for memory size.

As shown in Figure 71 , the application sees the SRAM shared with the HSP as a contiguous memory block, with the capacity to restrict access to CRAM and DRAM blocks. When the HSP is enabled, the CPU can still access this SRAM, but the HSP also uses it.

For the HSP to run safely, it is recommended to write-protect CRAM and DRAM as soon as the application has loaded the main firmware code and its data into CRAM and DRAM.

The CPU can access:

- • BRAM-A, BRAM-B, and DRAM in 8, 16, or 32 bits (and in 64 bits, if the product supports it)

- • CRAM in 8, 16, or 32 bits.

Figure 71. Memory mapping seen from the AHB slave port SP1

Memory resource arbitration

When the HSP is running, the BRAM-AB, BRAM-A, or BRAM-B can be accessed by the SPE or by the application through the AHB slave interface.

To keep the best SPE performances, the MMC arbiter gives the highest priority to the SPE. However, some processing done by the SPE can take 100% of the BRAM resource, preventing the other requesters from accessing the BRAM. To avoid this, the MMC ensures that if the application requests the BRAM resource, the resource is granted in the worst case after 16, 8, or 4 cycles. BARB[1:0] in the HSP control register (HSP_CR) allows the selection of one of these values.

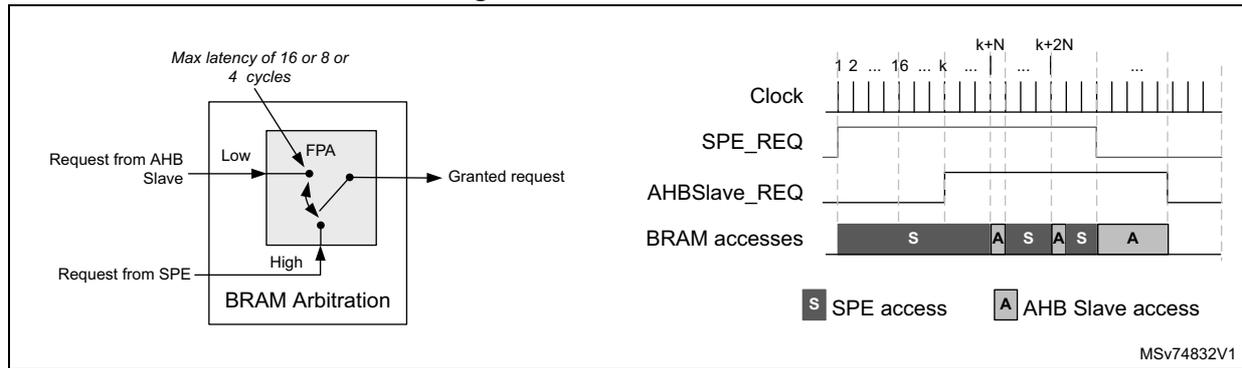

As shown in Figure 72 , a fixed-priority arbiter (FPA) ensures that the request coming from the AHB slave interface is granted at most every 16, 8, or 4 cycles. This mechanism prevents important degradation of SPE performances.

The right part of the figure shows an arbitration example.

- • The SPE occupies 100% of the BRAM bandwidth. After k clock periods, the AHB slave must access the BRAM-AB.

- • After N cycles (k + N), the AHB slave can perform its transaction. N can be either 4, 8, or 16.

When the SPE no longer uses the BRAM, the AHB slave transactions are served immediately using the full bandwidth.

Figure 72. BRAM arbitration

The diagram illustrates the BRAM arbitration mechanism. On the left, a block diagram shows the BRAM Arbitration unit with two inputs: 'Request from AHB Slave' (Low) and 'Request from SPE' (High). The unit contains an FPA (Fixed Priority Arbiter) and outputs a 'Granted request'. A note indicates a 'Max latency of 16 or 8 or 4 cycles'. On the right, a timing diagram shows the 'Clock', 'SPE_REQ', 'AHBSlave_REQ', and 'BRAM accesses' signals over time. The 'BRAM accesses' signal is divided into segments labeled 'S' (SPE access) and 'A' (AHB Slave access). The legend indicates 'S SPE access' and 'A AHB Slave access'. The reference 'MSv74832V1' is shown in the bottom right corner.

19.4.5 HSP boot

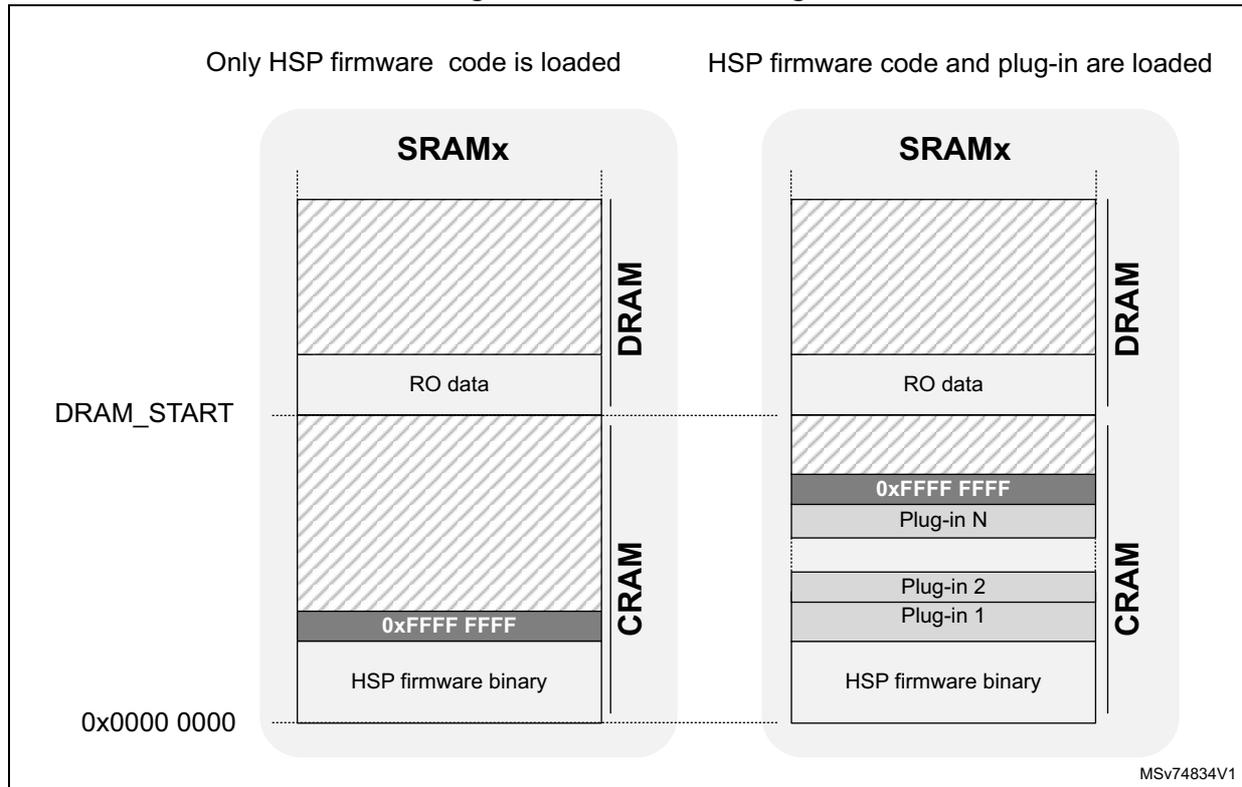

Before running the HSP, the application must copy the HSP firmware code into the code RAM (CRAM) and data RAM (DRAM). Additionally, some applications can also request to copy plug-ins. Plug-ins are extra binary codes provided by STMicroelectronics and used to correct the limitations of existing processing functions, or to add new processing functions not included in the original product.

The binary files must be copied as shown in Figure 73 :

- • If no plug-ins are loaded, the application must write a termination word (0xFFFF FFFF) right after the copied binary code.

- • If plug-ins must be added, they must be copied contiguous to the HSP firmware binary code, and the termination word must be added right after the last plug-in.

Figure 73. HSP code loading

The diagram illustrates two memory layout scenarios for HSP code loading within an SRAMx block, which is divided into DRAM and CRAM sections.

- Left Scenario: Only HSP firmware code is loaded

- The SRAMx block contains a DRAM section at the top with 'RO data'.

- Below the DRAM section is the CRAM section.

- The CRAM section contains a block labeled '0xFFFF FFFF' followed by 'HSP firmware binary' at the bottom.

- The address '0x0000 0000' is indicated at the bottom left of the CRAM section.

- A horizontal dashed line labeled 'DRAM_START' points to the boundary between the DRAM and CRAM sections.

- Right Scenario: HSP firmware code and plug-in are loaded

- The SRAMx block contains a DRAM section at the top with 'RO data'.

- Below the DRAM section is the CRAM section.

- The CRAM section contains several blocks: '0xFFFF FFFF', 'Plug-in N', 'Plug-in 2', 'Plug-in 1', and 'HSP firmware binary' at the bottom.

MSV74834V1

Refer to Section 19.3: HSP implementation to find which SRAM instance contains BRAM, CRAM, and DRAM on the product, as well as the relative address offset.

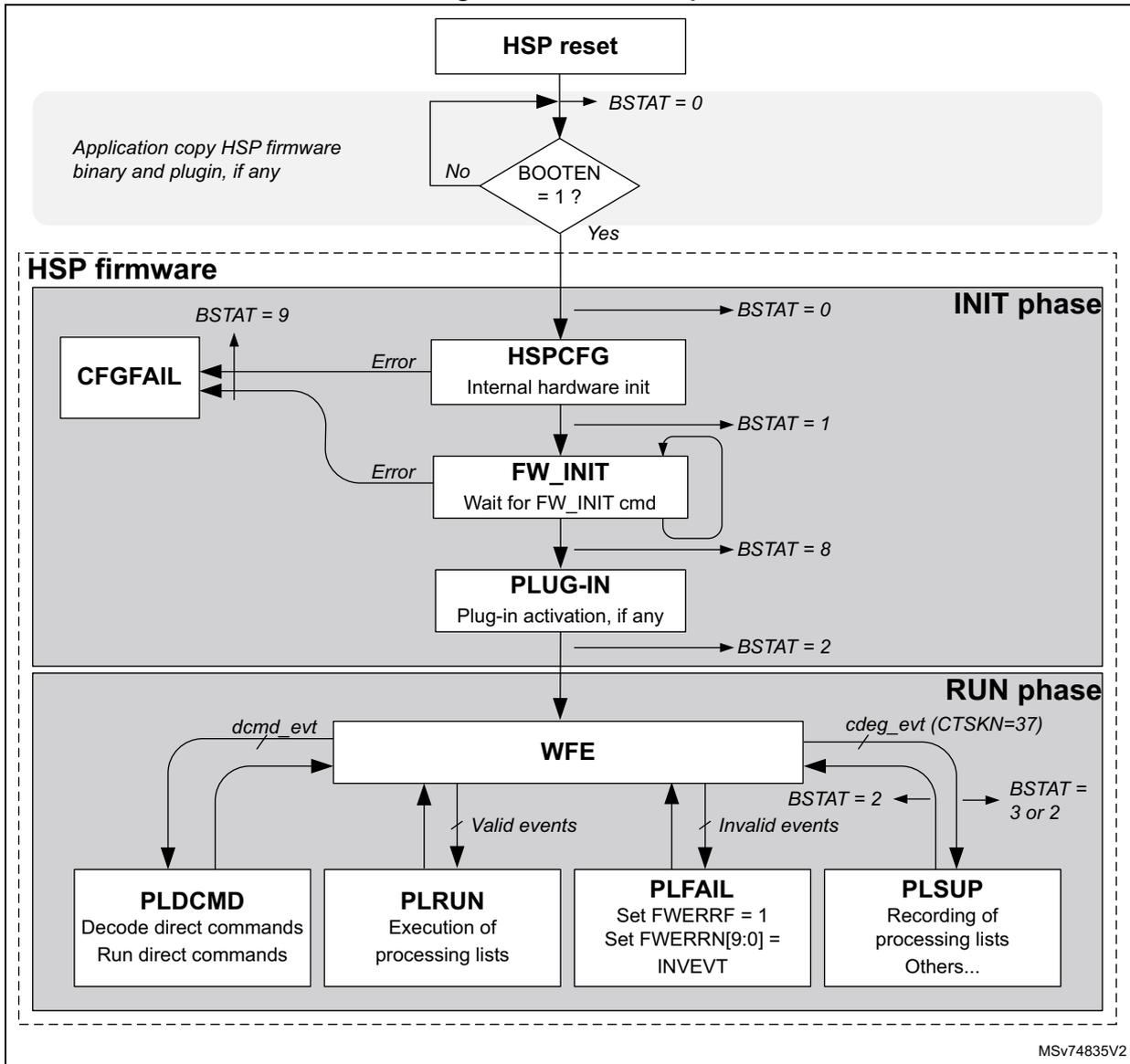

The application must execute the sequence below to run the HSP properly:

- 1. Reset the HSP using the reset bit in the RCC.

- 2. Copy the HSP firmware binary code and the RO data into the CRAM and DRAM sections respectively. Copy plug-in binaries, if any, into the CRAM.

- 3. Enable the HSP core clock via the RCC.

- 4. If needed, protect CRAM and DRAM sections against accidental corruption via CDRLCK[1:0].

- 5. Set the BOOTEN bit to run the HSP. The HSP executes the code starting at the CRAM base address of the CRAM, and enters the HSPCFG state.

- 6. In HSPCFG state, the HSP firmware performs the following operations:

- a) Initialize the internal HSP subblocks. TSKLUT is also initialized to only allow the activation of the supervisor (PLSUP) or Direct Command Accelerator functions (PLDCMD).

- b) Copy the firmware versions and SPE into HSP_FWVERR and HSP_SPEVERR.

- c) Set BSTAT[3:0] to 1, indicating it is waiting for the FW_INIT command.

- 7. The HSP firmware is now ready to accept the FW_INIT command.

- 8. When the FW_INIT command is complete, the HSP firmware activates the plugin codes, if any. This phase sets BSTAT[3:0] to 8.

- 9. The HSP enters the RUN phase and the WFE state, and sets BSTAT[3:0] to 2. As soon as an enabled event is activated, the HSP exits the WFE state and goes to:

- a) PLRUN if the selected event is valid (meaning it is associated with an existing processing list). The HSP firmware executes the processing list corresponding to the selected event, and goes back to WFE.

- b) PLSUP if the selected event corresponds to the supervisor. The HSP firmware executes the command sent by the application and goes back to WFE. Processing lists are created in this mode.

- c) PLDCMD if a direct command is programmed via the DCMD block.

- d) PLFAIL if the selected event is not valid.

- 6. In HSPCFG state, the HSP firmware performs the following operations:

- In PLDCMD mode, the HSP firmware executes the command sent by the application and goes back to WFE.

- In PLFAIL, the HSP firmware sets the FWERRF bit, sets the firmware error code in FWERRN[9:0], and goes back to WFE.

If an error occurs during this initialization process, the HSP firmware goes to the CFGFAIL state. In the CFGFAIL state, BSTAT[3:0] is set to 9. To set the HSP firmware back to the HSPCFG state, the HSP must be reset through the RCC.

When the HSP firmware initialization is completed, the application can enable the events, which are supposed to trigger the programmed processing list.

BOOTEN, CDRLOCK[1:0], and BSTAT[3:0] are located in the HSP control register (HSP_CR) .

Figure 74. HSP start-up

The flowchart illustrates the HSP start-up process. It begins with an HSP reset , which sets BSTAT = 0 . A note indicates that the application should copy HSP firmware binary and plugin, if any. A decision diamond asks if BOOTEN = 1 ? . If No , the process loops back to the start. If Yes , it enters the HSP firmware section, which is divided into INIT phase and RUN phase .

In the INIT phase :

- HSPCFG (Internal hardware init) is executed, setting BSTAT = 0 .

- FW_INIT (Wait for FW_INIT cmd) is executed, setting BSTAT = 1 . An Error from CFGFAIL (which sets BSTAT = 9 ) can occur here.

- PLUG-IN (Plug-in activation, if any) is executed, setting BSTAT = 8 .

- After PLUG-IN , BSTAT = 2 is set.

In the RUN phase , the WFE (Wait For Event) loop is entered. It handles dcmd_evt and cdeg_evt (CTSKN=37) . The loop can lead to PLDCMD (Decode direct commands, Run direct commands), PLRUN (Execution of processing lists), PLFAIL (Set FWERRF = 1, Set FWERRN[9:0] = INVEVT), or PLSUP (Recording of processing lists, Others...). Valid events lead to PLRUN , while Invalid events lead to PLFAIL . PLFAIL and PLSUP both set BSTAT = 2 , which then transitions to BSTAT = 3 or 2 .

MSV74835V2

The table below shows the different values BSTAT can take.

Table 151. BSTAT possible values

| Conditions | BSTAT[3:0] |

|---|---|

| Information | |

| Default value after reset | 0b0000 |

| The HSP firmware started | 0b0010 |

| The HSP firmware waits for firmware initialization command (FW_INIT) | 0b0001 |

| The HSP firmware is in RUN phase | 0b0011 |

| The HSP firmware is recording a processing list | 0b0100 |

| Errors | |

| The HSP firmware is in CFGFAIL state | 0b1100 |

19.4.6 Message box (MSGB)

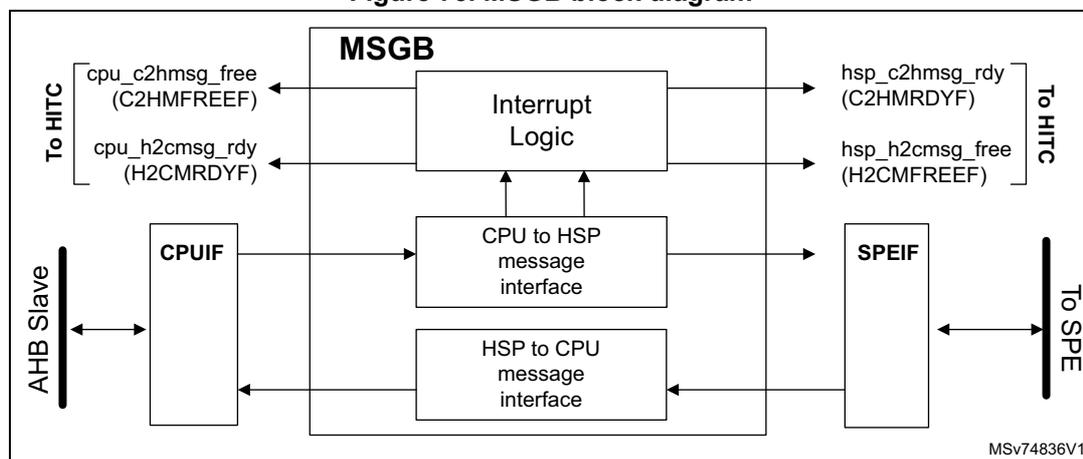

The message box (MSGB) offers various services dedicated to the HSP firmware configuration.

The MSGB block contains an HSP-to-CPU and a CPU-to-HSP message interface with:

- • Synchronization flags and interrupt capabilities

- • Two payload registers

The MSGB is generally used with the HSP parameter register x (HSP_PARAMRx) to provide the message payload. Messages are used to configure the HSP firmware part, especially to record the processing list.

Figure 75. MSGB block diagram

CPU to HSP message interface

Using polling mode

When the CPU wants to send a message to the HSP, it has to do the following:

- 1. Read C2HSEM in the HSP CPU-to-HSP semaphore register (HSP_C2HSEMR) .

- 2. Wait until C2HSEM = 0, indicating that the previous message has been read by the HSP and a new message can be transferred.

- 3. Write a new value in the HSP CPU-to-HSP message data register (HSP_C2HMSGDR) .

- 4. Set C2HSEM.

On its side, the HSP does the following:

- 1. Read the C2HSEM bit.

- 2. Wait until C2HSEM = 1, indicating that a new message is available.

- 3. Read the C2HDATA.

- 4. Clear C2HSEM to indicate that the message has been read.

Using interrupt mode

The MSGB can generate interrupts to the CPU when the CPU-to-HSP mailbox is ready to receive a new message (through the C2HMFREEF flag).

The CPU must first enable the interrupts by executing the sequence below:

- 1. Clear the C2HMFREEF flag by setting C2HMFREEC in the HSP events interrupt clear register (HSP_EVT_ICR) .

- 2. Allow the C2HMFREEF flag to generate an interrupt by setting C2HMFREEIE in the HSP events interrupt enable register (HSP_EVT_IER) .

When an event interrupt occurs, the interrupt subroutine (ISR) must do the following:

- 1. Read the C2HMFREEF flag in the HSP events interrupt status register (HSP_EVT_ISR) .

- 2. If C2HMFREEF is set:

- – The CPU can clear this flag by setting C2HMFREEC.

- – The CPU can write a new message.

- – When the CPU wants to notify the HSP that a new message is available, C2HSEM must be set.

The last two steps can be done outside the ISR.

HSP-to-CPU message interface

Using polling mode

When the HSP wants to send a message to the CPU, it does the following:

- 1. Read the H2CSEM flag.

- 2. Wait until H2CSEM = 0, indicating that the previous message has been read by the CPU and the content of HSP_SPE_H2CMSGDR can be overwritten.

- 3. Write the new value into C2HDATA.

- 4. Set H2CSEM.

On its side, the CPU does the following:

- 1. Read H2CSEM in the HSP HSP-to-CPU semaphore register (HSP_H2CSEMR) .

- 2. Wait until H2CSEM = 1, indicating that a new message is available.

- 3. Read the HSP HSP-to-CPU message data register (HSP_H2CMMSGDR) .

- 4. Clear H2CSEM in the HSP HSP-to-CPU semaphore register (HSP_H2CSEMR) to indicate that the message has been read.

Note: Handling the MSGB in polling mode also sets H2CMRDYF and C2HMFREEF. Prior to using these flags, the software must clear them.

If the CPU and the HSP set and clear C2HSEM at the same time respectively, C2HSEM is cleared.

If the CPU and the HSP set and clear C2HSEM at the same time respectively, C2HSEM is cleared.

Using interrupt mode

The MSGB can generate interrupts to the CPU when a new message is available for the CPU (through the H2CMRDYF flag).

The CPU must first enable the interrupts by executing the sequence below:

- 1. Clear the H2CMRDYF flag by setting the H2CMRDYC bit in the HSP events interrupt clear register (HSP_EVT_ICR) .

- 2. Allow the H2CMRDYF flag to generate an interrupt by setting the H2CMRDYIE bit in the HSP events interrupt enable register (HSP_EVT_IER) .

When an event interrupt occurs, the interrupt subroutine (ISR) must do the following:

- 1. Read the H2CMRDYF flag in the HSP events interrupt status register (HSP_EVT_ISR) .

- 2. If H2CMRDYF is set:

- – The CPU can clear this flag by setting H2CMRDYC.

- – The CPU can read the message.

- – When the CPU decides to free the message box, the H2CSEM bit must be cleared.

The last two steps can be done outside the ISR.

19.4.7 Direct command interface (DCMD)

The direct command interface (DCMD) is dedicated to the execution of direct commands, reducing the command overhead in an efficient way. It is used for HSP accelerator mode. This block is controlled by the HSP with a PLDCMD dedicated processing list (refer to Section 19.6.4: Executing direct commands (accelerator mode) ).

The DCMCD provides the following services:

- • Direct command ID register, for triggering events

- • Up to three data pointer interfaces

- • Status flags

The DCMD is generally used with the HSP parameter register x (HSP_PARAMRx) to provide the parameters corresponding to the command that the application wants to execute.

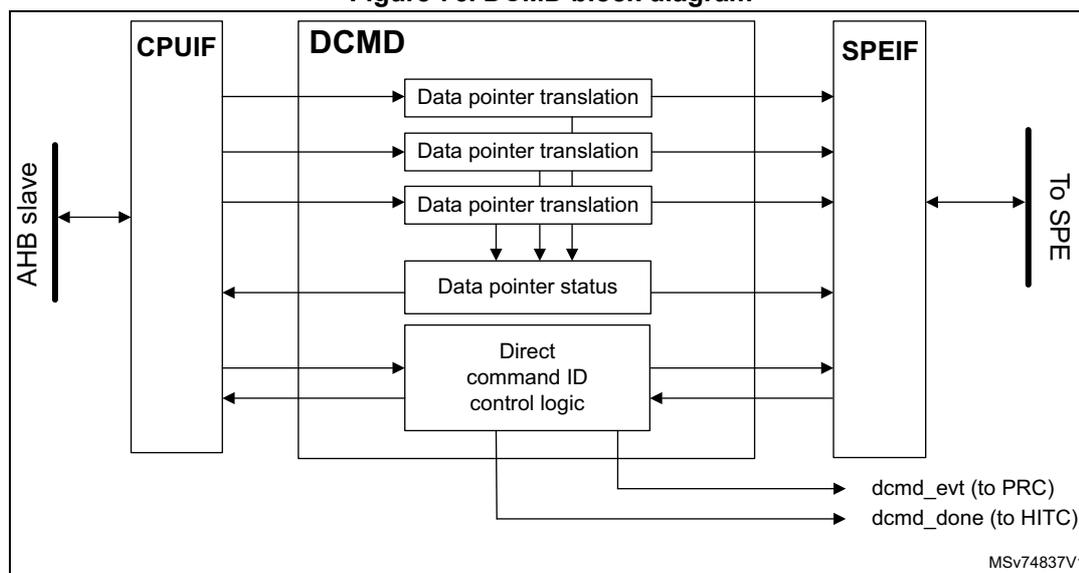

Figure 76. DCMD block diagram

Prior to running a direct command, the SPE must perform the following preliminary operations:

- 1. Decode the command

- 2. Adapt the data pointer values

- 3. Execute the command

To reduce latency in command decoding, the DCMD block allows the SPE to start command decoding while the CPU is still providing the parameters.

By default, the DCMD block is enabled. DCMDDIS in the HSP BUFF configuration register (HSP_BUFFCFGR) controls the enabling and disabling of this function. This bit is write-once after an HSP reset. If the application wants to ensure that the DCMD cannot be accidentally disabled, it must clear DCMDDIS. If the application wants to disable the DCMD, DCMDDIS must be set.

The CPU can transmit the command ID to be executed by writing the command ID in the HSP DCMD command ID register (HSP_DCMDIDR) .

A write access to this register triggers two actions:

- • It sets the DCBSY flag.

- • It asserts the DCMD event ( dcmd_evt ).

dcmd_evt triggers a processing list dedicated to the execution of direct commands. The number of this processing list is 38, and its priority is set to 26.

The DCBSY flag is cleared by the SPE when the direct command execution is completed.

The HSP DCMD address pointer register x (HSP_DCMDPTRx) allows the CPU to provide to the SPE the address pointers requested by the direct commands.

When the CPU writes an address pointer into one of the HSP_DCMDPTRx registers, the HSP hardware sets the corresponding PTRF[x] flag in the HSP DCMD pointer status register (HSP_DCMDPTRSR) .

When the SPE reads this pointer, the DCMD hardware sets the corresponding PTRFx bit to zero. The DCMD also provides a bit (RDOG) indicating if the SPE is performing a read operation of one of the three data pointers. This bit can be used in a debug phase to check if the SPE is waiting for a data pointer value.

Note: If the SPE reads a pointer register not yet updated by the CPU, the SPE remains frozen on the read operation until the CPU has updated the corresponding pointer register.

The DCMD also offers the possibility to generate an interrupt when the DCBSY flag is cleared, meaning that the command has been completed. The interrupt is enabled by setting DCDONEIE in the HSP events interrupt enable register (HSP_EVT_IER) .

Figure 77 shows a typical example of a command programming sequence, and the behavior of the various signals. During an initialization sequence, the CPU is assumed to clear DCMDDIS.

- 1. The CPU writes the command ID in the HSP DCMD command ID register (HSP_DCMDIDR) . The DCBSY and dcmd_evt are set (#1 in the figure).

- 2. The CPU writes data parameters in the HSP parameter register x (HSP_PARAMRx) (#2 in the figure).

- 3. The CPU starts to write the first two address pointers in the HSP DCMD address pointer register x (HSP_DCMDPTRx) . As soon as the EVTC allows it, task number 26 is activated (#3 in the figure).

- 4. The SPE first reads the command ID to check which command must be executed, and then starts to read the necessary address pointers. The first two address pointers are already available, but the SPE remains blocked for several cycles when reading the third pointer, because the CPU did not yet write it (#4 in the figure).

- 5. When the CPU writes the third pointer, the SPE gets it translated, and the command can be executed (#5 in the figure).

- 6. When the command execution is completed, the SPE clears the DCBSY flag. This action clears the dcmd_evt (#6 in the figure).

- 7. Finally, if DCDONEIE is set, an interrupt can be generated to inform that task execution has been completed. Then the CPU can clear the interrupt (and DCDONEF flag) by setting the clear bit (DCDONEC).

Figure 77. Direct command programming example

![Timing diagram for direct command programming example showing CPU operations, SPE operations, and various signal states (DCBSY, DCDONEF, PTRF[0-2], RDOG, dcmd_evt) over time. The diagram is divided into two main horizontal tracks: CPU operations and SPE operations. CPU operations include writing parameters, command ID, and pointers into HSP registers. SPE operations include reading command ID, pointers, and executing the command. Signal lines show the state of DCBSY, DCDONEF, PTRF[0], PTRF[1], PTRF[2], RDOG, and dcmd_evt. A task number 'Task 38' is shown. The diagram is labeled with numbered steps 1-6 and includes a reference code MSV74838V1.](/RM0487-STM32U3/7fb0a0df445fd4a349594ca52057c1d9_img.jpg)

The diagram illustrates the timing for direct command programming. It shows the sequence of events between the CPU and the SPE.

1. CPU writes parameters into HSP_PARAMRx and command ID into HSP_DCMDDDR.

2. CPU writes pointer into HSP_DCMDPTR0.

3. CPU writes pointer into HSP_DCMDPTR1.

4. SPE reads command ID, read pointer 0, and read pointer 1.

5. CPU writes pointer into HSP_DCMDPTR2.

6. SPE reads pointer 2, executes the command, and clears DCMDF.

Signals shown include DCBSY (active low), DCDONEF (active low), PTRF[0], PTRF[1], PTRF[2] (active high), RDOG (active low), and dcmd_evt (active high). The task number is set to Task 38. The CPU sets DCDONEC to 1 after the command is executed.

If the SPE reads a data pointer not written by the CPU, the SPE remains blocked in the reading operation. The SPE can no longer serve interrupts, nor enter debug mode. The SPE can exit this freeze state through one of the following actions:

- • The application provides the expected data pointer.

- • DCMDDIS is set (if possible). The SPE unfreezes, but executes a command with an invalid pointer, which could be unsafe.

- • The HSP is reset.

The HSP also provides a signal event for the CPU named hsp_txev , indicating that the current direct command execution has been completed. Every time a direct command execution is completed, a single-cycle pulse is generated. DCMDEVEN in the HSP control register (HSP_CR) allows this function activation (see also Section 19.4.12: HSP interrupt controller (HITC) ).

19.4.8 STREAM interface

The STREAM interface can be used if the application wants to trigger an HSP processing list when data are sent to or read from the STREAM interface. It allows the application to set up source- or sink-driven processing.

For example, a DAC associated with a DMA device can take its data from the STREAM interface. As soon as the STREAM interface is read by the DMA device, the SPE is advised and the associated processing list, recorded by the application during an initialization phase, is executed immediately. Typically, this processing list prepares the next sample for the DAC.

Conversely, an ADC associated with a DMA device can provide its data to the STREAM interface. As soon as the STREAM interface is written by the DMA device, the SPE is advised and the associated processing list, recorded by the application during an initialization phase, is executed immediately. Typically, this processing list processes the incoming sample and frees the STREAM interface for the next data.

Figure 78. STREAM block diagram

![Figure 78. STREAM block diagram. The diagram shows the internal architecture of the STREAM interface. On the left, a 'To SoC' connection leads to a 'REGIF' block. The 'REGIF' block connects to four 32-bit buffers: 'BUFF[0]', 'BUFF[1]', 'BUFF[2]', and 'BUFF[3]'. Each buffer has 'C2H' (CPU-to-HSP) and 'H2C' (HSP-to-CPU) input paths. Each buffer also outputs 'buff_err[x]' and 'buff_rxe_txne[x]' signals. All four buffers connect to a central 'BUF CMB' (Buffer Combiner) block. The 'BUF CMB' block outputs 'buff_att[x]' and 'buff_evt[x]' signals to a 'PRC' (Processor) block. Above the 'PRC' block is an 'SPEIF' (SPE Interface) block containing an 'I2F' (Interconnect to SPE) component, which connects 'To SPE'.](/RM0487-STM32U3/390ff4252a12484793ac68e3fe31e302_img.jpg)

The STREAM interface provides up to four data buffers of 32 bits. Each of them can be configured either in the CPU-to-HSP direction (C2H) or the HSP-to-CPU direction (H2C). Buffers configured in CPU-to-HSP direction are called C2HBUFF in this document, and buffers configured in HSP-to-CPU direction are called H2CBUFF.

These buffers can be accessed by the application through the HSP BUFFx data register x (HSP_BUFFxDR) .

The data provided by the CPU (C2H direction) can be converted to float32 automatically if the I2FEN bit in the HSP BUFF configuration register (HSP_BUFFCFGR) is set.

The conversion from integer to float32 only works for the following input formats:

- • Signed integers up to 32 bits. The sign extension must always be performed up to 32 bits. The accuracy of a signed 32-bit integer is reduced to 24 bits due to the float32 format.

- • Unsigned integers up to 31 bits. Bit 31 must be cleared. The accuracy is limited to 24 bits due to the float32 format.

The STREAM buffers configured in the C2H direction assert the buff_att signal when a data is written into a STREAM buffer by the application. The buff_att signal remains active as long as the SPE does not read the corresponding STREAM buffer.

The STREAM buffers configured in the H2C direction assert the buff_att signal when they are empty. The buff_att event signal remains active as long as the SPE does not write data into the corresponding STREAM buffer.

The BUFcmb block adds additional flexibility by combining the buff_att[x] signals to generate the buffer events ( buff_evt[x] ). The BUFcmb allows the generation of the buff_evt[x] event, when the corresponding buff_att[x] signal is activated or when both buff_att[x] and buff_att[x+1] signals are activated. The BUFcmb is configured in the HSP BUFF configuration register (HSP_BUFFCFGR) .

Figure 79. BUFcmb details

![Diagram of BUFcmb details showing four input signals (buff_att[0] to buff_att[3]) entering a chain of logic blocks labeled COMB0, COMB1, and COMB2. Each block contains an AND gate and an OR gate with a multiplexer. The outputs are buff_evt[0] to buff_evt[3]. A small text 'MSV74843V1' is in the bottom right corner.](/RM0487-STM32U3/bd49af920c6819521415b36d5e14491e_img.jpg)

The table below lists some of the possible configurations:

Table 152. BUFFcmb programming examples

| COMB2 | COMB1 | COMB0 | Outputs | |

|---|---|---|---|---|

| 0 | 0 | 0 | → | buff_evt[x] generated when buff_att[x] is activated |

| 1 | 0 | 1 | → | buff_evt[0]

generated when

buff_att[0]

&

buff_att[1]

are activated buff_evt[1] generated when buff_att[1] is activated buff_evt[2] generated when buff_att[2] & buff_att[3] are activated buff_evt[3] generated when buff_att[3] is activated |

Table 152. BUFFCMB programming examples (continued)

| COMB2 | COMB1 | COMB0 | Outputs | |

|---|---|---|---|---|

| 0 | 1 | 1 | → | buff_evt[0]

generated when

buff_att[0]

&

buff_att[1]

&

buff_att[2]

are activated buff_evt[1] generated when buff_att[1] & buff_att[2] are activated buff_evt[2] generated when buff_att[2] is activated buff_evt[3] generated when buff_att[3] is activated |

| 1 | 1 | 1 | → | buff_evt[0]

generated when

buff_att[0]

&

buff_att[1]

&...&

buff_att[3]

are activated buff_evt[1] generated when buff_att[1] & buff_att[2] & buff_att[3] are activated buff_evt[2] generated when buff_att[2] & buff_att[3] are activated buff_evt[3] generated when buff_att[3] is activated |

The CPU can configure the buffer directions and the BUF CMB with the HSP BUFF configuration register (HSP_BUFFCFGR) .

The STREAM interface is activated by setting STREAMEN in the HSP BUFF configuration register (HSP_BUFFCFGR) . When STREAMEN is set, it is no longer possible to change the buffer direction, nor to modify the BUFFCMB configuration.

Note: Clearing STREAMEN resets the STREAM block, and all pending buffer events are cleared. Any write access operation to the STREAM buffers is ignored, and read access returns the last data.

The STREAM interface generates an error signal for each buffer and the error signals buff_err[3:0] are asserted:

- • If new data are written into a buffer configured in the C2H direction while the previous data have not been read by the SPE, an overrun error is detected. The new data are written, and the previous ones are lost.

- • If a buffer configured in the H2C direction is read by the CPU while the SPE did not have time to write the new data, an underrun error is detected. In this case, the CPU reads the previous data.

These error signals activate the B[3:0]ERRF flags in the HSP error interrupt status register (HSP_ERR_ISR) . An interrupt to the CPU can be generated if the corresponding interrupt enable flag is set.

The STREAM interface also generates buffer status signals ( buff_rxe_txne[3:0] ). These signals set the corresponding B[3:0]EVT in the HSP events interrupt status register (HSP_EVT_ISR) in each of the following conditions:

- • If the corresponding C2H buffer is empty

- • If the corresponding H2C buffer is not empty

An interrupt to the CPU can be generated if the corresponding interrupt enable flag is set.

buff_att[x] signals are also provided to the TRGO to generate a trigger pulse on hsp_trgo[x] if the SPE reads a C2H buffer, or writes into the H2C buffer.

Figure 80 shows how buff_evt[x] , BxEVT, buff_evt[y] , ByEVT, and TRGO (when enabled) behave in the case of C2H and H2C buffers, when BUF CMB is configured with its default

values (bypass). When STREAMEN is cleared, the complete STREAM interface is reset and the buff_evt[x] and buff_rxe_txne[x] signals return to 0.

Case where BUFF[x] is set in the C2H direction:

- 1. As soon as STREAMEN is set, B[x]EVTF goes high, indicating that BUFF[x] is empty.

- 2. When the CPU writes into a BUFF[x], the B[x]EVTF flag goes back to 0 and buff_evt[x] is activated, requesting SPE processing (#1 in the figure).

- 3. When the SPE reads BUFF[x], the B[x]EVTF flag is set again, buff_evt[x] is released, and a TRGO[x] pulse is generated if selected for the STREAM buffer (#2 in the figure).

Case where BUFF[x] is set in the H2C direction:

- 1. As soon as STREAMEN is set, the buff_evt[y] signal goes high, requesting SPE activation.

- 2. When the SPE writes BUFF[x], the B[x]EVTF flag is set, buff_evt[x] is released, and a TRGO[y] pulse is generated if selected for the STREAM buffer (#3 in the figure).

- 3. When the CPU reads BUFF[x], the B[x]EVTF flag goes back to 0 and buff_evt[x] is activated, requesting SPE processing (#4 in the figure).

When the SPE writes into a BUFF[x], the buff_evt[y] flag goes back to 0, and a TRGO[x] pulse is generated if it is selected for the STREAM buffer (#1 in the figure).

Figure 80. Buffer usage generation example

![Timing diagram showing buffer usage generation for C2H and H2C directions. The diagram is divided into two sections: C2H direction (top) and H2C direction (bottom). Each section shows the timing of STREAMEN, CPU/SPE write/read operations, B[x]EVTF flag, buff_evt[x] signal, and TRGO[x] pulse. The C2H section shows CPU writes to C2HBUFF[x] and SPE reads from C2HBUFF[x]. The H2C section shows SPE writes to H2CBUFF[x] and CPU reads from H2CBUFF[x]. Arrows indicate the flow of data and control signals between the CPU, SPE, and the buffer.](/RM0487-STM32U3/8d1a2921e31db968bce73a250f004177_img.jpg)

The figure is a timing diagram illustrating buffer usage generation for two directions: C2H (CPU to SPE) and H2C (SPE to CPU). The diagram is divided into two horizontal sections.

C2H direction (top section):

- STREAMEN: A signal that goes high to enable the buffer.

- CPU writes C2HBUFF[x]: A signal indicating a write operation from the CPU to the buffer.

- B[x]EVTF: A flag that goes high when the buffer is empty and low when it contains data.

- SPE reads C2HBUFF[x]: A signal indicating a read operation from the buffer by the SPE.

- buff_evt[x]: A signal that goes high when the buffer is empty and low when it contains data.

- TRGO[x]: A pulse generated when the buffer is empty and selected for the STREAM buffer.

- Events:

- ①: CPU writes to C2HBUFF[x] while B[x]EVTF is high. B[x]EVTF goes low, and buff_evt[x] goes high.

- ②: SPE reads from C2HBUFF[x]. B[x]EVTF goes high, buff_evt[x] goes low, and a TRGO[x] pulse is generated.

H2C direction (bottom section):

- CPU reads H2CBUFF[x]: A signal indicating a read operation from the buffer by the CPU.

- B[x]EVTF: A flag that goes high when the buffer is empty and low when it contains data.

- SPE writes H2CBUFF[x]: A signal indicating a write operation to the buffer by the SPE.

- buff_evt[x]: A signal that goes high when the buffer is empty and low when it contains data.

- TRGO[x]: A pulse generated when the buffer is empty and selected for the STREAM buffer.

- Events:

- ③: SPE writes to H2CBUFF[x] while B[x]EVTF is high. B[x]EVTF goes low, buff_evt[x] goes high, and a TRGO[x] pulse is generated.

- ④: CPU reads from H2CBUFF[x]. B[x]EVTF goes high, buff_evt[x] goes low, and a TRGO[x] pulse is generated.

MSV74844V1

19.4.9 Trigger input interface (TRGITF)

The HSP embeds up to 10 trigger input blocks, named TRGINx. Each TRGINx receives a trigger input signal from TRGMX. For each TRGINx, the application can select any trigger input signal, and program the activation of an event on a rising or falling edge of the selected signal.

TRGINx blocks can be configured through the HSP TRGIN configuration register (HSP_TRGINCFGR) , HSP TRGIN input selection register 0 (HSP_TRGINSEL0) , HSP TRGIN input selection register 1 (HSP_TRGINSEL1) , and HSP TRGIN input selection register 2 (HSP_TRGINSEL2) .

Each trigger interface can be independently enabled through the HSP BUFF configuration register (HSP_BUFFCFGR) .

The TRGIN blocks perform the following functions:

- • Selecting the rising or falling edge sensitivity to generate an event.

- • Storing a transition, even if this transition is faster than the EVTC internal clock.

- • Performing the clock domain crossing.

- • Storing the event until it is taken into account by the priority encoder.

The pending events are automatically cleared by the TCTL block when the SPE starts the corresponding processing.

Figure 81. TRGITF block diagram

![TRGITF block diagram showing internal components like TRGMX, TRGIN[0] to TRGIN[9], WKTRG, CPUIF, and external connections to TCTL, PRC, HCC, and HITC blocks.](/RM0487-STM32U3/8fe5bbc0de8103afa00eaa54501e957a_img.jpg)

The diagram illustrates the internal architecture of the TRGITF block. On the left, multiple trigger inputs (hsp_trgi[0], hsp_trgi[N-2], hsp_trgi[N-1]) are connected to the TRGMX block, which routes them to various TRGIN interfaces (TRGIN[0] through TRGIN[9]) via TRG0SEL and TRG9SEL multiplexers. Each TRGIN interface contains a D flip-flop (clr, D, Q), a Re-sync block, and an Overrun Detector. These are controlled by TRGIxEN, TRGxPOL, and hsp_xclk_core_ck signals. The TRGIN[0] and TRGIN[9] blocks also output events (trgin_evt[0], trgin_evt[9]) to the PRC block and clear commands (clear command 0, clear command 9) to the TCTL block. A central WKTRG block receives the hsp_xclk_core_ck signal and outputs trgin_wkup to the HCC block. Below the TRGIN blocks, an Overrun controller receives trgin_err[0] through trgin_err[9] and od_clear signals, outputting trgin_err[9:0], trgin_ovr, and TRGIOVRC signals to the HITC block. At the bottom, a CPUIF block is connected to the Slave AHB (CPU side) and receives signals from the Overrun controller. The diagram is labeled MSv74845V1 in the bottom right corner.

1. The number of trigger inputs depends on the product (see Section 19.3: HSP implementation ).

The TRGMX block allows the application to route any trigger input to any TRGIN interface.

The WKTRG block allows the detection of an enabled pending event even if the TRGITF is not clocked. This signal is used for autonomous functions or to wake up the product if needed.

Note: When TRGIxEN are cleared, the corresponding TRGIN logic is maintained to reset, avoiding the storage of a spurious transition, for example when the polarity is changed. The overrun detector and pending event are also reset when TRGIxEN is cleared.

It is recommended to change the polarity bit and the signal source selection when the corresponding TRGIxEN bit is cleared.

TRGIN overrun detection

Each TRGIN block has an overrun detector checking if a new trigger event occurred while the previous one was not yet taken into account by the SPE. The overrun detector sets the trgin_err[x] signal when an overrun is detected. The overrun controller generates the trgin_ovr signal, setting the TRGIOVRF flag. If the TRGIOVRIE bit is set, an interrupt is generated to the CPU. The application can check which TRGIN block causes the overrun by reading TRGIERR[9:0] in the HSP error information register (HSP_ERRINFR) . When the

application clears the TRGIOVRF flag through the TRGIOVRC bit, all overrun detectors are reset.

See Section 19.4.12: HSP interrupt controller (HITC) .

Note: The overrun function does not work when hsp_hclk_core_ck is not present.

Figure 82 shows a case of overrun detection, using two TRGIN inputs. In the example, trgin_evt[2] activates the task number 2, and trgin_evt[5] activates the task number 5.

hsp_trgi[2] and hsp_trgi[5] receive an event at the same time (#1 in the figure). trgin_evt[2] and trgin_evt[5] are activated. In the example, a higher priority is given to trgin_evt[2] , which is executed as soon as the SPE is available. tsk_active[5:0] indicates that task number 2 is in execution.

While the trgin_evt[5] event is pending, a second trigger is detected in the hsp_trgi[5] input, causing an overrun error (#2 in the figure). The flag TRGIOVRF is set, and trgin_err[9:0] is set to 0x20 (bit 5 set). An interrupt can be activated for the application.

The SPE completed task number 2, and the HSP can serve the pending request from trgin_evt[5] . Task 5 is activated (#3 in the figure).

The hsp_trgi[2] receives two new triggers, the first one activates trgin_evt[2] and the second one activates the overrun error (#4 in the figure). The TRGIOVRF was already set, and the trgin_err[9:0] value is updated to 0x24 (bits 5 and 2 set).

The application reads trgin_err[9:0] and clears TRGIOVRF (#5 in the figure). trgin_err[x] , TRGIOVRF, and trgin_err[9:0] are reset. When the SPE completes task 5, the pending event is served and task 2 is executed again.

Note: Two events have been lost due to overrun.

Figure 82. TRGIN overrun detection

![Timing diagram for TRGIN overrun detection showing signals hsp_trgi[2], trgin_err[2], trgin_evt[2], hsp_trgi[5], trgin_err[5], trgin_evt[5], TRGIOVRF, trgin_err[9:0], CPU clears TRGIOVRF, TCTL clear command trgin[2], TCTL clear command trgin[5], and tsk_active[5:0] over time. The diagram includes numbered callouts (1) through (5) indicating key events in the overrun detection sequence.](/RM0487-STM32U3/c98d2bf3b799e86072e6d1acb610990c_img.jpg)

The timing diagram illustrates the TRGIN overrun detection process. The signals shown are:

- hsp_trgi[2] : Hardware signal processor trigger input 2. It has two rising edges marked (1) and (4).

- trgin_err[2] : Error signal for trigger 2. It goes high at point (4) when a second rising edge of hsp_trgi[2] occurs while the first event is still active.

- trgin_evt[2] : Event signal for trigger 2. It goes high at point (1) on the first rising edge of hsp_trgi[2] and goes low when hsp_trgi[2] falls.

- hsp_trgi[5] : Hardware signal processor trigger input 5. It has a rising edge marked (2).

- trgin_err[5] : Error signal for trigger 5. It goes high at point (2) on the rising edge of hsp_trgi[5] and at point (3) when hsp_trgi[5] falls while the event is still active.

- trgin_evt[5] : Event signal for trigger 5. It goes high at point (2) on the rising edge of hsp_trgi[5] and goes low when hsp_trgi[5] falls.

- TRGIOVRF : Overrun flag. It goes high at point (3) when trgin_err[5] goes high and is cleared by the CPU at point (5).

- trgin_err[9:0] : Error register. It contains the value 0 initially, then 0x20 (indicating an overrun on line 5) at point (3), then 0x24 (indicating overruns on lines 2 and 5) at point (4), and returns to 0 after being cleared at point (5).

- CPU clears TRGIOVRF : A signal indicating the CPU has cleared the overrun flag at point (5).

- TCTL clear command trgin[2] : A pulse generated by the CPU to clear the error flag for line 2 at point (5).

- TCTL clear command trgin[5] : A pulse generated by the CPU to clear the error flag for line 5 at point (5).

- tsk_active[5:0] : Task active register. It shows the number of active tasks: '?' initially, '2' after the first event, '5' after the overrun event, and '2' after the CPU clears the flags.

Numbered callouts in the diagram:

- (1) First rising edge of hsp_trgi[2], setting trgin_evt[2] high.

- (2) Rising edge of hsp_trgi[5], setting trgin_evt[5] high.

- (3) Falling edge of hsp_trgi[5] while trgin_evt[5] is high, setting trgin_err[5] high and TRGIOVRF high.

- (4) Second rising edge of hsp_trgi[2] while trgin_evt[2] is still high (due to a previous event), setting trgin_err[2] high.

- (5) CPU clears TRGIOVRF and sends TCTL clear commands for lines 2 and 5, resetting the error register and task active count.

MSv74846V1

19.4.10 Software events generator (SEG)

The CPU can trigger events:

- • By using the event lines shared with STREAM and TRGITF, through the CPU shared event generator (CSEG) block.

- • By using the dedicated event line input 27 through the CPU-dedicated event generator (CDEG) block.

Similarly, the SPE can trigger events either by using the HSEG, or by using the dedicated event line input 0 through the HDEG block.

Figure 83. SEG block diagram

![Figure 83. SEG block diagram. The diagram shows the internal structure of the SEG (Software event generator) block. It is divided into two main sections: CSEG (CPU shared event generator) and HSEG (HSP shared event generator). CSEG is connected to CPUIF and HSEG is connected to SPEIF. Both sections include CLR Logic, write detect, and PRC (Processing Request Control) blocks. CSEG generates cseg_evt[22:1] and cdeg_evt signals. HSEG generates hseg_evt[22:1] and hdeg_evt signals. Both sections also generate CT SKN[5:0] and HT SKN[5:0] signals. The CSEG section also includes a CDEGRDYF (cdeg_rdy) signal to HITC. The HSEG section includes an HDEGOVRF (hdeg_ovr) signal to HITC. The TCTL (Task Controller) block receives signals from both sections, including clear event source selected by TCTL, and generates tsk_active[5:0] output. The diagram is labeled MSV74847V1.](/RM0487-STM32U3/787bf73236d4caf860576e9c8f7f7483_img.jpg)

Generating events with CSEG

The CSEG allows the CPU to reuse events not allocated to a peripheral interface, such as STREAM or TRGITF.

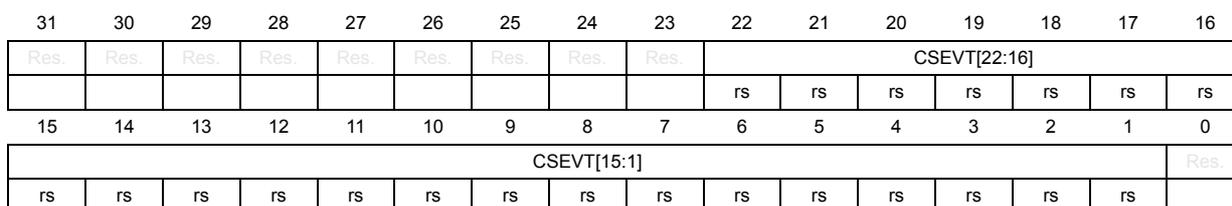

For event inputs 1 to 22, the CPU can select the CSEG as the event generator. This is done through the EVTxSRC field for each event input x.

Then, with a simple write access request to the HSP CPU shared event generator register (HSP_CSEGR) , the CPU can trigger one or several events.

The priority encoder of the HSP handles all the activated events according to their priority. The software can check which event is processed by reading back HSP_CSEGR.

Prior to generating an event, the application must enable the CSEG interface by setting CSEGEN in the HSP BUFF configuration register (HSP_BUFFCFG) . When CSEGEN is cleared, the CSEG block is reset and all pending events ( cseg_evt[x] ) are cleared.

Note: There is no protection against overrun situations; the application must ensure that CSEVTx is cleared before setting it again.

For example, if the application wants to activate the event N, it must follow this sequence:

- 1. Wait for CSEVT[N] = 0. If CSEVT[N] = 1, it means that the HSP did not yet consider the previous request.

- 2. When CSEVT[N] = 0, set it.

The CSEG block can also be used by the application for debugging purposes, by forcing the execution of a task connected to STREAM or TRGITF. It also allows the CPU to generate events with a high priority level if necessary.

Generating events with CDEG

The CDEG allows the application to trigger any of the 38 tasks through the cdeg_evt event.

The CDEG allows one event to be posted at a time: the CPU needs to wait until the previous event has been taken into account before activating a new event.

Note: The cdeg_evt event is routed to the input number 27 of the priority encoder (PE) having the lowest priority.

Prior to generating events, the application must enable the CDEG interface by setting CDEGEN in the HSP BUFF configuration register (HSP_BUFFCFGR) . When CDEGEN is set to 0, the DSEG block is reset, and cdeg_evt is cleared.

To generate a dedicated event, the CPU must do the following:

- 1. Wait until the CDEGBSY bit is cleared.

- 2. Write the task number to execute (0 to 38) in CTSKN[5:0].

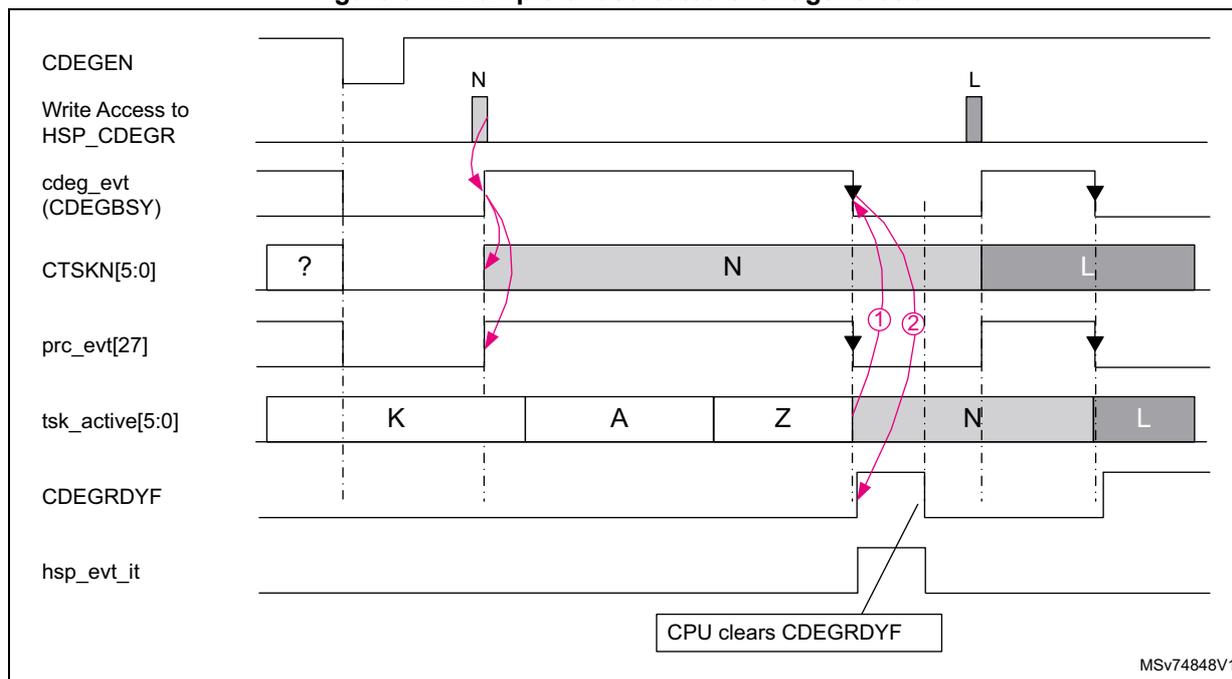

When the CPU writes in the HSP CPU dedicated event generation register (HSP_CDEGR) , the prc_evt[27] event is asserted, and CDEGBSY is set. The CDEG block can also generate an interrupt when the current CTSKN[5:0] is taken into account by the HSP.

Figure 84 shows a basic example. The CPU writes in HSP_CDEGR and CTSKN[5:0] is set to N. The write operation in this register sets the cdeg_evt signal and CDEGBSY flag. cdeg_evt is routed to prc_evt[27] . When the task controller is able to serve the task associated with prc_evt[27] , the cdeg_evt signal and CDEGBSY flag are cleared by the TCTL (#1 in the figure), and the CDEGRDYF flag is set, asserting an HSP interrupt if the corresponding interrupt enable control bit is set (#2 in the figure). The CDEG block is ready to accept a new request.

Note: CDEGRDYF is set when a transition from 1 to 0 is detected on the cdeg_evt signal.

CTSKN[5:0] and CDEGBSY are located in the HSP CPU dedicated event generation register (HSP_CDEGR) , and CDEGRDYF is located in the HSP events interrupt status register (HSP_EVT_ISR) .

Figure 84. Example of dedicated event generation

The timing diagram illustrates the interaction between several signals during dedicated event generation. The signals shown are:

- CDEGEN : A control signal that pulses low.

- Write Access to HSP_CDEGR : Shows two write pulses, labeled 'N' and 'L'.

- cdeg_evt (CDEGBSY) : A status signal that goes high following the first write access and stays high until the event is processed.

- CTSKN[5:0] : A multi-bit signal showing a transition from an unknown state '?' to state 'N', and later to state 'L'.

- prc_evt[27] : A processing event pulse triggered by the write access.

- tsk_active[5:0] : Shows task execution states labeled 'K', 'A', 'Z', 'N', and 'L'.

- CDEGRDYF : A ready flag that goes high after task 'Z' completes.

- hsp_evt_it : An interrupt signal that goes high when CDEGRDYF is set.

Generating events with HSEG

The HSP shared event generator (HSEG) allows the SPE to reuse events not allocated to a peripheral interface, such as STREAM or TRGITF.

The HSEG block is very similar to the CSEG, but it is dedicated to SPE usage.

Generating events with HDEG

The HSP dedicated event generator (HDEG) allows the SPE firmware to trigger any of the 38 tasks using the event 0.

The HDEG block is similar to the CDEG, but it is dedicated to SPE usage.

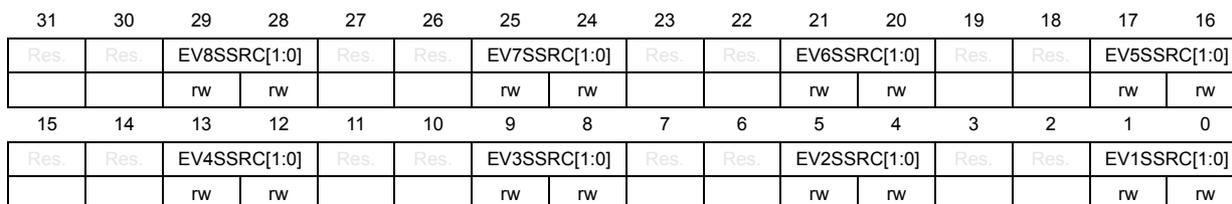

19.4.11 Event controller (EVTC)

The event controller (EVTC) collects the events generated by the various HSP internal peripherals and reconditions them. The event with the highest priority activates the corresponding task, which executes the recorded processing list.

- • Handle the STREAM interface.

- • Handle the trigger inputs.

- • Collect application events.

- • Select the event having the highest priority.

- • Ask the SPE to execute the processing list associated with the selected event.

The execution of a processing list can be triggered by several sources:

- • The CPU: up to 38 tasks can be triggered by software.

- • The SPE: up to 38 tasks can be triggered by firmware.

- • Trigger input lines (

hsp_trgi[X:0]

):

- – Triggers from various device peripherals, such as timers, ADCs, DACs, and ADF/MDF

- – Up to 20 trigger inputs are available.

- • The STREAM interface:

- – Allows any peripheral to trigger a processing list.

- – Has up to four buffers are available.

The EVTC is configured mainly by the application CPU through the AHB slave interface.

Figure 85. EVTC block diagram

![Figure 85. EVTC block diagram. The diagram shows the internal architecture of the EVTC (Event Vector Table Controller). At the top, a 'Slave AHB (CPU side)' interface connects to a 'CPUIF' block. Below the CPUIF is the main 'EVTC' block, which contains three sub-blocks: 'PRC (Processing Request Control)', 'Priority Encoder (PE)', and 'Task Controller (TCTL)'. The PRC block receives inputs from various sources: 'from SEG' (hdeg_evt, hseg_evt[22:1], cdeg_evt, cseg_evt[22:1]), 'from STREAM' (buff_evt[3:0]), 'from TRGITF' (trgin_evt[9:0]), 'from DCMD' (dcmd_evt), 'from TCU' (end_of_tsk[3:0]), and 'from SEG' (HSTKN[5:0], CSTKN[5:0]). The PRC outputs 'prc_evt' signals to the PE: prc_evt[0], prc_evt[22:1], prc_evt[25:23], prc_evt[26], and prc_evt[27]. The PE has priority levels: 'higher 0', '1 ... 22', '23...25', '26', and 'lower 27'. The PE outputs 'pe_evt[5:0]' to the TCTL. The TCTL outputs 'evtc_wkup', 'tsk_active[5:0]', and 'tsk_add[19:0]'. At the bottom, the EVTC connects to a 'SPEIF' block, which in turn connects to 'To SPE'. A reference code 'MSV74849V2' is in the bottom right corner.](/RM0487-STM32U3/c628365ae46dbea7b75ed3135d113dba_img.jpg)

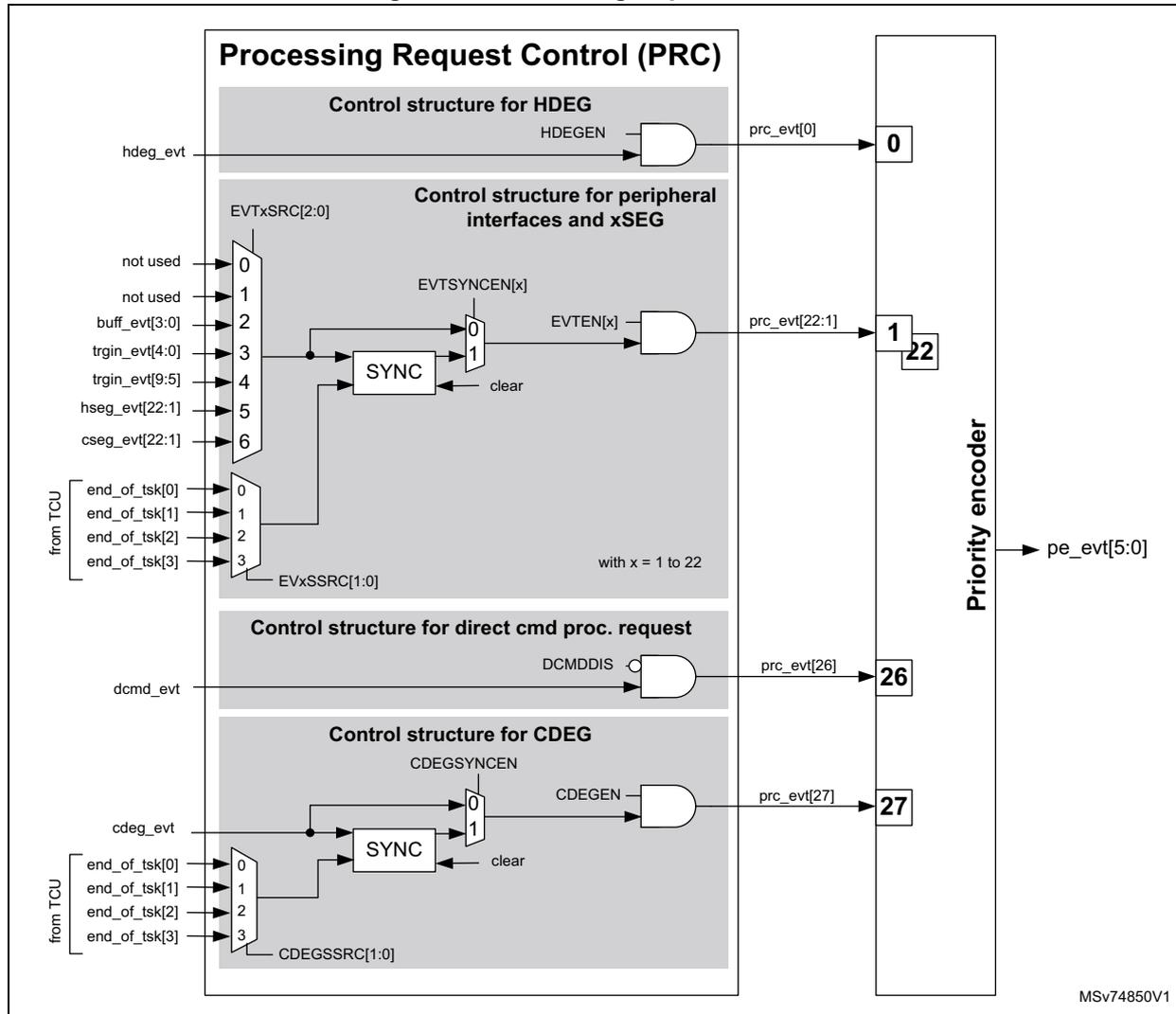

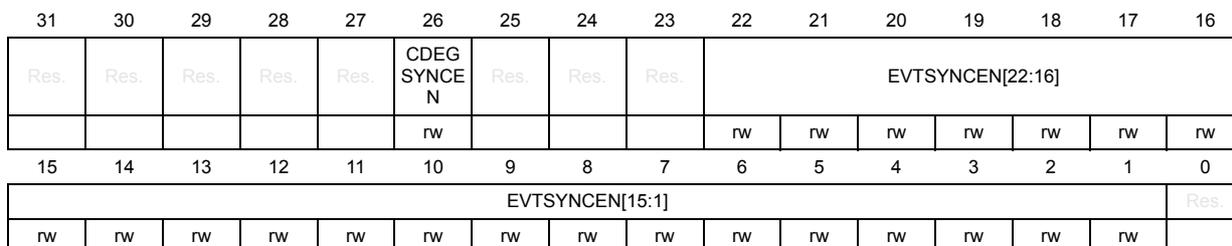

Processing request control (PRC)

For each input of the priority encoder, the processing request control (PRC) is in charge:

- • Of selecting the request source that triggers a task through the EVTSRC[2:0]R registers.

- • Of enabling and disabling the synchronization option with the HSP event synchronization enable register (HSP_ESYNCENR) .

- • Of enabling and disabling the generation of the processing request with the HSP event enable register (HSP_EVTENR) .

Figure 86 shows the processing request control details for each type of inputs. Most of the inputs have a processing request source selector, a synchronizer, and a processing request enable.

Figure 86. Processing request control

The diagram illustrates the internal structure of the Processing Request Control (PRC) block and its output to a priority encoder. The PRC block is divided into four main control structures:

- Control structure for HDEG:

Takes

hdeg_evtas input. It passes through an AND gate labeledHDEGENto produceprc_evt[0], which is connected to priority level 0. - Control structure for peripheral interfaces and xSEG:

This section is complex. It features a multiplexer

EVTxSRC[2:0]that selects between various input events:not used(0, 1),buff_evt[3:0](2),trgin_evt[4:0](3),trgin_evt[9:5](4),hseg_evt[22:1](5), andcseg_evt[22:1](6). This selection is followed by aSYNCblock with aclearinput. The output of the synchronizer goes through a multiplexerEVTSYNCEN[x](inputs 0 and 1) to an AND gate labeledEVTEN[x]. The output of this gate isprc_evt[22:1], which is connected to priority level 1. A note indicates "with x = 1 to 22". - Control structure for direct cmd proc. request:

Takes

dcmd_evtas input. It passes through an AND gate labeledDCMDDISto produceprc_evt[26], which is connected to priority level 26. - Control structure for CDEG:

Takes

cdeg_evtas input. It passes through aSYNCblock with aclearinput. The output goes through a multiplexerCDEGSSRC[1:0](inputs 0 and 1) to an AND gate labeledCDEGEN. The output of this gate isprc_evt[27], which is connected to priority level 27. This section also includes a multiplexerend_of_tsk[3:0](inputs 0, 1, 2, 3) labeled "from TCU".

The outputs

prc_evt[0]

,

prc_evt[22:1]

,

prc_evt[26]

, and

prc_evt[27]

are fed into a vertical

Priority encoder

. The priority encoder outputs

pe_evt[5:0]

. The diagram also shows priority levels 0, 1, 22, 26, and 27 indicated next to the encoder inputs.

The synchronization mechanism allows the application to delay the activation of an event until the completion of a specific task.

Figure 87 shows an example of the synchronization usage. Tasks 1 and 2 are running at a regular time interval, and their execution must not be delayed. From time to time, the application needs to run an additional task (18 in the figure), for example, to update dynamic parameters. The application does not want to delay the execution of tasks 1 and 2 due to task 18 execution, so it decides to run task 18 right after task 2, because the time interval between the end of task 2 and the start of task 1 allows it. The application sets

TSKCMP0[5:0]

to 2 to resynchronize the pending

cdeg_evt

event with the end of the execution of task 2.

Figure 87. Example of synchronization mechanism

![Timing diagram showing synchronization mechanism between prc_evt signals and task execution. The diagram includes signals prc_evt[1], prc_evt[2], cdeg_evt, tsk_cmp[0], prc_evt[27], tsk_active, and Tasks. Arrows show synchronization from cdeg_evt to tsk_cmp[0] and from tsk_cmp[0] to prc_evt[27].](/RM0487-STM32U3/29780909b15550c6bf8d7591a831b608_img.jpg)

The timing diagram illustrates the synchronization mechanism. The signals shown are:

- prc_evt[1] (from BUFF0): A periodic pulse signal.

- prc_evt[2] (from TRGIN4): A periodic pulse signal.

- cdeg_evt : A signal that goes high when a task is active.

- tsk_cmp[0] : A signal that goes low when a task is active. It is synchronized with cdeg_evt.

- prc_evt[27] : A signal that goes high when a task is active. It is synchronized with tsk_cmp[0].

- tsk_active : A sequence of task IDs (Idle, 1, 2, Idle, 1, 2, 18, Idle, 1, 2, Idle, 1, 2).

- Tasks : A sequence of task IDs (1, 2, 1, 2, 18, 1, 2, 1, 2).

The table below shows which event can be connected for each priority encoder input, and thus which processing task number is activated (tsk_active[5:0]).

Table 153. Trigger sources versus priority and task number (1)

| EVTxSRC[2:0] position (2) | Priority or prc_evt[x] | , | Processing task activated | ||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | |||

| HDEG | 0 | → | 0 to 37 | ||||||

| - | - | BUFF[0] | TRGIN[3] | TRGIN[8] | HSEG[1] | CSEG[1] | 1 | → | 1 |

| - | - | BUFF[1] | TRGIN[4] | TRGIN[9] | HSEG[2] | CSEG[2] | 2 | → | 2 |

| - | - | BUFF[2] | TRGIN[0] | TRGIN[5] | HSEG[3] | CSEG[3] | 3 | → | 3 |

| - | - | BUFF[3] | TRGIN[1] | TRGIN[6] | HSEG[4] | CSEG[4] | 4 | → | 4 |

| - | - | BUFF[0] | TRGIN[2] | TRGIN[7] | HSEG[5] | CSEG[5] | 5 | → | 5 |

| - | - | BUFF[1] | TRGIN[3] | TRGIN[8] | HSEG[6] | CSEG[6] | 6 | → | 6 |

| - | - | BUFF[2] | TRGIN[4] | TRGIN[9] | HSEG[7] | CSEG[7] | 7 | → | 7 |

| - | - | BUFF[3] | TRGIN[0] | TRGIN[5] | HSEG[8] | CSEG[8] | 8 | → | 8 |

| - | - | BUFF[0] | TRGIN[1] | TRGIN[6] | HSEG[9] | CSEG[9] | 9 | → | 9 |

| - | - | BUFF[1] | TRGIN[2] | TRGIN[7] | HSEG[10] | CSEG[10] | 10 | → | 10 |

| - | - | BUFF[2] | TRGIN[3] | TRGIN[8] | HSEG[11] | CSEG[11] | 11 | → | 11 |

| - | - | BUFF[3] | TRGIN[4] | TRGIN[9] | HSEG[12] | CSEG[12] | 12 | → | 12 |

| - | - | BUFF[0] | TRGIN[0] | TRGIN[5] | HSEG[13] | CSEG[13] | 13 | → | 13 |

| - | - | BUFF[1] | TRGIN[1] | TRGIN[6] | HSEG[14] | CSEG[14] | 14 | → | 14 |

| - | - | BUFF[2] | TRGIN[2] | TRGIN[7] | HSEG[15] | CSEG[15] | 15 | → | 15 |

| - | - | BUFF[3] | TRGIN[3] | TRGIN[8] | HSEG[16] | CSEG[16] | 16 | → | 16 |

| - | - | BUFF[0] | TRGIN[4] | TRGIN[9] | HSEG[17] | CSEG[17] | 17 | → | 17 |

| EVTxSRC[2:0] position (2) | Priority or prc_evt[x] | → | Processing task activated | ||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | |||

| - | - | BUFF[1] | TRGIN[0] | TRGIN[5] | HSEG[18] | CSEG[18] | 18 | → | 18 |

| - | - | BUFF[2] | TRGIN[1] | TRGIN[6] | HSEG[19] | CSEG[19] | 19 | → | 19 |

| - | - | BUFF[3] | TRGIN[2] | TRGIN[7] | HSEG[20] | CSEG[20] | 20 | → | 20 |

| - | - | BUFF[0] | TRGIN[3] | TRGIN[8] | HSEG[21] | CSEG[21] | 21 | → | 21 |

| - | - | BUFF[1] | TRGIN[4] | TRGIN[9] | HSEG[22] | CSEG[22] | 22 | → | 22 |

| not used | 23 | → | 23 | ||||||

| 24 | → | 24 | |||||||

| 25 | → | 25 | |||||||

| DCMD (Direct Command) | 26 | → | 38 | ||||||

| CDEG | 27 | → | 0 to 37 | ||||||

- 1. BUFF[y] represents the events

buff_evt[y]

,

BUFF[y] represents the events buff_evt[y] ,

TRGIN[y] represents the events trgin_evt[y] ,

HSEG[y] represents the events hseg_evt[y] ,

CSEG[y] represents the events cseg_evt[y] , - 2. With x = 1 to 22.

The following table shows a different view: for each event source, the possible priority levels are shown.

Table 154. Trigger sources versus priority and task number (1)(2)| Event sources | Possible priority levels | - | Event sources | Possible priority levels |

|---|---|---|---|---|

| BUFF[0] | 1, 5, 9, 13, 17, 21 | → | BUFF[1] | 2, 6, 10, 14, 18, 22 |

| BUFF[2] | 3, 7, 11, 15, 19 | → | BUFF[3] | 4, 8, 12, 16, 20 |

| TRGIN[0] | 3, 8, 13, 18 | → | TRGIN[1] | 4, 9, 14, 19 |

| TRGIN[2] | 5, 10, 15, 20 | → | TRGIN[3] | 1, 6, 11, 16, 21 |

| TRGIN[4] | 2, 7, 12, 17, 22 | → | TRGIN[5] | 3, 8, 13, 18 |

| TRGIN[6] | 4, 9, 14, 19 | → | TRGIN[7] | 5, 10, 15, 20 |

| TRGIN[8] | 1, 6, 11, 16, 21 | → | TRGIN[9] | 2, 7, 12, 17, 22 |

| HDEG | 0 | → | HSEG | 1 to 22 |

| CDEG | 27 | → | CSEG | 1 to 22 |

| DCMD | 26 | → | - | - |

- 1. The HDEG priority is fixed at 0 but can run any task number. The CDEG behaves similarly but has a priority fixed at 27.

- 2. BUFF[y] represents the events

buff_evt[y]

TRGIN[y] represents the events trgin_evt[y]

HSEG[y] represents the events hseg_evt[y]

CSEG[y] represents the events cseg_evt[y]

Priority encoder (PE) and task controller (TCTL)

The priority encoder defines which event has the highest priority when several events are requesting the execution of processing lists.

The event priority is fixed. The event having the highest priority is the event connected to input 0 of the PE (dedicated to the SPE). The event having the lowest priority is the event connected to input 27.

When no event is pending, pe_evt[5:0] , and task_active[5:0] are equal to 0x3F, and the SPE remains in “wait for event” (WFE).

The TCTL generates the task number to be executed ( task_nb[5:0] ), according to the output provided by the priority encoder ( pe_evt[5:0] signal):

- • If the output of the priority encoder corresponds to the event number 0 ( pe_evt[5:0] = 0 ), the TCTL activates the task number given by HTSKN[5:0]. This field is updated by the SPE when the SPE requests the execution of a specific processing list through the HDEG interface.

- • If the output of the priority encoder corresponds to the event number 27 ( pe_evt[5:0] = 27 ), then the TCTL activates the task number given by CTSKN[5:0]. This field is provided by the CPU when it requested the execution of a specific processing list through the CDEG interface. Note that a specific protection mechanism prevents having a task number higher than 39. If CTSKN is higher than 37, the task number is forced to 39.

- • If the output of the priority encoder corresponds to the event number 26 ( pe_evt[5:0] = 26 ), the TCTL activates task number 38. This task is reserved for direct command handling.

- • Finally, if the output of the priority encoder provides other values, the TCTL consider it as a task number.

When task_nb[5:0] becomes different from 0x3F, the TCSM block latches the value of the task to be executed ( task_active[5:0] ). The active task value is used as an index to read a look-up table (TSKLUT), which contains the address of the task (or processing list) to be executed by the SPE. The TSKLUT is updated by the SPE. Finally, the TCTL asserts the evtc_wkup signal to inform the SPE that a task needs to be executed.

The TCTL is also responsible for clearing TRGINx, SEG, and DCMD events when they are taken into account. When the SPE starts the execution of the selected task, spe_wfe goes to zero, and several cycles later the SPE generates a pulse (on spe_jump_evt ), indicating that the processing list address has been taken into account, and can be updated for the next task to process. In addition, the TCTL generates an error if the SPE does not activate spe_jump_evt in the expected time window.

Figure 88. Task controller details

![Figure 88. Task controller details. This block diagram shows the internal architecture of the Task Controller (TCTL). On the left, four input blocks (DCMD, CDEG, HDEG, PE) provide signals to a 'TSK Prot' block. DCMD provides NUM_TSK_MAX-1, CDEG provides CTSKN[5:0], HDEG provides HTSKN[5:0], and PE provides pe_evt[5:0]. The 'TSK Prot' block outputs dcmd_tsknb, cdeg_tsknb, and hdeg_tsknb. A logic block below 'TSK Prot' takes pe_evt[5:0] and the task numbers from the 'TSK Prot' block to determine tsk_nb[5:0] based on priority rules. The 'TSK Prot' block also outputs tsk_nb[5:0] to the 'Task Control State Machine (TCSM)'. The TCSM outputs tsk_idx[5:0] to a 'TSK LUT' block. The 'TSK LUT' block outputs tsk_add[19:0] (to SPE). The TCSM also outputs tsk_active[5:0] (to SNOOP, TSC, TCU...) and connects to 'Clear events logic'. The 'Clear events logic' block outputs signals to TRGIN[x], SEG, evtC_wkup (to SPE), spe_jump_evt (from SPE), and spe_wfe (from SPE). The SPEITF block is also shown.](/RM0487-STM32U3/f84c613a6e5597d1507e0a715e7e9092_img.jpg)

The task having the highest number (task number 39) is dedicated to the SPE firmware and indicates that an unexpected task number has been activated (PLFAIL). The SPE firmware activates the FWERRF flag with the error code described in Table 155: Firmware error number . An interrupt is generated to the application if enabled.

When no event is pending, the first event to become active is selected. If several events are waiting for a task completion by the SPE, the event having the highest priority is selected when the SPE acknowledges completion of the previous task.

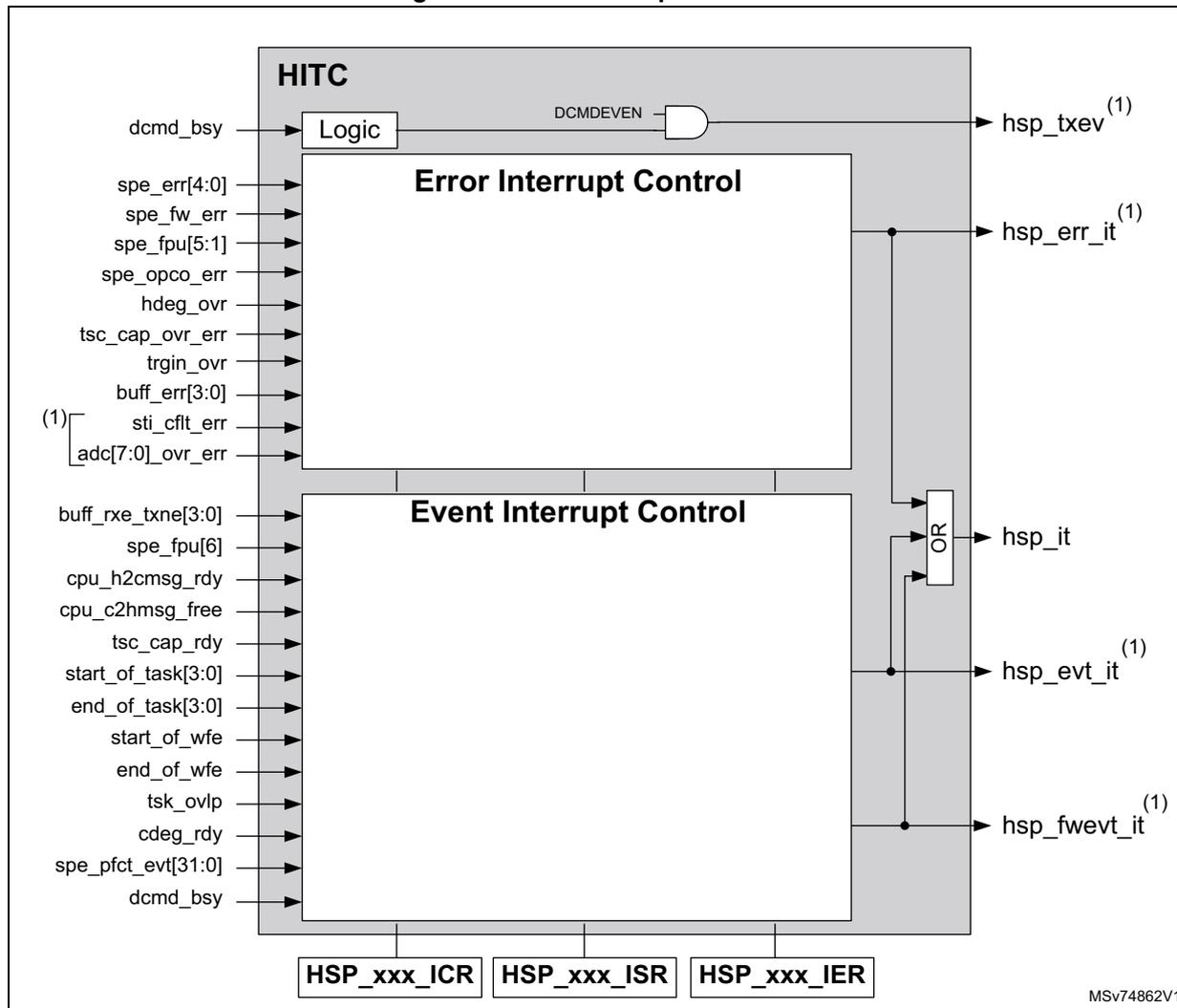

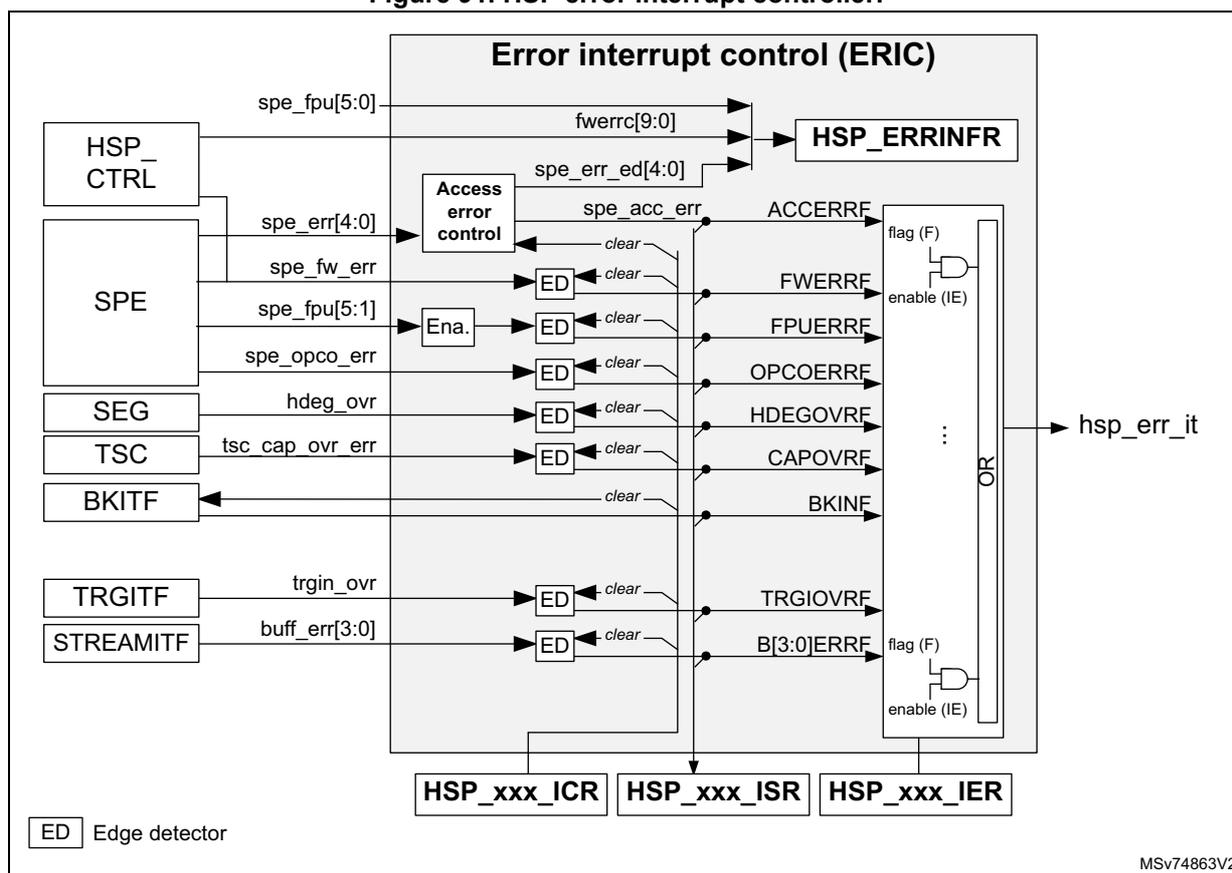

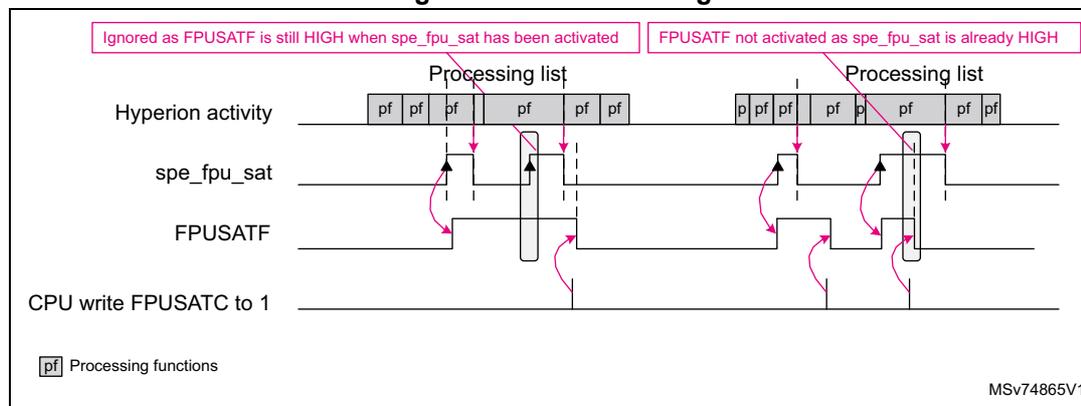

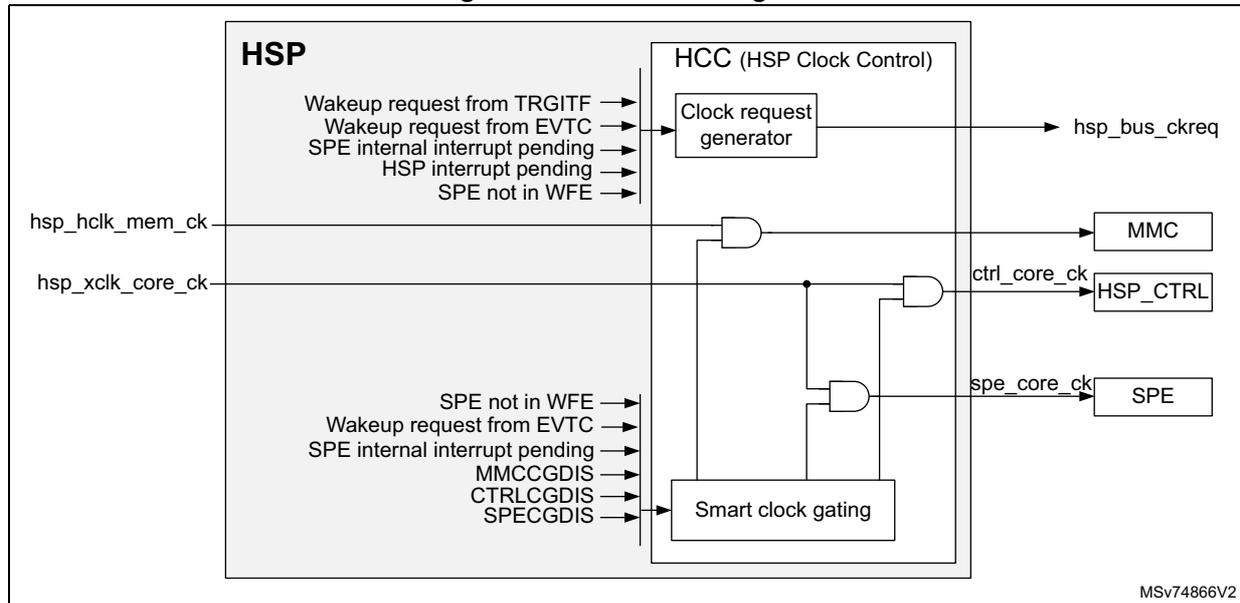

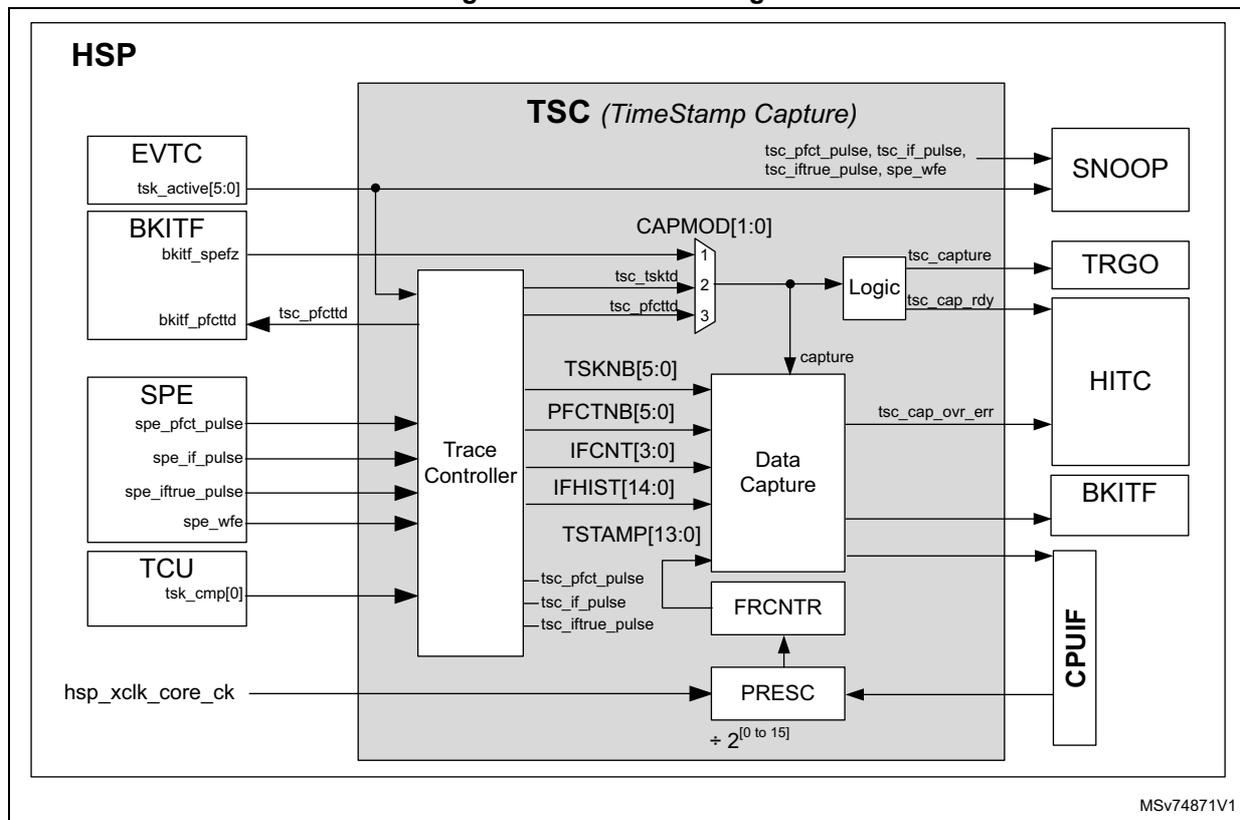

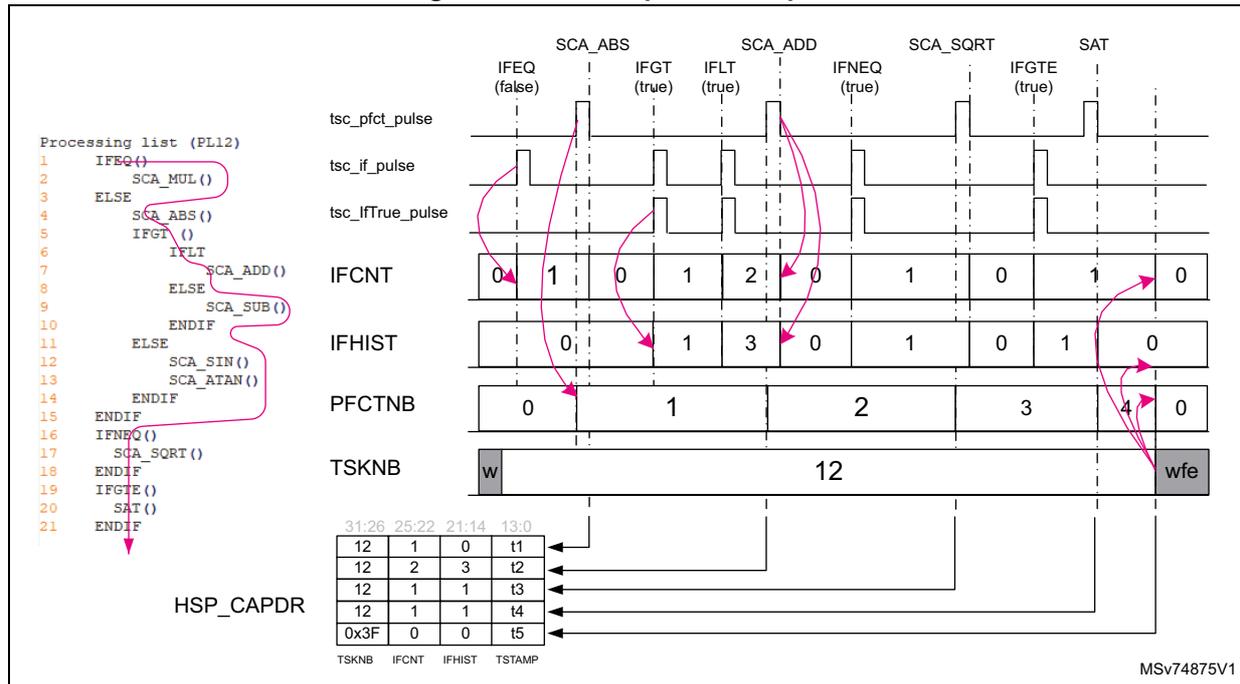

In the example below, initially there are no pending events and the SPE is in WFE. tsk_active[5:0] has a default value output of 0x3F. The evtC_wkup signal is inactive, and the output of tsk_add[19:0] is the address of the maximum task number supported by the product (see Section 19.3: HSP implementation ).