9. Power control (PWR)

9.1 PWR introduction

The power controller manages all device power supplies and power modes transitions.

9.2 PWR main features

The power controller (PWR) main features are:

- • Power supplies and supply domains

- – Core domain ( \( V_{CORE} \) )

- – \( V_{DD} \) domain

- – Backup domain

- – Analog domain ( \( V_{DDA} \) )

- – Supply for the SMPS power stage (available on SMPS packages)

- – \( V_{DDIO2} \) domain on port PG[15:2]

- – \( V_{DDUSB} \) for USB transceiver

- – \( V_{LCD} \) for LCD controller

- • System supply voltage regulation

- – SMPS step-down converter

- – Linear voltage regulator (LDO)

- • Power supply supervision

- – BOR monitor

- – PVD monitor

- – PVM monitor ( \( V_{DDA} \) , \( V_{DDUSB} \) , \( V_{DDIO2} \) )

- • Power management

- – Operating modes

- – Voltage scaling control

- – Low-power modes

- • \( V_{BAT} \) battery charging

- • TrustZone security and privileged protection

9.3 PWR functional description

9.3.1 PWR pins and internal signals

Table 82. PWR input/output pins

| Pin name | Pin type | Description |

|---|---|---|

| VDD | Supply | Main supply |

| GND | Supply | Main ground |

| VDDA | Supply | Analog peripherals supply |

Table 82. PWR input/output pins (continued)

| Pin name | Pin type | Description |

|---|---|---|

| VSSA | Supply | Analog peripherals ground |

| VDDIO2 | Supply | Independent I/O supply |

| VDDUSB | Supply | USB supply |

| VDD11 (packages with SMPS)/VCAP (packages without SMPS) | Supply | Logic supply ( \( V_{CORE} \) ) |

| VBAT | Supply | Backup domain supply |

| VDDSMPS | Supply | SMPS supply |

| VSSSMPS | Supply | SMPS ground |

| VLXSMPS | Supply | SMPS output |

| VREF+ | Supply | ADC/DAC high reference voltage |

| VREF- | Supply | ADC/DAC low reference voltage |

| WKUPx (x = 1 to 8) | Input | Wake-up pins |

| PWR_CSLEEP | Output | MCU in Sleep mode |

| PWR_CSTOP | Output | MCU in Stop mode |

Table 83. PWR internal input/output signals

| Internal signal name | Signal type | Description |

|---|---|---|

| WKUPx_y (x = 1 to 10, y = 1 to 4) | Input | Wake-up event source selection |

Each of ten wake-up events WKUPx, (x = 1 to 10), can be generated from pins or internal events, selected by WUSELx[1:0] in PWR_WUCR3.

Table 84. PWR wake-up source selection

| Wake-up event | Internal signal source (x = 1 to 8) | |||

|---|---|---|---|---|

| WKUPx_0 (WUSELx = 00) | WKUPx_1 (WUSELx = 01) | WKUPx_2 (WUSELx = 10) | WKUPx_3 (WUSELx = 11) | |

| WKUP1 | PA0 | PB2 | PE4 | Reserved |

| WKUP2 | PA4 | PC13 | PE5 | Reserved |

| WKUP3 | PE6 | PA1 | PB6 | Reserved |

| WKUP4 | PA2 | PB1 | PB7 | Reserved |

| WKUP5 | PC5 | PA3 | PB8 | IWDG |

| WKUP6 | PB5 | PA5 | PE7 | RTC_ALRA_S or RTC_ALRB_S or RTC_WUT_S or RTC_TS_S |

| WKUP7 | PB15 | PA6 | PE8 | RTC_ALRA or RTC_ALRB or RTC_WUT or RTC_TS |

Table 84. PWR wake-up source selection (continued)

| Wake-up event | Internal signal source (x = 1 to 8) | |||

|---|---|---|---|---|

| WKUPx_0 (WUSELx = 00) | WKUPx_1 (WUSELx = 01) | WKUPx_2 (WUSELx = 10) | WKUPx_3 (WUSELx = 11) | |

| WKUP8 | PF2 (1) | PA7 | PB10 | TAMP |

| WKUP9 | I3C1 reset pattern | |||

| WKUP10 | I3C2 reset pattern (2) /PVD (3) | |||

- 1. Pin available only on STM STM32U3B5/3C5 devices.

- 2. Not available on STM32U356/366.

- 3. Available only on STM32U356/366 devices.

9.3.2 PWR power supplies and supply domains

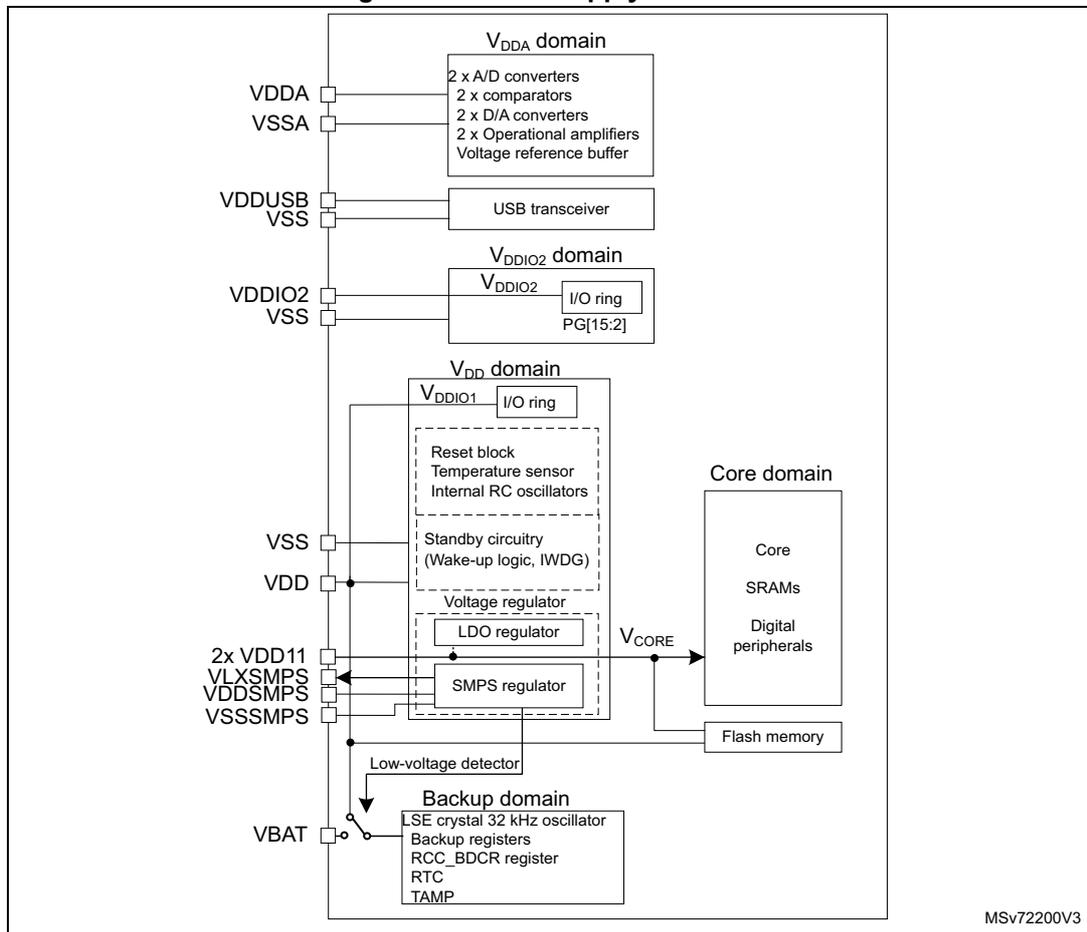

Figure 26. Power supply overview

The diagram illustrates the internal power supply architecture of the microcontroller. On the left, external pins are shown: VDDA, VSSA, VDDUSB, VSS, VDDIO2, VSS, VSS, VDD, 2x VDD11, VLXSMPS, VDDSMPS, VSSSMPS, and VBAT. These pins connect to various internal power domains and components:

- V DDA domain: Connected to VDDA and VSSA. It contains 2 x A/D converters, 2 x comparators, 2 x D/A converters, 2 x Operational amplifiers, and a Voltage reference buffer.

- USB transceiver: Connected to VDDUSB and VSS.

- V DDIO2 domain: Connected to VDDIO2 and VSS. It contains an I/O ring and PG[15:2].

- V DD domain: Connected to VDD. It contains an I/O ring (V DDIO1 ), a Reset block (Temperature sensor, Internal RC oscillators), Standby circuitry (Wake-up logic, IWDG), a Voltage regulator (LDO regulator), and an SMPS regulator. This domain also connects to the Core domain via V CORE .

- Core domain: Contains Core, SRAMs, and Digital peripherals. It is connected to the V DD domain via V CORE and to Flash memory.

- Backup domain: Connected to VBAT. It contains a Low-voltage detector, LSE crystal 32 kHz oscillator, Backup registers, RCC_BDCR register, RTC, and TAMP.

MSV72200V3

External power supplies

The devices require a 1.71 V to 3.6 V V DD operating voltage supply. Several independent supplies can be provided for specific peripherals. Those supplies must not be provided without a valid operating supply on the V DD pin:

- •

\(

V_{DD} = 1.71 \text{ V}

\)

to

\(

3.6 \text{ V}

\)

(functionality guaranteed down to

\(

V_{BOR}

\)

minimum value)

\( V_{DD} \) is the external power supply for the I/Os, the internal regulator and the system analog such as reset, power management and internal clocks. It is provided externally through the VDD pins. - •

\(

V_{DDA} = 1.58 \text{ V}

\)

(COMPs) /

\(

1.6 \text{ V}

\)

(DACs, OPAMP) /

\(

1.62 \text{ V}

\)

(ADCs) /

\(

1.8 \text{ V}

\)

(VREFBUF) to

\(

3.6 \text{ V}

\)

\( V_{DDA} \) is the external analog power supply for A/D converters, D/A converters, voltage reference buffer, operational amplifiers and comparators. The \( V_{DDA} \) voltage level is independent from the \( V_{DD} \) voltage and must be connected to VDD when these peripherals are not used. - •

\(

V_{DDSMPS} = 1.71 \text{ V}

\)

to

\(

3.6 \text{ V}

\)

\( V_{DDSMPS} \) is the external power supply for the SMPS step-down converter. It is provided externally through VDDSMPS supply pin, and must be connected to the same supply as VDD pin when the SMPS is used in the application. When the SMPS is not used, it is recommended to connect both VDDSMPS and VLXSMPS to GND. - •

\(

V_{LXSMPS}

\)

is the SMPS step-down converter output.

Note: The SMPS power supply pins are available only on a specific package with SMPS step-down converter option. - •

\(

V_{DDUSB} = 3.0 \text{ V}

\)

to

\(

3.6 \text{ V}

\)

\( V_{DDUSB} \) is the external independent power supply for USB transceivers. The \( V_{DDUSB} \) voltage level is independent from the \( V_{DD} \) voltage and must preferably be connected to VDD when the USB is not used. - •

\(

V_{DDIO2} = 1.08 \text{ V}

\)

to

\(

3.6 \text{ V}

\)

\( V_{DDIO2} \) is the external power supply for 14 I/Os (port G[15:2]). The \( V_{DDIO2} \) voltage level is independent from the \( V_{DD} \) voltage and must preferably be connected to VDD when PG[15:2] are not used. - •

\(

V_{BAT} = 1.55 \text{ V}

\)

to

\(

3.6 \text{ V}

\)

\( V_{BAT} \) is the power supply when \( V_{DD} \) is not present (through power switch) for RTC, TAMP, external 32 kHz oscillator, and backup registers. - •

\(

V_{REF-}

\)

,

\(

V_{REF+}

\)

\( V_{REF+} \) is the input reference voltage for ADCs and DACs. It is also the output of the internal voltage reference buffer when enabled.

\( V_{REF+} \) can be grounded when ADC and DAC are not active.

The internal voltage reference buffer supports four output voltages, that are configured with VRS bit in the VREFBUF_CSR register:- – \( V_{REF+} \) around \( 1.5 \text{ V} \) . This requires \( V_{DDA} \geq 1.8 \text{ V} \) .

- – \( V_{REF+} \) around \( 1.8 \text{ V} \) . This requires \( V_{DDA} \geq 2.1 \text{ V} \) .

- – \( V_{REF+} \) around \( 2.048 \text{ V} \) . This requires \( V_{DDA} \geq 2.4 \text{ V} \) .

- – \( V_{REF+} \) around \( 2.5 \text{ V} \) . This requires \( V_{DDA} \geq 2.8 \text{ V} \) .

When the \( V_{REF+} \) is double-bonded with VDDA in a package, the internal voltage reference buffer is not available and must be kept disabled.

\( V_{REF-} \) must always be equal to \( V_{SSA} \) . - •

\(

V_{LCD} = 2.5 \text{ V}

\)

to

\(

3.6 \text{ V}

\)

(available on STM32U356/366 devices only)

The LCD controller can be powered either externally through the VLCD pin or internally

from a voltage generated by the embedded step-up converter. VLCD is multiplexed with PA0, which can be used as a GPIO when the LCD is not used.

Internal regulators

The devices embed two regulators: one LDO and one SMPS in parallel to provide the \( V_{CORE} \) supply for digital peripherals, SRAMs and embedded flash memory. The SMPS generates this voltage on VDD11 (two pins) with a total external capacitor of 4.7 \( \mu\text{F} \) typical and requires an external coil of 2.2 \( \mu\text{H} \) typical.

The LDO generates this voltage on VCAP (one pin) with a total of external capacitor of 4.7 \( \mu\text{F} \) typical.

Both regulators can provide two different voltages (voltage scaling) and can operate in Stop mode.

It is possible to switch from SMPS to LDO and from LDO to SMPS on the fly.

Power-up and power-down power sequences

During power-up and power-down phases, the following power sequence requirements must be respected:

- • When \( V_{DD} \) is below 1 V, other power supplies ( \( V_{DDA} \) , \( V_{DDIO2} \) , \( V_{DDUSB} \) ) must remain below \( V_{DD} + 300 \text{ mV} \) .

- • When \( V_{DD} \) is above 1 V, all power supplies are independent.

During the power-down phase, \( V_{DD} \) can temporarily become lower than other supplies only if the energy provided to the MCU remains below 1 mJ. This allows external decoupling capacitors to be discharged with different time constants during the power-down transient phase.

Independent analog peripherals supply

To improve ADC and DAC conversion accuracy and to extend the supply flexibility, the analog peripherals have an independent power supply that can be separately filtered and shielded from noise on the PCB:

- • The analog peripherals voltage supply input is available on a separate \( V_{DDA} \) pin.

- • An isolated supply ground connection is provided on VSSA pin.

The \( V_{DDA} \) supply voltage can be different from \( V_{DD} \) . The presence of \( V_{DDA} \) must be checked before enabling any of the analog peripherals supplied by \( V_{DDA} \) (A/D converter, D/A converter, comparators, operational amplifiers, voltage reference buffer).

After reset, ADC and analog switch control supplied by \( V_{DDA} \) are logically and electrically isolated and therefore are not available. The isolation must be removed before using the analog peripherals, by setting the ASV bit in the PWR_SVMCR register, once the \( V_{DDA} \) supply is present.

The \( V_{DDA} \) supply can be monitored by the analog voltage monitors (AVM), and compared with two thresholds (1.6 V for AVM1 or 1.8 V for AVM2), refer to Peripheral voltage monitoring (PVM) for more details.

When a single supply is used, \( V_{DDA} \) can be externally connected to \( V_{DD} \) through the external filtering circuit in order to ensure a noise-free \( V_{DDA} \) reference voltage.

ADC and DAC reference voltage

To ensure a better accuracy on low-voltage inputs and outputs, the user can connect to V REF+ , a separate reference voltage lower than V DDA . V REF+ is the highest voltage, represented by the full scale value, for an analog input (ADC) or output (DAC) signal.

V REF+ can be provided either by an external reference or by an internal buffered voltage reference (VREFBUF).

The internal voltage reference can output a configurable voltage: 1.5 V, 1.8 V, 2.048 V or 2.4 V. The internal voltage reference can also provide the voltage to external components through VREF+ pin. Refer to the device datasheet and to Section 25.5.3: VREFBUF register map for further information.

Independent I/O supply rail

Some I/Os from port G (PG[15:2]) are supplied from a separate supply rail. The power supply for this rail can range from 1.08 V to 3.6 V and is provided externally through the VDDIO2 pin. The V DDIO2 voltage level is completely independent from V DD or V DDA . The VDDIO2 pin is available only for some packages. Refer to the pinout diagrams or tables in the related device datasheet(s) for I/O list(s).

After reset, the I/Os supplied by V DDIO2 are logically and electrically isolated and therefore are not available. The isolation must be removed before using any I/O from PG[15:2], by setting the IO2SV bit in PWR_SVMCR, once the V DDIO2 supply is present.

The V DDIO2 supply is monitored by the IO2 voltage monitoring (IO2VM) and compared with the internal reference voltage (3/4 VREFINT, around 0.9 V), refer to Peripheral voltage monitoring (PVM) for more details.

Independent USB transceivers supply

The USB transceivers are supplied from a separate VDDUSB power supply pin. V DDUSB range is from 3.0 V to 3.6 V and is completely independent from V DD or V DDA . The VDDUSB pin is not available for some small packages. It is internally connected with V DD . Refer to the pinout diagrams or tables in the related device datasheet(s) for I/O list(s).

After reset, the USB features supplied by V DDUSB are logically and electrically isolated and therefore are not available. The isolation must be removed before using the USB peripheral, by setting the USV bit in PWR_SVMCR, once the V DDUSB supply is present.

The V DDUSB supply is monitored by the USB voltage monitoring (UVM) and compared with the internal reference voltage (V REFINT , around 1.2 V), refer to Peripheral voltage monitoring (PVM) for more details.

Battery backup domain (also known as RTC domain)

To retain the content of the backup registers and supply the RTC and TAMP functions when V DD is turned off, the V BAT pin can be connected to an optional backup voltage supplied by a battery or by another source.

The backup domain supply is V SW , which is the output of a power switch between V DD and V BAT . The switch between V DD and V BAT supplies is automatically controlled by the brownout reset circuitry.

When V DD is below the lowest brownout reset threshold (V BOR0 ), the V BAT pin powers the RTC and TAMP peripherals, and LSE oscillators.

PC13, PC14 and PC15 pins, that can be configured by the RTC, the TAMP, or the LSE, are also powered by the VBAT pin.

When \( V_{DD} \) is higher than \( V_{BOR0} \) , the \( V_{DD} \) pin powers all previous functions.

Note: Due to the fact that the analog power switch can transfer only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in output mode is restricted: the speed must be limited (refer to the datasheet for more details) and these I/Os must not be used as a current source (for example to drive a LED).

Caution: During \( t_{RSTTEMPO} \) (temporization at \( V_{DD} \) startup) or after a PDR has been detected, the power switch between \( V_{BAT} \) and \( V_{DD} \) remains connected to \( V_{BAT} \) .

Caution: During the startup phase, if \( V_{DD} \) is established in less than \( t_{RSTTEMPO} \) (refer to the datasheet for the value of \( t_{RSTTEMPO} \) ) and \( V_{DD} > V_{BAT} + 0.6 \) V, a current may be injected into \( V_{BAT} \) through an internal diode connected between \( V_{DD} \) and the power switch ( \( V_{BAT} \) ). If the power supply/battery connected to the VBAT pin cannot support this current injection, it is strongly recommended to connect an external low-drop diode between this power supply and the VBAT pin.

If no external battery is used in the application, it is recommended to connect \( V_{BAT} \) externally to \( V_{DD} \) with a 100 nF external ceramic decoupling capacitor.

Backup domain access

After a system reset, the backup domain (RCC_BDCR, RTC registers, TAMP registers and backup registers) is protected against possible unwanted write accesses. To enable access to the backup domain, proceed as follows:

- 1. Enable the power interface clock by setting the PWREN bits in the RCC_AHB1ENR2.

- 2. Set the DBP bit in the PWR disable backup domain register (PWR_DBPR) to enable access to the backup domain.

VBAT battery charging

When \( V_{DD} \) is present, It is possible to charge the external battery on VBAT through an internal resistance.

The \( V_{BAT} \) charging is done either through a 5 k \( \Omega \) resistor or through a 1.5 k \( \Omega \) resistor depending on the VBRS bit value in PWR_BDCR.

The battery charging is enabled by setting VBE bit in PWR_BDCR. It is automatically disabled in \( V_{BAT} \) mode.

9.3.3 PWR system supply voltage regulation

SMPS and LDO embedded regulators

The devices embed two internal regulators, that can be selected when the application runs, depending on the application requirements:

- • a SMPS step-down converter

- • a linear voltage regulator (LDO)

The SMPS allows the power consumption to be reduced but some applications can be perturbed by the noise generated by the SMPS, requiring the application to switch to LDO.

The LDO and the SMPS regulators have two modes: Main regulator mode (used when performance is needed), and Low-power regulator mode. LDO or SMPS can be used in all voltage scaling ranges, and in all Stop modes.

LDO and SMPS versus reset, voltage scaling, and low-power modes

After reset, the regulator is the LDO, in range 2. Switching to SMPS provides lower consumption in particular at high \( V_{DD} \) voltage. It is possible to switch from LDO to SMPS, or from SMPS to LDO in any range, by configuring the REGSEL bit.

When exiting the Stop or Standby mode, the regulator is the same than when entering low-power modes. The voltage range is the range 2, except when exiting Stop 0 mode.

LDO and SMPS step-down converter fast startup

Note: After BOR reset, the LDO and SMPS regulators starts in slowstartup mode. This slowstartup feature is selected to limit the inrush current after power-on reset. This increases the wake-up time when exiting Stop or Standby mode.

However, it is possible to configure a faster startup on the fly and it is applied for next startup either after a system reset or wake-up from low-power mode except Shutdown and \( V_{BAT} \) modes. The fast startup is selected by setting the FSTEN bit in the PWR_CR3 register.

Dynamic voltage scaling management

The dynamic voltage scaling is a power management technique that consists in increasing or decreasing the voltage used for the digital peripherals ( \( V_{CORE} \) ), according to the application performance and power consumption needs.

Dynamic voltage scaling to increase \( V_{CORE} \) is known as overvolting. It allows the device to improve its performance.

Dynamic voltage scaling to decrease \( V_{CORE} \) is known as undervolting. It is performed to save power, particularly in laptop and other mobile devices where the energy comes from a battery and is thus limited.

The regulator operates in the following ranges:

- • Range 1: high performance

It provides a typical output voltage at 0.9 V. It is used when the system clock frequency is up to 96 MHz. - • Range 2: low-power range

It provides a typical output voltage at 0.75 V. The system clock frequency can be up to 48 MHz.

Caution: On STM32U3B5/3C5 devices, the HSP1 peripheral is not functional in range 2.

Voltage scaling is selected through the R1EN and R2EN bits in the PWR_VOSR register. The EPOD (embedded power distribution) booster must be enabled and ready before increasing the system clock frequency above 24 MHz in range 1 and range 2.

The sequence to switch the voltage scaling from range 2 (lower power) to range 1 (high performance) with system clock above 24 MHz is the following:

- 1. Configure the BOOSTSEL[1:0] and the BOOSTDIV[3:0] in the RCC_CFGR4 register to generate a booster clock frequency between 3 and 16 MHz.

- 2. Program R1EN = 1 and R2EN = 0 in the PWR_VOSR register.

- 3. Wait until the R1RDY flag is set in the PWR_VOSR register.

- 4. Set BOOSTEN in the PWR_VOSR register. This step can be done together with R1EN and R2EN programming

- 5. Wait until the BOOSTRDY flag is set in the PWR_VOSR register.

- 6. Adjust number of wait states according new frequency target in range 1 (LATENCY bits in the FLASH_ACR).

- 7. Configure and switch to new system frequency.

The sequence to switch the voltage scaling from range 1 (higher performance) to range 2 (lower power) is:

- 1. Reduce the system frequency to a value lower than 48 MHz.

- 2. Adjust number of wait states according new frequency target (LATENCY bits in the FLASH_ACR).

- 3. If new SYSCLK \( \leq \) 24 MHz, clear BOOSTEN in the PWR_VOSR register.

- 4. Program R1EN = 0 and R2EN = 1 in the PWR_VOSR register. This step can be done together with BOOSTEN clearing.

Caution: The booster clock source must not be disabled when the booster is enabled.

9.3.4 PWR power supply supervision

Brownout reset (BOR)

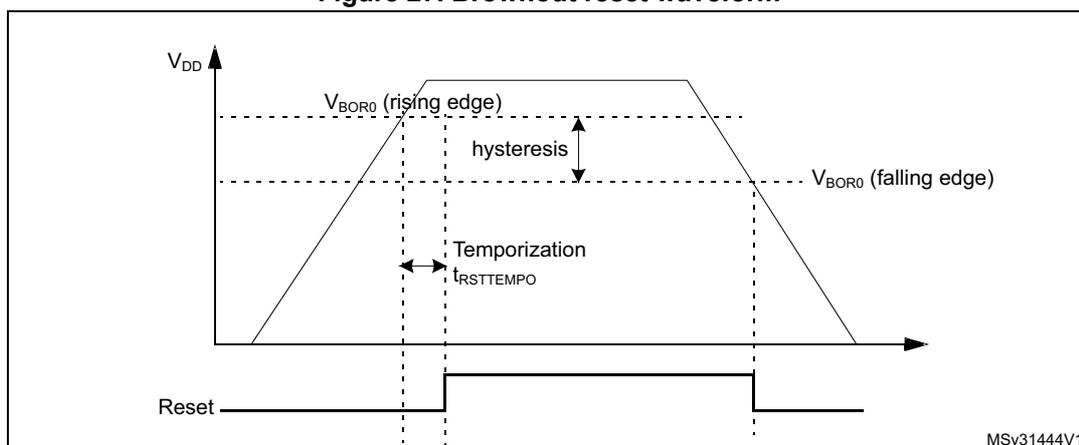

The device has an integrated brownout reset (BOR) circuitry. The BOR is active in all power modes except Shutdown mode, and cannot be disabled.

Five BOR thresholds can be selected through option bytes. BOR0 provides the always enabled power-on/powerdown functionality, independent from any other higher BOR level selection.

During power-on, the BOR keeps the device under reset until the supply voltage \( V_{DD} \) reaches the specified VBORx threshold. When \( V_{DD} \) drops below the selected threshold, a device reset is generated. When \( V_{DD} \) is above the VBORx upper limit, the device reset is released and the system can start.

For more details on the brownout reset thresholds, refer to the electrical characteristics section in the datasheet.

During Standby mode and if BOR level 0 is selected, it is possible to set the BOR in ultra-low-power mode to further reduce the current consumption by setting the ULPMEN bit in PWR control register 1 (PWR_CR1).

Figure 27. Brownout reset waveform

- 1. The reset temporization \( t_{RSTTEMPO} \) is present only for the BOR lowest threshold ( \( V_{BOR0} \) ).

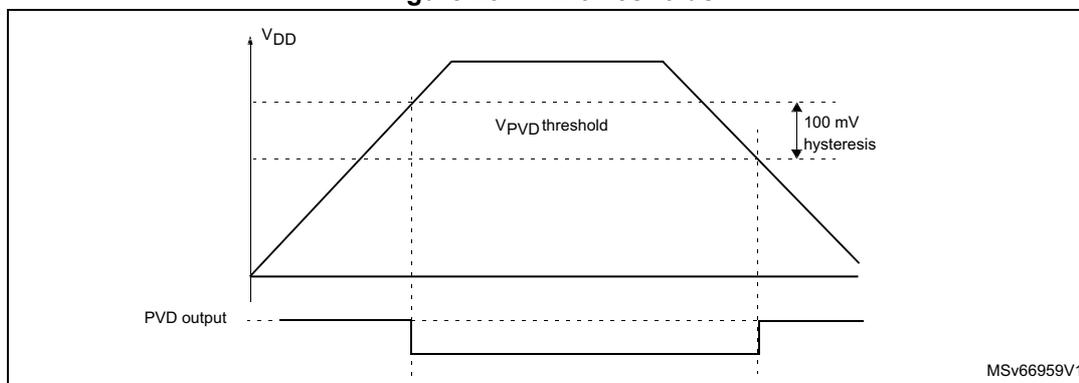

Programmable voltage detector (PVD)

The PVD can be used to monitor the \( V_{DD} \) power supply by comparing it to a threshold selected by the PVDLS[2:0] bits in the PWR supply voltage monitoring control register (PWR_SVMCR).

The PVD is enabled by setting the PVDE bit.

A PVDO flag is available in the PWR supply voltage monitoring control register (PWR_SVMSR) to indicate if \( V_{DD} \) is higher or lower than the PVD threshold. This event is internally connected to the EXTI and can generate an interrupt if enabled through the EXTI registers (refer to Table 97: PWR interrupt requests ).

The rising/falling edge sensitivity of the EXTI Line must be configured according to PVD output behavior. For example, if the EXTI line is configured to rising edge sensitivity, the interrupt is generated when \( V_{DD} \) drops below the PVD threshold. As an example, the service routine can perform emergency shutdown tasks.

The PVD can remain active in Stop 0, Stop 1, Stop 2 modes, and the PVD interrupt can wake up from the Stop mode.

For STM32U356/366 devices:

The PVD can also remain active in Stop 3 and Standby modes and can wake up from these modes by configuring associated wakeup line.

Figure 28. PVD thresholds

Peripheral voltage monitoring (PVM)

Only \( V_{DD} \) is monitored by default, as it is the only supply required for all system-related functions. The other supplies ( \( V_{DDA} \) , \( V_{DDIO2} \) and \( V_{DDUSB} \) ) can be independent from \( V_{DD} \) and can be monitored with four peripheral voltage monitoring (PVM):

- • The UVM monitors the USB supply \( V_{DDUSB} \) . \( V_{DDUSB}RDY \) indicates if the \( V_{DDUSB} \) independent power supply is higher or lower than the \( V_{UVM} \) threshold.

- • The IO2VM monitors the PG[15:2] supply \( V_{DDIO2} \) . \( V_{DDIO2}RDY \) indicates if the \( V_{DDIO2} \) independent power supply is higher or lower than the \( V_{IO2VM} \) threshold.

- • The AVM1 monitors the analog supply \( V_{DDA} \) . \( V_{DDA1}RDY \) indicates if the \( V_{DDA} \) independent power supply is higher or lower than the \( V_{AVM1} \) threshold.

- • The AVM2 monitors the analog supply \( V_{DDA} \) . \( V_{DDA2}RDY \) indicates if the \( V_{DDA} \) independent power supply is higher or lower than the \( V_{AVM2} \) threshold.

Each PVM output is connected to an EXTI line and can generate an interrupt if enabled through the EXTI registers. The PVMx output interrupt is generated when the independent power supply drops below the PVM threshold and/or when it rises above the PVM threshold, depending on EXTI line rising/falling edge configuration.

Refer to Table 97: PWR interrupt requests .

Each PVM can remain active in Stop 0, Stop 1, Stop 2 modes, and the PVM interrupt can wake up from the Stop mode. The PVM is not functional in Stop 3 mode.

Table 85. PVM features

| PVM | Power supply | PVM threshold |

|---|---|---|

| UVM | \( V_{DDUSB} \) | \( V_{UVM} \) (around 1.2 V) |

| IO2VM (1) | \( V_{DDIO2} \) | \( V_{IO2VM} \) (around 0.9 V) |

| AVM1 | \( V_{DDA} \) | \( V_{AVM1} \) (around 1.6 V) |

| AVM2 | \( V_{DDA} \) | \( V_{AVM2} \) (around 1.8 V) |

1. Not available on STM32U356/366.

The independent supplies ( \( V_{DDA} \) , \( V_{DDIO2} \) and \( V_{DDUSB} \) ) are not considered as present by default, and a logical and electrical isolation is applied to ignore any information coming from the peripherals supplied by these dedicated supplies:

- • If these supplies are shorted externally to \( V_{DD} \) , the application assumes they are available without enabling any peripheral voltage monitoring.

- • If these supplies are independent from \( V_{DD} \) , the peripheral voltage monitoring (PVM) can be enabled to confirm whether the supply is present or not.

The following sequence must be done before using the USB peripheral:

- 1. If

\(

V_{DDUSB}

\)

is independent from

\(

V_{DD}

\)

:

- a) Enable the UVM by setting UVMEN bit in the PWR supply voltage monitoring control register (PWR_SVMCR).

- b) Wait for the UVM wake-up time.

- c) Wait until VDDUSBRDY bit is set in the PWR supply voltage monitoring status register (PWR_SVMSR).

- d) Disable the UVM for consumption saving (optional).

- 2. Set the USV bit in the PWR supply voltage monitoring control register (PWR_SVMCR) to remove the \( V_{DDUSB} \) power isolation.

The following sequence must be done before using any I/O from PG[15:2]:

- 1. If

\(

V_{DDIO2}

\)

is independent from

\(

V_{DD}

\)

:

- a) Enable the IO2VM by setting IO2VM bit in the PWR supply voltage monitoring control register (PWR_SVMCR).

- b) Wait for the IO2CVM wake-up time.

- c) Wait until VDDIO2RDY bit is set in the PWR supply voltage monitoring status register (PWR_SVMSR).

- d) Disable the IO2VM for consumption saving (optional).

- 2. Set the IO2SV bit in the PWR supply voltage monitoring control register (PWR_SVMCR) to remove the \( V_{DDIO2} \) power isolation.

The following sequence must be done before using any of these analog peripherals: analog to digital converters, digital to analog converters, comparators, operational amplifiers, voltage reference buffer:

- 1. If

\(

V_{DDA}

\)

is independent from

\(

V_{DD}

\)

:

- a) Enable the AVM1 or AVM2 by setting AVM1EN or AVM2EN bit in the PWR supply voltage monitoring control register (PWR_SVMCR).

- b) Wait for the AVM wake-up time.

- c) Wait until VDDA1RDY or VDDA2RDY bit is set in the PWR supply voltage monitoring status register (PWR_SVMSR).

- d) Disable the AVM for consumption saving (optional).

- 2. Set the ASV bit in the PWR supply voltage monitoring control register (PWR_SVMCR) to remove the \( V_{DDA} \) power isolation.

9.3.5 PWR power management

Power modes overview

By default, the microcontroller is in Run mode after a system or a power reset. Reducing power consumption in Run mode is done by configuring voltage scaling according to application performance needs. Refer to Dynamic voltage scaling management . Unused RAMs can definitively be powered-off with SRAMxPD bits in PWR_CR1. Once an SRAM has been powered off using this configuration bit, it cannot be powered on back again until the next power-on reset. Power consumption is also reduced by reducing SYSCLK, HCLK and PCLK clocks speed, or gating unused peripherals clocks. Refer to Section 10: Reset and clock control (RCC) for more details.

Several low-power modes are available to save power when the CPU does not need to be kept running, for example when waiting for an external event. It is up to the user to select the mode that gives the best compromise between low-power consumption, short startup time and available wake-up sources.

The device features these low-power modes:

- • Sleep mode:

CPU clock off, all peripherals including Cortex-M33 core such as NVIC and SysTick can run and wake up the CPU when an interrupt or an event occurs (refer to Sleep mode ). - • Stop 0, Stop 1, Stop 2, Stop 3 modes:

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. In Stop 0 and Stop 1, the SRAMs can be programmed, with the SRAMFWU bit of the PWR_CR2 register, to remain in normal run mode, to allow short wake-up time.

In Stop 1, Stop 2, and Stop3, the SRAMs can be totally or partially switched off, to further reduce consumption (refer to the xRAMyPDS bits of the PWR_CR2 register). When the SRAM is definitively powered down through PWR_CR1, the power-down in Stop mode configuration in the PWR_CR2 register for the same SRAM has no effect. All clocks in the core domain are stopped. The MSI (MSIS and MSIK) RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals are autonomous and can operate in Stop mode by requesting their kernel clock and their bus (APB or AHB) when needed, in order to transfer data with GPDMA1 depending on peripherals and power mode.

In Stop 0 mode, the regulator remains in main regulator mode, allowing a very fast wake-up time but with much higher consumption.

In Stop 1, the regulator is in low power mode, and the whole core domain is fully powered. All autonomous peripherals are functional.

In Stop 2 mode, most of the core domain (D1 domain) is put in a lower leakage mode, keeping registers retention, but without any possible functionality. The D2 domain, embedding APB3 peripherals, is kept fully powered, so those peripherals can be kept functional.

Stop 3 is the lowest power mode with full retention, but the functional peripherals and sources of wake-up are reduced to the same ones than in Standby mode.

The system clock when exiting from Stop mode can be either MSIS up to 48 MHz or HSI16, depending on software configuration.

In case the wake-up clock is MSIS at 48 MHz, the EPOD booster must be configured (BOOSTSEL[1:0] = 01 in RCC_CFGR4) and enabled (BOOSTEN = 1 in PWR_VOSR) before entering Stop mode. Refer to System clock (SYSCLK) selection for more details.

Refer to Stop 0 mode , Stop 1 mode , Stop 2 mode , and Stop 3 mode .

- • Standby mode:

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the core domain is powered off. The MSI (MSIS and MSIK) RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brownout reset (BOR) always remains active in Standby mode.

The state of each I/O during Standby mode can be selected by software: I/O with internal pull-up, internal pulldown or floating.

After entering Standby mode, SRAMs and register contents are lost except for registers in the backup domain and Standby circuitry. Optionally, the full SRAM2 or 8 Kbytes or 24 Kbytes or 32 Kbytes can be retained in Standby mode, supplied by the low-power regulator (standby with SRAM2 retention mode).

Caution: The SRAM2 erase on system reset option bit (SRAM2_RST) also erases the SRAM2 memory content on standby exit. Therefore, it must not be used in conjunction with the standby retention mode.

The BOR can be configured in ultra-low-power mode to further reduce power consumption during standby mode and when the lowest threshold is selected (VBOR0).

The device exits Standby mode when an external reset (NRST pin), an IWDG early wake-up event or reset, WKUP pin event (configurable rising or falling edge), a RTC event occurs (alarm, periodic wake-up, timestamp), a tamper detection, a PVD event (only for STM32U356/366 devices), or a I3C reset pattern detection.

The system clock after wake-up is MSIS up to 12 MHz.

Refer to Standby mode .

- • Shutdown mode:

The Shutdown mode allows the lowest power consumption. The internal regulator is switched off so that the core domain is powered off. The HSI16, the MSI (MSIS and MSIK), the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to backup domain is not supported.

SRAMs and register contents are lost except for registers in the backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or a RTC event occurs (alarm, periodic wake-up, timestamp), a tamper detection or a I3C reset pattern detection.

The system clock after wake-up is MSIS at 12 MHz.

Refer to Shutdown mode .

The table below shows the power modes overview.

Table 86. Low-power mode summary

| Mode name | Entry | Wake-up source (1) | Wake-up system clock | Effect on clocks | Voltage regulators |

|---|---|---|---|---|---|

| Sleep (Sleep-now or Sleep-on-exit) | WFI or Return from ISR | Any interrupt | Same as before entering Sleep mode | CPU clock OFF | Range 1, 2 |

| WFE | Wake-up event | No effect on other clocks or analog clock sources | |||

| Stop 0 | LPMS = 000 + SLEEPDEEP bit + WFI or Return from ISR or WFE | Any EXTI line (configured in the EXTI registers) Any PWR wake-up line (WKUP pins and I3C reset pattern) Specific peripherals events/interrupts (2) | HSI16 when STOPWUCK = 1 in RCC_CFGR1 MSIS with the frequency before entering the Stop mode, limited to 48 MHz, when STOPWUCK = 0 | All clocks OFF except LSI and LSE | Range 1, 2 |

| Stop 1 | LPMS = 001 + SLEEPDEEP bit + WFI or Return from ISR or WFE | MSIK, MSIS or HSI16 can be enabled temporarily when requested by an autonomous peripheral, or forced to be kept enabled. | Low-power regulator (SMPS or LDO) | ||

| Stop 2 | LPMS = 010 + SLEEPDEEP bit + WFI or Return from ISR or WFE | ||||

| Stop 3 | LPMS = 011 + SLEEPDEEP bit + WFI or Return from ISR or WFE | WKUP pin edge, RTC/TAMP events/interrupts, external reset in NRST pin, IWDG events/interrupts or reset, I3C reset pattern, PVD (3) | MSIS from 3 MHz up to 12 MHz | All clocks OFF except LSI and LSE | |

| Standby with SRAM2_8 Kbytes | LPMS = 10X+ RRS1 = 1 + SLEEPDEEP bit + WFI or Return from ISR or WFE | ||||

| Standby with SRAM2_Full | LPMS = 10X+ RRS1 = RRS2 = RRS3 = 1 + SLEEPDEEP bit + WFI or Return from ISR or WFE | ||||

| Standby | LPMS = 10X + RRS1 = RRS2 = RRS3 = 0 + SLEEPDEEP bit + WFI or Return from ISR or WFE | OFF | |||

| Shutdown | LPMS = 11x + SLEEPDEEP bit + WFI or Return from ISR or WFE | WKUP pin edge, RTC/TAMP events/interrupts, external reset in NRST pin, I3C reset pattern | MSIS 12 MHz | All clocks OFF except LSE | OFF |

1. Refer to the next table.

- 2. A wake-up event from Stop mode can be generated with the peripheral interrupt signal depending on their wake-up capability. Refer to Exiting a low-power mode and see Table 87 below.

- 3. PVD is available only on STM32U356/366 devices.

Table 87. Functionalities depending on the working mode (1)

| Peripheral | Run | Sleep | Stop 0/1 | Stop 2 | Stop 3 | Standby | Shutdown | VBAT | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | ||||

| CPU | Y | - | - | - | - | - | - | - | - | - | - | - | - |

| Flash memory | O (2) | O (2) | - | O (3) | - | O (3) | - | - | - | - | - | - | - |

| SRAM1 | Y (4) | Y (5) | O (6) | - | O (6) | - | O (6) | - | - | - | - | - | - |

| SRAM2 | Y (4) | Y (5) | O (6) | O (7) | O (6) | O (7) | O (6) | - | O (8) | - | - | - | - |

| SRAM3 (9) | Y (4) | Y (5) | O (6) | O (7) | O (6) | O (7) | O (6) | - | - | - | - | - | - |

| SRAM4 (9) | Y (4) | Y (5) | O (6) | - | O (6) | - | O (6) | - | - | - | - | - | - |

| HSP1 (9) | O (10) | O (10) | - | - | - | - | - | - | - | - | - | - | - |

| OCTOSPI1 | O | O | - | - | - | - | - | - | - | - | - | - | - |

| Backup registers | Y | Y | Y | - | Y | - | Y | - | Y | - | Y | - | Y |

| Brownout reset (BOR) | Y | Y | Y | Y | Y | Y | Y | Y | Y | Y | - | - | - |

| Programmable voltage detector (PVD) | O | O | O | O | O | O | O (11) | O (11) | O (11) | O (11) | - | - | - |

| Peripheral voltage monitor (PVM) | O | O | O | O | O | O | - | - | - | - | - | - | - |

| GTZC | O | O | O | O (12) | O | O (12) | - | - | - | - | - | - | - |

| RAMCFG | O | O | O | O (7) | O | O (7) | - | - | - | - | - | - | - |

| GPDMA1 | O | O | O (13) | O (13) | O (14) | O (14) | - | - | - | - | - | - | - |

| High-speed internal (HSI16) | O | O | (15) | - | (15) | - | - | - | - | - | - | - | - |

| Oscillator HSI48 | O | O | - | - | - | - | - | - | - | - | - | - | - |

| High-speed external (HSE) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| Low-speed internal (LSI) | O | O | O | - | O | - | O | - | O | - | - | - | - |

| Low-speed external (LSE) | O | O | O | - | O | - | O | - | O | - | O | - | O |

| Multi-speed internal (MSIS and MSIK) | O | O | (15) | - | (15) | - | - | - | - | - | - | - | - |

| Clock security system (CSS) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| Clock security system on LSE | O | O | O | O | O | O | O | O | O | O | O | O | O |

| RTC/TAMP | O | O | O | O | O | O | O | O | O | O | O | O | O |

| Peripheral | Run | Sleep | Stop 0/1 | Stop 2 | Stop 3 | Standby | Shutdown | VBAT | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | ||||

| Number of TAMP tamper pins | 5 | 5 | 5 | O | 5 | O | 5 | O | 5 | O | 5 | O | 5 |

| USB | O | O | - | O | - | - | - | - | - | - | - | - | - |

| USARTx (x=1,2 (9) ,3,4,5) | O | O | O (16) | O (16) | - | - | - | - | - | - | - | - | - |

| Low-power UART (LPUART1) | O | O | O (16) | O (16) | O (16) | O (16) | - | - | - | - | - | - | - |

| I2Cx (x = 1,2 (9) ,4 (9) ) | O | O | O (17) | O (17) | - | - | - | - | - | - | - | - | - |

| I2C3 | O | O | O (17) | O (17) | O (17) | O (17) | - | - | - | - | - | - | - |

| I3Cx (x=1,2 (9) ) | O | O | O (18) | O (18) | - | O (19) | - | O (19) | - | O (19) | - | O (19) | - |

| SPIx (x = 1,2,3,4 (9) ) | O | O | O (20) | O (20) | - | - | - | - | - | - | - | - | - |

| FDCANx (x = 1,2) (9) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| SDMMC1 (9) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| SAI1 (9) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| ADC12 | O | O | - | - | - | - | - | - | - | - | - | - | - |

| DAC1 (2 converters) | O | O | O (21) | - | - | - | - | - | - | - | - | - | - |

| VREFBUF | O | O | O | - | - | - | - | - | - | - | - | - | - |

| OPAMPx (x = 1,2) | O | O | O | - | - | - | - | - | - | - | - | - | - |

| COMPx (x = 1,2) | O | O | O | O | O | O | - | - | - | - | - | - | - |

| Temperature sensor | O | O | O | - | - | - | - | - | - | - | - | - | - |

| Timers (TIMx) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| LPTIMx (x = 1,3,4) | O | O | O (22) | O (22) | O (22) | O (22) | - | - | - | - | - | - | - |

| LPTIM2 | O | O | O (22) | O (22) | - | - | - | - | - | - | - | - | - |

| Independent watchdog (IWDG) | O | O | O | O | O | O | O | O | O | O | - | - | - |

| Window watchdog (WWDG) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| SysTick timer | O | O | - | - | - | - | - | - | - | - | - | - | - |

| Audio digital filter (ADF) | O | O | O (23) | O (23) | - | - | - | - | - | - | - | - | - |

| LCD (9)(24) | O | O | O | O | O | O | O | - | - | - | - | - | - |

| Touch sensing controller (TSC) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| Peripheral | Run | Sleep | Stop 0/1 | Stop 2 | Stop 3 | Standby | Shutdown | VBAT | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | ||||

| Random number generator (RNG) (9) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| AES and secure AES (9) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| Public key accelerator (PKA) | O | O | - | - | - | - | - | - | - | - | - | - | - |

| HASH accelerator | O | O | - | - | - | - | - | - | - | - | - | - | - |

| CRC calculation unit | O | O | - | - | - | - | - | - | - | - | - | - | - |

| GPIOs | O | O | O | O | O | O | (25) | 24 pins (26) | (25) | 24 pins (26) | (27) | 24 pins (26) | - |

- 1. Y = yes (enable). O = optional (disable by default, can be enabled by software). - = not available.

- 2. The flash banks can be configured in power-down mode. By default, they are not in power-down mode.

- 3. Flash can be accessed by GPDMA1 in Stop 0, Stop 1 and Stop 2 modes. ECC error interrupt or NMI wakes up from these Stop modes.

- 4. The SRAMs can definitively be powered off independently until the next device power on reset.

- 5. The SRAM clock can be gated on or off independently.

- 6. Sub-blocks of SRAMx can be powered-off in Stop 1, Stop 2, and Stop 3, to save power. SRAMx can be accessed by GPDMA1 in Stop 0, Stop 1 and Stop 2 modes.

- 7. Parity error interrupt or NMI wakes up from Stop mode.

- 8. Content of 32 Kbyte, 24 Kbyte, and/or 8 Kbyte block can be preserved.

- 9. This feature is available only on certain STM32U3 devices. Refer to the device datasheet for the availability of the associated peripheral.

- 10. The HSP1 peripheral is not functional in range 2.

- 11. Only available on STM32U356/366 devices.

- 12. Illegal access interrupt wakes up from Stop 0, 1, 2 modes.

- 13. GPDMA1 transfers are functional and autonomous in Stop 0 and 1 mode. Interrupts wake up from these Stop modes.

- 14. In Stop 2 mode, GPDMA1 supports only LPUART1, I2C3, LPTIM1, LPTIM3 and LPTIM4 requests. None of GPDMA1 triggers are supported. Interrupts wake up from Stop 2 modes.

- 15. Some peripherals with autonomous mode and wake-up from Stop capability can request HSI16, MSIS or MSIK to be enabled. In this case, the oscillator is woken up by the peripheral, and is automatically put off when no peripheral needs it.

- 16. USART and LPUART reception and transmission is functional and autonomous in Stop mode, in asynchronous and in SPI master modes. Interrupts wake up from Stop mode.

- 17. I2C reception and transmission is functional and autonomous in Stop mode. Interrupts wake up from Stop mode.

- 18. I3C reception and transmission, in controller and target modes, is functional and autonomous in Stop mode. Interrupts wake up from Stop mode.

- 19. I3C reset pattern detection wakes up from Stop 2, Stop 3, Standby and Shutdown modes. I3C pull-ups can be applied in Stop and Standby modes.

- 20. SPI reception and transmission is functional and autonomous in Stop mode. Interrupts wake up from Stop mode.

- 21. DAC1 (2 channels) conversion in sample and hold mode is functional and autonomous in Stop mode.

- 22. LPTIM is functional and autonomous in Stop mode. Interrupts wake up from Stop mode.

- 23. ADF is functional and autonomous in Stop mode. Interrupts wake up from Stop mode.

- 24. LCD is functional and autonomous in Stop mode.

- 25. I/Os can be configured with internal pull-up, pull-down or floating in Stop 3 and Standby mode.

- 26. The exact number depends on the STM32U3 device. Refer to the device datasheet.

- 27. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

Autonomous peripherals

Several peripherals support the autonomous mode which allows it to be functional and perform DMA transfers in Stop 0, Stop 1, and Stop 2 modes. Their interrupts wake up from Stop mode.

In Stop 0 and Stop 1 modes, the autonomous peripherals are DAC1 (2 channels), LPTIMx (x = 1 to 4), U(S)ARTx (x = 1 to 5), LPUART1, SPIx (x = 1 to 4), I2Cx (x = 1 to 4), I3Cx (x = 1 to 2), ADF1, and GPDMA1.

In Stop 2 mode, the autonomous peripherals are LPTIM1, LPTIM3, LPTIM4, LPUART1, and I2C3. If one of these peripherals requests the AHB/APB clocks for a DMA transfer, the whole core domain is switched to Stop 1 higher leakage mode and the clock is distributed to GPDMA1, enabled SRAMs and peripherals in order to perform the autonomous peripheral DMA transfer. Then the core domain automatically returns to Stop 2 lower leakage mode.

Note: Only DMA requests from LPTIM1, LPTIM3, LPTIM4, LPUART1, or I2C3 peripherals are supported in Stop 2 mode. It is not possible to trig a GPDMA1 transfer in Stop 2 mode using GPDMA1 hardware triggers signals, even from those peripherals.

Low-power modes

Entering a low-power mode

The MCU enters low-power modes by executing the WFI (wait for interrupt), or WFE (wait for event) instructions, or when the SLEEPONEXIT bit in the Cortex-M33 system control register is set on Return from ISR.

Entering a low-power mode through WFI or WFE is executed only if no interrupt is pending or no event is pending.

Caution: The peripherals with autonomous mode feature are able to generate an AHB or APB clock request, depending on their internal events. If a clock request is present when WFI or WFE is executed, the low-power mode entry is delayed until the clock request is released.

Exiting a low-power mode

The way the MCU exits the Sleep or Stop mode depends on the way the low-power mode was entered:

- • If the WFI instruction or Return from ISR was used to enter the low-power mode, any peripheral interrupt acknowledged by the NVIC can wake up the device.

- • If the WFE instruction is used to enter the low-power mode, the MCU exits the low-power mode as soon as an event occurs. The wake-up event can be generated either by:

- – an NVIC IRQ peripheral interrupt:

When SEVONPEND = 0 in the Cortex-M33 system control register: By enabling an interrupt in the peripheral control register and in the NVIC. When the MCU resumes from WFE, the peripheral interrupt pending bit and the NVIC IRQ

- – an NVIC IRQ peripheral interrupt:

peripheral channel pending bit (in the NVIC interrupt clear pending register) must be cleared. Only NVIC interrupts with high enough priority wake up and interrupt the MCU.

When SEVONPEND = 1 in the Cortex-M33 system control register: By enabling an interrupt in the peripheral control register and optionally in the NVIC. When the MCU resumes from WFE, the peripheral interrupt pending bit and the NVIC IRQ peripheral channel pending bit (in the NVIC interrupt clear pending register) must be cleared. All NVIC interrupts wake up the MCU, even the disabled ones.

- – an event: by configuring a EXTI line in event mode. When the CPU resumes from WFE, it is not necessary to clear the EXTI peripheral interrupt pending bit or the NVIC IRQ channel pending bit as the pending bits corresponding to the event line is not set. It may be necessary to clear the interrupt flag in the peripheral.

After waking up from Standby or Shutdown mode, the program execution restarts in the same way as after a reset (boot pin sampling, option bytes loading, reset vector is fetched).

Caution: When the device is in Stop mode, a peripheral interrupt powers on an internal oscillator. The corresponding NVIC interrupt channel must be enabled to allow the interrupt to exit the device from Stop mode. It is not allowed to disable a peripheral interrupt by disabling only the NVIC channel while keeping the peripheral interrupt enable, as the device could remain in Stop mode with clock ON.

Caution: The peripherals with autonomous mode feature are able to generate an AHB or APB clock request when the device is in Stop mode, depending on their internal events. The software must ensure that either DMA transfer or interrupt is served, by configuring properly and in a consistent way the RCC, the autonomous peripherals, the DMA channels and NVIC. Note that when an autonomous peripheral requests the bus clock in Stop mode, the AHB and APB clocks are distributed to all enabled peripherals. Consequently, enabled peripherals, even without autonomous mode capability, are temporarily clocked and can also generate an interrupt during this time. These peripherals interrupts wake up the device from Stop mode.

Sleep mode

I/O states in Sleep mode

In Sleep mode, all I/O pins keep the same state as in Run mode.

Entering Sleep mode

The MCU enters the Sleep mode as described in Entering a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is clear (see the table below for details on how to enter the Sleep mode).

Exiting Sleep mode

The MCU exits the Sleep mode as described in Exiting a low-power mode (see the table below for details on how to exit the Sleep mode).

Table 88. Sleep mode

| Sleep mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

Refer to the Cortex-M33 system control register. On return from ISR while:

Refer to the Cortex-M33 system control register. |

| Mode exit | If WFI or Return from ISR was used for entry Interrupt (refer to Table 134: STM32U3 series vector table ) If WFE was used for entry and SEVONPEND = 0: Wake-up event (refer to Section 17.3: EXTI functional description ) If WFE was used for entry and SEVONPEND = 1: Interrupt even when disabled in NVIC (refer to Table 134: STM32U3 series vector table ) or wake-up event (refer to Section 17.3: EXTI functional description ) |

| Wake-up latency | None |

Stop 0 mode

The Stop 0 mode is based on the Cortex-M33 DeepSleep mode combined with the peripheral clock gating. The voltage regulator is configured in main regulator mode. The MSIS, MSIK, HSI16 and HSE oscillators are disabled by hardware. The LSE and LSI are kept enabled if they were before entering Stop 0 mode.

Some peripherals with the autonomous mode capability can switch on HSI16 or MSIS or MSIK for transferring data (see Autonomous peripherals for details).

All SRAMs and register contents are preserved. SRAMs can be kept in normal mode to allow fast wake-up at a cost of extra power consumption.

The BOR is always available in Stop 0 mode.

I/O states in Stop 0 mode

In the Stop 0 mode, all I/O pins keep the same state as in the Run mode.

Entering Stop 0 mode

The MCU enters the Stop 0 mode as described in Entering a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is set (see Table 89 for details on how to enter the Stop 0 mode).

If the flash memory programming is ongoing, the Stop 0 mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, the Stop 0 mode entry is delayed until the APB access is finished.

In Stop 0 mode, the following features can be selected by programming the individual control bits:

- • The independent watchdog (IWDG) is started by writing to its key register or by hardware option. Once started, it cannot be stopped except by a reset (see Section 10.3 PWR functional description).

- • The real-time clock (RTC) and tamper (TAMP) kernel clock is enabled by the RTCEN bit in RCC_BDCR.

- • The internal RC oscillator LSI clock or LSI clock divided by 128, is configured by the LSION and LSIPREDIV bits in RCC_CSR.

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in RCC_BDCR.

Several peripherals can be autonomous in Stop 0 mode and can add consumption if they are enabled (see Autonomous peripherals for more details).

The OPAMPs, the COMPs, the DAC1 (two channels), the VREFBUF, the PVM, and the PVD can be used in Stop 0 mode. If they are not needed, they must be disabled by software to save their power consumptions.

The ADCx (x = 1, 2) and the temperature sensor can consume power during the Stop 0 mode, unless they are disabled before entering this mode.

Exiting Stop 0 mode

The MCU exits the Stop 0 mode as described in Exiting a low-power mode (see Table 89 for details on how to exit Stop 0 mode).

When exiting Stop 0 mode by issuing an interrupt or a wake-up event, HSI16 is selected as system clock if the bit STOPWUCK is set in RCC_CFGR1. The MSIS oscillator is selected as system clock if STOPWUCK is cleared. The MSIS selection allows a wake-up at higher frequency (up to 48 MHz).

Several peripherals are autonomous in Stop mode, and can generate interrupts with wake-up from Stop capability.

All peripheral clocks must be enabled to allow a wake-up from Stop interrupt (Refer to RCC for more details).

When exiting the Stop 0 mode, the MCU is in Run mode (Range 1 or Range 2 depending on regulator range configuration).

Table 89. Stop 0 mode

| Stop 0 mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

To enter Stop 0 mode, all EXTI line pending bits and the peripheral flags generating wake-up interrupts must be cleared. Otherwise, the Stop 0 mode entry procedure is ignored and the program execution continues. |

| Mode exit | If WFI or Return from ISR was used for entry:

If WFE was used for entry and SEVONPEND = 0:

If WFE was used for entry and SEVONPEND = 1:

All peripheral clocks must be enabled to allow this peripheral to generate a wake-up from Stop interrupt ([PERIPH]JEN, [PERIPH]SLPEN and [PERIPH]STPEN bits must be set in the RCC, and a functional independent clock must be selected). |

| Wake-up latency | Wake-up on flash:

|

Stop 1 mode

The Stop 1 mode is the same as Stop 0 mode except that the regulator is in low-power mode and the SRAMs can be totally or partially switched off to further reduce consumption (see the following table for details on how to enter and exit Stop 1 mode).

Table 90. Stop 1 mode

| Stop 0 mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

To enter Stop 0 mode, all EXTI line pending bits and the peripheral flags generating wake-up interrupts must be cleared. Otherwise, the Stop 0 mode entry procedure is ignored and the program execution continues. |

| Mode exit | If WFI or Return from ISR was used for entry:

If WFE was used for entry and SEVONPEND = 0:

If WFE was used for entry and SEVONPEND = 1:

All peripheral clocks must be enabled to allow this peripheral to generate a wake-up from Stop interrupt ([PERIPH]EN, [PERIPH]SLPEN and [PERIPH]STPEN bits must be set in the RCC, and a functional independent clock must be selected). |

| Wake-up latency | Wake-up on flash:

|

Stop 2 mode

The Stop 2 mode is similar to Stop 1 except that most of the core domain (D1 domain) is put in a lower leakage mode. Only the part of the core domain embedding APB3 peripherals (D2 domain) remains fully powered, allowing those peripherals to be functional.

The APB3 peripherals with the autonomous mode capability can switch on HSI16 or MSIS or MSIK for transferring data (see Autonomous peripherals for details).

All SRAMs and register contents are preserved, but the SRAMs can be totally or partially switched off to further reduced consumption.

The BOR is always available in Stop 2 mode.

I/O states in Stop 2 mode

In the Stop 2 mode, all I/O pins keep the same state as in the Run mode; except for I3C specific pull-up. PWR I3C pull-up control register 1 or 2 must be configured before entering Stop 2 mode in order to apply I3C pull-ups on corresponding I/Os. The I3C pull-up control bits must be cleared after exiting Stop 2 mode, to let I3C peripheral controls I/O pull-up activation.

Entering Stop 2 mode

The MCU enters the Stop 2 mode as described in Entering a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is set (see Table 91 for details on how to enter the Stop 2 mode).

If the flash memory programming is ongoing, the Stop 2 mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, the Stop 2 mode entry is delayed until the APB access is finished.

In Stop 2 mode, the following features can be selected by programming individual control bits:

- • The independent watchdog (IWDG) is started by writing to its key register or by hardware option. Once started it cannot be stopped except by a reset (see Section 9.3: PWR functional description ).

- • The real-time clock (RTC) and Tamper (TAMP) kernel clock is enabled by the RTCEN bit in the RCC_BDCR.

- • The internal RC oscillator LSI clock or LSI clock divided by 128, is configured by the LSION and LSIPREDIV bits in RCC_CSR.

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in RCC_BDCR.

- • The I3Cx (x = 1, 2) reset pattern detection are enabled by the WUPEN9 and WUPEN10 bits in PWR_WUCR1.

Several peripherals can be autonomous in Stop 2 mode and can add consumption if they are enabled (see Autonomous peripherals for more details).

The COMPs, the PVM and the PVD can be used in Stop 2 mode. If they are not needed, they must be disabled by software to save their power consumptions.

The ADCx (x = 1, 2), the DAC1 (two channels), the temperature sensor, the OPAMP and the VREFBUF can consume power during the Stop 2 mode, unless they are disabled before entering this mode.

Caution: All the peripherals that cannot be functional in Stop 2 mode must be either disabled by clearing the enable bit in the peripheral itself, or put under reset state by configuring the RCC registers.

Exiting Stop 2 mode

The MCU exits the Stop 2 mode as defined in Exiting a low-power mode (see Table 91 for details on how to exit Stop 2 mode).

When exiting Stop 2 mode by issuing an interrupt or a wake-up event, HSI16 is selected as system clock if the bit STOPWUCK is set in RCC_CFGR1. MSIS is selected as system clock if STOPWUCK is cleared. The MSI selection allows a wake-up at higher frequency (up to 48 MHz).

Several peripherals are autonomous in Stop mode, and can generate interrupts with wake-up from Stop capability.

All peripheral clocks must be enabled to allow a wake-up from Stop interrupt (Refer to Reset and clock control (RCC) for more details).

When exiting the Stop 2 mode, the MCU is in Run mode, range 2.

Table 91. Stop 2 mode

| Stop 2 mode | Description |

|---|---|

WFI (wait for interrupt) or WFE (wait for event) while:

| |

| Mode entry | On Return from ISR while:

|

| To enter Stop 2 mode, all EXTI line pending bits and the peripheral flags generating wake-up interrupts must be cleared. Otherwise, the Stop mode entry procedure is ignored and the program execution continues. |

Table 91. Stop 2 mode (continued)

| Stop 2 mode | Description |

|---|---|

| Mode exit | If WFI or Return from ISR was used for entry:

If WFE was used for entry and SEVONPEND = 0:

If WFE was used for entry and SEVONPEND = 1:

All peripheral clocks must be enabled to allow this peripheral to generate a wake-up from Stop interrupt ([PERIPH]EN, [PERIPH]SLPEN and [PERIPH]STPEN bits must be set in the RCC, and a functional independent clock must be selected). |

| Wake-up latency | Wake-up on flash:

|

Stop 3 mode

The Stop 3 mode is based on the Cortex-M33 DeepSleep mode combined with peripheral clock gating. In Stop 3 mode, all clocks in the core domain are stopped. The MSIS, MSIK, HSI16 and HSE oscillators are disabled.

All SRAMs and register contents are preserved, but the SRAMs can be totally or partially switched off to further reduce consumption.

The BOR is always available in Stop 3 mode.

I/O states in Stop 3 mode

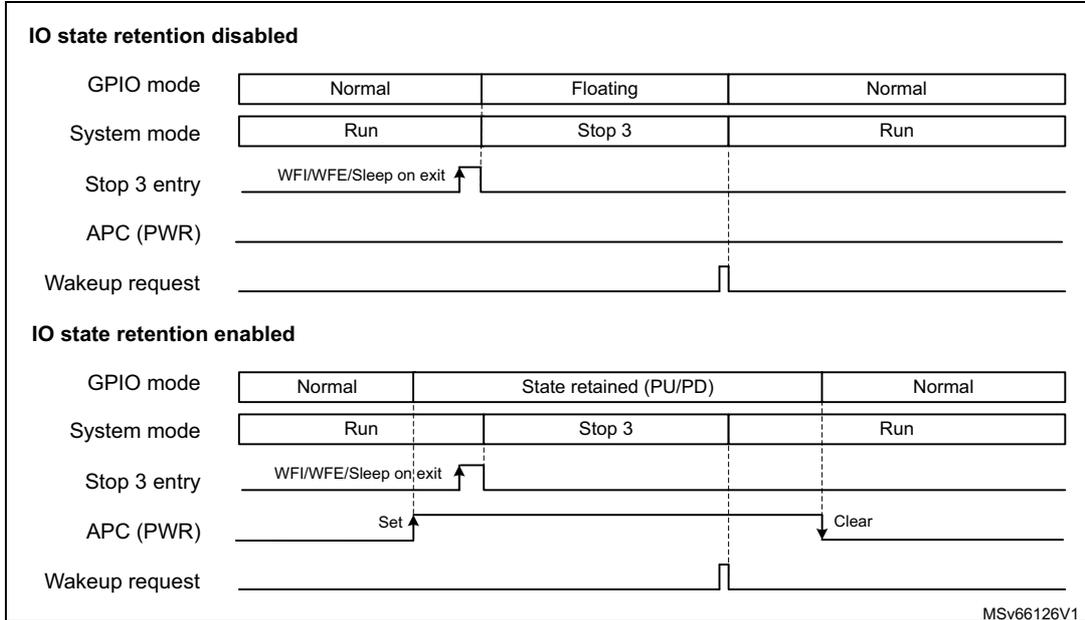

In the Stop 3 mode, the I/Os are by default in floating state. If the APC bit in the PWR_APCR register is set, the I/Os can be configured either with a pull-up (see PWR_PUCRx registers), or with a pull-down (see PWR_PDCRx registers), or can be kept in analog state if none of the PWR_PUCRx or PWR_PDCRx register is set. The pulldown configuration has highest priority over pull-up configuration in case both PWR_PUCRx and PWR_PDCRx are set for the same I/O. After wakeup from Stop 3 mode, the pull-up/pull-down I/O configuration remains retained based on PWR_PUCRx/PWR_PDCRx as long as APC bit is set.

Some I/Os (listed in Section 12: General-purpose I/Os (GPIO) ) are used for JTAG/SW debug and can only be configured to their respective reset pull-up or pull-down state during Stop 3 mode setting their respective bit to 1 in the PWR_PUCRx or PWR_PDCRx registers, or to be configured to floating state if the bit is kept at 0.

I3C specific pull-ups are activated thanks to PWR I3C pull-up control registers 1 or 2. These registers must be configured before entering Stop 3 mode in order to apply I3C pull-ups on corresponding I/Os. The I3C pull-up control bits must be cleared after exiting Stop 3 mode, to let I3C peripheral controls I/O pull-up activation.

The RTC outputs on PC13 and PB2 are functional in Stop 3 mode. The 22 wake-up pins multiplexed on eight events (WKUPx, x = 1 to 8).

Entering Stop 3 mode

The MCU enters the Stop 3 mode as described in Entering a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 System Control register is set (see Table 92 for details on how to enter the Stop 3 mode).

If the flash memory programming is ongoing, the Stop 3 mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, the Stop 3 mode entry is delayed until the APB access is finished.

In Stop 3 mode, the following features can be selected by programming individual control bits:

- • The independent watchdog (IWDG) is started by writing to its key register or by hardware option. Once started it cannot be stopped except by a reset (see Section 9.3: PWR functional description ).

- • The real-time clock (RTC) and Tamper (TAMP) kernel clock is enabled by the RTCEN bit in the RCC_BDCR.

- • The internal RC oscillator LSI clock or LSI clock divided by 128, is configured by the LSION and LSIPREDIV bits in RCC_CSR.

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in RCC_BDCR.

- • The I3Cx (x = 1, 2) reset pattern detection are enabled by the WUPEN9 and WUPEN10 bits in PWR_WUCR1.

Exiting Stop 3 mode

The MCU exits the Stop 3 mode as described in Exiting a low-power mode (see Table 92 for details on how to exit Stop 3 mode).

When exiting Stop 3 mode by issuing an interrupt or a wake-up event, HSI16 is selected as system clock if the bit STOPWUCK is set in RCC_CFGR1. MSIS is selected as system clock if STOPWUCK is cleared. The MSI selection allows a wake-up at higher frequency (up to 48 MHz).

When exiting the Stop 3 mode, the MCU is in Run mode, range 2.

When exiting Stop 3 mode, I/Os that were configured with pull-up or pull-down during Stop 3 through PWR_PUCRx or PWR_PDCRx, keep this configuration upon exiting Stop 3 mode until the APC bit in PWR_CR3 is cleared by software. Once APC is cleared, the I/Os pull-up/pull-down state is configured according to the GPIOx_PUPDR registers. The content of

the PWR_PUCRx or PWR_PDCRx registers is not lost and can be re-used for a subsequent entering into Stop 3 mode.

Figure 29. I/O states in Stop 3 mode

IO state retention disabled

| GPIO mode | Normal | Floating | Normal |

| System mode | Run | Stop 3 | Run |

| Stop 3 entry | WFI/WFE/Sleep on exit | ||

| APC (PWR) | |||

| Wakeup request | |||

IO state retention enabled

| GPIO mode | Normal | State retained (PU/PD) | Normal |

| System mode | Run | Stop 3 | Run |

| Stop 3 entry | WFI/WFE/Sleep on exit | ||

| APC (PWR) | Set | Clear | |

| Wakeup request | |||

MSv66126V1

Table 92. Stop 3 mode

| Stop 3 mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

To enter Stop 3 mode, all WUFx, and the RTC/TAMP flags generating wake-up interrupts must be cleared. Otherwise, the Stop 3 mode entry procedure is completed but the Stop 3 is exited immediately after entry. |

Table 92. Stop 3 mode (continued)

| Stop 3 mode | Description |

|---|---|

| Mode exit |

|

| Wake-up latency | wake-up on flash:

|

Standby mode

The lowest power mode in which the BOR is active is the Standby mode. It is based on the Cortex-M33 DeepSleep mode, with the voltage regulators disabled (except when SRAM2 content is preserved). The PLL, HSI16, MSIS, MSIK and HSE oscillators are also switched off.

The SRAMs and register contents are lost except for registers in the backup domain and Standby circuitry (see Figure 26: Power supply overview ). SRAM2 content can be partially or fully preserved depending on RRSB1, RRSB2 and RRSB3 bits configuration in PWR_CR1. In this case, the low-power regulator is ON and provides the supply to SRAM2 only.

The BOR is always available in Standby mode. The ULPMEN bit in the PWR_CR1 register must be configured to 1 to reach the lowest power consumption by forcing the BOR in ultra-low-power mode (only available when BOR level 0 is selected).

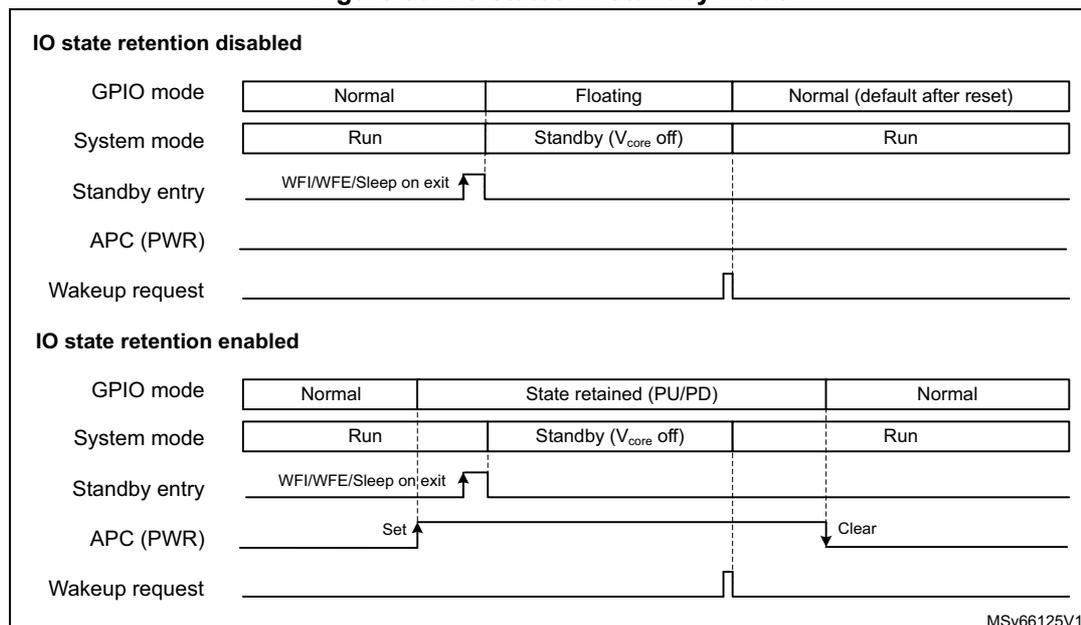

I/O states in Standby mode

In the Standby mode, the I/Os are by default in floating state. If the APC bit in the PWR_APCR register is set, the I/Os can be configured either with a pull-up (see PWR_PUCRx registers), or with a pull-down (see PWR_PDCRx registers), or can be kept in analog state if none of the PWR_PUCRx or PWR_PDCRx register is set. The pulldown configuration has highest priority over pull-up configuration in case both PWR_PUCRx and PWR_PDCRx are set for the same I/O. After wakeup from Standby mode, the pull-up/pull-down I/O configuration remains retained based on PWR_PUCRx/PWR_PDCRx as long as APC bit is set.

Some I/Os (listed in Section 12: General-purpose I/Os (GPIO) ) are used for JTAG/SW debug and can only be configured to their respective reset pull-up or pull-down state during Standby mode setting their respective bit to 1 in the PWR_PUCRx or PWR_PDCRx registers, or to be configured to floating state if the bit is kept at 0.

I3C specific pull-ups are activated thanks to PWR I3C pull-up control registers 1 or 2. These registers must be configured before entering Standby mode in order to apply I3C pull-ups on corresponding I/Os. The I3C pull-up control bits must be cleared after exiting Standby mode, and after I3C initialization is done, to let I3C peripheral controls I/O pull-up activation.

The RTC outputs on PC13 and PB2 are functional in Standby mode. PC14 and PC15 used for LSE are also functional. 22 wake-up pins multiplexed on eight events (WKUPx, x = 1 to 8) and the five tamper pins are available.

Entering Standby mode

The MCU enters the Standby mode as described in Entering a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is set (see Table 93 for details on how to enter Standby mode).

In Standby mode, the following features can be selected by programming individual control bits:

- • The independent watchdog (IWDG) is started by writing to its Key register or by hardware option. Once started it cannot be stopped except by a reset (see Section 9.3: PWR functional description ).

- • The real-time clock (RTC) and Tamper (TAMP) kernel clock is enabled by the RTCEN bit in the RCC_BDCR.

- • The internal RC oscillator LSI clock or LSI clock divided by 128, is configured by the LSION and LSIPRE bits in RCC_BDCR.

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in RCC_BDCR.

- • The I3Cx (x = 1, 2) reset pattern detection are enabled by the WUPEN9 and WUPEN10 bits in PWR_WUCR1.

Exiting Standby mode

The MCU exits the Standby mode as described in Exiting a low-power mode . The SBF status flag in the PWR status register (PWR_SR) indicates that the MCU was in Standby mode.

When exiting Standby mode, I/Os that were configured with pull-up or pull-down during Standby through PWR_PUCRx or PWR_PDCRx, keep this configuration upon exiting Standby mode until the APC bit in PWR_CR3 is cleared by the software. The application can release the retained I/O state (clear the retained pull-up/pull-down) by clearing the APC bit, after reconfiguring the GPIOs and related peripherals. Once APC is cleared, the I/Os state is configured according to the GPIOx registers. The content of the PWR_PUCRx or PWR_PDCRx registers is not lost and can be re-used for a sub-sequent entering into Standby mode.

Some I/Os (listed in Section 13 General-purpose I/Os (GPIO) ) are used for JTAG/SW debug and have internal pull-up or pull-down activated after reset so is configured at this reset value, as well when exiting Standby mode.

For I/Os, with a pull-up or pull-down pre-defined after reset (some JTAG/SW I/Os) or with the GPIOx_PUPDR programming done after exiting from Standby, in case those programming is different from the PWR_PUCRx or PWR_PDCRx programmed value during Standby, both a pull-down and pull-up are applied until APC is cleared, releasing the PWR_PUCRx or PWR_PDCRx programmed value.

Figure 30. I/O states in Standby mode

IO state retention disabled

| GPIO mode | Normal | Floating | Normal (default after reset) |

| System mode | Run | Standby ( \( V_{core} \) off) | Run |

| Standby entry | WFI/WFE/Sleep on exit | ||

| APC (PWR) | |||

| Wakeup request | |||

IO state retention enabled

| GPIO mode | Normal | State retained (PU/PD) | Normal |

| System mode | Run | Standby ( \( V_{core} \) off) | Run |

| Standby entry | WFI/WFE/Sleep on exit | ||

| APC (PWR) | Set | Clear | |

| Wakeup request | |||

MSv66125V1

Table 93. Standby mode

| Standby mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

(1)

|

| Mode exit |

|

| Wake-up latency | Reset phase. In case SRAM2 is retained in Standby, the wake-up latency is shorter as LDO setup is from low-power, instead of from OFF state. In the case where SRAM2 is in Standby, the wake-up latency is shorter because LDO setup is done in low-power, instead of in OFF state. |

1. The Standby mode is also entered if LPMS = 11X in PWR_CR1 with BREN = 1 in PWR_BDCR.

Shutdown mode

The lowest power consumption is reached in Shutdown mode. It is based on the DeepSleep mode with the voltage regulator disabled. The core domain is consequently powered off. The PLL, HSI16, MSIS, MSIK and HSE oscillators are also switched off.

The SRAMs and register contents are lost except for registers in the backup domain. The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to backup domain is not supported.

I/O states in Shutdown mode

In the Shutdown mode, I/Os are by default in floating state. If the APC bit in the PWR_APCR register is set, the I/Os can be configured either with a pull-up (see PWR_PUCRx registers), or with a pull-down (see PWR_PDCRx registers), or can be kept in analog state if none of the PWR_PUCRx or PWR_PDCRx register is set. The pull-down configuration has highest priority over pull-up configuration in case both PWR_PUCRx and PWR_PDCRx are set for the same I/O. However this configuration is lost when exiting the Shutdown mode due to the power-on reset.

I3C specific pull-ups are activated thanks to PWR_I3C pull-up control registers 1 or 2. However this configuration is lost when exiting the Shutdown mode due to the power-on reset.

Some I/Os (listed in Section 12: General-purpose I/Os (GPIO) ) are used for JTAG/SW debug and can only be configured to their respective reset pull-up or pull-down state during Shutdown mode setting to 1 their respective bit in the PWR_PUCRx or PWR_PDCRx registers, or to be configured to floating state if the bit is kept at 0.

The RTC outputs on PC13 and PB2 are functional in Shutdown mode. PC14 and PC15 used for LSE are also functional. 22 wake-up pins are multiplexed on eight events (WKUPx, x = 1 to 8) and the five RTC tampers pins are available.

Entering Shutdown mode

The MCU enters the Shutdown mode as described in Entering a low-power mode , when the SLEEPDEEP bit in the Cortex-M33 system control register is set (see Table 94 for details on how to enter Shutdown mode).

In Shutdown mode, the following features can be selected by programming individual control bits:

- • The real-time clock (RTC) and Tamper (TAMP) kernel clock is enabled by the RTCEN bit in the RCC_BDCR.

Caution: In case of V DD power-down, the RTC/TAMP and backup registers content is lost.

- • The external 32.768 kHz oscillator (LSE) is configured by the LSEON bit in the backup domain control register (RCC_BDCR).

- • The I3Cx (x = 1, 2) reset pattern detection are enabled by the WUPEN9 and WUPEN10 bits in PWR_WUCR1.

Exiting Shutdown mode

The MCU exits the Shutdown mode as described in Exiting a low-power mode . A power-on reset occurs when exiting from Shutdown mode. All registers (except for the ones in the backup domain) are reset after a wake-up from Shutdown (see Table 94 for more details on how to exit Shutdown mode).

When exiting Shutdown mode, I/Os that were configured with pull-up or pull-down during Shutdown through registers PWR_PUCRx or PWR_PDCRx lose their configuration and are configured in floating state or to their pull-up pull-down reset value (for some I/Os listed in Section 12: General-purpose I/Os (GPIO) ).

Table 94. Shutdown mode

| Shutdown mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

|

| Mode exit |

|

| Wake-up latency | Reset phase |

Power mode output pins

In order to help the debug, two signals are available as device pin alternate functions:

- • PWR_CSLEEP

When set, PWR_CSLEEP indicates that the CPU is in Sleep mode: WFI or WFE has been executed.

When cleared, PWR_CSLEEP indicates that the CPU is in Run mode.

- • PWR_CSTOP

When set, PWR_CSTOP indicates that the device entered a Stop mode, and no autonomous peripheral requests its bus clock:

- • WFI or WFE has been executed with CPU SLEEPDEEP = 1.

- • No AHB/APB clock is running.

Note: The AHB/APB clocks run after WFI or WFE has been executed if an autonomous peripheral requests its bus clock in Stop mode. The peripherals bus clock request can delay or prevent the device to enter low-power modes (refer to Autonomous peripherals and Low-power modes ).

The table below explains the MCU power mode depending on these signals states.

Table 95. Power modes output states versus MCU power modes

| PWR_CSLEEP | PWR_CSTOP | MCU power mode (1) |

|---|---|---|

| 0 | 0 | Run mode |

| 1 | 0 | Sleep mode or Stop 0, Stop 1 or Stop 2 mode with AHB/APB clocks running |

| 1 | 1 | Stop 0, Stop 1 or Stop 2 mode with no AHB/APB clocks running |

1. PWR_CSLEEP and PWR_CSTOP are not driven in Stop 3, Standby and Shutdown modes.

Debug mode

By default, the debug connection is lost if the application puts the MCU in Stop 0, Stop 1, Stop 2, Stop 3, Standby or Shutdown mode while the debug features are used. This is due to the fact that the Cortex-M33 core is no longer clocked.

However, by setting some configuration bits in the DBGMCU control registers, the software can be debugged even when using the low-power modes extensively. For more details, refer to Section 57.2.5: Debug and low-power modes .

9.3.6 PWR security and privileged protection

PWR security protection

When the TrustZone security is activated by the TZEN option bit in the FLASH_OPTR register, some PWR register fields can be secured against nonsecure access.

The PWR TrustZone security allows the following features to be secured through the PWR_SECCFGR register:

- • Low-power mode

- • Wake-up (WKUP) pins

- • Voltage detection and monitoring

- • VBAT mode