7. Embedded flash memory (FLASH)

7.1 FLASH introduction

The flash memory interface manages accesses to the flash memory, maximizing throughput to the CPU, instruction cache, and DMAs. It implements the flash memory erase and program operations, as well as the read and write protection mechanisms. It also implements the security and privileged access control features. It is optimized in terms of power consumption with dedicated modes when the MCU is in low-power modes.

7.2 FLASH main features

- • Up to 2 Mbytes of flash memory supporting read-while-write capability (RWW)

- • Memory organization

- – Dual bank architecture (bank 1 and bank 2)

- – Main memory: up to 1 Mbyte per bank

- – Information block: 104.5 Kbytes

- • 64-bit wide data read with prefetch

- • Standard and burst programming modes

- • Read operations

- • Program and erase operations only in range 1

- • 10 kcycles endurance on all flash memory

- • Page erase, bank erase and mass erase (both banks)

- • Bank swapping: the user flash memory address mapping of each bank can be swapped.

- • Product security activated by TrustZone option bit (TZEN)

- • Device life cycle managed by readout protection option byte (RDP)

- • 4 write protection areas (two per bank)

- • TrustZone support:

- – 2 secure areas (1 per bank)

- – 2 secure HDP (hide protection) areas part of the secure areas (one per bank)

- – 2 secure HDP (hide protection) extension areas part of the secure areas (one per bank)

- • Configurable protection against unprivileged accesses with flash page granularity

- • Error code correction: 8-bit ECC per 64-bit double-word allowing 2-bit error detection and 1-bit error correction

- • Option-byte loader

- • Advanced low-power modes (low-power read mode, bank power-down mode)

7.3 FLASH functional description

7.3.1 Flash memory organization

The flash memory has the following main features:

- • Capacity up to 2 Mbytes

- • Dual-bank mode:

- – Up to 1 Mbyte per bank for main memory

- – 4-Kbyte page size

- – 72-bit wide data read and write (64 effective bits plus 8 ECC bits)

- – Page, bank and mass erase

The flash memory is organized as follows:

- • Main memory block organized as two banks of up to 1 Mbyte each containing up to 256 pages of 4 Kbytes

- • An information block containing:

- – 68 Kbytes for system memory. This area is immutable and reserved for use by STMicroelectronics. It contains the bootloader that is used to reprogram the flash memory through one of the user communication interfaces such as USB (DFU). The system memory is programmed by STMicroelectronics when the device is manufactured. For further details, refer to the application note STM32 microcontroller system memory boot mode (AN2606).

- – 36 Kbytes immutable secure area containing the root security services (RSS and RSS library) developed by STMicroelectronics.

- – 512-byte OTP (one-time programmable) for user data (64 double-words). The OTP data cannot be erased and can be written only once. If only one bit is at 0, the entire double-word cannot be written anymore, even with the value 0x0000 0000 0000 0000.

- – Option bytes for user configuration. Unlike user flash memory and system memory, it is not mapped to any memory address and can be accessed only through the FLASH register interface.

The memory organization is based on a main area and an information block as shown in the table below.

Table 40. Flash module 512-Kbyte dual-bank organization for STM32U356/366 (1)(2)

| Flash memory area | Flash memory address | ADDR_ECC | Size (bytes) | Name | |

|---|---|---|---|---|---|

| Main memory | Bank 1 | 0x0800 0000 - 0x0800 0FFF | 0x000000 - 0x000FFF | 4K | Page 0 |

| 0x0800 1000 - 0x0800 1FFF | 0x010000 - 0x010FFF | 4K | Page 1 | ||

| ... | ... | ... | ... | ||

| 0x0803 F000 - 0x0803 FFFF | 0x3F0000 - 0x3FFFFF | 4K | Page 63 | ||

| Bank 2 | 0x0804 0000 - 0x0804 0FFF | 0x000000 - 0x000FFF | 4K | Page 0 | |

| 0x0804 1000 - 0x0804 1FFF | 0x010000 - 0x010FFF | 4K | Page 1 | ||

| ... | ... | ... | ... | ||

| 0x0807 F000 - 0x0807 FFFF | 0x3F0000 - 0x3FFFFF | 4K | Page 63 | ||

| Flash memory area | Flash memory address | ADDR_ECC | Size (bytes) | Name | |

|---|---|---|---|---|---|

| Nonsecure information block | Bank 1 | 0x0BF8 F000 - 0x0BF9 77FF | 0x04800 - 0x0CFFF | 34K | System memory |

| Bank 2 | 0x0BF9 7800 - 0x0BF9 FFFF | 0x04800 - 0x0CFFF | 34K | ||

| Bank 1 | 0x0BFA 0000 - 0x0BFA 01FF | 0x0D000 - 0x0D1FF | 512 | OTP area | |

| Secure information block (3) | Bank 1 | 0x0FF8 0000 - 0x0FF8 3BFF | 0x00000 - 0x03BFF | 15K | RSS |

| Bank 1 | 0x0FF8 3C00 - 0x0FF8 47FF | 0x03C00 - 0x047FF | 3K | RSS library | |

| Bank 2 | 0x0FF8 4800 - 0x0FF8 8FFF | 0x00000 - 0x047FF | 18K | RSS library | |

- 1. When DUALBANK is set to 1 in the option bytes, for 256-Kbyte dual-bank STM32U356/366 devices, the base address of bank 2 is 0x0802 0000, and the total number of pages is divided by two.

- 2. When DUALBANK is set to 0 in the option bytes, for 256-Kbyte single-bank STM32U356/366 devices, the flash is addressed as a single bank, and the page numbers are continuous from 0 to 63. Set BKER = 0 to select bank 1.

- 3. The secure information block is only accessible when TrustZone is active.

| Flash memory area | Flash memory address | ADDR_ECC | Size (bytes) | Name | |

|---|---|---|---|---|---|

| Main memory | Bank 1 | 0x0800 0000 - 0x0800 0FFF | 0x00000 - 0x00FFF | 4K | Page 0 |

| 0x0800 1000 - 0x0800 1FFF | 0x01000 - 0x01FFF | 4K | Page 1 | ||

| ... | ... | ... | ... | ||

| 0x0807 F000 - 0x0807 FFFF | 0x7F000 - 0x7FFFF | 4K | Page 127 | ||

| Bank 2 | 0x0808 0000 - 0x0808 0FFF | 0x00000 - 0x00FFF | 4K | Page 0 | |

| 0x0808 1000 - 0x0808 1FFF | 0x01000 - 0x01FFF | 4K | Page 1 | ||

| ... | ... | ... | ... | ||

| 0x080F F000 - 0x080F FFFF | 0x7F000 - 0x7FFFF | 4K | Page 127 | ||

| Nonsecure information block | Bank 1 | 0x0BF8 F000 - 0x0BF9 77FF | 0x04800 - 0x0CFFF | 34K | System memory |

| Bank 2 | 0x0BF9 7800 - 0x0BF9 FFFF | 0x04800 - 0x0CFFF | 34K | ||

| Bank 1 | 0x0BFA 0000 - 0x0BFA 01FF | 0x0D000 - 0x0D1FF | 512 | OTP area | |

| Secure information block (3) | Bank 1 | 0x0FF8 0000 - 0x0FF8 3BFF | 0x00000 - 0x03BFF | 15K | RSS |

| Bank 1 | 0x0FF8 3C00 - 0x0FF8 47FF | 0x03C00 - 0x047FF | 3K | RSS library | |

| Bank 2 | 0x0FF8 4800 - 0x0FF8 8FFF | 0x00000 - 0x047FF | 18K | RSS library | |

- 1. When DUALBANK is set to 1 in the option bytes, for 512-Kbyte dual-bank STM32U375/385 devices, the base address of bank 2 is 0x0804 0000, and the total number of pages is divided by two.

- 2. When DUALBANK is set to 0 in the option bytes, for 512-Kbyte single-bank STM32U375/385 devices, the flash is addressed as a single bank, and the page numbers are continuous from 0 to 127. Set BKER = 0 to select bank 1.

- 3. The secure information block is only accessible when TrustZone is active.

Table 42. Flash module 2-Mbyte dual-bank organization for STM32U3B5/3C5 (1)(2)

| Flash memory area | Flash memory address | ADDR_ECC | Size (bytes) | Name | |

|---|---|---|---|---|---|

| Main memory | Bank 1 | 0x0800 0000 - 0x0800 0FFF | 0x000000 - 0x000FFF | 4K | Page 0 |

| 0x0800 1000 - 0x0800 1FFF | 0x010000 - 0x011FFF | 4K | Page 1 | ||

| ... | ... | ... | ... | ||

| 0x080F F000 - 0x080F FFFF | 0xFF0000 - 0xFFFFF | 4K | Page 255 | ||

| Bank 2 | 0x0810 0000 - 0x0810 0FFF | 0x000000 - 0x000FFF | 4K | Page 0 | |

| 0x0810 1000 - 0x0810 1FFF | 0x010000 - 0x011FFF | 4K | Page 1 | ||

| ... | ... | ... | ... | ||

| 0x081F F000 - 0x081F FFFF | 0xFF0000 - 0xFFFFF | 4K | Page 255 | ||

| Nonsecure information block | Bank 1 | 0x0BF8 F000 - 0x0BF9 77FF | 0x04800 - 0x0CFFF | 34K | System memory |

| Bank 2 | 0x0BF9 7800 - 0x0BF9 FFFF | 0x04800 - 0x0CFFF | 34K | ||

| Bank 1 | 0x0BFA 0000 - 0x0BFA 01FF | 0x0D000 - 0x0D1FF | 512 | OTP area | |

| Secure information block (3) | Bank 1 | 0x0FF8 0000 - 0x0FF8 3BFF | 0x00000 - 0x03BFF | 15K | RSS |

| Bank 1 | 0x0FF8 3C00 - 0x0FF8 47FF | 0x03C00 - 0x047FF | 3K | RSS library | |

| Bank 2 | 0x0FF8 4800 - 0x0FF8 8FFF | 0x00000 - 0x047FF | 18K | RSS library | |

- 1. When DUALBANK is set to 1 in the option bytes, for 1-Mbyte dual-bank STM32U3B5/3C5 devices, the base address of bank 2 is 0x0808 0000, and the total number of pages is divided by two.

- 2. When DUALBANK is set to 0 in the option bytes, for 1-Mbyte single-bank STM32U3B5/3C5 devices, the flash is addressed as a single bank, and the page numbers are continuous from 0 to 255. Set BKER = 0 to select bank 1.

- 3. The secure information block is only accessible when TrustZone is active.

7.3.2 Error code correction (ECC)

Data in flash memory are 72-bit words: 8 bits are added per double-word (64-bit). The ECC mechanism supports:

- • One error detection and correction

- • Two errors detection

When one error is detected and corrected, the ECCC flag (ECC correction) is set in FLASH_ECCCORR. If the ECCCIE bit is set, an interrupt is generated.

When two errors are detected, the ECCD flag (ECC detection) is set in FLASH_ECCDETR. In this case, a NMI is generated.

When an ECCC (respectively ECCD) error is detected, the address of the failing double-word and its associated bank are saved in ADDR_ECC[19:0] and BK_ECC in FLASH_ECCCORR (respectively FLASH_ECCDETR). ADDR_ECC[2:0] are always cleared.

When ECCC (respectively ECCD) is set, ADDR_ECC[19:0] and BK_ECC are not updated if a new ECCC (respectively ECCD) error occurs. FLASH_ECCCORR (respectively FLASH_ECCDETR) is updated only when ECCC (respectively ECCD) flags are cleared.

Note: For an erased flash line, one error is detected and corrected but two errors detection is not supported. When an ECC error is reported, a new read at the failing address may not

generate an ECC error if the data is still present in the current buffer, even if ECCC and ECCD are cleared. As the ECC interface is shared by the two banks, if the same error is registered simultaneously, a physical bank 1 error is registered. Both errors are registered if one bank reports ECCD and the other bank ECCC.

The following addresses in the system flash memory are used to store words including ECC errors to allow run-time tests by software on ECC correction detection capability:

- • 0x0BFA 0F00 (embeds a word with 1-bit error)

- • 0x0BFA 0F80 (embeds a word with 2-bit error)

In case the second address is read, for instance by the debugger memory viewer, a NMI is generated.

7.3.3 Read access latency

To correctly read data from flash memory, the number of wait states (latency) must be correctly programmed in FLASH_ACR, according to the frequency of the CPU clock (HCLK) and the internal voltage range of the device \( V_{CORE} \) (refer to Dynamic voltage scaling management in PWR section).

The table below shows the correspondence between wait states and CPU clock frequency.

Table 43. Number of wait states according to CPU clock (HCLK) frequency (LPM = 0)

| Wait states (WS) (latency) | HCLK (MHz) | ||

|---|---|---|---|

| \( V_{CORE} \) range 1 | \( V_{CORE} \) range 2 | ||

| STM32U356/366 STM32U375/385 | STM32U3B5/3C5 | ||

| 0 WS (1 CPU cycle) | \( \leq 32 \) | \( \leq 25 \) | \( \leq 16 \) |

| 1 WS (2 CPU cycles) | \( \leq 64 \) | \( \leq 50 \) | \( \leq 32 \) |

| 2 WS (3 CPU cycles) | \( \leq 96 \) | \( \leq 75 \) | \( \leq 48 \) |

| 3 WS (4 CPU cycles) | NA | \( \leq 96 \) | NA |

The flash memory supports a low-power read mode when setting the LPM bit in FLASH_ACR. The table below shows the correspondence between wait states and CPU clock frequency when LPM bit is set.

Table 44. Number of wait states according to CPU clock (HCLK) frequency (LPM = 1)

| Wait states (WS) (latency) | HCLK (MHz) | |

|---|---|---|

| \( V_{CORE} \) range 1 | \( V_{CORE} \) range 2 | |

| 0 WS (1 CPU cycle) | \( \leq 20 \) | \( \leq 16 \) |

| 1 WS (2 CPU cycles) | \( \leq 40 \) | \( \leq 32 \) |

| 2 WS (3 CPU cycles) | \( \leq 60 \) | \( \leq 48 \) |

| 3 WS (4 CPU cycles) | \( \leq 80 \) | NA |

| 4 WS (5 CPU cycles) | \( \leq 96 \) | NA |

After reset, the CPU clock frequency is 12 MHz, 1 wait state (WS) is configured in FLASH_ACR, and the normal read mode is selected (LPM = 0).

Instruction prefetch

The Cortex-M33 fetches instructions and literal pools (constants/data) over the C-bus and through the instruction cache if it is enabled. The prefetch block aims at increasing the efficiency of C-bus accesses in case the instruction cache is enabled, by reducing the cache refill latency. Prefetch is efficient in case of sequential code. Prefetch in the flash memory allows the next sequential instruction line to be read from the flash memory while the current instruction line is being filled in instruction cache and executed by the CPU.

Prefetch is enabled by setting the PRFTEN bit in FLASH_ACR. This bit must be set only if at least 1 wait state is needed to access the flash memory.

Note: Prefetch tends to increase the code execution performance at the cost extra flash memory accesses. It must be used carefully in low-power applications.

When changing the CPU frequency, the software sequences detailed below must be applied in order to tune the number of wait states needed to access the flash memory.

Increase the CPU frequency

- 1. Program the new number of wait states to the LATENCY bits in FLASH_ACR.

- 2. Check that the new number of wait states is taken into account to access the flash memory by reading back FLASH_ACR.

- 3. Modify the CPU clock source by writing the SW bits in RCC_CFGR1.

- 4. Modify the CPU clock prescaler, if needed, by writing the HPRE bits in RCC_CFGR2.

- 5. Check that the new CPU clock source or/and the new CPU clock prescaler value is/are taken into account, by reading the clock source status (SWS bits) or/and the AHB prescaler value (HPRE bits), respectively, in RCC_CFGR1 and RCC_CFGR2.

Decrease the CPU frequency

- 1. Modify the CPU clock source by writing the SW bits in RCC_CFGR1.

- 2. Modify the CPU clock prescaler, if needed, by writing the HPRE bits in RCC_CFGR2.

- 3. Check that the new CPU clock source or/and the new CPU clock prescaler value is/are taken into account by reading the clock source status (SWS bits) or/and the AHB prescaler value (HPRE bits), respectively, in RCC_CFGR1 and RCC_CFGR2.

- 4. Program the new number of wait states to the LATENCY bits in FLASH_ACR.

- 5. Check that the new number of wait states is used to access the flash memory by reading back FLASH_ACR.

The software sequences detailed below must be applied in order to modify the read mode.

From normal read mode to low-power read mode

- 1. Set the LPM bit in FLASH_ACR.

- 2. Check that the low-power read mode is activated by reading FLASH_ACR.

From low-power read mode to normal read mode

- 1. Reset the LPM bit in FLASH_ACR.

- 2. Check that the normal read mode is activated by reading FLASH_ACR.

7.3.4 Bank power-down mode

After reset, both banks are in normal mode. In order to reduce power consumption, each bank can be independently put in power-down mode by setting the PDREQx bit in FLASH_ACR.

Request entry in power-down mode for bank x

- 1. Check that bank x is not in power-down mode and no request to put it in power-down mode is pending (PDx bit in FLASH_SR and PDREQx bit in FLASH_ACR must be reset).

- 2. Unlock FLASH_PDKEYxR with correct keys.

- 3. Set the PDREQx bit in FLASH_ACR.

- 4. Check that the PDx bit in FLASH_SR is set. The PDREQx bit in FLASH_ACR is automatically reset, and FLASH_PDKEYxR is locked.

Note: If bank x is currently being accessed, the power-down request is delayed until the access is completed.

Requesting power-down entry for a bank already in power-down mode has no effect. The PDREQx bit in FLASH_ACR is automatically reset and FLASH_PDKEYxR is locked.

Return to normal mode

Any access to a bank in power-down mode automatically wakes up the bank. A penalty of 5 µs minimum is taken to wake up the bank.

Wake up bank 1 (respectively bank 2) is done in one of the following cases:

- • Upon a valid read access to bank 1 (resp. bank 2)

- • Upon a valid write access to bank 1 (resp. bank 2)

- • Upon a valid bank erase on bank 1 (resp. bank 2)

Waking up both bank 1 and bank 2 is done in one of the following cases:

- • Upon a valid mass erase

- • Upon an option-byte modification

- • Upon an option-byte loading

- • Upon system reset

Note: The software can reduce the flash bank wake-up time by enabling HSI16 before waking up the bank.

7.3.5 Flash memory program and erase operations

The embedded flash memory can be programmed using in-circuit programming or in-application programming.

The in-circuit programming (ICP) method is used to update the entire contents of the flash memory, using the JTAG, SWD protocol, or the bootloader to load the user application into the MCU. The ICP offers quick and efficient design iterations, and eliminates unnecessary package handling or socketing of devices.

In contrast to the ICP method, the in-application programming (IAP) can use any communication interface supported by the microcontroller (such as I/Os, USB, CAN, UART, I2C, or SPI) to download programming data into the memory. The IAP can be used to

reprogram the flash memory while the application is running. Nevertheless, part of the application must have been previously programmed in the flash memory using ICP.

An ongoing flash memory operation does not block the CPU as long as the CPU does not access the same flash memory bank. Code or data fetches are possible on one bank while a write/erase operation is performed to the other bank (refer to Section 7.3.9 ).

On the contrary, during a program/erase operation to the flash memory, any attempt to read the same flash memory bank stalls the bus. The read operation proceeds correctly once the program/erase operation has been completed.

The MCU supports TrustZone that defines secure and nonsecure areas in the flash memory. All program and erase operations can be performed in secure mode through secure registers, or in nonsecure mode through nonsecure registers (refer to Section 7.5 ).

Program, erase and option change operations are only allowed in range 1. An error is reported when these operations are launched in range 2.

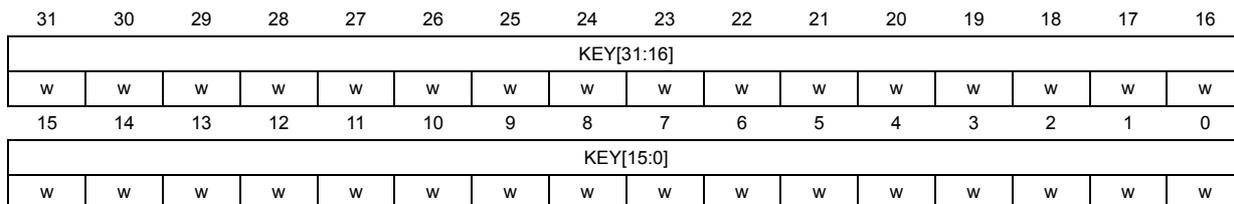

Unlock the secure/nonsecure flash control registers

After reset, write is not allowed in flash control registers (FLASH_SCR and FLASH_CR) in order to protect the flash memory against possible unwanted operations due (for example, electric disturbances).

The following sequence is used to unlock these registers:

- 1. Write KEY1 = 0x4567 0123 in FLASH_SKEYR or FLASH_KEYR.

- 2. Write KEY2 = 0xCDEF 89AB in FLASH_SKEYR or FLASH_KEYR.

Any wrong sequence locks up FLASH_SCR or FLASH_CR until the next system reset. In the case of a wrong key sequence, a bus error is detected and a hard fault interrupt is generated.

FLASH_CR (resp. FLASH_SCR) can be locked again by software by setting the LOCK bit in FLASH_CR (resp. FLASH_SCR).

Note: FLASH_CR and FLASH_SCR cannot be written when the BSY bits are set. Any attempt to write them with the BSY bits set, causes the AHB bus to stall until the BSY bits are cleared.

Wait for data-to-write flags (WDW)

WDW flags in FLASH_SR and FLASH_SSR are both set when a secure or nonsecure write access has been done in the write buffer. They are cleared when the BSY flags are set (meaning that the write buffer is freed and the programming operation actually starts in the flash memory), or in case of error.

It is software responsibility to ensure that the two words in the same double-word are all written.

FLASH secure and nonsecure busy flags

BSY flags in FLASH_SR and FLASH_SSR are both set when a secure or nonsecure flash operation is started:

- • Erase operation: setting the STRT bit in FLASH_CR or FLASH_SCR

- • Write operation: setting the PG bit in FLASH_CR or FLASH_SCR and writing a double-word in the flash memory

- • Option-byte programming: setting the OPTSTRT (in FLASH_CR)

7.3.6 Flash main memory erase sequences

The flash memory erase operation can be performed at page level, bank level or on the whole flash memory (mass erase). Mass erase does not affect the information block (system flash, OTP and option bytes). The erase operation is either secure or nonsecure.

Page erase

To erase a page, follow the procedure below:

- 1. Check that voltage range is set to range 1.

- 2. Check that no flash memory operation is ongoing by checking the BSY bit and that the write buffer is empty by checking the WDW bit in the FLASH_SR or FLASH_SSR.

- 3. Check and clear all error programming flags due to a previous programming. If not, PGSERR is set.

- 4. Set the PER bit and select the page to erase (PNB) with the associated bank (BKER) in FLASH_CR or FLASH_SCR.

- 5. Set the STRT bit in FLASH_CR or FLASH_SCR. Set the STRT by privilege code if targeted page is privileged.

- 6. Wait for the BSY bit to be cleared in FLASH_SR or FLASH_SSR.

- 7. Clear PER in FLASH_CR or FLASH_SCR if there is not anymore page erase request.

Bank 1 or bank 2 mass erase

To perform a bank mass erase, follow the procedure below:

- 1. Check that voltage range is set to range 1.

- 2. Check that no flash memory operation is ongoing by checking the BSY bit. Check that the write buffer is empty by checking the WDW bit in FLASH_SR or FLASH_SSR.

- 3. Check and clear all error programming flags due to a previous programming. If not, PGSERR is set.

- 4. Set the MER1 or MER2 bit (depending on the bank) in FLASH_CR or FLASH_SCR. Both banks can be selected in the same operation. In that case, it corresponds to a mass erase.

- 5. Set the STRT bit in FLASH_CR or FLASH_SCR. Set the STRT by privilege code if targeted banks are privileged.

- 6. Wait for the BSY bit to be cleared in FLASH_SR or FLASH_SSR.

- 7. The MER1 or MER2 bits can be cleared if no more bank erase is requested.

Mass erase

To perform a mass erase, follow the procedure below:

- 1. Check that voltage range is set to range 1.

- 2. Check that no flash memory operation is ongoing by checking the BSY bit. Check that the write buffer is empty by checking the WDW bit in FLASH_SR or FLASH_SSR.

- 3. Check and clear all nonsecure error programming flags due to a previous programming. If not, the PGSERR bit is set.

- 4. Set the MER1 bit and MER2 bits in FLASH_CR or FLASH_SCR.

- 5. Set the STRT bit in the FLASH_CR or FLASH_SCR.

- 6. Wait for the BSY bit to be cleared in the FLASH_SR or FLASH_SSR.

- 7. The MER1 and MER2 bit can be cleared if no more mass erase is requested.

Note: The internal oscillator HSI16 (16 MHz) is enabled automatically when the STRT bit is set, and disabled automatically when the STRT bit is cleared, except if the HSI16 is previously enabled with HSION in RCC_CR.

To erase a page, a bank or to perform a mass erase, software must have sufficient privilege (see Table 67 and Table 68 ).

STRT bit is cleared automatically at the end of erase or in case of error.

7.3.7 Flash memory programming sequences

The flash memory is programmed 72 bits at a time (64-bit data + 8-bit ECC).

Programming in a previously programmed address is not allowed except if the data to write is full zero, and any attempt sets the PROGERR flag in FLASH_SR or FLASH_SSR.

It is only possible to program double-word ( \( 2 \times 32 \) -bit data):

- • Any attempt to write byte or half-word sets the SIZERR flag in FLASH_SR or FLASH_SSR.

- • Any attempt to write a double-word that is not aligned with a double-word address sets the PGAERR flag in FLASH_SR or FLASH_SSR.

Flash programming

The flash memory programming sequence is as follows:

- 1. Check that voltage range is set to range 1.

- 2. Check that no flash main memory operation is ongoing by checking the BSY bit in FLASH_SR or FLASH_SSR.

- 3. Check that the write buffer is empty by checking the WDW bit in FLASH_SR or FLASH_SSR.

- 4. Check and clear all error programming flags due to a previous programming. If not, PGSERR is set.

- 5. Set the PG bit in FLASH_CR or FLASH_SCR.

- 6. Perform the data write operation at the desired flash memory address, or in the OTP area. Only a double-word can be programmed and OTP can be only programmed in nonsecure access:

- – Write a first word at a double-word address boundary. The WDW bits in FLASH_SR and FLASH_SSR are set to indicate that more data can be written in the write buffer.

- – Write the second word in the same double-word.

- 7. The BSY bit gets set. WDW is reset automatically.

- 8. Wait until the BSY bit is cleared in FLASH_SR or FLASH_SSR. Software must make sure that BSY is set or WDW is cleared before waiting for BSY to get cleared.

- 9. If the EOP flag is set in FLASH_SR or FLASH_SSR (meaning that the programming operation has succeeded, and the EOPIE bit is set), it must be cleared by software.

- 10. Clear the PG bit in FLASH_CR or FLASH_SCR if there are no more programming requests.

- 11. Clear PG bit in FLASH_CR or FLASH_SCR if there is no more programming request.

Note: When the flash memory interface receives a good sequence (a double-word), programming is automatically launched and the BSY bits are set. The internal oscillator HSI16 (16 MHz) is

enabled automatically when the PG bit is set, and disabled automatically when the PG bit is cleared, except if the HSI16 is previously enabled with HSION in RCC_CR.

No option-byte modification nor erase request is allowed when the WDW bit is set.

Programming is possible only if the privileged and security attributes are respected (refer to Section 7.8 ).

If the user needs to program only one word, the double-word must be completed with the erase value 0xFFFF FFFF to launch automatically the programming.

ECC is calculated from the double-word to program.

The OTP data cannot be erased and are writable only once. If only one bit is at 0, the entire double word is not writable anymore, even with the value 0x0.

It is only possible to write one bank/cut after the other .

Flash burst programming (16 double-words)

The flash memory burst programming sequence is as follows:

- 1. Check that voltage range is set to range 1.

- 2. Check that no flash main memory operation is ongoing by checking the BSY bit in FLASH_SR or FLASH_SSR.

- 3. Check that the write buffer is empty by checking the WDW bit in FLASH_SR or FLASH_SSR.

- 4. Check and clear all error programming flags due to a previous programming. If not, PGSERR is set.

- 5. Set the BWR and PG bits in FLASH_CR or FLASH_SCR.

- 6. Perform the data write operation at the desired flash memory address, or in the OTP area. Only 16 double-words can be programmed:

- – Write a first 32-bit word in an address aligned on a 16 double-word address (multiple of 0x80). The WDW bits in FLASH_SR and FLASH_SSR are set to indicate that more data can be written in the write buffer.

- – Write the 31 other 32-bit words consecutively.

- 7. The BSY bit gets set. WDW is reset automatically.

- 8. Wait until the BSY bit is cleared in FLASH_SR or FLASH_SSR. Software must make sure that BSY is set or WDW is cleared before waiting for BSY to get cleared.

- 9. If the EOP flag is set in FLASH_SR or FLASH_SSR (meaning that the programming operation has succeeded and the EOPIE bit is set), it has to be cleared by software.

- 10. Clear the BWR and PG bits in FLASH_CR or FLASH_SCR if there is no more programming request.

Note: When the flash memory interface receives a good sequence, programming is automatically launched and the BSY bits are set. The internal oscillator HSI16 (16 MHz) is enabled automatically when the PG bit is set, and disabled automatically when the PG bit is cleared, except if the HSI16 is previously enabled with HSION in RCC_CR.

No option-byte modification nor erase request is allowed when the WDW bit is set.

Programming is possible only if the privileged and security attributes are respected (refer to Section 7.8 ).

7.3.8 Flash memory errors flags

Flash programming errors

Several types of errors can be detected during secure and nonsecure operations. In case of error, the flash memory operation (programming or erasing) is aborted.

The secure errors flags are only set during a secure operation and nonsecure flags are only set during a nonsecure operation.

All error flags linked to an operation error have the effect to flush the write buffer.

- • PROGERR : secure/nonsecure programming error

It is set when the word to program is pointing to an address:

- – Not previously erased

- – Already fully programmed to 0

- – Already partially programmed (contains 0 and 1) and the new value to program is not full zero

- – For OTP programming, when the address is already partially programmed (contains 0 and 1)

- • SIZERR : secure/nonsecure size programming error

Only 32-bit data can be written. SIZERR flag is set if a byte or a half-word is written.

- • PGAERR : secure/nonsecure alignment programming error

It is set when the first word to be programmed is not aligned with a double-word address, or the second word does not belong to the same double-word address.

For burst programming, it is set when the first word to be programmed is not aligned on a 16 × double-word address or if the following word writes are not done at consecutive 32-bit addresses.

- • PGSERR : programming sequence error

It is set if one of the following conditions occurs during an erase, program, or option change programming operation:

- – A data is written when PG is cleared.

- – A program operation is requested during erase: PG is set while MER1 or MER2 or PER is set.

- – In the erase sequence, PG is set while STRT is already set.

- – In the erase sequence, if STRT is set while MER1 and MER2 and PER are cleared.

- – If page and mass erase are requested at the same time, STRT and PER are set while MER1 or MER2 is set.

- – If an operation is started while the write buffer is waiting for the next data, STRT or OPTSTRT is set while WDW is already set.

- – If STRT and OPTSTRT are set at the same time.

- – A nonsecure PGSERR is set if the non secure STRT bit is set by a secure access.

- – An erase, program, or option-byte programming (OPTSTRT) operation is launched while voltage range is set to range 2.

- – A secure PGSERR is set if PROGERR, SIZERR, PGAERR, WRPERR, or PGSERR is already set due to a previous programming error.

- – A nonsecure PGSERR is set if PROGERR, SIZERR, PGAERR, WRPERR, PGSERR, or OPTWERR is already set due to a previous programming error.

- • WRPERR : write protection error

- • OPTWERR : option-byte write error

It is set if when user option bytes are modified with an invalid configuration. It is set when attempting:

- – To program an invalid secure watermark-based area (refer to Table 48 )

- – To set or clear the TZEN option bit when RDP is not at correct level (refer to Rules for modifying specific option bytes )

- – To clear the BOOT_LOCK option bit when RDP is not at correct level (refer to Rules for modifying specific option bytes )

- – To modify SWAP_BANK option bit while BOOT_LOCK and TZEN are set

- – To modify ADD option bit (in FLASH_SBOOT0R) while BOOT_LOCK is set

- – To modify DUALBANK option bit while BOOT_LOCK and TZEN are set

- – To modify SECWM1Rx (resp. SECWM2Rx) in one of the following conditions:

- - while HDP1 (resp. HDP2) area access is disabled (HDP1_ACCDIS, resp. HDP2_ACCDIS, is different than 0xA3)

- - while HDP1 (resp. HDP2) extension area access is disabled (HDP1EXT_ACCDIS, resp. HDP2EXT_ACCDIS, is different than 0xA3).

- – To modify the option bytes, except the SWAP_BANK option bit, when RDP is set to two

- – To regress from RDP level 0.5 to RDP level 0

- – To modify OEM1KEYRx while RDP level is 0.5 or 1 and OEM1LOCK bit is set

- – To modify OEM2KEYRx while RDP level is 1 and OEM2LOCK bit is set

- – To regress from RDP level 1 to RDP level 0 while OEM1LOCK bit is set and a wrong OEM1KEY is shifted through JTAG or SWD

- – To regress from RDP level 1 to RDP level 0.5 while OEM2LOCK bit is set and a wrong OEM2KEY is shifted through JTAG or SWD

- – To program OEM1KEY with less than five zero.

- – To program OEM2KEY with less than five zero

- – To modify WRPxyR while its UNLOCK bit is cleared

- – To set the UNLOCK bit in the WRPxyR when RDP is not at correct level (refer to Rules for modifying specific option bytes )

If an error occurs during a secure or nonsecure program or erase operation, one of the following programming error flags is set:

- • Nonsecure programming error flags: PROGERR, SIZERR, PGAERR, PGSERR, OPTWRERR, or WRPERR is set in FLASH_SR.

- • If the nonsecure error interrupt enable bit ERRIE is set in FLASH_CR, an interrupt is generated and the operation error flag OPERR is set in FLASH_SR.

- • Secure programming error flags: PROGERR, SIZERR, PGAERR, PGSERR, or WRPERR is set in FLASH_SSR.

If the secure error interrupt enable bit ERRIE is set in FLASH_SCR, an interrupt is generated and the operation error flag OPERR is set in FLASH_SSR.

Note:

If several successive errors are detected (for example, DMA transfer to the flash memory), the error flags cannot be cleared until the end of the successive write requests.

Any programming error flushes the write buffer.

7.3.9 Read-while-write (RWW)

The flash memory is divided into two banks allowing read-while-write operations. This feature allows a read operation to be performed from one bank while erase or program operation is performed to the other bank.

Note: Write-while-write operations are not allowed. As an example, it is not possible to perform an erase operation on one bank while programming the other one.

Read from bank 1 while page erasing in bank 2 (or vice versa)

While executing a program code from bank 1, it is possible to perform a page erase operation on bank 2 (and vice versa).

Read from bank 1 while mass erasing bank 2 (or vice versa)

While executing a program code from bank 1, it is possible to perform a mass erase operation on bank 2 (and vice versa).

Read from bank 1 while programming bank 2 (or vice versa)

While executing a program code from bank 1, it is possible to perform a program operation on bank 2 (and vice versa).

Note: Due to the Cortex-M33 unified C-bus, user software must ensure to not stall C-bus with multiple consecutive writes. It is recommended to wait for the BSY flag to be cleared before programming the next double-word.

7.3.10 Power-down during flash programming or erase operation

The contents of the flash memory currently being accessed are not guaranteed if a power-down occurs during a flash memory program or erase operation.

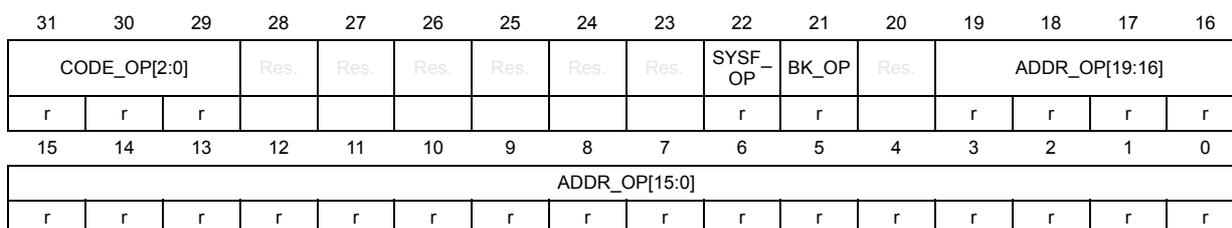

7.3.11 Reset during flash programming or erase operation

The contents of the flash memory currently being accessed are not guaranteed if a reset occurs during a flash memory program or erase operation. The status of the flash memory can be recovered from FLASH_OPSR when a system reset occurs during a flash memory program or erase operation.

It is software responsibility to check the status of the flash memory and to take corrective actions. This must be done after each system reset before any other programming or erase operation is performed.

The table below describes the corrective action to be taken according to the status provided in the CODE_OP field of the FLASH_OPSR.

Table 45. Flash operation interrupted by a system reset

| CODE_OP | Operation interrupted | Address | Bank | System flash | Corrective action |

|---|---|---|---|---|---|

| 0x0 | No operation | Reserved | None | ||

| 0x1 | Single write | ADDR_OP | BK_OP | SYSF_OP | Page erase and single write at same location |

| 0x2 | Burst Write | ADDR_OP | BK_OP | SYSF_OP | Page erase and burst write at same location |

| 0x3 | Page erase | ADDR_OP | BK_OP | Reserved | Erase same page |

| 0x4 | Bank erase | Reserved | BK_OP | Reserved | Erase same bank |

| 0x5 | Mass erase | Reserved | Mass erase | ||

| 0x6 | Option change | Reserved | Option change | ||

| 0x7 | Reserved | ||||

Note: For single and burst write, it is mandatory to perform a page erase because the current flash memory locations may no longer be writable. Consequently, the remaining page content must be saved before page erase and restored afterwards.

For OTP write, it is not possible to perform a page erase. The OTP double-word is lost.

For burst write, ADDR_OP gives the first address of burst. The user must restart the same burst operation. For page erase, ADDR_OP gives the first address of erased page.

7.4 FLASH option bytes

7.4.1 Option-byte description

The option bytes are configured by the end user depending on the application requirements. As a configuration example, the watchdog can be selected in hardware or software mode (refer to Section 7.4.2 ). The user option bytes are accessible through the flash memory registers.

Table 46 describes the organization of all user option bytes available in the flash memory registers.

Table 46. User option-byte organization mapping

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Register FLASH_ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| TZEN | IO_VDDIO2_HSLV | IO_VDD_HSLV | Res. | NBOOT0 | NSWBOOT0 | SRAM2_RST | SRAM2_PE | SRAM3_PE | Res. | DUALBANK | SWAP_BANK | WWDG_SW | IWDG_STDBY | IWDG_STOP | IWDG_SW | SRAM_RST | NRST_SHDW | NRST_STDBY | NRST_STOP | BDRST_POR. | BOR_LEV[2:0] | RDP | OPTR | |||||||||

| TZEN | IO_VDDIO2_HSLV | IO_VDD_HSLV | Res. | NBOOT0 | NSWBOOT0 | SRAM2_RST | SRAM2_PE | BL_IO_VDDIO2_HSLV [1:0] | DUALBANK | SWAP_BANK | WWDG_SW | IWDG_STDBY | IWDG_STOP | IWDG_SW | SRAM_RST | NRST_SHDW | NRST_STDBY | NRST_STOP | BDRST_POR. | BOR_LEV[2:0] | RDP | OPTR [alternate] STM32U375/ 385 only | ||||||||||

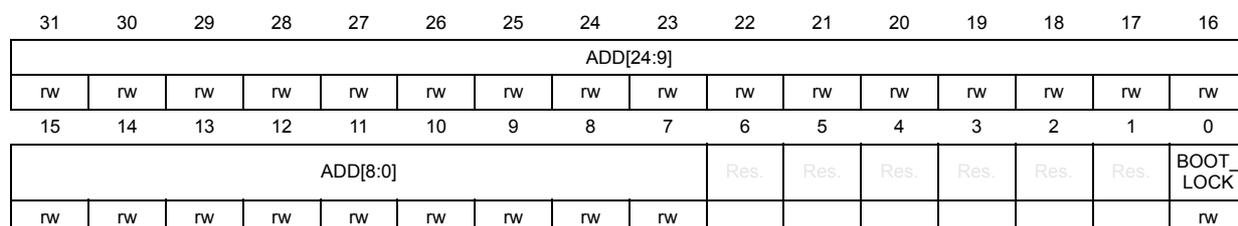

| ADD[24:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | BOOT0R | ||||||||||||||||||||||||

| ADD[24:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | BOOT1R | ||||||||||||||||||||||||

| ADD[24:0] | Res. | Res. | Res. | Res. | Res. | Res. | BOOT_LOCK | SBOOT0R | ||||||||||||||||||||||||

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM1_END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM1_STRT [7:0] | SECWM1R1 | ||||||||||||||

| HDP1EN | HDP1_END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM1R2 | ||||||||||||||||||||||

| UNLOCK | Res. | Res. | Res. | Res. | Res. | Res. | Res. | END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | STRT[7:0] | WRP1AR | ||||||||||||||

| UNLOCK | Res. | Res. | Res. | Res. | Res. | Res. | Res. | END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | WRP1BR | |||||||||||||||

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM2_END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM2_STRT [7:0] | SECWM2R1 | ||||||||||||||

| HDP2EN | HDP2_END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM2R2 | ||||||||||||||||||||||

| UNLOCK | Res. | Res. | Res. | Res. | Res. | Res. | Res. | END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | STRT[7:0] | WRP2AR | ||||||||||||||

| UNLOCK | Res. | Res. | Res. | Res. | Res. | Res. | Res. | END[7:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | WRP2BR | |||||||||||||||

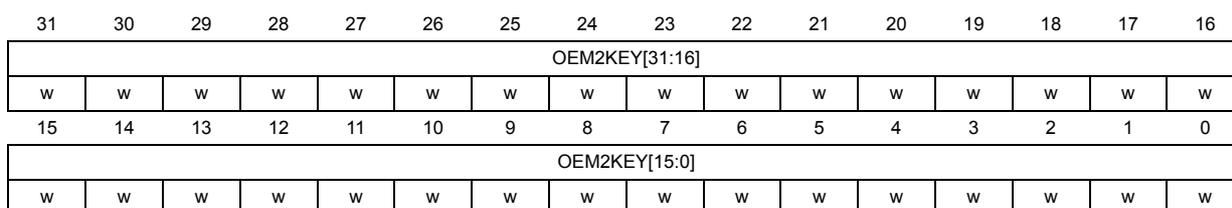

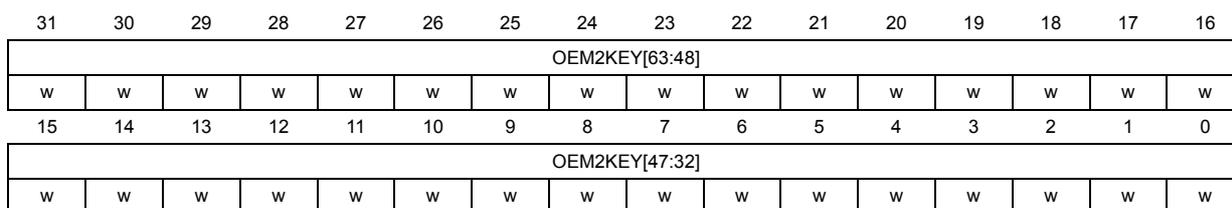

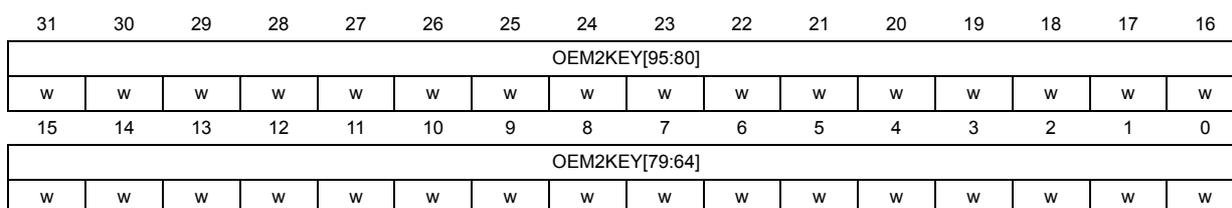

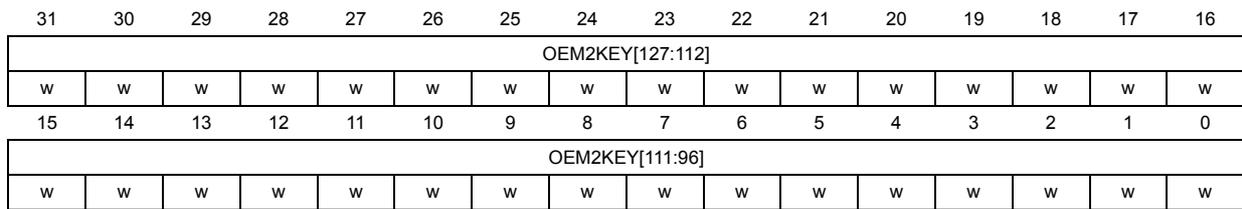

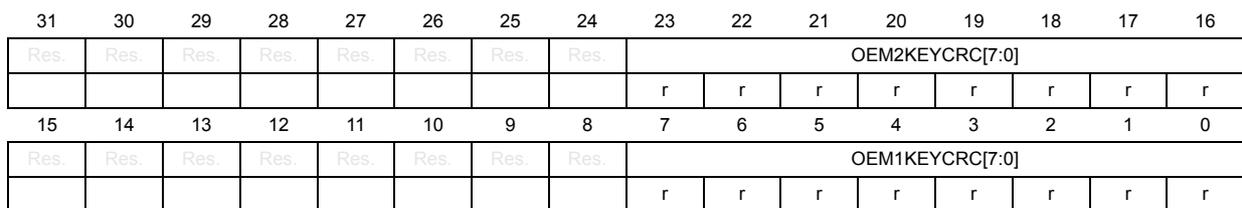

Table 46. User option-byte organization mapping (continued)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Register FLASH_ |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

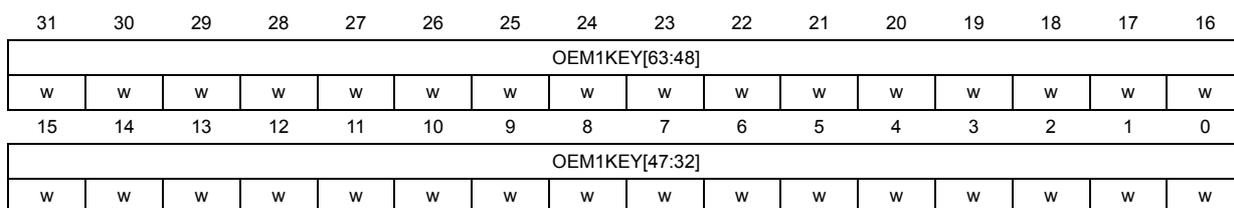

| OEM1KEY[31:0] | OEM1KEYRx | |||||||||||||||||||||||||||||||

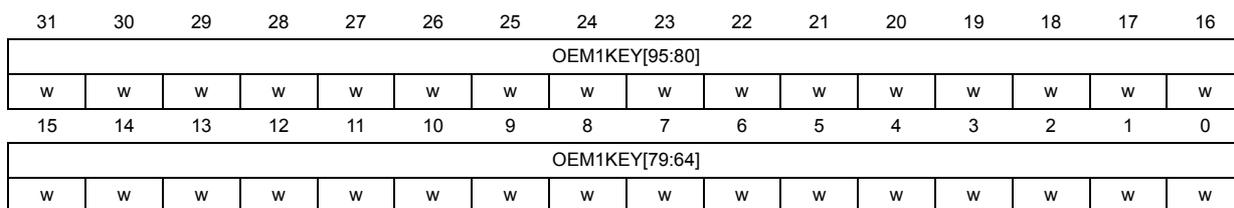

| OEM1KEY[63:32] | ||||||||||||||||||||||||||||||||

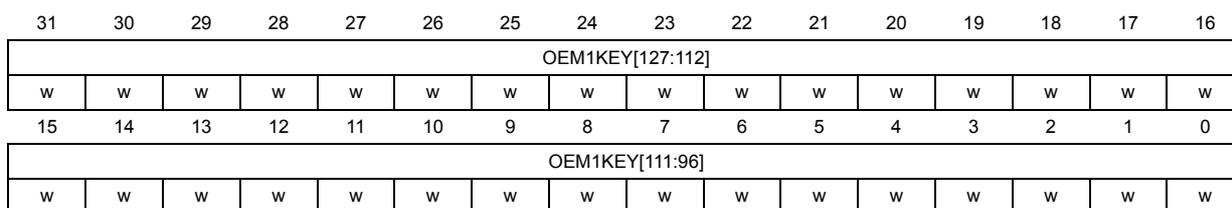

| OEM1KEY[95:64] | ||||||||||||||||||||||||||||||||

| OEM1KEY[127:96] | ||||||||||||||||||||||||||||||||

| OEM2KEY[31:0] | OEM2KEYRx | |||||||||||||||||||||||||||||||

| OEM2KEY[63:32] | ||||||||||||||||||||||||||||||||

| OEM2KEY[95:64] | ||||||||||||||||||||||||||||||||

| OEM2KEY[127:96] | ||||||||||||||||||||||||||||||||

7.4.2 Option-byte programming

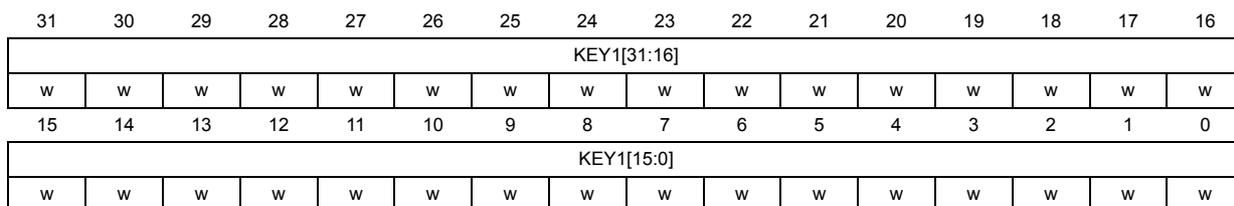

Unlocking option control register

After reset, the options related to the operation bits OPTSTRT and OBL_LAUNCH in FLASH_CR, are write-protected. To run any operation on the option-byte page, the option lock bit OPTLOCK in FLASH_CR must be cleared.

The option-byte programming (OPTSTRT) can only be launched in range 1.

The following sequence is used to unlock OPTSTRT and OBL_LAUNCH bits:

- 1. Unlock the FLASH_CR register with the LOCK clearing sequence (refer to Unlock the secure/nonsecure flash control registers ).

- 2. Write KEY1 = 0x08192A3B in FLASH_OPTKEYR.

- 3. Write KEY2 = 0x4C5D6E7F in FLASH_OPTKEYRR.

The user options can be protected against unwanted erase/program operations by setting the OPTLOCK bit by software.

Note: If the LOCK bit in FLASH_CR is set by software, OPTLOCK is automatically set too.

Option-byte modification sequence

To modify the user options value, follow the procedure below:

- 1. Check that voltage range is set to range 1.

- 2. Check that no flash memory operation is ongoing by checking the BSY bit. Check that the write buffer is empty by checking the WDW bit in FLASH_SR.

- 3. Clear OPTLOCK option lock bit with the clearing sequence described above.

- 4. Clear all nonsecure error flags due to a previous operation

- 5. Write the desired options value in the options registers.

- 6. Set the option start bit OPTSTRT in FLASH_CR.

- 7. Wait for the BSY bit to be cleared.

- 8. Set the OBL_LAUNCH option bit to start option-byte loading.

Note: If the OPTWERR or PGSERR error bit is set, the old option-byte values are kept.

Option-byte loading

After the BSY bit is cleared, all new options are updated into the flash memory but they are not applied to the system. They affect the system when they are loaded. Option-byte loading (OBL) is performed in two cases:

- • When OBL_LAUNCH bit is set in FLASH_CR

- • After a power reset (BOR reset or exit from Standby/Shutdown modes)

On system reset rising, internal option registers are copied into option registers. These registers are also used to modify the option bytes. If these registers are not modified by the user, they reflect the option state of the system.

Rules for modifying specific option bytes

Some of the option-bytes must respect specific rules before being updated with new values. These option bytes, as well as the associated constraints, are described below:

- • TZEN option bit

- – TZEN can only be set on RDP level 0.

- – Deactivation of TZEN is only possible when RDP is changing from level 1 to 0.

- • BOOT_LOCK option bit

- – BOOT_LOCK has only effect when TZEN is set.

- – BOOT_LOCK can be set without any constraint.

- – Deactivation of BOOT_LOCK is only possible when RDP is level 0.

- • SWAP_BANK option bit

- – It cannot be modified when BOOT_LOCK and TZEN option bits are set.

- • ADD (in FLASH_SBOOT0R) option bytes

- – It cannot be modified when BOOT_LOCK option bit is set.

- • DUALBANK option bit

- – It cannot be modified when BOOT_LOCK and TZEN option bits are set.

- • SECWMxRy option bits

- – It is not possible to modify secure (SECWMx_STRT[7:0] and SECWMx_END[7:0] option bits), and HDP (HDPx_END[7:0] and HDPxEN[7:0] option bits) area in bank x when the HDP area access is disabled (HDPx_ACCDIS \( \neq \) 0xA3), or when the HDP extension area access is disabled (HDPxEXT_ACCDIS \( \neq \) 0xA3).

- • RDP option bits

- • WRPxyR option bits

- – These bits cannot be modified when their UNLOCK bit is cleared.

- • UNLOCK option bits

- – These bits can be set only when regressing from RDP level 1 to level 0.

If the user option modification tries to set or modify one of the listed option bytes without following their associated rules, the option-byte modification is discarded and the OPTWERR error flag is set.

7.5 FLASH TrustZone security and privilege protections

7.5.1 TrustZone security protection

The global TrustZone system security is activated by setting the TZEN option bit in FLASH_OPTR. When TrustZone is active (TZEN = 1), the following additional security features are available:

- • Secure watermark-based user options bytes defining secure and HDP areas

- • Secure HDP extension areas

- • Secure or nonsecure block-based areas can be configured on-the-fly after reset. This is a volatile secure area.

- • An additional RDP protection: RDP level 0.5

- • Erase or program operation can be performed in secure or nonsecure mode with associated configuration bit.

When the TrustZone is disabled (TZEN = 0), the above features are deactivated, and all secure registers are RAZ/WI.

Activate TrustZone security

When the TrustZone is activated (TZEN modified from 0 to 1), the secure watermark-based user option bytes are set to default secure state: all flash memory is secure, and no HDP area, as shown in the table below.

Table 47. Default secure option bytes after TZEN activation

| Secure watermark option-byte values after OBL when TZEN is activated (from 0 to 1) | Security attribute |

|---|---|

| SECWMx_STRT = 0 and SECWMx_END = 0x3F for STM32U356/366 SECWMx_STRT = 0 and SECWMx_END = 0x7F for STM32U375/385 SECWMx_STRT = 0 and SECWMx_END = 0xFF for STM32U3B5/3C5 | All flash memory secure |

| HDPxEN = 0xB4 and HDPx_END = 0 | No secure HDP area |

Illegal access generation

A nonsecure access to a secure flash memory area is RAZ/WI and generates an illegal access event. An illegal access interrupt is generated if the FLASHIE illegal access interrupt is enabled in GTZC1_TZIC_IER2.

A nonsecure access to a secure FLASH register generates an illegal access event. An illegal access interrupt is generated if FLASH_REGIE illegal access interrupt is enabled in GTZC1_TZIC_IER2.

Deactivate TrustZone security

Deactivation of TZEN (from 1 to 0) is only possible when the RDP is changing from level 1 to level 0.

When the TrustZone is deactivated (TZEN modified from 1 to 0) after option-byte loading, the following security features are deactivated:

- • Watermark-based secure area (refer to Section 7.5.2 )

- • Block-based secure area (refer to Section 7.5.5 )

- • RDP level 0.5 (refer to Section 7.6.2 )

- • Secure interrupts (refer to Section 7.9 )

- • All secure registers are RAZ/WI.

7.5.2 Watermark-based secure flash memory area protection

When TrustZone security is active (TZEN = 1), a part of the flash memory can be protected against nonsecure read and write accesses. Up to two different nonvolatile secure areas can be defined by option bytes, and can be read or written by a secure access only: one area per bank can be selected with a page granularity.

The secure areas are defined by a start-page offset and end-page offset using SECWMx_STRT and SECWMx_END (x = 1,2 for area 1 and area 2) option bytes. These offsets are defined in secure watermark registers address registers FLASH_SECWM1R1 and FLASH_SECWM1R2.

SECWMx_STRT and SECWMx_END option bytes can only be modified by secure firmware when the HDPx_ACCDIS and HDPxEXT_ACCDIS value is reset (0xA3). If HDPx_ACCDIS or HDPxEXT_ACCDIS is different than reset value (0xA3), SECWMx_STRT and SECWMx_END cannot be modified until next system reset.

Table 48. Secure watermark-based area

| Secure watermark option-byte values (x = 1,2) | Secure watermark protection area |

|---|---|

| SECWMx_STRT > SECWMx_END | No secure area |

| SECWMx_STRT = SECWMx_END | One page defined by SECWMx_STRT is secure watermark-based protected |

| SECWMx_STRT < SECWMx_END | The area between SECWMx_STRT and SECWMx_END is secure watermark-based protected. |

Caution: Switching a flash memory area from secure to nonsecure does not erase its content. User secure software must perform the needed operation to erase the secure area before switching an area to nonsecure attribute, whenever is needed. It is also recommended to flush the instruction cache.

7.5.3 Secure hide protection (HDP)

The secure HDP area is part of the flash memory watermark-based secure area. Access to the hide protection area can be denied by setting HDPx_ACCDIS or HDPxEXT_ACCDIS (x = 1,2 for area 1 and area 2) to a value other than 0xA3 in FLASH_SECHDPCR.

When the HDPx_ACCDIS or HDPxEXT_ACCDIS bit is activated (value ≠ 0xA3), instruction fetch, data read, write and erase operations on this hide protection area are denied. For example, software code in the secure flash hide protected area can be executed only once, and deny any further access to this area until next system reset. The HDPx_ACCDIS

or HDPxEXT_ACCDIS bits can be reset (HDPx_ACCDIS = 0xA3 or HDPxEXT_ACCDIS = 0xA3) only by a system reset.

When a secure HDPx area is defined (HDPxEN \( \neq \) 0xB4 and SECWMx_STRT \( \leq \) HDPx_END \( \leq \) SECWMx_END), it is forbidden to fetch outside the HDPx area until the HDPx area is closed (HDPx_ACCDIS \( \neq \) 0xA3).

The HDP area protection are summarized in Table 62 .

Note: It is software responsibility to take any appropriate action to protect the HDP code before deactivating the HDPxEN bits (HDPxEN = 0xB4), such as erasing the HDP area and flushing the instruction cache.

One nonvolatile secure hide protection (HDP) area per bank can be defined with a page granularity.

The secure HDP area is enabled by the HDPxEN (x = 1,2 for area 1 and area 2). When the HDPxEN bit is deactivated (HDPxEN = 0xB4), there is no HDP area. The HDPxEN bits can be modified on-the-fly by secure firmware if the HDPx_ACCDIS is set to reset value (HDPx_ACCDIS = 0xA3). If HDPx_ACCDIS is different than reset value, the HDPxEN bits and secure watermark configuration cannot be modified until next system reset.

The secure HDP area size is defined by the end-page offset using the HDPx_END option bytes, while the start- page offset is already defined by SECWMx_STRT option bytes. These offsets are defined in secure watermark registers address registers (FLASH_SECWM1R1, FLASH_SECWM1R2, FLASH_SECWM2R1, and FLASH_SECWM2R2).

For example, to protect by HDP from the address 0x0C00 4000 (included) to the address 0x0C00 5FFF (included):

- • If banks are not swapped, the option-byte registers must be programmed with:

- – SECWM1_STRT = 0x4

- – HDP1_END = 0x5

- • If the two banks are swapped, the protection must apply to bank 2, and the option-byte registers must be programmed with:

- – SECWM2_STRT = 0x4

- – HDP2_END = 0x5

Note: For more details on the bank swapping mechanism, refer to Section 7.5.9 .

If an invalid secure HDP area is defined as described in the table below, the OPTWERR flag error is set, and option-byte modification is discarded.

Table 49. Secure hide protection

| HDPx watermark option-byte values (x = 1,2) | Hide protection area | |

|---|---|---|

| HDPxEN = 0xB4 | - | No secure HDP area |

| HDPxEN \( \neq \) 0xB4 | SECWMx_STRT \( \leq \) HDPx_END \( \leq \) SECWMx_END | The area between SECWMx_STRT and HDPx_END is secure HDP protected. |

| Others | Invalid secure area. Hide protection area is defined outside the secure area. | |

The table below summarizes the possible secure and HPD protection area configurations.

Table 50. Secure and HDP protections

| Secure and HDP watermark option-byte values | Protections area | |

|---|---|---|

| HDPxEN | Option bytes | |

| x | SECWMx_STRT > SECWMx_END | No secure area |

| 0xB4 | SECWMx_STRT ≤ SECWMx_END | No secure HDP area Secure between SECWMx_STRT and SECWMx_END If SECWMx_STRT = SECWMx_END, one page defined by SECWMx_STRT is secure protected. |

| ≠ 0xB4 | SECWMx_STRT ≤ HDPx_END ≤ SECWMx_END | The area between SECWMx_STRT and HDPx_END is secure HDP protected. If SECWMx_STRT = HDPx_END, one page defined by HDPx_END is secure HDP protected. |

| Others | Invalid secure area HDP area is defined outside the secure area. | |

7.5.4 Secure hide protection extension (HDP extension)

The secure HDPx (x = 1,2 for area 1 and area 2) area can be extended using HDPx_EXT values in FLASH_SECHDPEXTR register. HDPx_EXT indicates the number of pages added to the HDP area.

The HDPx extension is only composed by the secure HDPx_EXT pages which belong to the flash memory watermark-based secure area. Any pages outside the watermark-based secure area are not part of the HDPx extension area. It means the end page offset of the HDPx extension area cannot be greater than SECWMx_END.

The start page offset of the HDPx extension area depends on the presence of an HDPx area. If there is an HDPx area, the HDPx extension area starts from HDPx_END + 1. Otherwise, it starts from SECWMx_STRT.

Note: If there is no watermark-based secure area, there is no HDP extension. An HDP extension area can be defined even if there is no valid HDP area

HDP extension area access

Access to the HDPx extension area can be denied thanks to HDPxEXT_ACCDIS bits in FLASH_SECHDPCR.

- • When HDPxEXT_ACCDIS value is set to the reset value (0xA3), access to the HDPx extension is granted. There is no write access restrictions to HDPx_EXT and HDPxEXT_ACCDIS bits.

- • When HDPxEXT_ACCDIS value is set to 0x5C, any operations (instruction fetch, data read, write and erase) to the HDPx extension or HDPx is denied until next system reset. Moreover, HDPx extension area size can only be incremented.

There are some write access restrictions on HDPx_EXT and HPxEXT_ACCDIS bits:

- – HDPx_EXT can only be incremented.

- – HDPxEXT_ACCDIS cannot be set to 0xA3.

- When HDPxEXT_ACCDIS value is set to a value different than 0xA3 and 0x5C, any operations (instruction fetch, data read, write and erase) to the HDPx extension or HDPx is denied until next system reset. Moreover HDPx extension area size cannot be modified until next system reset.

There are some write access restrictions on HDPx_EXT and HPxEXT_ACCDIS bits:

- Write access to HDPx_EXT bits are ignored.

- Write access to HDPxEXT_ACCDIS bits are ignored

Table 51. Write access register to HDPx_EXT and HDPxEXT_ACCDIS

| Current HDPxEXT_ACCDIS value | Write access to | Operation (fetch, read, write, erase) in HDPx extended area | Operation (fetch, read, write, erase) in HDPx area | |

|---|---|---|---|---|

| HDPxEXT_ACCDIS | HDPx_EXT | |||

| 0xA3 (reset value) | OK | OK | Allowed | Depends on HDPx_ACCDIS value |

| 0x5C | OK if new value different than 0xA3. Otherwise, write access is ignored | OK if new value greater than current value. Otherwise, write access is ignored. | Denied | Denied |

| Others | Write ignored | Write ignored | ||

When the HDPx extension is enabled (HDPxEXT_ACCDIS \( \neq \) 0xA3), the HDPxEN bits and secure watermark configuration cannot be modified until next system reset (refer to Rules for modifying specific option bytes ).

One volatile secure hide protection extension (HDP extension) area per bank can be defined with a page granularity.

When a HDPx extension area is defined and it is still open (HDPxEXT_ACCDIS = 0xA3) and there is not any open HDP area, it is forbidden to fetch outside the HDPx extended area until it is closed (HDPxEXT_ACCDIS \( \neq \) 0xA3). The HDP and HDP extension area protection are summarized in Table 62 .

The table below summarizes the possible HDP extension area configurations.

Table 52. HDP extension protections

| Secure and HDP watermark option-byte values | HDP extension area | |

|---|---|---|

| HDPxEN | Option bytes | |

| \( \neq \) 0xB4 | HDPx_END \( < \) SECWMx_END | The secure HDPx extension is composed by the following pages: \( \text{HDPx\_END} + 1 \leq \text{pages} \leq \min(\text{HDPx\_END} + \text{HDPx\_EXT}, \text{SECWMx\_END}) \) |

| \( \neq \) 0xB4 | HDPx_END = SECWMx_END | No secure HDPx extension area |

| 0xB4 | - | The secure HDPx extension is composed by the following pages: \( \text{SECWMx\_STRT} \leq \text{pages} \leq \min(\text{SECWMx\_STRT} - 1 + \text{HDPx\_EXT}, \text{SECWMx\_END}) \) |

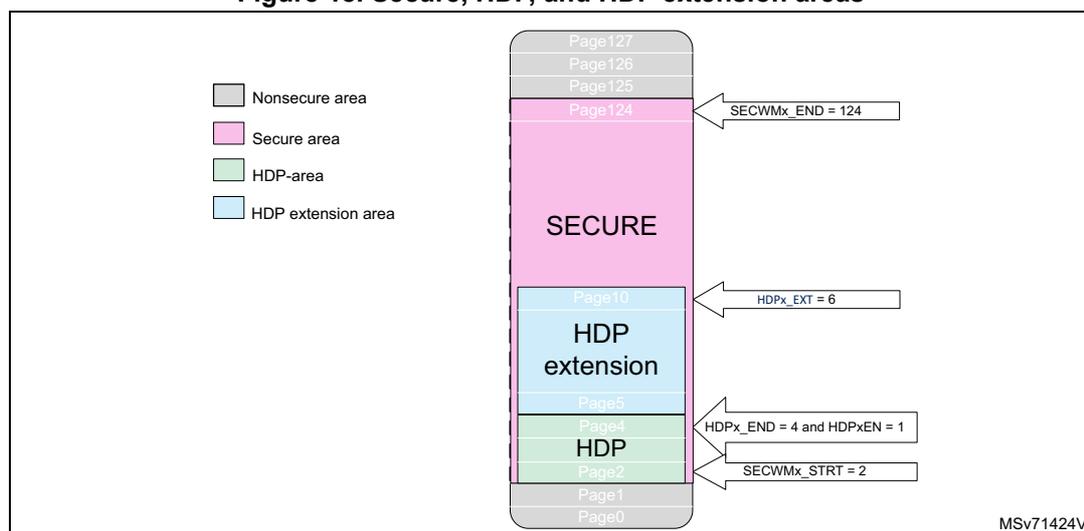

For example:

SECWM1_STRT = 0x2 SECWM1_END = 0x7C

HDP1_END = 0x4 and HDP1EN ≠ 0xB4

HDP1_EXT = 0x6

Pages from 0x2 to 0x4 (included) are protected by HDP and the pages from 0x5 to 0xA are protected by the HDP extension. This is illustrated by the figure below.

Figure 18. Secure, HDP, and HDP extension areas

Other examples:

- • SECWM1_STRT = 0x6 and SECWM1_END = 0x7C

HDP1EN = 0xB4

HDP1_EXT = 0x6

There is no valid HDP area. Pages from 0x6 to 0x7C are secure. The pages from 0x6 to 0xB are protected by the HDP extension.

- • SECWM1_STRT = 0x6 and SECWM1_END = 0x10

HDP1_END = 0xB and HDP1EN ≠ 0xB4

HDP1_EXT = 0x9

Pages from 0x6 to 0xB (included) are protected by HDP. The pages from 0xC to 0x10 are protected by the HDP extension.

7.5.5 Block-based secure flash memory area protection

Any page can be programmed on-the-fly as secure or nonsecure using the block-based configuration registers. FLASH_SECB1Rx (resp. FLASH_SECB2Rx) are used to configure the security attribute for pages in bank 1 (resp. bank 2).

When the page security attribute (bit i in SECBByRx) is set, the security attribute is the same as the secure watermark-based area. The secure page is only accessible by a secure access.

If the SECBByRx[i] bit is set or reset for a page already included in a secure watermark-based area, the page keeps the watermark-based protection security attributes.

To modify a block-based page security attribution, the following actions are recommended:

- • Check that no flash memory operation is ongoing on the related page.

- • Add an ISB instruction after modifying the page security attribute bit i in SECByRx.

Caution: Switching a page or memory block from secure to nonsecure does not erase the content of the associated block. User secure software must perform the following needed operations before switching a block to nonsecure attribute:

- • Erase page content,

- • Invalidate the instruction cache.

Note: For SECByRx bit i access control, refer to Table 69 .

7.5.6 Flash security attribute state

The flash memory is secure when at least one secure area is defined either by watermark-based option bytes or block-based security registers.

It is possible to override the flash security state using the INV bit in FLASH_SCR.

FLASHEN and FLASHSMEN bits security attributes in the RCC follow the flash memory security attribute. It is possible to override the flash memory security attribute in the RCC using the INV bit in FLASH_SCR. A secure firmware setting this INV bit allows a nonsecure firmware to disable the flash memory clock when the flash memory is in power down or when the MCU enters low-power modes.

Table 53. Flash security state

| Secure area | INV bit | Flash security state |

|---|---|---|

| None | 0 | Nonsecure |

| 1 | Secure | |

| Yes | 0 | Secure |

| 1 | Nonsecure |

7.5.7 Block-based privileged flash memory area protection

Any page can be programmed on-the-fly as privileged or unprivileged using the block-based configuration registers. FLASH_PRIVBB1Rx (resp. FLASH_PRIVBB2Rx) are used to configure the privilege attribute for pages in bank 1 (resp. bank 2).

When the page privilege attribute (bit i in PRIVByRx) is set, the page is only accessible by a privileged access. An unprivileged page is accessible by a privileged or unprivileged access.

To modify a block-based privilege attribution, the following actions are recommended:

- • Check that no flash operation is ongoing on the related page.

- • Add an ISB instruction after modifying the page security attribute bit i in PRIVByRx.

Caution: Switching a page or memory block from privileged to unprivileged does not erase the content of the associated block.

Note: For PRIVByRx bit i access control, refer to Table 70 and Table 71 .

7.5.8 Flash memory register privileged and unprivileged modes

The flash memory registers can be read and written by privileged and unprivileged accesses, depending on the SPRIV and PRIV bits in FLASH_PRIVCFG, with the following rules:

- • When the SPRIV (resp. PRIV) bit is reset, all secure (resp. nonsecure) flash memory registers can be read and written by both privileged or unprivileged access.

- • When the SPRIV (resp. PRIV) bit is set, all secure (resp. nonsecure) flash memory registers can be read and written by privileged access only. Unprivileged access to a privileged registers is RAZ/WI.

Table 66 summarizes the flash memory registers access control.

7.5.9 Flash memory bank attributes in case of bank swap

The SWAP_BANK option bit modifies the address of each bank in the memory map. When SWAP_BANK is reset, the flash memory bank 1 is at the lower address range. When SWAP_BANK is set, the flash memory bank 1 is at the higher address range.

Flash memory bank attributes follow their bank so there is no need to modify the following registers when swapping banks:

- • FLASH secure watermark y register x FLASH_SECWMyRx

- • FLASH write protection x area y FLASH_WRPxyR (refer to Section 7.6.1 )

- • FLASH secure block based bank y register x FLASH_SECBByRx

- • FLASH privilege block based bank y register x FLASH_PRIVBByRx

- • PDREQx bits in FLASH_ACR

- • PDx bits in FLASH_SR

Note: The BK_ECC bit in FLASH_ECCCORR always refers to bank 1 (resp. bank 2) when it is low (resp. high), whatever SWAP_BANK value.

The BK_OP bit in FLASH_ECCDETR always refers to bank 1 (resp. bank 2) when it is low (resp. high), whatever SWAP_BANK value.

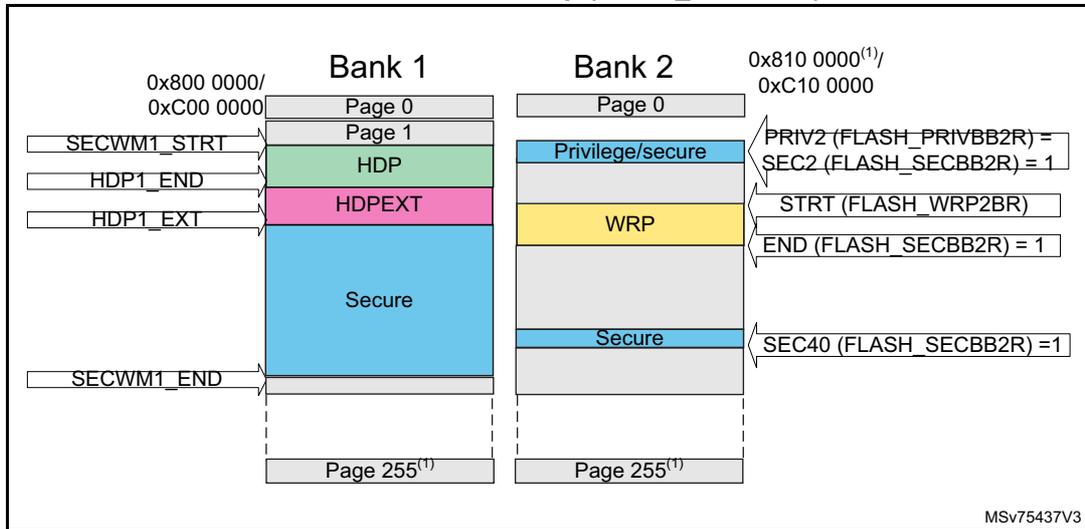

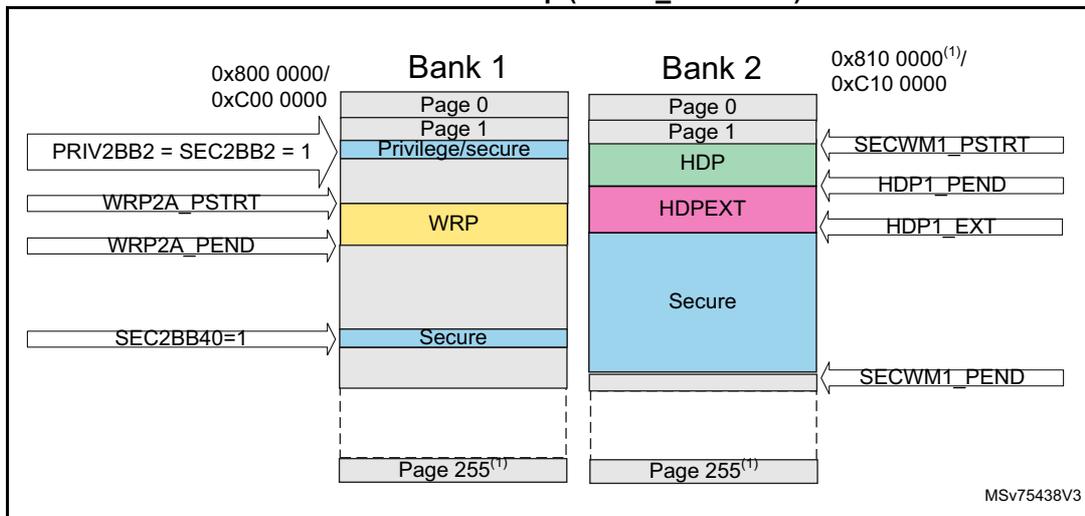

The figures below show how security attributes and protections behave in case of bank swap.

Figure 19. Flash memory security attributes and protections in case of no bank swap (SWAP_BANK = 0)

This diagram illustrates the flash memory layout for Bank 1 and Bank 2 when no bank swap is performed (SWAP_BANK = 0). Both banks start at address 0x800 0000. Bank 1 contains pages 0 to 255. Its security attributes are: SECWM1_STRT at the beginning, HDP (green) from page 1 to HDP1_END, HDPEXT (pink) from HDP1_END to HDP1_EXT, and a large Secure region (blue) from HDP1_EXT to SECWM1_END. Bank 2 also contains pages 0 to 255. Its security attributes are: Privilege/secure (light blue) for pages 0-1, WRP (yellow) for pages 2 to STRT(FLASH_WRP2BR), a gap until END(FLASH_SECB2R) = 1, and a Secure region (blue) from that point to the end of the bank. Register values for Bank 2 are: PRIV2(FLASH_PRIVBB2R) = SEC2(FLASH_SECB2R) = 1, STRT(FLASH_WRP2BR), END(FLASH_SECB2R) = 1, and SEC40(FLASH_SECB2R) = 1. A reference MSv75437V3 is noted at the bottom right.

1. Refer to Table 40 to Table 42 for Bank 2 base address and last page number.

Figure 20. Flash memory security attributes and protections in case of bank swap (SWAP_BANK = 1)

This diagram illustrates the flash memory layout for Bank 1 and Bank 2 when a bank swap is performed (SWAP_BANK = 1). Bank 1 (starting at 0x800 0000) now contains the security attributes originally for Bank 2: Privilege/secure (pages 0-1), WRP (yellow) from WRP2A_PSTRT to WRP2A_PEND, and a Secure region (blue) starting at SEC2BB40=1. Bank 2 (starting at 0x810 0000) contains the security attributes originally for Bank 1: HDP (green) from SECWM1_PSTRT to HDP1_PEND, HDPEXT (pink) from HDP1_PEND to HDP1_EXT, and a Secure region (blue) from HDP1_EXT to SECWM1_PEND. Register values for Bank 1 are: PRIV2BB2 = SEC2BB2 = 1, WRP2A_PSTRT, WRP2A_PEND, and SEC2BB40=1. A reference MSv75438V3 is noted at the bottom right.

1. Refer to Table 40 to Table 42 for Bank 2 base address and last page number.

7.6 FLASH memory protection

The flash memory interface implements the following protection mechanisms:

- • Write protection (WRP)

- • Readout protection (RDP)

- • Additional secure protections when TrustZone is active (refer to

Section 7.5

)

- – Up to two secure watermark-based nonvolatile areas

- – Up to two secure hide protection areas

- – Secure block-based volatile areas with page granularity

- • Privileged block-based volatile areas with page granularity (refer to Section 7.5.7 )

7.6.1 Write protection (WRP)

The user area in the flash memory can be protected against unwanted write operations. Two write-protected (WRP) areas can be defined in each bank, with page granularity.

Each area is defined by a start page offset and an end page offset related to the physical flash bank base address. These offsets are defined in the WRP address registers: FLASH_WRP1AR, FLASH_WRP1BR, FLASH_WRP2AR, and FLASH_WRP2BR.

The bank "x" WRP "y" area (x = 1,2 and y = A,B) is defined as follows:

- • From the address: bank "x" base address + [FLASH_WRPxyR[STRT] × 0x1000] (included)

- • To the address: bank "x" base address + [(FLASH_WRPxyR[END]+1) × 0x1000] (excluded)

For example, to protect by WRP from the address 0x0806 2000 (included) to the address 0x0807 3FFF (included):

- • If the banks are not swapped, FLASH_WRP1AR must be programmed with:

- – STRT = 0x62

- – END = 0x73

- • If the two banks are swapped, the protection must apply to bank 2, and FLASH_WRP2AR must be programmed with:

- – STRT = 0x62

- – END = 0x73

Note: For more details on the bank swapping mechanism, refer to Section 7.5.9 .

When WRP is active, protected flash memory pages cannot be erased or programmed. Consequently, a software mass erase cannot be performed if one area is write-protected.

If an erase/program operation to a write-protected part of the flash memory is attempted, the secure or nonsecure write protection error flag (WRPERR) is set in FLASH_SR or FLASH_SSR. This flag is also set for any write access to the following:

- • System flash memory

- • OTP area

Note: When the memory readout protection level 1 is selected (RDP level = 1), it is not possible to program or erase the flash memory (secure or nonsecure) if the CPU debug features are

connected (JTAG or single wire) or boot code is being executed from RAM or system flash memory, even if WRP is not activated.

When the memory readout protection level 0.5 is selected (RDP level = 0.5), it is not possible to program or erase the flash secure memory if the CPU debug features are connected (JTAG or single wire), even if WRP is not activated.

To validate the WRP options, the option bytes must be reloaded through the OBL_LAUNCH bit in the flash control register.

Table 54. WRP protection

| WRP registers values (x = 1/2 y = A/B) | WRP area |

|---|---|

| FLASH_WRPxy[STRT] = FLASH_WRPxy[END] | Page WRPxy is protected. |

| FLASH_WRPxy[STRT] > FLASH_WRPxy[END] | No WRP area |

| FLASH_WRPxy[STRT] < FLASH_WRPxy[END] | The pages from FLASH_WRPxy[STRT] to FLASH_WRPxy[END] are protected. |

Write protection lock

Each WRP area can be independently locked by writing 0 to the UNLOCK bit in FLASH_WRP1AR, FLASH_WRP1BR, FLASH_WRP2AR, or FLASH_WRP2BR. Once a WRP area is locked, it is not possible to modify its settings. In order to unlock a WRP area, a regression to RDP level 0 must be launched.

In order to make the WRP area immutable and act as a ROM, the following actions are needed:

- • If RDP level is 0, 0.5 or 1, provision a OEM1KEY in order to prevent a regression to RDP level 0 for users not knowing the key.

- • If RDP level is 2, either provision a OEM1KEY (refer to first bullet) or do not provision a OEM2KEY (preventing regression from level 2 to level 1).

For more information on RDP regressions, refer to Device life cycle managed by readout protection (RDP) transitions .

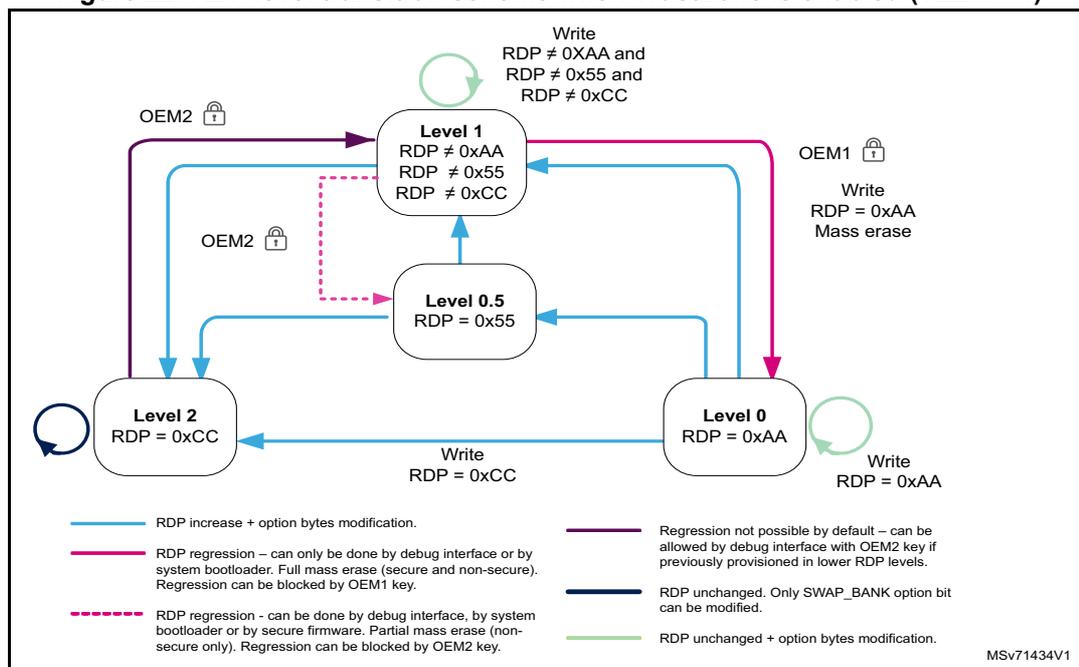

7.6.2 Readout protection (RDP)

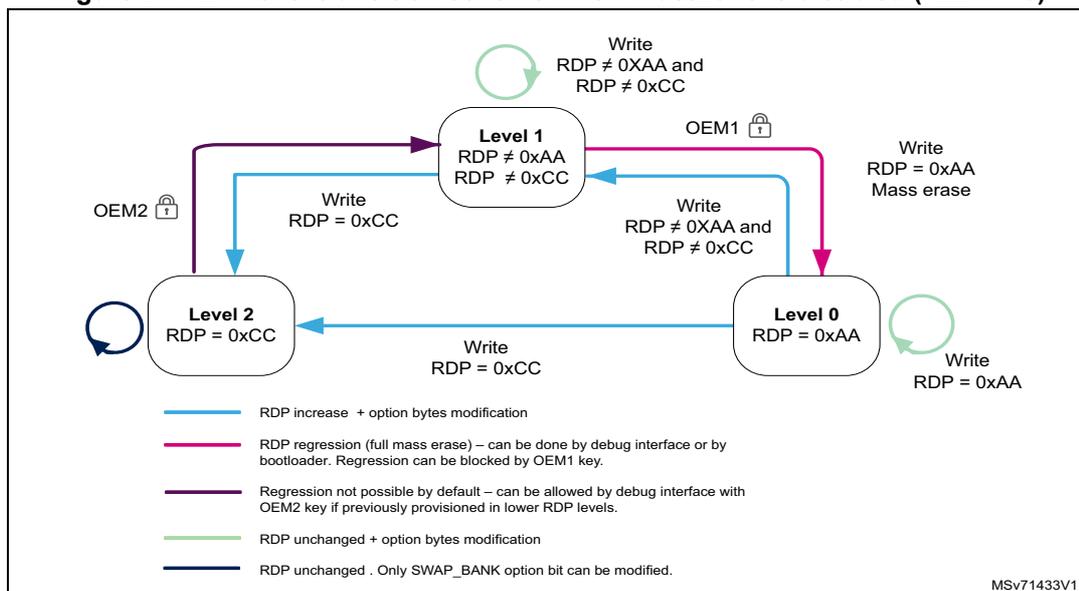

The readout protection protects the flash main memory, the option bytes, the backup registers, and the SRAMs. In order to reach the best protection level, it is recommended to activate TrustZone, and to set the RDP level 2 with password authentication regression enabled (refer to Readout protection levels when TrustZone is enabled ).

Readout protection levels when TrustZone is disabled

There are three levels of readout protection from no protection (level 0) to maximum protection or no debug (level 2).

The flash memory is protected according to the RDP option-byte value shown in the table below.

Table 55. Flash memory readout protection status (TZEN = 0)

| RDP byte value | Readout protection level |

|---|---|

| 0xAA | Level 0 |

| Any value except 0xAA or 0xCC | Level 1 |

| 0xCC | Level 2 |

- • Level 0: no protection

Read, program and erase operations into the flash main memory area are possible. Option bytes, SRAMs, and backup registers are also accessible by all operations.

- • Level 1: readout protection

When the readout protection level 1 is set:

- – User mode: code executing in user mode (boot flash) can access the flash main memory, option bytes, SRAMs, and backup registers with all operations (read, erase, program).

- – Debug, boot RAM, and bootloader modes: in debug mode or when the microcontroller boots from RAM or system memory, the flash main memory, the backup registers, and the SRAM2 are totally inaccessible. Any read or write access to the flash main memory generates a bus error and a hard fault interrupt.

- • Level 2: no debug

When the readout protection level 2 is set:

- – The protection level 1 is guaranteed.

- – All debug features are disabled:

- - if OEM2 key has not been provided, JTAG and SWD are definitively disabled.

- - if OEM2 key has been provided under a lower RDP protection, JTAG and SWD remain enabled under reset only to interface with DBGMCU_SR, DBGMCU_DBG_AUTH_HOST, and DBGMCU_DBG_AUTH_DEVICE registers to obtain device identification and provide OEM2 key to request RDP regression.

- – The boot from SRAM (boot RAM mode) and the boot from system memory (bootloader mode) are no longer available.

- – Only boot from main flash memory is possible; all operations are allowed on the flash main memory. Read, erase and program accesses to the flash memory and SRAMs from user code are allowed.

- – Option bytes cannot be programmed nor erased except the SWAP_BANK option bit. Thus, the level 2 cannot be removed: it is an irreversible operation unless an OEM2 key has been provisioned (refer to OEM2 RDP lock mechanism ).

Note: The debug feature is also disabled under reset.

STMicroelectronics is not able to perform analysis on defective parts on which the level 2 protection has been set. Regress parts to RDP level 1 before returning them for analysis (refer to OEM2 RDP lock mechanism ).

Table 56. Access status versus protection level and execution mode when TZEN = 0| Area | RDP level | User execution (boot from flash) | Debug/boot from RAM/ bootloader (1) | ||||

|---|---|---|---|---|---|---|---|

| Read | Write | Erase | Read | Write | Erase | ||

| Flash main memory | 1 | Yes | Yes | Yes | No | No | No (2) |

| 2 | Yes | Yes | Yes | N/A | N/A | N/A | |

| System memory (3) | 1 | Yes | No | No | Yes | No | No |

| 2 | Yes | No | No | N/A | N/A | N/A | |

| Option bytes (4) | 1 | Yes | Yes (2) | N/A | Yes | Yes | N/A |

| 2 | Yes | No (5) | N/A | N/A | N/A | N/A | |

| OTP | 1 | Yes | Yes (6) | N/A | Yes | Yes (6) | N/A |

| 2 | Yes | Yes (6) | N/A | N/A | N/A | N/A | |

| Backup registers | 1 | Yes | Yes | N/A | No | No | N/A (7) |

| 2 | Yes | Yes | N/A | N/A | N/A | N/A | |

| SRAM2 | 1 | Yes | Yes | N/A | No | No | N/A (8) |

| 2 | Yes | Yes | N/A | N/A | N/A | N/A | |

- 1. When the protection level 2 is active, the debug port, the boot from RAM and the boot from system memory are disabled.

- 2. The system memory is only read-accessible, whatever the protection level (0, 1 or 2) and execution mode.

- 3. The system memory is only read-accessible, whatever the protection level (0, 1 or 2) and execution mode.

- 4. Option bytes are only accessible through the flash registers interface and OPTSTRT bit.

- 5. SWAP_BANK option bit can be modified.

- 6. OTP can only be written once.

- 7. The backup registers are erased when RDP changes from level 1 to level 0.

- 8. All SRAMs are erased when RDP changes from level 1 to level 0. On STM32U3B5/3C5 devices, SRAM4 is not erased on RDP regression.

Readout protection levels when TrustZone is enabled

There are four levels of readout protection from no protection (level 0) to maximum protection or no debug (level 2). The flash memory is protected according to the RDP option-byte value shown in the table below.

Table 57. Flash memory readout protection status (TZEN = 1)| RDP byte value | Readout protection level |

|---|---|

| 0xAA | Level 0 |

| 0x55 | Level 0.5 |

| Any value except 0xAA or 0x55 or 0xCC | Level 1 |

| 0xCC | Level 2 |

- • Level 0: no protection

Read, program and erase operations into the flash main memory area are possible. The option bytes, the SRAMs and the backup registers are also accessible by all operations.

- – RSS mode: when booting from RSS, the debug access is disabled while executing RSS code.

- • Level 0.5: nonsecure debug only

All read and write operations (if no write protection is set) from/to the nonsecure flash memory are possible. The debug access to secure area is prohibited. Debug access to nonsecure area remains possible.

- – User mode: code executing in user mode (boot flash) can access the flash main memory, option bytes, SRAMs and backup registers with all operations (read, erase, program).

- – Nonsecure debug mode: nonsecure debug is possible when the CPU is in nonsecure state. The secure flash memory, secure backup registers, and SRAMs are inaccessible. The nonsecure flash memory, nonsecure backup registers, and nonsecure SRAMs remain accessible for debug purpose.

- – RSS mode: when booting from RSS, the debug access is disabled while executing RSS code.

- – Boot RAM mode: boot from SRAM is not possible.

- • Level 1: readout protection

When the readout protection level 1 is set:

- – User mode: code executing in user mode (boot flash) can access the flash main memory, option bytes, SRAMs and backup registers with all operations (read, erase, program).

- – Nonsecure debug mode: nonsecure debug is possible when the CPU is in nonsecure state. However, an intrusion is detected in case of debug access: the flash main memory, backup registers, and the SRAM2 are totally inaccessible. Any read or write access to the flash main memory generates a bus error and a hard fault interrupt.

- – RSS mode: when booting from RSS, the debug access is disabled while executing RSS code.

- – Boot RAM mode: boot from SRAM is not possible.

- • Level 2: no debug

When the readout protection level 2 is set:

- – The protection level 1 is guaranteed.

- – All debug features are disabled

- -if OEM2 key has not been provided, JTAG and SWD are definitively disabled.

- – -if OEM2 key has been provided under a lower RDP protection, JTAG and SWD remain enabled under reset only to interface with DBGMCU_SR, DBGMCU_DBG_AUTH_HOST, and DBGMCU_DBG_AUTH_DEVICE registers to obtain device identification and provide OEM2 key to request RDP regression.

- – The boot from SRAM (boot RAM mode) and the boot from system memory (boot loader mode) are no longer available.

- – Boot from RSS is possible.

- – When booting from main flash or RSS, all operations are allowed on the flash main memory. Read, erase and program accesses to flash memory and SRAMs from user code are allowed.

- – Option bytes cannot be programmed nor erased except the SWAP_BANK option bit. Thus, the level 2 cannot be removed: it is an irreversible operation unless an OEM2 key has been provisioned (refer to OEM2 RDP lock mechanism ).

Note: The debug feature is also disabled under reset.

STMicroelectronics is not able to perform analysis on defective parts on which the level 2 protection has been set. Regress parts to RDP level 1 before returning them for analysis (refer to OEM2 RDP lock mechanism ).

Table 58. Access status versus protection level and execution modes when TZEN = 1

| Area | RDP level | User execution (boot from flash) | Debug/bootloader (1) | ||||

|---|---|---|---|---|---|---|---|

| Read | Write | Erase | Read | Write | Erase | ||

| Flash main memory | 0.5 | Yes | Yes | Yes | Yes (2) | Yes (2) | Yes (2) |

| 1 | Yes | Yes | Yes | No | No | No (5) | |

| 2 | Yes | Yes | Yes | N/A | N/A | N/A | |

| System memory (3) | 0.5 | Yes | No | No | Yes | No | No |

| 1 | Yes | No | No | Yes | No | No | |

| 2 | Yes | No | No | N/A | N/A | N/A | |

| Option bytes (4) | 0.5 | Yes | Yes (5) | N/A | Yes | Yes (5) | N/A |