79. Device electronic signature

The device electronic signature is set in hardware or stored in the OTP (visible in BSEC registers), and can be read using the debug interface or by the CPU. It contains factory-programmed identification data that allow the user firmware or other external devices to automatically match the characteristics of the component.

79.1 Unique device ID register (96 bits) (UID)

The unique device identifier is ideally suited to be used:

- • as serial number (USB string serial number, or other end applications)

- • as part of the security keys, to increase the security of code while using and combining this unique ID with software cryptographic primitives and protocols before programming the memory

- • during processes such as secure boot

The 96-bit unique device identifier provides a reference number, unique for a given device and in any context. These bits cannot be altered by the user.

Base address: 0x4600 9000 (BSEC base address on APB4)

Address offset: 0x014 (BSEC_OTP_DATA5)

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| UID[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| UID[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 UID[31:0] : 31:0 unique ID bits

Address offset: 0x018 (BSEC_OTP_DATA6)

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| UID[63:48] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| UID[47:32] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 UID[63:32] : 63:32 unique ID bits

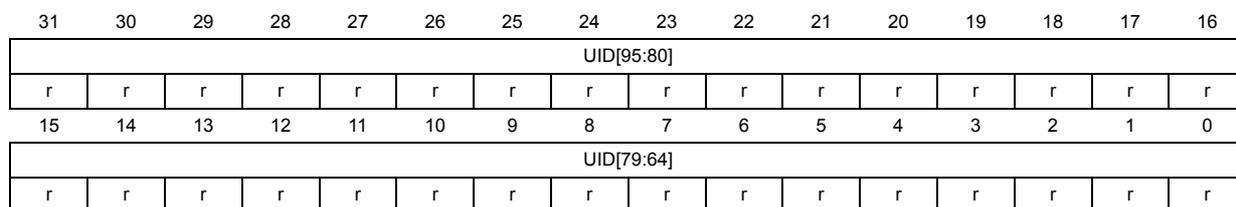

Address offset: 0x01C (BSEC_OTP_DATA7)

Read only = 0xXXXX XXXX, where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| UID[95:80] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| UID[79:64] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 UID[95:64] : 95:64 unique ID bits

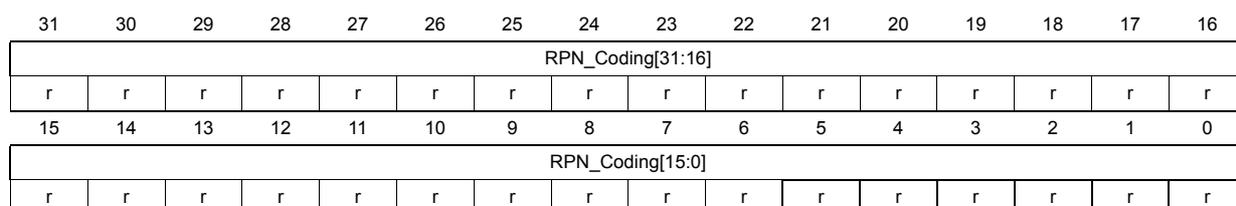

79.2 Device part number (RPN)

Base address: 0x4600 9000 (BSEC base address on APB4)

Address offset: 0x024 (BSEC_OTP_DATA9)

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| RPN_Coding[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RPN_Coding[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 RPN_Coding[31:0] :

0x0000 2000: STM32N657

0x0000 2200: STM32N647

0x0000 6000: STM32N655

0x0000 6200: STM32N645

Others: Reserved

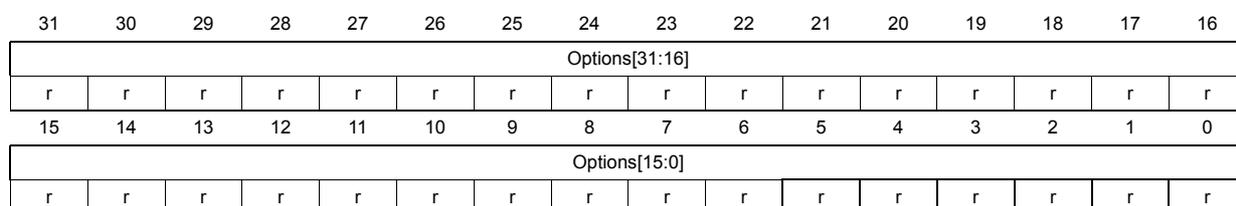

Base address: 0x4600 9000 (BSEC base address on APB3)

Address offset: 0x020 (BSEC_OTP_DATA8)

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Options[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Options[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 Options[31:0] :

0x00000000: No options

79.3 Package data register (PKG)

Base address: 0x4600 9000 (BSEC base address on APB4)

Address offset: 0x1E8 (BSEC_OTP_DATA122)

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PKG[3:0] | |||

| r | r | r | r | ||||||||||||

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 PKG[3:0] : Package type

- 0010: BGA142

- 0100: BGA169

- 0110: BGA178

- 1000: BGA198

- 1010: BGA223

- 1100: BGA264

- Others: Reserved

79.4 Device version

Base address: 0x4400 1000 (DBGMCU is defined in Table 870: System ROM table )

Address offset: 0x000 (DBGMCU_IDCODE)

Read only = 0xXXXX 6XXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| REV_ID[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | DEV_ID[11:0] | |||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | ||||

Bits 31:16 REV_ID[15:0] : Silicon revision

0x1000: Revision A

Bits 15:12 Reserved, must be kept at reset value.

Bits 11:0 DEV_ID[11:0] : Device identifier

0x486: STM32N6xx

79.5 Boot ROM version

Base address: 0x1800 1000

Address offset: 0x0000

Read only = 0xXXXX XXXX where X is factory-programmed (data are in little endian format).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ChipVersion[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ChipVersion[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 ChipVersion[31:0] :

0x0000 8604: STM32N6

Base address: 0x1800 1000

Address offset: 0x0004

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CutVersion[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CutVersion[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 CutVersion[31:0] :

0x0000 0200: Cut 2.0

Base address: 0x1800 1000

Address offset: 0x0008

Read only = 0xXXXX XXXX where X is factory-programmed.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ROM mask version[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ROM mask version[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 ROM mask version[31:0] :

0x0000 0001: version 1