76. Ethernet (ETH): gigabit media access control (GMAC) with DMA controller

76.1 Ethernet introduction

Portions Copyright (c) Synopsys, Inc. All rights reserved. Used with permission.

The Ethernet peripheral enables to transmit and receive data over Ethernet in compliance with the IEEE 802.3-2015 standard.

The peripheral is configurable to meet the needs of a large variety of consumer and industrial applications, including AV nodes and TSN (time sensitive networking) nodes.

76.2 Ethernet main features

The Ethernet peripheral embeds a dedicated DMA for direct memory interface, a media access controller (MAC) and a PHY interface block supporting several formats.

76.2.1 Standard compliance

The Ethernet peripheral is compliant with the following standards:

- • IEEE 802.3-2015 for Ethernet MAC and media independent interface (MII)

- • IEEE 1588-2008 for precision networked clock synchronization (PTP)

- • IEEE 802.1AS-2011 and 802.1-Qav-2009 for Audio Video (AV) traffic

- • IEEE 802.3az-2010 for Energy Efficient Ethernet (EEE)

- • IEEE 802.1Qbv-2015, 802.1Qbu-2016, and 802.1AS-Rev D5.0 for Time-Sensitive Networking (TSN) traffic

- • AMBA 2.0 for AHB slave port

- • AMBA4 for AXI master port

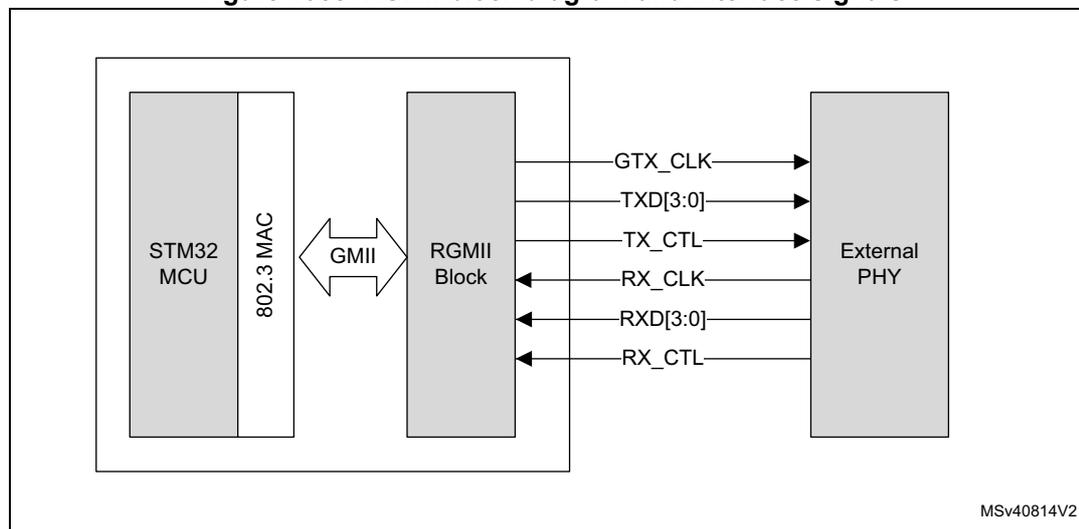

- • RGMII specification version 2.6 from HP/Marvell

- • RMII specification version 1.2 from RMII consortium

Caution: The gigabit media independent interface (GMII) is only available internally to supply the RGMII adapter. No GMII signals are available off-chip.

76.2.2 MAC features

MAC Tx and Rx common features

- • Separate transmission, reception, and control interfaces to the application

- • 10, 100, and 1000 Mbit/s data transfer rates with the following PHY interfaces:

- – IEEE 802.3-compliant MII interface to communicate with an external Fast Ethernet PHY

- – RGMII interface to communicate with an external gigabit PHY

- – RMII interface to communicate with an external Fast Ethernet PHY

- • Half-duplex operation:

- – CSMA/CD protocol support

- – Flow control using back pressure (based on implementation-specific white papers and UNH Ethernet Clause 4 MAC Test Suite - Annex D)

- – Packet bursting and packet extension in 1000 Mbps Half-duplex operation

- • Standard IEEE 802.3az-2010 for Energy Efficient Ethernet in MII and reduced gigabit media independent interface (RGMII) PHYs

- • 64-bit data transfer interface on the application side

- • Full-duplex flow control operations (IEEE 802.3x Pause packets and Priority flow control)

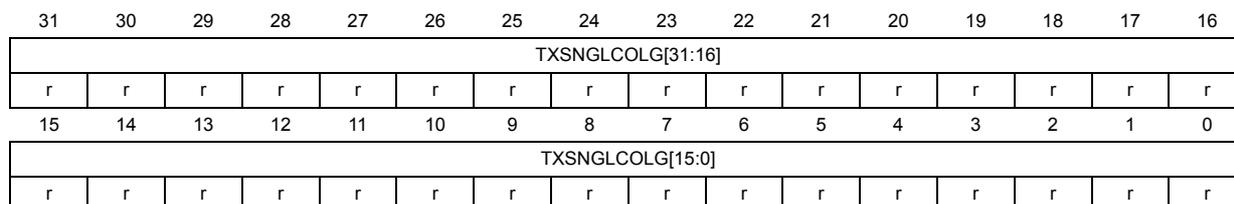

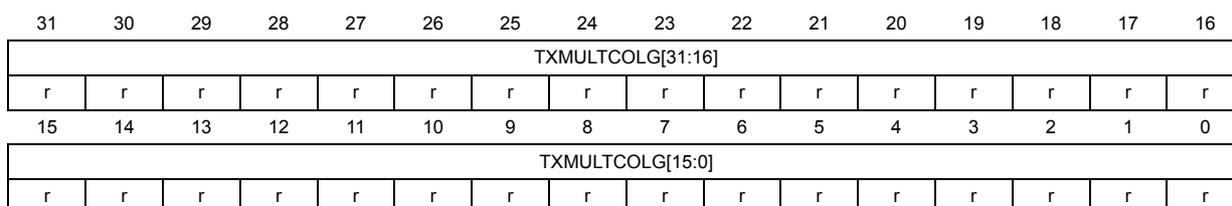

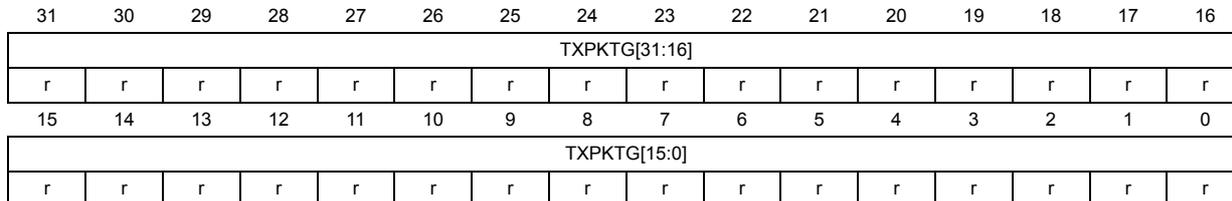

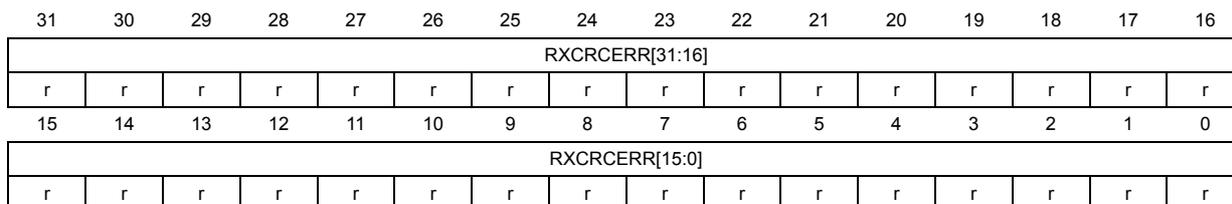

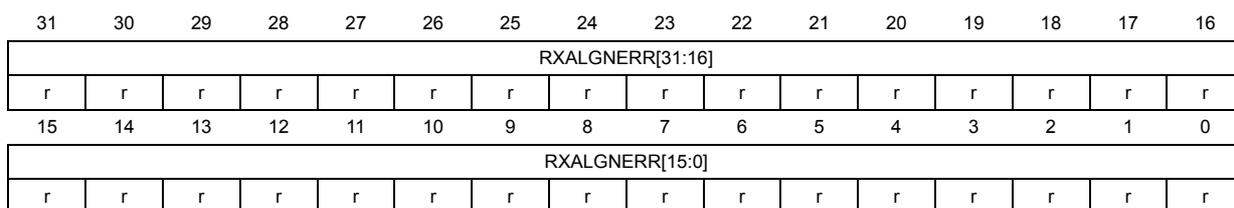

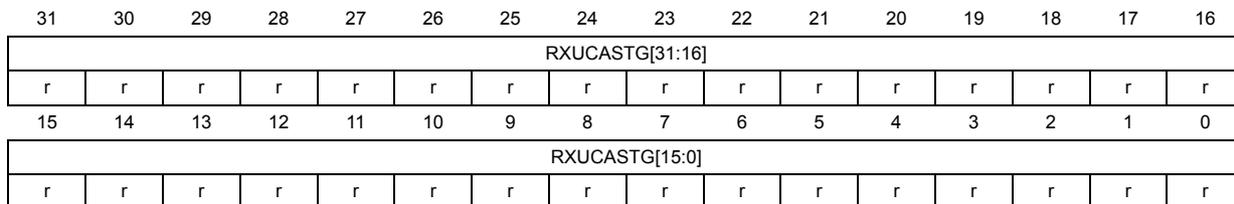

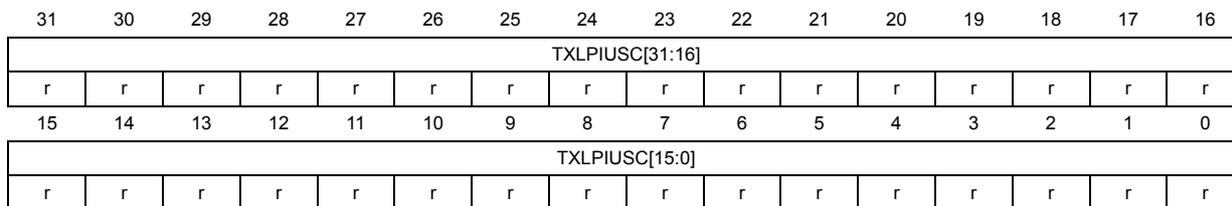

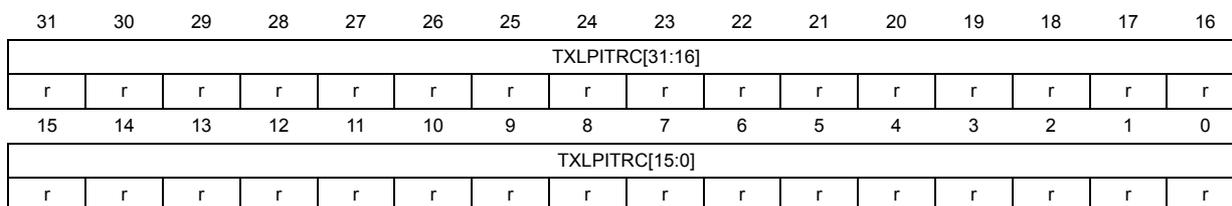

- • Network statistics with RMON or MIB counters (partial support of RFC2819/RFC2665)

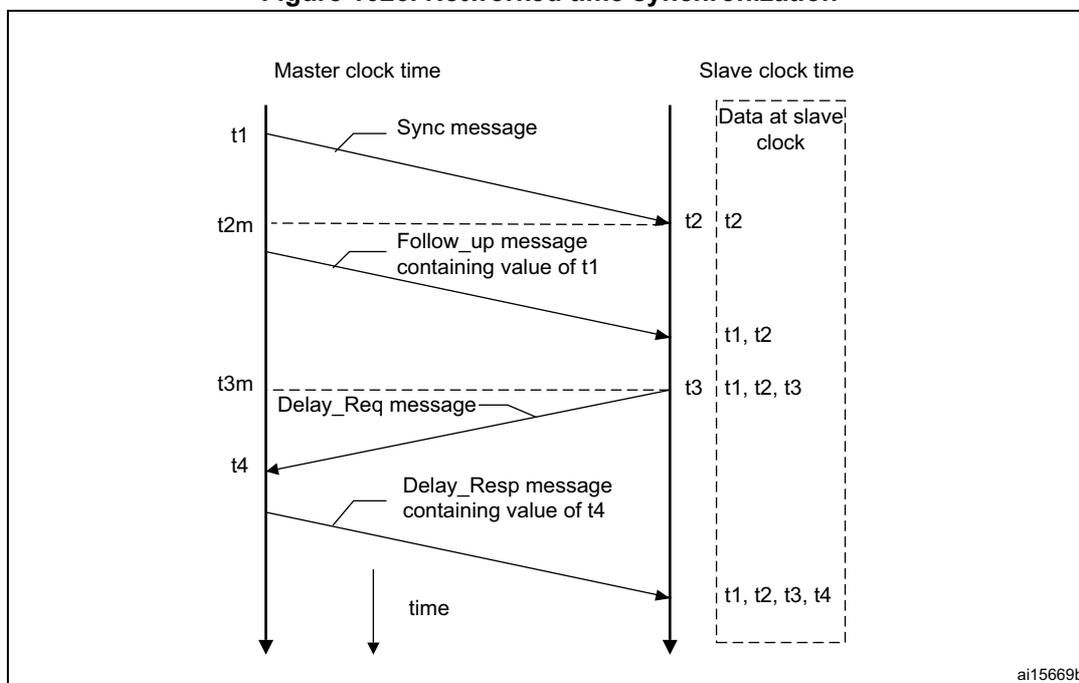

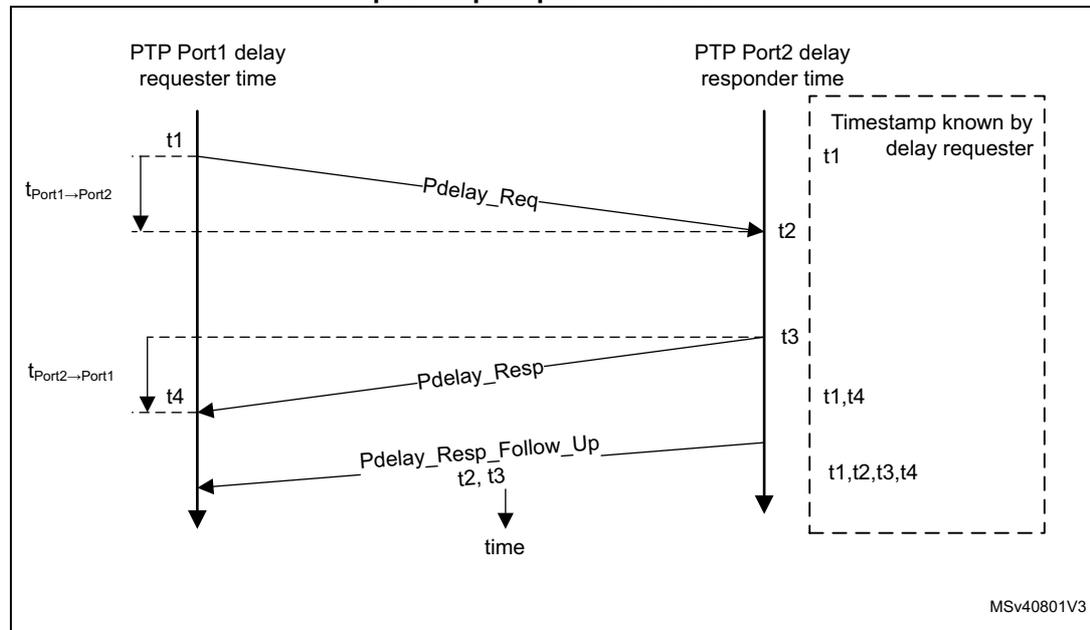

- • Ethernet packet timestamping as described in IEEE 1588-2002 and IEEE 1588-2008 (64-bit timestamps given in the Tx or Rx status of PTP packet). Both one-step and two-step timestamping are supported in Tx direction.

- • Flexibility to control up to two pulse-per-second (PPS) output signals (eth_otp_pps_outx and ETH_PPS_OUT)

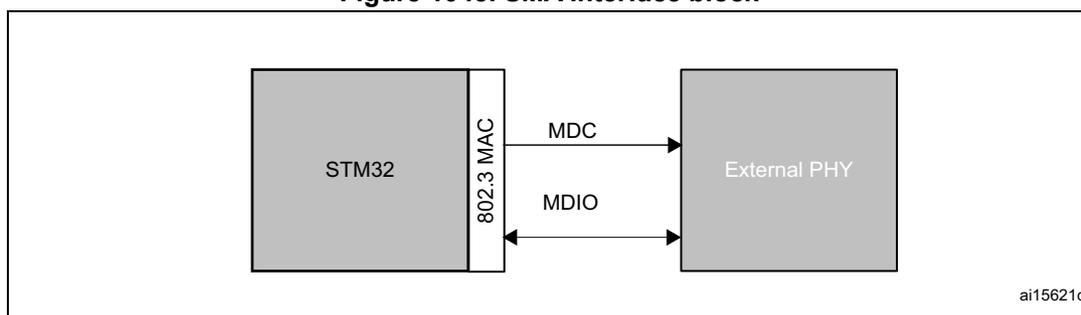

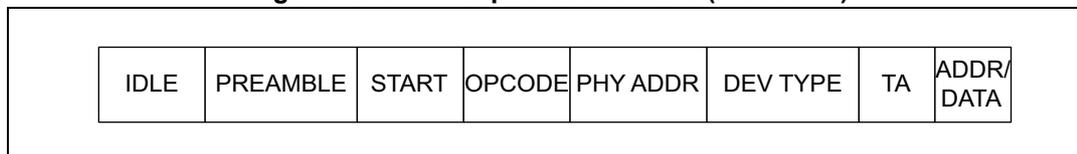

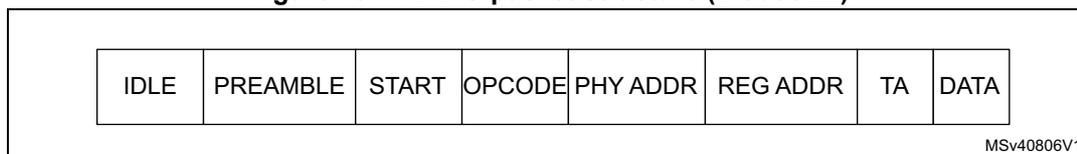

- • MDIO (Clause 22 and Clause 45) master interface for PHY device configuration and management

MAC Tx features

- • Preamble and start-of-frame data (SFD) insertion

- • Separate 32-bit status for each packet transmitted from the application

- • Automatic CRC and pad generation controllable on a per-frame basis

- • Programmable packet length to support Standard or Jumbo Ethernet packets of up to 16 Kbytes

- • Programmable Inter Packet Gap (40–96 bit times in steps of 8)

- • IEEE 802.3x Flow Control automatic transmission of zero-quanta Pause packet when flow control input transitions from assertion to de-assertion (in Full-duplex mode)

- • Source address field insertion or replacement, and VLAN insertion, replacement, and deletion in transmitted packets with per-packet or static-global control

- • Insertion, replacement, or deletion of up to two VLAN tags

- • Option to transmit packets with reduced preamble size in Full-duplex mode

- • Insert, replace, or delete queue/channel-based VLAN tags

- • Frame preemption for MAC Tx

MAC Rx features

- • Automatic Pad and CRC stripping options

- • Option to disable automatic CRC checking

- • Preamble and SFD deletion

- • Separate 112-bit or 128-bit status

- • Programmable watchdog timeout limit

- • Flexible address filtering modes:

- – Four 48-bit perfect (DA) address filters with masks for each byte

- – Four 48-bit SA address comparison check with masks for each byte

- – 64 bit Hash filter for multicast and unicast (DA) addresses

- • Option to pass all multicast addressed packets

- • Promiscuous mode to pass all packets without any filtering for network monitoring

- • Pass all incoming packets (as per filter) with a status report

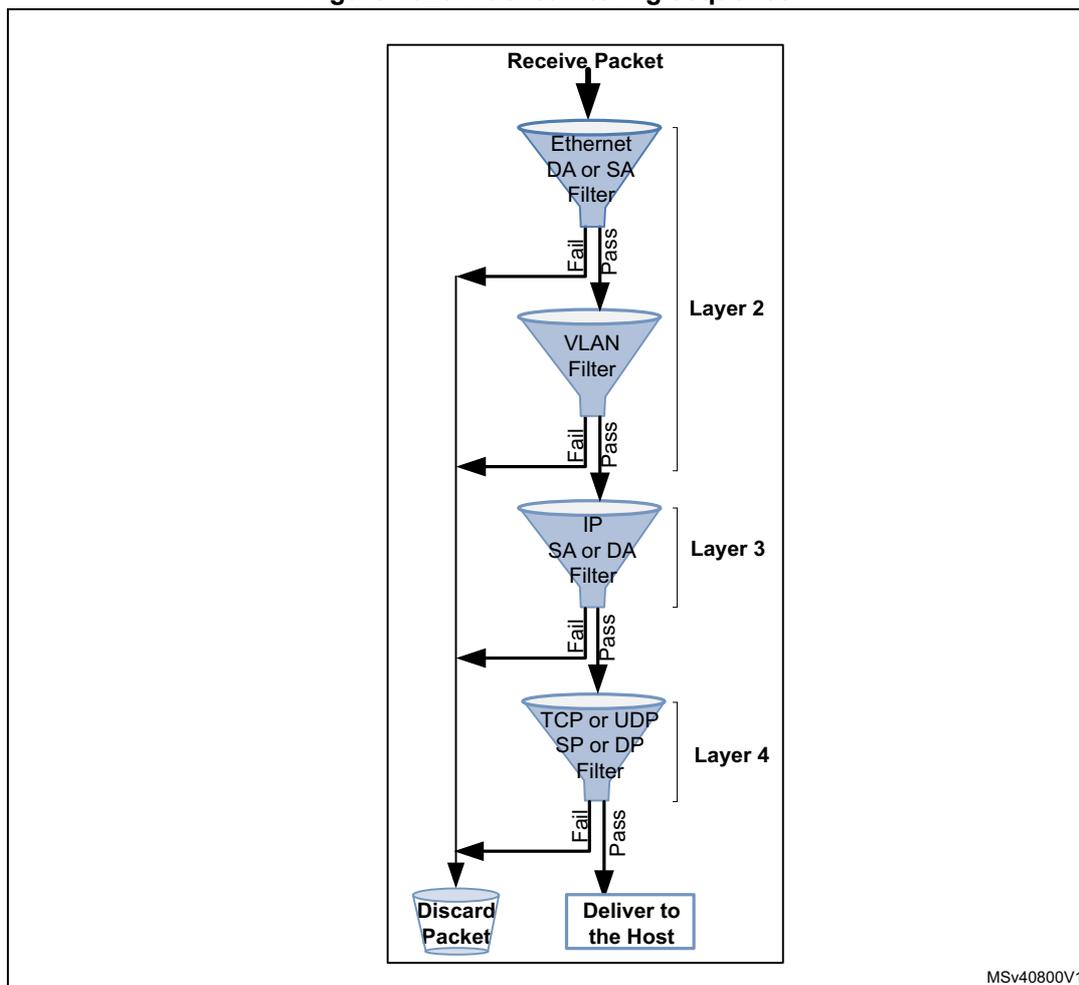

- • Additional packet filtering:

- – VLAN tag-based: Perfect match and Hash-based filtering based either on the outer or inner VLAN tag

- – Layer 3 and Layer 4-based: TCP or UDP over IPv4 or IPv6

- – Extended VLAN tag based filtering with four filter selection

- • IEEE 802.1Q VLAN tag detection and option to delete the VLAN tags in received packets

- • Detection of remote wake-up packets and AMD magic packets

- • Optional forwarding of received Pause packets to the application (in Full-duplex mode)

- • Layer 3/Layer 4 checksum offload for received packets

- • Stripping of up to two VLAN tags and providing the tags in the status

- • Frame preemption for MAC Rx

76.2.3 Transaction layer (MTL) features

MTL Tx and Rx common features

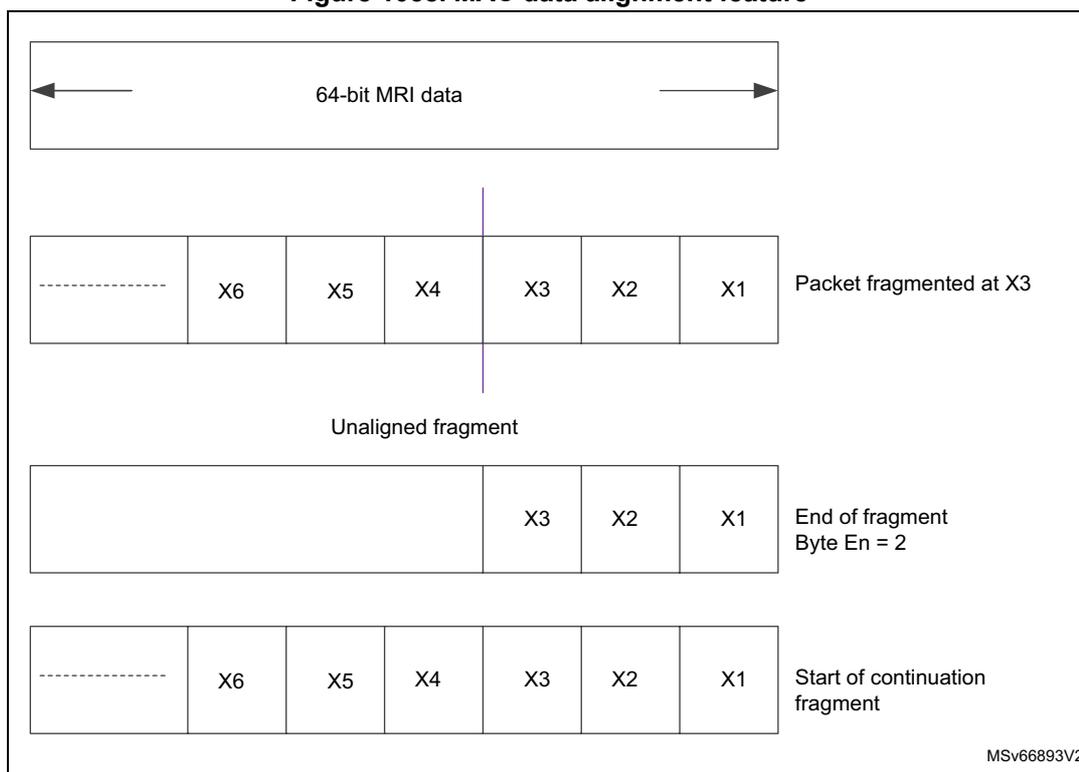

- • 64-bit transaction layer block (bridges the application and the MAC)

- • Optimization for packet-oriented transfers with packets delimiters

- • Programmable burst length, up to half the size of the MTL Rx queue or Tx queue size, to support burst data transfer in the EQOS-MTL configuration

- • Programmable threshold capability for each queue (default of 64 bytes)

MTL Tx features

- • 4096-byte transmit FIFO with programmable threshold capability

- • Two Tx queues on the transmit path with a common memory for all Tx queues

- • Store-and-forward mechanism or threshold mode (cut-through) for transmission to the MAC

- • Programmable queue size in configurations with multiple queues. Each queue size can be programmed in terms of 256 bytes

- • Automatic retransmission of collision packets in Half-duplex mode

- • Discard packets on late collision, excessive collisions, excessive deferral, and under-run conditions with appropriate status

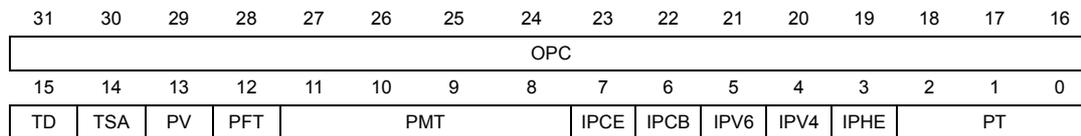

- • Module to calculate and insert IPv4 header checksum and TCP, UDP, or ICMP checksum on frames transmitted in Store-and-forward mode

- • Statistics by generating pulses for packets dropped (because of underflow) in the Tx FIFO

- • Optional statistics related to bandwidth consumption for each queue of up to 16 blocks over a 125 µs period

- • Packet-level control for

- – VLAN tag insertion or replacement

- – Ethernet source address insertion

- – Layer 3/Layer 4 checksum insertion control

- – One-step timestamp

- – Timestamp control

- – CRC and pad control

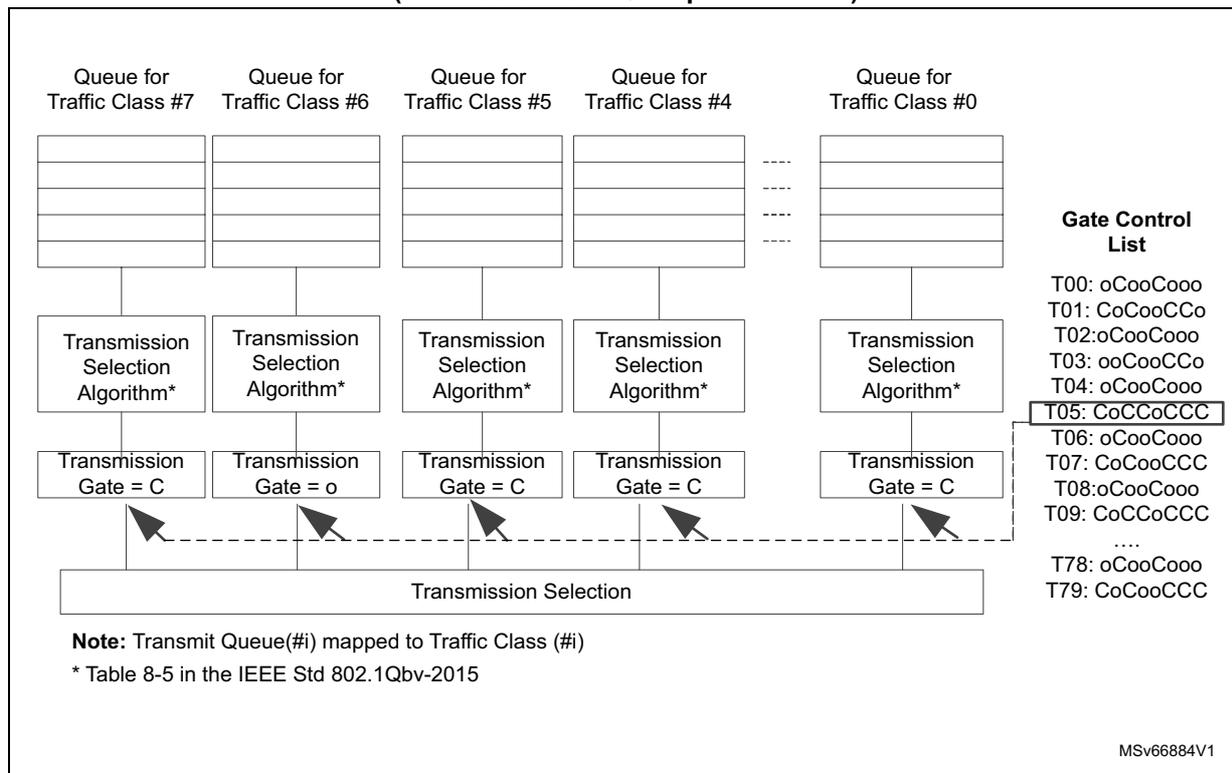

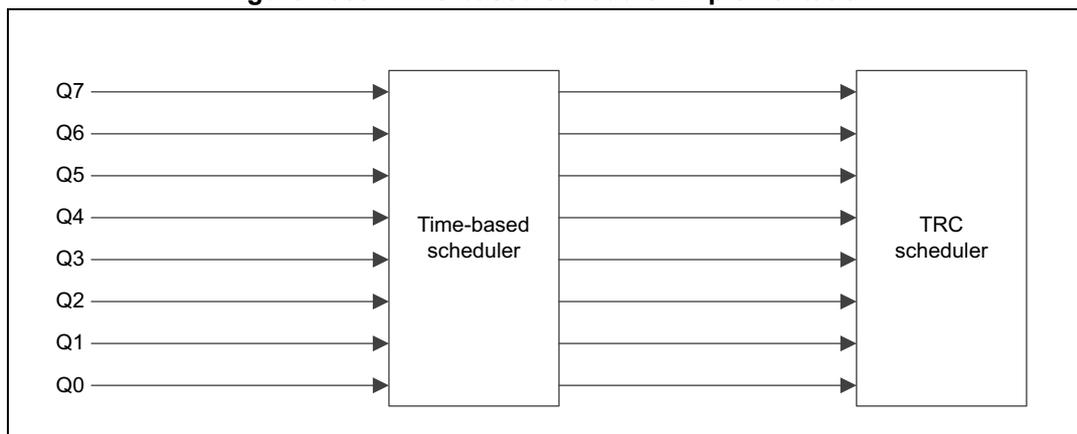

- • Following scheduling algorithms in configurations with multiple queues

- – Weighted round robin (WRR)

- – Strict priority (SP)

- – Credit-based shaper (CBS)

- – Enhancement to scheduled traffic (EST)

- – Time-based scheduling (TBS)

MTL Rx features

- • 4096-byte receive FIFO with configurable threshold

- • Two Rx queues on the receive path with a common memory for all Rx queues

- • Programmable Rx queue threshold (default fixed at 64 bytes) in threshold (or cut-through) mode

- • Option to filter all error packets on reception and not forward them to the application in the store-and-forward mode

- • Option to forward the undersized good packets

- • Statistics by generating pulses for packets dropped (because of overflow) in the Rx FIFO

- • Automatic generation of Pause packet control or backpressure signal to the MAC based on the Rx Queue fill level

- • Arbitration among queues when multiple queues are present. The following arbitration schemes are supported:

- – Weighted round robin (WRR)

- – Weighted Strict priority (WSP)

- – Strict priority (SP)

76.2.4 DMA block features

The DMA block exchanges data between the peripheral and the system memory. DMA transfers are driven by software descriptors structure. The application can use a set of registers (see Section 76.11.2: Ethernet DMA registers ) to control the DMA operations. The DMA block supports the following features:

- • 64-bit data transfers

- • Separate DMA channel in the transmit path for each queue

- • Separate DMA channel in the receive path for each queue

- • Optimization for packet-oriented DMA transfers with packet delimiters

- • Byte-aligned addressing for data buffer support

- • Dual-buffer (ring) descriptor support

- • Descriptor architecture allowing large blocks of data transfer with minimum CPU intervention (each descriptor can transfer up to 32 Kbytes of data)

- • Comprehensive status reporting normal operation and transfer errors

- • Individual programmable burst length for Tx DMA and Rx DMA engines for optimal host bus utilization

- • Programmable interrupt options for different operational conditions

- • Per-packet transmit or receive complete interrupt control

- • Round-robin or fixed-priority arbitration between the receive and transmit engines

- • Fixed-priority, weighted-strict-priority or weighted-round-robin arbitration for data read requests from multiple transmit DMA engines

- • Start and Stop modes

- • Separate ports for host control access and host data interface (AXI)

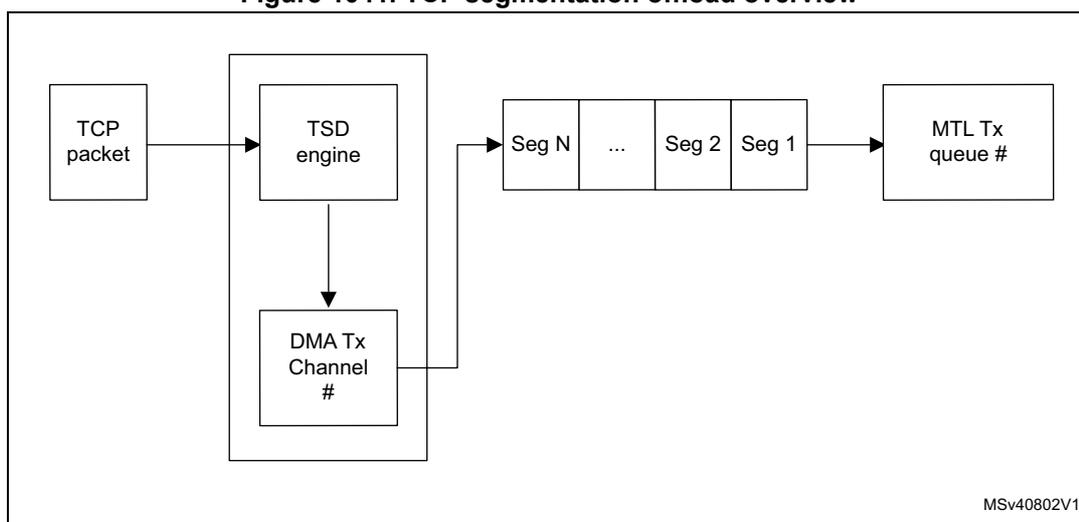

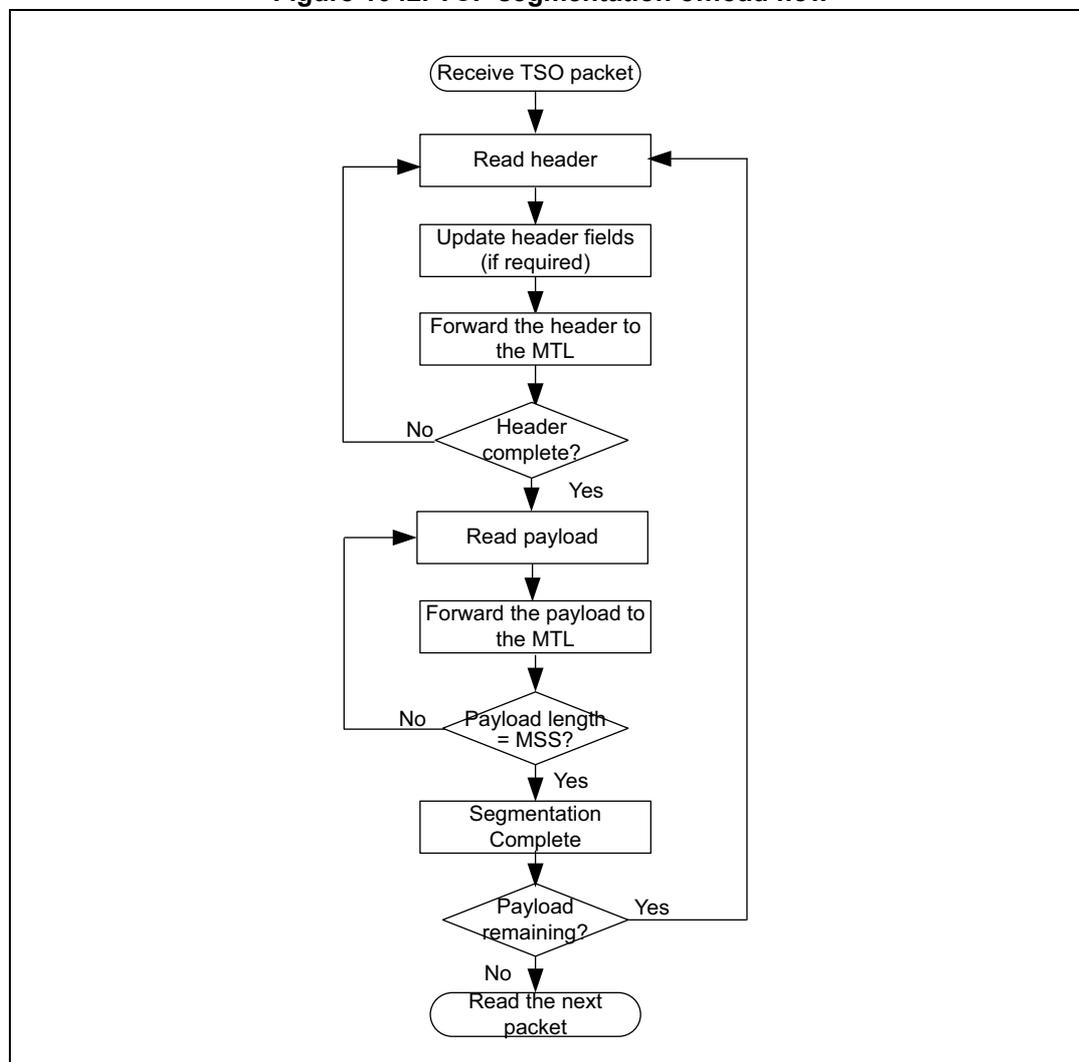

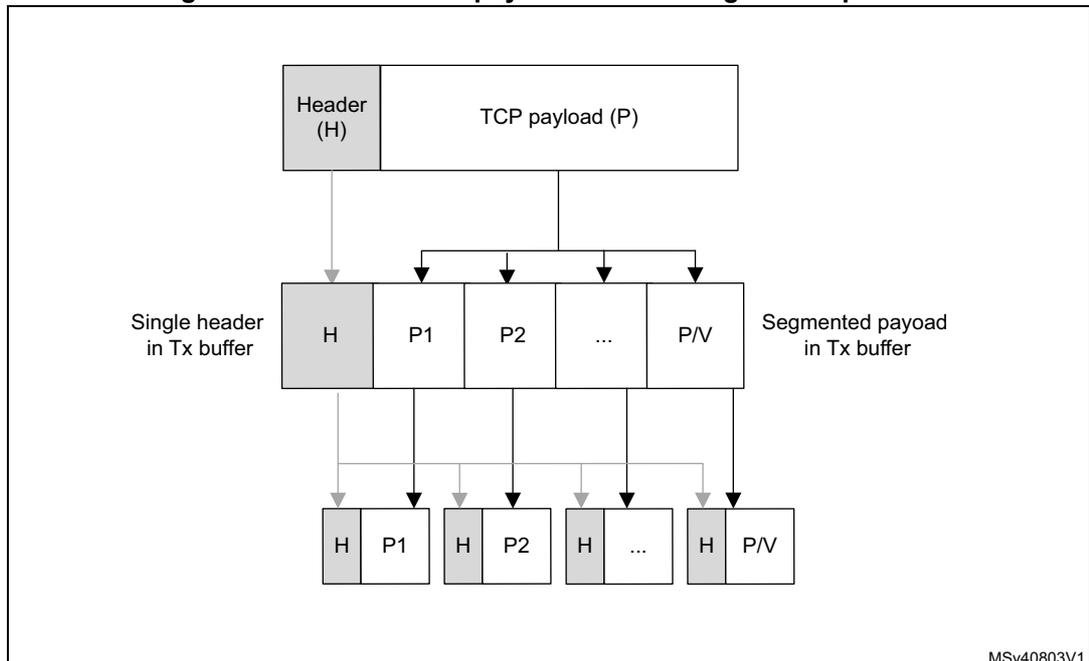

- • Tx DMA channels with TCP segmentation offload (TSO) feature enabled

- • Routing of received packets to the DMA channels based on the DA or VLAN priority in multichannel DMA configurations

- • Time-sensitive conditional packet transmission by comparing the slot time or IEEE 1588 time information provided in the descriptor (useful for AV applications)

- • Programmable control for transmit descriptor posted writes to improve the throughput

76.2.5 Bus interface features

AXI master interface

The AXI master interface features are the following:

- • Interfaces with the application through AXI4 compatible interface

- • 32-bit address width

- • 64-bit data

- • OKAY, SLVERR, and DECERR responses

- • Software-selected type of AXI burst (fixed and variable length burst) in AXI master interface; extended length fixed bursts of 32, 64, 128, and 256

- • Handshaking on AXI read and write data channels

AHB slave interface

The AHB slave interface supports the following features:

- • Interfaces with the application through AHB

- • AHB slave interface (32-bit) for CSR access

- • All AHB burst types

The AHB slave interface does not generate the following responses:

- • Split

- • Retry

76.2.6 Audio and video features

The Ethernet peripheral can be used in Audio Video (AV) mode. The supported features are compliant with the industry standards for AV traffic:

- • Separate channels or queues for AV data transfer in 100 Mbps and 1000 Mbps modes

- • Multiple Rx queues on the receive paths for AV traffic, and multiple Tx queues on the Transmit path for AV traffic

- • IEEE 802.1-Qav specified credit-based shaper (CBS) algorithm for Transmit channels

- • Single Tx FIFO and Rx FIFO (MTL) for all selected queues

- • Programmable Slot Interval with range from 1 µs to 4096 µs and granularity of 1 µs.

76.2.7 Time sensitive networking features

The Ethernet peripheral supports the following time sensitive networking (TSN) features:

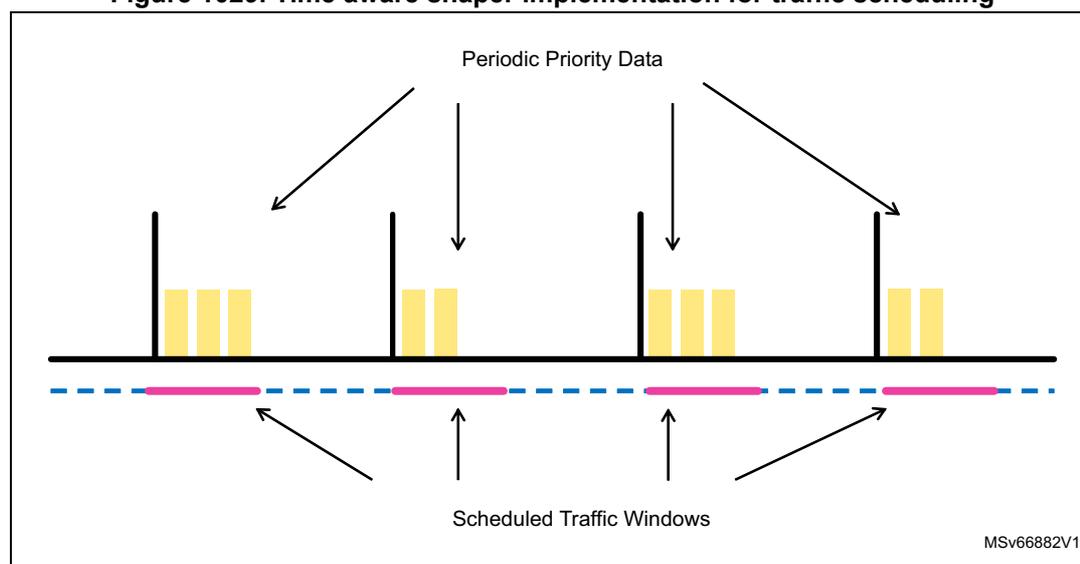

- • IEEE 802.1Qbv-2015, Enhancements to Scheduling Traffic

- • IEEE802.1Qbu/802.3br, Frame preemption and Interspersing Express Traffic

76.2.8 Generic queuing features

The Ethernet peripheral supports the following features for generic queuing:

- • Programmable control for routing receive packets with Multicast/Broadcast destination address to a programmable receive queue

- • Support routing of untagged receive packets to a programmable receive queue

- • Programmable control for routing VLAN tagged and untagged IEEE 1588 PTP over Ethernet receive packets to a same or separate programmable receive queue

- • Programmable control for routing Unicast/Multicast receive packets that fail the destination address filter to a separate programmable receive queues

76.3 Ethernet pins and internal signals

Table 762 lists the Ethernet inputs and output signals connected to package pins or balls. Active pins depend on the PHY type selected (MII, RMII or RGMII) and on the device configuration.

Table 763 shows the internal Ethernet signals.

Table 762. Ethernet peripheral pins

| Port name | Digital port type | Description |

|---|---|---|

| ETH_COL | Input | Collision detection signal, MII only. |

| ETH_CRS | Input | Carrier sense signal, MII only |

| ETH_REF_CLK | Input | RMII reference clock |

| ETH_RX_CLK | Input | MII/RGMII timing reference for Rx data transfers |

| ETH_RXD[3:0] | Input | Receive data. 4 pins for MII and RGMII, 2 for RMII. |

| ETH_RX_DV | Input | Receive data valid |

Table 762. Ethernet peripheral pins (continued)

| Port name | Digital port type | Description |

|---|---|---|

| ETH_CRS_DV | Input | RMII: Carrier Sense (CRS) and RX_Data Valid (RX_DV) multiplexed on alternate clock cycles. In 10 Mbit/s mode, it alternates every 10 clock cycles. |

| ETH_RX_CTL | Input | After demultiplexing, this pin provides ETH_RX_DV on the rising edge of ETH_RX_CLK, and ETH_RX_ER (logical XOR between ETH_RX_CTL values on rising edge and falling edge of ETH_RX_CLK). |

| ETH_RX_ER | Input | Receive error |

| ETH_TX_CLK | Input | MII timing reference for Tx data transfers |

| ETH_GTX_CLK | Output | RGMII timing reference for Tx data transfers |

| ETH_TXD[3:0] | Output | Transmit data. 4 pins for MII and RGMII, 2 for RMII. |

| ETH_TX_EN | Output | Transmit data enable |

| ETH_TX_CTL | Output | Multiplexing of ETH_TX_EN on the rising edge of ETH_TX_CLK, and a logical XOR between ETH_TX_EN and ETH_TX_ER values on falling edge of ETH_TX_CLK |

| ETH_TX_ER | Output | Transmit error |

| ETH_MDC | Output | Management data clock |

| ETH_MDIO | Input/output | Management data |

| ETH_PHY_INTN | Input | PHY interrupt |

| ETH_PPS_OUT | Output | PTP pulse-per-second output 0 |

| ETH_PTP_AUX_TS (1) | Input | Trigger input for the auxiliary snapshots of the PTP system time |

1. This pin is not available on all devices.

Table 763. Ethernet internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| eth_hclk | Digital input | AHB clock |

| eth_aclk | Digital input | AXI clock |

| eth_sbd_intr_it | Digital output | Main Ethernet interrupt |

| lpi_intr_o | Digital output | Sideband signal generated when the transmitter or receiver enters or exits the LPI state. |

| pmt_intr_o | Digital output | Sideband signal generated when a valid remote wake-up packet is received |

| eth_tx_clk | Digital input | Tx kernel clock |

| eth_rx_clk | Digital input | Rx kernel clock |

| eth_rmii_ref_clk | Digital input | RMII reference kernel clock |

| eth_ptp_pps_out1 | Digital output | PTP pulse-per-second signal |

| mac_speed_o[1:0] | Digital output | MAC speed information used by the RCC |

Table 763. Ethernet internal input/output signals (continued)

| Signal name | Signal type | Description |

|---|---|---|

| clk_ptp_ref_i | Digital input | PTP reference clock input |

| eth_ptp_trig[3:0] | Digital input | Trigger input for auxiliary snapshots of the PTP system time |

76.4 Ethernet architecture

The Ethernet peripheral is composed of 4 main functional modules:

- • The control and status register module (CSR) that controls the registers access through AHB 32-bit slave interface

- • The direct memory access interface (DMA)

This is the logical DMA module with two physical channel for reception and two for transmission. It controls the data transfers between MAC and system memory through the AMBA AXI4 64-bit master interface. - • The media access control module (MAC) in charge of implementing the Ethernet protocol

- • The MAC transaction layer (MTL) in charge of controlling the data flow between application and MAC.

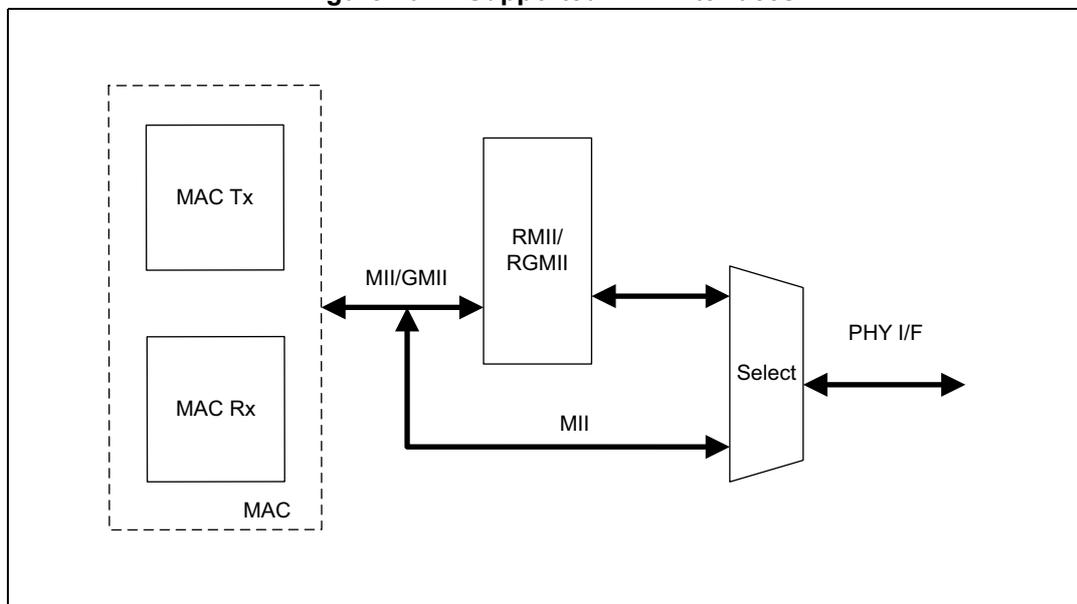

A protocol adaption module is added to support the RMII or the RGMII PHY Media Independent Interfaces.

Caution: The gigabit media independent interface (GMII) is only available internally to supply the RGMII adapter. No GMII signals are available off-chip.

Figure 1019. Ethernet high-level block diagram

![Figure 1019. Ethernet high-level block diagram. The diagram shows the internal architecture of the Ethernet MAC. On the left, a 64-bit AXI Master and a 32-bit AHB Slave are connected to a DMA Arbitrer and a CSR (Control and Status Register). The DMA Arbitrer is connected to two DMA channels (Ch.0 and Ch.1), each with Tx and Rx engines. These channels are connected to 4KB Tx and Rx FIFOs, which in turn connect to the MAC Tx and MAC Rx blocks. The MAC blocks are connected to a GMII/MII interface, which includes a RGMII/RMII block and a Select block. The Select block is connected to the PHY I/F. Various clock and control signals are shown: eth_aclk, eth_hclk, eth_sbd_intr_it, lpi_intr_o, pmt_intr_o, mac_speed_o[1:0], clk_ptp_ref_i, eth_ptp_trig[3:0], and ETH_PTP_AUX_TS. Output signals include eth_tx_clk, eth_ref_clk, eth_rx_clk, ETH_PPS_OUT, and eth_ptp_pps_out1. The diagram is labeled MSv71200V4.](/RM0486-STM32N6x5-x7/9072ca12a447da802bf2911032481e25_img.jpg)

- 1. For a definition of the internal signals, refer to Table 763 .

- 2. Refer to RCC chapter “Clock distribution for Ethernet” for a detailed description of the Ethernet clock architecture.

- 3. The ETH_PTP_AUX_TS pin is not available on all devices.

76.4.1 DMA controller

The DMA has independent transmit (Tx) and receive (Rx) engines. The Tx engine transfers data from the system memory to the MAC Transaction Layer (MTL), whereas the Rx engine transfers data from the device port (PHY) to the system memory.

The controller uses descriptors to efficiently move data from source to destination with minimal application CPU intervention. The DMA is designed for packet-oriented data transfers such as packets in Ethernet. The controller can be programmed to interrupt the application CPU for situations such as Packet transmit and receive Transfer completion, and other normal or error conditions.

DMA data structures

The DMA and the application communicate through the following two data structures:

- • Control and Status registers (CSR)

- • Descriptor lists and data buffers

The DMA transfers the data packets received by the MAC to the Rx buffer in system memory and Tx data packets from the Tx buffer in the system memory. The descriptors that reside in the system memory contain the pointers to these buffers.

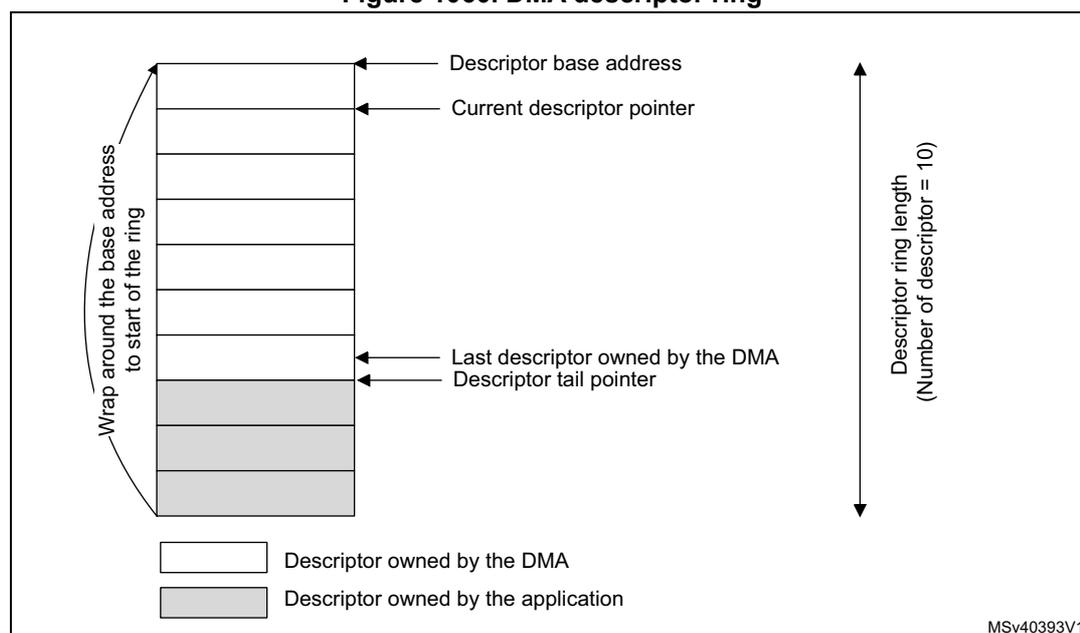

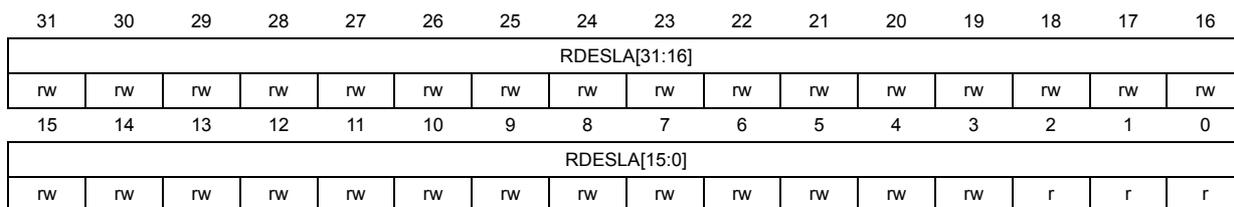

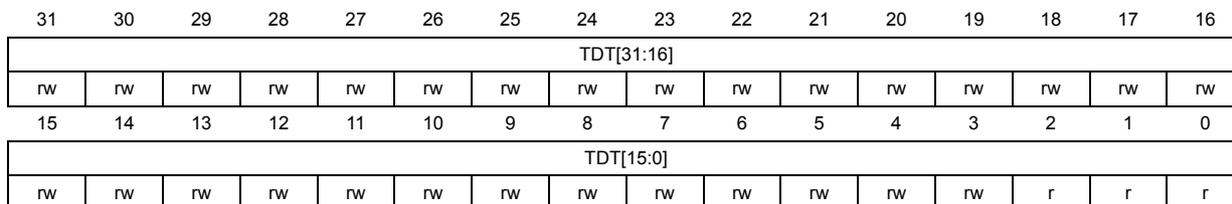

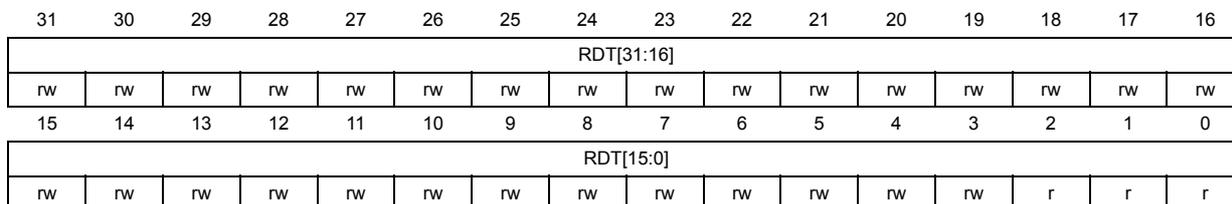

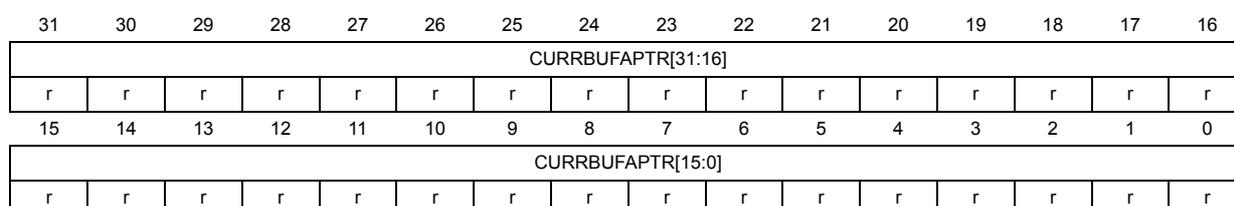

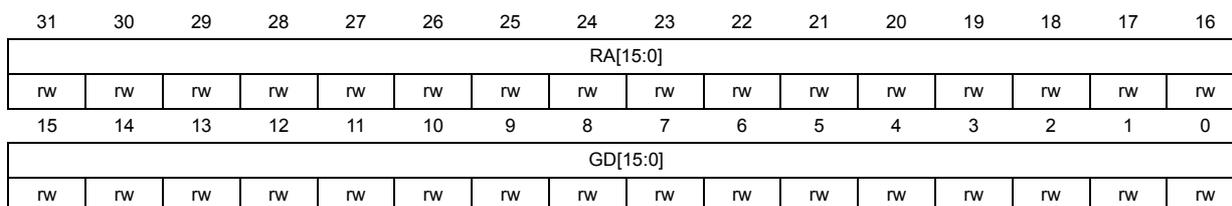

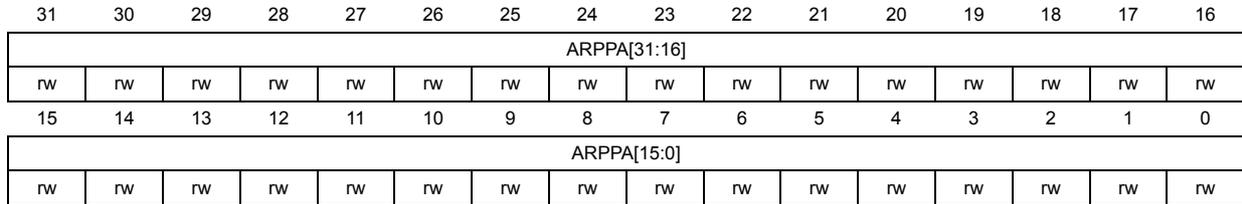

The base address of each list is written to the respective Tx and Rx registers: Channel x Tx descriptor list address register (ETH_DMACxTXDLAR) and Channel x Rx descriptor list address register (ETH_DMACxRXDLAR) .

The descriptor list is forward linked and the next descriptor is always considered at a fixed offset to the current one. The number of descriptors in the list is programmed in the respective Tx/Rx, Channel x Tx descriptor ring length register (ETH_DMACxTXRLR) and Channel x Rx descriptor ring length register (ETH_DMACxRXRLR) .

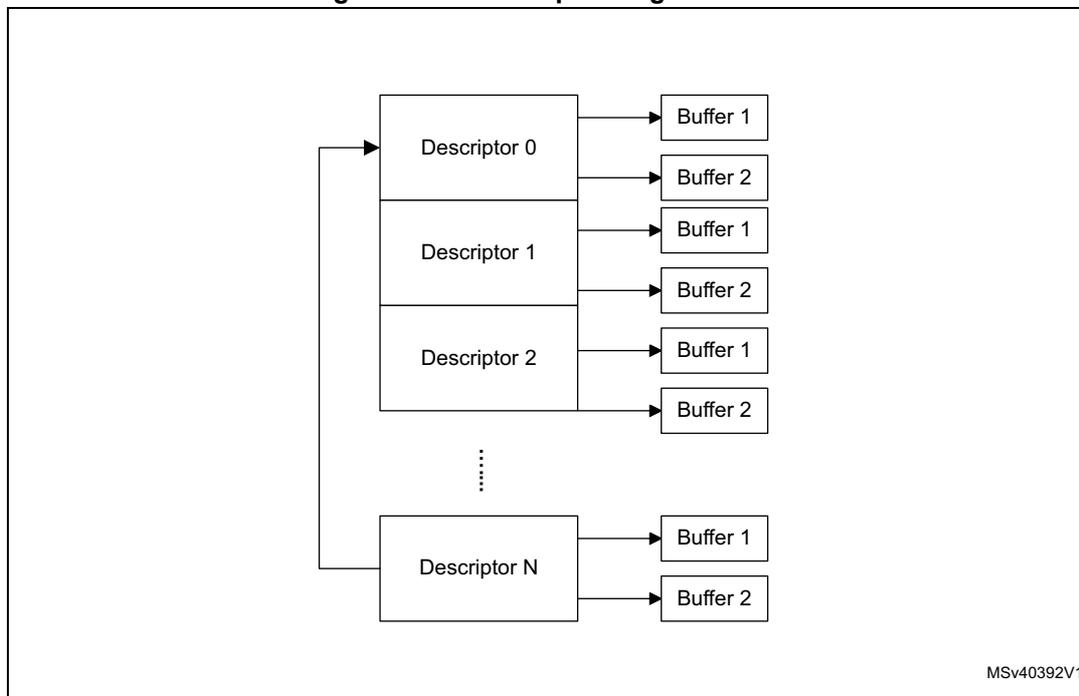

Once the DMA processes the last descriptor in the list, it automatically jumps back to the descriptor in the List address register to create a descriptor ring. The descriptor lists reside in the physical memory address space of the application. Each descriptor can point to a maximum of two buffers. This enables two buffers to be used and physically addressed, rather than contiguous buffers in memory.

A data buffer resides in the application physical memory space and consists of an entire packet or part of a packet, but cannot exceed a single packet. Buffers contain only data. The buffer status is saved in the descriptor. Data chaining refers to packets that span multiple data buffers. However, a single descriptor cannot span multiple packets. The DMA skips to the data buffer of next packet when EOP is detected.

Descriptors are specified in Section 76.10: Descriptors .

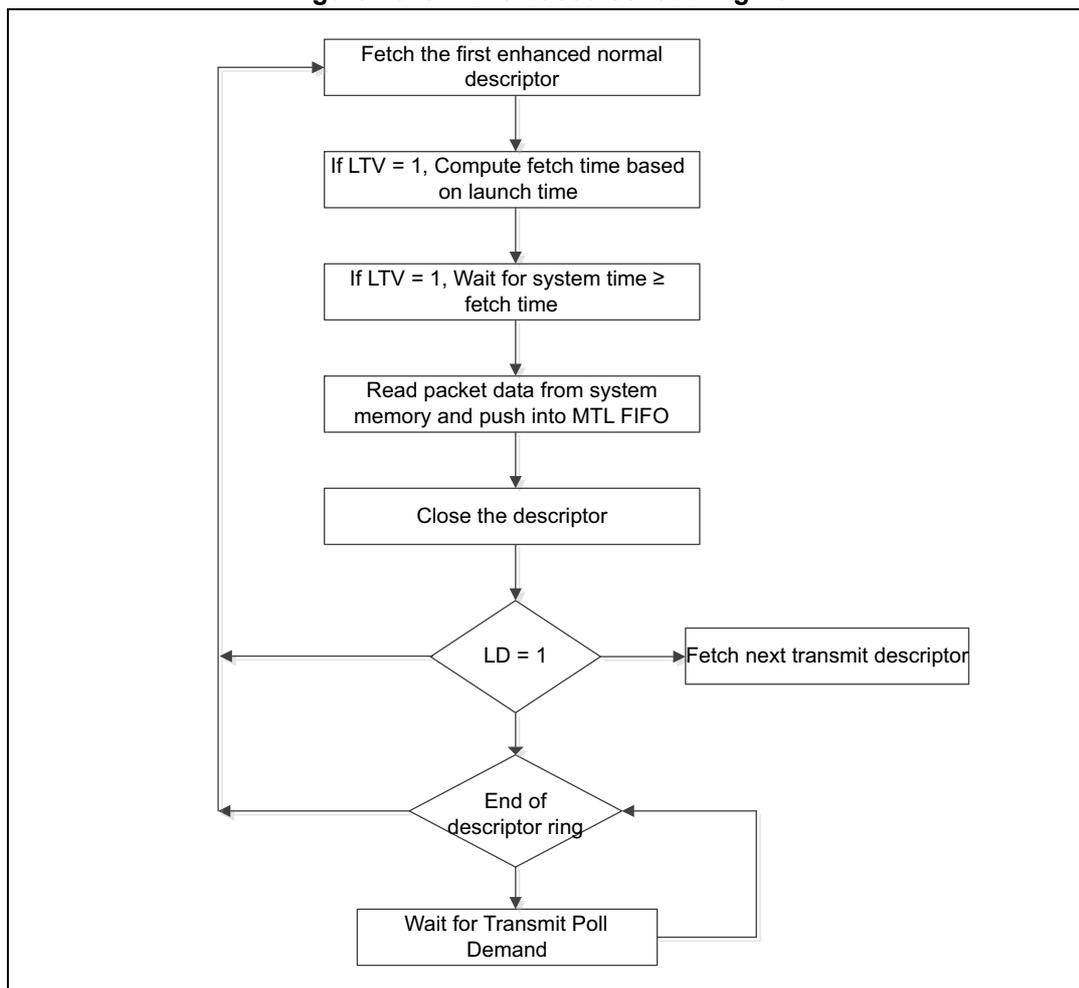

DMA transmission in default mode

The Tx DMA engine in default mode proceeds as follows:

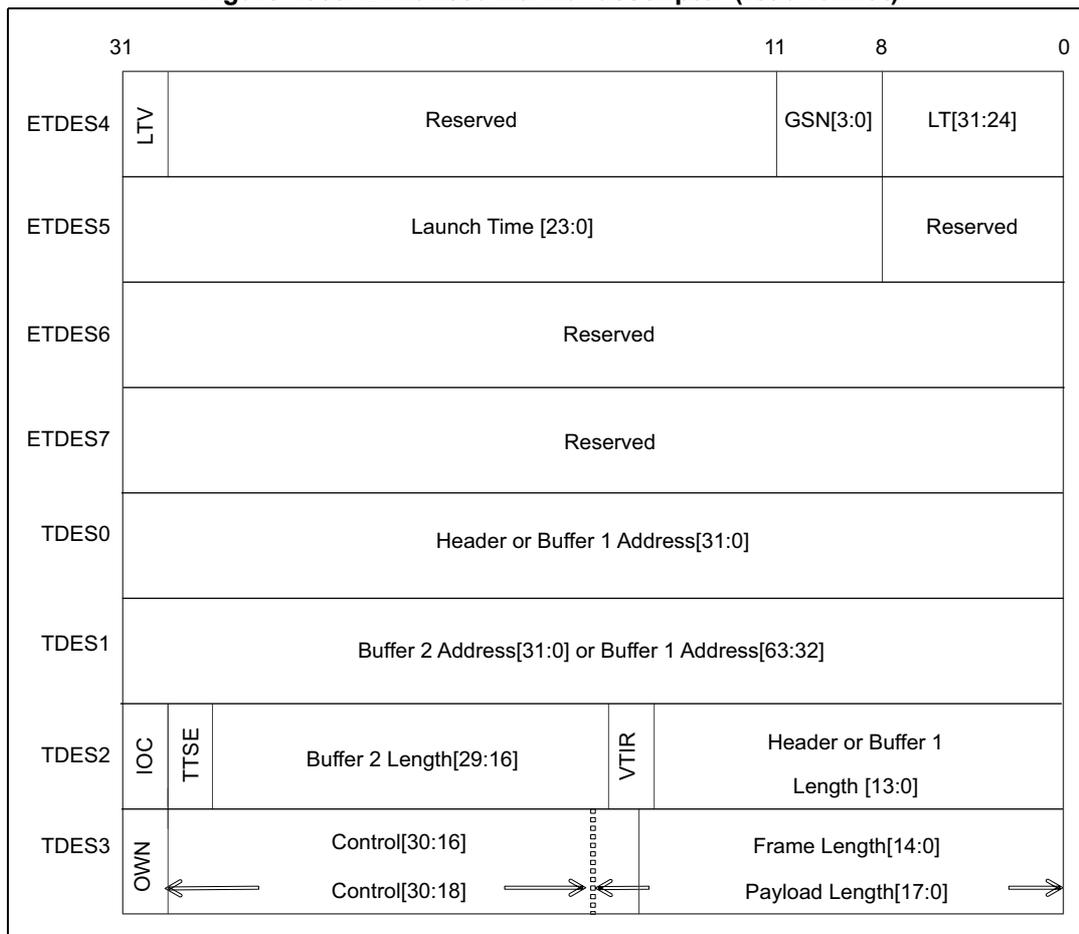

- 1. The application sets up the Transmit descriptor (TDES0–TDES3) and sets the Own bit (TDES0[31]) after setting up the corresponding data buffer(s) with Ethernet Packet data.

- 2. The application shifts the descriptor tail pointer offset value of the Transmit channel.

- 3. While in the Run state, the DMA runs an arbitration cycle to select the next Tx DMA channel from which the packets requiring transmission should be processed.

- 4. The DMA fetches the descriptor from the application memory.

- 5. If the DMA detects one of the following conditions, the transmission from that channel is suspended, bit 2 and 16 of the corresponding DMA channel Status register are set, and the Tx engine proceeds to step 11:

- – The descriptor is flagged as owned by the application (TDES3 [31] = 0).

- – The descriptor tail pointer is equal to the current descriptor pointer in Ring Descriptor list mode.

- – An error condition occurs.

- 6. If the acquired descriptor is flagged as owned by the DMA (TDES3[31] = 1), the DMA decodes the Transmit Data Buffer address from the acquired descriptor.

- 7. The DMA fetches the Transmit data from the system memory and transfers the data to the MTL for transmission.

- 8. If an Ethernet packet is stored over data buffers in multiple descriptors, the DMA closes the intermediate descriptor and fetches the next descriptor. Steps 3 through 7 are repeated until the end-of-Ethernet-packet data is transferred to the MTL.

- 9. When packet transmission is complete, if IEEE 1588 timestamp feature was enabled for the packet (as indicated in the Tx status), the timestamp value obtained from MTL is written to the Tx descriptor (TDES0 and TDES1) that contains the EOP buffer. The status information is written to this Tx descriptor (TDES3). The application now owns

this descriptor because the Own bit is cleared during this step. If the timestamp feature is disabled for this packet, the DMA does not alter TDES0 and TDES1 contents.

- 10. Bit 0 of Channel x status register (ETH_DMACxSR) is set after completing transmission of a packet that has Interrupt on Completion (TDES2[31]) set in its Last Descriptor. The DMA engine returns to step 3.

- 11. In the Suspend state, the DMA tries to acquire the descriptor again (and thereby return to step 3). A poll demand command is triggered by writing any value to the Channel x Tx descriptor tail pointer register (ETH_DMACxTXDTPR) when it receives a Transmit Poll demand and the underflow interrupt status bit is cleared. If the application stopped the DMA by clearing Bit 0 of Transmit control register of corresponding DMA channel, the DMA enters the Stop state.

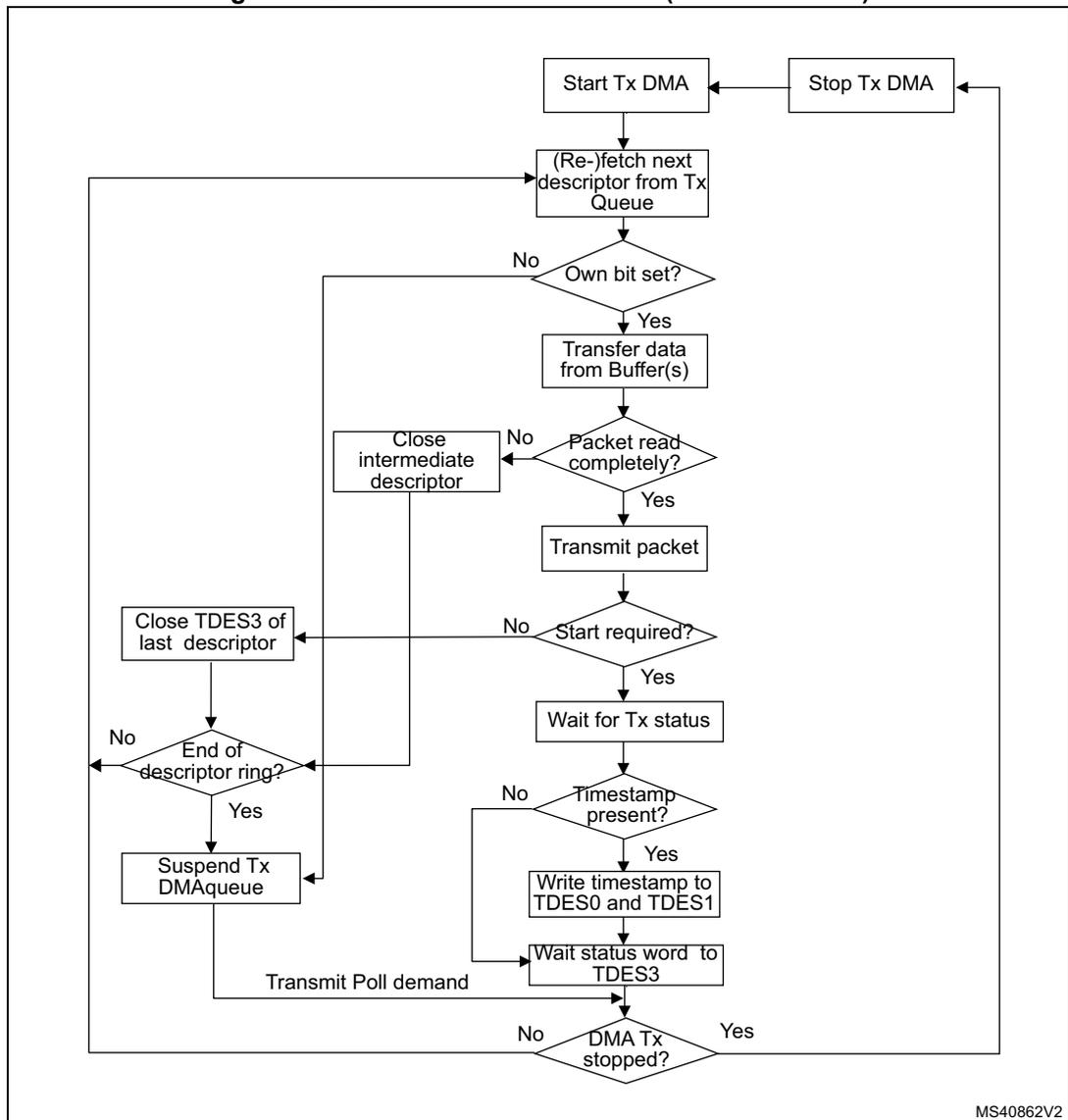

Figure 1020. DMA transmission flow (standard mode)

graph TD

StartTx[Start Tx DMA] --> Fetch[(Re-)fetch next descriptor from Tx Queue]

StopTx[Stop Tx DMA] --> Fetch

Fetch --> OwnBit{Own bit set?}

OwnBit -- No --> EndRing{End of descriptor ring?}

OwnBit -- Yes --> Transfer[Transfer data from Buffer(s)]

Transfer --> PacketRead{Packet read completely?}

PacketRead -- No --> CloseInt[Close intermediate descriptor]

PacketRead -- Yes --> Transmit[Transmit packet]

Transmit --> StartReq{Start required?}

StartReq -- No --> EndRing

StartReq -- Yes --> WaitTx[Wait for Tx status]

WaitTx --> Timestamp{Timestamp present?}

Timestamp -- No --> EndRing

Timestamp -- Yes --> WriteTS[Write timestamp to TDES0 and TDES1]

WriteTS --> WaitStatus[Wait status word to TDES3]

WaitStatus --> DMAStopped{DMA Tx stopped?}

DMAStopped -- Yes --> StopTx

DMAStopped -- No --> PollDemand[Transmit Poll demand]

PollDemand --> Fetch

EndRing -- Yes --> Suspend[Suspend Tx DMAqueue]

EndRing -- No --> CloseLast[Close TDES3 of last descriptor]

CloseLast --> Fetch

CloseInt --> FetchMS40862V2

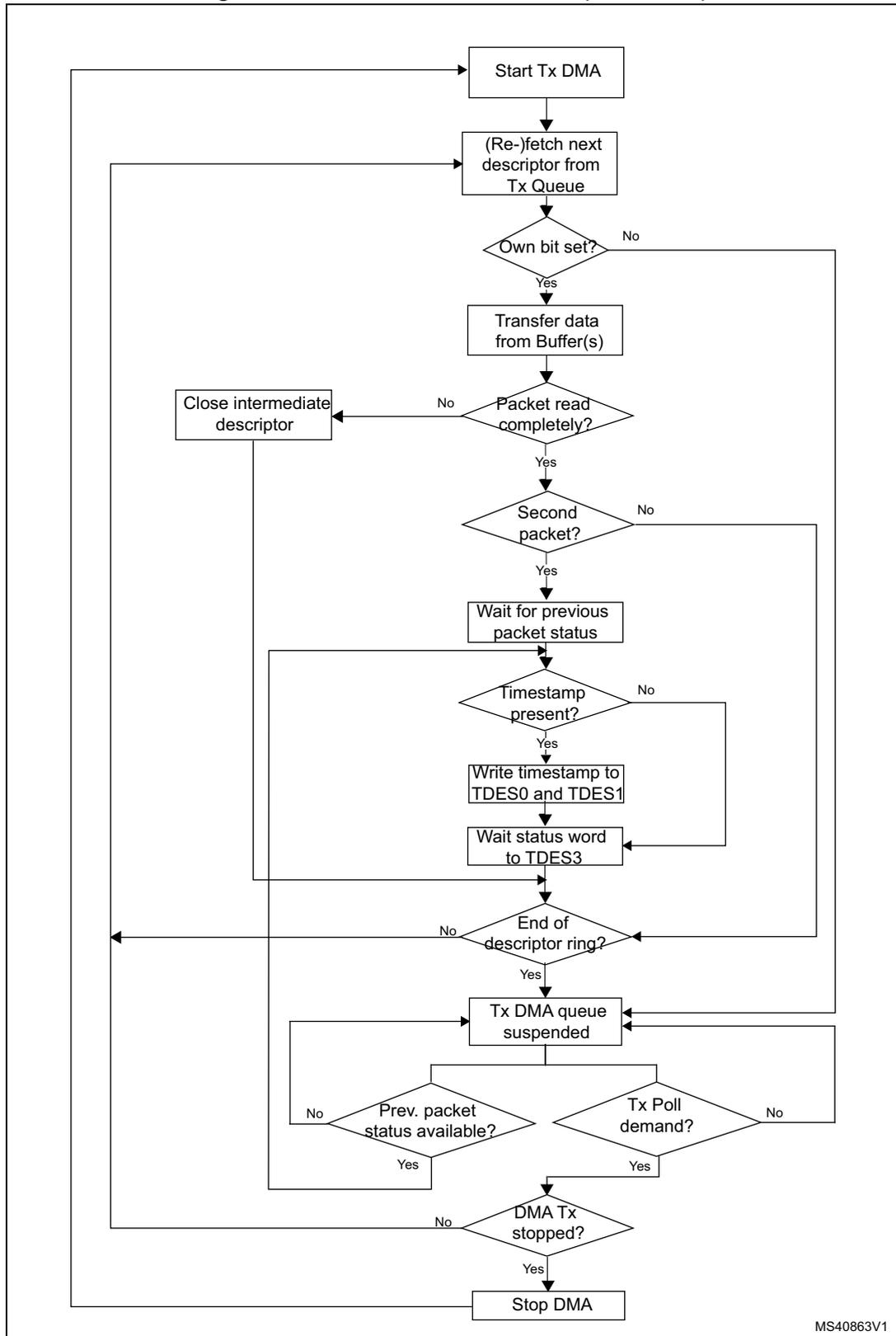

DMA transmission in OSP (operate on second packet) mode

In Run state, if bit 4 is set in the Channel x transmit control register (ETH_DMACxTXCR) , the Transmit process can simultaneously acquire two packets without closing the Status descriptor of the first packet. While the Transmit process completes the first packet transfer, it immediately polls the Transmit descriptor list for the second packet. If the second packet is valid, the Transmit process transfers this packet before writing the status information of the first packet.

In OSP mode, DMA transmission in the Run state operates as described in the following sequence:

- 1. The DMA executes steps 1 to 7 of the DMA transmission sequence in default mode (see Section : DMA transmission in default mode ).

- 2. The DMA fetches the next descriptor without closing previous packet last descriptor.

- 3. If the DMA owns the acquired descriptor, the DMA decodes the transmit buffer address in this descriptor. If the DMA does not own the descriptor, the DMA goes into Suspend mode and jumps to step 7.

- 4. The DMA fetches the Transmit packet from the system memory and transfers the packet to the MTL until the EOP data is transferred, closing the intermediate descriptors if this packet is split across multiple descriptors.

- 5. The DMA waits for the packet transmission status and timestamp of previous packet. When the status is available, the DMA writes the timestamp to TDES0 and TDES1 if such timestamp was captured (as indicated by a status bit). The DMA writes the status, with a cleared Own bit, to the corresponding TDES3, thus closing the descriptor. If Timestamp feature is not enabled for the previous packet, the DMA does not alter the contents of TDES2 and TDES3.

- 6. The Transmit interrupt is set (if enabled). The DMA fetches the next descriptor and proceeds to step 3 (when Status is normal). If the previous transmission status shows an underflow error, the DMA goes into Suspend mode (step 7).

- 7. In Suspend mode, if a pending status and timestamp are received from the MTL, the DMA performs the following operations:

- a) The DMA writes the timestamp (if enabled for the current packet) to TDES2 and TDES3.

- a) The DMA writes the status to the corresponding TDES3.

- a) The DMA sets the relevant interrupts and returns to Suspend mode.

- 8. The DMA can exit Suspend mode and enter the Run state (it goes either to step 1 or to step 2 depending on pending status) only after receiving a Transmit Poll demand in the transmit descriptor tail pointer register of corresponding channel.

A description of the basic DMA transmission flow in OSP mode is given in Figure 1022: Receive DMA flow .

Figure 1021. DMA transmission flow (OSP mode)

graph TD

Start[Start Tx DMA] --> Fetch[(Re-)fetch next descriptor from Tx Queue]

Fetch --> OwnBit{Own bit set?}

OwnBit -- No --> EndRing{End of descriptor ring?}

OwnBit -- Yes --> Transfer[Transfer data from Buffer(s)]

Transfer --> ReadComplete{Packet read completely?}

ReadComplete -- No --> CloseDesc[Close intermediate descriptor]

ReadComplete -- Yes --> SecondPacket{Second packet?}

SecondPacket -- No --> EndRing

SecondPacket -- Yes --> WaitStatus[Wait for previous packet status]

WaitStatus --> TimestampPresent{Timestamp present?}

TimestampPresent -- No --> EndRing

TimestampPresent -- Yes --> WriteTimestamp[Write timestamp to TDES0 and TDES1]

WriteTimestamp --> WaitStatusWord[Wait status word to TDES3]

WaitStatusWord --> EndRing

EndRing -- No --> Fetch

EndRing -- Yes --> Suspended[Tx DMA queue suspended]

Suspended --> PrevPacketStatus{Prev. packet status available?}

PrevPacketStatus -- Yes --> DMAStopped{DMA Tx stopped?}

PrevPacketStatus -- No --> TxDMAQueueSuspended[Tx DMA queue suspended]

TxDMAQueueSuspended --> TxDemand{Tx Poll demand?}

TxDemand -- Yes --> DMAStopped

TxDemand -- No --> DMAStopped

DMAStopped -- Yes --> StopDMA[Stop DMA]

DMAStopped -- No --> Fetch

CloseDesc --> EndRing

MS40863V1[MS40863V1]

style MS40863V1 fill:none,stroke:none

The flowchart illustrates the DMA transmission process in OSP mode. It begins with 'Start Tx DMA', followed by '(Re-)fetch next descriptor from Tx Queue'. A decision 'Own bit set?' follows; if 'No', it proceeds to 'End of descriptor ring?'; if 'Yes', it goes to 'Transfer data from Buffer(s)'. From 'Transfer data from Buffer(s)', a decision 'Packet read completely?' follows; if 'No', it goes to 'Close intermediate descriptor' and then to 'End of descriptor ring?'; if 'Yes', it proceeds to 'Second packet?'. If 'Second packet?' is 'No', it goes to 'End of descriptor ring?'; if 'Yes', it goes to 'Wait for previous packet status'. From 'Wait for previous packet status', a decision 'Timestamp present?' follows; if 'No', it goes to 'End of descriptor ring?'; if 'Yes', it goes to 'Write timestamp to TDES0 and TDES1', then 'Wait status word to TDES3', and finally to 'End of descriptor ring?'. From 'End of descriptor ring?', if 'No', it loops back to '(Re-)fetch next descriptor from Tx Queue'; if 'Yes', it goes to 'Tx DMA queue suspended'. From 'Tx DMA queue suspended', a decision 'Prev. packet status available?' follows; if 'Yes', it goes to 'DMA Tx stopped?'; if 'No', it loops back to 'Tx DMA queue suspended'. From 'Tx DMA queue suspended', a decision 'Tx Poll demand?' follows; if 'Yes', it goes to 'DMA Tx stopped?'; if 'No', it goes to 'DMA Tx stopped?'. From 'DMA Tx stopped?', if 'Yes', it goes to 'Stop DMA'; if 'No', it loops back to '(Re-)fetch next descriptor from Tx Queue'. A label 'MS40863V1' is present in the bottom right corner.

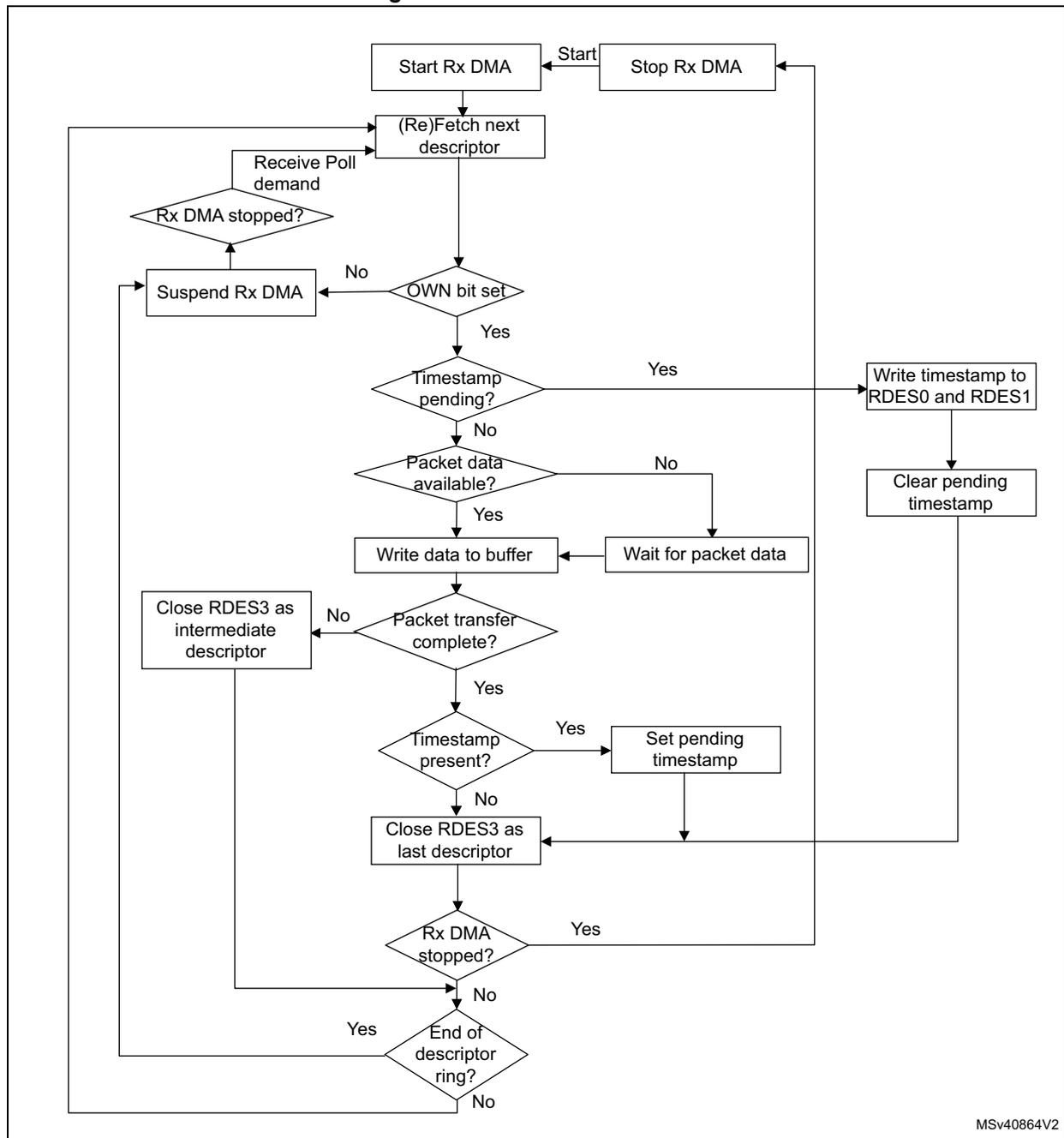

DMA reception

In the receive path, the DMA reads a packet from the MTL receive queue and writes it to the packet data buffers of the corresponding DMA channel.

The DMA Rx descriptor ring structure is described in Section 76.10: Descriptors .

The reception sequence for Rx DMA engine is as follows (see also Figure 1022: Receive DMA flow ):

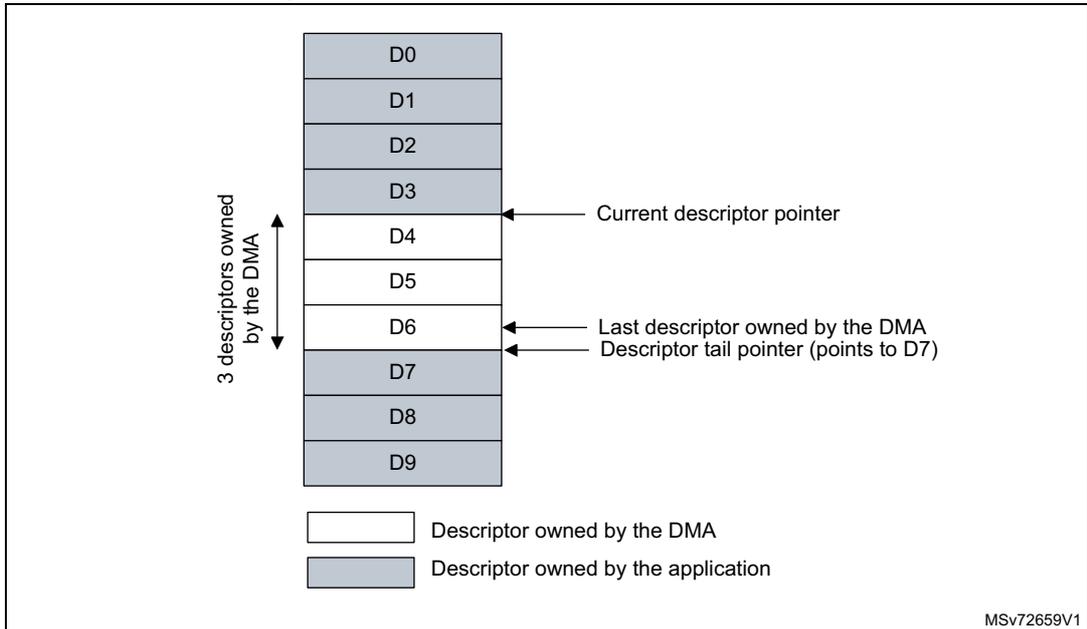

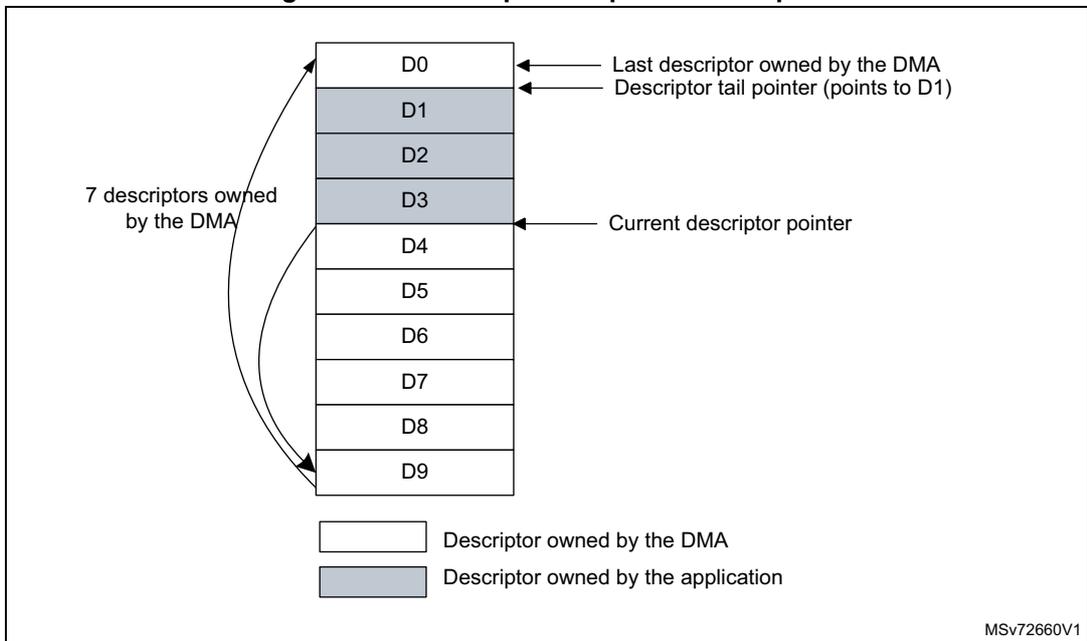

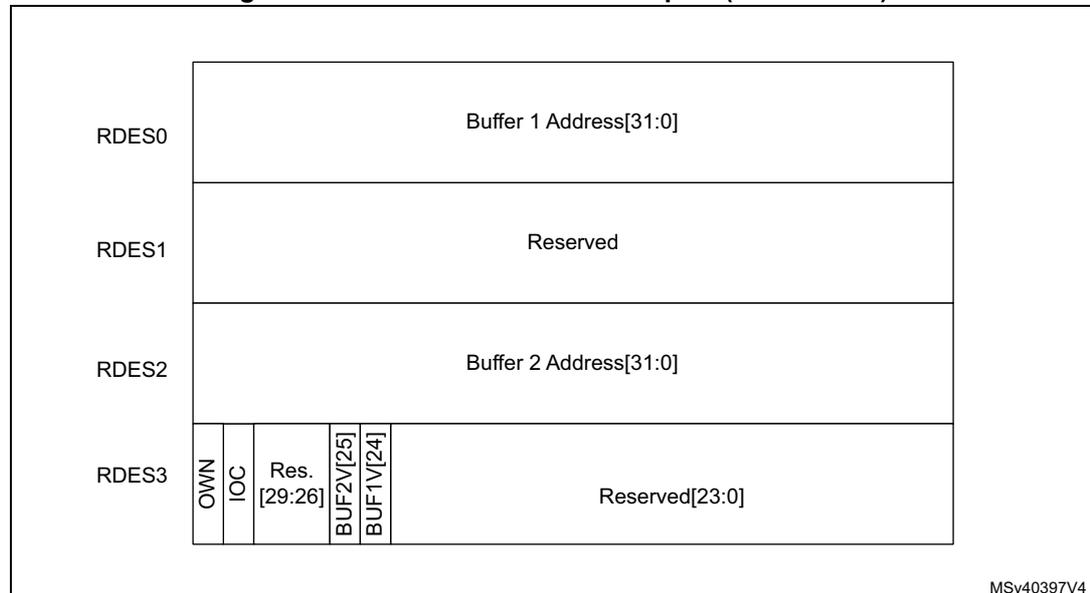

- 1. The application sets up the Rx descriptors (RDES0-RDES3) and the Own bit (RDES3[31]). The application should set the correct value in the receive descriptor tail pointer register of corresponding DMA channel to indicate the location of the last valid descriptor for the DMA. If the tail pointer points to descriptor N, the last valid descriptor for the DMA is descriptor N - 1.

- 2. When bit 0 of Channel x receive control register (ETH_DMAxCxRXCR) is set, the DMA enters the Run state. The DMA looks for free descriptors based on the Rx Current Descriptor and Descriptor tail pointer register values. The descriptors referenced between the current descriptor and the tail pointer registers are available for the DMA. If there are no free descriptors, the DMA channel enters the Suspend state and goes to step 11.

- 3. The DMA fetches the next available descriptor in the ring and decodes the receive data buffer address from acquired descriptors.

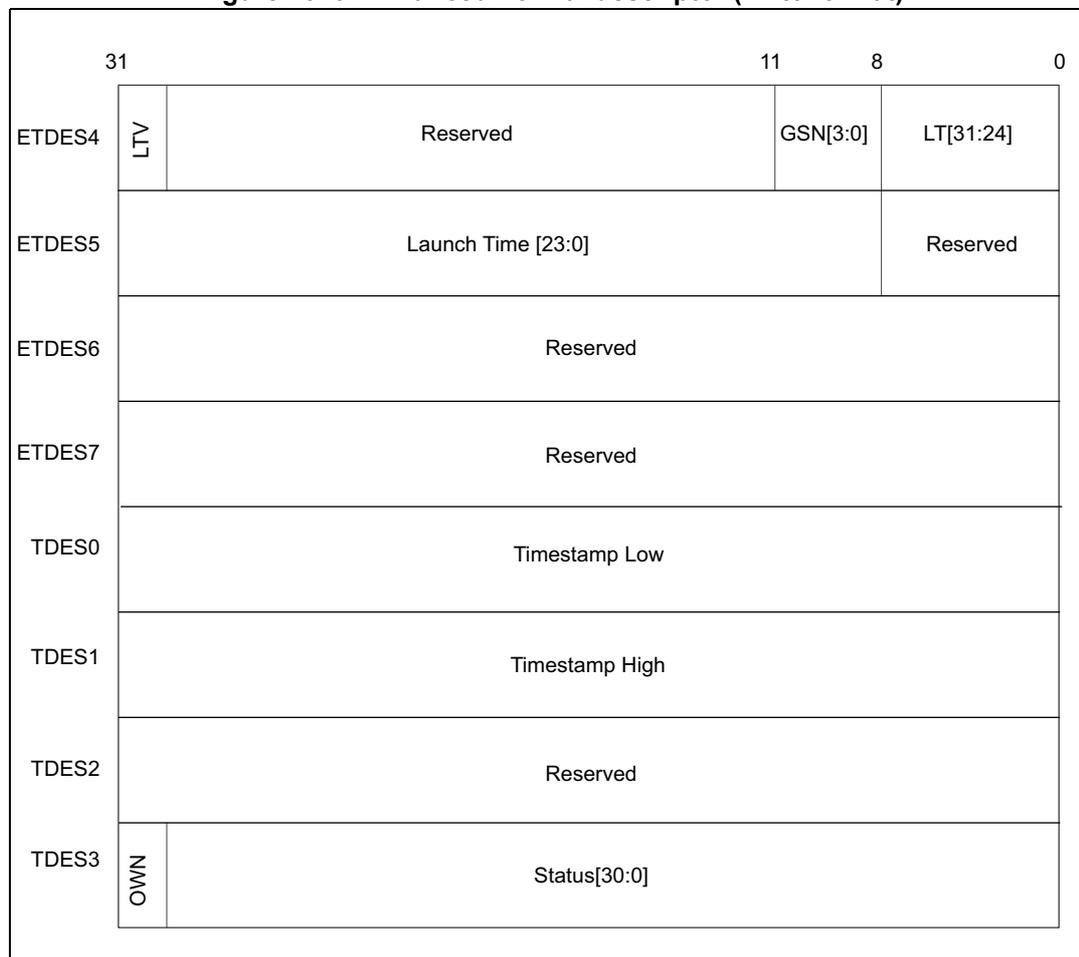

- 4. If IEEE 1588 timestamping is enabled and the timestamp is available for the previous packet, the DMA writes the timestamp (if available) to the RDES0 and RDES1 of current descriptor and sets the CTXT field (RDES3[30]).

- 5. The DMA processes the incoming packets and stores them in the data buffers of acquired descriptor.

- 6. If the current packet transfer is not complete, the DMA closes the current descriptor as intermediate and goes to step 10.

- 7. The DMA retrieves the status of the receive frame from the MTL and writes the status word to current descriptor with the Own bit cleared and the Last descriptor bit set.

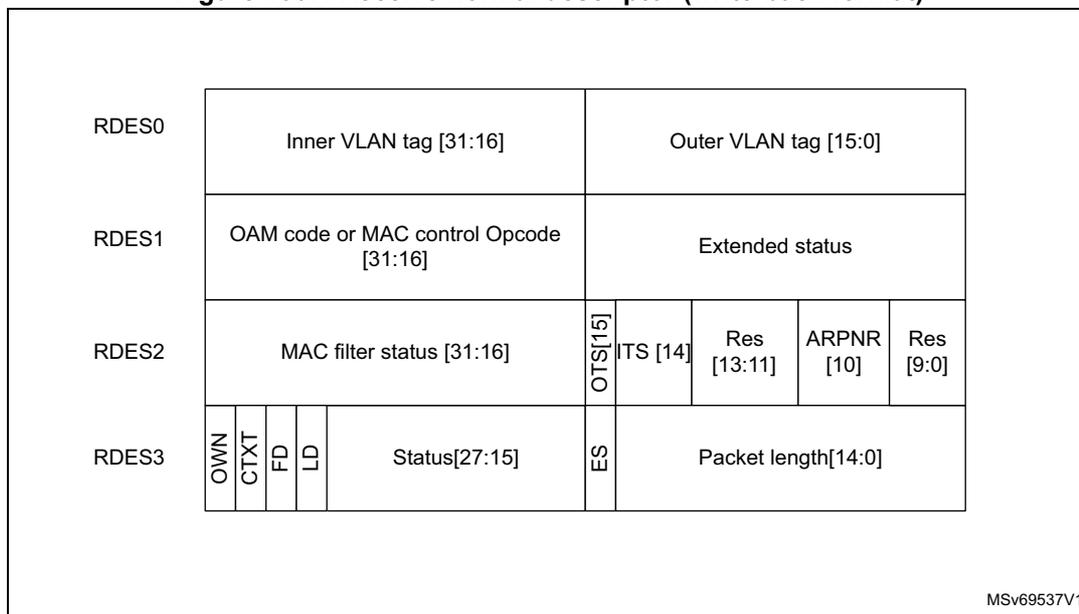

- 8. The DMA writes the Frame Length to RDES3 and the VLAN tag to RDES0. The DMA also writes the MAC control frame opcode, OAM control frame code, and extended status information (if available) to RDES1 of the last descriptor.

- 9. The DMA stores the timestamp (if available). The DMA writes the context descriptor after the last descriptor for the current packet (in the next available descriptor).

- 10. If more descriptors are available in the Rx DMA descriptor ring, go to step 3, otherwise go to the Suspend state (step 11).

- 11. The receive DMA exits the Suspend state when a receive Poll demand is given, and the application updates the channel receive descriptor tail pointer register to indicate the location of the last valid descriptor for DMA. Then, the engine proceeds to step 2 and fetches again the next descriptor.

Note: Refer to Section : Descriptor tail pointer handling examples for updating the correct value in receive descriptor tail pointer register.

Figure 1022. Receive DMA flow

graph TD

Start[Start Rx DMA] -- Start --> Stop[Stop Rx DMA]

Stop --> Fetch[(Re)Fetch next descriptor]

Fetch --> Poll{Receive Poll demand}

Poll --> Stopped{Rx DMA stopped?}

Stopped -- No --> OWN{OWN bit set}

OWN -- No --> Suspend[Suspend Rx DMA]

OWN -- Yes --> TimestampPending{Timestamp pending?}

TimestampPending -- Yes --> WriteTimestamp[Write timestamp to RDES0 and RDES1]

WriteTimestamp --> ClearTimestamp[Clear pending timestamp]

TimestampPending -- No --> PacketData{Packet data available?}

PacketData -- No --> Wait[Wait for packet data]

PacketData -- Yes --> WriteData[Write data to buffer]

Wait --> WriteData

WriteData --> TransferComplete{Packet transfer complete?}

TransferComplete -- No --> CloseIntermediate[Close RDES3 as intermediate descriptor]

TransferComplete -- Yes --> TimestampPresent{Timestamp present?}

TimestampPresent -- Yes --> SetPending[Set pending timestamp]

SetPending --> Stopped

TimestampPresent -- No --> CloseLast[Close RDES3 as last descriptor]

CloseLast --> Stopped

CloseIntermediate --> RingEnd{End of descriptor ring?}

Stopped -- No --> RingEnd

RingEnd -- Yes --> Suspend

RingEnd -- No --> Fetch

MSv40864V2

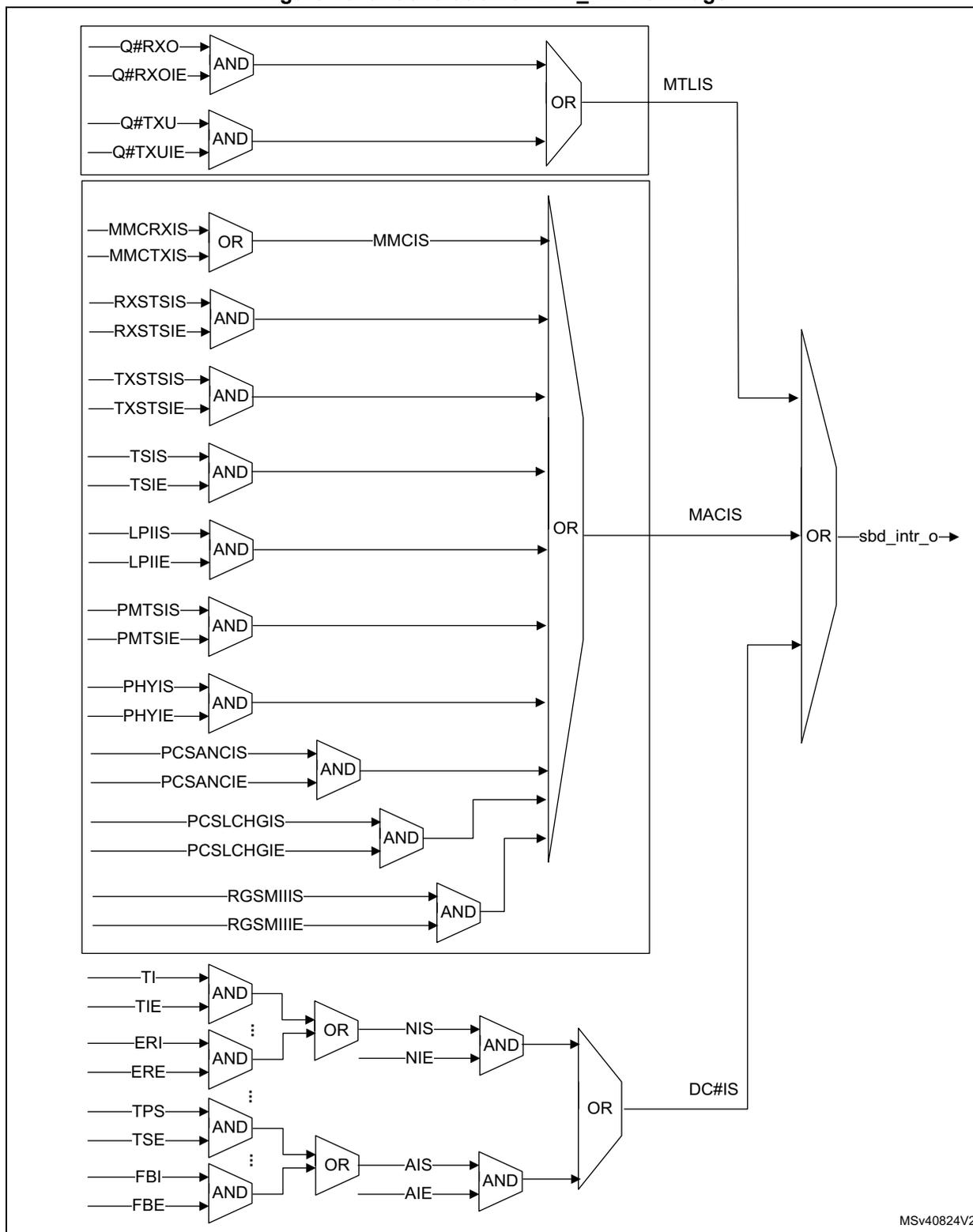

Priority scheme for Tx DMA and Rx DMA

The DMA arbiter performs the arbitration between the Tx and Rx paths of DMA channel 0 to access descriptors and data buffers.

If the Tx DMA and Rx DMA of a given channel are enabled, the DMA which gets the bus when the channel gets control of the bus must be specified. The priority between the corresponding Tx DMA and Rx DMA can be configured through the TXPR field of the DMA mode register (ETH_DMAMR) .

76.4.2 MTL

The MAC Transaction Layer (MTL) provides the FIFO memory interface to buffer and regulate the packets between the application system memory and the MAC. It also enables the data to be transferred between the application clock and MAC clock domains. The MTL layer features two 64-bit wide data paths: the Transmit path and the receive path.

- •

Transmit path

The application or internal DMA pushes the Ethernet packets read from the application or system memory into the corresponding queue in Tx FIFO. The packet is then popped out and transferred to the MAC when the queue threshold is reached (threshold mode) or complete packet is in the queue (store-and-forward mode). When EOP is transferred, the status of the transmission is taken from the MAC and transferred back to the application or internal DMA. The Tx queue size is 4096 bytes. - •

Receive path

The MTL Rx module receives the packets from the MAC and pushes them into the Rx queue. The status (fill level) of the queue is indicated to the application or to DMA when it crosses the configured receive threshold (RTC bits[1:0] defined in the operating mode register of the corresponding queue), or when the complete packet was received. The MTL also indicates the queue fill level so that the DMA can initiate preconfigured burst transfers towards the master interface. The Rx queue size is 4096 bytes.

76.4.3 MAC

The MAC is responsible of the Ethernet protocol processing. In Transmission mode, it receives data from MTL before transferring it to the PHY interface. In Reception mode, the MAC receives data from the PHY interface before transferring them to the Rx FIFO of the MTL module.

This section briefly describes transmission and reception sequences.

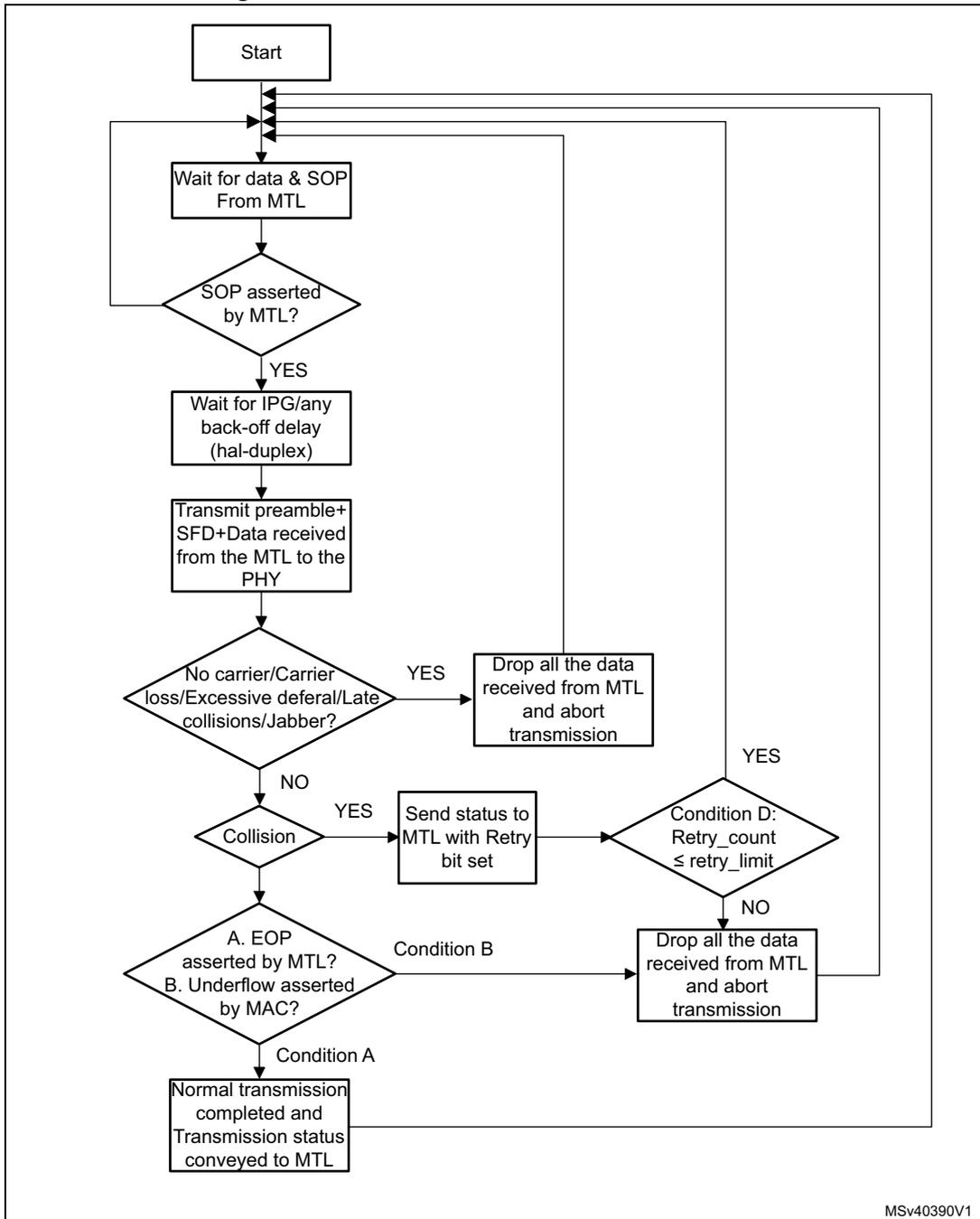

MAC transmission

The transmission sequence is as follows:

- 1. Transmission is initiated when the MTL application pushes in data with the SOP (Start of packet) signal asserted.

- 2. When the SOP signal is detected, the MAC accepts the data and begins the transmission to the GMII or MII.

- 3. When the EOP (End of packet) is transferred to the MAC, the MAC does one of the following:

- – The MAC completes the normal transmission and provides the transmission status to the MTL.

- – If a normal collision (in Half-duplex mode) occurs during transmission, the MAC provides the Transmit status to the MTL, with the Retry bit set. The MAC provides the Retry request till one of the following is true:

- the packet was successfully transmitted;

- the maximum number of Retry requests expires. In this case, the MAC aborts the packet transmission with Excessive Collision Transmit status. The MAC accepts and drops all further data until the next SOP is received. The MTL block should retransmit the same packet from SOP when a Retry request (in the Status) is observed from the MAC.

- – If any one of the following event happens, the MAC aborts the packet transmission:

- no carrier (Half-duplex mode)

- loss of carrier (Half-duplex mode)

- excessive deferral (Half-duplex mode)

- late collisions (Half-duplex mode)

- jabber

the MAC accepts and drops all further data until the next SOP is received.

- 4. The MAC issues an underflow status if the MTL is not able to provide the data continuously during the transmission. The MAC accepts and drops all further data until the next SOP is received.

- 5. During the normal transfer of a packet from MTL, if the MAC receives a SOP without getting an EOP for the previous packet, it ignores the SOP and considers the new packet as continuation of the previous packet.

Figure 1023: Overview of MAC transmission flow illustrates the MAC transmission process flow.

Figure 1023. Overview of MAC transmission flow

graph TD; Start[Start] --> WaitSOP[Wait for data & SOP From MTL]; WaitSOP --> SOPAsserted{SOP asserted by MTL?}; SOPAsserted -- YES --> WaitIPG[Wait for IPG/any back-off delay hal-duplex]; SOPAsserted -- NO --> WaitSOP; WaitIPG --> Transmit[Transmit preamble+SFD+Data received from the MTL to the PHY]; Transmit --> NoCarrier{No carrier/Carrier loss/Excessive defer/Late collisions/Jabber?}; NoCarrier -- YES --> DropData1[Drop all the data received from MTL and abort transmission]; NoCarrier -- NO --> Collision{Collision}; Collision -- YES --> SendStatus[Send status to MTL with Retry bit set]; SendStatus --> ConditionD{Condition D: Retry_count ≤ retry_limit}; ConditionD -- YES --> WaitSOP; ConditionD -- NO --> DropData2[Drop all the data received from MTL and abort transmission]; Collision -- NO --> EOPUnderflow{A. EOP asserted by MTL? B. Underflow asserted by MAC?}; EOPUnderflow -- Condition A --> NormalTrans[Normal transmission completed and Transmission status conveyed to MTL]; EOPUnderflow -- Condition B --> DropData2; NormalTrans --> WaitSOP; DropData1 --> WaitSOP; DropData2 --> WaitSOP;MSv40390V1

MAC reception

A receive operation is initiated when the MAC detects an SFD on GMII. The MAC strips the preamble and SFD before proceeding to process the packet. The header fields are checked for filtering and the FCS field used to verify the CRC for the packet. The received packet is stored in a shallow buffer until the address filtering is performed. The packet is dropped in the MAC if it fails the address filter.

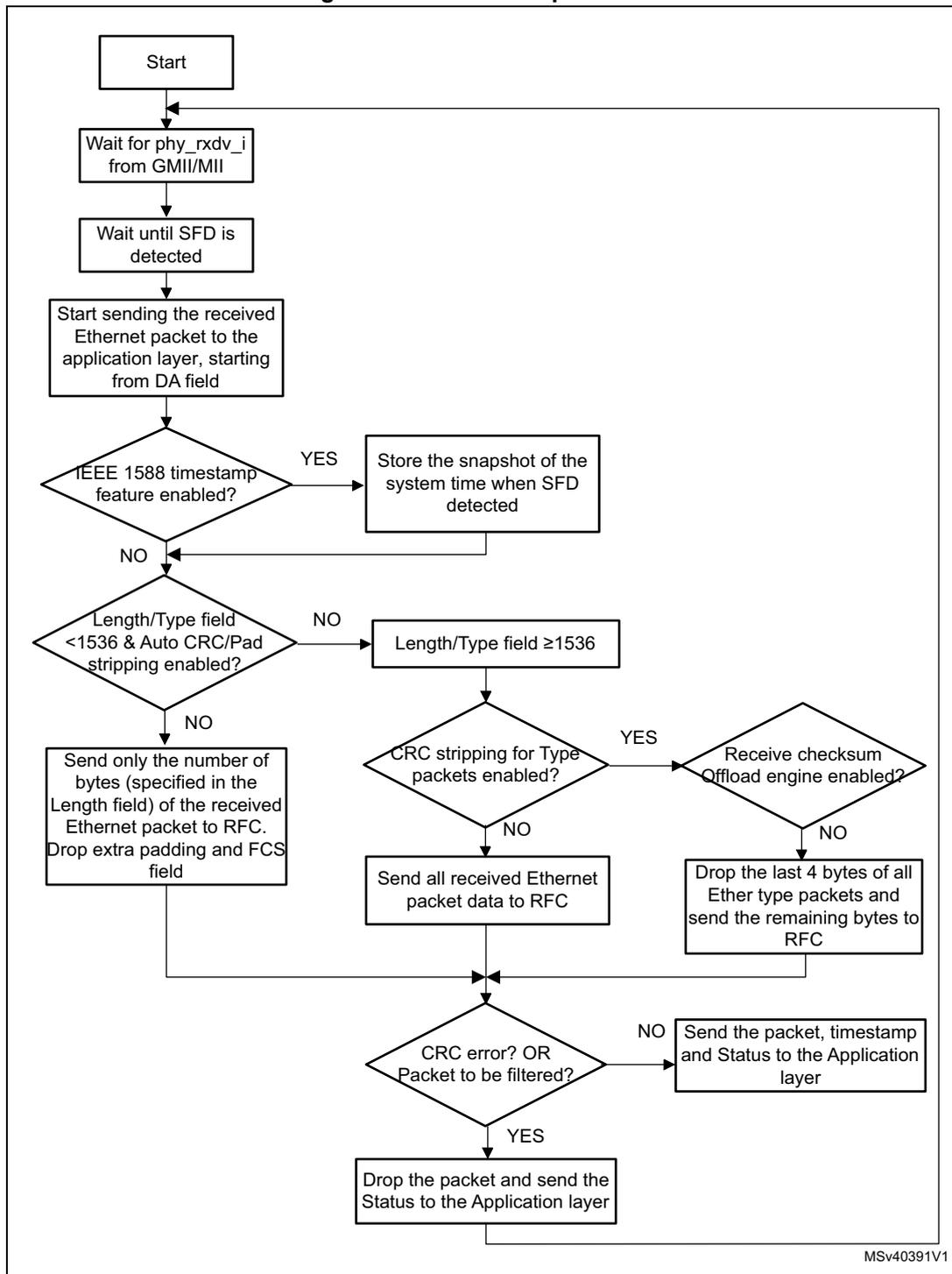

The reception sequence is as follows:

- 1. When the receive data valid signal (RxDV) of GMII or MII becomes active, the receive State Machine (RSM) starts looking for the SFD field (0x5D byte).

The state machine drops received packets until it detects SFD.

- 2. When SFD is detected, the state machine starts sending the data of Ethernet packet to the RPC module, beginning with the first byte following the SFD (destination address).

- 3. If IEEE 1588 timestamp feature is enabled, the MAC takes a snapshot of the system time at which SFD of any packet is detected on GMII or MII. If this packet is not dropped during MAC filtering, the timestamp is passed to the application. The receive state machine decodes the Length/Type field of the Ethernet packet being received.

If the Length/Type field is less than 1,536 and if the MAC is programmed for the Auto CRC/Pad Stripping (bit 20 of the Operating mode configuration register (ETH_MACCR) ), the state machine sends the packet data up to the count specified in the Length/Type field and starts dropping bytes (including the FCS field). The state machine decodes the Length/Type field and checks for the Length interpretation.

- 4. If the Length/Type field is greater than or equal to 1,536, the RPE module sends all received Ethernet packet data to the RFC module if you have not enabled the CRC stripping for Type packet in Bit 21 of the Operating mode configuration register (ETH_MACCR) . However, if the CRC stripping has been enabled for Type packets and not enabled the receive checksum offload engine, the MAC strips and drops the last 4 bytes of all packets of ether type before forwarding the packets to the application.

- 5. By default, the MAC is programmed for watchdog timer to be enabled, that is, packets above 2,048 (10,240 if Jumbo Packet is enabled) bytes (DA + SA + LT + DATA + PAD + FCS) are cut off at the RPE module. In addition, you can use a programmable watchdog timer (bit 16 of Watchdog timeout register (ETH_MACWTR) ) to override the fixed timeout of 2,048 or 10,240 bytes. You can disable the watchdog timer by programming bit 19 of Operating mode configuration register (ETH_MACCR) . However, even if the watchdog timer is disabled, a packet greater than 32 Kbytes is cut off and a watchdog timeout status is given.

Figure 1024. MAC reception flow

graph TD

Start([Start]) --> Wait1[Wait for phy_rxdv_i from GMII/MII]

Wait1 --> Wait2[Wait until SFD is detected]

Wait2 --> SendDA[Start sending the received Ethernet packet to the application layer, starting from DA field]

SendDA --> IEEE1588{IEEE 1588 timestamp feature enabled?}

IEEE1588 -- YES --> StoreTime[Store the snapshot of the system time when SFD detected]

IEEE1588 -- NO --> LengthType{Length/Type field <1536 & Auto CRC/Pad stripping enabled?}

StoreTime --> LengthType

LengthType -- NO --> LengthGE1536[Length/Type field ≥1536]

LengthType -- NO --> SendOnly[Send only the number of bytes (specified in the Length field) of the received Ethernet packet to RFC. Drop extra padding and FCS field]

LengthGE1536 --> CRCStrip{CRC stripping for Type packets enabled?}

CRCStrip -- YES --> ChecksumOffload{Receive checksum Offload engine enabled?}

CRCStrip -- NO --> SendAll[Send all received Ethernet packet data to RFC]

ChecksumOffload -- YES --> DropLast4[Drop the last 4 bytes of all Ether type packets and send the remaining bytes to RFC]

ChecksumOffload -- NO --> DropLast4

SendOnly --> CRCError{CRC error? OR Packet to be filtered?}

SendAll --> CRCError

DropLast4 --> CRCError

CRCError -- NO --> SendPacket[Send the packet, timestamp and Status to the Application layer]

CRCError -- YES --> DropPacket[Drop the packet and send the Status to the Application layer]

DropPacket --> Start

SendPacket --> Start

DropLast4 --> Start

SendAll --> Start

SendOnly --> Start

MSv40391V1

76.4.4 Multiple channels and queues support

This chapter describes how the Ethernet peripheral core supports multiple queues and channels.

Two queues on Rx side and two queues on Tx side are supported. Two DMA channels are implemented on Tx side, one channel per queue. Two DMA channels are implemented on Rx side, one channel per queue.

The multiple queues enable to support the Audio video bridging (AVB) protocol.

Multiple queues and channels support in the Transmit path

The number of Tx DMA channels is equal to the number of Tx queues, and is direct one-to-one mapping. This enables the interleaving of packet/data transfer of multiple Tx DMA on the host/system bus, and each Tx queue is reserved for the corresponding Tx DMA. Therefore, the integrity of packet transfer by each Tx DMA is maintained in the Tx queue and enables efficient utilization of the host bus for data transfers among multiple Tx DMA without depending on the packet length, Transmit buffer availability and so on.

If two Tx DMAs are allowed to transfer data into the same Tx queue, when a Tx DMA starts a packet transfer, the other Tx DMA cannot transfer data to the same Tx queue unless the previous packet transfer is complete. This means that the second DMA remains idle until the first packet transferred is complete, which is effectively a one-to-one mapping of the Tx DMA to the Tx queue.

The Ethernet peripheral supports multiple Tx channels. The priority scheme between both channels is fixed priority. In fixed priority scheme, the channel with the highest priority always wins the arbitration when it requests the bus, as shown in Table 764 .

Table 764. Fixed priority scheme for DMA channels

| Priority level | Channel |

|---|---|

| 0 | Channel 0 |

| 1 | Channel 1 |

The fixed priority scheme does not necessarily cause the “starving” of lower priority channels for the AXI bus because of the capabilities of the AXI protocol and characteristics of the TxDMA, described as follows:

- • Read command requests from a TxDMA for a burst of data transfers are driven on a separate AXI channel, and their execution takes one clock cycle. The actual data transfer starts on a separate AXI channel only after the request is accepted. It takes several clock cycles to complete with relatively large read access latencies.

- • The AXI master is free to issue subsequent requests even before the previous data transfers are complete.

- • A TxDMA requests another data transfer only after the data transfer corresponding to its previous request is complete and transferred to the MTL Tx queue and space is available in Tx queue to accept the next request.

- • The Ethernet peripheral can be programmed to control the maximum number of outstanding requests, requested burst sizes by DMA, and the burst sizes of each data transfer on the AXI bus.

Considering the previous points, the Ethernet peripheral can be programmed so that the requests of all TxDMAs are placed and executed on the AXI bus before the data transfer of the first TxDMA is complete and it raises the next request to the arbiter. For example, in a 64-bit AXI data bus, proceed as follows:

- 1. TxDMA PBL = 64 (512 bytes).

- 2. Number of outstanding AXI read requests = 16.

- 3. Maximum burst length on AXI (BLEN) = 32 (256 bytes).

- 4. Number of active TxDMAs = 8.

Assuming that all TxDMAs place a request simultaneously and get serviced by the fixed priority algorithm, all the requests are placed on the AXI bus in a window of 32 clocks (two clocks per AXI request, two AXI burst requests per TxDMA request). The data transfer of the first request takes 32 clock cycles + the read-access latencies (assuming that there are tens of cycles). So, the TxDMA arbiter is already IDLE and has completed servicing all the TxDMA requests before this data transfer completes.

Effectively, all the TxDMA channels get equal access to AXI bus and the corresponding Tx queues get filled up at the same rate. The data gets read out from the Tx queues as per the traffic class scheduler in the MTL. So at a steady state, the bandwidth for each channel is controlled by the priorities and settings of the traffic scheduler in the MTL.

Programming guidelines for multiple queues and channels in the Transmit path

See Section 76.9.8: Programming guidelines for multichannel multiqueue operation on page 4128 .

Multiple queues and channels support in the receive path

The Ethernet controller supports independent selection of the number of Rx DMA channels and the number of Rx queues in the MTL Rx buffer. Therefore, the packets from any Rx queue can be serviced by any of the Rx DMA. As all the packets of Rx queues are stored in a shared RxFIFO buffer in MTL, the Rx scheduler selects the Rx queue whose packet data are to be transferred to the destination Rx DMA, which then forwards the packet data to the host memory. The sequence of events in time is as follows:

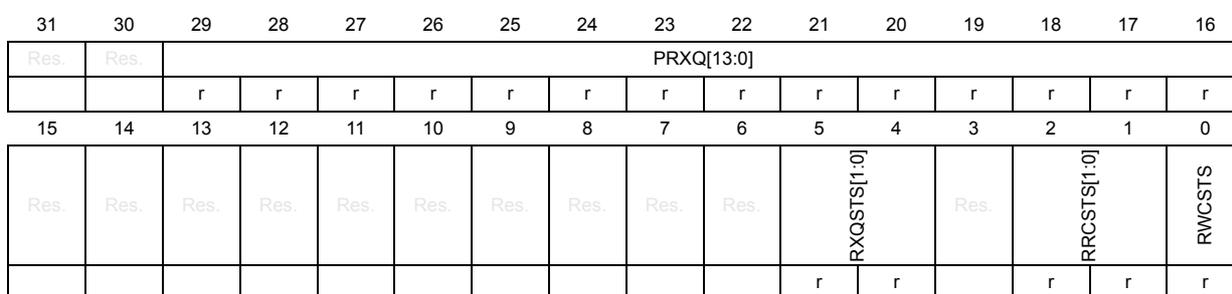

- 1. Each Rx DMA indicates whether it is ready to transfer data, that is, when the Rx DMA has fetched the descriptor and has a receiver buffer ready to accept the packet data. Each Rx DMA also indicates the number of words that it can transfer, based on the space available in the Rx buffer and the value programmed in the RXPBL[5:0] bitfield of its Channel x receive control register (ETH_DMACxRXCR) .

- 2. The MTL Rx scheduler matches the number of bytes/packets available for transfer at the top of all Rx queues with the corresponding Rx DMA ready status and the number of bytes requested by it.

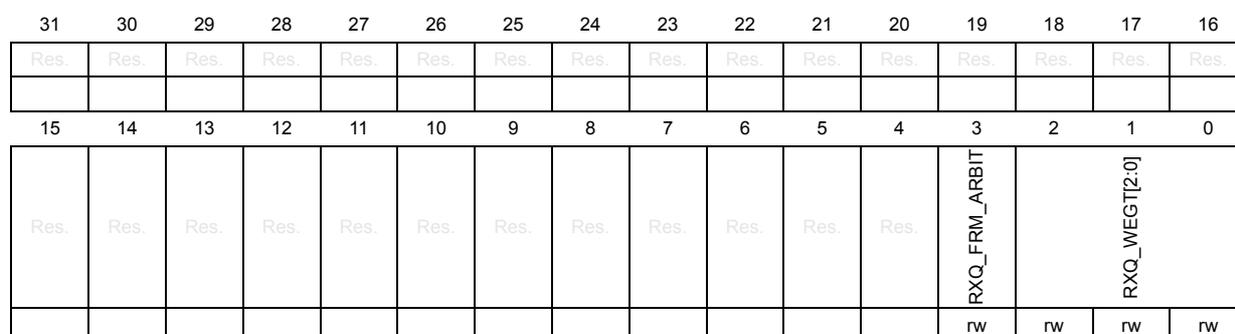

- 3. If there are multiple successful matches, the scheduler selects the Rx queue to be serviced, based on the arbitration schemes (Strict priority or Weighted Strict priority) decided by the RAA field of the Operating mode register (ETH_MTLOMR) . In the Weighted Strict priority scheme, the weight of each Rx queue is set in the RXQ_WEGT[2:0] bitfield of the corresponding Rx queue x control register (ETH_MTLRXQxCR) .

- 4. The MTL Rx controller fetches the data of the selected Rx queue from the shared RxFIFO memory and starts the transfer of the requested PBL number of bytes to the

DMA block or until the end of packet and the corresponding Rx status is transferred (whichever is first).

- 5. After completing the current request, the scheduler repeats the process by starting a new arbitration cycle. However, it selects the same Rx queue for servicing, if the end of packet is not transferred and the RXQ_FRM_ARBIT field of the Rx queue x control register (ETH_MTLRXQxCR) is 1, for the Rx queue.

Rx queue to DMA mapping

The packets in the MTL Rx queues can be routed to any of the multiple DMA channels, by programming the Rx queue and the Rx queue and DMA channel mapping register (ETH_MTLRXQDMAMR) .

Two types of Rx queue-to-DMA mapping are possible through programming: static mapping and dynamic (per packet) mapping.

- • Static mapping

In Static mapping mode, all the packets of an Rx queue are connected to a specific DMA channel. For example, all the packets from Rx Queue 0 can be routed to a DMA channel by programming Q0MDMACH and Q0DDMACH of the Rx queue and DMA channel mapping register (ETH_MTLRXQDMAMR) .

Similarly, packets from other Rx queues can be routed to any DMA channel by programming the register fields corresponding to each queue.

- • Dynamic (per packet) mapping

In Dynamic (per packet) mapping mode, the destination DMA channel is decided by the MAC core receiver for each packet.

In this mode, the destination DMA channel of a packet being read from a Rx queue is not constant but decided independently for each packet. For example, by setting the Q1DDMACH bit of the Rx queue and DMA channel mapping register (ETH_MTLRXQDMAMR) , the static mapping is disabled for Rx Queue 1 and the value in Q1MDMACH is ignored. The destination DMA channel is decided by the MAC receiver for each packet, depending on the following, in decreasing order of priority:

- – L3-L4 filter based DMA selection

When the Layer 3 and Layer 4 packet filtering is enabled, the TCP/UDP and IP header fields of the received packet are matched against the corresponding values programmed and enabled for comparison in the MAC L3 and L4 address control register. If the match is successful, the DMA channel number programmed in the DMCHNx bits of the L3 and L4 control 0 register (ETH_MACL3L4C0R) and L3 and L4 control 1 register (ETH_MACL3L4C1R) is selected as the destination DMA channel number provided DMCHEN bit of the same register is set.

If none of the L3-L4 registers give a comparison match, the Ethernet peripheral proceeds to the next step.

- – Extended VLAN based DMA selection

Extended routing is applicable only if the VLAN filter has passed. Routing is only based on perfect filter result. Each perfect filter has a DMA channel enable and a DMA channel number field which can be programmed. Routing is applicable for a filter only if the DMA channel enable bit is set.

The frame is routed to the smallest matching filter DMA channel provided it is enabled. If that filter DMA channel number is not enabled, the frame gets routed to Channel 0. For example, if a frame VLAN tag matches filter 1, then the MAC checks if filter 1 DMA channel number is enabled through programming. If yes, the

frame gets routed to the programmed value; otherwise it gets routed to DMA. When the inverse filter is enabled, the frame is routed to the least mismatched filter DMA channel number provided it is enabled. If the DMA channel enable bit is not set, then the frame is routed based on DA-based addressing or to Channel 0. If Hash filter is also enabled, it is used to determine the filter result only. Routing still depends on the enabled perfect filters. If none of the perfect filters are enabled or if all of them are bypassed, the VLAN filter based routing is not done. The frame is routed through DA-based addressing or to Channel 0. If all the perfect filters give a fail result and the Hash filter has passed, VLAN filter result is a pass. However, routing is based on DA-based addressing or to Channel 0. The behavior is similar when the inverse filtering is enabled.

- – Ethernet DA-based DMA selection

The DA address of the received packet is compared against the programmed DA values in MAC address registers. If the address matches any of the programmed values, the corresponding DCS field (when enabled) determines the destination DMA channel number.

If none of the previous operations is able to make a successful match/decision, then the packet is routed to DMA Channel 0 by default.

Programming guidelines for multiple queues and channels in the receive path

See Section 76.9.8: Programming guidelines for multichannel multiqueue operation on page 4128 .

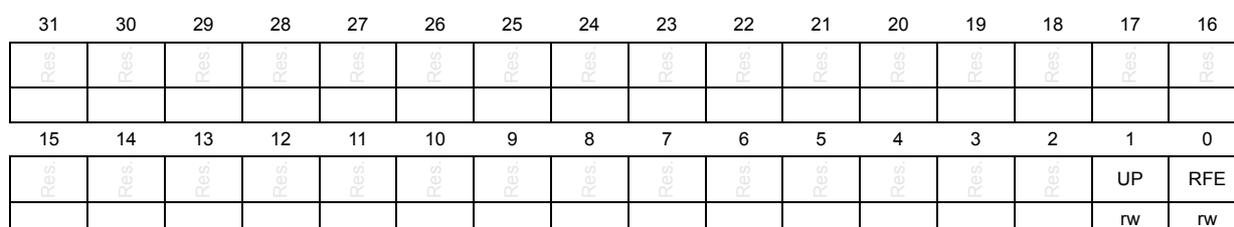

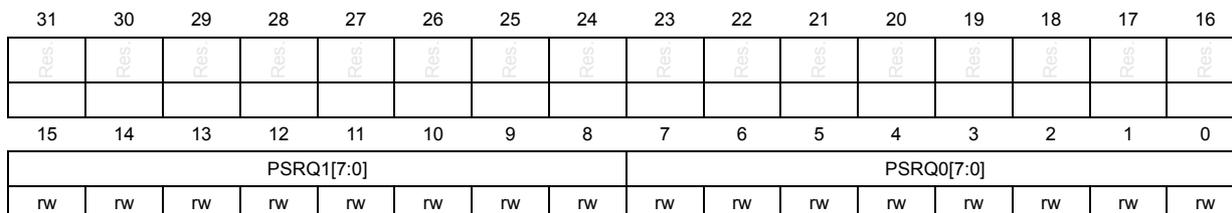

Selection of the tag priorities assigned to Rx queues

The VLAN tag priorities can be assigned to Rx queues by programming the PSRQ field in the corresponding Rx queue control 2 register (ETH_MACRXQC2R) . The bit corresponding to the VLAN tag priority can be set in the PSRQ field to assign the corresponding priority to the Rx queue. As an example, to assign VLAN tag priority 3 to Rx queue 0, set bit3 of PSRQ field in the Rx queue control 2 register (ETH_MACRXQC2R) . The VLAN tag priority assigned to a given Rx queue must be unique. This means that multiple Rx queues cannot be assigned the same VLAN tag priority. However, multiple VLAN tag priorities can be assigned to the same Rx queue.

The settings in the PSRQ field is used for VLAN tagged Rx packet routing to Rx queues as well as for PFC based Tx flow control. The received VLAN tagged Rx packet is routed to the Rx queue that matches the VLAN tag priority. In PFC-based Tx flow control, the PSRQ field corresponding to a particular Rx queue is used to enable VLAN tag priorities in the PFC packet that is transmitted when the corresponding Rx queue threshold levels are reached.

Distribution of Rx packets from MAC to Rx queues

The Ethernet peripheral provides multiple Rx queues to support classification and distribution of ingress packets. The MAC receiver pushes the ingress packets to the Rx queues based on packet type (such as tagged, untagged, multicast, PTP, AVB), tag priorities, MAC packet filter results, preemptable or express packet, and so on. The distribution is controlled by the settings of:

- • Rx Queue control register (ETH_MACRXQCR)

- • Rx queue control 0 register (ETH_MACRXQC0R)

- • Rx queue control 1 register (ETH_MACRXQC1R)

- • Rx queue control 2 register (ETH_MACRXQC2R)

- • Packet filtering control register (ETH_MACPFR)

Additionally, the Ethernet peripheral supports distribution of ingress packets based on user-defined Type field of the ingress packets when TBRQE bit of the Rx queue control 1 register (ETH_MACRXQC1R) is enabled. Up to eight types for matching can be programmed in the MAC type-based Rx queue mapping register (ETH_MAC_TMRQR) which is accessible through MAC indirect access control register (ETH_MAC_IACR) . The ETH_MAC_TMRQR register contains

- • TYP[15:0] field: 16-bit type

- • TMRQ[2:0] bitfield: Rx queue number to which ingress packet is pushed when its Type field matches TYP.

- • PFEX field: this bit indicates whether the TYP is applicable for express packets or preemptable packets.

Based on the packet filter settings, the MAC receiver decides either to drop or forward the ingress packet (for more details, see Section 76.5.4: Packet filtering ). However, the results of Layer 3 and Layer 4 filtering, mentioned in Section : Layer 3 and Layer 4 filtering , are not considered for the distribution of ingress packets into the Rx queues. Only the results of DA/SA/VLAN filters mentioned in Section : MAC source or destination address filtering and Section : VLAN filtering are applicable.

The filtering of the broadcast packets is exclusively controlled by the DBF bit of the Packet filtering control register (ETH_MACPFR) . The filtering of multicast packets is controlled by the PM bit of the Packet filtering control register (ETH_MACPFR) , in addition to the DA/SA match.

By default, packets that fail any of the DA/SA filters, are dropped by the MAC receiver. However, packets that fail the DA/SA/VLAN filter can still be forwarded to the application when the RA field of the Packet filtering control register (ETH_MACPFR) is 1. Even when RA field is 0, VLAN filter fail packets can be forwarded if the VTFR field of the Packet filtering control register (ETH_MACPFR) is 0.

The ingress packets go through the following operations in decreasing order of priority.

- 1. RA = 0: ingress packets are dropped if any of the following conditions is true.

- – DA/SA filter fail

- – VLAN filter fail and VTFR field of the Packet filtering control register (ETH_MACPFR) is 1

- 2. RA = 1: ingress packets that fail the DA/SA filter are also forwarded to the Rx queue as mentioned in Table 765 .

Table 765. Routing DA/SA failed packets to Rx queue

| Packet type | TSN type | Destination Rx queue determined by |

|---|---|---|

| Broadcast/Multicast | Express | if MFFQE = 1, MFFQ; else if VFFQE = 1, VFFQ; (only for tagged packets) else RxQ0 |

| Unicast | Express | if UFFQE = 1, UFFQ; else if VFFQE = 1, VFFQ; (only for tagged packets) else RxQ0 |

| All | Preemptable | FPRQ field |

- 3. RA = 1 and VTFR = 0: ingress tagged packets that pass the DA/SA filter but fail the VLAN filter are forwarded to the Rx queue as mentioned in Table 766 .

| TSN packet type | Destination Rx queue determined by |

|---|---|

| Express | if VFFQE = 1, VFFQ; else RxQ0 |

| Preemptable | RQ field |

- 4. Ingress packets that pass the DA/SA/VLAN filters are forwarded to the Rx queue.

- – Table 767 shows the routing priority in the decreasing order when OMCBCQ field of the Rx queue control 0 register (ETH_MACRXQC0R) is 0.

| Packet type | TSN type | Tagged | Destination Rx queue determined by |

|---|---|---|---|

| Broadcast/Multicast | Express | Yes | if MBCQEN = 1, MBCQ; else if TBRQE = 1, TBRQ; else PSRQ |

| No | if MBCQEN = 1, MBCQ; else if TBRQE = 1, TBRQ; else UPQ | ||

| Unicast AVTP control | Express | No | AVCPQ |

| Yes | if TACPQE = 1, AVCPQ; else PSRQ | ||

| Unicast PTP over Ethernet | Express | No | PTPQ |

| Yes | PTPQ or PSRQ based on the value of TPQC. | ||

| Remaining Unicast | Express | No | If TBRQE = 1, TBRQ; else UPQ |

| Yes | If TBRQE = 1, TBRQ; else PSRQ | ||

| All Packets | Preemptable | No | If TBRQE = 1, TBRQ; else FPRQ |

| Yes | If TBRQE = 1, TBRQ; else PSRQ |

- – Table 768 shows the routing priority in the decreasing order when OMCBCQ field of the Rx queue control 1 register (ETH_MACRXQC1R) is 1.

| Packet type | TSN type | Tagged | Destination Rx queue determined by |

|---|---|---|---|

| All AVTP Control | Express | No | AVCPQ |

| Yes | if TACPQE = 1, AVCPQ; else PSRQ | ||

| All PTP over Ethernet | Express | No | PTPQ |

| Yes | PTPQ or PSRQ based on TPQC | ||

| Remaining Broadcast/Multicast | Express | Yes | if MBCQEN = 1, MBCQ; else if TBRQE = 1, TBRQ; else PSRQ |

| No | if MBCQEN = 1, MBCQ; else if TBRQE = 1, TBRQ; else UPQ |

| Packet type | TSN type | Tagged | Destination Rx queue determined by |

|---|---|---|---|

| Remaining Unicast | Express | No | if TBRQE = 1, TBRQ; else UPQ |

| Yes | if TBRQE = 1, TBRQ; else PSRQ | ||

| All Packets | Preemptable | No | if TBRQE = 1, TBRQ; else FPRQ |

| Yes | if TBRQE = 1, TBRQ; else PSRQ |

Note: The fields mentioned in Table 765 through Table 768 belong to Rx queue control 0 register (ETH_MACRXQC0R) , Rx queue control 1 register (ETH_MACRXQC1R) and Rx queue control 2 register (ETH_MACRXQC2R) .

Note: If the RxQ pointed by the various fields in Table 765 through Table 768 is not enabled in the Rx queue control 0 register (ETH_MACRXQC0R) as per the packet type, the packet is written to

- • RxQ0 for Express packets

- • FPRQ field for Preemptable packets

If RxQ0/FPRQ is not enabled, the packet is dropped.

Note: If the AV8021ASMEN field of the Timestamp control register (ETH_MACTSCR) is 1, MAC receiver checks only for untagged PTP packet. Packets tagged with PTP payload are considered as Remaining (Unicast/Broadcast/Multicast) tagged packets in Table 765 through Table 768 .

The priority field of the outer VLAN tag is considered for routing.

AV feature

The Ethernet peripheral supports the AV data transfer in 100-Mbps and 1000-Mbps modes. The AV feature enables transmission of time-sensitive traffic over bridged local area networks (LANs). The following standards define various aspects of the AV feature implementation:

- • IEEE 802.1Qav-2009: enables the bridges to provide time-sensitive and loss-sensitive real-time audio video data transmission (AV traffic). It specifies the priority regeneration and controlled bandwidth queue draining algorithms that are used in bridges and AV traffic sources.

- • IEEE 802.1Qat-2009: enables the network resources to be reserved for specific traffic streams traversing a bridged local area network.

- • IEEE 802.1AS-2011: specifies the protocol and procedures used to ensure that the synchronization requirements are met for time-sensitive applications such as audio and video across bridged and virtual-bridged LANs consisting of LAN media where the transmission delays are fixed and symmetrical. For example, IEEE 802.3 Full-duplex links include the maintenance of synchronized time during normal operation followed by addition, removal, or failure of network components and network reconfiguration.

While the AVB standards were originally designed for audio and video over standard Ethernet, extending these to control streams would additionally benefit the industrial and automotive sectors. Time sensitive networking (TSN) is a set of standards developed by the Time Sensitive Networking Task Group with the intent to extend the future AVB enhancements to other sectors that could benefit.

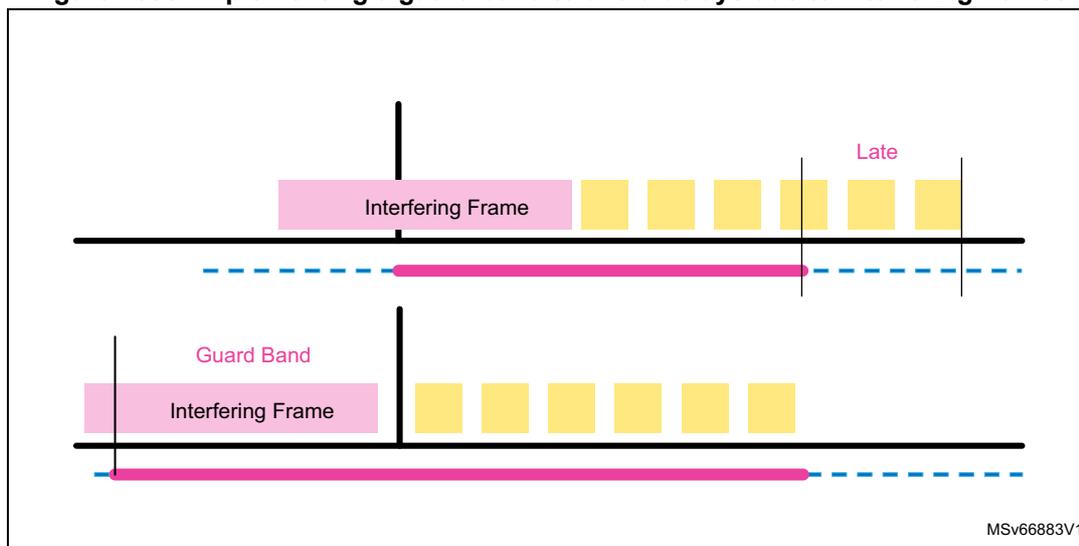

Bridges are increasingly used to interconnect devices that support scheduled applications (for example, industrial automation, process control and vehicle control). The IEEE 802.1Qbv-2015 (Enhancements to Scheduling Traffic) provides performance assurances of latency and delivery variation to enable these applications in an engineered LAN while maintaining the existing guarantees for the credit-based shaper and best-effort traffic.

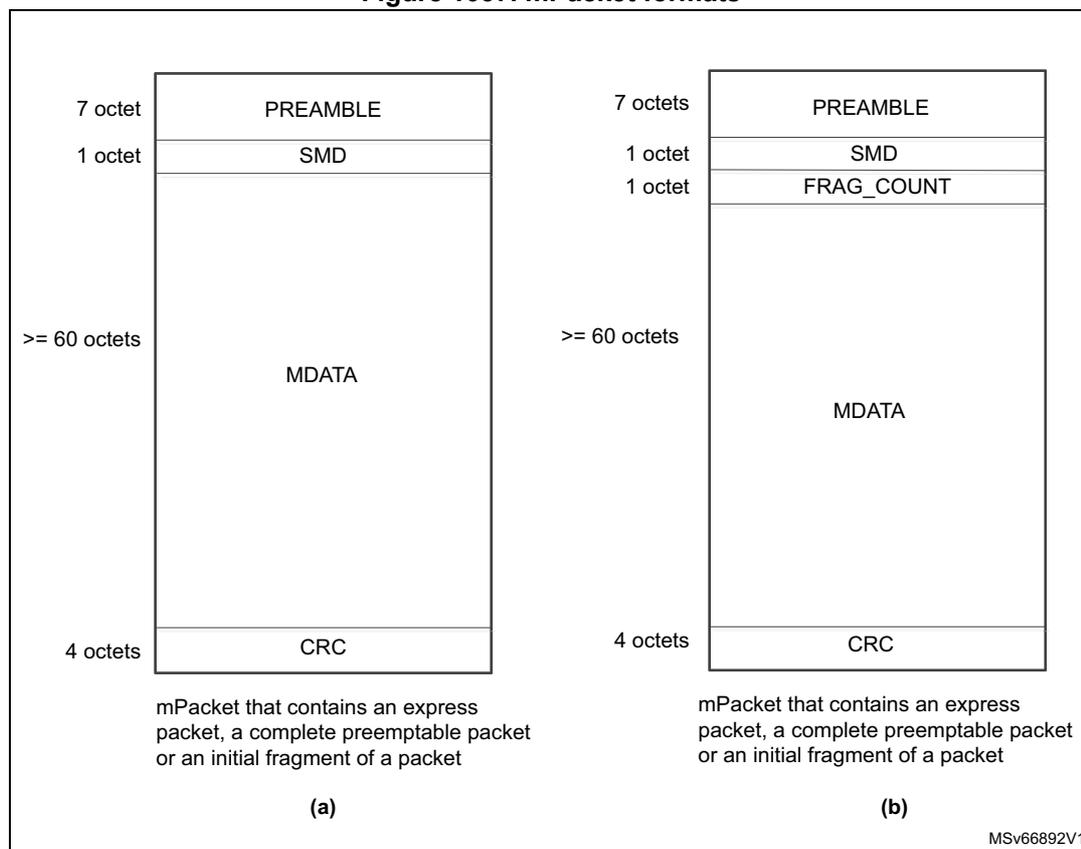

The IEEE 802.3br (Interspersing Traffic) and IEEE 802.1Qbu (frame preemption) enables the suspension of a large preemptable packet being transmitted by the MAC layer to enable one or more express packets to be transmitted before the transmission of the preemptable packet is resumed. This provides the capability to schedule express traffic packets with minimal delays/latencies or at predictable times with efficient utilization of the line bandwidth.

As per the IEEE specification for 802.1Qbv, 802.1Qbu, and 802.3br, the TSN features are supported only in the following modes:

- • Full duplex

- • 100 Mbps or higher link speed

- • Pause or no flow control

- • When Qbv schedule is enabled for time-sensitive traffic, Pause or PFC is likely to interfere with the Qbv schedules. So, it is recommended not to enable PFC/PAUSE when Qbv scheduler is enabled.

- • Multiple Tx queues (for Qbv) enabled

- • One or more Express queues and one or more preemption queues on both transmit and receive (for Qbu/802.3br) enabled.

Transmit path functions

When the AV feature is selected, the Transmit paths of Tx queues are enabled by default.

The Transmit path of queue 0 supports the strict priority algorithm, and it is used for best-effort traffic. For a queue, the strict priority algorithm determines that a packet is available for transmission if the queue contains one or more packets. When the threshold mode for MTL Tx FIFO is enabled, the strict priority algorithm determines that a packet is available for transmission if the queue contains a partial packet of size equal to the programmed threshold limit.

The Transmit path of the AVB Tx queue supports traffic management by using the credit-based shaper algorithm. For a queue, the credit-based shaper algorithm determines that a queue is available for transmission if the following conditions are true:

- • The queue contains one or more packets.

- • The credit for the queue is positive as per the algorithm.

When the credit-based shaper algorithm is disabled for a queue, the channel uses the default strict priority algorithm.

Each Transmit DMA has a separate descriptor chain for fetching the transmit data. The Transmit channel that gets the access to the system bus depends on the DMA arbiter.

The Transmit path has a shared FIFO (MTL layer) for each queue. The data fetched by the DMA is put in the respective part of the FIFO. The MTL Tx Queue Scheduler controls which part of the FIFO data is transmitted by the MAC. If the credit-based shaper algorithm is enabled for queue 1, the queue is selected if the packet is available in the channel and has a positive or zero credit.

If the credit-based shaper algorithm is disabled for a given Tx queue, the packet to be transmitted is selected based on the fixed priority scheme as described in Table 769 .

Table 769. Weight for DMA channels

| TCW field | Transmit channel weight |

|---|---|

| 000 | 1 |

| 001 | 2 |

Receive path functions

When the AV feature is enabled, the receive path of Queue 0 is enabled by default. The whole traffic is received on this channel. The receive paths of additional queues can be enabled. By enabling the receive paths of multiple channels, the received data can be demultiplexed to send the packets into separate receive channels.

To differentiate between the AV and non-AV traffic, the MAC provides a status that indicates if the received packet is an AV packet as well as the corresponding VLAN Priority tag value. This status is updated in the Extended Status field of the receive descriptor as explained in Section 76.10.4: Receive descriptor . All received packets with an EtherType field of 0x22F0 are detected as AV packets. The AV packets can be of the following two types:

- AV data packets

AV data packets are always tagged. Tagged AV data packets are received following the programmed priority value. To specify the channel to which an AV packet with a given priority must be sent, program bits[15:8] in the transmit flow control register of the corresponding queue.

- AV control packets

The AV control packets can be either tagged or untagged. By default, untagged AV control packets are received on queue 0. To receive these packets on queue 1, program bits[2:0] of the Rx queue control 1 register (ETH_MACRXQC1R) . Similarly to the AV data packets, tagged AV control packets are received following the programmed priority value.

In addition to the AV packets, you can receive the untagged PTP packets on any queue. By default, the PTP packets (tagged or untagged) are received on queue 0. To receive these packets on any other queue, program bits[6:4] of the Rx queue control 1 register (ETH_MACRXQC1R) .

Credit-based shaper algorithm

The Queue Scheduler uses the credit-based shaper algorithm to arbitrate the AV traffic in all queues and the legacy Ethernet traffic in queue 0. Queue 1 can be programmed to use the credit-based shaper algorithm.

The following sections provide information on the credit-based shaper algorithm implementation:

- Credit value

- idleSlopeCredit and sendSlopeCredit values

- Bandwidth status

The credit value is accumulated every transmit clock cycle, that is every 40 ns in 100-Mbps mode and every 8 ns in 1000-Mbps mode. The credit to be added or subtracted per cycle can be fractional depending on the required idleSlope and sendSlope values, as described in Table 770 .

Table 770. Example of credit value per transmit cycle| Mode | portTransmitRate, idleSlope, sendSlope | Credit value |

|---|---|---|

| 100 Mbps |

|

|

The DMA stores the queue traffic in the respective part of the Tx FIFO depending on the slot number in the transmit descriptor (if enabled) or the bandwidth availability on the AMBA application bus.

The credit for a queue builds up only when the packet is available, but it cannot be transmitted because the MAC is sending a packet from another queue. The Ethernet peripheral supports another mode in which the credit can build up in advance for a queue in which no packet is available in respective part of the FIFO. This enables sending a burst of high priority traffic in a queue as soon as the data is available. This mode can be enabled through the CC bit of the CBS control register ( Tx queue 1 ETS control register (ETH_MTLTXQ1ECR) ).

- • When reset, the accumulated credit parameter in the credit-based shaper algorithm is set to zero if there is positive credit, and there is no packet to transmit in a queue. The credit does not accumulate when there is no packet waiting in a queue and other queues are transmitting.

- • When set, the accumulated credit parameter in the credit-based shaper algorithm is not reset to zero if there is positive credit and no packet to transmit in a queue. The credit accumulates even when there is no packet waiting in a queue and other queues are transmitting.

The software must program the idleSlopeCredit and sendSlopeCredit values. The programmed values should be the credit accumulated or drained per clock cycle scaled by 1024 (such as \( 2.8 \times 1024 = 2867 \) and \( 1.2 \times 1024 = 1229 \) ). In addition, the software must program the hiCredit and loCredit values, scaled by 1024, to adjust for scaling of the idleSlopeCredit and sendSlopeCredit values. This means that if computed hiCredit and loCredit values are 12,000 bits and 3,036 bits respectively, the values to be programmed in the hiCredit and loCredit registers of the corresponding channel are \( 12000 \times 1024 \) bits and two's complement of \( 3036 \times 1024 \) , respectively.

Bandwidth status

The hardware maintains the status of the actual bandwidth consumed by each higher priority queue in the CBS status registers. This enables the software to estimate the average bandwidth consumed by numerically higher traffic classes as compared to the reserved bandwidth.

The CBS status register ( Tx queue x ETS status register (ETH_MTLTXQxESR) ) gives the average number of bits transmitted during the previous programmed slot interval (1, 2, 4, 8, or 16 slots of 125 µs) in a queue. The status register is updated even if the credit-based shaper algorithm is not enabled for a queue. The number of slots over which the average bits transmitted per slot are computed is programmed in bits[6:4] of the CBS control register of the respective queue. For example, if you have programmed two slots, the average bits are computed over slot numbers 0–1, 2–3, 4–5, and so on.

The value programmed in the idleSlopeCredit register of a queue is proportional to the bandwidth reserved for the queue. The software can allocate any bandwidth that is not used by the higher priority queue to the reserved bandwidth of the lower priority queue.

A lower priority queue, which is using the credit-based shaper algorithm, cannot use the unused reserved bandwidth of any higher priority queue that is using the credit-based shaper algorithm. However, a lower priority queue, which is using the strict-priority algorithm, can use the unused reserved bandwidth of any higher priority queue that uses the credit-based shaper algorithm. For example, queue 1 and queue 2 use the credit-based shaper algorithm (with reserved bandwidth of 50% and 25%, respectively) and queue 0 uses the strict-priority algorithm. If queue 1 uses only 40% of reserved bandwidth, the remaining 10% is used by queue 0. Queue 2 cannot exceed the reserved bandwidth of 25%.

Slot number function

When the AV feature is enabled, the slot number function can be used to schedule the data fetching from the system memory by the DMA. This feature is useful when the source AV data needs to be transmitted at specific intervals.

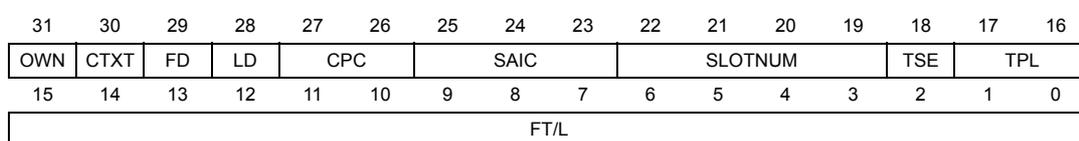

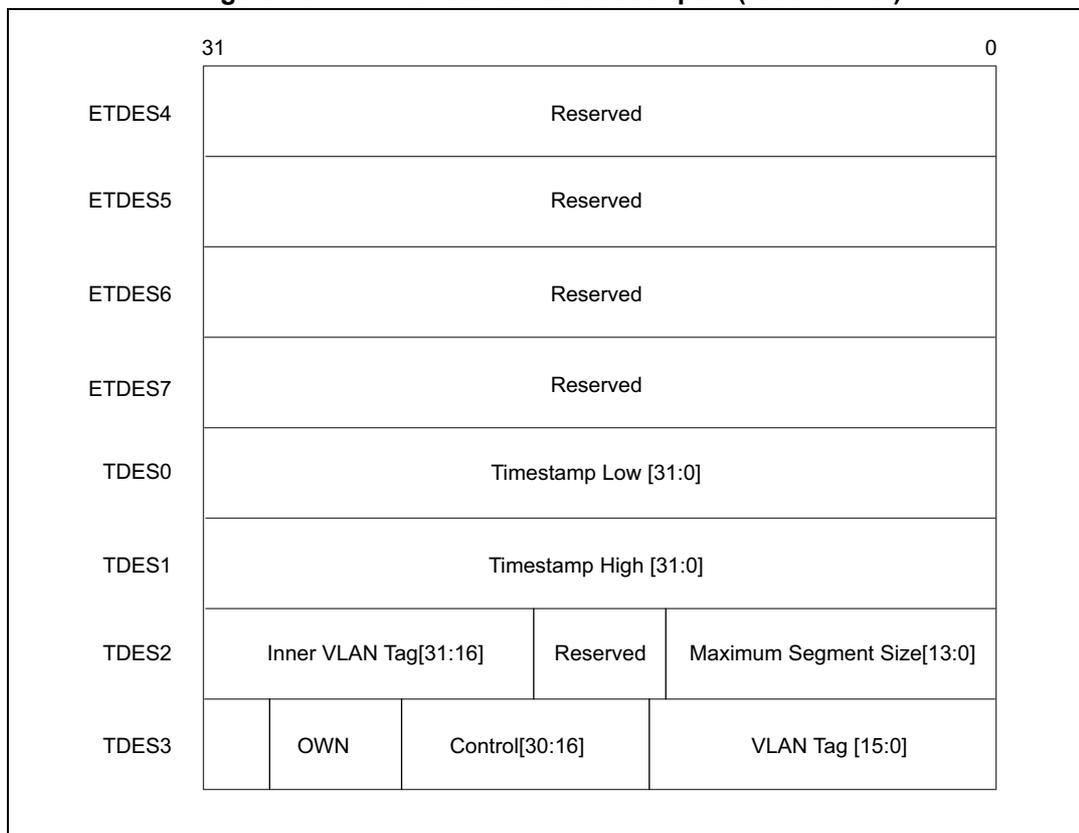

The slot number at which the DMA should fetch the data from system memory can be programmed in the transmit descriptor Word 3 (TDES3). This 4-bit field enables the application to schedule data fetching at up to 16 slots with a programmable slot interval that ranges from 1 µs to 4096 µs and a granularity of 1 µs. This field is applicable only to the AV channels.

When the DMA fetches a Tx descriptor, it compares the slot number of the Tx descriptor with the internally generated reference slot interval. The slot interval is a counter that is updated based on a programmable slot interval (with range from 1 µs to 4096 µs) of the IEEE 1588 system time. In addition, the slot interval counter is initialized to zero when the seconds field of the system time is incremented, that is, when the subsecond counter rolls over. The DMA fetches the data only if it matches the current slot or the next slot. The DMA remains in the descriptor fetch state until a match is found.

To enable the DMA to fetch data only if it matches the current slot or the next two slots, program bit 1 of the Channel x slot function control status register (ETH_DMACxSFCSR) of the corresponding DMA channel.

If the slot number in the descriptor is less than the reference slot number, the DMA considers it as a future slot.

The slot number check can be enabled by setting bit 0 in the Channel x slot function control status register (ETH_DMACxSFCR) of corresponding DMA channel. If this check is disabled, the packets are fetched immediately after the descriptor is read. In addition, bits [19:16] indicate the value of the reference slot number in DMA.

Programming guidelines for AV feature

See Section : Initializing the DMA on page 4137 .

See Section : Enabling slot number checking on page 4138 .

See Section : Enabling average bits per slot reporting on page 4138 .

Queue modes

A Tx queue can be enabled for generic or AV traffic. When multiple Tx queues are enabled for generic traffic, queuing is based on WRR or WSP algorithms.

When a Tx queue is enabled for AVB traffic, queuing is based on CBS or SP algorithms.

A Rx queue can be enabled for generic or AV traffic. A particular queue enabled for generic or AV based routing is determined by the RXQ0EN and RXQ1EN fields in the Rx queue control 0 register (ETH_MACRXQC0R) .

Below an explanation on how Rx queues are enabled based on the selected features:

- • Multiple Rx queues

When multiple Rx queues are selected, all queues are enabled for generic queuing based on the VLAN tag priority. The VLAN tag priority should match the PSRQ[7:0] bitfield of the Rx queue control 2 register (ETH_MACRXQC2R) . By default untagged packets are routed to receive queue specified in UPQ field of Rx queue control 1 register (ETH_MACRXQC1R) . Queue 0 is the default value of UPQ[2:0] bitfield. The default value can be overridden with any other value, for the UPQ[2:0] bitfield. The Rx packets can also be routed to a particular DMA channel based on the DCS field of the perfectly-matched MAC Address register ( MAC address x high register (ETH_MACAxHR) ).

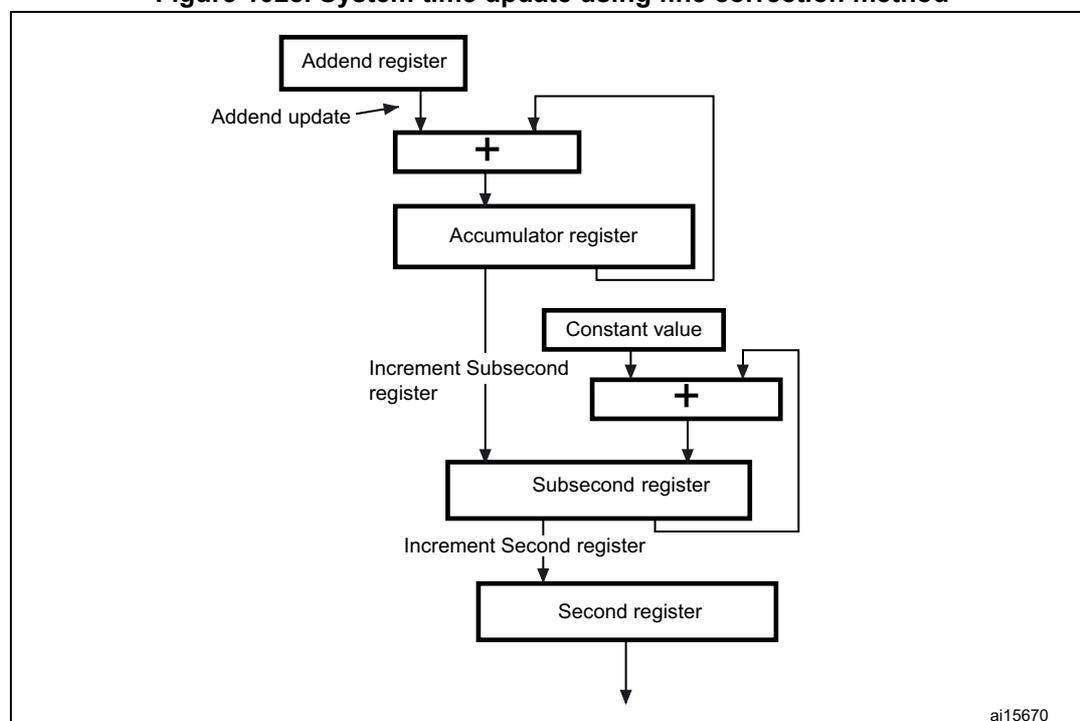

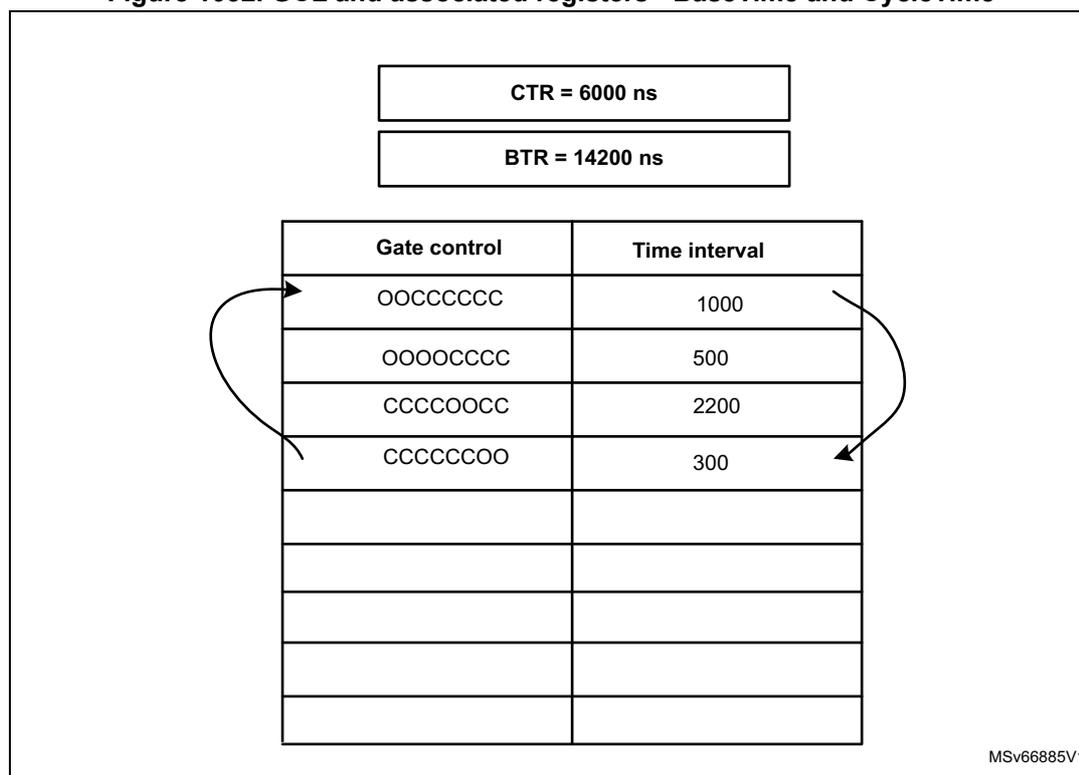

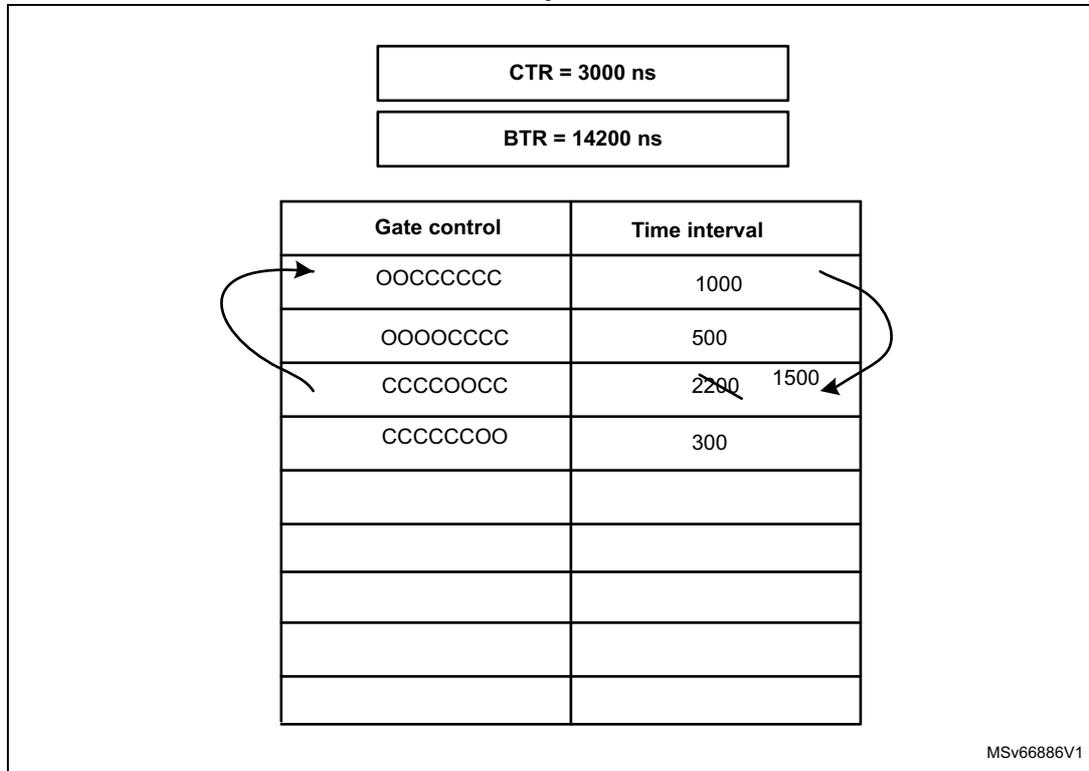

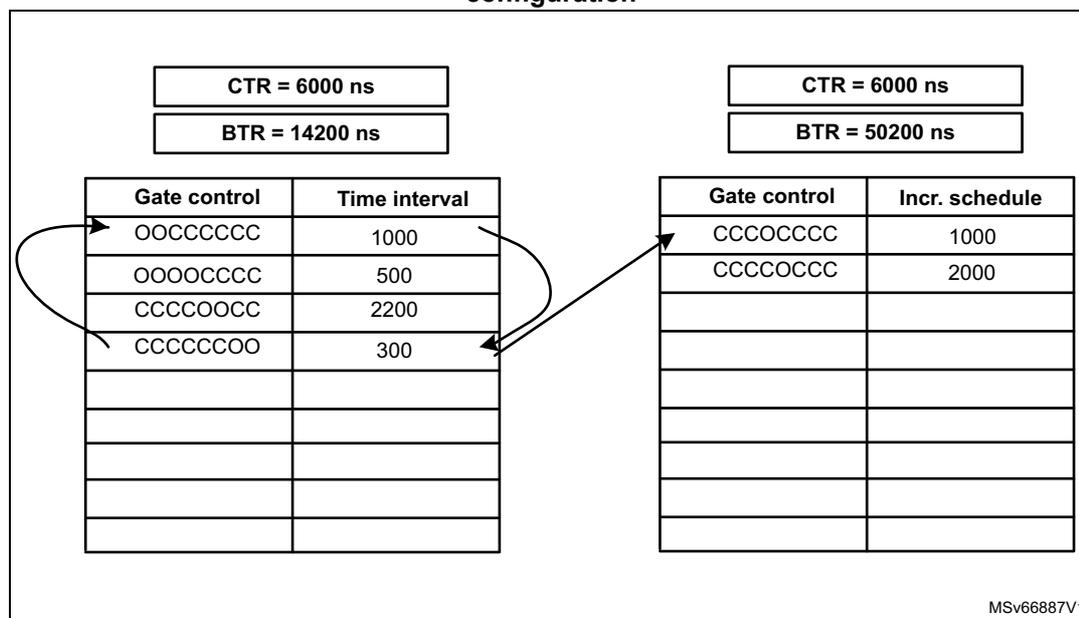

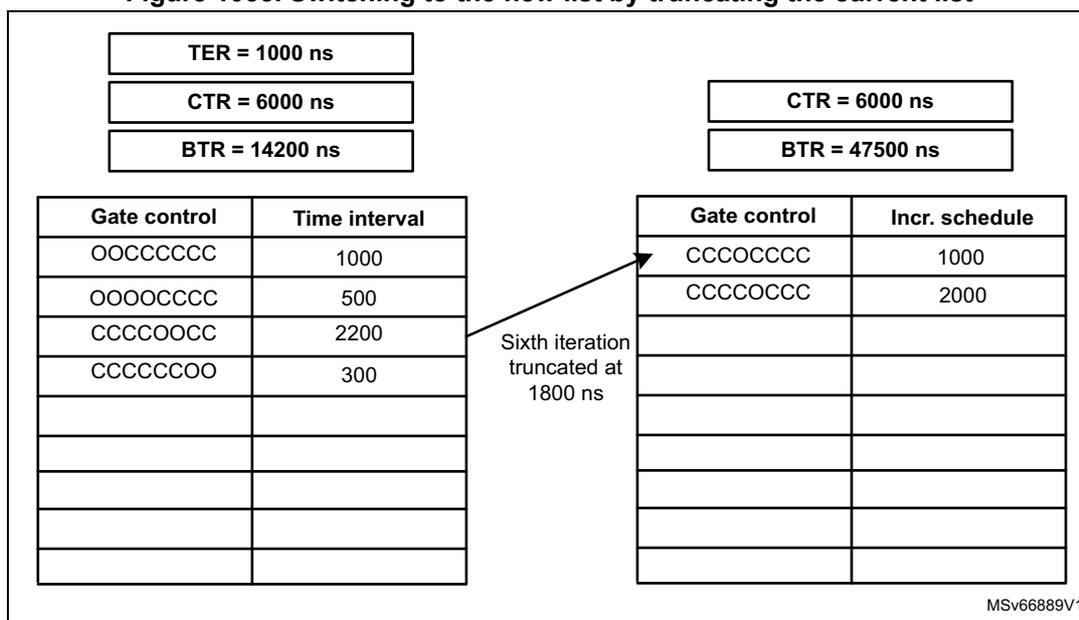

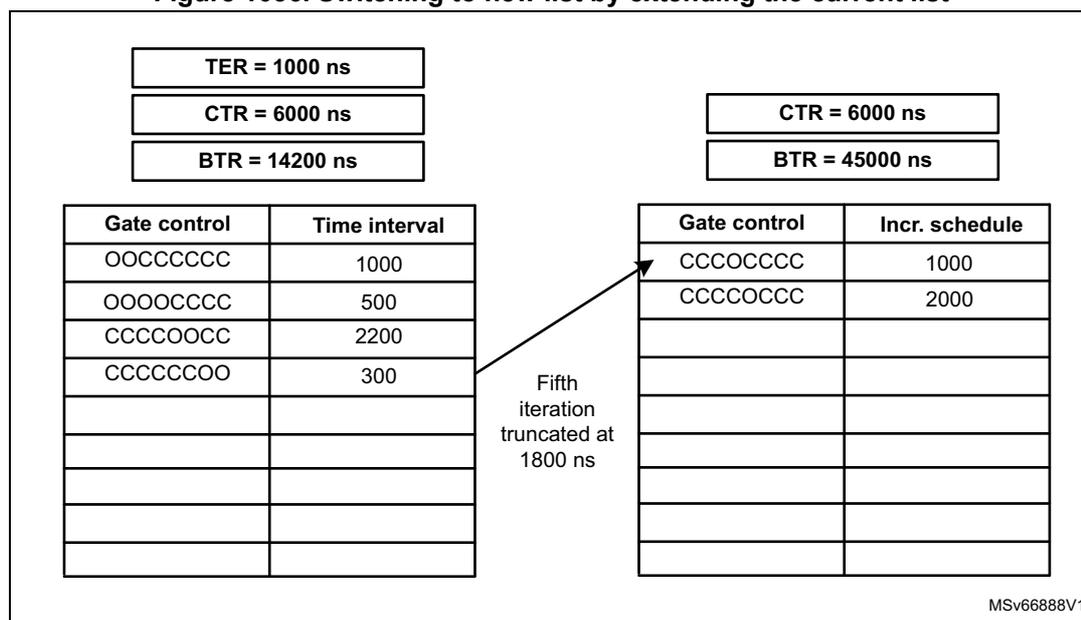

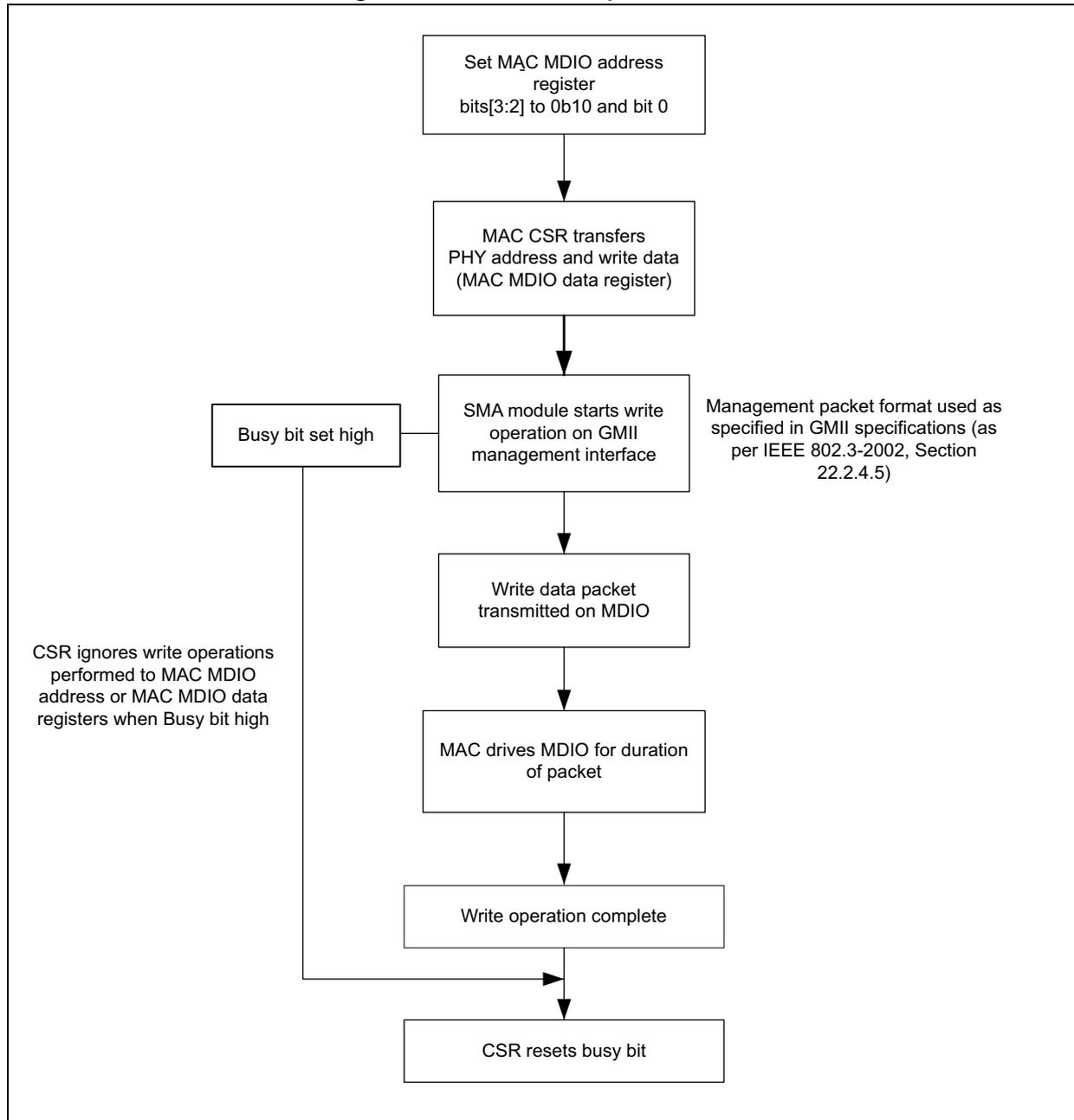

- • Multiple Rx queues with AV feature