45. Video encoder (VENC)

45.1 VENC introduction

The video encoder (VENC) provides a hardware acceleration to encode a 1080p15 video stream in H264 (= MPEG4_Part10/AVC).

The VENC also provides hardware acceleration to encode still images (JPEG) of up to 300 Mpixel/s.

The VENC implementation embeds a large 128-Kbyte video RAM (VENCRAM).

When the VENC is disabled, the VENCRAM is unused for video purposes, and is accessible by the system as a contiguous extension of the system SRAM.

45.2 VENC main features

The VENC supports the following features:

- • Video encode:

- – codecs: H264 (MPEG4_Part10/AVC, baseline/Main/High up to 5.2)

- – performance: 1080p15 for H264

- • Still-image encode:

- – codecs: JPEG (baseline interleaved)

- – performance: 300 Mpixel/s for JPEG

- • VENCRAM:

- – size: 128 Kbytes

- – access: can be statically assigned to the system by SYSCFG settings

The VENC also provides the following features:

- • Security via RIF:

- – The VENC is protected by a default slave and master control (RISUP and RIMU).

- – By default, the VENC works in non-protected mode.

- – The VENC can be set in protected mode, for instance to handle DRM tasks with a secure datapath. In such cases, the drivers must run in a protected process.

- • Synchronization from an upstream peripheral:

Thanks to this feature, pixels can be streamed from an upstream peripheral (such as the camera) directly to the VENC, without writing to a full frame buffer, nor requiring external bandwidth.

- • Encode with multiple codecs on a same system:

The VENC can encode using different codecs on a same system: the VENC hardware processes the encode tasks sequentially, interleaved at frame level. Performances are shared across all the tasks.

45.3 VENC implementation

The VENC with a 400 MHz core clock supports up to 1080p15 video encode, or 300 Mpixel/s JPEG encode.

Since the VENC encoder is multi-instance, the input image can be changed at each encoding. The video format and resolution can thus be different for each instance.

The method for sharing the resource between several instances must be managed by software. This is to be done with locking mechanism, so that exclusive access to the VENC hardware is ensured for one instance at a time. The number of streams to be encoded this way is limited only by the external memory availability.

Note: Any use case with two (or more) simultaneous video encoding sessions must be tuned within the bandwidth limit of the system (especially memories accesses). Typical tunings are on pixel format, frame rate, and resolution.

45.4 VENC functional description

45.4.1 VENC block diagram

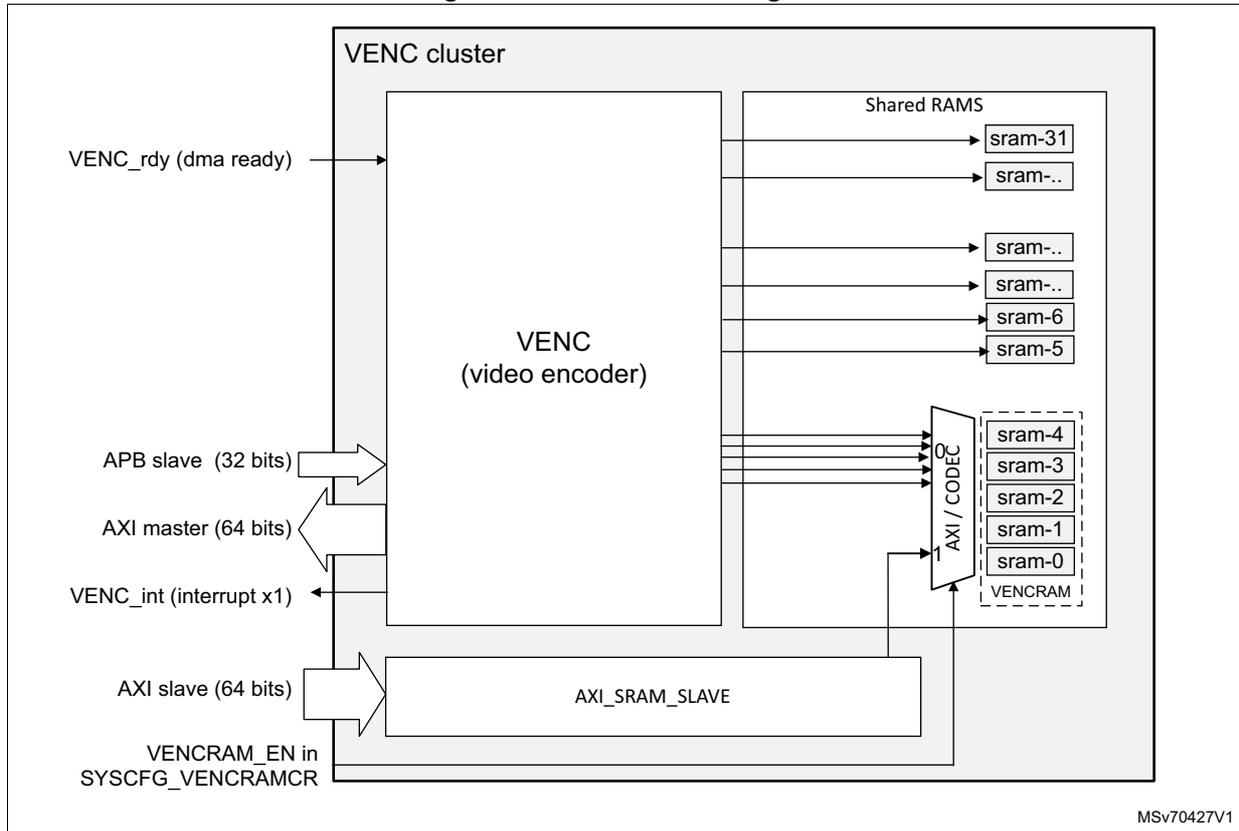

The following block diagram shows the VENC, the VENC RAM, and its interfaces.

Figure 449. VENC block diagram

The diagram illustrates the internal architecture of the VENC cluster. At the center is the 'VENC (video encoder)' block. To its left, several interfaces are shown: 'VENC_rdy (dma ready)' as an output, 'APB slave (32 bits)' as an input, 'AXI master (64 bits)' as an output, 'VENC_int (interrupt x1)' as an output, and 'AXI slave (64 bits)' as an input. Below these is the 'VENC RAM' section, which includes an 'AXI_SRAM_SLAVE' block and a 'VENCRAM_EN in SYSCFG_VENCRAMCR' control signal. To the right of the VENC block is the 'Shared RAMS' section, which contains several SRAM blocks: 'sram-31', 'sram-..', 'sram-..', 'sram-6', and 'sram-5'. Below these are five more SRAM blocks labeled 'sram-4', 'sram-3', 'sram-2', 'sram-1', and 'sram-0', which are collectively labeled as 'VENC RAM'. These five SRAMs are connected to an 'AXI / CODEC' block, which is further connected to the 'AXI_SRAM_SLAVE' block. The entire cluster is enclosed in a 'VENC cluster' boundary. A reference code 'MSv70427V1' is located in the bottom right corner.

45.4.2 VENC pins and internal signals

The VENC implements the following group of signals:

- • APB Slave 32-bit bus: to configure the VENC and start its tasks.

- • AXI Master 64-bit bus: for the VENC to fetch and store its needed data

A 1080p15 video encode generates a bandwidth of 250 Mbyte/s to the buffer of its reference frame. An additional 90 Mbyte/s can be used to load the frame to encode.

- • interrupts returned to the CPU interrupt controller

- • venc_rdy: synchronization signals with an external peripheral like the DCMIPP

45.4.3 VENC reset and clocks

The VENC receives the following external signals:

- • rstn_venc: to reset the whole VENC

- • ck_icn_s_venc: to clock the APB Slave to configure the VENC

- • ck_icn_m_venc: to clock the AXI Master controlled by the VENC

45.4.4 VENC pre-processor

The VENC includes a pre-processor implemented at the input of the encoding pipe. This pre-processor allows on-the-fly processing of a frame that is read to be encoded, at no bandwidth cost.

The VENC pre-processor supports the following features:

- • xRGB-to-YUV420 conversion: for direct encoding of an xRGB frame, for instance to store compressed the display output (that is usually in xRGB format)

- • Cropping: for direct encoding of a specific region of interest

- • Rotation90/270: for compensation of a rotated camera

Note: Any other feature is not supported.

The VENC pre-processor supports the following input pixel formats:

- • YCbCr 4:2:0 planar (3 buffers)

- • YCbCr 4:2:0 semi-planar (2 buffers)

- • YCrCb 4:2:0 semi-planar (2 buffers)

- • YCbYCr 4:2:2 interleaved (1 buffer)

- • CbYCrY 4:2:2 interleaved (1 buffer)

- • RGB444, BGR444 (16 bpp)

- • RGB555, BGR555 (16 bpp)

- • RGB565, BGR565 (16 bpp)

- • RGB888, BGR888 (32 bpp)

45.4.5 VENC H264 encoder

The VENC supports the following features in H264 mode:

- • Performance: 1080p15

- • Spec version: 12ISO/IEC 14496-10 / ITU-T Rec. H.264 (03/2010)

- – Baseline profile: levels 1 – 5.2

- – Main profile: levels 1 - 5.2

- – High profile: levels 1 – 5.2

- • Profile: Baseline/Main/High, levels 1-52

- • MVC supported

- • Motion search: horizontal: \( \pm 126 \) pixels, vertical: \( \pm 30 \) pixels

- • Output format: for H.264: byte unit stream or NAL unit stream

- • Image size: 96x96 to 4080x4080 (by steps of 4 pixels)

- • Bit rate: 10 Kbit/s to 40 Mbit/s

- • Coding output: such as best matching motion vector, quality estimation (SAD)

- • Bandwidth: optimized by buffering the luma search area in the SRAM

- • Region of interest: two user definable rectangular areas with separate QP settings

- • Region of intra: one user definable rectangular area coded as intra

- • Cyclic intra refresh supported

- • H264 ROI map: can define a different quantization delta for each macro-block, according to a table defined in the external DDR. A total of three quantization delta values can be selected in one picture.

Note: SVC is not supported.

45.4.6 VENC JPEG encoder

The VENC supports the following feature in JPEG mode:

- • Performance: 300 Mpixel/s at 400 MHz

- • Spec version: JPEG ISO/IEC 10918-1, ITU-T T.81

- • Baseline process

- • Huffman coding interleaved

- • YUV420 supported internally

- • Output format: JFIF file format 1.02, non-progressive JPEG 4:2:0

- • Image size: 96x32 to 8176x8176 (by step of 4 pixels)

- • Thumbnail insertion: RGB 8-bit, RGB 24-bit, JPEG compressed thumbnails

- • User-defined quantization table: luma and chroma quantization tables

- • Partial encoding: slice-by-slice according to the user defined restart interval

- • ROI implemented by crop feature in pre-processor

The VENC shares its performance between video and JPEG encode: one task runs exclusively versus the other on a time-sharing basis.

45.4.7 VENC synchronization

The VENC can be synchronized, if needed, onto an external peripheral: it is used to encode a full frame, per chunk of one/more line of macro-blocks.

Initialization

The software allocates a double buffer, with each one line of macro-blocks (16 pixel high). This double buffer is used in a ping-pong way: when the external peripheral writes into one buffer, the VENC reads from the other buffer, and encodes it.

Before one frame

- 1. The software configures and triggers the VENC for a new frame.

- 2. The VENC waits for

venc_rdyto become high (set by the source peripheral). - 3. The VENC starts to encode the current ping-pong buffer.

- 4. The VENC finishes its encoding: it swaps its ping-pong buffer, and waits to a next

venc_rdysignal high.

Note:

The VENC is thus fully slaved onto the external peripheral, and solely driven by the

venc_rdy

trigger from the source signal:

- - The encoding of one line of macroblock must be guaranteed faster than the reception of the next line of macroblock.

- - The external peripheral triggers the VENC each time it has finished writing one line of the macroblock.

45.4.8 VENC security

The VENC security is based on the RIF, with the following protections:

- • protection of VENC register map (AHB slave) with a RISUP (see Table 20: RISUP indexes , the index for the VENC is 97).

- • protection of VENC access to memory (AXI master) with a RIMU (index = 12)

The VENC RIMU by default inherits from its RISUP settings. More information can be found in Section 6: Resource isolation framework security controller (RIFSC) .

The security configuration is, by default, non-protected:

- • It allows the default OS drivers to handle the VENC.

- • AXI transactions are not protected, although they can be tagged with a CID specific for pixel buffers.

- • The VENC can work in protected mode to allow secure data path (SDP) support with both the input flow and output bitstream being stored in protected buffers:

- • The VENC AXI transaction becomes protected.

- • The VENC APB configuration space becomes protected.

- • The low-level software must work in protected mode to have access to the VENC registers.

45.4.9 VENC power-on sequence

The VENC power-on sequence is similar for all supported codecs, H264 or JPEG.

The RCC provides the needed master, slave, and core clocks. The software makes sure the VENC can access its VENCRAM, and lets the driver configure the VENC to start encoding.

The corresponding set up includes the following steps:

- 1. Set up security settings (see VENC index in

Table 20: RISUP indexes

).

- – The VENC is kept by default as non-protected.

- 2. Allocate the VENCRAM to the VENC:

- – Clear

VENCRAM_ENto 0 inSYSCFG_VENCRAMCR.

- – Clear

- 3. Set up the clock and reset (see

Section 14: Reset and clock control (RCC)

):

- – VENC master:

ck_icn_m_vencto activate in the RCC (400 MHz typical)

- – VENC master:

- – VENC slave: ck_icn_p_venc to activate in the RCC (200 MHz typical)

45.4.10 VENCRAM power-on sequence for AXI access

This section describes settings to access the VENCRAM with the AXI-Slave. The RCC provides needed slave clocks, and makes sure the AXI Slave can access its VENCRAM, so that the system can start to use the SRAM.

The steps to set up this path are as follows:

- 1. Set up the security settings (see VENCRAM index in

Table 20: RISUP indexes

).

- – The VENCRAM can be set as protected or not-protected, depending on the system needs.

- 2. Allocate the VENCRAM to the CPU (the VENC no longer works correctly).

- – Set VENCRAM to 1 in SYSCFG_VDERAMCR.

- 3. Setup the clock and reset (see

Section 14: Reset and clock control (RCC)

):

- – VENCRAM AXI: ck_icn_s_vencram to activate in the RCC (400 MHz typical).

45.5 VENC low power modes

The VENC has no voltage power modes.

45.6 VENC interrupts

The VENC can trigger a global interrupt (venc_gbl_int) that is referenced in the CPU interrupt handler as VENC.

45.7 VENC registers

45.7.1 VENC ID register (VENC_SWREG0)

Address offset: 0x000

Reset value: 0x6E65 5000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Identification register (all format mode)

45.7.2 VENC interrupt register (VENC_SWREG1)

Address offset: 0x004

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Interrupt register (all format mode)

45.7.3 VENC bus interface configuration register (VENC_SWREG2)

Address offset: 0x008

Reset value: 0x0000 0010

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Bus interface configuration register (all format mode)

45.7.4 VENC device configuration register (VENC_SWREG3)

Address offset: 0x00C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Device configuration register (all format mode)

45.7.5 VENC base address for output stream data register (VENC_SWREG5)

Address offset: 0x014

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for output stream data (all format mode)

45.7.6 VENC base address for output control data register (VENC_SWREG6)

Address offset: 0x018

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for output control data (all format mode)

45.7.7 VENC base address for reference luma register (VENC_SWREG7)

Address offset: 0x01C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for reference luma (all format mode)

45.7.8 VENC base address for reference chroma register (VENC_SWREG8)

Address offset: 0x020

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for reference chroma (all format mode)

45.7.9 VENC base address for reconstructed luma register (VENC_SWREG9)

Address offset: 0x024

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for reconstructed luma (all format mode)

45.7.10 VENC base address for reconstructed chroma register (VENC_SWREG10)

Address offset: 0x028

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for reconstructed chroma (all format mode)

45.7.11 VENC base address for input picture luma register (VENC_SWREG11)

Address offset: 0x02C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for input picture luma (all format mode)

45.7.12 VENC base address for input picture cb register (VENC_SWREG12)

Address offset: 0x030

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for input picture cb (all format mode)

45.7.13 VENC base address for input picture cr register (VENC_SWREG13)

Address offset: 0x034

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for input picture cr (all format mode)

45.7.14 VENC encoder control register 0 (VENC_SWREG14)

Address offset: 0x038

Reset value: 0x0000 0000

This register is used to control data such as picture information or encoding mode.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Encoder control register 0 (such as picture information or encoding mode) (all format mode)

45.7.15 VENC encoder control register 1 (VENC_SWREG15)

Address offset: 0x03C

Reset value: 0x0000 0000

This register is used to control data such as preprocessing control, crop, rotate, or input format.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Encoder control register 1 (such as preprocessing control, crop, rotate, input format) (all format mode)

45.7.16 VENC encoder control register 2 (VENC_SWREG16)

Address offset: 0x040

Reset value: 0x0000 0000

This register controls the base address for second reference luma (H264 control).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for second reference luma (H264 control) (all format mode)

45.7.17 VENC encoder control register 3 (VENC_SWREG17)

Address offset: 0x044

Reset value: 0x0000 0000

This register controls the base address for second reference chroma (H264 control).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for second reference chroma (H264 control) (all format mode)

45.7.18 VENC encoder control register 4 (VENC_SWREG18)

Address offset: 0x048

Reset value: 0x0000 0000

This register controls the deblock filter mode (H264 control).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Encoder control register 4 (deblock filter mode, H264 control) (all format mode)

45.7.19 VENC encoder control register 5 (VENC_SWREG19)

Address offset: 0x04C

Reset value: 0x0000 0000

This register controls data such as input format or motion vector.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Encoder control register 5 (input format, motion vector etc) (all format mode)

45.7.20 VENC encoder control register 6 (VENC_SWREG20)

Address offset: 0x050

Reset value: 0x0000 0000

This register controls JPEG.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Control of data JPEG (all format mode)

45.7.21 VENC encoder control register 7 (VENC_SWREG21)

Address offset: 0x054

Reset value: 0x0000 0000

This register controls data such as H264.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Control of H264 (all format mode)

45.7.22 VENC stream header remainder MSB bits register (VENC_SWREG22)

Address offset: 0x058

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stream header remainder bits MSB (MSB aligned) (all format mode)

45.7.23 VENC stream header remainder LSB bits register (VENC_SWREG23)

Address offset: 0x05C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stream header remainder bits LSB (MSB aligned) (all format mode)

45.7.24 VENC stream buffer limit/output stream size register (VENC_SWREG24)

Address offset: 0x060

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stream buffer limit (64-bit addresses)/output stream size (bits) (all format mode)

45.7.25 VENC encoder control register 8 (VENC_SWREG25)

Address offset: 0x064

Reset value: 0x0000 0000

This register controls the MAD control and QP sum output.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Control of MAD control and QP sum output (all format mode)

45.7.26 VENC intra-slice bitmap register (VENC_SWREG26)

Address offset: 0x068

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : intra-slice bitmap for probability updates (all format mode)

45.7.27 VENC encoder control register 9 (VENC_SWREG27)

Address offset: 0x06C

Reset value: 0x0000 0000

This register controls H264 QP.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Control of H264 QP (all format mode)

45.7.28 VENC encoder control register 10 (VENC_SWREG28)

Address offset: 0x070

Reset value: 0x0000 0000

This register controls H264 checkpoint 1-2 .

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H264 checkpoint 1-2 (all format mode)

45.7.29 VENC encoder control register 11 (VENC_SWREG29)

Address offset: 0x074

Reset value: 0x0000 0000

This register controls H264 checkpoint 3-4 .

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 Checkpoint 3 -4 (all format mode)

45.7.30 VENC encoder control register 12 (VENC_SWREG30)

Address offset: 0x078

Reset value: 0x0000 0000

This register controls H264 checkpoint 5-6 .

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 checkpoint 5 -6 (all format mode)

45.7.31 VENC encoder control register 13 (VENC_SWREG31)

Address offset: 0x07C

Reset value: 0x0000 0000

This register controls H264 checkpoint 7-8.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 checkpoint 7 -8 (all format mode)

45.7.32 VENC encoder control register 14 (VENC_SWREG32)

Address offset: 0x080

Reset value: 0x0000 0000

This register controls H264 checkpoint 8-10.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 Checkpoint 8 -10 / Encoder control register 14 (all format mode)

45.7.33 VENC encoder control register 15 (VENC_SWREG33)

Address offset: 0x084

Reset value: 0x0000 0000

This register controls H264 checkpoint 1-2.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 Checkpoint word error 1-2 (all format mode)

45.7.34 VENC encoder control register 16 (VENC_SWREG34)

Address offset: 0x088

Reset value: 0x0000 0000

This register controls H264 checkpoint 3-4 and the second reference frame.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 checkpoint word error 3-4 and the second reference frame control (all format mode)

45.7.35 VENC H.264 checkpoint word error 5-6/encoder control register 17 (VENC_SWREG35)

Address offset: 0x08C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 Checkpoint word error 5-6 / Encoder control register 17 (all format mode)

45.7.36 VENC H.264 checkpoint delta QP 1-8/encoder control register 18 (VENC_SWREG36)

Address offset: 0x090

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : H.264 Checkpoint delta QP 1-8 / Encoder control register 18 (all format mode)

45.7.37 VENC encoder control register 19, stream start offset (VENC_SWREG37)

Address offset: 0x094

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Encoder control register 19 (all format mode)

45.7.38 VENC macroblock count output register (VENC_SWREG38)

Address offset: 0x098

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Macroblock count output (all format mode)

45.7.39 VENC base address for next pic luminance register (VENC_SWREG39)

Address offset: 0x09C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for next pic luminance (all format mode)

45.7.40 VENC stabilization mode control register (VENC_SWREG40)

Address offset: 0x0A0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization mode control (all format mode)

45.7.41 VENC stabilization motion sum div8 output register (VENC_SWREG41)

Address offset: 0x0A4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization motion sum div8 output (all format mode)

45.7.42 VENC stabilization GMV output, matrix 1, up-left position output register (VENC_SWREG42)

Address offset: 0x0A8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization GMV output, matrix 1 (up-left position) output (all format mode)

45.7.43 VENC stabilization GMV output, matrix 2, up position output register (VENC_SWREG43)

Address offset: 0x0AC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization GMV output, matrix 2 (up position) output (all format mode)

45.7.44 VENC stabilization matrix 3, up-right position output register (VENC_SWREG44)

Address offset: 0x0B0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 3 (up-right position) output (all format mode)

45.7.45 VENC stabilization matrix 4, left position output register (VENC_SWREG45)

Address offset: 0x0B4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 4 (left position) output (all format mode)

45.7.46 VENC stabilization matrix 5, GMV position output register (VENC_SWREG46)

Address offset: 0x0B8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 5 (GMV position) output (all format mode)

45.7.47 VENC stabilization matrix 6, right position output register (VENC_SWREG47)

Address offset: 0x0BC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 6 (right position) output (all format mode)

45.7.48 VENC stabilization matrix 7, down-left position output register (VENC_SWREG48)

Address offset: 0x0C0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 7 (down-left position) output (all format mode)

45.7.49 VENC stabilization matrix 8, down position output register (VENC_SWREG49)

Address offset: 0x0C4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 8 (down position) output (all format mode)

45.7.50 VENC stabilization matrix 9, down-right position output register (VENC_SWREG50)

Address offset: 0x0C8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Stabilization matrix 9 (down-right position) output (all format mode)

45.7.51 VENC base address for cabac context tables H264 register (VENC_SWREG51)

Address offset: 0x0CC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for cabac context tables (H264) or probability tables (all format mode)

45.7.52 VENC base address for MV output writing register (VENC_SWREG52)

Address offset: 0x0D0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : Base address for MV output writing (all format mode)

45.7.53 VENC RGB to YUV conversion coefficient A - B register (VENC_SWREG53)

Address offset: 0x0D4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : RGB to YUV conversion coefficient A - B (all format mode)

45.7.54 VENC RGB to YUV conversion coefficient C - E register (VENC_SWREG54)

Address offset: 0x0D8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : RGB to YUV conversion coefficient C - E (all format mode)

45.7.55 VENC RGB to YUV conversion coefficient F, RGB mask MSB bit position register (VENC_SWREG55)

Address offset: 0x0DC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : RGB to YUV conversion coefficient F, RGB mask MSB bit position (all format mode)

45.7.56 VENC intra area register (VENC_SWREG56)

Address offset: 0x0E0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : intra area (all format mode)

45.7.57 VENC CIR intra mb position register (VENC_SWREG57)

Address offset: 0x0E4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : CIR intra mb position (all format mode)

45.7.58 VENC intra slice bitmap for slices 0..31/base address for 1st DCT partition register (VENC_SWREG58)

Address offset: 0x0E8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : intra slice bitmap for slices 0..31 / Base address for 1st DCT partition (all format mode)

45.7.59 VENC intra slice bitmap for slices 32..63/base address for 2nd DCT partition register (VENC_SWREG59)

Address offset: 0x0EC

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : intra slice bitmap for slices 32..63 / Base address for 2nd DCT partition (all format mode)

45.7.60 VENC 1st ROI area register (VENC_SWREG60)

Address offset: 0x0F0

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : 1st ROI area (all format mode)

45.7.61 VENC 2nd ROI area register (VENC_SWREG61)

Address offset: 0x0F4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : 2nd ROI area (all format mode)

45.7.62 VENC ROI area delta QP, MV register (VENC_SWREG62)

Address offset: 0x0F8

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : ROI area delta QP, MV (all format mode)

45.7.63 VENC synthesis configuration register encoder 0 register (VENC_SWREG63)

Address offset: 0x0FC

Reset value: 0x1A62 2780

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 SWREG_FIELD[31:0] : Synthesis configuration register encoder 0 (read only) (all format mode)

45.7.64 VENC JPEG luma quantization 1/intra 16x16 mode 0-1 penalty register (VENC_SWREG64)

Address offset: 0x100

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 1 / intra 16x16 mode 0-1 penalty (all format mode)

45.7.65 VENC JPEG luma quantization 2/intra 16x16 mode 2-3 penalty register (VENC_SWREG65)

Address offset: 0x104

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 2 / intra 16x16 mode 2-3 penalty (all format mode)

45.7.66 VENC JPEG luma quantization 3/intra 4x4 mode 0-1 penalty register (VENC_SWREG66)

Address offset: 0x108

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 3 / intra 4x4 mode 0-1 penalty (all format mode)

45.7.67 VENC JPEG luma quantization 4/intra 4x4 mode 2-3 penalty register (VENC_SWREG67)

Address offset: 0x10C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 4 / intra 4x4 mode 2-3 penalty (all format mode)

45.7.68 VENC JPEG luma quantization 5/intra 4x4 mode 4-5 penalty register (VENC_SWREG68)

Address offset: 0x110

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 5 / intra 4x4 mode 4-5 penalty (all format mode)

45.7.69 VENC JPEG luma quantization 6/intra 4x4 mode 6-7 penalty register (VENC_SWREG69)

Address offset: 0x114

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 6 / intra 4x4 mode 6-7 penalty (all format mode)

45.7.70 VENC JPEG luma quantization 7/intra 4x4 mode 8-9 penalty register (VENC_SWREG70)

Address offset: 0x118

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 7 / intra 4x4 mode 8-9 penalty (all format mode)

45.7.71 VENC JPEG luma quantization 8/base address for segmentation map register (VENC_SWREG71)

Address offset: 0x11C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 8 / Base address for segmentation map (all format mode)

45.7.72 VENC JPEG luma quantization 9/segment1 parameter register (VENC_SWREG72)

Address offset: 0x120

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 9 / segment1 parameter (all format mode)

45.7.73 VENC JPEG luma quantization 10/segment1 parameter register (VENC_SWREG73)

Address offset: 0x124

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 10 / segment1 parameter (all format mode)

45.7.74 VENC JPEG luma quantization 11/segment1 parameter register (VENC_SWREG74)

Address offset: 0x128

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 11 / segment1 parameter (all format mode)

45.7.75 VENC JPEG luma quantization 12/segment1 parameter register (VENC_SWREG75)

Address offset: 0x12C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 12 / segment1 parameter (all format mode)

45.7.76 VENC JPEG luma quantization 13/segment1 parameter register (VENC_SWREG76)

Address offset: 0x130

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 13 / segment1 parameter (all format mode)

45.7.77 VENC JPEG luma quantization 14/segment1 parameter register (VENC_SWREG77)

Address offset: 0x134

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 14 / segment1 parameter (all format mode)

45.7.78 VENC JPEG luma quantization 15/segment1 parameter register (VENC_SWREG78)

Address offset: 0x138

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 15 / segment1 parameter (all format mode)

45.7.79 VENC JPEG luma quantization 16/segment2 parameter register (VENC_SWREG79)

Address offset: 0x13C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG luma quantization 16 / segment2 parameter (all format mode)

45.7.80 VENC JPEG chroma quantization 1/segment2 parameter register (VENC_SWREG80)

Address offset: 0x140

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 1 / segment2 parameter (all format mode)

45.7.81 VENC JPEG chroma quantization 2/segment2 parameter register (VENC_SWREG81)

Address offset: 0x144

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 2 / segment2 parameter (all format mode)

45.7.82 VENC JPEG chroma quantization 3/segment2 parameter register (VENC_SWREG82)

Address offset: 0x148

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 3 / segment2 parameter (all format mode)

45.7.83 VENC JPEG chroma quantization 4/segment2 parameter register (VENC_SWREG83)

Address offset: 0x14C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 4 / segment2 parameter (all format mode)

45.7.84 VENC JPEG chroma quantization 5/segment2 parameter register (VENC_SWREG84)

Address offset: 0x150

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 5 / segment2 parameter (all format mode)

45.7.85 VENC JPEG chroma quantization 6/segment2 parameter register (VENC_SWREG85)

Address offset: 0x154

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 6 / segment2 parameter (all format mode)

45.7.86 VENC JPEG chroma quantization 7/segment2 parameter register (VENC_SWREG86)

Address offset: 0x158

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 7 / segment2 parameter (all format mode)

45.7.87 VENC JPEG chroma quantization 8/segment2 parameter register (VENC_SWREG87)

Address offset: 0x15C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 8 / segment2 parameter (all format mode)

45.7.88 VENC JPEG chroma quantization 9/segment3 parameter register (VENC_SWREG88)

Address offset: 0x160

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 9 / segment3 parameter (all format mode)

45.7.89 VENC JPEG chroma quantization 10/segment3 parameter register (VENC_SWREG89)

Address offset: 0x164

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 10 / segment3 parameter (all format mode)

45.7.90 VENC JPEG chroma quantization 11/segment3 parameter register (VENC_SWREG90)

Address offset: 0x168

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 11 / segment3 parameter (all format mode)

45.7.91 VENC JPEG chroma quantization 12/segment3 parameter register (VENC_SWREG91)

Address offset: 0x16C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 12 / segment3 parameter (all format mode)

45.7.92 VENC JPEG chroma quantization 13/segment3 parameter register (VENC_SWREG92)

Address offset: 0x170

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 13 / segment3 parameter (all format mode)

45.7.93 VENC JPEG chroma quantization 14/segment3 parameter register (VENC_SWREG93)

Address offset: 0x174

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 14 / segment3 parameter (all format mode)

45.7.94 VENC JPEG chroma quantization 15/segment3 parameter register (VENC_SWREG94)

Address offset: 0x178

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 SWREG_FIELD[31:0] : JPEG chroma quantization 15 / segment3 parameter (all format mode)

45.7.95 VENC JPEG chroma quantization 16/segment3 parameter register (VENC_SWREG95)

Address offset: 0x17C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

45.7.96 VENC DMV 4p/1p penalty values 0-3 register (VENC_SWREG96)

Address offset: 0x180

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

45.7.97 VENC DMV 4p/1p penalty values 4-7 register (VENC_SWREG97)

Address offset: 0x184

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SWREG_FIELD[31:16] | |||||||||||||||

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWREG_FIELD[15:0] | |||||||||||||||

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

45.7.98 VENC DMV 4p/1p penalty values register (VENC_SWREGx)

Address offset: 0x188 + 0x4 * (x - 98), (x = 98 to 126)

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SWREG_FIELD[31:16] | |||||||||||||||