27. Flexible memory controller (FMC)

The flexible memory controller (FMC) includes three memory controllers:

- • the NOR/PSRAM memory controller

- • the NAND memory controller

- • the synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) controller

27.1 FMC main features

The FMC functional block makes the interface with: synchronous and asynchronous static memories, SDRAM memories, and NAND flash memory. Its main purposes are:

- • to translate AXI transactions into the appropriate external device protocol

- • to meet the access time requirements of the external memory devices

All external memories share the addresses, data and control signals with the controller. Each external device is accessed by means of a unique Chip Select. The FMC performs only one access at a time to an external device.

The main features of the FMC are the following:

- • Interface with static-memory mapped devices including:

- – Static random access memory (SRAM)

- – NOR flash memory/One NAND flash memory

- – PSRAM (4 memory subregions)

- – Ferroelectric RAM (FRAM)

- – NAND flash memory with ECC hardware to check up to 8 Kbytes of data

- • Interface with synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) memories

- • Burst mode support for faster access to synchronous devices such as NOR flash memory, PSRAM and SDRAM

- • Programmable continuous clock output for asynchronous and synchronous accesses

- • 8-, 16- or 32-bit wide data bus

- • Independent chip-select control for each memory region

- • Independent configuration for each memory region

- • Write enable and byte lane select outputs for use with PSRAM, SRAM and SDRAM devices

- • External asynchronous wait control

At startup the FMC pins must be configured by the user application. The FMC input/output pins which are not used by the application can be used for other purposes.

After reset, the FMC is disabled. Once all the used memory controllers are configured, the FMC must be enabled by setting the FMCEN bit.

The FMC registers that define the external device type and associated characteristics are set at boot time and do not change until the next reset or power-up. If some registers have to be re-configured, the FMC must be disabled (FMCEN bit set to 0x0). However, only few bits can be changed on the fly:

- • FMCEN bit

- • ECCEN and PBEN bits in FMC_PCR register

- • FMC_CSQICR and FMC_CSQIER register bits

- • FMC command sequencer registers and FMC BCH registers

- • WEN bit in the FMC_PCR register

- • MODE[2:0], DS1/DS2, NRFS[3:0] and MRD[13:0] bits in FMC_SDCMR register

- • REIE and CRE bits in the FMC_SDRTR register.

If some parameters have to be modified while the FMC is enabled, the FMC must be first disabled so that no further access is allowed to any memory controller during register modification. Once all needed configurations are updated, enable the FMC as follows:

- 1. Disable FMC by resetting the FMCEN bit.

- 2. Wait ISOST[1:0] bits in FMC_SR register to be set to 0b11.

- 3. Wait until PEF flag is set in the FMC_SR register.

- 4. Program the registers with new values.

- 5. Enable the FMC by setting the FMCEN bit.

When the SDRAM controller is available, if the SDCLK clock ratio or refresh rate has to be modified after the initialization phase, the following procedure must be followed.

- 1. Stop by software, the AXI traffic from/to the SDRAM devices only.

- 2. Put all the SDRAM devices in self refresh and wait for the CMDOK command completion flag.

- 3. Change the clock ratio to the new value.

- 4. Send a normal mode command (NRM) to exit from SR and wait for the CMDOK command completion flag.

- 5. Send a load mode register command (LMR) as needed to update devices timing (optional)

- 6. Resume the AXI traffic to SDRAM devices.

27.2 FMC implementation

Table 146. FMC features

| Modes/features | FMC |

|---|---|

| NAND flash chip-select outputs | 4 |

| NAND flash ready/busy | 1 |

| NAND/NOR flash with common WAIT pin | No |

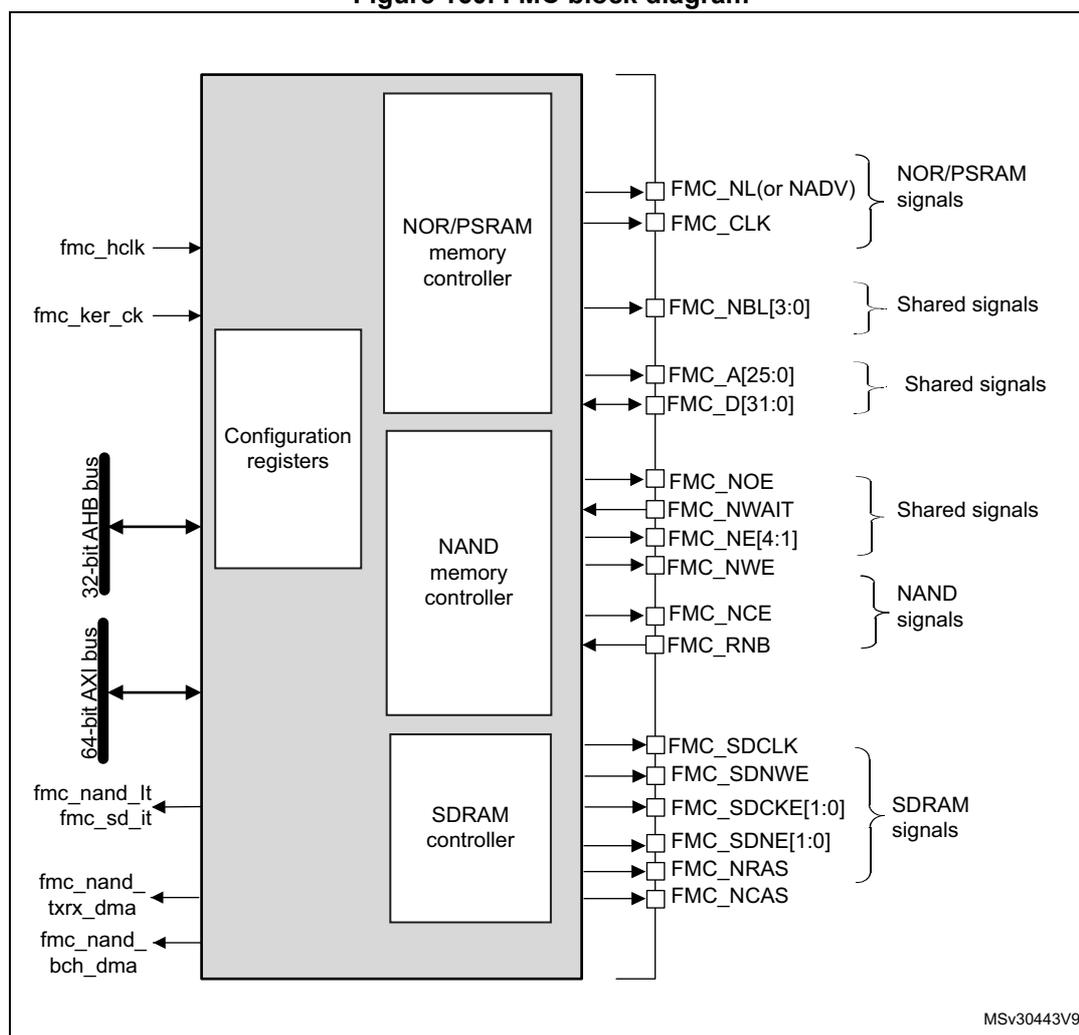

27.3 FMC block diagram

The FMC consists of the following main blocks:

- • The NOR flash/PSRAM/SRAM controller

- • The NAND controller

- • The SDRAM controller

- • The AXI interface

- • The AHB interface (including the FMC configuration registers)

The block diagram is shown in the below figure.

Figure 160. FMC block diagram

The block diagram illustrates the internal architecture and external connections of the Flexible Memory Controller (FMC). The main components and their connections are as follows:

- Internal Components:

- NOR/PSRAM memory controller: Located at the top right of the FMC block.

- NAND memory controller: Located in the middle right of the FMC block.

- SDRAM controller: Located at the bottom right of the FMC block.

- Configuration registers: Located in the center-left of the FMC block.

- External Connections (Left Side):

- fmc_hclk: Input signal to the top of the FMC block.

- fmc_ker_ck: Input signal to the middle of the FMC block.

- 32-bit AHB bus: Bidirectional connection to the configuration registers.

- 64-bit AXI bus: Bidirectional connection to the configuration registers.

- fmc_nand_it / fmc_sd_it: Input signals to the bottom of the FMC block.

- fmc_nand_txrx_dma: Input signal to the bottom of the FMC block.

- fmc_nand_bch_dma: Input signal to the bottom of the FMC block.

- External Connections (Right Side):

- NOR/PSRAM signals:

- FMC_NL(or NADV): Output signal.

- FMC_CLK: Output signal.

- Shared signals:

- FMC_NBL[3:0]: Output signal.

- FMC_A[25:0]: Output signal.

- FMC_D[31:0]: Bidirectional data bus.

- Shared signals:

- FMC_NOE: Output signal.

- FMC_NWAIT: Input signal.

- FMC_NE[4:1]: Output signal.

- FMC_NWE: Output signal.

- NAND signals:

- FMC_NCE: Output signal.

- FMC_RNB: Input signal.

- SDRAM signals:

- FMC_SDCLK: Output signal.

- FMC_SDNWE: Output signal.

- FMC_SDCKE[1:0]: Output signal.

- FMC_SDNE[1:0]: Output signal.

- FMC_NRAS: Output signal.

- FMC_NCAS: Output signal.

- NOR/PSRAM signals:

MSv30443V9

27.4 FMC internal signals

Table 147 gives the list of FMC internal signals. FMC pins (or external signals) are described in Section 27.8.1: External memory interface signals .

Table 147. FMC internal signals

| Names | Signal type | Description |

|---|---|---|

| fmc_nand_it | Digital output | FMC NAND flash interrupt |

| fmc_sd_it | Digital output | FMC SDRAM interrupt |

| fmc_ker_ck | Digital input | FMC kernel clock |

| fmc_hclk | Digital input | FMC interface clock |

| fmc_nand_txrx_dma | Digital output | DMA request for reading or writing data from/to NAND flash memory |

| fmc_nand_bch_dma | Digital output | DMA request for BCH results |

27.5 AHB interface

The AHB slave interface allows internal CPUs to configure the FMC registers.

The AHB clock (HCLK) is the reference clock for the FMC register accesses.

The FMC registers must be accessed by words (32 bits). For non 32-bit AHB accesses, FMC does not return an AHB bus error and the register value can be corrupted.

27.6 AXI interface

The AXI slave interface allows internal CPUs and other bus master peripherals to access the external memories.

AXI transactions are translated into the external device protocol. As the AXI data bus is 64-bit wide, the AXI transactions might be split into several consecutive 32- or 16- or 8-bit accesses according to data size accesses.

The FMC generates an AXI slave error when one of the following conditions is met:

- • When reading or writing to an FMC memory region (memory region 1 to 4) which is not enabled

- • When reading or writing to any FMC memory region while the FMC is disabled (FMCEN bit is reset)

- • When reading or writing by the command sequencer to NAND memory region while it is disabled

- • When reading or writing to the NOR flash memory region while the MBKEN bit is reset in the FMC_BCRx register

- • When writing to a write-protected SDRAM device (WP bit set in the SDRAM_SDCRx register)

- • When the SDRAM address range is violated (access to a reserved address range)

- • When reading or writing to an SDRAM device with the SDEN bit cleared in the FMC_SDCRx register

The FMC generates an AXI decoder error in the following conditions:

- • When ADDR[31:28] address bits are not supported by the FMC memory region base address following the BMAP[1:0] bits configuration

- • and when an access to an SDRAM or a NAND memory region is performed while the SDRAM or the NAND controller is not present.

The kernel clock for the FMC is the asynchronous fmc_ker_ck clock (refer the Reset and Clock control (RCC) section for details on fmc_ker_ck clock source selection).

27.6.1 Supported memories and transactions

General transaction rules

The requested AXI transaction data size can be 8-, 16-, 32- or 64-bit wide whereas the accessed external device has a fixed data width. This may lead to inconsistent transfers.

Therefore, some simple transaction rules must be followed:

- • AXI transaction size and memory data size must be equal to prevent issues from occurring.

- • AXI transaction size is greater than the memory size:

In this case, the FMC splits the AXI transaction into smaller consecutive memory accesses to meet the external data width.

- • AXI transaction size is smaller than the memory size:

The transfer may or not be consistent depending on the type of external device:

- – Accesses to devices that have the byte select feature (SRAM, ROM, PSRAM, SDRAM)

In this case, the FMC allows read/write transactions and accesses the right data through its byte lanes NBL[3:0].

Bytes to be written are addressed by NBL[3:0].

All memory bytes are read (NBL[3:0] are driven low during read transaction) and the useless ones are discarded.

- – Accesses to devices that do not have the byte select feature (NOR and NAND flash memories)

This situation occurs when a byte access is requested to a 16-bit wide flash memory. Since the device cannot be accessed in Byte mode (only 16-bit words can be read/written from/to the flash memory), write transactions are not allowed while read transactions are allowed (the controller reads the entire 16-bit memory word and uses only the required byte).

Wrap support for NOR flash/PSRAM

Synchronous memories must be configured in Linear burst mode of undefined length as not all masters can issue wrap transactions.

If a master generates a wrap transaction:

- • The read operation is split into two linear burst transactions.

- • The write operation is split into two linear burst transactions.

Configuration registers

The FMC can be configured through a set of registers. Refer to Section 27.8.6 , for a detailed description of the NOR flash/PSRAM controller registers. Refer to Section 27.9.9 , for a detailed description of the NAND flash registers and to Section 27.10.5 for a detailed description of the SDRAM controller registers.

27.7 External device address mapping

From the FMC point of view, the external memory is divided into fixed-size memory regions of 256 Mbytes each (see Table 148 ):

- • Memory region 1 is used to address up to 4 NOR flash memories or PSRAM devices. This region is split into four NOR/PSRAM subregions with four dedicated Chip Selects, as follows:

- – Subregion 1 - NOR/PSRAM 1

- – Subregion 2 - NOR/PSRAM 2

- – Subregion 3- NOR/PSRAM 3

- – Subregion 4 - NOR/PSRAM 4

Note: The Memory region 1 type attribute must be declared as 'device'.

- • Memory region 5 and 6 are used to address SDRAM devices (one device per region).

For each memory region, the type of memory to be used can be configured by the user application through the Configuration register.

Table 148. FMC memory regions (default mapping)

| Address | Memory region | Supported memory type |

|---|---|---|

| 0x6000 0000 - 0x6FFF FFFF | Memory region 1 | NOR flash memory/PSRAM/SRAM |

| 0xC000 0000 - 0xCFFF FFFF | Memory region 5 | SDRAM device 1 |

| 0xD000 0000 - 0xDFFF FFFF | Memory region 6 | SDRAM device 2 |

The mapping of FMC memory regions can be modified through the BMAP[1:0] bits in FMC_BCR1 register. Table 149 shows the configuration to swap the NOR/PSRAM and SDRAM memory regions or remap SDRAM device 1 and 2. Thus allowing to access the SDRAM devices at two different address mapping.

Table 149. FMC memory region remap using BMAP[1:0]

| FMC memory region | BMAP[1:0] = 00 (Default mapping) | BMAP[1:0] = 01 | BMAP[1:0] = 10 |

|---|---|---|---|

| Memory region 1 | NOR/PSRAM/SRAM | SDRAM device 1 | NOR/PSRAM/SRAM |

| Memory region 5 | SDRAM device 1 | NOR/PSRAM/SRAM | SDRAM device 1 |

| Memory region 6 | SDRAM device 2 | SDRAM device 2 | SDRAM device 2 |

27.7.1 NOR/PSRAM address mapping

ADDR[27:26] bits are used to select one of the four memory subregions as shown in Table 150 .

Table 150. NOR/PSRAM subregion selection

| ADDR[27:26] (1) | Selected subregion |

|---|---|

| 00 | Subregion 1 - NOR/PSRAM 1 |

| 01 | Subregion 2 - NOR/PSRAM 2 |

| 10 | Subregion 3- NOR/PSRAM 3 |

| 11 | Subregion 4- NOR/PSRAM 4 |

- 1. ADDR are internal address lines that are translated to external memory.

The ADDR[25:0] bits contain the external memory address. Since ADDR is a byte address whereas the memory is addressed at word level, the address actually issued to the memory varies according to the memory data width, as shown in the following table.

Table 151. NOR/PSRAM External memory address

| Memory width (1) | Data address issued to the memory | Maximum memory capacity (bits) |

|---|---|---|

| 8-bit | ADDR[25:0] | 64 Mbytes * 8 = 512 Mbit |

| 16-bit | ADDR[25:1] >> 1 | 64 Mbytes/2 * 16 = 512 Mbit |

| 32-bit | ADDR[25:2] >> 2 | 64 Mbytes/4 * 32 = 512 Mbit |

- 1. In case of a 16-bit external memory width, the FMC internally uses ADDR[25:1] to generate the address for external memory FMC_A[24:0]. In case of a 32-bit memory width, the FMC internally uses ADDR[25:2] to generate the external address.

Whatever the external memory width, FMC_A[0] must be connected to external memory address A[0].

27.7.2 NAND flash memory address mapping

The 4 Kbyte NAND flash address bits are mapped according to Table 152 .

Table 152. NAND access memory map

| Address field | FMC signal name | Function | Detailed description |

|---|---|---|---|

| ADDR[10] | NCE | NAND chip enable selection | 00: NCE1 |

| ADDR[9:8] | - | Reserved | - |

| ADDR[7] | - | Timing selection | 0: Common space, timing defined by FMC_PMEM 1: Attribute space, timing defined by FMC_PATT |

| ADDR[6] | - | Reserved | - |

| ADDR[5] | A[17] | Address (ALE) | 00: Data section 01: Command section 10: Address section 11: reserved |

| ADDR[4] (1) | A[16] | Command (CLE) |

- 1. Four address LSBs are don't care: each section has 16 bytes mapped to the alias region.

The application software uses the 3 sections to access the NAND flash memory:

- • To send a command to NAND flash memory , the software must write the command value to any memory location in the command section.

- • To specify the NAND flash address that must be read or written , the software must write the address value to any memory location in the address section. Since an address can be 4 or 5 bytes long (depending on the actual memory size), several consecutive write operations to the address section are required to specify the full address.

- • To read or write data , the software reads or writes the data from/to any memory location in the data section.

Since the NAND flash memory automatically increments addresses, there is no need to increment the address of the data section to access consecutive memory locations.

Note: The NAND region has to be accessed as a device and not as memory. Write accesses to command and address sections must be done in Byte mode and aligned with the section base address (offset = 0).

Read and Write accesses to NAND data section must be in Byte mode for 8-bit NAND flash memories and Byte or Half-word mode for 16-bit NAND flash memories.

Read and Write bursts must start at section base address (offset = 0) and must not cross the 16-byte section boundary.

27.7.3 SDRAM address mapping

Two SDRAM regions are available as indicated in Table 153 .

Table 153. SDRAM device selection

| Selected device | Control register | Timing register |

|---|---|---|

| SDRAM device 1 | FMC_SDCR1 | FMC_SDTR |

| SDRAM device 2 | FMC_SDCR2 |

The following table shows SDRAM mapping for an 13-bit row, a 11-bit column and 4 internal bank configuration.

Table 154. SDRAM address mapping

| Memory width (1) | Internal bank | Row address | Column address (2) | Maximum memory capacity (Mbytes) |

|---|---|---|---|---|

| 8-bit | ADDR[25:24] | ADDR[23:11] | ADDR[10:0] | 64 Mbytes: 4 * 8K * 2K |

| 16-bit | ADDR[26:25] | ADDR[24:12] | ADDR[11:1] | 128 Mbytes: 4 * 8K * 2K * 2 |

| 32-bit | ADDR[27:26] | ADDR[25:13] | ADDR[12:2] | 256 Mbytes: 4 * 8K * 2K * 4 |

1. When interfacing with a 16-bit memory, the FMC internally uses the ADDR[11:1] internal address lines to generate the external address. When interfacing with a 32-bit memory, the FMC internally uses ADDR[12:2] lines to generate the external address. Whatever the memory width, FMC_A[0] has to be connected to the SDRAM A[0].

2. The AutoPrecharge is not supported. However, FMC_A[10] must be connected to SDRAM A[0].

The ADDR[27:0] bits are translated to external SDRAM address depending on the SDRAM controller configuration:

- • Row size: 11, 12 or 13 bits

- • Column size: 8, 9, 10 or 11 bits

- • Number of internal banks: two or four internal banks

The following tables show the SDRAM address mapping versus the SDRAM controller configuration.

Table 155. SDRAM address mapping with 8-bit data bus width (1)(2)

| Row size configuration | ADDR (Internal address lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 11-bit row size configuration | Res. | Bank [1:0] | Row[10:0] | Column[7:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[8:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[9:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[10:0] | |||||||||||||||||||||||||

| 12-bit row size configuration | Res. | Bank [1:0] | Row[11:0] | Column[7:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[8:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[9:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[10:0] | |||||||||||||||||||||||||

| 13-bit row size configuration | Res. | Bank [1:0] | Row[12:0] | Column[7:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[8:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[9:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[10:0] | |||||||||||||||||||||||||

1. BANK[1:0] are the Bank Address BA[1:0]. When only 2 internal banks are used, BA1 must always be cleared.

2. Access to Reserved (Res.) address range generates an AXI slave error.

Table 156. SDRAM address mapping with 16-bit data bus width (1)(2)

| Row size Configuration | ADDR (address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 11-bit row size configuration | Res. | Bank [1:0] | Row[10:0] | Column[7:0] | BM0 (3) | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[8:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[9:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[10:0] | BM0 | ||||||||||||||||||||||||

| 12-bit row size configuration | Res. | Bank [1:0] | Row[11:0] | Column[7:0] | BM0 | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[8:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[9:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[10:0] | BM0 | ||||||||||||||||||||||||

| 13-bit row size configuration | Res. | Bank [1:0] | Row[12:0] | Column[7:0] | BM0 | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[8:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[9:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[10:0] | BM0 | ||||||||||||||||||||||||

- 1. BANK[1:0] are the Bank Address BA[1:0]. When only 2 internal banks are used, BA1 must always be cleared.

- 2. Access to Reserved space (Res.) generates an AXI Slave error.

- 3. BM0: is the byte mask for 16-bit access.

Table 157. SDRAM address mapping with 32-bit data bus width (1)(2)

| Row size configuration | ADDR (address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 11-bit row size configuration | Res. | Bank [1:0] | Row[10:0] | Column[7:0] | BM[1:0] (3) | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[8:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[9:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[10:0] | BM[1:0] | ||||||||||||||||||||||||

| Row size configuration | ADDR (address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 12-bit row size configuration | Res. | Bank [1:0] | Row[11:0] | Column[7:0] | BM[1:0] | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[8:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[9:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[10:0] | BM[1:0] | ||||||||||||||||||||||||

| 13-bit row size configuration | Res. | Bank [1:0] | Row[12:0] | Column[7:0] | BM[1:0] | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[8:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[9:0] | BM[1:0] | ||||||||||||||||||||||||

| Bank [1:0] | Row[12:0] | Column[10:0] | BM[1:0] | |||||||||||||||||||||||||

1. BANK[1:0] are the Bank Address BA[1:0]. When only 2 internal banks are used, BA1 must always be cleared.

2. Access to Reserved space (Res.) generates an AXI slave error.

3. BM[1:0]: is the byte mask for 32-bit access.

27.8 NOR flash/PSRAM controller

The FMC generates the appropriate signal timings to drive the following types of memories:

- • Asynchronous SRAM, FRAM and ROM

- – 8 bits

- – 16 bits

- – 32 bits

- • PSRAM (CellularRAM™)

- – Asynchronous mode

- – Burst mode for synchronous accesses with configurable option to split burst access when crossing boundary page for CRAM 1.5.

- – Multiplexed or non-multiplexed

- • NOR flash memory

- – Asynchronous mode

- – Burst mode for synchronous accesses

- – Multiplexed or non-multiplexed

The FMC outputs a unique Chip Select signal, NE[4:1], per memory region. All the other signals (addresses, data and control) are shared.

The FMC supports a wide range of devices through a programmable timings among which:

- • Programmable wait-states (up to 15)

- • Programmable bus turnaround cycles (up to 15)

- • Programmable output enable and write enable delays (up to 15)

- • Independent read and write timings and protocol to support the widest variety of memories and timings

- • Programmable continuous clock (FMC_CLK) output.

The FMC output Clock (FMC_CLK) is a submultiple of the fmc_ker_ck clock. It can be delivered to the selected external device either during synchronous accesses only or during asynchronous and synchronous accesses depending on the CCKEN bit configuration in the FMC_BCR1 register:

- • If the CCKEN bit is reset, the FMC generates the clock (FMC_CLK) only during synchronous accesses (Read/write transactions).

- • If the CCKEN bit is set, the FMC generates a continuous clock during asynchronous and synchronous accesses. To generate the FMC_CLK continuous clock, memory region 1 must be configured in synchronous mode (see Section 27.8.6: NOR/PSRAM controller registers ). Since the same clock is used for all synchronous memories, when a continuous output clock is generated and synchronous accesses are performed, the AXI data size has to be the same as the memory data width (MWID[1:0]) otherwise the FMC_CLK frequency is changed depending on AXI data transaction (refer to Section 27.8.5: Synchronous transactions for FMC_CLK divider ratio formula).

The size of each memory region is fixed and equal to 64 Mbytes. Each memory region is configured through dedicated registers (see Section 27.8.6: NOR/PSRAM controller registers ).

The programmable memory parameters include access times (see Table 158 ) and support for wait management (for PSRAM and NOR flash accessed in burst mode).

Table 158. Programmable NOR/PSRAM access parameters

| Parameter | Function | Access mode | Unit | Min. | Max. |

|---|---|---|---|---|---|

| Address setup | Duration of the address setup phase | Asynchronous | FMC clock cycle (fmc_ker_ck) | 0 | 15 |

| Address hold | Duration of the address hold phase | Asynchronous, muxed I/Os | FMC clock cycle (fmc_ker_ck) | 1 | 15 |

| NBL setup | Duration of the Byte lanes setup phase | Asynchronous | FMC clock cycle (fmc_ker_ck) | 0 | 3 |

| Data setup | Duration of the data setup phase | Asynchronous | FMC clock cycle (fmc_ker_ck) | 1 | 256 |

| Data hold | Duration of the data hold phase | Asynchronous | FMC clock cycle (fmc_ker_ck) | 0 | 3 |

| Bust turn | Duration of the bus turnaround phase | Asynchronous and synchronous read | FMC clock cycle (fmc_ker_ck) | 0 | 15 |

| Parameter | Function | Access mode | Unit | Min. | Max. |

|---|---|---|---|---|---|

| Clock divide ratio | Number of FMC clock cycles (fmc_ker_ck) to build one memory clock cycle (CLK) | Synchronous | FMC clock cycle (fmc_ker_ck) | 2 | 16 |

| Data latency | Number of clock cycles to issue to the memory before the first data of the burst | Synchronous | Memory clock cycle (fmc_ker_ck) | 2 | 17 |

27.8.1 External memory interface signals

Table 159 , Table 160 and Table 161 list the signals that are typically used to interface with NOR flash memory, SRAM and PSRAM.

Note: The prefix “N” identifies the signals which are active low.

NOR flash memory, non-multiplexed I/Os

Table 159. Non-multiplexed I/O NOR flash memory| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:0] | O | Address bus |

| D[31:0] | I/O | Bidirectional data bus |

| NE[x] | O | Chip Select, x = 1 to 4 |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(=NADV) | O | Latch enable (this signal is called address valid, NADV, by some NOR flash devices) |

| NWAIT | I | NOR flash wait input signal to the FMC |

The maximum capacity is 512 Mbits (26 address lines).

NOR flash memory, 16-bit multiplexed I/Os

Table 160. 16-bit multiplexed I/O NOR flash memory| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:16] | O | Address bus |

| AD[15:0] | I/O | 16-bit multiplexed, bidirectional address/data bus (the 16-bit address A[15:0] and data D[15:0] are multiplexed on the databus) |

| NE[x] | O | Chip Select, x = 1 to 4 |

| NOE | O | Output enable |

| NWE | O | Write enable |

| FMC signal name | I/O | Function |

|---|---|---|

| NL(=NADV) | O | Latch enable (this signal is called address valid, NADV, by some NOR flash devices) |

| NWAIT | I | NOR flash wait input signal to the FMC |

The maximum capacity is 512 Mbits.

PSRAM/SRAM/FRAM, non-multiplexed I/Os

Table 161. Non-multiplexed I/Os PSRAM/SRAM| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (only for PSRAM synchronous access) |

| A[25:0] | O | Address bus |

| D[31:0] | I/O | Data bidirectional bus |

| NE[x] | O | Chip Select, x = 1 to 4 (called NCE by PSRAM (CellularRAM™, CRAM)) |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(= NADV) | O | Address valid only for PSRAM input (memory signal name: NADV) |

| NWAIT | I | PSRAM wait input signal to the FMC |

| NBL[3:0] | O | Byte lane output (upper and lower byte enable) |

The maximum capacity is 512 Mbits.

PSRAM, 16-bit multiplexed I/Os

Table 162. 16-bit multiplexed I/O PSRAM| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:16] | O | Address bus |

| AD[15:0] | I/O | 16-bit multiplexed, bidirectional address/data bus (the 16-bit address A[15:0] and data D[15:0] are multiplexed on the databus) |

| NE[x] | O | Chip Select, x = 1 to 4 (called NCE by PSRAM (CellularRAM™, CRAM)) |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(= NADV) | O | Address valid PSRAM input (memory signal name: NADV) |

| NWAIT | I | PSRAM wait input signal to the FMC |

| NBL[3:0] | O | Byte lane output (upper and lower byte enable) |

The maximum capacity is 512 Mbits (26 address lines).

27.8.2 Supported memories and transactions

Table 163 below shows an example of the supported devices, access modes and transactions when the memory data bus is 16-bit wide for NOR flash memory, PSRAM and SRAM. The transactions not allowed (or not supported) by the FMC are shown in gray in this example.

Table 163. NOR flash/PSRAM: Example of supported memories and transactions

| Device | Mode | R/W | AXI data size | Memory data size | Allowed/ not allowed | Comments |

|---|---|---|---|---|---|---|

| NOR flash (muxed I/Os and non-muxed I/Os) | Asynchronous | R | 8 | 16 | Y | - |

| Asynchronous | W | 8 | 16 | N | - | |

| Asynchronous | R | 16 | 16 | Y | - | |

| Asynchronous | W | 16 | 16 | Y | - | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | R | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous | W | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous page | R | - | 16 | N | Mode is not supported | |

| Synchronous | R | 8 | 16 | N | - | |

| Synchronous | R | 16 | 16 | Y | - | |

| Synchronous | R | 32 | 16 | Y | - | |

| Synchronous | R | 64 | 16 | Y | Split into 4 FMC accesses |

Table 163. NOR flash/PSRAM: Example of supported memories and transactions

| Device | Mode | R/W | AXI data size | Memory data size | Allowed/ not allowed | Comments |

|---|---|---|---|---|---|---|

| PSRAM (multiplexed I/Os and non- multiplexed I/Os) | Asynchronous | R | 8 | 16 | Y | - |

| Asynchronous | W | 8 | 16 | Y | Use of byte lanes NBL[3:0] | |

| Asynchronous | R | 16 | 16 | Y | - | |

| Asynchronous | W | 16 | 16 | Y | - | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | R | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous | W | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous page | R | - | 16 | N | Mode is not supported | |

| Synchronous | R | 8 | 16 | N | - | |

| Synchronous | R | 16 | 16 | Y | - | |

| Synchronous | R | 32/64 | 16 | Y | - | |

| Synchronous | W | 8 | 16 | Y | Use of byte lanes NBL[3:0] | |

| Synchronous | W | 16/32/64 | 16 | Y | - | |

| SRAM and ROM | Asynchronous | R | 8 / 16 | 16 | Y | - |

| Asynchronous | W | 8 / 16 | 16 | Y | Use of byte lanes NBL[3:0] | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | R | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous | W | 64 | 16 | Y | Split into 4 FMC accesses |

27.8.3 General timing rules

Signals synchronization

- • All controller output signals change on the rising edge of the fmc_ker_ck clock

- • In synchronous mode (read or write), all output signals change on the rising edge of fmc_ker_ck clock.

- • NBL signals

They are applicable to memories which support byte enable.

- – The NBL signals are driven low:

from the start of a read memory transfer and optionally earlier according to NBLSET, when the device requires some setup time from NBL to NCE, for bytes to be written during data transfer and according to the first data bytes during the address transfer. - – The NBL signals are driven high two FMC_CLK clock cycles after the completion of the read or write transfer.

27.8.4 NOR flash/PSRAM controller asynchronous transactions

Asynchronous static memories (NOR flash, PSRAM, SRAM, FRAM)

- • Signals are synchronized by the internal clock fmc_ker_ck. This clock is not issued to the memory.

- • The FMC always samples the data before deasserting the Chip Select signal NE. This guarantees that the memory data hold timing constraint is met (minimum chip enable high to data transition is usually 0 ns).

- • If the extended mode is enabled (EXTMOD bit is set in the FMC_BCRx register), up to four extended modes (A, B, C and D) are available. It is possible to mix A, B, C and D modes for read and write operations. For example, read operation can be performed in mode A and write in mode B. The extended mode is not compatible with the muxed mode (EXTMOD bit must be kept cleared in muxed mode).

- • If the extended mode is disabled (EXTMOD bit is reset in the FMC_BCRx register), the FMC can operate in mode 1 or mode 2 as follows:

- – Mode 1 is the default mode when SRAM/PSRAM memory type is selected (MTYP[1:0] = 0x0 or 0x01 in the FMC_BCRx register)

- – Mode 2 is the default mode when NOR memory type is selected (MTYP[1:0] = 0x10 in the FMC_BCRx register).

Mode 1 - SRAM/FRAM/PSRAM (CRAM)

The next figures show the read and write transactions for the supported modes followed by the required configuration of FMC_BCRx, and FMC_BTRx/FMC_BWTRx registers.

Figure 161. Mode 1 read access waveforms

![Timing diagram for Mode 1 read access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over time with various setup and hold time parameters.](/RM0486-STM32N6x5-x7/f3f8841ae3b111d0d5d1100a018eeda4_img.jpg)

This timing diagram illustrates the read access waveforms for Mode 1. The signals shown are address lines A[25:0], byte lane signals NBL[x:0], active low address strobe NEx, active low output enable NOE, active low write enable NWE, and a multi-bit Data bus. The timing is measured in fmc_ker_ck cycles. The sequence starts with NBLSET, followed by ADDSET, then DATAST (when data is driven by memory), and finally DATAHLD. NWE is held high throughout the read transaction. The diagram is labeled MSV45371V1.

Figure 162. Mode 1 write access waveforms

![Timing diagram for Mode 1 write access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over time with various setup and hold time parameters.](/RM0486-STM32N6x5-x7/40f67e00366f8c9865fa5006f1407680_img.jpg)

This timing diagram illustrates the write access waveforms for Mode 1. The signals shown are address lines A[25:0], byte lane signals NBL[x:0], active low address strobe NEx, active low output enable NOE, active low write enable NWE, and a multi-bit Data bus. The timing is measured in fmc_ker_ck cycles. The sequence starts with NBLSET, followed by ADDSET, then DATAST (when data is driven by controller), and finally DATAHLD + 1. NWE is asserted low during the data transfer phase. The diagram is labeled MSV45372V1.

The DATAHLD time at the end of the read and write transaction guarantee the address and data hold time after the NOE/NWE rising edge. For write, the DATAST value must be greater than zero (DATAST > 0).

Table 164. FMC_BCRx bitfields (mode 1)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | 0x0 (no effect in asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in asynchronous mode) |

| 15 | ASYNCWAIT | Set if the memory supports this feature. Otherwise keep cleared. |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | 0x0 (no effect in asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP | As needed, exclude 0x2 (NOR flash memory) |

| 1 | MUXE | 0x0 |

| 0 | MBKEN | 0x1 |

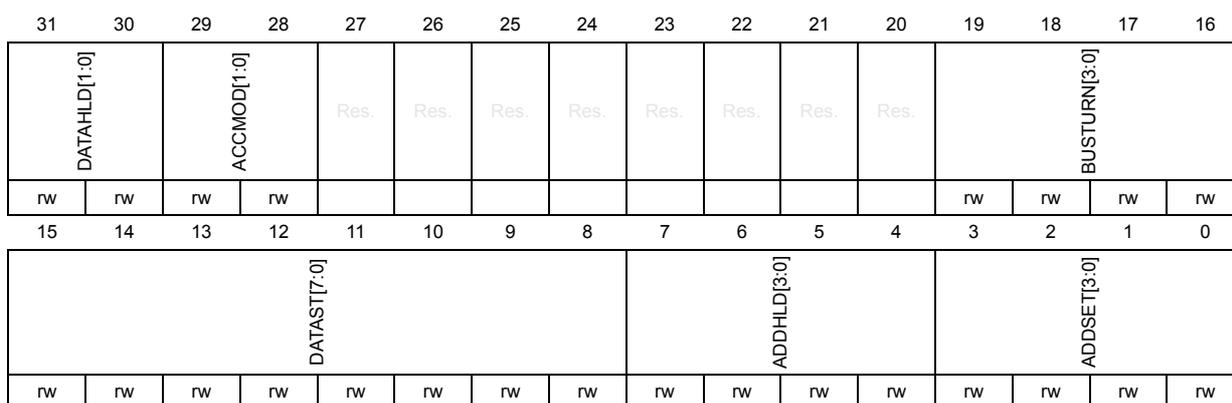

Table 165. FMC_BTRx bitfields (mode 1)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD fmc_ker_ck cycles) for read accesses. |

| 29-28 | ACCMOD | Don't care |

| 27-24 | DATLAT | Don't care |

| 23-20 | CLKDIV | Don't care |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles). |

Table 165. FMC_BTRx bitfields (mode 1) (continued)

| Bit number | Bit name | Value to set |

|---|---|---|

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles). Minimum value for ADDSET is 0. |

Mode A - SRAM/FRAM/PSRAM (CRAM) OE toggling

Figure 163. Mode A read access waveforms

![Timing diagram for Mode A read access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over time. The diagram illustrates the 'Memory transaction' period and various timing parameters: NBLSET, ADDSET, DATAST, and DATAHLD in fmc_ker_ck cycles. The Data bus is shown as 'Data driven by memory' during the transaction.](/RM0486-STM32N6x5-x7/5a3424c76b3674cce0dc31919ba42821_img.jpg)

The timing diagram shows the following signals and timing parameters:

- A[25:0]: Address lines, stable during the memory transaction.

- NBL[x:0]: Byte Lane signals, active low, toggling at the start and end of the transaction.

- NEx: Address Enable, active low, goes low at the start and high at the end of the transaction.

- NOE: Output Enable, active low, goes low to enable data output and high to disable it.

- NWE: Write Enable, active low, held high during this read transaction.

- Data bus: Bidirectional data bus, driven by memory when NOE is low.

- Timing parameters (in fmc_ker_ck cycles):

- NBLSET: Setup time for byte lane signals before the start of the transaction.

- ADDSET: Setup time for address and NEx signals before the start of the transaction.

- DATAST: Setup time for data signals before the end of the transaction.

- DATAHLD: Hold time for data signals after the end of the transaction.

Reference: MSV45373V1

Figure 164. Mode A write access waveforms

![Timing diagram for Mode A write access waveforms. The diagram shows the relationship between address (A[25:0]), non-byte-lane (NBL[x:0]), next (NEx), output enable (NOE), write enable (NWE), and data bus signals over time. The 'Memory transaction' period is marked. Timing parameters are defined: NBLSET (fmc_ker_ck cycles), ADDSET (fmc_ker_ck cycles), DATAST (fmc_ker_ck cycles), and DATAHLD + 1 (fmc_ker_ck cycles). The data bus is driven by the controller during the transaction. Reference MSV45372V1 is noted.](/RM0486-STM32N6x5-x7/ab3d9e0b5e0ab802e76381ca6f67ad3d_img.jpg)

The differences compared with mode 1 are the toggling of NOE and the independent read and write timings.

Table 166. FMC_BCRx bitfields (mode A)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | 0x0 (no effect in asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in asynchronous mode) |

| 15 | ASYNCWAIT | Set if the memory supports this feature. Otherwise keep cleared. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP | As needed, exclude 0x2 (NOR flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD fmc_ker_ck cycles for read accesses). |

| 29-28 | ACCMOD | 0x0 |

| 27-24 | DATLAT | Don't care |

| 23-20 | CLKDIV | Don't care |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 0. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD+1 fmc_ker_ck cycles for write accesses). |

| 29-28 | ACCMOD | 0x0 |

| 27-20 | Reserved | 0x0 |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for write accesses. |

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 0. |

Mode 2/B - NOR flash

Figure 165. Mode 2 and mode B read access waveforms

![Timing diagram for Mode 2 and mode B read access waveforms. It shows signals A[25:0], NADV, NEx, NOE, NWE (High), and Data bus over time. The Data bus is driven by memory. Timing parameters include ADDSET, DATAST, and DATAHLD in fmc_ker_ck cycles. Reference MSv45374V1.](/RM0486-STM32N6x5-x7/57db40980dc77b81e222c422e60d3364_img.jpg)

This timing diagram illustrates the read access for Mode 2 and Mode B. The signals shown are address A[25:0], NADV (address valid), NEx (external memory enable), NOE (output enable), NWE (write enable, held high), and the Data bus. The Data bus is driven by the memory. The timing is defined by three parameters: ADDSET (address setup time), DATAST (data start time), and DATAHLD (data hold time), all measured in fmc_ker_ck cycles. The diagram is labeled MSv45374V1.

Figure 166. Mode 2 write access waveforms

![Timing diagram for Mode 2 write access waveforms. It shows signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. The Data bus is driven by controller. Timing parameters include ADDSET, DATAST, and DATAHLD + 1 in fmc_ker_ck cycles. Reference MSv45375V1.](/RM0486-STM32N6x5-x7/b5f75de5c835ebd2fe5ffd4e32a17230_img.jpg)

This timing diagram illustrates the write access for Mode 2. The signals shown are address A[25:0], NADV (address valid), NEx (external memory enable), NOE (output enable), NWE (write enable), and the Data bus. The Data bus is driven by the controller. The timing is defined by three parameters: ADDSET (address setup time), DATAST (data start time), and DATAHLD + 1 (data hold time plus one cycle), all measured in fmc_ker_ck cycles. The diagram is labeled MSv45375V1.

Figure 167. Mode B write access waveforms

![Timing diagram for Mode B write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. The diagram shows the relationship between address, control signals, and data bus during a memory transaction. Key timing parameters like ADDSET, DATAST, and DATAHLD are indicated in fmc_ker_ck HCLK cycles.](/RM0486-STM32N6x5-x7/342a85461c77f8ce6129d9961b6e03a7_img.jpg)

The diagram illustrates the timing for a Mode B write access. The signals shown are:

- A[25:0] : Address bus, stable during the memory transaction.

- NADV : Address Valid signal, goes low to indicate valid address.

- NEx : External memory signal, goes low to enable the memory.

- NOE : Output Enable signal, goes low to enable data output from memory.

- NWE : Write Enable signal, goes low to initiate a write.

- Data bus : Bidirectional data bus, driven by the controller during the write phase.

Timing parameters are defined relative to the fmc_ker_ck clock:

- ADDSET : Time from NADV falling edge to data bus driving start (in fmc_ker_ck HCLK cycles).

- DATAST : Time from data bus driving start to NWE falling edge (in fmc_ker_ck cycles).

- DATAHLD + 1 : Time from NWE falling edge to data bus tri-state (in fmc_ker_ck cycles).

Reference: MSV45376V1

The differences with mode 1 are the toggling of NWE and the independent read and write timings when extended mode is set (mode B).

Table 169. FMC_BCRx bitfields (mode 2/B)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | 0x0 (no effect in asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in asynchronous mode) |

| 15 | ASYNCWAIT | Set if the memory supports this feature. Otherwise keep cleared. |

| 14 | EXTMOD | 0x1 for mode B, 0x0 for mode 2 |

| 13 | WAITEN | 0x0 (no effect in asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP | 0x2 (NOR flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD fmc_ker_ck cycles for read accesses). |

| 29:28 | ACCMOD | 0x1 if extended mode is set |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the access second phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the access first phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 0. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD+1 fmc_ker_ck cycles for write accesses). |

| 29:28 | ACCMOD | 0x1 if extended mode is set |

| 27:20 | Reserved | 0x0 |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the access second phase (DATAST fmc_ker_ck cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the access first phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 0. |

Note: The FMC_BWTRx register is valid only if the extended mode is set (mode B), otherwise its content is don't care.

Mode C - NOR flash - OE toggling

Figure 168. Mode C read access waveforms

![Timing diagram for Mode C read access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. The diagram shows a memory transaction with timing parameters ADDSET, DATAST, and DATAHLD in fmc_ker_ck cycles. The data bus is driven by memory during the DATAST and DATAHLD phases.](/RM0486-STM32N6x5-x7/fd4b3638d88ebdc44ee9393123f62ab8_img.jpg)

The diagram illustrates the timing for a read access in Mode C. The signals shown are A[25:0] (address), NADV (address valid), NEx (external memory), NOE (output enable), NWE (write enable), and the Data bus. The timing is measured in fmc_ker_ck cycles. The memory transaction starts with the address and NADV signal. NEx is active low. NOE is toggled to enable data output from the memory. NWE is high during read operations. The data bus is driven by the memory during the DATAST and DATAHLD phases. The timing parameters are: ADDSET (address setup time), DATAST (data setup time), and DATAHLD (data hold time).

Figure 169. Mode C write access waveforms

![Timing diagram for Mode C write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. The diagram shows a memory transaction with timing parameters ADDSET, DATAST, and DATAHLD + 1 in fmc_ker_ck cycles. The data bus is driven by the controller during the DATAST and DATAHLD + 1 phases.](/RM0486-STM32N6x5-x7/983f4833a1a6259ed7f6300f3855a7b9_img.jpg)

The diagram illustrates the timing for a write access in Mode C. The signals shown are A[25:0] (address), NADV (address valid), NEx (external memory), NOE (output enable), NWE (write enable), and the Data bus. The timing is measured in fmc_ker_ck cycles. The memory transaction starts with the address and NADV signal. NEx is active low. NOE is toggled to enable data output from the memory. NWE is active low during write operations. The data bus is driven by the controller during the DATAST and DATAHLD + 1 phases. The timing parameters are: ADDSET (address setup time), DATAST (data setup time), and DATAHLD + 1 (data hold time + 1 cycle).

The differences compared with mode 1 are the toggling of NOE and the independent read and write timings.

Table 172. FMC_BCRx bitfields (mode C)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | 0x0 (no effect in asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in asynchronous mode) |

| 15 | ASYNCWAIT | Set if the memory supports this feature. Otherwise keep cleared. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP[1:0] | 0x02 (NOR flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

Table 173. FMC_BTRx bitfields (mode C)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD fmc_ker_ck cycles for read accesses). |

| 29-28 | ACCMOD | 0x2 |

| 27-24 | DATLAT | 0x0 |

| 23-20 | CLKDIV | 0x0 |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 0. |

Table 174. FMC_BWTRx bitfields (mode C)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD+1 fmc_ker_ck cycles for write accesses). |

| 29:28 | ACCMOD | 0x2 |

| 27:20 | Reserved | 0x0 |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 0. |

Mode D - asynchronous access with extended address

Figure 170. Mode D read access waveforms

![Timing diagram for Mode D read access waveforms showing signals A[25:0], NADV, NBL[x:0], NEx, NOE, NWE, and Data bus over time. The diagram illustrates the sequence of a memory transaction with various setup and hold times defined in fmc_ker_ck cycles.](/RM0486-STM32N6x5-x7/b7ec06fff3a9266026541639b62c79f3_img.jpg)

The diagram shows the timing for a Mode D read access. The signals shown are:

- A[25:0] : Address lines, valid during the memory transaction.

- NADV : Address Valid signal, goes low to indicate valid address.

- NBL[x:0] : Byte Lane signals, go low to indicate active byte lanes.

- NEx : Next signal, goes high when the next transaction starts.

- NOE : Output Enable, goes low to enable data output from memory.

- NWE : Write Enable, stays high during read access.

- Data bus : Data lines, driven by memory when NOE is low.

Timing parameters defined in the diagram:

- NBLSET : fmc_ker_ck cycles (time from NADV falling edge to NBL[x:0] falling edge)

- ADDSET : fmc_ker_ck cycles (time from NADV falling edge to A[25:0] valid)

- ADDHLD : fmc_ker_ck cycles (time from A[25:0] valid to NEx rising edge)

- DATAST : fmc_ker_ck cycles (time from NOE falling edge to Data bus driven)

- DATAHLD : fmc_ker_ck cycles (time from Data bus driven to NOE rising edge)

MSV45378V1

Figure 171. Mode D write access waveforms

![Timing diagram for Mode D write access waveforms. The diagram shows the relationship between address (A[25:0]), NADV, NBL[x:0], NEx, NOE, NWE, and the Data bus over time. The 'Memory transaction' starts when A[25:0] is stable and NADV goes low. The Data bus is driven by the controller during the transaction. Timing parameters are defined in fmc_ker_ck cycles: NBLSET, ADDSET, ADDHLD, DATAST, and DATAHLD + 1.](/RM0486-STM32N6x5-x7/ffe54ceb5b4269688f30aed2cd48a84a_img.jpg)

The diagram illustrates the timing for a Mode D write access. The signals shown are A[25:0], NADV, NBL[x:0], NEx, NOE, NWE, and the Data bus. The 'Memory transaction' is indicated by a double-headed arrow spanning from the start of the address and NADV signal changes to the end of the data burst. The Data bus is labeled 'Data driven by controller' during the transaction. Timing parameters are defined in fmc_ker_ck cycles: NBLSET, ADDSET, ADDHLD, DATAST, and DATAHLD + 1. The reference MSv45379V1 is noted in the bottom right corner.

The differences with mode 1 are the toggling of NOE that goes on toggling after NADV changes and the independent read and write timings.

Table 175. FMC_BCRx bitfields (mode D)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | 0x0 (no effect in asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in asynchronous mode) |

| 15 | ASYNCWAIT | Set if the memory supports this feature. Otherwise keep cleared. The ASYNCWAIT feature is not supported in mode D mode. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP[1:0] | As needed |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD fmc_ker_ck cycles for read accesses). |

| 29-28 | ACCMOD | 0x3 |

| 27-24 | DATLAT | Don't care |

| 23-20 | CLKDIV | Don't care |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7-4 | ADDHLD | Duration of the middle phase of the read access (ADDHLD fmc_ker_ck cycles) |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 1. |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD+1 fmc_ker_ck cycles for write accesses). |

| 29-28 | ACCMOD | 0x3 |

| 27:20 | Reserved | 0x0 |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST + 1 fmc_ker_ck cycles) for write accesses. |

| 7-4 | ADDHLD | Duration of the middle phase of the write access (ADDHLD fmc_ker_ck cycles) |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 1. |

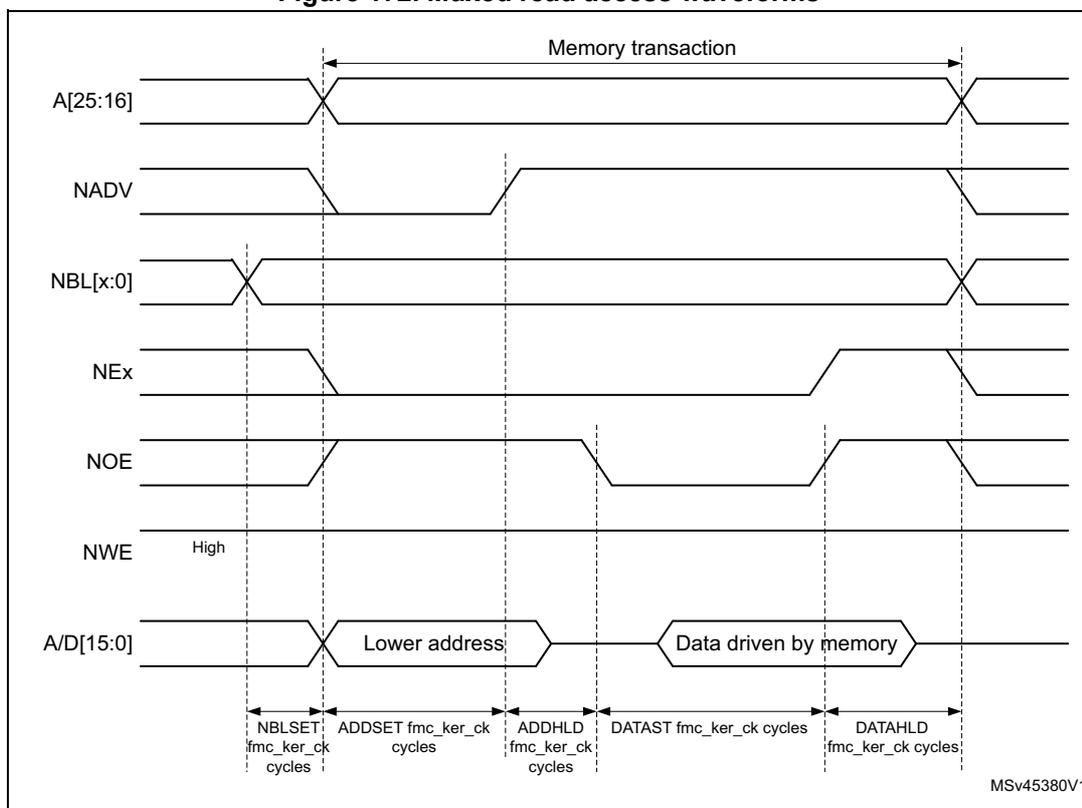

Muxed mode - multiplexed asynchronous access to NOR flash memory

Figure 172. Muxed read access waveforms

The diagram illustrates the timing for a muxed read access to NOR flash memory. It shows the relationship between address, data, and control signals over time, measured in fmc_ker_ck cycles.

Signals:

- A[25:16]: Address lines, stable during the memory transaction.

- NADV: Address Valid signal, goes low to indicate valid address and data.

- NBL[x:0]: Byte Lane signals, active-low.

- NEx: External memory signal, goes low to enable the memory.

- NOE: Output Enable signal, goes low to enable data output from the memory.

- NWE: Write Enable signal, held high during read access.

- A/D[15:0]: Multiplexed address/data lines. They carry the "Lower address" initially and then become "Data driven by memory".

Timing Parameters:

- NBLSET: Time from NBL[x:0] falling edge to the start of the address/data phase, in fmc_ker_ck cycles.

- ADDSET: Time from the start of the address/data phase to the start of the data phase, in fmc_ker_ck cycles.

- ADDHLD: Time from the start of the data phase to the end of the address/data phase, in fmc_ker_ck cycles.

- DATAST: Time from the start of the data phase to the end of the data phase, in fmc_ker_ck cycles.

- DATAHLD: Time from the end of the data phase to the end of the memory transaction, in fmc_ker_ck cycles.

The diagram also indicates the "Memory transaction" duration and the state of the A/D[15:0] lines as "Lower address" and "Data driven by memory". The identifier MSv45380V1 is shown in the bottom right corner.

Figure 173. Muxed write access waveforms

![Timing diagram for muxed write access waveforms showing signals A[25:16], NADV, NBL[x:0], NEx, NOE, NWE, and A/D[15:0] over time. The diagram illustrates the 'Memory transaction' period and the drive of 'Lower address' and 'Data driven by controller' on the A/D[15:0] bus. Timing parameters like NBLSET, ADDSET, ADDHLD, DATAST, and DATAHLD are indicated in fmc_ker_ck cycles.](/RM0486-STM32N6x5-x7/766e21426d9222eaddeb218061fad21d_img.jpg)

The figure shows the timing for a muxed write access. The signals shown are A[25:16], NADV, NBL[x:0], NEx, NOE, NWE, and A/D[15:0]. The A/D[15:0] bus is used for both address and data. The timing parameters are defined as follows:

- NBLSET : fmc_ker_ck cycles

- ADDSET : fmc_ker_ck cycles

- ADDHLD : fmc_ker_ck cycles

- DATAST : fmc_ker_ck cycles

- DATAHLD + 1 : fmc_ker_ck cycles

MSV45381V1

The difference with mode D is the drive of the lower address byte(s) on the data bus.

Table 178. FMC_BCRx bitfields (muxed mode)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | 0x0 (no effect in asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in asynchronous mode) |

| 15 | ASYNCWAIT | Set if the memory supports this feature. Otherwise keep cleared. The ASYNCWAIT feature is not supported in muxed mode. |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | 0x0 (no effect in asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP[1:0] | 0x2 (NOR flash memory) |

| 1 | MUXEN | 0x1 |

| 0 | MBKEN | 0x1 |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the Data hold phase (DATAHLD fmc_ker_ck cycles for read accesses, DATAHLD+1 fmc_ker_ck cycles for write accesses). |

| 29-28 | ACCMOD | 0x0 |

| 27-24 | DATLAT | Don't care |

| 23-20 | CLKDIV | Don't care |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles for read accesses and DATAST+1 fmc_ker_ck cycles for write accesses). |

| 7-4 | ADDHLD | Duration of the middle phase of the access (ADDHLD fmc_ker_ck cycles). |

| 3-0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles). Minimum value for ADDSET is 1. |

WAIT management for asynchronous accesses

If the asynchronous memory asserts the WAIT signal to indicate that it is not yet ready to accept or to provide data, the ASYNCWAIT bit has to be set in FMC_BCRx register.

If the WAIT signal is active (high or low depending on the WAITPOL bit), the second access phase (Data setup phase), programmed by the DATAST bits, is extended until WAIT becomes inactive. Unlike the data setup phase, the first access phases (Address setup and Address hold phases), programmed by the ADDSET and ADDHLD bits, are not WAIT sensitive and so they are not prolonged.

The data setup phase must be programmed so that WAIT can be detected 4 fmc_ker_ck cycles before the end of the memory transaction. The following cases must be considered:

- 1. The memory asserts the WAIT signal aligned to NOE/NWE which toggles:

- 2. The memory asserts the WAIT signal aligned to NEx (or NOE/NWE not toggling):

if

then:

otherwise

where max_wait_assertion_time is the maximum time taken by the memory to assert the WAIT signal once NEx/NOE/NWE is low.

Figure 174 and Figure 175 show the number of fmc_ker_ck clock cycles that are added to the memory access phase after WAIT is released by the asynchronous memory (independently of the above cases).

Figure 174. Asynchronous wait during a read access waveforms

![Timing diagram for asynchronous wait during a read access. It shows signals A[25:0], NEx, NWAIT, NOE, and Data bus over time. The memory transaction is divided into an address phase and a data setup phase. NWAIT is shown as 'don't care' in both phases. Data is driven by memory during the data setup phase, with a setup time of 4 fmc_ker_ck.](/RM0486-STM32N6x5-x7/10ec4ad502af0e61defa0fcad0f3ed49_img.jpg)

The diagram illustrates the timing for an asynchronous wait during a read access. The signals shown are:

- A[25:0] : Address bus, stable during the address phase and data setup phase.

- NEx : Address Status signal, active low, goes low at the start of the address phase and high at the start of the data setup phase.

- NWAIT : Asynchronous wait signal, labeled as 'don't care' in both the address and data setup phases.

- NOE : Output Enable signal, active low, goes low at the start of the data setup phase and high at the end of the memory transaction.

- Data bus : Data is driven by memory during the data setup phase. The setup time is indicated as 4 fmc_ker_ck.

The memory transaction is divided into two phases: address phase and data setup phase . The address phase starts when NEx goes low and ends when NEx goes high. The data setup phase starts when NEx goes high and ends when NOE goes high. The data bus is driven by memory during the data setup phase, and the setup time is 4 fmc_ker_ck.

MSv40382V2

- 1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

Figure 175. Asynchronous wait during a write access waveforms

![Timing diagram for asynchronous wait during a write access. It shows signals A[25:0], NEx, NWAIT, NWE, and Data bus over time. The memory transaction is divided into an address phase and a data setup phase. NWAIT is shown as 'don't care' in both phases. Data is driven by FMC during the data setup phase, with a setup time of 3 fmc_ker_ck. NWE is shown going high 1 fmc_ker_ck after the data setup phase begins.](/RM0486-STM32N6x5-x7/52179e91740c104154f22856f25e588b_img.jpg)

The diagram illustrates the timing for an asynchronous wait during a write access. The signals shown are:

- A[25:0] : Address bus, stable during the address phase and data setup phase.

- NEx : Address Status signal, active low, goes low at the start of the address phase and high at the start of the data setup phase.

- NWAIT : Asynchronous wait signal, labeled as 'don't care' in both the address and data setup phases.

- NWE : Write Enable signal, active low, goes low at the start of the address phase and high at the start of the data setup phase. The setup time for NWE is 1 fmc_ker_ck.

- Data bus : Data is driven by FMC during the data setup phase. The setup time is indicated as 3 fmc_ker_ck.

The memory transaction is divided into two phases: address phase and data setup phase . The address phase starts when NEx goes low and ends when NEx goes high. The data setup phase starts when NEx goes high and ends when NWE goes high. The data bus is driven by FMC during the data setup phase, and the setup time is 3 fmc_ker_ck.

MSv40383V3

- 1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

CellularRAM™ (PSRAM) refresh management

The CellularRAM™ does not allow maintaining the chip select signal (NE) low for longer than the \( t_{CEM} \) timing specified in memory device. This timing can be programmed in the FMC_CFGR register. It defines the maximum duration of the NE low pulse (expressed in fmc_ker_ck cycles) in synchronous mode for PSRAM read or write accesses.

27.8.5 Synchronous transactions

The memory clock, FMC_CLK, is a submultiple of fmc_ker_ck. It depends on the value of CLKDIV.

NOR flash memories specify a minimum time from NADV assertion to FMC_CLK high. To meet this constraint, the FMC does not issue the clock to the memory during the first internal clock cycle of the synchronous access (before NADV assertion). This guarantees that the rising edge of the memory clock occurs in the middle of the NADV low pulse.

Data latency versus NOR memory latency

The data latency is the number of cycles to wait before sampling the data. The DATLAT value must be consistent with the latency value specified in the NOR flash configuration register. The FMC does not include the clock cycle when NADV is low in the data latency count.

Caution: Some NOR flash memories include the NADV Low cycle in the data latency count, so that the exact relation between the NOR flash latency and the FMC DATLAT parameter can be either:

- • NOR flash latency = (DATLAT + 2) CLK clock cycles

- • or NOR flash latency = (DATLAT + 3) CLK clock cycles

Some recent memories assert NWAIT during the latency phase. In such cases DATLAT can be set to its minimum value. As a result, the FMC samples the data and waits long enough to evaluate if the data are valid. Thus the FMC detects when the memory exits latency and real data are processed.

Other memories do not assert NWAIT during latency. In this case the latency must be set correctly for both the FMC and the memory, otherwise invalid data are mistaken for good data, or valid data are lost in the initial phase of the memory access.

Single-burst transfer

When the selected memory region is configured in burst mode for synchronous accesses, if for example a single-burst transaction is requested on 16-bit memories, the FMC performs a burst transaction of length 1 (if the AXI transfer is 16 bits), or length 2 (if the AXI transfer is 32 bits) and deassert the Chip Select signal when the last data is strobed.

Such transfers are not the most efficient in terms of cycles compared to asynchronous read operations. Nevertheless, a random asynchronous access first requires to re-program the memory access mode, which altogether lasts longer.

Cross boundary page for CellularRAM™ 1.5

CellularRAM™ 1.5 does not allow burst access to cross the page boundary. The FMC allows to split automatically the burst access when the memory page size is reached by configuring the CPSIZE bits in the FMC_BCR1 register following the memory page size.

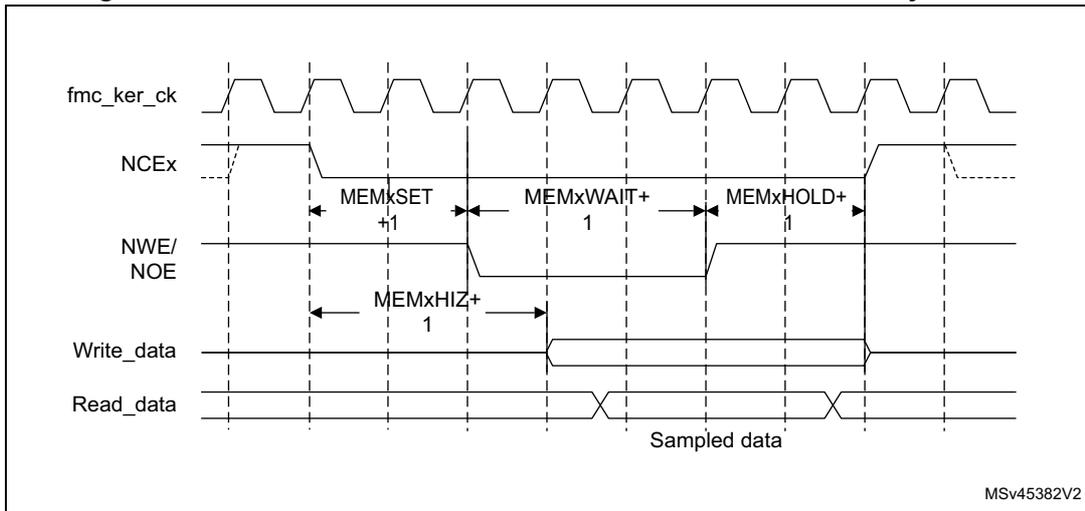

Wait management

For synchronous NOR flash memories, NWAIT is evaluated after the programmed latency period, which corresponds to (DATLAT+2) FMC_CLK clock cycles.

If NWAIT is active (low level when WAITPOL = 0, high level when WAITPOL = 1), wait-states are inserted until NWAIT is inactive (high level when WAITPOL = 0, low level when WAITPOL = 1).

When NWAIT is inactive, the data is considered valid either immediately (bit WAITCFG = 1) or on the next clock edge (bit WAITCFG = 0).

During wait-state insertion via the NWAIT signal, the controller continues to send clock pulses to the memory, keeping the Chip Select and output enable signals valid. It does not consider the data as valid.

In burst mode, there are two timing configurations for the NOR flash NWAIT signal:

- • The flash memory asserts the NWAIT signal one data cycle before the wait-state (default after reset).

- • The flash memory asserts the NWAIT signal during the wait-state

The FMC supports both NOR flash wait-state configurations, for each Chip Select, thanks to the WAITCFG bit in the FMC_BCRx registers (x = 0 to 3).

Figure 176. Wait configuration waveforms

![Timing diagram showing FMC_CLK, A[25:16], NADV, NWAIT (WAITCFG = 0), NWAIT (WAITCFG = 1), and A/D[15:0] signals. The diagram illustrates the insertion of a wait state when NWAIT is active. The address is sent on A[25:16] and A/D[15:0]. Data is sent on A/D[15:0]. The NWAIT signal is active (low) during the wait state. The FMC_CLK signal is a periodic clock. The NADV signal is active (low) during the address phase. The A[25:16] signal is high-impedance (X) during the data phase. The A/D[15:0] signal is high-impedance (X) during the address phase. The NWAIT (WAITCFG = 0) signal is active (low) during the wait state. The NWAIT (WAITCFG = 1) signal is active (high) during the wait state. The inserted wait state is indicated by a double-headed arrow between the first and second data cycles. Data strobes are indicated by vertical arrows pointing to the data cycles.](/RM0486-STM32N6x5-x7/75a9d26a084d8a8f5695d96920844157_img.jpg)

The diagram shows the following signals and timing:

- FMC_CLK: A periodic clock signal.

- A[25:16]:

Address lines. It shows an address

addr[25:16]being sent, followed by high-impedance (X) states. - NADV: Address Valid signal, active low. It goes low during the address phase and returns high before the data phase.

- NWAIT (WAITCFG = 0): Wait signal, active low. It goes low before the second data cycle and returns high after the third data cycle.

- NWAIT (WAITCFG = 1): Wait signal, active high. It goes high during the second data cycle (the wait state) and returns low before the third data cycle.

- A/D[15:0]:

Address/Data lines. It shows an address

addr[15:0]being sent, followed by data cycles labeleddata. The first data cycle occurs while NWAIT (WAITCFG = 0) is low. The second data cycle is skipped because NWAIT (WAITCFG = 1) is high. The third data cycle occurs after NWAIT (WAITCFG = 1) goes low. - Data strobes: Vertical arrows pointing to the start of each valid data cycle.

- inserted wait state: A double-headed arrow between the first and third data cycles, indicating the skipped second cycle.

MSV40384V4

Figure 177. Synchronous multiplexed read mode waveforms - NOR, PSRAM (CRAM)

![Timing diagram showing waveforms for FMC_CLK, A[25:16], NEx, NOE, NWE, NADV, NWAIT, and A/D[15:0] signals during a synchronous multiplexed read operation. The diagram shows address phases, data phases with strobes, and an inserted wait state.](/RM0486-STM32N6x5-x7/a458ee0e471e1f3659df99e86b8daaea_img.jpg)

The timing diagram illustrates the signal transitions for a synchronous multiplexed read operation.

•

FMC_CLK

: A periodic clock signal.

•

A[25:16]

: Address lines, showing 'addr[25:16]' during the initial address phase.

•

NEx

: Address Status signal, active-low, goes low during the address phase and returns high at the start of the data phase.

•

NOE

: Output Enable signal, active-low, goes low to enable data output on the A/D[15:0] bus.

•

NWE

: Write Enable signal, active-low, held high throughout this read operation.

•

NADV

: Address Valid signal, active-low, goes low to indicate valid address and returns high when address is no longer valid.

•

NWAIT (WAITCFG=0)

: Wait signal, active-low, goes low to insert a wait state between data phases.

•

A/D[15:0]

: Multiplexed address/data bus. It starts with 'Addr[15:0]', followed by 'data' phases.

•

Data Strobes

: Pulses that indicate valid data on the bus during each 'data' phase.

•

Timing

: The interval between the start of the first data phase and the second is labeled '(DATLAT + 2) FMC_CLK'. The duration of the inserted wait state is also indicated. The initial address phase duration is marked as 'clock cycle'.

Table 180. FMC_BCRx bitfields (Synchronous multiplexed read mode)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | As needed |

| 18:16 | CPSIZE | As needed. (0x1 when using CRAM 1.5) |

| 15 | ASYNCWAIT | 0x0 |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | to be set if the memory supports this feature, to be kept cleared otherwise |

| 12 | WREN | no effect on synchronous read |

| 11 | WAITCFG | to be set according to memory |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | to be set according to memory |

| 8 | BURSTEN | 0x1 |

| 7 | Reserved | 0x1 |

| 6 | Reserved | 0x0 |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 5-4 | MWID[1:0] | As needed |

| 3-2 | MTYP[1:0] | 0x1 or 0x2 |

| 1 | MUXEN | As needed |

| 0 | MBKEN | 0x1 |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Don't care |

| 29:28 | ACCMOD | 0x0 |

| 27-24 | DATLAT | Data latency |

| 27-24 | DATLAT | Data latency |

| 23-20 | CLKDIV | FMC_CLK divider ratio |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15-8 | DATAST | Don't care |

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Don't care |

Figure 178. Synchronous multiplexed write mode waveforms - PSRAM (CRAM)

![Timing diagram for synchronous multiplexed write mode. It shows signals FMC_CLK, A[25:16] (addr[25:16]), NEx, Hi-Z, NOE, NWE, NADV, NWAIT (WAITCFG = 0), and A/D[15:0] (addr[15:0], data). The diagram illustrates the timing relationship between address, data, and control signals over several clock cycles. Key timing parameters shown include (DATLAT + 2) FMC_CLK cycles between address and data, and an 'inserted wait state' before the final data burst. Data strobes are indicated for each data burst.](/RM0486-STM32N6x5-x7/56eb872af4b63bd24305ab2599901752_img.jpg)

- 1. The memory must issue NWAIT signal one cycle in advance, accordingly WAITCFG must be programmed to 0.

Table 182. FMC_BCRx bitfields (Synchronous multiplexed write mode)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | Reserved | 0x0 |

| 30-24 | Reserved | 0x00 |

| 23:22 | NBLSET[1:0] | As needed |

| 21:20 | CSCOUNT | As needed |

| 19 | CBURSTRW | As needed |

| 18:16 | CPSIZE | As needed. (0x1 when using CRAM 1.5) |

| 15 | ASYNCWAIT | 0x0 |

| 14 | EXTMOD | 0x0 |

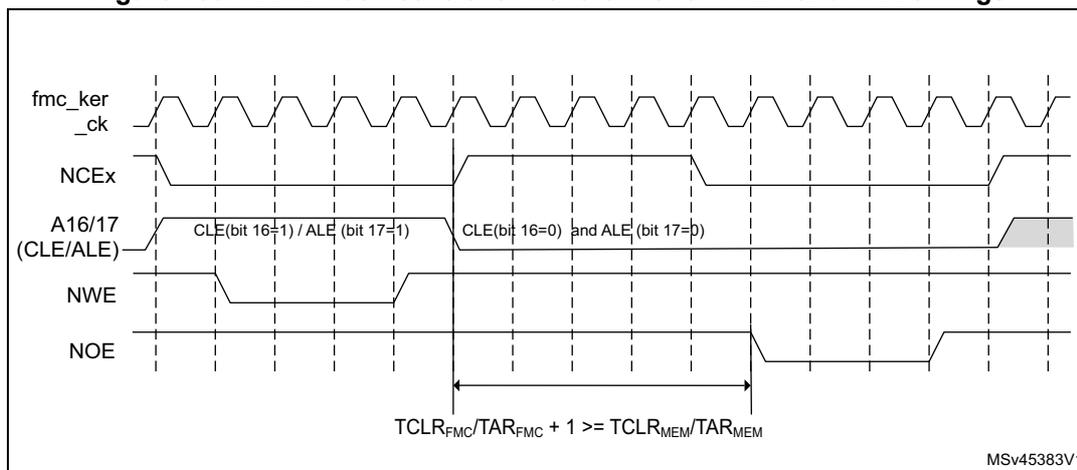

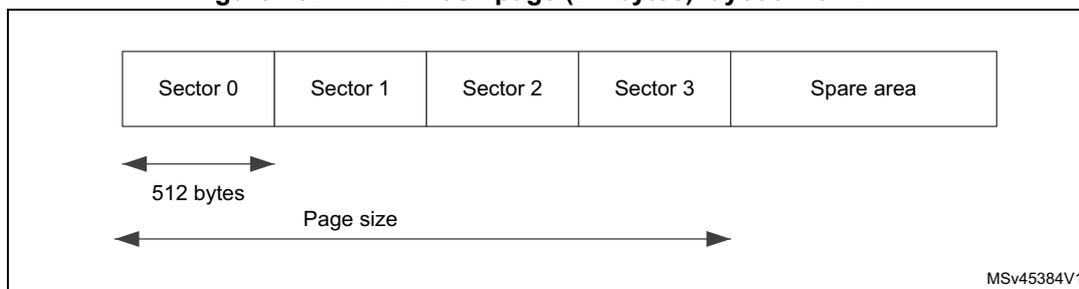

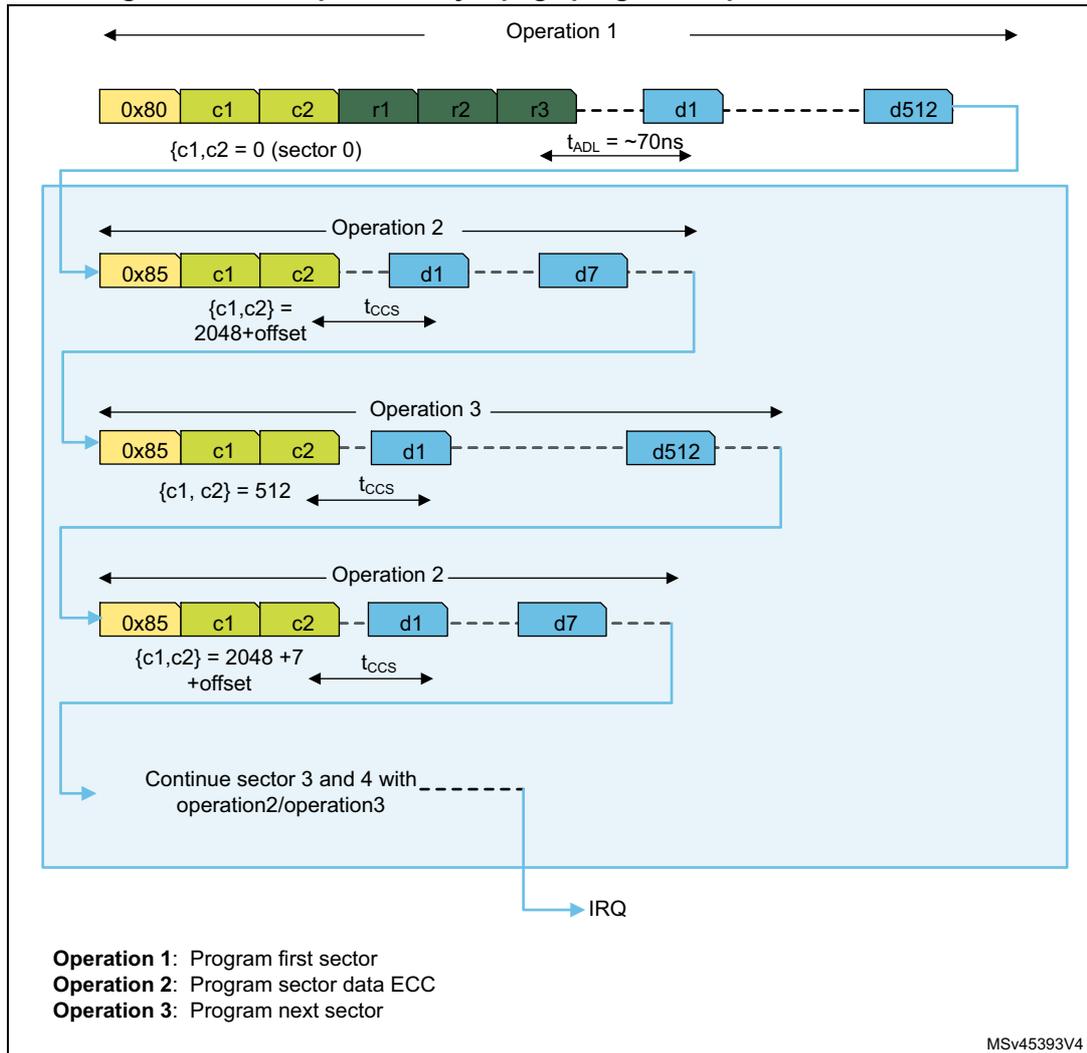

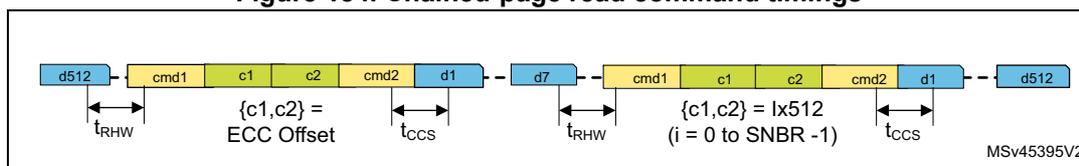

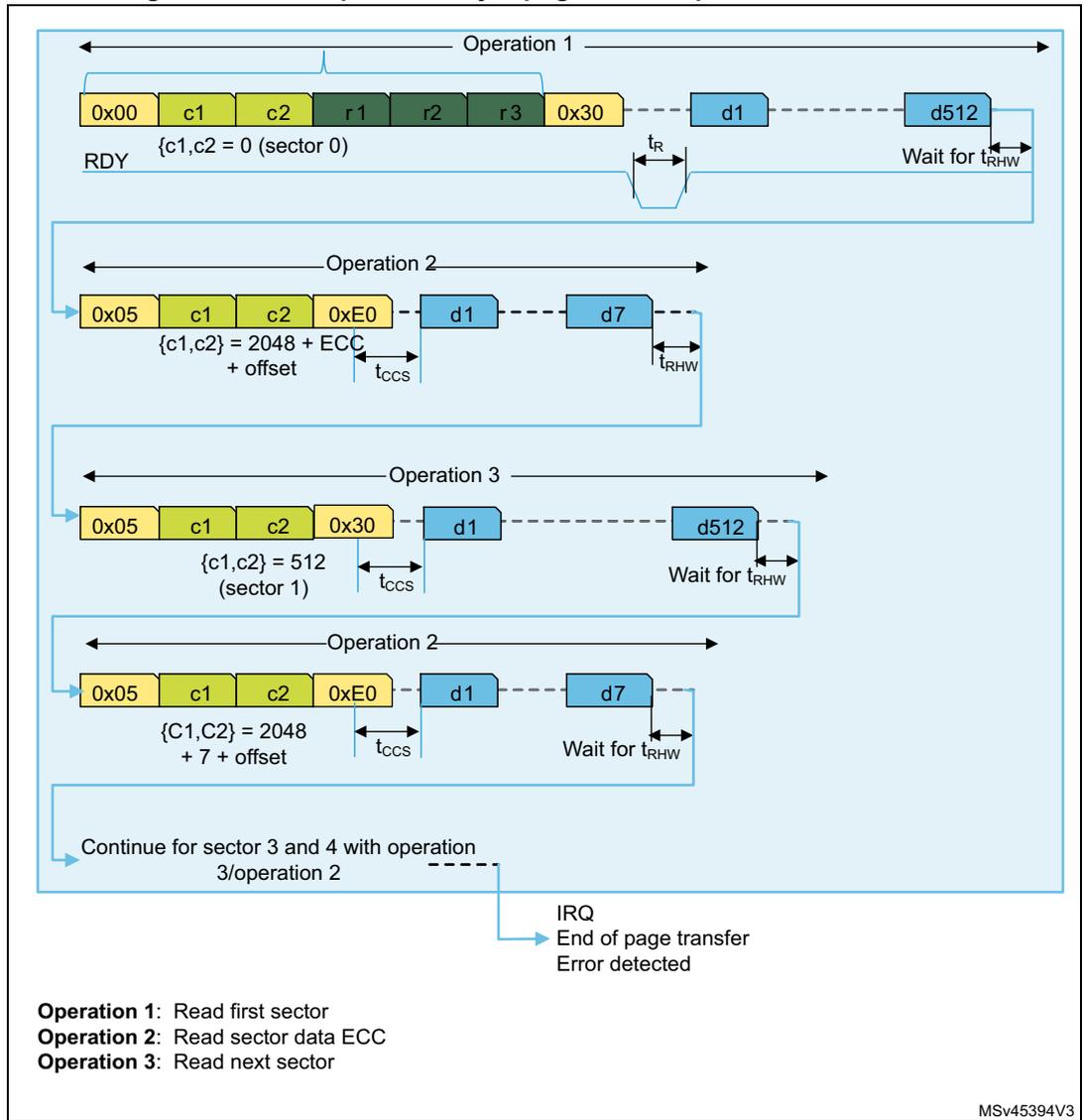

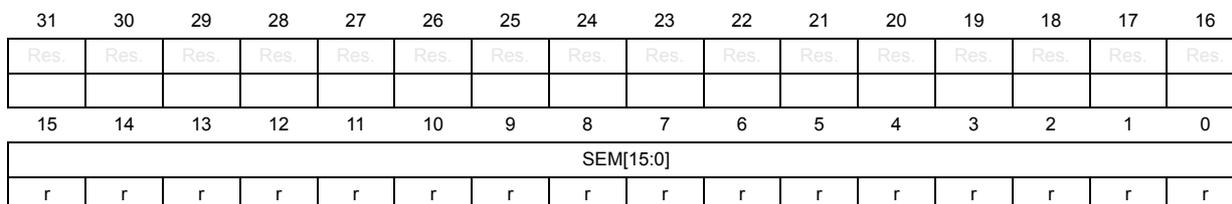

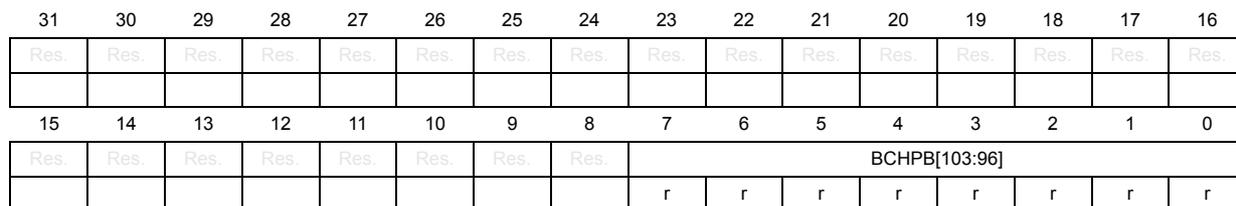

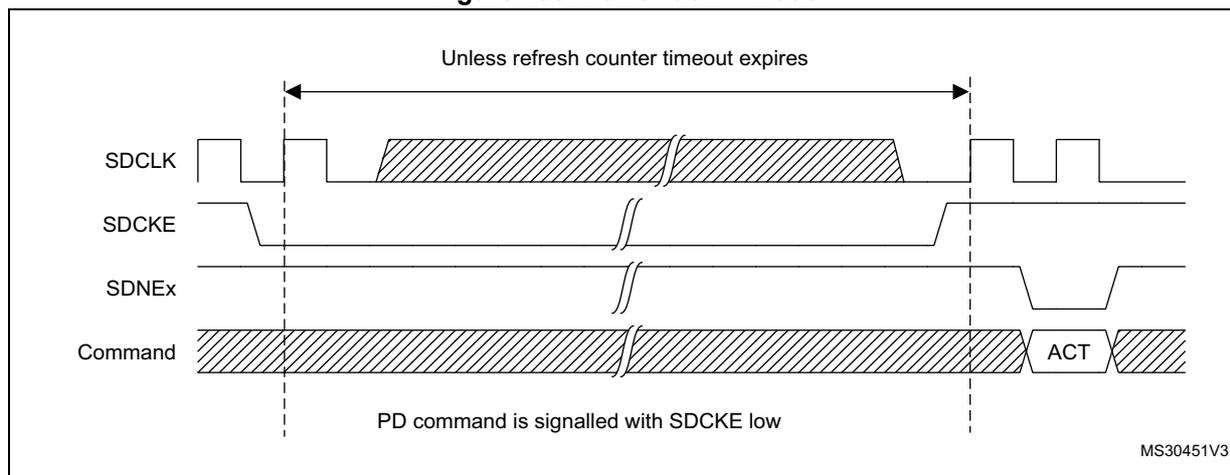

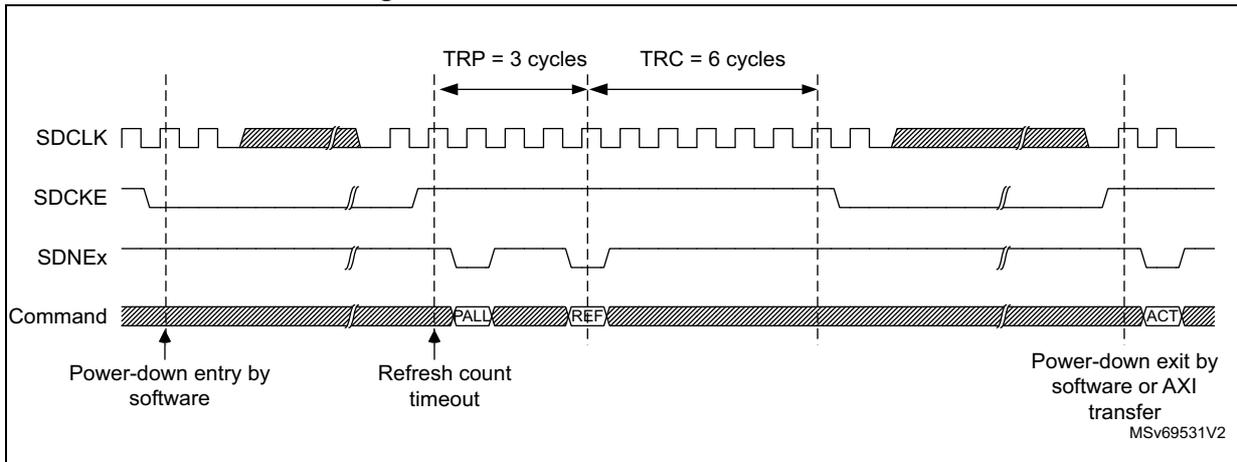

| 13 | WAITEN | to be set if the memory supports this feature, to be kept cleared otherwise. |