14. Reset and clock control (RCC)

The RCC manages the clock and reset generation for the whole microcontroller.

The operating modes to which this section refers are defined in Section 13.6.1: Operating modes of the PWR.

14.1 RCC main features

- • AHB-Lite bus interface

- • RIF (resource isolation framework) aware

- • Reset part:

- – Generation of local and system reset

- – Bidirectional pin to reset the microcontroller and/or external devices

- – WWDG and IWDG reset supported

- – Power-on (POR) and brownout (BOR) resets initiated by the PWR

- • Clock generation:

- – Generation and dispatching of clocks for the complete device

- – Four separate PLLs using integer or fractional ratios

- – Clock gating to reduce power dissipation

- – Two external oscillators:

- > High-speed external oscillator (HSE) supporting a wide range of crystals from 8 to 48 MHz (when the USBHSPHY is used, the HSE frequency must be 19.2, 20, or 24 MHz)

- > Low-speed external oscillator (LSE) for a 32.768 kHz crystal

- – Four internal oscillators:

- > High-speed internal oscillator (HSI)

- > Low-power internal oscillator (MSI)

- > Low-speed internal oscillator (LSI)

- > High-speed internal secure oscillator (HSIS)

- – Buffered clock outputs for external devices

- – Generation of two types of interrupt lines:

- > Dedicated interrupt lines for clock failure management

- > General interrupt line for other events (separated into secure and nonsecure)

- – Clock generation handling in Stop and Standby modes

14.2 RCC power domains

RCC interfaces with four power domains, namely core ( \( V_{DDCORE} \) ), retention ( \( V_{DD} \) , \( V_{RET} \) ), backup ( \( V_{SW} \) , \( V_{BKP} \) ), and analog ( \( V_{DDA18ADC} \) ).

14.3 RCC block diagram

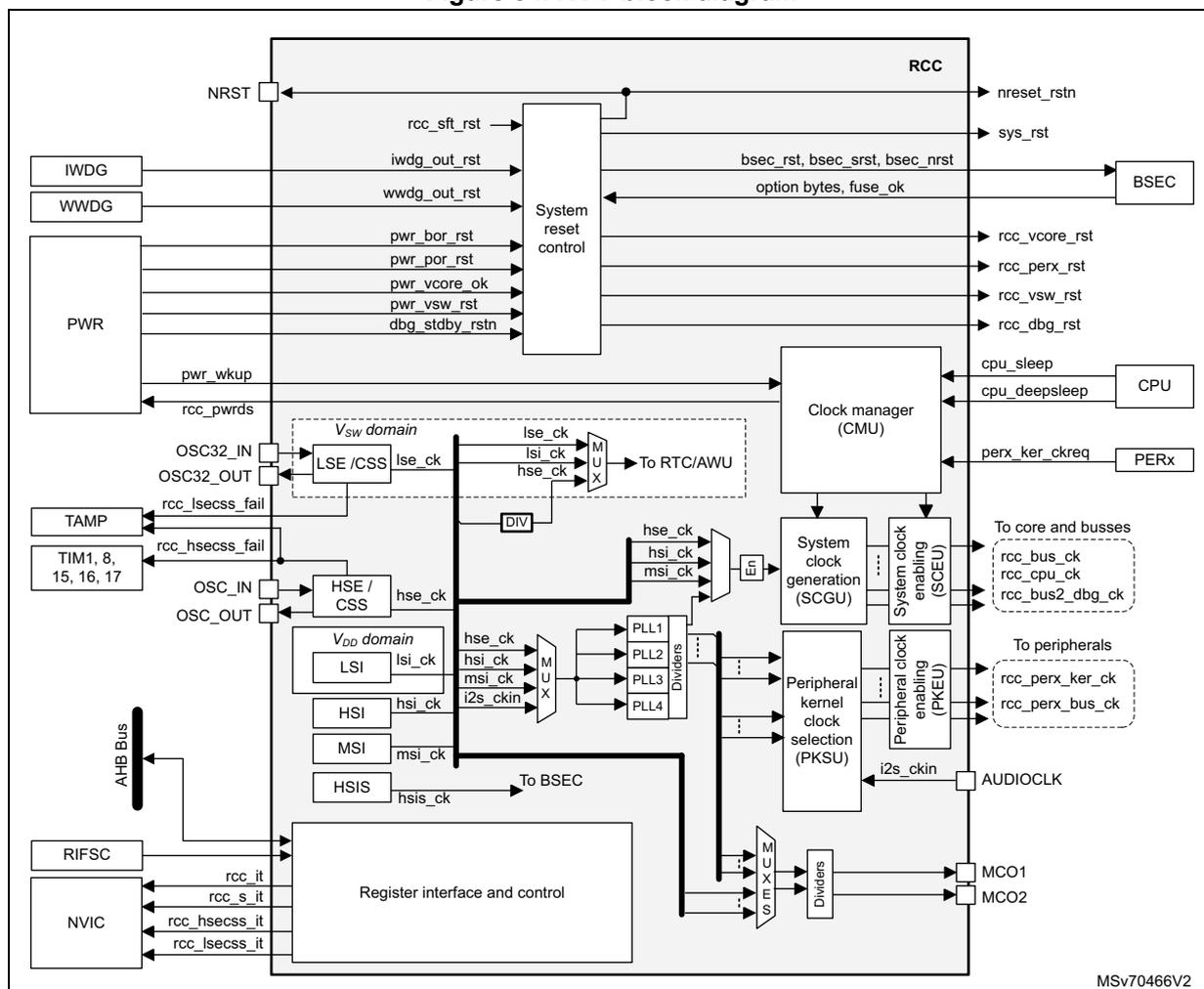

Figure 34. RCC block diagram

The diagram illustrates the internal architecture of the RCC. On the left, external components are connected to the RCC: IWDG, WWDG, PWR, TAMP, TIM1 (pins 8, 15, 16, 17), RIFSC, and NVIC. The PWR block provides signals like pwr_wkup, rcc_pwrd, pwr_bor_rst, pwr_por_rst, pwr_vcore_ok, pwr_vsw_rst, and dbg_stdby_rstn. The System reset control block receives inputs from these components and generates rcc_sft_rst, iwdg_out_rst, wwdg_out_rst, bsec_rst, bsec_srst, bsec_nrst, rcc_vcore_rst, rcc_perx_rst, rcc_vsw_rst, and rcc_dbg_rst. The Clock manager (CMU) receives inputs from the LSE/CSS (V sw domain), HSE/CSS (V DD domain), LSI, HSI, MSI, and HSIS. It also receives rcc_sft_rst, iwdg_out_rst, wwdg_out_rst, bsec_rst, bsec_srst, bsec_nrst, rcc_vcore_rst, rcc_perx_rst, rcc_vsw_rst, and rcc_dbg_rst. The CMU generates signals for the CPU (cpu_sleep, cpu_deepsleep), PERx (perx_ker_ckreq), and the System clock generation (SCGU). The SCGU generates rcc_bus_ck, rcc_cpu_ck, and rcc_bus2_dbg_ck. The Peripheral kernel clock selection (PKSU) generates rcc_perx_ker_ck and rcc_perx_bus_ck. The Register interface and control block is connected to the AHB Bus and provides control signals to the various RCC blocks. The diagram is labeled MSV70466V2.

14.4 RCC pins and internal signals

Table 64. RCC input/output signals connected to package pins or balls

| Name | Type | Description |

|---|---|---|

| NRST (1) | Reset | System reset, can be used to provide reset to external devices |

| OSC32_IN | I | 32 kHz oscillator input |

| OSC32_OUT | O | 32 kHz oscillator output |

| OSC_IN | I | System oscillator input |

| OSC_OUT | O | System oscillator output |

| MCO1 | O | Output clock 1 for external devices |

| Name | Type | Description |

|---|---|---|

| MCO2 | O | Output clock 2 for external devices |

| AUDIOCLK | I | External kernel clock input for digital audio interfaces: SPI/I2S, SAI, MDF, ADF |

1. Bidirectional reset pin with embedded weak pull-up resistor.

The RCC exchanges signals with all components of the product. Table 65 shows only the most significant internal signals.

Table 65. RCC internal input/output signals| Name | Type | Description |

|---|---|---|

| rcc_it | O | General interrupt request line (nonsecure) |

| rcc_s_it | O | General interrupt request line (secure) |

| rcc_hsecss_it | O | HSE clock security failure interrupt |

| rcc_lsecss_it | O | LSE clock security failure interrupt |

| rcc_hsecss_fail | O | Event indicating that an HSE clock security failure is detected |

| rcc_lsecss_fail | O | Event indicating that an LSE clock security failure is detected |

| nreset_rstn | I/O | Application reset |

| sys_rst | I/O | System reset |

| bsec_rstn | O | BSEC warm reset |

| bsec_srstn | O | BSEC scratch (cold) reset |

| bsec_hrstn | O | BSEC hot reset |

| fuse_ok | I | BSEC has finished loading the OTP (one-time programmable, which contains the option bytes) |

| option bytes | I | Configuration bits from BSEC, affecting RCC behavior (reset, clock, osc) |

| iwdg_out_rst | I | Reset line driven by the IWDG, indicating that a timeout occurred |

| wwdg_out_rst | I | Reset line driven by the WWDG, indicating that a timeout occurred |

| pwr_bor_rst | I | Brownout reset generated by the PWR |

| pwr_por_rst | I | Power-on reset generated by the PWR |

| pwr_vsw_rst | I | Power-on reset of the V SW domain generated by the PWR |

| dbg_stdby_rstn | I | Standby emulation mode reset generated by the PWR |

| rcc_perx_rst | O | Reset generated by the RCC for the peripherals |

| pwr_wkup | I | Wake-up request generated by the PWR, and used to restore the clocks |

| rcc_pwrd | O | Informs the PWR that the RCC has stopped all clocks (PWR can then go to Stop or Standby mode) |

| cpu_sleep | I | Signals generated by the CPU, indicating if it is in Run, Sleep, or Stop mode |

| cpu_deepsleep | I | |

| cpu_SLEEPHOLDACKn | I | When this signal is asserted, the CPU does not advance in execution, and does not perform any memory operation |

Table 65. RCC internal input/output signals (continued)

| Name | Type | Description |

|---|---|---|

| rcc_SLEEPHOLDREQn | O | Request to extend the CPU sleep state regardless of wake-up events. If the CPU acknowledges this request (SLEEPHOLDACKn asserted), the CPU remains idle even when it receives a wake-up event. |

| perx_ker_ckreq | I | Generated by some peripherals to request the activation of their kernel clock |

| rcc_perx_ker_ck | O | Kernel clock signals generated by the RCC for some peripherals |

| rcc_perx_bus_ck | O | Bus interface clock signals generated by the RCC for peripherals |

| rcc_bus_ck | O | Clocks generated by the RCC for APB, AHB, and AXI bridges |

| rcc_cpu_ck | O | Clocks generated by the RCC for the CPU |

| ck_cpu_dbg | O | |

| rcc_bus2_dbg_ck | O | Debug components clock |

| ck_cpu_tsgen | O | TSGEN clock (timestamp generator) |

| ck_cpu_tpiu | O | TPIU clock (double data rate) |

14.5 Functional description of RCC reset

The RCC handles the reset generation for the complete product, using events coming from different sources:

- assertion of the NRST pin from an external device

- a failure on the supply voltage applied to \( V_{DD} \) or \( V_{BAT} \)

- an exit from Standby mode

- a watchdog timeout

- a software command

The reset scope depends on the source that generates it.

14.5.1 Reset from the PWR

The PWR provides several reset signals to the RCC:

- power-on/off reset signal (pwr_por_rstn): asserted when the \( V_{DD} \) supply is lower than the \( V_{POR} \) threshold

- brownout reset signal (pwr_bor_rstn): asserted when the \( V_{DD} \) supply is lower than the \( V_{BOR} \) threshold

- core reset signal (pwr_okin_vcore_rstn): asserted when the \( V_{DDCORE} \) supply is not valid or available

Note: \( V_{DDCORE} \) is switched off when the product is in Standby mode. When the system exits Standby mode, pwr_okin_vcore_rstn is asserted while \( V_{DDCORE} \) from the regulator is not valid. pwr_okin_vcore_rstn is also asserted when the \( V_{DD} \) supply is not valid.

- \( V_{SW} \) domain reset signal (pwr_vsw_rstn): asserted when the \( V_{SW} \) supply is lower than the expected threshold

Refer to Table 66 for more details.

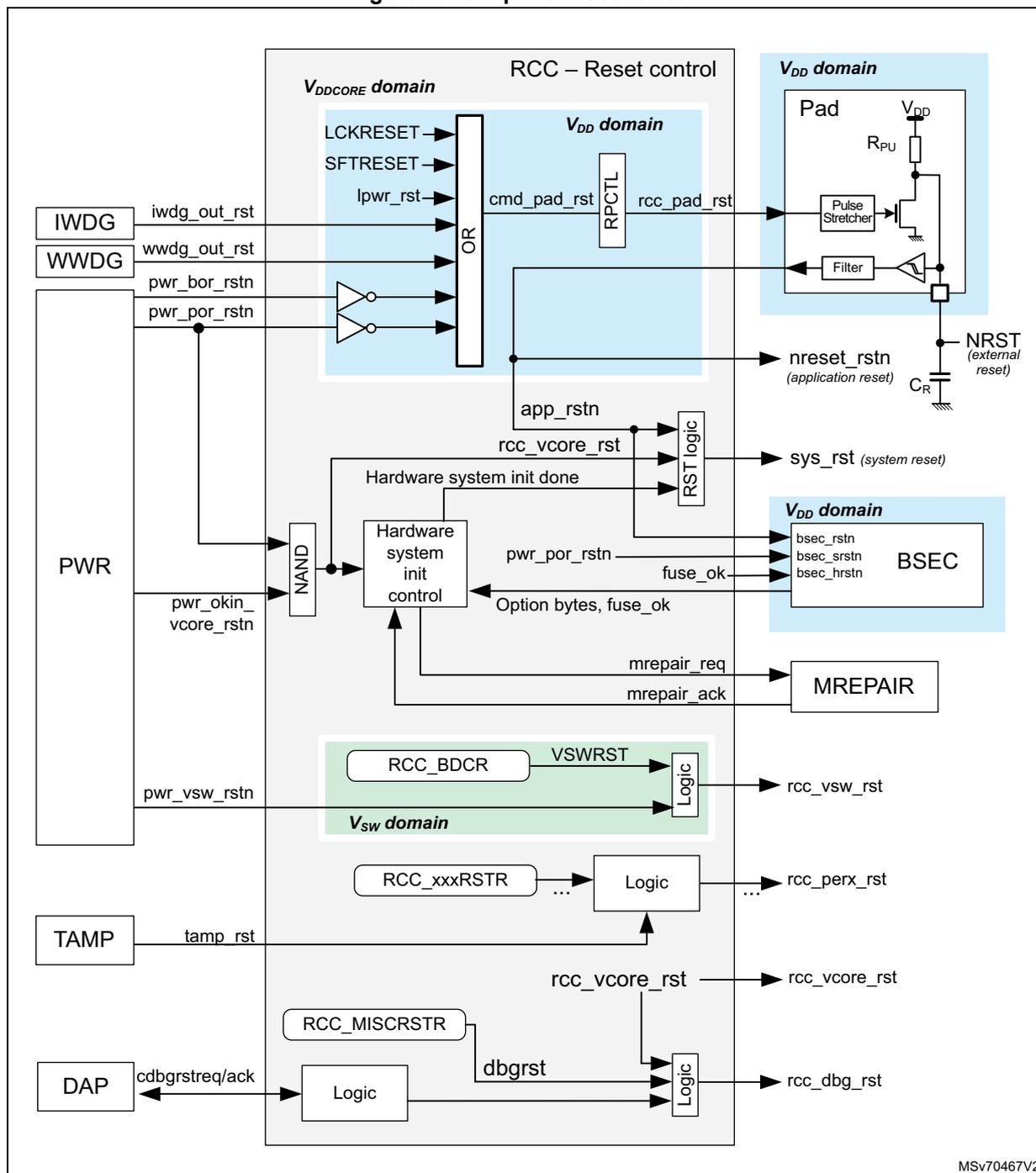

Figure 35. Simplified reset circuit

The diagram illustrates the simplified reset circuit for the microcontroller, organized into several functional blocks and voltage domains:

- V DDCORE domain: Contains the RCC – Reset control block. It includes an OR gate that combines signals from LCKRESET , SFTRESET , and lpwr_rst . The output of this gate is connected to cmd_pad_rst and rcc_pad_rst . cmd_pad_rst is connected to an RPCTL block, which in turn connects to the Pad block in the V DD domain .

- V DD domain: Contains the Pad block, which includes a pull-up resistor ( R PU ), a Pulse Stretcher , and a Filter . The NRST (external reset) pin is connected to this filter. The output of the filter is nreset_rstn (application reset).

- PWR block:

Provides power management signals:

- iwdg_out_rst (from IWDG ) and wwdg_out_rst (from WWDG ) are connected to the OR gate.

- pwr_bor_rstn and pwr_por_rstn are connected to inverters, whose outputs are connected to the OR gate.

- pwr_okin_vcore_rstn is connected to a NAND gate.

- pwr_vsw_rstn is connected to a Logic block in the V sw domain .

- Hardware system init control: Receives inputs from the NAND gate and Hardware system init done . It outputs app_rstn , rcc_vcore_rst , and pwr_por_rstn .

- RST logic: Combines app_rstn , rcc_vcore_rst , and Hardware system init done to generate sys_rst (system reset).

- BSEC block: Receives pwr_por_rstn , fuse_ok , and Option bytes, fuse_ok . It outputs bsec_rstn , bsec_srstn , and bsec_hrstn .

- MREPAIR block: Receives mrepair_req and mrepair_ack signals.

- V sw domain: Contains RCC_BDCR (outputting VSWRST ) and RCC_xxxRSTR (outputting rcc_perx_rst ), both connected to Logic blocks.

- TAMP block: Outputs tamp_rst to a Logic block.

- DAP block: Outputs cdmgrstreq/ack to a Logic block.

- RCC_MISCSTR block: Outputs dbgrst to a Logic block.

- Final Logic blocks: Combine various signals to generate rcc_vsw_rst , rcc_perx_rst , rcc_vcore_rst , and rcc_dbg_rst .

MSV70467V2

14.5.2 System and application resets (sys_rst, nreset_rstn)

A system reset ( sys_rst ) resets most of the registers to their default values, unless otherwise specified in the register description (summary in Table 66 ).

A system reset can be generated from one of the following sources:

- • an assertion of the NRST pin (external reset)

- • a reset from the power-on/off reset block (pwr_por_rstn)

- • a reset from the brownout reset block (pwr_bor_rstn), see Section 13.5.2: Brownout reset (BOR) for a detailed description of the BOR function

- • a reset from the independent watchdogs (iwdg_out_rst)

- • an exit from Standby mode (rcc_vcore_rst)

- • a reset from the window watchdogs depending on WWDG configuration (wwdg_out_rst)

- • a software reset (SFTRESET) signal, connected to SYSRESETREQ from the Cortex-M55 core

- • a lockup reset (LCKRESET) signal, connected to LOCKUP from the Cortex-M55 core

- • a reset from the low-power mode security reset, depending on the option byte configuration (lpwr_rst)

The application reset (nreset_rstn) is similar to the system reset, but it is not asserted when the system exits Standby mode.

Note: The sys_rst is actually a combination the native internal reset signal (int_sys_rstn) and the debug Standby reset signal (dbg_stdby_rstn). Some registers are reset by int_sys_rstn only. See Section 14.6.13 for more details about dbg_stdby_rstn.

The SYSRESETREQ bit in Cortex-M55 must be set to force a software reset on the device. Refer to the Cortex-M55 with FPU Technical Reference Manual for more details. There is also a SYSCFG register, which affects SYSRESETREQ.

14.5.3 NRST reset

The NRST is active low. A pulse stretcher guarantees a minimum reset pulse duration of 20 µs (see the datasheet for details). The NRST assertion can also be extended by adding the C R capacitor.

It is not recommended to leave the NRST pin unconnected. When not used, connect this pin to ground via a 4.7 to 10 nF capacitor (C R in Figure 35 ). As shown in Figure 35 , a filter is present to suppress spurious coming from the NRST pin.

14.5.4 Low-power mode security reset (lpwr_rst)

To prevent critical applications from mistakenly entering a low-power mode, two low-power mode security resets are available. When enabled through RST_STOP and RST_STDBY option bytes, a system reset (sys_rst) is generated if the following conditions are met:

- • The CPU mistakenly enters Stop mode.

This type of reset is enabled by setting RST_STOP user option byte. If a Stop mode entry sequence is successfully executed, a system reset is generated. - • The system mistakenly enters Standby mode.

This type of reset is enabled by setting RST_STDBY user option byte. If a Standby mode entry sequence is successfully executed, a system reset is generated.

LPWRRSTF bit in RCC_RSR indicates that a low-power mode security reset occurred (see row 8 in Table 67 ).

The lpwr_rst input is activated when a low-power mode security reset is required. This signal is generated by the PWR.

See Section 5: OTP mapping (OTP) for additional information, and Table 54: Operating mode summary for the overview of existing power modes.

14.5.5 Backup domain reset

A backup domain reset (rcc_vsw_rst) is generated when one of the following occurs:

- • a software reset, triggered by setting VSWRST in RCC_BDCR: the BKPSRAM is not affected.

- • V SW voltage outside the operating range: the BKPSRAM content is no longer valid.

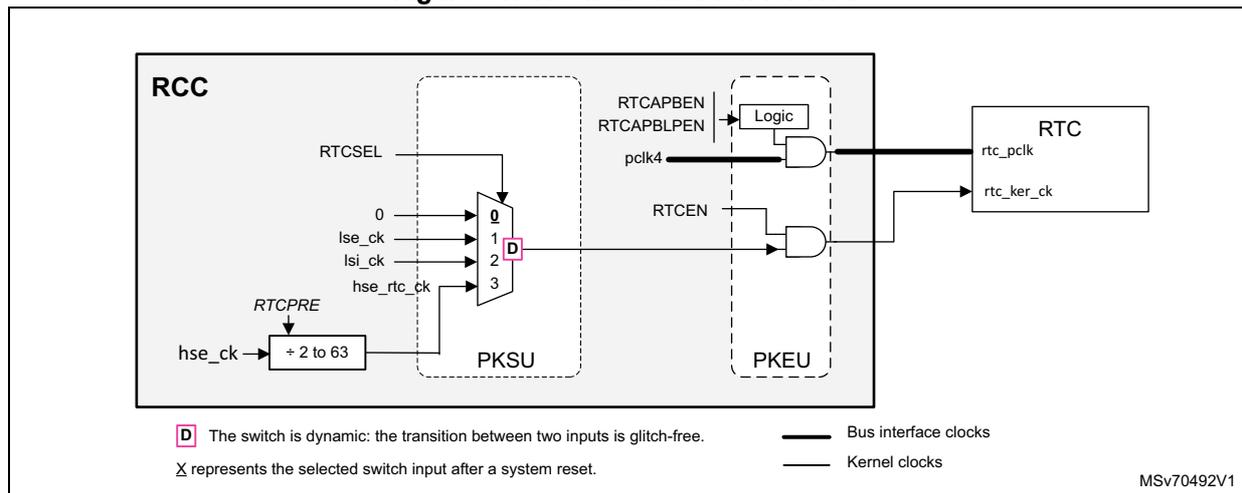

The RCC_BDCR register and all bitfields in the backup domain (including RTC) return to their reset values: these include RTCEN, RTCLPEN, RTCPRE, RTCSEL, LSECSSRA, LSECSSD, LSECSSON, LSERDY, LSERDYF, LSEON, LSEDRV, LSEEXT, LSEBYP, LSEGON.

See Section 13.4.4: Backup domain and Section 3: System security for additional information.

14.5.6 CoreSight debug reset

CoreSight debug components can be reset in three different ways:

- • using the DAP by setting CDBGRSTREQ in DP_CTRLSTAT

This asserts the debug reset request signal (cdbgrstreq) connected to the RCC. The RCC then asserts the debug reset (rcc_dbg_rst), and a handshake signal cdbgrstack acknowledges the DAP request. The debug reset remains asserted while cdbgrstreq is asserted (see Figure 35 for details).

- • when the application sets DBGRST in RCC_MISCSTR

This asserts the rcc_dbg_rst reset, which is deasserted when DBGRST is cleared to 0.

- • when a V DDCORE power-on reset occurs (rcc_vcore_rst)

This reset is asserted after a POR, or when the product exits Standby mode.

Refer to Section 14.5.6 for details.

14.5.7 Option-byte loading

As shown in Figure 37 , the option-byte loading (OBL via OTP_LD) sequence happens after a POR or a pin reset.

The system reset (sys_rst) is released only after the OBL has completed.

The BSEC manages an OTP array of fuse words, which hold the option-byte configuration for the device. This configuration must be set every time an app_rstn is asserted, and the system stays in reset until this configuration has been properly loaded (fuse_ok signal is received from the BSEC module).

The BSEC handles the following reset sources:

- • a main reset (bsec_rstn) asserted when an app_rstn is asserted

- • a scratch reset (bsec_srstn) asserted when a pwr_por_rstn is asserted

- • a hot reset (bsec_hrstn) asserted when fuse_ok is low

14.5.8 Reset of peripherals

The application can reset individually any peripheral, whenever requested. This can be done via registers named

RCC_xxxxRSTR

(

xxxx

is the bus name on which the peripheral is connected).

To reset a peripheral, the corresponding reset bit must be set to 1 (peripheral clock not required), and then set back to 0 (peripheral clock must be enabled and running in advance). There is no need to enable a peripheral clock to reset a peripheral.

Caution: PKA, CRYP, SAES, and HASH may be reset directly in hardware upon a tamper event.

14.5.9 Reset pulse control (RPCTL)

The RPCTL allows the application to control the minimum activation time of the NRST pad. This feature is particularly helpful because some external devices may require a specific reset duration. In addition, the internal reset pulse, for example from IWDG, may be too short for external devices.

The RPCTL is located in the V DD domain, and is reset only after a power-on reset.

The RPCTL is controlled by

MRD[4:0]

in

RCC_RDCR

.

If

MRD

is 0, then the RPCTL is bypassed. The minimum activation time in this case is given by the pulse stretcher embedded in the reset pad (typically 20 μs).

If

MRD

is non-0, then the rising edge of

cmd_pad_rst

causes NRST to be immediately driven low, for at least the duration set by

MRD[4:0]

. The duration of the reset is unchanged if the

cmd_pad_rst

signal is active for longer than the duration set by

MRD[4:0]

. The minimum activation time is between 1 and 31 ms.

The RPCTL uses the LSI clock to measure time. When the

cmd_pad_rst

goes high, the RPCTL requests the LSI clock to control the reset duration. If the LSI was not enabled by another function, it may take some microseconds before obtaining LSI ready (T

LSI_SU

).

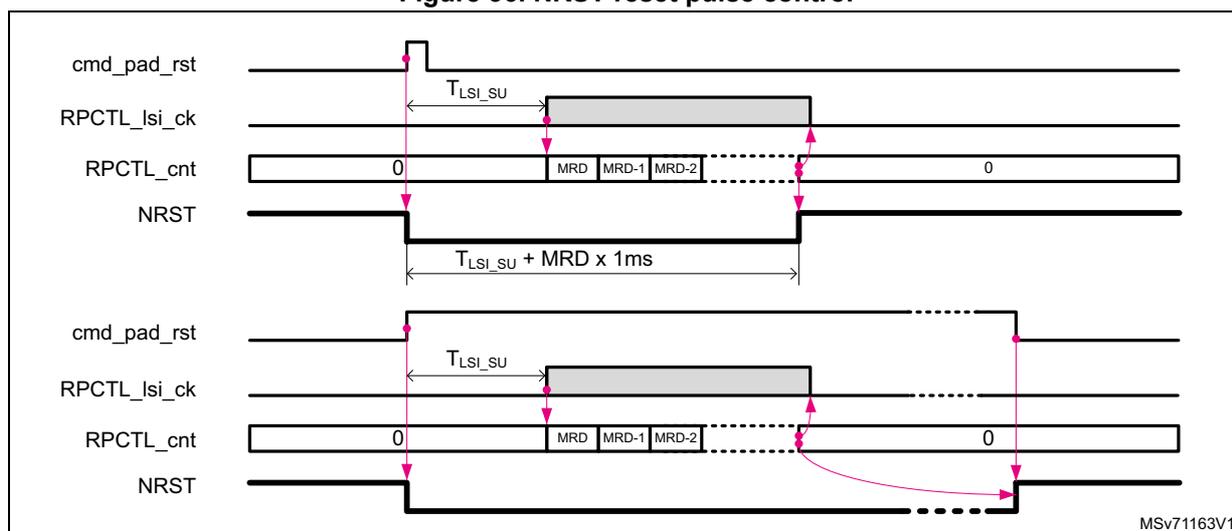

Figure 36 shows two scenarios.

Figure 36. NRST reset pulse control

The figure is a timing diagram illustrating two scenarios for NRST reset pulse control. It consists of four signal lines:

cmd_pad_rst

,

RPCTL_lsi_ck

,

RPCTL_cnt

, and

NRST

.

Top Scenario (Short pulse):

The

cmd_pad_rst

signal pulses low briefly. This triggers the

NRST

signal to go low. The

RPCTL_lsi_ck

becomes active after a startup time T

LSI_SU

. The

RPCTL_cnt

then counts down from

MRD

to 0. The

NRST

signal remains low until the counter reaches 0, resulting in a total pulse width of T

LSI_SU

+ MRD × 1ms.

Bottom Scenario (Long pulse):

The

cmd_pad_rst

signal stays low for a duration longer than the programmed RPCTL time. The

NRST

signal follows

cmd_pad_rst

and goes high only when

cmd_pad_rst

returns high, even though the

RPCTL_cnt

has already finished counting down to 0.

The diagram is labeled MSV71163V1.

14.5.10 Reset coverage summary

Table 66 gives a detailed view of the coverage of the most important reset sources.

Note: When \( V_{DD} \) is not valid, \( V_{DDCORE} \) is not valid as well.

Table 66. Reset coverage summary (1)

| Reset functions | Main reset lines | ||||||

|---|---|---|---|---|---|---|---|

| pwr_por_rstn (2) | rcc_vcore_rst (3) | sys_rst | nreset_rstn (4) | rcc_dbg_rst | rcc_perx_rst | rcc_vsw_rstn | |

| \( V_{DD} \) domain | X | - | - | - | - | - | - |

| MCU | X | X | X | - | - | - | - |

| WWDG | X | X | X | - | - | - | - |

| IWDG | X | - | - | X | - | - | - |

| AXI/AHB interconnections | X | X | X | - | - | - | - |

| Debug components (including DBGMCU): reset all the debug parts except the SWJ-DP function, which is reset by the NJTRST or rcc_vcore_rst resets. | X | X | - | - | X | - | - |

| Hardware system init: includes the memory repair. | X | X | - | - | - | - | - |

| RCC | RCC reset register (RCC_RSR) | X | - | - | - | - | - |

| RCC control register (RCC_CR) and RCC APB5 Sleep enable register (RCC_RDCR) | X | - | - | - | - | - | |

| RCC bitfields in the backup domain | - | - | - | - | - | X | |

| Other RCC registers | X | X | X | - | - | - | |

| PWR | PWR_CSR1 | - | - | - | - | - | X |

| PWR_CSR2 | X | - | - | - | - | - | |

| PWR_CSR3: individual bits of this register do not have the same reset condition (see Section 13: Power control (PWR) for details). | X | X | X | - | - | - | |

| PWR_WKUPCR, PWR_WKUPFR, and PWR_WKUPEPR | X | - | - | X | - | - | |

| Other registers | X | X | X | - | - | - | |

| RTC | Peripheral (except APB) | - | - | - | - | - | X |

| Peripheral APB | X | X | X | - | - | - | |

| BKPSRAM: after a reset of the \( V_{SW} \) domain, the BKPSRAM backup regulator is disabled. This function is controlled via BKPRBSEN (in PWR_BDCR2). If the rcc_vsw_rst reset is due to a too low \( V_{SW} \) voltage, the BKPSRAM content is lost. | - | - | - | - | - | - | X |

| Other peripherals | X | X | X | - | - | X | - |

1. 'X' means that the function is reset by the corresponding reset line. '-' means that the function is not reset by the corresponding reset line.

2. pwr_por_rstn is asserted when the voltage applied to \( V_{DD} \) is not valid. When pwr_por_rstn is asserted, the rcc_vcore_rst, NRST, sys_rst, and nreset_rstn are asserted as well.

- 3.

rcc_vcore_rstis asserted when the voltage applied to VDD is not valid, or when the system exits Standby mode (because \( V_{DDCORE} \) is switched off). Whenrcc_vcore_rstis asserted,sys_rstandpwr_dbg_rstare asserted as well. - 4. When

nreset_rstnis asserted,sys_rstis asserted as well.

14.5.11 Reset source identification

The CPU can identify the reset source by checking reset flags in RCC_RSR or PWR_CSR3 registers.

The CPU can clear flags in RCC_RSR by setting RMVF bit in this register.

Table 67 shows how the status bits behave according to the situation that generated the reset. For example, when an IWDG timeout occurs (row 7), if the CPU reads RCC_RSR during the boot phase, both PINRSTF and IWDGRSTF bits are set, indicating that the IWDG also generated a pin reset.

Table 67. Reset source identification (1)

| # | Situation generating a reset | SBF (2) | LPWRRSTF | IWDGRSTF | WWDGRSTF | LCKRSTF | SFTRSTF | BORRSTF | PINRSTF | PORRSTF |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | Power-on reset (

pwr_por_rstn

) | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 2 | Pin reset (NRST) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 3 | Brownout reset (

pwr_bor_rstn

) | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4 | System reset generated by the CPU (SFTRESET) | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 5 | System reset generated by the CPU (LCKRESET) | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 6 | WWDG reset (

wwdg_out_rst

) | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 7 | IWDG reset (

iwdg_out_rst

) | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 8 | CPU erroneously enters Stop or Standby mode | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 9 | The product exits Standby mode | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

1. Grayed cells highlight the register bits that are set.

2. The SBF bit is located in PWR_CSR3 register.

14.5.12 Power-on and wake-up sequences

For detailed diagrams, refer to Section 13.4.1: System supply startup in the PWR.

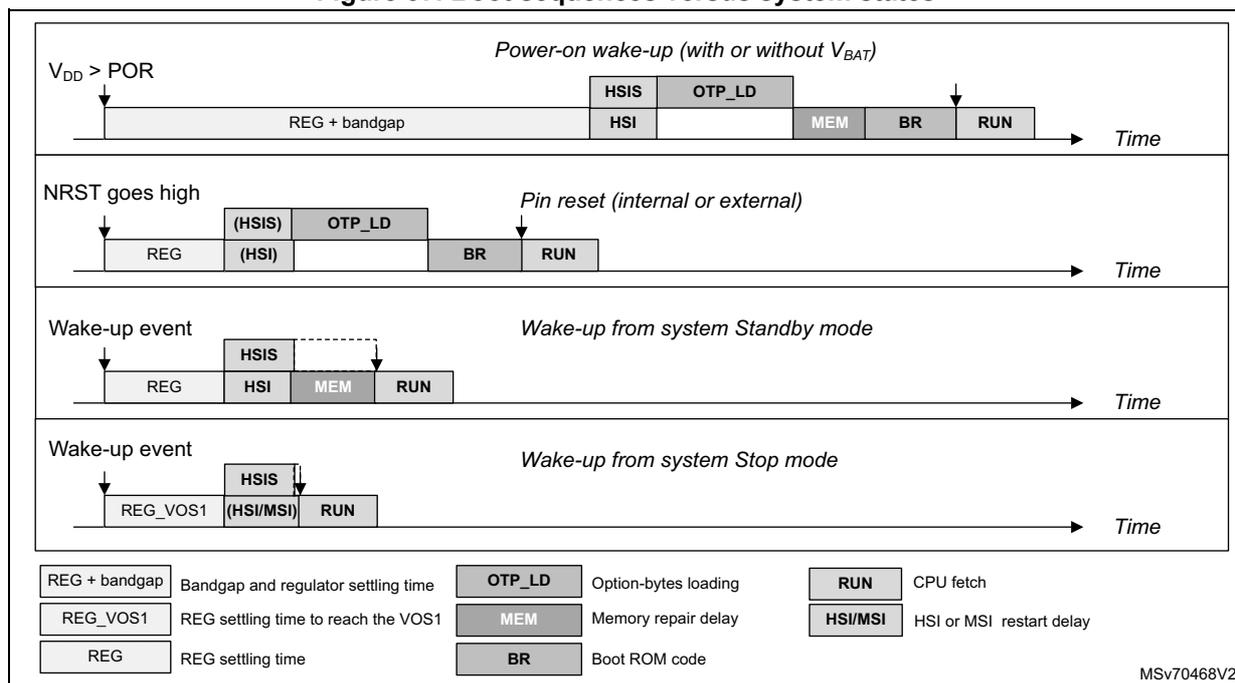

The time interval between the event that exits the device from a low-power, and the moment where the CPU is able to execute code, depends on the system state and on its configuration. Figure 37 shows the most usual examples.

Power-on wake-up sequence

The sequence shown in Figure 37 gives the most significant phases of the power-on wake-up. It is the longest sequence since the circuit was not powered.

Note: This sequence remains unchanged whatever \( V_{BAT} \) is present or not.

Boot from pin reset (NRST)

When a pin reset occurs, \( V_{DD} \) is still present. As a result:

- the regulator settling time is faster since the reference voltage is already stable

- the HSI restart delay may be needed if the HSI was not enabled when the NRST occurred, otherwise this restart delay phase is skipped.

Boot from system standby

When waking up from system standby, the reference voltage is stable since \( V_{DD} \) has not been removed. As a result, the regulator settling time is fast. Since \( V_{DDCORE} \) was not present, the restart delay for the HSI and HSIS cannot be skipped.

sys_rst remains asserted until HSIS runs and the memory repair completes.

Restart from system stop

When restarting from system stop, \( V_{DD} \) is still present. As a result, the sequence is mainly composed of two steps:

- The regulator settling time reaches \( V_{OS1} \) (default voltage).

- HSI/MSI restart delay. This step can be skipped if HSISTOPEN = MSISTOPEN = 1 in RCC_STOPCR.

sys_rst remains asserted until HSIS runs.

Figure 37. Boot sequences versus system states

Figure 37. Boot sequences versus system states

The diagram illustrates four boot sequences over time:

- Power-on wake-up (with or without \( V_{BAT} \) ): Triggered by \( V_{DD} > POR \) . Sequence: REG + bandgap → HSIS (HSI) → OTP_LD → MEM → BR → RUN.

- Pin reset (internal or external): Triggered when NRST goes high. Sequence: REG → (HSIS) (HSI) → OTP_LD → BR → RUN.

- Wake-up from system Standby mode: Triggered by a wake-up event. Sequence: REG → HSIS (HSI) → MEM → RUN.

- Wake-up from system Stop mode: Triggered by a wake-up event. Sequence: REG_VOS1 → HSIS (HSI/MSI) → RUN.

Legend:

- REG + bandgap: Bandgap and regulator settling time

- REG_VOS1: REG settling time to reach the \( V_{OS1} \)

- REG: REG settling time

- OTP_LD: Option-bytes loading

- MEM: Memory repair delay

- BR: Boot ROM code

- RUN: CPU fetch

- HSIS/MSI: HSI or MSI restart delay

MSV70468V2

14.6 Functional description of RCC clocks

The RCC provides a wide choice of clock generators:

- HSI (high-speed internal oscillator) clock: ~ 8, 16, 32, or 64 MHz

- • HSE (high-speed external oscillator) clock: 8 to 48 MHz

- • LSE (low-speed external oscillator) clock: 32 kHz

- • LSI (low-speed internal oscillator) clock: ~ 32 kHz

- • MSI (low-power internal oscillator) clock: ~ 4 or 16 MHz

The RCC offers a high flexibility for the application to select the appropriate clock for the CPU and peripherals (in particular for peripherals that require a specific clock, such as SPI/I2S and SAI).

To optimize the power consumption, each clock source can be switched ON or OFF independently.

The RCC provides up to four PLLs; each of them can be configured in integer mode (with or without SSCG - spread spectrum clock generation), or fractional mode.

As shown in the Figure 38 , the RCC offers two clock outputs (MCO1 and MCO2), with flexibility on the clock selection and frequency adjustment.

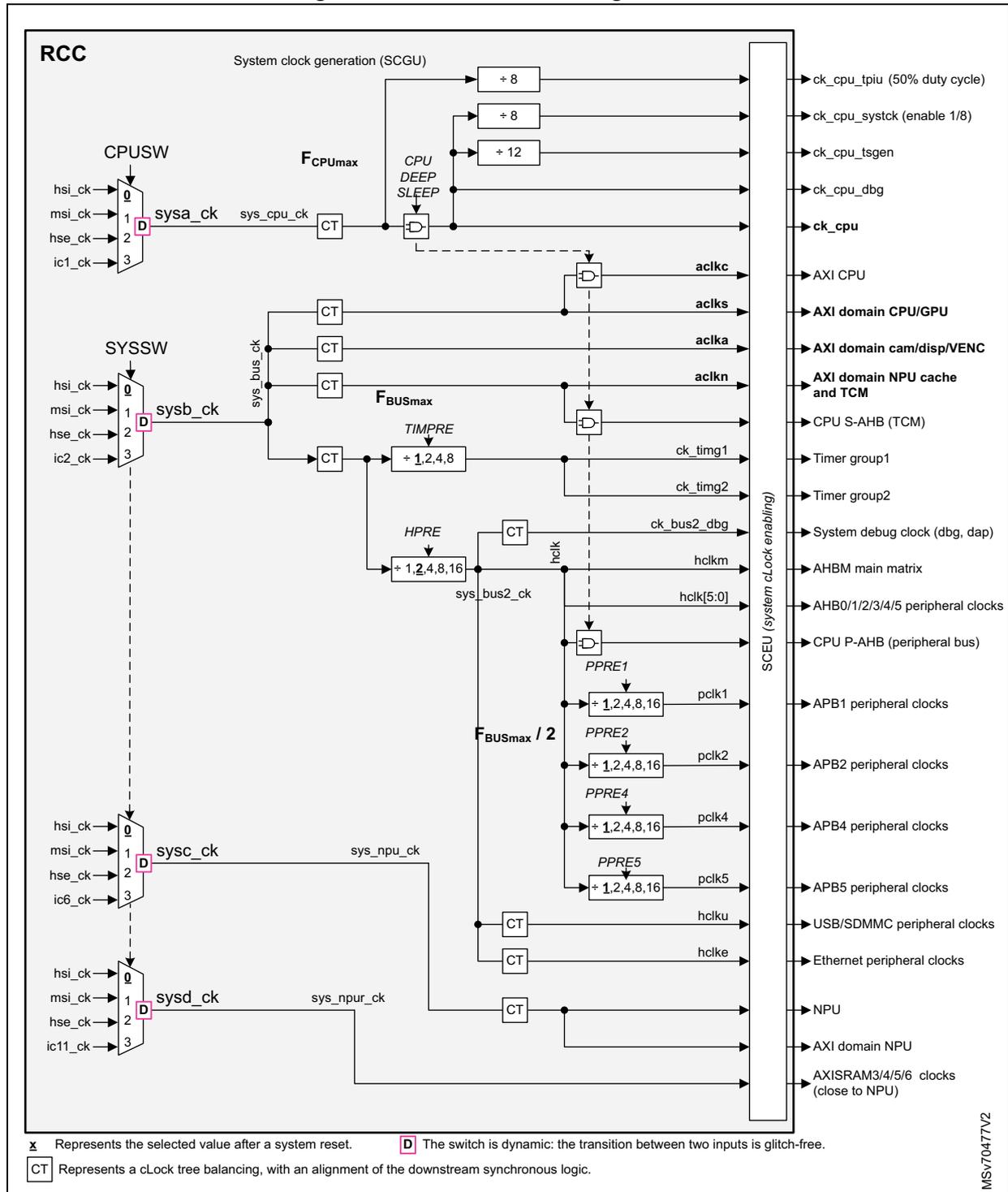

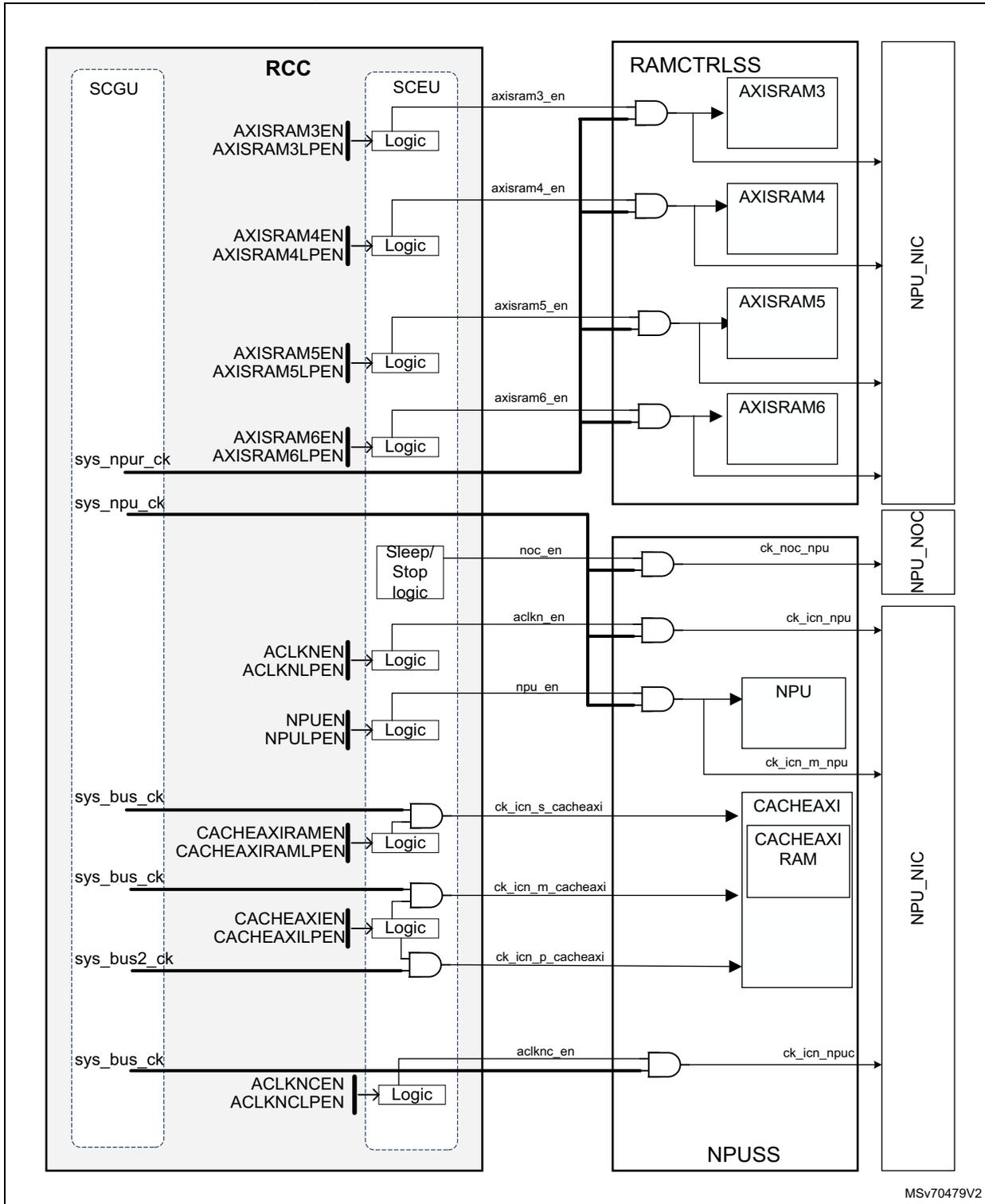

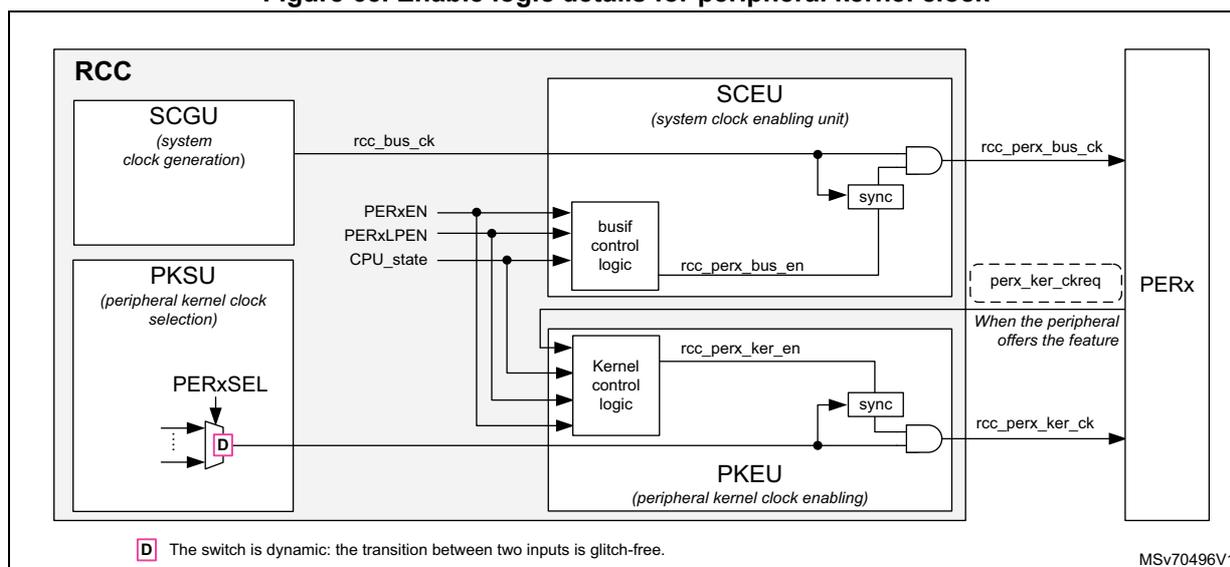

The SCGU (system clock generation unit) contains several prescalers to configure the CPU and bus matrix clock frequencies.

The PKSU (peripheral kernel clock selection unit) provides several dynamic switches, which give a large choice of kernel clock distribution to peripherals.

The PKEU (peripheral kernel clock enable unit) performs the peripheral kernel clock gating. The SCEU (system clock enable unit) performs the clock gating for the bus interface, cores, and the bus matrix.

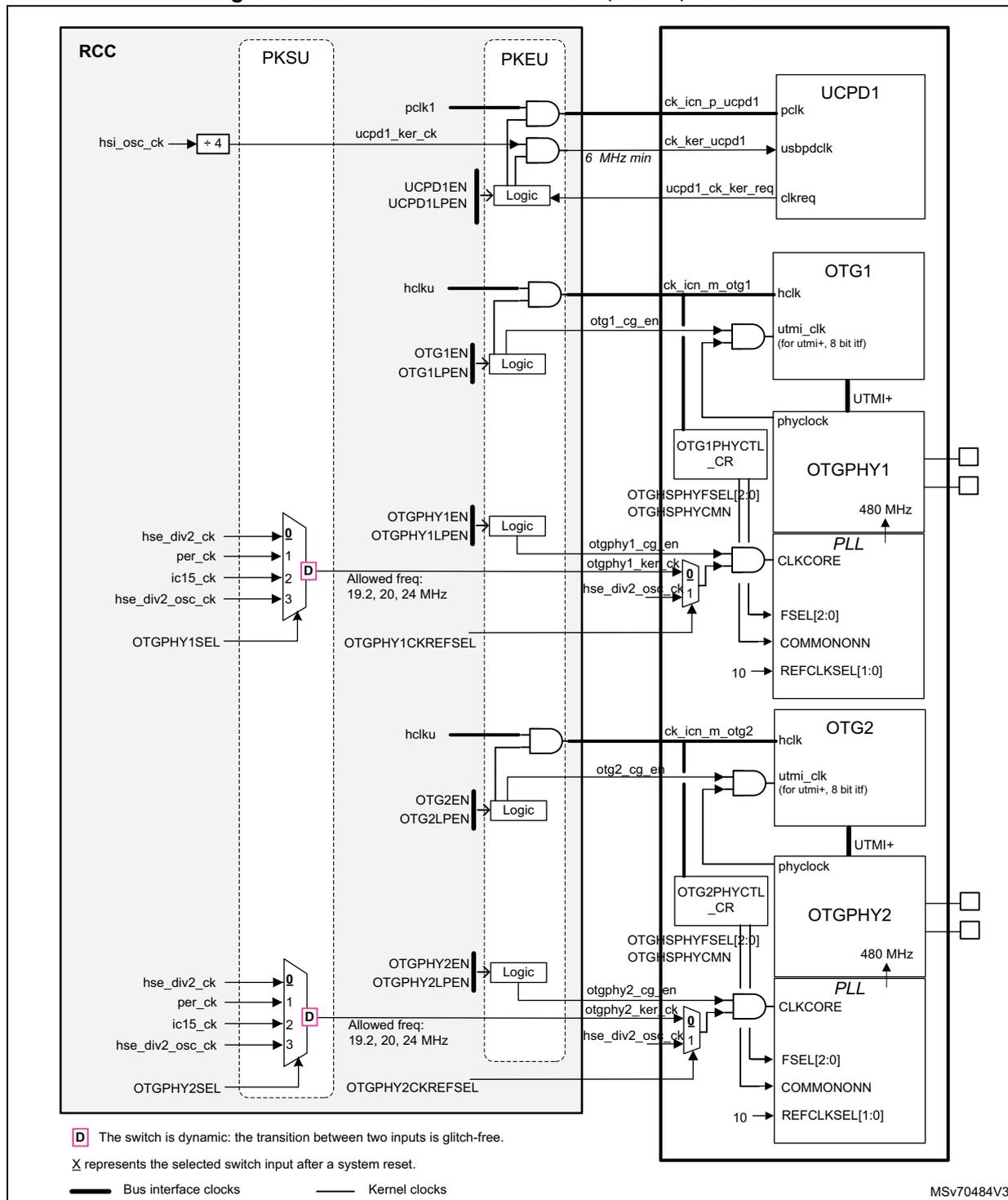

Figure 38. Top-level clock tree

![Top-level clock tree diagram for RCC. It shows various clock sources (LSI, LSE, HSE, MSI, HSIS) and their paths through dividers and PLLs (PLL1-4) to generate system clocks (sys[b,c,d]_ck) and peripheral clocks (ic1_ck to ic20_ck).](/RM0486-STM32N6x5-x7/d74ed29ed2b7aca01173043c14d46cab_img.jpg)

The diagram illustrates the top-level clock tree for the RCC. It shows the following components and paths:

- VDD domain: Contains LSI (activated by LSIEN or IWDG) and tempo. LSI provides lsi_ck to the IWDG.

- VSW (Backup): Contains LSE (activated by LSEON) and CSS. OSC32_IN and OSC32_OUT are connected to LSE. LSE provides lse_ck to the RTC.

- HSE: Activated by HSEON. OSC_IN and OSC_OUT are connected. HSE provides hse_osc_ck. This is divided by HSECSSBPRE (+1,2,16) to produce hse_div2_osc_ck and hse_cal_ck. HSE also provides hse_ck, which is divided by HSEPRE (+2 to 63) to produce hse_div2_ck.

- HSI: Activated by HSION. HSI provides hsi_osc_ck, which is divided by HSIIDIV (+1,2,4,8) to produce hsi_div_ck and hsi_div4_ck. HSI also provides hsi_ck, which is divided by HSIIDIV (+128) to produce msi_cal_ck.

- MSI: Activated by MSION. MSI provides msi_osc_ck, which is divided by tempo to produce msi_ck. MSI also provides msi_ck, which is divided by +128 to produce msi_cal_ck.

- HSIS: Activated by BSEC. HSIS provides hsis_osc_ck, which is divided by tempo to produce hsis_ck.

- RTCSEL: A multiplexer that selects the RTC clock source (0: LSI, 1: LSE, 2: HSE, 3: HSE_RTC). RTCEN enables the RTC clock (rcc_rtc_ck) to the RTC/AWU.

- PERSEL: A multiplexer that selects the PER clock source (0: hsi_ck, 1: msi_ck, 2: hse_ck, 3: ic19_ck, 4: ic5_ck, 5: ic10_ck, 6: ic15_ck, 7: ic20_ck). PER provides per_ck to the MCO1 and MCO2 outputs.

- CPU SW: A multiplexer that selects the CPU clock source (0: hsi_ck, 1: msi_ck, 2: hse_ck, 3: ic1_ck). CPU SW provides sysa_ck to the SCGU and SCEU.

- SYSSW: A multiplexer that selects the system clock source (0: hsi_ck, 1: msi_ck, 2: hse_ck, 3: ic2,6,11_ck). SYSSW provides sys[b,c,d]_ck to the SCGU and SCEU.

- PLL1-4: Each PLL consists of a DIVMx, VCO, DIVNx, FRACNx, and SSCGx. PLL1-4 are selected by PLL1SEL-4SEL (0: hsi_ck, 1: msi_ck, 2: hse_ck, 3: i2s_ckin). PLL1-4 provide pll1_ck to pll4_ck to the IC1-20.

- IC1-20: Integrated Circuits 1 through 20, each receiving a clock from the PLLs and providing ic1_ck to ic20_ck to the PKSU.

- SCGU (system clock generation): Receives sysa_ck and sysd_ck. It generates system clocks for the CPU, busses, and peripherals.

- SCEU (system clock enabling): Receives sysa_ck and sysd_ck. It enables clocks for the CPU, busses, and peripherals.

- PKSU (peripheral kernel clock selection): Receives ic1_ck to ic20_ck. It selects peripheral kernel clocks for the PKEU.

- PKEU (peripheral clock enabling): Receives sysa_ck, sysb_ck, sysc_ck, sysd_ck, and PKSU outputs. It enables peripheral clocks for the CPU, busses, and peripherals.

- AUDIOCLK: Provided by i2s_ckin. It is used for ETH1_CLK_SEL, ETH1_REF_CLK_SEL, and ETH1_SEL(2:0).

✱ Represents the selected mux input after a system reset.

MSV70469V5

14.6.1 Clock naming convention

The RCC provides clocks to the complete circuit. To avoid misunderstandings, the following terms are used in this document:

- • Peripheral clocks provided by the RCC to the peripherals

Two kinds of clock are available, namely bus interface and kernel clocks

A peripheral receives from the RCC a bus interface clock to access its registers, and thus control the peripheral operation. This clock is generally the AHB, APB, or AXI clock, depending on which bus the peripheral is connected to. Some peripherals need only a bus interface clock.

Some peripherals require also a dedicated clock (named kernel clock) to handle the interface function. As an example, SAI must generate specific and accurate master clock frequencies, which require dedicated kernel clock frequencies.

An advantage of decoupling the bus interface clock from the kernel clock is that the bus clock can be changed without reprogramming the peripheral.

- • CPU clock: derived from a dedicated system clock (sysa_ck), is asynchronous to the bus clocks.

- • Bus matrix clocks: provided to the different bridges (APB, AHB, AXI, or NoC), are derived from a system clock (sysb_ck).

- • NPU and NPU AXI clocks: the NPU clock is derived from a dedicated system clock, sysc_ck, also used for the AXI matrix close to the NPU.

- • AXISRAM1/2 clocks: derived from sysb_ck.

- • AXISRAM3/4/5/6 clocks: derived from sysd_ck.

14.6.2 Oscillator description

Table 68 shows the oscillator states versus system modes, when the oscillators are enabled via registers. Available means that the resource can be used if activated via registers.

Table 68. Oscillator states versus system modes

| System modes | V DDCORE domain | V DD domain | V SW domain | |||

|---|---|---|---|---|---|---|

| HSIS | HSE | HSI | MSI | LSI | LSE | |

| Exit from system reset | On | Off | On | Off | Available | Available |

| Exit from system stop | On | Off | On (1) | On (2) | Available | Available |

| In Run/Sleep mode | On | Available | Available | Available | Available | Available |

| In Stop mode | Off | Off | Available (3) | Available (4) | Available | Available |

| In Standby mode | Off | Off | Off | Off | Available | Available |

| In V BAT mode | Off | Off | Off | Off | Off | Available |

1. If STOPWUCK = 0.

2. If STOPWUCK = 1.

3. HSI can remain activated in Stop mode if HSISTOPEN = 1, or if a peripheral selecting HSI generates a kernel clock request. Caution: HSI must be off if the PWR is programmed to use SVOS low.

4. MSI can remain activated in Stop mode if MSISTOPEN = 1, or if the peripheral selecting MSI generates a kernel clock request. Caution: MSI must be off if the PWR is programmed to use SVOS low.

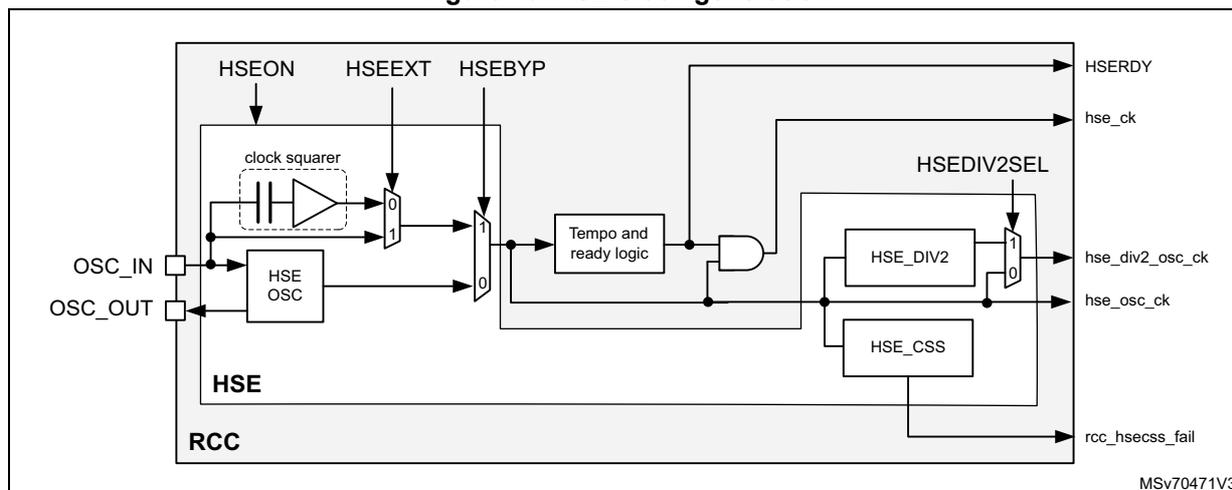

HSE oscillator

The HSE allows the application to provide a very accurate high-speed clock for the device. The HSE can generate an internal clock from two sources:

- • external clock source (analog or digital)

- • external crystal/ceramic resonator

Refer to the datasheet for the values of CL1, CL2, and R1.

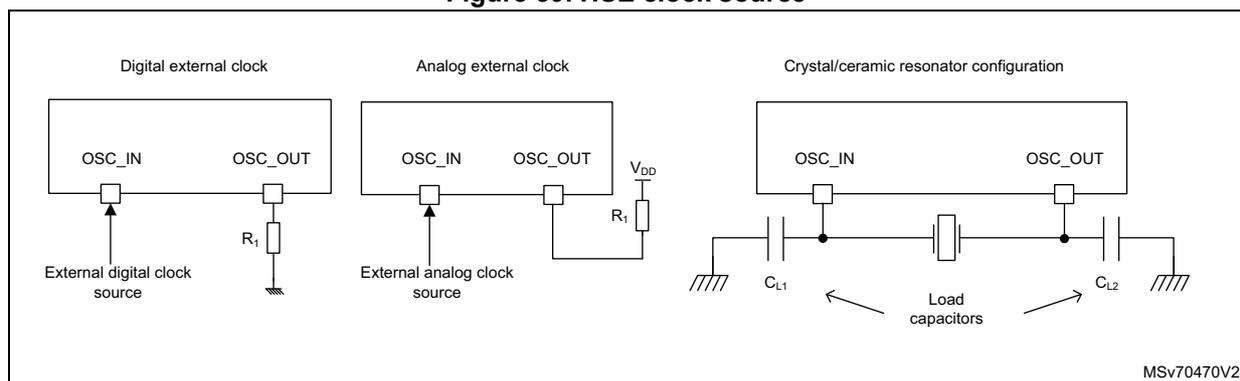

Figure 39. HSE clock source

External clock source (HSE bypass)

In this mode, the oscillator is not used, and an external clock source must be provided to the OSC_IN pin. The external clock can be low swing (analog) or digital.

In order to allow the boot ROM to detect in which configuration the HSE is used, a resistor (R1) must be connected to GND or \( V_{DD} \) (see Figure 39 ).

The resistor must be connected to GND when the HSE uses an external digital clock, and to \( V_{DD} \) when the HSE is using an external analog clock. The resistor must be removed if a crystal or ceramic resonator is used.

The external clock signal can be digital or analog (square, sinus, or triangle). An analog clock signal with a reduced amplitude is supported thanks to an internal clock squarer.

The input signal must have a duty cycle close to 50% (refer to the datasheet for additional information).

This mode is selected when HSEBYP = 1 in RCC_HSECFGR and HSEON = 1 in RCC_CR. In case of an analog clock input (low swing) HSEEXT must be set to 0 in RCC_HSECFGR. For a digital clock input, HSEEXT must be set to 1.

Figure 40. HSE clock generation

External crystal/ceramic resonator

A crystal/resonator can be connected as shown in Figure 39 : the crystal/resonator and the load capacitors must be placed as close as possible to the oscillator pins in order to minimize the output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected crystal or ceramic resonator. Refer to the electrical characteristics section of the datasheet for more details.

The oscillator mode is enabled by setting HSEBYP = 0 and HSEON = 1.

HSE ready logic

The HSERDY flag indicates when a valid clock is available at HSE output (hse_ck). When the HSE is enabled (HSEON = 1), the HSERDY flag goes to 1 when 1024 valid cycles of HSE have been detected. The hse_ck clock is not released until HSERDY goes to 1.

An interrupt can be generated if enabled in RCC_CIER.

HSE controls

The HSE can be switched on and off through HSEON.

The HSE is automatically disabled by hardware when the system enters Stop or Standby mode (see Table 68 ).

The HSE clock can also be driven to MCO1 and MCO2 outputs, and used as clock source for other application components.

HSE programming sequence

In order to initialize the HSE, the application must follow this sequence:

- 1. Make sure the HSE is not directly or indirectly used as system clock. If it is, switch to the HSI or MSI as clock source for system clock.

- 2. Disable the HSE by writing 0 to HSEON.

- 3. Check that the HSE is disabled by waiting HSERDY = 0.

- 4. If the oscillator mode is needed, select the oscillator mode with HSEBYP = 0.

- 5. If an external clock is connected to OSC_IN:

- – Select the bypass mode by setting HSEBYP = 1.

- – If the input clock is a full-swing digital signal, set HSEEXT = 1.

- – If the input clock is a low-swing signal, set HSEEXT = 0.

- Enable again the HSE by writing 1 to HSEON.

- Wait for HSERDY = 1, then the HSE is ready for use.

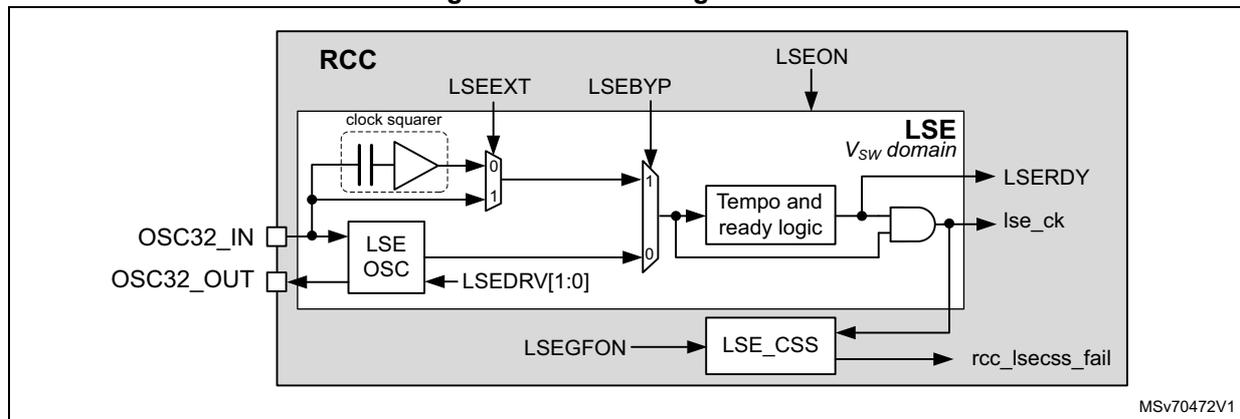

LSE oscillator

The LSE allows the application to provide a very accurate low-frequency clock for the device. The LSE can generate an internal clock from two possible sources:

- • external user clock

- • external crystal/ceramic resonator

External clock source (LSE bypass)

In this mode, the oscillator is not used, and an external clock source must be provided to the OSC32_IN pin. The OSC32_OUT pin must be left high-Z.

The external clock signal can have a frequency up to 32.768 kHz, and can be digital or analog (square, sinus, or triangle). An analog clock signal with a reduced amplitude is supported thanks to an internal clock squarer. The input signal must have a duty cycle close to 50%. Refer to the datasheet for additional information.

This mode is selected by setting LSEBYP = 1 in RCC_LSECFGR, and LSEON = 1 in RCC_CR. In case of an analog clock input (low swing), LSEEXT must be set to 0 in RCC_LSECFGR. For a digital clock input, LSEEXT must be set to 1.

Figure 41. LSE clock generation

External crystal/ceramic resonator source (LSE crystal)

The LSE clock is generated from a 32.768 kHz crystal or ceramic resonator. It provides a low-power highly accurate clock source to the RTC for clock/calendar, or other timing functions. A crystal/resonator can be connected as shown in Figure 39. The crystal/resonator and the load capacitors must be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected crystal or ceramic resonator. Refer to the electrical characteristics section of the datasheet for more details.

The oscillator mode is selected by setting LSEBYP bit to 0 and LSEON bit to 1.

The LSE offers a programmable driving capability (LSEDRV in RCC_LSECFGR) to modulate the amplifier driving capability. This driving capability is chosen according to the external crystal/ceramic component requirement to ensure a stable oscillation.

The driving capability must be set before enabling the LSE oscillator.

Warning: The driving capability must not be changed when the LSE is enabled. The LSE behavior is not guaranteed in that case.

LSE ready logic

The LSE offers an LSERDY flag, which indicates whether the LSE clock is available or not. When the LSE is enabled (LSEON = 1), LSERDY goes to 1 in RCC_SR when a certain number of valid LSE clock cycles has been detected. The lse_ck clock is not released until LSERDY goes to 1.

When LSEBYP = 0, the RCC waits 4096 clocks cycles before activating the LSERDY flag. When LSEBYP = 1, the RCC waits 16 clocks cycles.

An interrupt can be generated if enabled in RCC_CIER.

LSE controls

LSEBYP, LSEEXT, LSEDRV, and LSEON are write-protected by DBP in PWR_DBPCR. In order to modify the bits, DBP must be set 1.

The LSE oscillator is switched on and off using the LSEON bit.

The LSE remains enabled when the system enters Stop, Standby, or V BAT mode (see Table 68 ).

The LSE clock can also be driven to MCOx outputs, and used as clock source for external components.

LSE programming sequence

To initialize the LSE, the application must follow the sequence hereafter:

- 1. Set DBP = 1 in PWR_DBPCR in order to allow write access.

- 2. Disable the LSE by writing to 0 to LSEON.

- 3. Check that the LSE is disabled by waiting LSERDY = 0.

- 4. If the oscillator mode is needed:

- – Select the oscillator mode by setting LSEBYP = 0.

- – Configure LSEDRV (if needed).

- 5. If an external clock is connected to OSC32_IN:

- – Select the bypass mode by setting LSEBYP = 1.

- – If the input clock is a full-swing digital signal, set LSEEXT = 1.

- – If the input clock is a low-swing signal, set LSEEXT = 0.

- 6. enable again the LSE by writing 1 to LSEON.

- 7. Wait for LSERDY = 1, then the LSE is ready for use.

- 8. If no further changes are needed, set DBP = 0 in PWR_DBPCR to write-protect the settings.

If the RTC is used, the LSE bypass must not be configured in digital mode, but in low-swing analog mode (default value after reset).

HSI oscillator

The HSI block provides the default clock to the device. It is a high-speed internal RC oscillator that can be used directly as system clock, peripheral clock, or as PLL input. A predivider allows the application to select an HSI output frequency of 8, 16, 32, or 64 MHz. This predivider is controlled by the HSIDIV in RCC_HSICFGR.

The HSI advantages are the following:

- • low-cost clock source (no external crystals required)

- • faster startup time than HSE (a few microseconds)

- • reduced power consumption

The HSI frequency, even with frequency calibration, is less accurate than an external crystal oscillator or ceramic resonator.

HSI controls

The HSI can be switched on and off using HSION in RCC_CR. The HSIRDY flag in RCC_SR indicates if the HSI is stable or not. At startup, the HSI output clock is not released until HSIRDY is set to 1 by hardware.

The HSI clock can also be used as a backup source (auxiliary clock) if the HSE fails (see CSS on HSE ).

The HSI can be disabled or not when the system enters Stop mode (see Table 68 ).

The HSI clock can also be driven to MCOx outputs, and used as clock source for other application components.

Care must be taken when the HSI is used as kernel clock for communication peripherals. The application must take into account the following parameters:

- • the time interval between the moment where the peripheral generates a kernel clock request, and the moment where the clock is really available

- • the frequency accuracy

HSI calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations. That is why each device is factory calibrated by STMicroelectronics to achieve an ACC HSI accuracy (refer to the product datasheet for more information).

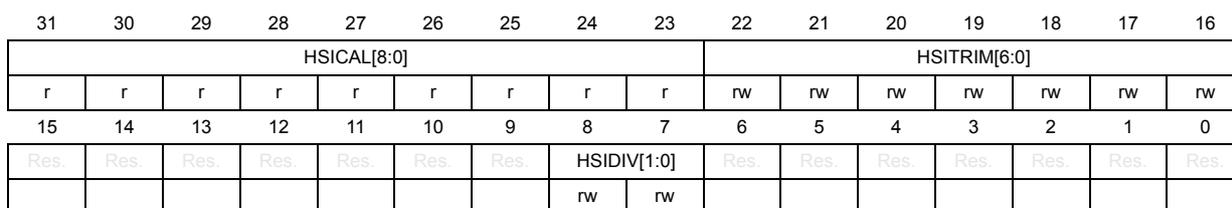

After a power-on reset or pin reset, the factory calibration value is loaded in HSICAL[8:0] in RCC_HSICFGR.

If the application is subject to voltage or temperature variations, this may affect the RC oscillator frequency. The user application can trim the HSI frequency using HSITRIM[6:0] in RCC_HSICFGR.

Figure 42. HSI calibration flow

![Figure 42. HSI calibration flow diagram. The diagram shows the HSI calibration process within the RCC (Reset and Clock Control) block. An external 'Engineering option bytes (factory calibration)' block provides a value 'bsec_hsi_cal[8:0]' to an adder (+). The adder also receives a signed value 'HSITRIM[6:0]' from the 'RCC_HSICFGR' register. The output of the adder is 'hsi_cal[8:0]', which is then passed to the HSI block's 'CAL[8:0]' register. The 'CAL[8:0]' register outputs an unsigned value 'HSICAL[8:0]' back to the 'RCC_HSICFGR' register. The diagram is labeled 'MSV70473V1' in the bottom right corner.](/RM0486-STM32N6x5-x7/79af6440ba722a77eabbe7c089e03d66_img.jpg)

Note: The HSI clock divided by eight is also used for PAD compensation mechanism, and must be enabled if the PAD compensation mechanism is activated. Refer to Section 16: System configuration controller (SYSCFG) for additional details.

MSI oscillator

The MSI is a low-power RC oscillator that can be used directly as system clock, peripheral clock, or PLL input.

However, the following point must be considered: If the MSI clock is currently used as kernel clock for some peripherals, the application must ensure that the MSI frequency change does not disturb these peripherals.

The MSI advantages are the following:

- • low-cost clock source (no external crystals required)

- • faster startup time than HSE (a few microseconds)

- • very low-power consumption

The MSI provides a clock frequency of 4 MHz (default MSIFREQSEL) or 16 MHz, while the HSI is able to provide a clock up to 64 MHz.

The MSI frequency, even with frequency calibration, is less accurate than an external crystal oscillator or ceramic resonator.

MSI controls

The MSI can be switched on and off through the MSION in RCC_CR. The MSIRDY flag in RCC_SR indicates whether the MSI is stable or not. At startup, the MSI output clock is not released until MSIRDY is set by hardware.

The MSI can be disabled or not when the system enters Stop mode (see Table 68 ).

The MSI clock can also be driven to MCOx outputs, and used as clock source for other application components.

Even if the MSI settling time is faster than the HSI, care must be taken when the MSI is used as kernel clock for communication peripherals: the application must take into account the following parameters:

- • the interval between the moment when the peripheral generates a kernel clock request, and the moment when the clock is really available

- • the frequency precision

MSI calibration

RC oscillator frequencies can vary because of manufacturing process variations. Each device is factory calibrated by ST to achieve the specified ACC MSI accuracy (refer to the product datasheet for more information).

After a power-on or pin reset, the factory calibration value for 4 MHz is loaded in MSICAL[7:0] in RCC_MSICFGR.

If MSIFREQSEL is set to 16 MHz in RCC_MSICFGR, a different calibration value is provided by the BSEC.

Voltage or temperature variations can affect the RC oscillator frequency. The user application can trim the MSI frequency using MSITRIM[4:0] in RCC_MSICFGR.

Figure 43. MSI calibration flow

![Figure 43. MSI calibration flow diagram. The diagram shows the BSEC (Engineering option bytes (factory calibration)) providing msi_trim values (4mhz[7:0] and 16mhz[7:0]) to an RCC block. Inside the RCC block, a multiplexer (MSIFREQSEL) selects between these values based on the MSIFREQSEL signal. The selected value is added (indicated by a '+' symbol) to the MSITRIM[4:0] (signed) value from the RCC_MSICFGR register. The result is msi_cal[7:0], which is then used by the MSI CAL[7:0] block. The RCC_MSICFGR register also provides the MSICAL[7:0] (unsigned) value to the MSI CAL[7:0] block. The diagram is labeled MSv70474V2.](/RM0486-STM32N6x5-x7/31f8bb7414dd80674d3ca96b1c3031c7_img.jpg)

HSIS oscillator

The HSIS is a 64 MHz RC oscillator to clock only the BSEC. It is always activated after pwr_por_rstn or app_rstn reset.

When the system goes into Stop or Standby mode, the HSIS clock is disabled by hardware. Refer to Section 14.6.7 for additional information.

HSIS calibration

RC oscillator frequencies can vary from one device to another, due to manufacturing process variations. To compensate for this, there is an HSISCAL[8:0] input on the oscillator.

The BSEC provides two calibration values (ambient and not ambient). The RCC selects between these two values using a select signal from the BSEC.

After a power-on reset, or pad reset, the factory calibration value is loaded in HSISCAL[8:0].

LSI oscillator

The LSI acts as a very low-power clock source that can be kept running when the system is in Stop or Standby mode for the IWDG and the auto-wake-up unit (AWU). The clock frequency is around 32 kHz. For more details, refer to the electrical characteristics section of the datasheet.

The LSI can be switched on and off using LSION. The LSIRDY flag indicates whether the LSI oscillator is stable or not. If an independent watchdog is started either by hardware or software, the LSI is forced on, and cannot be disabled.

The LSI remains enabled when the system enters Stop or Standby mode (see Table 68 ).

At LSI startup, the clock is not provided until the hardware sets LSIRDY. An interrupt can be generated if enabled in RCC_CIER.

The LSI clock can also be driven to MCOx outputs, and used as a clock source for other application components.

14.6.3 Clock security system (CSS)

The CSS can detect a failure of either (or both) LSE and HSE oscillators. There are signals that can be connected to the TAMP (rcc_lsecss_fail and rcc_hsecss_fail), and signals for the interrupt controller (rcc_lsecss_it, rcc_hsecss_it, and rcc_it).

CSS on HSE

The CSS can be enabled by software via HSECSSON. This bit can be enabled even when HSEON = 0.

The CSS on HSE is activated when the HSE is enabled and ready, and when the software sets HSECSSON = 1. The CSS on HSE does no longer work when the HSE is disabled. For example, this function does not work when the system is in Stop mode.

HSECSSON cannot be cleared directly by software. It is cleared by hardware when a system reset occurs, or when the system enters Standby mode (see Section 14.5.2 ).

On an HSE failure, an HSI injection feature can automatically inject a divided HSI clock in replacement at the root of the HSE tree. Users of the failed HSE keep running, but potentially at a slightly lower frequency. The HSI injected clock is adapted to the HSE frequency by an integer division. The PLLs relocks, but at the same or lower speed.

To enable the automatic HSI injection, first configure HSECSSBPRE in RCC_HSECFGR, then set HSECSSBYP = 1.

The HSI division ratio is configured with HSECSSBPRE. For instance, with the HSI at 64 MHz and an HSE at 48 MHz, the division ratio must be configured to 2x (HSECSSBPRE = 1): a failed HSE is replaced by a clock at \( 64 / 2 = 32 \) MHz.

When the CSS on HSE is enabled, the following actions are done by the RCC if a failure is detected:

- • If the HSI injection feature is enabled, the HSI oscillator is forced active, and the HSE clock is replaced by hsi_css_ck.

- • rcc_hsecss_fail is asserted.

- • The clock failure event (rcc_hsecss_fail) is also sent to the break inputs of advanced-control timers (TIM1/8/15/16/17).

- • An NMI interrupt is generated to inform the software about the failure (rcc_hsecss_it). This allows the MCU to perform rescue operations. The NMI interrupt is asserted until HSECSSF = 0 in RCC_CICR. The HSECSSF flag can be cleared by setting HSECSSC = 1.

- • A tamper event can also be triggered to clear content of backup registers and BKPSRAM.

CSS on LSE

A CSS on the LSE oscillator can be enabled by software by programming LSECSSON. This bit is disabled by hardware if one of the following conditions is met:

- • after a \( V_{SW} \) hardware reset (pwr_vsw_rst)

- • after a \( V_{SW} \) software reset via VSWRST bit

The software can also disable the CSS after an LSE failure detection.

The CSS on LSE works in all modes (Run, Stop, and Standby modes) including \( V_{BAT} \) mode.

The LSECSS provides a re-arm feature, offering the possibility to the software to re-arm the LSECSS, and to re-enable the LSE clock when a failure has been detected. This feature allows the application to decide if the LSE must be provided again to the RTC even if a failure occurred, or if another action must be performed. For example, the application can decide to reset the \( V_{SW} \) domain only if a certain number of consecutive LSE failures occurred, within a time window.

The LSECSS offers two flag signals:

- • the LSECSSD able to retain an LSE failure even in \( V_{BAT} \) mode

- • the LSECSSF used to generate an interrupt in case of LSE failure (flag not affected by a failure detected when the product is in \( V_{BAT} \) mode)

The sequence hereafter describes the LSE that enables sequence with the CSS enabled:

- 1. Follow the LSE enable procedure given in LSE programming sequence , except the last step.

- 2. Select the LSE clock via RTCSEL[1:0].

- 3. Set the LSECSSON bit to 1.

- 4. If no further changes are needed, clear DBP to 0 in PWR_DBPCR to write-protect accesses.

Note: The LSECSSON bit must be enabled after the LSE is enabled (LSEON set by software) and ready (LSERDY set by hardware), and after the RTC clock has been selected through RTCSEL.

If a failure is detected on the LSE, the hardware does the following:

- • The LSE clock is no more delivered to the RTC.

- • RTCSEL, LSECSSON, and LSEON are not changed by the hardware.

- • A failure event is generated (rcc_lsecss_fail). This event allows the system to wake up from Standby mode, but also to protect the backup registers and BKPSRAM via TAMP. This event is also generated in \( V_{BAT} \) mode.

- • The LSECSSF is activated (except in \( V_{BAT} \) mode) in order to generate an interrupt (rcc_lsecss_it, enabled by LSECSSIE).

- • The LSECSSD is activated as well, retaining the first LSE failure even in \( V_{BAT} \) mode.

On the software side, different actions can be taken according to the application requirements. Three different cases are described hereafter in order to illustrate the hardware behavior, they can also be combined. The application can also decide to handle LSE failure differently.

Case A

The application no longer wants to use LSE when a failure is detected:

- 1. Unlock registers by setting DBP in PWR_DBPCR to 1.

- 2. Disable the CSS function (this step is mandatory):

- a) Clear LSECSSF if the interrupt was enabled for this event.

- b) Clear LSECSSON to 0.

- c) Clear LSEON to 0 in order to disable the LSE.

- 3. Change the clock source for the RTC if needed:

- a) Clear RTCEN to 0 to disable the RTC clock.

- b) Enable the new clock source for the RTC.

- c) Set RTCPRE if HSE is a new clock source.

- d) Select the proper clock source via RTCSEL.

- e) Set RTCEN to 1 to enable the RTC clock.

- 4. The application must perform specific actions for TAMP events if enabled (see

Section 4: Boot and security control (BSEC)

and

Section 61: Real-time clock (RTC)

).

- • Lock registers by clearing DBP to 0 in PWR_DBPCR

Case B

The application wants to re-initialize the \( V_{SW} \) domain:

- 1. Unlock registers by setting the DBP bit of PWR_DBPCR to 1

- 2. Perform a VSW reset by setting VSWRST bit to 1, then back to 0.

- 3. The application must perform specific actions for TAMP events if enabled (see Section 4: Boot and security control (BSEC) and Section 61: Real-time clock (RTC) ).

- 4. Re-initialize all components of the \( V_{SW} \) domain.

- 5. Lock registers by clearing DBP to 0 in PWR_DBPCR.

Case C

The application tries to reuse LSE when a failure is detected:

- 1. If the number of failures in a given time window is higher than a given threshold then go to case A or B. Otherwise, continue to next step.

- 2. Unlock registers by setting DBP to 1 in PWR_DBPCR.

- 3. Clear LSECSSF if interrupt was enabled for this event.

- 4. The application must perform specific actions for TAMP events if enabled (see Section 4: Boot and security control (BSEC) and Section 61: Real-time clock (RTC) ).

- 5. Clear LSECSSON to 0.

- 6. Rearm the LSECSS function by writing 1 to LSECSSRA, then back to 0.

- 7. Wait for LSERDY = 1. The LSERDY flag must go to 1 after the oscillator settling time delay plus, 4096 periods of LSE clock. If it is not the case, it probably means that the LSE failure is permanent. LSECSSON cannot be set to 1. It is recommended to execute case A or B.

- 8. Set LSECSSON to 1.

- 9. When LSECSSON = 1, the LSE is enabled, and protected by LSECSS.

- 10. Lock registers by clearing DBP to 0 in PWR_DBPCR.

14.6.4 Clock output generation (MCO1/MCO2)

There are two MCO1 and MCO2 microcontroller clock output pins. A clock source can be selected for each output. The selected clock can be divided thanks to a configurable prescaler (refer to Figure 38 for additional information on signal selection).

MCO1 and MCO2 are enabled using MCO1EN and MCO2EN in RCC_MISCENR.

The GPIO port corresponding to each MCO pin must be programmed in alternate function mode.

MCO1 and MCO2 are controlled via MCO1PRE[3:0], MCO1SEL[2:0], MCO2PRE[3:0], and MCO2SEL[2:0] located in RCC_CCIPR5.

MCO1PRE and MCO2PRE dividers provide a clock with a duty cycle of 50% for even divisions values, and around 53% for odd division values.

Note: MCO1 and MCO2 are available in Run, Stop, and Sleep modes.

Caution: The clock provided to the MCOx outputs must not exceed the maximum pin speed (refer to the product datasheet for information about the supported pin speed).

Table 69 shows the signals available on each MCO output.

Table 69. Clock output selection

| MCO1SEL | MCO2SEL | ||

|---|---|---|---|

| Position | Clock source | Position | Clock source |

| 0 | hsi_div_ck | 0 | hsi_div_ck |

| 1 | lse_ck | 1 | lse_ck |

| 2 | msi_ck | 2 | msi_ck |

| 3 | lsi_ck | 3 | lsi_ck |

| 4 | hse_ck | 4 | hse_ck |

| 5 | ic5_ck | 5 | ic15_ck |

| 6 | ic10_ck | 6 | ic20_ck |

| 7 | sysa_ck | 7 | sysb_ck |

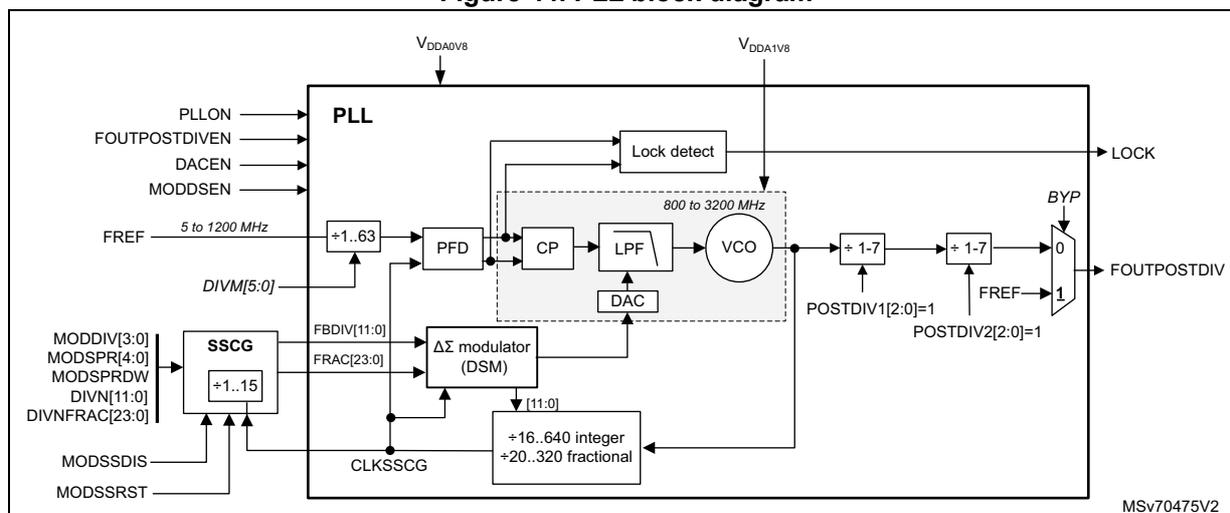

14.6.5 PLL description

The RCC features four PLLs with the same features.

A typical allocation is:

- • PLL1, clocks to the CPU, buses, and storage (XSPI, SDMMC)

- • PLL2, clocks to NPU and audio peripherals

- • PLL3, clocks to CACHEAXI RAM and Ethernet

- • PLL4, clocks to display, camera, FDCAN, and other peripherals

Each PLL has the following features:

- • FREF frequency range:

- – 5 to 1200 MHz in integer mode

- – 10 to 1200 MHz in fractional mode

- • VCO frequency range from 800 to 3200 MHz

- • Three working modes:

- – fractional mode, using a 24-bit delta-sigma modulator (DSM)

- – integer mode

- – spread spectrum mode to reduce EMI. The fully digital spread spectrum clock generator (SSCG) is used in that case.

The internal post-dividers (POSTDIV1, POSTDIV2) are powered-off by default. They must be powered-on when the PLL is in use (PLLxPDIVEN).

The active post-dividers (ICx) are outside the PLL design. Each post-divider has a 4-way multiplexer before it, which can select any PLL output as input.

The DIVMx divider in RCC_PLLxCFGR1 must be properly programmed to keep the PFD input frequency below 50 MHz.

Figure 44. PLL block diagram

graph LR

subgraph PLL_Block

FREF[FREF 5-1200 MHz] --> DIV1["+1..63"] --> PFD

PFD --> CP --> LPF --> VCO[VCO 800-3200 MHz]

VCO --> FB_DIV["+16..640 int / +20..320 frac"] --> PFD

VCO --> PD1["+ 1-7"] --> PD2["+ 1-7"] --> MUX

FREF --> MUX

MUX --> FOUTPOSTDIV

SSCG --> DIV2["+1..15"] --> PFD

DSM --> FB_DIV

DAC --> LPF

VCO --> LockDetect --> LOCK

end

The PLL is enabled by setting PLLxON to 1 in RCC_CR. PLLxRDY in RCC_SR indicates that the PLL is ready (locked).

The DIVNx loop divider must be programmed to achieve the expected VCO output frequency before enabling the PLL. Changing the value on-the-fly can result in a spike on the VCO output proportional to the PFD frequency step. A frequency step of more than 0.01% per PFD clock period must be avoided. The SSCG typically steps the frequency by less than 0.005% per PFD clock period, so does not generate spikes.

The VCO output range must be respected.

The clock from FOUTPOSTDIV has a 50% duty-cycle ( \( \pm 3\% \) ).

The ICx post-dividers provide clocks with 50% duty-cycle when dividing by an even value.

If an ICx post-divider enable is set to 0, its value can be changed without disabling any PLL.

The PLLs are disabled by hardware when the system enters Stop or Standby mode.

PLLs using HSE as reference clock are also disabled by hardware if an HSE failure is detected.

PLL programming recommendations

- • Before enabling the PLLs, the user must ensure that the reference frequency (FREF) provided to the PLL is stable and in the correct range.

- • POSTDIV1 and POSTDIV2 must be set to 1.

- • PLLxPDIVN must be set to 1 to output the clock FOUTPOSTDIV.

- • When a PLL output is used, PLLxON and PLLxRDY must be set to 1. The application can then set any connected post-divider enable bits to 1 (in RCC_DIVEN).

- • When a PLL output is not used, PLLxON must be cleared to 0. The application must also set any connected post-divider enable bits to 0 (in RCC_DIVEN).

Caution: The 4 MHz setting for the MSI oscillator cannot be used as FREF.

The PLLs can work in three different modes:

- • integer

- • fractional

- • spread spectrum

Using PLLs in integer mode

The PLLx works in integer mode when the delta-sigma modulator (DSM) is loaded with a 0 value, and PLLxMODSSDIS = 1.

To load 0 into the DSM and to set DIVN, use the following sequence:

- 1. Clear PLLxON to 0.

- 2. Set DIVN value (valid range 16 to 640).

- 3. Clear DIVNFRAC (in RCC_PLLxCFGR2) and PLLxMODDSEN to 0.

- 4. Set PLLxMODSSRST to 1.

- 5. Set PLLxON to 1.

Caution: Do not update DIVN after the PLL has been enabled.

The VCO frequency (F VCO ) and output frequency expressions are the following:

Using the PLLs in fractional mode

This mode is enabled when DSM ≠ 0, PLLxMODDSEN = 1, and PLLxMODSSDIS = 1.

To load the value into the DSM perform the following sequence:

- 1. Clear PLLxON to 0.

- 2. Set DIVN value (valid range 20 to 320).

- 3. Set DIVNFRAC (in RCC_PLLxCFGR2) to the required value, and set PLLxMODDSEN = DACEN 1.

- 4. Set PLLxMODSSRST to 1.

- 5. Set PLLxON to 1.

Caution:

Do not update DIVN and DIVNFRAC after the PLL has been enabled.

The minimum FREF is 10 MHz in fractional mode.

The VCO frequency ( \( F_{VCO} \) ) and output frequency expressions are the following:

Using PLLs in spread spectrum mode

The spread spectrum mode is activated when the DSM is loaded with 0, and PLLxMODSSDIS is cleared to 0. This feature is available for all PLLs.

The spread spectrum method is to modulate the VCO frequency with a low-frequency triangular signal, in order to spread the clock energy into a wider frequency band. The amount of emitted EMI is then reduced.

The spread spectrum modulation is adjusted using the following fields:

- • MODDIV[3:0] to adjust the modulation frequency

- • MODSPR[4:0] to adjust the modulation depth (or modulation index)

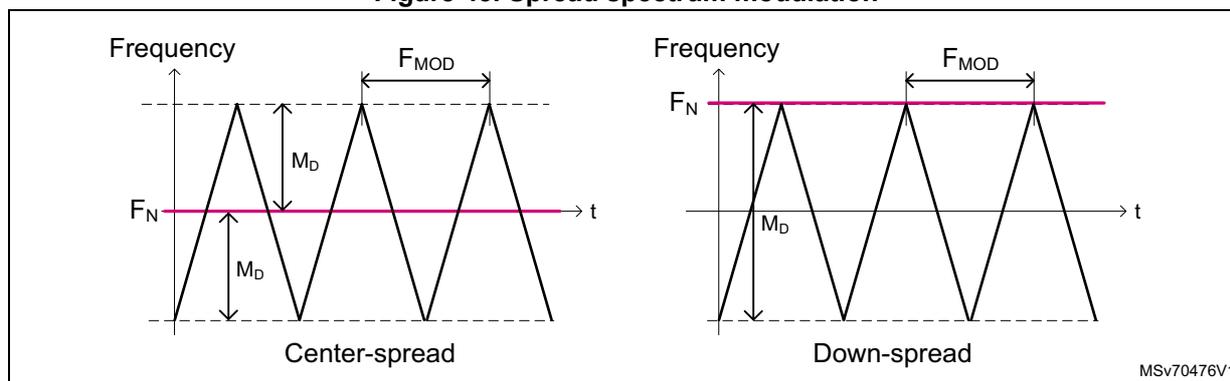

- • MODSPRDW to define if the modulation is centered around the VCO frequency (center-spread), or lowered with respect to VCO frequency (down-spread)

MODDIV[3:0], MODSPR[4:0] and MODSPRDW are in RCC_PLLxCFGR3.

Figure 45 shows the SSCG modulating the nominal frequency ( \( F_N \) ), when MODSPRDW = 0 (center-spread), and MODSPRDW = 1 (down-spread). The nominal frequency is that output by the PLL in integer mode, when no clock spreading is applied.

Down-spread guarantees that the PLL output frequency does not exceed the programmed frequency value when SSCG is enabled.

Figure 45. Spread spectrum modulation

The peak modulation depth (in percentage) is given by the formula \( M_D (\%) = \text{MODSPR} / 10 \) .

Note: Modulation is turned off when MODSPR = 0.

The modulation frequency ( \( F_{MOD} \) ) is given by:

where 128 is the number of points in the internal wave table.

Note: When the PLL is locked, \( F_{CLKSSCG} = F_{PFD} \) . The upper limit of the frequency of modulation ( \( F_{MOD} \) ) is set by the PLL bandwidth. The PLL bandwidth limits the maximum modulation to \( F_{CLKSSCG} / 200 \) , where \( F_{CLKSSCG} = F_{REF} / DIVM \) or 50 MHz, whichever is lower.

To use the spread spectrum feature, to do the following:

- 1. Program the PLL to the nominal frequency ( \( F_N \) ) using the \( F_{OUTPOSTDIV} \) formula from Using PLLs in integer mode

- 2. Compute the MODDIV value according to the desired modulation frequency ( \( F_{MOD} \) ):

- 3. Compute the MODSPR value according to the desired modulation depth ( \( M_D \) ).

- 4. Set the MODSPRDW value according to the desired modulation type (center-spread or down-spread).

- 5. Compute DIVN accordingly ( \( DIVNFRAC=0 \) ):

- 6. Clear PLLxMODSSDIS, PLLxMODDSEN, and DACEN to 0.

- 7. Set PLLxMODSSRST to 1, and clear PLLxON to 0. PLLxON must be held at 0 for 1 \( \mu\text{s} \) to make sure the PLL is fully reset.

- 8. Set PLLxON, PLLxMODDSEN, and DACEN to 1 (see Note: ).

- 9. Wait until the first edge of CLKSSCG, and then clear PLLxMODSSRST to 0 (this can be done before or after the PLL is locked).

Note: The spread spectrum accuracy relies on the PLL fractional-N capability, so MODDSEN and DACEN must be set to 1.

The user can check \( F_{MIN} \) , \( F_{MAX} \) as follows:

- • Calculate \( F_N \) as above.

- • If MODSPRDW = 0 (center-spread):

\( F_{MIN} = F_N \times (1 - M_D / 100) \) and \( F_{MAX} = F_N \times (1 + M_D / 100) \) - • If MODSPRDW = 1 (down-spread):

\( F_{MIN} = F_N \times (1 - M_D / 100) \) and \( F_{MAX} = F_N \)

Programming sequence for spread spectrum mode

The programming sequence to enable SSCG and the PLL is:

- 1. Deassert PLLxMODSSRST.

- 2. Set PLLxDIVN, PLLxDIVNFRAC, and PLLxMODSSDIS to 0.

- 3. Assert PLLxMODDSEN and PLLxDACEN.

- 4. Assert PLLxMODSSRST and deassert PLLxON.

- 5. PLLxON must be deasserted for 1µs to make sure PLL is fully reset. Then assert PLLxON.

- 6. Wait until PLLxRDY is asserted, then deassert PLLxMODSSRST.

14.6.6 System clocks

System clock selection

After a system reset, the HSI is selected as system clock (sys[a,b,c,d]_ck), and all PLLs are switched off.

The system clock can be stopped by hardware when the system enters Stop or Standby mode.

When the system runs, the user can select system clocks (sys[a,b,c,d]_ck) from the four following sources:

- • HSE

- • HSI

- • MSI

- • ic[1,2,6,11]_ck

This function is controlled by programming RCC_CFGR1. A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked). If a clock source that is not yet ready is selected, the switch occurs when the clock source is ready.

The SYSSW only selects the ic[2,6,11]_ck if all three IC dividers are enabled.

SWS bits in RCC_CFGR1 indicate which clock sources are currently selected. Other status bits in RCC_CR indicate which clock(s) is (are) ready.

System clock generation

Figure 46 shows a simplified view of the clock distribution for the CPU and buses. All the dividers shown in the block diagram can be changed on-the-fly, without generating timing violations. This feature is a very simple solution to adapt bus frequencies to application needs, thus optimizing the power consumption.

The AXI sys_bus_ck is divided by HPRE to generate the AHB clock. HPRE is controlled by RCC_CFGR2.

In addition to the divide values shown, PPRE1, PPRE2, PPRE4, and PPRE5 can divide by 32, 64, and 128.

There is almost no clock protection, so the software must avoid configurations that can block the system.

Note:

The application must respect the maximum allowed frequencies:

\(

F_{CPUmax}

\)

and

\(

F_{BUSmax}

\)

.

\(

F_{BUS}

\)

represents the maximum allowed frequency for AHB and AXI buses (refer to the datasheet for the maximum values).

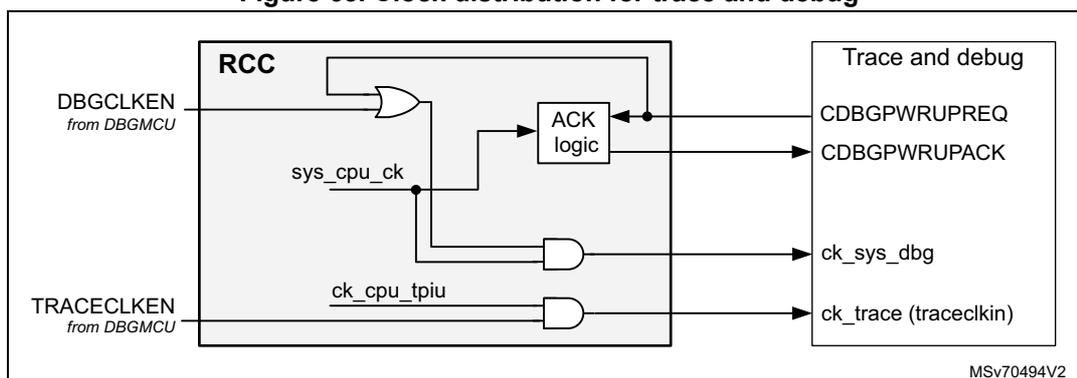

The trace clock (

ck_cpu_tpiu

) is generated from

sys_cpu_ck

clock, divided by eight. For additional information, refer to

Clock distribution for trace and debug

.

Figure 46. Core and bus clock generation

RCC

System clock generation (SCGU)

CPUSW

- hsi_ck → 0

- msi_ck → 1

- hse_ck → 2

- ic1_ck → 3

sysa_ck → sys_cpu_ck → [CT] → F CPUmax

F CPUmax paths:

- ÷ 8 → ck_cpu_tpiu (50% duty cycle)

- ÷ 8 → ck_cpu_systck (enable 1/8)

- ÷ 12 → ck_cpu_tsgen

- [CPU DEEP SLEEP] → [D] → ck_cpu_dbg

- ck_cpu

SYSSW

- hsi_ck → 0

- msi_ck → 1

- hse_ck → 2

- ic2_ck → 3

sysb_ck → sys_bus_ck → [CT] → F BUSmax

F BUSmax paths via SCEU (system cLock enabling):

- [CT] → [D] → aclkc → AXI CPU

- [CT] → aclks → AXI domain CPU/GPU

- [CT] → aclka → AXI domain cam/disp/VENC

- [CT] → aclkn → AXI domain NPU cache and TCM

- [CT] → [D] → CPU S-AHB (TCM)

- [CT] → TIMPRE → ÷ 1,2,4,8 → ck_timg1 → Timer group1

- ck_timg2 → Timer group2

- ck_bus2_dbg → System debug clock (dbg, dap)

- HPRE ÷ 1,2,4,8,16 → [CT] → hclk → AHBM main matrix

- hclk → hclk[5:0] → AHB0/1/2/3/4/5 peripheral clocks

- [D] → CPU P-AHB (peripheral bus)

- PPRE1 ÷ 1,2,4,8,16 → pclk1 → APB1 peripheral clocks

- PPRE2 ÷ 1,2,4,8,16 → pclk2 → APB2 peripheral clocks

- PPRE4 ÷ 1,2,4,8,16 → pclk4 → APB4 peripheral clocks

- PPRE5 ÷ 1,2,4,8,16 → pclk5 → APB5 peripheral clocks

- [CT] → hclku → USB/SDMMC peripheral clocks

- [CT] → hclke → Ethernet peripheral clocks

sysc_ck (from SYSCW) → sys_npu_ck → [CT] → NPU

sysd_ck (from SYSDW) → sys_npur_ck → [CT] → AXI domain NPU

AXISRAM3/4/5/6 clocks (close to NPU)

x Represents the selected value after a system reset.

D The switch is dynamic: the transition between two inputs is glitch-free.

CT Represents a cLock tree balancing, with an alignment of the downstream synchronous logic.

MSV70477V2

- 1. Dividers values can be changed on-the-fly. All dividers have 50% duty-cycles.

14.6.7 Clock generation in Stop and Standby modes

When the system enters Stop mode, all clocks (system and kernel) are stopped, and the following clock sources are disabled as well:

- • MSI, HSI

- • HSE

- • PLL1, PLL2, PLL3, PLL4

Note: The MSI and HSI stay active based on xxxSTOPEN bits in RCC_STOPCR.

HSIS is also disabled.

The content of the RCC registers is not altered, except CPUSW and SYSSW, forced to HSI or MSI (depending on STOPWUCK value), and PLLxON and HSEON, set to 0.

HSION and MSION are also modified, depending on STOPWUCK (see Table 70 ).

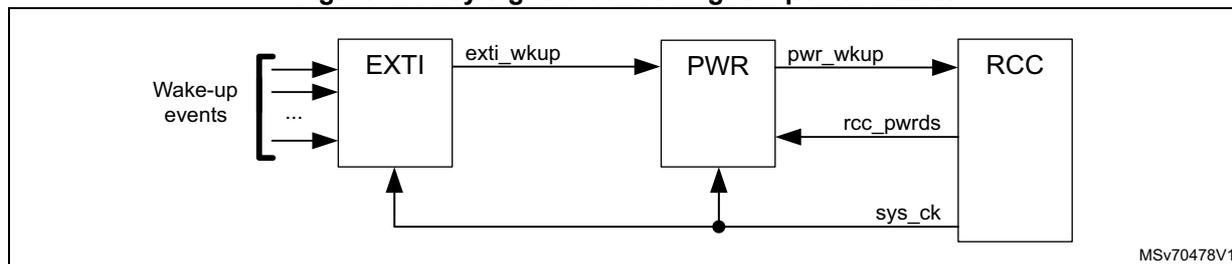

When the CPU requests to go in Stop mode, the RCC first stops all requested clocks, and informs the PWR that all clocks have been properly stopped. As shown in Figure 47 , three main signals are used to control power transitions:

- • rcc_pwrds: used to indicate to the PWR that the RCC stopped all clocks. The PWR can then go to Stop or Standby mode.

- • pwr_wkup is used to indicate to the RCC to re-enable the clocks.

- • The exti_wkup is used to indicate to the PWR that an event requests to exit the system from Stop mode.

Figure 47. Key signals controlling low-power modes

graph LR

WE[Wake-up events] --> EXTI[EXTI]

EXTI -- exti_wkup --> PWR[PWR]

PWR -- pwr_wkup --> RCC[RCC]

RCC -- rcc_pwrds --> PWR

SC((sys_ck)) --> EXTI

SC --> PWR

SC --> RCC

MSv70478V1

Exiting Stop mode

When the device exits system Stop mode via a wake-up event, HSIS is started automatically.

Note: sys_rst is only deasserted after HSIS has successfully started.

The application can select which other oscillator (HSI and/or MSI) is used to restart the system. STOPWUCK in RCC_CFGR1 selects the oscillator used as system clock. Table 70 describes their behavior.

Table 70. STOPWUCK description

| STOPWUCK | Activated oscillator when system exits Stop mode | Distributed clocks when system exits Stop mode | |

|---|---|---|---|

| System clock | Kernel clock | ||

| 0 | HSI | HSI | HSI |

| 1 | MSI | MSI | MSI |

During Stop mode

There are two specific cases where the HSI or MSI can be enabled during system Stop mode:

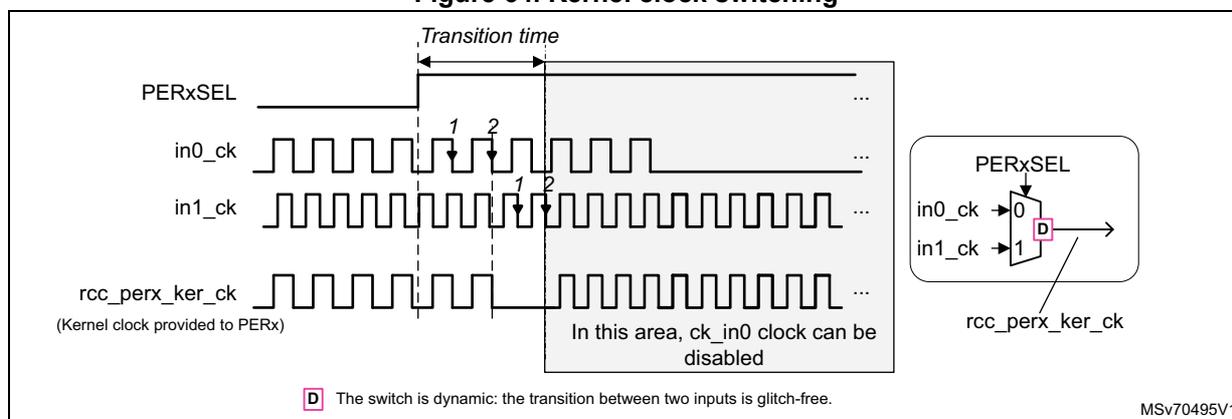

- • When a dedicated peripheral requests the kernel clock, the peripheral receives the HSI or MSI according to the kernel clock source selected for this peripheral (via PERxSEL).

- • When HSISTOPEN or MSISTOPEN are set in RCC_STOPCR, the HSI and MSI are kept running during Stop mode but the outputs are gated. The clock is then available immediately when the system exits Stop mode, or when a peripheral requests the kernel clock (see Table 71 for details).

Caution: HSI and MSI are always off in Stop mode when the PWR is set to SVOS low.

Table 71. HSISTOPEN and MSISTOPEN behavior

| HSISTOPEN (MSISTOPEN) | HSI (MSI) state during Stop mode | HSI (MSI) setting time |

|---|---|---|

| 0 | Off | \( t_{su(HSI)} \) ( \( t_{su(MSI)} \) ) (1) |

| 1 | Running and gated | Immediate |

1. \( t_{su(HSI)} \) and \( t_{su(MSI)} \) are the startup times of the HSI and MSI oscillators (see the datasheet for their values).

When the microcontroller exits Standby mode, the HSI is selected as system and kernel clock. RCC registers are reset to their initial values except for the backup domain configurations (LSE in RCC_CR/RCC_LSECFG, RTC in RCC_CCIPR7, RCC_BDCR), and the reset cause (RCC_RSR, RCC_HWRCSR).

Caution: When leaving Stop mode without reset (but not from Standby mode), the RCC returns in the same state as before, except for the software that has been forced to select the STOPWUCK source. When leaving Standby mode, the application can restore previous CPU clock settings, if needed.

Caution: If the system clock switch selection (SYSSW) is HSI or MSI oscillator, STOPWUCK (system clock selection after a wake-up from system Stop) must select the same oscillator.

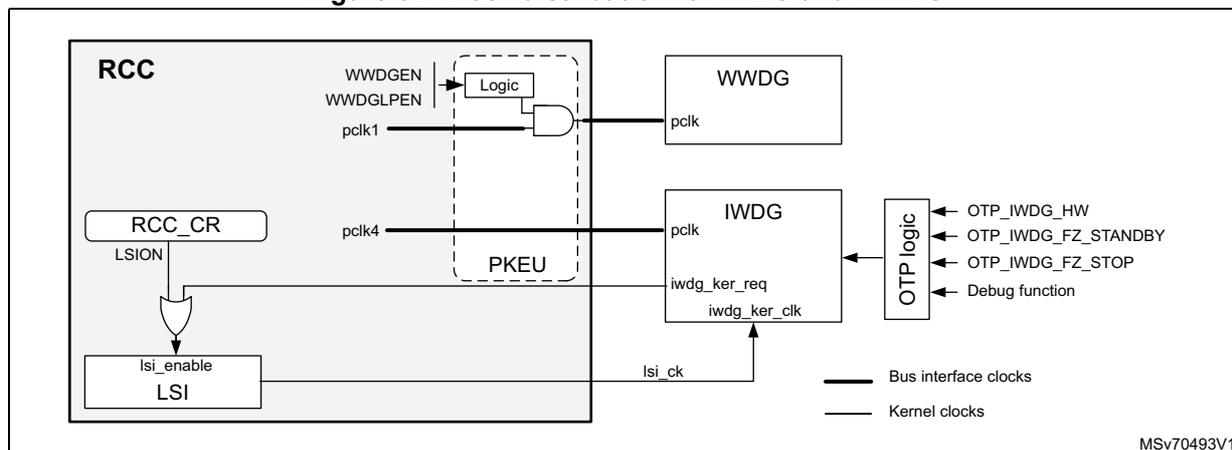

14.6.8 Peripheral clock distribution

Some peripherals are designed to work with two different clock domains, operating asynchronously:

- • a domain synchronous with the register and bus interface (ckg_bus_perx clock)

- • a domain generally synchronous with the peripheral (kernel clock)

Other peripherals only need a bus interface clock, hence the user application has more freedom to choose an optimized clock frequency for the CPU, bus matrix, and for the kernel part of the peripheral. The user can change the bus frequency without reprogramming peripherals (example: an ongoing transfer with UART is not disturbed if its APB clock is changed on-the-fly).

Table 72 summarizes the clocks from RCC to the peripherals. The clock named per_ck is the output of a mux (see Figure 38 ).

Table 72. Peripheral clock distribution summary

| Peripherals | Clock | Kernel clock MUX | Max kernel clock frequency (in MHz) | Type (1)(2) | ||

|---|---|---|---|---|---|---|

| Type | Source | Position | Control field | |||

| ADF1 | Kernel | hclk2 | 0 (3) | ADF1SEL | 200 | A |

| per_ck | 1 | |||||

| ic7_ck | 2 | |||||

| ic8_ck | 3 | |||||

| msi_ck | 4 | |||||

| hsi_div_ck | 5 | |||||

| I2S_CKIN | 6 | |||||

| timg_ck | 7 | |||||

| Bus | hclk2 | - | - | 200 | - | |

| ADC12 | Kernel | hclk1 | 0 (3) | ADC12SEL | 125 | A |

| per_ck | 1 | |||||

| ic7_ck | 2 | |||||

| ic8_ck | 3 | |||||

| msi_ck | 4 | |||||

| hsi_div_ck | 5 | |||||

| I2S_CKIN | 6 | |||||

| timg_ck | 7 | |||||

| Bus | hclk1 | - | - | 200 | - | |

| CACHEAXI | Bus | sys_bus_ck | - | - | 400 | - |

| hclk5 | - | - | 200 | - | ||

| CRC | Bus | hclk4 | - | - | 200 | - |

| CRYP | Bus | hclk3 | - | - | 200 | - |

| DBG | Kernel | sys_cpu_ck | - | - | 800 | A |

| Bus | ck_bus2_dbg | - | - | 200 | - | |

| DTS | Kernel | hsi_div8_ck | - | - | 10 | A |

| Bus | pclk4 | - | - | 100 | - | |

| CSI | Kernel | As DCMIPP | - | DCMIPPSEL | - | A |

| Bus | pclk5 | - | - | 200 | - | |

| CSIPHY | Kernel | ic18_ck | - | - | 20 | A |

| Bus | pclk5 | - | - | 200 | - | |

Table 72. Peripheral clock distribution summary (continued)

| Peripherals | Clock | Kernel clock MUX | Max kernel clock frequency (in MHz) | Type (1)(2) | ||

|---|---|---|---|---|---|---|

| Type | Source | Position | Control field | |||

| DCMIPP | Kernel | pclk5 | 0 | DCMIPPSEL | 333 | A |

| per_ck | 1 | |||||

| ic17_ck | 2 | |||||

| hsi_div_ck | 3 | |||||

| Bus | sys_busa_ck | - | - | 400 | - | |

| pclk5 | - | - | 200 | - | ||

| GPDMA1 | Bus | hclk1 | - | - | 200 | - |

| HPDMA1 | Bus | hclk5 | - | - | 200 | - |

| DMA2D | Bus | hclk5 | - | - | 200 | - |

| aclk | ||||||

| DTS | Kernel | hsi_div8_ck | - | - | 10 | A |

| Bus | pclk4 | - | - | 200 | - | |

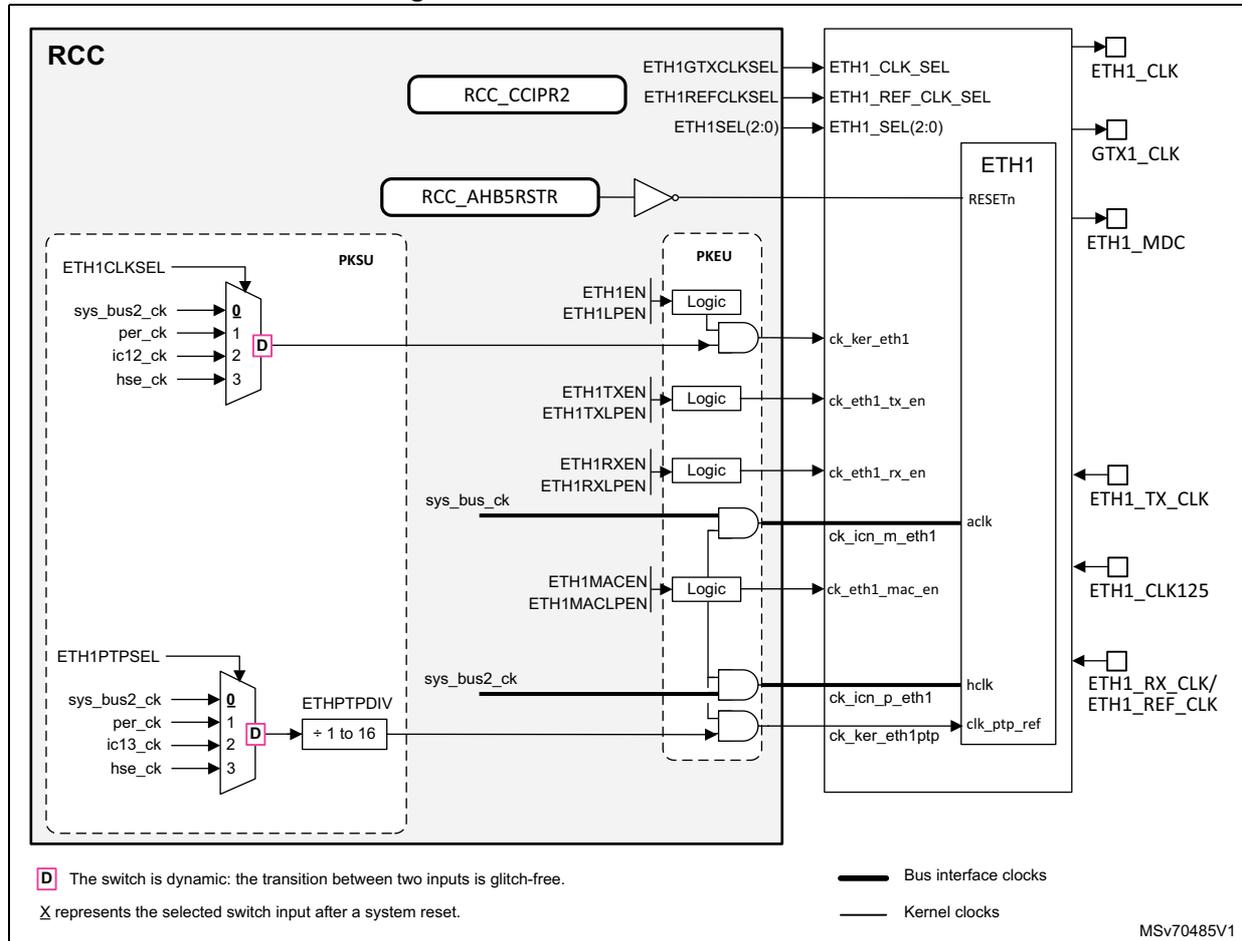

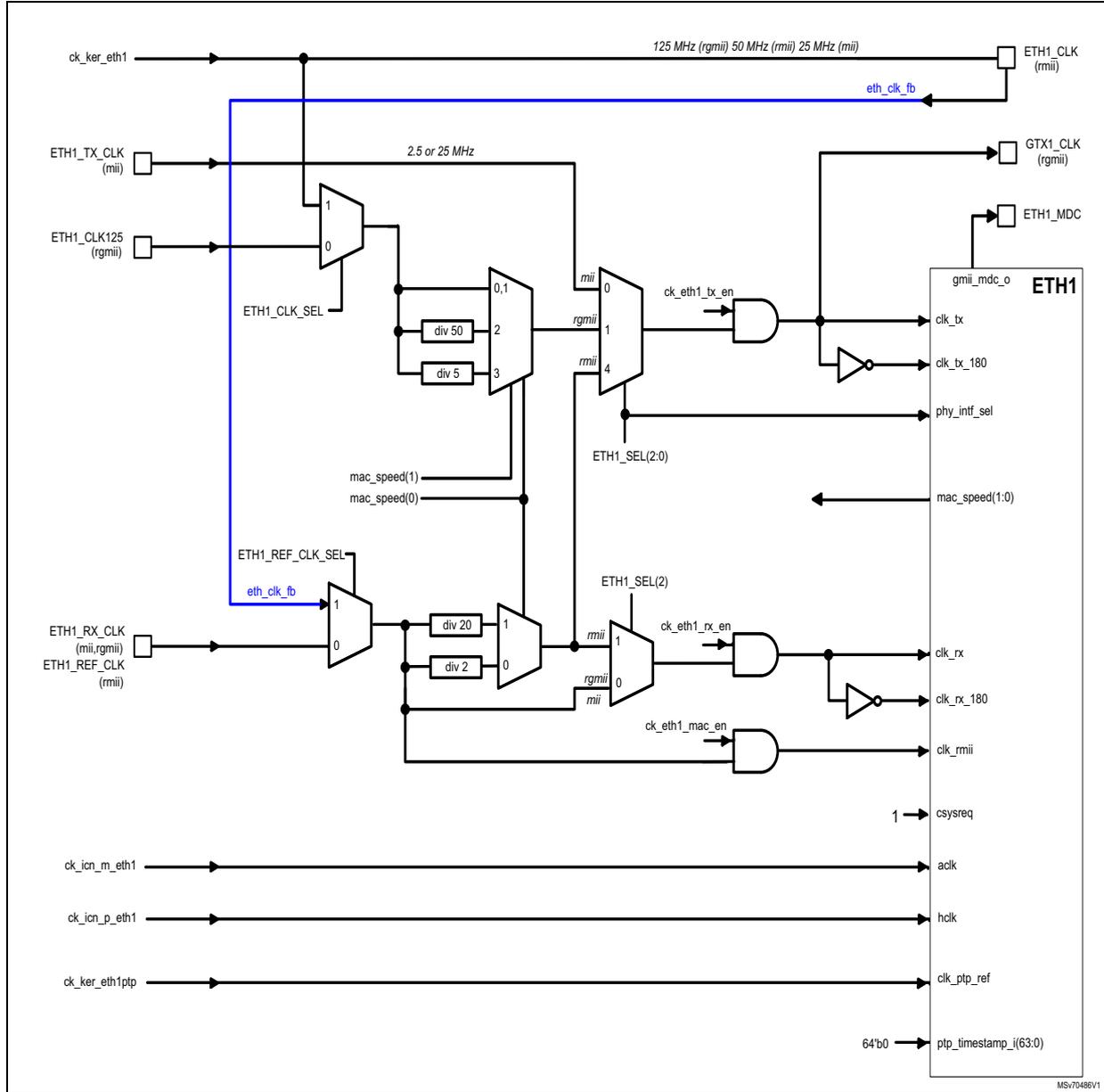

| ETH1 | Kernel | ETH1_TX_CLK | - | - | 25 | A |

| ETH1_RX_CLK/ETH1_REF_CLK | 0 (3) | ETH1REFCLKSEL | 125 | A | ||

| eth1_clk_fb | 1 | |||||

| sys_bus2_ck | 0 (3) | ETH1CLKSEL | 125 | A | ||

| per_ck | 1 | |||||

| ic12_ck | 2 | |||||

| hse_ck | 3 | |||||

| sys_bus2_ck | 0 | ETH1PTPSEL | 200 | A | ||

| per_ck | 1 | |||||

| ic13_ck | 2 | |||||

| hse_ck | 3 | |||||

| Bus | hclk1 | - | - | 200 | - | |

| EXTI | Bus | pclk4 | - | - | 125 | - |

| FDCAN | Kernel | pclk1 | 0 (3) | FDCANSEL | 150 | A |

| per_ck | 1 | |||||

| ic19_ck | 2 | |||||

| hse_ck | 3 | |||||

| Bus | pclk1 | - | - | 200 | - | |

Table 72. Peripheral clock distribution summary (continued)

| Peripherals | Clock | Kernel clock MUX | Max kernel clock frequency (in MHz) | Type (1)(2) | ||

|---|---|---|---|---|---|---|

| Type | Source | Position | Control field | |||

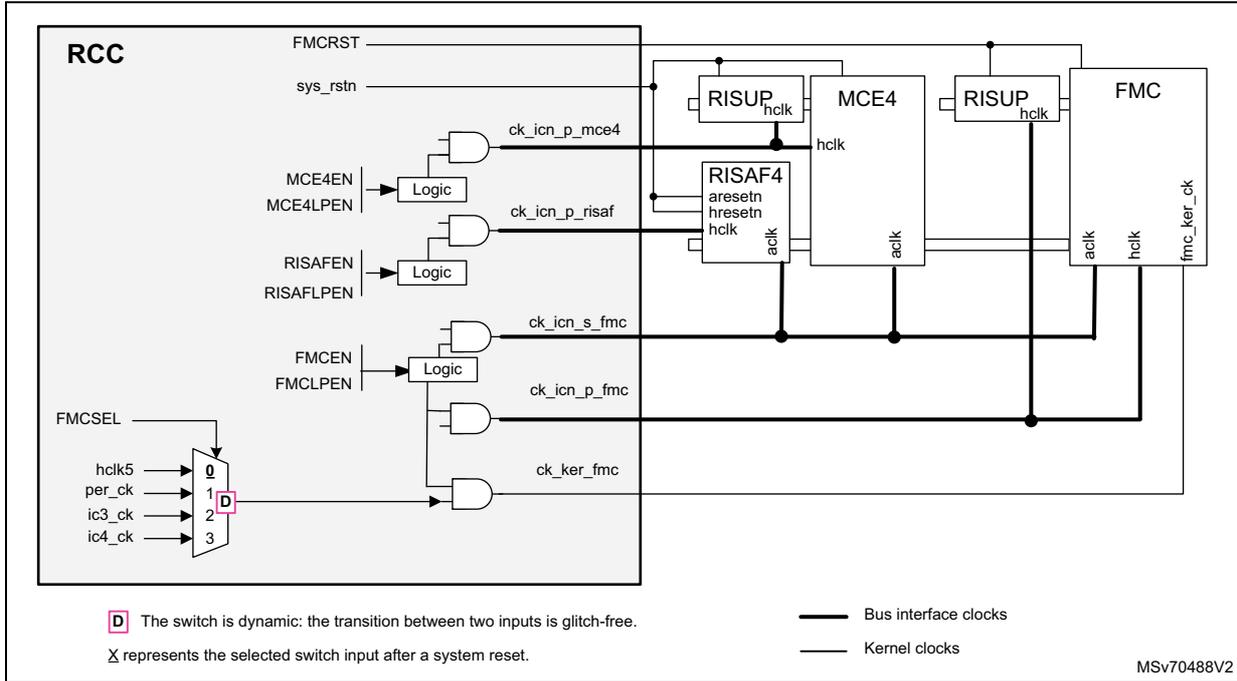

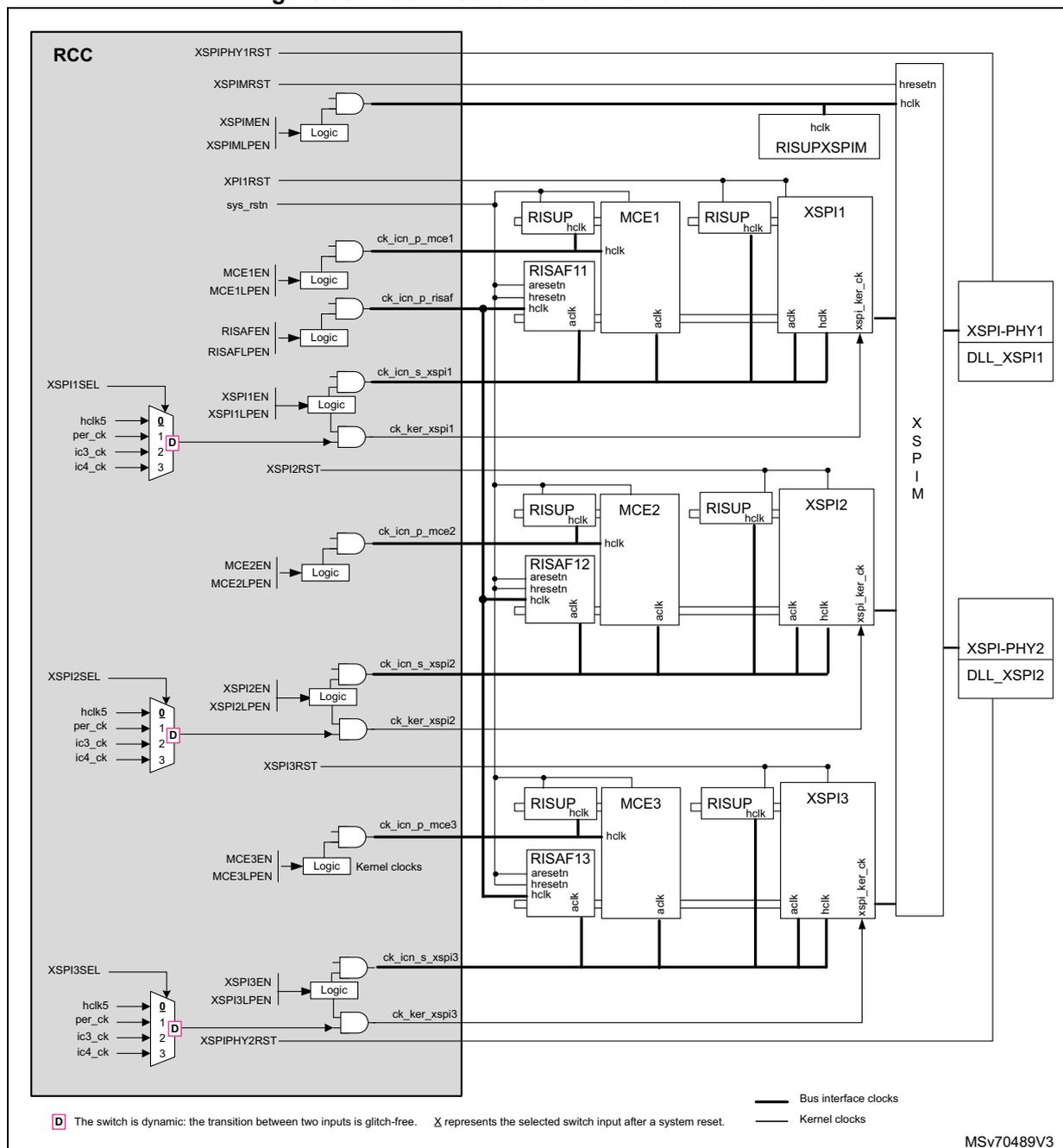

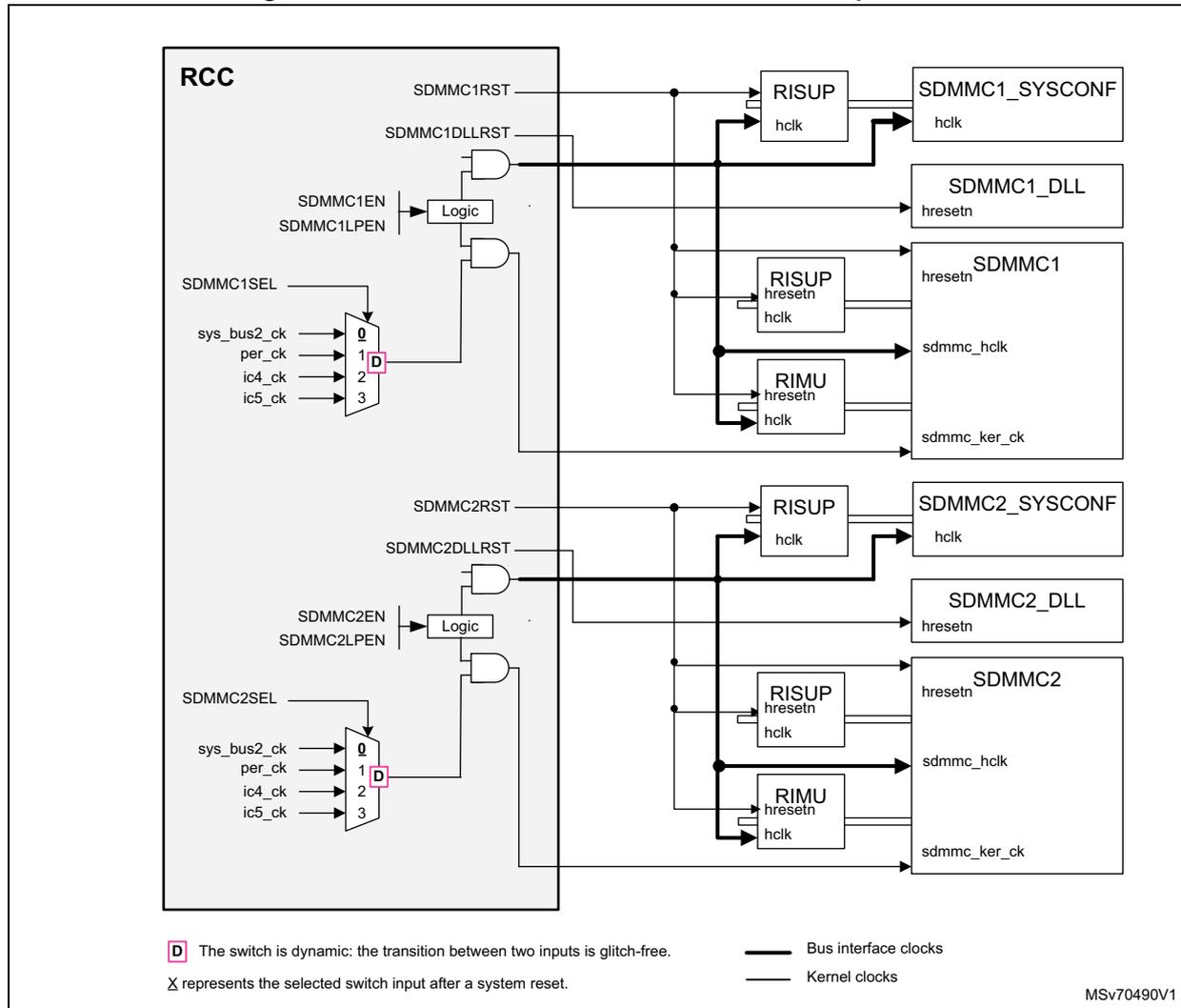

| FMC | Kernel | hclk5 | 0 (3) | FMCSEL | 200 | A |

| per_ck | 1 | |||||

| ic3_ck | 2 | |||||

| ic4_ck | 3 | |||||

| Bus | sys_buss_ck | - | - | 400 | - | |

| hclk5 | - | |||||

| GPIOA-H, GPION-Q | Bus | hclk4 | - | - | 200 | - |

| GPU2D | Bus | sys_buss_ck | - | - | 400 | - |

| GFXMMU | Bus | sys_buss_ck | - | - | 400 | - |

| hclk5 | ||||||