2. Memory and bus architecture

2.1 System architecture

2.1.1 Introduction

The STM32N6x5 and STM32N6x7 device architecture relies on an Arm Cortex-M55 core optimized for execution:

- • Main masters:

- – Cortex-M55 with Arm TrustZone mainline with two master ports:

- > M-AXI provides access to the memory and to peripherals

- > P-AHB provides access to peripherals

- – NPU (neural processor unit), which includes two master AXI ports (STM32N6x7 devices only)

- – Cortex-M55 with Arm TrustZone mainline with two master ports:

- • Memories:

- – AHB and APB peripherals

- – 4.2 Mbytes of SRAM

- – 64 Kbytes I-TCM RAM with ECC for critical real-time routines, and 128 Kbytes of D-TCM RAM with ECC for critical real-time data

- – 8 Kbytes of backup SRAM (BKPSRAM) active in \( V_{BAT} \) mode

- – 2 x 16-Kbyte AHB RAMs

- – Flexible external memory controller (FLEXMEM) with cypher engine supporting up to 32-bit data bus: SRAM, PSRAM, SDRAM, LPSDR SDRAM, NOR/NAND flash memories

- – XSPIM port2 8-bit configuration with cypher engine

- – XSPIM port1 16-bit configuration with cypher engine

2.1.2 Bus architecture

The bus architecture is divided in two domains, high- and low-performance (see Figure 1 and Figure 2 ).

High-speed, multi-frequency domain, AXI compliant interconnect

This high-performance interconnect is mainly used by the CPU, the NPU (STM32N6x7 devices only), and by the high-bandwidth masters (GPU, DMA2D, GFXMMU, VENC, DCMIPP, LTDC, ETH1, OTG1/2, SDMMC1/2, HPDMA1 AXI port).

This domain manages accesses to:

- • external flash memories and SRAMs (through the FMC and the XSPI manager)

- • main system internal memories AXISRAM1/2/3/4/5/6, boot ROM, VENCRAM (when the VENC is off), and CACHEAXI RAM (STM32N6x7 devices when NPU is off) or SRAM7 (STM32N6x5 devices)

- • the CPU internal memory (TCM) when accessed by the HPDMA1 AXI and the NPU

Note: The CPU has internally access to the TCM. - • the GFXMMU

- • the STM (system trace macrocell)

The CPU uses its M-AXI master port to access the above-described targets.

The NPU uses a local interconnect (NPU_NIC) to have a direct access to AXISRAM3/4/5/6 and to the CPU TCM. This results in a high-performance and low-latency bus when accessing these targets.

In addition, data interleaving can be enabled on AXISRAM3/4/5/6 to balance the traffic and to improve access performance.

The CPU and high-bandwidth masters use another local interconnect called CPU_NOC to have high-performance access on AXISRAM1/2 and external flash memories.

Note: The boot ROM is accessible only by the CPU through an intermediate interconnect called CPU_NIC.

Multi-layer AHB interconnect

This interconnect is used to access AHBSRAM1/2, BKPSRAM, and peripherals.

The CPU can reach peripherals mapped in the peripheral region (address range from 0x4000 0000 to 0x5FFF FFFF), using the following masters ports:

- • the CPU P-AHB master port for data accesses

- • the CPU M-AXI master port for instruction accesses

When P-AHB is disabled, data accesses are performed on M-AXI.

The CPU accesses AHBSRAM1/2 and BKPSRAM through its M-AXI master port. The CPU memory accesses start on the high-performance interconnect before reaching the AHB interconnect.

GPDMA1 and HPDMA1 AHB ports are the other masters on this interconnect.

The GPDMA1_P has a dedicated access to APB1/2/4 peripherals.

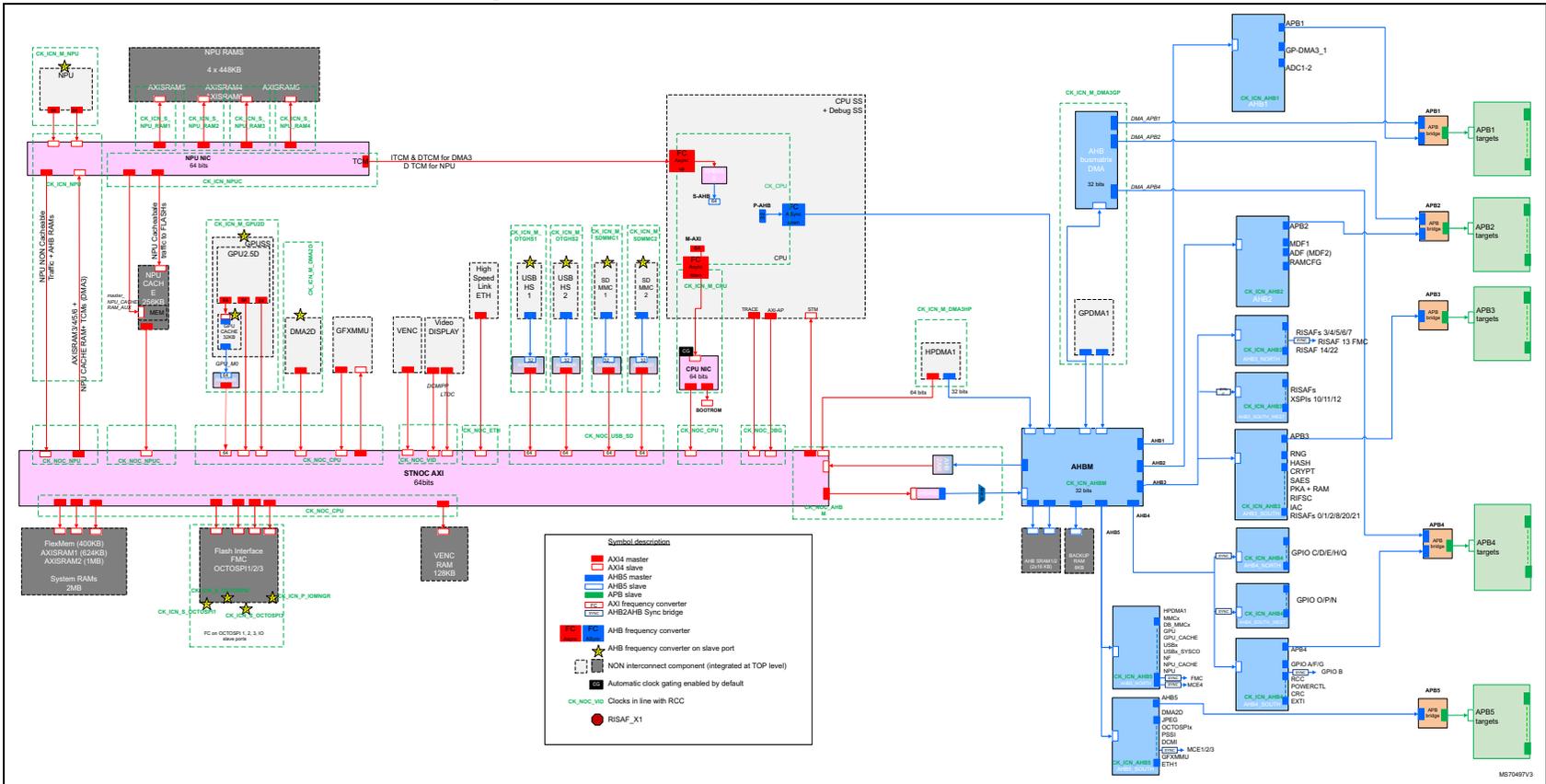

Figure 1. Interconnect top view - STM32N6x7 devices

The diagram illustrates the interconnect architecture for STM32N6x7 devices, divided into two main domains: the high-performance domain (highlighted in pink) and the low-performance domain (highlighted in blue).

- High-Performance Domain (Pink):

- Contains the CPU (Cortex-A55) and its associated memory (NPU RAMs, AXISRAMs).

- Includes the NPU (Neural Processing Unit) and its cache (NPU CACHE).

- Features the GPU (GPU2D) and its associated memory (GPU RAMs).

- Contains the DMA2D and GFXMMU blocks.

- Includes the VENC (Video Encoder) and VIDEO DISPLAY blocks.

- Features the Right Speed Link (ETH) block.

- Contains the USB HS 1 and USB HS 2 blocks.

- Includes the SD MMC 1 and SD MMC 2 blocks.

- Features the CPU NC 64 bits block.

- Contains the STM32CAXI 64bits block.

- Includes the Flash Interface FMC (OCTOSPI1/2/3) block.

- Contains the VENC RAM (256KB) block.

- Low-Performance Domain (Blue):

- Contains the AHBM (AHB Bridge) block, which acts as a bridge between the two domains.

- Includes the APB1, APB2, APB3, APB4, and APB5 bridges.

- Features various APB targets: APB1 targets, APB2 targets, APB3 targets, APB4 targets, and APB5 targets.

- Contains the RISAFs (RISAF 34/56/7, RISAF 15 FMC, RISAF 14/22, RISAFs XSPIs 10/11/12) blocks.

- Includes the RNG, HASH, CRYPT, SAES, PKA, RAM, RIFSC, IAC, and RISAFs 0/1/2/8/20/21 blocks.

- Features the GPIO O/E/H/Q and GPIO O/P/N blocks.

- Contains the GPIO AF/FG, RCC, POWERCTL, CRC, and EXTI blocks.

- Includes the DMA2D, OCTOSPIx, PPI, DOM, MCF1/3, GP2XAMU, and ET11 blocks.

A legend titled "Symbol description" is provided at the bottom center of the diagram, defining the symbols used for AXI4 master, AXI4 slave, AHB5 master, AHB5 slave, APB slave, AXI frequency converter, AHB2AHB Sync bridge, AHB frequency converter, AHB frequency converter on slave port, NON interconnect component (integrated at TOP level), Automatic clock gating enabled by default, and RISAF_X1.

- 1. The high-performance domain is shown in pink. The low-performance domain is shown in blue.

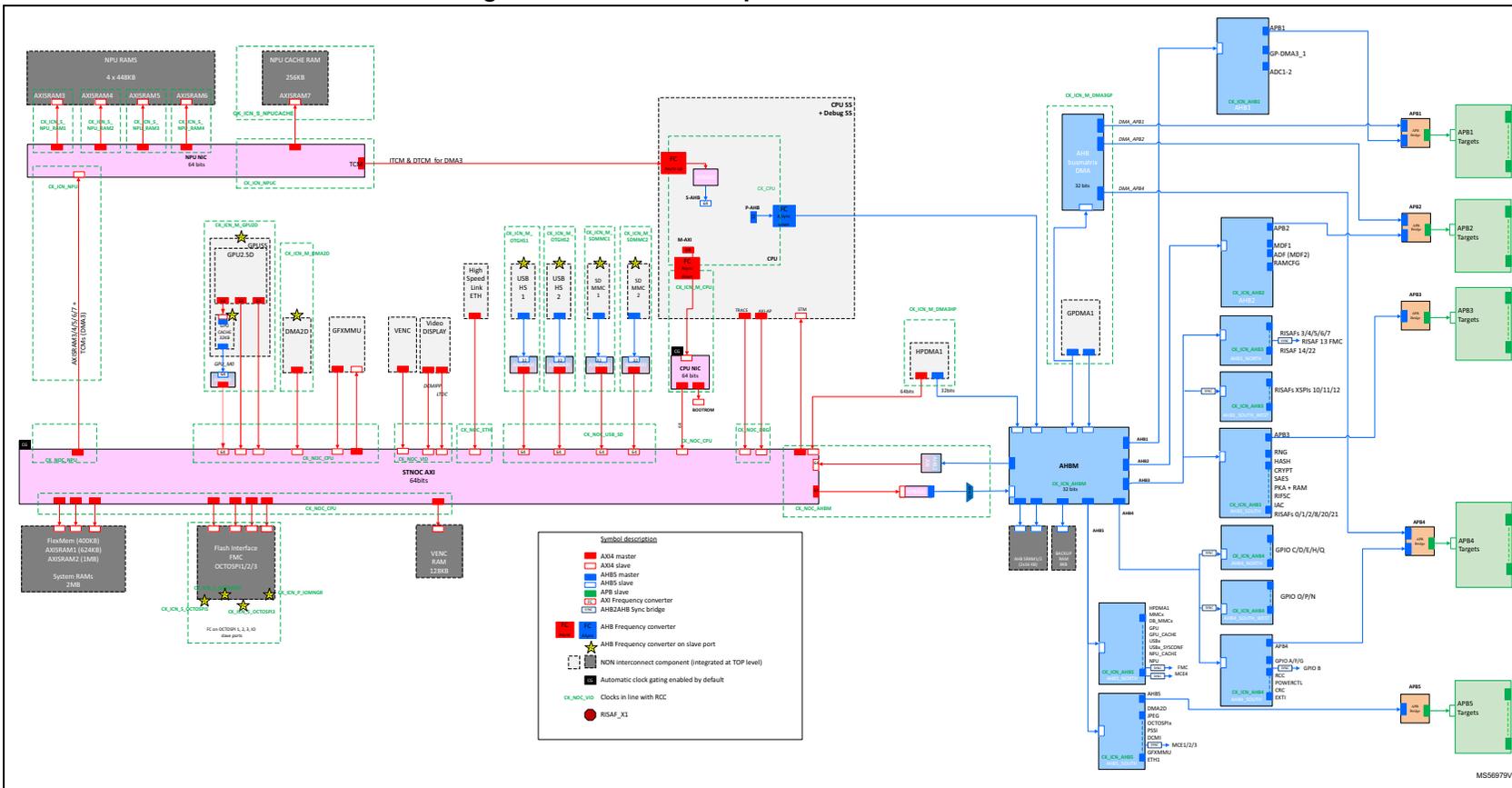

Figure 2. Interconnect top view - STM32N6x5 devices

The diagram illustrates the interconnect architecture for STM32N6x5 devices, divided into two main domains:

- High-performance domain (pink):

- Contains the CPU (Cortex-A55 + Debug SS).

- Connected to NPU RAMs (4 x 44KB) via AXI4-Stream interfaces.

- Connected to NPU Cache RAM (256KB) via AXI4-Stream interfaces.

- Connected to System RAMs (4096B AXISRAM1, 1024B AXISRAM2, 1MB) via AXI4-Stream interfaces.

- Connected to Flash Interface FMC (OCTOSPI1/2/3) via AXI4-Stream interfaces.

- Connected to VENC RAM (128KB) via AXI4-Stream interfaces.

- Contains various

peripherals

including:

- GPU2.5D, DMA2D, GFXMMU, VENC, VIDEO DISPLAY, and High Speed Link ETH.

- Four USB HS 1, USB HS 2, USB HS 3, and USB HS 4 interfaces.

- Four I2C interfaces (I2C1, I2C2, I2C3, I2C4).

- Four SPI interfaces (SPI1, SPI2, SPI3, SPI4).

- Four UART interfaces (UART1, UART2, UART3, UART4).

- Four CAN interfaces (CAN1, CAN2, CAN3, CAN4).

- Four LIN interfaces (LIN1, LIN2, LIN3, LIN4).

- Four RS485 interfaces (RS485-1, RS485-2, RS485-3, RS485-4).

- Low-performance domain (blue):

- Contains the AHB (Advanced High-performance Bus) bridge.

- Connected to the high-performance domain via the AHB bridge.

- Contains various

peripherals

including:

- ADC1, ADC2, and ADC3.

- CRS (Clock Recovery System).

- DFM (Device File Memory).

- GPIOs (GPIOA, GPIOB, GPIOC, GPIOD, GPIOE, GPIOF, GPIOG, GPIOH, GPIOI, GPIOJ, GPIOK, GPIOL, GPIOM, GPION, GPIOO, GPIOQ, GPIOV, GPIOX, GPIOY, GPIOZ).

- I2C (Inter-Integrated Circuit) interfaces.

- MDF1 (Memory Data File).

- RNG (Random Number Generator).

- RSAF (RSA Accelerator) interfaces.

- SAI (Serial Audio Interface) interfaces.

- SDMMC1 and SDMMC2 (Secure Digital MultiMediaCard) interfaces.

- USART1, USART2, USART3, and USART6 (Universal Synchronous Asynchronous Receiver Transmitter) interfaces.

- WWDG (Window Watchdog) interface.

Symbol description:

- Red square: DSI4 master

- Red rectangle: AXI4 slave

- Blue square: AHB master

- Blue rectangle: AXI4 slave

- Green rectangle: APB slave

- Green rectangle with star: AXI frequency converter

- Green rectangle with star and dashed border: AHB/APB Sync bridge

- Red rectangle with star: AXI frequency converter

- Blue rectangle with star: AXI frequency converter on slave port

- Yellow star: AXI frequency converter on slave port

- Dashed rectangle: NON interconnect component (integrated at TOP level)

- Black rectangle: Automatic clock gating enabled by default

- Green rectangle with star: Clocks in line with RCC

- Red circle: RS485_x1

1. The high-performance domain is shown in pink. The low-performance domain is shown in blue.

2.2 Bus network-on-chip (NoC)

2.2.1 STNoC AXI

The STNoC AXI interconnect is built out of the ST in-house network-on-chip. Its main features are:

- • Source routed, packet based, wormhole switching forwarding scheme for simultaneous and parallel/pipelined accesses from master to slave

- • Independent read and write input/output points to cope with AXI independent channels

- • Size and frequency conversion, asynchronism management

- • Fine grain automatic clock gating shutting down the clocks to unused network parts at any point in time, with zero delay clock resume

- • Internal packets buffering for improved traffic efficiency

- • Independent request and response network

- • Software accessible registers to observe and report traffic statistics, performance, blocking sources (if any) over the network.

2.2.2 NPU_NIC network interconnect

The NPU_NIC interconnect is based on Arm NIC-400 Network Interconnect. Its main features are:

- • High-performance and low-latency interconnect

- • Independent read/write request/response channel as defined in AXI protocol

- • Asynchronism management

- • Address interleaving to AXISRAM3/4/5/6/7 (can be disabled by software)

- • CACHEAXI / SRAM7:

- – for STM32N6x7, when CACHEAXI is disabled, 256 KB SRAM7 can be accessible

- – for STM32N6x5, no CACHEAXI feature, only 256 KB accessible

- • Static QoS assigned by software used at any arbitration node. The highest value has the highest priority. Arbitration with same QoS value uses an LRU (least recently used) algorithm.

2.2.3 Multi-layer AHB interconnect (AHBM)

The multi-layer AHB main features are:

- • 32-bit bus matrix running at 200 MHz using a master clock from the RCC

- • Simultaneous accesses from different masters to the slaves connected to separated layers

- • Five master ports: CPU P-AHB, HPDMA1, GPDMA1_P /M, and CPU_NOC

- • Nine slave ports: memories (AHB SRAM1/2 and BKPSRAM), peripherals for AHBx/APBx targets, and CPU_NOC target to reach AXI.

Note: The GPDMA1_P has a direct path to APB1, APB2, and APB4 targets. It bypasses this multi-layer AHB.

2.3 Memory organization

2.3.1 Introduction

Program memory, data memory, registers and I/O ports are organized within the same linear 4-Gbyte address space.

The bytes are coded in memory in Little Endian format. The lowest numbered byte in a word is considered the word's least significant byte and the highest numbered byte the most significant.

2.3.2 Memory map and register boundary addresses

Program memory, data memory, registers, and I/O ports are organized within the same linear 4-Gbyte address space.

The bytes are coded in memory in little-endian format. The lowest numbered byte in a word is considered the word least significant byte, and the highest numbered byte the most significant.

All memory map areas that are not allocated to on-chip memories and peripherals are considered reserved.

The IDAU mapping indicates if a particular memory address is secure or nonsecure.

Table 1. Memory map based on IDAU mapping

| IDAU security type | Mapping | Description |

|---|---|---|

| - | 0xFFFFFFFF | Reserved |

| - | 0xE0100000 | Reserved |

| Cortex-M55 nonsecure | 0xE0000000 | Cortex-M55 internal peripherals, debug and trace |

| SDRAM nonsecure | 0xD0000000 | SDRAM 2 |

| 0xC0000000 | SDRAM 1 | |

| - | 0xA0000000 | Reserved |

| XSPI bank nonsecure | 0x90000000 | XSPI1 |

| 0x80000000 | XSPI3 | |

| 0x70000000 | XSPI2 | |

| SDRAM nonsecure | 0x60000000 | FMC NOR/SRAM |

Table 1. Memory map based on IDAU mapping (continued)

| IDAU security type | Mapping | Description |

|---|---|---|

| Reserved peripheral secure | 0x5E000000 | Trace and debug |

| 0x58120000 | Reserved | |

| 0x58020000 | AHB5 peripherals | |

| 0x58010000 | Reserved for APB | |

| 0x58000000 | APB5 peripherals | |

| 0x56030000 | Reserved | |

| 0x56020000 | AHB4 peripherals | |

| 0x56010000 | Reserved for APB | |

| 0x56000000 | APB4 peripherals | |

| 0x54040000 | Reserved | |

| 0x54020000 | AHB3 peripherals | |

| 0x54010000 | Reserved for APB | |

| 0x54000000 | APB3 peripherals | |

| 0x52040000 | Reserved | |

| 0x52020000 | AHB2 peripherals | |

| 0x52010000 | Reserved for APB | |

| 0x52000000 | APB2 peripherals | |

| 0x50188000 | Reserved | |

| 0x50020000 | AHB1 peripherals | |

| 0x50010000 | Reserved | |

| 0x50000000 | APB1 peripherals |

Table 1. Memory map based on IDAU mapping (continued)

| IDAU security type | Mapping | Description |

|---|---|---|

| Peripheral nonsecure | 0x4E000000 | Trace and debug |

| 0x48120000 | Reserved | |

| 0x48020000 | AHB5 peripherals | |

| 0x48010000 | Reserved for APB | |

| 0x48000000 | APB5 peripherals | |

| 0x46030000 | Reserved | |

| 0x46020000 | AHB4 peripherals | |

| 0x46010000 | Reserved for APB | |

| 0x46000000 | APB4 peripherals | |

| 0x44040000 | Reserved | |

| 0x44020000 | AHB3 peripherals | |

| 0x44010000 | Reserved for APB | |

| 0x44000000 | APB3 peripherals | |

| 0x42040000 | Reserved | |

| 0x42020000 | AHB2 peripherals | |

| 0x42010000 | Reserved for APB | |

| 0x42000000 | APB2 peripherals | |

| 0x40188000 | Reserved | |

| 0x40020000 | AHB1 peripherals | |

| 0x40010000 | Reserved | |

| 0x40000000 | APB1 peripherals | |

| Reserved SRAM/AXI bank secure | 0x3C002000 | Reserved |

| 0x3C000000 | Backup SRAM (8 Kbytes) | |

| 0x38008000 | Reserved | |

| 0x38004000 | AHBSRAM2 | |

| 0x38000000 | AHBSRAM1 | |

| 0x37F00000 | STM500 channels (system trace) | |

| 0x37EFF000 | FMC-NAND | |

| 0x36000000 | Reserved | |

| 0x35000000 | GFXMMU SLV | |

| 0x34420000 | Reserved | |

| 0x34400000 | VENCRAM/AXISRAM8 | |

| 0x343C0000 | CACHEAXI/AXISRAM7 | |

| 0x34350000 | AXISRAM6 | |

| 0x342E0000 | AXISRAM5 |

Table 1. Memory map based on IDAU mapping (continued)

| IDAU security type | Mapping | Description |

|---|---|---|

| Reserved SRAM/AXI bank secure | 0x34270000 | AXISRAM4 |

| 0x34200000 | AXISRAM3 | |

| 0x34100000 | AXISRAM2 | |

| 0x34064000 | AXISRAM1 | |

| Data secure | 0x34000000 | FLEXRAM |

| 0x30040000 | Reserved | |

| 0x30000000 | DTCM - Baseline | |

| SRAM/AXI bank nonsecure | 0x2C002000 | Reserved |

| 0x2C000000 | Backup SRAM (8 Kbytes) | |

| 0x28008000 | Reserved | |

| 0x28004000 | AHBSRAM2 | |

| 0x28000000 | AHBSRAM1 | |

| 0x27F00000 | STM500 channels (system trace) | |

| 0x27EFF000 | FMC-NAND | |

| 0x26000000 | Reserved | |

| 0x25000000 | GFXMMU SLV | |

| 0x24420000 | Reserved | |

| 0x24400000 | VENCRAM/AXISRAM8 | |

| 0x243C0000 | CACHEAXI/AXISRAM7 | |

| 0x24350000 | AXISRAM6 | |

| 0x242E0000 | AXISRAM5 | |

| 0x24270000 | AXISRAM4 | |

| 0x24200000 | AXISRAM3 | |

| 0x24100000 | AXISRAM2 | |

| 0x24064000 | AXISRAM1 | |

| Data nonsecure | 0x24000000 | FLEXRAM |

| 0x20040000 | Reserved | |

| 0x20000000 | DTCM - Baseline | |

| Code secure | 0x18020000 | Reserved |

| 0x18000000 | BootROM 128 Kbytes | |

| 0x10040000 | Reserved | |

| 0x10000000 | ITCM |

| IDAU security type | Mapping | Description |

|---|---|---|

| Code nonsecure | 0x08020000 | Reserved |

| 0x08000000 | BootROM 128 Kbytes | |

| 0x00040000 | Reserved | |

| 0x00000000 | ITCM |

| Zone | Name | IDAU security type | Mapping | Description | Size (Mbytes) |

|---|---|---|---|---|---|

| - | Reserved | - | 0xE0100000 - 0xFFFFFFFF | Reserved | 512 |

| - | - | 0xE0000000 - 0xE00FFFFF | Cortex-M55 internal peripherals, trace and debug | ||

| AXI(D1) | External device | Nonsecure | 0xD0000000 - 0xDFFFFFFF | SDRAM 2 - Reserved (through FMC) | 256 |

| 0xC0000000 - 0xCFFFFFFF | SDRAM 1 - Remap NOR/SRAM bank (through FMC) | 256 | |||

| 0xA0000000 - 0xBFFFFFFF | Reserved | 512 | |||

| External RAM | 0x90000000 - 0x9FFFFFFF | XSPI1 | 256 | ||

| 0x80000000 - 0x8FFFFFFF | XSPI3 | 256 | |||

| 0x70000000 - 0x7FFFFFFF | XSPI2 | 256 | |||

| 0x60000000 - 0x6FFFFFFF | NOR/SRAM - Remap SDRAM 1 (through FMC) | 256 | |||

| Peripherals | Trace and debug | Secure | 0x5E000000 - 0x5FFFFFFF | Trace and debug | 32 |

| Reserved | 0x5C000000 - 0x5DFFFFFF | Reserved | 32 | ||

| Reserved | 0x5A000000 - 0x5BFFFFFF | Reserved | 32 | ||

| Reserved | 0x58120000 - 0x59FFFFFF | Reserved | 32 | ||

| AHB5 | 0x58020000 - 0x5811FFFF | AHB5 peripherals | |||

| Reserved | 0x58010000 - 0x5801FFFF | Reserved for APB | |||

| APB5 | 0x58000000 - 0x5800FFFF | APB5 peripherals | |||

| Reserved | Secure | 0x56030000 - 0x57FFFFFF | Reserved | 32 | |

| AHB4 | 0x56020000 - 0x5602FFFF | AHB4 peripherals | |||

| Reserved | 0x56010000 - 0x5601FFFF | Reserved for APB | |||

| APB4 | 0x56000000 - 0x5600FFFF | APB4 peripherals | |||

Table 2. Memory map and peripheral register boundary addresses (continued)

| Zone | Name | IDAU security type | Mapping | Description | Size (Mbytes) |

|---|---|---|---|---|---|

| Peripherals | Reserved | Secure | 0x54040000 - 0x55FFFFFF | Reserved | 32 |

| AHB3 | 0x54020000 - 0x5403FFFF | AHB3 peripherals | |||

| Reserved | 0x54010000 - 0x5401FFFF | Reserved for APB | |||

| Reserved | 0x54000000 - 0x5400FFFF | APB3 peripherals | |||

| Reserved | 0x52040000 - 0x53FFFFFF | Reserved | 32 | ||

| AHB2 | 0x52020000 - 0x5203FFFF | AHB2 peripherals | |||

| Reserved | 0x52010000 - 0x5201FFFF | Reserved for APB | |||

| Reserved | 0x52000000 - 0x5200FFFF | APB2 peripherals | |||

| Reserved | 0x50188000 - 0x51FFFFFF | Reserved | 32 | ||

| AHB1 | 0x50020000 - 0x50187FFF | AHB1 peripherals | |||

| APB2 | 0x50010000 - 0x5001FFFF | Reserved | |||

| APB1 | 0x50000000 - 0x5000FFFF | APB1 peripherals | |||

| Trace and debug | Nonsecure | 0x4E000000 - 0x4FFFFFFF | Trace and debug | 32 | |

| Reserved | 0x4C000000 - 0x4DFFFFFF | Reserved | 32 | ||

| Reserved | 0x4A000000 - 0x4BFFFFFF | Reserved | 32 | ||

| Reserved | 0x48120000 - 0x49FFFFFF | Reserved | 32 | ||

| AHB5 | 0x48020000 - 0x4811FFFF | AHB5 peripherals | |||

| Reserved | 0x48010000 - 0x4801FFFF | Reserved for APB | |||

| APB5 | 0x48000000 - 0x4800FFFF | APB5 peripherals | |||

| Reserved | 0x46030000 - 0x47FFFFFF | Reserved | 32 | ||

| AHB4 | 0x46020000 - 0x4602FFFF | AHB4 peripherals | |||

| Reserved | 0x46010000 - 0x4601FFFF | Reserved for APB | |||

| APB4 | 0x46000000 - 0x4600FFFF | APB4 peripherals |

| Zone | Name | IDAU security type | Mapping | Description | Size (Mbytes) |

|---|---|---|---|---|---|

| Peripherals | Reserved | Nonsecure | 0x44040000 - 0x45FFFFFF | Reserved | 32 |

| AHB3 | 0x44020000 - 0x4403FFFF | AHB3 peripherals | |||

| Reserved | 0x44010000 - 0x4401FFFF | Reserved for APB | |||

| Reserved | 0x44000000 - 0x4400FFFF | APB3 peripherals | |||

| Reserved | 0x42040000 - 0x43FFFFFF | Reserved | 32 | ||

| AHB2 | 0x42020000 - 0x4203FFFF | AHB2 peripherals | |||

| Reserved | 0x42010000 - 0x4201FFFF | Reserved for APB | |||

| Reserved | 0x42000000 - 0x4200FFFF | APB2 peripherals | |||

| Reserved | 0x40188000 - 0x41FFFFFF | Reserved | 32 | ||

| AHB1 | 0x40020000 - 0x40187FFF | AHB1 peripherals | |||

| APB2 | 0x40010000 - 0x4001FFFF | Reserved | |||

| APB1 | 0x40000000 - 0x4000FFFF | APB1 peripherals | |||

| SRAM | - | Secure | 0x3C002000 - 0x3FFFFFF | Reserved | 64 |

| AHB_IC2_L5 | 0x3C000000 - 0x3C001FFF | Backup SRAM | |||

| - | 0x38008000 - 0x3BFFFFFF | Reserved | 64 | ||

| AHB_IC2_L1 | 0x38004000 - 0x38007FFF | AHBSRAM2 | |||

| AHB_IC2_L0 | 0x38000000 - 0x38003FFF | AHBSRAM1 |

Table 2. Memory map and peripheral register boundary addresses (continued)

| Zone | Name | IDA security type | Mapping | Description | Size (Mbytes) |

|---|---|---|---|---|---|

| SRAM | - | Secure | 0x37F00000 - 0x37FFFFFF | STM channels (system trace) | 64 |

| - | 0x37EFF000 - 0x37FFFFFF | FMC-NAND | |||

| AXI_IC1_GFX | 0x36000000 - 0x37EFFFFF | Reserved | |||

| - | 0x35000000 - 0x35FFFFFF | GFXMMU SLV | |||

| - | 0x34420000 - 0x34FFFFFF | Reserved | |||

| - | 0x34400000 - 0x3441FFFF | VENCRAM/AXISRAM8 | |||

| AXI_IC1_L4-C | 0x343C0000 - 0x343FFFFF | CACHEAXI/AXISRAM7 | |||

| - | 0x34350000 - 0x343BFFFF | AXISRAM6 | |||

| AXI_IC1_L4 | 0x342E0000 - 0x3434FFFF | AXISRAM5 | |||

| - | 0x34270000 - 0x342DFFFF | AXISRAM4 | |||

| AXI_IC1_L3 | 0x34200000 - 0x3426FFFF | AXISRAM3 | |||

| AXI_IC1_L2 | 0x34100000 - 0x341FFFFF | AXISRAM2 | |||

| AXI_IC1_L1 | 0x34000000 - 0x340FFFFF | AXISRAM1 (FLEXMEM extension bites on the lower end) | |||

| DTCM | 0x30040000 - 0x33FFFFFF | Reserved | 64 | ||

| 0x30020000 - 0x3003FFFF | DTCM - FLEXMEM extension | ||||

| 0x30000000 - 0x3001FFFF | DTCM - Base line | ||||

| - | Nonsecure | 0x2C002000 - 0x2FFFFFFF | Reserved | 64 | |

| AHB_IC2_L5 | 0x2C000000 - 0x2C001FFF | BKPSRAM | |||

| - | 0x28008000 - 0x2BFFFFFF | Reserved | |||

| AHB_IC2_L1 | 0x28004000 - 0x28007FFF | AHBSRAM2 | |||

| AHB_IC2_L0 | 0x28000000 - 0x28003FFF | AHBSRAM1 | |||

Table 2. Memory map and peripheral register boundary addresses (continued)

| Zone | Name | IDAU security type | Mapping | Description | Size (Mbytes) |

|---|---|---|---|---|---|

| SRAM | - | Nonsecure | 0x27F00000 - 0x27FFFFFF | STM channels (system trace) | 64 |

| - | 0x27EFF000 - 0x27FFFFFF | FMC-NAND | |||

| AXI_IC1_GFX | 0x26000000 - 0x27EFFFFF | Reserved | |||

| - | 0x25000000 - 0x25FFFFFF | GFXMMU SLV | |||

| - | 0x24420000 - 0x24FFFFFF | Reserved | |||

| - | 0x24400000 - 0x2441FFFF | VENCRAM/AXISRAM8 | |||

| AXI_IC1_L4-C | 0x243C0000 - 0x243FFFFF | CACHEAXI/AXISRAM7 | |||

| - | 0x24350000 - 0x243BFFFF | AXISRAM6 | |||

| AXI_IC1_L4 | 0x242E0000 - 0x2434FFFF | AXISRAM5 | |||

| - | 0x24270000 - 0x242DFFFF | AXISRAM4 | |||

| AXI_IC1_L3 | 0x24200000 - 0x2426FFFF | AXISRAM3 | |||

| AXI_IC1_L2 | 0x24100000 - 0x241FFFFF | AXISRAM2 | |||

| AXI_IC1_L1 | 0x24000000 - 0x240FFFFF | AXISRAM1 (FLEXMEM extension bites on the lower end) | |||

| DTCM | 0x20040000 - 0x23FFFFFF | Reserved | 64 | ||

| 0x20020000 - 0x2003FFFF | DTCM - FLEXMEM extension | ||||

| 0x20000000 - 0x2001FFFF | DTCM - Base line | ||||

| CODE | AXI_IC1_L0 | Secure | 0x1C080000 - 0x1FFFFFFF | Reserved | 128 |

| 0x1C000000 - 0x1C07FFFF | Reserved | ||||

| 0x18020000 - 0x1BFFFFFF | Reserved | ||||

| 0x18000000 - 0x1801FFFF | BootROM | ||||

| ITCM | 0x10040000 - 0x17FFFFFF | Reserved | 128 | ||

| 0x10010000 - 0x1003FFFF | ITCM - FLEXMEM extension | ||||

| 0x10000000 - 0x1000FFFF | ITCM - Base line | ||||

Table 2. Memory map and peripheral register boundary addresses (continued)

| Zone | Name | IDAU security type | Mapping | Description | Size (Mbytes) |

|---|---|---|---|---|---|

| CODE | AXI_IC1_L0 | Nonsecure | 0x0C080000 - 0x0FFFFFF | Reserved | 128 |

| 0x0C000000 - 0x0C07FFFF | Reserved | ||||

| 0x08020000 - 0x0BFFFF | Reserved | ||||

| 0x08000000 - 0x0801FFFF | BootROM | ||||

| ITCM | 0x00040000 - 0x07FFFF | Reserved | 128 | ||

| 0x00010000 - 0x0003FFFF | ITCM - FLEXMEM extension | ||||

| 0x00000000 - 0x0000FFFF | ITCM - Baseline | ||||

Table 3. Peripheral register boundary addresses

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| AHB5 | 0x58100000 - 0x5811FFFF | 0x48100000 - 0x4811FFFF | Reserved (for AHB peripherals) | 128 |

| 0x580E0000 - 0x580FFFFF | 0x480E0000 - 0x480FFFFF | NPU | 128 | |

| 0x580DFC00 - 0x580DFFFF | 0x480DFC00 - 0x480DFFFF | CACHEAXI (STM32N6x7xx only) | 1 | |

| 0x580C0400 - 0x580DFBFF | 0x480C0400 - 0x480DFBFF | Reserved (NPU) | 126 | |

| 0x580C0000 - 0x580C03FF | 0x480C0000 - 0x480C03FF | OTG2PHYCTL | 1 | |

| 0x58080000 - 0x580BFFFF | 0x48080000 - 0x480BFFFF | OTG2_HS | 256 | |

| 0x58040000 - 0x5807FFFF | 0x48040000 - 0x4807FFFF | OTG1_HS | 256 | |

| 0x5803FC00 - 0x5803FFFF | 0x4803FC00 - 0x4803FFFF | OTG1PHYCTL | 1 | |

| 0x58037400 - 0x580377FF | 0x48037400 - 0x480377FF | Reserved | 34 | |

| 0x58036000 - 0x580373FF | 0x48036000 - 0x480373FF | ETH1 | 5 | |

| 0x58035400 - 0x58035FFF | 0x48035400 - 0x48035FFF | Reserved (ETH1) | 3 | |

| 0x58035000 - 0x580353FF | 0x48035000 - 0x480353FF | GPU cache (ICACHE) | 1 | |

| 0x58034000 - 0x58034FFF | 0x48034000 - 0x48034FFF | GPU2D | 4 | |

| 0x58030000 - 0x58033FFF | 0x48030000 - 0x48033FFF | GFXMMU | 16 | |

| 0x5802E400 - 0x5802FFFF | 0x4802E400 - 0x4802FFFF | Reserved | 7 | |

| 0x5802E000 - 0x5802E3FF | 0x4802E000 - 0x4802E3FF | MCE4 | 1 | |

| 0x5802D000 - 0x5802DFFF | 0x4802D000 - 0x4802DFFF | XSPI3 | 4 | |

| 0x5802C400 - 0x5802CFFF | 0x4802C400 - 0x4802CFFF | Reserved (XSPI3) | 3 | |

| 0x5802C000 - 0x5802C3FF | 0x4802C000 - 0x4802C3FF | MCE3 | 1 | |

| 0x5802BC00 - 0x5802BFFF | 0x4802BC00 - 0x4802BFFF | MCE2 (former OTFDEC2) | 1 | |

| 0x5802B800 - 0x5802BBFF | 0x4802B800 - 0x4802BBFF | MCE1 (former OTFDEC1) | 1 | |

| 0x5802B400 - 0x5802B7FF | 0x4802B400 - 0x4802B7FF | XPIM (XSPI I/O manager) | 1 | |

| 0x5802B000 - 0x5802B3FF | 0x4802B000 - 0x4802B3FF | Reserved (delay block XSPI2) | 1 | |

| 0x5802A000 - 0x5802AFFF | 0x4802A000 - 0x4802AFFF | XSPI2 | 4 | |

| 0x58028800 - 0x58029FFF | 0x48028800 - 0x48029FFF | Reserved | 6 | |

| 0x58028400 - 0x580287FF | 0x48028400 - 0x480287FF | DCMI | 1 | |

| 0x58028000 - 0x580283FF | 0x48028000 - 0x480283FF | DLYB1 | 1 | |

| 0x58027000 - 0x58027FFF | 0x48027000 - 0x48027FFF | SDMMC1 | 4 | |

| 0x58026C00 - 0x58026FFF | 0x48026C00 - 0x48026FFF | DLYB2 | 1 | |

| 0x58026800 - 0x58026BFF | 0x48026800 - 0x48026BFF | SDMMC2 | 1 | |

| 0x58026400 - 0x580267FF | 0x48026400 - 0x480267FF | PSSI | 1 | |

| 0x58026000 - 0x580263FF | 0x48026000 - 0x480263FF | Reserved (delay block XSPI1) | 1 | |

| 0x58025000 - 0x58025FFF | 0x48025000 - 0x48025FFF | XSPI1 | 4 |

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| 0x58024000 - 0x58024FFF | 0x48024000 - 0x48024FFF | FMC | 4 | |

| AHB5 | 0x58023000 - 0x58023FFF | 0x48023000 - 0x48023FFF | JPEG | 4 |

| 0x58022000 - 0x58022FFF | 0x48022000 - 0x48022FFF | Reserved | 4 | |

| 0x58021000 - 0x58021FFF | 0x48021000 - 0x48021FFF | DMA2D | 4 | |

| 0x58020000 - 0x58020FFF | 0x48020000 - 0x48020FFF | HPDMA1 | 4 | |

| AHB4 | 0x5602A000 - 0x5602FFFF | 0x4602A000 - 0x4602FFFF | Reserved (for AHB peripherals) | 24 |

| 0x56028000 - 0x56029FFF | 0x46028000 - 0x46029FFF | RCC | 8 | |

| 0x56025400 - 0x56027FFF | 0x46025400 - 0x46027FFF | Reserved | 11 | |

| 0x56025000 - 0x560253FF | 0x46025000 - 0x460253FF | EXTI | 1 | |

| 0x56024C00 - 0x56024FFF | 0x46024C00 - 0x46024FFF | CRC | 1 | |

| 0x56024800 - 0x56024BFF | 0x46024800 - 0x46024BFF | PWR | 1 | |

| 0x56024400 - 0x560247FF | 0x46024400 - 0x460247FF | Reserved | 1 | |

| 0x56024000 - 0x560243FF | 0x46024000 - 0x460243FF | GPIO Q | 1 | |

| 0x56023C00 - 0x56023FFF | 0x46023C00 - 0x46023FFF | GPIO P | 1 | |

| 0x56023800 - 0x56023BFF | 0x46023800 - 0x46023BFF | GPIO O | 1 | |

| 0x56023400 - 0x560237FF | 0x46023400 - 0x460237FF | GPIO N | 1 | |

| 0x56022000 - 0x560223FF | 0x46022000 - 0x460223FF | Reserved | 5 | |

| 0x56021C00 - 0x56021FFF | 0x46021C00 - 0x46021FFF | GPIO H | 1 | |

| 0x56021800 - 0x56021BFF | 0x46021800 - 0x46021BFF | GPIO G | 1 | |

| 0x56021400 - 0x560217FF | 0x46021400 - 0x460217FF | GPIO F | 1 | |

| 0x56021000 - 0x560213FF | 0x46021000 - 0x460213FF | GPIO E | 1 | |

| 0x56020C00 - 0x56020FFF | 0x46020C00 - 0x46020FFF | GPIO D | 1 | |

| 0x56020800 - 0x56020BFF | 0x46020800 - 0x46020BFF | GPIO C | 1 | |

| 0x56020400 - 0x560207FF | 0x46020400 - 0x460207FF | GPIO B | 1 | |

| 0x56020000 - 0x560203FF | 0x46020000 - 0x460203FF | GPIO A | 1 |

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| AHB3 | 0x54038000 - 0x5403FFFF | 0x44038000 - 0x4403FFFF | Reserved (for AHB peripherals) | 32 |

| 0x54037000 - 0x54037FFF | 0x44037000 - 0x44037FFF | RISAF23: backup RAM | 4 | |

| 0x54036000 - 0x54036FFF | 0x44036000 - 0x44036FFF | RISAF22: AHB RAM 1 | 4 | |

| 0x54035000 - 0x54035FFF | 0x44035000 - 0x44035FFF | RISAF21: AHB RAM 0 | 4 | |

| 0x54034000 - 0x54034FFF | 0x44034000 - 0x44034FFF | RISAF15: cache configuration port | 4 | |

| 0x54033000 - 0x54033FFF | 0x44033000 - 0x44033FFF | RISAF14: FMC2 | 4 | |

| 0x54032000 - 0x54032FFF | 0x44032000 - 0x44032FFF | RISAF13: XSPI3 | 4 | |

| 0x54031000 - 0x54031FFF | 0x44031000 - 0x44031FFF | RISAF12: XSPI2 | 4 | |

| 0x54030000 - 0x54030FFF | 0x44030000 - 0x44030FFF | RISAF11: XSPI1 | 4 | |

| 0x5402F000 - 0x5402FFFF | 0x4402F000 - 0x4402FFFF | Reserved | 4 | |

| AHB3 | 0x5402E000 - 0x5402EFFF | 0x4402E000 - 0x4402EFFF | RISAF9: VENCRAM/AXISRAM8 | 4 |

| 0x5402D000 - 0x5402DFFF | 0x4402D000 - 0x4402DFFF | RISAF8: CACHEAXI/AXISRAM7 | 4 | |

| 0x5402C000 - 0x5402CFFF | 0x4402C000 - 0x4402CFFF | RISAF7: FLEXMEM | 4 | |

| 0x5402B000 - 0x5402BFFF | 0x4402B000 - 0x4402BFFF | RISAF6: CPU_MST | 4 | |

| 0x5402A000 - 0x5402AFFF | 0x4402A000 - 0x4402AFFF | RISAF5: NPU_MST1 | 4 | |

| 0x54029000 - 0x54029FFF | 0x44029000 - 0x44029FFF | RISAF4: NPU_MST0 | 4 | |

| 0x54028000 - 0x54028FFF | 0x44028000 - 0x44028FFF | RISAF3: AXISRAM2 | 4 | |

| 0x54027000 - 0x54027FFF | 0x44027000 - 0x44027FFF | RISAF2: AXISRAM1 | 4 | |

| 0x54026000 - 0x54026FFF | 0x44026000 - 0x44026FFF | RISAF1: TCMs | 4 | |

| 0x54025400 - 0x54025FFF | 0x44025400 - 0x44025FFF | Reserved | 3 | |

| 0x54025000 - 0x540253FF | 0x44025000 - 0x440253FF | IAC | 1 | |

| 0x54024000 - 0x54024FFF | 0x44024000 - 0x44024FFF | RIFSC | 4 | |

| 0x54022000 - 0x54023FFF | 0x44022000 - 0x44023FFF | PKA + RAM | 8 | |

| 0x54021400 - 0x54021FFF | 0x44021400 - 0x44021FFF | Reserved | 3 | |

| 0x54021000 - 0x540213FF | 0x44021000 - 0x440213FF | SAES | 1 | |

| 0x54020C00 - 0x54020FFF | 0x44020C00 - 0x44020FFF | Reserved | 1 | |

| 0x54020800 - 0x54020BFF | 0x44020800 - 0x44020BFF | CRYP1 | 1 | |

| 0x54020400 - 0x540207FF | 0x44020400 - 0x440207FF | HASH | 1 | |

| 0x54020000 - 0x540203FF | 0x44020000 - 0x440203FF | RNG | 1 |

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| AHB2 | 0x52027000 - 0x5203FFFF | 0x42027000 - 0x4203FFFF | Reserved (for AHB peripherals) | 100 |

| 0x52026000 - 0x52026FFF | 0x42026000 - 0x42026FFF | ADF1 (MDF2) | 4 | |

| 0x52025000 - 0x52025FFF | 0x42025000 - 0x42025FFF | MDF1 | 4 | |

| 0x52024000 - 0x52024FFF | 0x42024000 - 0x42024FFF | Reserved | 4 | |

| 0x52023000 - 0x52023FFF | 0x42023000 - 0x42023FFF | RAMCFG | 4 | |

| 0x52020000 - 0x52022FFF | 0x42020000 - 0x42022FFF | Reserved | 12 | |

| AHB1 | 0x50100000 - 0x50187FFF | 0x40100000 - 0x40187FFF | Reserved (for AHB peripherals) | 544 |

| 0x50022400 - 0x500FFFFF | 0x40022400 - 0x400FFFFF | Reserved | 887 | |

| 0x50022000 - 0x500223FF | 0x40022000 - 0x400223FF | ADC1/2 | 1 | |

| 0x50021000 - 0x50021FFF | 0x40021000 - 0x40021FFF | GPDMA1 | 4 | |

| 0x50020000 - 0x50020FFF | 0x40020000 - 0x40020FFF | Reserved | 4 | |

| APB5 | 0x58008000 - 0x5800FFFF | 0x48008000 - 0x4800FFFF | Reserved (for APB peripherals) | 32 |

| 0x58006000 - 0x58007FFF | 0x48006000 - 0x48007FFF | CSI2 HOST wrapper | 8 | |

| 0x58005000 - 0x58005FFF | 0x48005000 - 0x48005FFF | VENC H264/JPEG encoder | 4 | |

| 0x58004000 - 0x58004FFF | 0x48004000 - 0x48004FFF | GFXTIM | 4 | |

| APB5 | 0x58003000 - 0x58003FFF | 0x48003000 - 0x48003FFF | Reserved | 4 |

| 0x58002000 - 0x58002FFF | 0x48002000 - 0x48002FFF | DCMIPP | 4 | |

| 0x58001000 - 0x58001FFF | 0x48001000 - 0x48001FFF | LTDC | 4 | |

| 0x58000000 - 0x58000FFF | 0x48000000 - 0x48000FFF | Reserved | 4 |

Table 3. Peripheral register boundary addresses (continued)

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| APB4 | 0x5600C000 - 0x5600FFFF | 0x4600C000 - 0x4600FFFF | Reserved | 16 |

| 0x5600B000 - 0x5600BFFF | 0x4600B000 - 0x4600BFFF | Reserved | 4 | |

| 0x5600A000 - 0x5600AFFF | 0x4600A000 - 0x4600AFFF | DTS (16FF version) | 4 | |

| 0x56009000 - 0x56009FFF | 0x46009000 - 0x46009FFF | BSEC | 4 | |

| 0x56008000 - 0x56008FFF | 0x46008000 - 0x46008FFF | SYSCFG | 4 | |

| 0x56004C00 - 0x56007FFF | 0x46004C00 - 0x46007FFF | Reserved(WDG_LS_D2) | 13 | |

| 0x56004800 - 0x56004BFF | 0x46004800 - 0x46004BFF | IWDG (WDG_LS_D1) | 1 | |

| 0x56004400 - 0x560047FF | 0x46004400 - 0x460047FF | TAMP | 1 | |

| 0x56004000 - 0x560043FF | 0x46004000 - 0x460043FF | RTC and backup registers | 1 | |

| 0x56003C00 - 0x56003FFF | 0x46003C00 - 0x46003FFF | VREFBUF | 1 | |

| 0x56003400 - 0x56003BFF | 0x46003400 - 0x46003BFF | Reserved | 2 | |

| 0x56003000 - 0x560033FF | 0x46003000 - 0x460033FF | LPTIMER5 | 1 | |

| 0x56002C00 - 0x56002FFF | 0x46002C00 - 0x46002FFF | LPTIMER4 | 1 | |

| 0x56002800 - 0x56002BFF | 0x46002800 - 0x46002BFF | LPTIMER3 | 1 | |

| 0x56002400 - 0x560027FF | 0x46002400 - 0x460027FF | LPTIMER2 | 1 | |

| 0x56002000 - 0x560023FF | 0x46002000 - 0x460023FF | Reserved | 1 | |

| 0x56001C00 - 0x56001FFF | 0x46001C00 - 0x46001FFF | I2C4 | 1 | |

| 0x56001800 - 0x56001BFF | 0x46001800 - 0x46001BFF | Reserved | 1 | |

| 0x56001400 - 0x560017FF | 0x46001400 - 0x460017FF | SPI6/I2S | 1 | |

| 0x56001000 - 0x560013FF | 0x46001000 - 0x460013FF | Reserved | 1 | |

| 0x56000C00 - 0x56000FFF | 0x46000C00 - 0x46000FFF | LPUART1 | 1 | |

| 0x56000800 - 0x56000BFF | 0x46000800 - 0x46000BFF | HDP | 1 | |

| 0x56000000 - 0x460007FF | 0x46000000 - 0x460007FF | Reserved | 2 | |

| APB3 | 0x54002400 - 0x5400FFFF | 0x44002400 - 0x4400FFFF | Reserved (for APB peripherals) | 55 |

| 0x54002000 - 0x540023FF | 0x44002000 - 0x440023FF | DFT APB registers | 1 | |

| 0x54001000 - 0x54001FFF | 0x44001000 - 0x44001FFF | DBG_MCU | 4 | |

| 0x54000000 - 0x54000FFF | 0x44000000 - 0x44000FFF | DAP ROM table | 4 | |

| APB2 | 0x52008000 - 0x5200FFFF | 0x42008000 - 0x4200FFFF | Reserved (for APB peripherals) | 32 |

| 0x52006000 - 0x52007FFF | 0x42006000 - 0x42007FFF | Reserved | 7 | |

| 0x52005C00 - 0x52005FFF | 0x42005C00 - 0x42005FFF | SAI2 | 1 |

Table 3. Peripheral register boundary addresses (continued)

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| APB2 | 0x52005800 - 0x52005BFF | 0x42005800 - 0x42005BFF | SAI1 | 1 |

| 0x52005400 - 0x520057FF | 0x42005400 - 0x420057FF | Reserved | 1 | |

| 0x52005000 - 0x520053FF | 0x42005000 - 0x420053FF | SPI5 | 1 | |

| 0x52004C00 - 0x52004FFF | 0x42004C00 - 0x42004FFF | TIMER9 | 1 | |

| 0x52004800 - 0x52004BFF | 0x42004800 - 0x42004BFF | TIMER17 | 1 | |

| 0x52004400 - 0x520047FF | 0x42004400 - 0x420047FF | TIMER16 (16-bit) | 1 | |

| 0x52004000 - 0x520043FF | 0x42004000 - 0x420043FF | TIMER15 (16-bit) | 1 | |

| 0x52003C00 - 0x52003FFF | 0x42003C00 - 0x42003FFF | TIMER18 (16-bit) | 1 | |

| 0x52003800 - 0x52003BFF | 0x42003800 - 0x42003BFF | Reserved | 1 | |

| 0x52003400 - 0x520037FF | 0x42003400 - 0x420037FF | SPI4 | 1 | |

| 0x52003000 - 0x520033FF | 0x42003000 - 0x420033FF | SPI1/I2S1 | 1 | |

| 0x52002000 - 0x52002FFF | 0x42002000 - 0x42002FFF | Reserved | 4 | |

| 0x52001C00 - 0x52001FFF | 0x42001C00 - 0x42001FFF | USART10 | 1 | |

| 0x52001800 - 0x52001BFF | 0x42001800 - 0x42001BFF | UART9 | 1 | |

| 0x52001400 - 0x520017FF | 0x42001400 - 0x420017FF | USART6 | 1 | |

| 0x52001000 - 0x520013FF | 0x42001000 - 0x420013FF | USART1 | 1 | |

| 0x52000800 - 0x52000FFF | 0x42000800 - 0x42000FFF | Reserved | 2 | |

| 0x52000400 - 0x520007FF | 0x42000400 - 0x420007FF | TIMER8 (16-bit)/PWM2 | 1 | |

| 0x52000000 - 0x520003FF | 0x42000000 - 0x420003FF | TIMER1 (16-bit)/PWM1 | 1 | |

| APB1 | 0x50010000 - 0x5000FFFF | 0x40010000 - 0x4000FFFF | Reserved (for APB peripherals) | 0 |

| 0x5000FC00 - 0x5000FFFF | 0x4000FC00 - 0x4000FFFF | UCPD | 1 | |

| 0x5000EC00 - 0x5000FBFF | 0x4000EC00 - 0x4000FBFF | Reserved | 4 | |

| 0x5000E800 - 0x5000EBFF | 0x4000E800 - 0x4000EBFF | FDCAN3 | 1 | |

| 0x5000C000 - 0x5000E7FF | 0x4000C000 - 0x4000E7FF | CAN memory | 10 | |

| 0x5000AC00 - 0x5000BFFF | 0x4000AC00 - 0x4000BFFF | Reserved | 5 | |

| 0x5000A800 - 0x5000ABFF | 0x4000A800 - 0x4000ABFF | CAN calibration unit | 1 | |

| 0x5000A400 - 0x5000A7FF | 0x4000A400 - 0x4000A7FF | FDCAN2 | 1 | |

| 0x5000A000 - 0x5000A3FF | 0x4000A000 - 0x4000A3FF | FDCAN1 | 1 | |

| 0x50009800 - 0x50009FFF | 0x40009800 - 0x40009FFF | Reserved | 2 | |

| 0x50009400 - 0x500097FF | 0x40009400 - 0x400097FF | MDIOS | 5 | |

| 0x50008000 - 0x500093FF | 0x40008000 - 0x400093FF | Reserved | 1 | |

| 0x50007C00 - 0x50007FFF | 0x40007C00 - 0x40007FFF | UART8 | 1 | |

| 0x50007800 - 0x50007BFF | 0x40007800 - 0x40007BFF | UART7 | 4 | |

| 0x50006800 - 0x500077FF | 0x40006800 - 0x400077FF | Reserved | 1 |

Table 3. Peripheral register boundary addresses (continued)

| Bus | Secure boundary address | Nonsecure boundary address | Description | Size (Kbytes) |

|---|---|---|---|---|

| APB1 | 0x50006400 - 0x500067FF | 0x40006400 - 0x400067FF | I3C2 | 1 |

| 0x50006000 - 0x500063FF | 0x40006000 - 0x400063FF | I3C1 | 1 | |

| 0x50005C00 - 0x50005FFF | 0x40005C00 - 0x40005FFF | I2C3 | 1 | |

| 0x50005800 - 0x50005BFF | 0x40005800 - 0x40005BFF | I2C2 | 1 | |

| 0x50005400 - 0x500057FF | 0x40005400 - 0x400057FF | I2C1 | 1 | |

| 0x50005000 - 0x500053FF | 0x40005000 - 0x400053FF | UART5 | 1 | |

| 0x50004C00 - 0x50004FFF | 0x40004C00 - 0x40004FFF | UART4 | 1 | |

| 0x50004800 - 0x50004BFF | 0x40004800 - 0x40004BFF | USART3 | 1 | |

| 0x50004400 - 0x500047FF | 0x40004400 - 0x400047FF | USART2 | 1 | |

| 0x50004000 - 0x500043FF | 0x40004000 - 0x400043FF | SPDIFRX | 1 | |

| 0x50003C00 - 0x50003FFF | 0x40003C00 - 0x40003FFF | SPI3/I2S3 | 1 | |

| 0x50003800 - 0x50003BFF | 0x40003800 - 0x40003BFF | SPI2/I2S2 | 1 | |

| 0x50003400 - 0x500037FF | 0x40003400 - 0x400037FF | TIMER11 (basic) | 1 | |

| 0x50003000 - 0x500033FF | 0x40003000 - 0x400033FF | TIMER10 (basic) | 1 | |

| 0x50002C00 - 0x50002FFF | 0x40002C00 - 0x40002FFF | WWDG | 1 | |

| 0x50002800 - 0x50002BFF | 0x40002800 - 0x40002BFF | Reserved | 1 | |

| 0x50002400 - 0x500027FF | 0x40002400 - 0x400027FF | LPTIMER1 | 1 | |

| 0x50002000 - 0x500023FF | 0x40002000 - 0x400023FF | TIMER14 (light) | 1 | |

| 0x50001C00 - 0x50001FFF | 0x40001C00 - 0x40001FFF | TIMER13 (light) | 1 | |

| 0x50001800 - 0x50001BFF | 0x40001800 - 0x40001BFF | TIMER12 (light) | 1 | |

| 0x50001400 - 0x500017FF | 0x40001400 - 0x400017FF | TIMER7 (basic) | 1 | |

| 0x50001000 - 0x500013FF | 0x40001000 - 0x400013FF | TIMER6 (basic) | 1 | |

| 0x50000C00 - 0x50000FFF | 0x40000C00 - 0x40000FFF | TIMER5 (32-bit) | 1 | |

| 0x50000800 - 0x50000BFF | 0x40000800 - 0x40000BFF | TIMER4 (32-bit) | 1 | |

| 0x50000400 - 0x500007FF | 0x40000400 - 0x400007FF | TIMER3 (32-bit) | 1 | |

| 0x50000000 - 0x500003FF | 0x40000000 - 0x400003FF | TIMER2 (32-bit) | 1 |