52. Serial peripheral interface (SPI)

52.1 SPI introduction

The serial peripheral interface (SPI) can be used to communicate with external devices while using the specific synchronous protocol. The SPI protocol supports half-duplex, full-duplex, and simplex synchronous, serial communication with external devices. The interface can be configured as master or slave and can operate in multislave or multimaster configurations. The device configured as master provides a communication clock (SCK) to the slave device. The slave select (NSS) and ready (RDY) signals can be applied optionally just to set up communication with a concrete slave and to ensure it handles the data flow properly. The Motorola data format is used by default, but some other specific modes are supported as well.

52.2 SPI main features

- • Full-duplex synchronous transfers on three lines

- • Half-duplex synchronous transfer on two lines (with bidirectional data line)

- • Simplex synchronous transfers on two lines (with unidirectional data line)

- • From 4-bit up to 32-bit data size selection

- • Multimaster or multislave mode capability

- • Dual clock domain, the peripheral kernel clock is independent from the APB bus clock

- • Baud rate prescaler up to kernel frequency/2 or bypass from RCC in master mode

- • Protection of configuration and setting

- • Slave select hardware or software management for both master and slave

- • Adjustable minimum delays between data and between NSS and data flow

- • Configurable NSS signal polarity and timing, MISO x MOSI swap capability

- • Programmable clock polarity and phase

- • Programmable data order with MSB-first or LSB-first shifting

- • Programmable number of data within a transfer to control NSS and CRC

- • Dedicated transmission and reception flags with interrupt capability

- • SPI Motorola and TI format support

- • Hardware CRC can verify the integrity of the communication at the end of a transfer by:

- – Adding CRC value in Tx mode

- – Automatic CRC error checking for Rx mode

- • Error detection with interrupt capability in case of data overrun, CRC error, data underrun, the mode fault, and frame error, depending on the operating mode

- • Two 8-bit width embedded Rx and Tx FIFOs (FIFO size depends on instances)

- • Configurable FIFO thresholds (to handle the data packets)

- • Capability to handle data streams by system DMA controller

- • Configurable behavior at slave underrun condition (support of cascaded circular buffers)

- • Optional status pin RDY signaling that the slave device is ready to handle the data flow

52.3 SPI implementation

The table below describes the SPI implementation.

Table 569. SPI features

| SPI feature | SPI1, SPI2, SPI3 (full-featured instances) | SPI4, SPI5

(1)

, SPI6

(1) (full-featured instances) |

|---|---|---|

| Data and CRC size | Configurable from 4 to 32 bits | Configurable from 4 to 16 bits |

| CRC computation | CRC polynomial length configurable from 5 to 33 bits | CRC polynomial length configurable from 5 to 17 bits |

| FIFO size | 16x8 bits | 8x8 bits |

| FIFO threshold | 1 - 16 data | 1 - 16 data |

| Number of data control (TSIZE) | Up to 65535 | Up to 65535 |

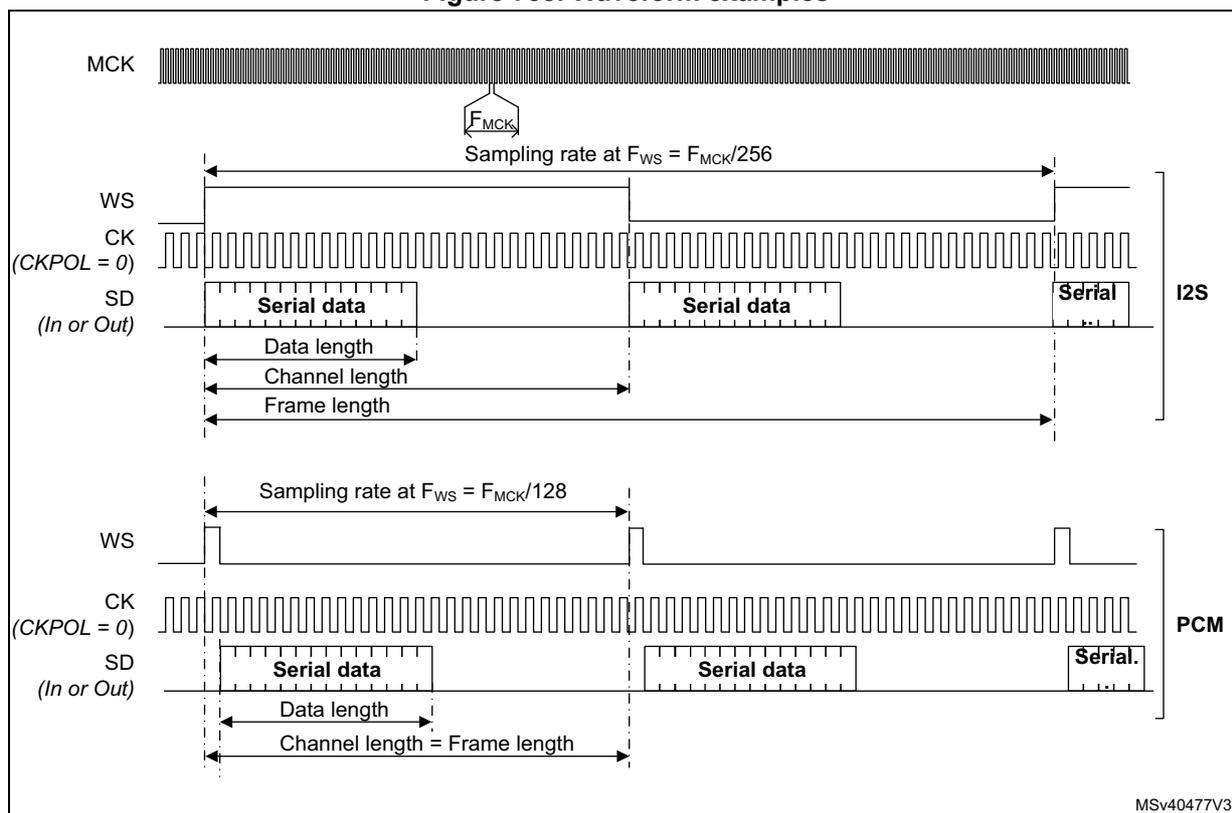

| I2S feature | Yes | No |

| Autonomous in Stop modes with wake-up capability | No | No |

| Autonomous in LP-Stop and Standby modes with wake-up capability | No | No |

1. Available only on STM32H562xl, STM32H563xl and STM32H573xx devices

Note: For detailed information about instance capabilities to exit from Stop and Standby modes, refer to Table 573: SPI wake-up and interrupt requests .

52.4 SPI functional description

52.4.1 SPI block diagram

The SPI enables synchronous, serial communications between the MCU and external devices. The application software can manage the communication by polling the status flag or using a dedicated SPI interrupt. The main SPI elements and their interactions are shown in Figure 724.

Figure 724. SPI/I2S block diagram

![Figure 724. SPI/I2S block diagram. This is a complex block diagram of the SPI/I2S peripheral. On the left, a 32-bit APB bus connects to various internal components. External signals on the left include spi_wkup, spi_it, spi_pclk_req, spi_tx_dma, and spi_rx_dma. External signals on the right include RDY, NSS / WS, MOSI / SDO, MISO / SDI, SCK / CK, and MCK. The internal architecture is divided into three clock domains: 'spi_pclk clock domain' (containing the APB bus, COM Controller, SPI_TXDR, SPI_UDRDR, SPI_RXDR, SPI_CR1, SPI_CR2, SPI_CFG[2:1]), 'spi_ker_ck clock domain' (containing the Clock Generator and Prescaler), and 'Serial interface clock domain' (containing the IRQ Interface, DMA Interface, COM Controller registers like SPI_IER, SPI_SR, SPI_IFCR, SPI_CRCPOLY, SPI_TXCRC, SPI_RXCRC, RDY Logic, NSS Logic, CRC Controller, TX Shift Reg, UDR Controller, RX Shift Reg, and a multiplexer for MOSI/SDO and MISO/SDI). A note at the bottom right indicates 'Bold: I2S signal names'.](/RM0481-STM32H523-33-562-63-573/2d2ba8e7aa58c625004728e8ffd61a98_img.jpg)

The simplified scheme of Figure 724 shows three fully independent clock domains:

- • The spi_pclk clock domain

- • The spi_ker_ck kernel clock domain

- • The serial interface clock domain

All the control and status signals between these domains are strictly synchronized. There is no specific constraint concerning the frequency ratio between these clock signals. The user

has to consider a ratio compatible with the data flow speed to avoid data underrun or overrun events.

The spi_pclk clock signal feeds the peripheral bus interface. It must be active when accesses to the SPI registers are required.

The SPI working in slave mode handles a data flow using the serial interface clock derived from the external SCK signal provided by the external master SPI device. That is why the SPI slave is able to receive and send data even when the spi_pclk and spi_ker_ck clock signals are inactive. As a consequence, a specific slave logic working within the serial interface clock domain needs some additional traffic to be set up correctly (for example when underrun or overrun is evaluated, see Section 52.5.2 for details). This cannot be done when the bus becomes idle. In some specific cases, the slave even requires the clock generator working (see Section 52.5.1 ).

When the SPI works as a master, the RCC must provide the spi_ker_ck kernel clock to the peripheral during communication to feed the serial interface clock via the clock generator where it can be divided by prescaler or bypassed. The signal is then provided to the slaves via the SCK pin and internally to the serial interface domain of the master.

52.4.2 SPI pins and internal signals

Up to five I/O pins are dedicated to SPI communication with external devices.

- • MISO: master in / slave out data. In the general case, this pin is used to transmit data in slave mode and receive data in master mode.

- • MOSI: master out / slave in data. In the general case, this pin is used to transmit data in master mode and receive data in slave mode.

- • SCK: serial clock output pin for SPI masters and input pin for SPI slaves.

- •

NSS:

slave select pin. Depending on the SPI and NSS settings, this pin can be used to either:

- – Select an individual slave device for communication

- – Synchronize the data frame, or

- – Detect a conflict between multiple masters

See Section 52.4.7 for details.

- • RDY: optional status pin signaling slave FIFO occupancies and so the slave availability to continue the transfer without any risk of data flow corruption. It can be checked by the master to control the temporal suspension of the ongoing communication.

All these pins (except RDY) are shared in the I2S mode. This mode features an additional I2S specific MCK signal. For more details about I2S signals, see Section 52.9.2 .

The SPI bus enables the communication between one master device and one or more slave devices. The bus consists of at least two wires: one for the clock signal and the other for synchronous data transfer. Other signals are optional and can be added depending on the data exchange between SPI nodes and their communication control management.

Refer to Table 570 and Table 571 for the list of SPI input / output pins and internal signals.

Table 570. SPI/I2S input/output pins (1)| Pin name | I/O type | Description |

|---|---|---|

| MISO/SDI (2) | Input/output | Master data input / slave data output |

| MOSI/SDO (2) | Input/output | Master data output / slave data input |

| SCK/CK | Input/output | Master clock output / slave clock input |

| NSS/WS | Input/output | Master output / slave selection input |

| RDY | Input/output | SPI master input / slave FIFOs status occupancy output |

| MCK | Output | I2S master frequency output |

- 1. Refer to the section Section 52.9.2: Pin sharing with SPI function for details.

- 2. Functionality of MOSI/SDO and MISO/SDI pins can be swapped. Their directions may vary in SPI bidirectional half-duplex mode.

Description of SPI input/output signals

Table 571. SPI internal input/output signals| Signal name | Signal type | Description |

|---|---|---|

| spi_pclk | Input | SPI clock signal feeds the peripheral bus interface |

| spi_ker_ck | Input | SPI kernel clock |

| spi_ker_ck_req | Output | SPI kernel clock request |

| spi_pclk_req | Output | SPI clock request |

| spi_wkup | Output | SPI provides a wake-up interrupt |

| spi_it | Output | SPI global interrupt |

| spi_tx_dma | Input/output | SPI transmit DMA request |

| spi_rx_dma | Input/output | SPI receive DMA request |

52.4.3 SPI communication general aspects

The SPI allows the MCU to communicate using different configurations, depending on the device targeted and the application requirements. These configurations use two or three wires (with software slave select management) or three or four wires (with hardware slave select management). The communication is always initiated and controlled by the master. The master provides a clock signal on the SCK line and selects or synchronizes slaves for communication by NSS line when it is managed by hardware.

The data between the master and the slave flow synchronously on the MOSI and/or MISO lines.

52.4.4 Communications between one master and one slave

The communication flow can use one of three possible modes: the full-duplex (three wires) mode, half-duplex (two wires) mode, or the simplex (two wires) mode. The NSS signal is optional in single master-slave configuration and is often not connected between the two communication nodes. Nevertheless, the NSS signal can be helpful in this configuration to synchronize the data flow and it is used by default for some specific SPI modes (for example the TI mode).

The next optional RDY signal can help to ensure the correct management of all the transferred data at slave side.

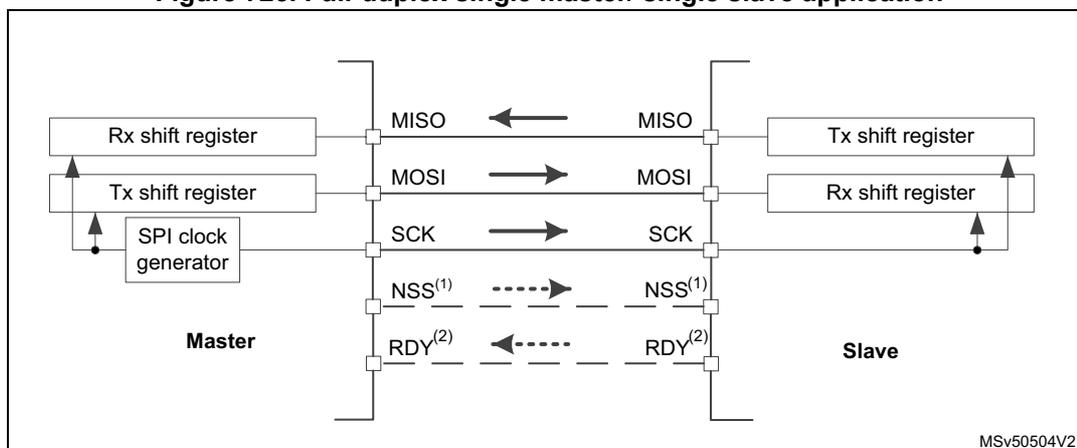

Full-duplex communication

By default, the SPI is configured for full-duplex communication (bits COMM[1:0] = 00 in the SPI_CFG2 register). In this configuration, the shift registers of the master and slave are linked using two unidirectional lines between the MOSI and the MISO pins. During the SPI communication, the data are shifted synchronously on the SCK clock edges provided by the master. The master transmits the data to be sent to the slave via the MOSI line and receives data from the slave via the MISO line simultaneously. When the data frame transfer is complete (all the bits are shifted) the information between the master and slave is exchanged.

Figure 725. Full-duplex single master/ single slave application

The diagram illustrates a full-duplex SPI connection between a Master and a Slave. The Master side includes an 'SPI clock generator' connected to the SCK pin. The Master has two shift registers: an 'Rx shift register' connected to the MISO pin and a 'Tx shift register' connected to the MOSI pin. The Slave side also has two shift registers: a 'Tx shift register' connected to the MISO pin and an 'Rx shift register' connected to the MOSI pin. The connections are as follows: MISO (Slave) to MISO (Master), MOSI (Master) to MOSI (Slave), SCK (Master) to SCK (Slave), NSS (1) (Slave) to NSS (1) (Master) via a dashed line, and RDY (2) (Slave) to RDY (2) (Master) via a dashed line. Arrows indicate the direction of data flow: MISO from Slave to Master, MOSI from Master to Slave, and SCK from Master to Slave. The diagram is labeled 'MSv50504V2' in the bottom right corner.

- 1. The NSS pin interconnection is optional. The slave can be configured to be permanently selected to operate in a single master-slave pair (see Section 52.4.7 ).

- 2. The RDY signal provided by the slave can be read by the master optionally.

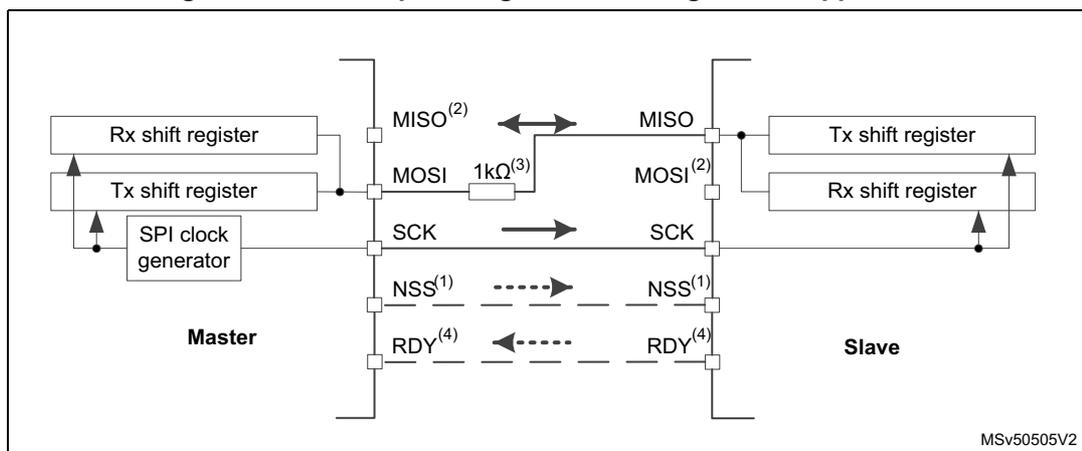

Half-duplex communication

The SPI can communicate in half-duplex mode by setting COMM[1:0] = 11 in the SPI_CFG2 register. In this configuration, one single cross-connection line is used to link the shift registers of the master and slave together. During this communication, the data are synchronously shifted between the shift registers on the SCK clock edge in the transfer direction selected reciprocally by both master and slave with the HDDIR bit in their SPI_CR1 registers. Note that the SPI must be disabled when changing the direction of the communication. In this configuration, the MISO pin at master and the MOSI pin at slave are free for other application uses and act as GPIOs.

Figure 726. Half-duplex single master/ single slave application

- 1. The NSS pin interconnection is optional. The slave can be configured to be permanently selected to operate in a single master-slave pair (see Section 52.4.7 ).

- 2. In this configuration, the MISO pin at master and MOSI pin at slave can be used as GPIOs

- 3. A critical situation can happen when the communication direction is not changed synchronously between two nodes working in bidirectional mode. The new transmitter accesses the common data line while the former transmitter still keeps an opposite value on the line (the value depends on the SPI configuration and communicated data). The nodes can conflict temporarily with opposite output levels on the line until the former transmitter changes its data direction setting. It is suggested to insert a serial resistance between MISO and MOSI pins in this mode to protect the conflicting outputs and limit the current flow between them.

- 4. The RDY signal provided by the slave can be read by the master optionally.

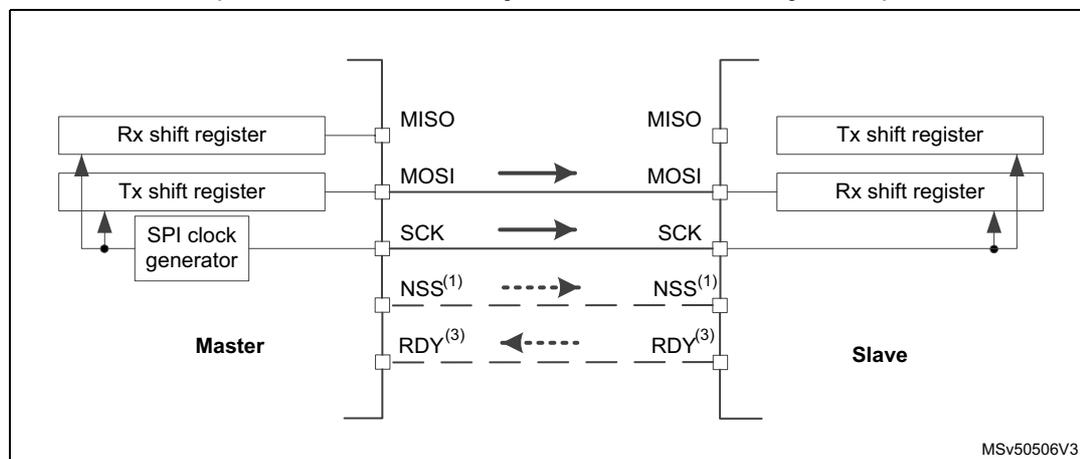

Simplex communications

The SPI can communicate in simplex mode by setting the SPI in transmit-only or in receive-only using the COMM[1:0] field in the SPI_CFG2 register. In this configuration, only one line is used for the transfer between the shift registers of the master and slave. The remaining MISO or MOSI pin pair is not used for communication and can be used as standard GPIOs.

- • Transmit-only mode: COMM[1:0] = 01

The master in transmit-only mode generates the clock as long as there are data available in the TxFIFO and the master transfer is ongoing.

The slave in transmit-only mode sends data as long as it receives a clock on the SCK pin and the NSS pin (or software managed internal signal) is active (see Section 52.4.7 ).

- • Receive-only mode: COMM[1:0] = 10

In master mode, the MOSI output is disabled and can be used as a GPIO. The clock signal is generated continuously as long as the SPI is enabled and the CSTART bit in the SPI_CR1 register is set. The clock is stopped either by software explicitly requesting this by setting the CSUSP bit in the SPI_CR1 register or automatically when the RxFIFO is full, when the MASRX bit in the SPI_CR1 is set.

In slave configuration, the MISO output is disabled and the pin can be used as a GPIO. The slave continues to receive data from the MOSI pin while its slave select signal is active (see Section 52.4.7 ).

Note: In whatever master and slave modes, the data pin dedicated for transmission can be replaced by the data pin dedicated for reception and vice versa by changing the IOSWP bit value in the SPI_CFG2 register (this bit can only be modified when the SPI is disabled).

Any simplex communication can be replaced by a variant of the half-duplex communication with a constant setting of the transfer direction (bidirectional mode is enabled, while the

HDDIR bit is never changed) or by full-duplex control when unused data line and corresponding data flow is ignored.

Figure 727. Simplex single master / single slave application

(master in transmit-only / slave in receive-only mode)

The diagram illustrates a simplex single master / single slave SPI application. On the Master side, there is an Rx shift register, a Tx shift register, and an SPI clock generator. The Slave side has a Tx shift register and an Rx shift register. The connections are as follows:

- MISO: Connected between the Master's Rx shift register and the Slave's MISO pin.

- MOSI: Connected between the Master's Tx shift register and the Slave's Rx shift register. An arrow indicates data flow from Master to Slave.

- SCK: Connected between the Master's SPI clock generator and the Slave's SCK pin.

- NSS (1) : An optional connection between the Master and Slave.

- RDY (3) : A signal line from the Slave's RDY pin to the Master's RDY pin. A dashed arrow indicates data flow from Slave to Master.

- 1. The NSS pin interconnection is optional. The slave can be configured to be permanently selected to operate in a single master-slave pair (see Section 52.4.7 ).

- 2. In this configuration, both the MISO pins can be used as GPIOs.

- 3. The RDY signal provided by the slave can be read by the master optionally.

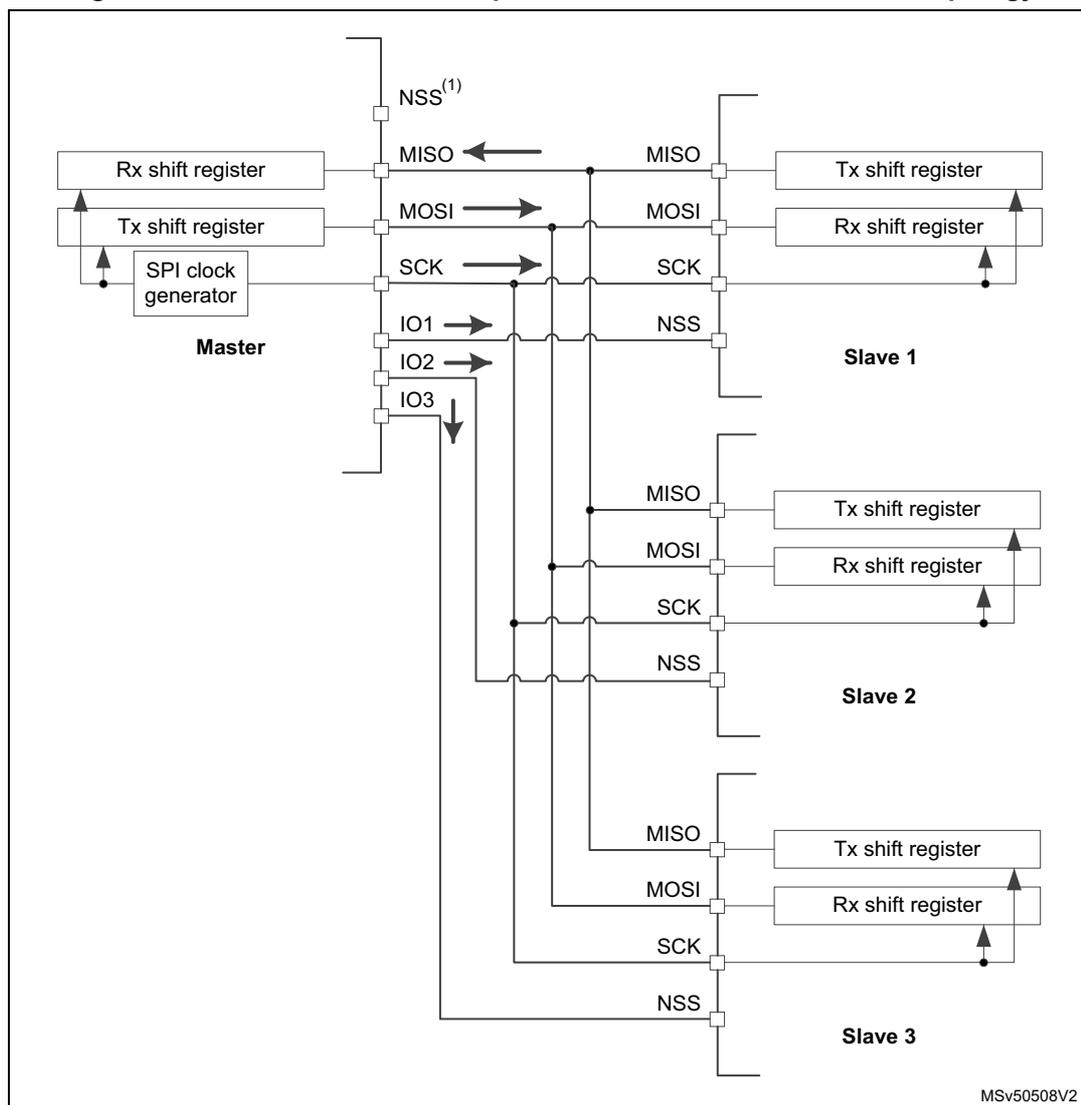

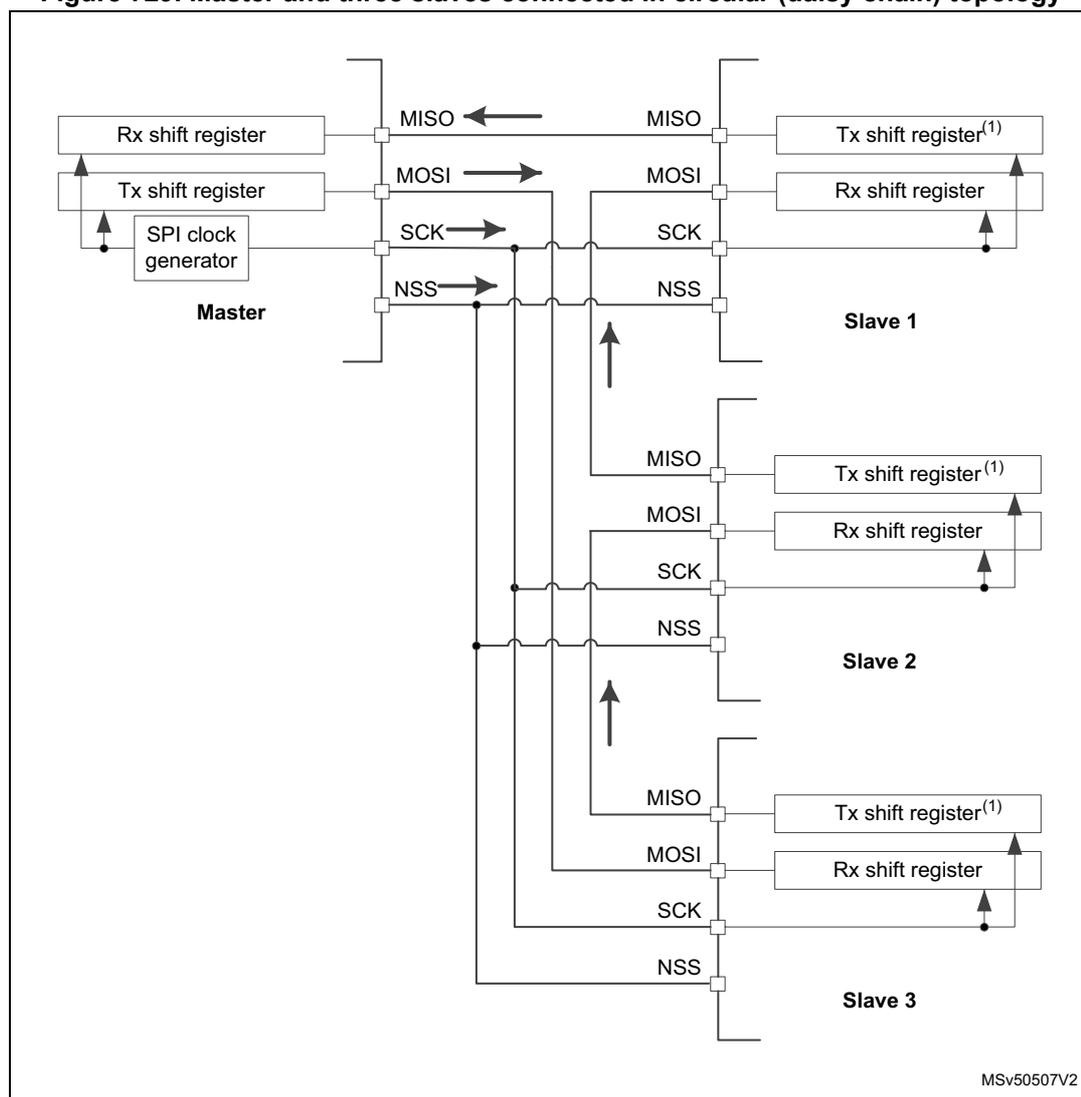

52.4.5 Standard multislave communication

In a configuration with two or more independent slaves, the master uses a star topology with dedicated GPIO pins to manage the chip select lines for each slave separately (see Figure 728 ).

The master must select one of the slaves individually by pulling low the GPIO connected to the slave NSS input (only one slave can control data on a common MISO line at a given time).

When this is done, a communication between the master and the selected slave is established. In addition to the simplicity, the advantage of this topology is that a specific SPI configuration can be applied for each slave as all the communication sessions are performed separately just within a single master-slave pair. Optionally, when there is no need to read any information from slaves, the master can transmit the same information to the multiple slaves.

Figure 728. Master and three independent slaves connected in star topology

- 1. The master single NSS pin hardware output functionality cannot support this topology (to be replaced by a set of GPIOs under software control). The NSS pin is free for other application uses (such as GPIO or other alternate functions). Refer to Section 52.4.7 for details.

- 2. If the application cannot ensure that no more than a single NSS active signal is provided by the master at a given time, it is better to configure the MISO pins in an open-drain configuration with an external pull-up on the MISO line to prevent conflicts between the interconnected outputs of the slaves. Else, a push-pull configuration can be applied without an extra resistor (see I/O alternate function input/output (GPIO) section).

- 3. The RDY signals can be read by the master from the slaves optionally.

The master can handle the SPI communication with all the slaves in time when a circular topology is applied (see Figure 729 ). All the slaves behave like simple shift registers applied in serial chain under control of common slave select (NSS) and clock (SCK) signals. All the information is shifted simultaneously around the circle while returning back to the master. Sessions have fixed the length where the number of data frames transferred by the master is equal to the number of slaves.

Then when a first data frame is transferred in the chain, the master just sends the information dedicated for the last slave node in the chain, via the first slave node input, while the first information received by the master comes from the last node output at this time.

Correspondingly, the last transferred data finishing the session is dedicated for the first slave node while its first outgoing data just reaches the master input, after its circling around the chain passing through all the other slaves during the session.

The data format configuration and clock setting must be the same for all the nodes in the chain in this topology. As the receive and transmit shift registers are separated internally, a trick with intentional underrun must be applied to the TxFIFO slaves when the information is transferred between the receiver and the transmitter by hardware.

In this case, the transmission underrun feature is configured in a mode repeating the last received data frame (UDRCFG=1). A session can start optionally with a single data pattern written into the TxFIFO by each slave (usually slave status information is applied) before the session starts. In this case, the underrun happens in fact after this first data frame is transferred. To be able to clear the internal underrun condition immediately and restart the session by the TxFIFO content again, the user must disable and enable the SPI between the sessions and must fill the TxFIFO by a new single data pattern (to overcome the propagating delay of the clearing raised in case the underrun is cleared in a standard way by the UDRC bit).

Figure 729. Master and three slaves connected in circular (daisy chain) topology

- 1. The underrun feature is used by the slaves in this configuration when the slaves are able to transmit data received previously into the Rx shift register once their TxFIFOs become empty.

- 2. The RDY signals can be read by the master optionally, either separately or configured as open drain outputs (while RDIOP = 0) and connected with a pull-up resistor as a common chain ready status overdriven by the slowest device.

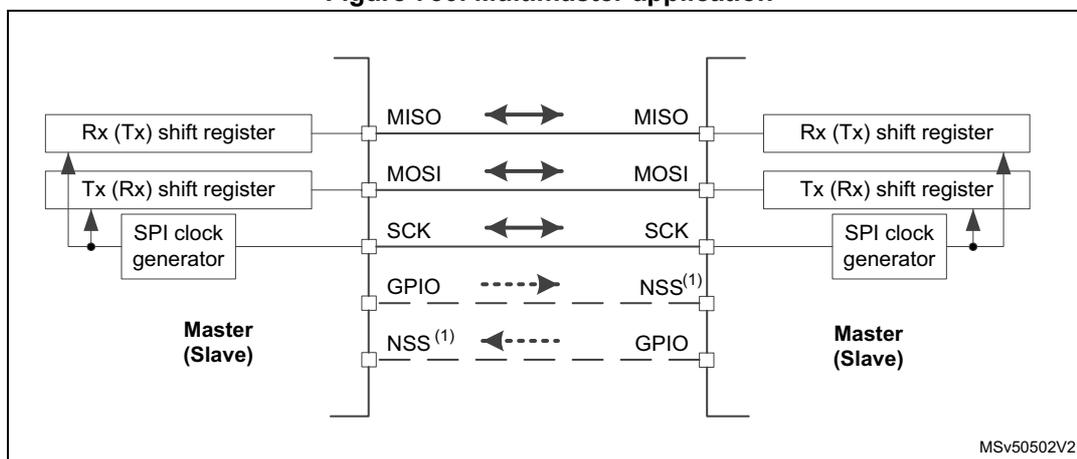

52.4.6 Multimaster communication

Unless the SPI bus is not designed primarily for a multimaster capability, the user can use a built-in feature that detects a potential conflict between two nodes trying to master the bus at the same time. For this detection, the NSS pin is configured in hardware input mode. The connection of more than two SPI nodes working in this mode is impossible, as only one node can apply its output on a common data line at a given time.

When the nodes are not active, both stay in slave mode by default. Once a node wants to overtake control on the bus, it switches itself into master mode and applies active level on the slave select input of the other node via the dedicated GPIO pin. After the session is

complete, the active slave select signal is released and the node mastering the bus temporarily returns back to passive slave mode waiting for the next session to start.

If both nodes raise their mastering request at the same time, a bus conflict event appears (see mode fault MODF event). The user can apply some simple arbitration process (for example postpone the next attempt by different predefined timeouts applied to both nodes).

Figure 730. Multimaster application

The diagram illustrates a multimaster SPI configuration with two nodes. Each node contains an 'Rx (Tx) shift register', a 'Tx (Rx) shift register', and an 'SPI clock generator'. The nodes are connected via four lines: MISO (Master In Slave Out), MOSI (Master Out Slave In), SCK (Serial Clock), and NSS (Slave Select). The MISO, MOSI, and SCK lines are bidirectional, indicated by double-headed arrows. The NSS line is also bidirectional, with one node's NSS pin connected to the other node's GPIO pin and vice versa. The left node is labeled 'Master (Slave)' and the right node is labeled 'Master (Slave)'. The diagram is labeled 'MSv50502V2' in the bottom right corner.

- 1. The NSS pin is configured at hardware input mode at both nodes. Its active level enables the MISO line output control as the passive node is configured as a slave.

- 2. The RDY signal is not used in this communication.

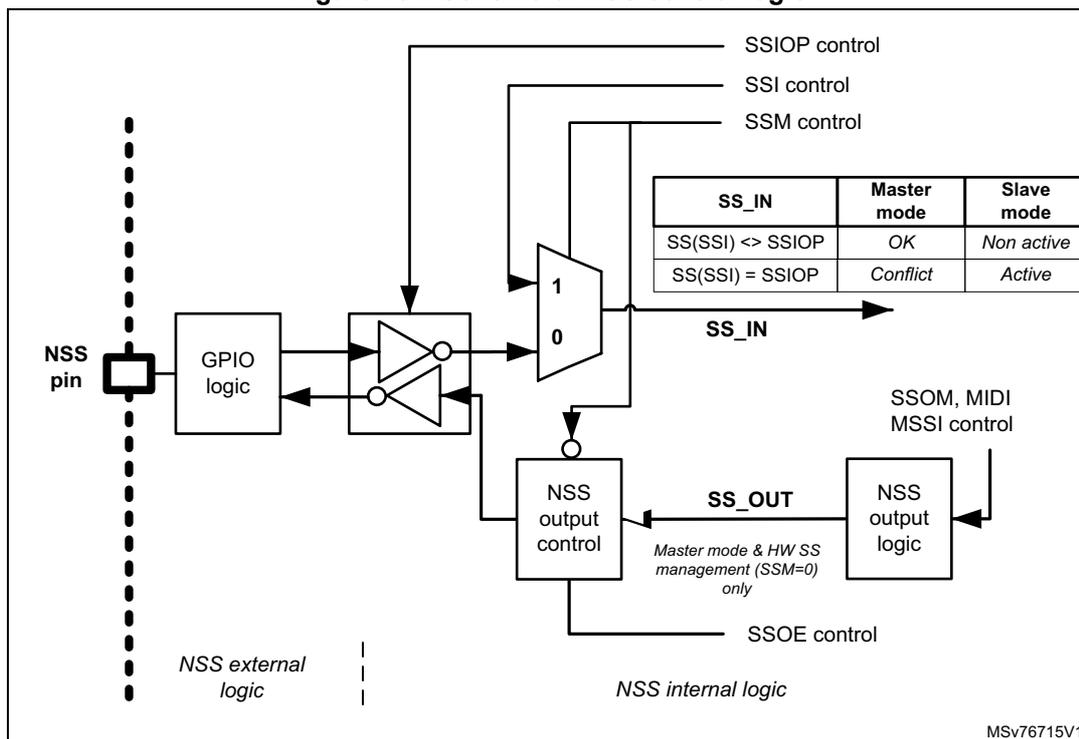

52.4.7 Slave select (NSS pin) management

In slave mode, the NSS works as a standard 'chip select' input and lets the slave communicate with the master. In master mode, the NSS can be used either as an output or an input. As an input it can prevent a multimaster bus collision, and as an output it can drive a slave select signal of a single slave. The NSS signal can be managed internally (software management of the NSS input) or externally when both the NSS input and output are associated with the NSS pin (hardware slave select management). The user can configure which level of this input/output external signal (present on the NSS pin) is considered as active by the SSIOP bit setting. NSS level is considered as active if it is equal to SSIOP.

The hardware or software slave select management can be set using the SSM bit in the SPI_CFG2 register:

- • Software slave select management (SSM = 1) : in this configuration, slave select information is driven internally by the SSI bit value in the SPI_CR1 register. The external NSS pin is free for other application uses (such as GPIO or other alternate functions).

- •

Hardware slave select management (SSM = 0)

: in this case, there are two possible configurations. The configuration used depends on the NSS output configuration (SSOE bit in the SPI_CFG2 register).

- – NSS output enable (SSOE = 1) : this configuration is only used when the MCU is set as master. The NSS pin is managed by the hardware. The functionality is tied to CSTART and EOT control. As a consequence, the master must apply the proper TSIZE > 0 setting to control the NSS output correctly. Even if SPI AF is not applied at the NSS pin (it can be used as a standard GPIO then), keep anyway SSOE = 1 to ensure the default NSS input level and prevent any mode fault

evaluation at the input of the master NSS internal logic applicable at a multimaster topology exclusively.

- a) When SSOM = 0 and SP = 000, the NSS signal is driven to the active level as soon as the master transfer starts (CSTART = 1) and it is kept active until its EOT flag is set or the transmission is suspended.

- b) When SP = 001, a pulse is generated as defined by the TI mode.

- c) When SSOM = 1, SP = 000 and MIDI > 1 the NSS is pulsed inactive between data frames, and kept inactive for a number of SPI clock periods defined by the MIDI value decremented by one (from 1 to 14).

- d) NSS input is forced to nonactive state internally at master to prevent any mode fault.

- – NSS output disable (SSM = 0, SSOE = 0):

- a) If the microcontroller is acting as the master on the bus, this configuration allows multimaster capability. If the NSS pin is pulled into an active level in this mode, the SPI enters master mode fault state and the SPI device is automatically reconfigured in slave mode (MASTER = 0).

- b) In slave mode, the NSS pin works as a standard 'chip select' input and the slave is selected while the NSS line is at its active level.

Note: The purpose of automatic switching into slave mode when a mode fault occurs is to avoid the possible conflicts on data and clock lines. As the SPE is automatically reset in this condition, both Rx and Tx FIFOs are flushed and current data is lost.

When the SPI slave is enabled in the hardware slave select management mode, all the transfers are ignored even in case of the NSS is found at active level. They are ignored until the slave detects a start of the NSS signal (transition from nonactive to active level) just synchronizing the slave with the master. This is because the hardware management mode cannot be used when the external NSS pin is fixed. There is no such protection in the slave select software management. Then the SSI bit must be changed when there is no traffic on the bus and the SCK signal is in idle state level between transfers exclusively in this case.

Figure 731. Scheme of NSS control logic

The diagram illustrates the internal logic for NSS control. On the left, an 'NSS pin' is connected to 'GPIO logic', which is part of 'NSS external logic'. The 'GPIO logic' output is inverted and connected to a multiplexer. The multiplexer's inputs are 'SSIOP control' (input 1) and 'SSI control' (input 0). The output of the multiplexer is 'SS_IN'. A table to the right defines the modes for 'SS_IN':

| SS_IN | Master mode | Slave mode |

|---|---|---|

| SS(SSI) <> SSIOP | OK | Non active |

| SS(SSI) = SSIOP | Conflict | Active |

The 'SS_IN' signal is also connected to 'NSS output control'. The 'NSS output control' block is part of 'NSS internal logic' and receives 'SSOM, MIDI, MSI control' and 'SSOE control'. It outputs 'SS_OUT' to 'NSS output logic', which in turn drives the 'NSS pin'.

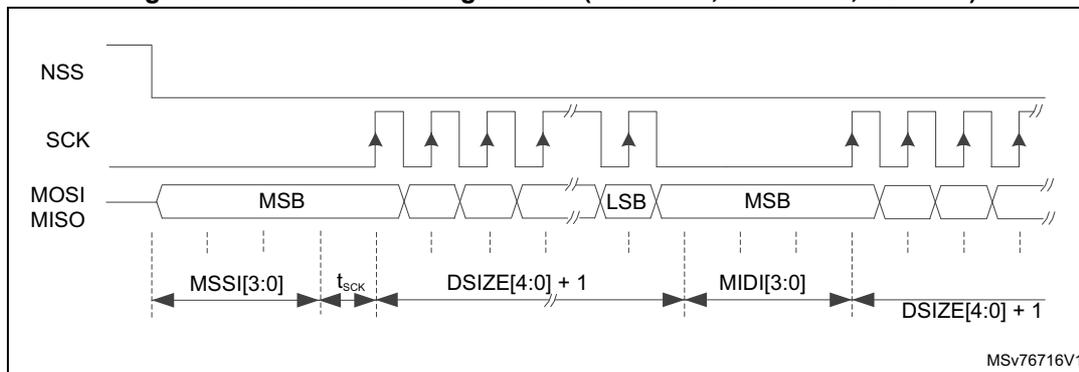

When the hardware output NSS control is applied (SSM = 0, SSOE = 1), by configuration of the MIDI[3:0] and MSI[3:0] bitfields, the user can control the timing of the NSS signal between data frames and can insert an extra delay at the beginning of every transfer (to separate the NSS and clock starts). This can be useful when the slave needs to slow down the flow to obtain sufficient room for correct data handling (see Figure 732).

Figure 732. Data flow timing control (SSOE = 1, SSOM = 0, SSM = 0)

The timing diagram shows the relationship between the NSS, SCK, MOSI, and MISO signals during a data transfer. The NSS signal is shown as a horizontal line. The SCK signal is a periodic square wave. The MOSI and MISO signals are shown as a sequence of data frames, with the Most Significant Bit (MSB) and Least Significant Bit (LSB) indicated. The timing parameters are defined as follows:

- MSSI[3:0] : The time interval from the start of the first SCK pulse to the start of the first data bit (MSB).

- t sck : The period of the SCK signal.

- DSIZE[4:0] + 1 : The number of data bits in a frame.

- MIDI[3:0] : The time interval from the start of the first data bit (MSB) to the start of the next data frame.

- 1. MSI[3:0] = 0011, MIDI[3:0] = 0011 (SCK flow is continuous when MIDI[3:0] = 0).

- 2. CPHA = 0, CPOL = 0, SSIOP = 0, LSBFRST = 0.

Additionally, setting the SSOM bit invokes a specific mode, which interleaves pulses between data frames if there is a sufficient space to provide them (MIDI[3:0] must be set greater than one SPI period). Some configuration examples are shown in Figure 733.

Figure 733. NSS interleaving pulses between data (SSOE = 1, SSOM = 1, SSM = 0)

![Timing diagram for SPI mode I. Shows NSS (active low), SCK (idle low), MOSI, and MISO signals. Data is MSB first. Timing parameters: MSSI[3:0], t_SCK, DSIZE[4:0]+1, MIDI[3:0]. NSS pulses high between data frames for a duration of MIDI[3:0]-1. Timing diagram for SPI mode II. Similar to mode I but with CPHA=1. The first SCK edge is delayed by t_SCK/2. NSS pulses high between data frames. Timing diagram for SPI mode III. Shows NSS (active high), SCK (idle high), MOSI, and MISO signals. Data is LSB first. Timing parameters: MSSI[3:0], t_SCK, DSIZE[4:0]+1, MIDI[3:0]. NSS pulses low between data frames. Timing diagram for SPI mode IV. Similar to mode III but with CPHA=1. The first SCK edge is delayed by t_SCK/2. NSS pulses low between data frames.](/RM0481-STM32H523-33-562-63-573/7cb870ca6bdffdcb24e842848fed20c5_img.jpg)

I. CPHA=0, CPOL=0, SSIOP=0, LSBFRST=0

II. CPHA=1, CPOL=0, SSIOP=0, LSBFRST=0

III. CPHA=0, CPOL=1, SSIOP=1, LSBFRST=1

IV. CPHA=1, CPOL=1, SSIOP=1, LSBFRST=1

MSv76717V1

- 1. MSS[3:0] = 0010, MIDI[3:0] = 0010.

- 2. NSS interleaves between data when MIDI[3:0] > 1 wide of the interleaving pulse is always one SCK period less than the gap provided between the frames (defined by the MIDI parameter). If MIDI is set, the frames are separated by a single SCK period but no interleaving pulse appears on NSS.

52.4.8 Ready pin (RDY) management

The status of the slave capability to handle data can be checked on the RDY pin. By default, a low level indicates that the slave is not ready for transfer. The reason can be that the slave TxFIFO is empty, RxFIFO full or the SPI is disabled. An active level of the signal can be selected by the RDIOP bit. If the master continues or starts to communicate with the slave when it indicates a not ready status, it is highly probable that the transfer fails.

The logic to control the RDY output is rather complex, tied closely with the TSIZE and DSIZE settings. The RDY reaction is more pessimistic and sensitive to TxFIFO becoming nearly empty and/or RxFIFO nearly full during a frame transfer. This pessimistic logic is suppressed at the end of a transfer only when RDY stays active, despite TxFIFO becomes fully empty and/or RxFIFO becomes fully occupied. The target is to prevent any data corruption and inform the master in time that it is necessary to suspend the transfer temporarily until the next transferred data can be processed safely again. When the RDY signal input is enabled at master side, the master suspends the communication once the slave indicates not ready status. This prevents the master to complete the transfer of an ongoing frame, which just empties the slave TxFIFO or full fills its RxFIFO until a next data is written and/or read there (despite the frame still can be completed without any constraint). It can make a problem if the TSIZE = 0 configuration is applied at slave because slave then never evaluates the end of the transfer (which suppresses the not ready status just when the last data is sent). Then the user has to release the RxFIFO and/or write additional (even dummy) data to TxFIFO by software at slave side to release the not RDY signal, unblock ST master and so enable it to continue at the communication suspended at middle of a frame occasionally.

When RDY is not used by the master, it must be disabled (RDIOM = 0). Then an internal logic of the master simulates the slave status always ready. In this case, the RDIOP bit setting has no meaning.

Due to synchronization between clock domains and evaluation of the RDY logic on both master and slave sides, the RDY pin feature is not reliable and cannot be used when the size of data frames is configured shorter than 8 bits.

52.4.9 Communication formats

During SPI communication, receive and transmit operations are performed simultaneously. The serial clock (SCK) synchronizes the shifting and sampling of the information on the data lines. The communication format depends on the clock phase, the clock polarity, and the data frame format. To be able to communicate together, the master and slave devices must follow the same communication format and be synchronized correctly.

Clock phase and polarity controls

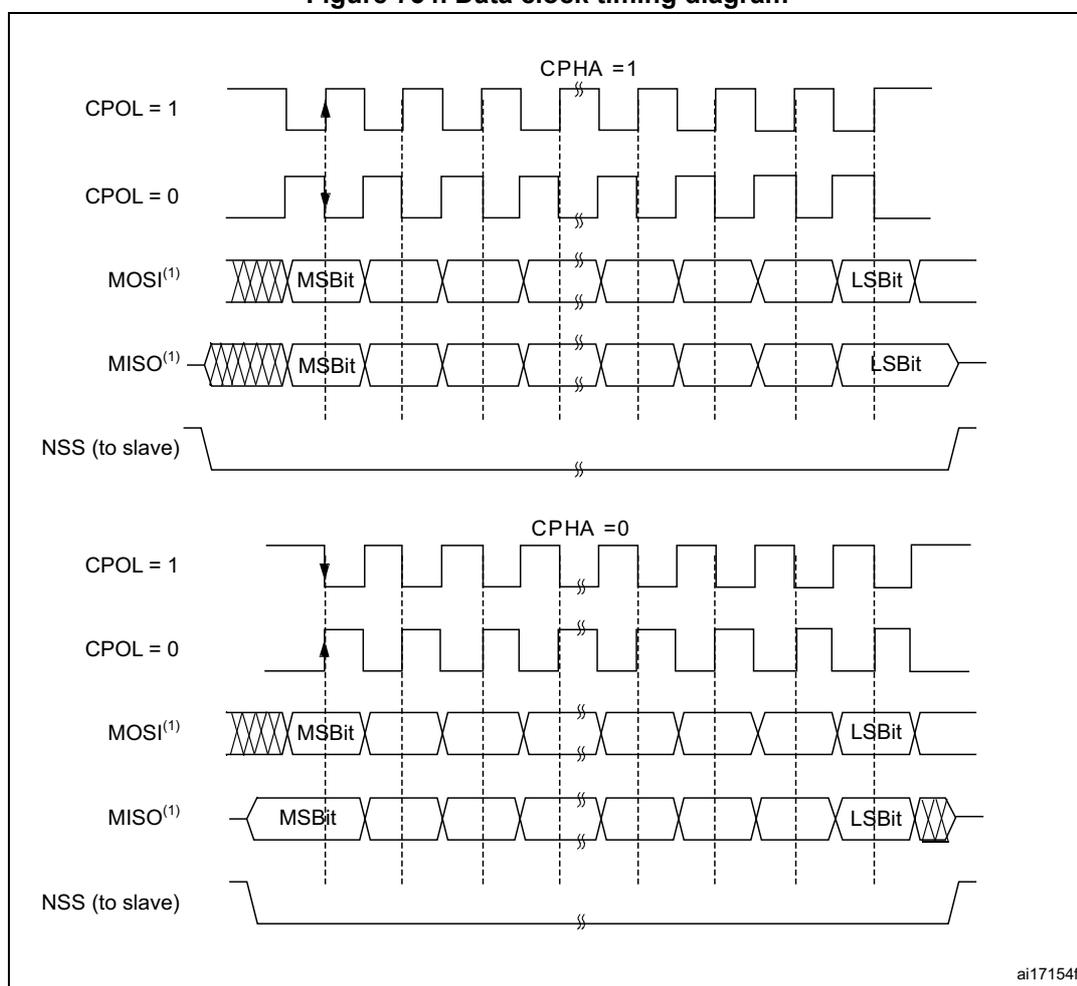

Four possible timing relationships can be chosen by software, using the CPOL and CPHA bits in the SPI_CFG2 register. The CPOL (clock polarity) bit controls the idle state value of the clock when no data is being transferred. This bit affects both master and slave modes. If CPOL is reset, the SCK pin has a low-level idle state. If CPOL is set, the SCK pin has a high-level idle state.

If the CPHA bit is set, the second edge on the SCK pin captures the first data bit transferred (falling edge if the CPOL bit is reset, rising edge if the CPOL bit is set). Data are latched on each occurrence of this clock transition type. If the CPHA bit is reset, the first edge on the SCK pin captures the first data bit transferred (falling edge if the CPOL bit is set, rising edge if the CPOL bit is reset). Data are latched on each occurrence of this clock transition type.

The combination of the CPOL (clock polarity) and CPHA (clock phase) bits selects the data capture clock edges (dotted lines in Figure 734).

Figure 734 shows an SPI full-duplex transfer with the four combinations of the CPHA and CPOL bits.

Note: Prior to changing the CPOL/CPHA bits the SPI must be disabled by resetting the SPE bit.

The idle state of SCK must correspond to the polarity selected in the SPI_CFG2 register (by pulling the SCK pin up if CPOL = 1 or pulling it down if CPOL = 0).

Figure 734. Data clock timing diagram

The diagram shows two timing diagrams for SPI full-duplex transfer. The top diagram is for CPHA = 1, and the bottom diagram is for CPHA = 0. Both diagrams show the relationship between the SCK signal (CPOL = 1 and CPOL = 0), MOSI (Master Out Slave In), MISO (Master In Slave Out), and NSS (to slave) signals. Data bits are labeled MSB (Most Significant Bit) and LSB (Least Significant Bit). The timing diagrams show the clock edges used for data latching. In the CPHA = 1 case, the first clock edge is a rising edge (for CPOL = 1) or a falling edge (for CPOL = 0). In the CPHA = 0 case, the first clock edge is a falling edge (for CPOL = 1) or a rising edge (for CPOL = 0). The data is latched on the second clock edge in the CPHA = 1 case and on the first clock edge in the CPHA = 0 case.

- 1. The order of data bits depends on the LSBFIRST bit setting.

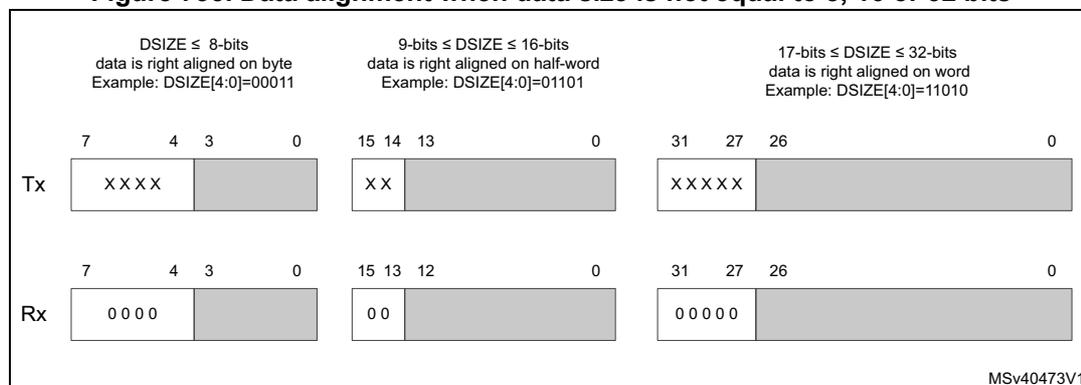

Data frame format

The SPI shift register can be set up to shift out MSB-first or LSB-first, depending on the value of the LSBFRST bit of the SPI_CFG2 register.

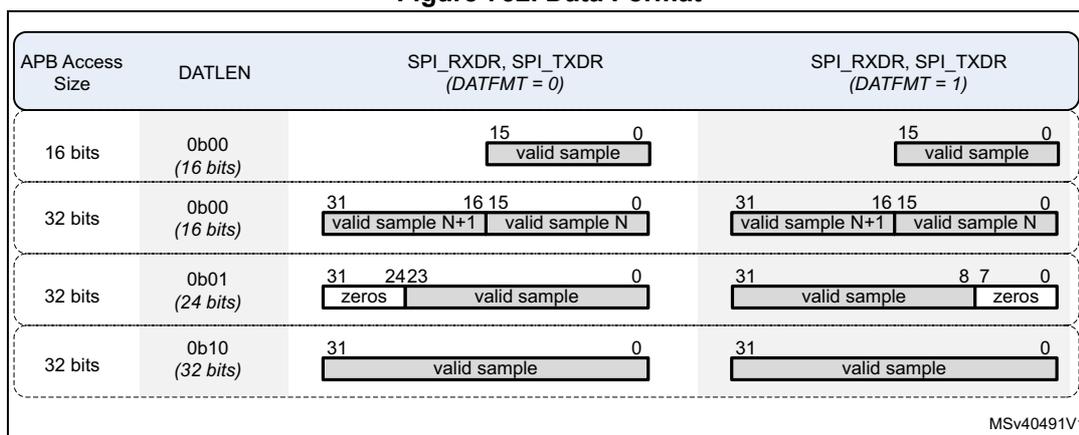

The data frame size is configured through the DSIZE bitfield of the SPI_CFG1 register to a range that depends on the SPI instance (see Section 52.3: SPI implementation ). The setting applies to both transmission and reception. The data bits in the SPI_TXDR/SPI_RXDR registers are right-aligned with 8, 16, or 32 bits, depending on the data size (see Figure 735 ). These registers can consequently be accessed by bytes, half-words, or words. FIFO accesses smaller than a single data are forbidden. When the FIFO occupancy flag is raised, a FIFO access greater than the FIFO threshold can lead to spurious data being read or written data being lost. When the access to/from the SPI_TXDR/SPI_RXDR registers is a multiple of the configured data size, data packing is applied automatically, while the lowest significant bits/bytes are communicated first. For more details, see Section 52.4.12: SPI data transmission and reception procedures .

Figure 735. Data alignment when data size is not equal to 8, 16 or 32 bits

| DSIZE ≤ 8-bits data is right aligned on byte Example: DSIZE[4:0]=00011 | 9-bits ≤ DSIZE ≤ 16-bits data is right aligned on half-word Example: DSIZE[4:0]=01101 | 17-bits ≤ DSIZE ≤ 32-bits data is right aligned on word Example: DSIZE[4:0]=11010 | ||||

| 7 | 4 3 0 | 15 14 13 | 0 | 31 27 26 | 0 | |

| Tx | X X X X | X X | X X X X X | |||

| Rx | 0 0 0 0 | 0 0 | 0 0 0 0 0 | |||

MSV40473V1

52.4.10 Configuring the SPI

The configuration procedure is almost the same for the master and the slave. For specific mode setups, follow the dedicated chapters. When a standard communication must be initialized, perform these steps:

- Write the proper GPIO registers: configure GPIO alternate functions at MOSI, MISO, SCK, NSS, and RDY pins if applied.

- Write into the SPI_CFG1 and SPI_CFG2 registers and set up the proper values of all ‘not reserved’ bits and bitfields, prior to enabling the SPI, with the following exceptions:

- The SSOM, MASRX, SSOE, RDIOM, MBR[2:0], BPASS, MIDI[3:0], MSSI[3:0] bits are taken into account in master mode only, the MSSI[3:0] bits take effect when the SSOE bit is set, the RDIOP bit takes no effect when the RDIOM bit is not set in master mode. When the slave is configured in TI mode, the MBR[2:0] setting is also considered.

- UDRCFG is taken into account in slave mode only.

- CRCSIZE[4:0] bitfield must be configured if CRCEN is set.

- CPOL, CPHA, LSBFRST, SSOM, SSOE, SSIOP, SSM, RDIOP, RDIOM, MSSI, and MIDI are not required in TI mode.

- e) Once the AFCNTR bit is set in the SPI_CFG2 register, all the SPI outputs start to be propagated onto the associated GPIO pins regardless of the peripheral enable. So, any later configuration changes of the SPI_CFG1 and SPI_CFG2 registers can affect the level of signals on these pins.

- 3. Write to the SPI_CR2 register to select the length of the transfer, if it is not known TSIZE must be programmed to zero.

- 4. Write to the SPI_CRPOLY and into the TCRCINI, RCRCINI, and CRC33_17 bits of the SPI_CR1 register to configure the CRC polynomial and CRC calculation if needed.

- 5. Configure DMA streams dedicated for the SPI Tx and Rx in DMA registers if the DMA streams are used (see Section 52.4.14: Communication using DMA (direct memory addressing) ).

- 6. Configure SSI, HDDIR, and MASRX in the SPI_CR1 register if required.

- 7. Program the IOLOCK bit in the SPI_CR1 register if the configuration protection is required (for safety).

52.4.11 Enabling the SPI

It is recommended to configure and enable the SPI slave before the master sends the clock. But there is no impact if the configuration and enabling procedure is done while traffic is ongoing on the bus, assuming that the NSS signal is managed by hardware at slave or kept inactive by the slave software when the software management of the NSS signal is applied (see Section 52.4.7 ). To prevent any risk of any data underrun, all the data to be sent have to be written to the slave transmitter data register before the master starts its clocking. The SCK signal must be settled to the idle state level corresponding to the selected polarity, before the SPI slave is selected by NSS, else the following transfer may be desynchronized.

When the SPI slave is enabled at the hardware slave select management mode, all the transfers are ignored even in case of the NSS is found at active level. They are ignored until the slave detects a start of the NSS signal (its transition from nonactive to active level) just synchronizing the slave with the master. That is why the hardware management mode cannot be used when the external NSS pin is fixed. There is no such protection at the slave select software management. In this case, the SSI bit must be changed when there is no traffic on the bus and the SCK signal is at idle state level between transfers exclusively in this case.

The master in full duplex (or in any transmit-only mode) starts to communicate when the SPI is enabled, the CSTART bit is set, and the TxFIFO is not empty, or with the next write to TxFIFO.

In any master receive-only mode, the master starts to communicate and the clock starts running after the SPI is enabled and the CSTART bit is set.

For handling DMA, see Section 52.4.14 .

52.4.12 SPI data transmission and reception procedures

The SPI can transfer data at a very high communication speed. Even though the data is FIFO buffered, handling a continuous data flow by servicing data frames individually leads to an enormous CPU or DMA load, in particular when the data size is small. This potentially leads to a significant limitation of the overall system performance, as well as communication errors such as data overrun or underrun that may be raised when the system latencies in servicing requests become comparable to single data frame transfer time.

The SPI offers advanced hardware control features to prevent these issues from occurring:

- • Decreasing the number of events requiring service by collecting the data frames into larger data packets

The number of data frames per packet (FIFO threshold) can be configured. The complete data packet generates a FIFO occupancy event, which is then handled within a single, compact, service.

- • Decreasing the number of CPU execution cycles required for the service, by applying the appropriate

data access

:

- – The widest access to the SPI data registers must be applied. This allows cumulative data to be handled by a single register read or write operation (data packing).

- – The number of read/write accesses necessary to complete the data packet must be aligned with the data frame size and the FIFO threshold.

- • Concurrent read and write services to handle full-duplex data flow based on common FIFO occupancy events.

- • Embedded hardware data counters to define the exact number of data involved in transfers.

Note: Using these features is optional. Nothing prevents the application from handling the data flow frame by frame.

The following sections give more details and describe specific cases for using these advanced hardware control features to handle data transfers.

Data packet control

The data frame size (number of bits in the frame) is defined through the DSIZE bitfield of the SPI_CFG1 register. The number of data frames per packet can be configured by selecting the FIFO threshold through the FTHLV bitfield of the SPI_CFG1 register. If the threshold value is set to zero, each completed data frame raises the FIFO occupancy event. The data packet occupancy must not exceed half of the FIFO size, which depends on the SPI instance of the product. The FIFO capacity (multiple of 8 bits) is consumed according to the following rules, depending on the data frame size:

- • Data frames from 4 to 8 bits occupy one byte of the FIFO.

- • Data frames from 9 to 16 bits occupy two bytes of the FIFO.

- • Data frames from 17 to 24 bits occupy three bytes of the FIFO.

- • Data frames from 25 to 32 bits occupy four bytes of the FIFO.

For example, if the FIFO capacity is 16 bytes, it accommodates up to five 24-bit frames. In this case, the data packet configuration must not exceed two data frames.

The SPI features two separate FIFOs to handle the reception and transmission data flow, the RxFIFO, and the TxFIFO. Their content can be handled by monitoring the occupancy

flags RXP, TXP, and DXP of the SPI_SR register according to the SPI mode (duplex or simplex):

- • If RXP is set, at least one complete data packet can be read from the RxFIFO.

- • If TXP is set, at least one complete data packet can be written to the TxFIFO.

- • If DXP is set, at least one complete data packet can be read from the RxFIFO and written to the TxFIFO at full-duplex mode.

These flags can be polled by software, or they can trigger an interrupt and/or a DMA request (if enabled through the RXPIE, TXPIE, and DXPIE bits of the SPI_EIR register or the RXDMAEN and TXDMAEN bits of the SPI_CFG1 register).

Once an occupancy flag is set, the software or the DMA must read and/or write a complete data packet before checking the flag again to verify if the next packet can be handled. This cycle can be repeated until the corresponding flag is read at zero.

Both RxFIFO and TxFIFO contents are flushed and cannot be accessed when the SPI is disabled (SPE cleared in the SPI_CR1 register).

Data packing versus data register access control

The content of the RxFIFO and TxFIFO can be accessed by reading/writing from/to the SPI data registers SPI_RXDR and SPI_TXDR, respectively. A read access from the SPI_RXDR register returns the oldest values stored in the RxFIFO that have not been read yet. A write access to the SPI_TXDR register stores the data written at the end of the send queue in the TxFIFO.

These data registers can be accessed by 8-, 16-, or 32-bit read and write CPU instructions, forced by the register address casting applied by the software. Data packing is performed automatically by hardware if the data access applied by the software is a multiple of the data size. It allows handling more than one data in parallel in a single data register access. Then the SPI operates using the lowest significant byte or half-word first. FIFO data accesses of less than the configured data size are forbidden. To avoid spurious data being read or written data being lost, a complete data packet (configured through the FIFO threshold) must be serviced when the corresponding FIFO occupancy flag is set. If the data pattern is not byte-, half-word, or word-aligned, only the valid data bits are stored right-aligned to the FIFO and transferred on the bus. Unused bits are discarded on the transmitter side and padded with zeros on the receiver side.

For example, if the data frame size fits into one byte, the data packing is used automatically when a 16-bit or 32-bit read/write access is performed by software from/to the SPI_RXDR/SPI_TXDR register. In this case, two respectively four data are handled by a single 16-bit respectively 32-bit access. Additionally, if such data frames are grouped into packets of four via the FIFO threshold setting, the packet to be serviced is signalized by raising the corresponding FIFO occupancy flag (TXP, RXP, or DXP). If the instance FIFO threshold is sufficient, a packet containing eight 8-bit data frames can be handled by two consecutive 32-bit accesses upon the same single threshold event. The most efficient data handling is achieved when the data packet size (defined by DSIZE and FTHLV bitfields) is aligned with the read/write access from/to the data registers.

Concurrent read and write services

In full-duplex mode, both TxFIFO and RxFIFO packet occupancies can be monitored through a common FIFO flag (DXP). When the DXP flag is set, the application performs the specified number of writes to SPI_TXDR to upload the content of one entire data packet for transmission, followed by the same number of reads from SPI_RXDR to download the

content of one received data packet. Once one data packet is uploaded and one packet is downloaded, the application software or the DMA checks again the DXP flag and repeats the data packet read and write operation sequence until DXP is read as zero.

The drawback of services based on DXP exclusively is that servicing the TxFIFO is delayed on purpose due to the SPI nature since the TXP events precedes the RXP ones. To allow continuous SCK clock flow on the master side and prevent underrun on the slave side, it is recommended to prefill a few data ahead to the TxFIFO at the transfer start, and wait until the transfer is complete to read the last received data.

Hardware data counter

If a hardware data counter is used (TSIZE bitfield of the SPI_CR2 register set to a nonzero value), the application software does not need to calculate the remaining number of data to be handled. The end of transfer automatically controls the CRC, as well as the hardware slave select management, when used. The user application does not need to ensure that the overall number of data is a multiple of the packet size. If the last data packet is incomplete, it is serviced in the same way as any full packet. The unused part of this last packet is not handled by the peripheral. Only the valid data are written into the TxFIFO and/or read from the RxFIFO, and the redundant writes and reads are discarded. When the hardware counter reaches zero, the EOT flag is raised, and the RXP flag is not set for the last data packet. If the last packet is not aligned with the packet size, the TXP and EOT occupancy events are not related to the configured packet size but to the number of remaining data calculated by hardware.

If TSIZE is kept at zero (for example due to an unpredictable number of data), only the number of transferred data corresponding to the FIFO thresholds is supported. If some data are not aligned with the configured packet size, they may remain pending and available in the RxFIFO. In this case, the FTHLV level is not reached and the RXP flag is not set. Then the number of remaining received data frames in the RxFIFO is indicated by the RXWNE and RXPLVL bitfields of the SPI_SR register. Nevertheless, the application software can still read the complete data packet from the RxFIFO and the redundant data are read as zero. To prevent such an unaligned data reception, the user must configure the FIFO threshold to a single data (FTHLV = 0). In this case, each data frame is serviced by its own RXP occupancy event.

Data transfer handling

Data are transferred using MOSI and MISO lines, depending on the SPI communication mode and associated configuration. The mode is configured through the COMM[1:0] bitfield of the SPI_CFG2 register. The HDDIR bit of the SPI_CR1 register controls the data flow direction in half-duplex mode. The communication flow is handled by the master via the NSS and SCK signals. The slave selected for the communication is fully subordinated to the master communication activity, no matter if it handles the data flow on time or not. The slave can only temporarily suspend the master communication by using the RDY signal. The active levels of RDY and NSS signals can be changed, or MISO and MOSI functionality swapped (via the RDIOP, SSIOP and IOSWP bits of the SPI_CFG2 register).

The SPI master transmitter can operate in full-duplex, simplex, or half-duplex mode. In full-duplex mode, data are received synchronously. The master starts the data transfer once the CSTART bit of the SPI_CR1 register is set, provided the SPI is enabled and the TxFIFO

content is not empty. The master then provides the serial clock signal continuously on the SCK pin until:

- • The total number of required data programmed in TSIZE is transferred, or

- • The transfer is suspended.

An automatic temporary suspension of the master transmission occurs when:

- • The slave does not assert the RDY signal, if it is used, or

- • The TxFIFO becomes empty, or

- • In full-duplex mode, the RxFIFO becomes full while the automatic suspension is enabled (MASRX set in the SPI_CR1 register).

When an automatic suspension occurs, the master stops providing the clock, and the transfer proceeds depending on the cause of the suspension, when:

- • The slave asserts RDY.

- • The master software or the DMA writes additional data to TxFIFO.

- • In full-duplex mode, the master software or the DMA releases the RxFIFO to enable it to accommodate new data.

The SPI master can receive data only when it operates in simplex receiver or half-duplex receiver mode. In these modes, the master starts the data transfer when the SPI is enabled, and the transfer is released by setting the CSTART bit. The serial clock signal is then provided continuously on the SCK pin by the master until:

- • The total number of required data programmed in TSIZE is received, or

- • The transfer is suspended by the master.

An automatic temporary suspension of the reception occurs when:

- • The slave does not assert the RDY signal, if it is used, or

- • The RxFIFO becomes full while the automatic suspension is enabled (MASRX bit set in the SPI_CR1 register).

When an automatic suspension occurs, the master stops providing the clock and the transfer proceeds depending on the cause of the suspension, when:

- • The slave asserts RDY.

- • The master software or the DMA releases the RxFIFO to enable it in order to accommodate new data.

A preferable way to terminate a transfer is to program the TSIZE bitfield to generate an EOT event. Hardware NSS signal or CRC handshake can then be controlled. To restart the internal state machine properly, it is recommended to disable the SPI and enable it again when the transfer is complete, even if the SPI configuration is not changed.

A transfer can be suspended at any time by setting the CSUSP bit of the SPI_CR1 register, which clears the CSTART bit. This software suspension control ensures the completion of any ongoing data frame. To restart the internal state machine properly, the SPI must be disabled and enabled again before the next transfer starts.

Oppositely, a temporary automatic suspension controlled by hardware typically results in a frozen and incomplete data frame transfer. This depends on baud rate setting, but usually, due to internal synchronization delays, the SCK signal stops when a few bits from the next data frame are already transferred on the bus. Once the suspension is released, the data frame transmission completes by transferring the remaining bits. That is why this automatic suspension is not quite reliable when the data frame size is less than eight bits. When shorter data frames are used, to prevent any data loss and assure proper RDY and/or

MASRX operation, the user can interleave and so extend the transfer time by inserting additional dummy clock cycles so that the period for a single data frame is higher or equal to eight SCK duration. This is done by setting the MIDI[3:0] bitfield of the SPI_CFG2 register.

Caution: If the SPE bit is cleared in master mode while the transfer is ongoing without any suspension, the clock is stopped even if the current frame transmission is not complete, and the content of the FIFOs is flushed and lost.

52.4.13 Disabling the SPI

To disable the SPI, it is mandatory to follow the disable procedures described in this paragraph.

In the master mode, it is important to do this before the system enters a low-power mode when the peripheral clock is stopped, otherwise, ongoing transfers may be corrupted.

In slave mode, the SPI communication can continue when the spi_pclk and spi_ker_ck clocks are stopped, without interruption, until any end of communication or data service request condition is reached. The spi_pclk can generally be stopped by setting the system into Stop mode. Refer to the RCC section for further information.

The master in full-duplex or transmit-only mode can finish any transfers when it stops providing data for transmission. In this case, the clock stops after the last data transfer. TXC flag can be polled (or interrupt enabled with EOTIE = 1) in order to wait for the last data frame to be sent.

When the master is in any receive-only mode, to stop the peripheral, the SPI communication must first be suspended, by setting the CSUSP bit.

The data received but not read remain stored in RxFIFO when the SPI is suspended.

After such a software suspension, SPI must always be disabled to restart the internal state machine properly.

When SPI is disabled, RxFIFO is flushed. To prevent losing unread data, the user must ensure that RxFIFO is empty when disabling the SPI, by reading all remaining data (as indicated by the RXP, RXWNE, and RXPLVL fields in the SPI_SR register).

The standard disable procedure is based on polling EOT and/or TXC status to check if a transmission session is (fully) completed. This check can be done in specific cases, too, when it is necessary to identify the end of ongoing transfers, for example:

- • When the master handles the NSS signal by a GPIO not related to SPI (for example at case of multislave star topology) and it has to provide a proper end-of-NSS pulse for the slave, or

- • When transfers from DMA or FIFO are completed while the last data frame or CRC frame transfer is still ongoing in the peripheral bus.

When TSIZE > 0, EOT and TXC signals are equal so polling of EOT is reliable at whatever SPI communication mode to check the end of the bus activity. When TSIZE = 0, the user has to check TXC, SUSP, or FIFO occupancy flags according to the applied SPI mode and the way of the data flow termination.

The correct disable procedure in master mode, except when receive-only mode is used, is:

- 1. Wait until TXC = 1 and/or EOT = 1 (no more data to transmit and last data frame sent). When CRC is used, it is sent automatically after the last data in the block is processed.

TXC/EOT is set when the CRC frame is complete in this case. When a transmission is suspended the software has to wait until the CSTART bit is cleared.

- 2. Read all RxFIFO data (until RXWNE = 0 and RXPLVL = 00).

- 3. Disable the SPI (SPE = 0).

The correct disable procedure for master receive-only modes is:

- 1. Wait on EOT or break the receive flow by suspending SPI (CSUSP = 1).

- 2. Wait until SUSP = 1 (the last data frame is processed) if the receive flow is suspended.

- 3. Read all RxFIFO data (until RXWNE = 0 and RXPLVL = 00).

- 4. Disable the SPI (SPE = 0).

In slave mode, any ongoing data are lost when disabling the SPI.

Controlling the I/Os

As soon as the SPI is disabled, the associated and enabled AF outputs can still be driven by the device depending on the AFCNTR bit of the SPI_CFG2 register. When active output control is applied (AFCNTR = 1) and SPI has just been disabled (SPE = 0), the enabled outputs associated with SPI control signals (like NSS and SCK at master and RDY at slave) can immediately toggle to inactive level (according to SSIOP and CPOL settings at master and RDIOP at slave respectively). Instead, the data line output (MOSI at master and MISO at slave) can immediately change its level depending on the actual TxFIFO content, with the effect of potentially making invalid and no more guaranteed the value of the latest transferred bit on the bus. If necessary, the user has to take care about proper data hold time at the data line and avoid any eventual fast SPI disable just after the last data transfer is complete.

Note: Despite stability of the latest bit is guaranteed by design during the sampling edge of the clock, some devices can require even extension of this data bit stability interval during the sampling. It can be done, for example by inserting a small software delay between EOT event occurrence and SPI disable action.

52.4.14 Communication using DMA (direct memory addressing)

To operate at its maximum speed and to facilitate the data register read/write process required to avoid overrun, the SPI features a DMA capability, which implements a simple request/acknowledge protocol.

A DMA access is requested when the TXDMAEN or RXDMAEN enable bits of the SPI_CFG1 register are set. Separate requests must be issued to the Tx and Rx buffers to fulfill the service of the defined packet.

- • In transmission, a series of DMA requests is triggered each time TXP is set. The DMA then performs a series of writes to the SPI_TXDR register.

- • In reception, a series of DMA requests is triggered each time RXP is set. The DMA then performs a series of reads from the SPI_RXDR register. When EOT is set at the end of the transfer and the last data packet is incomplete, then DMA request is activated automatically according to RXWNE and RXPLVL[1:0] setting to read the rest of data.

If the SPI is programmed in receive-only mode, UDR is never set.

If the SPI is programmed in a transmit mode, TXP and UDR can be eventually set at slave side, because transmit data may not be available. In this case, some data are sent on the TX line according with the UDR management selection.

When the SPI is used at a simplex mode, the user must enable the adequate DMA channel only while keeping the complementary unused channel disabled.

If the SPI is programmed in transmit-only mode, RXP and OVR are never set.

If the SPI is programmed in full-duplex mode, RXP and OVR are eventually set, because received data are not read.

In transmission mode, when the DMA or the user has written all the data to be transmitted (the TXTF flag is set in the SPI_SR register), the EOT (or TXC at case TSIZE = 0) flag can be monitored to ensure that the SPI communication is complete. This is required to avoid corrupting the last transmission before disabling the SPI or before disabling the spi_pclk in master mode. The software must first wait until EOT = 1 and/or TXC = 1.

When starting communication using DMA, to prevent DMA channel management raising error events, these steps must be followed in order:

- 1. Enable the DMA Rx buffer in the RXDMAEN bit of the SPI_CFG1 register, if DMA Rx is used.

- 2. Enable DMA requests for Tx and Rx in DMA registers, if the DMA is used.

- 3. Enable the DMA Tx buffer in the TXDMAEN bit of the SPI_CFG1 register, if DMA Tx is used.

- 4. Enable the SPI by setting the SPE bit.

To close communication, it is mandatory to follow these steps in order:

- 1. Disable DMA requests for Tx and Rx in the DMA registers, if the DMA issued.

- 2. Disable the SPI by following the SPI disable procedure.

- 3. Disable DMA Tx and Rx buffers by clearing the TXDMAEN and RXDMAEN bits of the SPI_CFG1 register, if DMA Tx and/or DMA Rx are used.

Data packing with DMA

If the transfers are managed by DMA (TXDMAEN and RXDMAEN set in the SPI_CFG1 register) the packing mode is enabled/disabled automatically depending on the PSIZE value configured for SPI TX and the SPI RX DMA channel.

The packing mode is enabled if the DMA channel PSIZE value is a multiple of the data size. Then the DMA automatically manages the sequences of write and read operations to/from the SPI data registers, based on FIFO occupancy flags, and depending on the FIFO threshold and data size configurations.

The DMA completes the transfer automatically according to the TSIZE field setting, whatever the data packing mode used, and even if the number of data to transfer is not a multiple of the DMA data size (16 bits or 32 bits) while the frame size is smaller.

Alternatively, the last data frames can be written by software, in the single/unpacked mode.

Configuring any DMA data access to less than the configured data size is forbidden. One complete data frame must be always accessed at minimum.

52.5 SPI specific modes and control

52.5.1 TI mode

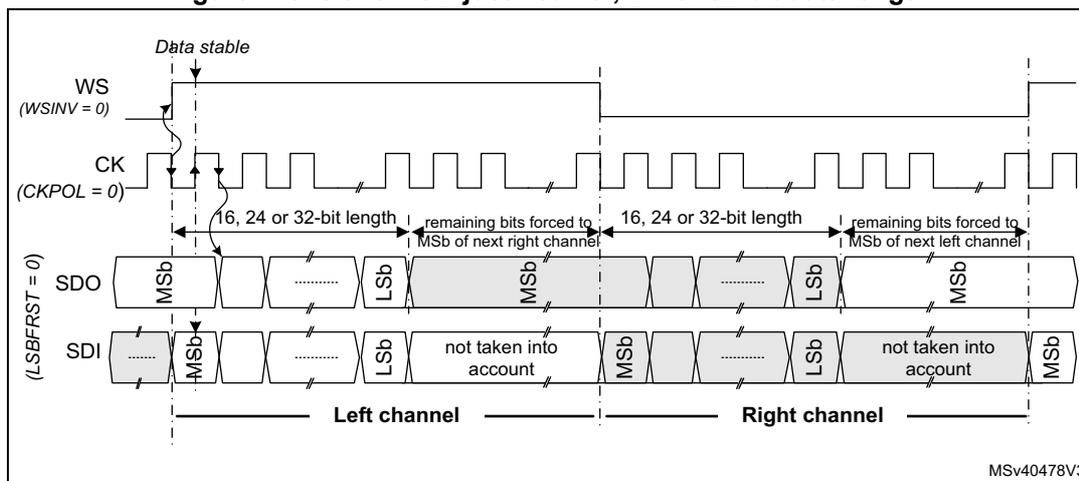

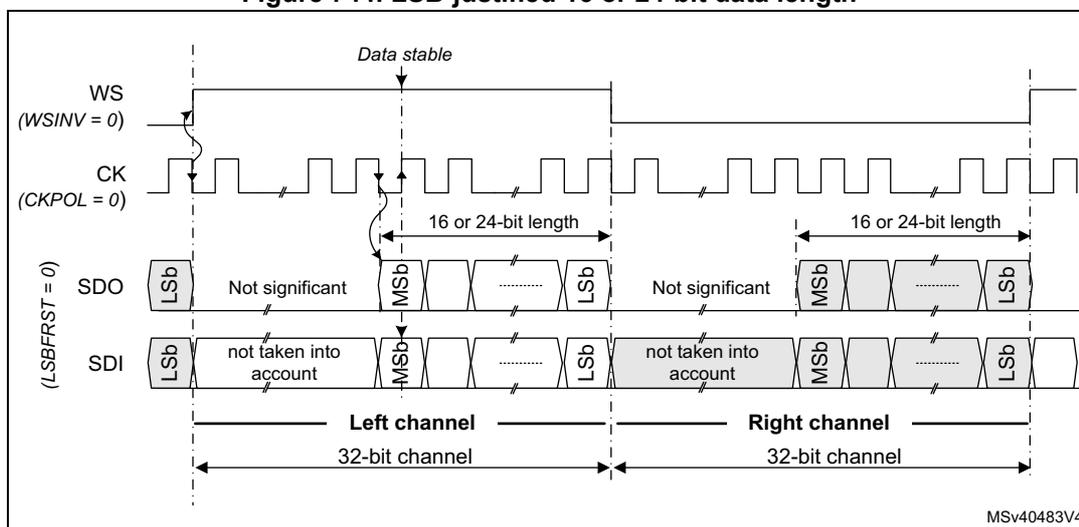

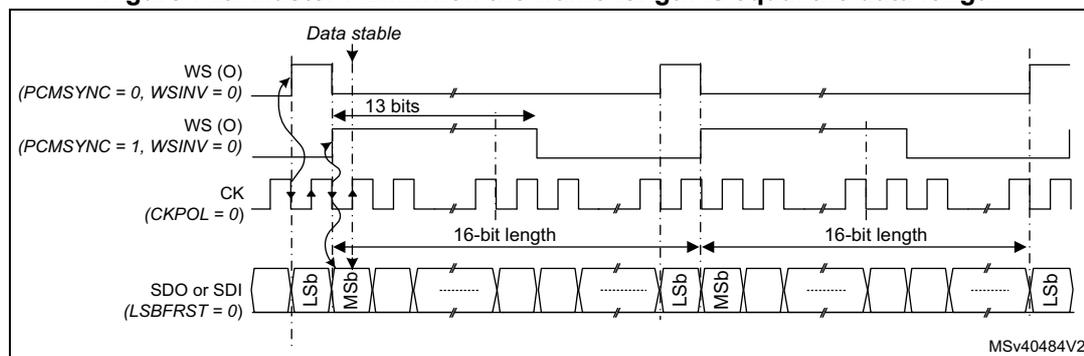

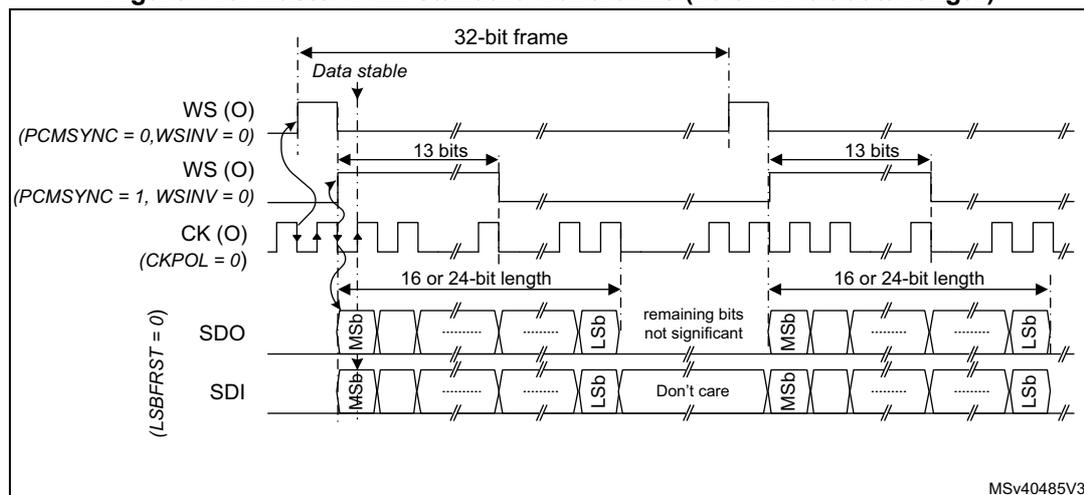

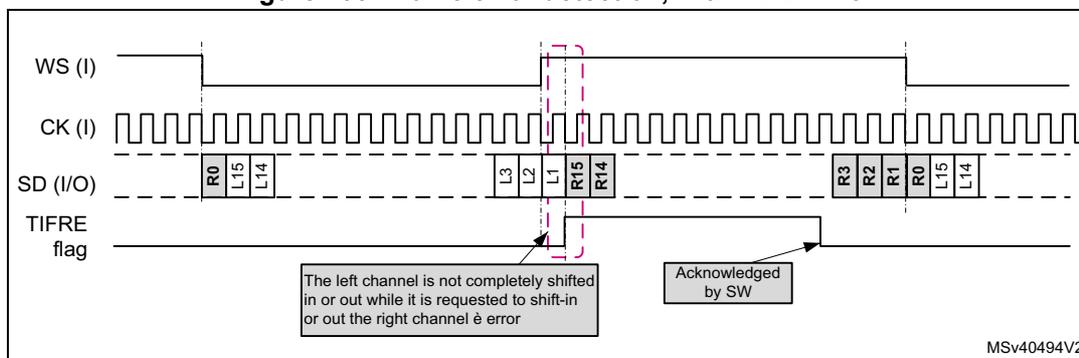

With a specific SP[2:0] bitfield setting of the SPI_CFG2 register, the SPI can be configured compliant with the TI protocol. The SCK and NSS signals polarity, phase and flow, as well as the bit order are fixed, so the setting of CPOL, CPHA, LSBFRST, SSOM, SSOE, SSIOP, SSM, RDIOP, RDIOM, MSSI, and MIDI is not required when the SPI is in TI mode configuration. The NSS signal synchronizes the protocol by pulses over the LSB data bit as it is shown in Figure 736.

Figure 736. TI mode transfer

![Timing diagram for TI mode transfer showing NSS, SCK, MOSI, and MISO signals. The diagram illustrates the relationship between the Slave Select (NSS) signal, the Serial Clock (SCK), Master Out Slave In (MOSI), and Slave Out Master In (MISO) signals during a data transfer. The NSS signal is shown as a series of pulses. The SCK signal is a periodic square wave. The MOSI signal is shown as a series of bytes, with the Most Significant Bit (MSB) and Least Significant Bit (LSB) indicated. The MISO signal is shown as a series of bytes, with the MSB and LSB indicated. The diagram also shows the data size (DSIZE[4:0] + 1) and the release time (TRELEASE) for the MISO signal.](/RM0481-STM32H523-33-562-63-573/6621ad85a6f55cddf84d81c7e99cba73_img.jpg)

In slave mode, the clock generator is used to define the time when the slave output at MISO pin becomes high-Z when the current transfer finishes. The master baud rate setting (MBR[2:0] of SPI_CFG1) is applied and any baud rate can be used to determine this moment with optimal flexibility. The delay for the MISO signal to become high-Z (T RELEASE ) depends on internal resynchronization, too, which takes the next additional 2-4 periods of the clock signal feeding the generator. It is given by the following formula:

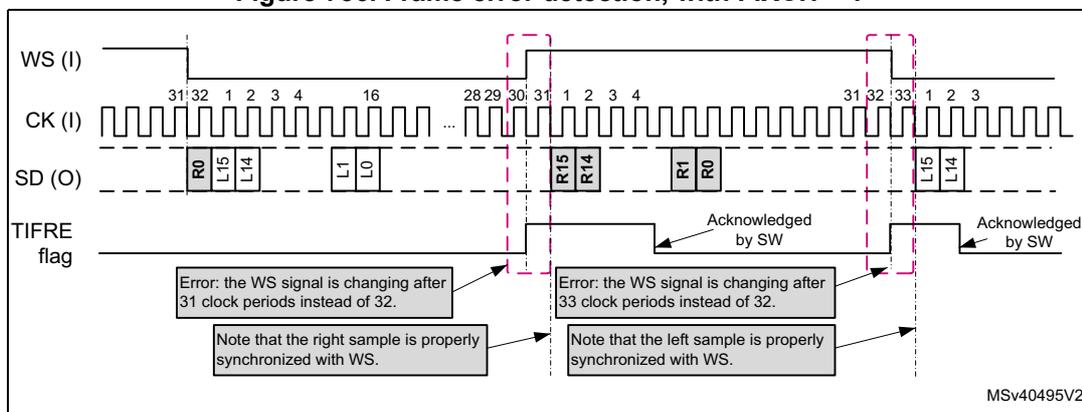

If the slave detects a misplaced NSS pulse during a data transfer the TIFRE flag is set.

52.5.2 SPI error flags

An SPI interrupt is generated if one of the following error flags is set and the interrupt is enabled by setting the corresponding interrupt enable bit.

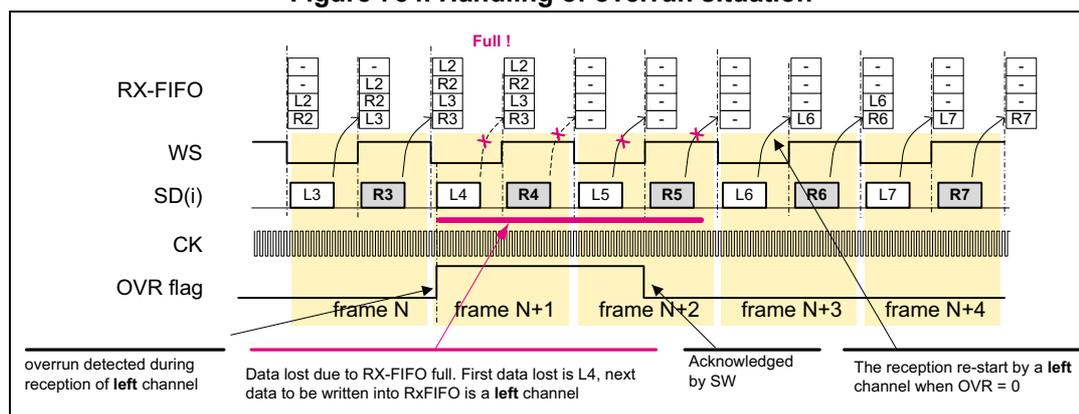

Overrun flag (OVR)

An overrun condition occurs when data are received by a master or slave and the RxFIFO has not enough space to store these received data. This can happen if the software or the DMA did not have enough time to read the previously received data (stored in the RxFIFO).

When an overrun condition occurs, the OVR flag is set and the newly received value does not overwrite the previous one in the RxFIFO. The newly received value is discarded and all

data transmitted subsequently are lost. The OVR flag triggers an interrupt if the OVRIE bit is set. Clearing the OVR bit is done by setting the OVRC bit of the SPI_IFCR register. Clearing the RxFIFO content by performing software reads before the OVR bit is cleared reduces the risk of any immediate repetition of its next overrun. It is suggested to release the RxFIFO space as much as possible, this means to read out all the available data packets based on RXP flag indication.

In master mode, the user can prevent the RxFIFO overrun by automatic communication suspend (MASRX bit).

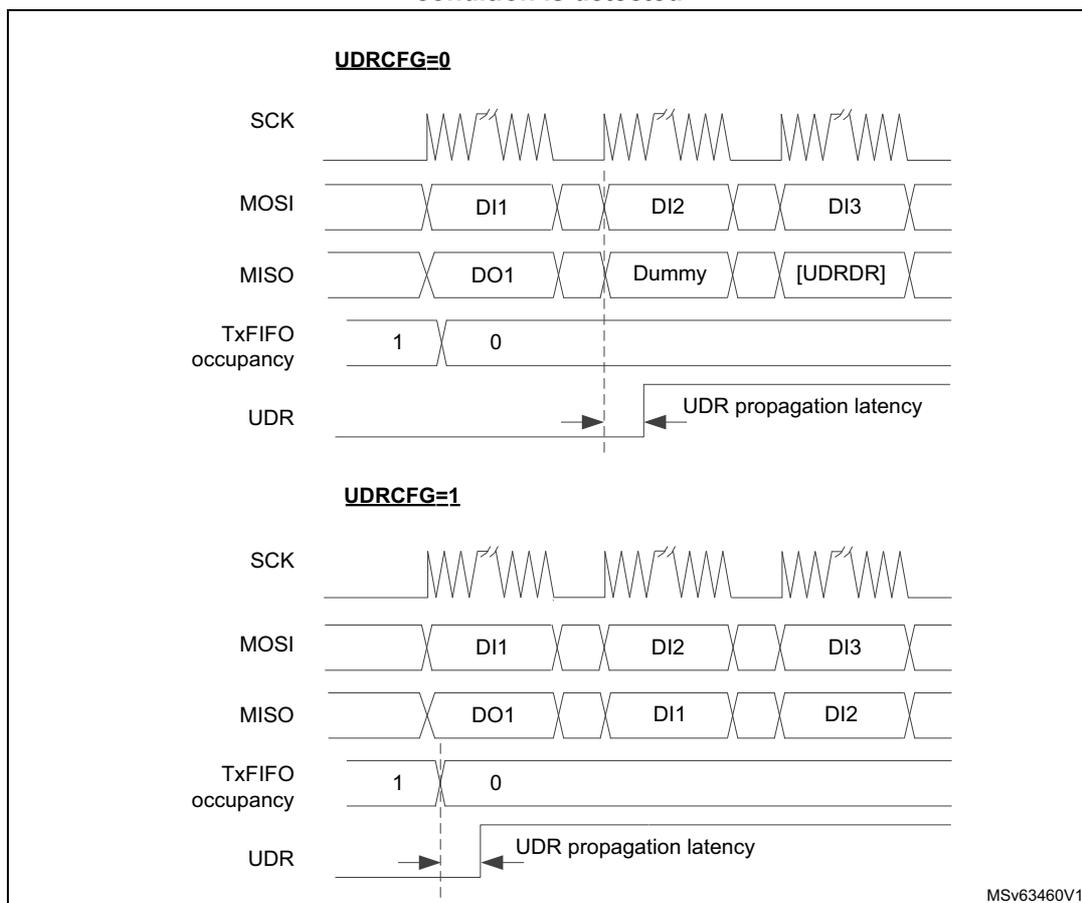

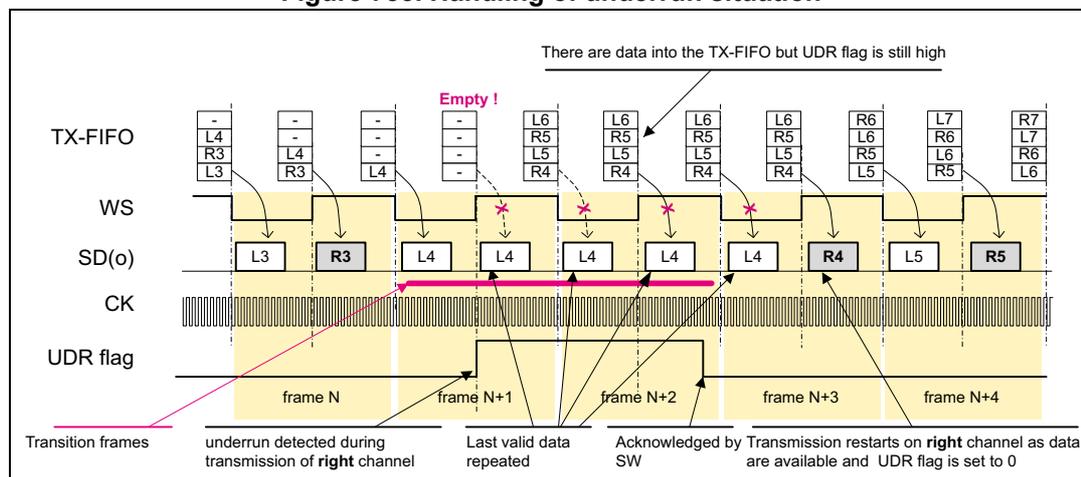

Underrun flag (UDR)

In a slave-transmitting mode, the underrun condition is captured internally by hardware if no data is available for transmission in the slave TxFIFO commonly. The UDR flag setting is then propagated into the status register by hardware (see note below). UDR triggers an interrupt if the UDRIE bit is set.

Underrun detection logic and system behavior depend on the UDRCFG bit. When an underrun is detected by the slave, it can provide out either a constant pattern stored by the user at the UDRDR register or the data received previously from the master. When the first configuration (UDRCFG = 0) is applied, the underrun condition is evaluated whenever the master starts to communicate a new data frame while TxFIFO is empty. Then single additional dummy (accidental) data is always inserted between the last valid data and the constant pattern defined at the UDRDR register (see Figure 737 ). The second configuration (UDRCFG=1) can be used in circular topography structures (see Figure 729 ). Assuming that TxFIFO is not empty when the master starts the communication, the underrun condition is evaluated just once the FIFO becomes empty during the next data flow. Valid data from TxFIFO is then upended by the lastly received data immediately.

The standard transmission is reenabled once the software clears the UDR flag and this clearing is propagated into SPI logic by hardware. Writing some data to the TxFIFO before the UVR bit is cleared reduces the risk of any immediate repetition of its next underrun.

The data transferred by the slave is unpredictable especially when the transfer starts or continues while TxFIFO is empty and the underrun condition is either not yet captured or just cleared. Typically, this is the case when SPI is just enabled or when a transfer with a defined size just starts. First bits can be corrupted in this case, as well, when the slave software writes the first data into the empty TxFIFO too close prior to starting the data transfer (propagation of the data into TxFIFO takes a few APB clock cycles).

Figure 737. Optional configurations of the slave behavior when an underrun condition is detected

The diagram illustrates two optional configurations for slave behavior during an underrun condition in SPI.

UDRCFG=0

- SCK: Shows a continuous clock signal.

- MOSI: Shows data frames DI1, DI2, and DI3 being transmitted by the master.

- MISO: Shows the slave transmitting DO1, then a 'Dummy' value, and then [UDRDR] (Underrun Data Register) when the TxFIFO is empty.

- TxFIFO occupancy: Shows the FIFO level dropping from 1 to 0.

- UDR: Shows the Underrun flag being set when the FIFO is empty. A dashed vertical line marks the point where the flag is set. An arrow labeled 'UDR propagation latency' indicates the time between the flag being set and the slave's response on the MISO line.

UDRCFG=1

- SCK: Shows a continuous clock signal.

- MOSI: Shows data frames DI1, DI2, and DI3 being transmitted by the master.

- MISO: Shows the slave transmitting DO1, then DI1 (repeating the last received data), and then DI2 when the TxFIFO is empty.

- TxFIFO occupancy: Shows the FIFO level dropping from 1 to 0.

- UDR: Shows the Underrun flag being set when the FIFO is empty. A dashed vertical line marks the point where the flag is set. An arrow labeled 'UDR propagation latency' indicates the time between the flag being set and the slave's response on the MISO line.

MSV63460V1

Note: The hardware propagation of an UDR event needs additional traffic on the bus. It always takes a few extra SPI clock cycles after the event happens (both underrun captured by hardware and cleared by software). If clearing of the UDR flag by software is applied close to the end of the data frame transfer or when the SCK line is at idle in between the frames, the next extra underrun pattern is sent initially by the slave before the valid data from TxFIFO becomes transferred again. The user can prevent this by SPI disable/enable action between sessions to restart the underrun logic and so initiate the next session by the valid data.

Mode fault (MODF)

Mode fault occurs when the master device has its internal NSS signal (NSS pin in slave select hardware mode, or SSI bit in slave select software mode) pulled low. This automatically affects the SPI interface in the following ways:

- • The MODF bit is set and the SPI interrupt is triggered if the MODFIE bit is set.

- • The SPE bit is forced to zero until the MODF bit is set. This disables the SPI and blocks all the peripheral outputs except the MODF interrupt request if enabled.

- • The MASTER bit is cleared, thus forcing the device into slave mode.

MODF is cleared by writing 1 to the MODFC bit of the SPI_IFCR register.

To avoid any multiple slave conflicts in a system comprising several MCUs, the NSS pin must be pulled to its nonactive level before reenabling the SPI, by setting the SPE bit.

As a security, the hardware does not allow the SPE bit to be set while the MODF bit is set. In a slave device, the MODF bit cannot be set except as the result of a previous multimaster conflict.

A correct software procedure when a master overtakes the bus in multimaster systems must be the following one:

- 1. Switch into master mode while SSOE = 0 (potential conflict can appear when another master occupies the bus. In this case, MODF is raised, which prevents any next node switching into master mode).

- 2. Put GPIO pin dedicated for another master slave select control into active level.

- 3. Perform a data transfer.

- 4. Put GPIO pin dedicated for another master slave select control into nonactive level.

- 5. Switch back to slave mode.

CRC error (CRCE)

This flag is used to verify the validity of the value received when the CRCEN bit of the SPI_CFG1 register is set. The CRCE flag of the SPI_SR register is set if the value received in the shift register does not match the receiver SPI_RXCRC value, after the last data is received (as defined by TSIZE). The CRCE flag triggers an interrupt if the CRCEIE bit is set. Clearing the bit CRCE is done by a writing 1 to the CRCEC bit of the SPI_IFCR register.

TI mode frame format error (TIFRE)

A TI mode frame format error is detected when an NSS pulse occurs during an ongoing communication when the SPI is operating in slave mode and configured to conform to the TI mode protocol. When this error occurs, the TIFRE flag is set in the SPI_SR register. The SPI is not disabled when an error occurs, the NSS pulse is ignored, and the SPI waits for the next NSS pulse before starting a new transfer. The data may be corrupted since the error detection may result in the loss of a few data frames.

The TIFRE flag is cleared by writing 1 to the TIFREC bit of the SPI_IFCR register. If the TIFREIE bit is set, an interrupt is generated on the NSS error detection. As data consistency is no longer guaranteed, communication must be reinitiated by software between master and slave.

52.5.3 CRC computation

Two separate CRC calculators are implemented to check the reliability of transmitted and received data. The CRC polynomial configuration depends on the instance. Refer to Section 52.3: SPI implementation for more information.

The length of the polynomial is defined by the most significant bit of the value stored in the SPI_CRCPOLY register. It must be greater than the data frame size (in bits) defined in the DSIZE[4:0] bitfield of the SPI_CFG1 register. To obtain a full-size polynomial, the polynomial length must exceed the maximum data size of the peripheral instance, and the CRC33_17 bit of the SPI_CR1 register must be set to select the most significant bit of the polynomial string.

For example, to select the standard CRC16-CCITT (XMODEM) polynomial \( x^{16} + x^{12} + x^5 + 1 \) :

- • For a 32-bit instance: write 0x11021 to the SPI_CRCPOLY register and clear the CRC33_17 bit.

- • For a 16-bit instance: to obtain the full size, write 0x1021, and set the CRC33_17 bit.

The CRCSIZE field of the SPI_CFG1 register then defines how many most significant bits from the CRC calculation registers are transferred and compared as CRC frame. It is defined independently from the data frame length, but it must be either equal or an integer multiple of the data frame size. Its size cannot exceed the maximum data size of the instance.

To fully benefit from the CRC calculation capability, the polynomial length setting must correspond to the CRC frame size, else the bits unused at the calculation are transferred and expected all zero at the end of the CRC frame if its size is set greater than the polynomial length.

CRC principle

The CRC calculation is enabled by setting the CRCEN bit of the SPI_CFG1 register before the SPI is enabled (SPE = 1). The CRC value is then calculated using the CRC polynomial defined by the CRCPOLY register and CRC33_17 bit. When SPI is enabled, the CRC polynomial can be changed but only in the case when there is no traffic on the bus.

The CRC computation is done, bit by bit, on the sampling clock edge defined by the CPHA and CPOL bits of the SPI_CR1 register. The calculated CRC value is checked automatically at the end of the data block defined by the SPI_CR2 register exclusively.

When a mismatch is detected between the CRC calculated internally on the received data and the CRC received from the transmitter, a CRCE flag is set to indicate a data corruption error. The right procedure for handling the CRC depends on the SPI configuration and the chosen transfer management.

CRC transfer management

Communication starts and continues normally until the last data frame has been sent or received in the SPI_DR register.

The length of the transfer must be defined by TSIZE. When the desired number of data is transferred, the TXCRC is transmitted and the data received on the line are compared to the RXCRC value.