49. Improved inter-integrated circuit (I3C)

49.1 I3C introduction

The I3C interface handles communication with other devices such as sensor(s) and host processor.

An I3C bus is a two-wire, serial single-ended, multi-drop bus, intended to improve the legacy I 2 C bus. The I3C interface improves the features of the I 2 C interface (adding especially in-band interrupts, dynamic address assignment, energy-efficient data rates, power management) meanwhile preserving some backward compatibility: it allows an I 2 C target to operate on an I3C bus in legacy I 2 C standard-mode (Sm), fast-mode (Fm), or legacy I 2 C fast-mode plus (Fm+), provided that the latter does not perform clock stretching.

The I3C SDR-only peripheral implements all the required features and many optional features of the MIPI ® I3C specification v1.1 (see Table 536: I3C peripheral controller/target features versus MIPI v1.1 ). It can control all I3C bus-specific sequencing, protocol, arbitration, and timing.

After reset, the software can initialize the I3C peripheral as primary controller or as target:

- • As I3C controller, the software can enable the I3C peripheral and initialize the I3C bus.

- • As I3C target, the software can enable the I3C peripheral to operate on an I3C bus.

The I3C peripheral can be used with DMA, to off-load the CPU.

49.2 I3C main features

The I3C peripheral supports:

- • MIPI

®

I3C specification v1.1 (see details in

Table 536

), as:

- – I3C SDR-only primary controller

- – I3C SDR-only secondary controller

- – I3C SDR-only target

- • I3C SCL bus clock frequency up to 12.5 MHz

- • Registers configuration from the host application via the APB slave port

- • Queued data transfers:

- – Transmit FIFO (TX-FIFO) for data bytes/words to be transmitted on the I3C bus

- – Receive FIFO (RX-FIFO) for received data bytes/words on the I3C bus

- – For each FIFO, optional DMA mode with a dedicated DMA channel

- • Queued control/status transfers, when controller:

- – Control FIFO (C-FIFO) for control words to be sent on the I3C bus

- – Optional status FIFO (S-FIFO) for status words as received on the I3C bus

- – For each FIFO, optional DMA mode with a dedicated DMA channel

- • Messages:

- • Frame-level management, when controller:

- – Optional C-FIFO and TX-FIFO preload

- – Multiple messages encapsulation

- – Optional arbitrable header generation on the I3C bus

- – HDR exit pattern generation on the I3C bus for error recovery

- • Programmable bus timing, when controller:

- – SCL high and low period

- – SDA hold time

- – Bus free (minimum) time

- – Bus available/idle condition time

- – Clock stall time

- • Target-initiated requests management:

- – Simultaneous support up to four I3C targets, when controller

- – In-band interrupts, with programmable IBI payload (up to 4 bytes), with pending read notification support

- – Bus control request, with recovery flow support and hand-off delay

- – Hot-join mechanism

- • HDR exit pattern detection, when target

- • Bus error management:

- – CEx with x = 0, 1, 2, 3 when controller

- – TEx with x = 0, 1, ... , 6 when target

- – Bus control switch error and recovery

- – Target reset

- • Individual programmable event-based management:

- – Per-event identification with flag reporting and clear control

- – Host application notification via flag polling, and/or via interrupt with a per-event programmable enable

- – Error type identification

- • Wake-up from Stop mode(s), as controller (see

Section 49.3.2

):

- – On an in-band interrupt without payload

- – On a hot-join request

- – On a controller-role request

- • Wake-up from Stop mode(s), as target (see

Section 49.3.2

):

- – On a reset pattern

- – On a missed start

- • Multi-clock domain management:

- – Separate APB clock and kernel clock, driven from independently programmed clock sources via the RCC, in addition to SCL clock

- – Minimum operating frequency for the kernel clock and the APB clock vs. the application-driven SCL clock (see clocks constraints in Section 49.6.2 )

49.3 I3C implementation

49.3.1 I3C instantiation

There is a single I3C instance in the device.

49.3.2 I3C wake-up from low-power mode(s)

The I3C peripheral can wake up the device from a low-power mode, as detailed in Table 533 . For more details about the wake-up capabilities, refer to Section 49.13 .

Table 533. I3C wake-up

| Wake-up |

|---|

| From Stop mode with SVOS3 |

49.3.3 I3C FIFOs

The FIFOs are implemented as defined in Table 534 .

Table 534. I3C FIFOs implementation

| FIFO | Content | Unit | Size (in unit) | Used as controller/target (rationale) |

|---|---|---|---|---|

| C-FIFO | (32-bit) Control words | Word | 2 | Controller (a frame can be based on multiple control words; this is not the case as target) |

| S-FIFO | (32-bit) Status words | Controller (target: status only in register mode) | ||

| TX-FIFO | Transmitted data | Byte | 8 | Controller and target |

| RX-FIFO | Received data |

49.3.4 I3C triggers

This feature is not available in this product: no hardware trigger signal is connected as an input to the I3C peripheral.

49.3.5 I3C interrupt(s)

The interrupt mapping is implemented as detailed in Table 535 .

Table 535. I3C interrupt(s)

| Signal name | Signal type | Description |

|---|---|---|

| i3c_err_it | O | Error interrupt line |

| i3c_evt_it | O | Event interrupt line |

49.3.6 I3C MIPI ® support

The I3C peripheral supports the MIPI specification v1.1, as defined in Table 536 .

Table 536. I3C peripheral controller/target features versus MIPI v1.1

| Feature | MIPI I3C v1.1 | I3C peripheral | Comments | |

|---|---|---|---|---|

| When controller | When target | |||

| I3C SDR message | X | X | X | - |

| Legacy I 2 C message (Sm/Fm/Fm+) | X | X | - | Mandatory when controller if the I3C bus is mixed with (external) legacy I

2

C target(s). Optional in MIPI v1.1 when target. |

| HDR DDR message | X | - | - | Optional in MIPI v1.1 |

| HDR-TSL/TSP, HDR-BT | X | - | - | Optional in MIPI v1.1 |

| Dynamic address assignment | X | X | X | Supported broadcast ENTDAI when controller and target. Supported broadcast SETAASA and direct SETDASA when controller. |

| 7-bit static I 2 C address | X | X | - | No support of the I3C peripheral as target on an I 2 C bus. |

| Grouped addressing | X | X | - | Optional in MIPI v1.1 |

| CCC | X | X | X | Mandatory and some optional CCCs supported (refer to Table 542 when controller/target). |

| Error detection and recovery | X | X | X | - |

| In-band interrupt (with MDB) | X | X | X | - |

| Secondary controller | X | X | X | - |

| Hot-join mechanism | X | X | X | - |

| Target reset | X | X | X | - |

| Synchronous timing control | X | X | - | Optional in MIPI v1.1 |

| Asynchronous timing control 0 | X | X | - | Mandatory in MIPI v1.1 when controller. Optional in MIPI v1.1 when target. |

| Asynchronous timing control 1, 2, 3 | X | - | - | Optional in MIPI v1.1 |

| Device to device tunneling | X | X | - | Optional in MIPI v1.1 |

| Multi-lane data transfer | X | - | - | Optional in MIPI v1.1 |

| Monitoring device early termination | X | - | - | Optional in MIPI v1.1 |

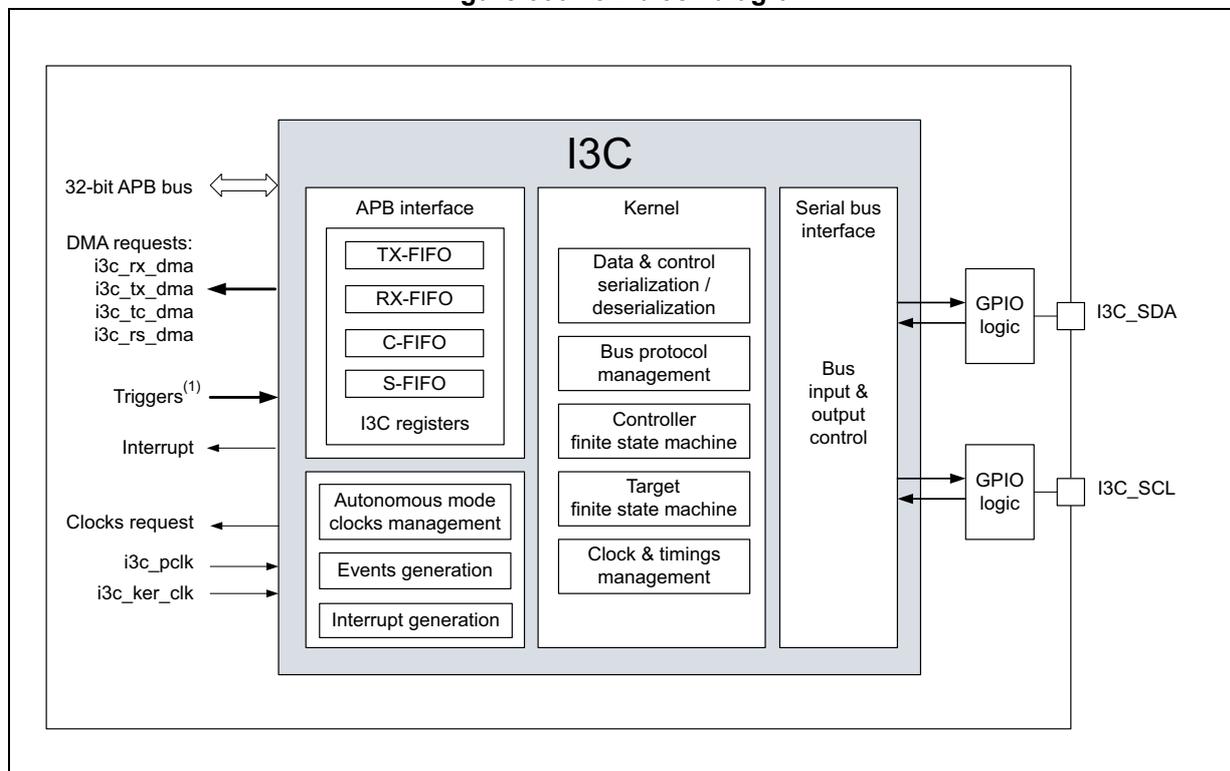

49.4 I3C block diagram

The I3C block diagram is illustrated in Figure 660 .

Figure 660. I3C block diagram

The block diagram illustrates the internal architecture of the I3C block. It is divided into three main functional blocks: APB interface, Kernel, and Serial bus interface.

- APB interface:

- Connects to a 32-bit APB bus.

- Contains TX-FIFO, RX-FIFO, C-FIFO, S-FIFO, and I3C registers.

- Receives DMA requests: i3c_rx_dma, i3c_tx_dma, i3c_tc_dma, and i3c_rs_dma.

- Receives Triggers (1) .

- Generates an Interrupt.

- Receives a Clocks request.

- Receives i3c_pclk and i3c_ker_clk inputs.

- Kernel:

- Contains Data & control serialization / deserialization, Bus protocol management, Controller finite state machine, Target finite state machine, and Clock & timings management.

- Serial bus interface:

- Contains Bus input & output control.

- Connects to GPIO logic blocks.

- GPIO logic blocks connect to external pins I3C_SDA and I3C_SCL.

1. Refer to Section 49.3.4: I3C triggers .

49.5 I3C pins and internal signals

Table 537. I3C input/output pins

| Pin name | Pin type | Description |

|---|---|---|

| I3C_SDA | Input/output | Serial bus data line |

| I3C_SCL | Input/output | Serial bus clock line |

Table 538. I3C internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| i3c_pclk | I | APB clock |

| i3c_ker_clk | I | Kernel clock (also named as I3CCLK) |

| i3c_pclk_req | O | APB clock request |

| i3c_ker_clk_req | O | Kernel clock request |

| i3c_it (1) | O | Global interrupt line |

| Signal name | Signal type | Description |

|---|---|---|

| i3c_err_it (1) | O | Error interrupt line |

| i3c_evt_it (1) | O | Event interrupt line |

| i3c_rx_dma | O | DMA request for reading received bytes/words from RX-FIFO |

| i3c_tx_dma | O | DMA request for writing to be transmitted bytes/words to TX-FIFO |

| i3c_tc_dma | O | DMA request for writing to be transmitted control words to C-FIFO, when the I3C peripheral acts as controller |

| i3c_rs_dma | O | DMA request for reading status words from S-FIFO, when the I3C peripheral acts as controller |

1. Refer to Section 49.3.5: I3C interrupt(s) .

49.6 I3C reset and clocks

49.6.1 I3C reset

On a system reset, the I3C peripheral is reset.

Alternatively, the software can reset specifically the I3C peripheral by writing the corresponding reset control bit (I3CxRST) of the reset and clock controller (RCC). Refer to the RCC section of this document for more details.

Additionally, when acting as target, the enabled I3C peripheral (EN = 1 in the I3C_CFGR register) can receive an in-band reset pattern on the I3C bus from the controller. The software is then notified (when RSTF = 1 in the I3C_EVR register and/or the corresponding interrupt is enabled) to perform the requested action, as registered in RSTACT[1:0] of the I3C_DEVR0 register, on the former reception of the broadcast or direct RSTACT CCC. Refer to Table 542 and Section 49.16.16 for more details.

This reset interrupt notification can be used to wake up from a low power mode. For more details about the corresponding low-power mode(s), refer to the power management in the PWR section.

49.6.2 I3C clocks and requirements

As indicated in Figure 660 , the I3C peripheral is implemented with several clock domains:

- • SCL bus clock: for the I3C bus interface

- – When controller: the user must set and can adjust SCL/SDA timings by programming I3C timing register 0 (I3C_TIMINGR0) , I3C timing register 1 (I3C_TIMINGR1) and I3C timing register 2 (I3C_TIMINGR2) , as summarized in Controller initialization and Updating the configuration for a transfer, as controller .

- – When target: the user must set and comply with the bus available condition ( \( t_{AVAL} \) for an in-band interrupt or controller-role request), and the bus idle condition ( \( t_{IDLE} \) for a hot-join request), by programming I3C timing register 1 (I3C_TIMINGR1) , as summarized in Target initialization .

- • I3CCLK kernel clock: for the I3C protocol management, data and control serialization/deserialization, controller and target finite state machines, bus clock and timings management

- • APB clock: for the APB interface, DMA interface, events, and interrupt generation

APB clock and kernel clocks are driven from independently programmed clock sources via the RCC (refer to section Reset and clock control (RCC) for more details).

I3C kernel clock requirement, as controller

According to the intended value of the SCL clock on the bus, the application must guarantee that the frequency of the I3CCLK kernel clock be at least 2x the frequency of the SCL clock

Note: Sustaining \( F_{SCL\ max} = 12.9 \) MHz means a frequency of the I3CCLK kernel clock \( > 25.8 \) MHz.

I3C kernel clock requirements, as target

According to the intended value of the SCL clock on the bus, the application must guarantee a minimum operating frequency for the I3CCLK kernel clock, meeting the following constraints:

- 1. Period of the I3CCLK kernel clock

\(

< t_{HIGH}

\)

(SCL clock high period)

- – \( t_{HIGH\ min} = 24 \) ns. A frequency higher than 41.7 MHz guarantees this constraint, which can be relaxed, depending on the I3C bus/controller

- 2. Period of the I3CCLK kernel clock

\(

< t_{CASr}

\)

(clock after repeated start condition)

- – \( t_{CASr\ min} = t_{CAS\ min} / 2 = 19.2 \) ns. A frequency higher than 52 MHz guarantees this constraint, which can be relaxed, depending on the I3C bus/controller

- 3. Two periods of the I3CCLK kernel clock

\(

< t_{LOW\_OD}

\)

(SCL clock low period in open drain)

- – \( t_{LOW\_OD\ min} = 200 \) ns. A frequency higher than 10 MHz guarantees this constraint, which can be relaxed, depending on the I3C bus/controller

- 4. Frequency of the I3CCLK kernel clock

\(

> 2.5x

\)

frequency of the SCL clock

- – \( F_{SCL\ max} = 12.9 \) MHz. A frequency higher than 32.3 MHz guarantees this constraint, which can be relaxed, depending on the I3C controller

Note:

APB clock requirement

According to the intended value of the SCL clock on the bus, the application must guarantee a minimum operating frequency for the APB clock:

APB clock period \( < 3x \) (SCL clock period) - I3CCLK kernel clock period

This means that \( F_{APB} > [F_{SCL} \times F_{I3CCLK} / (3 \times F_{I3CCLK} - F_{SCL})] \)

Note: This equation can be simplified to a minimum value of 5 MHz for the APB frequency.

49.7 I3C peripheral state and programming

49.7.1 I3C peripheral state

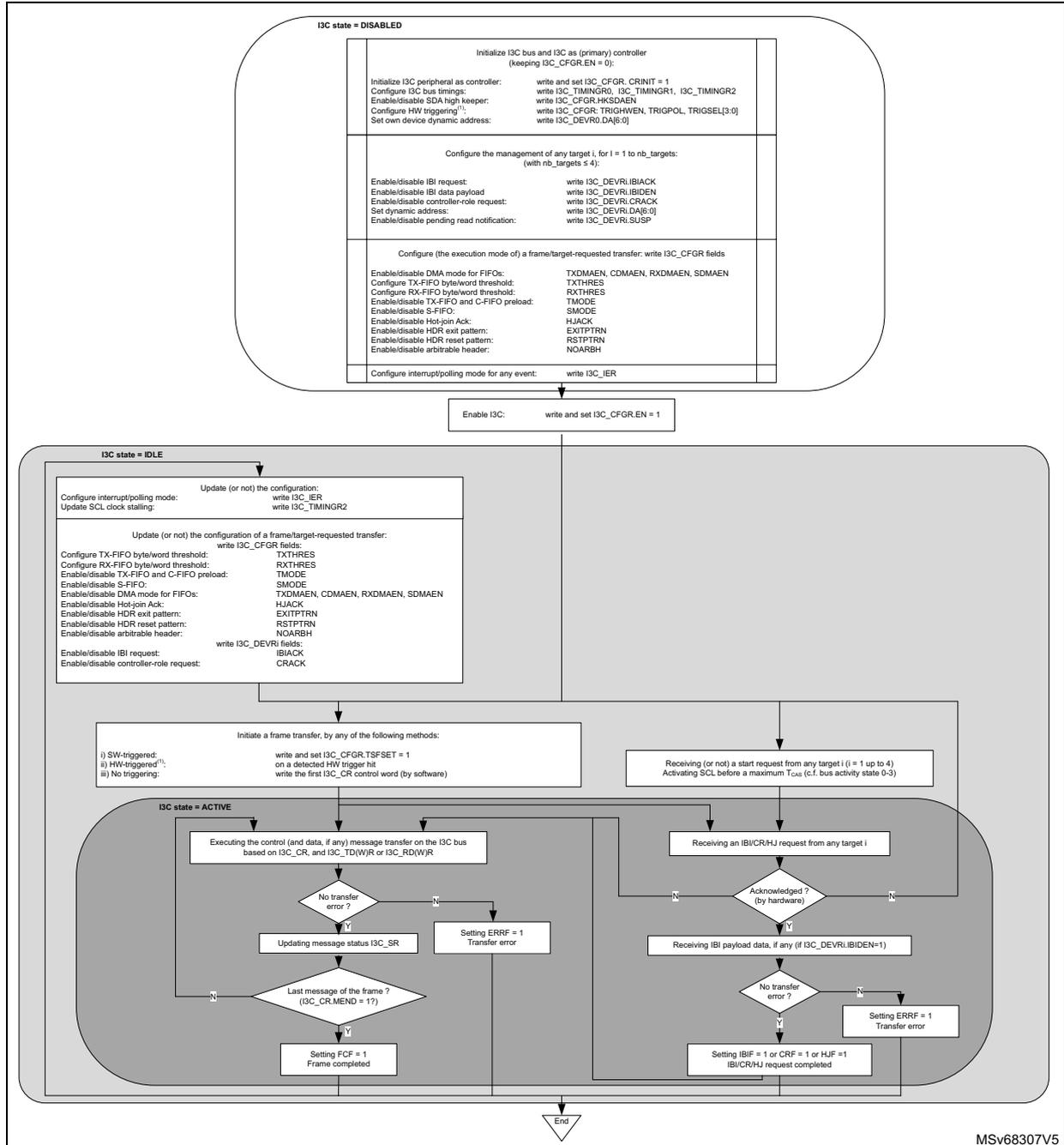

The I3C peripheral plays the role of I3C bus controller, or the role of an I3C target. In any case (see Figure 661 and Figure 662 ), the peripheral is in one of the following states:

- • Disabled state:

- – After an I3C reset (system reset or I3C reset from RCC), the I3C peripheral is in disabled state.

- – When the software sets to 1 bit EN in the I3C_CFGFR register, the I3C peripheral takes into account the value of the different initialized configuration registers, and switches to the (enabled and) idle state. The peripheral is initialized as I3C target or I3C controller.

- – As I3C controller, then software can enable the I3C peripheral and initialize the I3C bus.

- – As I3C target, then the software can enable the I3C peripheral to operate on an I3C bus.

- • Idle state:

- – After being enabled (EN = 1), the I3C peripheral activates its I3CCLK and SCL clock domains, and is able to communicate on the I3C bus.

- – The software can partly update the I3C peripheral configuration, see Updating the configuration for a transfer, as controller and Updating the configuration of the I3C peripheral, as target for more details.

- – The I3C peripheral switches to the (enabled and) active state in either one of the following conditions:

Once the software initiates a transfer (as controller: when the software initiates a frame transfer; as target: when the software initiates an IBI/CR/HJ request).

Once the hardware receives a request from another I3C device on the bus (as controller: after a start request from a target and a maximum \( T_{CAS} \) time; as target: when receiving a broadcast/direct CCC or a private read/write).

- • Active state:

- – The I3C peripheral executes the transfer(s) on the bus.

- – When the requested transfer(s) is(are) completed, the software is notified by an event from the I3C event register (I3C_EVR) , and the corresponding interrupt is enabled by I3C interrupt enable register (I3C_IER) . The I3C peripheral switches to idle state, is still able to communicate on the bus, and can be (partly) reconfigured:

As controller: the raised event/flag can be frame completed (FCF), IBI/controller-role/hot-join request completed (IBIF/CRF/HJF), or transfer error (ERRF).

As target: the raised event/flag can be dynamic address assignment completed (DAUPDF), IBI completed (IBIENDF), controller-role gaining completed (CRUPDF), broadcast/direct CCC completed (xxUPDF/RSTF/GETF/STAF), private read/write completed (FCF), or transfer error (ERRF).

Note: The software can disable the I3C peripheral (write EN = 0), partially resetting it (subparts within the SCL clock domain and the I3CCLK kernel clock domain). Event, interrupt, and clock request generation are also impacted. The previously written configuration of the APB registers is kept and not modified.

49.7.2 I3C controller state and programming sequence

Figure 661 illustrates the overall programming sequence of the I3C peripheral acting as (primary) controller, including state transitions, main subtasks, and conditions, as explained in this section.

Figure 661. I3C (primary) controller state and programming sequence diagram

I3C state = DISABLED

Initialize I3C bus and I3C as (primary) controller (keeping I3C_CFGREN = 0):

- Initialize I3C peripheral as controller: write and set I3C_CFGR_CRINIT = 1

- Configure I3C bus timings: write I3C_TIMINGR0, I3C_TIMINGR1, I3C_TIMINGR2

- Enable/disable SDA high keeper: write I3C_CFGR_HKSDAEN

- Configure HW triggering 1 : write I3C_CFGR_TRIGHWEN, TRIGPOL, TRIGSEL[3:0]

- Set own device dynamic address: write I3C_DEVR0.DA[6:0]

Configure the management of any target i, for i = 1 to nb_targets: (with nb_targets ≤ 4):

- Enable/disable IBI request: write I3C_DEVRI.IBIACK

- Enable/disable IBI data payload: write I3C_DEVRI.IBIDEN

- Enable/disable controller-role request: write I3C_DEVRI.CRACK

- Set dynamic address: write I3C_DEVRI.DA[6:0]

- Enable/disable pending read notification: write I3C_DEVRI.SUSP

Configure (the execution mode of) a frame/target-requested transfer: write I3C_CFGR fields

- Enable/disable DMA mode for FIFOs: TXDMAEN, CDMAEN, RXDMAEN, SDMAEN

- Configure TX-FIFO byte/word threshold: TXTHRES

- Configure RX-FIFO byte/word threshold: RXTHRES

- Enable/disable TX-FIFO and C-FIFO preload: TMODE

- Enable/disable S-FIFO: SMODE

- Enable/disable Hot-join Ack: HJACK

- Enable/disable HDR exit pattern: EXITPTRN

- Enable/disable HDR reset pattern: RSTPTRN

- Enable/disable arbitrable header: NOARBH

Configure interrupt/polling mode for any event: write I3C_IER

Enable I3C: write and set I3C_CFGREN = 1

I3C state = IDLE

Configure interrupt/polling mode: Update (or not) the configuration: write I3C_IER

Update SCL clock stalling: write I3C_TIMINGR2

Update (or not) the configuration of a frame/target-requested transfer: write I3C_CFGR fields:

- Configure TX-FIFO byte/word threshold: TXTHRES

- Configure RX-FIFO byte/word threshold: RXTHRES

- Enable/disable TX-FIFO and C-FIFO preload: TMODE

- Enable/disable S-FIFO: SMODE

- Enable/disable DMA mode for FIFOs: TXDMAEN, CDMAEN, RXDMAEN, SDMAEN

- Enable/disable Hot-join Ack: HJACK

- Enable/disable HDR exit pattern: EXITPTRN

- Enable/disable HDR reset pattern: RSTPTRN

- Enable/disable arbitrable header: NOARBH

Enable/disable IBI request: write I3C_DEVRI fields: IBIACK

Enable/disable controller-role request: CRACK

Initiate a frame transfer, by any of the following methods:

- SW-triggered 1 : write and set I3C_CFGR_TSFSET = 1

- HW-triggered 1 : on a detected HW trigger bit: write the first I3C_CR control word (by software)

- No triggering:

Receiving (or not) a start request from any target (i = 1 up to 4) Activating SCL before a maximum T us (c.f. bus activity state 0-3)

I3C state = ACTIVE

Executing the control (and data, if any) message transfer on the I3C bus based on I3C_CR, and I3C_TD(W)R or I3C_RD(W)R

No transfer error? (Y/N)

Last message of the frame? (I3C_CR.MEND = 1?)

Setting FCF = 1 Frame completed

Setting ERRF = 1 Transfer error

Receiving an IBICRHJ request from any target i

Acknowledged? (by hardware) (Y/N)

Receiving IBI payload data, if any (if I3C_DEVRI.IBIDEN=1)

No transfer error? (Y/N)

Setting IBIF = 1 or CRF = 1 or HJF = 1 IBI/CR/HJ request completed

Setting ERRF = 1 Transfer error

End

MSV68307V5

1. This feature is implementation-dependent and can be unavailable. Refer to Section 49.3.4: I3C triggers .

Controller initialization

When the controller is in disabled state (EN = 0 in the I3C_CFGR register), the software must initialize as follows:

- • Configure

I3C configuration register (I3C_CFGR)

with the following fields:

- – CRINIT = 1: as I3C bus controller

- – HKSDAEN: high keeper on SDA enable/disable

- • Configure I3C bus timings:

- a)

I3C timing register 0 (I3C_TIMINGR0)

:

- – SCL clock high time period ( \( t_{DIG\_H} \) , \( t_{DIG\_H\_MIXED} \) ) in legacy I 2 C and I3C open-drain/push-pull

- – SCL clock low time period ( \( t_{DIG\_L} \) , \( t_{DIG\_OD\_L} \) ) in legacy I 2 C and I3C open-drain/push-pull

- b)

I3C timing register 1 (I3C_TIMINGR1)

:

- – SDA hold time in push-pull ( \( t_{HD\_PP} \) )

- – bus free condition time (I3C \( t_{CAS} \) , legacy I 2 C \( t_{BUF} \) )

- – I3C repeated start timing ( \( t_{CASr} \) , \( t_{CBSr} \) )

- – I3C stop timing ( \( t_{CBP} \) )

- – SCL clock low maximum stalling on the ENTDAA CCC ( \( t_{STALLDAA} \) ), or on the ACK/NACK of a legacy I 2 C or address phase of an I3C transfer, or the parity bit of a write data transfer, or on the ACK/NACK data phase of a legacy I 2 C write, or on the transition bit of an I3C read transfer, or on the ACK/NACK phase of a legacy I 2 C write ( \( t_{STALL} \) ), to adjust SCL clock low stalling, if needed by the I3C peripheral itself, when used as controller

- – \( t_{NEWCRLock} \) for controller-role hand-off procedure (after GETACCCR CCC)

- c)

I3C timing register 2 (I3C_TIMINGR2)

:

- – SCL clock low stalling time, with separated enable/disable for each phase, to adjust SCL clock low stalling, if needed on the SDA hand-off with the addressed I3C target or legacy I 2 C target

- a)

I3C timing register 0 (I3C_TIMINGR0)

:

- • Configure its own dynamic address: DA [6:0] field of the I3C own device characteristics register (I3C_DEVR0)

- • Configure the management of any device target x: I3C device x characteristics register (I3C_DEVRx) , for x = 1 to x ≤ 4

- • Configure the execution mode of a frame transfer or a target-requested transfer:

I3C configuration register (I3C_CFGR)

, with the following fields:

- – TXDMAEN, CDMAEN, RXDMAEN, SDMAEN: DMA mode enable/disable for respectively, TX-FIFO, C-FIFO, RX-FIFO, S-FIFO

- – TXTHRES, RXTHRES: respectively TX-FIFO and RX-FIFO byte/world threshold

- – TMODE: transmit mode (enable/disable for both TX-FIFO and C-FIFO preload)

- – SMODE: S-FIFO enable/disable

- – EXITPTRN, RSTPTRN: exit, reset pattern enable/disable

- – HJACK: hot-join acknowledge enable/disable

- – NOARBH: arbitrable header disable/enable

- • Configure interrupt generation or polling mode from any event: I3C interrupt enable register (I3C_IER)

Then, the software can enable the I3C peripheral (set EN = 1).

Note: The software can write once all the fields of the I3C_CFGR while enabling it.

Start a controller-initiated frame transfer

When the controller is in enabled state (EN = 1 in the I3C_CFGR register), the software can initiate a frame transfer by any of the following configuration methods:

- • Software-triggering: on a write and set TSFSET = 1 in the I3C_CFGR register

- – This causes the hardware to raise the flag CFNFF = 1 in the I3C_EVR register, to request a first control word I3C_CR to be written.

- • No triggering: on a write of the first control word I3C_CR by software.

Then, regardless of the frame starting method, the I3C peripheral switches to active state. While the control word is not the last message of the I3C frame (while MEND = 0 in the I3C_CR register), and while there is no transfer error (while ERRF = 1 in the I3C_EVR register), the hardware keeps requesting a next control word, and continuing the frame transfer:

- • If the C-FIFO is not configured in DMA mode (CDMAEN = 0 in the I3C_CFGR register), the software writes a next control word following the flag CFNFF = 1 in the I3C_EVR register, or the corresponding interrupt if enabled (if CFNFIE = 1 in I3C_IER register)

- • If the C-FIFO is configured in DMA mode (CDMAEN = 1), a next control word is automatically pushed and written by the allocated DMA channel consequently to the asserted I3C DMA request (i3c_tc_dma).

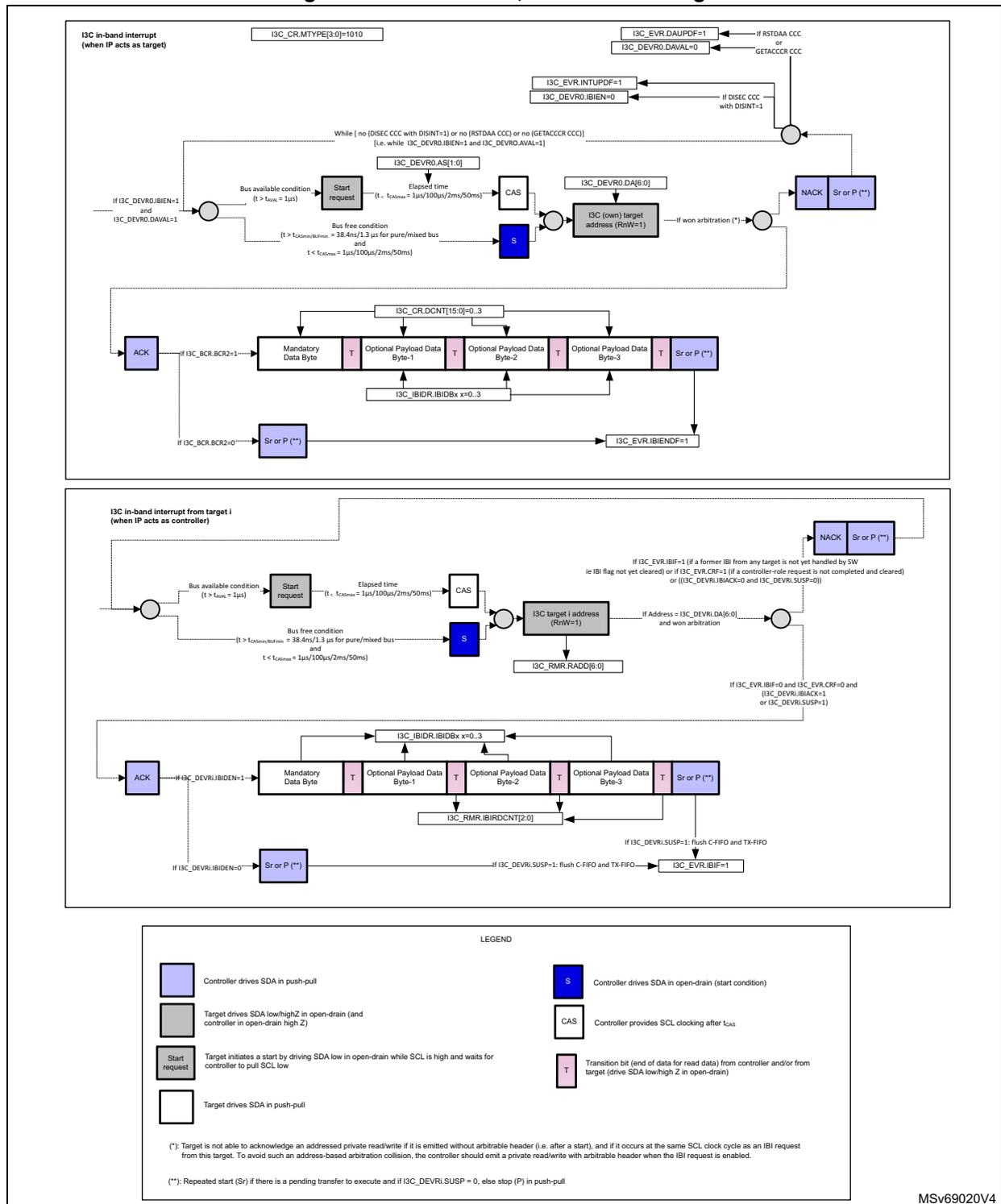

Start and receiving a target-initiated transfer

When the controller is in enabled state (EN = 1 in the I3C_CFGR register), concurrently to a possible controller-initiated transfer, a target can initiate a transfer by issuing a start request (drive SDA low), provided the controller has allowed a hot-join request, an IBI request, or a controller-role request via the I3C_DEVR0 register.

In this case, even though the controller software has no intent to start a frame transfer, the hardware switches to active state (activates the SCL clock before a maximum \( t_{CAS} \) time defined as 1 µs, 100 µs, 2 ms, or 50 ms, depending on, respectively, the bus activity state 0, 1, 2, or 3) to receive the hot-join/in-band interrupt/controller-role request from the target.

For more information about the execution of target-initiated I3C bus transfer and its related programming as a controller, refer to the relevant figures in Section 49.9 :

- • Figure 673: IBI transfer, as controller/target

- • Figure 674: Hot-join request transfer, as controller/target

- • Figure 675: Controller-role request transfer, as controller/target

Executing a (controller-initiated) frame transfer

The controller executes on the bus the frame transfer until the completion of the last message (FCF = 1 in the I3C_EVR register), or a transfer error (ERRF = 1 in the I3C_EVR register), and the corresponding interrupt, if enabled. This is based on I3C_CR and I3C_TD(W)R registers, written explicitly by software or pushed by the allocated DMA channel, and based on the I3C_RD(W)R, read explicitly by the software or by the allocated DMA channel. Then the I3C controller switches back to idle state.

For more information about the execution of controller-initiated I3C bus transfer and its related programming as a controller, refer to figures in Section 49.9 :

- • Figure 663: I3C CCC messages, as controller

- • Figure 664: I3C broadcast ENTDAA CCC, as controller

- • Figure 665: I3C broadcast, direct read and direct write RSTACT CCC, as controller

- • Figure 670: I3C private read/write messages, as controller

- • Figure 672: Legacy I2C read/write messages, as controller

Figure 661 does not include the management of the FIFOs (TX-FIFO, RX-FIFO, C-FIFO, and S-FIFO). This is detailed in Section 49.10 .

For each completed message without transfer error, the hardware reports the exchanged transfer on the I3C bus by updating I3C status register (I3C_SR) , which can be read or not by the software when the S-FIFO is disabled (SMODE = 0 in the I3C_CFGR register).

- • In the case of a direct CCC read or a private read transfer, in addition to the completion of the last message (FCF = 1 in the I3C_EVR register) or a transfer error (ERRF = 1 in the I3C_EVR register) and the corresponding interrupt if enabled, and provided that the S-FIFO is disabled for the status register I3C_SR (SMODE = 0 in the I3C_CFGR register), the software is notified if the read transfer is ended prematurely by the target by RXTGTENDF = 1 in the I3C_EVR register, and the corresponding interrupt, if enabled. The software can then read I3C_SR, to get more information about the executed transfer.

Alternatively, if the S-FIFO is enabled (SMODE = 1 in the I3C_CFGR register), the status register I3C_SR must be read for each executed message, either directly by the software (notified by SFNEF = 1 in the I3C_EVR register and the corresponding interrupt, if enabled), or via the DMA (if SDMAEN = 1 in the I3C_CFGR register), no matter if a read is prematurely ended by the target or not. Frame completion (FCF = 1 in the I3C_EVR register) occurs only after reading the status of the last message (S-FIFO is empty). For more information, refer to Section 49.10.4 .

Updating the configuration for a transfer, as controller

Back in idle state, the software can update the configuration of the I3C peripheral before the next transfer:

- • Modify SCL clock stalling via I3C timing register 2 (I3C_TIMINGR2)

- • Modify the interrupt/polling mode policy via I3C interrupt enable register (I3C_IER)

- • Modify the following fields of the

I3C configuration register (I3C_CFGR)

:

- – TXTHRES, RXTHRES

- – TMODE, SMODE

- – TXDMAEN, CDMAEN, RXDMAEN, SDMAEN

- – EXITPTRN, RSTPTRN

- – NOARBH

- • Modify/prepare the control words, status words, read/write data of the next frame transfer to be executed, by software and/or DMA

- – I3C message control register (I3C_CR), I3C message control register [alternate] (I3C_CR)

- – I3C status register (I3C_SR)

- – I3C transmit data byte register (I3C_TDR), I3C transmit data word register (I3C_TDWR)

- – I3C receive data byte register (I3C_RDR), I3C receive data word register (I3C_RDWR)

- • Typically after having issued and completed a broadcast/direct DISEC/ENEC CCC:

- – Modify the hot-join acknowledge policy via bit HJACK in the I3C_CFGR register

- – Modify IBI/CR acknowledge policy to any target x, via I3C device x characteristics register (I3C_DEVRx)

The registers usage versus the I3C peripheral role as controller is summarized in Section 49.8.1 .

The static/dynamic registers fields usage when acting as controller is summarized in Table 540 .

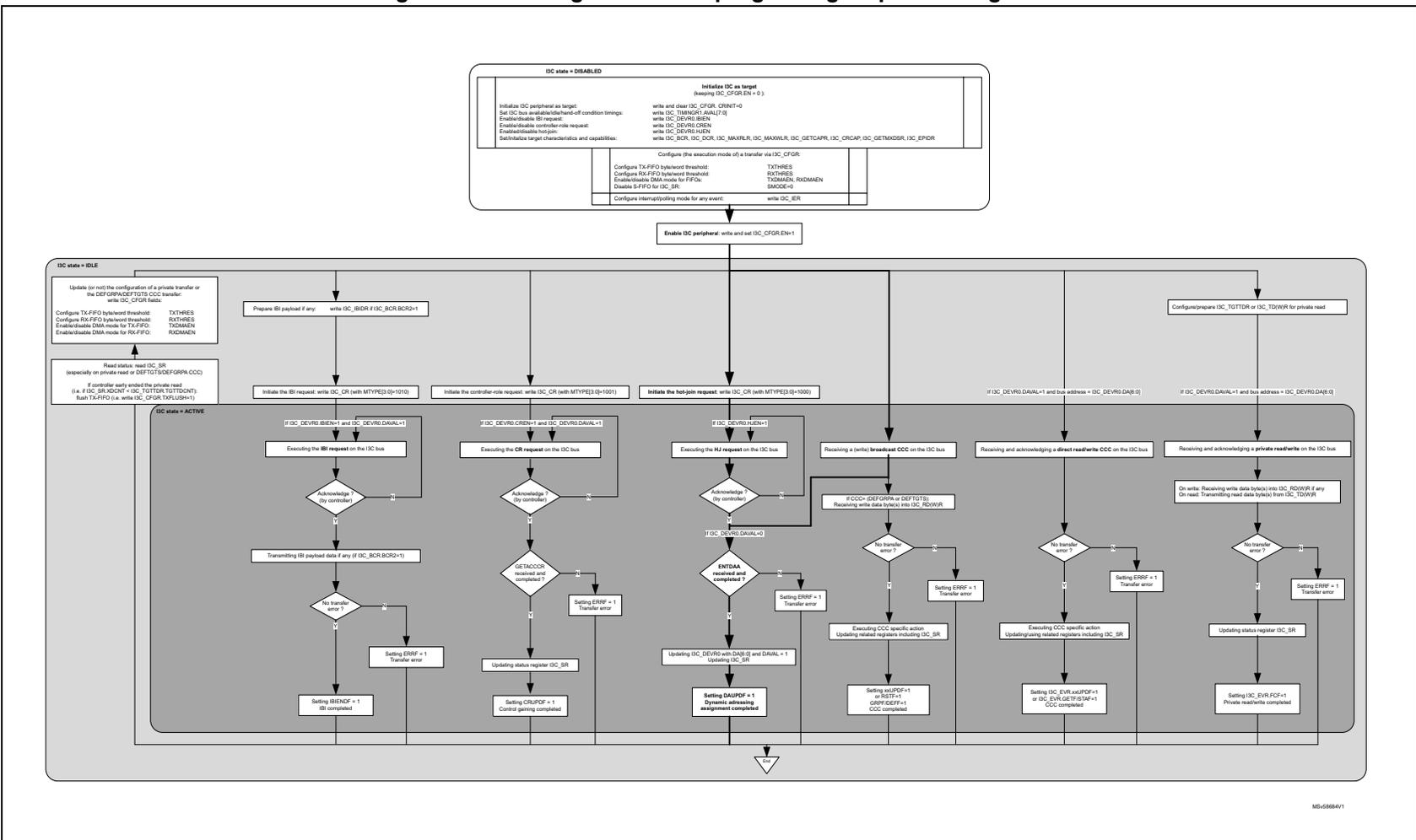

49.7.3 I3C target state and programming sequence

Figure 662 illustrates the overall programming sequence of the I3C peripheral acting as target, including state transitions, main subtasks, and conditions, as explained in this section.

Figure 662. I3C target state and programming sequence diagram

I3C state = DISABLED

- Initialize I3C as target (keeping I3C_CFSR.EN = 0).

- Initialize I3C peripheral as target:

- Set I3C bus availability/detachment condition settings: write and clear I3C_CFGR.CRINT=0

- Enable/disable IB request: write I3C_TAMSR.ANAVL[0]

- Enable/disable controller role request: write I3C_DEVIRD.IBEN

- Enable/disable target: write I3C_DEVIRD.CREN

- Enable/disable hot-plug: write I3C_DEVIRD.HEN

- Set I3C bus availability/detachment condition settings: write I3C_EOR.IGL, I3C_DEVIRD.MAWXR, I3C_DEVIRD.MAWXR, I3C_GETCAPR, I3C_CRCP, I3C_GETMDR, I3C_EPIDR

- Configure the execution mode of a transfer via I3C_CFGR:

- Configure TX-FIFO watermark threshold: TXTHRES

- Configure RX-FIFO watermark threshold: RXTHRES

- Enable/disable DMA mode for TX-FIFO: TXDMAEN, RXDMAEN

- Disable S-FIFO for I3C_SR: SMODE=0

- Configure interrupt/spoofing mode for any event: write I3C_ER

Enable I3C peripheral: write and set I3C_CFGR.EN=1

I3C state = IDLE

- Update (or reset) the configuration of a private transfer or the DEFUPA/DEFTOTS/CCC transfer: write I3C_CFGR.RAITS

- Configure TX-FIFO watermark threshold: TXTHRES

- Configure RX-FIFO watermark threshold: RXTHRES

- Enable/disable DMA mode for TX-FIFO: TXDMAEN, RXDMAEN

- Read status: read I3C_SR (especially on private read or DEFTOTS/DEFGRP.CCC) (i.e. if I3C_SR.RCNT = I3C_TOTDR.TOTDRN): flush TX-FIFO (i.e. write I3C_CFGR.TXFLUSH=1)

Preparation for transfer:

- Prepare IB payload if any: write I3C_IBDR if I3C_IBCR.BCR=1

- Initiate the IB request with I3C_CR (with MTYP[3:0]=1010)

- Initiate the controller role request with I3C_CR (with MTYP[3:0]=1001)

- Initiate the hot-plug request with I3C_CR (with MTYP[3:0]=1000)

- Configure/prepare I3C_TOTDR or I3C_TDWR for private read

I3C state = ACTIVE

- IB request path:

- If I3C_DEVIRD.IBEN=1 and I3C_DEVIRD.DAVAL=1: Executing the IB request on the I3C bus → Acknowledge? (by controller) → No transfer error? → Transmitting IB payload data if any (if I3C_IBCR.BCR=1) → No transfer error? → Setting IBENDF = 1 (IB completed)

- Else: Setting ERRIF = 1 (Transfer error)

- Controller role request path:

- If I3C_DEVIRD.CREN=1 and I3C_DEVIRD.DAVAL=1: Executing the CR request on the I3C bus → Acknowledge? (by controller) → SETACCR received and completed? → Updating status register I3C_SR → Setting CRRUPF = 1 (Control pairing completed)

- Else: Setting ERRIF = 1 (Transfer error)

- Hot-plug request path:

- If I3C_DEVIRD.HEN=1: Executing the NUT request on the I3C bus → Acknowledge? (by controller) → ENTAA received and completed? → Updating I3C_DEVIRD.DAVAL and DAVAL=1 → Updating I3C_SR → Setting DAUPF = 1 (Dynamic addressing assignment completed)

- Else: Setting ERRIF = 1 (Transfer error)

- Broadcast CCC path:

- Receiving a (only) broadcast CCC on the I3C bus → If CCC=0xDE/0F/0A or DEFTOTS: Receiving write data bytes into I3C_RDWR → No transfer error? → Executing CCC specific action: Updating related registers including I3C_SR → Setting xALLPF=1 or RSTP=1 (GENR/GETP=1 CCC completed)

- Else: Setting ERRIF = 1 (Transfer error)

- Direct read/write CCC path:

- Receiving and acknowledging a direct read/write CCC on the I3C bus → No transfer error? → Executing CCC specific action: Updating related registers including I3C_SR → Setting I3C_EVR.FCF=1 or I3C_EVR.GETP/STAF=1 (CCC completed)

- Else: Setting ERRIF = 1 (Transfer error)

- Private read/write path:

- Receiving and acknowledging a private read/write on the I3C bus → On read: Transmitting read data bytes from I3C_TDWR if any → No transfer error? → Updating status register I3C_SR → Setting I3C_EVR.FCF=1 (Private read/write completed)

- Else: Setting ERRIF = 1 (Transfer error)

End of sequence

Target initialization

When the target is in disabled state (EN = 0 in the I3C_CFGR register), the software must initialize as follows:

- • Set the I3C peripheral as target: write and clear CRINIT = 0 in the I3C_CFGR register

- • Set the I3C bus timings via

I3C timing register 1 (I3C_TIMINGR1)

: write AVAL[7:0] for:

- – Bus available condition time ( \( t_{\text{AVAL}} \) ) for IBI or controller-role request

- – Bus idle condition time ( \( t_{\text{IDLE}} \) ) for hot-join request

- – \( t_{\text{NEWCRLock}} \) for controller-role hand-off procedure (after GETACCCR CCC)

- • Configure target-initiated requests: write

I3C own device characteristics register (I3C_DEVR0)

with

- – IBIEN: in-band interrupt (also known as IBI) request enable/disable

- – CREN: controller-role request enable/disable

- – HJEN: hot-join request enable/disable

- • Initialize target characteristics and capabilities: write

- – I3C bus characteristics register (I3C_BCR)

- – I3C device characteristics register (I3C_DCR)

- – I3C maximum read length register (I3C_MAXRLR)

- – I3C maximum write length register (I3C_MAXWLR)

- – I3C get capability register (I3C_GETCAPR)

- – I3C controller-role capability register (I3C_CRCAPR)

- – I3C get max data speed register (I3C_GETMXDSR)

- – I3C extended provisioned ID register (I3C_EPIDR)

- • Configure the execution mode of a transfer:

I3C configuration register (I3C_CFGR)

, with the following fields:

- – TXDMAEN, RXDMAEN: DMA mode enable/disable for, respectively, TX-FIFO and RX-FIFO

- – TXTHRES, RXTHRES: respectively TX-FIFO and RX-FIFO byte/world threshold

- – Disable S-FIFO: SMODE = 0 (default/reset value)

- • Configure interrupt generation or polling mode from any event: I3C interrupt enable register (I3C_IER)

Then, the software can enable the I3C peripheral (write and set EN = 1).

Note: The software can write once all the fields of the I3C_CFGR register while enabling it.

Receiving a (broadcast CCC, direct read/write CCC or private read/write) message on the I3C bus

When the target is in idle state (EN = 1 in the I3C_CFGR register), the target is ready to receive a communication message on the I3C bus from the controller, and is ready to switch to the active state.

Typically, first, the active target is receiving a broadcast ENTDAA CCC, possibly after optional received broadcast ENEC/DISEC CCC(s), and is then assigned a dynamic address. The event DAUPF in the I3C_EVR register is raised to 1, the related interrupt is generated if enabled, and the target goes back to idle state.

After that, the idle target is ready to receive any other broadcast CCC message, or direct read/write CCC, or private read/write message from the controller.

For more information about the execution of controller-initiated I3C bus transfers and its related programming as a target, including the updated I3C registers and fields, refer to figures in Section 49.9 :

- • Figure 666: I3C CCC messages, as target

- • Figure 667: I3C broadcast ENTDAA CCC, as target

- • Figure 668: I3C broadcast DEFTGTS CCC, as target

- • Figure 669: I3C broadcast DEFGRPA CCC, as target

- • Figure 671: I3C private read/write messages, as target

Figure 662 does not include the FIFOs management (TX-FIFO, RX-FIFO). This is detailed in Section 49.10 .

Read the message status register

For each received and completed message without transfer error, the hardware reports the exchanged transfer on the bus by updating the I3C status register (I3C_SR) , which can be read by the software after being notified by the corresponding flag in the I3C event register (I3C_EVR) , or by the corresponding interrupt if enabled in the I3C interrupt enable register (I3C_IER) .

I3C status register (I3C_SR) must be read by the software after the following messages:

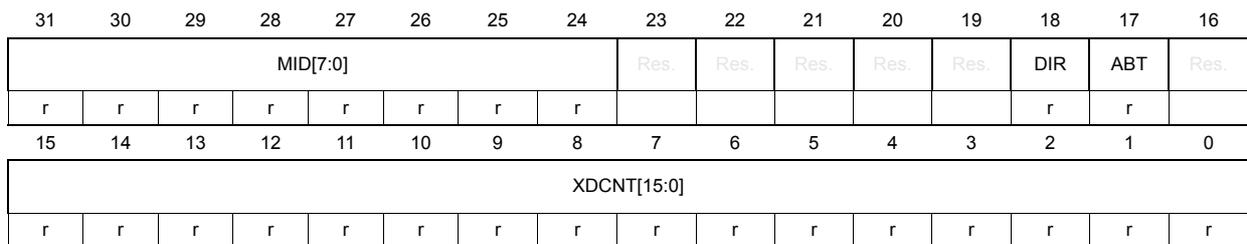

- • A private read: to get the number of exchanged data bytes, as the controller can have ended the transfer earlier than expected by the target (if XDCNT[15:0] in the I3C_SR register is lower than TGTDCNT[15:0] in the I3C_TGTDR register). If so, software must flush the TX-FIFO (write TXFLUSH = 1 in the I3C_CFGR register).

- • A DEFTGTS CCC or a DEFGRPA CCC: to get the number of received data bytes in the RX-FIFO

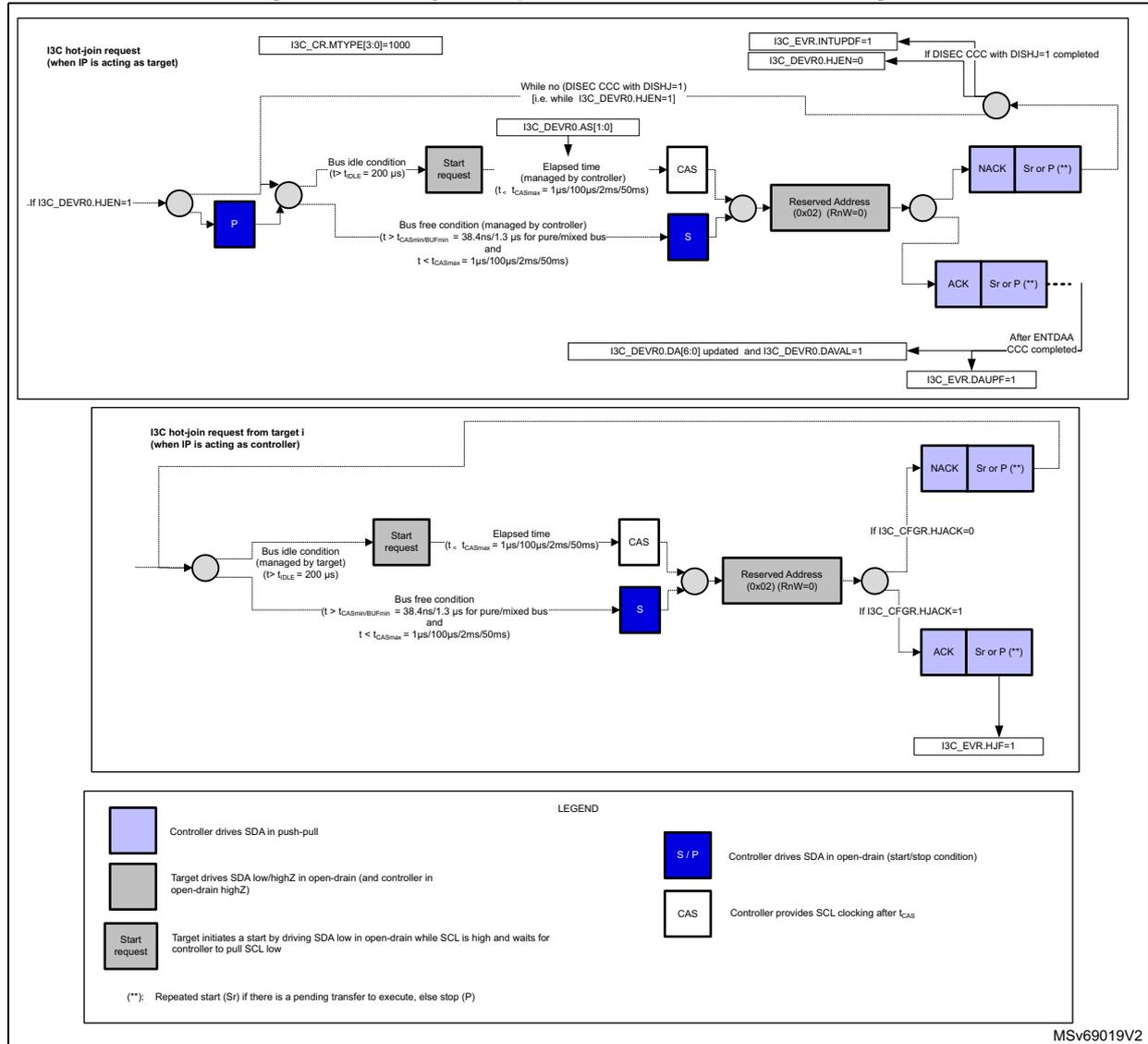

Start a (target-initiated) transfer on the I3C bus

When the target goes first from disabled to idle state (software writes EN = 1 in the I3C_CFGR register), concurrently to be able to receive a broadcast CCC from the controller, the software can initiate a hot-join request (the software writes MTYPE[3:0] = 1000 in the I3C_CR register) to be eligible to participate to a next ENTDAA CCC, provided it is allowed to do so (HJEN = 1 in the I3C_DEVR0 register).

Once a dynamic address is assigned (DAUPF = 1 in the I3C_EVR register), more generally and possibly concurrently to a frame transfer emitted by the controller, the software can initiate an IBI (in-band interrupt request) to the controller, or a controller-role request by writing the related control word into the I3C_CR register.

For more information about the execution of target-initiated I3C bus transfer, and its related programming as a target, refer to figures in Section 49.9 :

- • Figure 673: IBI transfer, as controller/target

- • Figure 674: Hot-join request transfer, as controller/target

- • Figure 675: Controller-role request transfer, as controller/target

Updating the configuration of the I3C peripheral, as target

Back in idle state, the software can update the configuration of the I3C target before a next transfer:

- • Modify the interrupt/polling mode policy via I3C interrupt enable register (I3C_IER)

- • Modify following fields of the

I3C configuration register (I3C_CFGR)

:

- – TXTHRES, RXTHRES

- – TXDMAEN, RXDMAEN

- • Modify/prepare the I3C IBI payload data register (I3C_IBIDR) , if any payload (if BCR2 = 1 in the I3C_BCR register), before initiating an IBI transfer (write I3C message control register [alternate] (I3C_CR) with MTYPE[3:0] = 1010)

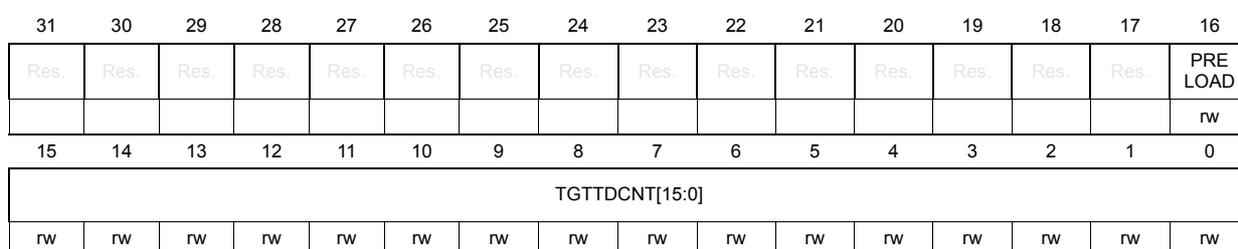

- • Modify/prepare I3C target transmit configuration register (I3C_TGTTDR) , to disable or enable the TX-FIFO to be preloaded with a defined number of data bytes to be transmitted, before receiving a private read or a direct CCC read (out of the GETSTATUS CCC)

The registers usage vs. the I3C peripheral role as target is summarized in Section 49.8.1 .

The static/dynamic registers fields usage, when acting as target, is summarized in Table 541 .

49.8 I3C registers and programming

49.8.1 I3C register set, as controller/target

Table 539 lists the registers and their usage versus the I3C peripheral role.

Table 539. I3C register usage

| Register | Used as controller | Used as target |

|---|---|---|

| I3C_CR | X | X |

| I3C_CFGR | X | X |

| I3C_RDR | X | X |

| I3C_RDWR | X | X |

| I3C_TDR | X | X |

| I3C_TDWR | X | X |

| I3C_IBIDR | X | X |

| I3C_TGTTDR | - | X |

| I3C_SR | X | X |

| I3C_SER | X | X |

| I3C_RMR | X | X |

| I3C_EVR | X | X |

| I3C_IER | X | X |

| I3C_CEVR | X | X |

| I3C_DEVR0 | X | X |

Table 539. I3C register usage (continued)

| Register | Used as controller | Used as target |

|---|---|---|

| I3C_DEVRx (x = 1 to 4) | X | - |

| I3C_MAXRLR | - | X |

| I3C_MAXWLR | - | X |

| I3C_TIMINGR0 | X | - |

| I3C_TIMINGR1 | X | X |

| I3C_TIMINGR2 | X | - |

| I3C_BCR | - | X |

| I3C_DCR | - | X |

| I3C_GETCAPR | - | X |

| I3C_CRCAPR | - | X |

| I3C_GETMXDSR | - | X |

| I3C_EPIDR | - | X |

49.8.2 I3C registers and fields use versus peripheral state, as controller

When the I3C peripheral acts as controller, Table 540 lists the registers and their usage versus the controller state (disabled, idle, and active).

Table 540. I3C registers/fields usage versus controller state

| Register | Used as controller | Writable only in disabled state | Typically written/read in idle state | Typically written/read in idle or active state |

|---|---|---|---|---|

| I3C_CR | X | - | - | X |

Table 540. I3C registers/fields usage versus controller state (continued)

| Register | Used as controller | Writable only in disabled state | Typically written/read in idle state | Typically written/read in idle or active state |

|---|---|---|---|---|

| I3C_CFGR | X | CRINIT HKSDAEN EN (1) | Write: any used field except {CRINIT, HKSDAEN}, namely {CDMAEN SDMAEN TXDMAEN RXDMAEN TMODE SMODE TXTHRES RXTHRES HJACK EXITPTRN RSTPTRN NOARBH} (2) CFLUSH SFLUSH TXFLUSH RXFLUSH TSFSET | - |

| I3C_RDR | X | - | - | Read |

| I3C_RDWR | X | - | - | Read |

| I3C_TDR | X | - | - | Write |

| I3C_TDWR | X | - | - | Write |

| I3C_IBIDR | X | - | - | Read |

| I3C_TGTTDR | - | |||

| I3C_SR | X | - | - | Read |

| I3C_SER | X | - | Read | - |

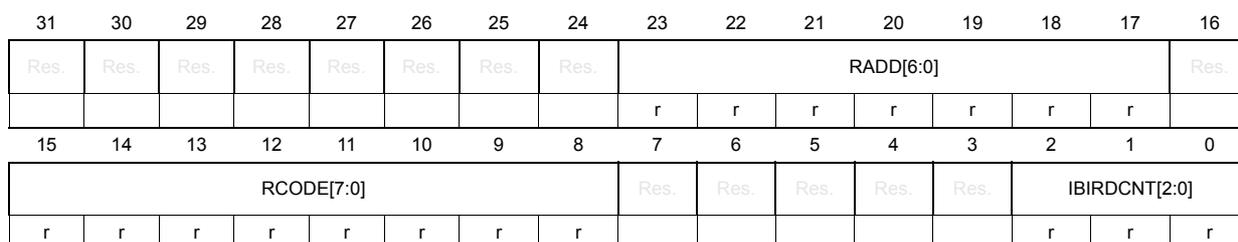

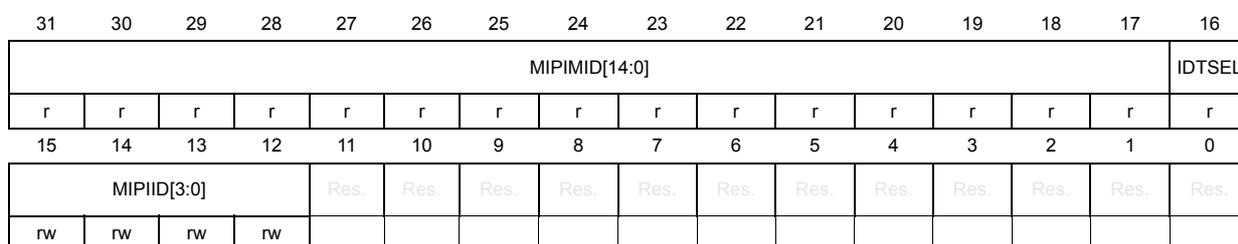

| I3C_RMR | X | - | - | Read RADD[6:0] IBIRDCNT[2:0] |

Table 540. I3C registers/fields usage versus controller state (continued)

| Register | Used as controller | Writable only in disabled state | Typically written/read in idle state | Typically written/read in idle or active state |

|---|---|---|---|---|

| I3C_EVR | X | - | - | Read (controller-role fields): HJF CRF IBIF FCF ERRF RXTGTENDF RXFNEF TXFNFF SFNEF CFNFF RXLASTF TXLASTF TXFEF CFEF |

| I3C_IER | X | Write xIE with x = HJ, CR, IBI, FC, ERR, RXTGTEND, RXFNE, TXFNF, SFNE, CFNF (2) | ||

| I3C_CEVR | X | - | - | Write (controller-role fields, refer to I3C_EVR) |

| I3C_DEVR0 | X | Write DA[6:0] (2) | ||

| I3C_DEVRx x = 1..4 | X | Write SUSP, IBIDEN, IBIACK, CRACK, DA[6:0] (2) | ||

| I3C_MAXRLR | - | |||

| I3C_MAXWLR | - | |||

| I3C_TIMINGR0 | X | X | - | - |

| I3C_TIMINGR1 | X | X | - | - |

| I3C_TIMINGR2 | X | Write (2) | ||

| I3C_BCR | - | |||

| I3C_DCR | - | |||

| I3C_GETCAPR | - | |||

| I3C_CRCAPR | - | |||

| I3C_GETMXDSR | - | |||

| I3C_EPIDR | - | |||

1. Bit EN in the I3C_CFGR register is written and set in disabled state (when the same bit is 0). This field can be also written and de-asserted in idle state.

2. These fields are typically written and initialized in disabled state during bus configuration. They are not write-protected when EN = 0, and can be also written and updated in other state(s).

49.8.3 I3C registers and fields usage versus peripheral state, as target

When the I3C peripheral acts as target, Table 541 lists the registers and their usage versus the I3C target state (disabled, idle, and active).

Table 541. I3C registers/fields usage versus target state

| Register | Used as target | Writable only in disabled state | Typically written/read in idle state | Typically written/read in idle or active state |

|---|---|---|---|---|

| I3C_CR | X | - | MTYPE[3:0] DCNT[2:0] | - |

| I3C_CFGR | X | CRINIT EN (1) | Write: any used field except CRINIT, namely: {TXDMAEN RXDMAEN TXTHRES RXTHRES} (2) TXFLUSH RXFLUSH | - |

| I3C_RDR | X | - | - | Read |

| I3C_RDWR | X | - | - | Read |

| I3C_TDR | X | - | - | Write |

| I3C_TDWR | X | - | - | Write |

| I3C_IBIDR | X | - | Write | - |

| I3C_TGTTDR | X | - | Write | - |

| I3C_SR | X | - | - | Read DIR, XDCNT[15:0] |

| I3C_SER | X | - | Read DOVR, STALL, PERR, CODERR[3:0] | - |

| I3C_RMR | X | - | - | Read RCODE[7:0] |

Table 541. I3C registers/fields usage versus target state (continued)

| Register | Used as target | Writable only in disabled state | Typically written/read in idle state | Typically written/read in idle or active state |

|---|---|---|---|---|

| I3C_EVR | X | - | - | Read (target-role fields): GRPF DEFF INTUPDF ASUPDF RSTF MRLUPDF MWLUPDF DAUPDF STAF GETF WKPF CRUPDF IBIENDF ERRF FCF RXFNEF TXFNFF TXLASTF TXFEF |

| I3C_IER | X | Write xIE with x = GRP, DEF, INTUPD, ASUPD, RST, MRLUPD, MWLUPD, DAUPD, STA, GET, WKP, CRUPD, IBIEND, ERR, FC, RXFNE, TXFNF (2) | ||

| I3C_CEVR | X | - | - | Write (target-role fields, refer to I3C_EVR) |

| I3C_DEVR0 | X | HJEN CREN IBIEN | Read RSTVAL, RSTACT[1:0], and AS[1:0] | - |

| I3C_DEVRx x = 1..4 | - | |||

| I3C_MAXRLR | X | X | - | - |

| I3C_MAXWLR | X | X | - | - |

| I3C_TIMINGR0 | - | |||

| I3C_TIMINGR1 | X | AVAL[7:0] | - | - |

| I3C_TIMINGR2 | - | |||

| I3C_BCR | X | X | - | - |

| I3C_DCR | X | X | - | - |

| I3C_GETCAPR | X | X | - | - |

| I3C_CRCAPR | X | X | - | - |

| Register | Used as target | Writable only in disabled state | Typically written/read in idle state | Typically written/read in idle or active state |

|---|---|---|---|---|

| I3C_GETMXDSR | X | X | - | - |

| I3C_EPIDR | X | X | - | - |

- 1. Bit EN in the I3C_CFGR register is written and set in disabled state (when the same bit is 0). This field can be also written and de-asserted in idle state.

- 2. These fields are typically written and initialized in disabled state during I3C bus configuration. They are not write-protected when EN = 0.

49.9 I3C bus transfers and programming

49.9.1 I3C command set (CCCs), as controller/target

The list of the supported I3C command set (for example, list of CCCs, common command codes) and the overview of how they are handled by the I3C peripheral acting as controller or target, is specified in Table 542 .

Table 542. List of supported I3C CCCs, as controller/target

| CCC name | CCC value | Read /write | With/without defining byte With/without sub-command byte | With/without optional data byte(s) | Use as controller | Use as target, raised I3C_EVR event | When target: specific action |

|---|---|---|---|---|---|---|---|

| Broadcast CCCs | |||||||

| ENEC | 0x00 | Write | No defining/sub-command byte | With one data byte (enable target events byte) | X | X, INTUPDF | Update and enable I3C_DEVR0: HJEN, CREN, IBIEN if any |

| DISEC | 0x01 | With one data byte (disable target events byte) | X | X, INTUPDF | Update and disable I3C_DEVR0: HJEN, CREN, IBIEN if any | ||

| ENTASx x = 0...3 | 0x02 ... 0x05 | No data byte | X | X, ASUPDF | Update I3C_DEVR0.AS[1:0] | ||

| RSTDAA | 0x06 | - | X | X, DAUPDF | Clear I3C_DEVR0.DAVAL = 0 | ||

| ENTDAA | 0x07 | - | X | X, DAUPDF if DAVAL = 0 | Update I3C_DEVR0: DA[6:0] and set DAVAL = 1 | ||

| DEFTGTS | 0x08 | With [1+ 4x (1+ number_of_targets)] x data bytes | X | X, DEFF | Update I3C_RDR/ I3C_RDWR. Refer to Figure 668 . | ||

| SETMWL | 0x09 | With two data byte | X | X, MWLUPDF | Update I3C_MAXWLR | ||

| SETMRL | 0x0A | With 2 or 3 data bytes | X | X, MRLUPDF | Update I3C_MAXRLR | ||

| ENTTM | 0x0B | With one data byte | X | - | - | ||

| SETXTIME | 0x28 | With sub-command byte | Without or with one or more data bytes | X | - | - | |

| SETAASA | 0x29 | No defining/sub-command byte | No data byte | X | - | - | |

| RSTACT | 0x2A | With defining byte (0x00, 0x01 or 0x02) | X | X, RSTF after detected reset pattern | Update I3C_DEVR0: RSTACT[1:0] and set RSTVAL = 1 | ||

| DEFGRP | 0x2B | No defining/sub-command byte | With several data bytes | X | X, GRPF | Update I3C_RDR/ RDWR. Refer to Figure 669 . | |

| RSTGRP | 0x2C | No data byte | X | - | - | ||

Table 542. List of supported I3C CCCs, as controller/target (continued)

| CCC name | CCC value | Read /write | With/without defining byte With/without sub-command byte | With/without optional data byte(s) | Use as controller | Use as target, raised I3C_EVR event | When target: specific action |

|---|---|---|---|---|---|---|---|

| Direct CCCs | Action if ACK (if I3C target Address = I3C_DEVR0.DA[6:0] and I3C_DEVR0.DAVAL = 1) (else NACK) | ||||||

| ENEC | 0x80 | Write | No defining/sub-command byte | With one data byte (enable target events byte) | X | X, INTUPDF | Update and enable I3C_DEVR0: HJEN, CREN, IBIEN if any |

| DISEC | 0x81 | With one data byte (disable target events byte) | X | X, INTUPDF | Update and disable I3C_DEVR0: HJEN, CREN, IBIEN if any | ||

| ENTASx x = 0...3 | 0x82.. ..0x85 | No data byte | X | X, ASUPDF | Update I3C_DEVR0.AS[1:0] | ||

| SETDASA | 0x87 | No data byte | X | - | - | ||

| SETNEWDA | 0x88 | With one data byte | X | X, DAUPDF if DAVAL = 1 | Update I3C_DEVR0: DA[6:0] (and keep DAVAL = 1) | ||

| SETMWL | 0x89 | With two data bytes | X | X, MWLUPDF | Update I3C_MAXWLR | ||

| SETMRL | 0x8A | With two or three data bytes | X | X, MRLUPDF | Update I3C_MAXRLR | ||

| GETMWL | 0x8B | Read | No defining/sub-command byte | With two data bytes | X | X, GETF | Return data bytes from I3C_MAXWLR[15:0]. Refer to Section 49.16.19 . |

| GETMRL | 0x8C | With two or three data bytes | X | X, GETF | Return data bytes from I3C_MAXRLR[15:0] and if I3C_BCR.BCR2 = 1 return third byte from I3C_MAXRLR.IBIP[2:0]. Refer to Section 49.16.18 . | ||

Table 542. List of supported I3C CCCs, as controller/target (continued)

| CCC name | CCC value | Read /write | With/without defining byte With/without sub-command byte | With/without optional data byte(s) | Use as controller | Use as target, raised I3C_EVR event | When target: specific action |

|---|---|---|---|---|---|---|---|

| GETPID | 0x8D | Read | No defining/sub-command byte | With six data bytes | X | X, GETF | Return data bytes from I3C_EPIDR. Refer to Section 49.16.28 . |

| GETBCR | 0x8E | With one data byte | X | X, GETF | Return data byte from I3C_BCR[7:0]. Refer to Section 49.16.23 . | ||

| GETDCR | 0x8F | X | X, GETF | Return I3C_DCR[7:0]. Refer to Section 49.16.24 . | |||

| GETSTATUS | 0x90 | With or without defining byte (TGTSTAT, PRECR) | With two data bytes (format 1 or format 2 with PRECR) | X | X, STAF if format 1 X, GETF if format 2 | Return 2 data bytes, as detailed in Section 49.9.9 . | |

| GETACCCR | 0x91 | No defining/sub-command byte | With one data byte | X | X, CRUPDF | Return data byte from I3C_DEVR0.DA[6:0] with parity bit | |

| GETMXDS | 0x94 | With or without defining byte (WRRDTURN, CRHDLY) | With two data bytes (format 1) or 5 data bytes (format 2 or format 3 with WRRDTURN) or 1 data byte (format 3 with CRHDLY) | X | X, GETF | Return data byte(s) from I3C_GETMXDSR. Refer to Section 49.16.27 . | |

| GETCAPS | 0x95 | With or without defining byte (TGTSTAT, CRCAPS) | With 3 data bytes (format 1 or format 2 with TGTSTAT) or two data bytes (format 2 with CRCAPS) | X | X, GETF | Return 3 GETCAPx data bytes from I3C_GETCAPR (refer to Section 49.16.25 ) or Return 2 CRCAPx data bytes from I3C_CRCAPR (refer to Section 49.16.26 ) | |

| D2DXFER | 0x97 | Write | With defining byte | With defining byte | X | - | - |

| SETXTIME | 0x98 | With sub-command byte | With sub-command byte | X | |||

| GETXTIME | 0x99 | Read | No defining/sub-command byte | No defining/sub-command byte | X |

Table 542. List of supported I3C CCCs, as controller/target (continued)

| CCC name | CCC value | Read /write | With/without defining byte With/without sub-command byte | With/without optional data byte(s) | Use as controller | Use as target, raised I3C_EVR event | When target: specific action |

|---|---|---|---|---|---|---|---|

| RSTACT | 0x9A | Read/Write | With defining byte (0x00, 0x01, or 0x02) | With defining byte (0x00, 0x01, or 0x02) | X | X, RSTF if detected reset pattern | Read: return data byte from RSTACT[1:0] in the I3C_DEVR0 register. Write: update I3C_DEVR0: RSTACT[1:0] and set RSTVAL = 1 |

| SETGRPA | 0x9B | Write | No defining/sub-command byte | No defining/sub-command byte | X | - | - |

| RSTGRPA | 0x9C | X |

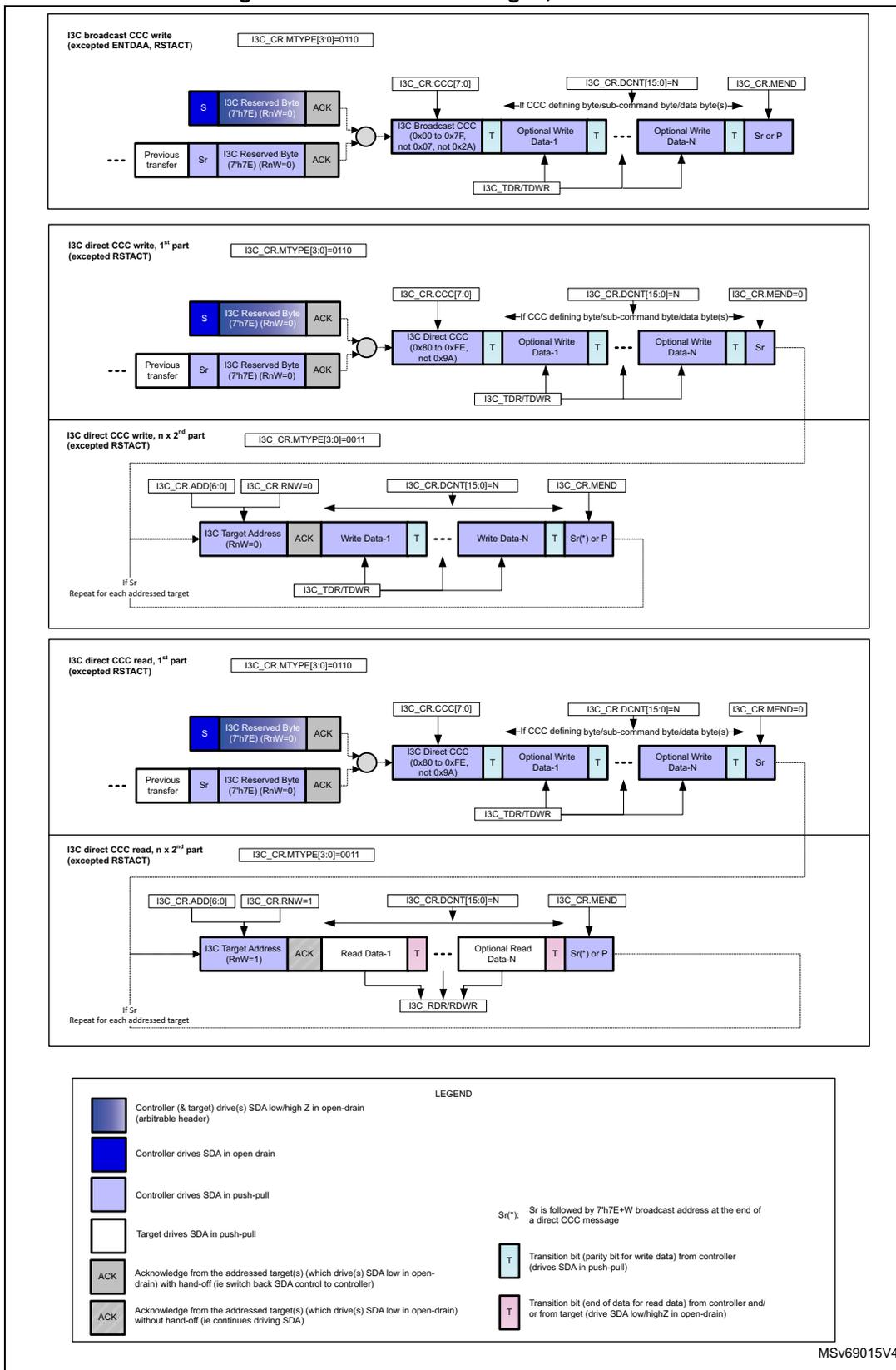

49.9.2 I3C broadcast/direct CCC transfer (except ENTDAA, RSTACT), as controller

Figure 663 illustrates I3C broadcast CCC write transfer (except ENTDAA, RSTACT), and direct CCC read/write transfer, as communicated on the I3C bus, and as programmed when acting as controller.

Figure 663. I3C CCC messages, as controller

I3C broadcast CCC write (excepted ENTDA, RSTACT)

I3C_CR.MTYPE[3:0]=0110

Sequence: Previous transfer → Sr → I3C Reserved Byte (7h/E) (RnW=0) → ACK → I3C Broadcast CCC (0x00 to 0x7F, not 0x07, not 0x2A) → T → Optional Write Data-1 → T → ... → Optional Write Data-N → T → Sr or P

Control signals: I3C_CR.CCC[7:0], I3C_CR.DCNT[15:0]=N, I3C_CR.MEND, I3C_TDR/TDWR

I3C direct CCC write, 1

st

part (excepted RSTACT)

I3C_CR.MTYPE[3:0]=0110

Sequence: Previous transfer → Sr → I3C Reserved Byte (7h/E) (RnW=0) → ACK → I3C Direct CCC (0x80 to 0xFE, not 0x9A) → T → Optional Write Data-1 → T → ... → Optional Write Data-N → T → Sr

Control signals: I3C_CR.CCC[7:0], I3C_CR.DCNT[15:0]=N, I3C_CR.MEND=0, I3C_TDR/TDWR

I3C direct CCC write, n x 2

nd

part (excepted RSTACT)

I3C_CR.MTYPE[3:0]=0011

Sequence: I3C Target Address (RnW=0) → ACK → Write Data-1 → T → ... → Write Data-N → T → Sr(*) or P

Control signals: I3C_CR.ADD[6:0], I3C_CR.RNW=0, I3C_CR.DCNT[15:0]=N, I3C_CR.MEND, I3C_TDR/TDWR

Note: Repeat for each addressed target if Sr

I3C direct CCC read, 1

st

part (excepted RSTACT)

I3C_CR.MTYPE[3:0]=0110

Sequence: Previous transfer → Sr → I3C Reserved Byte (7h/E) (RnW=0) → ACK → I3C Direct CCC (0x80 to 0xFE, not 0x9A) → T → Optional Write Data-1 → T → ... → Optional Write Data-N → T → Sr

Control signals: I3C_CR.CCC[7:0], I3C_CR.DCNT[15:0]=N, I3C_CR.MEND=0, I3C_TDR/TDWR

I3C direct CCC read, n x 2

nd

part (excepted RSTACT)

I3C_CR.MTYPE[3:0]=0011

Sequence: I3C Target Address (RnW=1) → ACK → Read Data-1 → T → ... → Optional Read Data-N → T → Sr(*) or P

Control signals: I3C_CR.ADD[6:0], I3C_CR.RNW=1, I3C_CR.DCNT[15:0]=N, I3C_CR.MEND, I3C_RDR/RDWR

Note: Repeat for each addressed target if Sr

LEGEND

- Controller (& target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in open drain

- Controller drives SDA in push-pull

- Target drives SDA in push-pull

- ACK: Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) with hand-off (ie switch back SDA control to controller)

- ACK: Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) without hand-off (ie continues driving SDA)

- T: Transition bit (parity bit for write data) from controller (drives SDA in push-pull)

- T: Transition bit (end of data for read data) from controller and/or from target (drive SDA low/highZ in open-drain)

- Sr(*): Sr is followed by 7h7E+W broadcast address at the end of a direct CCC message

MSV69015V4

49.9.3 I3C broadcast ENTDAA CCC transfer, as controller

Figure 664 illustrates I3C broadcast ENTDAA CCC, as communicated on the I3C bus, and as programmed when acting as controller.

Figure 664. I3C broadcast ENTDAA CCC, as controller

![Timing diagram for I3C broadcast ENTDAA CCC transfer. The sequence starts with a Previous transfer ending in ACK. The controller then generates a Start (Sr) condition, followed by an I3C reserved byte (7'h7E) with RnW=0, and an ACK. Next, the controller sends the I3C broadcast CCC (ENTDAA=0x07) with a transition bit (T=0). This is followed by a loop for each target to be assigned: the controller sends an I3C reserved byte (7'h7E) with RnW=1, an ACK, 8 bytes of read data (48-bit unique ID(*), BCR, DCR), an assign address to the winning target (7 bits), a parity bit (PAR), and an ACK/NACK. The controller then generates another Start (Sr) condition, followed by an I3C reserved byte (7'h7E) with RnW=1, a NACK, and a Stop (P) condition. Control signals shown include I3C_CR.CCC[7:0]=0x07, I3C_CR.DCNT[15:0]=0, I3C_RDR/RDWR, I3C_TDR/TDWR, I3C_EVR.FCF=1, and I3C_SR (MID[7:0], DIR=0, XDCNT[15:0]=# of assigned targets).](/RM0481-STM32H523-33-562-63-573/0dd926e824c4039a745aba4554bd751c_img.jpg)

ENTDAA (I3C broadcast CCC write) (when IP is acting as controller)

Legend:

- Controller (and target) drives SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in open-drain

- Controller drives SDA in push-pull

- Target(s) drive SDA low/highZ in open-drain (and controller in open-drain highZ)

- ACK Acknowledge from the addressed target(s) (which drives SDA low in open-drain) with hand-off (i.e. switch back SDA control to controller)

- ACK Acknowledge from the addressed target(s) (which drives SDA low in open-drain) without hand-off (i.e. continues driving SDA low/highZ in open-drain)

- T Transition bit (parity bit for CCC) from controller (drives SDA in push-pull)

(*): 48-bit unique/provisioned ID is subject to arbitration. The target which wins arbitration continues to provide its BCR and DCR.

MSV69013V4

49.9.4 I3C broadcast/direct RSTACT CCC transfer, as controller

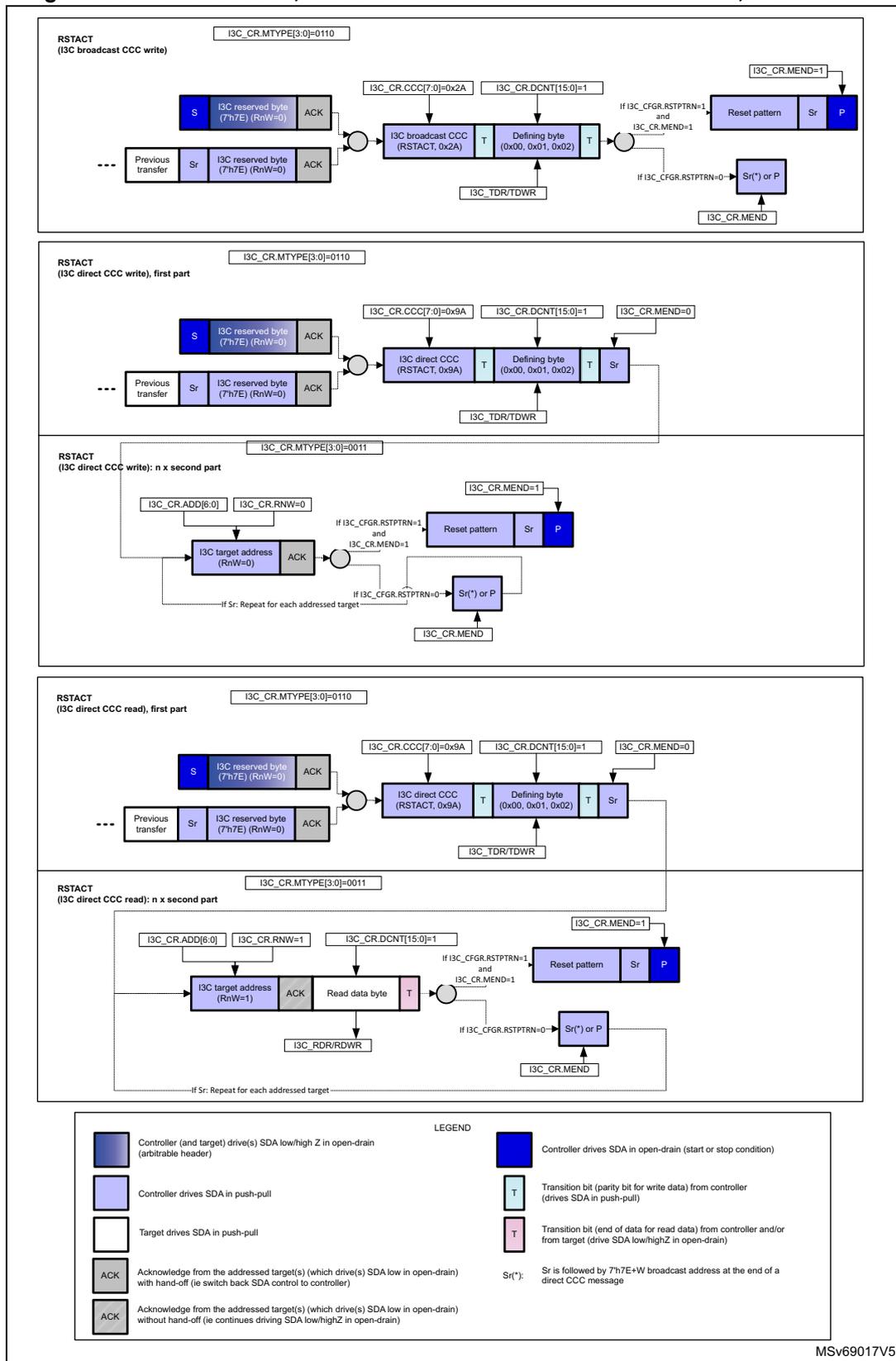

Figure 665 illustrates I3C broadcast (write), direct write and read RSTACT CCC, as communicated on the I3C bus, and as programmed when acting as controller.

Figure 665. I3C broadcast, direct read and direct write RSTART CCC, as controller

The figure illustrates five timing diagrams for I3C RSTART conditions, categorized by the I3C_CR.MTYPE[3:0] register value.

- RSTART (I3C broadcast CCC write): I3C_CR.MTYPE[3:0]=0110. The sequence starts with a previous transfer (Sr, I3C reserved byte (7h7E) (RnW=0), ACK). The controller drives the I3C broadcast CCC (RSTART, 0x2A) followed by a defining byte (0x00, 0x01, 0x02). The I3C_CR.CCC[7:0] register is set to 0x2A and I3C_CR.DCNT[15:0] is set to 1. The transfer ends with a reset pattern, Sr, and P if I3C_CR.MEND=1, or Sr(*) or P if I3C_CR.MEND=0.

- RSTART (I3C direct CCC write), first part: I3C_CR.MTYPE[3:0]=0110. The sequence starts with a previous transfer (Sr, I3C reserved byte (7h7E) (RnW=0), ACK). The controller drives the I3C direct CCC (RSTART, 0x9A) followed by a defining byte (0x00, 0x01, 0x02). The I3C_CR.CCC[7:0] register is set to 0x9A and I3C_CR.DCNT[15:0] is set to 1. The transfer ends with Sr and I3C_CR.MEND=0.

- RSTART (I3C direct CCC write): n x second part: I3C_CR.MTYPE[3:0]=0011. The sequence starts with the I3C target address (RnW=0) followed by ACK. The transfer ends with a reset pattern, Sr, and P if I3C_CR.MEND=1, or Sr(*) or P if I3C_CR.MEND=0. A note indicates that if Sr is repeated for each addressed target, the sequence continues.

- RSTART (I3C direct CCC read), first part: I3C_CR.MTYPE[3:0]=0110. The sequence starts with a previous transfer (Sr, I3C reserved byte (7h7E) (RnW=0), ACK). The controller drives the I3C direct CCC (RSTART, 0x9A) followed by a defining byte (0x00, 0x01, 0x02). The I3C_CR.CCC[7:0] register is set to 0x9A and I3C_CR.DCNT[15:0] is set to 1. The transfer ends with Sr and I3C_CR.MEND=0.

- RSTART (I3C direct CCC read): n x second part: I3C_CR.MTYPE[3:0]=0011. The sequence starts with the I3C target address (RnW=1) followed by ACK. The controller then drives the read data byte. The transfer ends with a reset pattern, Sr, and P if I3C_CR.MEND=1, or Sr(*) or P if I3C_CR.MEND=0. A note indicates that if Sr is repeated for each addressed target, the sequence continues.

LEGEND

- Controller (and target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in push-pull

- Target drives SDA in push-pull

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) with hand-off (ie switch back SDA control to controller)

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) without hand-off (ie continues driving SDA low/highZ in open-drain)

- Controller drives SDA in open-drain (start or stop condition)

- T Transition bit (parity bit for write data) from controller (drives SDA in push-pull)

- T Transition bit (end of data for read data) from controller and/or from target (drive SDA low/highZ in open-drain)

- Sr(*) or P Sr is followed by 7h7E+W broadcast address at the end of a direct CCC message

MSV69017V5

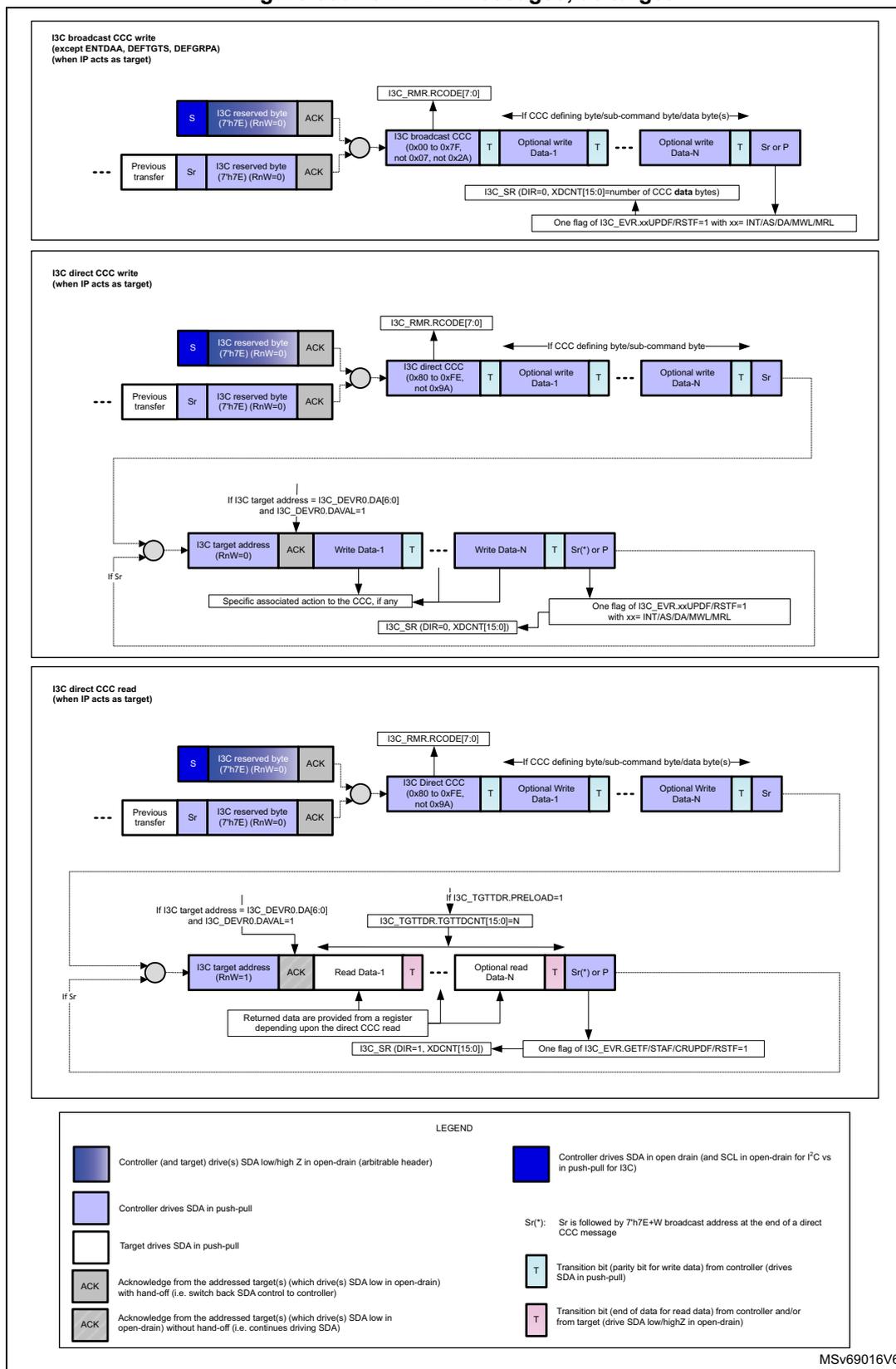

49.9.5 I3C broadcast/direct CCC transfer

(except ENTDA, DEFTGTS, DEFGRPA), as target

Figure 666 illustrates I3C broadcast CCC write transfer (except ENTDA, DEFTGTS, DEFGRPA), direct CCC read/write transfer, as communicated on the I3C bus, and as programmed when acting as target.

Figure 666. I3C CCC messages, as target

The diagram illustrates three types of I3C CCC messages when the IP acts as a target:

- I3C broadcast CCC write (except ENTDA, DEFTGTS, DEFGRPA) (when IP acts as target): This sequence starts with a previous transfer ending in a Stop (Sr) and an I3C reserved byte (7h7E) (RnW=0) followed by an ACK. The target then drives an I3C broadcast CCC (0x00 to 0x7F, not 0x07, not 0x2A) followed by optional write data (Data-1 to Data-N). Each data byte is followed by a Transition bit (T). The sequence ends with a Stop (Sr) or a P (Pre-emption). Control signals include I3C_RMR.CODE[7:0], I3C_SR (DIR=0, XDCNT[15:0]=number of CCC data bytes), and a flag in I3C_EVR.xxUPDF/RSTF=1 with xx= INT/AS/DA/MWL/MRL.

- I3C direct CCC write (when IP acts as target): This sequence starts with a previous transfer ending in a Stop (Sr) and an I3C reserved byte (7h7E) (RnW=0) followed by an ACK. The target then drives an I3C direct CCC (0x80 to 0xFE, not 0x9A) followed by optional write data (Data-1 to Data-N). Each data byte is followed by a Transition bit (T). The sequence ends with a Stop (Sr) or a P. Control signals include I3C_RMR.CODE[7:0], I3C_SR (DIR=0, XDCNT[15:0]), and a flag in I3C_EVR.xxUPDF/RSTF=1 with xx= INT/AS/DA/MWL/MRL. If the I3C target address equals I3C_DEVR0.DA[6:0] and I3C_DEVR0.DAVAL=1, the target address (RnW=0) is followed by an ACK and then write data (Data-1 to Data-N).

- I3C direct CCC read (when IP acts as target): This sequence starts with a previous transfer ending in a Stop (Sr) and an I3C reserved byte (7h7E) (RnW=0) followed by an ACK. The target then drives an I3C direct CCC (0x80 to 0xFE, not 0x9A) followed by optional write data (Data-1 to Data-N). Each data byte is followed by a Transition bit (T). The sequence ends with a Stop (Sr) or a P. Control signals include I3C_RMR.CODE[7:0], I3C_TGTTDR.PRELOAD=1, I3C_TGTTDR.TGTTDCNT[15:0]=N, I3C_SR (DIR=1, XDCNT[15:0]), and a flag in I3C_EVR.GETF/STAF/CRUPDF/RSTF=1. If the I3C target address equals I3C_DEVR0.DA[6:0] and I3C_DEVR0.DAVAL=1, the target address (RnW=1) is followed by an ACK and then read data (Data-1 to Data-N). Returned data are provided from a register depending upon the direct CCC read.

LEGEND

- Controller (and target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in push-pull

- Target drives SDA in push-pull

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) with hand-off (i.e. switch back SDA control to controller)

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) without hand-off (i.e. continues driving SDA)

- Sr('): Sr is followed by 7h7E+W broadcast address at the end of a direct CCC message

- T Transition bit (parity bit for write data) from controller (drives SDA in push-pull)

- T Transition bit (end of data for read data) from controller and/or from target (drive SDA low/highZ in open-drain)

MSV69016V6

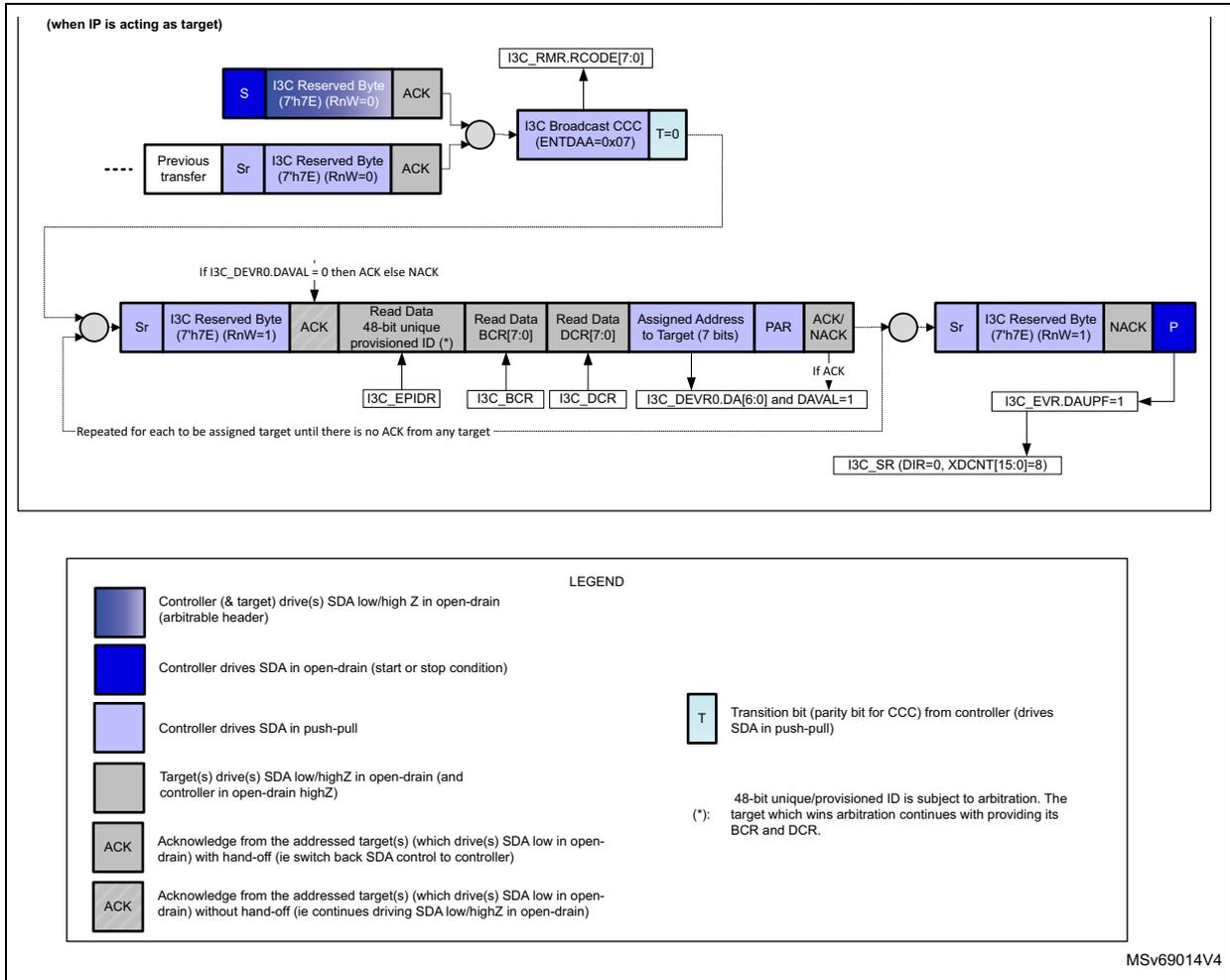

49.9.6 I3C broadcast ENTDAA CCC transfer, as target

Figure 667 illustrates I3C broadcast ENTDAA CCC, as communicated on the I3C bus, and as programmed when acting as target.

Figure 667. I3C broadcast ENTDAA CCC, as target

(when IP is acting as target)

The diagram illustrates the I3C broadcast ENTDAA CCC transfer sequence when the IP is acting as a target. The sequence starts with a previous transfer followed by a start condition (Sr) and an I3C Reserved Byte (7'h7E) with RnW=0, which is acknowledged (ACK). The controller then drives the I3C Broadcast CCC (ENTDAA=0x07) with a transition bit (T=0). This is followed by a read data sequence: Sr, I3C Reserved Byte (7'h7E) with RnW=1, ACK, Read Data 48-bit unique provisioned ID (*), Read Data BCR[7:0], Read Data DCR[7:0], Assigned Address to Target (7 bits), PAR, and ACK/NACK. The target responds with ACK if I3C_DEVR0.DAVAL = 0, otherwise NACK. The sequence repeats for each target until no ACK is received from any target. Upon receiving a NACK, the controller drives a stop condition (P). The target then sets I3C_EVR.DAUPF=1 and I3C_SR(DIR=0, XDCNT[15:0]=8). The I3C_RMR.RCODE[7:0] is also updated.

LEGEND

- Controller (& target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in open-drain (start or stop condition)

- Controller drives SDA in push-pull

- Target(s) drive(s) SDA low/highZ in open-drain (and controller in open-drain highZ)

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) with hand-off (ie switch back SDA control to controller)

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) without hand-off (ie continues driving SDA low/highZ in open-drain)

- T Transition bit (parity bit for CCC) from controller (drives SDA in push-pull)

- (*): 48-bit unique/provisioned ID is subject to arbitration. The target which wins arbitration continues with providing its BCR and DCR.

MSV69014V4

49.9.7 I3C broadcast DEFTGTS CCC transfer, as target

Figure 668 illustrates I3C broadcast DEFTGTS CCC, as communicated on the I3C bus, and as programmed when acting as target.

Figure 668. I3C broadcast DEFTGTS CCC, as target

![Timing diagram for I3C broadcast DEFTGTS CCC transfer. The diagram shows the sequence of events on the I3C bus between an Active Controller and multiple Target or Group units. The sequence starts with a Start (S) or Repeated Start (Sr), followed by the I3C Reserved Byte (7'h7E) (RnW=0), and an ACK. Then the I3C Broadcast CCC (DEFTGTS=0x08) is sent with a parity bit T=0, followed by Count[7:0] and a transition bit T. This is followed by a sequence for the Active Controller: {DynAddr[7:1], 1'b0}, T, DCR[7:0], T, BCR[7:0], T, and StaticAddr (7'h7E), T. Then for each Target or Group: {DynAddr[7:1], 1'b0}, T, DCR[7:0], T, BCR[7:0], T, {StaticAddr[7:1], 1'b0}, T. The sequence ends with a Repeated Start (Sr) or Stop (P). Register interactions like I3C_RMR.RCODE[7:0], I3C_RDR/RDWR, I3C_SR (DIR=0, XDCNT[15:0]=1+ 4x Count), and I3C_EVR.DEFF=1 are shown.](/RM0481-STM32H523-33-562-63-573/227c29905779ea7f9e244fd963a460c5_img.jpg)

DEFTGTS

(I3C broadcast CCC write)

(when IP is acting as target)

LEGEND

- Controller (& target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in open-drain

- Controller drives SDA in push-pull

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) with hand-off (ie switch back SDA control to controller)

- T Transition bit (parity bit for CCC) from controller (drives SDA in push-pull)

MSV69012V3

49.9.8 I3C broadcast DEFGRPA CCC transfer, as target

Figure 669 illustrates I3C broadcast DEFGRPA CCC, as communicated on the I3C bus, and as programmed when acting as target.

Figure 669. I3C broadcast DEFGRPA CCC, as target

![Timing diagram for I3C broadcast DEFGRPA CCC transfer. The diagram shows a sequence of messages on the I3C bus. It starts with a 'Previous transfer' followed by a 'Sr' (Start) and an 'I3C Reserved Byte (7'h7E) (RnW=0)' with an 'ACK'. The main part is the 'I3C Broadcast CCC (DEFGRPA=0x2B)' which includes fields for 'T=0', 'Group Addr. 1'b0', 'T', 'Group Descriptor', 'T', 'Count', 'T', 'Dyn Addr#1, 1'b0', 'T', 'DynAddr#n, 1'b0', 'T', and 'Sr or P'. Above the 'I3C Broadcast CCC' field is a register 'I3C_RMR.RCODE[7:0]'. Below the 'Group Descriptor' field is a register 'I3C_RDR/RDWR'. Below the 'DynAddr#n, 1'b0' field are registers 'I3C_SR (DIR=0,XDCNT[15:0])' and 'I3C_EVR.GRPF=1'. A legend at the bottom explains the SDA signal states: dark blue for open-drain (arbitrable header), medium blue for open-drain, light blue for push-pull, and grey for ACK from target(s).](/RM0481-STM32H523-33-562-63-573/c42119e25068c68e19d2746037c4b5e4_img.jpg)

DEFGRPA (I3C broadcast CCC write) (when IP is acting as target)

LEGEND

- Controller (& target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in open-drain

- Controller drives SDA in push-pull

- ACK Acknowledge from the addressed target(s) (which drive(s) SDA low in open-drain) with hand-off (ie switch back SDA control to controller)

- T Transition bit (parity bit for CCC) from controller (drives SDA in push-pull)

MSV69010V3

49.9.9 I3C direct GETSTATUS CCC response, as target

When the I3C acts as target, the hardware returns two data bytes on reception of GETSTATUS CCC, with format 1 (without defining byte or with defining byte TGTSTAT = 0x00), or format 2 (with defining byte PRECR = 0x91).

The returned 2-byte STATUS[15:0] with format 1 on the I3C bus is then as follows:

- • STATUS[15:14] = 00 (unused)

- • STATUS[13] = 1 if a missed start was detected since the former GETSTATUS CCC, else 0

- • STATUS[12] = 1 if an overrun/underrun error was detected since the former GETSTATUS CCC, else 0

- • STATUS[11] = 1 if an SCL stable for more than 125 µs was detected during an SDR read since the former GETSTATUS CCC, else 0

- • STATUS[10:8] = 000 to 110: encoded value x = 0 to 6, corresponding to a target error TEx if a protocol error was detected since the former GETSTATUS CCC (if STATUS[5] = 1), else 000

- • STATUS[7:6] = 00 (ready to prepare for hand-off procedure)

- • STATUS[5] = 1 if a protocol error was detected since the former GETSTATUS CCC, else 0

- • STATUS[4] = 0 (reserved)

- • STATUS[3:1] = 000 (unused)

- • STATUS[0] = 1 if there is a pending interrupt (if an IBI is configured in the I3C_CR register, and IBIEN = 1 and DAVAL = 1 in the I3C_DEVR0 register, and the IBI is not yet acknowledged by the controller neither disabled via DISEC), else 0

The returned 2-byte STATUS[15:0] with format 2 on the I3C bus is then as follows:

- • STATUS[15:8] = 0000 0000 (unused)

- • STATUS[7:2] = 000000 (unused)

- • STATUS[1] = 1 if a received DEFTGTS or a received DEFGRPA CCC is still under software processing, and the related event is not yet cleared by software (DEFF = 1 or GRPF = 1 in the I3C_EVR register); the controller must wait before issuing a GETACCR CCC (else it is not acknowledged)

- • STATUS[0] = 1 if a DEFTGTS or DEFGRPA CCC may have been missed. This bit is asserted if a missed start is detected (WKPF = 1 in the I3C_EVR register), de-asserted if DEFF = 1 or GRPF = 1 in the I3C_EVR register.

Completion of a GETSTATUS CCC of format 1 is reported by STAF = 1 in the I3C_EVR register, and the corresponding interrupt if enabled (if STAIE = 1 in the I3C_IER register).

Completion of a GETSTATUS CCC of format 2 is reported by GETF = 1 in the I3C_EVR register, and the corresponding interrupt if enabled (if GETIE = 1 in the I3C_IER register).

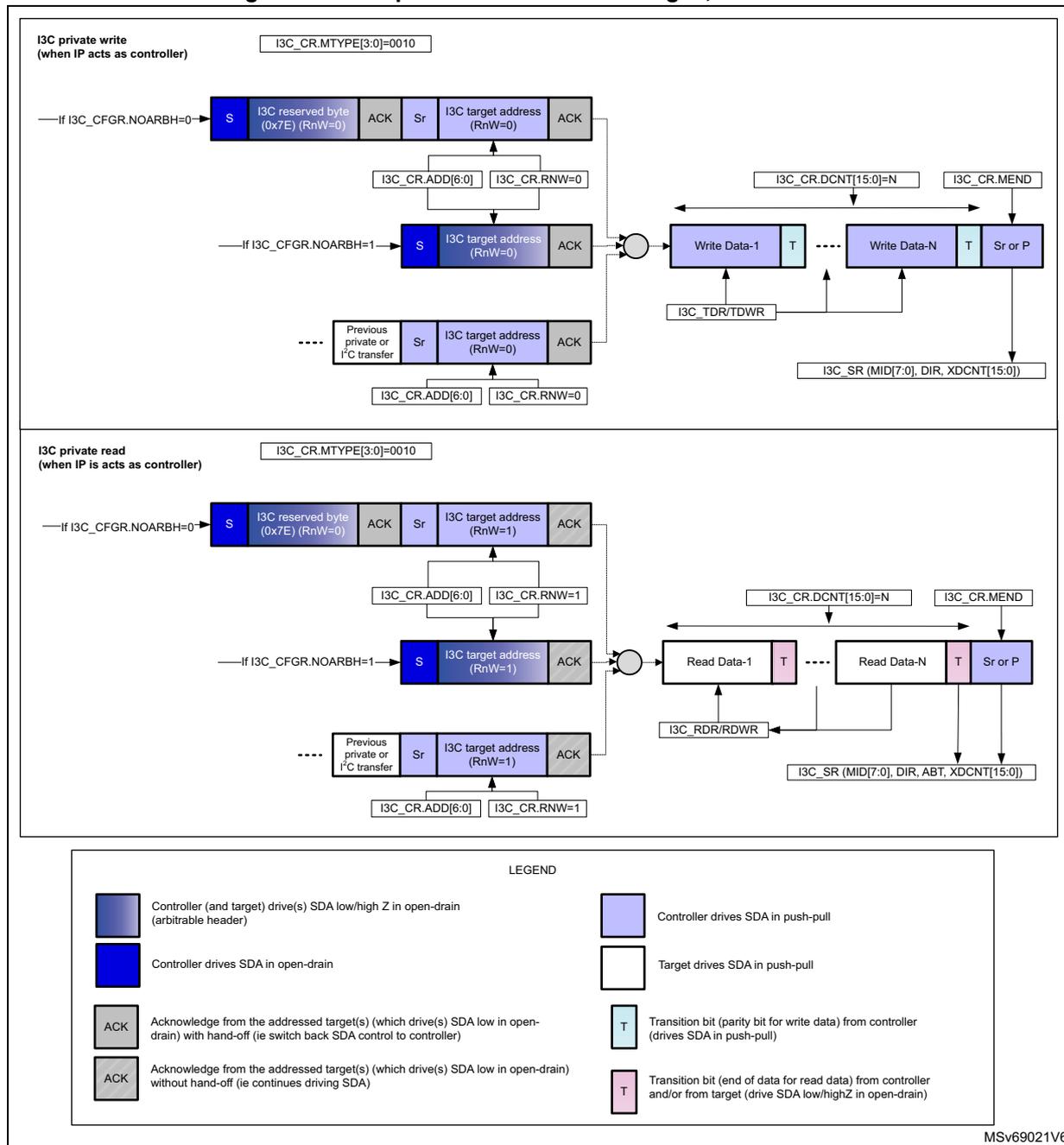

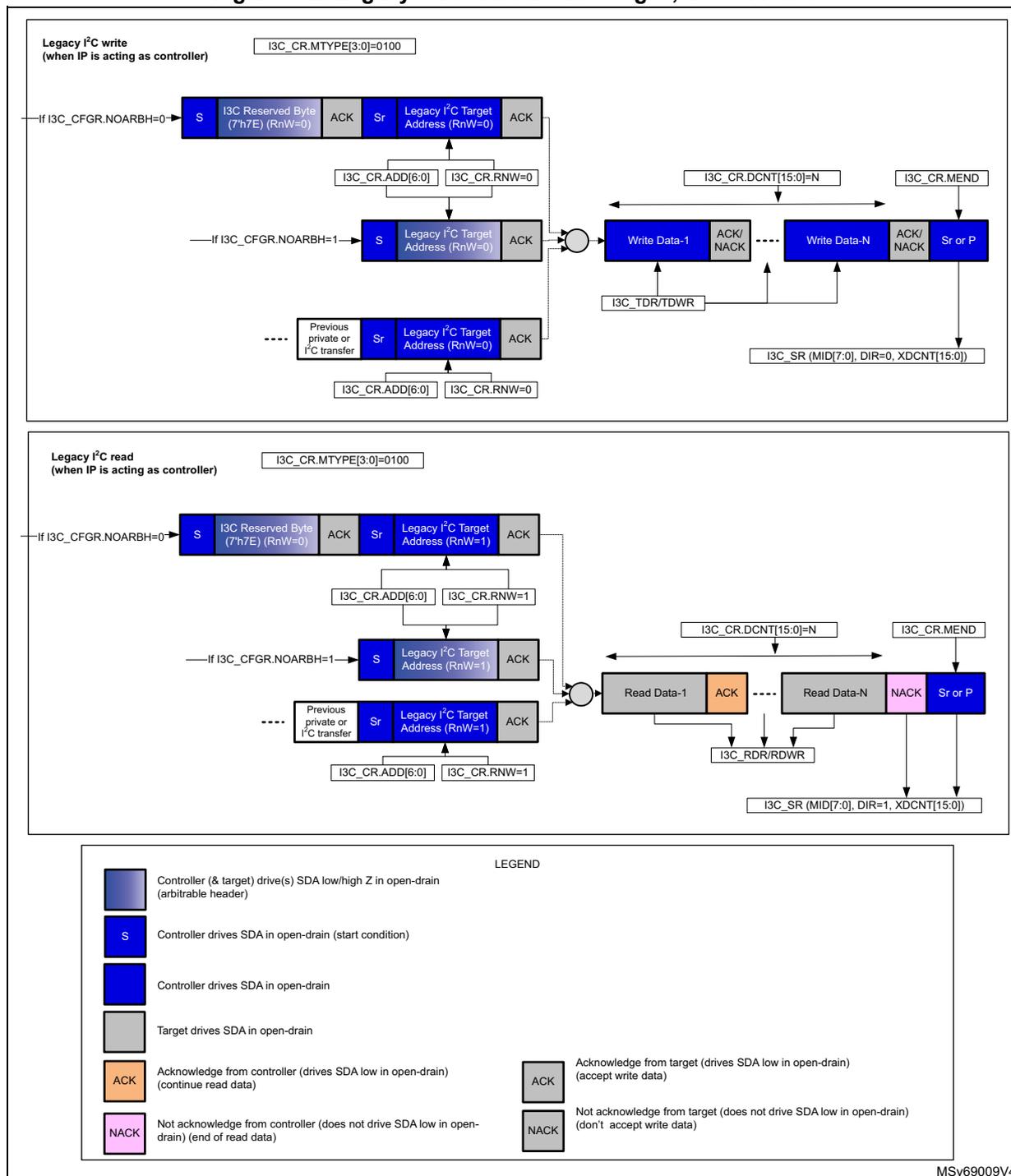

49.9.10 I3C private read/write transfer, as controller

Figure 670 illustrates private read/write transfer, as communicated on the I3C bus, and as programmed when acting as controller.

Figure 670. I3C private read/write messages, as controller

I3C private write (when IP acts as controller)

Condition:

I3C_CR_MTYPE[3:0]=0010

Sequence 1 (if

I3C_CFGR.NOARBH=0

): S (Controller drives SDA in open-drain) → I3C reserved byte (0x7E) (RnW=0) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) with hand-off → Sr (Controller drives SDA in open-drain) → I3C target address (RnW=0) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off.

Sequence 2 (if

I3C_CFGR.NOARBH=1

): S (Controller drives SDA in open-drain) → I3C target address (RnW=0) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off.

Previous private or I2C transfer: Sr (Controller drives SDA in open-drain) → I3C target address (RnW=0) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off.

Data transfer: Write Data-1 (T) → ... → Write Data-N (T) → Sr or P. Control signals:

I3C_CR_DCNT[15:0]=N

,

I3C_CR_MEND

,

I3C_TDR/TDWR

,

I3C_SR (MID[7:0], DIR, XDCNT[15:0])

.

I3C private read (when IP acts as controller)

Condition:

I3C_CR_MTYPE[3:0]=0010

Sequence 1 (if

I3C_CFGR.NOARBH=0

): S (Controller drives SDA in open-drain) → I3C reserved byte (0x7E) (RnW=0) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) with hand-off → Sr (Controller drives SDA in open-drain) → I3C target address (RnW=1) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off.

Sequence 2 (if

I3C_CFGR.NOARBH=1

): S (Controller drives SDA in open-drain) → I3C target address (RnW=1) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off.

Previous private or I2C transfer: Sr (Controller drives SDA in open-drain) → I3C target address (RnW=1) (Controller drives SDA in open-drain) → ACK (Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off.

Data transfer: Read Data-1 (T) → ... → Read Data-N (T) → Sr or P. Control signals:

I3C_CR_DCNT[15:0]=N

,

I3C_CR_MEND

,

I3C_RDR/RDWR

,

I3C_SR (MID[7:0], DIR, ABT, XDCNT[15:0])

.

LEGEND

- Controller (and target) drive(s) SDA low/high Z in open-drain (arbitrable header)

- Controller drives SDA in open-drain

- Controller drives SDA in push-pull

- Target drives SDA in push-pull

- ACK: Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) with hand-off (ie switch back SDA control to controller)

- ACK: Acknowledge from the addressed target(s) which drive(s) SDA low in open-drain) without hand-off (ie continues driving SDA)

- T: Transition bit (parity bit for write data) from controller (drives SDA in push-pull)

- T: Transition bit (end of data for read data) from controller and/or from target (drive SDA low/highZ in open-drain)

MSv69021V6

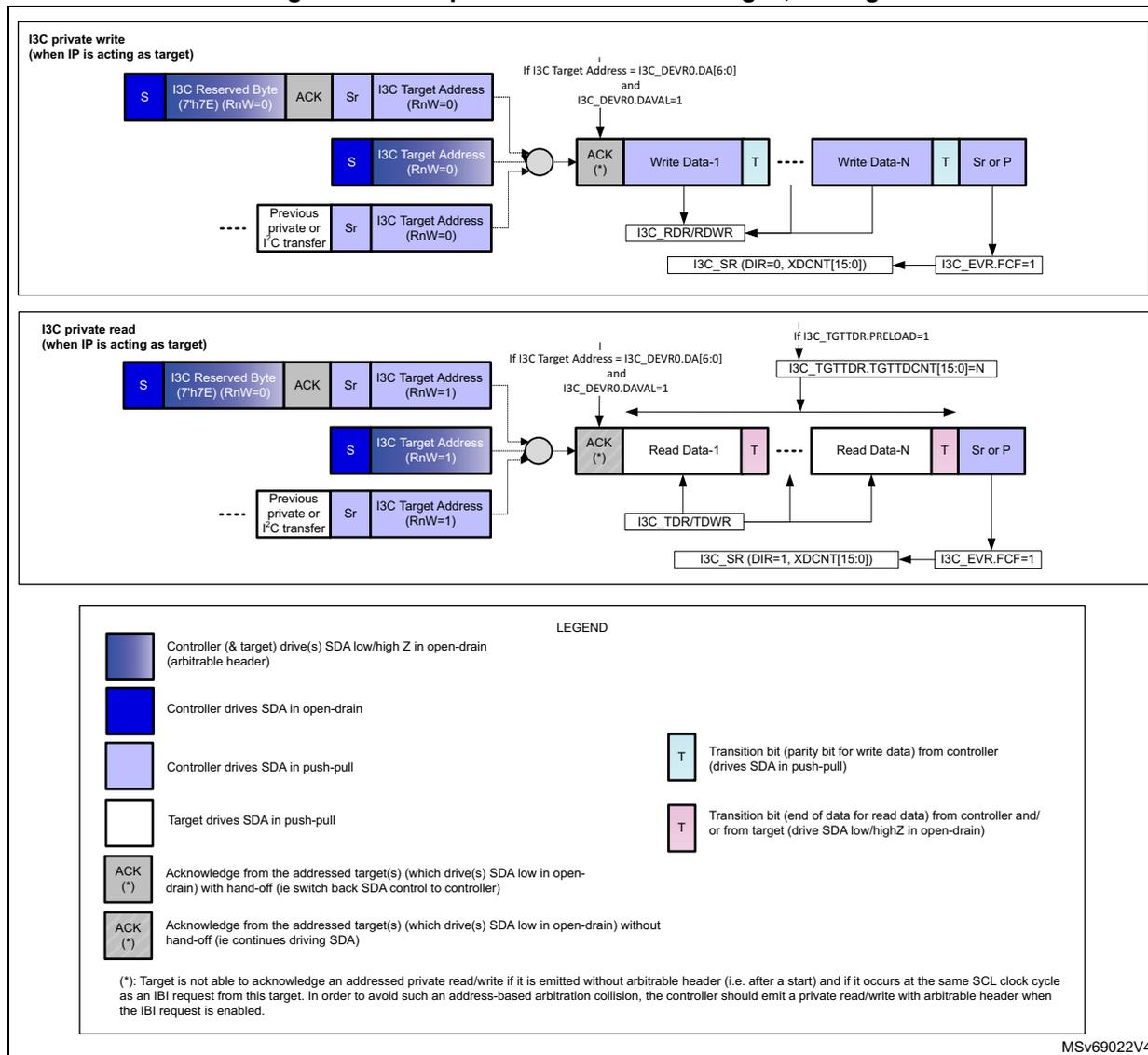

49.9.11 I3C private read/write transfer, as target

Figure 671 illustrates I3C private read/write transfer, as communicated on the I3C bus, and as programmed when acting as target.

Figure 671. I3C private read/write messages, as target

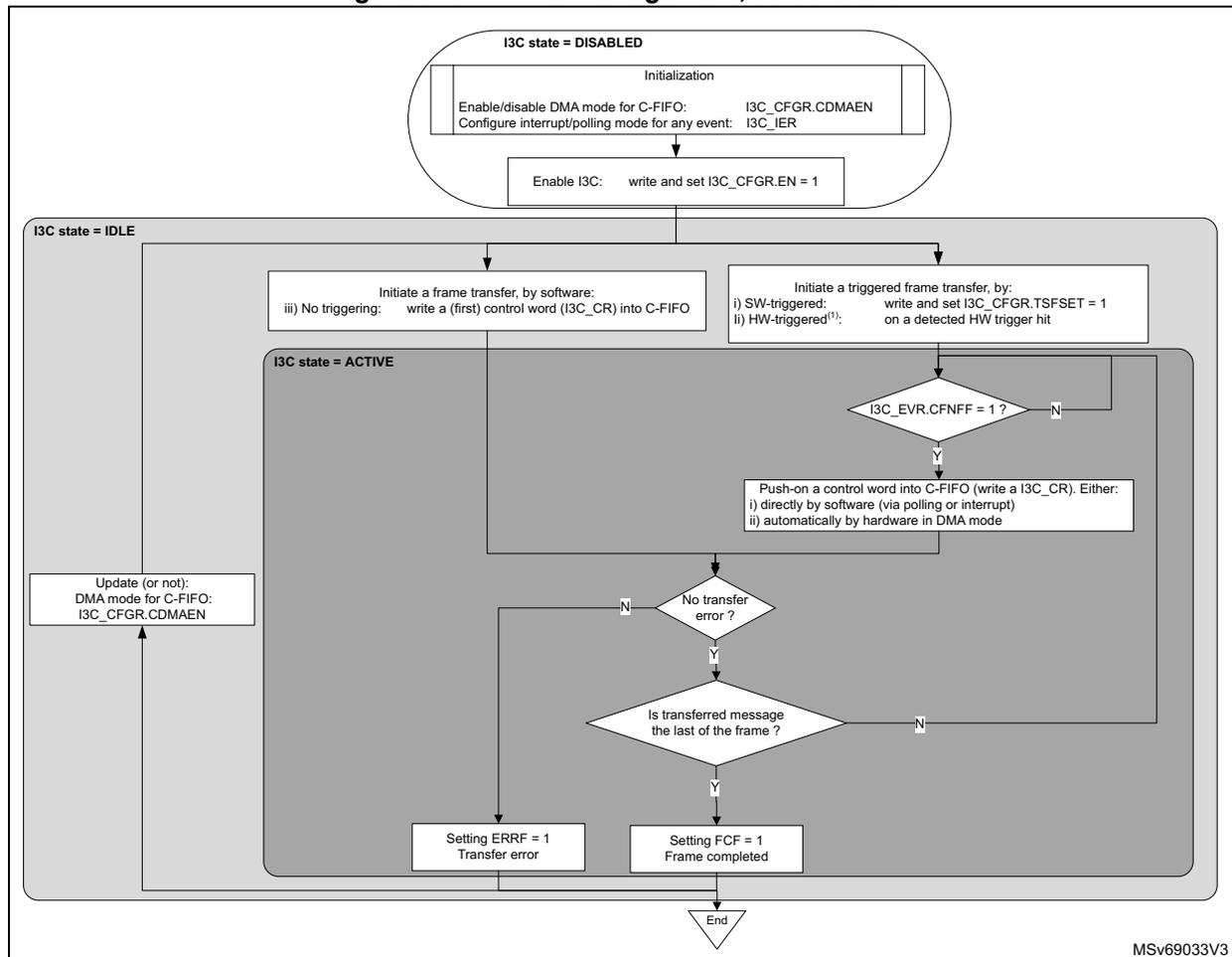

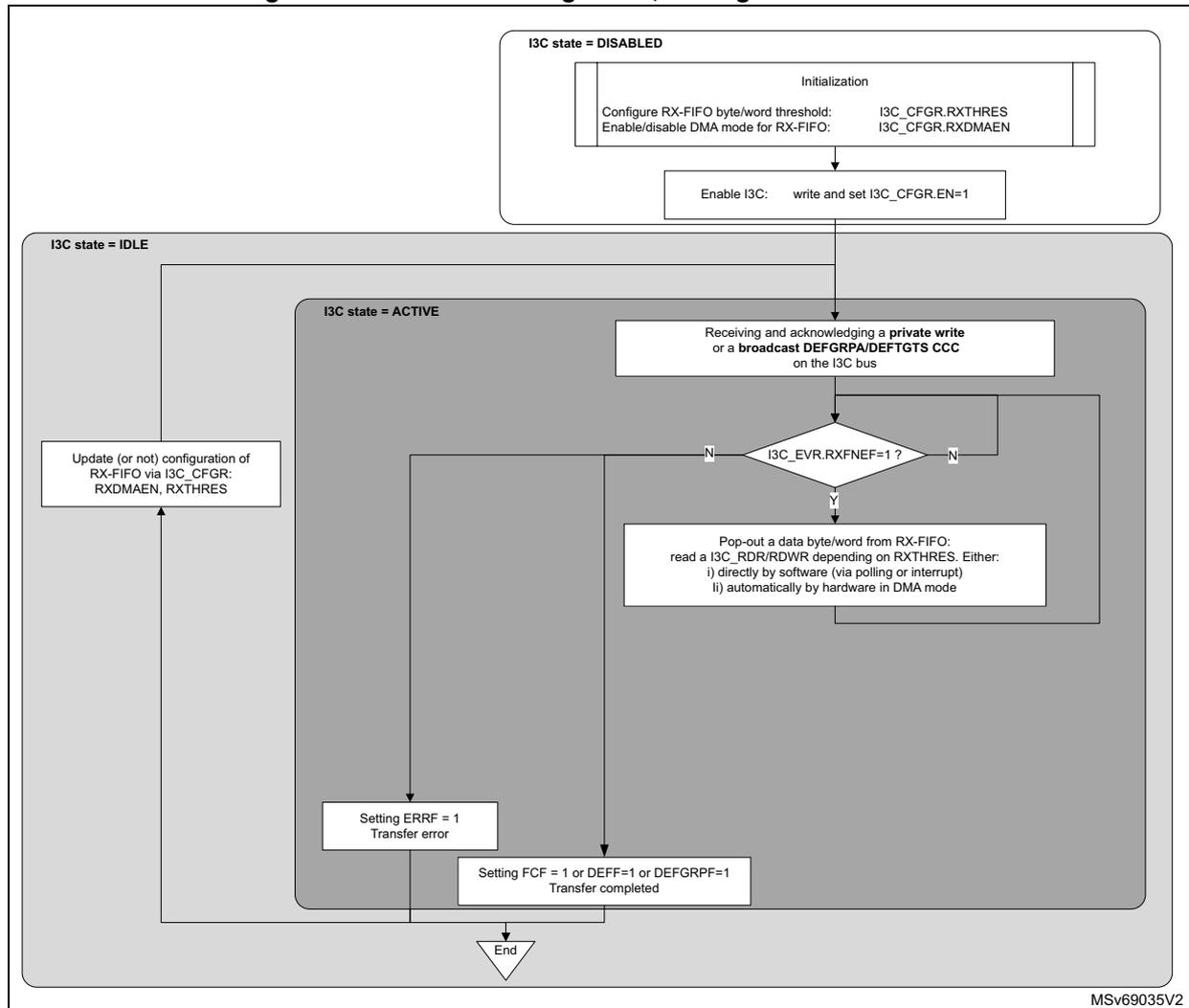

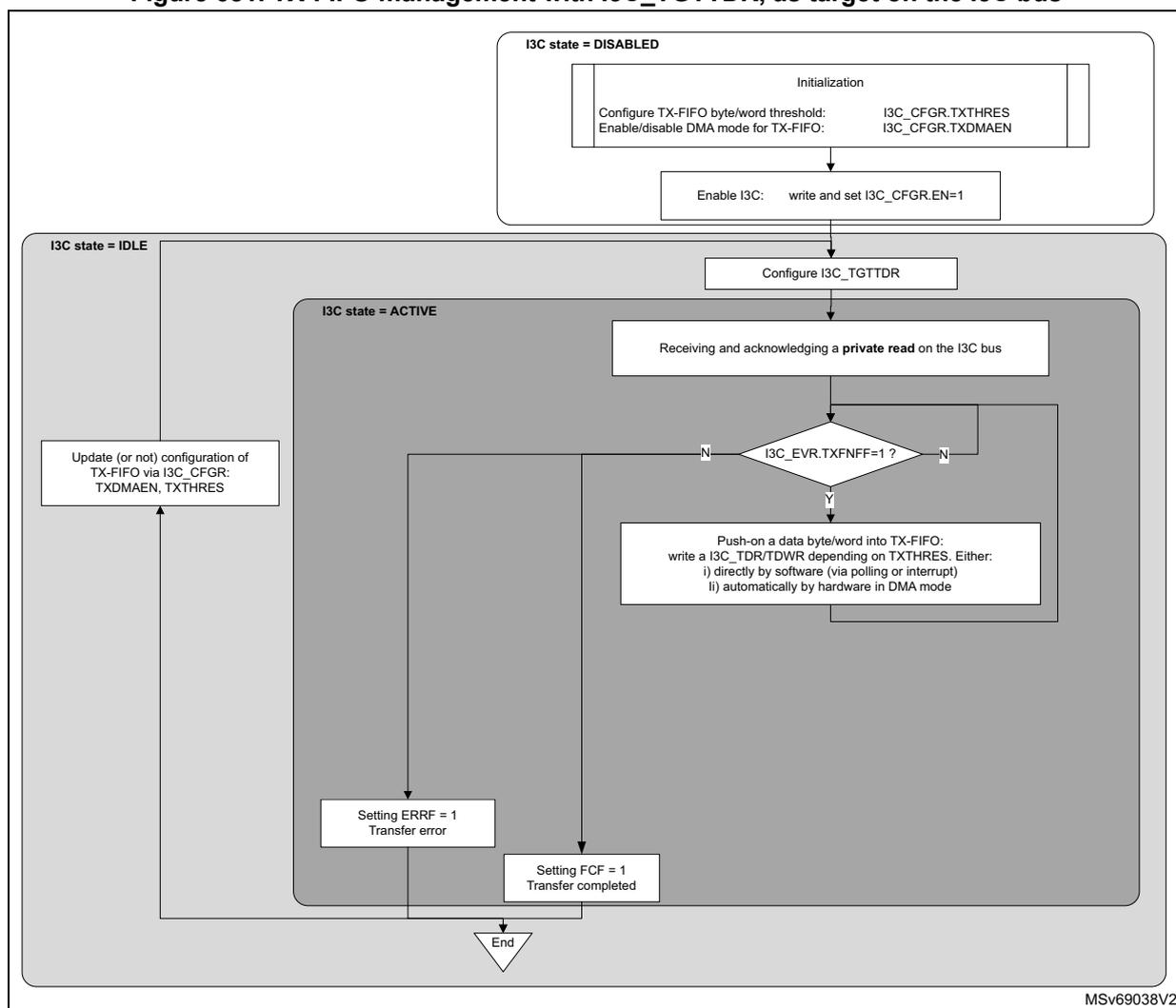

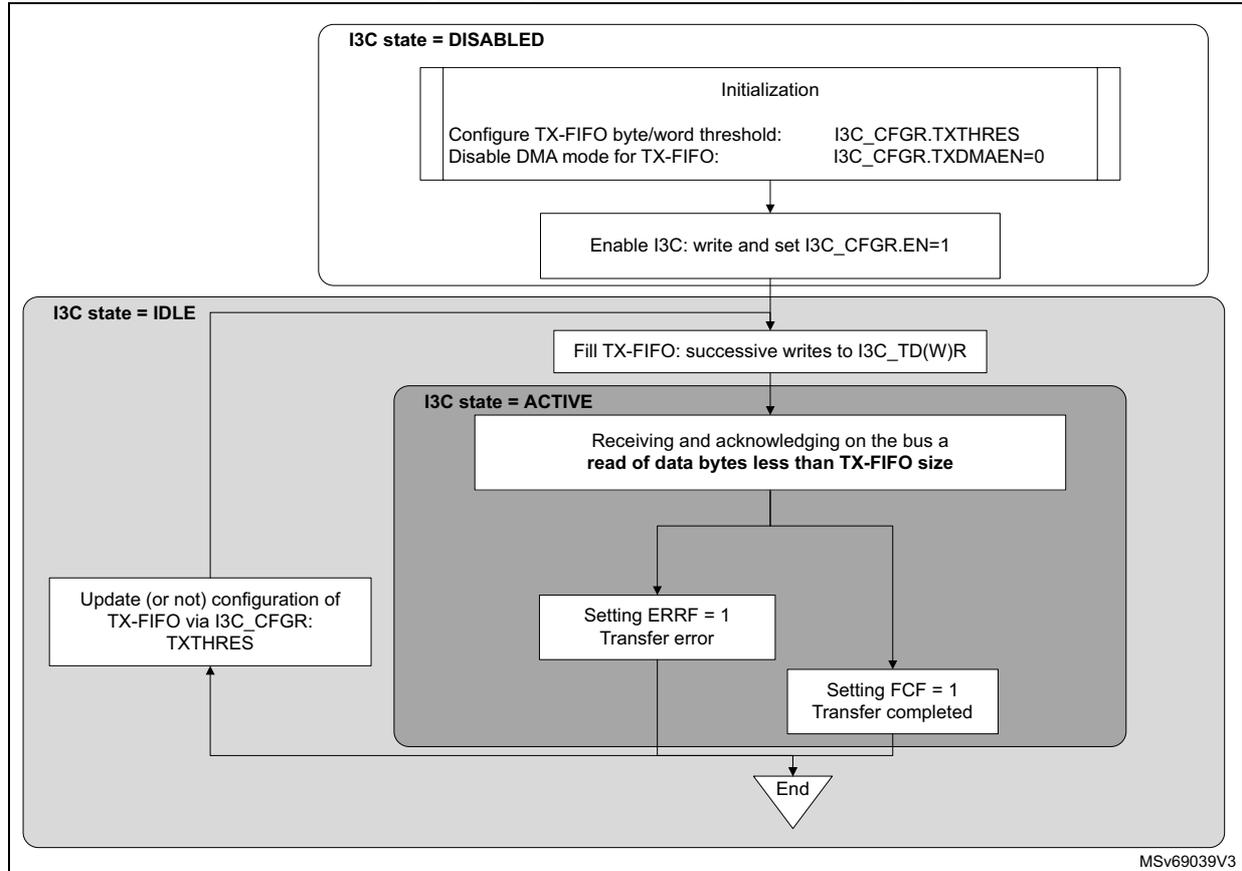

I3C private write (when IP is acting as target)