11. Reset and clock control (RCC)

11.1 Introduction

The reset and clock control (RCC) manages the different resets, and generates the clocks for the bus and peripherals.

11.2 RCC pins and internal signals

Table 111 lists the RCC inputs and output signals connected to package pins or balls.

Table 111. RCC input/output signals connected to package pins or balls

| Signal name | Signal type | Description |

|---|---|---|

| NRST | I/O | System reset, can be used to provide reset to external devices |

| OSC32_IN | I | 32 kHz oscillator input |

| OSC32_OUT | O | 32 kHz oscillator output |

| OSC_IN | I | System oscillator input |

| OSC_OUT | O | System oscillator output |

| MCO | O | Output clock for external devices |

| LSCO | O | Low-speed output clock for external devices |

| AUDIOCLK | I | External kernel clock input for SAI1, SAI2, I2S1, I2S2, and I2S3 |

11.3 RCC reset functional description

There are three types of reset:

- • a system reset

- • a power reset

- • a Backup domain reset

11.3.1 Power reset

A power reset is generated when one of the following events occurs:

- • a brownout reset (BOR)

- • when exiting Standby mode

A brownout reset, including power-on or power-down reset (POR/PDR), sets all registers to their reset values except the ones in the Backup domain.

When exiting Standby mode, all registers in the core domain are set to their reset value. Registers outside the core domain (RTC, WKUP, IWDG, and GPIO pullup/pulldown configuration during Standby and Standby mode exit) are not impacted.

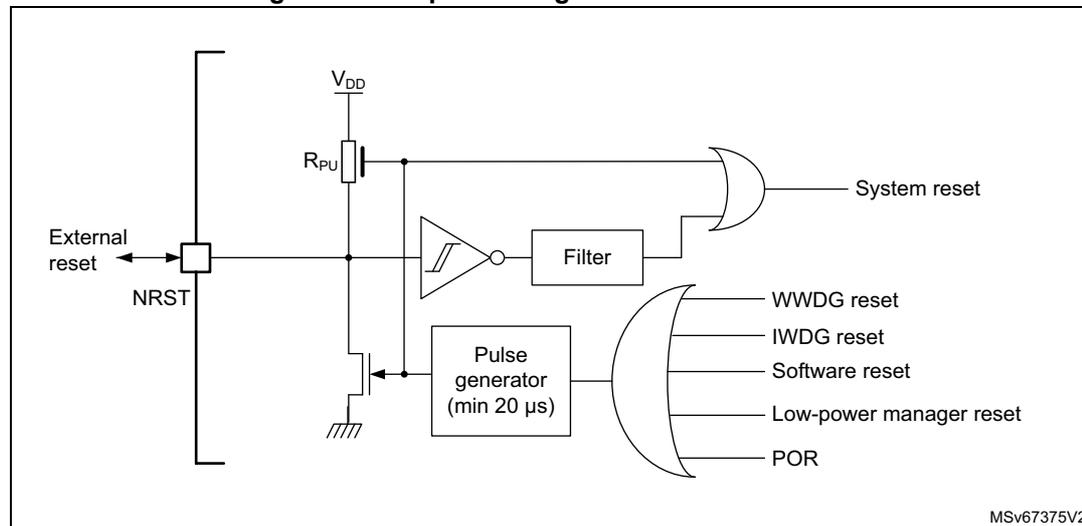

11.3.2 System reset

A system reset sets all registers to their reset values except the reset flags in RCC reset status register (RCC_RSR) and the registers in the Backup domain.

A system reset is generated when one of the following events occurs:

- • a low level on the NRST pin (external reset)

- • a window watchdog event (WWDG reset)

- • an independent watchdog event (IWDG reset)

- • a software reset (SW reset) (see Software reset )

- • a low-power mode security reset (see Low-power mode security reset )

- • a brownout reset

The reset source can be identified by checking the reset flags in RCC reset status register (RCC_RSR) .

These sources act on the NRST pin and this pin is always kept low during the delay phase. The reset service routine vector is selected depending on product state, on Boot option bytes or on both.

The system reset signal provided to the device is output on the NRST pin. The pulse generator guarantees a minimum reset pulse duration of 20 µs for each internal reset source. In case of an external reset, the reset pulse is generated while the NRST pin is asserted low.

In case of an internal reset, the internal pull-up \( R_{PU} \) is deactivated to save the power consumption through the pull-up resistor.

Figure 51. Simplified diagram of the reset circuit

Software reset

The SYSRESETREQ bit in Cortex-M33 application interrupt and reset control register must be set to force a software reset on the device.

Low-power mode security reset

To avoid that critical applications mistakenly enter a low-power mode, the following low-power mode security resets are available. If enabled in option bytes, the resets are generated in any of the following conditions:

- • Entering Standby mode: this type of reset is enabled by resetting nRST_STDBY bit in user option bytes. In this case, whenever a Standby mode entry sequence is successfully executed, the device is reset instead of entering Standby mode.

- • Entering Stop mode: this type of reset is enabled by resetting nRST_STOP bit in user option bytes. In this case, whenever a Stop mode entry sequence is successfully executed, the device is reset instead of entering Stop mode.

For further information on the user option bytes, refer to Section 7.4.1: Option bytes description .

11.3.3 Backup domain reset

The Backup domain has two specific resets, generated after one of the following events:

- • a software reset, triggered by setting the VSWRST bit in the RCC Backup domain control register (RCC_BDCR) . Write access to this domain must be enabled before setting VSWRST bit to perform the reset.

- • a V DD or V BAT power on, if both supplies have previously been powered off

A Backup domain reset affects the LSE oscillator, the RTC, the backup registers, the backup SRAM, and the RCC_BDCR register.

11.3.4 Reset source identification

The application can identify the reset source by checking the reset flags in the RCC_RSR register. The software can reset the flags by setting the RMVF bit.

Table 112 shows how the status bits of the RCC_RSR register behave according to the situation that generated the reset. For example, when an IWDG timeout occurs, if the CPU is reading the RCC_RSR register during the boot phase, both PINRSTF and IWDGRSTF bits are set, indicating that the IWDG also generated a pin reset.

Table 112. Reset source identification (RCC_RSR) (1)

| Reset | LPWRRSTF | WWDGRSTF | IWDGRSTF | SFTRSTF | BORRSTF | PINRSTF | |

|---|---|---|---|---|---|---|---|

| 1 | Power-on reset | 0 | 0 | 0 | 0 | 1 | 1 |

| 2 | Pin/pad reset | 0 | 0 | 0 | 0 | 0 | 1 |

| 3 | Brownout (low or high) reset | 0 | 0 | 0 | 0 | 1 | 1 |

| 4 | System reset generated by CPU | 0 | 0 | 0 | 1 | 0 | 1 |

| 5 | WWDG reset | 0 | 1 | 0 | 0 | 0 | 1 |

| 6 | IWDG reset | 0 | 0 | 1 | 0 | 0 | 1 |

| 7 | Illegal stop entry reset | 1 | 0 | 0 | 0 | 0 | 1 |

1. Gray cells highlight the register bits that are set.

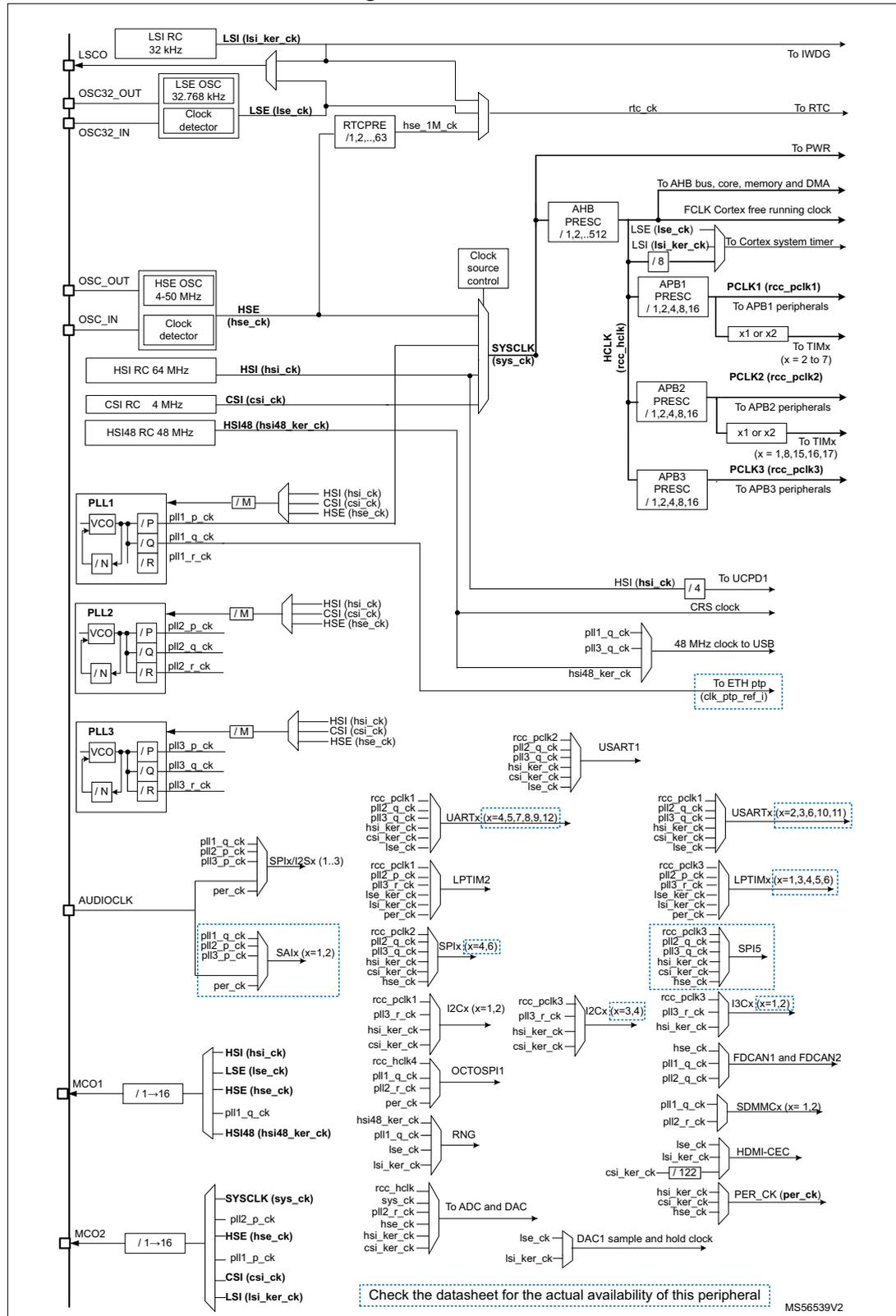

11.4 RCC clocks functional description

Four different clock sources can be used to drive the system clock (SYSCLK):

- • HSI: high-speed internal up to 64 MHz RC oscillator clock

- • CSI: low power internal RC oscillator clock

- • HSE: high-speed external crystal or clock, from 4 to 50 MHz

- • PLL1 clock

The HSI is used as system clock source after startup from reset, configured at 32 MHz.

The device has the following additional clock sources:

- • LSI: 32 kHz low-speed internal RC that drives the independent watchdog and optionally the RTC used for auto-wakeup from Stop and Standby modes

- • LSE: 32.768 kHz low-speed external crystal or clock that optionally drives the real-time clock (rtc_ck)

- • HSI48: internal 48 MHz RC that potentially drives the USB FS and the RNG

- • PLL2 and PLL3 clocks

Each clock source can be switched on or off independently when it is not used, to optimize power consumption.

Several prescalers can be used to configure the AHB frequency, the APB1 and APB2 domains. The maximum frequency of the AHB and APB domains is 250 MHz.

The peripheral clocks are derived from their bus clock (HCLK, PCLK1, PCLK2 or PCLK3), except those that receive an independent kernel clock. This kernel clock can be selected by software between several sources thanks to RCC_CCIPRx registers (x = 1,2,3,4,5).

In addition, the RTC kernel clock is selected by software in RCC_BDCR. The IWDG clock is always the LSI 32 kHz clock.

The RCC feeds the Cortex system timer (SysTick) external clock with the AHB clock (HCLK) divided by eight, or LSE or LSI. The SysTick can work either with this clock or directly with the Cortex clock (HCLK), configurable in the SysTick control and status register.

FCLK acts as Cortex-M33 free-running clock.

Figure 52. Clock tree

The diagram illustrates the internal clock architecture of an STM32 microcontroller. It shows the following components and paths:

- External Oscillators:

- LSI RC 32 kHz: Connected to LSI (lsi_ker_ck), which feeds into the IWDG and RTC.

- LSE OSC 32.768 kHz: Connected via OSC32_IN and OSC32_OUT pins. It feeds into the RTC (via RTCPRE) and the Clock detector.

- HSE OSC 4-50 MHz: Connected via OSC_IN and OSC_OUT pins. It feeds into the HSE (hse_ck) input of the Clock source control.

- Internal Oscillators:

- HSI RC 64 MHz: Feeds into HSI (hsi_ck).

- CSI RC 4 MHz: Feeds into CSI (csi_ck).

- HSI48 RC 48 MHz: Feeds into HSI48 (hsi48_ker_ck).

- PLLs (Phase-Locked Loops):

- PLL1: Input can be HSI (hsi_ck) or HSE (hse_ck). It has VCO, /P, /Q, and /R dividers, producing pll1_p_ck, pll1_q_ck, and pll1_r_ck outputs.

- PLL2: Input can be HSI (hsi_ck), CSI (csi_ck), or HSE (hse_ck). It has VCO, /P, /Q, and /R dividers, producing pll2_p_ck, pll2_q_ck, and pll2_r_ck outputs.

- PLL3: Input can be HSI (hsi_ck), CSI (csi_ck), or HSE (hse_ck). It has VCO, /P, /Q, and /R dividers, producing pll3_p_ck, pll3_q_ck, and pll3_r_ck outputs.

- Clock Source Control: A central block that selects the system clock (SYSCLK) from HSE, HSI, LSI, or PLL1_r_ck. It also controls the AHB prescaler (1, 2, ..., 512).

- System Clock (SYSCLK):

The main clock for the CPU and AHB bus. It is distributed to:

- AHB bus, core, memory and DMA.

- FCLK Cortex free running clock.

- APB1, APB2, and APB3 prescalers.

- USB 48 MHz clock (derived from PLL1_q_ck or PLL3_q_ck).

- UCPD1 (derived from HSI via /4).

- CRS clock.

- APB Prescalers:

- APB1: Prescaler (1, 2, 4, 8, 16) produces PCLK1 (rcc_pclk1) for APB1 peripherals and TIMx (x = 2 to 7).

- APB2: Prescaler (1, 2, 4, 8, 16) produces PCLK2 (rcc_pclk2) for APB2 peripherals and TIMx (x = 1, 8, 15, 16, 17).

- APB3: Prescaler (1, 2, 4, 8, 16) produces PCLK3 (rcc_pclk3) for APB3 peripherals.

- Peripherals:

Various peripherals are connected to specific clock lines:

- USART1: Connected to rcc_pclk2, pll2_q_ck, pll3_q_ck, hsi_ker_ck, csi_ker_ck, and lse_ck.

- UARTx (x=4,5,7,8,9,12): Connected to rcc_pclk1, pll2_q_ck, hsi_ker_ck, csi_ker_ck, and lse_ck.

- UARTx (x=2,3,6,10,11): Connected to rcc_pclk1, pll2_q_ck, hsi_ker_ck, csi_ker_ck, and lse_ck.

- LPTIM2: Connected to rcc_pclk1, lse_ck, and per_ck.

- LPTIMx (x=1,3,4,5,6): Connected to rcc_pclk3, lse_ck, and per_ck.

- SPIx (x=4,6): Connected to rcc_pclk2, hsi_ker_ck, csi_ker_ck, and hse_ck.

- SPI5: Connected to rcc_pclk3, hsi_ker_ck, csi_ker_ck, and hse_ck.

- I2Cx (x=1,2): Connected to rcc_pclk1, hsi_ker_ck, csi_ker_ck, and lse_ck.

- I2Cx (x=3,4): Connected to rcc_pclk3, hsi_ker_ck, csi_ker_ck, and lse_ck.

- I3Cx (x=1,2): Connected to rcc_pclk3, hsi_ker_ck, csi_ker_ck, and lse_ck.

- OCTOSPI1: Connected to rcc_hclk4, hse_ck, csi_ker_ck, and per_ck.

- FDCAN1 and FDCAN2: Connected to hse_ck, pll1_q_ck, and pll2_q_ck.

- SDMMCx (x=1,2): Connected to pll1_q_ck and pll2_r_ck.

- RNG: Connected to hsi48_ker_ck, pll1_q_ck, lse_ck, and lsi_ker_ck.

- HDMI-CEC: Connected to lse_ck, lsi_ker_ck, and csi_ker_ck (via /7/122).

- PER_CK (per_ck): Derived from hsi_ker_ck, csi_ker_ck, and hse_ck.

- ADC and DAC: Connected to rcc_hclk, sys_ck, pll2_p_ck, hse_ck, hsi_ker_ck, and csi_ker_ck.

- DAC1 sample and hold clock: Derived from lse_ck and lsi_ker_ck.

- Other Connections:

- AUDIOCLK: Derived from HSI (hsi_ck), LSE (lse_ck), HSE (hse_ck), pll1_q_ck, and HSI48 (hsi48_ker_ck). It feeds into SPIx/I2Sx (1..3) and SAIx (x=1,2).

- MCO1: Output clock derived from HSI, LSE, HSE, pll1_q_ck, or HSI48 via a /1 to /16 divider.

- MCO2: Output clock derived from SYSCLK, pll2_p_ck, HSE, pll1_p_ck, CSI, or LSI via a /1 to /16 divider.

Check the datasheet for the actual availability of this peripheral!

MS56539V2

1. For details on the internal/external clock source, refer to the Electrical characteristics in the datasheet.

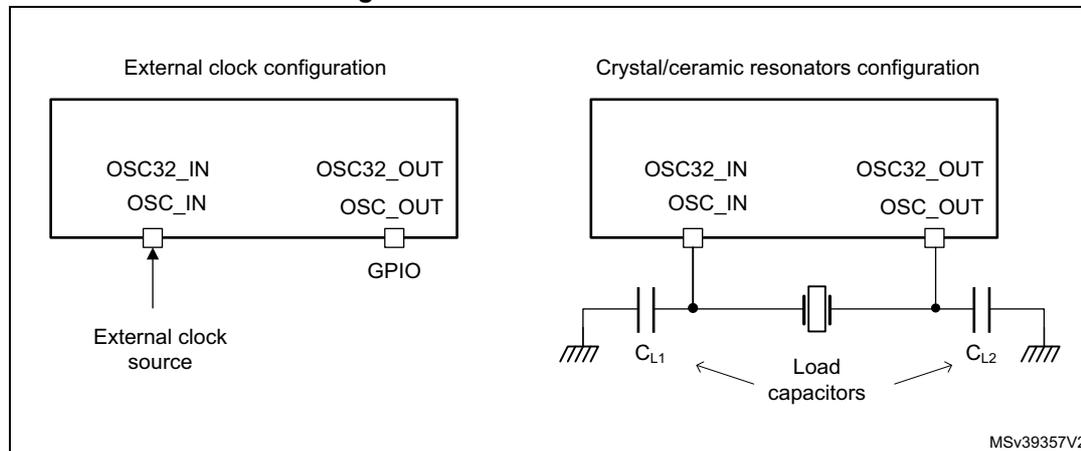

11.4.1 HSE clock

The HSE block can generate a clock from an external crystal/ceramic resonator, or from an external clock source.

Figure 53. HSE/LSE clock sources

External clock source (HSE bypass)

In this mode, an external clock source must be provided to OSC_IN pin. The external clock can be low swing (analog) or digital. If this clock is directly used by a peripheral, the duty cycle requirement is defined by the peripheral and the application (refer to datasheet for more details).

In case of an analog clock (low swing) the HSEBYP and HSEON bits must be set to 1 in the RCC clock control register (RCC_CR) .

In case of a digital clock, the HSEBYP and the HSEEXT bits must be set to 1 followed by setting the HSEON bit to 1 in the RCC clock control register (RCC_CR) .

External crystal/ceramic resonator

The oscillator is enabled by setting the HSEBYP bit to 0 and HSEON bit to 1.

The HSE can be used when the product requires a very accurate high-speed clock.

The associated hardware configuration is shown in Figure 53 : the resonator and the load capacitors must be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected crystal or ceramic resonator. Refer to the electrical characteristics section of the datasheet for more details.

The HSERDY flag of the RCC clock control register (RCC_CR) indicates whether the HSE oscillator is stable or not. At startup, the hse_ck clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in the RCC clock source interrupt enable register (RCC_CIER) .

The HSE can be switched ON and OFF through the HSEON bit. Note that the HSE cannot be switched OFF if one of the following two conditions is met:

- • the HSE is used directly (via software mux) as system clock

- • the HSE is selected as reference clock for PLL1, with PLL1 enabled and selected to provide the system clock (via software mux).

In that case the hardware does not allow programming the HSEON bit to 0.

The HSE is automatically disabled by hardware, when the system enters Stop or Standby mode.

In addition, the HSE clock can be driven to the MCO1 and MCO2 outputs and used as clock source for other application components.

11.4.2 HSI clock

The HSI block provides the default clock to the product.

The HSI is a high-speed internal RC oscillator that can be used directly as system clock, peripheral clock, or as PLL input. A predivider allows the application to select an HSI output frequency of 8, 16, 32 or 64 MHz. This predivider is controlled by the HSIDIV.

The HSI advantages are the following:

- • low-cost clock source, as no external crystal is required

- • faster startup time than HSE (a few microseconds)

The HSI frequency, even with frequency calibration, is less accurate than an external crystal oscillator or ceramic resonator.

The HSI can be switched ON and OFF using the HSION bit. Note that the HSI cannot be switched OFF if one of the two conditions is met:

- • the HSI is used directly (via software mux) as system clock

- • the HSI is selected as reference clock for PLL1, with PLL1 enabled and selected to provide the system clock (via software mux).

In that case the hardware does not allow programming the HSION bit to 0. Note that the HSIDIV cannot be changed if the HSI is selected as reference clock for at least one enabled PLL (PLLxON bit set to 1). In that case the hardware does not update the HSIDIV with the new value. However it is possible to change the HSIDIV if the HSI is used directly as system clock.

The HSIRDY flag indicates if the HSI is stable or not. At startup, the HSI output clock is not released until this bit is set by hardware.

The HSI clock can also be used as a backup source (auxiliary clock) if the HSE fails (refer to Section 11.4.10: Clock security system (CSS) ). The HSI can be disabled or not when the system enters Stop mode.

In addition, the HSI clock can be driven to the MCO1 output and used as clock source for other application components.

Care must be taken when the HSI is used as kernel clock for communication peripherals, the application must take into account the following parameters:

- • the time interval between the moment where the peripheral generates a kernel clock request and the moment where the clock is really available

- • the frequency accuracy.

Note: The HSI can remain enabled when the system is in Stop mode.

HSI calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations. That is why each device is factory calibrated by STMicroelectronics to achieve an accuracy of ACCHSI (refer to the product datasheet for more information).

After a power-on reset, the factory calibration value is loaded in the HSICAL[11:0] bits. If the application is subject to voltage or temperature variations, this may affect the RC oscillator frequency. The user application can trim the HSI frequency using the HSITRIM[6:0] bits.

Note: HSICAL[11:0] and HSITRIM[6:0] are located in the RCC CSI calibration register (RCC_CSI/CFGR) .

11.4.3 CSI oscillator

The CSI is a low-power RC oscillator that can be used directly as system clock, peripheral clock, or PLL input.

The CSI advantages are the following:

- • low-cost clock source since no external crystal is required

- • faster startup time than HSE (a few microseconds)

- • very low-power consumption,

The CSI provides a clock frequency of about 4 MHz, while the HSI is able to provide a clock up to 64 MHz.

CSI frequency, even with frequency calibration, is less accurate than an external crystal oscillator or ceramic resonator.

The CSI can be switched ON and OFF through the CSION bit. The CSIRDY flag indicates whether the CSI is stable or not. At startup, the CSI output clock is not released until this bit is set by hardware.

The CSI cannot be switched OFF if one of the two conditions is met:

- • The CSI is used directly (via software mux) as system clock.

- • The CSI is selected as reference clock for PLL1, with PLL1 enabled and selected to provide the system clock (via software mux).

In that case the hardware does not allow programming the CSION bit to 0.

The CSI can be disabled or not when the system enters Stop mode.

In addition, the CSI clock can be driven to the MCO2 output and used as clock source for other application components.

Even if the CSI settling time is faster than the HSI, care must be taken when the CSI is used as kernel clock for communication peripherals: the application must take into account the following parameters:

- • the time interval between the moment where the peripheral generates a kernel clock request and the moment where the clock is really available,

- • the frequency precision.

Note: CSION and CSIRDY bits are located in the RCC clock control register (RCC_CR) .

CSI calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated to achieve ACC CSI accuracy (refer to the product datasheet for more information). After reset, the factory calibration value is loaded in the CSICAL[7:0] bits.

Voltage and/or temperature variations affect the RC oscillator frequency. The user application can trim the CSI frequency using the CSITRIM[5:0] bits.

Note: Bits CSICAL[7:0] and CSITRIM[5:0] are located into the RCC CSI calibration register (RCC_CSICFGR) .

Figure 54. CSI calibration flow

![Figure 54. CSI calibration flow diagram. The diagram shows the flow of calibration data from Engineering option bytes (factory calibration) through the RCC block to the CSI block. Inside the RCC block, the data from FLASH_CSI_opt[7:0] is added to CSITRIM[5:0] (unsigned) to produce csi_cal[7:0]. This value is then stored in the CSICAL[7:0] (unsigned) register within the RCC_CSICFGR. The CSI block then reads the CAL[7:0] register.](/RM0481-STM32H523-33-562-63-573/98f92f79b14fa055e8bc8db8bab650ec_img.jpg)

graph LR

subgraph RCC

direction TB

CSICFGR[RCC_CSICFGR]

CSICAL[CSICAL[7:0] unsigned]

CSITRIM[CSITRIM[5:0] unsigned]

Adder((+))

csi_cal[csi_cal[7:0]]

CSICFGR -- CSICAL --> CSICAL

CSICFGR -- CSITRIM --> CSITRIM

CSITRIM --> Adder

FLASH_CSI_opt[FLASH_CSI_opt[7:0]] --> Adder

Adder --> csi_cal

csi_cal --> CSICAL

end

EOB[Engineering option bytes factory calibration] -- FLASH_CSI_opt --> FLASH_CSI_opt

CSICAL -- CSICAL --> CSI

subgraph CSI

CAL[CAL[7:0]]

end

CAL --> CSICAL

11.4.4 HSI48 clock

The HSI48 clock signal is generated from an internal 48 MHz RC oscillator, and can be used directly for USB and for random number generator (RNG).

The internal 48 MHz RC oscillator is mainly dedicated to provide a high-precision clock to the USB peripheral by means of a special clock recovery system (CRS) circuitry. The CRS can use the USB SOF signal, the LSE, or an external signal to automatically and quickly adjust the oscillator frequency on-the-fly. It is disabled as soon as the system enters Stop or Standby mode. When the CRS is not used, the HSI48 RC oscillator runs on its default frequency, subject to manufacturing process variations.

For more details on how to configure and use the CRS peripheral, refer to Section 12: Clock recovery system (CRS) .

The HSI48RDY flag in the RCC_CR register indicates whether the HSI48 RC oscillator is stable or not. At startup, the HSI48 RC oscillator output clock is not released until this bit is set by hardware.

The HSI48 can be switched on and off using the HSI48ON bit in the RCC_CR register.

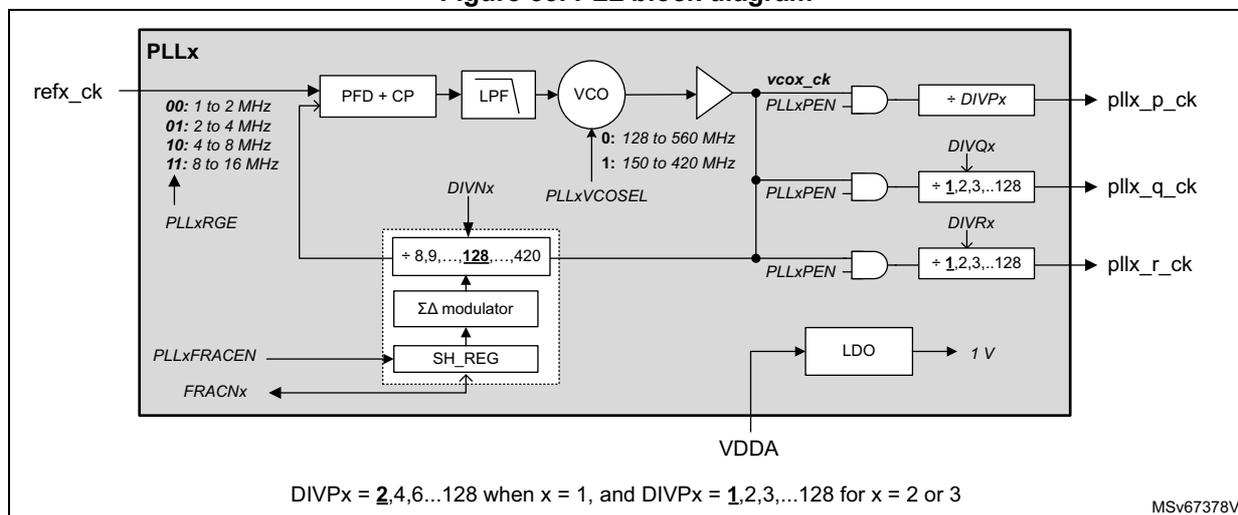

11.4.5 PLL description

The RCC features three PLLs:

- • a main PLL (PLL1), generally used to provide clocks to the CPU and some peripherals

- • two dedicated PLLs (PLL2 and PLL3), used to generate the kernel clock for peripherals

The PLLs integrated into the RCC are completely independent. They offer the following features:

- • A VCO supporting two modes:

- – a wide-range

- – a low-range used, for instance, in audio applications

- • Input frequency range:

- – 2 to 16 MHz for the VCO in wide-range mode

- – 1 to 2 MHz for the VCO in low-range mode

- • Capability to work either in integer or fractional mode

- • 13-bit sigma-delta modulator, to fine-tune the VCO frequency by 11 to 0.3 ppm steps

- • The sigma-delta modulator can be updated on-the-fly without generating frequency overshoots on PLLs outputs

- • Each PLL offers three outputs with post-dividers

Figure 55. PLL block diagram

DIVPx = 2,4,6...128 when x = 1, and DIVPx = 1,2,3,...128 for x = 2 or 3

MSv67378V2

The PLLs are controlled via RCC_PLLxDIVR, RCC_PLLxFRACR, RCC_PLLCFGR, and RCC_CR registers.

The frequency of the reference clock provided to the PLLs ( refx_ck ) must range from 1 to 16 MHz. The PLLxM dividers of the RCC PLLx clock source selection register (RCC_PLLxCFGR) must be properly programmed to match this condition. In addition, the PLLxRGE[1:0] field of the RCC PLLx clock source selection register (RCC_PLLxCFGR) must be set according to the reference input frequency to optimize performance.

The user application can then configure the VCO. The smaller range (150 to 420 MHz) must be chosen when the reference clock frequency is lower than 2 MHz.

To reduce the power consumption, it is recommended to configure the VCO output to the smaller range.

DIVNx loop divider must be programmed to achieve the expected frequency at VCO output. In addition, the VCO output range must be respected.

The PLLs operate in integer mode when the value of SH_REG bit of the FRACNx shadow register is set to 0. The SH_REG bit is updated with the FRACNx value when PLLxFRACEN

bit goes from 0 to 1. The sigma-delta modulator is designed to minimize the jitter impact, while allowing very small frequency steps.

The PLLs can be enabled by setting PLLxON to 1. The PLLxRDY bits indicate that the PLL is ready (locked).

Note: Before enabling the PLLs, make sure that the reference frequency ( refx_ck ) provided to it is stable, so the hardware does not allow changing PLLxM when the PLLx is ON, and it is also not possible to change PLLSRC when one of the PLLs is ON.

The hardware prevents writing PLL1ON to 0 if the PLL1 is currently used to deliver the system clock. There are other hardware protections on the clock generators (refer to HSE clock , HSI clock , and CSI oscillator ).

The following PLL parameters cannot be changed once the PLL is enabled: DIVNx, PLLxRGE, PLLxVCOSEL, PLLxP (DIVP), PLLxQ (DIVQ), and PLLxR (DIVR).

For optimal behavior of the PLL when one of the post-divider (DIVP, DIVQ or DIVR) is not used, the application must set the enable bit (DIVyEN) as well as the corresponding post-divider bits (DIVP, DIVQ or DIVR) to 0.

If the above rules are not respected, the PLL output frequency is not guaranteed.

Output frequency computation

When the PLL is configured in integer mode (SH_REG = 0), the VCO frequency ( \( F_{VCO} \) ) is given by the following expression:

When the PLL is configured in fractional mode (SH_REG different from 0), the DIVN divider must be initialized before enabling the PLLs. However, it is possible to change the value of FRACNx on-the-fly without disturbing the PLL output.

This feature can be used either to generate a specific frequency from any crystal value with a good accuracy, or to fine-tune the frequency on-the-fly.

For each PLL, the VCO frequency is given by the following formula:

Note: For PLL1, DIVP can only take odd values.

The PLLs are disabled by hardware when:

- • the system enters Stop or Standby mode

- • an HSE failure occurs when HSE or PLL (clocked by HSE) are used as system clock

PLL initialization phase

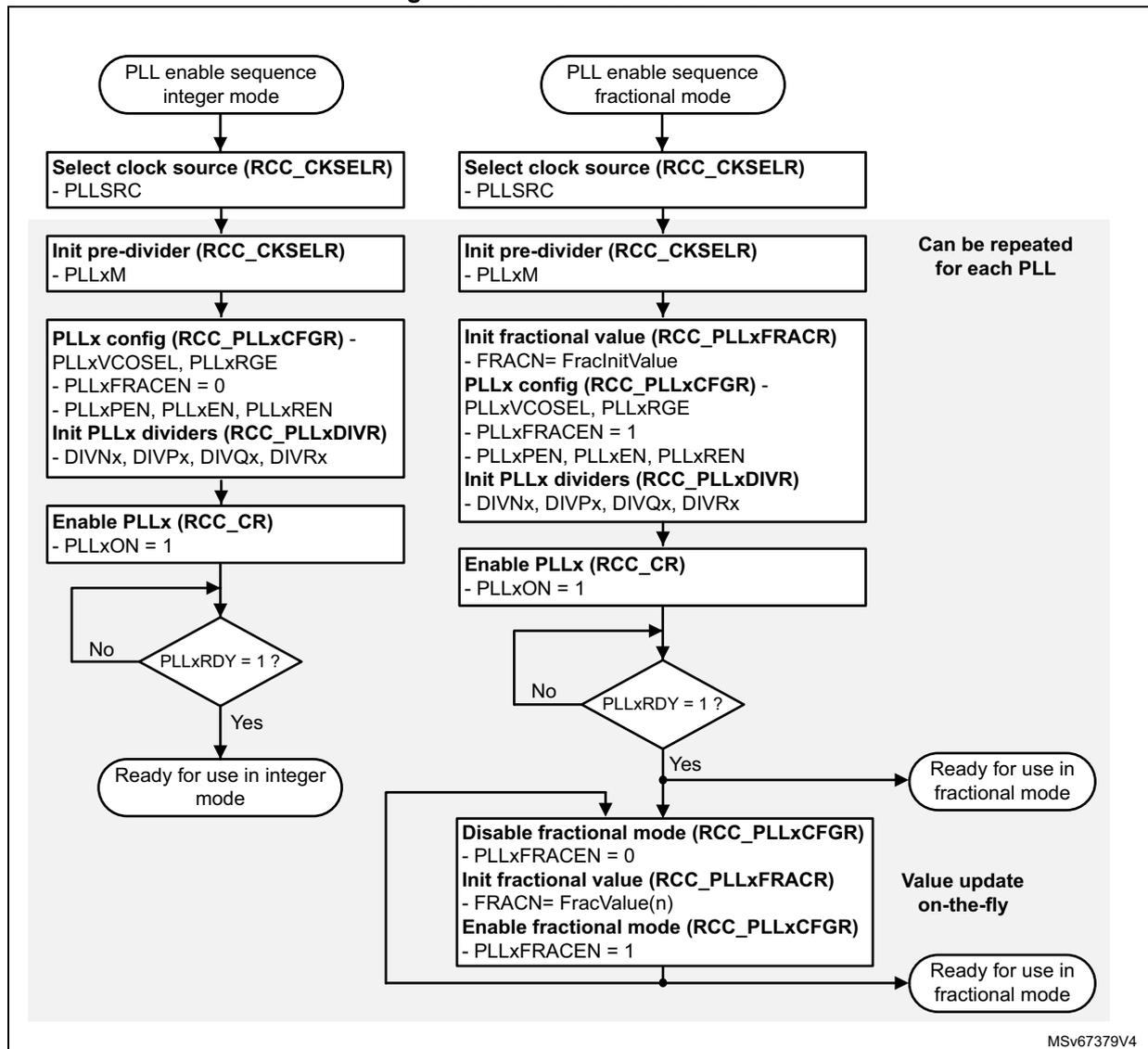

Figure 56 shows the recommended PLL initialization sequence in integer and fractional mode. The PLLx are supposed to be disabled at the start of the initialization sequence:

- 1. Initialize the PLLs registers according to the required frequency.

- – Set PLLxFRACEN of RCC PLLx clock source selection register (RCC_PLLxCFGR) to 0 for integer mode.

- – For fractional mode, set FRACN to the required initial value (FracInitValue) and then set PLLxFRACEN to 1.

- 2. Once the PLLxON bit is set to 1, the user application must wait until PLLxRDY bit is set to 1. If the PLLx is in fractional mode, the PLLxFRACEN bit must not be set back to 0 as long as PLLxRDY = 0.

- 3. Once the PLLxRDY bit is set to 1, the PLLx is ready to be used.

- 4. If the application intends to tune the PLLx frequency on-the-fly (possible only in fractional mode), then:

- a) PLLxFRACEN must be set to 0. When PLLxFRACEN = 0, the sigma-delta modulator is still operating with the value latched into SH_REG. The application must wait for three clock periods of refx_ck (PLLxFRACEN bit propagation delay).

- b) A new value must be uploaded into PLLxFRACR (FracValue(n)).

- c) PLLxFRACEN must be set to 1, to latch the content of PLLxFRACR into its shadow register. The new value is considered after three clock periods of refx_ck (PLLxFRACEN bit propagation delay).

Note: When the PLLxRDY goes to 1 the difference between the PLLx output frequency and the target value is lower than \( \pm 2\% \) .

Figure 56. PLLs initialization flow

graph TD

subgraph IntegerMode [PLL enable sequence integer mode]

I1([PLL enable sequence integer mode]) --> I2[Select clock source (RCC_CKSELR)

- PLLSRC]

I2 --> I3[Init pre-divider (RCC_CKSELR)

- PLLxM]

I3 --> I4[PLLx config (RCC_PLLxCFGR) -

PLLxVCOSEL, PLLxRGE

- PLLxFRACEN = 0

- PLLxPEN, PLLxEN, PLLxREN

Init PLLx dividers (RCC_PLLxDIVR)

- DIVNx, DIVPx, DIVQx, DIVRx]

I4 --> I5[Enable PLLx (RCC_CR)

- PLLxON = 1]

I5 --> I6{PLLxRDY = 1 ?}

I6 -- No --> I5

I6 -- Yes --> I7([Ready for use in integer mode])

end

subgraph FractionalMode [PLL enable sequence fractional mode]

F1([PLL enable sequence fractional mode]) --> F2[Select clock source (RCC_CKSELR)

- PLLSRC]

F2 --> F3[Init pre-divider (RCC_CKSELR)

- PLLxM]

F3 --> F4[Init fractional value (RCC_PLLxFRACR)

- FRACN= FracInitValue

PLLx config (RCC_PLLxCFGR) -

PLLxVCOSEL, PLLxRGE

- PLLxFRACEN = 1

- PLLxPEN, PLLxEN, PLLxREN

Init PLLx dividers (RCC_PLLxDIVR)

- DIVNx, DIVPx, DIVQx, DIVRx]

F4 --> F5[Enable PLLx (RCC_CR)

- PLLxON = 1]

F5 --> F6{PLLxRDY = 1 ?}

F6 -- No --> F5

F6 -- Yes --> F7([Ready for use in fractional mode])

end

F3 -.-> G[Can be repeated for each PLL]

G -.-> F3

I7 --> F8[Disable fractional mode (RCC_PLLxCFGR)

- PLLxFRACEN = 0

Init fractional value (RCC_PLLxFRACR)

- FRACN= FracValue(n)

Enable fractional mode (RCC_PLLxCFGR)

- PLLxFRACEN = 1]

F8 --> F9([Ready for use in fractional mode])

F8 -.-> H[Value update on-the-fly]

H -.-> F9

The flowchart illustrates the initialization process for PLLs in two modes: integer and fractional. Both modes start with a 'PLL enable sequence' (integer or fractional). The integer mode steps are: Select clock source (RCC_CKSELR) - PLLSRC, Init pre-divider (RCC_CKSELR) - PLLxM, PLLx config (RCC_PLLxCFGR) - PLLxVCOSEL, PLLxRGE, - PLLxFRACEN = 0, - PLLxPEN, PLLxEN, PLLxREN, Init PLLx dividers (RCC_PLLxDIVR) - DIVNx, DIVPx, DIVQx, DIVRx, Enable PLLx (RCC_CR) - PLLxON = 1, and a loop until PLLxRDY = 1. The fractional mode steps are: Select clock source (RCC_CKSELR) - PLLSRC, Init pre-divider (RCC_CKSELR) - PLLxM, Init fractional value (RCC_PLLxFRACR) - FRACN= FracInitValue, PLLx config (RCC_PLLxCFGR) - PLLxVCOSEL, PLLxRGE, - PLLxFRACEN = 1, - PLLxPEN, PLLxEN, PLLxREN, Init PLLx dividers (RCC_PLLxDIVR) - DIVNx, DIVPx, DIVQx, DIVRx, Enable PLLx (RCC_CR) - PLLxON = 1, and a loop until PLLxRDY = 1. A note indicates that the 'Init pre-divider' step can be repeated for each PLL. A transition from the integer mode 'Ready' state to the fractional mode 'Ready' state involves: Disable fractional mode (RCC_PLLxCFGR) - PLLxFRACEN = 0, Init fractional value (RCC_PLLxFRACR) - FRACN= FracValue(n), Enable fractional mode (RCC_PLLxCFGR) - PLLxFRACEN = 1, with a note 'Value update on-the-fly'.

MSV67379V4

11.4.6 LSE clock

The LSE can generate a clock from an external crystal/ceramic resonator, or from an external user clock.

External clock source (LSE bypass)

In this mode, an external clock source must be provided to OSC32_IN pin (see Figure 53). The input clock can have a frequency up to 1 MHz, and be low swing (analog) or digital. A duty cycle close to 50% is recommended.

In case of an analog clock (low swing), the LSEBYP and LSEON bits must be set to 1 ( RCC Backup domain control register (RCC_BDCR) ).

In case of a digital clock, the LSEBYP and the LSEEXT bits must be set to 1 followed by setting the LSEON bit to 1 ( RCC Backup domain control register (RCC_BDCR) ). If the RTC

is used, the LSE bypass must not be configured in digital mode, but in low swing analog mode (default value after reset).

External crystal/ceramic resonator (LSE crystal)

The LSE clock is generated from a 32.768 kHz crystal or ceramic resonator. It has the advantage to provide a low-power, highly accurate clock source to the real-time clock (RTC) for clock/calendar or other timing functions.

The LSERDY flag of the RCC Backup domain control register (RCC_BDCR) indicates whether the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by hardware. An interrupt can be generated if enabled in the RCC clock source interrupt enable register (RCC_CIER) .

The LSE oscillator is switched ON and OFF using the LSEON bit. The LSE remains enabled when the system enters Stop or Standby mode.

In addition, the LSE clock can be driven to the MCO1 output and used as clock source for other application components.

The LSE also offers a programmable driving capability (LSEDRV[1:0]), which can be used to modulate the amplifier driving capability. This driving capability is chosen according to the external crystal/ceramic component requirement to ensure a stable oscillation.

The driving capability must be set before enabling the LSE oscillator.

11.4.7 LSI clock

The LSI acts as a low-power clock source that can be kept running when the system is in Stop or Standby mode for the independent watchdog (IWDG) and auto-wakeup unit (AWU).

The clock frequency is around 32 kHz. For more details, refer to the electrical characteristics section of the datasheet.

The LSI can be switched ON and OFF using the LSION bit. The LSIRDY flag indicates whether the LSI oscillator is stable or not. If an independent watchdog is started either by hardware or software, the LSI is forced ON and cannot be disabled.

The LSI remains enabled when the system enters Stop or Standby mode.

At LSI startup, the clock is not provided until the hardware sets the LSIRDY bit. An interrupt can be generated if enabled in the RCC clock source interrupt enable register (RCC_CIER) .

In addition, the LSI clock can be driven to the MCO2 output, and used as a clock source for other application components.

Note: Bits LSION and LSIRDY are located in the RCC Backup domain control register (RCC_BDCR).

11.4.8 System clock (SYSCLK) selection

Four different clock sources can be used to drive the system clock (SYSCLK):

- • HSI oscillator

- • CSI oscillator

- • HSE oscillator

- • PLL

The system clock maximum frequency is 250 MHz. After a system reset (or after leaving Standby mode), the HSI oscillator, at 32 MHz, is selected as system clock. When a clock source is used directly or through the PLL as a system clock, it is not possible to stop it.

A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked). If a clock source not yet ready is selected, the switch occurs when the clock source becomes ready. Status bits in the RCC clock control register (RCC_CR) indicate which clocks are ready, and which clock is currently used as a system clock.

11.4.9 Handling clock generators in stop and standby modes

When the whole system enters Stop mode, all the clocks (system and kernel clocks) are stopped, as well as the following clock sources:

- • CSI, HSI (depending on HSIKERON and CSIKERON bits)

- • HSE

- • PLL1, PLL2, and PLL3

- • HSI48

The content of the RCC registers is not altered except for PLL1ON, PLL2ON, PLL3ON, HSEON, and HSI48ON, set to 0.

Exiting Stop mode

When the system exits this mode via a wake-up event, the application can select which oscillator (HSI and/or CSI) is used to restart. The STOPWUCK bit selects the oscillator used as system clock. The STOPKERWUCK bit selects the oscillator used as kernel clock for peripherals. The STOPKERWUCK bit is useful if after a system Stop, a peripheral needs a kernel clock generated by an oscillator different from the one used for the system clock.

These bits belong to the RCC clock configuration register1 (RCC_CFGR1)

Table 113. STOPWUCK and STOPKERWUCK description

| STOPWUCK | STOPKERWUCK | Activated oscillator(s) when the system exits Stop mode | Distributed clocks when the system exits Stop mode | |

|---|---|---|---|---|

| System clock | Kernel clock | |||

| 0 | 0 | HSI | HSI | HSI |

| 1 | HSI and CSI | HSI and/or CSI | ||

| 1 | 0 | CSI | ||

| 1 | CSI | CSI | ||

During Stop mode

There are two specific cases where the HSI or CSI can be enabled during this mode.

- • When a dedicated peripheral requests the kernel clock the peripheral receives the HSI or CSI according to the kernel clock source selected for this peripheral (via CKPERSEL[1:0]).

- • When the HSIKERON or CSIKERON bits of the RCC clock control register (RCC_CR) are set, the HSI and CSI are kept running, but the outputs are gated. The clock is then

available immediately when the system exits Stop mode, or when a peripheral requests the kernel clock (see Table 111 for details).

Table 114. HSIKERON and CSIKERON behavior

| HSIKERON (CSIKERON) | HSI (CSI) state during Stop mode | HSI (CSI) state setting time |

|---|---|---|

| 0 | OFF | \( t_{su(HSI)} \) \( t_{su(CSI)} \) (1) |

| 1 | Running and gated | Immediate |

- 1. \( t_{su(HSI)} \) and \( t_{su(CSI)} \) are the startup times of, respectively, the HSI and CSI oscillators (refer to the product datasheet for the values of these parameters).

When the microcontroller exists system standby mode, the HSI is selected as system and kernel clock. The RCC registers are reset to their initial values except for the RCC_RSR and RCC_BDCR registers.

Note: The HSI and CSI outputs provide two clock paths:

- • one path for the system clock (hsi_ck or csi_ck)

- • one path for the peripheral kernel clock (hsi_ker_ck or csi_ker_ck).

When a peripheral requests the kernel clock in system stop mode, only the path providing the hsi_ker_ck or csi_ker_ck is activated.

11.4.10 Clock security system (CSS)

Clock security system on HSE

The clock security system can be enabled by software via the HSECSSON bit, which can be enabled even when the HSEON is set to 0.

The CSS on HSE is enabled by the hardware when the HSE is enabled and ready, and HSECSSON set to 1.

The CSS on HSE is disabled when the HSE is disabled. As a result, this function does not work when the system is in Stop mode.

It is not possible to clear directly the HSECSSON bit by software.

The HSECSSON bit is cleared by hardware when a system reset occurs or when the system enters Standby mode.

If a failure is detected on the HSE clock, the system automatically switches to the HSI or CSI, depending on STOPWUCK bit configuration in RCC clock configuration register1 (RCC_CFGR1) , to provide a safe clock. The HSE is then automatically disabled, a clock failure event is sent to the break inputs of the advanced-control timers (TIM1, TIM8), and an NMI is automatically generated to inform the application about the failure, allowing the MCU to perform rescue operations. If the HSE output was used as clock source for PLLs when the failure occurred, the PLLs are also disabled.

If an HSE clock failure occurs when the CSS is enabled, the CSS generates an interrupt that causes the automatic generation of an NMI. The HSECSSF flag in RCC clock source interrupt flag register (RCC_CIFR) is set to 1 to allow the application to identify the failure source. The NMI routine is executed indefinitely until the HSECSSF bit is cleared. As a consequence, the application must clear the HSECSSF flag in the NMI ISR by setting the HSECSSC bit in the RCC clock source interrupt clear register (RCC_CICR) .

Clock security system on LSE

A clock security system on LSE can be activated by software writing the LSECSSON bit in the RCC Backup domain control register (RCC_BDCR) . This bit can be disabled only by a hardware or RTC software reset, or after a failure detection on LSE. LSECSSON must be written after LSE is enabled (LSEON enabled) and ready (LSERDY set by hardware), and after the RTC clock has been selected by RTCSEL.

The CSS operates in all modes, including VBAT. It works also under system reset (excluding power-on reset). The system detects when the LSE disappears, or if it is over frequency.

If a failure is detected on the external 32 kHz oscillator, the LSE clock is no longer supplied to the RTC, but no hardware action is made to the registers.

The CSS on LSE detection event is connected to the internal tamper 3 of the TAMP peripheral. The internal tamper 3 must be enabled (ITAMP3E = 1 in TAMP_CR1 register) and the associated interrupt enabled (ITAMP3IE in TAMP_IER) to wake up from the low-power modes. This erases also the TAMP backup registers and backup SRAM unless the ITAMP3NOER = 1 in the TAMP_CR3 (see Section 47: Tamper and backup registers (TAMP) for more details).

In case of CSS on LSE detection event (LSECSSD = 1 in the RCC_BDCR), the software must disable the LSECSSON bit, stop the defective 32 kHz oscillator (disabling LSEON), and change the RTC clock source (no clock or LSI or HSE, with RTCSEL), or take actions to secure the application.

Refer to datasheet for CSS on LSE electrical characteristics.

11.4.11 Clock output generation (MCO1/MCO2)

Two microcontroller clock output pins (MCO1 and MCO2) are available. A clock source can be selected for each output. The selected clock can be divided thanks to configurable prescaler (refer to Figure 52 for additional information on signal selection).

MCO1 and MCO2 outputs are controlled via MCO1PRE[3:0], MCO1[2:0], MCO2PRE[3:0], and MCO2[2:0], located in the RCC clock configuration register1 (RCC_CFGR1) .

The GPIO port corresponding to each MCO pin must be programmed in alternate function mode.

The clock provided to the MCOs outputs must not exceed the maximum pin speed (refer to the product datasheet for information on the supported speed).

Another output (LSCO) allows one of the low-speed clocks (LSI, LSE) to be output onto the external LSCO pin. This output is available in Stop mode, not available in Standby and VBAT modes. The selection is controlled by the LSCOSEL bit, and enabled by the LSCOEN bit in the RCC Backup domain control register (RCC_BDCR) .

The MCO clock output requires the corresponding alternate function selected on the MCO pin. The LSCO pin must be left in default POR state.

11.4.12 Kernel clock selection

Some peripherals are designed to work with two different clock domains that operate asynchronously:

- • a clock domain synchronous with the register and bus interface ( ckg_bus_perx clock)

- • a clock domain generally synchronous with the peripheral (kernel clock)

The benefit of having peripherals supporting these two clock domains is that the user application has more freedom to choose optimized clock frequency for the CPU, bus matrix and for the kernel part of the peripheral. The user application can thus change the bus frequency without reprogramming the peripherals. As an example, an ongoing transfer with UART is not disturbed if its APB clock is changed on-the-fly.

Table 115 shows the kernel clock that the RCC can deliver to the peripherals. Each row represents a multiplexer and the peripherals connected to its output.

Table 115. Kernel clock distribution overview

| Peripherals (1) | Clock multiplexer control bits | pll1_q_ck | pll2_p_ck | pll2_q_ck | pll2_r_ck | pll3_p_ck | pll3_q_ck | pll3_r_ck | sys_ck | bus clocks (2) | hse_ck | hsi_ker_ck | csi_ker_ck | hsi48_ck | lse_ck | lsi_ck | per_ck (3) | AUDIOCLK | Disabled |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| OCTOSPI | OSPSEL | 1 | - | - | 2 | - | - | - | - | 0 | - | - | - | - | - | - | 3 | - | - |

| SDMMC1 (4) | SDMMC1SEL | 0 | - | - | 1 | - | - | - | - | - | - | - | - | - | - | - | - | - | - |

| SDMMC2 (4) | SDMMC2SEL | 0 | - | - | 1 | - | - | - | - | - | - | - | - | - | - | - | - | - | - |

| FDCAN | FDCANSEL | 1 | - | 2 | - | - | - | - | - | - | 0 | - | - | - | - | - | - | - | - |

| CEC | CECSEL | - | - | - | - | - | - | - | - | - | - | - | 2 (5) | - | 0 | 1 | - | - | - |

| I2C1 | I2C1SEL | - | - | - | - | - | - | 1 | - | 0 | - | 2 | 3 | - | - | - | - | - | - |

| I2C2 | I2C2SEL | - | - | - | - | - | - | 1 | - | 0 | - | 2 | 3 | - | - | - | - | - | - |

| I2C3 | I2C3SEL | - | - | - | - | - | - | 1 | - | 0 | - | 2 | 3 | - | - | - | - | - | - |

| I2C4 | I2C4SEL | - | - | - | - | - | - | 1 | - | 0 | - | 2 | 3 | - | - | - | - | - | - |

| I3C1 | I3C1SEL | - | - | - | - | - | - | 1 | - | 0 | - | 2 | - | - | - | - | - | - | - |

| I3C2 | I3C2SEL | - | - | - | - | - | - | 1 | - | 0 | - | 2 | - | - | - | - | - | - | - |

| LPTIM1 | LPTIM1SEL | - | 1 | - | - | - | - | 2 | - | 0 | - | - | - | - | 3 | 4 | 5 | - | - |

| LPTIM2 | LPTIM2SEL | - | 1 | - | - | - | - | 2 | - | 0 | - | - | - | - | 3 | 4 | 5 | - | - |

| LPTIM3 | LPTIM3SEL | - | 1 | - | - | - | - | 2 | - | 0 | - | - | - | - | 3 | 4 | 5 | - | - |

| LPTIM4 | LPTIM4SEL | - | 1 | - | - | - | - | 2 | - | 0 | - | - | - | - | 3 | 4 | 5 | - | - |

| LPTIM5 | LPTIM5SEL | - | 1 | - | - | - | - | 2 | - | 0 | - | - | - | - | 3 | 4 | 5 | - | - |

| LPTIM6 | LPTIM6SEL | - | 1 | - | - | - | - | 2 | - | 0 | - | - | - | - | 3 | 4 | 5 | - | - |

| TIM[8:1], | - | - | - | - | - | - | - | - | - | x | - | - | - | - | - | - | - | - | - |

| TIM[17:12] | - | - | - | - | - | - | - | - | - | x | - | - | - | - | - | - | - | - | - |

| TIM16/17 | TIMICSEL | - | - | - | - | - | - | - | - | - | - | 1 | 1 | - | - | - | - | - | 0 |

| RNG | RNGSEL | 1 | - | - | - | - | - | - | - | - | - | - | - | 0 | 2 | 3 | - | - | - |

| SAI1 | SAI1SEL | 0 | 1 | - | - | 2 | - | - | - | - | - | - | - | - | - | - | 4 | 3 | - |

| SAI2 | SAI2SEL | 0 | 1 | - | - | 2 | - | - | - | - | - | - | - | - | - | - | 4 | 3 | - |

| SPI(I2S)1 | SPI1SEL | 0 | 1 | - | - | 2 | - | - | - | - | - | - | - | - | - | - | 4 | 3 | - |

| SPI(I2S)2 | SPI2SEL | 0 | 1 | - | - | 2 | - | - | - | - | - | - | - | - | - | - | 4 | 3 | - |

| SPI(I2S)3 | SPI3SEL | 0 | 1 | - | - | 2 | - | - | - | - | - | - | - | - | - | - | 4 | 3 | - |

Table 115. Kernel clock distribution overview (continued)

| Peripherals (1) | Clock multiplexer control bits | pll1_q_ck | pll2_p_ck | pll2_q_ck | pll2_r_ck | pll3_p_ck | pll3_q_ck | pll3_r_ck | sys_ck | bus clocks (2) | hse_ck | hsi_ker_ck | csi_ker_ck | hsi48_ck | lse_ck | lsi_ck | per_ck (3) | AUDIOCLK | Disabled |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SPI4 | SPI4SEL | - | - | 1 | - | - | 2 | - | - | 0 | 5 | 3 | 4 | - | - | - | - | - | - |

| SPI5 | SPI5SEL | - | - | 1 | - | - | 2 | - | - | 0 | 5 | 3 | 4 | - | - | - | - | - | - |

| SPI6 | SPI6SEL | - | - | 1 | - | - | 2 | - | - | 0 | 5 | 3 | 4 | - | - | - | - | - | - |

| USARTx | USARTxSEL | - | - | 1 | - | - | 2 | - | - | 0 | - | 3 | 4 | - | 5 | - | - | - | - |

| UARTx | UARTxSEL | - | - | 1 | - | - | 2 | - | - | 0 | - | 3 | 4 | - | 5 | - | - | - | - |

| LPUART1 | LPUART1SEL | - | - | 1 | - | - | 2 | - | - | 0 | - | 3 | 4 | - | 5 | - | - | - | - |

| USB | USBSEL | 1 | - | - | - | - | 2 | - | - | - | - | - | - | 3 | - | - | - | - | 0 |

| ADC DAC (6) | ADC DACSEL | - | - | - | 2 | - | - | - | 1 | 0 | 3 | 4 | 5 | - | - | - | - | - | - |

| DAC | DACSEL | - | - | - | - | - | - | - | - | - | - | - | - | - | 0 | 1 | - | - | - |

| UCPD1 | - | - | - | - | - | - | - | - | - | - | - | x (7) | - | - | - | - | - | - | - |

| ETH (ptp) | - | x | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - |

| RTC/AWU | RTCSEL | - | - | - | - | - | - | - | - | - | 3 (8) | - | - | - | 1 | 2 | - | - | 0 |

| All | CKPERSEL | - | - | - | - | - | - | - | - | - | 2 | 0 | 1 | - | - | - | - | - | 3 |

1. For the actual availability of the peripheral refer to the device datasheet.

2. The bus (APB or AHB) clocks are the bus interface clocks to whom the peripherals are connected.

3. The per_ck clock can be hse_ck, hsi_ker_ck, or csi_ker_ck, according to CKPERSEL selection.

4. With a duty cycle close to 50%, meaning that PLL1Q or PLL2R values must be even. For SDMMCx the duty cycle must be 50% when supporting DDR.

5. Clock CSI divided by 122.

6. With a duty cycle close to 50%, meaning that PLL2R values must be even

7. Clock HSI divided by 4.

8. Clock HSE divided by RTCPRE.

To reduce the number of switches, some peripherals share the same kernel clock source, but all have their dedicated enable signal.

Peripherals dedicated to audio applications

The audio peripherals generally need specific accurate frequencies, the kernel clock of the SAIs or SPI(I2S)s can be generated by:

- • PLL1 when the amount of active PLLs must be reduced (for SAIs and SPI1 to 3)

- • APB2 peripheral clock (for SPI4 and 5)

- • APB3 peripheral clock (for SPI6)

- • PLL2 or 3 for optimal flexibility in frequency generation

- • HSE, HSI, or CSI when the current consumption is critical

- • AUDIOCLK when an external clock reference must be used

Peripherals dedicated to control and data transfer

Peripherals such as SPIs, I2Cs, UARTs do not need a specific kernel clock frequency but a clock fast enough to generate the correct baud rate, or the required bit clock on the serial interface. For that purpose the source can be selected among the following ones:

- • PLL1 when the amount of active PLLs must be reduced

- • PLL2 or PLL3 if better flexibility is required. As an example, this solution allows changing the frequency bus via PLL1 without affecting the speed of some serial interfaces.

- • HSI or CSI for low-power use-cases or when the peripheral must quickly wake up from Stop mode (such as UART or I2C)

Note: UARTs also need the LSE clock when high baud rates are not required.

The OCTOSPI and SDMMC1/2 can also use a clock different from the bus interface one for more flexibility.

RTC/AWU clock

The rtc_ck clock source can be one of the following:

- • the hse_1M_ck ( hse_ck divided by a programmable prescaler)

- • the lse_ck

- • the lsi_ck clock

The source clock is selected by programming the RTCSEL[1:0] bits in the RCC Backup domain control register (RCC_BDCR) and the RTCPRE[5:0] bits in the RCC clock configuration register1 (RCC_CFGR1) .

This selection cannot be modified without resetting the Backup domain.

If the LSE is selected as RTC clock, the RTC works normally even if the backup or the \( V_{DD} \) supply disappears.

The LSE clock is in the Backup domain, whereas the other oscillators are not. As a consequence:

- • If LSE is selected as RTC clock, the RTC continues working even if the \( V_{DD} \) supply is switched OFF, provided the \( V_{BAT} \) supply is maintained.

- • If LSI is selected as the RTC clock, the AWU state is not guaranteed if the \( V_{DD} \) supply is powered off.

- • If the HSE clock is used as RTC clock, the RTC state is not guaranteed if the \( V_{DD} \) supply is powered off or if the \( V_{CORE} \) supply is powered off.

The rtc_ck clock is enabled through RTCEN bit located in the RCC Backup domain control register (RCC_BDCR) .

The RTC bus interface clock (APB clock) is enabled through RTCAPBEN and RTCAPBLPEN bits located in RCC_APB3ENR/LPENR registers.

Note: To read the RTC calendar register when the APB clock frequency is less than seven times the RTC clock frequency ( \( F_{APB} < 7 \times F_{RTCLK} \) ), the software must read the calendar time and date registers twice. The data are correct if the second read access to RTC_TR gives the same result than the first one. Otherwise a third read access must be performed.

Watchdog clocks

The RCC provides the clock for the two watchdog blocks available on the circuit. The independent watchdog (IWDG) is connected to the LSI. The window watchdog (WWDG) is connected to the APB clock.

If an independent watchdog is started by either hardware option or software access, the LSI is forced ON and cannot be disabled. After the LSI oscillator setup delay, the clock is provided to the IWDG.

Clock frequency measurement using TIMx

Most of the clock source generator frequencies can be measured by means of the input capture of TIMx.

- • Calibrating the HSI or CSI with the LSE:

The primary purpose of having the LSE connected to a TIMx input capture is to be able to accurately measure the HSI or CSI. This requires to use the HSI or CSI as system clock source either directly or via PLL1. The number of system clock counts between consecutive edges of the LSE signal gives a measurement of the internal clock period. Taking advantage of the high precision of LSE crystals (typically a few tens of ppm) we can determine the internal clock frequency with the same resolution, and trim the source to compensate for manufacturing-process and/or temperature- and voltage-related frequency deviations.

The basic concept consists in providing a relative measurement (e.g. HSI/LSE ratio). The precision is therefore tightly linked to the ratio between the two clock sources. The greater the ratio is, the more accurate the measurement is.

The HSI and CSI oscillators have dedicated user-accessible calibration bits for this purpose (see RCC CSI calibration register (RCC_CSICFGR) ). When HSI or CSI is used via the PLLx, the system clock can also be fine-tuned by using the fractional divider of the PLLs.

- • Calibrating the LSI with the HSI:

The LSI frequency can also be measured: this is useful for applications that do not have a crystal. The ultra-low-power LSI oscillator has a large manufacturing process deviation. The LSI clock frequency can be measured using the more precise HSI clock source. Using this measurement, a more accurate RTC time base timeouts (when LSI is used as the RTC clock source) and/or an IWDG timeout with an acceptable accuracy can be obtained.

11.4.13 RTC and TAMP clock

The RTCCLK clock source is used by RTC and TAMP, and can be either the HSE / 32, LSE or LSI clock. It is selected by programming the RTCSEL[1:0] bits in the RCC Backup domain control register (RCC_BDCR) . This selection cannot be modified without resetting the Backup domain. The system must always be configured so as to get a PCLK frequency greater than or equal to the RTCCLK frequency for a proper operation of the RTC. The TAMP does not require any kernel clock if only the backup registers are used, with tamper in edge detection mode. All other tamper detection modes require a kernel clock (refer to Section 47: Tamper and backup registers (TAMP) for more details).

The LSE is in the Backup domain, whereas the HSE and LSI clocks are not. Consequently:

- • If LSE is selected as RTC and TAMP clock, these peripherals continue to work even if the \( V_{DD} \) supply is switched off, provided the \( V_{BAT} \) supply is maintained.

- • If the HSE clock divided by a prescaler is used as the RTC or TAMP clock, the RTC state is not guaranteed if the \( V_{DD} \) supply is powered off or if the internal voltage regulator is powered off (removing power from the core domain). Depending on the TAMP configuration, this one can remain functional if used in a mode that does not need any kernel clock.

- • If the LSI is used as the RTC or TAMP clock, the RTC state is not guaranteed if the \( V_{DD} \) supply is powered off. Depending on the TAMP configuration, this one can remain functional if used in a mode that does not need any kernel clock.

When the RTC and TAMP clock is LSE or LSI, the RTC remains clocked and functional under system reset.

11.4.14 Timer clock

The timer clock frequencies are automatically defined by hardware.

There are two cases:

- • If the APB prescaler equals 1, the timer clock frequencies are set to the APB domain frequency.

- • Otherwise, they are set to twice ( \( \times 2 \) ) the APB domain frequency.

11.4.15 Watchdog clock

If the independent watchdog (IWDG) is started by either hardware option or software access, the LSI oscillator is forced on and cannot be disabled. After the LSI oscillator temporization, the LSI 32 kHz clock is provided to the IWDG.

11.4.16 Peripherals clock gating and autonomous mode

Peripherals clock gating in Run mode

Each peripheral clock can be enabled by the corresponding EN bit in the RCC_AHBxENR and RCC_APBxENR registers.

When the peripheral clock is not active, read or write accesses to the peripheral registers are not supported.

The enable bit has a synchronization mechanism to create a glitch-free clock for the peripheral. After the enable bit is set, there the clock is active after 2 cycles of the peripheral bus clock.

Caution: Just after enabling the clock for a peripheral, the software must wait for these 2 clock cycles before accessing the peripheral registers.

Peripherals clock gating in Sleep mode

When a peripheral is enabled, its clock can be automatically gated off when the device is in Sleep mode, by clearing the peripheral LPEN bit in the RCC_AHBxLPENR and RCC_APBxLPENR registers. Both EN and LPEN bit of the peripheral must be set to keep the clock on in Sleep mode.

11.5 RCC security and privilege functional description

11.5.1 RCC TrustZone security protection modes

When the TrustZone security is activated by the TZEN option byte in the Flash option byte configuration register, the RCC is able to secure RCC configuration and status bits from being modified by non-secure accesses.

This is configured through the RCC secure configuration register (RCC_SECCFGR) to prevent non-secure access to read or modify the following features:

- • HSE, HSE-CSS, HSI, CSI, LSI, LSE, LSE-CSS, LSCO, HSI48 configuration and status bits

- • PLL1, PLL2, PLL3, AHB and APB prescalers configuration and status bits

- • system clock (SYSCLK) and ICLK source clock selection and status bits

- • MCO clock output configuration and STOPWUCK and STOPKERWUCK bit

- • Remove reset flag RMVF configuration

If SPRIV is set in the RCC privilege configuration register (RCC_PRIVCFGR) , the RCC_SECCFGR register can be written only by secure and privileged access. If SPRIV is cleared in RCC_PRIVCFGR, RCC_SECCFGR can be written only by secure access, privileged or unprivileged.

RCC_SECCFGR can be read by secure, non-secure, privileged and unprivileged access.

When a peripheral is configured as secure, its related clock, reset, clock source selection and clock enable during low-power modes control bits, are also secure in the RCC_AHBxENR, RCC_APBxENR, RCC_CCIPRx and RCC_BDCR registers.

A peripheral is secure when:

- • For securable peripherals by TZSC (see Section 5.4.3: TrustZone security controller (TZSC) ), the SEC security bit corresponding to this peripheral is set in the GTZC TZSC secure configuration registers.

- • For TrustZone ® -aware peripherals, a security feature of this peripheral is enabled through its dedicated bits.

Table 116 summarizes the RCC secured bits following the security configuration bit in the RCC_SECCFGR register.

When one security configuration bit is set, some configuration and status bits are secured. The RCC registers may contain secure and non-secure bits:

- • Secured bits: read and write operations are only allowed by a secure access. Non-secure read returns 0 and write accesses are ignored. No illegal access event is generated.

- • Non-secure bits: no restriction. Read and write operations are allowed by both secure and non-secure accesses.

- • A non-secure write access to RCC_SECCFGR is ignored and generates an illegal access event. An illegal access interrupt is generated if the RCC illegal access interrupt is enabled in the GTZC TZIC registers. RCC_SECCFGR can be read by secure or non-secure access.

When the TrustZone security is disabled (TZEN = 0xC3), all registers are non-secure. RCC_SECCFGR write accesses are ignored.

Table 116. RCC security configuration summary

| Configuration bit in RCC_SECCFGR | Secured bits | Corresponding register |

|---|---|---|

| HSISEC | HSION, HSIKERON, HSIRDY | RCC_CR |

| HSICAL[11:0], HSITRIM[6:0] | RCC_HSICFGR | |

| HSIRDYIE | RCC_CIER | |

| HSIRDYIF | RCC_CIFR | |

| HSIRDYC | RCC_CICR | |

| HSESEC | HSEON, HSERDY, HSEBYP, HSECSSON, HSEEXT | RCC_CR |

| HSERDYIE, HSECSSF | RCC_CIER | |

| HSERDYIF, HSECSSF | RCC_CIFR | |

| HSERDYC, HSECSSC | RCC_CICR | |

| CSISEC | CSISON, CSIKERON, CSISRDY | RCC_CR |

| CSICAL[7:0], CSITRIM[5:0] | RCC_CSICFGR | |

| CSISRDYIE | RCC_CIER | |

| CSISRDYIF | RCC_CIFR | |

| CSISRDYC | RCC_CICR | |

| LSISEC | LSION, LSIRDY, LSIPREDIV, LSCOSEL, LSCOEN | RCC_BDCR |

| LSIRDYIE | RCC_CIER | |

| LSIRDYIF | RCC_CIFR | |

| LSIRDYC | RCC_CICR | |

| LSESEC | LSECSSON, LSECSSD, LSEDRV[1:0], LSEBYP, LSERDY, LSEON, LSEEXT, LSCOSEL, LSCOEN | RCC_BDCR |

| LSERDYIE | RCC_CIER | |

| LSERDYF | RCC_CIFR | |

| LSERDYC | RCC_CICR | |

| SYSCLKSEC | SW[1:0], SWS[1:0], STOPWUCK, STOPKERWUCK, MCO1SEL[3:0], MCO1PRE[2:0], MCO2SEL[3:0], MCO2PRE[2:0] | RCC_CFGR1 |

| SYSTICKSEL[1:0] | RCC_CCIPR4 | |

| VOS[1:0] | PWR_VOSR | |

| TIMPRE | RCC_CFGR1 | |

| PRESCSEC | HPRE[3:0], PPRE1[2:0], PPRE2[2:0], PPRE3[2:0] | RCC_CFGR2 |

Table 116. RCC security configuration summary (continued)

| Configuration bit in RCC_SECCFGR | Secured bits | Corresponding register |

|---|---|---|

| PLL1SEC | PLL1SRC[1:0], PLL1RGE[1:0], PLL1FRACEN, PLL1M[3:0], PLL1VCOSEL, PLL1PEN, PLL1QEN, PLL1REN | RCC_PLL1CFGR |

| PLL1N[8:0], PLL1P[6:0], PLL1Q[6:0], PLL1R[6:0] | RCC_PLL1DIVR | |

| PLL1FRACN[12:0] | RCC_PLL1FRACR | |

| PLL1RDY, PLL1ON | RCC_CR | |

| PLL1RDYIE | RCC_CIER | |

| PLL1RDYF | RCC_CIFR | |

| PLL1RDYC | RCC_CICR | |

| PLL2SEC | PLL2SRC[1:0], PLL2RGE[1:0], PLL2FRACEN, PLL2M[3:0], PLL2PEN, PLL2QEN, PLL2REN, PLL2VCOSEL | RCC_PLL2CFGR |

| PLL2N[8:0], PLL2P[6:0], PLL2Q[6:0], PLL2R[6:0] | RCC_PLL2DIVR | |

| PLL2FRACN[12:0] | RCC_PLL2FRACR | |

| PLL2RDY, PLL2ON | RCC_CR | |

| PLL2RDYIE | RCC_CIER | |

| PLL2RDYF | RCC_CIFR | |

| PLL2RDYC | RCC_CICR | |

| PLL3SEC | PLL3SRC[1:0], PLL3RGE[1:0], PLL3FRACEN, PLL3M[3:0], PLL3PEN, PLL3QEN, PLL3REN, PLL3VCOSEL | RCC_PLL3CFGR |

| PLL3N[8:0], PLL3P[6:0], PLL3Q[6:0], PLL3R[6:0] | RCC_PLL3DIVR | |

| PLL3FRACN[12:0] | RCC_PLL3FRACR | |

| PLL3RDY, PLL3ON | RCC_CR | |

| PLL3RDYIE | RCC_CIER | |

| PLL3RDYF | RCC_CIFR | |

| PLL3RDYC | RCC_CICR | |

| HSI48SEC (1) | HSI48ON, HSI48RDY | RCC_CR |

| HSI48CAL[9:0] | RCC_CRRRCR | |

| HSI48RDYE | RCC_CIER | |

| HSI48RDYF | RCC_CIFR | |

| HSI48RDYC | RCC_CICR | |

| IPKERSECCFG | CKERPSEL[1:0] | RCC_CCIPR5 |

| RMVFSEC | RMVF | RCC_CSR |

1. TRIM field of the HSI48 is located in CRS peripheral. Be sure to secure it using CRSSEC bit in GTZC1 TZSC secure configuration register 1.

11.5.2 RCC privilege protection modes

By default, after reset, all RCC registers can be read or written with both privileged and unprivileged access except RCC privilege configuration register (RCC_PRIVCFGR) that can be written with privileged access only. RCC_PRIVCFGR can be read by secure and non secure, privileged and unprivileged access.

The SPRIV bit in RCC_PRIVCFGR can be written with secure privileged access only. This bit configures the privileged access of all RCC secure functions (as defined by RCC secure configuration register (RCC_SECCFGR) or by the GTZC for securable peripherals, or by the peripheral itself in case of TrustZone-aware peripherals).

When the SPRIV bit is set in RCC_PRIVCFGR:

- • Writing the RCC secure bits is possible only with privileged access, including RCC_SECCFGR.

- • The RCC secure bits can be read only with privileged access except RCC_SECCFGR and RCC_PRIVCFGR that can be read by privileged or unprivileged access.

- • An unprivileged access to a privileged RCC bit or register is discarded: the bits are read as zero and the write to these bits is ignored (RAZ/WI).

The NSPRIV bit in RCC_PRIVCFGR can be written with privileged access only, secure or non-secure. This bit configures the privileged access of all RCC non-secure functions (as defined by RCC_SECCFGR, or by the GTZC for securable peripherals, or by the peripheral itself in case of TrustZone-aware peripherals).

When the NSPRIV bit is set in RCC_PRIVCFGR:

- • Writing the RCC non-secure bits is possible only with privileged access.

- • The RCC non-secure bits can be read only with privileged access except RCC_PRIVCFGR that can be read by privileged or unprivileged access.

- • An unprivileged access to a privileged RCC bit or register is discarded: the bits are read as zero and the write to these bits is ignored (RAZ/WI).

11.6 RCC low-power modes

- • AHB and APB peripheral clocks, including DMA clock, can be disabled by software.

- • Sleep mode stops the CPU clock. The memory interface clocks (flash memory, caches and all SRAM interfaces) can be stopped by software during Sleep mode. The AHB to APB bridge clocks are disabled by hardware during Sleep mode when all the clocks of the peripherals connected to them are disabled.

- • Stop mode stops all the clocks in the core domain and disable the PLLs, HSI, HSI48, CSI and HSE oscillators. However, HSI or CSI can be switched ON to generate a wakeup interrupt. LSI and LSE remain active in Stop mode.

- • Standby mode stops all the clocks in the core domain and disable the PLLs, HSI, HSI48, CSI and HSE oscillators.

The CPU DeepSleep mode can be overridden for debugging by setting the DBG_STOP or DBG_STANDBY bit in the DBGMCU_CR register.

When exiting Stop mode, the system clock is either HSI or CSI, depending on the software configuration of STOPWUCK in the RCC CPU domain clock configuration register 2 (RCC_CFGR2) . The frequency (range and user trim) of the HSI is the one configured before entering Stop mode.

The other internal oscillator can be automatically woken up in addition to the one used by the system clock, to avoid waiting for the other oscillator wake-up time when the device is back in Run mode. This is done thanks to STOPKERWUCK in RCC_CFGR1.

When leaving the Standby mode, the system clock is HSI (32 MHz). The user trim is lost.

If a flash memory programming operation is ongoing, Stop or Standby mode entry is delayed until the flash memory interface access is finished. If an access to the APB domain is ongoing, Stop or Standby mode entry is delayed until the APB access is finished.

11.7 RCC interrupts

Table 117 summarizes the interrupt sources and the way to control them.

Table 117. Interrupt sources and control

| Interrupt vector | Interrupt event flag | Description | Enable control bits | Interrupt clear method | Exit from Sleep mode | Exit from Stop and Standby modes |

|---|---|---|---|---|---|---|

| RCC | LSIRDYF | LSI ready | LSIRDYIE and LSISEC = 0 | Set LSIRDYC to 1 | Yes | No |

| LSERDYF | LSE ready | LSERDYIE and LSESEC = 0 | Set LSERDYC to 1 | Yes | No | |

| HSIDRYF | HSI ready | HSIDRYIE and HSISEC = 0 | Set HSIRDYC to 1 | Yes | No | |

| HSERDYF | HSE ready | HSERDYIE and HSESEC = 0 | Set HSERDYC to 1 | Yes | No | |

| CSISRDYF | CSIS ready | CSISRDYIE and CSISEC = 0 | Set CSISRDYC to 1 | Yes | No | |

| HSI48RDYF | HSI48 ready | HSI48RDYIE and HSI48SEC = 0 | Set HSI48RDYC to 1 | Yes | No | |

| PLL1RDYF | PLL1 ready | PLL1RDYIE and PLL1SEC = 0 | Set PLL1RDYC to 1 | Yes | No | |

| PLL2RDYF | PLL2 ready | PLL2RDYIE and PLL2SEC = 0 | Set PLL2RDYC to 1 | Yes | No | |

| PLL3RDYF | PLL3 ready | PLL3RDYIE and PLL3SEC = 0 | Set PLL3DYC to 1 | Yes | No | |

| RCC_S (1) | LSIRDYF | LSI ready | LSIRDYIE and LSISEC = 1 | Set LSIRDYC to 1 | Yes | No |

| LSERDYF | LSE ready | LSERDYIE and LSESEC = 1 | Set LSERDYC to 1 | Yes | No | |

| HSIDRYF | HSI ready | HSIDRYIE and HSISEC = 1 | Set HSIRDYC to 1 | Yes | No | |

| HSERDYF | HSE ready | HSERDYIE and HSESEC = 1 | Set HSERDYC to 1 | Yes | No | |

| CSISRDYF | CSIS ready | CSISRDYIE and CSISEC = 1 | Set CSISRDYC to 1 | Yes | No | |

| HSI48RDYF | HSI48 ready | HSI48RDYIE and HSI48SEC = 1 | Set HSI48RDYC to 1 | Yes | No | |

| PLL1RDYF | PLL1 ready | PLL1RDYIE and PLL1SEC = 1 | Set PLL1RDYC to 1 | Yes | No | |

| PLL2RDYF | PLL2 ready | PLL2RDYIE and PLL2SEC = 1 | Set PLL2RDYC to 1 | Yes | No | |

| PLL3RDYF | PLL3 ready | PLL3RDYIE and PLL3SEC = 1 | Set PLL3RDYC to 1 | Yes | No |

Table 117. Interrupt sources and control (continued)

| Interrupt vector | Interrupt event flag | Description | Enable control bits | Interrupt clear method | Exit from Sleep mode | Exit from Stop and Standby modes |

|---|---|---|---|---|---|---|

| TAMP | ITAMP3F (2) | LSE CSS failure | LSECSSON and ITAMP3E (2) and ITAMP3IE (2) | Set CITAMP3F (2) to 1 | Yes | Yes |

| NMI | HSECSSF | HSE CSS failure | (3) | Set HSECSSC to 1 | Yes | No |

- 1. The RCC secure interrupt vector is used only when TrustZone is enabled.

- 2. The LSE CSS failure event (LSECSSD) is connected to TAMP internal tamper 3. to get the interrupt associated to this event, the internal tamper 3 must be enabled, and the internal tamper 3 interrupt must be enabled. The ITAMP3F, ITAMP3E, ITAMP3IE, and CITAMP3F bits are in the TAMP peripheral.

- 3. It is not possible to mask this interrupt when the security system feature is enabled (HSECSSON = 1).

11.8 RCC registers

11.8.1 RCC clock control register (RCC_CR)

Address offset: 0x000

Reset value: 0x0000 002B

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | PLL3 RDY | PLL3 ON | PLL2 RDY | PLL2 ON | PLL1 RDY | PLL1 ON | Res. | Res. | Res. | HSE EXT | HSE CSSON | HSE BYP | HSE RDY | HSE ON |

| r | rw | r | rw | r | rw | rw | rs | rw | r | rw | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | HSI48 RDY | HSI48 ON | Res. | CSI KERON | CSI RDY | CSI ON | Res. | Res. | HSI DIVF | HSIDIV[1:0] | HSI KERON | HSI RDY | HSI ON | |

| r | rw | rw | r | rw | r | rw | rw | rw | r | rw | |||||

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 PLL3RDY : PLL3 clock ready flag

Set by hardware to indicate that the PLL3 is locked.

0: PLL3 unlocked (default after reset)

1: PLL3 locked

Bit 28 PLL3ON : PLL3 enable

Set and cleared by software to enable PLL3.

Cleared by hardware when entering Stop or Standby mode.

0: PLL3 OFF (default after reset)

1: PLL3 ON

Bit 27 PLL2RDY : PLL2 clock ready flag

Set by hardware to indicate that the PLL is locked.

0: PLL2 unlocked

1: PLL2 locked

Bit 26 PLL2ON : PLL2 enable

Set and cleared by software to enable PLL2.

Cleared by hardware when entering Stop or Standby mode.

0: PLL2 OFF (default after reset)

1: PLL2 ON

Bit 25 PLL1RDY : PLL1 clock ready flag

Set by hardware to indicate that the PLL1 is locked.

0: PLL1 unlocked (default after reset)

1: PLL1 locked

Bit 24 PLL1ON : PLL1 enable

Set and cleared by software to enable PLL1.

Cleared by hardware when entering Stop or Standby mode. Note that the hardware prevents writing this bit to 0, if the PLL1 output is used as the system clock.

0: PLL1 OFF (default after reset)

1: PLL1 ON

Bits 23:21 Reserved, must be kept at reset value.

Bit 20 HSEEXT : external high speed clock type in Bypass mode

Set and reset by software to select the external clock type (analog or digital).

The external clock must be enabled with the HSEON bit to be used by the device. The HSEEXT bit can be written only if the HSE oscillator is disabled.

0: HSE in analog mode (default after reset)

1: HSE in digital mode

Bit 19 HSECSSON : HSE clock security system enable

Set by software to enable clock security system on HSE.

This bit is “set only” (disabled by a system reset or when the system enters in Standby mode). When HSECSSON is set, the clock detector is enabled by hardware when the HSE is ready and disabled by hardware if an oscillator failure is detected.

0: CSS on HSE OFF (clock detector OFF) (default after reset)

1: CSS on HSE ON (clock detector ON if the HSE oscillator is stable, OFF if not).

Bit 18 HSEBYP : HSE clock bypass

Set and cleared by software to bypass the oscillator with an external clock. The external clock must be enabled with the HSEON bit to be used by the device.

The HSEBYP bit can be written only if the HSE oscillator is disabled.

0: HSE oscillator not bypassed (default after reset)

1: HSE oscillator bypassed with an external clock

Bit 17 HSERDY : HSE clock ready flag

Set by hardware to indicate that the HSE oscillator is stable.

0: HSE clock is not ready (default after reset)

1: HSE clock is ready

Bit 16 HSEON : HSE clock enable

Set and cleared by software.

Cleared by hardware to stop the HSE when entering Stop or Standby mode.

This bit cannot be cleared if the HSE is used directly (via SW mux) as system clock, or if the HSE is selected as reference clock for PLL1 with PLL1 enabled (PLL1ON bit set to 1).

0: HSE is OFF (default after reset)

1: HSE is ON

Bits 15:14 Reserved, must be kept at reset value.

Bit 13 HSI48RDY : HSI48 clock ready flag

Set by hardware to indicate that the HSI48 oscillator is stable.

0: HSI48 clock is not ready (default after reset)

1: HSI48 clock is ready

Bit 12 HSI48ON : HSI48 clock enable

Set by software and cleared by software or by the hardware when the system enters to Stop or Standby mode.

0: HSI48 is OFF (default after reset)

1: HSI48 is ON

Bit 11 Reserved, must be kept at reset value.

Bit 10 CSIKERON : CSI clock enable in Stop mode

Set and reset by software to force the CSI to ON, even in Stop mode, to be quickly available as kernel clock for some peripherals. This bit has no effect on the value of CSION.

0: no effect on CSI (default after reset)

1: CSI is forced to ON even in Stop mode

Bit 9 CSIRDY: CSI clock ready flagSet by hardware to indicate that the CSI oscillator is stable. This bit is activated only if the RC is enabled by CSION (it is not activated if the CSI is enabled by CSIKERON or by a peripheral request).

0: CSI clock is not ready (default after reset)

1: CSI clock is ready

Bit 8 CSION: CSI clock enableSet and reset by software to enable/disable CSI clock for system and/or peripheral.

Set by hardware to force the CSI to ON when the system leaves Stop mode, if STOPWUCK = 1 or STOPKERWUCK = 1.

This bit cannot be cleared if the CSI is used directly (via SW mux) as system clock, or if the CSI is selected as reference clock for PLL1 with PLL1 enabled (PLL1ON bit set to 1).

0: CSI is OFF (default after reset)

1: CSI is ON

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 HSIDIVF: HSI divider flagSet and reset by hardware.

As a write operation to HSIDIV has not an immediate effect on the frequency, this flag indicates the

current status of the HSI divider. HSIDIVF goes immediately to 0 when HSIDIV value is changed, and is set back to 1 when the output frequency matches the value programmed into HSIDIV.

0: new division ratio not yet propagated to hsi_ck, hsi_ker_ck (default after reset)

1: hsi_ck, hsi_ker_ck clock frequency reflects the new HSIDIV value (default register value when the clock setting is completed).

Bits 4:3 HSIDIV[1:0]: HSI clock dividerSet and reset by software.

These bits allow selecting a division ratio to configure the wanted HSI clock frequency. The HSIDIV cannot be changed if the HSI is selected as reference clock for at least one enabled PLL (PLLxON bit set to 1). In that case, the new HSIDIV value is ignored.

00: division by 1, hsi_ck, hsi_ker_ck = 64 MHz

01: division by 2, hsi_ck, hsi_ker_ck = 32 MHz (default after reset)

10: division by 4, hsi_ck, hsi_ker_ck = 16 MHz

11: division by 8, hsi_ck, hsi_ker_ck = 8 MHz

Bit 2 HSIKERON: HSI clock enable in Stop modeSet and reset by software to force the HSI to ON, even in Stop mode, to be quickly available as kernel clock for peripherals. This bit has no effect on the value of HSION.

0: no effect on HSI (default after reset)

1: HSI is forced to ON even in Stop mode

Bit 1 HSIRDY: HSI clock ready flagSet by hardware to indicate that the HSI oscillator is stable.

0: HSI clock is not ready (default after reset)

1: HSI clock is ready

Bit 0 HSION : HSI clock enable

Set and cleared by software.

Set by hardware to force the HSI to ON when the product leaves Stop mode, if STOPWUCK = 1 or STOPKERWUCK = 1.

Set by hardware to force the HSI to ON when the product leaves Standby mode or in case of a failure of the HSE which is used as the system clock source.

This bit cannot be cleared if the HSI is used directly (via SW mux) as system clock, or if the HSI is selected as reference clock for PLL1 with PLL1 enabled (PLL1ON bit set to 1).

0: HSI is OFF

1: HSI is ON (default after reset)

11.8.2 RCC HSI calibration register (RCC_HSICFGR)

Address offset: 0x010

Reset value: 0x0040 0XXX

Reset value depends on the flash memory option bytes setting.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | HSITRIM[6:0] | ||||||

| rw | rw | rw | rw | rw | rw | rw | |||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | HSICAL[11:0] | |||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | ||||

Bits 31:23 Reserved, must be kept at reset value.

Bits 22:16 HSITRIM[6:0] : HSI clock trimming

Set by software to adjust calibration.

HSITRIM field is added to the engineering option bytes loaded during reset phase (FLASH_HSI_OPT) to form the calibration trimming value.

HSICAL = HSITRIM + FLASH_HSI_OPT.

After a change of HSITRIM it takes one system clock cycle before the new HSITRIM value is updated

Note: The reset value of the field is 0x40.

Bits 15:12 Reserved, must be kept at reset value.

Bits 11:0 HSICAL[11:0] : HSI clock calibration

Set by hardware by option byte loading during system reset. Adjusted by software through trimming bits HSITRIM.

This field represents the sum of engineering option byte calibration and HSITRIM bits values.

11.8.3 RCC clock recovery RC register (RCC_CRRRCR)

Address offset: 0x014

Reset value: 0x0000 0XXX

Reset value depends on the flash option bytes setting