7. Embedded flash memory (FLASH)

7.1 Introduction

The embedded flash memory (FLASH) manages the accesses of any master to the up to 2 Mbytes of embedded nonvolatile memory. It implements read, program, and erase operations, error corrections, as well as various integrity and confidentiality protection mechanisms.

FLASH manages the automatic loading of nonvolatile user option bytes at power-on reset, and implements the dynamic update of these options. It also features a high-cycle data area, a one-time-programmable (OTP) area, a secure key storage area (OBKeys), and a read-only area configured by STMicroelectronics during manufacturing.

7.2 FLASH main features

- • Up to 2 Mbytes of nonvolatile memory, divided into two 1-Mbyte banks

- • Flash memory read operations supporting multiple lengths: 128 bits, 64 bits, 32 bits, 16 bits, or one byte

- • Flash memory programming by 128 (user area, OBKeys) and by 16 bits (OTP and flash high-cycle data area)

- • 8-Kbyte sector erase, bank erase and dual-bank mass erase

- • Dual-bank organization supporting:

- – Simultaneous operations: read-while-write (program and erase) is supported, including flash high-cycle data area. The two banks share the same interface, hence write and erase cannot be performed in parallel (write-while-write is not supported).

- – Bank swapping: the address mapping of the user memory of each bank can be swapped, along with the corresponding registers. Security flags remain valid for the physical bank, so the data are not revealed by swapping to a bank with lower security configuration.

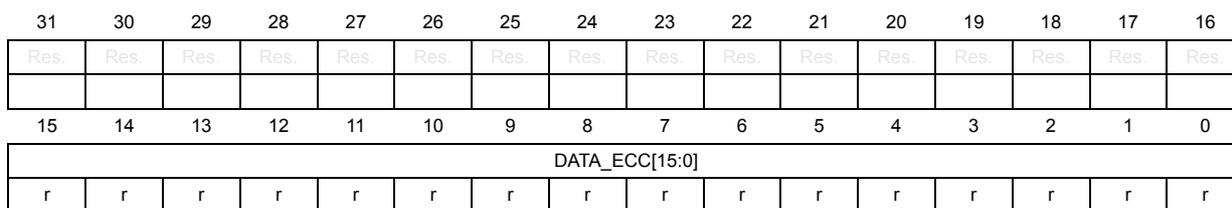

- • Error code correction (ECC): one error detection/correction, or two errors detection per 128-bit flash word using nine ECC bits, on 16-bit words with six bits within configurable flash high-cycle data area.

- • User configurable nonvolatile option bytes

- • Flash memory enhanced protections, activated by option bytes

- – different product states for protecting memory content from debug access

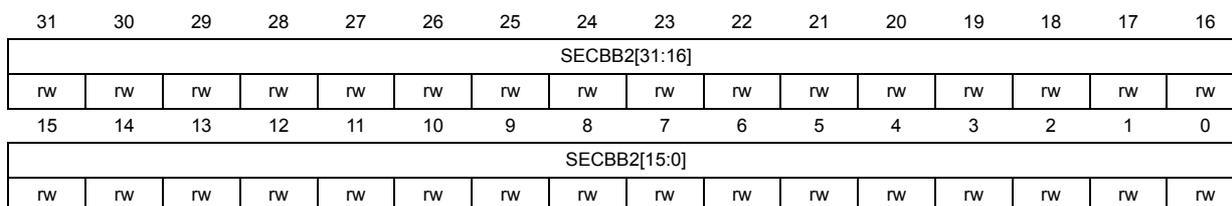

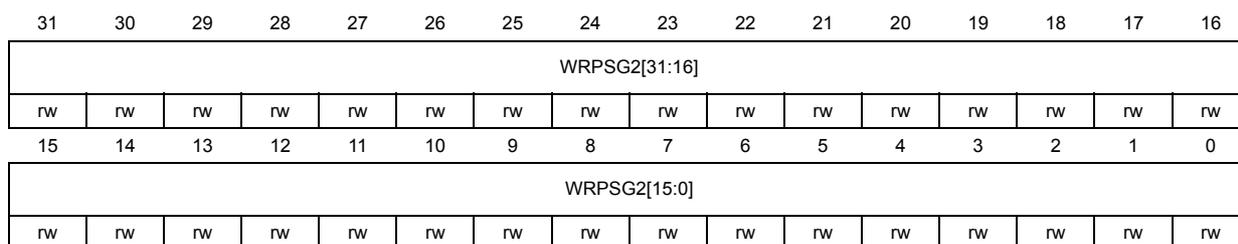

- – sector group write-protection (WRPSG), protecting up to 32 groups of four sectors (32 Kbytes) per bank

- – two secure-only areas (one per user flash bank): when enabled, these areas are accessible only if the microcontroller operates in Secure access mode

- – HDP protection, providing temporal isolation for startup code

- • 2-Kbyte one-time programmable (OTP) area

- • Read-only area configured by STMicroelectronics

- • Prefetch reads the next sequential instruction from flash memory

- • Up to 48 Kbytes per bank supporting high-cycling capability (100 kcycles), to be used for data (EEPROM emulation)

7.3 FLASH functional description

7.3.1 FLASH block diagram

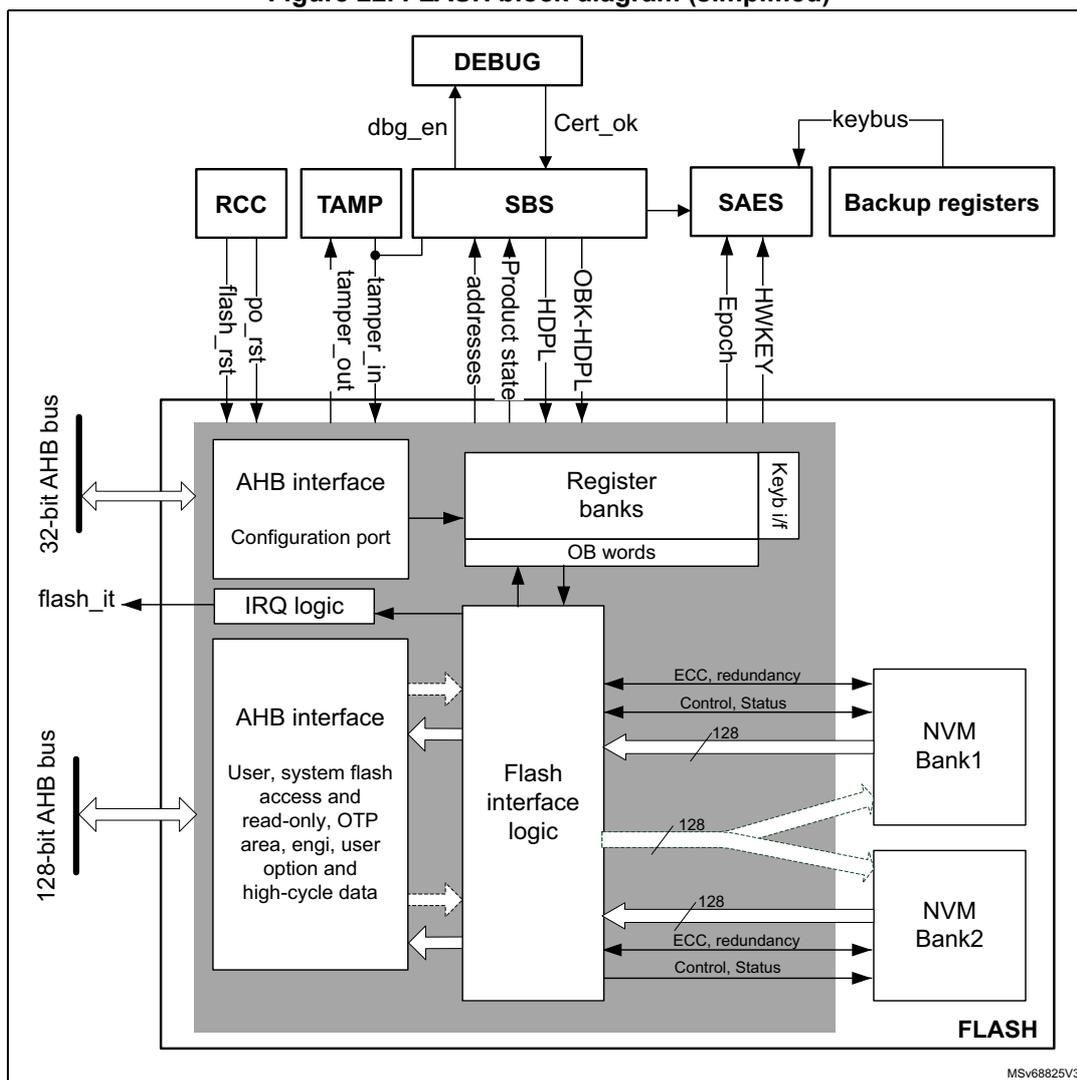

Figure 22 shows the embedded flash memory block diagram.

Figure 22. FLASH block diagram (simplified)

This block diagram illustrates the internal architecture of the FLASH memory system. At the top, a

DEBUG

block connects to the

SBS

(System Bus Security) block via

dbg_en

and

Cert_ok

signals. The

SBS

block is central, receiving

addresses

,

Product state

,

HDPL

, and

OBK-HDPL

. It interfaces with

RCC

(Reset and Clock Control) via

po_rst

and

flash_rst

, and with

TAMP

(Tamper) via

tamper_in

and

tamper_out

. The

SAES

(Secure AES) block receives

keybus

from

Backup registers

and provides

Epoch

and

HWKEY

to the

SBS

.

The main FLASH block contains two AHB interfaces. A

32-bit AHB bus

connects to an

AHB interface

for the

Configuration port

, which leads to

Register banks

(including

OB words

) and a

Keyb i/f

. A

128-bit AHB bus

connects to another

AHB interface

for

User, system flash access and read-only, OTP area, engi, user option and high-cycle data

. Both interfaces connect to the

Flash interface logic

. The

IRQ logic

outputs a

flash_it

signal.

The

Flash interface logic

manages two memory banks:

NVM Bank1

and

NVM Bank2

. Each bank is connected via a

128

-bit data bus and control lines for

ECC, redundancy

and

Control, Status

. The entire system is labeled

FLASH

at the bottom right.

7.3.2 FLASH signals

The flash memory has two AHB connections, namely the flash AHB register interface and the main AHB interface.

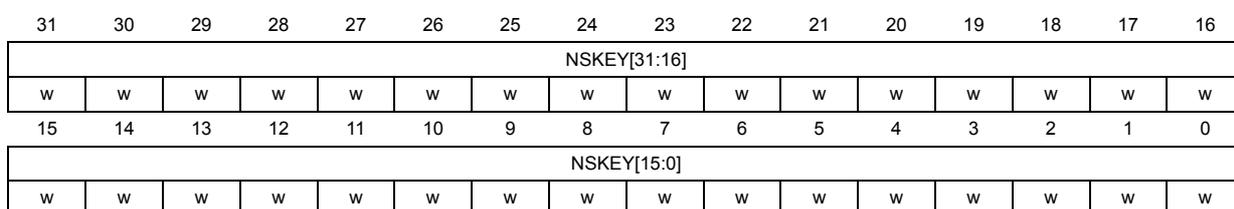

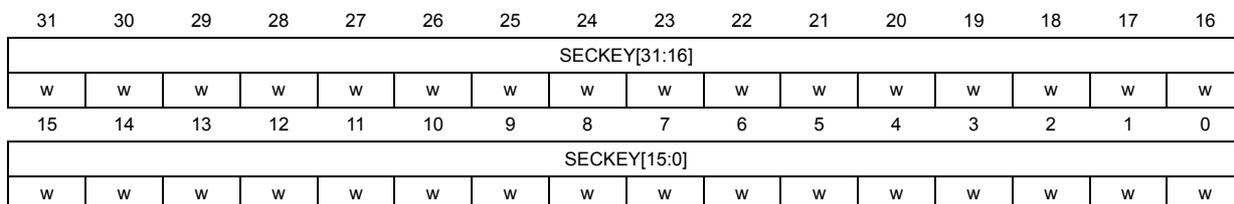

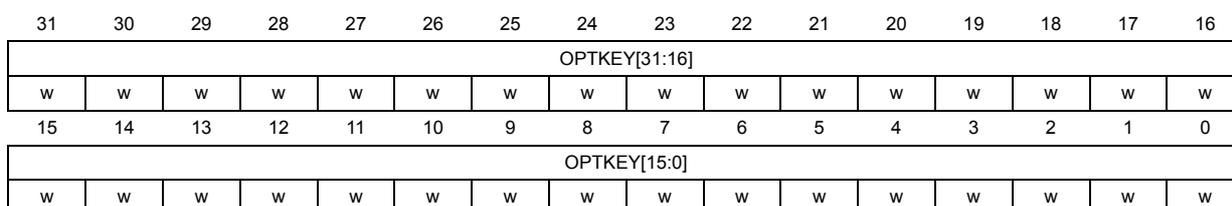

Flash AHB register interface

- • Data size is 32 bits

- • Except for some registers (FLASH_NS/SECKEYR, FLASH_NS/SECOBKKEYR and FLASH_OPTKEYR, used to insert unlock sequences for control, and option registers that can be written by 32 bits), it is possible to read and write all registers by 8, 16 and 32 bits.

- • When unlock sequence for control and option registers is wrong, a bus error is raised, otherwise no read or write errors are generated on the bus.

Main AHB interface

The AHB data bus size is 128 bits. This interface is used to handle three different targets:

- • Code placed in user and system memory, protected by 9 bits of ECC.

- • Secure keys placed in OBKey sectors, protected by 9 bits of ECC.

- • OTP, read-only and flash memory high-cycle data area, protected by 6 bits of ECC.

The main AHB interface is implemented as follows:

- • User and system memory, OBKeys storage:

- – Supports multiple length: 128-, 64-, 32-, 16- and 8-bit data width.

- – There is a read buffer of 128 bits for each bank where the last data read is stored. If data are available in the read buffer, no read access is given to the flash memory. Buffer is flushed when write access, OTP access, OBK swap, OBK alternate sector erase, high-cycle data area access, user option change request or erase operation occur.

- – There is a prefetch of the same size as the read buffer.

- – A 9-bit ECC is associated to each 128-bit data flash memory word.

- • OTP, read-only and flash high-cycle data

- – Two dedicated data buffer of 137 bits are used to manage 16-bit data with 6-bit ECC

- – Reading two times the same address triggers two flash read accesses.

- – During a read access, two wait states are added in addition to the memory wait states. These wait states are necessary to parse the data buffer.

- – Each write access triggers a write in the flash memory.

- – 6-bit ECC is associated to each 16-bit data.

By default, all the AHB memory range is cacheable. For regions where caching is not practical (OTP, RO, data area), MPU must be used to disable local cacheability.

7.3.3 Flash memory architecture and usage

Flash memory architecture

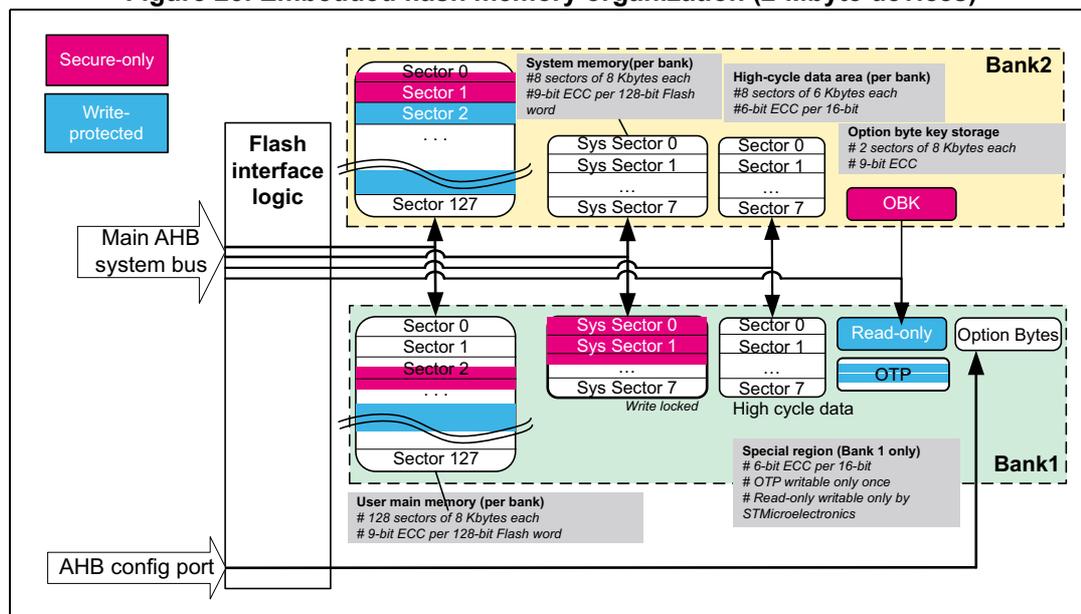

Figure 23 shows the organization supported by the embedded flash memory. By default, all the AHB memory range is cacheable. For regions where caching is unpractical (OTP, read-only, data) use MPU to disable local cacheability.

Figure 23. Embedded flash memory organization (2-Mbyte devices)

The diagram illustrates the internal organization of a 2-Mbyte embedded flash memory device. It is divided into two banks, Bank1 and Bank2, each containing different types of memory sectors. Bank1 includes user main memory (128 sectors of 8 Kbytes), system memory (8 sectors of 8 Kbytes), high-cycle data area (8 sectors of 6 Kbytes), and option byte key storage (2 sectors of 8 Kbytes). Bank2 includes user main memory (128 sectors of 8 Kbytes), system memory (8 sectors of 8 Kbytes), high-cycle data area (8 sectors of 6 Kbytes), and option bytes. The diagram also shows the Flash interface logic, Main AHB system bus, and AHB config port. Special regions like Read-only, OTP, and OBK are also indicated.

The embedded flash nonvolatile memory is composed of:

- • A main memory block, organized in two banks. Each bank is divided in sectors of 8 Kbytes each, and features flash-word rows of 128 bits + 9 bits of ECC per word (see Table 48 ).

- • A system memory block of 128 Kbytes, divided into two 64-Kbyte banks. Each bank is divided in eight 8-Kbyte sectors. The system flash memory is ECC protected (9-bit ECC per 128-bit word).

- • A set of nonvolatile option bytes loaded at reset by the embedded flash memory and accessible by the application software only through the AHB configuration register interface.

- • A 2-Kbyte one-time-programmable (OTP) area that can be written only once by the application software.

- • A 2-Kbyte read-only area. It contains a unique device ID and product information.

- • Two memory sectors (2 x 8 Kbytes) of secure key storage, OBKeys.

- • Up to 16 sectors of user flash memory with high cycling capability (100 K cycles) for data, 8 sectors per bank.

The overall flash memory architecture and its corresponding access interface is summarized in Table 48 .

Partition usage

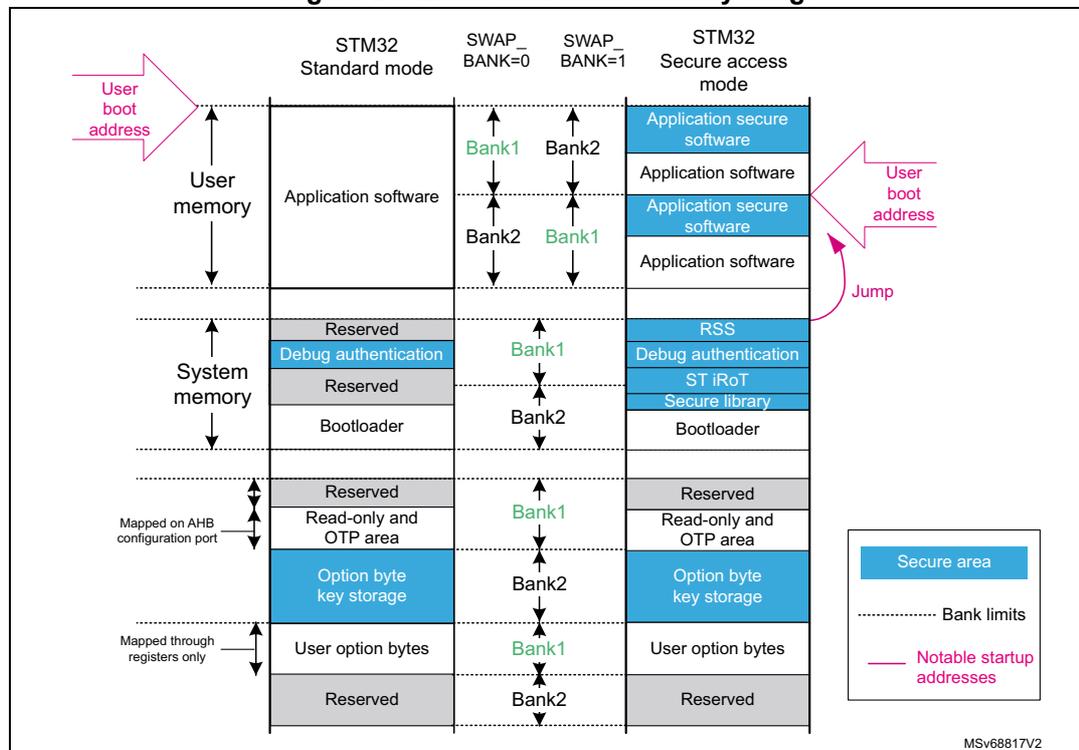

Figure 24 shows how the embedded flash memory is used by STMicroelectronics and by the application software.

Figure 24. Embedded flash memory usage

The diagram illustrates the memory layout for different STM32 modes. The columns represent: STM32 Standard mode, SWAP_BANK=0, SWAP_BANK=1, and STM32 Secure access mode. The rows represent different memory sections: User memory (Application software, Reserved, Debug authentication, Reserved, Bootloader, Reserved, Read-only and OTP area, Option byte key storage, User option bytes, Reserved), System memory (Application secure software, Application software, RSS, Debug authentication, ST iRoT, Secure library, Bootloader), and Mapped on AHB configuration port (Reserved, Read-only and OTP area, Option byte key storage, User option bytes, Reserved). The diagram also shows Bank1 and Bank2 labels, a 'Jump' arrow, and a legend for Secure area, Bank limits, and Notable startup addresses. The code MSV68817V2 is visible in the bottom right corner.

User and system memories are used differently, according to product state and other option bytes settings:

- • The user memory contains the application code and data, while the system memory is used with root secure services (RSS), the debug authentication code, and the STM32 bootloader. When a reset occurs, the core jumps to the boot address configured through the BOOT pin, the (SEC/NS)BOOTADD option bytes, and the product state.

- • The unique boot entry (BOOT_UBE) is set to either ST iRoT located in the system flash memory, or iRoT in the user flash memory. This feature is available only on cryptography enabled devices.

- • Secure service library in system flash memory is available in secure mode.

- • If the debugger is attached to the product, the entry point is the debug authentication policy, used to unlock the device via the SBS when attached to debugger. A digital signature must be provided to perform a regression to product state, where debug is allowed.

- • If (SEC/NS)BOOTADD is not yet configured, dedicated libraries can be used for secure boot. They are located in the system flash memory:

- – ST libraries in system flash memory assist the application software boot with special features, such as secure boot and secure firmware install (SFI-RSS)

- – ST iROT (immutable root of trust) secure software in user flash memory is used for secure firmware update and provisioning (SFU)

Note: For more information on option byte setup for boot, refer to Section 7.4.6 .

7.3.4 FLASH read operations

Read operation overview

Read access to main and system flash memory operates as follows:

- • There is a 128-bit read data buffer associated to each bank, which stores the last data read. If several consecutive read accesses request data belonging to the same flash data word (128 bits), data are read directly from the current data read buffer, without triggering additional flash read operations. This mechanism occurs each time a read access is granted. When a read access is rejected for security reasons, the corresponding read error response is issued by the embedded flash memory and no read operation to flash memory is triggered.

- • The read data buffer is disabled when write access or OTP access, user option change request, OBK swap, OBK erase or other erase operation occur.

Read access to OTP, RO and flash high-cycle data operates as follows:

- 1. Flash data word of 137 bits is read and stored in a temporary buffer.

- 2. The interface parses the 137-bit data word, and selects the 16- or 32-bit data requested.

- 3. While parsing the 137-bit data word, (two) wait states are added, and the AHB bus is stalled.

- 4. If the application reads an OTP data or flash high-cycle data not previously written, a double ECC error is reported and only a word full of set bits is returned (see Section 7.3.9 for details). The read data (in 16 bits) is stored in FLASH_ECCDR register, so that the user can identify if the double ECC error is due to a virgin data or a real ECC error.

- 5. Reading two times the same address triggers two reads in the flash memory.

- 6. For 8-bit accesses, an AHB bus error is generated.

Note: The embedded flash memory can perform single-error correction and double-error detection while read operations are being executed (see Section 7.3.8 ).

Instruction prefetch

The Cortex-M33 fetches instructions and literal pools (constants/data) over the C-Bus and through the instruction cache, if it is enabled. The prefetch block aims at increasing the efficiency of C-Bus accesses when the instruction cache is enabled, by reducing the cache refill latency.

Prefetch is efficient in case of sequential code; prefetch in the flash memory allows the next sequential instruction line to be read from the memory, while the current instruction line is being filled in instruction cache and executed by the CPU.

Prefetch is enabled by setting the PRFTEN bit in the FLASH access control register (FLASH_ACR). PRFTEN must be set only if at least one wait state is needed to access the flash memory.

Adjusting read timing constraints

The embedded clock must be enabled and running before reading data from a nonvolatile memory.

To correctly read data from the memory, the number of wait states (LATENCY) must be correctly programmed in the access control register (FLASH_ACR), according to the main AHB interface clock frequency, and the internal voltage range of the device ( \( V_{core} \) ).

Table 45 shows the correspondence between the number of wait states (LATENCY), the programming delay parameter (WRHIGHFREQ), the embedded flash memory clock frequency, and the supply voltage range.

Table 45. Recommended number of wait states and programming delay

| Number of wait states (LATENCY) | Programming delay (WRHIGHFREQ) | Interface clock frequency vs. \( V_{CORE} \) range (1) | |||

|---|---|---|---|---|---|

| VOS3 range 0.95 to 1.05 V | VOS2 range 1.05 to 1.15 V | VOS1 range 1.15 to 1.26 V | VOS0 range 1.30 to 1.40 V | ||

| 0 WS (1 FLASH clock cycle) | 00 | 0 to 20 MHz | 0 to 30 MHz | 0 to 34 MHz | 0 to 42 MHz |

| 1 WS (2 FLASH clock cycles) | 20 to 40 MHz | 30 to 60 MHz | 34 to 68 MHz | 42 to 84 MHz | |

| 2 WS (3 FLASH clock cycles) | 01 | 40 to 60 MHz | 60 to 90 MHz | 68 to 102 MHz | 84 to 126 MHz |

| 3 WS (4 FLASH clock cycles) | 60 to 80 MHz | 90 to 120 MHz | 102 to 136 MHz | 126 to 168 MHz | |

| 4 WS (5 FLASH clock cycles) | 10 | 80 to 100 MHz | 120 to 150 MHz | 136 to 170 MHz | 168 to 210 MHz |

| 5 WS (6 FLASH clock cycles) | N/A | N/A | 170 to 200 MHz | 210 to 250 MHz | |

1. Voltage range from 1.26 to 1.30 V is not supported.

Adjusting system frequency

After power-on, the embedded flash memory is clocked by the 64 MHz high-speed internal oscillator (HSI), with a voltage range set at a scaled value of VOS3: a conservative 3 wait-state latency is specified in FLASH_ACR register (see Table 45 ).

When changing the bus frequency, the application software must follow the sequence described below, to tune the number of wait states required to access the memory.

To increase the CPU frequency:

- 1. If necessary, program the LATENCY and WRHIGHFREQ bits to the right value in the FLASH_ACR register, as described in Table 45 .

- 2. Check that the new number of wait states is taken into account by reading back the FLASH_ACR register.

- 3. Modify the embedded flash memory clock source and/or the clock prescaler in the RCC_CFGR register of the reset and clock controller (RCC).

- 4. Check that the new embedded flash memory clock source and/or the new AHB clock prescaler value are taken in account by reading back the embedded flash memory clock source status and/or the prescaler value in the RCC_CFGR register of the reset and clock controller (RCC).

To decrease the CPU frequency:

- 1. Modify the embedded flash memory clock source and/or the clock prescaler in the RCC_CFGR register of reset and clock controller (RCC).

- 2. Check that the embedded flash memory new clock source and/or the new clock prescaler value are taken into account by reading back the embedded flash memory clock source status and/or the AHB interface prescaler value in the RCC_CFGR register of reset and clock controller (RCC).

- 3. If necessary, program the LATENCY and WRHIGHFREQ bits to the right value in FLASH_ACR register, as described in Table 45 .

- 4. Check that the new number of wait states has been taken into account by reading back the FLASH_ACR register.

Error code correction (ECC)

The memory embeds an error correction mechanism. Single-error correction and double-error detection are performed for each read operation. For more details, refer to Section 7.3.8 .

Read errors

When the ECC mechanism is unable to correct the read operation, the memory reports read errors, as described in Section 7.9.10 .

Read interrupts

See Section 7.10 for details.

7.3.5 FLASH program operations

Program operation overview

Program operation consists in issuing write commands. The memory supports the execution of only one write-command at a time. Write-while-write is not supported. Nothing prevents overwriting a non-virgin flash word, but this is not recommended. The result may lead to invalid data and inconsistent ECC code.

User flash, OBK storage and system flash memories sectors

For the user and system flash memories, 9-bit ECC is associated to each 128-bit data flash word. In this case, the embedded flash memory must always perform write operations to nonvolatile memory with a 128-bit word granularity. Once the write buffer is full (128 bits), the Busy flag is set, and a programming operation is triggered.

There is a write buffer common to Bank1 and 2, which supports multiple write-access types (128, 64, 32, 16 or 8 bits). The application can decide to write from 8 bits to 128 words. In this case, a force-write mechanism to the 128 bits + ECC is used (see FW bit of FLASH_NS/SECCR register).

When the write request is issued to the memory, any new write request stalls the main AHB bus. Moreover, while a write operation is ongoing, any new read request to the same bank stalls the main AHB bus.

OTP, RO, flash high-cycle data

When the target memory is OTP, RO and flash high-cycle data sectors, 6-bits ECC code is associated to each 16-bit data flash word. The embedded flash memory supports 16- or 32-bit write operations (8-bit write operations are not supported). For 8-bit accesses, write accesses are ignored. There is no write data buffer. Each write access triggers a write in the flash memory.

Note: The OTP area is typically write-protected on the final product, as described in Section 7.3.9 .

The write protection check is performed at the reception of the write request (during address phase). Write protection is not checked anymore at the output of the write buffer. If a write protection violation is detected, the write operation is canceled, and write protection error (WRPERR) is raised in FLASH_NS/SECSR register.

Note: For write protections of main flash, ICP, and OTP see Section 7.6 .

Monitoring ongoing write operations

The application software can use a status flag located in FLASH_NS/SECSR to monitor ongoing write operations. Since only one operation is possible at a time, this flag indicates if any operation (write, erase, option change) is ongoing, whatever the bank.

- •

BSY

: indicates that an effective write, erase, option byte change, OBK swap, OBK alt sector erase is ongoing in the nonvolatile memory. This flag is not dedicated to a specific bank. It is set when an operation is starting on the memory, whatever the bank. An operation is triggered by:

- – An erase (FLASH_NS/SECCR.STRT)

- – A write (FLASH_NS/SECCR.PG + AHB write)

- – An option modification (FLASH_OPTCR.OPTSTRT)

- – OBKeys sector swap and OBKeys sector erase (FLASH_NS/SECOBKCFGR.SWAP_SECT_REQ and FLASH_NS/SECOBKCFGR.ALT_SECT_ERASE)

They are cleared when the current operation ends, or in case of error.

- • WBNE : this bit indicates that the embedded flash memory is waiting for new data to complete the 128-bit write buffer. In this state the write buffer is not empty. It is reset as soon as the application software fills the write buffer, or forces the writes by using FW bit in FLASH_NS/SECCR, or an error is detected. When WBNE is high, it is not possible to launch an erase, an option modification, an OBK swap or OBK alternate sector erase operation on flash memory.

- •

DBNE

: this bit indicates that the data buffer for parsing 16-bits data is not empty:

- – 16-bit data write access is received, and the data buffer is being filled. It is set at the receipt of a valid write access, and reset as soon as the write request preparation has been processed.

Note: If the memory is busy at the receipt of the AHB write request, the CPU execution is stalled.

Enabling write operations

Before programming the user flash memory in Bank1 or in Bank2, the application software must ensure that the PG bit is set to 1 in FLASH_NS/SECCR. If not, an unlock sequence must be used (see Section 7.6.7 ), and the PG bit must be set.

When an option byte or an option byte key must be modified, or a mass erase must be started, the application software must ensure that FLASH_OPTCR is unlocked. If this is not the case, an unlock sequence must be used (see Section 7.6.7 ).

A separate mechanism with similar use exists for FLASH_NS/SECOBKCFGR. The control register must be unlocked prior to the start of any OBKeys storage modification. Writing the correct sequence to the FLASH_NSOBKKEYR unlocks FLASH_NSOBKCFGR. FLASH_SECOBKKEYR is linked to FLASH_SECOBKCFGR, as described in Section 7.6.7 .

Note: The application software must not unlock an already unlocked register, otherwise this register remains locked until the next system reset.

If needed, the application software can update the programming delay, as described in Adjusting programming timing constraints .

Writing to the FLASH control register FLASH_NS/SECCR and FLASH_OPTCR

The FLASH_NS/SECCR, FLASH_OPTCR and FLASH_NS/SECOBKCFGR registers are not accessible in write mode when the BSY bit is set. Any attempt to write these registers while the BSY bits is set causes the AHB bus to stall until SEC/NSBSY bit is cleared.

Single-write sequence

The recommended single-write sequence is the following:

- 1. Make sure protection mechanism does not prevent programming

- 2. Check that no memory operations are ongoing by checking the BSY bit in the FLASH_NS/SECSR register and CDBNE bits in the FLASH_NS/SECSR register. Check that the write buffer is empty by checking the WBNE bit in the FLASH_NS/SECSR register

- 3. Check and clear all the error flags due to previous programming/erase operation

- 4. Unlock the FLASH_NS/SECCR register, as described in Section 7.6.7 (only if this register is not already unlocked)

- 5. Enable write operations by setting PG bit in the FLASH_NS/SECCR register

- 6. Write one flash-word at aligned address

Note: NS/SECWBNE flag indicates if the 128-bit write buffer is waiting for new data.

Note: No erase request, options change request, OBK operation is allowed between the first write and the completion of the write operation.

- 7. Wait for the BSY bit to be cleared in the corresponding FLASH_NS/SECSR register

- 8. Clear PG bit in FLASH_NS/SECCR register if there are not any more programming requests

If step 6 is executed incrementally (for example byte per byte), the write buffer can become partially filled. In this case the application software can decide to force-write what is stored in the write buffer by using FW bit in FLASH_NS/SECCR register. In this particular case, the unwritten bits are automatically set to 1. If no bit in the write buffer is cleared to 0, the FW bit has no effect.

Note: The usage of a force-write operation prevents the application from updating, in a later stage, the missing bits with a value different from 1. This can lead to unexpected or inconsistent data, or ECC.

Adjusting programming timing constraints

Program operation timing constraints depend of the memory clock frequency, which directly impacts the performance. If timing constraints are too tight, the nonvolatile memory does not operate correctly, if they are too lax, the programming speed is not optimal.

The user must therefore trim the optimal programming delay through the WRHIGHFREQ parameter in the FLASH_ACR register. Refer to Table 45 for the recommended programming delay, depending upon the memory clock frequency.

FLASH_ACR configuration register is common to both banks.

The application software must check that no program/erase operation is ongoing before modifying WRHIGHFREQ.

Caution: Modifying WRHIGHFREQ while programming/erasing the memory can corrupt its content.

Programming errors

When a program operation fails, an error is reported, as described in Section 7.9 .

Programming interrupts

See Section 7.10: FLASH interrupts for details.

7.3.6 FLASH erase operations

Erase operation overview

The memory can perform erase operations on 8-Kbyte user sectors, on one user flash memory bank, or on two user flash memory banks (for example mass erase). For more details in user flash memory, ICP, user options and OTP erase protection, see Section 7.6 .

Erase commands are issued through the AHB configuration interface. The memory supports one operation at a time, if it receives simultaneously a write and an erase request an error flag is raised, and both operations are canceled. See Section 7.9 for details.

After successful completion of erase, all the bytes in the erased flash sectors are set to the flash default 0xFF value.

Erase and WRP

If the application software attempts to erase a write-protected user sector, the sector erase operation is aborted, and the WRPERR flag is raised in the FLASH_NS/SECSR register, as described in Section 7.9.2 .

Flash busy

Busy signals is described in Monitoring ongoing write operations .

Writing to the FLASH control register FLASH_NS/SECCR and FLASH_OPTCR

Refer to Writing to the FLASH control register FLASH_NS/SECCR and FLASH_OPTCR .

Enabling erase operations

Before erasing a sector, the application software must make sure that FLASH_NS/SECCR is unlocked. If this is not the case, an unlock sequence must be used (see Section 7.6.7 ).

Note: The application software must not unlock a register that is already unlocked, otherwise this register remains locked until next system reset. This can be used to deliberately lock-out a register from further accesses.

Similar constraints apply to bank erase requests.

Standard flash sector erase sequence

To erase an 8- or 6-Kbyte data user sector without security protections, proceed as follows:

- 1. Make sure protection mechanism does not prevent sector erase (WRP, secure flag, HDP).

- 2. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_NSSR register, and that the write buffer is empty by checking the WBNE bit in the FLASH_NSSR register.

- 3. Check and clear all the non-secure error flags due to previous programming/erase operation. Refer to Section 7.9 for details.

- 4. Unlock the FLASH_NSCR register, as described in Section 7.6.7 (only if this register is not already unlocked).

- 5. Set the BKSEL bit, the SER bit and SNB bitfield in the FLASH_NSCR register. BKSEL indicates in which physical bank sector must be erased, then SER indicates a sector erase operation, while SNB contains the target sector number. In case of data sector, use the number of the corresponding regular sector.

- 6. Set the STRT bit in the FLASH_NSCR register.

- 7. Wait for the BSY bit to be cleared in the FLASH_NSSR register.

- 8. STRT bit is automatically cleared at the end of the sector erase, or in case of error.

- 9. Clear SER in FLASH_NSCR register if there are not anymore sector erase request to be issued.

Note: If another erase flag is requested simultaneously to the sector erase, a PGSERR error is generated.

Secure flash memory sector erase sequence

To erase an 8- or 6-Kbyte data secure configured user sector, proceed as follows:

- 1. Make sure write protection or HDP mechanism does not prevent sector erase.

- 2. Ensure that no memory operations are ongoing (by checking the BSY and DBNE bits in the FLASH_SECSR register), and that the write buffer is empty (by checking the WBNE bit in the FLASH_SECSR register).

- 3. Check and clear all the secure error flags due to previous programming/erase operations. Refer to Section 7.9 for details.

- 4. Unlock the FLASH_SECCR register, as described in Section 7.6.7 (only if this register is not already unlocked).

- 5. Set the BKSEL bit, the SER bit and SNB bitfield in the FLASH_SECCR register. BKSEL indicates in which physical bank sector must be erased, then SER indicates a sector erase operation, while SNB contains the target secure sector number. In case of data sector, use the number of the corresponding regular sector.

- 6. Set the STRT bit in the FLASH_SECCR register.

- 7. Wait for the BSY bit to be cleared in the FLASH_SECSR register.

- 8. STRT bit is automatically cleared at the end of the sector erase or in case of error.

- 9. Clear SER in FLASH_SECCR register if there are not any secure sector erase request to be issued.

Note: If another erase flag is requested simultaneously to the sector erase, a PGSERR error is generated.

Standard flash memory bank erase sequence

To erase bank where no sector is configured as secure:

- 1. Make sure protection mechanism does not prevent sector erase.

- 2. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_NSSR register and that the write buffer is empty by checking the WBNE bit in the same register.

- 3. Check and clear all the non-secure error flags due to previous programming/erase operation. Refer to Section 7.9 for details.

- 4. Unlock the FLASH_NSCR register, as described in Section 7.6.7 (only if this register is not already unlocked).

- 5. Set the BKSEL bit and the BER bit in the FLASH_NSCR register to the targeted physical bank (swap setting is ignored).

- 6. Set the STRT bit in the FLASH_NSCR register to start the bank erase operation. Then wait until the BSY bit is cleared in the FLASH_NSSR register.

- 7. STRT bit is automatically cleared at the end of erase sequence or in case of error.

- 8. Clear BER in FLASH_NSCR register if there is not other bank erase request to be issued.

Secure flash memory bank erase sequence

To erase bank where all sectors are configured with secure flag:

- 1. Make sure protection mechanism does not prevent sector erase (for mass erase the HDP is also considered, it cannot be fully executed from HDPL= 2, 3 if HDP is defined).

- 2. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_SECSR register and that the write buffer is empty by checking the WBNE bit in the same register.

- 3. Check and clear all the secure error flags due to previous programming/erase operation. Refer to Section 7.9 for details.

- 4. Unlock the FLASH_SECCR register, as described in Section 7.6.7 (only if this register is not already unlocked).

- 5. Set the BKSEL bit and the BER bit in the FLASH_SECCR register to the targeted physical bank (swap setting is ignored).

- 6. Set the STRT bit in the FLASH_SECCR register to start the bank erase operation. Then wait until the BSY bit is cleared in the FLASH_SECSR register.

- 7. STRT bit is automatically cleared at the end of erase sequence or in case of error.

- 8. Clear BER in FLASH_SECCR register if there is not other bank erase request to be issued.

Flash mass erase sequence

To erase all sectors of both banks, using non-secure access, all sectors must be configured as non-secure. The application software can set the MER bit to 1 in FLASH_NSCR register, as described below:

- 1. Make sure protection mechanisms do not prevent mass erase ( Section 7.6 ).

- 2. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_NSSR register and that the write buffer is empty by checking the WBNE bit in the FLASH_NSSR register.

- 3. Check and clear all the non-secure error flags due to previous programming/erase operation. Refer to Section 7.9 for details.

- 4. Unlock the FLASH_NSCR register as described in Section 7.6.7 (only if the registers are not already unlocked).

- 5. Set the MER bit to 1 in FLASH_NSCR register.

- 6. Set the STRT bit in the FLASH_NSCR register. Then wait until BSY bit is cleared in the FLASH_NSSR register.

- 7. STRT bit is cleared automatically at the end of the erase sequence, or in case of error.

- 8. Clear MER in FLASH_NSCR register.

Secure flash memory mass erase sequence

To erase all sectors of both banks simultaneously, using secure access, all sectors must be configured as secure. The application software can set the MER bit to 1 in FLASH_SECCR register, as described below:

- 1. Make sure protection mechanisms do not prevent mass erase ( Section 7.6 ).

- 2. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_SECSR register and that the write buffer is empty by checking the WBNE bit in the FLASH_SECSR register.

- 3. Check and clear all the secure error flags due to previous programming/erase operation. Refer to Section 7.9 for details.

- 4. Unlock the FLASH_SECCR register as described in Section 7.6.7 (only if the registers are not already unlocked).

- 5. Set the MER bit to 1 in FLASH_SECCR register.

- 6. Set the STRT bit in the FLASH_SECCR register. Then wait until BSY bit is cleared in the FLASH_SECSR register.

- 7. STRT bit is cleared automatically at the end of the erase sequence, or in case of error.

- 8. Clear MER in FLASH_SECCR register.

Note: Mass and bank erase also erase high-cycle data sectors aliased from the erased bank.

7.3.7 FLASH parallel operations

As the memory is divided into two independent banks, the embedded flash memory interface supports a read in one bank while a write (RWW: read while write) or an erase is executed in the other bank. It does not support write-while-write, nor read-while-read. Same is valid for the high-cycle data area, system flash libraries, or the OBK (located on Bank2).

In all cases, the sequences described in Section 7.3.4 , Section 7.3.5 and Section 7.3.6 apply.

7.3.8 FLASH error protections

Error correction codes (ECC)

The embedded flash memory supports an error correction code (ECC) mechanism, based on the SECDED algorithm, to correct single errors and detect double errors.

This mechanism uses nine ECC bits per 128-bit flash word, and applies to user and system memory. For read-only, OTP, flash high-cycle data, a stronger six ECC bits per 16-bit word is used. A double ECC error is generated for an OTP or flash high-cycle data virgin word (for example a word with 22 bits at 1). When this OTP or flash high-cycle data word is no more virgin, the ECC error disappears.

More specifically, during each read operation from a 128-bit flash word, the embedded flash memory retrieves the 9-bit ECC information, computes the ECC of the flash word, and compares the result with the reference value. If they do not match, the corresponding ECC error is raised, as described in Section 7.9.10 .

During each program operation, a 9-bit ECC code is associated to each 128-bit data flash word, and the resulting 137-bit flash word information is written in nonvolatile memory.

A similar mechanism applies to read-only and OTP areas, but with 6-bit ECC for 16-bit data.

7.3.9 OTP and RO memory access

OTP and RO memory are accessed through main AHB interface. The OTP is accessible at addresses 0x08FF_F000 to 0x08FF_F7FF, and the read-only section is accessible from 0x08FF_F800 to 0x08FF_FFFF.

FLASH one-time programmable area

The embedded flash memory offers a 2048-byte memory area dedicated to application non-confidential, one-time programmable data (OTP). This area is composed by 1024 words of 16 bits (plus 6 bits of ECC). It cannot be erased, and can be written only once. The OTP area can be accessed through the main AHB interface from address 0x08FF_F000 to 0x08FF_F7FE.

OTP data can be programmed by the application software by 16-bit chunks. Overwriting an already programmed 16-bit half-word can lead to data and ECC errors, and is therefore not supported.

Note: The OTP area is virgin when the device is delivered by STMicroelectronics.

When reading OTP data with a single error corrected or a double error detected, the embedded flash memory reports read errors, as described in Section 7.9.10 .

When reading OTP data not written by the application software (such as virgin OTP), the ECC correction reports a double-error detection (ECCD), and the data are to be found in the FLASH_ECCDR register. ECCD implies an NMI raised.

OTP write protection

OTP data are organized as 32 blocks of 32 OTP words, as shown in Table 46 . An entire OTP block can be protected (locked) from write accesses by setting the LOCKBLi bit (i = 0 to 31) corresponding to each OTP block in the FLASH_OTPBLR register. A block can be write-protected, if it has been programmed (even partially) or not.

The OTP block locking operation is irreversible, and independent from the product life state.

Note: The OTP area can be accessed only in read mode.

Table 46. Flash memory OTP organization

| OTP block | AHB address | AHB word | Lock bit | |

|---|---|---|---|---|

| [31:16] | [15:0] | |||

| Block 0 | 0x08FF F000 | OTP001 | OTP000 | LOCKBL0 |

| 0x08FF F004 | OTP003 | OTP002 | ||

| ... | ||||

| 0x08FF F03C | OTP031 | OTP030 | ||

| Block 1 | 0x08FF F040 | OTP033 | OTP032 | LOCKBL1 |

| 0x08FF F044 | OTP035 | OTP034 | ||

| ... | ||||

| 0x08FF F07C | OTP063 | OTP062 | ||

| Block 2 | 0x08FF F080 | OTP065 | OTP064 | LOCKBL2 |

| 0x08FF F084 | OTP067 | OTP066 | ||

| ... | ||||

| 0x08FF F0BC | OTP95 | OTP94 | ||

| ... | ||||

| Block 31 | 0x08FF F7C0 | OTP993 | OTP992 | LOCKBL31 |

| 0x08FF F7C4 | OTP995 | OTP994 | ||

| ... | ||||

| 0x08FF F7FC | OTP1023 | OTP1022 | ||

OTP write sequence

Follow the sequence below to write an OTP word:

- 1. Check that no memory operations are ongoing by checking the BSY bit in the FLASH_NSSR register and that the data buffer is empty by checking the DBNE bit in the FLASH_NSSR register.

- 2. Check and clear all the error flags due to previous programming/erase operation.

- 3. Set PG bit in the FLASH_NSCR register.

- 4. Check the protection status of the target OTP word (see Table 46 ). The corresponding LOCKBLi bit must not be set to 1.

- 5. Write two OTP words (32 bits) corresponding to the 4-byte aligned address shown in Table 46 . Alternatively, the application software can program separately the 16-bit MSB or 16-bit LSB. In this case the first 16-bit write operation starts immediately, without waiting for the second one.

- 6. Wait for the BSY bit to be cleared in the FLASH_NSSR register.

- 7. Clear PG bit in FLASH_NSCR register if there is not any programming request anymore in the bank.

- 8. Optionally, lock the OTP block using LOCKBLi to prevent further data changes.

Note:

Do not write twice an OTP 16-bit word, otherwise an ECC error is generated.

Writing OTP data at byte level is not supported, and generates a bus error.

To avoid data corruption, it is important to complete the OTP write process (for example by reading back the OTP value), before starting an option change.

Flash read-only area

The embedded flash memory offers a 2-Kbyte area to store read-only data. This area can be accessed through the AHB main port, and is protected by a robust ECC scheme, as detailed in Section 7.3.8 .

The read-only information (programmed by STMicroelectronics) that can be used by the application software is detailed in Table 47 .

Table 47. Read-only public data organization

| Read-only data name | Address | Comment |

|---|---|---|

| Unique device ID | 0x08FF F800 | U_ID[31:0] |

| 0x08FF F804 | U_ID[63:32] | |

| 0x08FF F808 | U_ID[96:64] | |

| Flash memory size/ package | 0x08FF F80C | Flash memory size[15:0] / Package code[15:0] |

| Reserved | 0x08FF F810 to 0x08FF FFFF | Reserved information |

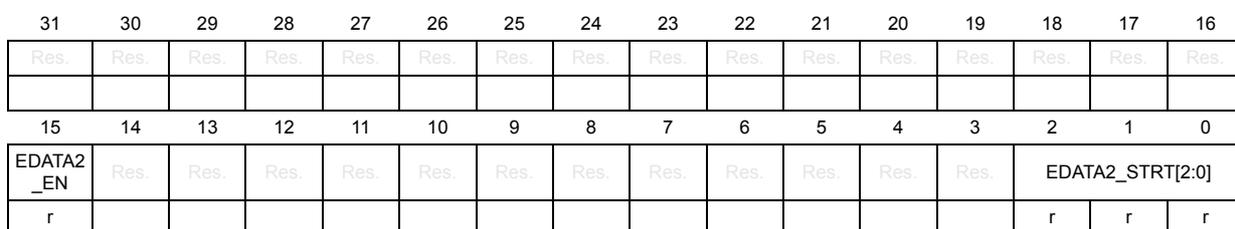

7.3.10 Flash high-cycle data

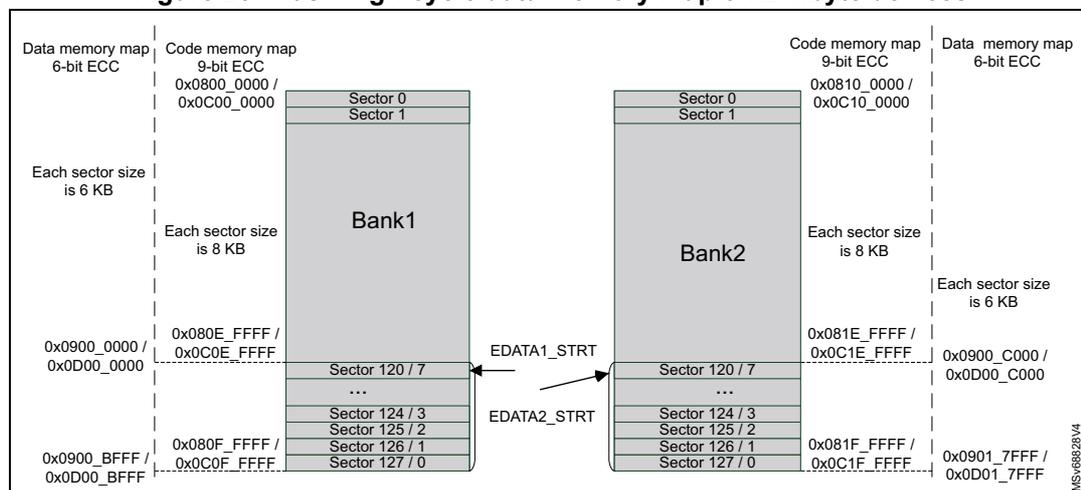

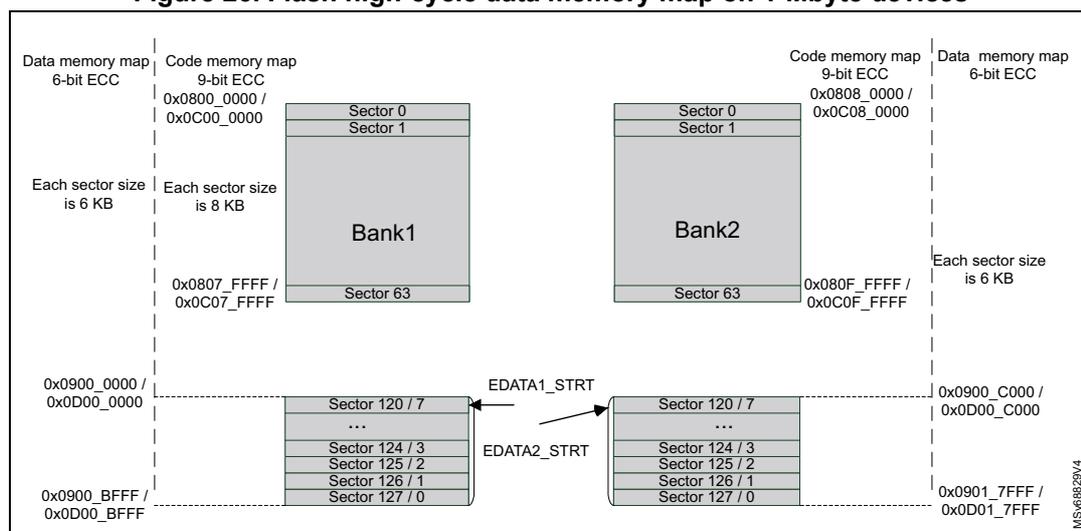

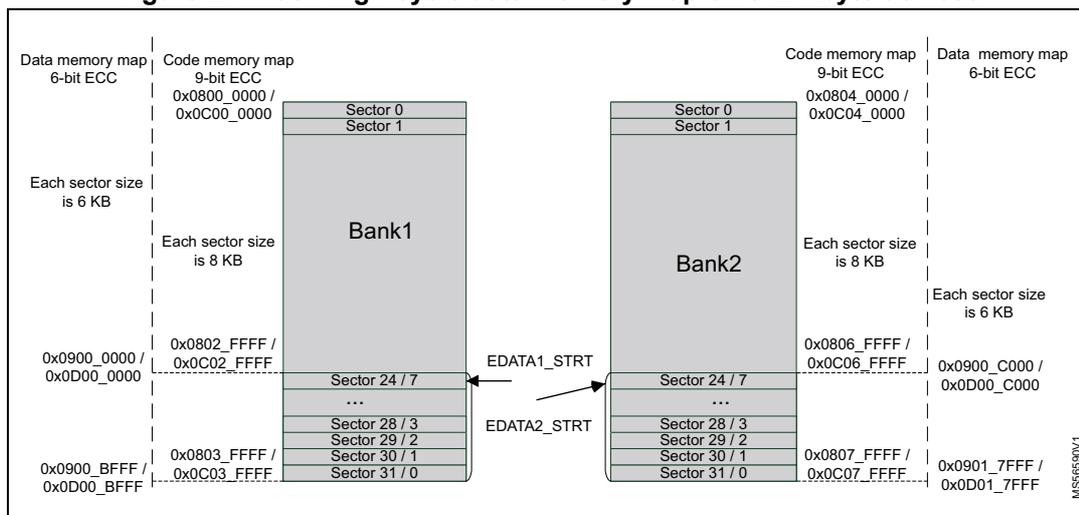

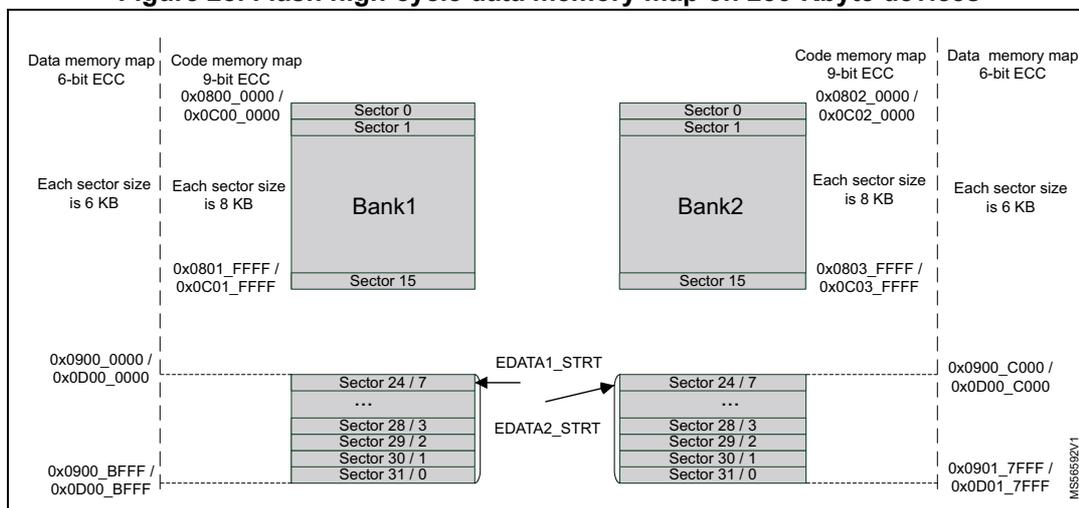

The embedded flash memory offers up to 96 Kbytes (maximum) memory area with high-cycling capability (100 kcycles) to store data and emulate EEPROM. It can be accessed through the AHB system port from address 0x0900_0000 to 0x0901_7FFF (see Figure 25 ). It is mapped in the 8 (or 4) last sectors of Bank 1 and 2. This area is protected by a robust 6-bit ECC, enabling a 16-bit read and write granularity, at the expense of having sector size shrunk to 6 Kbytes.

A threshold per bank (EDATA(1/2)_STRT) is programmable to determine the beginning of the data flash area. By default, the whole memory is used for code.

For example, if 48 Kbytes of data are needed in Bank 1, set EDATA1_EN to 1, and EDATA1_STRT to 7. If no data are needed in Bank2, set EDATA2_EN to 0. In this case the data are accessible from address 0x0900_0000 to 0x0900_BFFF for Bank 1.

For greater efficiency, it is recommended to use sector on the other bank for flash high-cycle data, so that the application benefits from RWW capability of the dual-bank arrangement.

When SWAP_BANK feature is enabled, the banks are swapped: the flash high-cycle data in Bank 2 are accessible from 0x0900_000 to 0x0900_BFFF, and the data in Bank 1 are accessible from 0x0900_C000 to 0x0901_7FFF.

A bus error is generated on:

- • Attempt to access an address between 0x0900_0000 to 0x0901_7FFF and this address is not valid (EDATA(1/2)_EN not enabled or EDATA(1/2)_STRT not correct).

- • Attempt to fetch instructions from flash high-cycle data area.

Erasing the data area sector is possible by normal erase request for the corresponding user flash sector (120-127 for the STM32H562/563/573xx devices, 24-31 for the STM32H523/33xx devices).

Protections and security of high-cycle area are detailed in Section 7.6.9 .

Figure 25. Flash high-cycle data memory map on 2-Mbyte devices

The diagram illustrates the flash memory map for 2-Mbyte devices, divided into two banks, Bank1 and Bank2. Each bank contains 128 sectors. Bank1 sectors 0 and 1 have a size of 6 KB, while sectors 2 through 127 have a size of 8 KB. Bank2 sectors 0 and 1 have a size of 6 KB, while sectors 2 through 127 have a size of 8 KB. The data memory map for Bank1 starts at 0x0900_0000 and ends at 0x0D00_0000. The data memory map for Bank2 starts at 0x0900_C000 and ends at 0x0D01_7FFF. The code memory map for Bank1 starts at 0x0800_0000 and ends at 0x0C00_0000. The code memory map for Bank2 starts at 0x0810_0000 and ends at 0x0C10_0000. The EDATA1_STRT and EDATA2_STRT markers are indicated between the banks.

Figure 26. Flash high-cycle data memory map on 1-Mbyte devices

The diagram illustrates the flash memory map for 1-Mbyte devices, divided into two banks, Bank1 and Bank2. Each bank contains 64 sectors. Bank1 sectors 0 and 1 have a size of 6 KB, while sectors 2 through 63 have a size of 8 KB. Bank2 sectors 0 and 1 have a size of 6 KB, while sectors 2 through 63 have a size of 8 KB. The data memory map for Bank1 starts at 0x0900_0000 and ends at 0x0D00_0000. The data memory map for Bank2 starts at 0x0900_C000 and ends at 0x0D01_7FFF. The code memory map for Bank1 starts at 0x0800_0000 and ends at 0x0C00_0000. The code memory map for Bank2 starts at 0x0808_0000 and ends at 0x0C08_0000. The EDATA1_STRT and EDATA2_STRT markers are indicated between the banks.

Figure 27. Flash high-cycle data memory map on 512-Kbyte devices

Figure 28. Flash high-cycle data memory map on 256-Kbyte devices

Note: When flash high-cycle data area on Bank1 is enabled, the code memory map is not continuous from Bank1 to Bank2 on 2M- and 512K-byte devices.

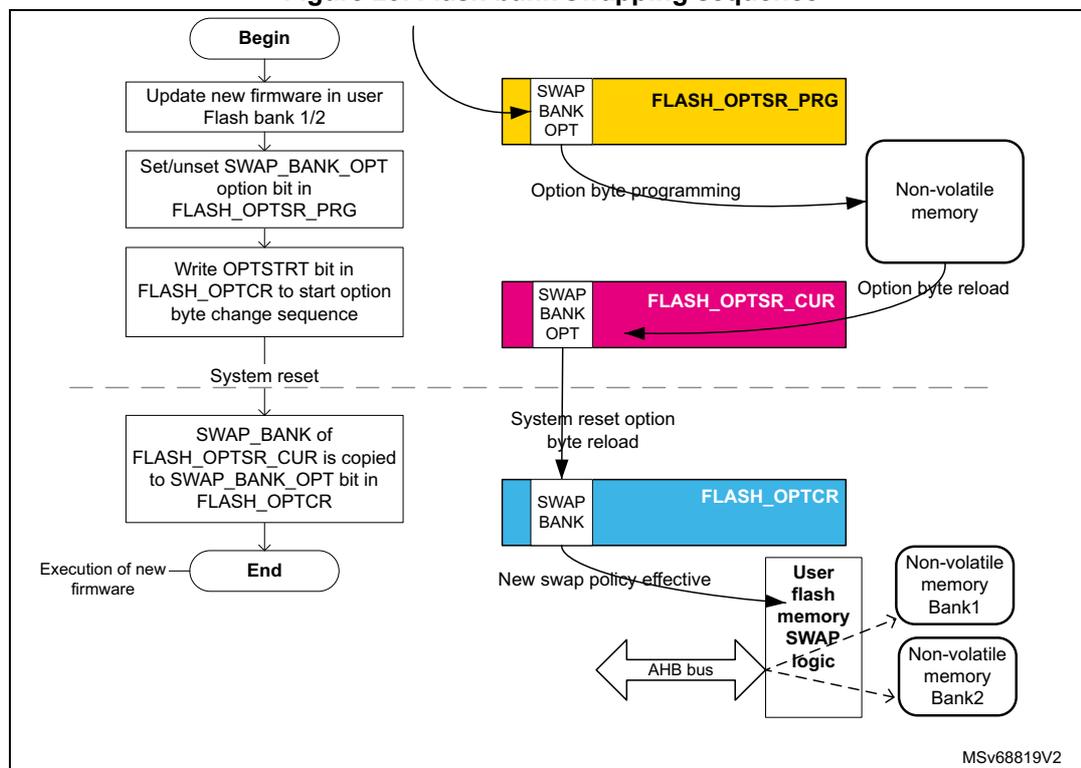

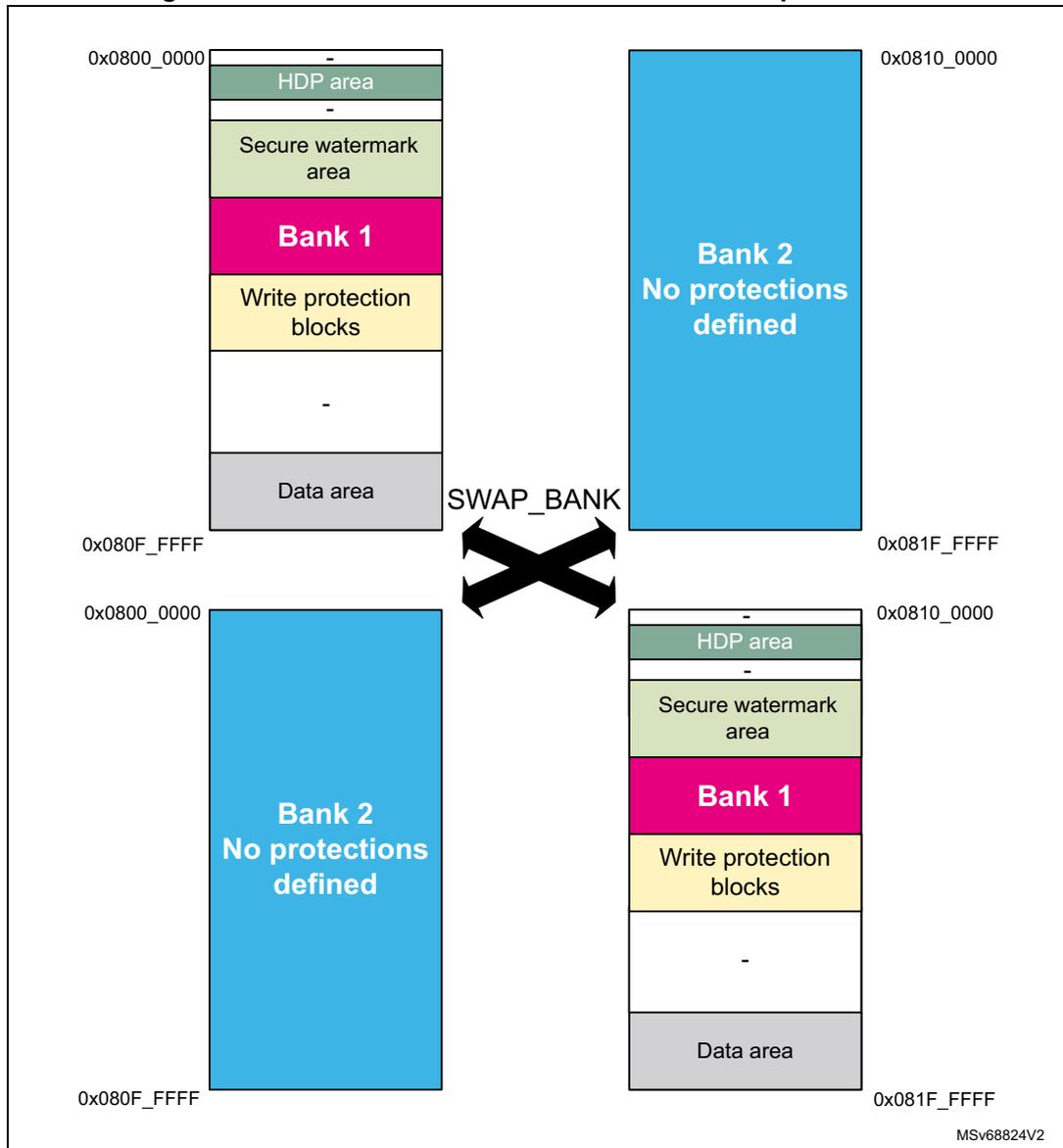

7.3.11 Flash bank swapping

Bank1 and Bank2 can be swapped for the user flash. This feature can be used after a firmware upgrade to restart the device on the new firmware. Bank swapping is an user option byte flag controlled by the SWAP_BANK bit of the FLASH_OPTCR register.

Bank specific settings for data area and security attributes follow the original bank and its contents. Control bit BKSEL always refers to physical bank, not the SWAP_BANK setting.

Table 48 shows the accessible memory, depending upon the SWAP_BANK bit value.

Table 48. Memory map and swapping options (STM32H562/563/573xx devices)

| Area | Corresponding bank | Start address | End address | Size (bytes) | Region name | |

|---|---|---|---|---|---|---|

| SWAP_BANK = 0 | SWAP_BANK = 1 | |||||

| User main memory | Bank1 | Bank2 | 0x0800 0000 | 0x0800 1FFF | 8 K | Sector 0 |

| 0x0800 2000 | 0x0800 3FFF | 8 K | Sector 1 | |||

| ... | ... | ... | ... | |||

| 0x080F E000 | 0x080F FFFF | 8 K | Sector 127 | |||

| Bank2 | Bank1 | 0x0810 0000 | 0x0810 1FFF | 8 K | Sector 0 | |

| 0x0810 2000 | 0x0810 3FFF | 8 K | Sector 1 | |||

| ... | ... | ... | ... | |||

| 0x081F E000 | 0x081F FFFF | 8 K | Sector 127 | |||

| System memory | Bank1 | 0x0BF8 0000 | 0x0BF8 1FFF | 8 K | System 1 Sector 0 | |

| 0x0BF8 2000 | 0x0BF8 3FFF | 8 K | System 1 Sector 1 | |||

| ... | ... | ... | ... | |||

| 0x0BF8 E000 | 0x0BF8 FFFF | 8 K | System 1 Sector 7 | |||

| Bank2 | 0x0BF9 0000 | 0x0BF9 1FFF | 8 K | System 2 Sector 0 | ||

| 0x0BF9 2000 | 0x0BF9 3FFF | 8 K | System 2 Sector 1 | |||

| ... | ... | ... | ... | |||

| 0x0BF9 E000 | 0x0BF9 FFFF | 8 K | System 2 Sector 7 | |||

Table 49. Memory map and swapping options (STM32H523/533xx devices)

| Area | Corresponding bank | Start address | End address | Size (bytes) | Region name | |

|---|---|---|---|---|---|---|

| SWAP_BANK = 0 | SWAP_BANK = 1 | |||||

| User main memory | Bank1 | Bank2 | 0x0800 0000 | 0x0800 1FFF | 8 K | Sector 0 |

| 0x0800 2000 | 0x0800 3FFF | 8 K | Sector 1 | |||

| ⋮ | ⋮ | ⋮ | ⋮ | |||

| 0x0803 E000 | 0x0803 FFFF | 8 K | Sector 31 | |||

| Bank2 | Bank1 | 0x0804 0000 | 0x0804 1FFF | 8 K | Sector 0 | |

| 0x0804 2000 | 0x0804 3FFF | 8 K | Sector 1 | |||

| ⋮ | ⋮ | ⋮ | ⋮ | |||

| 0x0807 E000 | 0x0807 FFFF | 8 K | Sector 31 | |||

Table 49. Memory map and swapping options (STM32H523/533xx devices) (continued)

| Area | Corresponding bank | Start address | End address | Size (bytes) | Region name | |

|---|---|---|---|---|---|---|

| SWAP_BANK = 0 | SWAP_BANK = 1 | |||||

| System memory | Bank1 | 0x0BF8 0000 | 0x0BF8 1FFF | 8 K | System 1 Sector 0 | |

| 0x0BF8 2000 | 0x0BF8 3FFF | 8 K | System 1 Sector 1 | |||

| ... | ... | ... | ... | |||

| 0x0BF8 E000 | 0x0BF8 FFFF | 8 K | System 1 Sector 7 | |||

| Bank2 | 0x0BF9 0000 | 0x0BF9 1FFF | 8 K | System 2 Sector 0 | ||

| 0x0BF9 0000 | 0x0BF9 3FFF | 8 K | System 2 Sector 1 | |||

| ... | ... | ... | ... | |||

| 0x0BF9 E000 | 0x0BF9 FFFF | 8 K | System 2 Sector 7 | |||

The SWAP_BANK bit in FLASH_OPTCR register is loaded from the SWAP_BANK option bit only after system reset or POR.

To change the SWAP_BANK bit (for example to apply a new firmware update), follow the sequence below:

- 1. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_NS/SECSR register and that the write buffer is empty by checking the WBNE bit in the FLASH_NS/SECSR register.

- 2. Clear all error flags due to a previous operation.

- 3. Unlock OPTLOCK bit, if not already unlocked.

- 4. Set the new desired SWAP_BANK value in the FLASH_OPTSR_PRG register.

- 5. Start the option byte change sequence by setting the OPTSTRT bit in the FLASH_OPTCR register.

- 6. Once the option byte change has completed, FLASH_OPTSR_CUR contains the expected SWAP_BANK value, but SWAP_BANK bit in FLASH_OPTCR has not yet been modified and the bank swapping is not yet effective.

- 7. Force a system reset or a POR. When the reset rises up, the bank swapping is effective (SWAP_BANK value updated in FLASH_OPTCR) and the new firmware shall be executed.

Note: The SWAP_BANK bit in FLASH_OPTCR is read-only, and cannot be modified by the application software.

The SWAP_BANK option bit in FLASH_OPTSR_PRG can be modified whatever the product state. Instead of being locked by PRODUCT_STATE, it is locked by (NS/SEC)BOOT_LOCK User OB.

Figure 29 gives an overview of the bank swapping sequence.

Figure 29. Flash bank swapping sequence

graph TD

Begin([Begin]) --> Step1[Update new firmware in user Flash bank 1/2]

Step1 --> Step2[Set/unset SWAP_BANK_OPT option bit in FLASH_OPTSR_PRG]

Step2 --> Step3[Write OPTSTRT bit in FLASH_OPTCR to start option byte change sequence]

Step3 --> Reset[System reset]

Reset -.-> Step4[SWAP_BANK of FLASH_OPTSR_CUR is copied to SWAP_BANK_OPT bit in FLASH_OPTCR]

Step4 --> End([End])

End --> Firmware[Execution of new firmware]

subgraph Registers

PRG[FLASH_OPTSR_PRG: SWAP BANK OPT]

CUR[FLASH_OPTSR_CUR: SWAP BANK OPT]

CR[FLASH_OPTCR: SWAP BANK]

end

Step2 -- "Option byte programming" --> NV[Non-volatile memory]

NV -- "Option byte reload" --> CUR

Reset -- "System reset option byte reload" --> CR

CR -- "New swap policy effective" --> Logic[User flash memory SWAP logic]

Logic --> Bank1[Non-volatile memory Bank1]

Logic --> Bank2[Non-volatile memory Bank2]

Bus[AHB bus] --> Logic

MSv68819V2

7.3.12 FLASH reset and clocks

Reset management

The embedded flash memory can be reset by a core domain reset, driven by the reset and clock control (RCC). The main effects of this reset are the following:

- • All registers, except for option byte registers, are cleared, including read and write latencies. If the bank swapping option is changed, it is applied.

- • Most control registers are automatically protected against write operations. To unprotect them, new unlock sequences must be used as described in Section 7.6.7 .

The memory can be reset by a power-on core domain reset, driven by the reset and clock control (RCC). When the reset falls, all option byte registers are reset. When the reset rises up, the option bytes are loaded, potentially applying new features. During this loading sequence, the device remains under reset, and the memory is not accessible.

The reset signal can have a critical impact on the memory: the content is not guaranteed if a device reset occurs during a write or erase operation.

Reset occurring during flash operation

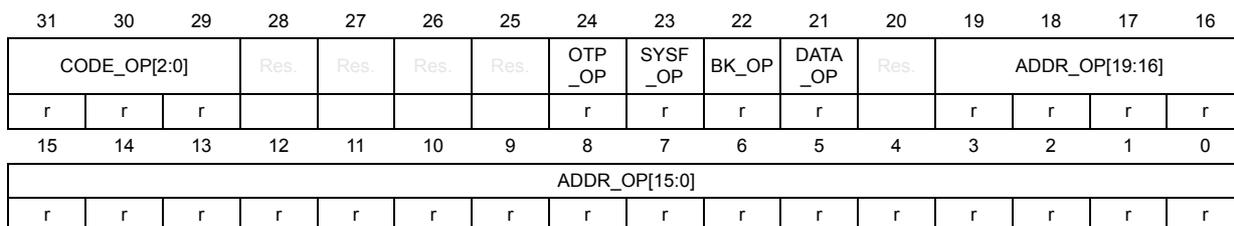

If a reset occurs during a flash operation (programming, erase or option change), the content of the memory is not guaranteed. It is mandatory for integrity to restart the operation. The status register FLASH_OPSR gives information about operations interrupted by a reset.

FLASH_OPSR.CODE_OP gives opcode of operation. Table 50 indicates how to use FLASH_OPSR, and which operation is required.

Table 50. Recommended reactions to FLASH_OPSR contents

| CODE_OP | Operation interrupted | OTP_OP | SYSF_OP | BK_OP | DATA_OP | Flash area | ADDR_OP min | ADDR_OP max | Recommended action |

|---|---|---|---|---|---|---|---|---|---|

| 0x000 | No operation ongoing while reset | 0 | 0 | 0 | 0 | _( 1 ) | - | - | No extra action |

| 0x001 | Write operation | 0 | 0 | 0/1 | 0 | User flash | 0x0000 | 0xFFFF | Erase sector and rewrite |

| 0 | 1 | 0/1 | 0 | System flash | 0x0000 | 0x0FFF | |||

| 1 | 0 | 0 | 0 | OTP | 0x0600 | 0x07FF | |||

| 1 | 0 | 1 | 0 | OBKeys (2) | 0x0000 | 0x03FF | |||

| 0 | 0 | 0/1 | 1 | Data area (3) | 0xF000 | 0xFFFF | |||

| 0x010 | OBK alternate sector erase | 0 | 0 | 1 | 0 | OBKeys | 0 | 0 | Relaunch the alternate sector erase |

| 0x011 | Sector erase (4) | 0 | 0 | 0/1 | 0 | User flash | 0x0000 | 0xFFFF | Relaunch sector erase |

| 0 | 1 | 0/1 | 0 | System flash | 0x0000 | 0x0FFF | |||

| 0x100 | Bank erase | 0 | 0 | 0/1 | 0 | User flash | - | - | Relaunch bank erase |

| 0x101 | Mass erase | 0 | 0 | 0 | 0 | - | - | Relaunch mass erase | |

| 0x110 | Option change | 0 | 0 | 0 | 0 | User configuration | - | - | New attempt on option change |

| 0x111 | OBK swap sector | 0 | 0 | 1 | 0 | OBKeys | - | - | Erase alternate sector, reprogram new OBKeys and relaunch swap |

1. Dash represents "does not matter".

2. Depends on current OBK sector.

3. Depends on EDATA setting in the OB.

4. Addresses indicated are aligned to sector start, data area sectors are erased by erase request to corresponding user flash memory sector.

Clock management

The memory uses the microcontroller system clock (sys_ck), here the AHB interface clock.

7.4 FLASH option bytes

7.4.1 About option bytes

The memory includes a set of nonvolatile option bytes. They are loaded at power-on reset and can be read and modified only through configuration registers. This section details:

- • when option bytes are loaded

- • how application software can modify them

- • their detailed list, together with their initial values (before the first option byte change, user default configuration).

7.4.2 Option bytes loading

There are multiple ways of loading the option bytes:

- • Power-on wake-up

When the device is first powered, the embedded flash memory automatically loads all the option bytes. During the option byte loading sequence, the device remains under reset and the embedded flash memory cannot be accessed.

- • Wake-up from system Standby

When the core power domain, which contains the embedded flash memory, is switched from Standby mode to Run mode, the embedded flash memory behaves as during a power-on sequence. During loading time the device is not under reset, unlike power-on sequence.

- • Dedicated option byte reloading by the application

When the user application successfully modifies the option byte content through the memory registers, the nonvolatile option bytes are programmed and the memory automatically reloads all option bytes to update the option registers.

Note: The option byte read sequence is protected by error correction code. In case of error, the option bytes are loaded with default values (see Section 7.4.3 ), different from the initial values (user default configuration), and more restrictive.

7.4.3 Option bytes modification

Changing user option bytes

A user option byte change operation can be used to modify the configuration and the protection settings saved in the nonvolatile option byte area.

There are several rules enforced when attempting to change a user option byte, they are summarized in Section 7.4.7 . Failing to stick to those rules usually results in errors, described in Section 7.9.12 .

The embedded flash memory features two sets of option byte registers:

- • The first register set contains the current values of the option bytes. Their names have the _CUR extension. All these registers are read-only. Their values are automatically loaded from the nonvolatile memory after power-on reset, wake-up from system standby or after an option byte change operation.

- • The second register set allows the modification of the option bytes. Their names contain the _PRG extension. All “_PRG” registers can be accessed in read/write mode.

When the OPTLOCK bit in FLASH_OPTCR register is set, it is not possible to modify the FLASH_XXX_PRG registers.

When OPTSTRT bit is set to 1, the memory checks the programming sequence (PGSERR) and the conditions described in Section 7.4.7 (OPTCHANGEERR). If no error has been detected (PGSERR/OPTCHANGEERR), the flash interface launches the option byte modification, and updates the option byte registers with _CUR extension.

If one of the condition described in Section 7.4.7 , Section 7.9.12 or Section 7.9.5 , alternatively Section 7.9.4 is not respected, the memory aborts the option byte change operation. In this case, the FLASH_XXX_PRG registers are not overwritten by the current option value. The user application can check what was wrong in their configuration.

Unlocking the option byte modification

After reset, the OPTLOCK bit is set to 1 and the FLASH_OPTCR is locked. As a result, the application software must unlock the option configuration register before attempting to change the option bytes. The FLASH_OPTCR unlock sequence is described in Section 7.6.7 .

Option bytes modification sequence

To modify user option bytes, follow the sequence below:

- 1. Check that no memory operations are ongoing by checking the BSY bit in the FLASH_NS/SECSR register and that the write buffer is empty by checking the WBNE bit in the FLASH_NS/SECSR register.

- 2. Check the data buffer is empty (DBNE = 0) in FLASH_NS/SECSR register.

- 3. Clear all error flags due to a previous operation.

- 4. Unlock FLASH_OPTCR register as described in Section 7.6.7 , unless the register is already unlocked.

- 5. Write the desired new option byte values in the corresponding option registers (FLASH_XXX_PRG).

- 6. Set the option byte start change OPTSTRT bit to 1 in the FLASH_OPTCR register.

- 7. Wait until BSY bit is cleared in FLASH_NS/SECSR register.

- 8. OPTSTRT bit is cleared automatically at the end of the sequence (or in case of error).

- 9. Reset the device. This step is always recommended, becomes mandatory when one of the following option bytes is impacted:

- a) SECBOOTADDR

- b) NSBOOTADDR

- c) TZEN

- d) BOOT_UBE

Note: If a reset or a power-down occurs while the option byte modification is ongoing, the original option byte value is kept. A new option byte modification sequence is required to program it.

Option bytes overview

Table 51 lists all the user option bytes managed through the memory registers, as well as the initial values before the first option byte change (user default configuration).

Table 51. Option bytes organization

| Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FLASH_OPTSR | SWAP BANK | BOOT_UBE | IWDG_STDBY | IWDG_STOP | Res. | Res. | IO_VDDIO2_HSLV | IO_VDD_HSLV | PRODUCT_STATE | NRST_STDBY | NRST_STOP | Res. | WWDG_SW | IWDG_SW | BORH_EN | BOR_LEV | ||||||||||||||||

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | |

| FLASH_OPTSR2 | TZEN | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | USBPD_DIS | Res. | SRAM2_ECC | SRAM3_ECC | BKPRAM_ECC | SRAM2_RST | SRAM13_RST | Res. | Res. | |||||||||

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | |

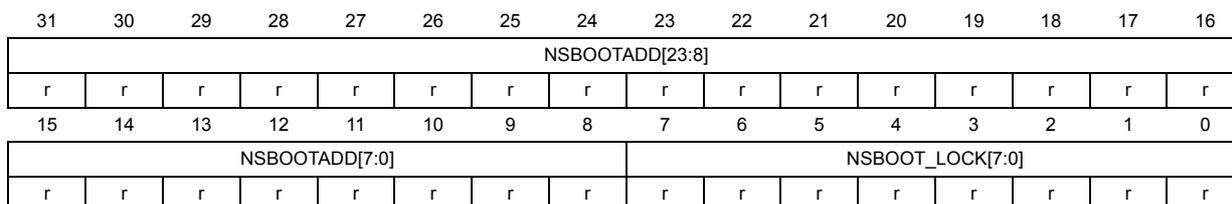

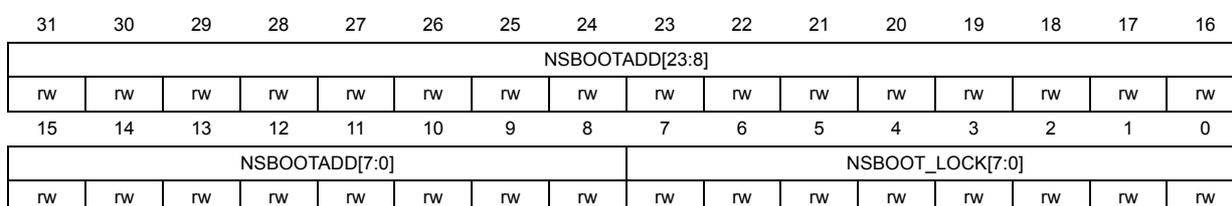

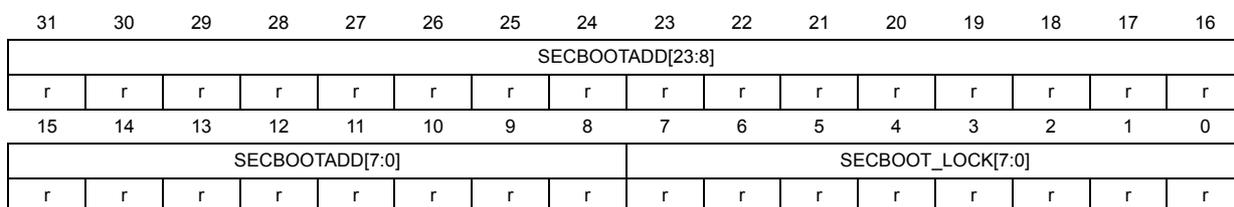

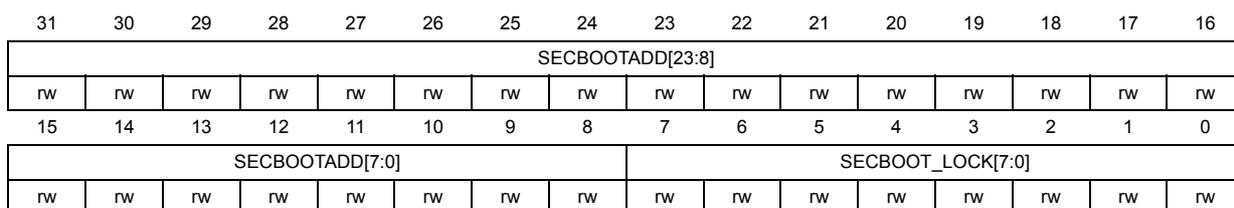

| FLASH_BOOTR | SECBOOTADD[23:8] | SECBOOTADD[7:0] | SECBOOT_LOCK | |||||||||||||||||||||||||||||

| 0x0C00 | 0x00 | 0xC3 | ||||||||||||||||||||||||||||||

| FLASH_NSBOOTR | NSBOOTADD[23:8] | NSBOOTADD[7:0] | NSBOOT_LOCK | |||||||||||||||||||||||||||||

| 0x0800 | 0x00 | 0xC3 | ||||||||||||||||||||||||||||||

| FLASH_SECWM1R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM1_END | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM1_STRT | |||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | |

| FLASH_SECWM2R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM2_END | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECWM2_STRT | |||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | |

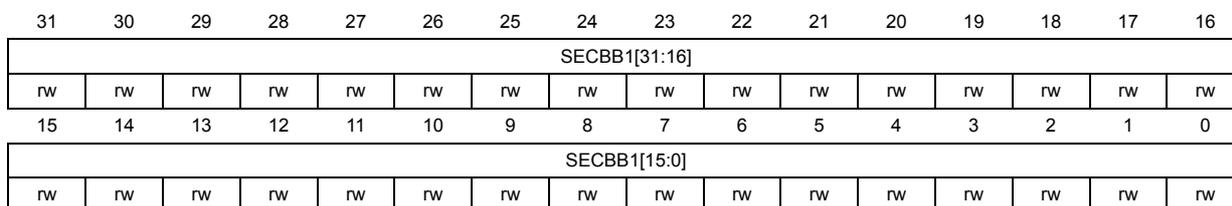

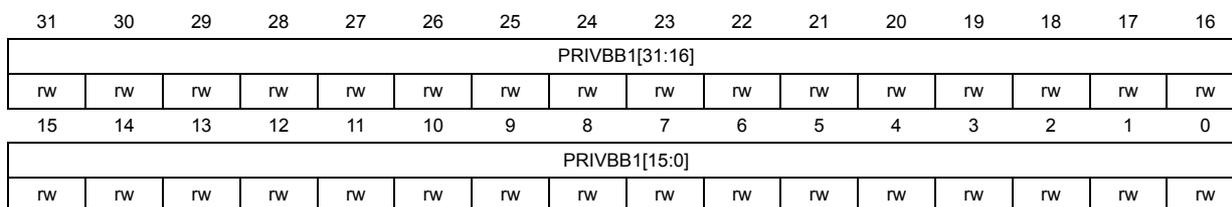

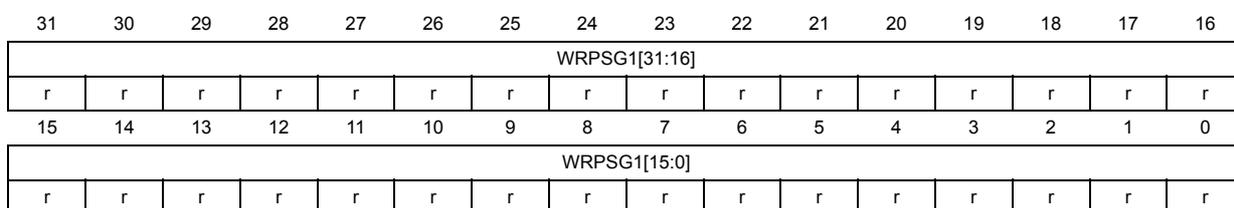

| FLASH_WRPSGN1R | WRPSG[127:124] | WRPSG[123:120] | ... | WRPSG[71:68] | WRPSG[67:64] | WRPSG[63:60] | WRPSG[59:56] | ... | WRPSG[7:4] | WRPSG[3:0] | ||||||||||||||||||||||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| FLASH_WRPSGN2R | WRPSG[127:124] | WRPSG[123:120] | ... | WRPSG[71:68] | WRPSG[67:64] | WRPSG[63:60] | WRPSG[59:56] | ... | WRPSG[7:4] | WRPSG[3:0] | ||||||||||||||||||||||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

Table 51. Option bytes organization (continued)

| Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FLASH_OTPBLR | LOCKBL | |||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| FLASH_EDATA1R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | DATA_EN1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECTOR_START_1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| FLASH_EDATA2R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | DATA_EN1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECTOR_START_2 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

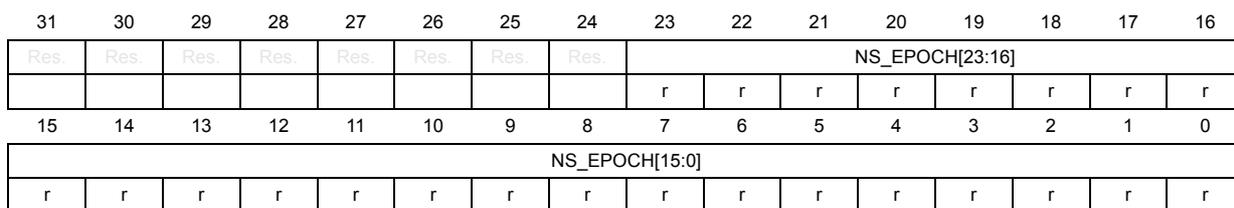

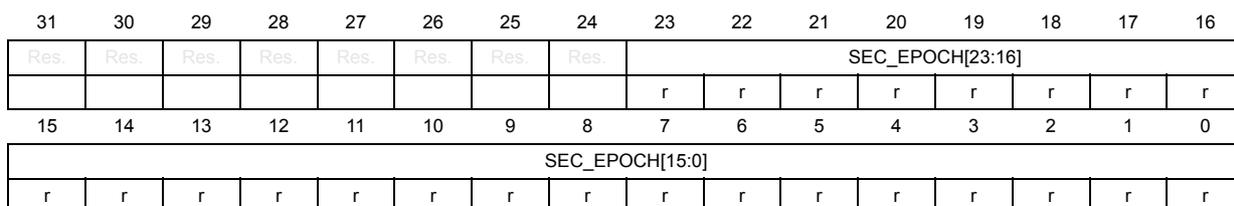

| FLASH_NSEPOCHR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | NS_EPOCH | 1 | |||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| FLASH_SECEPOCHR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SEC_EPOCH | 1 | |||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

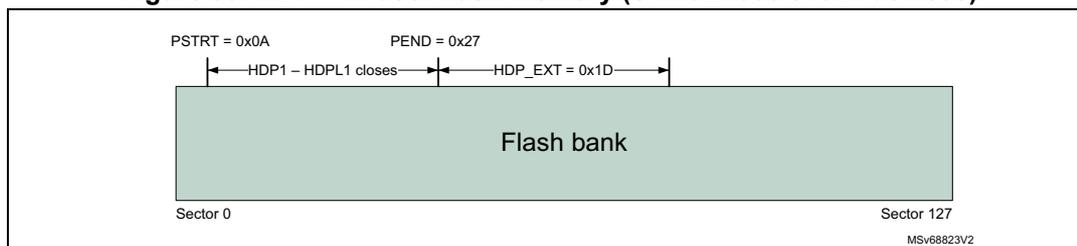

| FLASH_HDP1R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | HDP1_END | HDP1_STRT | 1 | ||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| FLASH_HDP2R | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | HDP2_END | HDP2_STRT | 1 | ||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

7.4.4 Description of user and system option bytes

The general-purpose option bytes that can be used by the application are listed below:

- Watchdog management

- IWDG_STOP: independent watchdog IWDG (also known as WDGLS_CD) counter active in Stop mode if 1 (stop counting or freeze if 0)

- IWDG_STDBY: independent watchdog IWDG (also known as WDGLS_CD) counter active in Standby mode if 1 (stop counting or freeze if 0)

- IWDG_SW: hardware (0) or software (1) IWDG (also known as WDGLS_CD) watchdog control selection

Note: If the hardware watchdog “control selection” feature is enabled (set to 0), the watchdog is automatically enabled at power-on, thus generating a reset unless the watchdog key register is written to or the down-counter is reloaded before the end-of-count is reached. Depending on the configuration of IWDG_STOP and IWDG_STDBY options, the IWDG can continue counting (1) or not (0) when the device is, respectively, in Stop or Standby mode.

When the IWDG is kept running during Stop or Standby mode, it can wake up the device from these modes.

- • Reset management

- – BOR_LEV: Brownout level option, indicating the supply level threshold that activates/releases the reset

- – BORH_EN: enabling a high BOR level

- – NRST_STDBY: generates a reset when entering Standby mode if cleared to 0

- – NRST_STOP: generates a reset when entering Stop mode if cleared to 0.

Note: Whenever a Standby (Stop) mode entry sequence is successfully executed, the device is reset instead of entering Standby (Stop) mode if NRST_STDBY (NRST_STOP) is cleared to 0.

- • Device options

- – IO_VDDIO2_HSLV: enables the configuration of pads below 2.7 V for VDDIO2 power rail if set to 1

- – IO_VDD_HSLV: enables the configuration of pads below 2.7 V for VDD power rail if set to 1

- – USBPD_DIS: bit to disable USB PD

At delivery, the values programmed in the user option bytes are the following:

- • Watchdog management

- – IWDG (also known as WDGLS_CD) active in Standby and Stop modes: 0x1

- – IWDG (also known as WDGLS_CD) not automatically enabled at power-on: 0x1

- • Reset management

- – BOR: brownout level option (reset level = 2.1 V): 0x0. A reset is not generated when the device enters Standby, Stop low-power mode (value = 0x1)

- • Device working in the full voltage range with I/O speed optimization at low-voltage disabled (IO_VDDIO2_HSLV = 0 and IO_VDD_HSLV = 0)

Refer to Section 7.11 for details.

7.4.5 Description of data protection option bytes

The option bytes that can be used to enhance data protection are listed below:

- • PRODUCT_STATE[7:0]: A product life cycle state (see Section 7.6.11 for details).

- • WRPSGn1/2: write protection option of the corresponding group of four consecutive sectors in Bank1 (respectively Bank2). It is active low. Refer to

Section 7.6.8

for details.

- – Bit N: Group embedding sectors \( 4 \times N \) to \( 4 \times N + 3 \)

- • SECWMx: TrustZone® secure only watermark area definition (refer to

Section 7.6.1

for details).

- – SECWM1_STRT (respectively SECWM1_END) contains the first (respectively last) sector of the secure access only zone in Bank1

- – SECWM2_STRT (respectively SECWM2_END) contains the first (respectively last) sector of the secure access only zone in Bank2.

- • TZEN: this nonvolatile option can be used by the application to activate the secure access mode, as described in Section 7.6 . For security reasons the TZEN is stored with redundancy on 8 bits. While the TZEN OB value is set immediately after

programming, to actually use TZ features, reset is required to set the TZ_STATE in SBS.

When TZEN is activated, secure watermark settings and secure boot address can be reset to default to prevent a deadlock in case the previous values were not correct.

- • HDPx: Secure hide protection - HDPL exclusive area control in the user flash memory.

When factory programmed values of the data protection option bytes are the following:

- • Product state depends on sales type

- • Flash bank erase operations do not impact watermarked secure data areas

- • Secure watermark areas protections disabled (start addresses higher than end addresses)

- • Write protection disabled (all option byte bits set to 1)

- • TrustZone Secure access mode disabled (TZEN option byte value = 0xC3)

Refer to Section 7.11 for details.

7.4.6 Description of boot address option bytes

Below the list of option bytes that can be used to configure the appropriate boot address for an application:

- • PRODUCT_STATE

- • BOOT_UBE: Selects either ST-iRoT or User flash as default boot address. Also used by RSS(SFI) to choose either Bootloader or ST-iRoT as next stage. Available only on products embedding cryptographic acceleration (STM32H533/573xx).

- • NSBOOTADD: Selects default boot address when TZ is disabled.

- • SECBOOTADD: Selects default boot address when TZ is enabled.

- • (NS/SEC)BOOT_LOCK: Protects the boot configuration from further modification attempts.

- • SWAP_BANK: bank swapping option, set to 1 to swap user flash banks after boot (see Section 7.3.11 ). If BOOT_LOCK corresponding to TZEN state (SEC/NS) is active, the value in SWAP_BANK is fixed, read-only.

When STMicroelectronics delivers the device, the PRODUCT_STATE is Open, BOOT_LOCK is not set (0xC3) and the BOOT_UBE is set to user flash (0xB4). Addresses are SECBOOTADD = 0x0C00 0000, NSBOOTADD = 0x0800 0000.

Refer to Section 7.11 for details.

7.4.7 Specific rules for modifying option bytes

On top of OPTLOCK bit and register access rules, there are other protections for selected security-sensitive option byte fields.

Different option bytes can be modified simultaneously, but if they rely on each other for protection, both states are checked. For example, when trying to modify PRODUCT_STATE and TZEN simultaneously, resulting state must be coherent with the rules. With few exceptions, listed in this section, failing to uphold the rules results in raising OPTCHANGEERR flag ( Section 7.9.12 for additional details).

Table 52. Specific modifying rules

| Option byte | HDPL | TZ secure | Value | Product state |

|---|---|---|---|---|

| PRODUCT_STATE | 1 (1) | Some values only when TZ is enabled | Set of possible transitions | Set of possible transitions ( Table 45 ) |

| HDP | 1 (2) | (3) | - | Refer to Table 53 |

| TZEN | - | - | - | Regression, Open or Provisioning |

| EPOCH | - | - | PRG > CUR | Regression |

| EPOCH_NS | - | - | PRG > CUR | NS-Regression, Regression |

| SECWM | - | Secure mode only (2) | - | Refer to Table 53 |

| BOOT_UBE | - | - | - | Open or Provisioning, SECBOOT_LOCK disabled |

| SECBOOTADD | - | Secure mode only (2) | - | |

| NSBOOTADD | - | - | - | Open or Provisioning, NSBOOT_LOCK disabled |

| LOCKBL | - | - | One way switch (2) | - |

| SWAP_BANK | - | Fixed if BOOT_LOCK corresponding to TZEN is set | - | - |

| SECBOOT_LOCK | - | Secure mode only (2) | - | Open, Regression or Provisioning to unlock |

| NSBOOT_LOCK | - | - | - |

- 1. Most transitions are possible regardless of HDPL, only a few require specific HDPL, see text below.

- 2. No OPTCHANGEERR raised in violation of this.

- 3. Dash means there is no limitation from this side.

Even in the closed PRODUCT_STATE progression, some OBs can still be modified, if all the other constraints are satisfied. An overview is presented in Table 53 .

Table 53. OB modifiable in closed product

| PRODUCT_STATE | OBs that can be modified |

|---|---|

| TZ-Closed | SWAP_BANK, LOCKBL, PRODUCT_STATE, SECWM, HDP |

| Closed | SWAP_BANK, LOCKBL, PRODUCT_STATE |

| Locked | SWAP_BANK, LOCKBL |

Specific rules must be respected to update the following OB:

- • PRODUCT_STATE

PRODUCT_STATE transitions follow a state machine with two types of transitions. Locking down the product is allowed without restriction. Opening the product is possible only using a debug interface and following a digital signature verification. The regression to a less secure state results in the erase of the protected content. More details are given in Section 7.6.11 .

Summary: Selected changes are possible only in HDPL1. Some states are accessible only when TZEN is enabled.

- •

HDP

Can be modified only in HDPL1. Do not set it to overlap with flash high-cycle data area. - •

TrustZone access mode (TZEN)

Can be changed only in Open, Regression and Provisioning. - •

SEC_EPOCH and NS_EPOCH

The value programmed must be greater than current value. The increment is done in specific product states: Regression and NS-Regression. - •

Secure watermark area (SECWM1/2_STRT and SECWM1/2_END)

Can be changed only in secure mode (TZ_state = 0xB4). Automatically reset to default value when TZEN is enabled. Do not set it to overlap with flash high-cycle data area. - •

BOOT_UBE

Available only on cryptography enabled devices. Can be changed only in product states open for debug like Open and also in Provisioning. SECBOOT_LOCK must be disabled to change. - •

SECBOOTADD

Can be changed only in Open and Provisioning. Locked by SECBOOT_LOCK. Automatically reset to default value when TZEN is enabled. - •

NSBOOTADD

Can be changed only in Open and Provisioning. Locked by NSBOOT_LOCK. - •

LOCKBL

Can be changed freely only in one direction. A permanent irreversible switch. - •

SWAP_BANK

Not modifiable when both TZEN and SECBOOT_LOCK are 0xB4 (set) or when TZEN = 0xC3 (disabled) and NSBOOT_LOCK is active (0xB4). - •

SECBOOT_LOCK

Can be changed only freely in locking direction. Unlock is possible in Open, Provisioning and Regression. - •

NSBOOT_LOCK

Can be changed only freely in locking direction. Unlock is possible in Open, Provisioning and Regression.

Note: For all user option bytes above: default values are loaded and Tamper is signaled when a double ECC error occurs during OBL.

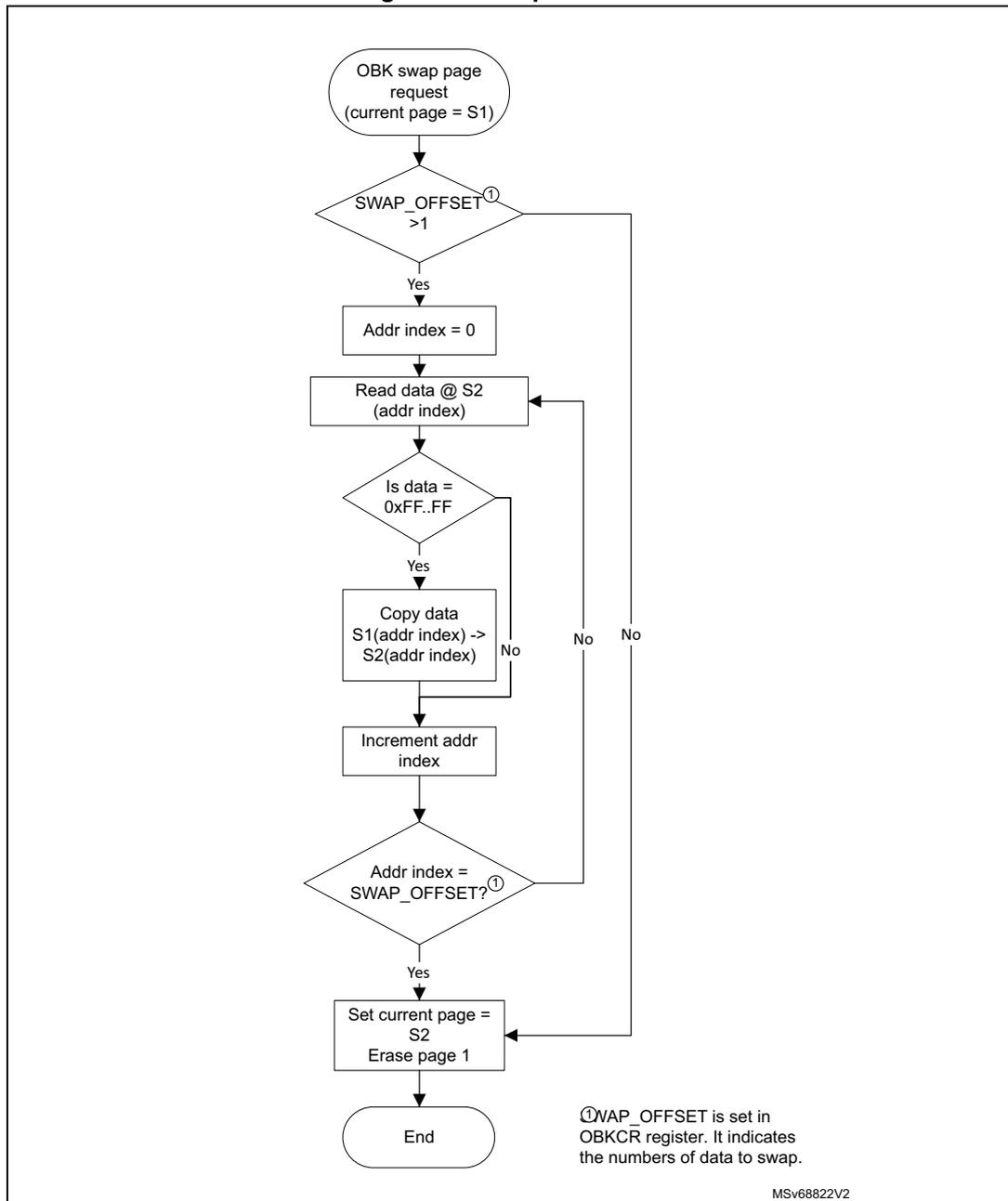

7.5 Option bytes key (OBK) management

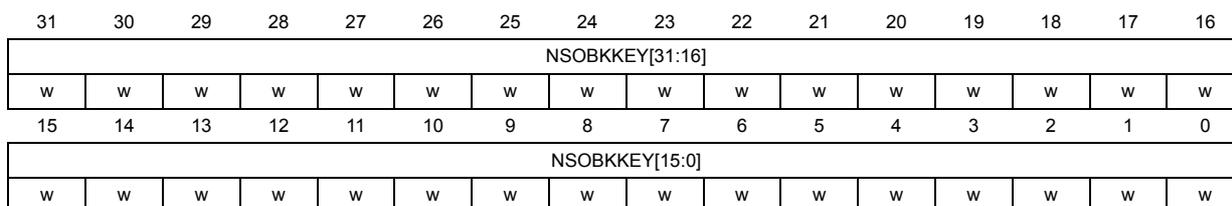

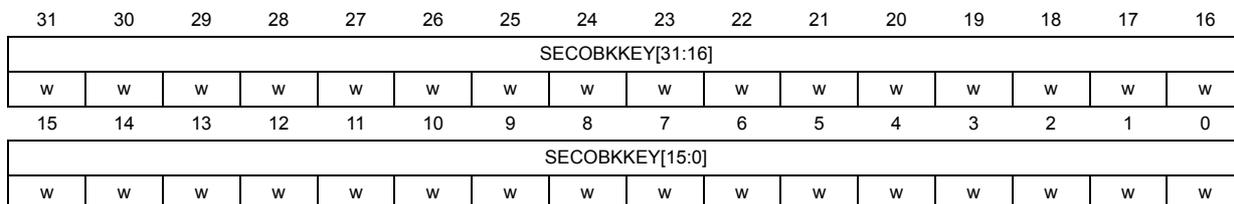

This section describes the key storage tied with SAES and OBK-HDPL value set by the SBS (refer to Section 14.3.7: SBS hardware secure storage control ). The OBKs are stored in 128 bits and protected by 9-bit ECC (SEC/DED). They are written alternatively in two sectors.

7.5.1 OBK loading

OBKs are memory mapped, and accessible through the main AHB bus (C-Bus), starting from address 0x0FFD 0000. A 9-bit ECC is associated to each 128-bit data flash word.

Note: Read access is allowed in the current and alternate sector, except for the last address of the current and alternate sector. In case of read access, no error is reported but the read data is always 0x0 (see Section 7.6.12 ).

7.5.2 OBK access per HDPL level

Table 54 describes the option byte key areas. The key storage is not dedicated to a particular key, and the usage is defined by the application.

An option byte key can be accessed only if the OBK-HDPL (set in SBS) matches the HDPL associated to the storage offset, indicated below (refer to Section 14.3.7: SBS hardware secure storage control ). If this is not the case, an OBKERR error is raised.

Table 54. Option bytes key area

| OBK-HDPL | Address offset start | Address offset end | Comment |

|---|---|---|---|

| - | 0x0000 | 0x00FF | Reserved |

| 1 | 0x0100 | 0x08FF | OEM iRoT keys |

| 2 | 0x0900 | 0x0BFF | uRoT, OS or secure application |

| 3 | 0x0C00 | 0x17FF | HDPL 3 secure keys |

| 3 | 0x1800 | 0x1FEF | HDPL 3 non-secure keys |

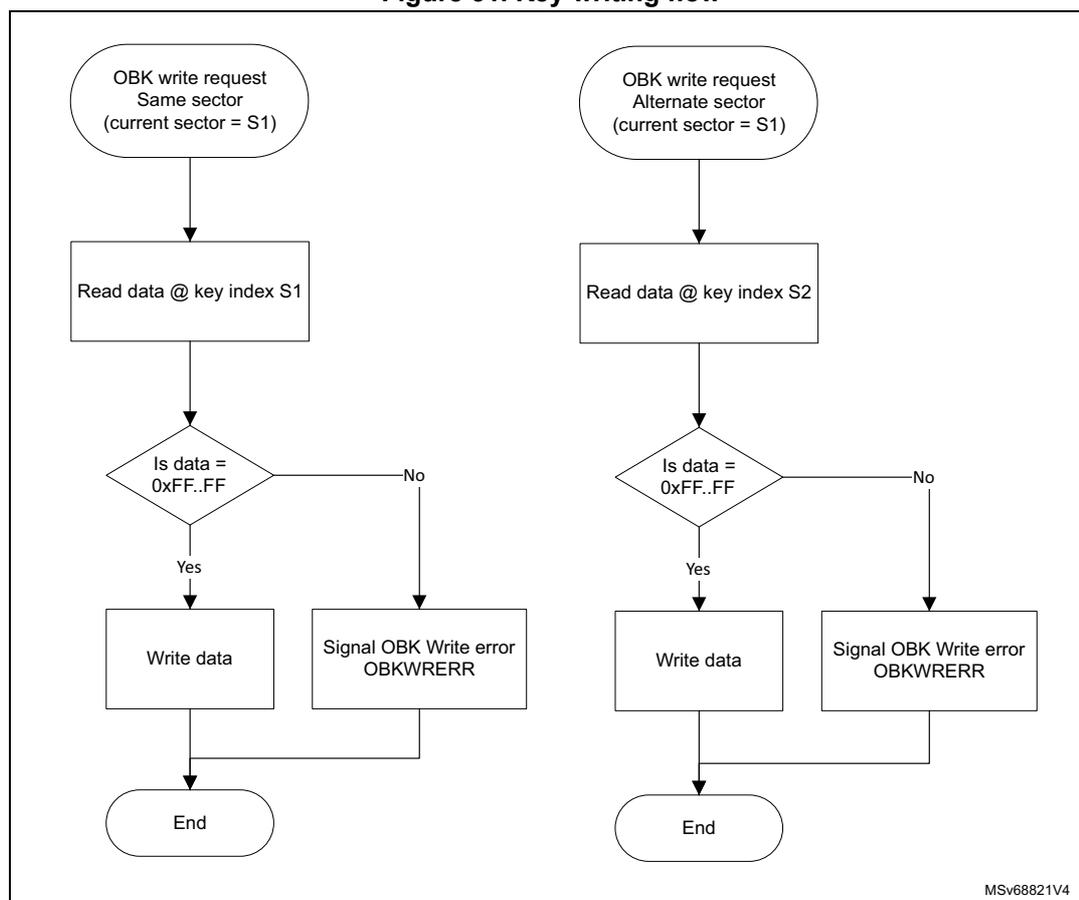

7.5.3 OBK programming sequence

The sequence to write OBK is the same as a write to main flash except that the “alternate sector” (ALT_SECT) bit must be set to write in the alternate OBK sector. The ALT_SECT bit is checked each time a write access is received. If it does not match the one stored in the write buffer, an error is raised.

Note:

Before writing in the alternate OBK sector the user must ensure that the whole key space (128, 256, or 512 bits) is free, by reading the alternate OBK sector.

If the alternate sector is not free, erase the sector using the command ALT_SECT_ERASE.

Secure programming method

Using the secure register if TrustZone is active (TZ_STATE = 0xB4):

- 1. Program the ALT_SECT bit.

- 2. Make sure protection mechanism does not prevent programming (TZ, PRIV and OBK-HDPL).

- 3. Check that no memory operations are ongoing by checking the BSY and DBNE bits in the FLASH_SECSR register and that the write buffer is empty by checking the WBNE bit in the FLASH_SECSR register.

- 4. Check and clear all the secure error flags due to previous operation.

- 5. Unlock the FLASH_SECCR register only if this register is not already unlocked, as described in Section 7.6.7 .

- 6. Enable write operations by setting the SECPG bit in the FLASH_SECCR register.

- 7. Write one flash-word corresponding to 16-byte data starting at 16-byte aligned address.

Note: WBNE flag indicates if the 128-bit write buffer is waiting for new data.

Note: No erase request, options change request, OBK swap sector or OBK alternate sector erase is allowed between first write and the completion of flash write operation.

- 8. Wait for the BSY bit to be cleared in the corresponding FLASH_SECSR register.

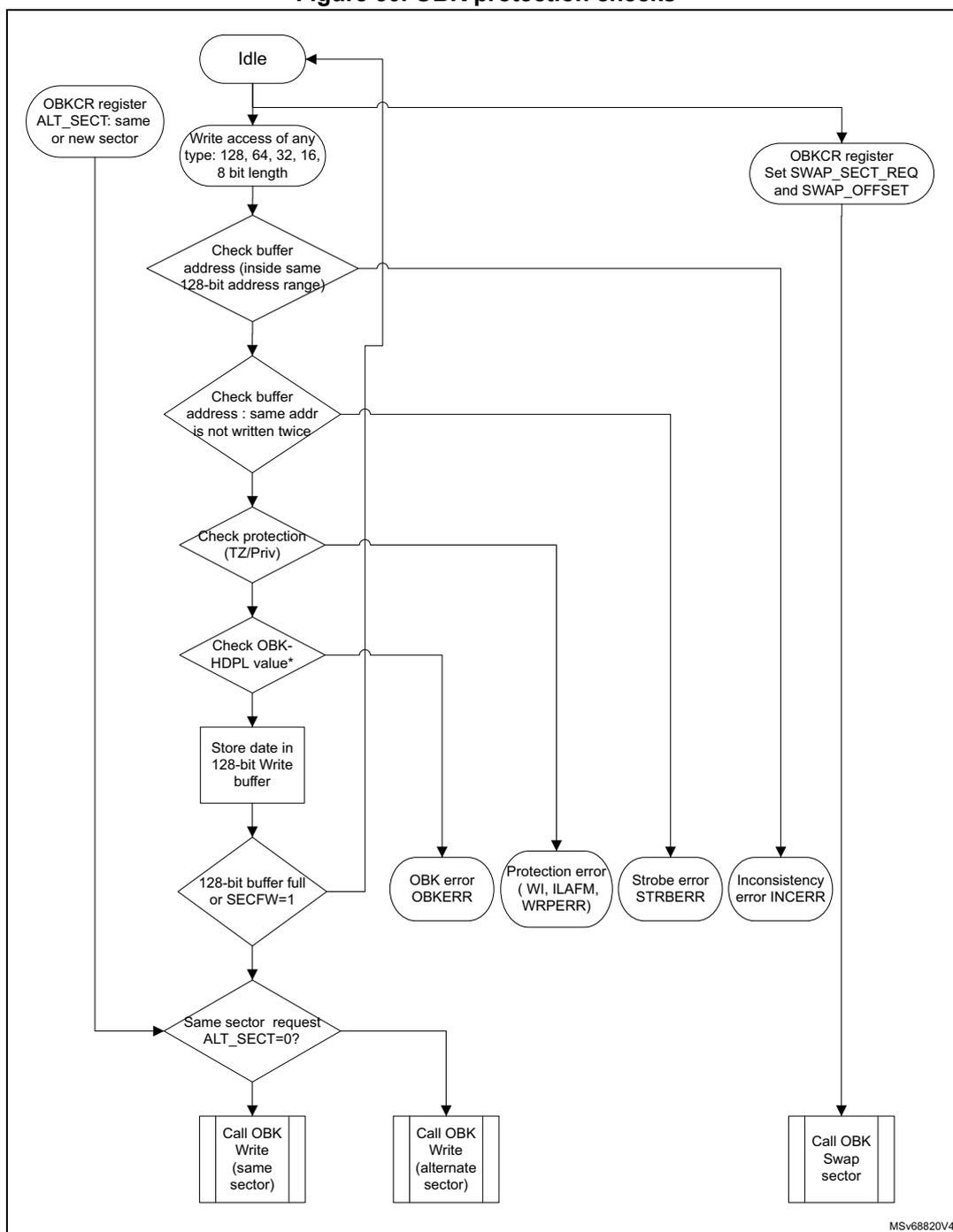

- 9. Clear PG bit in FLASH_SECCR register if there is not any programming request anymore in the bank.