13. Nested vectored interrupt controller (NVIC)

13.1 NVIC main features

The CPU1 NVIC features:

- • 63 maskable interrupt channels (not including the sixteen Cortex ® -M4 with FPU interrupt lines)

- • 16 programmable priority levels (four bits of interrupt priority are used)

- • Low-latency exception interrupt handling

- • Power management control

- • Implementation of System control registers

The CPU2 NVIC features:

- • 32 maskable interrupt channels (not including the sixteen Cortex ® -M0+ interrupt lines)

- • Four programmable priority levels (two bits of interrupt priority are used)

- • Low-latency exception interrupt handling

- • Power management control

The NVICs and the processor cores interfaces are closely coupled, resulting in low latency interrupt processing and efficient processing of late arriving interrupts.

All interrupts including the core exceptions are managed by the NVIC. For more information on exceptions and NVIC programming refer to STM32 Cortex ® -M4 MCUs and MPUs programming manual (PM0214) for Cortex ® -M4, and Cortex ® -M0+ programming manual for STM32L0, STM32G0, STM32WL and STM32WB Series (PM0223) for Cortex ® -M0+.

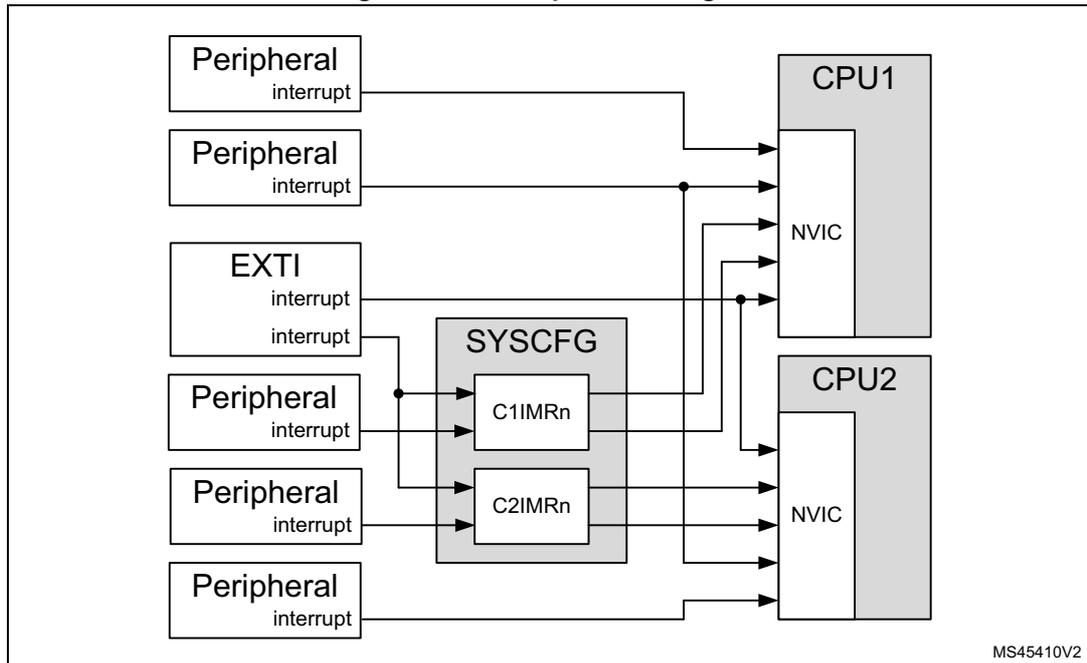

13.2 Interrupt block diagram

The different peripheral interrupts are connected in different ways, depending on the sharing between the two CPUs. To prevent a peripheral or EXTI interrupt to trigger both CPUs, they can be masked either in the NVIC, or, for the NVIC vector sharing multiple peripheral interrupts, by a pre-mask in the SYSCFG registers, see Section 10: System configuration controller (SYSCFG) .

The interrupt block diagram is shown in Figure 26 .

Figure 26. Interrupt block diagram

The diagram shows the interrupt signal routing for a dual-core system (CPU1 and CPU2). The components and connections are as follows:

- Peripheral interrupt sources: Multiple blocks labeled 'Peripheral interrupt' and one 'EXTI interrupt' block generate interrupt signals.

- Direct connections to CPU1: The top two peripheral interrupt signals go directly to the NVIC of CPU1.

- SYSCFG block: This block contains two sets of interrupt mask registers: C1IMRn (for CPU1) and C2IMRn (for CPU2).

- EXTI and lower Peripheral interrupts: These signals are routed into the SYSCFG block. Specifically, the EXTI interrupt and the three lower peripheral interrupts feed into both C1IMRn and C2IMRn.

- NVIC connections:

- The NVIC of CPU1 receives signals from the top two peripheral interrupts, the EXTI interrupt directly, and the output of the C1IMRn mask registers.

- The NVIC of CPU2 receives signals from the output of the C2IMRn mask registers and the bottom-most peripheral interrupt directly.

- CPUs: Both CPU1 and CPU2 have their own internal NVIC units to handle incoming interrupts.

Reference: MS45410V2

13.3 Interrupt and exception vectors

Each of the CPU1 and CPU2 has its own vector table, see, respectively, Table 53 and Table 54 , where shaded cells indicate the processor exceptions.

Table 53. CPU1 vector table

| Position | Priority | Type of priority | Acronym | Description | Address |

|---|---|---|---|---|---|

| - | - | - | - | Reserved | 0x0000 0000 |

| - | -3 | Fixed | Reset | Reset | 0x0000 0004 |

| - | -2 | Fixed | NMI | Non maskable interrupt HSE CSS, Flash ECC, and SRAM2 parity | 0x0000 0008 |

| - | -1 | Fixed | HardFault | All classes of fault | 0x0000 000C |

| - | 0 | Settable | MemManager | Memory manager | 0x0000 0010 |

| - | 1 | Settable | BusFault | Pre-fetch fault, memory access fault | 0x0000 0014 |

| - | 2 | Settable | UsageFault | Undefined instruction or illegal state | 0x0000 0018 |

| - | - | - | - | Reserved | 0x0000 001C 0x0000 0028 |

| - | 3 | Settable | SVCall | System service call via SWI instruction | 0x0000 002C |

| - | 4 | Settable | Debug | Debug monitor | 0x0000 0030 |

| - | - | - | - | Reserved | 0x0000 0034 |

| - | 5 | Settable | PendSV | Pendable request for system service | 0x0000 0038 |

| - | 6 | Settable | Systick | System tick timer | 0x0000 003C |

| 0 | 7 | Settable | WWDG | Window watchdog early wakeup | 0x0000 0040 |

| 1 | 8 | Settable | PVD | PVD through EXTI[16] (C1IMR2[20]) | 0x0000 0044 |

| 2 | 9 | Settable | TAMP, RTC_STAMP, LSE_CSS | Tamper, TimeStamp, LSECSS interrupt through EXTI[18] | 0x0000 0048 |

| 3 | 10 | Settable | RTC_WKUP | RTC wakeup interrupt through EXTI[19] | 0x0000 004C |

| 4 | 11 | Settable | Flash | Flash memory global interrupt and Flash memory ECC single error interrupt | 0x0000 0050 |

| 5 | 12 | Settable | RCC | RCC global interrupt | 0x0000 0054 |

| 6 | 13 | Settable | EXTI0 | EXTI line 0 interrupt through EXTI[0] | 0x0000 0058 |

| 7 | 14 | Settable | EXTI1 | EXTI line 1 interrupt through EXTI[1] | 0x0000 005C |

| 8 | 15 | Settable | EXTI2 | EXTI line 2 interrupt through EXTI[2] | 0x0000 0060 |

| 9 | 16 | Settable | EXTI3 | EXTI line 3 interrupt through EXTI[3] | 0x0000 0064 |

| 10 | 17 | Settable | EXTI4 | EXTI line 4 interrupt through EXTI[4] | 0x0000 0068 |

| 11 | 18 | Settable | DMA1_CH1 | DMA1 channel 1 interrupt | 0x0000 006C |

| 12 | 19 | Settable | DMA1_CH2 | DMA1 channel 2 interrupt | 0x0000 0070 |

| 13 | 20 | Settable | DMA1_CH3 | DMA1 channel 3 interrupt | 0x0000 0074 |

| 14 | 21 | Settable | DMA1_CH4 | DMA1 channel 4 interrupt | 0x0000 0078 |

| 15 | 22 | Settable | DMA1_CH5 | DMA1 channel 5 interrupt | 0x0000 007C |

| 16 | 23 | Settable | DMA1_CH6 | DMA1 channel 6 interrupt | 0x0000 0080 |

| 17 | 24 | Settable | DMA1_CH7 | DMA1 channel 7 interrupt | 0x0000 0084 |

Table 53. CPU1 vector table (continued)

| Position | Priority | Type of priority | Acronym | Description | Address |

|---|---|---|---|---|---|

| 18 | 25 | Settable | ADC1 | ADC1 global interrupt | 0x0000 0088 |

| 19 | 26 | - | - | Reserved | 0x0000 008C |

| 20 | 27 | - | - | Reserved | 0x0000 0090 |

| 21 | 28 | Settable | C2SEV PWR_C2H | CPU2 SEV through EXTI[40] PWR CPU2 HOLD wakeup interrupt | 0x0000 0094 |

| 22 | 29 | - | - | Reserved | 0x0000 0098 |

| 23 | 30 | Settable | EXTI[9:5] | EXTI line [9:5] interrupt through EXTI[9:5] (C1IMR1[25:21]) | 0x0000 009C |

| 24 | 31 | Settable | TIM1_BRK | Timer 1 break interrupt | 0x0000 00A0 |

| 25 | 32 | Settable | TIM1_UP | Timer 1 update (C1IMR1[13]) | 0x0000 00A4 |

| 26 | 33 | Settable | TIM1_TRG_COM | Timer 1 trigger and communication (C1IMR1[13]) | 0x0000 00A8 |

| 27 | 34 | Settable | TIM1_CC | Timer 1 capture compare interrupt | 0x0000 00AC |

| 28 | 35 | Settable | TIM2 | Timer 2 global interrupt | 0x0000 00B0 |

| 29 | 36 | Settable | PKA | Private key accelerator interrupt | 0x0000 00B4 |

| 30 | 37 | Settable | I2C1_EV | I2C1 event interrupt | 0x0000 00B8 |

| 31 | 38 | Settable | I2C1_ER | I2C1 error interrupt | 0x0000 00BC |

| 32 | 39 | - | - | Reserved | 0x0000 00C0 |

| 33 | 40 | - | - | Reserved | 0x0000 00C4 |

| 34 | 41 | Settable | SPI1 | SPI 1 global interrupt | 0x0000 00C8 |

| 35 | 42 | - | - | Reserved | 0x0000 00CC |

| 36 | 43 | Settable | USART1 | USART1 global interrupt | 0x0000 00D0 |

| 37 | 44 | - | - | Reserved | 0x0000 00D4 |

| 38 | 45 | - | - | Reserved | 0x0000 00D8 |

| 39 | 46 | Settable | TSC | TSC global interrupt | 0x0000 00DC |

| 40 | 47 | Settable | EXTI[15:10] | EXTI line [15:10] interrupt through EXTI[15:10] (C1IMR1[31:26]) | 0x0000 00E0 |

| 41 | 48 | Settable | RTC_ALARM | RTC alarms (A and B) interrupt through EXTI[17] | 0x0000 00E4 |

| 42 | 49 | - | - | Reserved | 0x0000 00E8 |

| 43 | 50 | Settable | PWR_SOTF PWR_BLEACT PWR_RFPHASE | PWR switching on the fly interrupt PWR end of BLE activity interrupt PWR end of critical radio phase interrupt | 0x0000 00EC |

| 44 | 51 | Settable | IPCC_C1_RX_IT | IPCC CPU1 RX occupied interrupt | 0x0000 00F0 |

| 45 | 52 | Settable | IPCC_C1_TX_IT | IPCC CPU1 TX free interrupt | 0x0000 00F4 |

| 46 | 53 | Settable | HSEM | Semaphore interrupt 0 to CPU1 | 0x0000 00F8 |

| 47 | 54 | Settable | LPTIM1 | LPtimer 1 global interrupt | 0x0000 00FC |

Table 53. CPU1 vector table (continued)

| Position | Priority | Type of priority | Acronym | Description | Address |

|---|---|---|---|---|---|

| 48 | 55 | Settable | LPTIM2 | LPtimer 2 global interrupt | 0x0000 0100 |

| 49 | 56 | - | - | Reserved | 0x0000 0104 |

| 50 | 57 | - | - | Reserved | 0x0000 0108 |

| 51 | 58 | - | - | Reserved | 0x0000 010C |

| 52 | 59 | Settable | AES2 | AES2 global interrupt | 0x0000 0110 |

| 53 | 60 | Settable | True RNG | True random number generator interrupt | 0x0000 0114 |

| 54 | 61 | Settable | FPU | Floating point unit interrupt | 0x0000 0118 |

| 55 | 62 | - | - | Reserved | 0x0000 011C |

| 56 | 63 | - | - | Reserved | 0x0000 0120 |

| 57 | 64 | - | - | Reserved | 0x0000 0124 |

| 58 | 65 | - | - | Reserved | 0x0000 0128 |

| 59 | 66 | - | - | Reserved | 0x0000 012C |

| 60 | 67 | - | - | Reserved | 0x0000 0130 |

| 61 | 68 | - | - | Reserved | 0x0000 0134 |

| 62 | 69 | Settable | DMAMUX1_OVR | DMAMUX1 overrun interrupt | 0x0000 0138 |

Table 54. CPU2 vector table

| Position | Priority | Type of priority | Acronym | Description | Address |

|---|---|---|---|---|---|

| - | - | - | - | Reserved | 0x0000 0000 |

| - | -3 | Fixed | Reset | Reset | 0x0000 0004 |

| -14 | -2 | Fixed | NMI | Non maskable interrupt HSE CSS, Flash ECC, and SRAM2 parity | 0x0000 0008 |

| -13 | -1 | Fixed | HardFault | All classes of fault | 0x0000 000C |

| - | - | - | - | Reserved | 0x0000 0010 0x0000 0028 |

| -5 | 0 | Settable | SVCall | System service call via SWI instruction | 0x0000 002C |

| - | - | - | - | Reserved | 0x0000 0030 0x0000 0034 |

| -2 | 1 | Settable | PendSV | Pendable request for system service | 0x0000 0038 |

| -1 | 2 | Settable | Systick | System tick timer | 0x0000 003C |

| 0 | 3 | Settable | - | Reserved | 0x0000 0040 |

| 1 | 4 | Settable | PVD | PVD through EXTI[16] (C2IMR2[20]) | 0x0000 0044 |

| 2 | 5 | Settable | RTC_WKUP, TAMP, RTC_STAMP LSE_CSS, RTC_ALARM | RTC wakeup interrupt through EXTI[19] (C2IMR1[3]) Tamper, TimeStamp LSECSS interrupt through EXTI[18] (C2IMR1[0]) RTC alarms (A and B) interrupt through EXTI[17] (C2IMR1[4]) | 0x0000 0048 |

| 3 | 6 | - | - | Reserved | 0x0000 004C |

| 4 | 7 | Settable | RCC FLASH C1SEV | RCC global interrupt (C2IMR1[5]) Flash memory global interrupt and Flash memory ECC single error interrupt (C2IMR1[6]) CPU1 SEV through EXTI[41] | 0x0000 0050 |

| 5 | 8 | Settable | EXTI[1:0] | EXTI line 1:0 interrupt through EXTI[1:0] (C2IMR1[17:16]) | 0x0000 0054 |

| 6 | 9 | Settable | EXTI[3:2] | EXTI line 3:2 interrupt through EXTI[3:2] (C2IMR1[19:18]) | 0x0000 0058 |

| 7 | 10 | Settable | EXTI[15:4] | EXTI line 15:4 interrupt through EXTI[15:4] (C2IMR1[31:20]) | 0x0000 005C |

| 8 | 11 | Settable | TSC | TSC global interrupt (C2IMR2[21]) | 0x0000 0060 |

| 9 | 12 | Settable | DMA1_CH[3:1] | DMA1 channel 3:1 interrupt (C2IMR2[2:0]) | 0x0000 0064 |

| 10 | 13 | Settable | DMA1_CH[7:4] | DMA1 channel 7:4 interrupt (C2IMR2[6:3]) | 0x0000 0068 |

| 11 | 14 | Settable | DMAMUX1_OVR | DMAMUX1 overrun interrupt (C2IMR2[15]) | 0x0000 006C |

| 12 | 15 | Settable | ADC1 | ADC1 global interrupt (C2IMR1[12]) | 0x0000 0070 |

| 13 | 16 | Settable | LPTIM1 | LP timer 1 global interrupt | 0x0000 0074 |

| 14 | 17 | Settable | LPTIM2 | LP timer 2 global interrupt | 0x0000 0078 |

Table 54. CPU2 vector table (continued)

| Position | Priority | Type of priority | Acronym | Description | Address |

|---|---|---|---|---|---|

| 15 | 18 | Settable | TIM1_BRK, TIM1_UP, TIM1_TRG_COM, TIM1_CC | Timer 1 break, update, trigger and communication, capture compare interrupt | 0x0000 007C |

| 16 | 19 | Settable | TIM2 | Timer 2 global interrupt | 0x0000 0080 |

| 17 | 20 | - | - | Reserved | 0x0000 0084 |

| 18 | 21 | - | - | Reserved | 0x0000 0088 |

| 19 | 22 | Settable | IPCC_C2_RX_IT IPCC_C2_TX_IT HSEM | IPCC CPU2 RX occupied interrupt IPCC CPU2 TX free interrupt Semaphore interrupt 1 o CPU2 | 0x0000 008C |

| 20 | 23 | Settable | PKA True RNG | Private key accelerator interrupt (C2IMR1[8]) True random number generator interrupt (C2IMR1[9]) | 0x0000 0090 |

| 21 | 24 | Settable | AES2 | AES2 global interrupt | 0x0000 0094 |

| 22 | 25 | - | - | Reserved | 0x0000 0098 |

| 23 | 26 | Settable | I2C1_EV I2C1_ER | I2C1 event interrupt I2C1 error interrupt | 0x0000 009C |

| 24 | 27 | - | - | Reserved | 0x0000 00A0 |

| 25 | 28 | Settable | SPI1 | SPI1 global interrupt | 0x0000 00A4 |

| 26 | 29 | - | - | Reserved | 0x0000 00A8 |

| 27 | 30 | Settable | USART1 | USART1 global interrupt | 0x0000 00AC |

| 28 | 31 | - | - | Reserved | 0x0000 00B0 |

| 29 | 32 | - | - | Reserved | 0x0000 00B4 |

| 30 | 33 | Settable | BLE_BLUE_IT BLE_RFC_IT BLE_RFFMS_IT BLE_HOST_WKUP | BLE blue controller interrupt BLE radio control interrupt BLE radio states interrupt BLE host wakeup interrupt | 0x0000 00B8 |

| 31 | 34 | - | - | Reserved | 0x0000 00BC |

13.4 Interrupt list

The device wakeup sources are listed in Table 55 . Depending on its origin, the wakeup is handled according to different types, see Section 14.4: EXTI functional behavior for more information.

Some wakeup sources are able to generate an event to the CPUs. see Event column.

The wakeup source capability to wakeup CPU1 and or CPU2 is listed in Wakeup column.

For CPUs interrupt handling see Section 13: Nested vectored interrupt controller (NVIC) .

For Wakeup handling see Section 14: Extended interrupt and event controller (EXTI) .

Table 55. Wakeup interrupt table

| EXTI no. | Acronym | Description | EXTI type | Event | Wakeup |

|---|---|---|---|---|---|

| 0 | EXTI[0] | EXTI line 0 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 1 | EXTI[1] | EXTI line 1 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 2 | EXTI[2] | EXTI line 2 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 3 | EXTI[3] | EXTI line 3 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 4 | EXTI[4] | EXTI line 4 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 5 | EXTI[5] | EXTI line 5 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 6 | EXTI[6] | EXTI line 6 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 7 | EXTI[7] | EXTI line 7 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 8 | EXTI[8] | EXTI line 8 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 9 | EXTI[8] | EXTI line 9 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 10 | EXTI[10] | EXTI line 10 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 11 | EXTI[11] | EXTI line 11 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 12 | EXTI[12] | EXTI line 12 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 13 | EXTI[13] | EXTI line 13 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 14 | EXTI[14] | EXTI line 14 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 15 | EXTI[15] | EXTI line 15 from SYSCFG | Configurable A | Yes | CPU1 and CPU2 |

| 16 | PVD | PVD line | Configurable A | No | CPU1 and CPU2 |

| 17 | RTC_ALARM | RTC Alarms (A and B) interrupt | Configurable A | Yes | CPU1 and CPU2 |

| 18 | TAMP, RTC_STAMP, LSE_CSS | RTC Tamper interrupt RTC TimeStamp interrupt RCC LSECSS interrupt | Configurable A | Yes | CPU1 and CPU2 |

| 19 | RTC_WKUP | RTC wakeup interrupt | Configurable A | Yes | CPU1 and CPU2 |

| 20 | Reserved | - | - | - | - |

| 21 | Reserved | - | - | - | - |

| 22 | I2C1 wakeup | I2C1 wakeup | Direct B | No | CPU1 and CPU2 |

| 23 | Reserved | - | - | - | - |

| 24 | USART1 | USART1 wakeup | Direct B | No | CPU1 and CPU2 |

| 25 | Reserved | - | - | - | - |

| 26 | Reserved | - | - | - | - |

| 27 | Reserved | - | - | - | - |

| 28 | Reserved | - | - | - | - |

| 29 | LPTIM1 wakeup | LP timer 1 wakeup | Direct B | No | CPU1 and CPU2 |

| 30 | LPTIM2 wakeup | LP timer 2 wakeup | Direct B | No | CPU1 and CPU2 |

| 31 | Reserved | - | - | - | - |

Table 55. Wakeup interrupt table (continued)

| EXTI no. | Acronym | Description | EXTI type | Event | Wakeup |

|---|---|---|---|---|---|

| 32 | Reserved | - | - | - | - |

| 33 | Reserved | - | - | - | - |

| 34 | Reserved | - | - | - | - |

| 35 | Reserved | - | - | - | - |

| 36 | IPCC CPU1 interrupts | IPCC CPU1 RX occupied and TX free interrupts | Direct C | No | CPU1 (1) |

| 37 | IPCC CPU2 interrupts | IPCC CPU2 RX occupied and TX free interrupts | Direct C | No | CPU2 (2) |

| 38 | HSEM interrupt 0 | Semaphore interrupt 0 for CPU1 | Direct C | No | CPU1 (1) |

| 39 | HSEM interrupt 1 | Semaphore interrupt 1 for CPU2 | Direct C | No | CPU2 (2) |

| 40 | C2SEV | CPU2 SEV line | Configurable A | Yes | CPU1 (3) |

| 41 | C1SEV | CPU1 SEV line | Configurable A | Yes | CPU2 (4) |

| 42 | Flash interrupt | Flash ECC and global interrupts | Direct C | No | CPU1 and CPU2 |

| 43 | Reserved | - | - | - | - |

| 44 | HSE CSS interrupt | RCC HSE CSS interrupt | Direct C | No | CPU1 and CPU2 |

| 45 | BLE interrupts | BLE, RADIO, & RF_FSM interrupts | Direct B | No | CPU2 (2) |

| 46 | Reserved | - | - | - | - |

| 47 | Reserved | - | - | - | - |

| 48 | CDBGPWRUPREQ | Debug power up request wakeup | Direct | No | CPU1 and CPU2 |

- 1. For correct operation the EXTI direct event C2IMRx.IMn bit must be set to 0 before CPU1 uses this direct event.

- 2. For correct operation the EXTI direct event C1IMRx.IMn bit must be set to 0 before CPU2 uses this direct event.

- 3. For correct operation the EXTI configurable event both C2IMRx.IMn and C2EMRx.EMn bits must be set to 0 before CPU1 uses this configurable event.

- 4. For correct operation the EXTI configurable event both C1IMRx.IMn and C1EMRx.EMn bits must be set to 0 before CPU2 uses this configurable event.