36. Secure AES coprocessor (SAES)

36.1 SAES introduction

The secure AES coprocessor (SAES) encrypts or decrypts data in compliance with the advanced encryption standard (AES) defined by NIST. It incorporates a protection against side-channel attacks (SCA), including differential power analysis (DPA), required for SESIP and PSA security assurance level 3 target.

SAES supports ECB, CBC, CTR, GCM, GMAC, and CCM chaining modes for key sizes of 128 or 256 bits, as well as special modes such as hardware secret key encryption/decryption (wrapped-key mode) and key sharing with faster CRYP peripheral (shared-key mode).

SAES has the possibility to load by hardware STM32 hardware secret master keys (boot hardware key BHK, application hardware key AHK, and derived hardware unique key DHUK), usable but not readable by the application.

The peripheral supports DMA single transfers for incoming and outgoing data (two DMA channels are required). It is hardware-linked with the true random number generator (TRNG) and with the CRYP peripheral.

36.2 SAES main features

- • Compliant with NIST FIPS publication 197 “ Advanced encryption standard (AES) ” (November 2001)

- • Encryption and decryption with multiple chaining modes:

- – Electronic codebook (ECB) mode

- – Cipher block chaining (CBC) mode

- – Counter (CTR) mode

- – Galois counter mode (GCM)

- – Galois message authentication code (GMAC) mode

- – Counter with CBC-MAC (CCM) mode

- • Protection against side-channel attacks (SCA), incl. differential power analysis (DPA), required for SESIP and PSA security assurance level 3 target

- • 128-bit data block processing, supporting cipher key lengths of 128-bit and 256-bit

- – 480 or 680 clock cycle latency in ECB mode for processing one 128-bit block with, respectively, 128-bit or 256-bit key

- • Hardware secret key encryption/ decryption (Wrapped-key mode)

- • Using dedicated key bus, optional key sharing with faster CRYP peripheral (shared-key mode), controlled by SAES

- • Integrated key scheduler to compute the last round key for ECB/CBC decryption

- • 256-bit of write-only registers for storing cryptographic keys (eight 32-bit registers)

- – Optional 128-bit or 256-bit hardware loading of two hardware secret keys (BHK, DHUK) that can be XOR-ed together

- – Optional 128-bit or 256-bit hardware loading of nonvolatile application hardware keys (AHK), secret to software and stored in the embedded flash memory

- • 128-bit of registers for storing initialization vectors (four 32-bit registers)

- • 32-bit buffer for data input and output

- • Automatic data flow control supporting two direct memory access (DMA) channels, one for incoming data, one for processed data. Only single transfers are supported.

- • Data-swapping logic to support 1-, 8-, 16-, or 32-bit data

- • AMBA AHB slave peripheral, accessible through 32-bit word single accesses only. Other access types generate an AHB error, and other than 32-bit writes may corrupt the register content.

- • Possibility for software to suspend a message if SAES needs to process another message with a higher priority, then resume the original message

36.3 SAES implementation

The devices have one SAES peripheral, connected with TAMP backup registers (BHK - boot hardware key) and with the Flash memory interface (AHK - application hardware key), and implemented as per the following table. It shares the key with the CRYP peripheral. For comparison, the CRYP peripheral is also included in the table.

Table 324. CRYP versus SAES features

| Modes or features (1) | CRYP | SAES |

|---|---|---|

| ECB, CBC chaining | X | X |

| CTR, CCM, GCM chaining | X | X |

| AES 128-bit ECB encryption in cycles | 14 | 480 |

| DHUK and BHK key selection | - | X |

| Resistance to side-channel attacks | - | X |

| Shared key between SAES and CRYP | X | |

| Key sizes in bits | 128, 192, 256 | 128, 256 |

1. X = supported.

36.4 SAES functional description

36.4.1 SAES block diagram

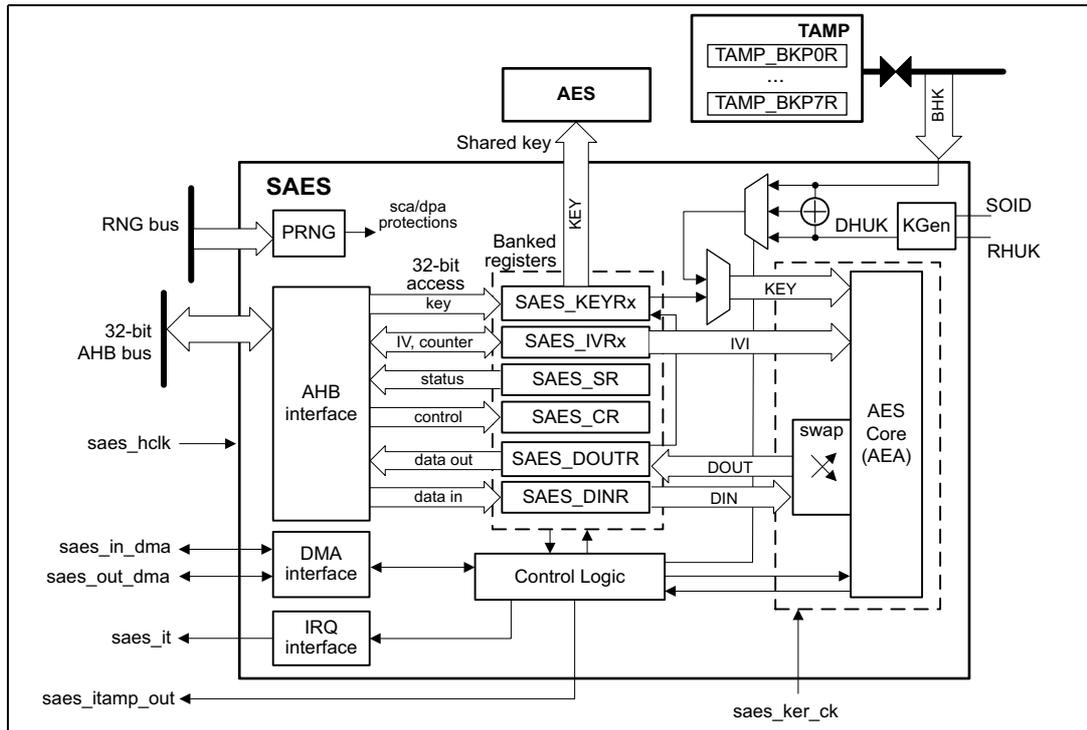

Figure 352 shows the block diagram of SAES.

Figure 352. SAES block diagram

The block diagram illustrates the internal architecture of the SAES peripheral. At the center is the 'AES Core (AEA)' which is connected to a 'swap' block. The 'swap' block feeds into 'DOUT' and 'DIN' lines that connect to 'SAES_DOUTR' and 'SAES_DINR' registers respectively. These registers are part of a 'Banked registers' group which also includes 'SAES_KEYRx', 'SAES_IVRx', 'SAES_SR', and 'SAES_CR'. A 'Control Logic' block manages these registers and interfaces with the 'AHB interface', 'DMA interface', and 'IRQ interface'. The 'AHB interface' connects to a '32-bit AHB bus' and provides 'status' and 'control' signals. The 'DMA interface' handles 'saes_in_dma' and 'saes_out_dma' signals. The 'IRQ interface' generates the 'saes_it' interrupt. A 'PRNG' block connected to an 'RNG bus' provides 'sca/dpa protections'. A 'Shared key' is passed from the 'AES' block to the 'KEY' input of the 'AES Core (AEA)'. This 'KEY' is also derived from 'RHUK' and 'BHK' inputs through a 'KGen' block and a 'DHUK' calculation block. The 'TAMP' block contains backup registers (TAMP_BKP0R to TAMP_BKP7R) and generates the 'saes_itamp_out' signal when a tamper event occurs.

Note: AES represents the CRYP peripheral.

36.4.2 SAES internal signals

Table 325 describes the user relevant internal signals interfacing the SAES peripheral.

Table 325. SAES internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| saes_hclk | Input | AHB bus clock |

| saes_ker_ck | Input | SAES kernel clock. |

| saes_it | Output | SAES interrupt request |

| saes_in_dma | Input/Output | SAES incoming data DMA single request/acknowledge |

| saes_out_dma | Input/Output | SAES processed data DMA single request/acknowledge |

| saes_itamp_out | Output | Tamper event signal to TAMP (XOR-ed), triggered when an unexpected hardware fault occurs. When this signal is triggered, SAES automatically clears key registers. A reset is required for SAES to be usable again. |

| RHUK | Input | 256-bit root hardware unique key (nonvolatile, unique per device and secret to software), used to internally compute the derived hardware unique key (DHUK) |

| BHK (1) | Input | 256-bit boot hardware key (BHK) stored in tamper-resistant backup registers and written during boot. Once written, this key cannot be read nor written by any application until the next product reset. |

| Signal name | Signal type | Description |

|---|---|---|

| AHK (2) | Input | 128-bit or 256-bit nonvolatile application hardware key from the embedded Flash memory, secret to software. |

| SOID | Input | Static operating ID hardware input used during each DHUK computation. Its change causes the erasure of key registers and sets the KEIF flag. |

- 1. Connected to a set of backup registers in TAMP peripheral that are written, then read/write locked, by the application software (see Section 36.4.17 for details).

- 2. Connected to the embedded flash memory controller (see Section 36.4.17 for details).

36.4.3 SAES reset and clocks

The SAES peripheral is clocked by the AHB bus clock. It has a dedicated reset bit and a dedicated kernel clock, controlled through the RCC.

The SAES reset in RCC is mandatory when a hardware tamper event occurs in SAES. Refer to Managing tamper errors in Section 36.4.19 for details.

After clocking then releasing the reset of the SAES peripheral in the RCC, SAES automatically draws random numbers from the RNG, setting the BUSY bit of the SAES_SR register. Refer to the RNG error interrupt flag (RNGEIF) in Section 36.4.19 for details.

This background task must be completed before the device enters a low-power mode.

36.4.4 SAES symmetric cipher implementation

The secure AES coprocessor (SAES) is a 32-bit AHB peripheral that encrypts or decrypts 16-byte blocks of data using the advanced encryption standard (AES). It also implements a set of approved AES symmetric key security functions summarized in Table 326 . Those functions can be certified NIST PUB 140-3.

Table 326. SAES approved symmetric key functions| Operations | Algorithm | Specification | Key bit lengths | Chaining modes |

|---|---|---|---|---|

| Encryption, decryption | AES | FIPS PUB 197 NIST SP800-38A | 128, 256 | ECB, CBC, CTR |

| Authenticated encryption or decryption | NIST SP800-38C NIST SP800-38D | GCM, CCM | ||

| Cipher-based message authentication code | NIST SP800-38D | GMAC |

SAES can be used directly by the CPU, or indirectly, using two DMA channels (one for the plaintext, one for the ciphertext).

It is possible to suspend then resume any SAES processing, following the sequence described in Section 36.4.8 .

36.4.5 SAES encryption or decryption typical usage

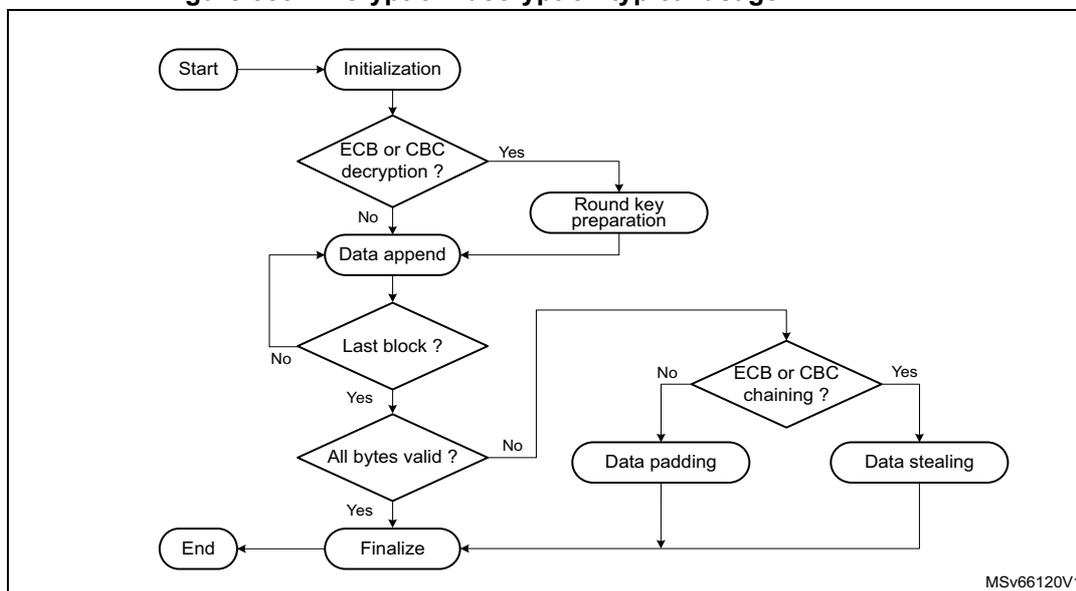

The following figure shows a typical operation for encryption or decryption.

Figure 353. Encryption/ decryption typical usage

graph TD

Start([Start]) --> Init([Initialization])

Init --> Dec{ECB or CBC decryption?}

Dec -- Yes --> RoundKey([Round key preparation])

Dec -- No --> DataAppend([Data append])

RoundKey --> LastBlock{Last block?}

DataAppend --> LastBlock

LastBlock -- Yes --> AllBytesValid{All bytes valid?}

LastBlock -- No --> DataAppend

AllBytesValid -- Yes --> Finalize([Finalize])

AllBytesValid -- No --> Chaining{ECB or CBC chaining?}

Chaining -- Yes --> DataStealing([Data stealing])

Chaining -- No --> DataPadding([Data padding])

DataStealing --> Finalize

DataPadding --> Finalize

Finalize --> End([End])

Initialization

The SAES peripheral is initialized according to the chaining mode. Refer to Section 36.4.9: SAES basic chaining modes (ECB, CBC) and Section 36.4.10: SAES counter (CTR) mode for details.

Data append

This section describes different ways of appending data for processing. For ECB or CBC chaining modes, refer to Section 36.4.7: SAES ciphertext stealing and data padding if the size of data to process is not a multiple of 16 bytes. The last block management in these cases is more complex than what is described in this section.

Appending data using the CPU in polling mode

This method uses flag polling to control the data append through the following sequence:

- 1. Enable the SAES peripheral when KEYVALID is set, by setting the EN bit of the SAES_CR register (if not already done).

- 2. Repeat the following sub-sequence until the payload is entirely processed:

- a) Write four input data words into the SAES_DINR register.

- b) Wait until the status flag CCF is set in the SAES_ISR register, then read the four data words from the SAES_DOUTR register.

- c) Clear the CCF flag, by setting the CCF bit of the SAES_ICR register.

- d) If the next processing block is the last block, pad (when applicable) the data with zeros to obtain a complete block, and specify the number of non-valid bytes (using

NPBLB[3:0]) in case of GCM payload encryption or CCM payload decryption (otherwise the tag computation is wrong).

- As the data block just processed is the last block of the message, optionally discard the data that is not part of the message/payload, then disable the SAES peripheral by clearing EN.

Note: Up to three wait cycles are automatically inserted between two consecutive writes to the SAES_DINR register, to allow sending the key to the AES co-processor.

NPBLB[3:0] bitfield is not used in header phase of GCM, GMAC and CCM chaining modes.

Appending data using the CPU in interrupt mode

The method uses interrupt from the SAES peripheral to control the data append, through the following sequence:

- Enable interrupts from SAES, by setting the CCFIE bit of the SAES_IER register.

- Enable the SAES peripheral when KEYVALID is set, by setting EN (if not already done).

- Write first four input data words into the SAES_DINR register.

- Handle the data in the SAES interrupt service routine. Upon each interrupt:

- Read four output data words from the SAES_DOUTR register.

- Clear the CCF flag and thus the pending interrupt, by setting the CCF bit of the SAES_ICR register.

- If the next processing block is the last block of the message, pad (when applicable) the data with zeros to obtain a complete block, and specify the number of non-valid bytes (through NPBLB[3:0]) in case of GCM payload encryption or CCM payload decryption (otherwise the tag computation is wrong). Then proceed with point 4e).

- If the data block just processed is the last block of the message, optionally discard the data that are not part of the message/payload, then disable the SAES peripheral by clearing EN and quit the interrupt service routine.

- Write next four input data words into the SAES_DINR register and quit the interrupt service routine.

Note: SAES is tolerant of delays between consecutive read or write operations, which allows, for example, an interrupt from another peripheral to be served between two SAES computations.

The NPBLB[3:0] bitfield is not used in the header phase of GCM, GMAC, and CCM chaining modes.

Appending data using DMA

With this method, all the transfers and processing are managed by DMA and SAES. Proceed as follows:

- If the last block of the message to process is shorter than 16 bytes, prepare the last four-word data block by padding the remainder of the block with zeros.

- Configure the DMA controller so as to transfer the data to process from the memory to the SAES peripheral input and the processed data from the SAES peripheral output to the memory, as described in Section 36.6: SAES DMA requests . Configure the DMA controller so as to generate an interrupt on transfer completion. For GCM payload encryption or CCM payload decryption, the DMA transfer must not include the last four-word block if padded with zeros. The sequence described in Appending data using the CPU in polling mode must be used instead for this last block, because the

NPBLB[3:0] bitfield must be set up before processing the block, for SAES to compute a correct tag.

- 3. Enable the SAES peripheral when KEYVALID is set, by setting EN (if not already done).

- 4. Enable DMA requests, by setting DMAINEN and DMAOUTEN.

- 5. Upon DMA interrupt indicating the transfer completion, get the SAES-processed data from the memory.

Note:

The CCF flag has no use with this method because the reading of the SAES_DOUTR register is managed by DMA automatically, without any software action, at the end of the computation phase.

The NPBLB[3:0] bitfield is not used in the header phase of GCM, GMAC, and CCM chaining modes.

36.4.6 SAES authenticated encryption, decryption, and cipher-based message authentication

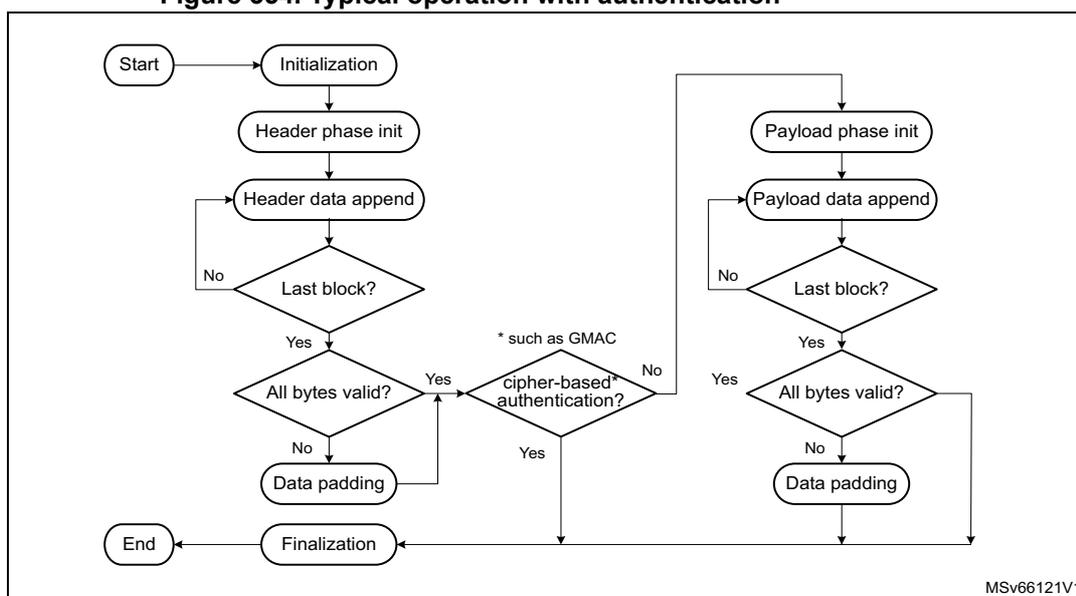

The following figure shows a typical operation for authenticated encryption or decryption, and for cipher-based message authentication.

Figure 354. Typical operation with authentication

graph TD

Start([Start]) --> Init([Initialization])

Init --> HInit([Header phase init])

HInit --> HData[Header data append]

HData --> HLast{Last block?}

HLast -- No --> HData

HLast -- Yes --> HValid{All bytes valid?}

HValid -- No --> HPad[Data padding]

HPad --> HAuth{cipher-based* authentication?}

HValid -- Yes --> HAuth

HAuth -- Yes --> Final([Finalization])

HAuth -- No --> PInit([Payload phase init])

PInit --> PData[Payload data append]

PData --> PLast{Last block?}

PLast -- No --> PData

PLast -- Yes --> PValid{All bytes valid?}

PValid -- No --> PPad[Data padding]

PPad --> Final

PValid -- Yes --> Final

Final --> End([End])

style HAuth note for HAuth "* such as GMAC"

Section 36.4.11: SAES Galois/counter mode (GCM) and Section 36.4.13: SAES counter with CBC-MAC (CCM) describe detailed sequences supported by SAES.

Cipher-based message authentication flow omits the payload phase, as shown in the figure. Detailed sequence supported by SAES is described in Section 36.4.12: SAES Galois message authentication code (GMAC) .

36.4.7 SAES ciphertext stealing and data padding

When using SAES in ECB or CBC modes to manage messages the size of which is not a multiple of the block size (16 bytes), the application must use ciphertext stealing techniques such as those described in NIST Special Publication 800-38A, Recommendation for Block

Cipher Modes of Operation: Three Variants of Ciphertext Stealing for CBC Mode. Since SAES does not implement such techniques, the application must complete the last block of input data using data from the second last block .

Note: Ciphertext stealing techniques are not documented in this reference manual.

Similarly, in modes other than ECB or CBC, an incomplete input data block (that is, a block with input data shorter than 16 bytes) must be padded with zeros prior to encryption. That is, extra bits must be appended to the trailing end of the data string. After decryption, the extra bits must be discarded. Since SAES does not implement automatic data padding operation to the last block , the application must follow the recommendation given in this document to manage messages the size of which is not a multiple of 16 bytes.

36.4.8 SAES suspend and resume operations

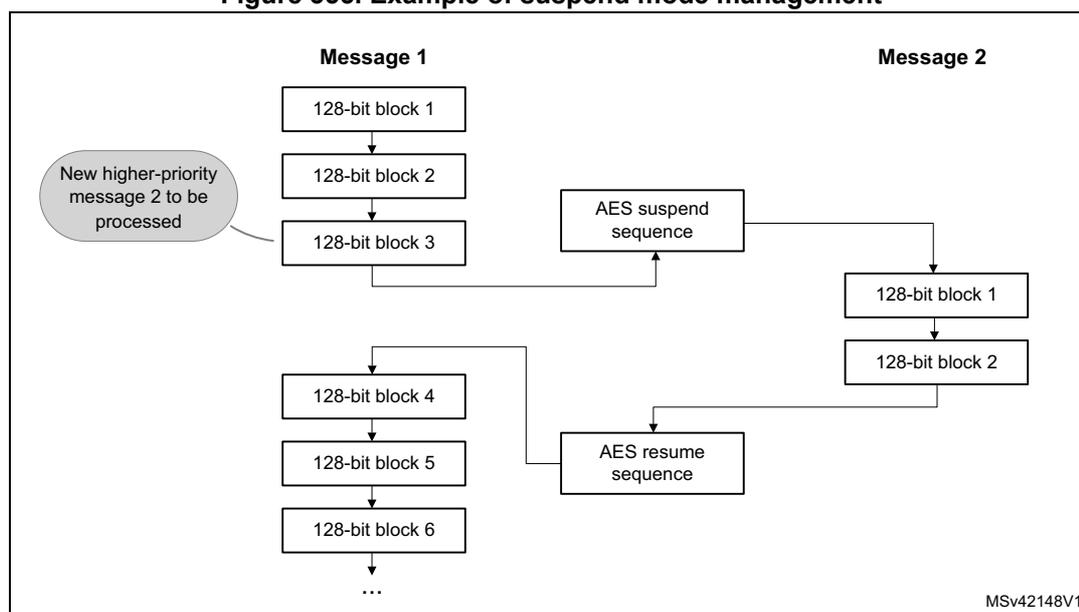

A message can be suspended to process another message with a higher priority. When the higher-priority message is sent, the suspended message can resume. This applies to both encryption and decryption mode.

Suspend and resume operations do not break the chaining operation. The message processing can resume as soon as SAES is enabled again, to receive a next data block.

Figure 355 gives an example of suspend and resume operations: Message 1 is suspended in order to send a shorter and higher-priority Message 2.

Figure 355. Example of suspend mode management

The diagram illustrates the flow of data blocks for two messages, Message 1 and Message 2, during suspend and resume operations. Message 1 consists of 128-bit blocks 1 through 6, followed by an ellipsis. Message 2 consists of 128-bit blocks 1 and 2. A callout bubble indicates that Message 2 is a 'New higher-priority message 2 to be processed'. The flow shows Message 1 blocks 1, 2, and 3 being processed. After block 3, an 'AES suspend sequence' is initiated, which suspends Message 1 and allows Message 2 to be processed. Message 2 blocks 1 and 2 are then processed. After Message 2, an 'AES resume sequence' is initiated, which resumes Message 1 processing from block 4. Message 1 blocks 4, 5, and 6 are then processed, followed by an ellipsis. The diagram is labeled MSv42148V1 in the bottom right corner.

A detailed description of suspend and resume operations is in the sections dedicated to each chaining mode.

36.4.9 SAES basic chaining modes (ECB, CBC)

ECB is the simplest mode of operation. There are no chaining operations, and no special initialization stage. The message is divided into blocks and each block is encrypted or decrypted separately. When decrypting in ECB, a special key scheduling is required before processing the first block.

Figure 356 and Figure 357 describe the electronic codebook (ECB) chaining implementation in encryption and in decryption, respectively. To select ECB chaining mode, write CHMOD[2:0] with 0x0.

Figure 356. ECB encryption

![Diagram of ECB encryption showing two blocks, Block 1 and Block 2. Each block consists of a Swap management block, an Encrypt block, and another Swap management block. Inputs are DIN (plaintext P1, P2), KEY, and DATATYPE[1:0]. Outputs are DOUT (ciphertext C1, C2). A legend indicates input is white and output is grey.](/RM0477-STM32H7Rx-7Sx/d7884894428419ff104e8d08737a485c_img.jpg)

The diagram illustrates the ECB encryption process for two blocks, Block 1 and Block 2. Each block follows a similar internal structure: a 16-bit DIN (plaintext P1 or P2) is input to a 'Swap management' block, which also receives 'DATATYPE[1:0]'. The output of this block, labeled I1 or I2, is then input to an 'Encrypt' block along with a 'KEY'. The output of the 'Encrypt' block, labeled O1 or O2, is input to a second 'Swap management' block, which again receives 'DATATYPE[1:0]'. The final output of each block is DOUT (ciphertext C1 or C2). A legend on the left indicates that white boxes represent 'input' and grey boxes represent 'output'.

Figure 357. ECB decryption

![Diagram of ECB decryption showing two blocks, Block 1 and Block 2. Each block consists of a Swap management block, a Decrypt block, and another Swap management block. Inputs are DIN (ciphertext C1, C2), KEY, and DATATYPE[1:0]. Outputs are DOUT (plaintext P1, P2). A legend indicates input is white and output is grey.](/RM0477-STM32H7Rx-7Sx/f5fcf648b8b70bfec07e09cacf6c3b8f_img.jpg)

The diagram illustrates the ECB decryption process for two blocks, Block 1 and Block 2. Each block follows a similar internal structure: a 16-bit DIN (ciphertext C1 or C2) is input to a 'Swap management' block, which also receives 'DATATYPE[1:0]'. The output of this block, labeled I1 or I2, is then input to a 'Decrypt' block along with a 'KEY'. The output of the 'Decrypt' block, labeled O1 or O2, is input to a second 'Swap management' block, which again receives 'DATATYPE[1:0]'. The final output of each block is DOUT (plaintext P1 or P2). A legend on the left indicates that white boxes represent 'input' and grey boxes represent 'output'.

In CBC encryption mode the output of each block chains with the input of the following block. To make each message unique, an initialization vector is used during the first block processing. When decrypting in CBC, a special key scheduling is required before processing the first block.

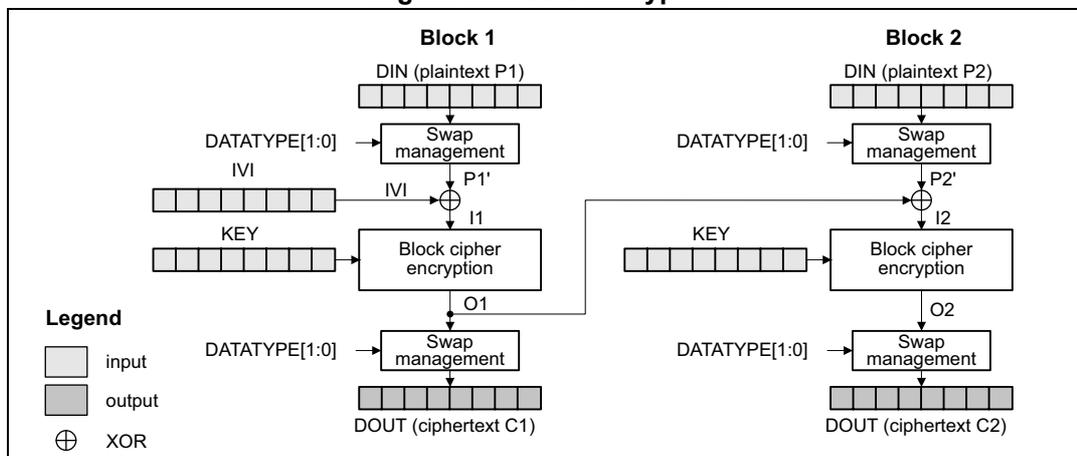

Figure 358 and Figure 359 describe the cipher block chaining (CBC) implementation in encryption and in decryption, respectively. To select this chaining mode, write CHMOD[2:0] with 0x1.

Figure 358. CBC encryption

Figure 358. CBC encryption

The diagram illustrates the CBC encryption process for two blocks, Block 1 and Block 2.

- Block 1:

- DIN (plaintext P1) is input to a Swap management block.

- The Swap management block outputs P1'.

- P1' is XORed with IVI.

- The result is input to the Block cipher encryption block, which also takes KEY as input.

- The Block cipher encryption block outputs O1.

- O1 is input to another Swap management block.

- The Swap management block outputs DOUT (ciphertext C1).

- Block 2:

- DIN (plaintext P2) is input to a Swap management block.

- The Swap management block outputs P2'.

- P2' is XORed with the previous ciphertext O1.

- The result is input to the Block cipher encryption block, which also takes KEY as input.

- The Block cipher encryption block outputs O2.

- O2 is input to another Swap management block.

- The Swap management block outputs DOUT (ciphertext C2).

Legend

- input (white box)

- output (grey box)

- XOR (circle with a cross)

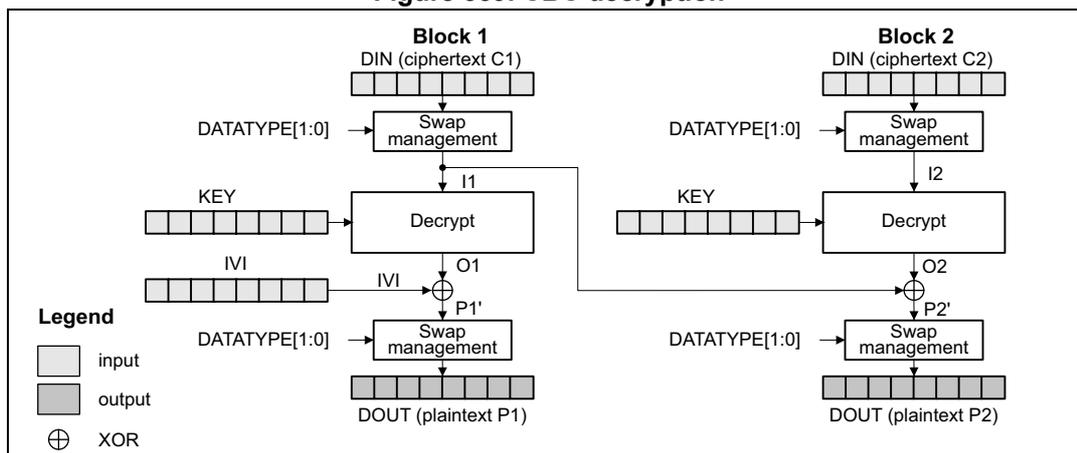

Figure 359. CBC decryption

Figure 359. CBC decryption

The diagram illustrates the CBC decryption process for two blocks, Block 1 and Block 2.

- Block 1:

- DIN (ciphertext C1) is input to a Swap management block.

- The Swap management block outputs I1.

- I1 is input to the Decrypt block, which also takes KEY as input.

- The Decrypt block outputs O1.

- O1 is XORed with IVI.

- The result is input to a Swap management block.

- The Swap management block outputs DOUT (plaintext P1).

- Block 2:

- DIN (ciphertext C2) is input to a Swap management block.

- The Swap management block outputs I2.

- I2 is input to the Decrypt block, which also takes KEY as input.

- The Decrypt block outputs O2.

- O2 is XORed with the previous plaintext P1'.

- The result is input to a Swap management block.

- The Swap management block outputs DOUT (plaintext P2).

Legend

- input (white box)

- output (grey box)

- XOR (circle with a cross)

For more details, refer to NIST Special Publication 800-38A, Recommendation for Block Cipher Modes of Operation .

ECB and CBC encryption process

This process is described in Section 36.4.5 , with the following sequence of events:

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register as follows:

- – Select ECB or CBC chaining mode (write CHMOD[2:0] with 0x0 or 0x1) in encryption mode (write MODE[1:0] with 0x0).

- – Configure the data type, through DATATYPE[1:0].

- – Configure the key size, through KEYSIZE.

- – Select normal key mode by writing KMOD[1:0] with 0x0. For the other KMOD[1:0] values, refer to Section 36.4.14 (wrapped keys) and Section 36.4.15 (shared keys).

- 4. Write the initialization vector into the SAES_IVRx registers if CBC mode is selected in the previous step.

- 5. Write the key into the SAES_KEYRx registers. Alternatively, select a key source different from the key registers by writing KEYSEL[2:0] with a value different from 0x0. Refer to Section 36.4.17: SAES key registers for details.

- 6. Wait until KEYVALID is set (the key loading completed).

- 7. Enable the SAES peripheral, by setting EN.

- 8. Append cleartext data:

- a) If it is the second-last or the last block and the plaintext size of the message is not a multiple of 16 bytes, follow the guidance in Section 36.4.7 .

- b) Append the cleartext block into SAES as described in Section 36.4.5 , then read the SAES_DOUTR register four times to save the ciphertext block.

- c) Repeat the step b) until the third-last plaintext block is encrypted. For the last two blocks, follow the steps a) and b) .

- 9. Finalize the sequence: disable the SAES peripheral, by clearing EN.

ECB/CBC decryption process

This process is described in Section 36.4.5 , with the following sequence of events:

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register as follows:

- – Select the key derivation mode (write MODE[1:0] with 0x1). The CHMOD[2:0] bitfield is not significant during this operation.

- – Configure the data type, through DATATYPE[1:0].

- – Configure the key size, through KEYSIZE.

- – Select normal key mode by writing KMOD[1:0] with 0x0. For the other KMOD[1:0] values, refer to Section 36.4.14 (wrapped keys) and Section 36.4.15 (shared keys).

- 4. Write the key into the SAES_KEYRx registers. Alternatively, select a key source different from the key registers by writing KEYSEL[2:0] with a value different from 0x0. Refer to Section 36.4.17: SAES key registers for details.

- 5. Wait until KEYVALID is set (the key loading completed).

- 6. Enable the SAES peripheral, by setting EN. The peripheral immediately starts an AES round for key preparation.

- 7. Wait until the CCF flag in the SAES_ISR register is set.

- 8. Clear the CCF flag, by setting the CCF bit of the SAES_ICR register. The decryption key is available in the AES core and SAES is disabled automatically.

- 9. Select ECB or CBC chaining mode (write CHMOD[2:0] with 0x0 or 0x1) in decryption mode (write MODE[1:0] with 0x2). Do not change other parameters.

- 10. Write the initialization vector into the SAES_IVRx registers if CBC mode is selected in the previous step.

- 11. Enable the SAES peripheral, by setting EN.

- 12. Append encrypted data:

- a) If it is the second-last or the last block and the ciphertext size of the message is not a multiple of 16 bytes, follow the guidance in Section 36.4.7 .

- b) Append the ciphertext block into SAES as described in Section 36.4.5 , then read the SAES_DOUTR register four times to save the plaintext block (MSB first).

- c) Repeat the step b ) until the third-last ciphertext block is decrypted. For the last two blocks, follow the steps a ) and b ).

- 13. Finalize the sequence: disable the SAES peripheral, by clearing EN.

Suspend/resume operations in ECB/CBC modes

The following sequences are valid for normal key mode (KMOD[1:0] at 0x0).

To suspend the processing of a message , proceed as follows:

- 1. If DMA is used, stop the SAES DMA transfers to the input FIFO, by clearing DMAINEN. If DMA is not used, wait until the CCF flag in the SAES_ISR register is set (computation completed).

- 2. If DMA is not used, read four times the SAES_DOUTR register to save the last processed block. If DMA is used, wait until the CCF flag is set in the SAES_ISR register then stop the DMA transfers from the output FIFO, by clearing DMAOUTEN.

- 3. Clear the CCF flag, by setting the CCF bit of the SAES_ICR register.

- 4. Save initialization vector registers (only required in CBC mode as the SAES_IVRx registers are altered during the data processing).

- 5. Disable the SAES peripheral, by clearing EN.

- 6. Save the SAES_CR register and clear the key registers if they are not needed, to process the higher-priority message.

- 7. If DMA is used, save the DMA controller status (pointers for SAES input and output data transfers, number of remaining bytes, and so on).

To resume the processing of a message , proceed as follows:

- 1. If DMA is used, configure the DMA controller so as to complete the remaining input FIFO and output FIFO transfers.

- 2. Disable the SAES peripheral, by clearing EN.

- 3. Restore the SAES_CR register (with correct KEYSIZE) then restore the SAES_KEYRx registers. For KEYSEL[2:0] selecting a key source different from key registers, refer to Section 36.4.17: SAES key registers for details.

- 4. Prepare the decryption key, as described in ECB/CBC decryption process (only required for ECB or CBC decryption).

- 5. Restore the SAES_IVRx registers, using the saved configuration (only required in CBC mode).

- 6. Enable the SAES peripheral, by setting EN.

- 7. If DMA is used, enable SAES DMA transfers, by setting DMAINEN and DMAOUTEN.

Note: It is not required to save the key registers as the application knows the original key.

36.4.10 SAES counter (CTR) mode

The CTR mode uses the AES core to generate a key stream. The keys are then XOR-ed with the plaintext to obtain the ciphertext. Unlike with ECB and CBC modes, no key scheduling is required for the CTR decryption since the AES core is always used in encryption mode.

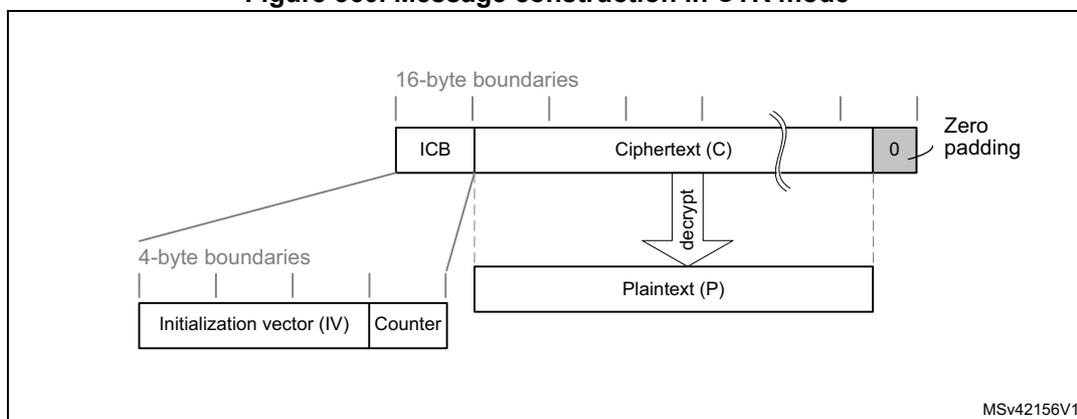

A typical message construction in CTR mode is given in Figure 360 .

Figure 360. Message construction in CTR mode

The diagram illustrates the message construction in CTR mode. At the top, a horizontal bar represents the message structure. It starts with a 16-byte Initial Counter Block (ICB), followed by Ciphertext (C), and ends with Zero padding (indicated by '0'). Vertical dashed lines mark 16-byte boundaries. Below the ICB, a callout shows its internal structure: a 4-byte Initialization vector (IV) and a 4-byte Counter, with 4-byte boundaries marked. Below the Ciphertext (C), a vertical arrow labeled 'decrypt' points to a block of Plaintext (P). The diagram is labeled with 'MSV42156V1' in the bottom right corner.

The structure of this message is:

- • A 16-byte initial counter block (ICB), composed of two distinct fields:

- – Initialization vector (IV) : a 96-bit value that must be unique for each encryption cycle with a given key.

- – Counter : a 32-bit big-endian integer that is incremented each time a block processing is completed. The initial value of the counter must be set to 1.

- • The plaintext P is encrypted as ciphertext C, with a known length. This length can be non-multiple of 16 bytes, in which case a plaintext padding is required.

For more details, refer to NIST Special Publication 800-38A, Recommendation for Block Cipher Modes of Operation .

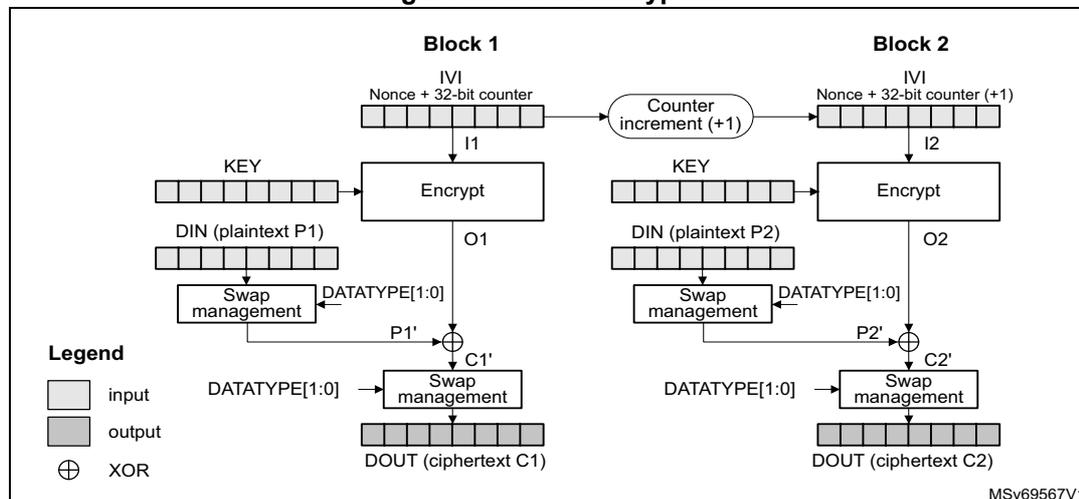

CTR encryption and decryption

Figure 361 describes the counter (CTR) chaining implementation in the SAES peripheral (encryption). To select this chaining mode, write CHMOD[2:0] with 0x2.

Figure 361. CTR encryption

The diagram illustrates the CTR encryption process across two blocks, Block 1 and Block 2.

Block 1:

An initialization vector (IVI) and a 32-bit counter are input to an 'Encrypt' block along with a 'KEY'. The 'Encrypt' block produces an output 'O1'. Simultaneously, 'DIN (plaintext P1)' is input to a 'Swap management' block, which outputs 'P1\''. 'P1\'' is XORed with 'O1' to produce 'C1\''. 'C1\'' is then processed by another 'Swap management' block (controlled by 'DATATYPE[1:0]') to produce the final 'DOUT (ciphertext C1)'.

Block 2:

The counter from Block 1 is incremented by 1 ('Counter increment (+1)') and passed to Block 2 as 'Nonce + 32-bit counter (+1)'. This counter and the 'KEY' are input to Block 2's 'Encrypt' block, which produces 'O2'. 'DIN (plaintext P2)' is processed by a 'Swap management' block to produce 'P2\''. 'P2\'' is XORed with 'O2' to produce 'C2\'', which is then processed by another 'Swap management' block to produce 'DOUT (ciphertext C2)'.

Legend:

Input is represented by a light gray rectangle, output by a dark gray rectangle, and XOR by a circle with a cross. The identifier 'MSV69567V1' is present in the bottom right corner.

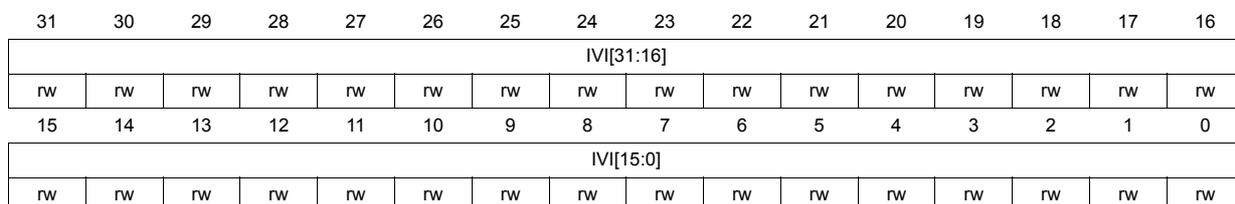

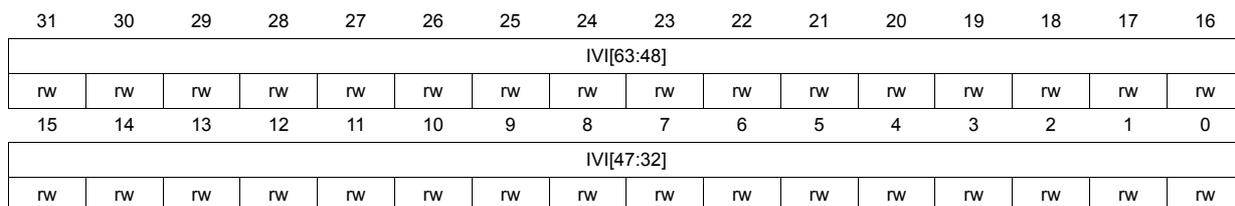

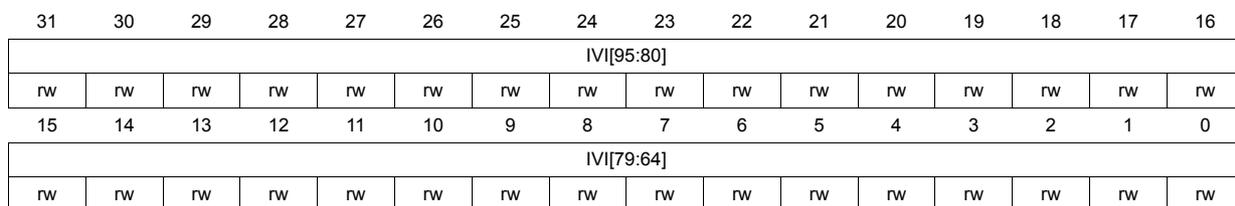

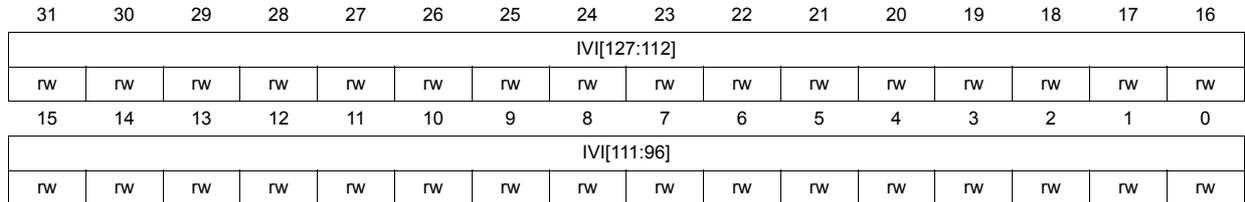

Initialization vectors in SAES must be initialized as shown in Table 327.

Table 327. Counter mode initialization vector definition

| SAES_IVR3[31:0] | SAES_IVR2[31:0] | SAES_IVR1[31:0] | SAES_IVR0[31:0] |

|---|---|---|---|

| IVI[127:96] | IVI[95:64] | IVI[63:32] | IVI[31:0] 32-bit counter = 0x0001 |

CTR encryption and decryption process

This process is described in Section 36.4.5, with the following sequence of events:

- Disable the SAES peripheral, by clearing EN.

- Wait until BUSY is cleared (no RNG random number fetch in progress).

- Initialize the SAES_CR register:

- Select CTR chaining mode (write CHMOD[2:0] with 0x2) in encryption or decryption mode (write MODE[1:0] with 0x0 or 0x2).

- Configure the data type, through DATATYPE[1:0].

- Configure the key size, through KEYSIZE.

- Select normal key mode, by writing KMOD[1:0] with 0x0. For the other KMOD[1:0] values, refer to Section 36.4.14 (wrapped keys) and Section 36.4.15 (shared keys).

- Write the initialization vector into the SAES_IVRx registers according to Table 327.

- Write the key into the SAES_KEYRx registers. Alternatively, select a key source different from the key registers by writing KEYSEL[2:0] with a value different from 0x0. Refer to Section 36.4.17: SAES key registers for details.

- Wait until KEYVALID is set (the key loading completed).

- Enable the SAES peripheral, by setting EN.

- 8. Append data:

- a) If it is the last block and the plaintext (encryption) or ciphertext (decryption) size in the block is less than 16 bytes, pad the remainder of the block with zeros.

- b) Append the data block into SAES as described in Section 36.4.5 , then read the SAES_DOUTR register four times to save the resulting block (MSB first).

- c) Repeat the step b) until the second-last block is processed. For the last block of plaintext (encryption only), follow the steps a) and b) . For the last block, discard the bits that are not part of the message when the last block is smaller than 16 bytes.

- 9. Finalize the sequence: disable the SAES peripheral, by clearing EN.

Suspend/resume operations in CTR mode

Like for the CBC mode, it is possible to interrupt a message to send a higher-priority message, then resume the interrupted message. Detailed CBC suspend and resume sequence is described in Section 36.4.9: SAES basic chaining modes (ECB, CBC) .

Note: Like for CBC mode, the IV registers must be reloaded during the resume operation.

36.4.11 SAES Galois/counter mode (GCM)

The AES Galois/counter mode (GCM) allows encrypting and authenticating a plaintext message into the corresponding ciphertext and tag (also known as message authentication code).

GCM mode is based on AES in counter mode for confidentiality. It uses a multiplier over a fixed finite field for computing the message authentication code. The following figure shows a typical message construction in GCM mode.

Figure 362. Message construction in GCM

![Diagram illustrating message construction in GCM mode. It shows the flow from Initialization vector (IV) and Counter through an ICB to Additional authenticated data (AAD) and Plaintext (P). The AAD and P are processed through an 'encrypt' block to produce Authenticated & encrypted ciphertext (C). The AAD and C are then processed through an 'authenticate' block to produce the Authentication tag (T). The diagram also shows 16-byte and 4-byte boundaries, zero padding, and length fields [Len(A)]64 and [Len(C)]64.](/RM0477-STM32H7Rx-7Sx/df7aea34b587e7bb8d15b07ff47aded0_img.jpg)

The diagram illustrates the message construction in GCM mode. It shows the following components and flow:

- Initialization vector (IV) and Counter: These are 4-byte boundaries that feed into the ICB (Initialization Counter Block).

- ICB: The ICB is a 16-byte boundary block that generates the counter for encryption.

- Additional authenticated data (AAD): This data, of length \( Len(A) \) , is processed for authentication. It is followed by a zero-padded block.

- Plaintext (P): This data, of length \( Len(P) = Len(C) \) , is encrypted to produce the ciphertext. It is also followed by a zero-padded block.

- Encrypt: The ICB, AAD, and Plaintext (P) are processed through an 'encrypt' block to produce the 'Authenticated & encrypted ciphertext (C)'.

- Authenticate: The AAD and the ciphertext (C) are processed through an 'authenticate' block to produce the 'Authentication tag (T)'.

- Length Fields: At the end of the message, there are two 64-bit length fields: \( [Len(A)]_{64} \) and \( [Len(C)]_{64} \) .

- Zero padding / zeroed bits: These are indicated by grey blocks in the diagram.

The message has the following structure:

- •

16-byte initial counter block (ICB)

, composed of two distinct fields:

- – Initialization vector (IV) : a 96-bit value that must be unique for each encryption cycle with a given key. The GCM standard supports IVs with less than 96 bits, but in this case strict rules apply.

- – Counter : a 32-bit big-endian integer that is incremented each time a block processing is completed. According to NIST specification, the counter value is 0x2 when processing the first block of payload.

- • Authenticated header AAD (also known as additional authentication data) has a known length \( \text{Len}(A) \) that may be a non-multiple of 16 bytes, and must not exceed \( 2^{64} - 1 \) bits. This part of the message is only authenticated, not encrypted.

- • Plaintext message P is both authenticated and encrypted as ciphertext C, with a known length \( \text{Len}(P) \) that may be non-multiple of 16 bytes, and cannot exceed \( 2^{32} - 2 \) 16-byte blocks.

- • Last block contains the AAD header length (bits [32:63]) and the payload length (bits [96:127]) information, as shown in Table 329 .

The GCM standard specifies that ciphertext C has the same bit length as the plaintext P.

When a part of the message (AAD or P) has a length that is a non-multiple of 16-bytes a special padding scheme is required.

For more details, refer to NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation - Galois/Counter Mode (GCM) and GMAC .

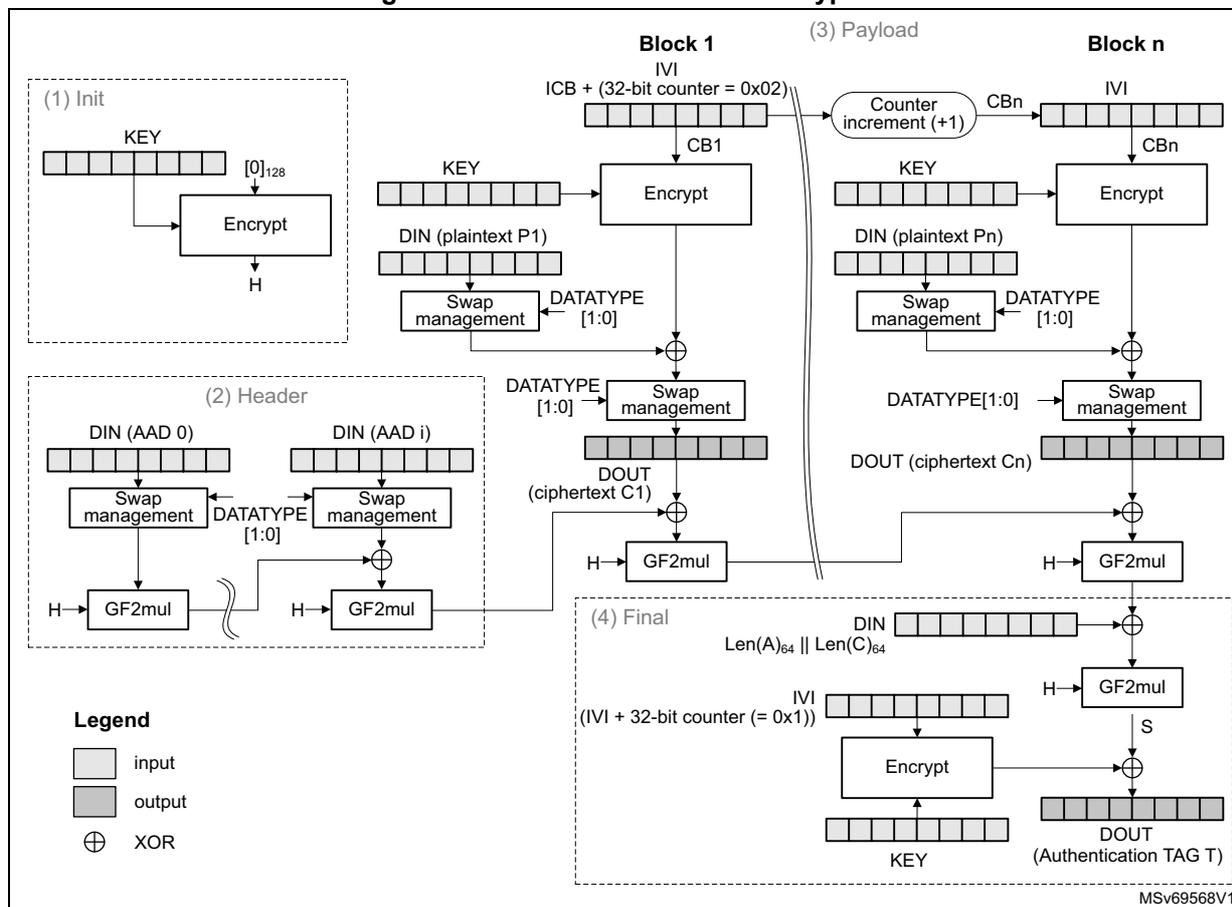

Figure 363 describes the GCM chaining implementation in the SAES peripheral (encryption). To select this chaining mode, write CHMOD[2:0] with 0x3.

Figure 363. GCM authenticated encryption

The diagram illustrates the GCM authenticated encryption process, divided into four main stages:

- (1) Init: A KEY is input to an Encrypt block, which outputs H. An initial vector [0] 128 is also input to the Encrypt block.

- (2) Header: Data (DIN (AAD 0) and DIN (AAD i)) is processed through Swap management blocks (controlled by DATATYPE [1:0]) and then XORed with H. The result is processed by a GF2mul block (controlled by H) to produce the next H value.

- (3) Payload: The process starts with Block 1. An Initial Counter Block (ICB) with a 32-bit counter set to 0x02 is input to an Encrypt block along with KEY to produce CB1. CB1 is XORed with DIN (plaintext P1) after Swap management (DATATYPE [1:0]) to produce DOUT (ciphertext C1). A Counter increment (+1) block takes ICB and produces CBn for Block n. Block n follows a similar structure: CBn is input to an Encrypt block with KEY to produce IVI. IVI is XORed with DIN (plaintext Pn) after Swap management (DATATYPE [1:0]) to produce DOUT (ciphertext Cn). Both C1 and Cn are processed by GF2mul blocks (controlled by H) to produce a value S.

- (4) Final: The final block takes DIN (containing Len(A) 64 || Len(C) 64 ) and XORs it with S. The result is processed by a GF2mul block (controlled by H) to produce S. S is then XORed with the output of an Encrypt block (which takes IVI with a 32-bit counter set to 0x1 and KEY) to produce the final DOUT (Authentication TAG T).

Legend:

- input (white rectangle)

- output (grey rectangle)

- XOR (circle with plus sign)

MSv69568V1

The first counter block (CB1) is derived from the initial counter block ICB by the application software, as defined in Table 328.

Table 328. Initialization of IV registers in GCM mode

| SAES_IVR3[31:0] | SAES_IVR2[31:0] | SAES_IVR1[31:0] | SAES_IVR0[31:0] |

|---|---|---|---|

| ICB[127:96] | ICB[95:64] | ICB[63:32] | ICB[31:0] 32-bit counter = 0x0002 |

The last block of a GCM message contains the AAD header length and the payload length information, as shown in Table 329.

Table 329. GCM last block definition

| Word order to SAES_DINR | First word | Second word | Third word | Fourth word |

|---|---|---|---|---|

| Input data | AAD length[63:32] | AAD length[31:0] | Payload length[63:32] | Payload length[31:0] |

GCM encryption and decryption process

This process is described in Section 36.4.6 , with the following sequence of events:

GCM initialize

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register:

- – Select GCM chaining mode (write CHMOD[2:0] with 0x3) in encryption or decryption mode (write MODE[1:0] with 0x0 or 0x2). Do not write MODE[1:0] with 0x1.

- – Configure the data type, through DATATYPE[1:0]

- – Configure the key size, through KEYSIZE.

- – Select normal key mode, by writing KMOD[1:0] with 0x0. For the other KMOD[1:0] values, refer to Section 36.4.14 (wrapped keys) and Section 36.4.15 (shared keys).

- – Select the GCM initialization phase, by writing GCMPH[1:0] with 0x0.

- 4. Write the initialization vector in SAES_IVRx registers according to Table 328 .

- 5. Write the key into the SAES_KEYRx registers. Alternatively, select a key source different from the key registers by writing KEYSEL[2:0] with a value different from 0x0. Refer to Section 36.4.17: SAES key registers for details.

- 6. Wait until KEYVALID is set (the key loading completed).

- 7. Set EN to start the calculation of the hash key. EN is automatically cleared when the calculation is completed.

- 8. Wait until the CCF flag is set in the SAES_ISR register, indicating that the GCM hash subkey (H) computation is completed.

- 9. Clear the CCF flag by setting the CCF bit of the SAES_ICR register.

GCM header phase

- 10. Initialize header phase:

- a) Select the GCM header phase, by writing 0x1 to GCMPH[1:0]. Do not change the other configurations written during GCM initialization.

- b) Enable the SAES peripheral, by setting EN.

- 11. Append header data:

- a) If it is the last block and the AAD in the block is smaller than 16 bytes, pad the remainder of the block with zeros.

- b) Append the data block into SAES as described in Section 36.4.5 .

- c) Repeat the step b) until the second-last AAD data block is processed. For the last block, follow the steps a) and b) .

Note: This phase can be skipped if there is no AAD, that is, Len(A) = 0.

No data are read during header phase.

GCM payload phase

- 12. Initialize payload phase:

- a) Select the GCM payload phase, by writing GCMPH[1:0] with 0x2. Do not change the other configurations written during GCM initialization.

- b) If the header phase is skipped, enable the SAES peripheral by setting EN.

- 13. Append payload data:

- a) If it is the last block and the message in the block is smaller than 16 bytes, pad the remainder of the block with zeros.

- b) Append the data block into SAES as described in Section 36.4.5 , then read the SAES_DOUTR register four times to save the resulting block

- c) Repeat the step b) until the second-last plaintext block is encrypted or until the last block of ciphertext is decrypted. For the last block of plaintext (encryption only), follow the steps a) and b) . For the last block, discard the bits that are not part of the payload when the last block is smaller than 16 bytes.

Note: This phase can be skipped if there is no payload, that is, Len(C)=0 (see GMAC mode).

GCM finalization

- 14. Encryption only: wait until the BUSY flag in the SAES_SR register is cleared.

- 15. Select the GCM final phase, by writing GCMPH[1:0] with 0x3. Do not change the other configurations written during GCM initialization.

- 16. Write the final GCM block into the SAES_DINR register. It is the concatenated AAD bit and payload bit lengths, as shown in Table 329 .

- 17. Wait until the CCF flag in the SAES_ISR register is set.

- 18. Get the GCM authentication tag, by reading the SAES_DOUTR register four times.

- 19. Clear the CCF flag, by setting the CCF bit of the SAES_ICR register.

- 20. Disable the SAES peripheral, by clearing EN. If it is an authenticated decryption, compare the generated tag with the expected tag passed with the message.

Note: In the final phase, data are written to SAES_DINR normally (no swapping), while swapping is applied to tag data read from SAES_DOUTR.

When transiting from the header or the payload phase to the final phase, the SAES peripheral must not be disabled, otherwise the result is wrong.

Suspend/resume operations in GCM mode

Suspend/resume operations are not supported in GCM mode.

36.4.12 SAES Galois message authentication code (GMAC)

The Galois message authentication code (GMAC) allows the authentication of a plaintext, generating the corresponding tag information (also known as message authentication code).

GMAC is similar to GCM, except that it is applied on a message composed only by plaintext authenticated data (that is, only header, no payload). The following figure shows typical message construction for GMAC.

Figure 364. Message construction in GMAC mode

![Figure 364: Message construction in GMAC mode. The diagram shows a message structure with 16-byte boundaries. It starts with an ICB (Initialization Counter Block), followed by 'Authenticated data' of length Len(A). The last block is split into two 8-byte parts: [Len(A)]64 and [0]64. Below the ICB, a 4-byte boundary separates the 'Initialization vector (IV)' and 'Counter'. An arrow labeled 'auth.' points from the 'Authenticated data' to an 'Authentication tag (T)'. A legend indicates that grey boxes represent 'Zero padding'.](/RM0477-STM32H7Rx-7Sx/0417e53ece62567e13394cc56d4360b9_img.jpg)

For more details, refer to NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation - Galois/Counter Mode (GCM) and GMAC .

Figure 365 describes the GMAC chaining implementation in the SAES peripheral. To select this chaining mode, write CHMOD[2:0] with 0x3.

Figure 365. GMAC authentication mode

![Figure 365: GMAC authentication mode. This diagram illustrates the four-step process: (1) Init, (2) Header, (3) Payload (omitted), and (4) Final. (1) Init: A KEY is input to an 'Encrypt' block along with [0]128 to produce H. (2) Header: Message blocks (DIN) are processed through 'Swap management' (controlled by DATATYPE [1:0]) and then 'GF2mul' with H. The outputs are XORed. (4) Final: The KEY is input to 'Encrypt' with IVI + 32-bit counter (= 0x0) to produce S. The final input is len(A)64 || [0]64, which is XORed and then processed by 'GF2mul' with H to produce the final output DOUT (authentication tag T). A legend defines input (white), output (grey), and XOR (circle with cross).](/RM0477-STM32H7Rx-7Sx/398bca224280c500afaaf5cf26714d5d_img.jpg)

The GMAC algorithm corresponds to the GCM algorithm applied on a message that only contains a header. As a consequence, all steps and settings are the same as with the GCM, except that the payload phase is omitted.

Suspend/resume operations in GMAC

Suspend/resume operations are not supported in GMAC mode.

36.4.13 SAES counter with CBC-MAC (CCM)

The AES counter with cipher block chaining-message authentication code (CCM) algorithm allows encryption and authentication of plaintext, generating the corresponding ciphertext and tag (also known as message authentication code). To ensure confidentiality, the CCM algorithm is based on AES counter mode processing. It uses cipher block chaining technique to generate the message authentication code. This is commonly called CBC-MAC.

Note: NIST does not approve CBC-MAC as an authentication mode outside the context of the CCM specification.

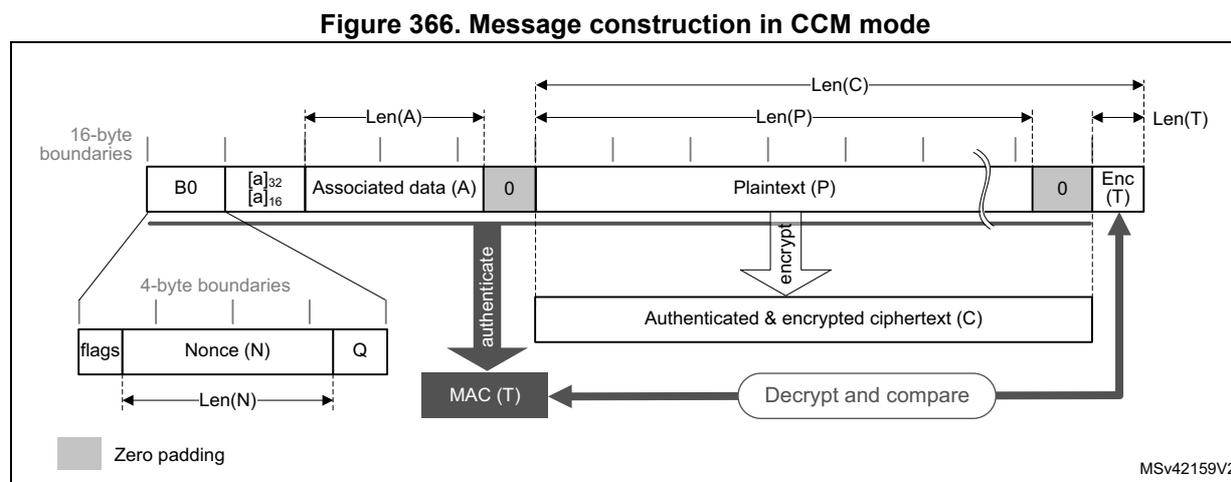

The following figure shows typical message construction for CCM.

Figure 366. Message construction in CCM mode

The structure of the message is:

- 16-byte first authentication block (B0)

, composed of three distinct fields:

- Q: a bit string representation of the octet length of P ( \( \text{Len}(P) \) )

- Nonce (N): a single-use value (that is, a new nonce must be assigned to each new communication) of \( \text{Len}(N) \) size. The sum \( \text{Len}(N) + \text{Len}(P) \) must be equal to 15 bytes.

- Flags: most significant octet containing four flags for control information, as specified by the standard. It contains two 3-bit strings to encode the values t (MAC length expressed in bytes) and Q (plaintext length such that \( \text{Len}(P) < 2^{8Q} \) bytes). The counter blocks range associated to Q is equal to \( 2^{8Q-4} \) , that is, if the maximum value of Q is 8, the counter blocks used in cipher must be on 60 bits.

- 16-byte blocks (B)

associated to the associated data (A).

This part of the message is only authenticated, not encrypted. This section has a known length \( \text{Len}(A) \) that can be a non-multiple of 16 bytes (see Figure 366). The standard also states that, on MSB bits of the first message block (B1), the associated data length expressed in bytes ( a ) must be encoded as follows:

- If \( 0 < a < 2^{16} - 2^8 \) , then it is encoded as \( [a]_{16} \) , that is, on two bytes.

- If \( 2^{16} - 2^8 < a < 2^{32} \) , then it is encoded as \( 0xff \parallel 0xfe \parallel [a]_{32} \) , that is, on six bytes.

- If \( 2^{32} < a < 2^{64} \) , then it is encoded as \( 0xff \parallel 0xff \parallel [a]_{64} \) , that is, on ten bytes.

- • 16-byte blocks (B) associated to the plaintext message P, which is both authenticated and encrypted as ciphertext C, with a known length Len(P). This length can be a non-multiple of 16 bytes (see Figure 366 ).

- • Encrypted MAC (T) of length Len(T) appended to the ciphertext C of overall length Len(C).

When a part of the message (A or P) has a length that is a non-multiple of 16-bytes, a special padding scheme is required.

Note: CCM chaining mode can also be used with associated data only (that is, no payload).

As an example, the C.1 section in NIST Special Publication 800-38C gives the following values (hexadecimal numbers):

N: 10111213 141516 (Len(N) = 56 bits or 7 bytes)

A: 00010203 04050607 (Len(A) = 64 bits or 8 bytes)

P: 20212223 (Len(P) = 32 bits or 4 bytes)

T: 6084341B (Len(T) = 32 bits or t = 4)

B0: 4F101112 13141516 00000000 00000004

B1: 00080001 02030405 06070000 00000000

B2: 20212223 00000000 00000000 00000000

CTR0: 0710111213 141516 00000000 00000000

CTR1: 0710111213 141516 00000000 00000001

For more details, refer to NIST Special Publication 800-38C, Recommendation for Block Cipher Modes of Operation - The CCM Mode for Authentication and Confidentiality .

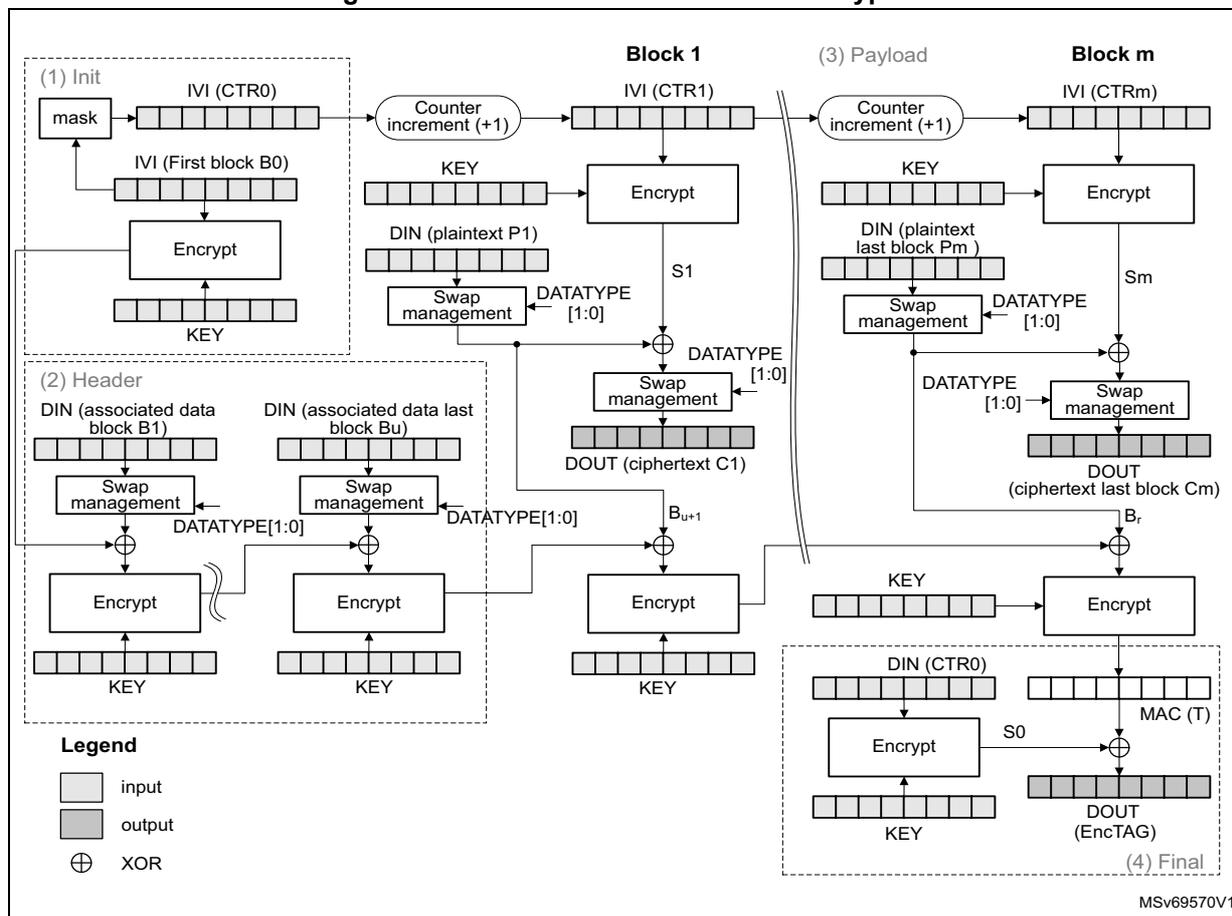

Figure 367 describes the CCM chaining implementation in the SAES peripheral (encryption). To select this chaining mode, write CHMOD[2:0] with 0x4.

Figure 367. CCM mode authenticated encryption

The diagram illustrates the CCM chaining implementation for encryption, divided into four main stages:

- (1) Init: This stage initializes the counter. A 'mask' and 'IVI (First block B0)' are inputs to an 'Encrypt' block. The output is XORed with 'KEY' to produce 'IVI (CTR0)'. A 'Counter increment (+1)' block takes 'IVI (CTR0)' and produces 'IVI (CTR1)'.

- (2) Header: This stage processes associated data blocks. 'DIN (associated data block B1)' and 'DIN (associated data last block Bu)' are inputs to 'Swap management' blocks. The outputs are XORed with 'DATATYPE[1:0]' and then passed to 'Encrypt' blocks. The outputs are XORed with 'KEY' to produce ciphertext blocks B r+1 and B u+1 .

- (3) Payload: This stage processes the data payload. For 'Block 1', 'DIN (plaintext P1)' is input to 'Swap management', which outputs to an 'Encrypt' block. The output is XORed with 'DATATYPE[1:0]' to produce 'DOUT (ciphertext C1)'. For 'Block m', 'DIN (plaintext last block Pm)' is input to 'Swap management', which outputs to an 'Encrypt' block. The output is XORed with 'DATATYPE[1:0]' to produce 'DOUT (ciphertext last block Cm)'. A 'Counter increment (+1)' block takes 'IVI (CTR1)' and produces 'IVI (CTRm)'.

- (4) Final: This stage generates the MAC. 'DIN (CTR0)' is input to an 'Encrypt' block, which outputs 'S0'. 'S0' is XORed with 'KEY' to produce 'MAC (T)'. 'MAC (T)' is XORed with 'KEY' to produce 'DOUT (EncTAG)'.

Legend:

- input (light gray rectangle)

- output (dark gray rectangle)

- XOR (circle with a cross)

MSv69570V1

The first block of a CCM message (B0) must be prepared by the application as defined in Table 330.

Table 330. Initialization of IV registers in CCM mode

| SAES_IVR3[31:0] | SAES_IVR2[31:0] | SAES_IVR1[31:0] | SAES_IVR0[31:0] |

|---|---|---|---|

| B0[127:96] (1) | B0[95:64] | B0[63:32] | B0[31:0] (2) |

- 1. The five most significant bits are cleared (flag bits).

- 2. Q length bits are cleared, except for the bit 0 that is set.

SAES supports counters up to 64 bits, as specified by NIST.

CCM encryption and decryption process

This process is described in Section 36.4.6 , with the following sequence of events:

CCM initialize

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register:

- – Select CCM chaining mode (write CHMOD[2:0] with 0x4) in encryption or decryption mode (write MODE[1:0] with 0x0 or 0x2). Do not write MODE[1:0] with 0x1.

- – Configure the data type, through DATATYPE[1:0]

- – Configure the key size, through KEYSIZE.

- – Select normal key mode, by writing KMOD[1:0] with 0x0. For the other KMOD[1:0] values, refer to Section 36.4.14 (wrapped keys) and Section 36.4.15 (shared keys).

- – Select the CCM initialization phase, by writing GCMPH[1:0] with 0x0.

- 4. Write the B0 data in SAES_IVRx registers according to Table 330 .

- 5. Write the key into the SAES_KEYRx registers. Alternatively, select a key source different from the key registers by writing KEYSEL[2:0] with a value different from 0x0. Refer to Section 36.4.17: SAES key registers for details.

- 6. Wait until KEYVALID is set (the key loading completed).

- 7. Set EN to start the first mask calculation. The EN bit is automatically cleared when the calculation is completed.

- 8. Wait until the CCF flag in the SAES_ISR register is set.

- 9. Clear the CCF flag, by setting the CCF bit of the SAES_ICR register.

CCM header phase

- 10. Initialize header phase:

- a) Prepare the first block of the (B1) data associated with the message, in accordance with CCM chaining rules.

- b) Select the CCM header phase, by writing GCMPH[1:0] with 0x1. Do not change the other configurations written during the CCM initialization.

- c) Enable the SAES peripheral, by setting EN.

- 11. Append header data:

- a) If it is the last block and the associated data in the block is smaller than 16 bytes, pad the remainder of the block with zeros.

- b) Append the data block into SAES as described in Section 36.4.5 .

- c) Repeat the step b) until the second-last associated data block is processed. For the last block, follow the steps a) and b) .

Note: This phase can be skipped if there is no associated data, that is, Len(A) = 0

No data are read during the header phase.

CCM payload phase

- 12. Initialize payload phase:

- a) Select the CCM payload phase, by writing GCM[1:0] with 0x2. Do not change the other configurations written during the CCM initialization.

- b) If the header phase is skipped, enable the SAES peripheral, by setting EN.

- 13. Append payload data:

- a) In encryption only, if it is the last block and the plaintext in the block is smaller than 16 bytes, pad the remainder of the block with zeros.

- b) Append the data block into SAES as described in Section 36.4.5 , then read the SAES_DOUTR register four times to save the resulting block.

- c) Repeat the step b) until the second-last plaintext block is encrypted or until the last block of ciphertext is decrypted. For the last block of plaintext (encryption only), follow the steps a) and b) . For the last block, discard the bits that are not part of the payload when the last block is smaller than 16 bytes.

Note: This phase can be skipped if there is no payload, that is, \( Len(P) = 0 \) or \( Len(C) = Len(T) \) . Remove \( LSB_{Len(T)}(C) \) encrypted tag information when decrypting ciphertext C.

CCM finalization

- 14. Select the CCM final phase, by writing GCM[1:0] with 0x3. Do not change the other configurations written during the CCM initialization.

- 15. Wait until CCF flag in the SAES_ISR register is set.

- 16. Get the CCM authentication tag, by reading the SAES_DOUTR register four times.

- 17. Clear the CCF flag, by setting the CCF bit of the SAES_ICR register.

- 18. Disable the SAES peripheral, by clearing EN. If it is an authenticated decryption, compare the generated tag with the expected tag passed with the message. Mask the authentication tag output with tag length to obtain a valid tag.

Note: In the final phase, swapping is applied to tag data read from SAES_DOUTR register. When transiting from the header or the payload phase to the final phase, the SAES peripheral must not be disabled, otherwise the result is wrong.

Suspend and resume operations in CCM mode

To suspend the processing of a message in header or payload phase, proceed as follows:

- 1. If DMA is used, stop the SAES DMA transfers to the input FIFO, by clearing DMAINEN. If DMA is not used, wait until the CCF flag of the SAES_ISR register is set (computation completed).

- 2. In the payload phase, if DMA is not used, read four times the SAES_DOUTR register to save the last-processed block. If DMA is used, wait until the CCF flag in the SAES_ISR register is set, then stop the DMA transfers from the output FIFO, by clearing DMAOUTEN.

- 3. Clear the CCF flag in the SAES_ISR register, by setting the CCF bit of the SAES_ICR register.

- 4. Save the SAES_SUSPRx registers in the memory.

- 5. Save the IV registers as they are altered during the data processing.

- 6. Disable the SAES peripheral, by clearing EN.

- 7. Save the current SAES_CR configuration in the memory. Key registers do not need to be saved as the original key value is known by the application.

- 8. If DMA is used, save the DMA controller status (pointer for SAES input data transfers, number of remaining bytes, and so on). In the payload phase, also save pointer for SAES output data transfers.

To resume the processing of a message, proceed as follows:

- 1. If DMA is used, configure the DMA controller in order to complete the remaining input FIFO transfers. In the payload phase, also configure the DMA controller for the remaining output FIFO transfers.

- 2. Disable the SAES peripheral, by clearing EN.

- 3. Write the suspend register values, previously saved in the memory, back into their corresponding SAES_SUSPRx registers.

- 4. Restore SAES_IVRx registers using the saved configuration.

- 5. Restore the initial setting values in the SAES_CR and SAES_KEYRx registers. For KEYSEL[2:0] selecting a key source different from the key registers, refer to Section 36.4.17: SAES key registers for details.

- 6. Enable the SAES peripheral, by setting EN.

- 7. If DMA is used, enable SAES DMA requests, by setting DMAINEN (and DMAOUTEN if in payload phase).

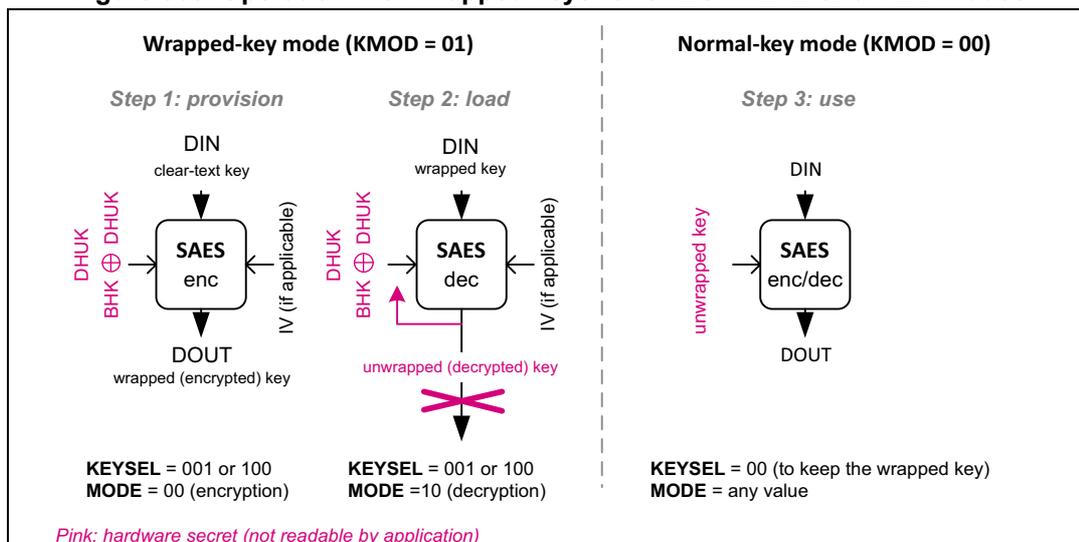

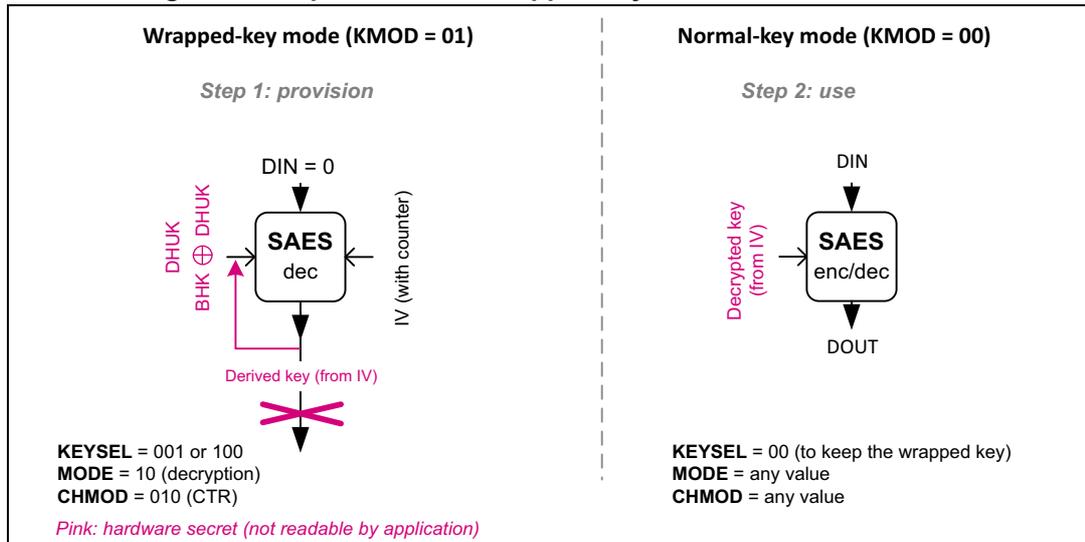

36.4.14 SAES operation with wrapped keys

SAES peripheral can wrap (encrypt) and unwrap (decrypt) application keys using hardware-secret key DHUK, XOR-ed or not with application key BHK or AHK. With this feature, AES keys can be made usable by application software without being exposed in clear-text (unencrypted).

Wrapped key sequences are too small to be suspended/resumed. SAES cannot unwrap a key using an unwrapped key.

Operation with wrapped keys for SAES in ECB and CBC modes

Figure 368 summarizes how to wrap or unwrap keys for SAES in ECB and CBC modes. To protect the wrapped key, select DHUK by writing KEYSEL[2:0] with 0x1, 0x5, or 0x4. Alternatively, select BHK by writing KEYSEL[2:0] with 0x2 if the corresponding registers are read/write-locked in the TAMP peripheral. AHK can also be selected, by writing KEYSEL[2:0] with 0x3.

Figure 368. Operation with wrapped keys for SAES in ECB and CBC modes

Wrapped-key mode (KMOD = 01)

Step 1: provision

DIN clear-text key → SAES enc → DOUT wrapped (encrypted) key

Inputs: DHUK, BHK ⊕ DHUK, IV (if applicable)

KEYSEL = 001 or 100

MODE = 00 (encryption)

Step 2: load

DIN wrapped key → SAES dec → unwrapped (decrypted) key

Inputs: DHUK, BHK ⊕ DHUK, IV (if applicable)

KEYSEL = 001 or 100

MODE = 10 (decryption)

Normal-key mode (KMOD = 00)

Step 3: use

DIN unwrapped key → SAES enc/dec → DOUT

KEYSEL = 00 (to keep the wrapped key)

MODE = any value

Pink: hardware secret (not readable by application)

Note: DHUK value depends on privilege, KMOD[1:0], KEYSEL[2:0], CHMOD[2:0], and KEYSIZE.

Key wrapping for SAES

The recommended sequence to wrap (that is, encrypt) a key is as follows:

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register as follow:

- – Select ECB or CBC chaining mode (write CHMOD[2:0] with 0x0 or 0x1) in encryption mode (MODE[1:0] at 0x0)

- – Select 32-bit data type (DATATYPE[1:0] at 0x0)

- – Configure the key size with KEYSIZE. This information is used both for the encryption key and for the key to be encrypt.

- – Select wrapped key mode by writing KMOD[1:0] with 0x1

- 4. Write the initialization vector in SAES_IVRx registers if CBC mode has been selected in previous step.

- 5. Select the DHUK key source by writing KEYSEL[2:0] with 0x1, 0x5 or 0x4. Optionally, select the BHK, by writing KEYSEL[2:0] with 0x2. Refer to Section 36.4.17 for details on the use of KEYSEL[2:0].

- 6. Wait until KEYVALID is set (DHUK loading completed).

- 7. Enable the SAES peripheral, by setting EN.

- 8. Write the SAES_DINR register four times to input the key to encrypt (MSB first, see Table 332 ).

- 9. Wait until CCF flag is set in the SAES_ISR register.

- 10. Get the encrypted key (MSB first) by reading the SAES_DOUTR register four times. Then clear the CCF flag, by setting the CCF bit in SAES_ICR register.

- 11. Repeat steps 8. to 10. if KEYSIZE is set.

- 12. Disable the SAES peripheral, by clearing EN.

Note: Encryption in Wrapped-key mode is only supported when ECB or CBC is selected.

Key unwrapping for SAES

The recommended sequence to unwrap (or decrypt) a wrapped (encrypted) key using ECB/CBC is as follows:

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register as follow:

- – Select the chaining mode used during the wrapping process (CHMOD[2:0] at 0x0 or 0x1) in key derivation mode (MODE[1:0] at 0x1)

- – Select 32-bit data type (DATATYPE[1:0] at 0x0)

- – Configure the key size used during the wrapping process, with KEYSIZE. This information is used both for the decryption key and for the key to decrypt.

- – Select wrapped key mode, by writing KMOD[1:0] with 0x1.

- 4. With KEYSEL[2:0], select the same key source as when the key was wrapped/encrypted.

- 5. Wait until KEYVALID is set (the key loading completed).

- 6. Set EN bit in SAES_CR to enable the peripheral

- 7. Wait until CCF flag is set in the SAES_ISR register.

- 8. Clear the CCF flag, by setting the CCF bit in SAES_ICR register. The decryption key is available in the AES core, and SAES is disabled automatically.

- 9. Select the decryption mode (MODE[1:0] at 0x2). Other parameters are unchanged.

- 10. Write the initialization vector in SAES_IVRx registers if CBC mode has been selected in previous step.

- 11. Enable the SAES peripheral, by setting EN.

- 12. Write the SAES_DINR register four times to input the key to decrypt (MSB first, see Table 332 ).

- 13. Wait until CCF flag is set in the SAES_ISR register. Then clear the CCF flag by setting the CCF bit in SAES_ICR register. Reading SAES_DOUTR returns zero and triggers a read error (RDERRF).

- 14. Repeat steps 12. and 13. if KEYSIZE is set.

- 15. Disable the SAES peripheral, by clearing EN.

At the end of this sequence, the decrypted wrapped key is immediately usable by the application for any AES operation (normal key mode, that is, with KMOD[1:0] = 0x0).

Note: When KMOD[1:0] = 0x1 (wrapped key) and MODE[1:0] = 0x2 (decryption) a read access to SAES_DOUTR register triggers a read error (RDERRF).

When KEYSEL[2:0] is at 0x1 (DHUK), 0x5 (DHUK XOR AHK), or 0x4 (DHUK XOR BHK), the application software must use the same privilege, KMOD[1:0], CHMOD[2:0] and KEYSIZE context for encryption and decryption. Otherwise, the result is incorrect.

Operation with wrapped keys for SAES in CTR mode

Figure 369 summarizes how to unwrap keys for SAES in CTR mode. To protect the derived key, select DHUK by writing KEYSEL[2:0] with 0x1, 0x5 or 0x4. Alternatively, select BHK by writing KEYSEL[2:0] with 0x2 if the corresponding registers are read/write-locked in the TAMP peripheral.

Figure 369. Operation with wrapped keys for SAES in CTR mode

Note: DHUK value depends on privilege, KMOD[1:0], KEYSEL[2:0], CHMOD[2:0], and KEYSIZE.

The recommended sequence for SAES wrapped key mode using CTR is as follows:

- 1. Disable the SAES peripheral, by clearing EN.

- 2. Wait until BUSY is cleared (no RNG random number fetch in progress).

- 3. Initialize the SAES_CR register as follow:

- – Select the CTR chaining mode (CHMOD[2:0] at 0x2) in decryption mode (MODE[1:0] at 0x2). Other MODE[1:0] values are not supported.

- – Select 32-bit data type (DATATYPE[1:0] at 0x0)

- – Configure the key size with KEYSIZE. It is used for encryption key and for the key to share.

- – Select wrapped key mode, by writing KMOD[1:0] with 0x1.

- 4. Write the initialization vector in SAES_IVRx registers, keeping the two least significant bits of SAES_IVR0 at zero.

- 5. Select the DHUK key source by writing KEYSEL[2:0] with 0x1, 0x5 or 0x4. Optionally, select the BHK, by writing KEYSEL[2:0] with 0x2. Refer to Section 36.4.17 for details on the use of KEYSEL[2:0].

- 6. Wait until KEYVALID is set (the key loading completed).

- 7. Enable the SAES peripheral, by setting EN.

- 8. Wait until CCF flag is set in the SAES_ISR register.

- 9. Clear the CCF flag, by setting the CCF bit in SAES_ICR register. The derived hardware secret key is available in SAES_KEYRx registers.

- 10. Repeat steps 8. and 9. if KEYSIZE is set.

- 11. Disable the SAES peripheral, by clearing EN.

At the end of this sequence, the hardware secret key derived from the public data in the SAES_IVRx registers is then immediately usable by the application for any AES operation (normal key mode, that is, with KMOD[1:0] = 0x0).

Note: The configuration KMOD[1:0] at 0x1 (wrapped key), CHMOD[2:0] at 0x2 (CTR chaining), and MODE at 0x0 (encryption) disables the peripheral, by automatically clearing the EN bit of the SAES_CR register.

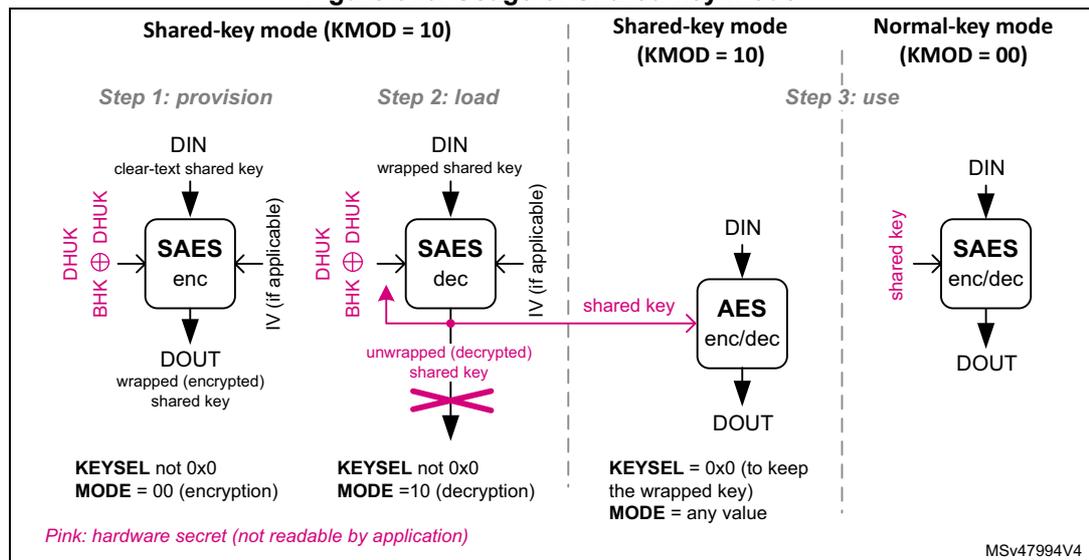

36.4.15 SAES operation with shared keys

SAES peripheral can share application keys wrapped with hardware-secret key DHUK, XOR-ed or not with application key BHK or AHK. With this feature, the application software can make the AES keys available to the CRYP peripheral, without exposing them in clear-text (unencrypted).

Shared key sequences are too small to be suspended/resumed. SAES cannot unwrap a shared key using an unwrapped key.

Figure 370 summarizes how to wrap or unwrap keys to share with CRYP peripheral. To protect the shared key, DHUK must be selected, by writing KEYSEL[2:0] with 0x1, 0x5, or 0x4. Alternatively, select BHK by writing KEYSEL[2:0] with 0x2 if the corresponding registers are read/write-locked in the TAMP peripheral. AHK can also be selected, by writing KEYSEL[2:0] with 0x3.

Figure 370. Usage of Shared-key mode

The diagram illustrates the usage of Shared-key mode for SAES, divided into three steps:

- Step 1: provision (Shared-key mode (KMOD = 10)): A clear-text shared key (DIN) is input to the SAES enc block. The block also receives DHUK (hardware secret) and BHK (hardware secret) as inputs. The output is a wrapped (encrypted) shared key (DOUT). The configuration is KEYSEL not 0x0 and MODE = 00 (encryption).

- Step 2: load (Shared-key mode (KMOD = 10)): The wrapped (encrypted) shared key (DIN) is input to the SAES dec block. The block also receives DHUK (hardware secret) and BHK (hardware secret) as inputs. The output is an unwrapped (decrypted) shared key (DOUT). The configuration is KEYSEL not 0x0 and MODE = 10 (decryption).

- Step 3: use : This step is split into two modes. In Shared-key mode (KMOD = 10), the unwrapped shared key is input to the AES enc/dec block. The configuration is KEYSEL = 0x0 (to keep the wrapped key) and MODE = any value. In Normal-key mode (KMOD = 00), a shared key is input to the SAES enc/dec block. The output is DOUT.

Pink: hardware secret (not readable by application)

Note: DHUK value depends on privilege, KMOD[1:0], KSHAREID, KEYSEL[2:0], CHMOD[2:0], and KEYSIZE.

In the step 3, AES represents the CRYP peripheral.

Key wrapping for CRYP peripheral

Before SAES can share a key with the CRYP peripheral, the key must be encrypted (wrapped) once. The encryption sequence of a shared key is the same as for a wrapped key, with KMOD[1:0] at 0x2 (shared key) and KSHAREID[1:0] kept at 0x0 in the step 3 in Figure 370. See Key wrapping for SAES for details.

Note: Encryption in Shared-key mode is only supported when ECB or CBC is selected.

Key unwrapping for CRYP peripheral (shared key)

Each time SAES needs to share a key with the CRYP peripheral, shared encrypted key must be decrypted (unwrapped) in SAES, then loaded by CRYP. The overall sequence is described next.

Sequence in the SAES peripheral

The decryption sequence of a shared key is the same as for a wrapped key, with KMOD[1:0] at 0x2 (shared key) and KSHAREID[1:0] kept at 0x0 in the step 3 in Figure 370 . See Key unwrapping for SAES for details.

In shared key mode when decryption mode is selected (MODE[1:0] at 0x2), a read access to the SAES_DOUTr register triggers a read error (RDERRF).

Note: Instead of being shared, a decrypted shared key can be used directly in SAES as the KEYSEL[2:0] bitfield is automatically cleared. In this case, KMOD[1:0] must be written with 0x0 (normal key mode).

Sequence in the CRYP peripheral

Once the shared key is decrypted in SAES key registers, it can be shared with the CRYP peripheral, while SAES peripheral remains in key sharing state, that is, with KMOD[1:0] at 0x2 and KEYVALID set. The sequence in the CRYP key share target peripheral is described in AES key sharing with secure AES co-processor of the corresponding section in this document. It can be run multiple times (for example, to manage a suspend/resume situation) as long as SAES is unused and duly remains in key sharing state.

Note: When KMOD[1:0] is at 0x2 and BUSY set in the CRYP peripheral, and KEYSIZE value of CRYP and SAES differs, the key sharing fails and the KEIF flag is raised in both peripherals.

When KEYSEL[2:0] is at 0x1 (DHUK), 0x5 (DHUK XOR AHK), or 0x4 (DHUK XOR BHK), the application software must use the same privilege, KMOD[1:0] / KSHAREID[1:0], CHMOD[2:0], and KEYSIZE context for encryption and decryption. Otherwise, the result is incorrect.

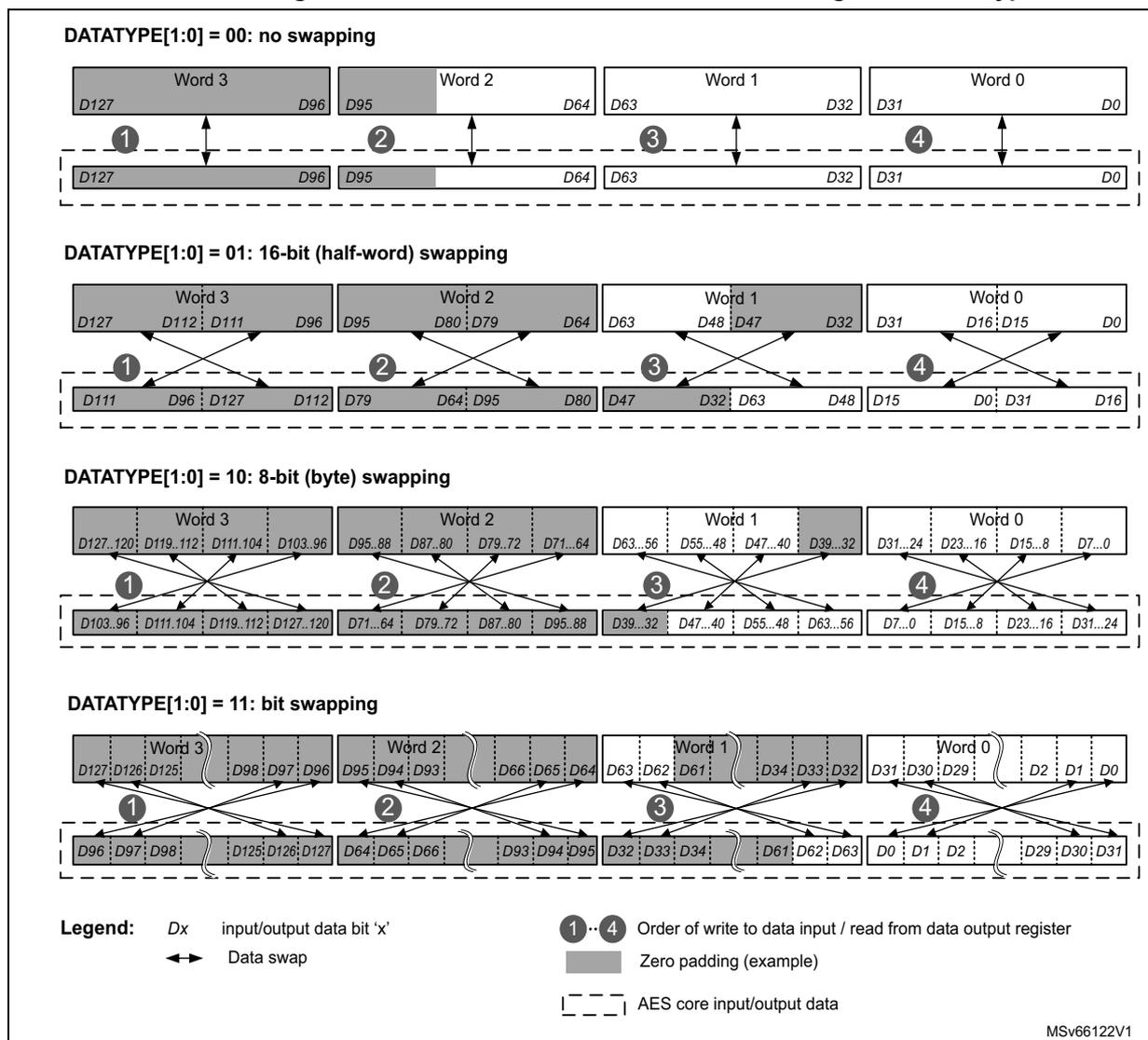

36.4.16 SAES data registers and data swapping

Data input and output

A 16-byte data block enters the SAES peripheral with four successive 32-bit word writes into the SAES_DINR register (bitfield DIN[31:0]), the most significant word (bits [127:96]) first, the least significant word (bits [31:0]) last.

A 16-byte data block is retrieved from the SAES peripheral with four successive 32-bit word reads of the SAES_DOUTr register (bitfield DOUT[31:0]), the most significant word (bits [127:96]) first, the least significant word (bits [31:0]) last.

The four 32-bit words of a 16-byte data block must be stored in the memory consecutively and in big-endian order, that is, with the most significant word on the lowest address. See Table 331 “no swapping” option for details.

Data swapping

The SAES peripheral can be configured to perform a bit-, a byte-, a half-word-, or no swapping on the input data word in the SAES_DINR register, before loading it to the AES processing core, and on the data output from the AES processing core, before sending it to

the SAES_DOUTR register. The choice depends on the type of data. For example, a byte swapping is used for an ASCII text stream.

The data swap type is selected through DATATYPE[1:0]. The selection applies to both SAES input and output.

Note: The data in SAES key registers (SAES_KEYRx) and initialization vector registers (SAES_IVRx) are not sensitive to the swap mode selection.

The SAES data swapping feature is summarized in Table 331 and Figure 371 .

Table 331. AES data swapping example

| DATATYPE[1:0] | Swapping performed | Data block |

|---|---|---|

| System memory data (big-endian) | ||

| 0x0 | No swapping | Block[127..64]: 0x04EEF672 2E04CE96 Block[63..0]: 0x4E6F7720 69732074 |

| Address @, word[127..96]: 0x04EEF672 Address @ + 0x4, word[95..64]: 0x2E04CE96 Address @ + 0x8, word[63..32]: 0x4E6F7720 Address @ + 0xC, word[31..0]: 0x69732074 | ||

| 0x1 | Half-word (16-bit) swapping | Block[63..0]: 0x 4E6F 7720 6973 2074 |

| Address @, word[63..32]: 0x7720

4E6F Address @ + 0x4, word[31..0]: 0x2074 6973 | ||

| 0x2 | Byte (8-bit) swapping | Block[63..0]: 0x 4E 6F 77 20 69 73 20 74 |

| Address @, word[63..32]: 0x20

77

6F4E Address @ + 0x4, word[31..0]: 0x74 20 7369 | ||

| 0x3 | Bit swapping | Block[63..32]: 0x4E6F7720 0100 1110 0110 1111 0111 0111 0010 0000 Block[31..0]: 0x69732074 0110 1001 0111 0011 0010 0000 0111 0100 |

| Address @, word[63..32]: 0x04EE F672 0000 0100 1110 1110 1111 0110 0111 0010 Address @ + 0x4, word[31..0]: 0x2E04 CE96 0010 1110 0000 0100 1100 1110 1001 0110 |

Figure 371. 128-bit block construction according to the data type

DATATYPE[1:0] = 00: no swapping

DATATYPE[1:0] = 01: 16-bit (half-word) swapping

DATATYPE[1:0] = 10: 8-bit (byte) swapping

DATATYPE[1:0] = 11: bit swapping

Legend:

- Dx: input/output data bit 'x'

- : Data swap

- : Order of write to data input / read from data output register

- : Zero padding (example)

- | - - - |: AES core input/output data

MSv66122V1

Data padding

Figure 371 also gives an example of memory data block padding with zeros such that the zeroed bits after the data swap form a contiguous zone at the MSB end of the AES core input buffer. The example shows the padding of an input data block containing:

- • 84 message bits, with DATATYPE[1:0] = 0x0

- • 48 message bits, with DATATYPE[1:0] = 0x1

- • 56 message bits, with DATATYPE[1:0] = 0x2

- • 34 message bits, with DATATYPE[1:0] = 0x3

36.4.17 SAES key registers

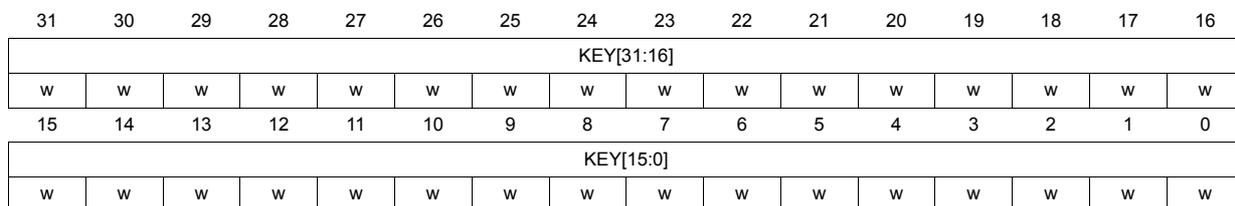

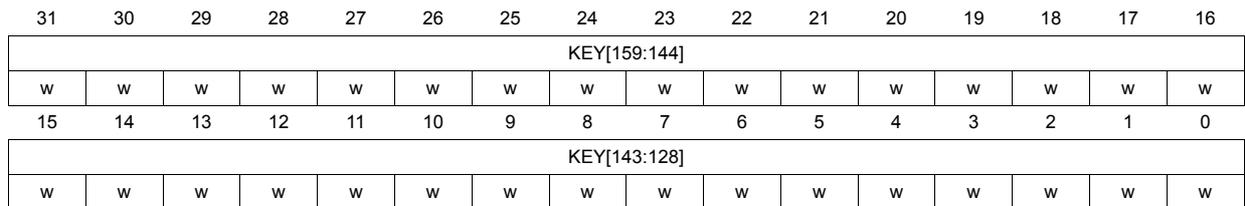

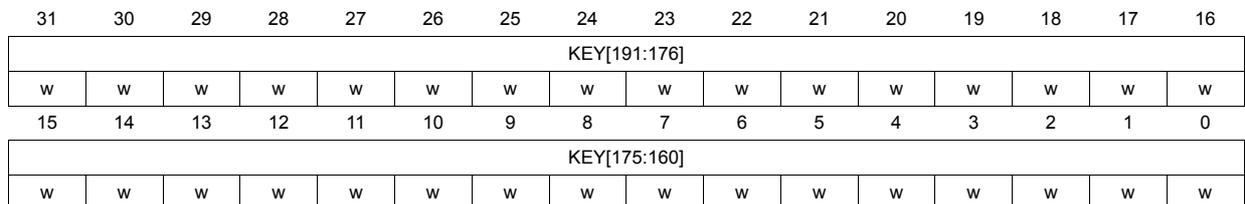

The eight SAES_KEYRx write-only registers store the encryption or decryption key information, as shown on Table 332 . Reads are not allowed for security reason.

Note: In memory and in SAES key registers, keys are stored in little-endian format, with most significant byte on the highest address.

Table 332. Key endianness in SAES_KEYRx registers (128/256-bit keys)

| SAES_KEYR 7 [31:0] | SAES_KEYR 6 [31:0] | SAES_KEYR 5 [31:0] | SAES_KEYR 4 [31:0] | SAES_KEYR 3 [31:0] | SAES_KEYR 2 [31:0] | SAES_KEYR 1 [31:0] | SAES_KEYR 0 [31:0] |

|---|---|---|---|---|---|---|---|

| - | - | - | - | KEY[127:96] | KEY[95:64] | KEY[63:32] | KEY[31:0] |