13. High-performance direct memory access controller (HPDMA)

13.1 HPDMA introduction

The high-performance direct memory access (HPDMA) controller is a bus master and system peripheral.

The HPDMA is used to perform programmable data transfers between memory-mapped peripherals, and/or memories via linked-lists, upon the control of an off-loaded CPU.

13.2 HPDMA main features

- • Single bidirectional 64-bit AXI master and single bidirectional 32-bit AHB master

- • Memory-mapped data transfers from a source to a destination:

- – Peripheral-to-memory

- – Memory-to-peripheral

- – Memory-to-memory

- – Peripheral-to-peripheral

- – One high-priority traffic class, for time-sensitive channels (queue 3)

- – Three low-priority traffic classes, with a weighted round-robin allocation for non time-sensitive channels (queues 0, 1, 2)

- • Per channel event generation, on any of the following events: transfer complete, half-transfer complete, data transfer error, user setting error, link transfer error, completed suspension, and trigger overrun

- • Per channel interrupt generation, with separately programmed interrupt enable per event

- • 16 concurrent HPDMA channels:

- – Per channel FIFO for queuing source and destination transfers (see Section 13.3.1 )

- – Intra-channel HPDMA transfers chaining via programmable linked-list into memory, supporting two execution modes: run-to-completion and link step mode

- • Per linked-list item within a channel:

- – Separately programmed source and destination transfers

- – Programmable data handling between source and destination: byte-based reordering, packing or unpacking, padding or truncation, sign extension and left/right realignment

- – Programmable number of data bytes to be transferred from the source, defining the block level

- – Linear source and destination addressing: either fixed or contiguously incremented addressing, programmed at block level, between successive burst transfers

- – 2D source and destination addressing: programmable signed address offsets between successive burst transfers (non-contiguous addressing within a block,

combined with programmable signed address offsets between successive blocks, at a second 2D/repeated block level, for a reduced set of channels (see Section 13.3.1 )

- – Support for scatter-gather (multi-buffer transfers), data interleaving and deinterleaving via 2D addressing

- – Selection of programmable HPDMA request and trigger

- – Generation of programmable HPDMA half-transfer and transfer-complete event

- – Pointer to the next linked-list item and its data structure in memory, with automatic update of the HPDMA linked-list control registers

- – Channel abort and restart

- • Debug:

- – Channel suspend and resume support

- – Channel status reporting, including FIFO level, and event flags

- • Privileged/unprivileged support:

- – Support for privileged and unprivileged HPDMA transfers, independently at channel level

- – Privileged-aware AHB slave port

13.3 HPDMA implementation

13.3.1 HPDMA channels

A given HPDMA channel x is implemented with the following features and intended use.

To make the best use of the HPDMA performance, the following table lists some general recommendations, allowing the user to select and allocate a channel, given its implemented FIFO size and the requested HPDMA transfer.

Table 100. Implementation of HPDMA1 channels

| Channel x | Hardware parameters | Features | |

|---|---|---|---|

| dma_fifo_size[x] | dma_addressing[x] | ||

| x = 0 to 11 | 3 | 0 | Channel x (x = 0 to 11) is implemented with:

|

| x = 12 to 15 | 5 | 1 | Channel x (x = 12 to 15) is implemented with:

|

13.3.2 HPDMA in low-power modes

The HPDMA wake-up feature is implemented in the device low-power modes as per the table below.

Table 101. HPDMA1 in low-power modes

| Feature | Low-power modes |

|---|---|

| Wake-up | HPDMA1 in Sleep mode |

13.3.3 HPDMA requests

An HPDMA request from a peripheral can be assigned to a HPDMA channel x, via REQSEL[4:0] in HPDMA_CxTR2, provided that SWREQ = 0.

The HPDMA requests mapping is specified in the table below.

Table 102. Programmed HPDMA1 request

| HPDMA_CxTR2.REQSEL[4:0] | Selected HPDMA request |

|---|---|

| 0 | jpeg_rx_dma |

| 1 | jpeg_tx_dma |

| 2 | xspi1_rx_dma |

| 3 | xspi2_rx_dma |

| 4 | spi3_rx_dma |

| 5 | spi3_tx_dma |

| 6 | spi4_rx_dma |

| 7 | spi4_tx_dma |

| 8 | adc1_dma |

| 9 | adc2_dma |

| 10 | adf1_flt0_dma |

| 11 | uart4_rx_dma |

| 12 | uart4_tx_dma |

| 13 | uart5_rx_dma |

| 14 | uart5_tx_dma |

| 15 | uart7_rx_dma |

| 16 | uart7_tx_dma |

| 17 | lptim2_ic1_dma |

| 18 | lptim2_ic2_dma |

| 19 | lptim2_ue_dma |

13.3.4 HPDMA block requests

Some HPDMA requests must be programmed as a block request, and not as a burst request. Then BREQ in HPDMA_CxTR2 must be set for a correct HPDMA execution of the requested peripheral transfer at the hardware level.

Table 103. Programmed HPDMA1 request as a block request

| HPDMA block requests |

|---|

| lptim2_ue_dma |

13.3.5 HPDMA channels with peripheral early termination

An HPDMA channel, if implemented with this feature, can support the early termination of the data transfer from the peripheral which does also support this feature.

Table 104. HPDMA1 channel with peripheral early termination

| HPDMA channel x with peripheral early termination |

|---|

| x = 15 |

This HPDMA support is activated when the channel x is programmed with HPDMA_CxTR2.PFREQ = 1. Then, the peripheral itself can initiate and request a data transfer completion, before the HPDMA has transferred the whole block (see Section 13.4.14 for more details).

Table 105. Programmed HPDMA request with peripheral early termination

| Programmed HPDMA channel x request with peripheral early termination |

|---|

| jpeg_tx_dma |

13.3.6 HPDMA triggers

An HPDMA trigger can be assigned to an HPDMA channel x, via TRIGSEL[5:0] in HPDMA_CxTR2, provided that TRIGPOL[1:0] defines a rising or a falling edge of the selected trigger (TRIGPOL[1:0] = 01 or TRIGPOL[1:0] = 10).

Table 106. Programmed HPDMA1 trigger

| HPDMA_CxTR2.TRIGSEL[5:0] | Selected HPDMA trigger |

|---|---|

| 0 | dcmpp_p0frame_evt |

| 1 | dcmip_p0hsync_evt |

| 2 | dcmpp_p0line_evt |

| 3 | dcmpp_p0vsync_evt |

| 4 | dma2d_ctc |

| 5 | dma2d_tc |

Table 106. Programmed HPDMA1 trigger (continued)

| HPDMA_CxTR2.TRIGSEL[5:0] | Selected HPDMA trigger |

|---|---|

| 6 | dma2d_tw |

| 7 | jpeg_eoc_trg |

| 8 | jpeg_ifnf_trg |

| 9 | jpeg_ift_trg |

| 10 | jpeg_ofne_trg |

| 11 | jpeg_oft_trg |

| 12 | lcd_li |

| 13 | gpu2d_gp_flag0 |

| 14 | gpu2d_gp_flag1 |

| 15 | gpu2d_gp_flag2 |

| 16 | gpu2d_gp_flag3 |

| 17 | gftxim_evt3 |

| 18 | gftxim_evt2 |

| 19 | gftxim_evt1 |

| 20 | gftxim_evt0 |

| 21 | gpdma1_ch0_tc |

| 22 | gpdma1_ch1_tc |

| 23 | gpdma1_ch2_tc |

| 24 | gpdma1_ch3_tc |

| 25 | gpdma1_ch4_tc |

| 26 | gpdma1_ch5_tc |

| 27 | gpdma1_ch6_tc |

| 28 | gpdma1_ch7_tc |

| 29 | gpdma1_ch8_tc |

| 30 | gpdma1_ch9_tc |

| 31 | gpdma1_ch10_tc |

| 32 | gpdma1_ch11_tc |

| 33 | gpdma1_ch12_tc |

| 34 | gpdma1_ch13_tc |

| 35 | gpdma1_ch14_tc |

| 36 | gpdma1_ch15_tc |

| 37 | hpdma1_ch0_tc |

| 38 | hpdma1_ch1_tc |

| 39 | hpdma1_ch2_tc |

| 40 | hpdma1_ch3_tc |

| HPDMA_CxTR2.TRIGSEL[5:0] | Selected HPDMA trigger |

|---|---|

| 41 | hpdma1_ch4_tc |

| 42 | hpdma1_ch5_tc |

| 43 | hpdma1_ch6_tc |

| 44 | hpdma1_ch7_tc |

| 45 | hpdma1_ch8_tc |

| 46 | hpdma1_ch9_tc |

| 47 | hpdma1_ch10_tc |

| 48 | hpdma1_ch11_tc |

| 49 | hpdma1_ch12_tc |

| 50 | hpdma1_ch13_tc |

| 51 | hpdma1_ch14_tc |

| 52 | hpdma1_ch15_tc |

13.4 HPDMA functional description

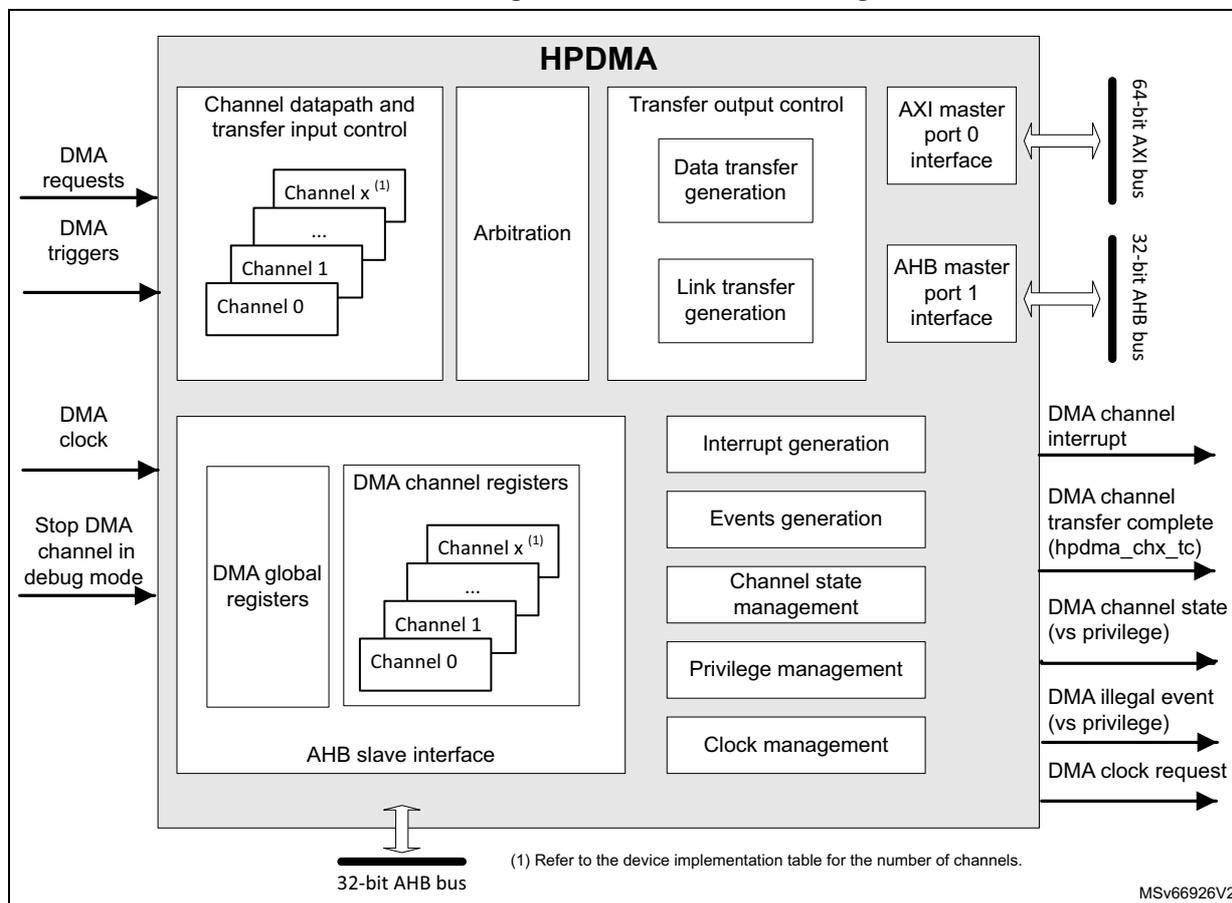

13.4.1 HPDMA block diagram

Figure 108. HPDMA block diagram

The block diagram illustrates the internal architecture and external connections of the HPDMA controller. The main HPDMA block contains several functional units:

- Channel datapath and transfer input control: Contains multiple channels (Channel 0, Channel 1, ..., Channel x (1) ).

- Arbitration: A central unit for managing channel priorities.

- Transfer output control: Includes 'Data transfer generation' and 'Link transfer generation'.

- AXI master port 0 interface: Connects to a 64-bit AXI bus.

- AHB master port 1 interface: Connects to a 32-bit AHB bus.

- AHB slave interface: Connects to a 32-bit AHB bus for register access.

- Registers: Divided into 'DMA global registers' and 'DMA channel registers' (one for each channel).

- Management and Control: Includes 'Interrupt generation', 'Events generation', 'Channel state management', 'Privilege management', and 'Clock management'.

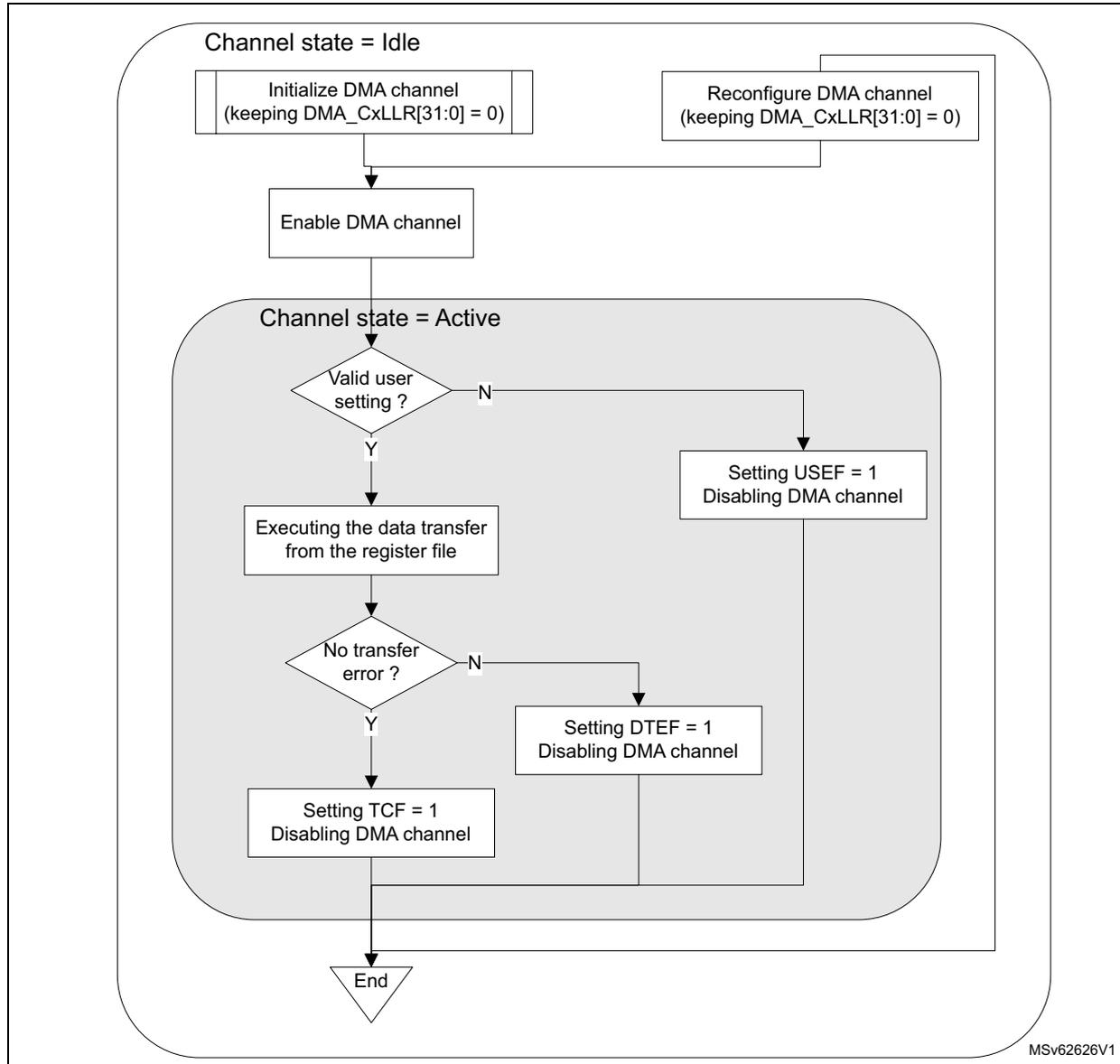

13.4.2 HPDMA channel state and direct programming without any linked-list

After an HPDMA reset, an HPDMA channel x is in idle state. When the software writes 1 into the HPDMA_CxCR.EN enable control bit, the channel takes into account the value of the different channel configuration registers (HPDMA_CxXXX), switches to the active/non-idle state, and starts to execute the corresponding requested data transfers.

After enabling/starting an HPDMA channel transfer by writing 1 into HPDMA_CxCR.EN, an HPDMA channel interrupt on a complete transfer notifies the software that the HPDMA channel is back in idle state (EN is then deactivated by hardware), and that the channel is ready to be reconfigured then enabled again.

The figure below illustrates this HPDMA direct programming without any linked-list (HPDMA_CxLLR = 0).

Figure 109. HPDMA channel direct programming without linked-list (HPDMA_CxLLR = 0)

graph TD; subgraph Idle; A[Initialize DMA channel

(keeping DMA_CxLLR[31:0] = 0)]; B[Reconfigure DMA channel

(keeping DMA_CxLLR[31:0] = 0)]; end; A --> C[Enable DMA channel]; B --> C; C --> D{Valid user setting?}; subgraph Active; D -- N --> E[Setting USEF = 1

Disabling DMA channel]; D -- Y --> F[Executing the data transfer

from the register file]; F --> G{No transfer error?}; G -- N --> H[Setting DTEF = 1

Disabling DMA channel]; G -- Y --> I[Setting TCF = 1

Disabling DMA channel]; end; E --> J((End)); H --> J; I --> J;

The flowchart illustrates the HPDMA channel direct programming process without a linked-list. It starts with the channel in an 'Idle' state, where the DMA channel is initialized or reconfigured, keeping DMA_CxLLR[31:0] = 0. The channel is then enabled. The state changes to 'Active'. A decision is made: 'Valid user setting?'. If 'No' (N), the channel is disabled by setting USEF = 1. If 'Yes' (Y), the data transfer is executed from the register file. Another decision is made: 'No transfer error?'. If 'No' (N), the channel is disabled by setting DTEF = 1. If 'Yes' (Y), the channel is disabled by setting TCF = 1. All three disabling paths lead to the 'End' state.

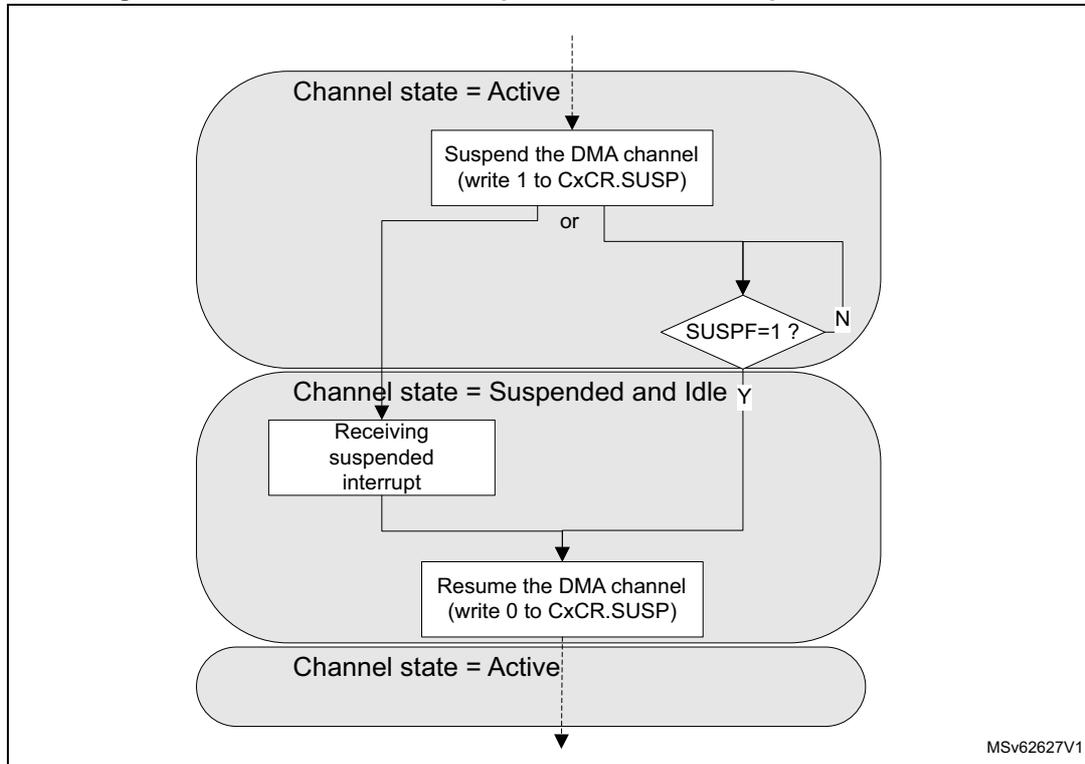

13.4.3 HPDMA channel suspend and resume

The software can suspend on its own a channel still active, with the following sequence:

- 1. The software writes 1 into the HPDMA_CxCR.SUSP bit.

- 2. The software polls the suspended flag HPDMA_CxSR.SUSPF until SUSPF = 1, or waits for an interrupt previously enabled by writing 1 to HPDMA_CxCR.SUSPIE. Wait for the channel to be effectively in suspended state means wait for the completion of any ongoing HPDMA transfer over its master ports. Then the software can observe, in a steady state, any read register or bitfield that is hardware modifiable.

Note: An ongoing HPDMA transfer can be a data transfer (a source/destination burst transfer,) or a link transfer for the internal update of the linked-list register file from the next linked-list item.

- 3. The software safely resumes the suspended channel by writing 0 to HPDMA_CxCR.SUSP.

Figure 110. HPDMA channel suspend and resume sequence

graph TD; subgraph Active [Channel state = Active]; A1[Suspend the DMA channel<br/>(write 1 to CxCR.SUSP)]; A2[or]; end; A1 --> D{SUSPF=1?}; A2 --> D; D -- N --> A1; D -- Y --> Suspended [Channel state = Suspended and Idle]; subgraph Suspended; S1[Receiving suspended interrupt]; S2[Resume the DMA channel<br/>(write 0 to CxCR.SUSP)]; end; S1 --> S2; S2 --> Active2[Channel state = Active];MSV62627V1

Note: A suspend and resume sequence does not impact the HPDMA_CxCR.EN bit. Suspending a channel (transfer) does not suspend a started trigger detection.

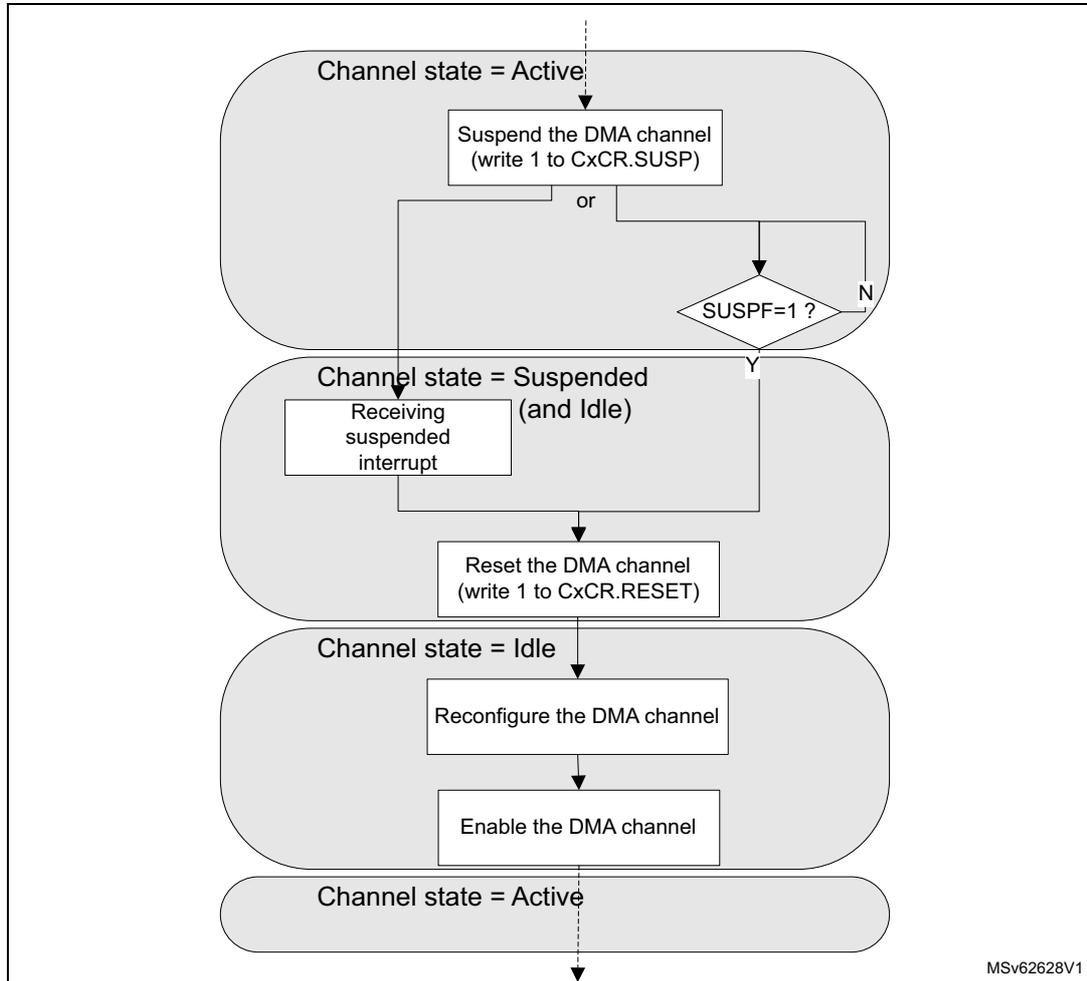

13.4.4 HPDMA channel abort and restart

Alternatively, like for aborting a continuous HPDMA transfer with a circular buffering or a double buffering, the software can abort, on its own, a still active channel with the following sequence:

- 1. The software writes 1 into the HPDMA_CxCR.SUSP bit.

- 2. The software polls suspended flag HPDMA_CxSR.SUSPF until SUSPF = 1, or waits for an interrupt previously enabled by writing 1 to HPDMA_CxCR.SUSPIE. Wait for the channel to be effectively in suspended state means wait for the completion of any ongoing HPDMA transfer over its master port.

- 3. The software resets the channel by writing 1 to HPDMA_CxCR.RESET. This causes the reset of the FIFO, the reset of the channel internal state, the reset of the HPDMA_CxCR.EN bit, and the reset of the HPDMA_CxCR.SUSP bit.

- 4. The software safely reconfigures the channel. The software must reprogram hardware-modified HPDMA_CxBR1, HPDMA_CxSAR, and HPDMA_CxDAR.

- 5. In order to restart the aborted then reprogrammed channel, the software enables it again by writing 1 to the HPDMA_CxCR.EN bit.

Figure 111. HPDMA channel abort and restart sequence

graph TD

subgraph State1 [Channel state = Active]

S1[Suspend the DMA channel

(write 1 to CxCR.SUSP)]

D1{SUSPF=1?}

S1 --> D1

D1 -- N --> S1

end

S1 --> State2 [Channel state = Suspended

(and Idle)]

subgraph State2

I1[Receiving suspended

interrupt]

R1[Reset the DMA channel

(write 1 to CxCR.RESET)]

I1 --> R1

end

R1 --> State3 [Channel state = Idle]

subgraph State3

Re[Reconfigure the DMA channel]

En[Enable the DMA channel]

Re --> En

end

En --> State4 [Channel state = Active]

The flowchart illustrates the sequence for aborting and restarting an HPDMA channel. It begins with the channel in an 'Active' state. The first step is to 'Suspend the DMA channel (write 1 to CxCR.SUSP)'. A decision point follows: 'SUSPF=1?'. If 'No' (N), the process loops back to the suspension step. If 'Yes' (Y), the channel enters a 'Suspended (and Idle)' state. In this state, the software receives a 'suspended interrupt' and then 'Resets the DMA channel (write 1 to CxCR.RESET)'. Following the reset, the channel enters an 'Idle' state. In this state, the software will 'Reconfigure the DMA channel' and then 'Enable the DMA channel'. Finally, the channel returns to an 'Active' state.

MSv62628V1

13.4.5 HPDMA linked-list data structure

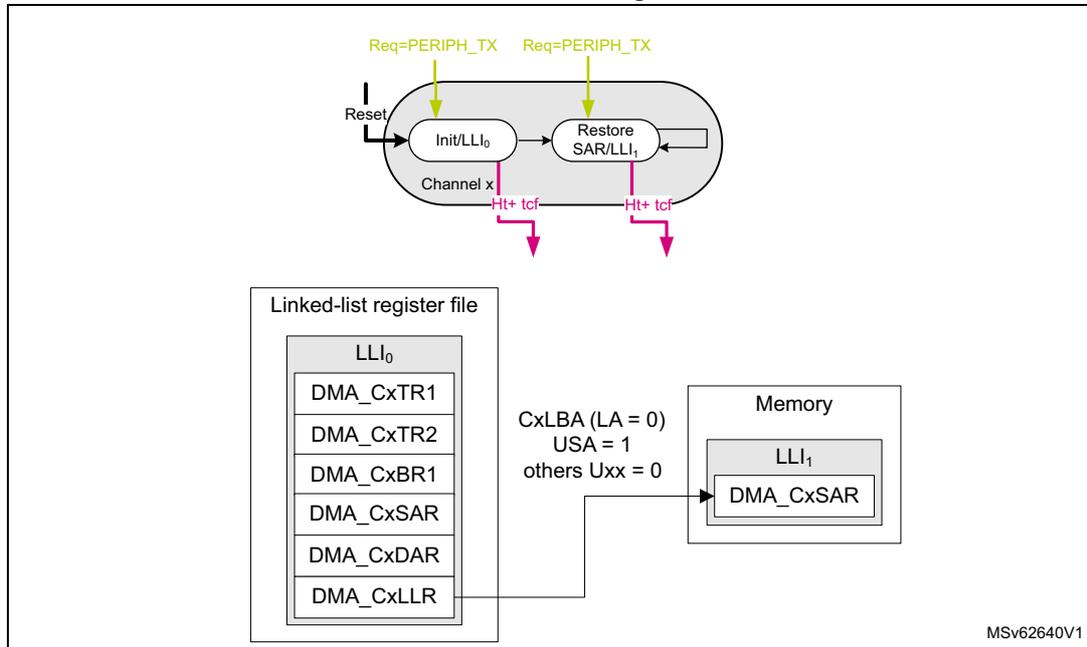

Alternatively to the direct programming mode, a channel can be programmed by a list of transfers, known as a list of linked-list items (LLI). Each LLI is defined by its data structure.

For a channel x, the base address in memory of the data structure of a next LLI n+1 is the sum of the following:

- • the link base address of the channel x (in HPDMA_CxLBAR)

- • the link address offset LA[15:2] bitfield in HPDMA_CxLLR, that is the updated result from the data structure of the previous LLI n of the channel x

The data structure for each LLI can be specific.

A linked-list data structure is addressed following the value of UT1, UT2, UB1, USA, UDA, and ULL bits, plus UB2 and UT3 when present, in HPDMA_CxLLR.

In linked-list mode, each HPDMA linked-list register (HPDMA_CxTR1, HPDMA_CxTR2, HPDMA_CxBR1, HPDMA_CxSAR, HPDMA_CxDAR or HPDMA_CxLLR,

plus HPDMA_CxTR3 or HPDMA_CxBR2 when present) is conditionally and automatically updated from the next linked-list data structure in the memory, following the current value of HPDMA_CxLLR that was conditionally updated from the linked-list data structure of the previous LLI.

Caution: The user must program the pointer to the next linked-list data structure (HPDMA_CxLLR[15:0]) not to exceed the 64-Kbyte addressable space defined by the link base address register (HPDMA_CxLBAR). The complete linked-list data structure must be included in the 64-Kbyte addressable space.

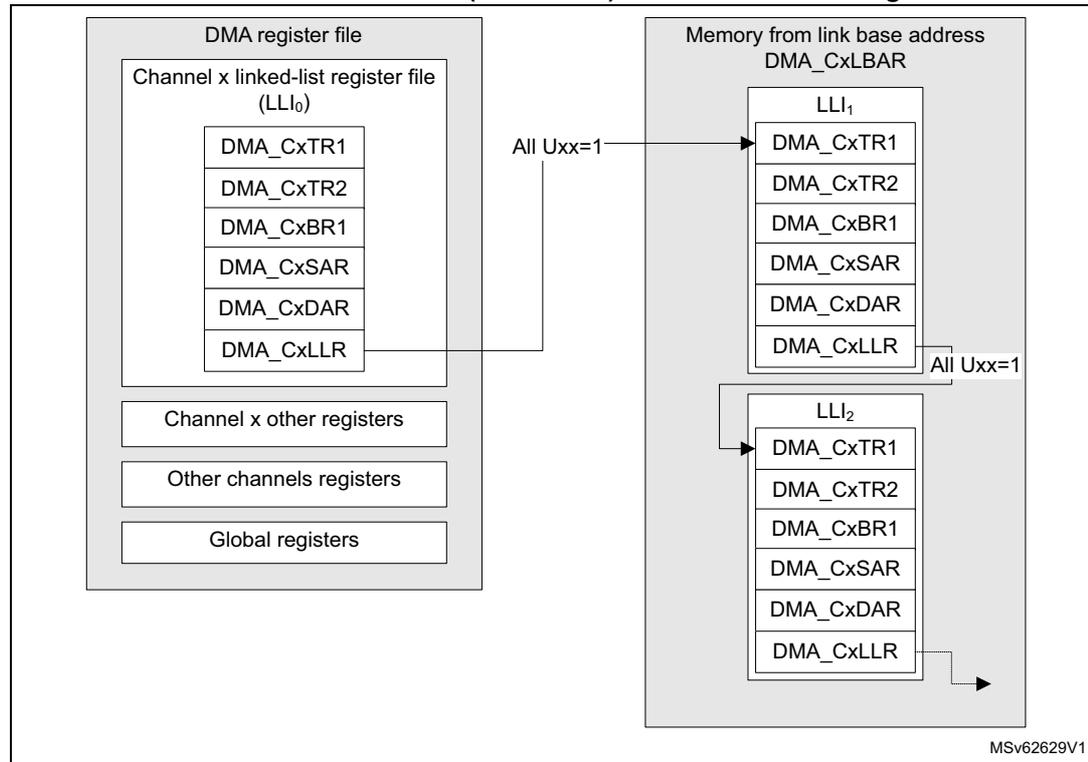

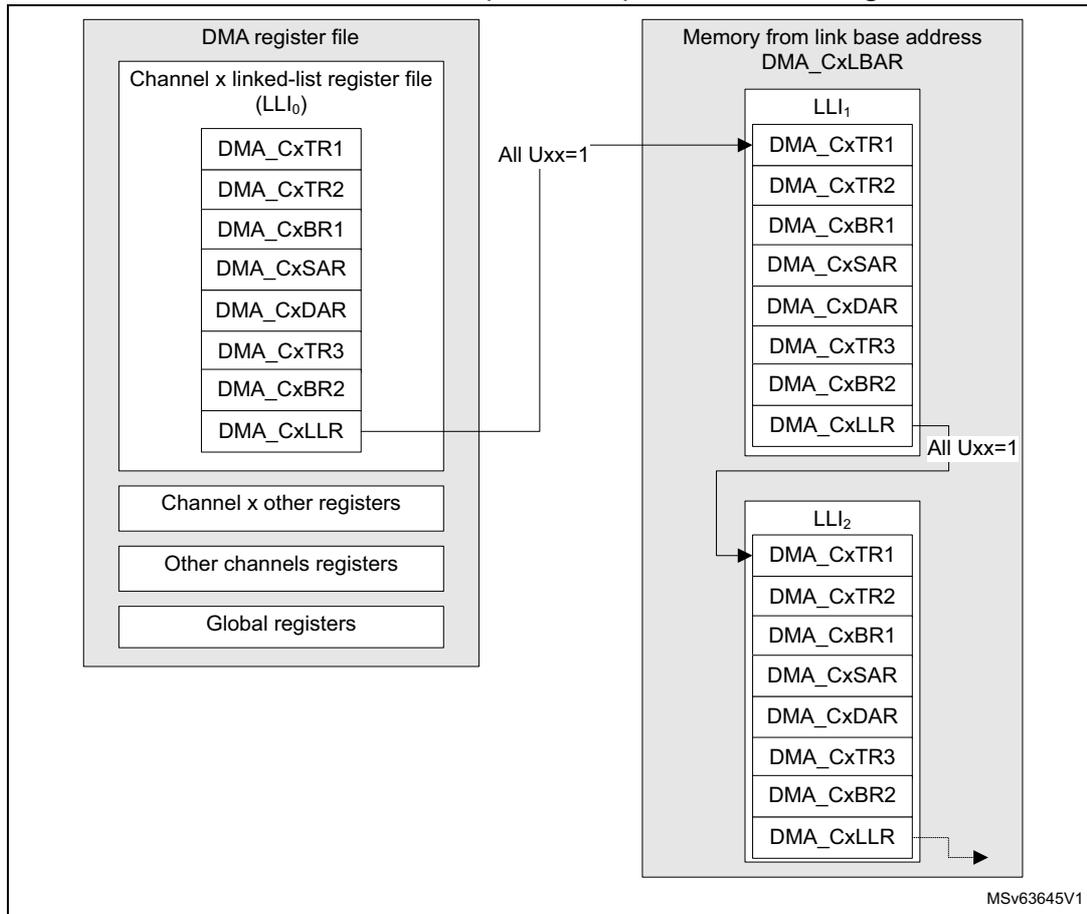

Static linked-list data structure

For example, when the update bits (UT1, UT2, UB1, USA, UDA, and ULL, plus UB2 and UT3 when present) in HPDMA_CxLLR are all asserted, the linked-list data structure in the memory is maximal with:

- • for channels without 2D addressing capability: six contiguous 32-bit locations, including HPDMA_CxTR1, HPDMA_CxTR2, HPDMA_CxBR1, HPDMA_CxSAR, HPDMA_CxDAR, and HPDMA_CxLLR (see Figure 112) and including the first linked-list register file (LLI 0 ), and the next LLIs (LLI 1 , LLI 2 ,...) in the memory

- • for channels with 2D addressing capability: eight contiguous 32-bit locations, including HPDMA_CxTR1, HPDMA_CxTR2, HPDMA_CxBR1, HPDMA_CxSAR, HPDMA_CxDAR, and HPDMA_CxLLR, plus HPDMA_CxTR3 and HPDMA_CxBR2 (see Figure 113), including the first linked-list register file (LLI 0 ), and the next LLIs (LLI 1 , LLI 2 ,...) in the memory

Figure 112. Static linked-list data structure (all Uxx = 1) of a linear addressing channel x

The diagram illustrates the static linked-list data structure for a linear addressing channel x. On the left, the DMA register file is shown, containing the Channel x linked-list register file (LLI 0 ) with registers DMA_CxTR1, DMA_CxTR2, DMA_CxBR1, DMA_CxSAR, DMA_CxDAR, and DMA_CxLLR. Below this are Channel x other registers, Other channels registers, and Global registers. On the right, the memory from the link base address DMA_CxLBAR is shown, containing LLI 1 and LLI 2 . Each LLI contains registers DMA_CxTR1, DMA_CxTR2, DMA_CxBR1, DMA_CxSAR, DMA_CxDAR, and DMA_CxLLR. The DMA_CxLLR register in LLI 0 points to LLI 1 , and the DMA_CxLLR register in LLI 1 points to LLI 2 . The condition 'All Uxx=1' is indicated for the registers in the LLIs.

The diagram illustrates the static linked-list data structure for a 2D addressing channel x. On the left, the DMA register file is shown, containing the Channel x linked-list register file (LLI 0 ) with registers DMA_CxTR1, DMA_CxTR2, DMA_CxBR1, DMA_CxSAR, DMA_CxDAR, DMA_CxTR3, DMA_CxBR2, and DMA_CxLLR. Below this are Channel x other registers, Other channels registers, and Global registers. An arrow labeled "All Uxx=1" points from the DMA_CxLLR register in LLI 0 to the first LLI in memory. On the right, the memory from link base address DMA_CxLBAR is shown, containing LLI 1 and LLI 2 . Each LLI contains the same registers as LLI 0 . An arrow labeled "All Uxx=1" points from the DMA_CxLLR register in LLI 1 to the start of LLI 2 . An arrow points from the DMA_CxLLR register in LLI 2 to the right, indicating the next LLI. The identifier MSv63645V1 is at the bottom right.

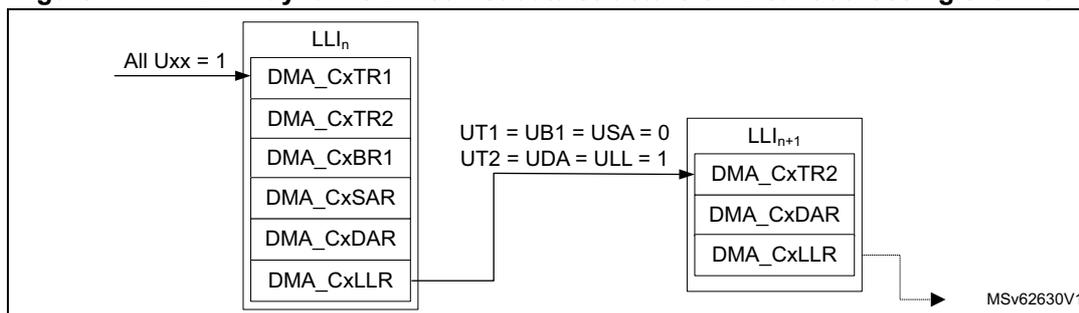

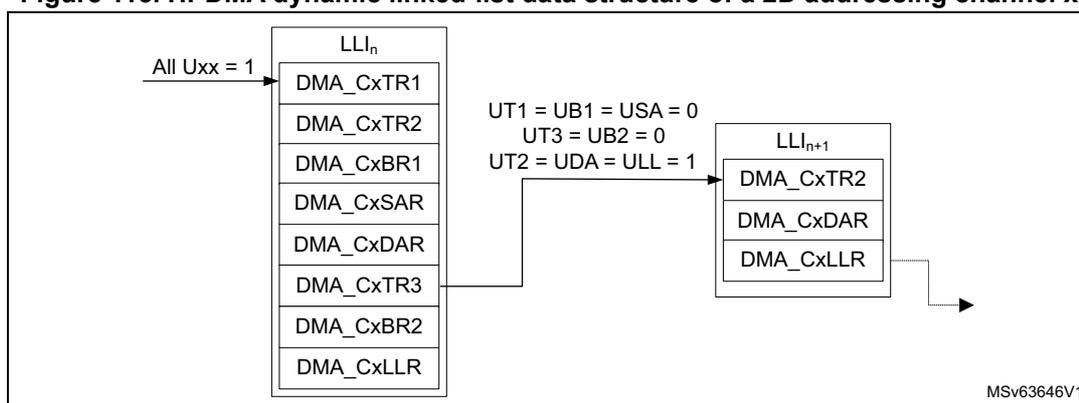

Dynamic linked-list data structure

Alternatively, the memory organization for the full list of LLIs can be compacted with specific data structure for each LLI.

If UT1 = 0 and UT2 = 1, the link address offset of HPDMA_CxLLR points to the updated value of HPDMA_CxTR2, instead of HPDMA_CxTR1 which is not to be modified (see Figure 114 ).

Example: if UT1 = UB1 = USA = 0, and if UT3 = UB2 = 0 when channel x is with 2D addressing, and if UT2 = UDA = ULL = 1, the next LLI does not contain an (updated) value for HPDMA_CxTR1, nor HPDMA_CxBR1, nor HPDMA_CxSAR, nor HPDMA_CxTR3, nor HPDMA_CxBR2 when channel x is with 2D addressing. The next LLI contains an updated value for HPDMA_CxTR2, HPDMA_CxDAR, and HPDMA_CxLLR, as shown in Figure 115 .

Figure 114. HPDMA dynamic linked-list data structure of linear addressing channel x

Figure 115. HPDMA dynamic linked-list data structure of a 2D addressing channel x

13.4.6 Linked-list item transfer execution

An LLI n transfer is the sequence of:

- 1. a data transfer: the HPDMA executes the data transfer as described by the HPDMA internal register file (this data transfer can be void/null for LLI 0 ).

- 2. a conditional link transfer: the HPDMA automatically and conditionally updates its internal register file by the data structure of the next LLI n+1 , as defined by the HPDMA_CxLLR value of the LLI n .

Note: The initial data transfer, as defined by the internal register file (LLI 0 ), can be null (HPDMA_CxBR1.BNDT[15:0] = 0 and HPDMA_CxTR2.PFREQ = 0), provided that UB1 is set in HPDMA_CxLLR (meaning there is a non-null data transfer described by the next LLI 1 in the memory to be executed).

Depending on the intended HPDMA use, an HPDMA channel x can be executed as described by the full linked-list (run-to-completion mode, HPDMA_CxCR.LSM = 0), or can be programmed for a single execution of a LLI (link step mode, HPDMA_CxCR.LSM = 1), as described in the next sections.

13.4.7 HPDMA channel state and linked-list programming in run-to-completion mode

When HPDMA_CxCR.LSM = 0 (in full-list execution mode, execution of the full sequence of LLIs, named run-to-completion mode), an HPDMA channel x is initially programmed, started

by writing 1 to HPDMA_CxCR.EN, and after completed at channel level.

The channel transfer is:

- • configured with at least the following:

- – the first \( LLI_0 \) , internal linked-list register file: HPDMA_CxTR1, HPDMA_CxTR2, HPDMA_CxBR1, HPDMA_CxSAR, HPDMA_CxDAR, and HPDMA_CxLLR, plus HPDMA_CxTR3 and HPDMA_CxBR2 when present

- – the last \( LLI_N \) described by the linked-list data structure in memory, as defined by HPDMA_CxLLR reflecting the before last \( LLI_{N-1} \)

- • completed when HPDMA_CxLLR[31:0] = 0 and HPDMA_CxBR1.BRC[10:0] = 0, if BRC[10:0] is present and HPDMA_CxBR1.BNDT[15:0] = 0, at the end of the last \( LLI_{N-1} \) transfer

HPDMA_CxLLR[31:0] = 0 is the condition of a linked-list based channel completion, and means the following:

- • The 16 low significant bits HPDMA_CxLLR.LA[15:0] of the next link address are null.

- • All bits HPDMA_CxLLR.Uxx are null (UT1, UT2, UB1, USA, UDA, and ULL, plus UB2 and UT3 when present).

The channel may never be completed when HPDMA_CxLLR.LSM = 0:

- • If the last

\(

LLI_N

\)

is recursive, pointing to itself as a next LLI, in one of the following:

- – HPDMA_CxLLR.ULL = 1 and HPDMA_CxLLR.LA[15:2] is updated with the same value.

- – HPDMA_CxLLR.ULL = 0

- • If \( LLI_N \) points to a previous LLI

At the regular data transfer completion at a block level, HPDMA_CxBR1.BNDT[15:0] = 0 and HPDMA_CxBR1.BRC[10:0] = 0 (if present). Alternatively, a block transfer may be early completed by a peripheral (such as an I3C in Rx mode), and then BNDT[15:0] is not null (see Section 13.4.14 for more details).

In the typical run-to-completion mode, the allocation of an HPDMA channel, including its fine programming, is done once during the HPDMA initialization. In order to have a reserved data communication link and HPDMA service during run-time, for continuously repeated transfers (from/to a peripheral respectively to/from memory or for memory-to-memory transfers). This reserved data communication link can consist of a channel, or the channel can be shared and a repeated transfer consists of a sequence of LLIs.

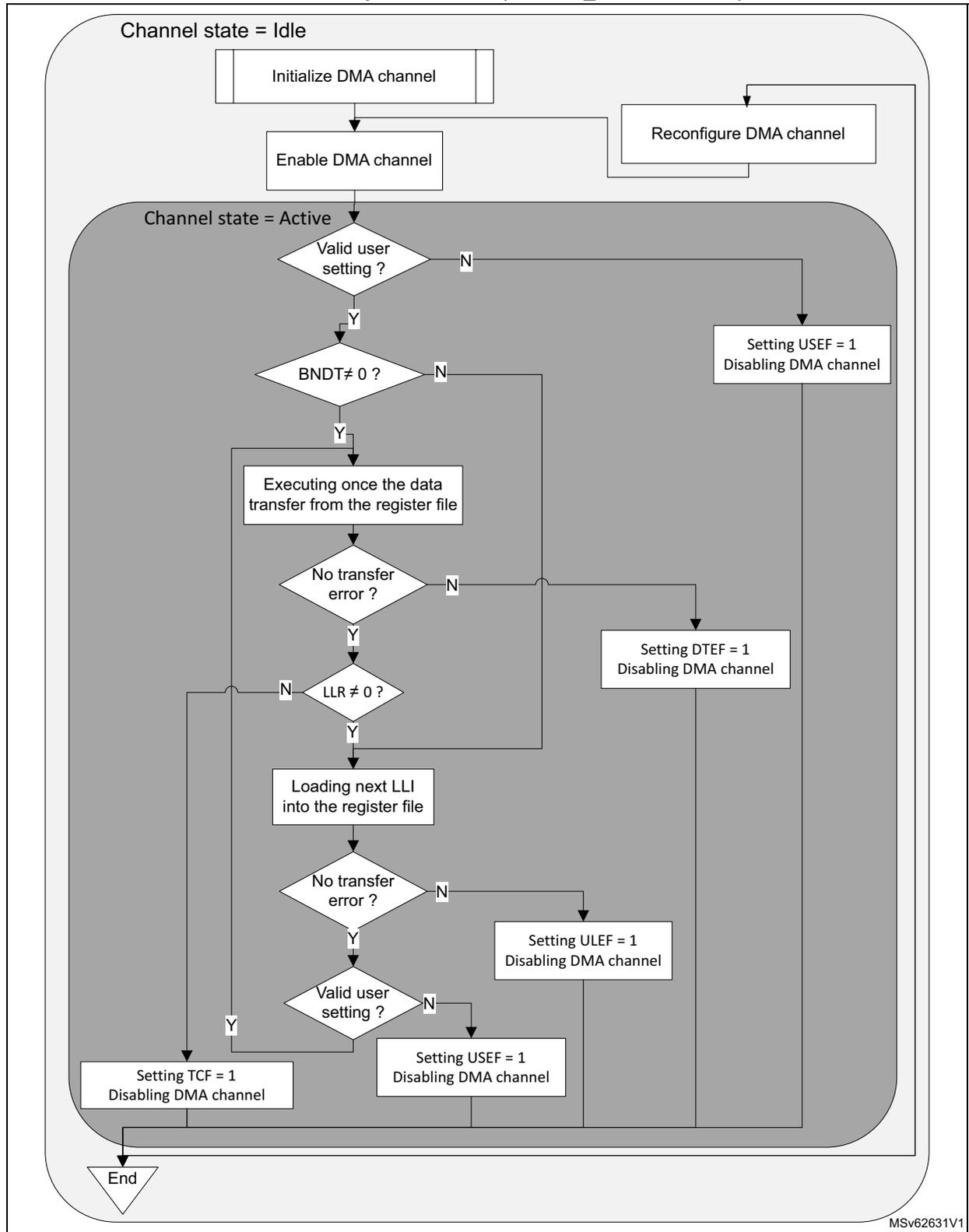

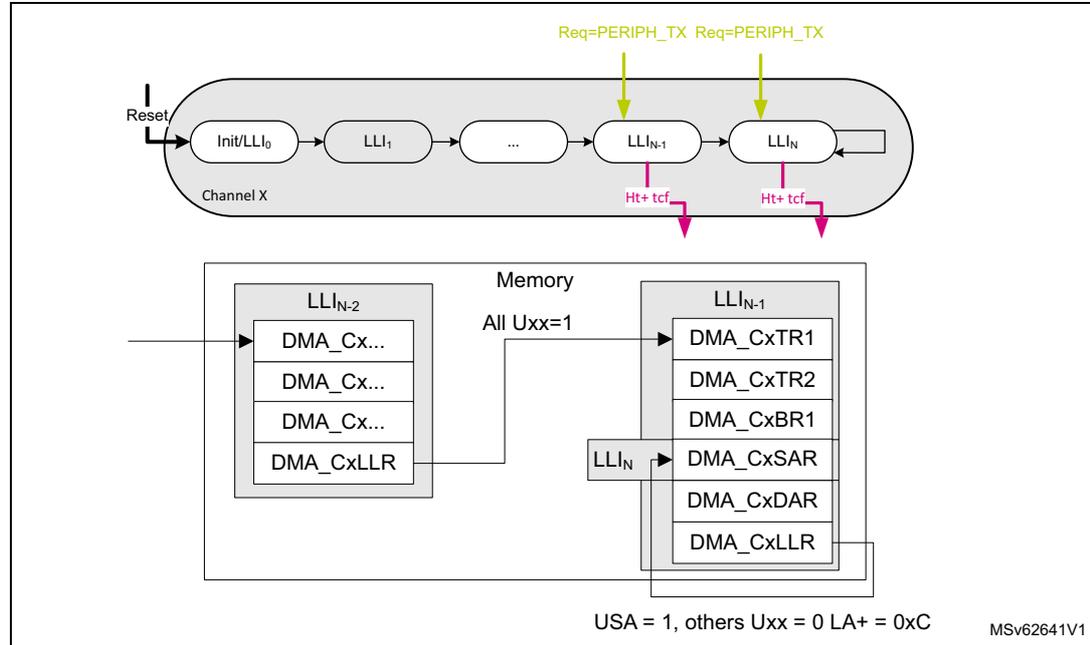

Figure 116 depicts the HPDMA channel execution and its registers programming in run-to-completion mode.

Note: Figure 116 is not intended to illustrate how often a TCEF can be raised, depending on the programmed value of TCEM[1:0] in HPDMA_CxTR2. It can be raised at (each) block completion, at (each) 2D block completion, at (each) LLI completion, or only at channel completion. In run-to-completion mode, whatever is the value of TCEM[1:0], at the channel completion, the hardware always set TCEF = 1 and disables the channel.

In Figure 116 , BNDT \( \neq \) 0 is the typical condition for starting the first data transfer. This condition becomes (BNDT \( \neq \) 0 and PFREQ = 1) if the peripheral requests a data transfer with early termination (see Section 13.3.5 ).

Figure 116. HPDMA channel execution and linked-list programming in run-to-completion mode (HPDMA_CxCR.LSM = 0)

graph TD; subgraph Idle; A[Initialize DMA channel] --> B[Enable DMA channel]; B --> C{Valid user setting?}; C -- N --> D[Setting USEF = 1<br/>Disabling DMA channel]; D --> E[Reconfigure DMA channel]; E --> A; C -- Y --> F{BNDT ≠ 0?}; F -- N --> G[No transfer error?]; F -- Y --> H[Executing once the data transfer from the register file]; H --> G; G -- N --> I[Setting DTEF = 1<br/>Disabling DMA channel]; G -- Y --> J{LLR ≠ 0?}; J -- N --> K[Setting TCF = 1<br/>Disabling DMA channel]; J -- Y --> L[Loading next LLI<br/>into the register file]; L --> M{No transfer error?}; M -- N --> N1[Setting ULEF = 1<br/>Disabling DMA channel]; M -- Y --> O{Valid user setting?}; O -- N --> N2[Setting USEF = 1<br/>Disabling DMA channel]; O -- Y --> K; end; subgraph Active; C; F; H; G; J; L; M; O; K; N1; N2; end; K --> P{End}; N1 --> P; N2 --> P; I --> P;The flowchart illustrates the execution and linked-list programming of an HPDMA channel in run-to-completion mode. It is divided into two main states: 'Channel state = Idle' and 'Channel state = Active'.

Channel state = Idle:

- The process starts with 'Initialize DMA channel'.

- Next is 'Enable DMA channel'.

- A decision diamond 'Valid user setting?' follows. If 'N' (No), it proceeds to 'Setting USEF = 1 Disabling DMA channel', which then leads to 'Reconfigure DMA channel' and loops back to 'Initialize DMA channel'. If 'Y' (Yes), it proceeds to the 'Active' state.

Channel state = Active:

- The first decision is 'Valid user setting?'. If 'N', it leads to 'Setting USEF = 1 Disabling DMA channel'. If 'Y', it proceeds to 'BNDT ≠ 0?'.

- 'BNDT ≠ 0?': If 'N', it leads to 'No transfer error?'. If 'Y', it leads to 'Executing once the data transfer from the register file'.

- 'Executing once the data transfer from the register file' leads to 'No transfer error?'.

- 'No transfer error?': If 'N', it leads to 'Setting DTEF = 1 Disabling DMA channel'. If 'Y', it proceeds to 'LLR ≠ 0?'.

- 'LLR ≠ 0?': If 'N', it leads to 'Setting TCF = 1 Disabling DMA channel'. If 'Y', it leads to 'Loading next LLI into the register file'.

- 'Loading next LLI into the register file' leads to 'No transfer error?'.

- 'No transfer error?': If 'N', it leads to 'Setting ULEF = 1 Disabling DMA channel'. If 'Y', it proceeds to 'Valid user setting?'.

- 'Valid user setting?': If 'N', it leads to 'Setting USEF = 1 Disabling DMA channel'. If 'Y', it leads to 'Setting TCF = 1 Disabling DMA channel'.

- All 'Disabling DMA channel' paths lead to the 'End' state.

MSv62631V1

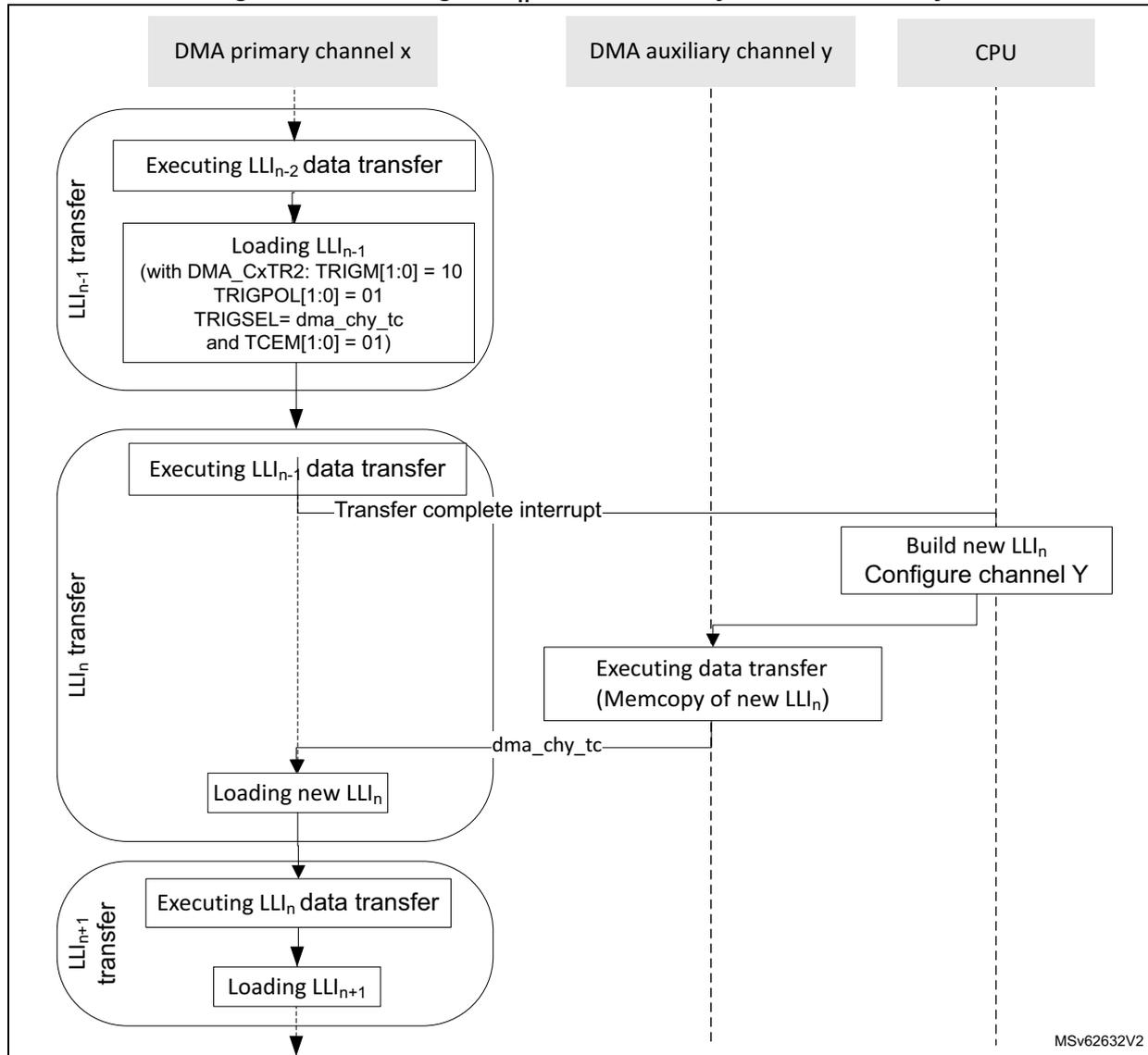

Run-time inserting a \( LLI_n \) via an auxiliary channel, in run-to-completion modeThe start of the link transfer of the \( LLI_{n-1} \) (start of the \( LLI_n \) loading) can be conditioned by the occurrence of a trigger, when programming the following bitfields of HPDMA_CxTR2 in the data structure of the \( LLI_{n-1} \) :

- • TRIGM[1:0] = 10 (link transfer triggering mode)

- • TRIGPOL[1:0] = 01 or 10 (rising or falling edge)

- • TRIGSEL[5:0] (see Section 13.3.6 for the trigger selection details)

Another auxiliary channel y can be used to store the channel x \( LLI_n \) in the memory, and to generate a transfer complete event hpdma_chy_tc. By selecting this event as the input trigger of the link transfer of the \( LLI_{n-1} \) of the channel x, the software can pause the primary channel x after its \( LLI_{n-1} \) data transfer, until it is indeed written the \( LLI_n \) .

Figure 117 depicts such a dynamic elaboration of a linked-list of a primary channel x, via another auxiliary channel y.

Caution: This use case is restricted to an application with an \( LLI_{n-1} \) data transfer that does not need a trigger. The triggering mode of this \( LLI_{n-1} \) is used to load the next \( LLI_n \) .

Figure 117. Inserting a\( LLI_n \) with an auxiliary HPDMA channel y

sequenceDiagram

participant DMA as DMA primary channel x

participant CPU as CPU

participant Aux as DMA auxiliary channel y

Note left of DMA: LLI_{n-2} transfer

DMA->>DMA: Executing LLI_{n-2} data transfer

Note left of DMA: LLI_{n-1} transfer

DMA->>DMA: Loading LLI_{n-1} (with DMA_CxTR2: TRIGM[1:0] = 10, TRIGPOL[1:0] = 01, TRIGSEL = dma_chy_tc and TCEM[1:0] = 01)

Note left of DMA: LLI_n transfer

DMA->>DMA: Executing LLI_{n-1} data transfer

DMA->>CPU: Transfer complete interrupt

Note right of CPU: Build new LLI_n, Configure channel Y

Note right of Aux: Executing data transfer (Memcpy of new LLI_n)

Aux->>DMA: dma_chy_tc

Note left of DMA: LLI_{n+1} transfer

DMA->>DMA: Loading new LLI_n

DMA->>DMA: Executing LLI_n data transfer

DMA->>DMA: Loading LLI_{n+1}

MSv62632V2

13.4.8 HPDMA channel state and linked-list programming in link step mode

When \( HPDMA\_CxCR.LSM = 1 \) (in link step execution mode, single execution of one \( LLI \) ), a channel transfer is executed and completed after each single execution of a \( LLI \) , including its (conditional) data transfer and its (conditional) link transfer.

An HPDMA channel transfer can be programmed at an \( LLI \) level, started by writing 1 into \( HPDMA\_CxCR.EN \) , and after completed at \( LLI \) level:

- • The current

\(

LLI_n

\)

transfer is described with the following:

- – \( HPDMA\_CxTR1 \) defines the source/destination elementary single/burst transfers.

- – \( HPDMA\_CxBR1 \) defines the number of bytes at a block level ( \( BNDT[15:0] \) ), and for channels with 2D addressing it defines also the number of blocks at a

2D/repeated block level (BRC[10:0]+1), and the incrementing/decrementing mode for address offsets.

- – HPDMA_CxTR2 defines the input control (request, trigger), and the output control (transfer-complete event) of the transfer.

- – HPDMA_CxSAR and HPDMA_CxDAR define the source/destination transfer start address.

- – HPDMA_CxTR3 for channels with 2D addressing defines the source/destination additional address offset between burst transfers.

- – HPDMA_CxBR2 for channels with 2D addressing defines the source/destination additional address offset between blocks at a 2D/repeated block level.

- – HPDMA_CxLLR defines the data structure, and the address offset of the next \( LLI_{n+1} \) in the memory.

- • The current

\(

LLI_n

\)

transfer is completed after the single execution of the current

\(

LLI_n

\)

:

- – after the (conditional) data transfer completion (when HPDMA_CxBR1.BRC[10:0] = 0 if BRC[10:0] is present, and HPDMA_CxBR1.BNDT[15:0] = 0)

- – after the (conditional) update of the HPDMA link register file from the data structure of the next \( LLI_{n+1} \) in memory

Note: If an LLI is recursive (pointing to itself as a next LLI, either HPDMA_CxLLR.ULL = 1 and HPDMA_CxLLR.LA[15:2] is updated with the same value, or HPDMA_CxLLR.ULL = 0), a channel in link step mode is completed after each repeated single execution of this LLI.

At the regular data transfer completion at a block level, HPDMA_CxBR1.BNDT[15:0] = 0 and HPDMA_CxBR1.BRC[10:0] = 0 (if present). Alternatively, a block transfer can be early completed by a peripheral (such as an I3C in Rx mode), and then BNDT[15:0] is not null (see Section 13.4.14 for more details).

The link step mode can be used to elaborate dynamically LLIs in memory during run-time. The software can be facilitated by using a static data structure for any \( LLI_n \) (all update bits of HPDMA_CxLLR have a static value, \( LLI_n.LLR.LA = LLI_{n-1}.LLR.LA + \text{constant} \) ).

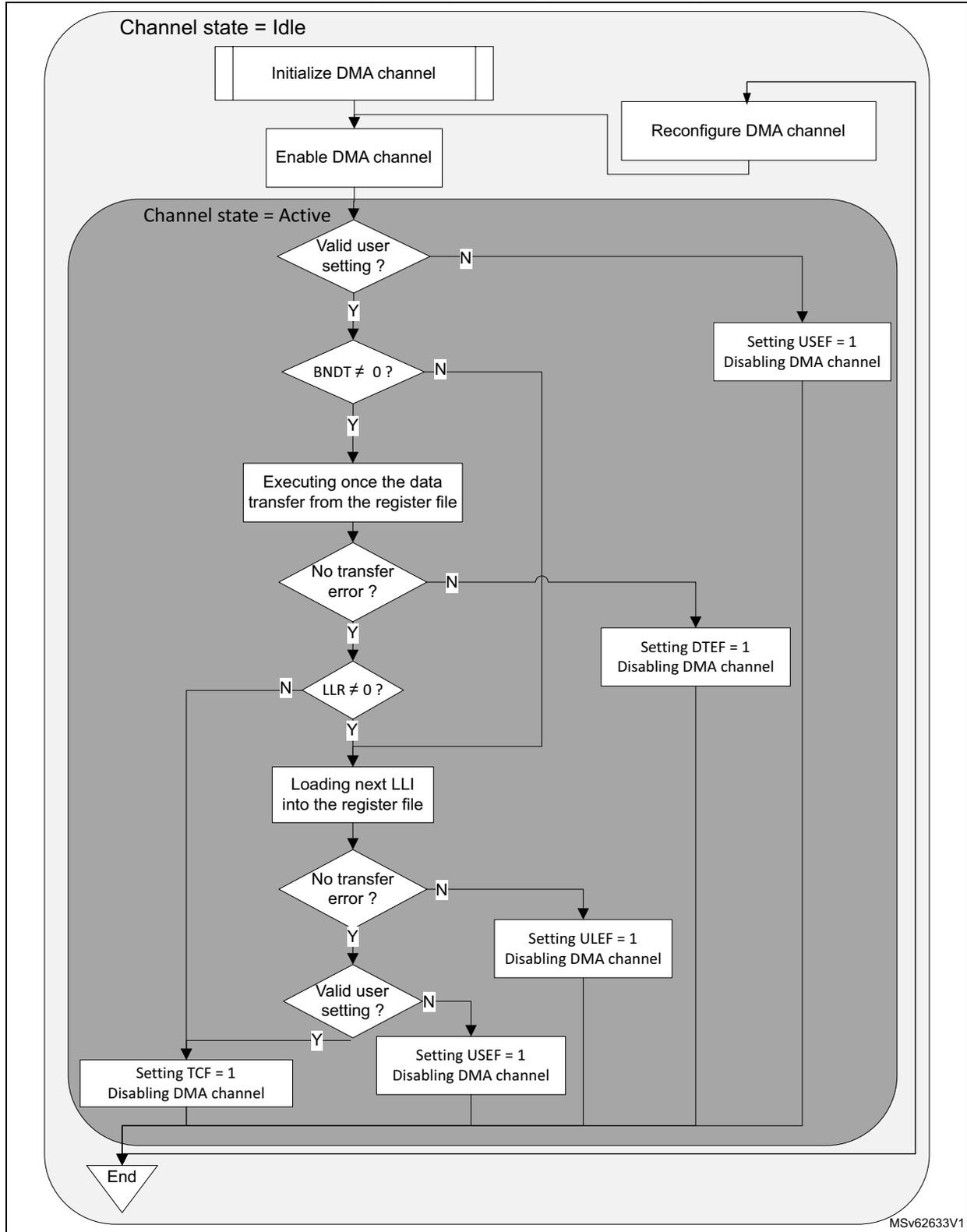

Figure 118 depicts the HPDMA channel execution mode, and its programming in link step mode.

Note: Figure 118 is not intended to illustrate how often a TCEF can be raised, depending on the programmed value of TCEM[1:0] in HPDMA_CxTR2. It can be raised at (each) block completion, at (each) 2D block completion, at (each) LLI completion, or only at the last LLI data transfer completion. In link step mode, the channel is disabled after each single execution of a LLI, and depending on the value of TCEM[1:0] a TCEF is raised or not.

In Figure 118 , BNDT ≠ 0 is the typical condition for starting the first data transfer. This condition becomes BNDT ≠ 0 and PFREQ = 1 if the peripheral requests a data transfer with early termination (see Section 13.3.5 ).

Figure 118. HPDMA channel execution and linked-list programming in link step mode (HPDMA_CxCR.LSM = 1)

graph TD; subgraph Idle [Channel state = Idle]; Init[Initialize DMA channel] --> Enable[Enable DMA channel]; end; Enable --> Active; subgraph Active [Channel state = Active]; Valid1{Valid user setting?}; BNDT{BNDT ≠ 0?}; Exec[Executing once the data transfer from the register file]; NoError1{No transfer error?}; LLR{LLR ≠ 0?}; ExecNext[Loading next LLI into the register file]; NoError2{No transfer error?}; Valid2{Valid user setting?}; USEF1[Setting USEF = 1<br/>Disabling DMA channel]; DTEF[Setting DTEF = 1<br/>Disabling DMA channel]; ULEF[Setting ULEF = 1<br/>Disabling DMA channel]; TCF[Setting TCF = 1<br/>Disabling DMA channel]; USEF2[Setting USEF = 1<br/>Disabling DMA channel]; End[/End/]; Init --> Valid1; Valid1 -- Y --> BNDT; BNDT -- Y --> Exec; BNDT -- N --> USEF1; Exec --> NoError1; NoError1 -- N --> DTEF; NoError1 -- Y --> LLR; LLR -- Y --> ExecNext; LLR -- N --> TCF; ExecNext --> NoError2; NoError2 -- N --> ULEF; NoError2 -- Y --> Valid2; Valid2 -- Y --> TCF; Valid2 -- N --> USEF2; TCF --> End; USEF1 --> End; DTEF --> End; ULEF --> End; USEF2 --> End; End --> Reconfig[Reconfigure DMA channel]; Reconfig --> Init;MSv62633V1

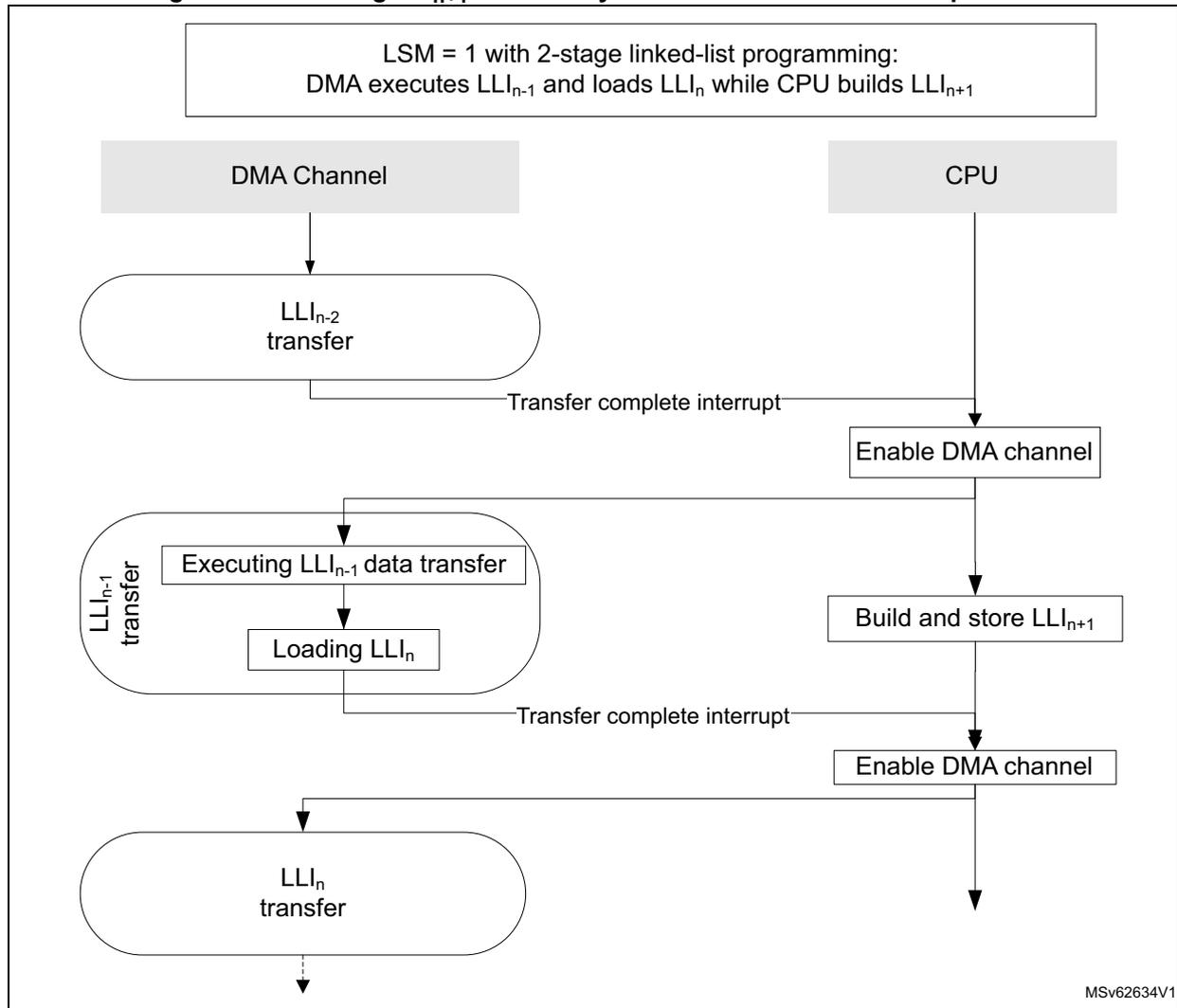

Run-time adding a \( LLI_{n+1} \) in link step mode

During run-time, the software can defer the elaboration of the \( LLI_{n+1} \) (and next LLIs), until/after the HPDMA executed the transfer from the \( LLI_{n-1} \) and loaded the \( LLI_n \) from the memory, as shown in the figure below.

Figure 119. Building \( LLI_{n+1} \) : HPDMA dynamic linked-lists in link step mode

LSM = 1 with 2-stage linked-list programming:

DMA executes

\(

LLI_{n-1}

\)

and loads

\(

LLI_n

\)

while CPU builds

\(

LLI_{n+1}

\)

sequenceDiagram

participant DMA Channel

participant CPU

Note right of DMA Channel: LSM = 1 with 2-stage linked-list programming: DMA executes LLI_{n-1} and loads LLI_n while CPU builds LLI_{n+1}

DMA Channel->>DMA Channel: LLI_{n-2} transfer

DMA Channel->>CPU: Transfer complete interrupt

CPU->>DMA Channel: Enable DMA channel

Note left of DMA Channel: LLI_{n-1} transfer

DMA Channel->>DMA Channel: Executing LLI_{n-1} data transfer

DMA Channel->>DMA Channel: Loading LLI_n

DMA Channel->>CPU: Transfer complete interrupt

CPU->>DMA Channel: Build and store LLI_{n+1}

CPU->>DMA Channel: Enable DMA channel

DMA Channel->>DMA Channel: LLI_n transfer

Note right of DMA Channel: MSv62634V1The diagram illustrates the sequence of events for adding a new \( LLI_{n+1} \) in link step mode. It starts with a box indicating that LSM = 1 with 2-stage linked-list programming, where the DMA executes \( LLI_{n-1} \) and loads \( LLI_n \) while the CPU builds \( LLI_{n+1} \) . The sequence begins with the DMA Channel performing an \( LLI_{n-2} \) transfer. Upon completion, a 'Transfer complete interrupt' is sent to the CPU. The CPU responds with 'Enable DMA channel'. The DMA Channel then performs the \( LLI_{n-1} \) transfer, which includes 'Executing \( LLI_{n-1} \) data transfer' and 'Loading \( LLI_n \) '. Another 'Transfer complete interrupt' is sent to the CPU. The CPU then performs 'Build and store \( LLI_{n+1} \) ' and 'Enable DMA channel'. Finally, the DMA Channel performs the \( LLI_n \) transfer. The diagram is labeled with 'MSv62634V1' in the bottom right corner.

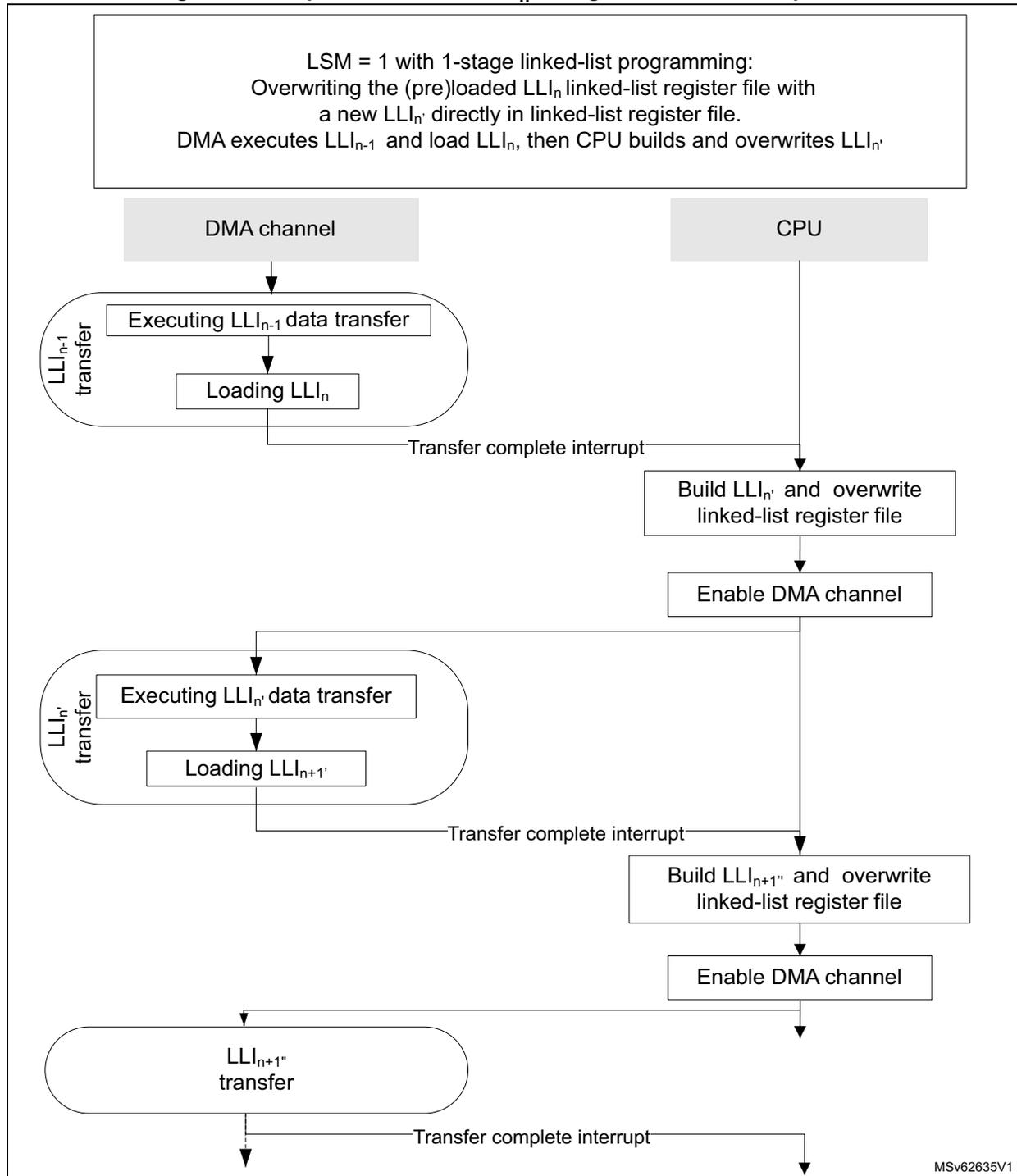

Run-time replacing an \( LLI_n \) with a new \( LLI_{n'} \) in link step mode (in linked-list register file)

In this link step mode, during run-time, the software can build and insert a new \( LLI_{n'} \) , after the HPDMA executed the transfer from the \( LLI_{n-1} \) , and loaded a formerly elaborated \( LLI_n \) from the memory by overwriting directly the linked-list register file with the new \( LLI_{n'} \) , as shown in Figure 120.

Figure 120. Replace with a new \( LLI_n \) , in register file in link step mode

LSM = 1 with 1-stage linked-list programming:

Overwriting the (pre)loaded

\(

LLI_n

\)

linked-list register file with

a new

\(

LLI_n

\)

' directly in linked-list register file.

DMA executes

\(

LLI_{n-1}

\)

and load

\(

LLI_n

\)

, then CPU builds and overwrites

\(

LLI_n

\)

'

sequenceDiagram

participant DMA as DMA channel

participant CPU as CPU

Note over DMA: LLI_{n-1} transfer

DMA->>DMA: Executing LLI_{n-1} data transfer

DMA->>DMA: Loading LLI_n

DMA->>CPU: Transfer complete interrupt

Note over CPU: Build LLI_n' and overwrite linked-list register file

Note over CPU: Enable DMA channel

Note over DMA: LLI_n' transfer

DMA->>DMA: Executing LLI_n' data transfer

DMA->>DMA: Loading LLI_{n+1}'

DMA->>CPU: Transfer complete interrupt

Note over CPU: Build LLI_{n+1}'' and overwrite linked-list register file

Note over CPU: Enable DMA channel

Note over DMA: LLI_{n+1}'' transfer

DMA->>CPU: Transfer complete interruptMSV62635V1

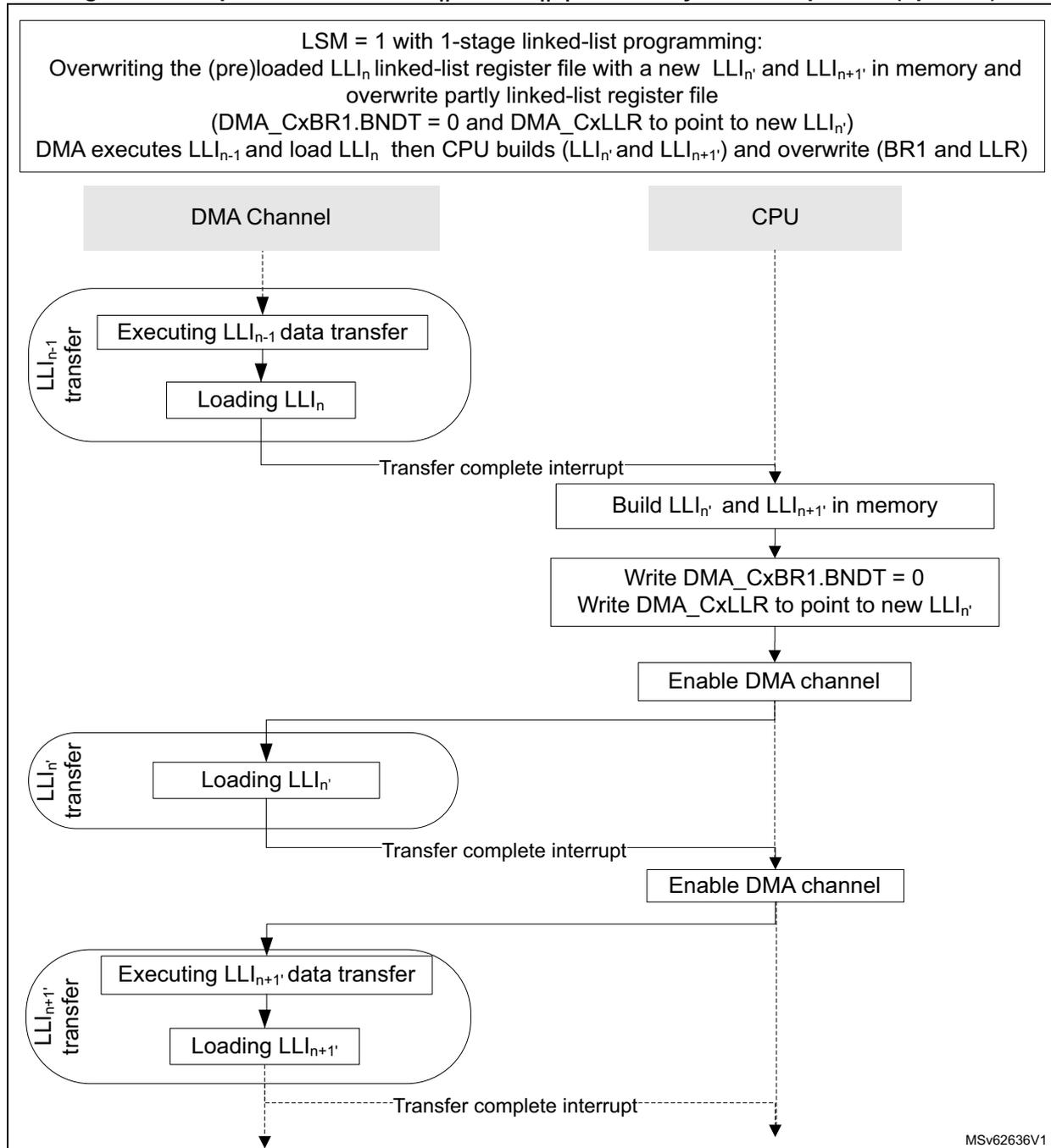

Run-time replacing an \( LLI_n \) with a new \( LLI_{n'} \) in link step mode (in the memory)The software can build and insert a new \( LLI_{n'} \) and \( LLI_{n+1'} \) in the memory, after HPDMA executed the transfer from the \( LLI_{n-1} \) , and loaded a formerly elaborated \( LLI_n \) from the memory, by overwriting partly the linked-list register file (HPDMA_CxBR1.BNDT[15:0] to be null, and HPDMA_CxLLR to point to new \( LLI_{n'} \) ) as shown in Figure 121.

Figure 121. Replace with a new \( LLI_{n'} \) and \( LLI_{n+1'} \) in memory in link step mode (option 1)

LSM = 1 with 1-stage linked-list programming:

Overwriting the (pre)loaded

\(

LLI_n

\)

linked-list register file with a new

\(

LLI_{n'}

\)

and

\(

LLI_{n+1'}

\)

in memory and overwrite partly linked-list register file

(DMA_CxBR1.BNDT = 0 and DMA_CxLLR to point to new

\(

LLI_{n'}

\)

)

DMA executes

\(

LLI_{n-1}

\)

and load

\(

LLI_n

\)

then CPU builds (

\(

LLI_{n'}

\)

and

\(

LLI_{n+1'}

\)

) and overwrite (BR1 and LLR)

sequenceDiagram

participant DMA Channel

participant CPU

Note left of DMA Channel: LLI_{n-1} transfer

rect rgb(255, 255, 255)

DMA Channel->>DMA Channel: Executing LLI_{n-1} data transfer

DMA Channel->>DMA Channel: Loading LLI_n

end

DMA Channel-->>CPU: Transfer complete interrupt

Note right of CPU: Build LLI_{n'} and LLI_{n+1'} in memory

Note right of CPU: Write DMA_CxBR1.BNDT = 0

Write DMA_CxLLR to point to new LLI_{n'}

Note right of CPU: Enable DMA channel

Note left of DMA Channel: LLI_{n'} transfer

rect rgb(255, 255, 255)

DMA Channel->>DMA Channel: Loading LLI_{n'}

end

DMA Channel-->>CPU: Transfer complete interrupt

Note right of CPU: Enable DMA channel

Note left of DMA Channel: LLI_{n+1'} transfer

rect rgb(255, 255, 255)

DMA Channel->>DMA Channel: Executing LLI_{n+1'} data transfer

DMA Channel->>DMA Channel: Loading LLI_{n+1'}

end

DMA Channel-->>CPU: Transfer complete interrupt

MSV62636V1

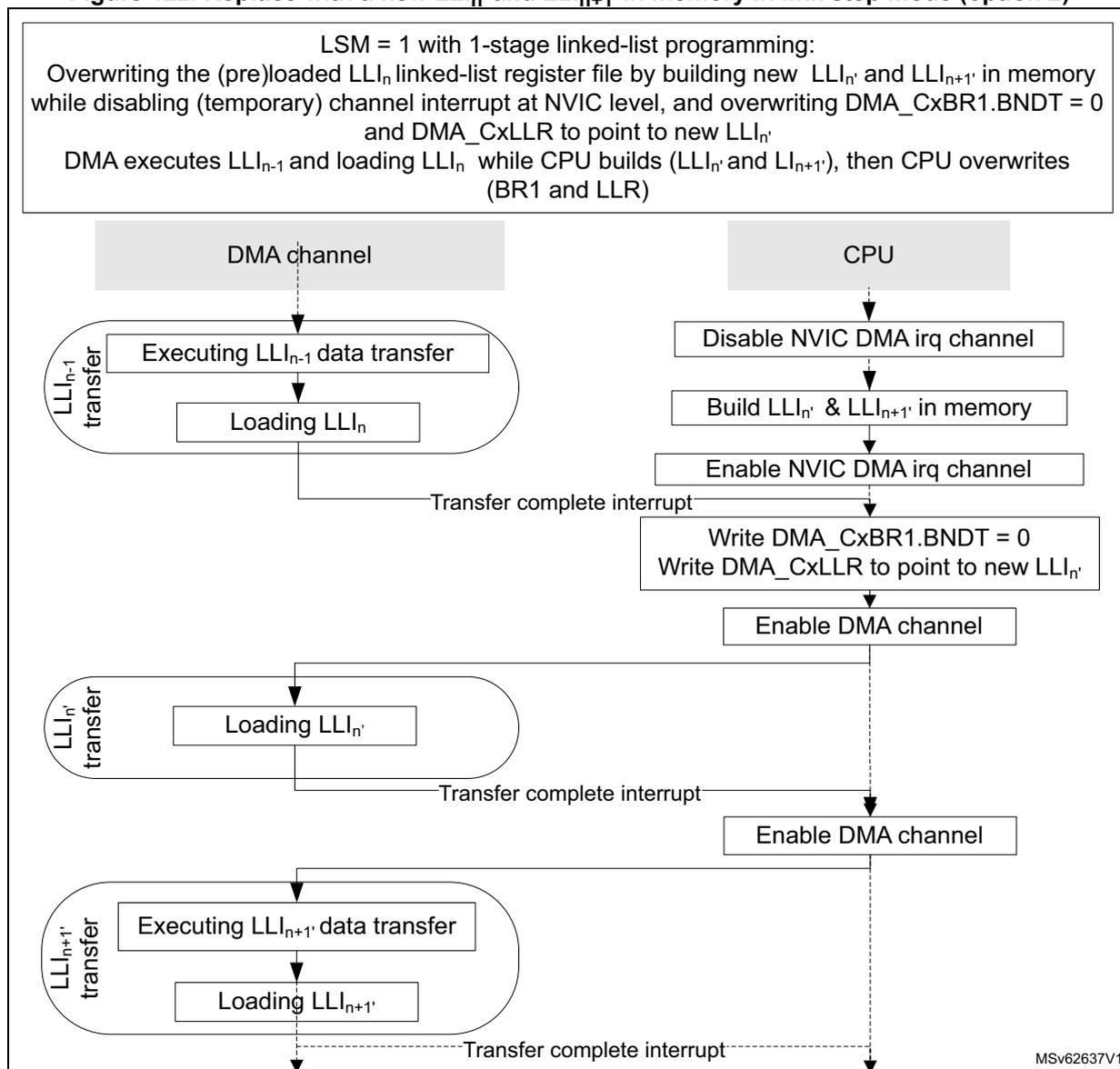

Run-time replacing a \( LLI_n \) with a new \( LLI_{n'} \) in link step mode

Other software implementations exist. Meanwhile the HPDMA executes the transfer from the \( LLI_{n-1} \) and loads a formerly elaborated \( LLI_n \) from the memory (or even earlier), the software can do the following:

- 1. Disable the NVIC for not being interrupted by the interrupt handling.

- 2. Build a new \( LLI_{n'} \) and a new \( LLI_{n+1'} \) .

- 3. Enable again the NVIC for the channel interrupt (transfer complete) notification.

The software in the interrupt handler for \( LLI_{n-1} \) is then restricted to overwrite HPDMA_CxBR1.BNDT[15:0] to be null and HPDMA_CxLLR to point to new \( LLI_{n'} \) , as shown in the figure below.

Figure 122. Replace with a new \( LLI_{n'} \) and \( LLI_{n+1'} \) in memory in link step mode (option 2)

LSM = 1 with 1-stage linked-list programming:

Overwriting the (pre)loaded

\(

LLI_n

\)

linked-list register file by building new

\(

LLI_{n'}

\)

and

\(

LLI_{n+1'}

\)

in memory while disabling (temporary) channel interrupt at NVIC level, and overwriting DMA_CxBR1.BNDT = 0 and DMA_CxLLR to point to new

\(

LLI_{n'}

\)

DMA executes

\(

LLI_{n-1}

\)

and loading

\(

LLI_n

\)

while CPU builds (

\(

LLI_{n'}

\)

and

\(

LLI_{n+1'}

\)

), then CPU overwrites (BR1 and LLR)

sequenceDiagram

participant DMA as DMA channel

participant CPU as CPU

Note left of DMA: LLI_{n-1} transfer

rect rgb(255, 255, 255)

DMA->>DMA: Executing LLI_{n-1} data transfer

DMA->>DMA: Loading LLI_n

end

DMA-->>CPU: Transfer complete interrupt

rect rgb(255, 255, 255)

CPU->>CPU: Disable NVIC DMA irq channel

CPU->>CPU: Build LLI_{n'} & LLI_{n+1'} in memory

CPU->>CPU: Enable NVIC DMA irq channel

CPU->>CPU: Write DMA_CxBR1.BNDT = 0

Write DMA_CxLLR to point to new LLI_{n'}

CPU->>CPU: Enable DMA channel

end

Note left of DMA: LLI_{n'} transfer

rect rgb(255, 255, 255)

DMA->>DMA: Loading LLI_{n'}

end

DMA-->>CPU: Transfer complete interrupt

rect rgb(255, 255, 255)

CPU->>CPU: Enable DMA channel

end

Note left of DMA: LLI_{n+1'} transfer

rect rgb(255, 255, 255)

DMA->>DMA: Executing LLI_{n+1'} data transfer

DMA->>DMA: Loading LLI_{n+1'}

end

DMA-->>CPU: Transfer complete interrupt

MSv62637V1

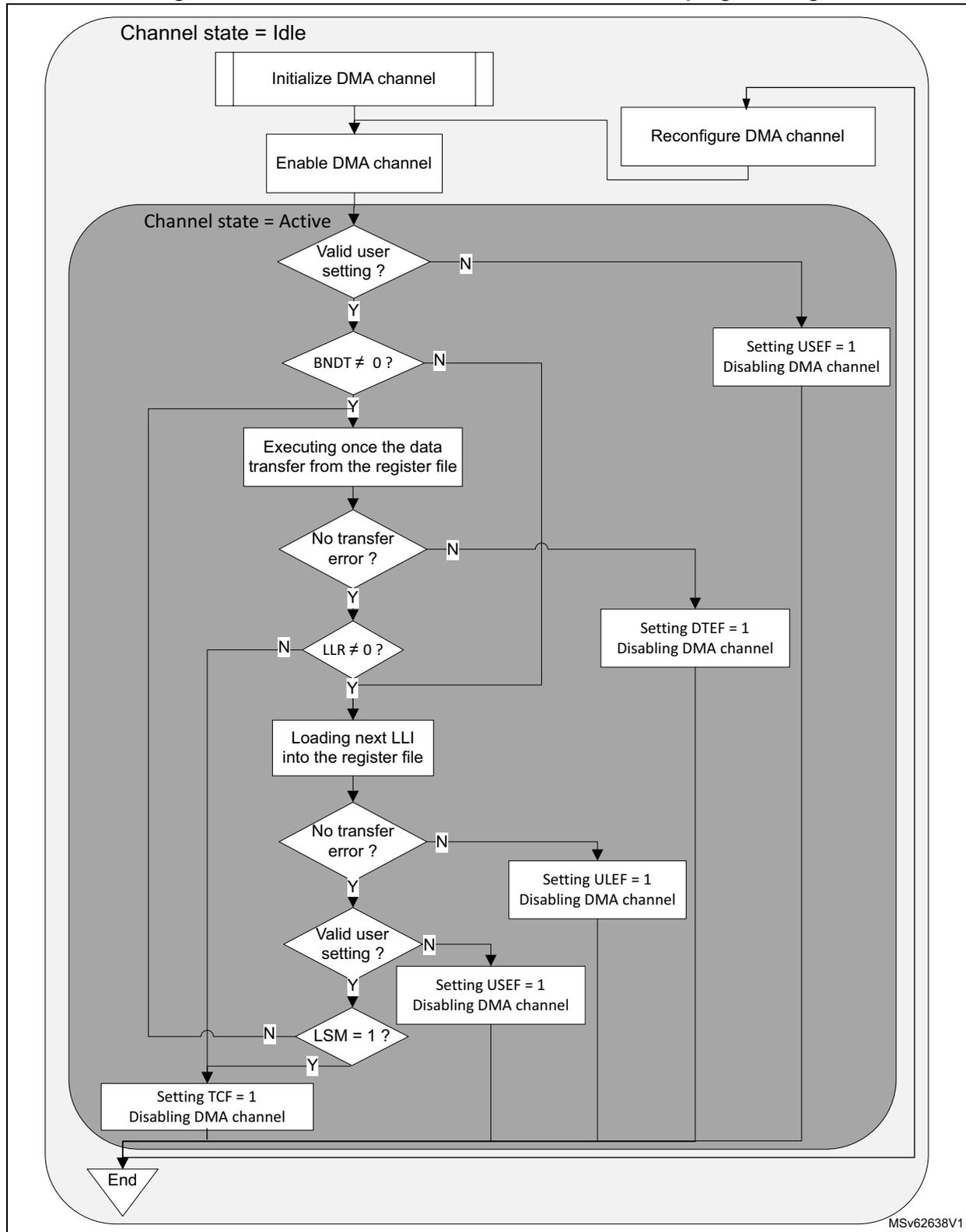

13.4.9 HPDMA channel state and linked-list programming

The software can reconfigure a channel when the channel is disabled (HPDMA_CxCR.EN = 0), and update the execution mode (HPDMA_CxCR.LSM) to change from/to run-to-completion mode to/from link step mode.

In any execution mode, the software can:

- • reprogram \( LLI_{n+1} \) in the memory to finally complete the channel by this \( LLI_{n+1} \) (clear the HPDMA_CxLLR of this \( LLI_{n+1} \) ), before this \( LLI_{n+1} \) is loaded/used by the HPDMA channel

- • abort and reconfigure the channel with an LSM update (see Section 13.4.4. )

In link step mode, the software can clear LSM after each a single execution of any LLI, during \( LLI_{n-1} \) .

Figure 123 shows the overall and unified HPDMA linked-list programming, whatever is the execution mode.

Note: Figure 123 is not intended to illustrate how often a TCEF can be raised, depending on the programmed value of TCEM[1:0] in HPDMA_CxTR2. It can be raised at (each) block completion, at (each) 2D block completion, at (each) LLI completion, or only at the last LLI data transfer completion. In run-to-completion mode, whatever is the value of TCEM[1:0], at the channel completion the hardware always set TCEF = 1 and disables the channel. In link step mode, the channel is disabled after each single execution of a LLI, and depending on the value of TCEM[1:0] a TCEF is raised or not.

In Figure 123 , BNDT ≠ 0 is the typical condition for starting the first data transfer. This condition becomes BNDT ≠ 0 and PFREQ = 1 if the peripheral requests a data transfer with early termination (see Section 13.3.5 ).

Figure 123. HPDMA channel execution and linked-list programming

graph TD; subgraph Idle [Channel state = Idle]; Init[Initialize DMA channel] --> Enable[Enable DMA channel]; Enable --> Active; end; subgraph Active [Channel state = Active]; Valid1{Valid user setting?}; BNDT{BNDT ≠ 0?}; Exec[Executing once the data transfer from the register file]; NoError1{No transfer error?}; LLR{LLR ≠ 0?}; Load[Loading next LLI into the register file]; NoError2{No transfer error?}; Valid2{Valid user setting?}; LSM{LSM = 1?}; End[/End/]; Usef1[Setting USEF = 1 Disabling DMA channel]; Dtef[Setting DTEF = 1 Disabling DMA channel]; Ulef[Setting ULEF = 1 Disabling DMA channel]; Tcf[Setting TCF = 1 Disabling DMA channel]; Reconfig[Reconfigure DMA channel]; Init --> Valid1; Valid1 -- Y --> BNDT; Valid1 -- N --> Usef1; BNDT -- Y --> Exec; BNDT -- N --> NoError1; Exec --> NoError1; NoError1 -- Y --> LLR; NoError1 -- N --> Dtef; LLR -- Y --> Load; LLR -- N --> Valid2; Load --> NoError2; NoError2 -- Y --> Valid2; NoError2 -- N --> Ulef; Valid2 -- Y --> LSM; Valid2 -- N --> Usef1; LSM -- Y --> Tcf; LSM -- N --> End; Tcf --> End; Usef1 --> Reconfig; Dtef --> Reconfig; Ulef --> Reconfig; Reconfig --> Init;MSv62638V1

13.4.10 HPDMA FIFO-based transfers

There is a single transfer operation mode: the FIFO mode. There are FIFO-based transfers. Any channel x is implemented with a dedicated FIFO whose size is defined by dma_fifo_size[x] (see Section 13.3.1 for more details).

HPDMA burst

A programmed transfer at the lowest level is an HPDMA burst.

An HPDMA burst is a burst of data received from the source, or a burst of data sent to the destination. A source (and destination) burst is programmed with a burst length by SBL_1[5:0] (respectively DBL_1[5:0]), and with a data width defined by SDW_LOG2[1:0] (respectively DDW_LOG2[1:0]) in HPDMA_CxTR1.

The addressing mode after each data (named beat) of an HPDMA burst is defined by SINC and DINC in HPDMA_CxTR1, for source and destination respectively: either a fixed addressing or an incremented addressing with contiguous data.

The start and next addresses of an HPDMA source/destination burst (defined by HPDMA_CxSAR and HPDMA_CxDAR) must be aligned with the respective data width.

The table below lists the main characteristics of an HPDMA burst.

Table 107. Programmed HPDMA source/destination burst

| SAP/DAP (allocated port) | SDW_LOG2[1:0] DDW_LOG2[1:0] | Data width (bytes) | SINC/DINC | SBL_1[5:0] DBL_1[5:0] | Burst length (data/ beats) | Next data/ beat address | Next burst addresses | Burst address alignment |

|---|---|---|---|---|---|---|---|---|

| 0: AXI 1: AHB | 00 | 1 | 0 (fixed) | n = 0 to 63 (1) | n+1 | + 0 | + 0 | 1 |

| 01 | 2 | 2 | ||||||

| 10 | 4 | 4 | ||||||

| 11 | 8 | 8 | ||||||

| 0: AXI 1: AHB | 00 | 1 | 1 (contiguously incremented) | + 1 | + (n + 1) | 1 | ||

| 01 | 2 | + 2 | + 2 * (n + 1) | 2 | ||||

| 10 | 4 | + 4 | + 4 * (n + 1) | 4 | ||||

| 0: AXI | 11 | 8 | + 8 | + 8 * (n + 1) | 8 | |||

| 0: AHB | 11 | forbidden user setting, causing USEF generation and none burst to be issued. | ||||||

1. When S/DBL_1[5:0] = 0, burst is of length 1. Then burst can be also named as single.

The next burst address in the above table is the next source/destination default address pointed by HPDMA_CxSAR or HPDMA_CxDAR, once the programmed source/destination burst is completed. This default value refers to the fixed/contiguously incremented address.

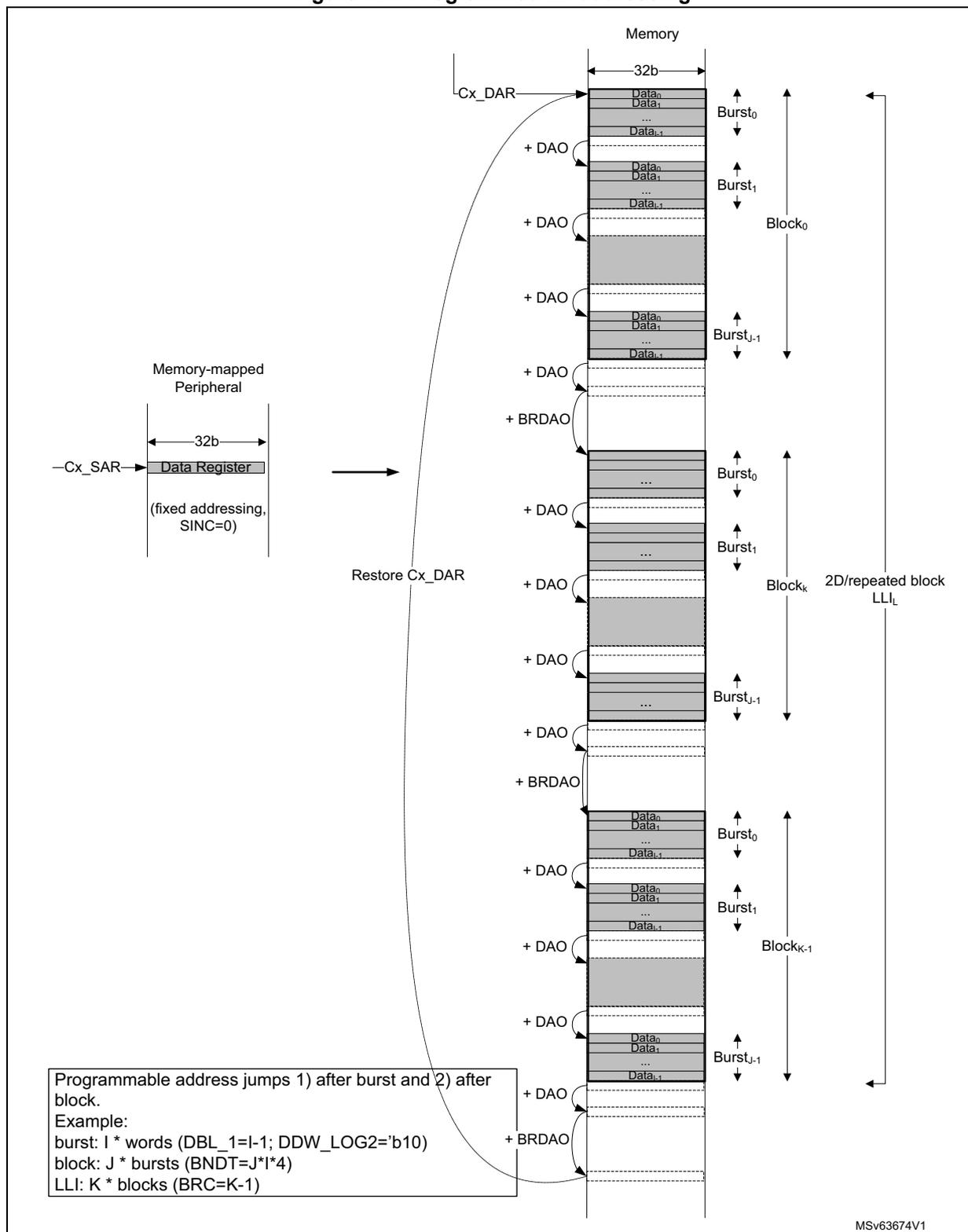

HPDMA burst with 2D addressing

When the channel has additional 2D addressing feature, this default value refers to the value without taking into account the two programmed incremented or decremented offsets. These two additional offsets (with a null default value) are applied:

- • after each completed source/destination burst, as defined respectively by HPDMA_CxTR2.SAO[12:0]/DAO[12:0] and HPDMA_CxBR1.SDEC/DDEC

- • after each completed block, as defined respectively by HPDMA_CxBR2.BRSAO[15:0]/BRDAO[15:0] and HPDMA_CxBR1.BRSDEC/BRDDEC)

Then, a 2D/repeated block can be addressed with a first programmed address jump after each completed burst, and with a second programmed address jump after each block, as depicted by Figure 124 with a 2D destination buffer.

Figure 124. Programmed 2D addressing

The diagram illustrates the memory addressing scheme for HPDMA. On the left, a 'Memory-mapped Peripheral' contains a 'Data Register' (32b wide) with fixed addressing (SINC=0). The 'Cx_SAR' register points to this register. An arrow indicates data transfer from the register to 'Memory'. In memory, the 'Cx_DAR' register is used to address data. The memory is organized into 'Bursts' (each containing 'Data n ' and 'Data n-1 ' - 32b wide) and 'Blocks'. Address jumps are indicated by '+ DAO' (after each burst) and '+ BRDAO' (after each block). A 'Restore Cx_DAR' arrow points from the bottom of the memory back to the 'Cx_DAR' register. The diagram shows 'Block 0 ', 'Block k ' (labeled as '2D/repeated block LLI L '), and 'Block K-1 '. Each block contains multiple bursts, with the last burst in a block being 'Burst J-1 '.

Programmable address jumps 1) after burst and 2) after block.

Example:

burst: I * words (DBL_1=I-1; DDW_LOG2='b10)

block: J * bursts (BNDT=J*I*4)

LLI: K * blocks (BRC=K-1)

MSv63674V1

HPDMA FIFO-based burst

In FIFO-mode, a transfer generally consists of two pipelined and separated burst transfers:

- • one burst from the source to the FIFO over the allocated source master port, as defined by HPDMA_CxTR1.SAP

- • one burst from the FIFO to the destination over the allocated destination master port, as defined by HPDMA_CxTR1.DAP

HPDMA source burst

The requested source burst transfer to the FIFO can be scheduled as early as possible over the allocated port, depending on the current FIFO level versus the programmed burst size (when the FIFO is ready to get one new burst from the source):

where:

- • FIFO level is the current filling level of the FIFO, in bytes.

- •

\(

2^{\text{dma\_fifo\_size}[x]}

\)

is half the FIFO size of channel x, in bytes (see

Section 13.3.1

for the implementation details and

dma_fifo_size[x]value). - • \( (\text{SBL\_1}[5:0]+1) * 2^{\text{SDW\_LOG2}[1:0]} \) is the size of the programmed source burst transfer, in bytes.

Based on the channel priority (HPDMA_CxCR.PRIO[1:0]), this ready FIFO-based source transfer is internally arbitrated versus the other requested and active channels.

HPDMA destination burst

The requested destination burst transfer from the FIFO can be scheduled as early as possible over the allocated port, depending on the current FIFO level versus the programmed burst size (when the FIFO is ready to push one new burst to the destination):

where:

- • FIFO level is the current filling level of the FIFO, in bytes.

- • \( (\text{DBL\_1}[5:0]+1) * 2^{\text{DDW\_LOG2}[1:0]} \) is the size of the programmed destination burst transfer, in bytes.

Based on the channel priority, this ready FIFO-based destination transfer is internally arbitrated versus the other requested and active channels.

HPDMA burst versus source block size, 1- or 4-Kbyte address boundary and FIFO size

The programmed source/destination HPDMA burst is implemented with an AHB/AXI burst as is, unless one of the following conditions is met:

- • When half of the FIFO size of the channel x is lower than the programmed source/destination burst size, the programmed source/destination HPDMA burst is implemented with a series of singles or bursts of a lower size. Each transfer is of a size that is lower than or equal than half of the FIFO size, without any user constraint.

- • If the source block size (HPDMA_CxBR1.BNDT[15:0]) is not a multiple of the source burst size but is a multiple of the data width of the source burst (HPDMA_CxTR1.SDW_LOG2[1:0]), the HPDMA modifies and shortens bursts into

singles or bursts of lower length, in order to transfer exactly the source block size, without any user constraint.

- • if the source/destination burst transfer have crossed the 1- or 4-Kbyte address boundary on, respectively, an AHB or AXI transfer, the HPDMA modifies and shortens the programmed burst into singles or bursts of lower length, to be compliant with the AHB/AXI protocol, without any user constraint.

- • If the source/destination burst length exceeds 16 on a AHB transfer, or if the source/destination burst on an AXI transfer is both with fixed addressing and with a burst length which exceeds 16, the HPDMA modifies and shortens the programmed burst into singles or bursts of lower length, to be compliant with the AHB/AXI protocol, without any user constraint.

In any case, the HPDMA keeps ensuring source/destination data (and address) integrity without any user constraint. The current FIFO level (software readable in HPDMA_CxSR) is compared to and updated with the effective transfer size, and the HPDMA re-arbitrates between each AHB/AXI single or burst transfer, possibly modified.

Based on the channel priority, each single or burst of a lower burst size versus the programmed burst, is internally arbitrated versus the other requested and active channels.

Note: In linked-list mode, the HPDMA read transfers related to the update of the linked-list parameters from the memory to the internal HPDMA registers, are scheduled over the link allocated port, as programmed by HPDMA_CxCR.LAP.

HPDMA data handling: byte-based reordering, packing/unpacking, padding/truncation, sign extension, and left/right alignment

The data handling is controlled by HPDMA_CxTR1. The source/destination data width of the programmed burst is byte, half-word, word, or double-word, as per SDW_LOG2[1:0] and DDW_LOG2[1:0] (see Table 108 ).

The user can configure the data handling between transferred data from the source and transfer to the destination. More specifically, programmed data handling is orderly performed with:

- 1. Byte-based source reordering

- – If SBX = 1 and if the source data width is a word or a double-word (for AXI source bus, SAP = 0), the two bytes of the unaligned half-word at the middle of each source data word are exchanged.

- 2. Data-width conversion by packing, unpacking, padding, or truncation, if destination data width is different than the source data width, depending on PAM[1:0]:

- – If destination data width > source data width, the post SBX source data is either right-aligned and padded with 0s, or sign extended up to the destination data width, or is FIFO queued and packed up to the destination data width.

- – If destination data width < source data width, the post SBX data is either right-aligned and left-truncated down to the destination data width, or is FIFO queued and unpacked and streamed down to the destination data width.

- 3. Byte-based destination re-ordering:

- – If DBX = 1 and if the destination data width is not a byte, the two bytes are exchanged within the aligned post PAM[1:0] half-words.

- – If DHX = 1 and if the destination data width is neither a byte nor a half-word, the two aligned half-words are exchanged within the aligned post PAM[1:0] words.

- – If DWX = 1 and if the destination data width is a double-word and if the selected destination port (via DAP) is 64-bit capable, the two aligned words are exchanged within aligned (post PAM[1:0]) double-words.

Note: Left-alignment with 0s-padding can be achieved by programming both a right-alignment with a 0s-padding, and a destination byte-based re-ordering.

The table below lists the possible data handling from the source to the destination.

Table 108. Programmed data handling

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 00 | Byte | B 7 ,B 6 ,B 5 ,B 4 ,B 3 ,B 2 ,B 1 ,B 0 | x | 00 | Byte | xx | x | B 7 ,B 6 ,B 5 ,B 4 ,B 3 ,B 2 ,B 1 ,B 0 | ||

| 01 | Half-word | 00 (RA, 0P) (3)(4) | 0 | x | 0B 3 ,0B 2 ,0B 1 ,0B 0 | |||||

| 1 | B 3 0,B 2 0,B 1 0,B 0 0 | |||||||||

| 01 (RA, SE) (3)(4) | 0 | SB 3 ,SB 2 ,SB 1 ,SB 0 | ||||||||

| 1 | B 3 S,B 2 S,B 1 S,B 0 S | |||||||||

| 1x (PACK) | 0 | B 7 B 6 ,B 5 B 4 ,B 3 B 2 ,B 1 B 0 | ||||||||

| 1 | B 6 B 7 ,B 4 B 5 ,B 2 B 3 ,B 0 B 1 | |||||||||

| 10 | Word | 00 (RA, 0P) (3)(4) | 0 | 0 | x | 000B 1 ,000B 0 | ||||

| 1 | 00B 1 0,00B 0 0 | |||||||||

| 0 | 1 | 0B 1 00,0B 0 00 | ||||||||

| 1 | B 1 000,B 0 000 | |||||||||

| 01 (RA, SE) (3)(4) | 0 | 0 | SSSB 1 ,SSSB 0 | |||||||

| 1 | SSB 1 S,SSB 0 S | |||||||||

| 1x (PACK) | 0 | 0 | SB 1 SS,SB 0 SS | |||||||

| 1 | B 1 SSS,B 0 SSS | |||||||||

| 1x (PACK) | 0 | 0 | B 7 B 6 B 5 B 4 ,B 3 B 2 B 1 B 0 | |||||||

| 1 | B 6 B 7 B 4 B 5 ,B 2 B 3 B 0 B 1 | |||||||||

| 1x (PACK) | 0 | 1 | B 5 B 4 B 7 B 6 ,B 1 B 0 B 3 B 2 | |||||||

| 1 | B 4 B 5 B 6 B 7 ,B 0 B 1 B 2 B 3 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 00 | Byte | B 7 ,B 6 ,B 5 ,B 4 ,B 3 ,B 2 ,B 1 ,B 0 | x | 11 (5) | Double-word | 00 (RA, 0P) (3)(4) | 0 | 0 | 0 | 0000000B 0 |

| 1 | 000000B 0 0 | |||||||||

| 0 | 1 | 00000B 0 00 | ||||||||

| 1 | 0000B 0 000 | |||||||||

| 0 | 0 | 1 | 000B 0 0000 | |||||||

| 1 | 00B 0 00000 | |||||||||

| 0 | 1 | 0B 0 000000 | ||||||||

| 1 | B 0 0000000 | |||||||||

| 01 (RA, SE) (3)(4) | 0 | 0 | 0 | SSSSSSSB 0 | ||||||

| 1 | SSSSSSSB 0 S | |||||||||

| 0 | 1 | SSSSSB 0 SS | ||||||||

| 1 | SSSSB 0 SSS | |||||||||

| 0 | 0 | 1 | SSSB 0 SSSS | |||||||

| 1 | SSB 0 SSSSS | |||||||||

| 0 | 1 | SB 0 SSSSS | ||||||||

| 1 | B 0 SSSSSS | |||||||||

| 1x (PACK) | 0 | 0 | 0 | B 7 B 6 B 5 B 4 B 3 B 2 B 1 B 0 | ||||||

| 1 | B 6 B 7 B 4 B 5 B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 B 0 B 1 B 2 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 2 B 1 B 0 B 7 B 6 B 5 B 4 | |||||||

| 1 | B 2 B 3 B 0 B 1 B 6 B 7 B 4 B 5 | |||||||||

| 0 | 1 | B 1 B 0 B 3 B 2 B 5 B 4 B 7 B 6 | ||||||||

| 1 | B 0 B 1 B 2 B 3 B 4 B 5 B 6 B 7 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 01 | Half-word | B 7 B 6 B 5 B 4 , B 3 B 2 B 1 B 0 | x | 00 | Byte | 00 (RA, LT) (3) | x | x | B 6 ,B 4 ,B 2 ,B 0 | |

| 01 (LA, RT) (3) | B 7 ,B 5 ,B 3 ,B 1 | |||||||||

| 1x (UNPACK) | B 7 ,B 6 ,B 5 ,B 4 ,B 3 ,B 2 ,B 1 ,B 0 | |||||||||

| 01 | Half-word | xx | 0 | B 7 B 6 ,B 5 B 4 ,B 3 B 2 ,B 1 B 0 | ||||||

| 1 | B 6 B 7 ,B 4 B 5 ,B 2 B 3 ,B 0 B 1 | |||||||||

| 10 | Word | 00 (RA, 0P) (3)(4) | 0 | 0 | x | 00B 3 B 2 ,00B 1 B 0 | ||||

| 1 | B 3 B 2 00,B 1 B 0 00 | |||||||||

| 0 | 1 | B 2 B 3 00,B 0 B 1 00 | ||||||||

| 1 | 00B 2 B 3 ,00B 0 B 1 | |||||||||

| 01 (RA, SE) (3)(4) | 0 | 0 | SSB 3 B 2 ,SSB 1 B 0 | |||||||

| 1 | B 3 B 2 SS,B 1 B 0 SS | |||||||||

| 0 | 1 | B 2 B 3 SS,B 0 B 1 SS | ||||||||

| 1 | SSB 2 B 3 ,SSB 0 B 1 | |||||||||

| 1x (PACK) | 0 | 0 | B 7 B 6 B 5 B 4 ,B 3 B 2 B 1 B 0 | |||||||

| 1 | B 6 B 7 B 4 B 5 ,B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 ,B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 ,B 0 B 1 B 2 B 3 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 01 | Half-word | B 7 B 6 B 5 B 4 , B 3 B 2 B 1 B 0 | x | 11 (5) | Double-word | 00 (RA, 0P) (3)(4) | 0 | 0 | 0 | 000000B 1 B 0 |

| 1 | 000000B 0 B 1 | |||||||||

| 0 | 1 | 0000B 1 B 0 00 | ||||||||

| 1 | 0000B 1 B 0 00 | |||||||||

| 0 | 0 | 1 | 00B 1 B 0 0000 | |||||||

| 1 | 00B 0 B 1 0000 | |||||||||

| 0 | 1 | B 1 B 0 000000 | ||||||||

| 1 | B 0 B 1 000000 | |||||||||

| 01 (RA, SE) (3)(4) | - | 0 | 0 | SSSSSSB 1 B 0 | ||||||

| 1 | SSSSSSB 0 B 1 | |||||||||

| 0 | 1 | SSSSB 1 B 0 SS | ||||||||

| 1 | SSSSB 1 B 0 SS | |||||||||

| 0 | 0 | 1 | SSB 1 B 0 SSSS | |||||||

| 1 | SSB 0 B 1 SSSS | |||||||||

| 0 | 1 | B 1 B 0 SSSSSS | ||||||||

| 1 | B 0 B 1 SSSSSS | |||||||||

| 1x (PACK) | 0 | 0 | 0 | B 7 B 6 B 5 B 4 B 3 B 2 B 1 B 0 | ||||||

| 1 | B 6 B 7 B 4 B 5 B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 B 0 B 1 B 2 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 2 B 1 B 0 B 7 B 6 B 5 B 4 | |||||||

| 1 | B 2 B 3 B 0 B 1 B 6 B 7 B 4 B 5 | |||||||||

| 0 | 1 | B 1 B 0 B 3 B 2 B 5 B 4 B 7 B 6 | ||||||||

| 1 | B 0 B 1 B 2 B 3 B 4 B 5 B 6 B 7 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 10 | Word | B

7

B

6

B

5

B

4

, B 3 B 2 B 1 B 0 | 0 | 00 | Byte | 00 (RA, LT) (3) | - | B 12 ,B 8 ,B 4 ,B 0 | ||

| 01 (LA, RT) (3) | - | B 15 ,B 11 ,B 7 ,B 3 | ||||||||

| 1x (UNPACK) | x | B 7 ,B 6 ,B 5 ,B 4 ,B 3 ,B 2 ,B 1 ,B 0 | ||||||||

| 01 | Half-word | 00 (RA, LT) (3) | 0 | x | x | B 5 B 4 ,B 1 B 0 | ||||

| 1 | B 4 B 5 ,B 0 B 1 | |||||||||

| 01 (LA, RT) (3) | 0 | B 7 B 6 ,B 3 B 2 | ||||||||

| 1 | B 6 B 7 ,B 2 B 3 | |||||||||

| 1x (UNPACK) | 0 | B 7 B 6 ,B 5 B 4 ,B 3 B 2 ,B 1 B 0 | ||||||||

| 1 | B 6 B 7 ,B 4 B 5 ,B 2 B 3 ,B 0 B 1 | |||||||||

| 10 | Word | xx | 0 | 0 | B 7 B 6 B 5 B 4 ,B 3 B 2 B 1 B 0 | |||||

| 1 | B 6 B 7 B 4 B 5 ,B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 ,B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 ,B 0 B 1 B 2 B 3 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 10 | Word | B 7 B 6 B 5 B 4 , B 3 B 2 B 1 B 0 | 0 | 11 (5) | Double-word | 1x (PACK) | 0 | 0 | 0 | B 7 B 6 B 5 B 4 B 3 B 2 B 1 B 0 |

| 1 | B 6 B 7 B 4 B 5 B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 B 0 B 1 B 2 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 2 B 1 B 0 B 7 B 6 B 5 B 4 | |||||||

| 1 | B 2 B 3 B 0 B 1 B 6 B 7 B 4 B 5 | |||||||||

| 0 | 1 | B 1 B 0 B 3 B 2 B 5 B 4 B 7 B 6 | ||||||||

| 1 | B 0 B 1 B 2 B 3 B 4 B 5 B 6 B 7 | |||||||||

| 00 (RA, 0P) (3)(4) | 0 | 0 | 0 | 0000B 3 B 2 B 1 B 0 | ||||||

| 1 | 0000B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | 0000B 1 B 0 B 3 B 2 | ||||||||

| 1 | 0000B 0 B 1 B 2 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 2 B 1 B 0 0000 | |||||||

| 1 | B 1 B 0 B 3 B 2 0000 | |||||||||

| 0 | 1 | B 3 B 2 B 1 B 0 0000 | ||||||||

| 1 | B 0 B 1 B 2 B 3 0000 | |||||||||

| 01 (RA, SE) (3)(4) | 0 | 0 | 0 | SSSSB 3 B 2 B 1 B 0 | ||||||

| 1 | SSSSB 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | SSSSB 1 B 0 B 3 B 2 | ||||||||

| 1 | SSSSB 0 B 1 B 2 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 2 B 1 B 0 SSSS | |||||||

| 1 | B 1 B 0 B 3 B 2 SSSS | |||||||||

| 0 | 1 | B 3 B 2 B 1 B 0 SSSS | ||||||||

| 1 | B 0 B 1 B 2 B 3 SSSS | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 10 | Word | B

7

B

6

B

5

B

4

, B 3 B 2 B 1 B 0 | 1 | 00 | Byte | 00 (RA, LT) (3) | - | B 12 ,B 8 ,B 4 ,B 0 | ||

| 01 (LA, RT) (3) | - | B 15 ,B 11 ,B 7 ,B 3 | ||||||||

| 1x (UNPACK) | x | B 7 ,B 5 ,B 6 ,B 4 ,B 3 ,B 1 ,B 2 ,B 0 | ||||||||

| 01 | Half-word | 00 (RA, LT) (3) | 0 | x | x | B 6 B 4 ,B 2 B 0 | ||||

| 1 | B 4 B 6 ,B 0 B 2 | |||||||||

| 01 (LA, RT) (3) | 0 | B 7 B 5 ,B 3 B 1 | ||||||||

| 1 | B 5 B 7 ,B 1 B 3 | |||||||||

| 1x (UNPACK) | 0 | B 7 B 5 ,B 6 B 4 ,B 3 B 1 ,B 2 B 0 | ||||||||

| 1 | B 5 B 7 ,B 4 B 6 ,B 1 B 3 ,B 0 B 2 | |||||||||

| 10 | Word | xx | 0 | 0 | B 7 B 5 B 6 B 4 ,B 3 B 1 B 2 B 0 | |||||

| 1 | B 5 B 7 B 4 B 6 ,B 1 B 3 B 0 B 2 | |||||||||

| 0 | 1 | B 6 B 4 B 7 B 5 ,B 2 B 0 B 3 B 1 | ||||||||

| 1 | B 4 B 6 B 5 B 7 ,B 0 B 2 B 1 B 3 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 10 | Word | B 7 B 6 B 5 B 4 , B 3 B 2 B 1 B 0 | 1 | 11 (5) | Double-word | 00 (RA, 0P) (3)(4) | 0 | 0 | 0 | 0000B 3 B 1 B 2 B 0 |

| 1 | 0000B 4 B 3 B 0 B 2 | |||||||||

| 0 | 1 | 0000B 2 B 0 B 3 B 1 | ||||||||

| 1 | 0000B 0 B 2 B 1 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 1 B 2 B 0 0000 | |||||||

| 1 | B 1 B 3 B 0 B 2 0000 | |||||||||

| 0 | 1 | B 2 B 0 B 3 B 1 0000 | ||||||||

| 1 | B 0 B 2 B 1 B 3 0000 | |||||||||

| 01 (RA, SE) (3)(4) | 0 | 0 | 0 | SSSSB 3 B 1 B 2 B 0 | ||||||

| 1 | SSSSB 1 B 3 B 0 B 2 | |||||||||

| 0 | 1 | SSSSB 2 B 0 B 3 B 1 | ||||||||

| 1 | SSSSB 0 B 2 B 1 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 1 B 2 B 0 SSSS | |||||||

| 1 | B 1 B 3 B 0 B 2 SSSS | |||||||||

| 0 | 1 | B 2 B 0 B 3 B 1 SSSS | ||||||||

| 1 | B 0 B 2 B 1 B 3 SSSS | |||||||||

| 1x (PACK) | 0 | 0 | 0 | B 7 B 5 B 6 B 4 B 3 B 1 B 2 B 0 | ||||||

| 1 | B 5 B 7 B 4 B 6 B 1 B 3 B 0 B 2 | |||||||||

| 0 | 1 | B 6 B 4 B 7 B 5 B 2 B 0 B 3 B 1 | ||||||||

| 1 | B 4 B 6 B 5 B 7 B 0 B 2 B 1 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 1 B 2 B 0 B 7 B 5 B 6 B 4 | |||||||

| 1 | B 1 B 3 B 0 B 2 B 5 B 7 B 4 B 6 | |||||||||

| 0 | 1 | B 2 B 0 B 3 B 1 B 6 B 4 B 7 B 5 | ||||||||

| 1 | B 0 B 2 B 1 B 3 B 4 B 6 B 5 B 7 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 11 (6) | Double-word | B 7 B 6 B 5 B 4 B 3 B 2 B 1 B 0 | 0 | 00 | Byte | 00 (RA, LT) (3) | - | B 24 ,B 16 ,B 8 ,B 0 | ||

| 01 (LA, RT) (3) | - | B 31 ,B 23 ,B 15 ,B 7 | ||||||||

| 1x (UNPACK) | x | B 7 ,B 6 ,B 5 ,B 4 ,B 3 ,B 2 ,B 1 ,B 0 | ||||||||

| 01 | Half-word | 00 (RA, LT) (3) | 0 | x | B 9 B 8 ,B 1 B 0 | |||||

| 1 | B 8 B 9 ,B 0 B 1 | |||||||||

| 01 (LA, RT) (3) | 0 | B 15 B 14 ,B 7 B 6 | ||||||||

| 1 | B 14 B 15 ,B 6 B 7 | |||||||||

| 1x (UNPACK) | 0 | B 7 B 6 ,B 5 B 4 ,B 3 B 2 ,B 1 B 0 | ||||||||

| 1 | B 6 B 7 ,B 4 B 5 ,B 2 B 3 ,B 0 B 1 | |||||||||

| 10 | Word | 00 (RA, LT) (3) | 0 | 0 | B 11 B 10 B 9 B 8 ,B 3 B 2 B 1 B 0 | |||||

| 1 | B 10 B 11 B 8 B 9 ,B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 9 B 8 B 11 B 10 ,B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 8 B 9 B 10 B 11 ,B 0 B 1 B 2 B 3 | |||||||||

| 01 (LA, RT) (3) | 0 | 0 | x | B 15 B 14 B 13 B 12 ,B 7 B 6 B 5 B 4 | ||||||

| 1 | B 14 B 15 B 12 B 13 ,B 6 B 7 B 4 B 5 | |||||||||

| 0 | 1 | B 13 B 12 B 15 B 14 ,B 5 B 4 B 7 B 6 | ||||||||

| 1 | B 12 B 13 B 14 B 15 ,B 4 B 5 B 6 B 7 | |||||||||

| 1x (UNPACK) | 0 | 0 | B 7 B 6 B 5 B 4 ,B 3 B 2 B 1 B 0 | |||||||

| 1 | B 6 B 7 B 4 B 5 ,B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 ,B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 ,B 0 B 1 B 2 B 3 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 11 (6) | Double-word | B

7

B

6

B

5

B

4

B

3

B

2 B 1 B 0 | 0 | 11 (5) | Double-word | xx | 0 | 0 | 0 | B 7 B 6 B 5 B 4 B 3 B 2 B 1 B 0 |

| 1 | B 6 B 7 B 4 B 5 B 2 B 3 B 0 B 1 | |||||||||

| 0 | 1 | B 5 B 4 B 7 B 6 B 1 B 0 B 3 B 2 | ||||||||

| 1 | B 4 B 5 B 6 B 7 B 0 B 1 B 2 B 3 | |||||||||

| 0 | 0 | 1 | B 3 B 2 B 1 B 0 B 7 B 6 B 5 B 4 | |||||||

| 1 | B 2 B 3 B 0 B 1 B 6 B 7 B 4 B 5 | |||||||||

| 0 | 1 | B 1 B 0 B 3 B 2 B 5 B 4 B 7 B 6 | ||||||||

| 1 | B 0 B 1 B 2 B 3 B 4 B 5 B 6 B 7 | |||||||||

| 1 | 00 | Byte | 00 (RA, LT) (3) | x | x | x | B 24 ,B 16 ,B 8 ,B 0 | |||

| 01 (LA, RT) (3) | B 31 ,B 23 ,B 15 ,B 7 | |||||||||

| 1x (UNPACK) | B 7 ,B 5 ,B 6 ,B 4 ,B 3 ,B 1 ,B 2 ,B 0 | |||||||||

| 01 | Half-word | 00 (RA, LT) (3) | 0 | B 10 B 8 ,B 2 B 0 | ||||||

| 1 | B 8 B 10 ,B 0 B 2 | |||||||||

| 01 (LA, RT) (3) | 0 | B 15 B 13 ,B 7 B 5 | ||||||||

| 1 | B 13 B 15 ,B 5 B 7 | |||||||||

| 1x (UNPACK) | 0 | B 7 B 5 ,B 6 B 4 ,B 3 B 1 ,B 2 B 0 | ||||||||

| 1 | B 5 B 7 ,B 4 B 6 ,B 1 B 3 ,B 0 B 2 | |||||||||

Table 108. Programmed data handling (continued)

| SDW_LOG2 [1:0] | Source data | Source data stream (1) | SBX | DDW_LOG2 [1:0] | Destination data | PAM[1:0] (2) | DBX | DHX | DWX | Destination data stream (1) |

|---|---|---|---|---|---|---|---|---|---|---|

| 11 (6) | Double-word | B

7

B

6

B

5

B

4

B

3

B

2 B 1 B 0 | 1 | 10 | Word | 00 (RA, LT) (3) | 0 | 0 | x | B 11 B 9 B 10 B 8 , B 3 B 1 B 2 B 0 |

| 1 | B 9 B 11 B 8 B 10 , B 1 B 3 B 0 B 2 | |||||||||

| 0 | 1 | B 10 B 8 B 11 B 9 , B 2 B 0 B 3 B 1 | ||||||||

| 1 | B 8 B 10 B 9 B 11 , B 0 B 2 B 1 B 3 | |||||||||

| 01 (LA, RT) (3) | 0 | 0 | B

15

B

13

B

14

B

12

, B 7 B 5 B 6 B 4 | |||||||

| 1 | B

13

B

15

B

12

B

14

, B 5 B 7 B 4 B 6 | |||||||||

| 0 | 1 | B

14

B

12

B

15

B

13

, B 6 B 4 B 7 B 5 | ||||||||

| 1 | B

12

B

14

B

13

B

15

, B 4 B 6 B 5 B 7 | |||||||||

| 1x (UNPACK) | 0 | 0 | B 7 B 5 B 6 B 4 , B 3 B 1 B 2 B 0 | |||||||

| 1 | B 5 B 7 B 4 B 6 , B 1 B 3 B 0 B 2 | |||||||||

| 0 | 1 | B 6 B 4 B 7 B 5 , B 2 B 0 B 3 B 1 | ||||||||

| 1 | B 4 B 6 B 5 B 7 , B 0 B 2 B 1 B 3 | |||||||||

| 11 (5) | Double-word | xx | 0 | 0 | B 7 B 5 B 6 B 4 B 3 B 1 B 2 B 0 | |||||

| 1 | B 5 B 7 B 4 B 6 B 1 B 3 B 0 B 2 | |||||||||

| 0 | 1 | B 6 B 4 B 7 B 5 B 2 B 0 B 3 B 1 | ||||||||

| 1 | B 4 B 6 B 5 B 7 B 0 B 2 B 1 B 3 | |||||||||

| 0 | 0 | B 3 B 1 B 2 B 0 B 7 B 5 B 6 B 4 | ||||||||

| 1 | B 1 B 3 B 0 B 2 B 5 B 7 B 4 B 6 | |||||||||

| 0 | 1 | B 2 B 0 B 3 B 1 B 6 B 4 B 7 B 5 | ||||||||

| 1 | B 0 B 2 B 1 B 3 B 4 B 6 B 5 B 7 | |||||||||

- 1. Data stream is timely ordered starting from the byte with the lowest index (B 0 ).

- 2. RA= right aligned, LA = left aligned, RT = right truncated, LT = left truncated, OP = zero bit padding up to the destination data width, SE = sign bit extended up to the destination data width.

- 3. RA= right aligned. LA = left aligned. RT = right truncated. LT = left truncated.

- 4. OP= zero-bit padding up to the destination data width. SE = sign bit extended up to the destination data width.

- 5. if DDW_LOG2[1:0] = 11 and if the selected destination port (via DAP) is 64-bit capable. If DDW_LOG2[1:0] = 11 and the selected destination port is not 64-bit capable, a user setting error (USEF) is reported.

- 6. if SDW_LOG2[1:0] = 11 and if the selected source port (via SAP) is 64-bit capable. If SDW_LOG2[1:0] = 11 and the selected source port is not 64-bit capable, a user setting error (USEF) is reported.

13.4.11 HPDMA transfer request and arbitration

HPDMA transfer request

As defined by HPDMA_CxTR2, a programmed HPDMA data transfer is requested with one of the following:

- • a software request if the control bit SWREQ = 1: This is used typically by the CPU for a data transfer from a memory-mapped address to another memory mapped address (memory-to-memory, GPIO to/from memory)

- • an input hardware request coming from a peripheral if SWREQ = 0: The selection of the HPDMA hardware peripheral request is driven by REQSEL[4:0] (see

Section 13.3.4

). The selected hardware request can be one of the following:

- – an hardware request from a peripheral configured in HPDMA mode (for a transfer from/to the peripheral data register respectively to/from the memory)

- – an hardware request from a peripheral for its control register update from the memory

- – an hardware request from a peripheral for a read of its status registers transferred to the memory

Caution: The user must not assign the same input hardware peripheral HPDMA request via HPDMA_CxTR.REQSEL[4:0] to two different channels, if at a given time this request is asserted by the peripheral, and each channel is ready to execute this requested data transfer. There is no user setting error reporting.

HPDMA transfer request for arbitration

A ready FIFO-based HPDMA source single/burst transfer (from the source address to the FIFO) to be scheduled over the allocated master port (HPDMA_CxTR1.SAP) is arbitrated based on the channel priority (HPDMA_CxCR.PRIO[1:0]) versus the other simultaneous requested HPDMA transfers to the same master port.

A ready FIFO-based HPDMA destination single/burst transfer (from the FIFO to the destination address) to be scheduled over the allocated master port (HPDMA_CxTR1.DAP) is arbitrated based on the channel priority (HPDMA_CxCR.PRIO[1:0]) versus the other simultaneous requested HPDMA transfers to the same master port.

An arbitrated HPDMA requested link transfer consists of one 32-bit read from the linked-list data structure in the memory to one of the linked-list registers (HPDMA_CxTR1, HPDMA_CxTR2, HPDMA_CxBR1, HPDMA_CxSAR, HPDMA_CxDAR, HPDMA_CxTR3, HPDMA_CxBR2 or HPDMA_CxLLR). Each 32-bit read from the memory is arbitrated with the same channel priority as for data transfers, in order to be scheduled over the allocated master port (HPDMA_CxCR.LAP).

Whatever the requested data transfer is programmed with a software request for a memory-to-memory transfer (HPDMA_CxTR2.SWREQ = 1), or with a hardware request (HPDMA_CxTR2.SWREQ = 0) for a memory-to-peripheral transfer or a peripheral-to-memory transfer and whatever is the hardware request type, re-arbitration occurs after each granted single/burst transfer.

When an hardware request is programmed from a destination peripheral (HPDMA_CxTR2.SWREQ = 0 and HPDMA_CxTR2.DREQ = 1), the first memory read of a (possibly 2D/repeated) block (the first ready FIFO-based source burst request), is gated by the occurrence of the corresponding and selected hardware request. This first read request

to memory is not taken into account earlier by the arbiter (not as soon as the block transfer is enabled and executable).

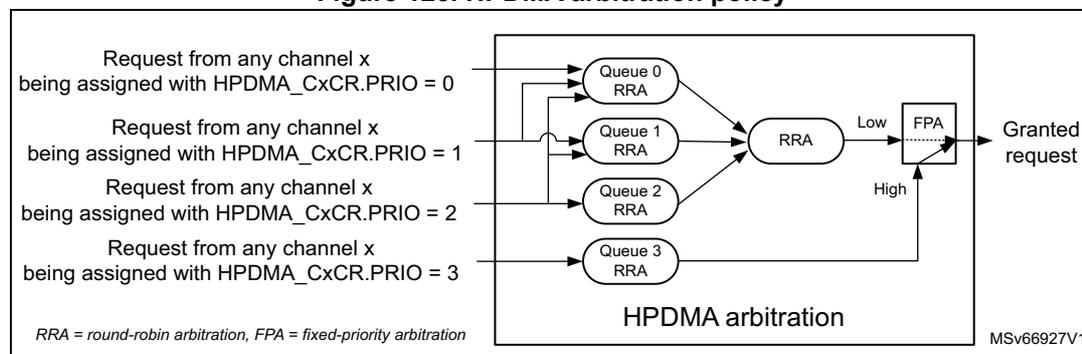

HPDMA arbitration

The HPDMA arbitration is directed from the 4-grade assigned channel priority (HPDMA_CxCR.PRIO[1:0]). The arbitration policy, as illustrated in Figure 125 , is defined by:

- • one high-priority traffic class (queue 3), dedicated to the assigned channels with priority 3, for time-sensitive channels

This traffic class is granted via a fixed-priority arbitration against any other low-priority traffic class. Within this class, requested single/burst transfers are round-robin arbitrated.

- • three low-priority traffic classes (queues 0, 1 or 2) for non time-sensitive channels with priority 0, 1 or 2

Each requested single/burst transfer within this class is round-robin arbitrated, with a weight that is monotonically driven from the programmed priority:

- – Requests with priority 0 are allocated to the queue 0.

- – Requests with priority 1 are allocated and replicated to the queue 0 and queue 1.

- – Requests with priority 2 are allocated and replicated to the queue 0, queue 1, and queue 2.

- – Any queue 0, 1 or 2 equally grants any of its active input requests in a round-robin manner, provided there are simultaneous requests.

- – Additionally, there is a second stage for the low-traffic with a round-robin arbiter that fairly alternates between simultaneous selected requests from queue 0, queue 1 and queue 2.

Figure 125. HPDMA arbitration policy

graph LR

P0[PRIO = 0] --> Q0[Queue 0 RRA]

P1[PRIO = 1] --> Q0

P1 --> Q1[Queue 1 RRA]

P2[PRIO = 2] --> Q0

P2 --> Q1

P2 --> Q2[Queue 2 RRA]

P3[PRIO = 3] --> Q3[Queue 3 RRA]

Q0 --> RRA_Low[RRA Stage]

Q1 --> RRA_Low

Q2 --> RRA_Low

RRA_Low --> FPA{FPA}

Q3 --> FPA

FPA -- High --> GR[Granted request]

FPA -- Low --> GR

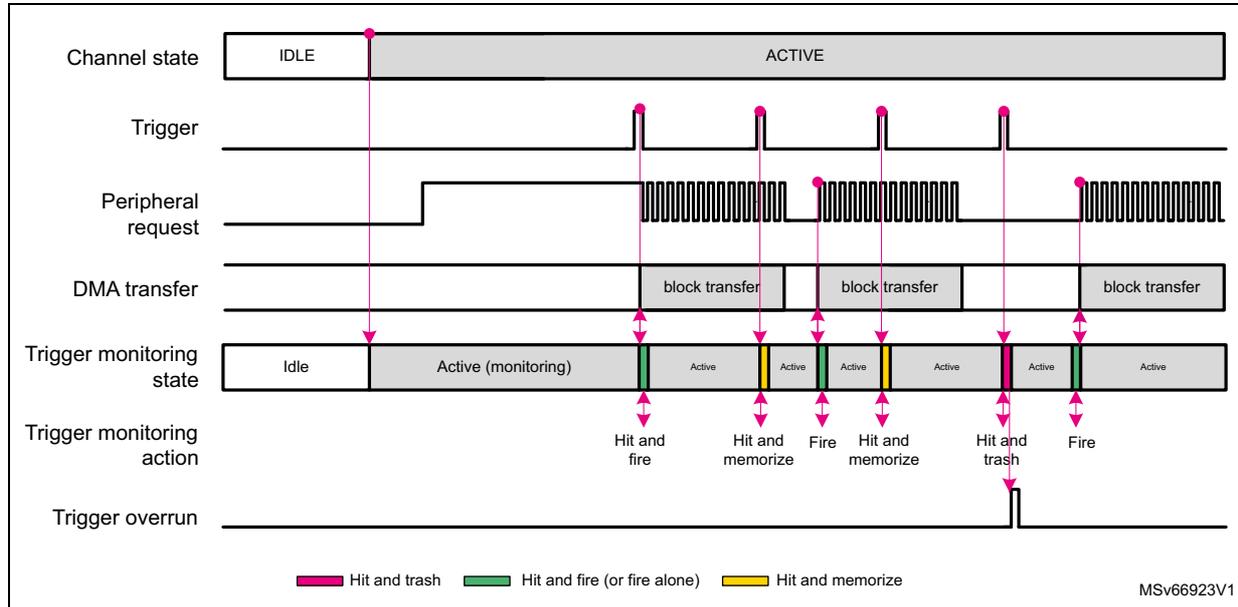

The diagram illustrates the HPDMA arbitration policy. On the left, four request sources are shown, each assigned a priority level via HPDMA_CxCR.PRIO: