7. Reset and clock control (RCC)

The RCC block manages the clock and reset generation for the whole microcontroller.

The operating modes to which this section refers are defined in Section 6.6.1: Operating modes of the PWR block.

7.1 RCC main features

AHB-Lite bus interface

Reset block:

- – Generation of local and system reset

- – Bidirectional pin reset allowing to reset the microcontroller or external devices

- – WWDG and IWDG reset supported

- – Power-on (POR) and Brownout (BOR) resets initiated by the power control (PWR)

Clock generation block:

- • Generation and dispatching of clocks for the complete device

- • 3 separate PLLs using integer or fractional ratios

- • Possibility of changing the PLL fractional ratios on-the-fly

- • Smart clock gating to reduce power dissipation

- • System clock protection

- • 2 external oscillators:

- – High-speed external oscillator (HSE) supporting a wide range of crystals from 4 to 50 MHz frequency (a)

- – Low-speed external oscillator (LSE) for the 32 kHz crystals

- • 4 internal oscillators

- – High-speed internal oscillator (HSI)

- – 48 MHz RC oscillator (HSI48)

- – Low-power internal oscillator (CSI)

- – Low-speed internal oscillator (LSI)

- • Buffered clock outputs for external devices

- • Generation of two types of interrupts lines:

- – Dedicated interrupt lines for clock security management

- – One general interrupt line for other events

- • Clock generation handling in Stop and Standby mode

a. Note that when the USBHSPHY is used, the HSE frequency must be 16, 19.2, 20, 24, 26 or 32 MHz.

7.2 RCC block diagram

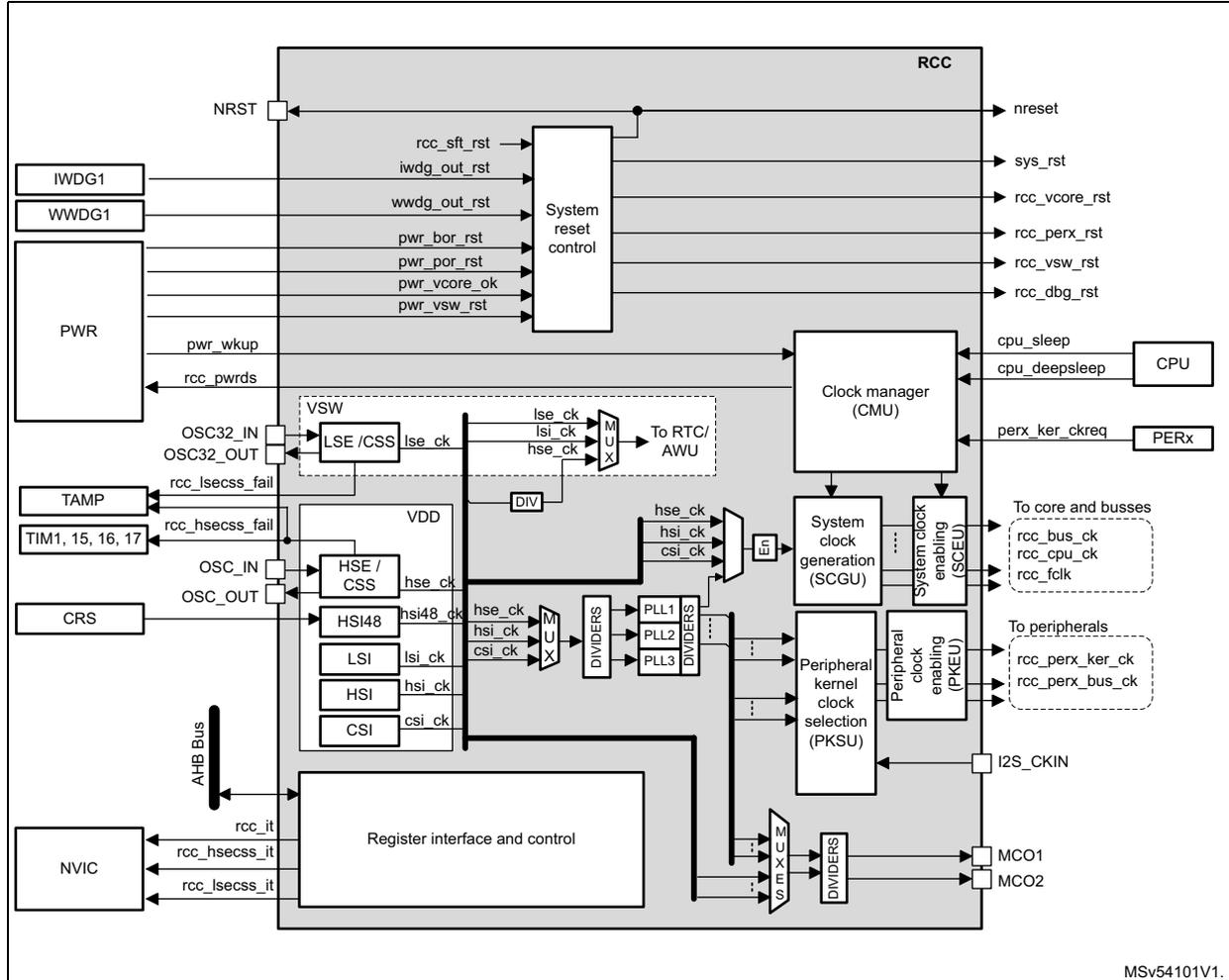

Figure 37 shows the RCC block diagram.

Figure 37. RCC block diagram

The diagram illustrates the internal architecture of the RCC block. On the left, external components are connected: IWDG1, WWDG1, and PWR (Power) to the System reset control; OSC32_IN/OUT, TAMP, TIM1, 15, 16, 17, and CRS to the VSW (Voltage Switcher) and VDD (Voltage Domain) blocks; and NVIC (Interrupt Controller) to the Register interface and control. The central part of the diagram shows the RCC internal blocks: System reset control, Clock manager (CMU), System clock generation (SCGU), Peripheral kernel clock selection (PKSU), and Register interface and control. The Register interface and control is connected to the AHB Bus and provides control signals to the other blocks. The SCGU block includes PLL1, PLL2, and PLL3 with dividers. The PKSU block includes a Peripheral clock enabling (PKEU) block. On the right, the CMU outputs nreset, sys_rst, rcc_vcore_rst, rcc_perx_rst, rcc_vsw_rst, and rcc_dbg_rst. The SCGU outputs rcc_bus_ck, rcc_cpu_ck, and rcc_fclk to the core and busses. The PKEU outputs rcc_perx_ker_ck and rcc_perx_bus_ck to the peripherals. The PKSU also outputs MCO1 and MCO2. The Register interface and control also outputs rcc_it, rcc_hsecss_it, and rcc_lsecss_it to the NVIC. The diagram is labeled MSv54101V1.

7.3 RCC pins and internal signals

Table 54 lists the RCC inputs and output signals connected to package pins or balls.

Table 54. RCC input/output signals connected to package pins or balls

| Signal name | Signal type | Description |

|---|---|---|

| NRST | I/O | System reset, can be used to provide reset to external devices |

| OSC32_IN | I | 32 kHz oscillator input |

| OSC32_OUT | O | 32 kHz oscillator output |

| OSC_IN | I | System oscillator input |

| OSC_OUT | O | System oscillator output |

| MCO1 | O | Output clock 1 for external devices |

| MCO2 | O | Output clock 2 for external devices |

| I2S_CKIN | I | External kernel clock input for digital audio interfaces: SPI/I2S, SAI, and ADF |

The RCC exchanges a lot of internal signals with all components of the product, for that reason, Table 55 only shows the most significant internal signals.

Table 55. RCC internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| rcc_it | O | General interrupt request line |

| rcc_hsecss_it | O | HSE clock security failure interrupt |

| rcc_lsecss_it | O | LSE clock security failure interrupt |

| rcc_hsecss_fail | O | Event indicating that a HSE clock security failure is detected. This signal is connected to TIMERS. |

| rcc_lsecss_fail | O | Event indicating that a LSE clock security failure is detected. This signal is connected to TAMP, EXTI and PWR |

| nreset | I/O | Application reset |

| sys_rst | I/O | System reset |

| iwdg_out_rst | I | Reset line driven by the IWDG, indicating that a timeout occurred |

| wwdg_out_rst | I | Reset line driven by the WWDG, indicating that a timeout occurred |

| pwr_bor_rst | I | Brownout reset generated by the PWR block |

| pwr_por_rst | I | Power-on reset generated by the PWR block |

| pwr_vsw_rst | I | Power-on reset of the VSW domain generated by the PWR block |

| rcc_perx_rst | O | Reset generated by the RCC for the peripherals |

| pwr_wkup | I | Wake-up domain request generated by the PWR and used to restore the domain clocks |

| rcc_pwd_req | O | Low-power request generated by the RCC and used to set the circuit into low-power mode |

Table 55. RCC internal input/output signals (Continued)

| Signal name | Signal type | Description |

|---|---|---|

| cpu_sleep | I | Signals generated by the CPU, indicating if the CPU is in CRun, Sleep or CStop |

| cpu_deepsleep | I | |

| perx_ker_ckreq | I | Signal generated by some peripherals in order to request the activation of their kernel clock |

| rcc_perx_ker_ck | O | Kernel clock signals generated by the RCC, for some peripherals |

| rcc_perx_bus_ck | O | Bus interface clock signals generated by the RCC for peripherals |

| rcc_bus_ck | O | Clocks for APB, AHB and AXI bridges generated by the RCC |

| rcc_cpu_ck | O | Clocks for the CPU, generated by the RCC |

| rcc_fclk | O |

7.4 RCC reset block functional description

The RCC handles the reset generation for the complete product, using events coming from different sources:

- • assertion of the NRST pin from an external device

- • a failure on the supply voltage applied to VDD, VBAT

- • an exit from Standby

- • a watchdog timeout

- • a software command

The reset scope depends on the source that generates the reset.

7.4.1 Reset from PWR block

The PWR block provides several reset signals to the RCC:

- • The power-on/off reset signal ( pwr_por_rst ), which is asserted when the VDD supply is lower than the VPOR threshold.

- • The brown-out reset signal ( pwr_bor_rst ), which is asserted when the VDD supply is lower than the VBOR threshold.

- • The core reset signal ( pwr_vcore_ok ), which is asserted when the VDDCORE supply is not valid or available. Note that the VDDCORE voltage is switched off, when the product is in Standby. So when the system exits from Standby mode, the pwr_vcore_ok signal is asserted as long the VDDCORE voltage provided by the internal regulator is not valid. Note that when VDD supply is not valid, pwr_vcore_ok is asserted as well.

- • The VSW domain reset signal ( pwr_vsw_rst ), which is asserted when the VSW supply is lower than the expected threshold.

Note: The rcc_vcore_rst is generated from the pwr_vcore_ok signal, the main difference between these two signals is that rcc_vcore_rst remains asserted until the option byte loading operation is completed.

Refer to Table 56: Reset coverage summary for details.

Figure 38. Simplified reset circuit

The diagram illustrates the simplified reset circuit architecture, organized into three main power domains: VDDCORE domain (grey), VDD domain (blue), and VSW domain (pink).

- External Reset (NRST): An external reset pin connected to a PAD with pull-up resistor \( R_{PU} \) and capacitor \( C_R \) . The PAD output is filtered and then stretched by a pulse stretcher.

- Internal Reset Sources:

- IWDG

(Independent Watchdog) and

WWDG

(Window Watchdog) provide

iwdg_out_rstandwwdg_out_rstsignals. - PWR

(Power) provides

pwr_bor_rst,pwr_por_rst, andpwr_vsw_rstsignals. - FLASH

provides

flitf_obl_reloadandTamp_rst_reqsignals. - DBGMCU provides a debug reset signal.

- DAP

(Debug Access Port) provides

cdbrstreq/acksignals.

- IWDG

(Independent Watchdog) and

WWDG

(Window Watchdog) provide

- Logic and Control:

- Signals from IWDG, WWDG, and the pulse stretcher are combined in an OR gate within the VDD domain.

- The output of the OR gate and

obl_rstare inputs to a PAD logic block. pwr_por_rstandrcc_vcore_rstare inputs to an RST Logic block.- A

HW system init control

block receives

pwr_vcore_ok,HW system init done, andOption bytes loadingsignals, and it controls the OBL (Option bytes loading) block. - In the VSW domain,

RCC_BDCR

provides the

VSWRSTsignal to a Logic block. - RCC_xxxRSTR

registers provide signals to a

LOGIC

block for

rcc_perx_rst. - Logic blocks combine various reset signals to generate final outputs:

nreset(Application Reset),pwr_por_rst,sys_rst(System Reset),rcc_vsw_rst,rcc_perx_rst,rcc_dbgbs_rst, andrcc_dbg_rst.

MSV54102V3.

7.4.2 The system and application resets (sys_rst and nreset)

A system reset ( sys_rst ) resets most of the registers to their default values unless otherwise specified in the register description.

A system reset can be generated from one of the following sources:

- • an assertion of the NRST pin (external reset)

- • a reset from the power-on/off reset block ( pwr_por_rst )

- • a reset from the brownout reset block (

pwr_bor_rst

)

Refer to Section 6.5.2: Brownout reset (BOR) for a detailed description of the BOR function. - • a reset from the independent watchdogs ( iwdg_out_rst )

- • an exit from Standby ( rcc_vcore_rst ).

- • a reset from the window watchdogs depending on WWDG configuration ( wwdg_out_rst )

- • a software reset from the Cortex®-M7 core

It is generated via the SYSRESETREQ signal issued by the Cortex®-M7 core. This signal is also named SFTRESET in this document. - • A reset from the low-power mode security reset, depending on option byte configuration ( lpwr_rst ).

- • An option byte reload request from the flash interface ( obl_rst )

The application reset ( nreset ) is similar to the system reset, but is not asserted when the system exits from Standby.

Note: The SYSRESETREQ bit in Cortex®-M7 through the FPU application interrupt and reset control register, must be set to force a software reset on the device. Refer to the Cortex®-M7 with FPU technical reference manual for more details (see http://infocenter.arm.com ).

7.4.3 The NRST reset

The NRST is active low. A pulse stretcher guarantees a minimum reset pulse duration of 20 µs (Refer to datasheet for details). In addition it is possible to extend the NRST assertion thanks to \( C_R \) capacitor. It is not recommended to let the NRST pin unconnected.

When it is not used, connect this pin to ground via a 10 to 100 nF capacitor (CR in Figure 38 ). As shown in Figure 38 , a filter is also present in order to suppress spurs coming from NRST PAD.

7.4.4 Low-power mode security reset (lpwr_rst)

To prevent critical applications from mistakenly enter a low-power mode, two low-power mode security resets are available. When enabled through nRST_STOP and nRST_STANDBY option bytes, a system reset is generated if the following conditions are met:

- • The CPU accidentally enters Stop mode.

This type of reset is enabled by resetting nRST_STOP user option byte. In this case, whenever the Stop mode entry sequence is successfully executed, a system reset is generated. - • The system accidentally enter Standby mode.

This type of reset is enabled by resetting nRST_STANDBY user option byte. In this

case, whenever a Standby mode entry sequence is successfully executed, a system reset is generated.

When the Standby mode is entered, a flag is also set in the power controller.

LPWRRSTF bit in the RCC Reset status register (RCC_RSR) indicates that a low-power mode security reset occurred (see line #7 in Table 57 ).

lpwr_rst is activated when a low-power mode security reset due to CPU occurred.

Refer to Section 5.4: FLASH option bytes for additional information.

Refer to Section 6: Power control (PWR) for additional information and Table 45: Operating mode summary for the overview of the existing power modes.

7.4.5 Backup domain reset

A backup domain reset ( pwr_vsw_rst ) is generated when one of the following events occurs:

- • Software reset, triggered by setting the VSWRST bit in the RCC Backup domain control register (RCC_BDCR) . All RTC registers and the RCC_BDCR register are set to their reset values, with the exception of LSEDRV, which is not changed if LSEON=1. The BKPSRAM is not affected.

- • When the VSW voltage is outside the operating range. All RTC registers and the RCC_BDCR register are set to their reset values. In this case the content of the BKPSRAM is no longer valid.

Refer to Section 6.4.4: Backup domain section of PWR block and to section “ System security ” for additional information.

7.4.6 Coresight debug reset

The coresight debug components can be reset in different ways:

- • Over the DAP by setting to 1 the bit CDBGIRSTREQ of the control/status register of the debug port. This action asserts the debug reset request signal cdbgirstreq connected to the RCC. Then the RCC activates the debug reset ( rcc_dbg_rst ), a handshake signal cdbgirstack is provided to the DAP request. The debug reset remains as long as the cdbgirstreq is to 1, refer to Figure 38 for details.

- • When VDDCORE power-on reset occurs ( rcc_vcore_rst ). This reset is activated after a power-on reset, or when the product exits from Standby.

Refer to Section 1.7.1: CoreSight Debug Reset for details.

7.4.7 Option bytes loading

As shown in Figure 38 , the option bytes loading (OBL) sequence is triggered under the following conditions:

- • After a power-on, or

- • When the system exits from Standby

- • When the flash interface requested a reload of option bytes

The system reset ( sys_rst ) can be released only when the option byte loading (OBL) is completed.

7.4.8 Peripheral resets

The application can individually reset any peripheral whenever requested. This can be done via the RCC_xxxxRSTR registers where “xxxx” is the name of the bus to which the peripheral is connected.

In order to reset a peripheral, the corresponding reset bit must be set to 1, and then set back to 0. There is no need to enable the peripheral clock in order to reset a peripheral.

Note also that the CRYPT, SAES and HASH blocks can be reset in the case of a tamper event.

7.4.9 Reset coverage summary

Table 56: Reset coverage summary gives a detailed view of the reset coverage of the most important reset sources.

Note: When \( V_{DD} \) is not valid, \( V_{DDCORE} \) is also not valid.

Table 56. Reset coverage summary (1)| Functions that are reset | Main reset lines | |||||||

|---|---|---|---|---|---|---|---|---|

| pwr_por_rst (2) | rcc_vcore_rst | sys_rst | nreset (4) | rcc_dbg_rst | rcc_perx_rst | rcc_vsw_rst | ||

| VDD domain | X | - | - | - | - | - | - | |

| MCU | X | X | X | - | - | - | - | |

| WWDG | X | X | X | - | - | - | - | |

| IWDG | X | - | - | X | - | - | - | |

| AXI/AHB Interconnections. | X | X | X | - | - | - | - | |

| Debug components, including DBGMCU Reset all the debug parts except the SWJ-DP function. The SWJ-DP is reset by the NJTRST or rcc_vcore_rst resets. The bit DCRT on DBGMCU_CR is reset with pwr_por_rst. | X | X | - | - | X | - | - | |

| Hardware system init. It includes the reload of the option bytes. | X | X | - | - | - | - | - | |

| RCC | RCC Reset status register (RCC_RSR) | X | - | - | - | - | - | - |

| RCC clock control and status register (RCC_CSR) | X | - | - | - | - | - | - | |

| RCC Backup domain control register (RCC_BDCR) | - | - | - | - | - | - | X | |

| Other RCC registers | X | X | X | - | - | - | - | |

| PWR | PWR_CSR1 | - | - | - | - | - | - | X |

| PWR_CSR2 | X | - | - | - | - | - | - | |

| PWR_CSR3 Individual bits of this register do not have the same reset condition, refer to the PWR section for details. | X | X | X | - | - | - | - | |

| PWR_WKUPCR, PWR_WKUPFR, PWR_WKUPEPR | X | - | - | X | - | - | - | |

| Other registers | X | X | X | - | - | - | - | |

| RTC | - | - | - | - | - | - | X | |

| BKPSRAM After a reset of the VSW domain, the backup regulator of the BKPSRAM is disabled, this function is controlled via the PWR block, BREN bit. If the rcc_vsw_rst reset is due to a too low VSW voltage, the content of BKPSRAM is lost. | - | - | - | - | - | - | X | |

| SBS | SBS_RSSCMR | X | - | - | - | - | - | - |

| Other Peripherals | X | X | X | - | - | X | - | |

1. The 'X' means that the function is reset by the corresponding reset line, the '-' means that the function is not reset by the corresponding reset line.

2. The pwr_por_rst is asserted when the voltage applied to VDD is not valid.

When pwr_por_rst is asserted, the rcc_vcore_rst, NRST, the sys_rst and the nreset, are asserted as well.

- 3. The

rcc_vcore_rstis asserted when the voltage applied to VDD is not valid, or when the system exits from Standby (because VDDCORE was switched off).

Whenrcc_vcore_rstis asserted, thesys_rst, and thepwr_dbg_rstare asserted as well. - 4. When nreset is asserted, the

sys_rstis also asserted.

7.4.10 Reset source identification

The CPU can identify the reset source by checking the reset flags in the

RCC_RSR

register.

The CPU can reset the flags by setting RMVF bit.

Table 57

shows how the status bits of the

RCC_RSR

register behave according to the situation that generated the reset. For example, when an IWDG timeout occurs (line #6), if the CPU is reading the

RCC_RSR

register during the boot phase, both PINRSTF and IWDGRSTF bits are set, indicating that the IWDG also generated a pin reset.

Table 57. Reset source identification (RCC_RSR) (1)

| # | Situations generating a reset | SBF (2) | LPWRRSTF | WWDGRSTF | IWDGRSTF | SFTRSTF | PORRSTF | PINRSTF | BORRSTF | OBLRSTF |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | Power-on reset ( pwr_por_rst ) | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 2 | Pin reset (NRST) | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 3 | Brownout reset ( pwr_bor_rst ) | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4 | System reset generated by CPU (SFTRESET) | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 5 | WWDG reset ( wwdg_out_rst ) | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6 | IWDG reset ( iwdg_out_rst ) | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 7 | CPU erroneously enters Stop or Standby mode | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 8 | The flash interface requested a reload of option bytes | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 9 | The product exits from Standby | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

- 1. Grayed cells highlight the register bits that are set.

- 2. The SBF bit is located into the

PWR_CSR3register of the PWR block

7.4.11 Power-on and wake-up sequences

For detailed diagrams refer to Section 6.4.1: System supply startup in the PWR section.

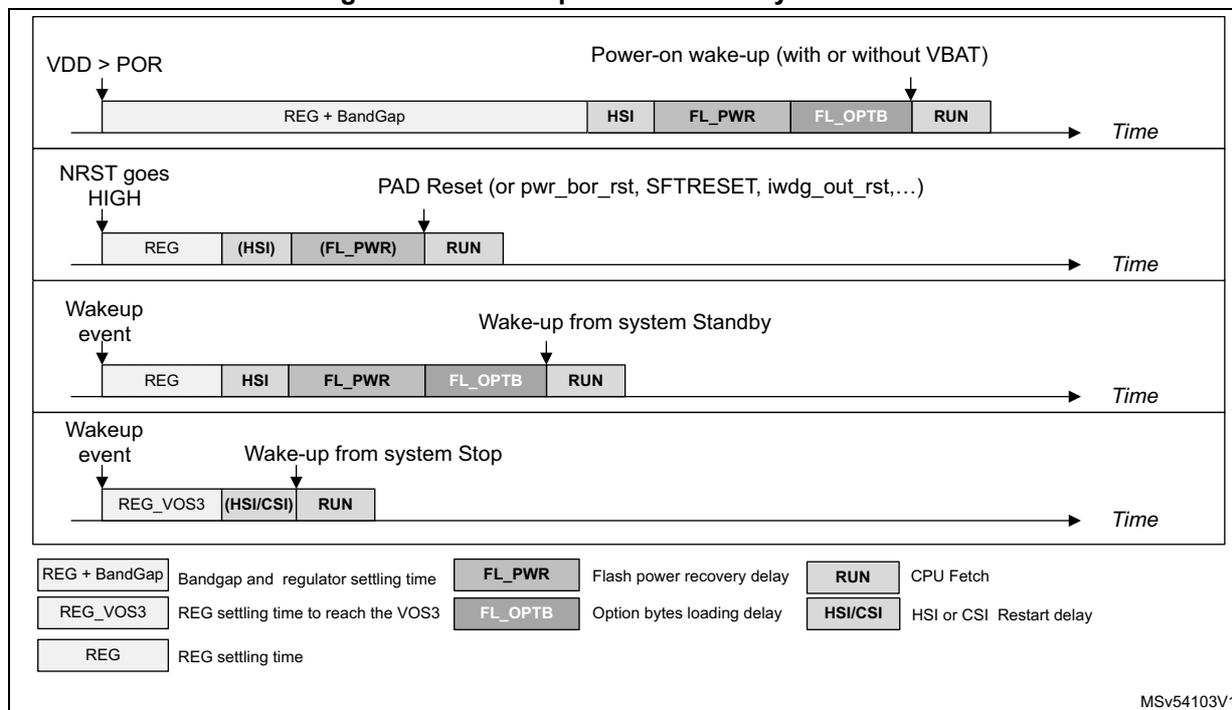

The time interval between the event that exits the product from a low-power and the moment where the CPU is able to execute code, depends on the system state and on its configuration. Figure 39 shows the most usual examples.

Power-on wake-up sequence

The power-on wake-up sequence shown in Figure 39 gives the most significant phases of the power-on sequence. It is the longest sequence since the circuit was not powered. Note that this sequence remains unchanged, whatever \( V_{BAT} \) was present or not.

Boot from pin reset

When a pin reset occurs, V DD is still present. As a result:

- • The regulator settling time is faster since the reference voltage is already stable.

- • The HSI restart delay may be needed if the HSI was not enabled when the NRST occurred, otherwise this restart delay phase is skipped.

- • The Flash memory power recovery delay can also be skipped if the Flash memory was enabled when the NRST occurred.

Note: The boot sequence is similar for pwr_bor_rst, lpwr_rst, STFRESET, iwdg_out_rst and wwdg_out_rst.

Boot from system Standby

When waking up from system Standby, the reference voltage is stable since V DD has not been removed. As a result, the regulator settling time is fast. Since V CORE was not present, the restart delay for the HSI, the Flash memory power recovery and the option byte reloading cannot be skipped.

Restart from system Stop

When restarting from Stop, V DD is still present. As a result, the sequence is mainly composed of two steps:

- 1. Regulator settling time to reach VOS low (default voltage).

- 2. HSI/CSI restart delay. This step can be skipped if HSIKERON or CSIKERON bit is set to 1 in the RCC register map .

Figure 39. Boot sequences versus system states

The figure displays four horizontal timelines representing boot sequences over time for different system states:

- Power-on wake-up (with or without VBAT): Triggered by V DD > POR. The sequence includes: REG + BandGap, HSI, FL_PWR, FL_OPTB, and RUN.

- PAD Reset (or pwr_bor_rst, STFRESET, iwdg_out_rst,...): Triggered when NRST goes HIGH. The sequence includes: REG, (HSI), (FL_PWR), and RUN. Parentheses indicate optional or skipped phases.

- Wake-up from system Standby: Triggered by a wakeup event. The sequence includes: REG, HSI, FL_PWR, FL_OPTB, and RUN.

- Wake-up from system Stop: Triggered by a wakeup event. The sequence includes: REG_VOS3, (HSI/CSI), and RUN.

Legend:

| REG + BandGap | Bandgap and regulator settling time | FL_PWR | Flash power recovery delay | RUN | CPU Fetch |

| REG_VOS3 | REG settling time to reach the VOS3 | FL_OPTB | Option bytes loading delay | HSI/CSI | HSI or CSI Restart delay |

| REG | REG settling time | ||||

MSv54103V1

7.5 RCC clock block functional description

The RCC provides a wide choice of clock generators:

- • HSI (high-speed internal oscillator) clock: ~ 8, 16, 32 or 64 MHz

- • HSE (high-speed external oscillator) clock: 4 to 50 MHz

- • LSE (low-speed external oscillator) clock: 32 kHz

- • LSI (low-speed internal oscillator) clock: ~ 32 kHz

- • CSI (low-power internal oscillator) clock: ~4 MHz

- • HSI48 (high-speed internal oscillator) clock: ~48 MHz

The RCC offers a high flexibility for the application to select the appropriate clock for CPU and peripherals, in particular for peripherals that require a specific clock such as SPI/I2S and SAI.

To optimize the power consumption, each clock source can be switched ON or OFF independently.

The RCC provides up to 3 PLLs; each of them can be configured in integer, with or without SSCG, or fractional mode.

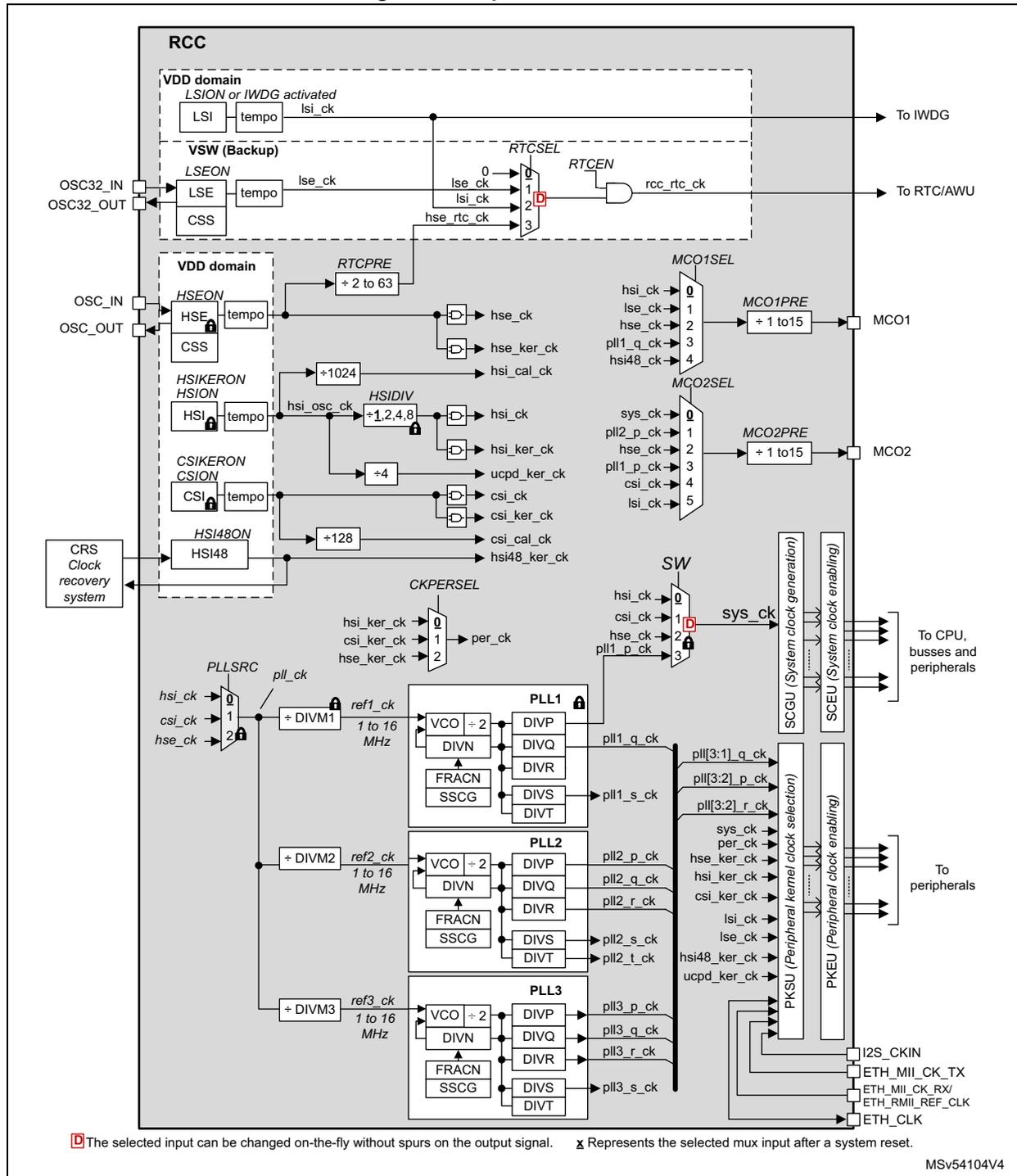

As shown in the Figure 40 , the RCC offers two clock outputs (MCO1 and MCO2), with a great flexibility on the clock selection and frequency adjustment.

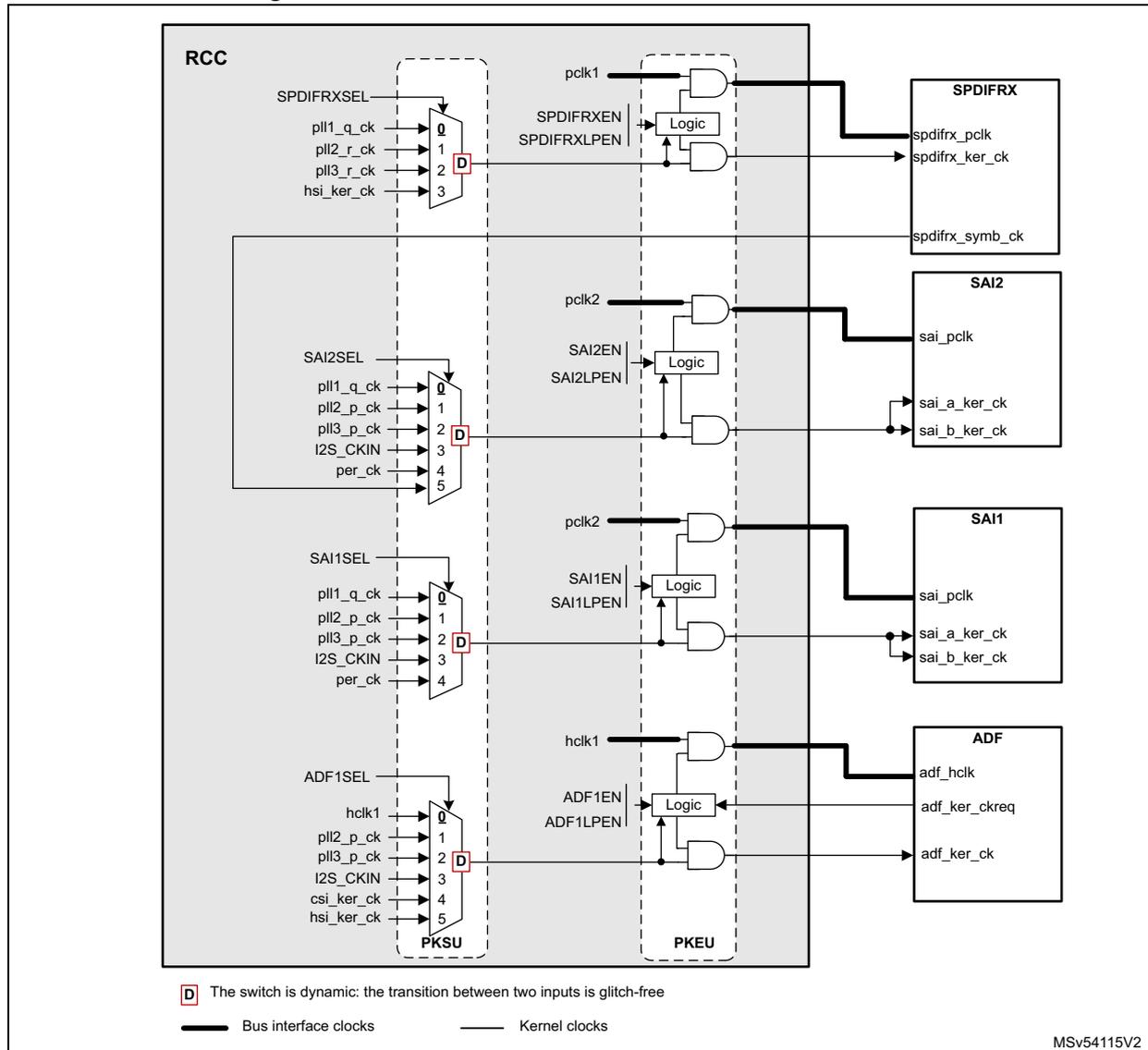

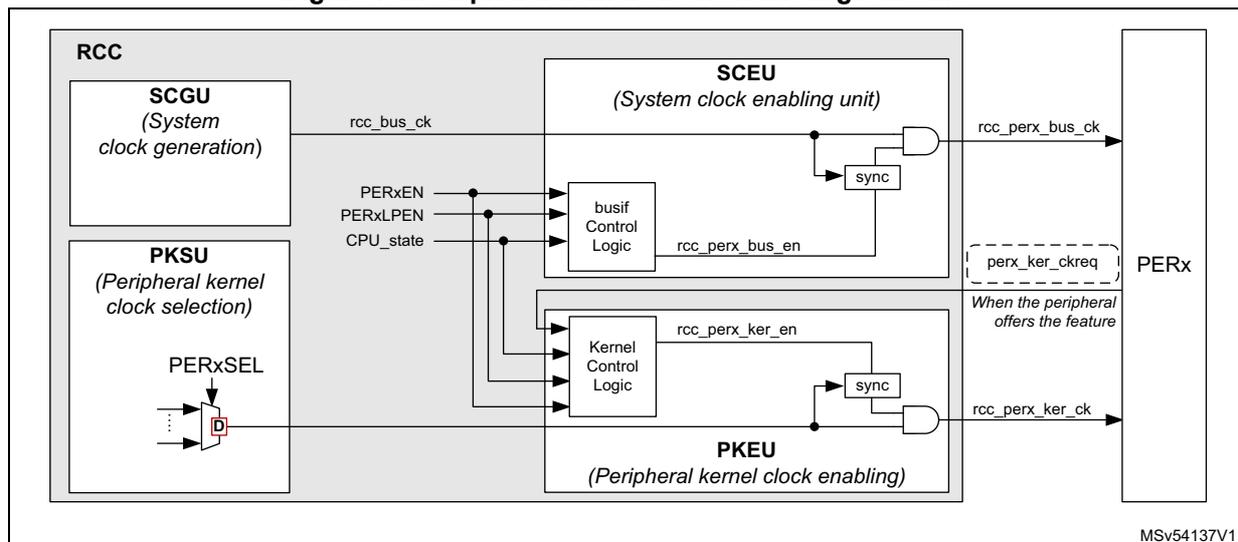

The SCGU block (system clock generation unit) contains several prescalers used to configure the CPU and bus matrix clock frequencies.

The PKSU block (peripheral kernel clock selection unit) provides several dynamic switches allowing a large choice of kernel clock distribution to peripherals.

The PKEU (peripheral kernel clock enable unit) and SCEU (system clock enable unit) blocks perform the peripheral kernel clock gating, and the bus interface/cores/bus matrix clock gating, respectively.

Figure 40. Top-level clock tree

The diagram illustrates the top-level clock tree for the RCC. It shows the following components and paths:

- RCC Domain:

- VDD domain: LSI (LSION or IWDG activated) provides lsi_ck to IWDG.

- VSW (Backup): OSC32_IN/OSC32_OUT (LSE, CSS) provides lse_ck. RTCSEL selects between lse_ck, lsi_ck, and hse_rtc_ck for the RTC/AWU via RTCCEN.

- VDD domain (Main):

- OSC_IN/OSC_OUT (HSE, CSS) provides hse_ck, hse_ker_ck, and hse_cal_ck.

- HSI (HSION, HSIKERON) provides hsi_osc_ck, which is divided by HSI48ON (+128) for hsi48_ker_ck and by HSI48ON (+128) for hsi_cal_ck. HSI also provides hsi_ck and hsi_ker_ck.

- CSI (CSION, CSIKERON) provides csi_osc_ck, which is divided by CSIDIV (+1,2,4,8) for csi_ck and csi_ker_ck, and by CSIDIV (+4) for ucpd_ker_ck.

- CRS Clock recovery system provides input to HSI48ON.

- MCUs:

- MCO1: MCO1SEL selects between hsi_ck, lse_ck, hse_ck, pll1_q_ck, and hsi48_ck. MCO1PRE (+1 to 15) provides the output.

- MCO2: MCO2SEL selects between sys_ck, pll2_p_ck, hse_ck, pll1_p_ck, csi_ck, and lsi_ck. MCO2PRE (+1 to 15) provides the output.

- PLLs:

- PLL1: PLLSRC selects between hsi_ck, csi_ck, and hse_ck. PLL1 includes VCO, DIVP, DIVN, DIVQ, DIVR, FRACN, SSGC, and DIVT. Outputs: pll1_q_ck, pll1_s_ck, and pll1_p_ck.

- PLL2: ref2_ck (from +DIVM2, 1 to 16 MHz) is the input. PLL2 includes VCO, DIVP, DIVN, DIVQ, DIVR, FRACN, SSGC, and DIVT. Outputs: pll2_p_ck, pll2_q_ck, pll2_r_ck, pll2_s_ck, and pll2_t_ck.

- PLL3: ref3_ck (from +DIVM3, 1 to 16 MHz) is the input. PLL3 includes VCO, DIVP, DIVN, DIVQ, DIVR, FRACN, SSGC, and DIVT. Outputs: pll3_p_ck, pll3_q_ck, pll3_r_ck, and pll3_s_ck.

- System Clock (sys_ck): SW selects between hsi_ck, csi_ck, hse_ck, and pll1_p_ck. sys_ck is distributed to CPU, busses, and peripherals via SCGU (System clock generation) and SCEU (System clock enabling).

- Peripheral Clocks:

- per_ck: CKPERSEL selects between hsi_ker_ck, csi_ker_ck, and hse_ker_ck.

- PKSU (Peripheral kernel clock selection) provides clocks to peripherals via PKEU (Peripheral clock enabling). Inputs include sys_ck, per_ck, hse_ker_ck, hsi_ker_ck, csi_ker_ck, lsi_ck, lse_ck, hsi48_ker_ck, and ucpd_ker_ck. Outputs include I2S_CKIN, ETH_MII_CK_TX, ETH_MII_CK_RX, ETH_RMII_REF_CLK, and ETH_CLK.

D The selected input can be changed on-the-fly without spurs on the output signal. x Represents the selected mux input after a system reset.

MSV54104V4

7.5.1 Clock naming convention

The RCC provides clocks to the complete circuit. To avoid misunderstanding, the following terms are used in this document:

- • Peripheral clocks

The peripheral clocks are the clocks provided by the RCC to the peripherals. Two kinds of clock are available:

- – bus interface clocks

- – kernel clocks

A peripheral receives from the RCC a bus interface clock in order to access its registers, and thus control the peripheral operation. This clock is generally the AHB, APB or AXI clock depending on which bus the peripheral is connected to. Some peripherals only need a bus interface clock (such as RNG, TIMx).

Some peripherals also require a dedicated clock to handle the interface function. This clock is named kernel clock. As an example, peripherals such as SAI must generate specific and accurate master clock frequencies, which require dedicated kernel clock frequencies. Another advantage of decoupling the bus interface clock from the specific interface needs, is that the bus clock can be changed without reprogramming the peripheral.

- • CPU clock

The CPU clock is the clock provided to the CPU. It is derived from the system clock ( sys_ck ).

- • Bus matrix clocks

The bus matrix clocks are the clocks provided to the different bridges (APB, AHB or AXI). These clocks are derived from the system clock ( sys_ck ).

7.5.2 Oscillators description

The table hereafter shows the oscillator states versus system modes, when the oscillators are enabled via registers. The term “available” means that the resource can be used if activated via registers.

Table 58. Oscillator states versus system modes

| System modes | VDD domain | VSW domain | ||||

|---|---|---|---|---|---|---|

| HSE | HSI | HSI48 | CSI | LSI | LSE | |

| Exit from system reset | OFF | ON | OFF | OFF | Available | Available |

| Exit from system Stop | OFF | ON (1) | OFF | ON (2) | Available | Available |

| In Run/Sleep | Available | Available | Available | Available | Available | Available |

| In Stop | OFF | Available (3) | OFF | Available (4) | Available | Available |

| In Standby | OFF | OFF | OFF | OFF | Available | Available |

| In VBAT | OFF | OFF | OFF | OFF | OFF | Available |

1. If STOPWUCK = 0 or STOPKERWUCK = 0

2. If STOPWUCK = 1 or STOPKERWUCK = 1

3. HSI can remain activated in Stop if HSIKERON = 1, or if a peripheral selecting HSI, generates a kernel clock request.

4. CSI can remain activated in Stop if CSIKERON = 1, or if the peripheral selecting CSI, generates a kernel clock request.

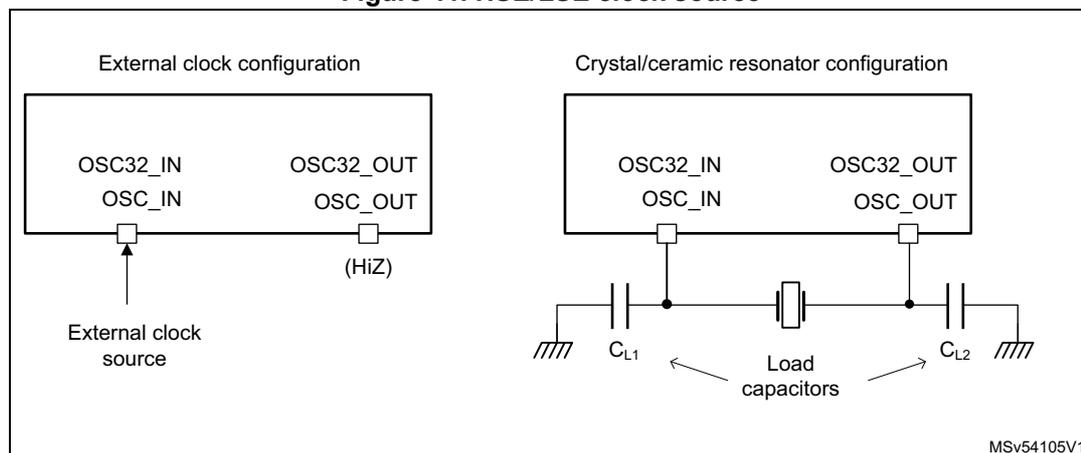

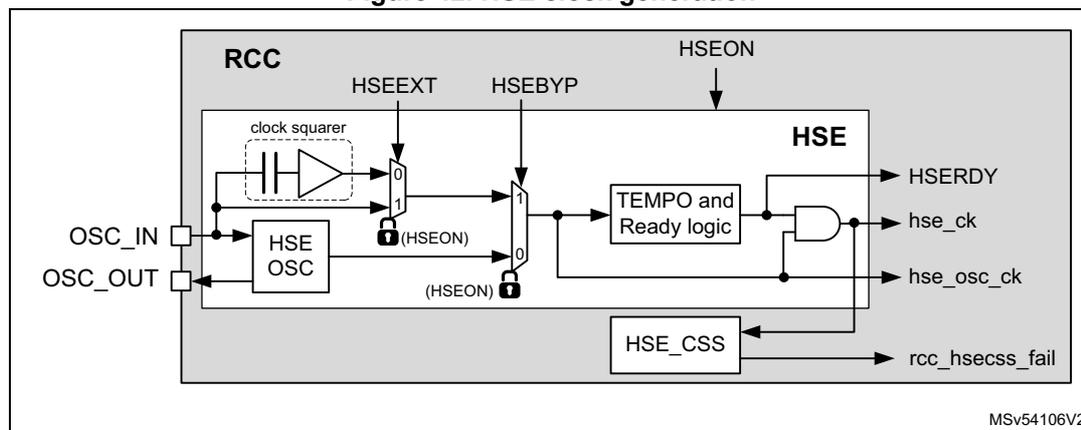

HSE oscillator

The HSE block allows the application to provide a very accurate high-speed clock for the product. The HSE can generate an internal clock from two possible sources:

- • external clock source

- • external crystal/ceramic resonator

Figure 41. HSE/LSE clock source

External clock source (HSE bypass)

In this mode the oscillator is not used, and an external clock source must be provided to OSC_IN pin. The external clock can be low swing (analog) or digital. The OSC_OUT pin must be left HI-Z (see Figure 41).

The external clock signal can be digital or analog (square, sinus or triangle). An analog clock signal with a reduced amplitude, is supported thanks to an internal clock squarer. The input signal must have a duty cycle close to 50%. Refer to the datasheet for additional information.

This mode is selected when HSEBYP = 1, and HSEON = 1. In case of an analog clock input (low swing) the HSEEXT must be set to 0, for a digital clock input, HSEEXT bits must be set to 1.

Figure 42. HSE clock generation

External crystal/ceramic resonator

A crystal/resonator can be connected as shown in Figure 41 : the crystal/resonator and the load capacitors must be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected crystal or ceramic resonator. Refer to the electrical characteristics section of the datasheet for more details.

The oscillator mode is enabled by setting the HSEBYP bit to 0 and HSEON bit to 1.

HSE ready logic

The HSERDY flag indicates when a valid clock is available at HSE output ( hse_ck ). When the HSE is enabled (HSEON set to '1'), the HSERDY flag goes to '1' when 256 valid cycles of HSE have been detected. The hse_ck clock is not released until HSERDY goes to 1.

An interrupt can be generated if enabled in the RCC clock source interrupt enable register (RCC_CIER) .

HSE controls

The HSE can be switched ON and OFF through the HSEON bit.

The hardware does not allow modifying HSEON bit if one of the condition is met:

- • The HSE is used directly (via SW switch) as system clock.

- • The HSE is selected as reference clock for PLL1, with PLL1 enabled and selected to provide the system clock (via SW switch).

- • The bit XSPICKP is set to 1.

- • The bit FMCKP is set to 1.

The hardware does not allow changing the values of HSEBYP, and HSEEXT when HSEON = 1. Bits HSEBYP, HSEEXT and HSEON are located into the RCC register map .

The HSE is automatically disabled by hardware when the system enters Stop or Standby mode (See Table 58: Oscillator states versus system modes ).

In addition, the HSE clock can be driven to the MCO1 and MCO2 outputs and used as clock source for other application components.

Programming sequence

In order initialize the HSE, the application must follow the sequence hereafter:

- • Make sure the HSE is not directly or indirectly used as system clock, if it is the case, use HSI or CSI as clock source for system clock.

- • Make sure that XSPICKP and FMCCKP are set to 0

- • Disable the HSE by writing to 0 the HSEON bit,

- • Check that the HSE is disabled by waiting that the bit HSERDY is set to 0,

- • If the oscillator mode is needed:

- – Select the oscillator mode by setting HSEBYP to 0,

- • If an external clock is connected to OSC_IN:

- – Select the bypass mode by setting HSEBYP to 1,

- – If the input clock is a full-swing digital signal, set HSEEXT to 1

- – If the input clock is a low-swing signal, set HSEEXT to 0

- • Enable again the HSE by writing the HSEON bit to 1,

- • Wait for HSERDY = 1, then the HSE is ready for use.

LSE oscillator

The LSE block allows the application to provide a very accurate low-frequency clock for the product. The LSE can generate an internal clock from two possible sources:

- • external user clock

- • external crystal/ceramic resonator

External clock source (LSE bypass)

In this mode, the oscillator is not used, and an external clock source must be provided to OSC32_IN pin. The OSC32_OUT pin must be left HI-Z (see Figure 41 ).

The external clock signal can have a frequency up to 1 MHz and be digital or analog (square, sinus or triangle). An analog clock signal with a reduced amplitude, is supported thanks to an internal clock squarer. The input signal must have a duty cycle close to 50%. Refer to the datasheet for additional information.

This mode is selected by setting the LSEBYP and LSEON bits to 1. In case of an analog clock input (low swing) the LSEEXT must be set to 0, for a digital clock input, LSEEXT bits must be set to 1.

Figure 43. LSE clock generation

![Figure 43. LSE clock generation block diagram. The diagram shows the internal architecture of the LSE block within the RCC. It includes an LSE OSC (Low-Speed External Oscillator) connected to OSC32_IN and OSC32_OUT pins. The OSC32_IN pin is also connected to a clock squarer. The LSE OSC output is connected to a multiplexer (MUX) labeled LSEEXT. The MUX has two inputs: one from the clock squarer (labeled 0) and one from the LSE OSC (labeled 1). The MUX output is connected to the LSE block. The LSE block contains a TEMPO and Ready logic block, which is also connected to the LSEON bit. The LSE block outputs LSECK and LSERDY. The LSECK output is connected to the LSE_CSS block, which in turn outputs rcc_lsecs_fail. The LSE block is also connected to the LSEDRV[1:0] register. The LSEON bit is connected to the LSE block and the TEMPO and Ready logic block. The LSEEXT bit is connected to the MUX. The LSEBYP bit is connected to the MUX. The LSEON bit is also connected to the LSE block. The LSE block is labeled Vsw domain. The diagram is labeled MSV54107V2.](/RM0477-STM32H7Rx-7Sx/922cbd842837181a486c2aceb2b6cd65_img.jpg)

External crystal/ceramic resonator source (LSE crystal)

The LSE clock is generated from a 32.768 kHz crystal or ceramic resonator. It has the advantage to provide a low-power highly accurate clock source to the real-time clock (RTC) for clock/calendar or other timing functions. A crystal/resonator can be connected as shown in Figure 41 : the crystal/resonator and the load capacitors must be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected crystal or ceramic resonator. Refer to the electrical characteristics section of the datasheet for more details.

The oscillator mode is selected by setting LSEBYP bit to 0 and LSEON bit to 1.

The LSE also offers a programmable driving capability (LSEDRV[1:0]) that can be used to modulate the amplifier driving capability. This driving capability is chosen according to the external crystal/ceramic component requirement to insure a stable oscillation.

The driving capability must be set before enabling the LSE oscillator.

Warning: It is not allowed to change the driving capability when the LSE is enabled. The LSE behavior is not guaranteed in that case.

LSE ready logic

The LSE offers a LSERDY flag which indicates whether the LSE clock is available or not. When the LSE is enabled (LSEON set to 1) the LSERDY flag goes to 1 when certain amount of valid cycles of LSE clock have been detected. The lse_ck clock is not released until LSERDY goes to 1.

When LSEBYP = 0, the RCC waits 4096 clocks cycles before activating the LSERDY flag, when LSEBYP = 1, the RCC waits 8 clocks cycles.

An interrupt, can be generated if enabled in the RCC clock source interrupt enable register (RCC_CIER) .

LSERDY bit is located into the RCC Backup domain control register (RCC_BDCR) .

LSE controls

The LSE control bits LSEBYP, LSEEXT, LSEDRV[1:0] and LSEON are located into the RCC Backup domain control register (RCC_BDCR) . This register is write-protected by DBP bit of PWR_CR1 register. In order to modify the RCC_BDCR register, the bit DBP must be set 1.

The LSE oscillator is switched ON and OFF using the LSEON bit.

The LSE remains enabled when the system enters Stop, Standby or VBAT mode (See Table 58: Oscillator states versus system modes ).

The hardware does not allow changing the values of LSEBYP, and LSEEXT when LSEON = 1.

In addition, the LSE clock can be driven to the MCO1 output and used as clock source for external components.

LSE Programming sequence

In order initialize the LSE, the application must follow the sequence hereafter:

- • Set DBP bit of PWR_CR1 to 1 in order to allow write accesses to RCC_BDCR register.

- • Disable the LSE by writing to 0 the LSEON bit,

- • Check that the LSE is disabled by waiting that the bit LSERDY is set to 0,

- • if the oscillator mode is needed:

- – Select the oscillator mode by setting LSEBYP to 0,

- – Configure LSEDRV[1:0],

- • if an external clock is connected to OSC32_IN:

- – Select the bypass mode by setting LSEBYP to 1,

- – If the input clock is a full-swing digital signal, set LSEEXT to 1

- – If the input clock is a low-swing signal, set LSEEXT to 0

- • Enable again the LSE by writing the LSEON bit to 1,

- • Wait for LSERDY = 1, then the LSE is ready for use.

- • If RCC_BDCR register no longer need to be changed, set DBP bit of PWR_CR1 to 0 in order to write-protect accesses.

If the RTC is used, the LSE bypass must not be configured in digital mode but in low swing analog mode (default value after reset).

HSI oscillator

The HSI block provides the default clock to the product.

The HSI is a high-speed internal RC oscillator that can be used directly as system clock, peripheral clock, or as PLL input. A predivider allows the application to select an HSI output frequency of 8, 16, 32 or 64 MHz. This predivider is controlled by the HSIDIV.

The HSI advantages are the following:

- • low-cost clock source since no external crystal is required

- • faster startup time than HSE (a few microseconds)

The HSI frequency, even with frequency calibration, is less accurate than an external crystal oscillator or ceramic resonator.

HSI controls

The HSI can be switched ON and OFF using the HSION bit.

The hardware does not allow modifying HSION bit if one of the condition is met:

- • The HSI is used directly (via software mux) as system clock.

- • The HSI is selected as reference clock for PLL1, with PLL1 enabled and selected to provide the system clock (via software mux).

- • The bit XSPICKP is set to 1.

- • The bit FMCCPK is set to 1.

Note that the HSIDIV cannot be changed if the HSI is selected as reference clock for at least one enabled PLL (PLLxON bit set to 1). In that case the hardware does not update the HSIDIV with the new value. However it is possible to change the HSIDIV if the HSI is used directly as system clock.

The HSIRDY flag indicates if the HSI is stable or not. At startup, the HSI output clock is not released until this bit is set by hardware.

The HSI clock can also be used as a backup source (auxiliary clock) if the HSE fails (refer to Section : CSS on HSE ).

The HSI can be disabled or not when the system enters Stop mode (See Table 58: Oscillator states versus system modes ).

In addition, the HSI clock can be driven to the MCO1 output and used as clock source for other application components.

Care must be taken when the HSI is used as kernel clock for communication peripherals, the application must take into account the following parameters:

- • the time interval between the moment where the peripheral generates a kernel clock request and the moment where the clock is really available,

- • the frequency accuracy.

HSION, HSIRDY and HSIDIV bits are located in the RCC register map .

HSI calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations. That is why each device is factory calibrated by STMicroelectronics to achieve an accuracy of ACC HSI (refer to the product datasheet for more information).

After a power-on reset, or at the exit of Standby mode, the factory calibration value is loaded in the HSICAL[11:0] bits.

If the application is subject to voltage or temperature variations, this may affect the RC oscillator frequency. The user application can trim the HSI frequency using the HSITRIM[6:0] bits.

Note: HSICAL[11:0] and HSITRIM[6:0] bits are located in the RCC HSI calibration register (RCC_HSICFGR) .

Figure 44. HSI calibration flow

![Figure 44. HSI calibration flow diagram. The diagram shows the flow of calibration data from Engineering option bytes (factory calibration) through the RCC block to the HSI block. The RCC block contains FLASH_HSI_opt[11:9] and FLASH_HSI_opt[8:0] registers. The FLASH_HSI_opt[8:0] register is connected to an adder (+) which also receives input from the HSITRIM[6:0] (unsigned) register. The output of the adder is connected to the HSI block's CAL[11:0] register. The HSI block also contains the HSICAL[11:9] and HSICAL[8:0] registers, which are connected to the RCC_HSICFGR register. The RCC_HSICFGR register is connected to the HSI block's CAL[11:0] register. The diagram is labeled MSV48151V2.](/RM0477-STM32H7Rx-7Sx/b38817d867550ae783546d5910d4db22_img.jpg)

CSI oscillator

The CSI is a low-power RC oscillator that can be used directly as system clock, peripheral clock, or PLL input.

The CSI advantages are the following:

- • low-cost clock source since no external crystal is required

- • faster startup time than HSE (a few microseconds)

- • very low-power consumption.

The CSI provides a clock frequency of about 4 MHz, while the HSI is able to provide a clock up to 64 MHz.

CSI frequency, even with frequency calibration, is less accurate than an external crystal oscillator or ceramic resonator.

CSI controls

The CSI can be switched ON and OFF through the CSION bit. The CSIRDY flag indicates whether the CSI is stable or not. At startup, the CSI output clock is not released until this bit is set by hardware.

The hardware does not allow modifying CSION bit if one of the condition is met:

- • The CSI is used directly (via software mux) as system clock.

- • The CSI is selected as reference clock for PLL1, with PLL1 enabled and selected to provide the system clock (via software mux).

- • The bit XSPICKP is set to 1.

- • The bit FMCCPK is set to 1.

The CSI can be disabled or not when the system enters Stop mode (See Table 58: Oscillator states versus system modes ).

In addition, the CSI clock can be driven to the MCO2 output and used as clock source for other application components.

Even if the CSI settling time is faster than the HSI, care must be taken when the CSI is used as kernel clock for communication peripherals: the application must take into account the following parameters:

- • the time interval between the moment where the peripheral generates a kernel clock request and the moment where the clock is really available,

- • the frequency precision.

Note: CSION and CSIRDY bits are located in the RCC register map .

CSI calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by STMicroelectronics to achieve accuracy of ACC CSI (refer to the product datasheet for more information).

After a power-on reset, or at the exit of Standby mode, the factory calibration value is loaded in the CSICAL[7:0] bits.

If the application is subject to voltage or temperature variations, this may affect the RC oscillator frequency. The user application can trim the CSI frequency using the CSITRIM[5:0] bits.

Note: Bits CSICAL[7:0] and CSITRIM[5:0] are located into the RCC CSI calibration register (RCC_CSICFGR)

Figure 45. CSI calibration flow

![Figure 45: CSI calibration flow diagram. An external block 'Engineering option bytes (factory calibration)' provides 'FLASH_CSI_opt[7:0]' to a summation node (+) inside the RCC block. The summation node also receives 'CSITRIM[5:0] (unsigned)' from the 'RCC_CSICFGR' register. The output of the summation node is 'csi_cal[7:0]', which goes into the 'CSI CAL[7:0]' block. Additionally, 'CSICAL[7:0] (unsigned)' is shown as an output from the 'RCC_CSICFGR' register.](/RM0477-STM32H7Rx-7Sx/b0390f547e09eaaa66fcea613b1ea46e_img.jpg)

MSV48152V1

HSI48 oscillator

The HSI48 is an RC oscillator delivering a 48 MHz clock that can be used directly as kernel clock for some peripherals.

The HSI48 oscillator mainly aims at providing an accurate clock to the USB Full-Speed peripherals by means of a special clock recovery system (CRS) circuitry. The CRS can use the USB SOF signal, the LSE or an external signal to automatically adjust the oscillator frequency on-the-fly, with a very small granularity. It is possible to read the calibration value provided to the HSI48 via RCC clock recovery RC register (RCC_CRRRCR) . The HSI48TRIM value can be adjusted through the CRS block, for more details, refer to Section 9: Clock recovery system (CRS) .

Figure 46. HSI48 calibration flow

![Figure 46. HSI48 calibration flow diagram. The diagram shows the HSI48 calibration process. A box labeled 'CRS' has an output 'HSI48TRIM[5:0] (unsigned)' pointing to a summation node (+). A box labeled 'Engineering option bytes (factory calibration)' points to the same summation node. The summation node is inside a larger box labeled 'RCC'. The output of the summation node is 'hs48_cal[9:0]', which points to a box labeled 'HSI48 CAL[9:0]'. Below the summation node is another output 'HSI48CAL[9:0] (unsigned)' pointing to a box labeled 'RCC_CRRRCR'. The 'RCC' box also contains 'FLASH_HSI48_opt[9:0]'.](/RM0477-STM32H7Rx-7Sx/6de875eb7a49c3352b45075b92e5ea9b_img.jpg)

The diagram illustrates the HSI48 calibration flow. At the top, a 'CRS' block provides a 6-bit unsigned value 'HSI48TRIM[5:0]'. This value is added to the 'FLASH_HSI48_opt[9:0]' value, which originates from 'Engineering option bytes (factory calibration)'. The summation result, 'hs48_cal[9:0]', is stored in the 'HSI48 CAL[9:0]' register. Additionally, the 'RCC' block contains a 10-bit unsigned value 'HSI48CAL[9:0]' which is also related to the calibration process and is stored in the 'RCC_CRRRCR' register. The 'RCC' block also includes the 'FLASH_HSI48_opt[9:0]' register.

MSV54108V1

The HSI48 oscillator is disabled as soon as the system enters Stop or Standby mode. When the CRS is not used, this oscillator is free running and thus subject to manufacturing process variations. This is why each device is factory calibrated by STMicroelectronics to achieve an accuracy of ACC HSI48 (refer to the product datasheet for more information).

The HSI48RDY flag indicates whether the HSI48 oscillator is stable or not. At startup, the HSI48 output clock is not released until this bit is set by hardware.

After a power-on reset, or at the exit of Standby mode, the factory calibration value is loaded into the HSI48.

The HSI48 can be switched ON and OFF using the HSI48ON bit.

The HSI48 clock can also be driven to the MCO1 multiplexer and used as clock source for other application components.

Note: HSI48ON and HSI48RDY bits are located in the RCC register map.

LSI oscillator

The LSI acts as a very-low-power clock source that can be kept running when the system is in Stop or Standby mode for the independent watchdog (IWDG) and auto-wake up unit (AWU). The clock frequency is around 32 kHz. For more details, refer to the electrical characteristics section of the datasheet.

The LSI can be switched ON and OFF using the LSION bit. The LSIRDY flag indicates whether the LSI oscillator is stable or not. If an independent watchdog is started either by hardware or software, the LSI is forced ON and cannot be disabled.

The LSI remains enabled when the system enters Stop or Standby mode (See Table 58: Oscillator states versus system modes ).

At LSI startup, the clock is not provided until the hardware sets the LSIRDY bit. An interrupt can be generated if enabled in the RCC clock source interrupt enable register (RCC_CIER) .

In addition, the LSI clock can be driven to the MCO2 output and used as a clock source for other application components.

Note: Bits LSION and LSIRDY bits are located into the RCC clock control and status register (RCC_CSR).

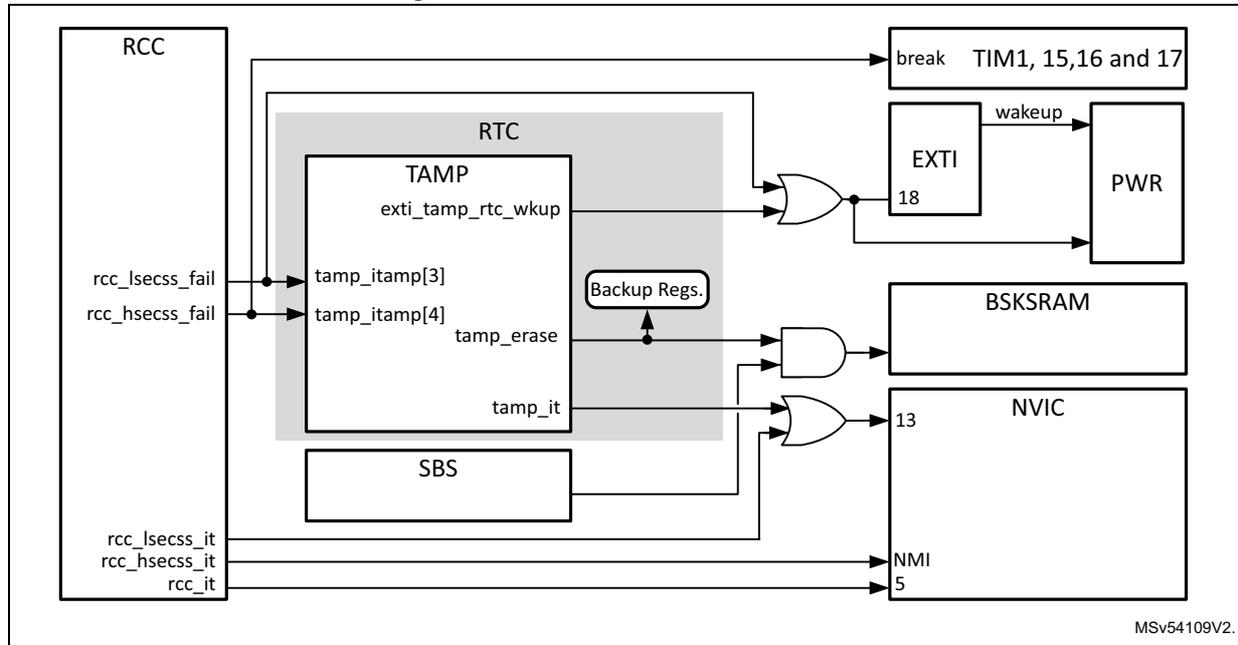

7.5.3 Clock security system (CSS)

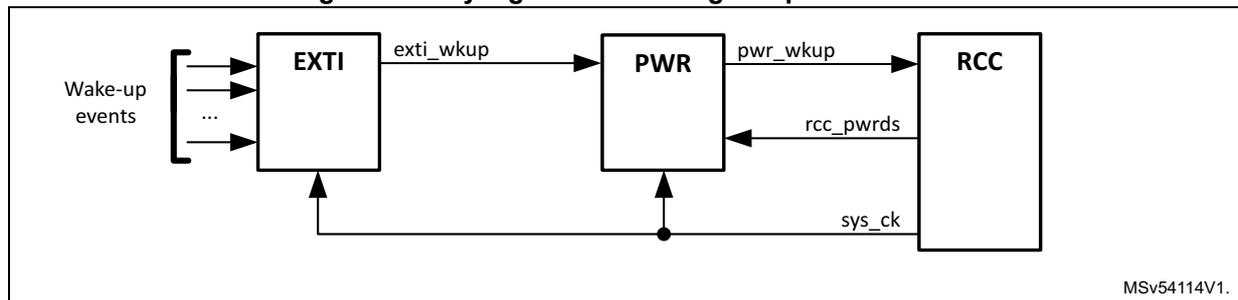

The RCC offers a clock security system for the HSE and LSE oscillators. The clock security systems are capable of detecting a failure on HSE and LSE oscillators. The figure hereafter shows how this function interacts with other blocks.

Figure 47. LSE and HSE CSS function

The diagram illustrates the internal architecture of the clock security system (CSS) for LSE and HSE. The main component is the RCC (Reset and Clock Control), which has several output signals:

rcc_lsecss_fail

,

rcc_hsecss_fail

,

rcc_lsecss_it

,

rcc_hsecss_it

, and

rcc_it

. These signals connect to various system blocks. The

rcc_lsecss_fail

and

rcc_hsecss_fail

signals are connected to the TAMP (Tamper and Backup) block, specifically to

tamp_itamp[3]

and

tamp_itamp[4]

inputs. The

rcc_lsecss_it

and

rcc_hsecss_it

signals are connected to the NMI (Non-Maskable Interrupt) block. The

rcc_it

signal is connected to the SBS (Standby) block. The TAMP block is part of the RTC (Real-Time Clock) system and includes

Backup Regs.

(Backup Registers). It has inputs for

exti_tamp_rtc_wkup

,

tamp_erase

, and

tamp_it

. The

tamp_it

signal is connected to the NVIC (Nested Vectored Interrupt Controller) block. The

exti_tamp_rtc_wkup

signal is connected to an OR gate, which is also connected to the

rcc_lsecss_fail

and

rcc_hsecss_fail

signals. The output of this OR gate is connected to the EXTI (External Interrupt) block, which has a

wakeup

signal connected to the PWR (Power) block. The

tamp_erase

signal is connected to an AND gate, which is also connected to the

rcc_lsecss_fail

and

rcc_hsecss_fail

signals. The output of this AND gate is connected to the BSKSRAM (Backup SRAM) block. The

rcc_lsecss_it

and

rcc_hsecss_it

signals are connected to the NMI block, which has a

break

signal connected to the TIM1 (Timer 1) block, specifically to the

TIM1, 15,16 and 17

inputs. The

rcc_it

signal is connected to the SBS block, which is connected to the NVIC block. The NVIC block has a

13

input connected to the

tamp_it

signal and a

5

input connected to the

rcc_lsecss_it

and

rcc_hsecss_it

signals. The diagram is labeled MSv54109V2.

CSS on HSE

The clock security system can be enabled by software via the HSECSSON bit. The HSECSSON bit can be enabled even when the HSEON is set to 0.

The CSS on HSE is activated when the HSE is enabled and ready, and the software sets the HSECSSON bit to 1. The CSS on HSE is no longer working when the HSE is disabled. For example, this function does not work when the system is in Stop mode.

It is not possible to clear directly the HSECSSON bit by software. The HSECSSON bit is cleared by hardware when a system reset occurs or when the system enters Standby mode (see Section 7.4.2: The system and application resets (sys_rst and nreset) ).

When the CSS on HSE is enabled, the following actions are done by the RCC if a failure is detected:

- • The signal rcc_hsecss_fail is asserted.

- • If the STOPWUCK = 0, the HSI clock is enabled and the SW switch automatically selects HSI as system clock.

- • If the STOPWUCK = 1, the CSI clock is enabled and the SW switch automatically selects CSI as system clock.

- • The HSE is then automatically disabled.

- • If the HSE output was used as clock source for PLLs, the PLLs are also disabled.

- • The XSPI[2:1]SEL switches go to recovery position.

- • The FMCSEL switch goes to recovery position:

- – if PLL1 has been disabled and FMCSEL is in position 1.

- – if PLL2 has been disabled and FMCSEL is in position 2.

See details on Section : Clock distribution for SDMMC, FMC, and XSPIs .

- • The clock failure event ( rcc_hsecss_fail ) is also sent to the break inputs of advanced-control timers (TIM1, TIM15, TIM16 and TIM17).

- • A NMI interrupt is generated to inform the software about the failure (CSS interrupt: rcc_hsecss_it ), thus allowing the MCU to perform rescue operations. The CSS interrupt is asserted until the HSECSSF bit is cleared. The HSECSSF flag can be cleared by setting the HSECSSC bit in the RCC clock source interrupt clear register (RCC_CICR) .

- • A tamper event can also be triggered, in order to clear content of the backup registers, and backup RAM.

CSS on LSE

A clock security system on the LSE oscillator can be enabled by software by programming the LSECSSON bit in the RCC Backup domain control register (RCC_BDCR) .

This bit is disabled by hardware if one of the following condition is met:

- • After a \( V_{SW} \) hardware reset ( pwr_vsw_rst ),

- • After a \( V_{SW} \) software reset via VSWRST bit

The software can also disable the clock security system after a LSE failure detection.

The CSS on LSE works in all modes (Run, Stop and Standby) including VBAT.

The LSECSS provides a re-arm feature, offering to the software the possibility to re-arm the LSECSS and re-enable the LSE clock when a failure has been detected. This feature allows the application to decide if the LSE is to be provided again to the RTC even if a failure occurred, or if another action must be performed. For example the application can decide to reset the \( V_{SW} \) domain only if a certain amount of consecutive LSE failures occurred, within a time window.

The LSECSS offers two flag signals:

- • The LSECSSD, capable of retaining an LSE failures even in VBAT mode.

- • The LSECSSF used to generate interrupt in case of LSE failure. This flag is not affected by a failure detected when the product is in VBAT mode

The sequence hereafter describes the LSE enabling sequence with the clock security system enabled.

- • Follow the LSE enable procedure given in the section LSE Programming sequence , except the last step

- • Select the LSE clock via RTCSEL[1:0]

- • Set the LSECSSON bit to 1

- • If RCC_BDCR register no longer needs to be changed, set DBP bit of PWR_CR1 to 0 in order to write-protect accesses.

Note: The LSECSSON bit must be enabled after the LSE is enabled (LSEON bit set by software) and ready (LSERDY set by hardware), and after the RTC clock has been selected through the RTCSEL bit.

If a failure is detected on the LSE, the hardware does the following:

- • The LSE clock is no more delivered to the RTC.

- • The values of RTCSEL, LSECSSON and LSEON bits are not changed by the hardware.

- • A failure event is generated ( rcc_lsecss_fail ). This event allows the system to wake-up from Standby, but also to protect the backup registers and BKPSRAM via TAMP block. This event is also generated in VBAT mode.

- • The interrupt flag LSECSSF is activated (except in VBAT mode) in order to generate an interrupt ( rcc_lsecss_it ).

- • The LSECSSD flag is activated as well, retaining the first LSE failure even in VBAT.

In the software side, different actions can be taken according to the application requirements. Three different cases are described hereafter in order to illustrate the hardware behavior, they can also be combined. The application can also decide to handle LSE failure differently.

Case A:

The application no longer wants to use LSE when a failure is detected:

- • Unlock RCC_BDCR register by setting the DBP bit of PWR_CR1 to 1

- • Disable the CSS function (this step is mandatory)

- – Clear the LSECSSF bit, if interrupt was enabled for this event

- – Set the LSECSSON bit to 0

- – Set the LSEON bit to 0, in order to disable the LSE

- • Change the clock source for the RTC if needed:

- – Set the RTCEN bit to 0 to disable the RTC clock

- – Enable the new clock source for the RTC

- – Select the proper clock source via RTCSEL

- – Set the RTCEN bit to 1 to enable the RTC clock

- • The application must perform specific actions consecutive to TAMPER events if enabled

- • Lock RCC_BDCR register by setting the DBP bit of PWR_CR1 to 0

Case B:

The application wants to re-initialize the \( V_{SW} \) domain:

- • Unlock RCC_BDCR register by setting the DBP bit of PWR_CR1 to 1

- • Perform a VSW reset by setting VSWRST bit to 1, then back to 0 (it is in reality a pulse of one period of sys_ck)

- • The application must perform specific actions consecutive to TAMPER events if enabled

- • Re-initialize all components of the VSW domain.

- • Lock RCC_BDCR register by setting the DBP bit of PWR_CR1 to 0

Case C:

The application tries to re-use LSE when a failure is detected:

- • If the number of failures in a given time window is higher than a given threshold then go to case A or B. Otherwise continue to next step.

- • Unlock RCC_BDCR register by setting the DBP bit of PWR_CR1 to 1

- • Clear the LSECSSF bit if interrupt was enabled for this event.

- • The application must perform specific actions consecutive to TAMPER events if enabled

- • Set the LSECSSON bit to 0.

- • Re-arm the LSECSS function by writing the LSECSSRA bit to 1, then back to 0.

- • Wait for LSERDY set 1. The LSERDY flag must go to 1 after the oscillator settling time delay plus, 4096 periods of LSE clock. If this is not the case, it probably means that the LSE failure is permanent. It is not possible to set LSECSSON to 1, it is recommended to execute case A or B.

- • Set the LSECSSON bit to 1.

- • When LSECSSON is seen to 1, the LSE is enabled, and protected by LSECSS.

- • Lock RCC_BDCR register by setting the DBP bit of PWR_CR1 to 0

All bits used in this sequences (except DBP) are located into RCC Backup domain control register (RCC_BDCR) .

7.5.4 Clock output generation (MCO1/MCO2)

Two microcontroller clock output pins MCO1 and MCO2, are available. A clock source can be selected for each output. The selected clock can be divided thanks to configurable prescaler (refer to Figure 40 for additional information on signal selection).

MCO1 and MCO2 outputs are controlled via MCO1PRE[3:0], MCO1SEL[2:0], MCO2PRE[3:0] and MCO2SEL[2:0] located in the RCC clock configuration register (RCC_CFGR) .

The GPIO port corresponding to each MCO pin must be programmed in alternate function mode.

The dividers MCO1PRE and MCO2PRE, provide a clock with a duty cycle of 50% for even divisions values. More generally the duty cycle is given by the following formula:

For MCOxPRE = 2 to 15.

Note that the MCO1 and MCO2 outputs are available in Run and Stop modes.

Caution: The clock provided to the MCOs outputs must not exceed the maximum PAD speed, refer to the product datasheet for information about the supported PAD speed.

The table hereafter show the signals available on each MCO output.

Table 59. Oscillator states versus system modes

| MCO1SEL | MCO2SEL | ||

|---|---|---|---|

| Pos. | Clock source | Pos. | Clock source |

| 0 | hsi_ck | 0 | sys_ck |

| 1 | lse_ck | 1 | pll2_p_ck |

| 2 | hse_ck | 2 | hse_ck |

| 3 | pll1_q_ck | 3 | pll1_p_ck |

| 4 | hsi48_ck | 4 | csi_ck |

| - | - | 5 | lsi_ck |

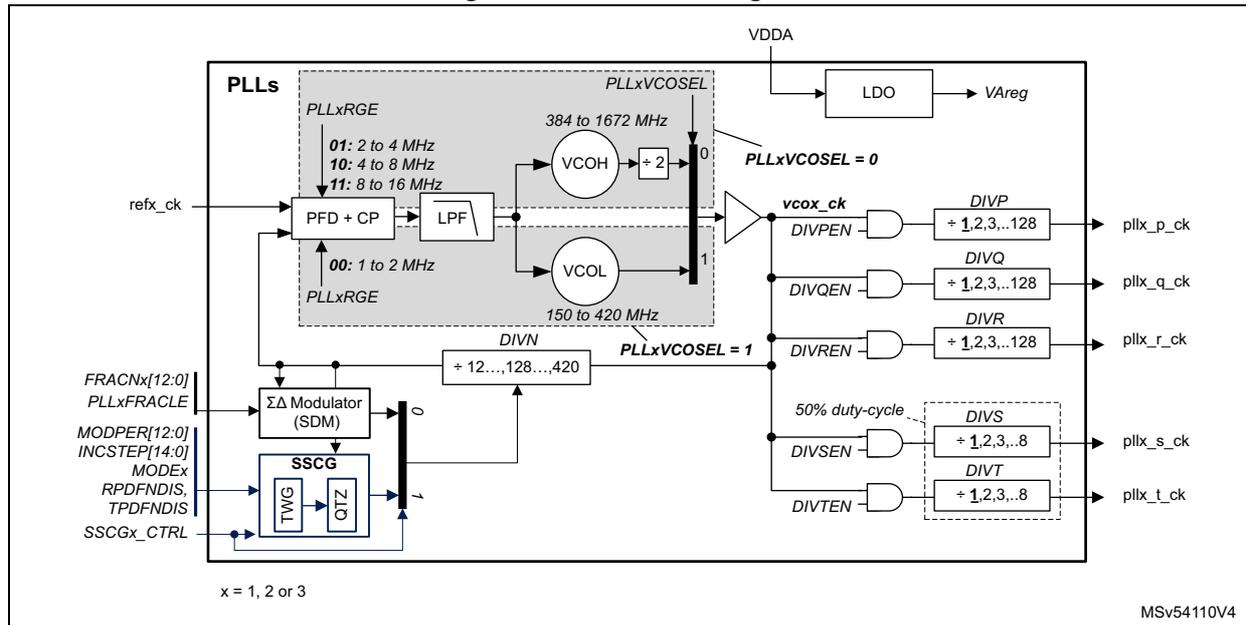

7.5.5 PLL description

The RCC features three PLLs:

- • PLL1, generally used to provide clocks to the CPU, busses, and some peripherals

- • PLL2, generally used to provide clocks to XSPI and SDMMC, and some peripherals

- • PLL3, dedicated to the kernel clock generation for peripherals

The PLLs integrated into the RCC are completely independent. They offer the following features:

- • A VCO supporting two modes:

- – a wide-range

- – a low-range used for instance in audio application cases

- • Input frequency range:

- – 2 to 16 MHz for the VCO in wide-range mode

- – 1 to 2 MHz for the VCO in low-range mode

- • VCO frequency range:

- – 384 to 1672 MHz for the VCO in high-range mode (VCOH), before the divider.

- – 150 to 420 MHz for the VCO in low-range mode (VCOL)

- • Capability to work either in integer with or without SSGC, or in fractional mode

- • 13-bit sigma-delta modulator, allowing to fine-tune the VCO frequency by steps of 10 to 0.3 ppm

- • The sigma-delta modulator can be updated on-the-fly without generating frequency overshoots on PLLs outputs.

- • PLLs offer up to 5 outputs with post-dividers.

For better flexibility, all PLLs offer two VCOs (VCOH and VCOL), the application can select the wanted VCO via PLLxVCOSEL bit.

The frequency of the reference clock provided to the PLLs ( refx_ck ) must range from 1 to 16 MHz. The DIVMx dividers of the RCC PLLs clock source selection register (RCC_PLLCKSEL) must be properly programmed in order to match this condition. In addition, the PLLxRGE[1:0] field of the RCC PLLs configuration register (RCC_PLLCFG) must be set according to the reference input frequency to guarantee an optimal performance of the PLL.

The user application can then configure the proper VCO. VCOL must be chosen when the reference clock frequency is lower than 2 MHz.

To reduce the power consumption, it is recommended to configure the VCO output to the smaller range.

Figure 48. PLL block diagram

x = 1, 2 or 3 MSv54110V4

The PLLs can be enabled by setting PLLxON to 1. The PLLxRDY bits indicate that the PLL is ready (means locked).

The DIVN loop divider must be programmed to achieve the expected frequency at VCO output. The VCO output range must be respected.

PLLs have a divider-by-2, at VCOH output, insuring that the clock provided to the post-dividers has a duty-cycle of 50%.

The frequency of the clocks provided by the PLLs can also be adjusted thanks to post-divider DIVP , DIVQ , DIVR , DIVS and DIVT . The post-divider values can be changed without disabling the PLLs, if their respective enable bits are set to 0.

The post-dividers provide clocks with 50% duty-cycle in the following conditions:

- • When the post-dividers are dividing the clock by an even value.

- • When VCOH is used and post-dividers are bypassed.

- • When VCOH is selected and post-dividers DIVS and DIVT are used,

PLL programming recommendations

This section is providing a list of recommendations to follow in order to guarantee a good usage of the PLLs. Note that programming examples are given in Section 1.6.2: PLL programming.

- • Before enabling the PLLs, the user must ensure that the reference frequency ( refx_ck ) provided to the PLL is stable and in the good range.

- • When one or several PLL outputs are not used, the application must set the corresponding enable bit DIV[y]ENx and the divider value DIV[y]x to 0 (with x = 1, 2 or 3, and y = P, Q, R, S or T).

- • In order to ensure the good behavior of the PLL, the bits PLLxPEN , PLLxQEN , PLLxREN , PLLxSEN and PLLxTEN must be set to 0 before disabling the corresponding PLL. In the same way, the bits PLLxPEN , PLLxQEN , PLLxREN ,

PLLxSEN and PLLxTEN can be set to 1 only if the corresponding bit PLLON is already set to 1 and the PLL is ready.

Refer to section Section 7.7.1: PLL programming procedure for additional information.

PLL protections

- • The RCC hardware does not allow changing DIVMx, DIVN, PLLxRGE, PLLxVCOSEL when the corresponding PLLx is ON and it is also not possible to change PLLSRC when one of the PLL is ON.

- • The RCC hardware does not allow changing of the post-dividers' DIVy when the corresponding PLLxyEN bit is set to 1 (with x = 1, 2 or 3, and y = P, Q, R, S or T).

- • The hardware prevents writing PLL1ON or PLL1PEN to 0 if the PLL1 is currently used to deliver the system clock. There are other hardware protections on the clock generators (refer to Section 7.5.7: Clock protection ).

The PLLs are disabled by hardware when the system enters Stop or Standby mode

PLLs using HSE as reference clock are also disabled by hardware if an HSE failure is detected.

Note: The

refx_ck

clock is provided to the PLLx when the corresponding PLLON bit is set to 1.

The PLLs can work in 3 different modes:

- • In integer mode

- • In fractional mode

- • In spread spectrum mode

Using the PLLs in integer mode

The PLL is working in integer mode when the sigma-delta modulator (SDM) is loaded with a 0, and the bit PLLxSSCGEN = 0.

In order to load 0 into the SDM, the user has to perform the following sequence:

- – Write PLLxFRACLE of RCC PLLs configuration register (RCC_PLLCFGR) to 0

- – Write FRACN[12:0] to 0,

- – Write PLLxFRACLE to 1

- – Wait at least 5 µs

The bits FRACN[12:0] are located in the RCC_PLLxFRACR registers.

The VCO frequency ( \( F_{VCO} \) ) and output frequencies expressions are given by the following table:

Table 60. VCO frequency and output frequency in integer mode

| PLLxVCOSEL = 0 | PLLxVCOSEL = 1 |

|---|---|

| \( F_{VCO} = 2 \times F_{ref\_ck} \times (DIVN + 1) \) | \( F_{VCO} = F_{ref\_ck} \times (DIVN + 1) \) |

\[

F_{pll\_y\_ck} = \frac{F_{VCO}}{2 \times (DIVy + 1)}

\] with y = P, Q, R, S or T | \[

F_{pll\_y\_ck} = \frac{F_{VCO}}{(DIVy + 1)}

\] with y = P, Q, R, S or T |

Refer to section Section 7.7.1: PLL programming procedure for additional information.

Using the PLLs in fractional mode

The fractional mode is activated when the value loaded into the SDM is different from 0, and the bit PLLxSSCGEN = 0.

The SDM value can be updated at anytime by the application by executing the following sequence:

- – Write PLLxFRACLE bit to '0'

- – Write into FRACN[12:0] the new fractional value,

- – Write PLLxFRACLE to '1'.

The new FRACN value is loaded into the SDM when PLLxFRACLE bit goes from 0 to 1. - – Wait at least 5 µs

The sigma delta modulator is designed in order to minimize the jitter impact while allowing very small frequency steps.

When the PLL is used in fractional mode, the DIVN divider must be initialized before enabling the PLL.

This feature can be used either to generate a specific frequency, with a good accuracy from any crystal value, or to perform a fine tuning of the frequency on-the-fly.

The VCO frequency ( \( F_{VCO} \) ) and output frequencies expressions are given by the following table:

Table 61. VCO frequency and output frequency in fractional mode

| PLLxVCOSEL = 0 | PLLxVCOSEL = 1 |

|---|---|

\[

F_{VCO} = 2 \times F_{ref\_ck} \times \left( DIVN + 1 + \frac{FRACN}{2^{13}} \right)

\] | \[

F_{VCO} = F_{ref\_ck} \times \left( DIVN + 1 + \frac{FRACN}{2^{13}} \right)

\] |

\[

F_{pll\_y\_ck} = \frac{F_{VCO}}{2 \times (DIVy + 1)}

\] with y = P, Q, R, S or T | \[

F_{pll\_y\_ck} = \frac{F_{VCO}}{(DIVy + 1)}

\] with y = P, Q, R, S or T |

Refer to section Section 7.7.1: PLL programming procedure for additional information.

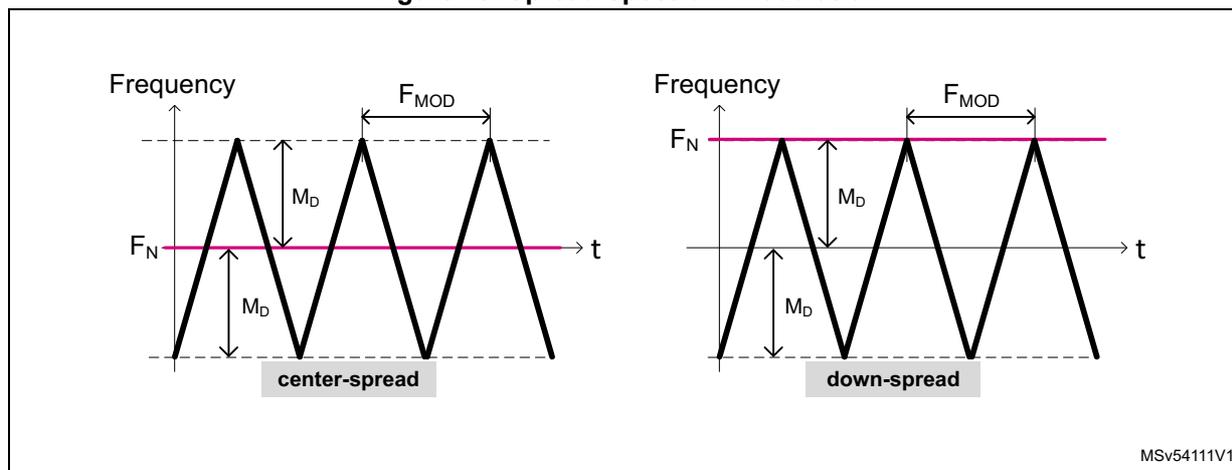

Using the PLLs in spread spectrum mode

The spread spectrum mode is activated when the SDM loaded with 0, and the bit PLLxSSCGEN = 1. This feature is available on all PLLs.

The VCOH must be selected when the spread spectrum mode is activated. VCOH is selected by setting PLLxVCOSEL to 0. PLLxVCOSEL are located into the RCC clock configuration register (RCC_CFGR) .

The spread spectrum technique consist of modulating the VCO frequency with a low-frequency signal (in our case a triangular signal), in order to spread the clock energy into a wider frequency band. As a consequence, the amount of emitted EMI peaks is reduced.

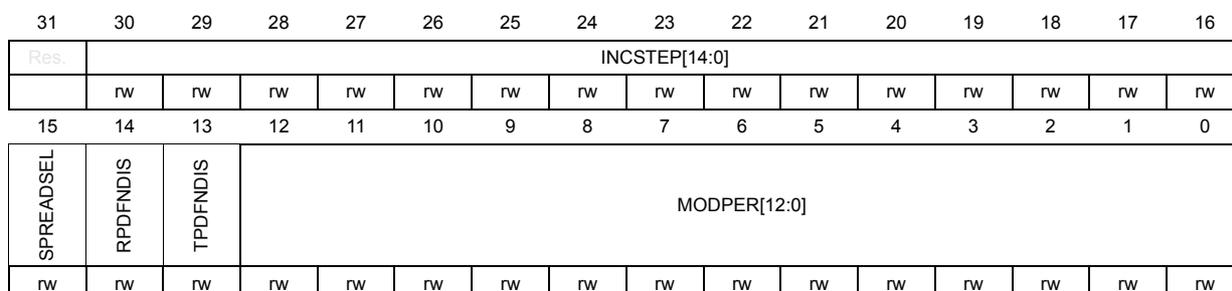

The parameters of the spread spectrum modulation are adjusted via the following fields:

- • MODPER[12:0]: used to adjust the modulation frequency

- • INCSTEP[14:0]: used to adjust the modulation depth (or modulation index)

- • SPREADSEL: used to define if the modulation is centered around the VCO frequency (center-spread) or if it is lowered with respect to VCO frequency (down-spread).

The bits MODPER[12:0], INCSTEP[14:0] and SPREADSEL are located into the RCC_PLLxSSCGR registers with x=1, 2 or 3.

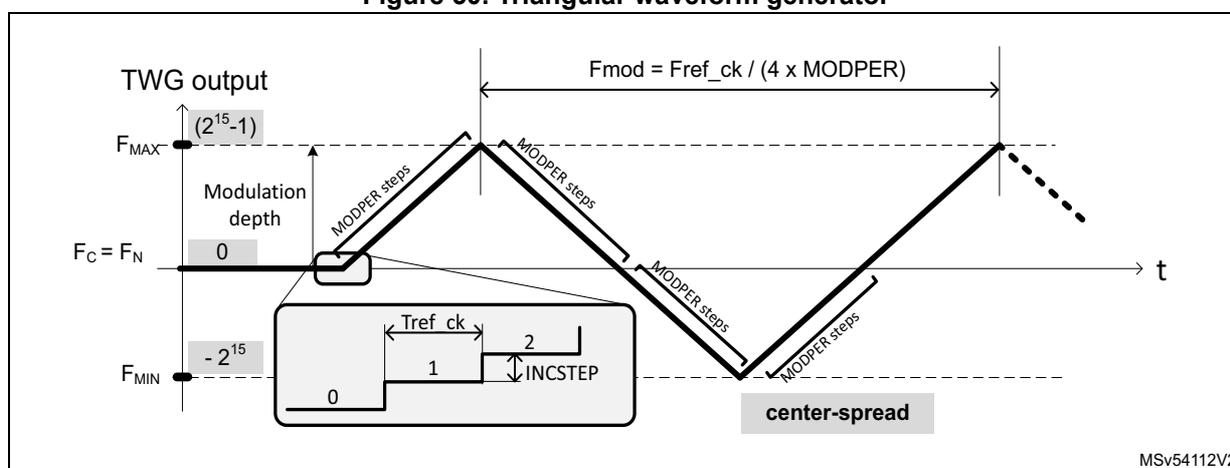

Figure 49 shows the signal modulating the nominal frequency ( \( F_N \) ), when SPREADSEL = 0 (center-spread) and SPREADSEL = 1 (down-spread). The nominal frequency is the frequency output by the PLL in integer mode, when no clock spreading is applied.

Setting the SPREADSEL bit to '1' (down-spread) guarantees that the PLL output frequency does not exceed the programmed frequency value when the SSCG is enabled.

Figure 49. Spread-spectrum modulation

MSV54111V1

The peak modulation depth (in percentage) is given by the following formula:

Note that MODPER x INCSTEP must not exceed \( (2^{15}-1) \) .

The modulation frequency ( \( F_{\text{mod}} \) ) is given by:

Note: Refer to the datasheet of the product for the recommended modulation frequency range

In order to use the spread spectrum feature, the user has to do the following:

- • Program the PLL as explained into Section : Using the PLLs in integer mode in order to adjust the nominal frequency ( \( F_N \) ) according to the targeted by the application.

- • Compute the MODPER value according to the wanted modulation frequency ( \( F_{\text{mod}} \) ):

- • Compute the INCSTEP value according to the wanted modulation depth ( \( M_D \) ):

Check that MODPER x INCSTEP does not exceed \( (2^{15}-1) \) .

- • Then DIVP, Q, R, S or T can be adjusted, and the bit PLLxSSCGEN can be set to 1, and the PLL enabled.

The user can check \( F_{MIN} \) , \( F_{MAX} \) and \( F_C \) as follow:

- • If SSCG_MODE = '0' (centered-spread)

\( F_C \) is given by the formula of the Section : Using the PLLs in integer mode

\( F_{MIN} = F_C \times (1 - M_D/100) \)

\( F_{MAX} = F_C \times (1 + M_D/100) \) - • If SSCG_MODE = '1' (down-spread)

\( F_{MAX} \) is given by the formula of the Section : Using the PLLs in integer mode

\( F_{MIN} = F_{MAX} \times (1 - 2 \times M_D/100) \)

\( F_C = F_{MAX} \times (1 - M_D/100) \)

Figure 50 shows the digital signal generated by Triangular Waveform Generator (TWG block), and the way of MODPER and INCSTEP are changing the triangular waveform.

Figure 50. Triangular waveform generator

Refer to section Section 7.7.1: PLL programming procedure for additional information.

7.5.6 System clock (sys_ck)

System clock selection

After a system reset, the HSI is selected as system clock and all PLLs are switched OFF. When a clock source is used for the system clock, it is not possible for the software to disable the selected source via the xxxON bits.

Of course, the system clock can be stopped by the hardware when the system enters Stop or Standby mode.

When the system is running, the user application can select the system clock ( sys_ck ) among the 4 following sources:

- • HSE

- • HSI

- • CSI

- • pll1_p_ck

This function is controlled by programming the RCC clock configuration register (RCC_CFGR) . A switch from one clock source to another occurs only if the target clock

source is ready (clock stable after startup delay or PLL locked). If a clock source that is not yet ready is selected, the switch occurs when the clock source is ready.

The SWS status bits in the RCC clock configuration register (RCC_CFGR) indicate which clock is currently used as system clock. The other status bits in the RCC_CR register indicate which clock(s) is (are) ready.

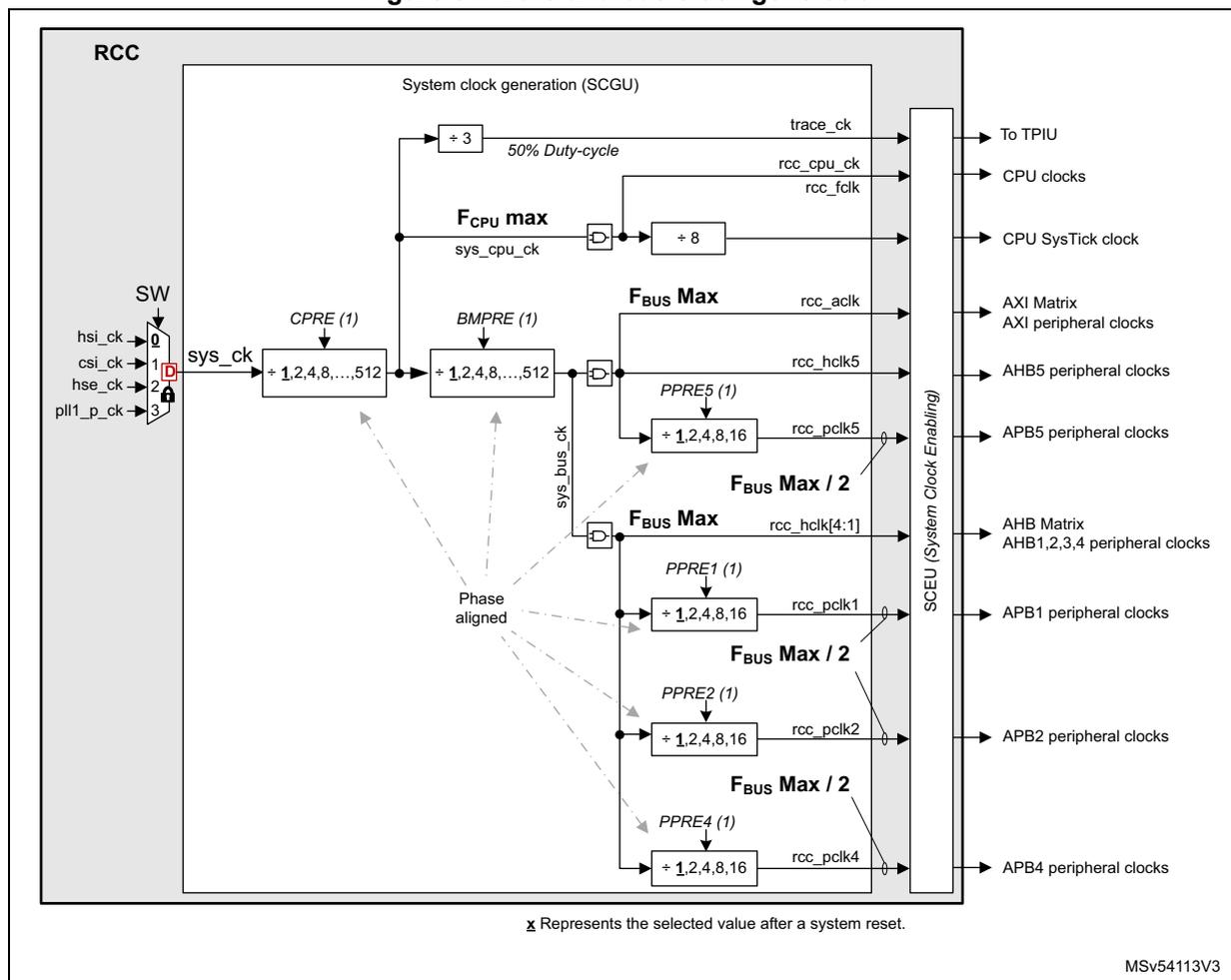

System clock generation

Figure 51 shows a simplified view of the clock distribution for the CPU and busses. All the dividers shown in the block diagram can be changed on-the-fly without generating timing violations. This feature is a very simple solution to adapt the busses frequencies to the application needs, thus optimizing the power consumption.

The CPRE divider can be used to adjust the CPU clock. However this also impacts the clock frequency of all bus matrix. CPRE is controlled via RCC_CDCFGR register.

In the same way, BMPRE divider can be used to adjust the clock for the bus matrix (AHB and AXI), but this also impacts the clock frequency of APB busses. BMPRE is controlled via RCC_BMCFGR register.

Most of the prescalers are controlled via RCC_CDCFGR and RCC_SRDCFGR registers.

Figure 51. Core and bus clock generation

The diagram illustrates the clock generation and distribution within the RCC (Reset and Clock Control) block. On the left, the system clock ( sys_ck ) is selected from four sources via a multiplexer (SW): hsi_ck (0), csi_ck (1), hse_ck (2), and pll1_p_ck (3). The sys_ck signal is distributed to several components:

- A ÷ 3 divider generates the trace_ck clock (50% Duty-cycle) for the TPIU.

- A divider labeled FCPU max generates the sys_cpu_ck clock. This clock is further divided by ÷ 8 to produce rcc_folk (CPU SysTick clock) and rcc_cpu_ck (CPU clocks).

- A divider labeled CPRE (1) with options + 1,2,4,8,...,512 generates the sys_bus_ck clock.

- A divider labeled BMPRE (1) with options + 1,2,4,8,...,512 also generates the sys_bus_ck clock.

The sys_bus_ck clock is distributed to various peripheral clock generators:

- A divider labeled FBUS Max generates rcc_aclk (AXI Matrix AXI peripheral clocks).

- A divider labeled PPRE5 (1) with options + 1,2,4,8,16 generates rcc_hclk5 (AHB5 peripheral clocks).

- A divider labeled FBUS Max / 2 generates rcc_hclk[4:1] (AHB Matrix AHB1,2,3,4 peripheral clocks).

- Four dividers labeled PPRE1 (1) , PPRE2 (1) , PPRE3 (1) , and PPRE4 (1) with options + 1,2,4,8,16 generate rcc_pclk1 (APB1 peripheral clocks), rcc_pclk2 (APB2 peripheral clocks), rcc_pclk3 (APB3 peripheral clocks), and rcc_pclk4 (APB4 peripheral clocks) respectively.

All dividers are Phase aligned to the sys_ck clock. A vertical block labeled SCEU (System Clock Enabling) controls the output of the various clock signals. A note at the bottom indicates that x represents the selected value after a system reset. The document code MSV54113V3 is shown in the bottom right corner.

1. Dividers values can be changed on-the-fly. All dividers provide have 50% duty-cycles.

Note that the application must respect the maximum allowed frequencies: F CPU Max and F BUS Max . F BUS represents the maximum allowed frequency for the AHB and AXI busses. Refer to the product datasheet for maximum values.

Note as well that the trace clock ( trace_ck ) is generated from sys_cpu_ck clock, divided by 3. For additional information refer to Section : Clock distribution for Debug and Trace .

7.5.7 Clock protection

The RCC does not allow to disable the system clock ( sys_ck ). Several protections are implemented in order to prevent actions disabling accidentally the system clock.

In addition, protection bits are available in order to prevent accidental disabling of FMC and XSPI block activities.

The protections consist on ignoring the invalid write operations. It is recommended to read back registers having protection to insure that the clock configuration expected by the software is accepted by the RCC.

The table hereafter shows the protections handled by the RCC.

Table 62. Clock protection summary

| Protected fields | Conditions checked by the RCC |

|---|---|

| SW[2:0] | Changing SW value is allowed only if the targetted clock is enabled and ready. |

| PLLSRC[1:0] | Changing PLLSRC value is allowed if: - The targetted clock is enabled and ready, and, - All PLL disabled |

| HSEON, HSION or CSION | Changing these fields is allowed if: - The oscillator is not used directly or indirectly (via PLL1) as system clock, and - FMCCKP = XSPICKP = 0. |

| DIVMx[5:0], PLLxRGE[1:0], PLLxVCOSEL, DIVN[8:0] | Changing these fields is allowed only if the corresponding PLL is disabled (PLLxON=0) |

| DIVP[6:0], DIVQ[6:0], DIVR[6:0], DIVS[2:0], DIVT[2:0] | Changing these fields is allowed only if the corresponding DIVyEN bit is equal to 0 (y = P, Q, R, S or T) |

| PLL1ON | Changing this field is allowed if: - SW switch is not selecting the PLL1, and - FMCCKP = 0. |

| PLL1PEN | Disabling the DIVP output of PLL1 is allowed if the SW switch is not selecting PLL1 |

| PLL2ON | Changing this field is allowed only if FMCCKP = XSPICKP = 0. |

| PLL2SEN, PLL2TEN, XSPI1EN XSPI2EN, XSPI1LPEN XSPI2LPEN, XSPI1RST XSPI2RST | Changing these fields is allowed only if XSPICKP = 0. |

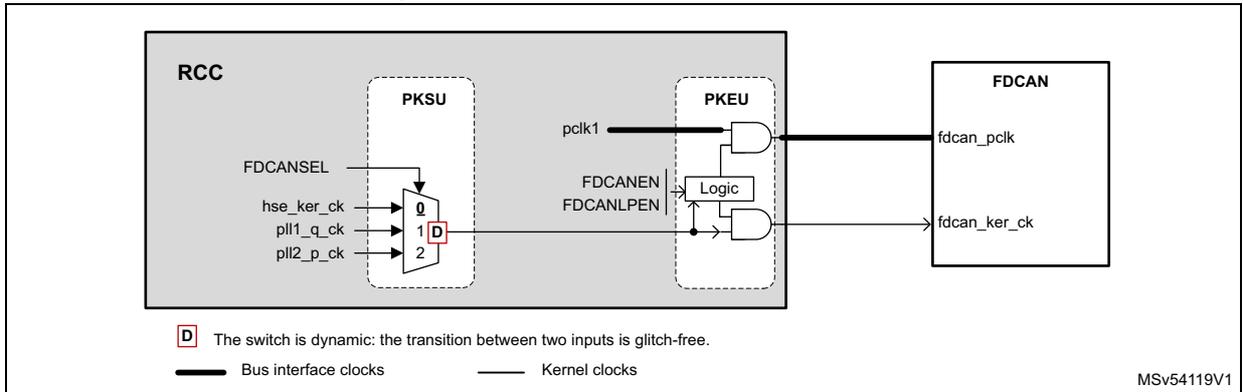

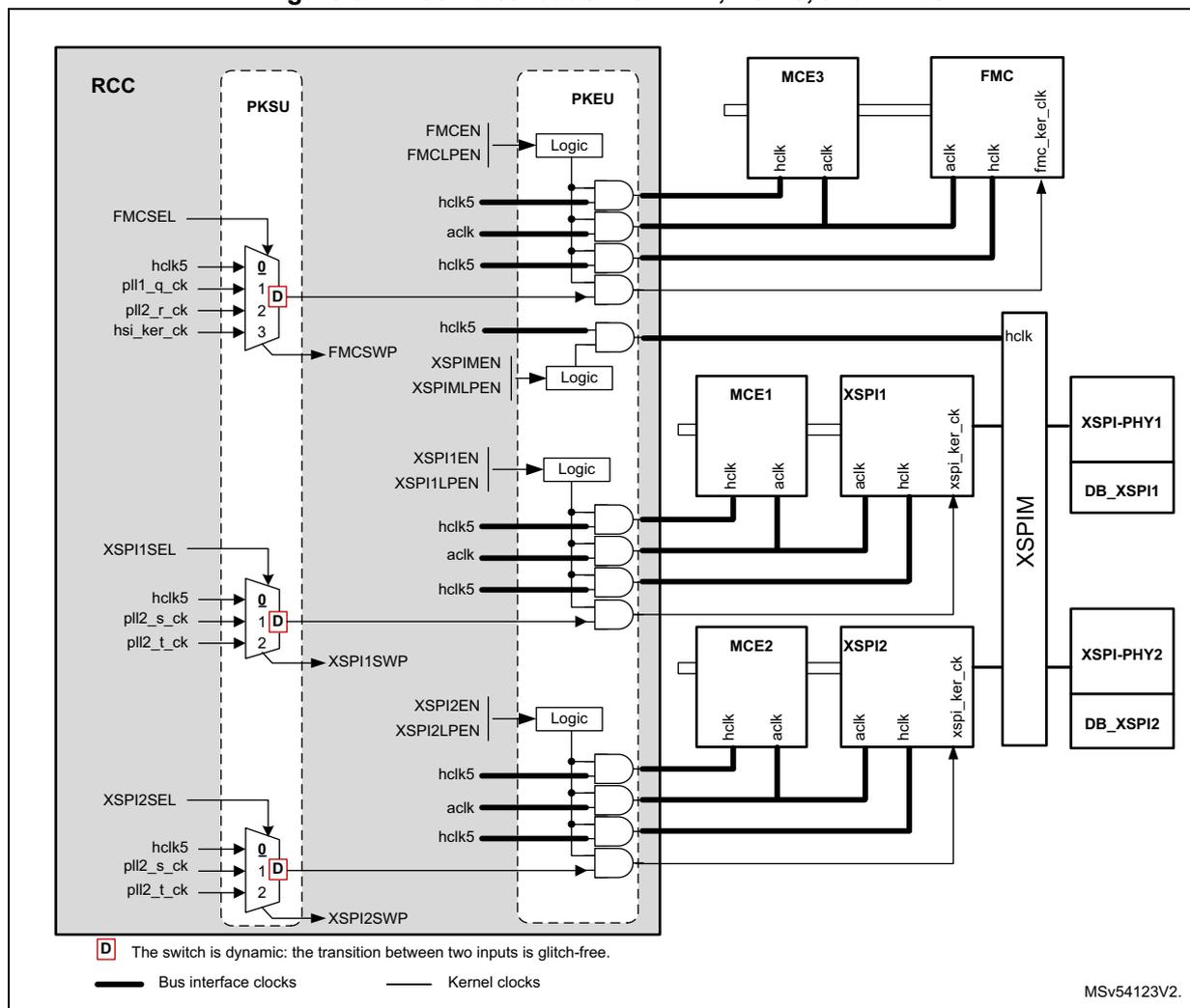

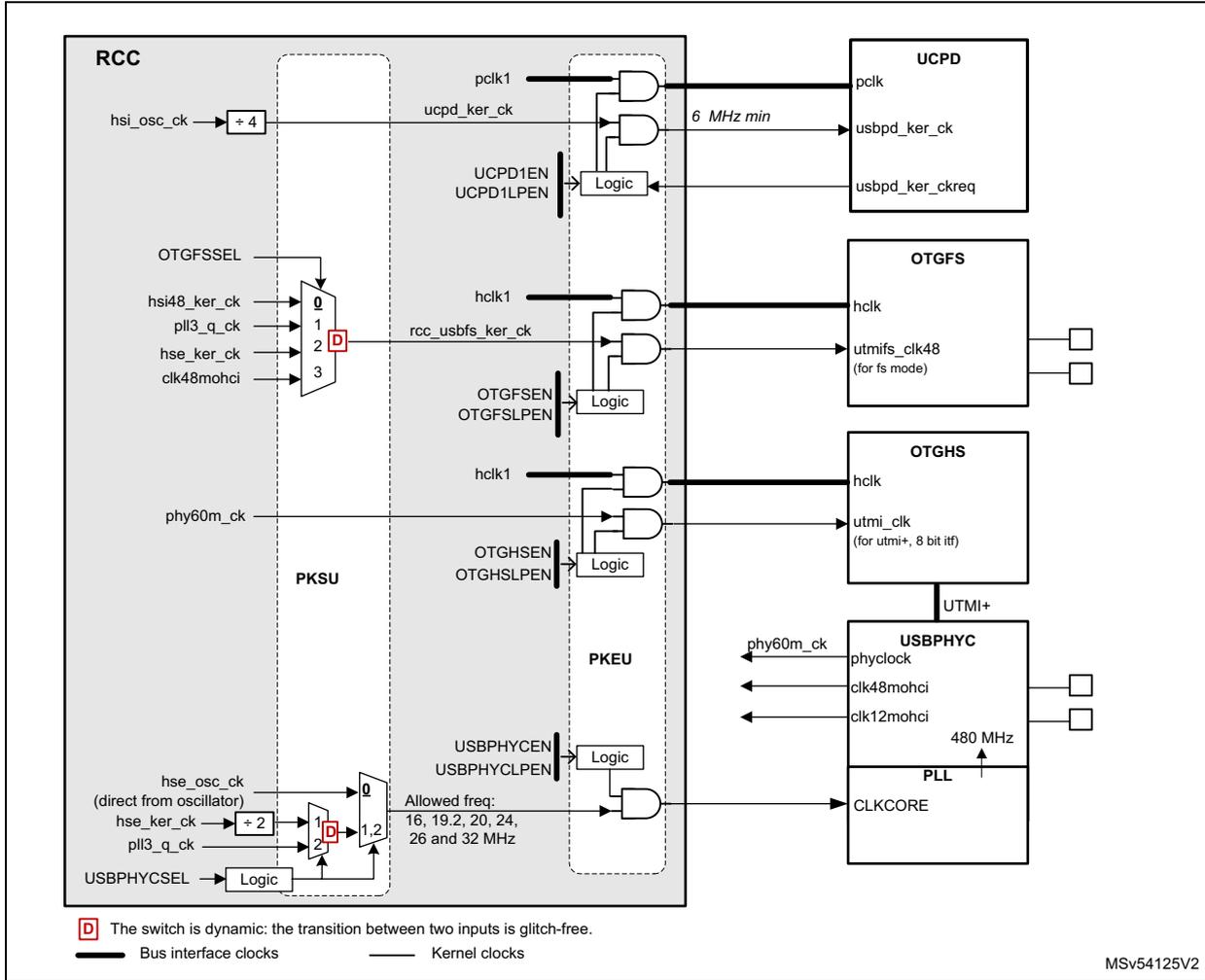

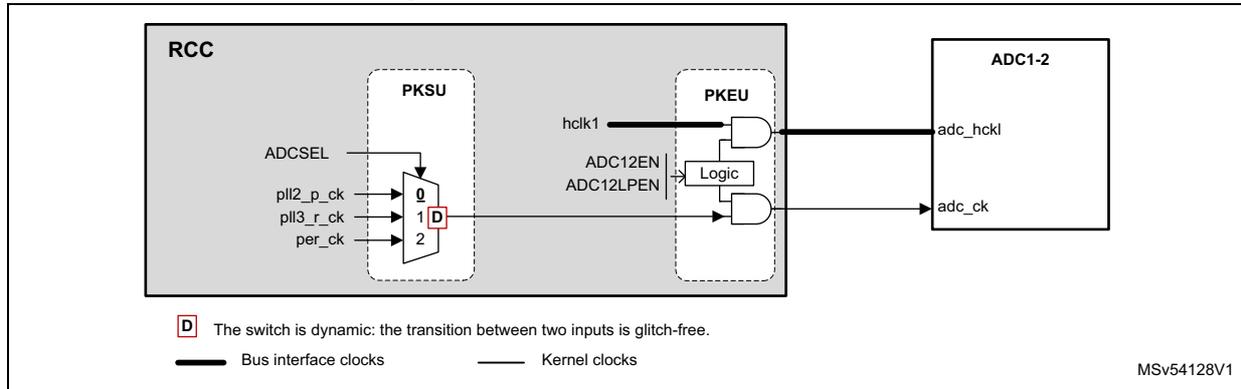

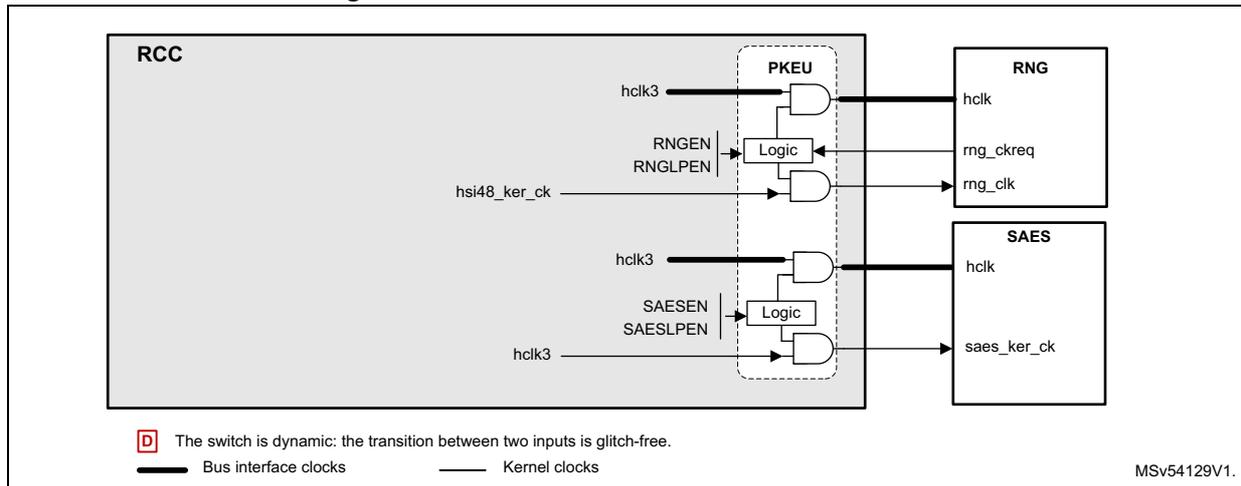

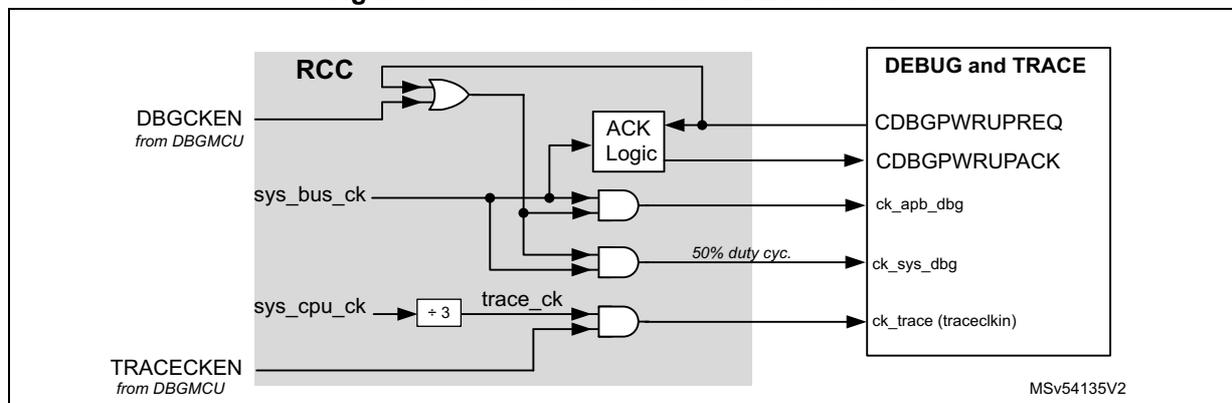

| PLL1QEN, PLL2REN, FMCEN, FMCLPEN, FMCRST | Changing these fields is allowed only if FMCCKP = 0. |