31. Inter-processor communication controller (IPCC)

31.1 Introduction

The inter-processor communication controller (IPCC) is used for communicating data between two processors.

The IPCC block provides a nonblocking signaling mechanism to post and retrieve communication data in an atomic way. It provides the signaling for twelve channels:

- • Six channels in the direction from processor 1 to processor 2

- • Six channels in the opposite direction

It is then possible to have two different communication types in each direction.

The IPCC communication data must be located in a common memory, which is not part of the IPCC block.

31.2 IPCC main features

- • Status signaling for the twelve channels

- – Channel occupied/free flag, also used as lock

- • Two interrupt lines per processor

- – One for RX channel occupied (communication data posted by sending processor)

- – One for TX channel free (communication data retrieved by receiving processor)

- • Interrupt masking per channel

- – Channel occupied mask

- – Channel free mask

- • Two channel operation modes

- – Simplex (each channel has its own communication data memory location)

- – Half duplex (a single channel associated with a bidirectional communication data information memory location)

31.3 IPCC functional description

The IPCC communication data are located in a common memory, which is not part of the IPCC block. The address location of the communication data must be known or located in a known common area that, as already stated, is not part of the IPCC block.

For each communication, the IPCC block provides a channel status flag CHnF.

- • When 0, the channel status flag CHnF indicates that the associated IPCC channel is free (the receiving processor has retrieved communication data), and can be accessed by the sending processor.

- • When 1, the channel status flag CHnF indicates that the associated IPCC channel is occupied (the sending processor has posted communication data) and can be accessed by the receiving processor.

The channel operation mode must be known to both processors. A common parameter can be used to indicate the channel transfer mode and must also be located in a known common area. This parameter is not available from the IPCC.

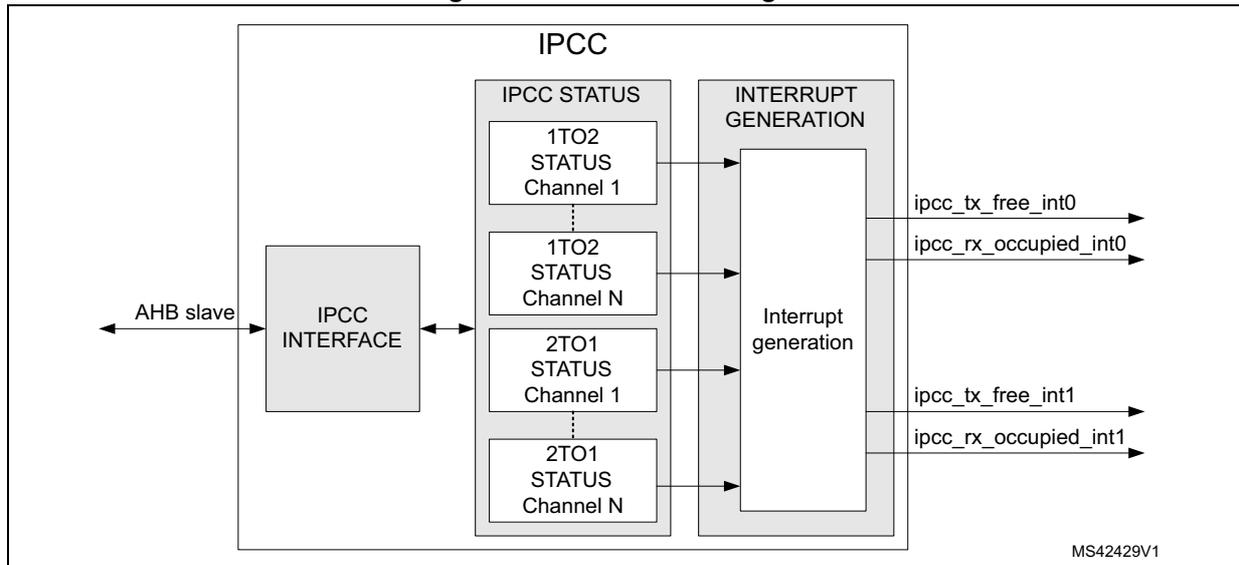

31.3.1 IPCC block diagram

The IPCC (see Figure 303) consists of the following subblocks:

- • Status block, containing the channel status

- • IPCC interface block, providing AHB access to the channel status registers

- • Interrupt interface block, providing control for the interrupts

Figure 303. IPCC block diagram

Table 198. IPCC interface signals

| Signal | Description | |

|---|---|---|

| Name | Type | |

| AHB slave | I/O | AHB register access bus |

| ipcc_tx_free_int1 | O | TX free interrupt to processor 1 |

| ipcc_rx_occupied_int1 | O | RX occupied interrupt to processor 1 |

| ipcc_tx_free_int2 | O | TX free interrupt to processor 2 |

| ipcc_rx_occupied_int2 | O | RX occupied interrupt to processor 2 |

31.3.2 IPCC Simplex channel mode

In Simplex channel mode, a dedicated memory location (used to transfer data in a single direction) is assigned to the communication data. The associated channel N control bits (see Table 199) are used to manage the transfer from the sending to the receiving processor.

Table 199. Bits used for the communication

| Processor | A | B |

|---|---|---|

| SEND A = 1 RECEIVE B = 2 | IPCC_C1CR.TXFIE IPCC_C1MR.CHnFM IPCC_C1SCR.CHnS IPCC_C1TOC2SR.CHnF | IPCC_C2CR.RXOIE IPCC_C2MR.CHnOM IPCC_C2SCR.CHnC |

| SEND A = 2 RECEIVE B = 1 | IPCC_C2CR.TXFIE IPCC_C2MR.CHnFM IPCC_C2SCR.CHnS IPCC_C2TOC1SR.CHnF | IPCC_C1CR.RXOIE IPCC_C1MR.CHnOM IPCC_C1SCR.CHnC |

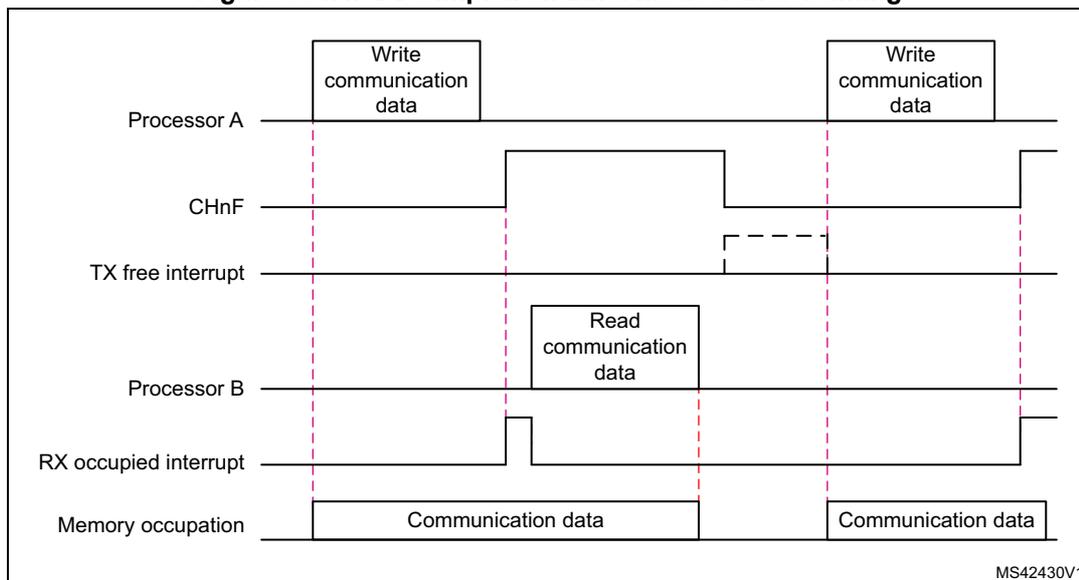

Once the sending processor has posted the communication data in the memory, it sets the channel status flag CHnF to occupied with CHnS.

Once the receiving processor has retrieved the communication data from the memory, it clears the channel status flag CHnF back to free with CHnC.

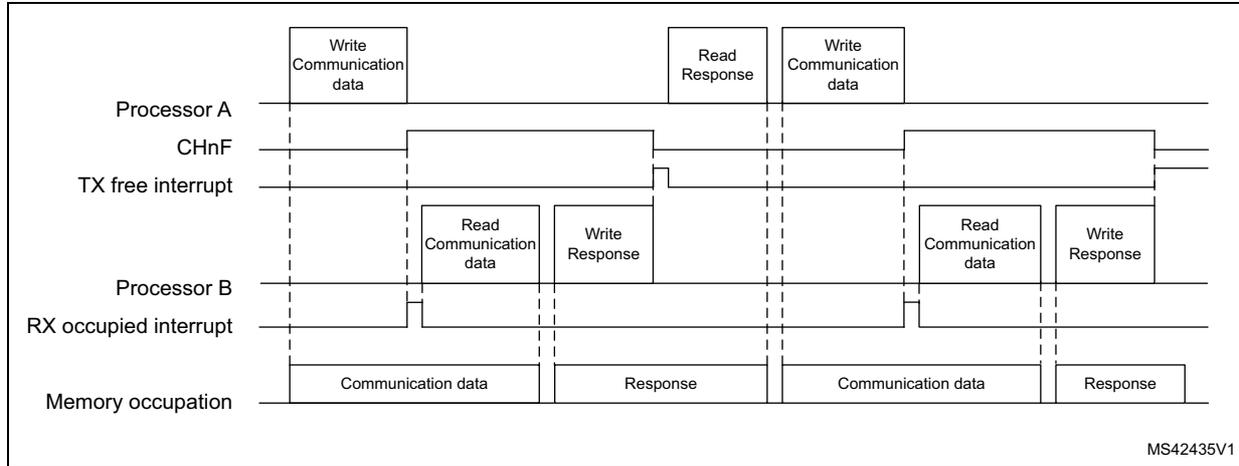

Figure 304. IPCC Simplex channel mode transfer timing

The timing diagram illustrates the interaction between Processor A and Processor B for a simplex channel mode transfer. The sequence of events is as follows:

- Processor A: Writes communication data to memory.

- CHnF: The channel status flag is set to occupied (CHnS).

- TX free interrupt: An interrupt is generated on Processor A.

- Processor B: Detects the RX occupied interrupt and reads the communication data from memory.

- CHnF: The channel status flag is cleared to free (CHnC).

- Memory occupation: The communication data is present in memory during the transfer.

The diagram shows the following signals and their states over time:

- Processor A: Shows two instances of "Write communication data".

- CHnF: Shows a pulse indicating the flag is set to occupied when data is written and cleared to free when data is read.

- TX free interrupt: Shows a pulse when the CHnF flag is set.

- Processor B: Shows a "Read communication data" block.

- RX occupied interrupt: Shows a pulse when the CHnF flag is set, indicating data is ready for processing.

- Memory occupation: Shows the communication data being written to and read from memory.

MS42430V1

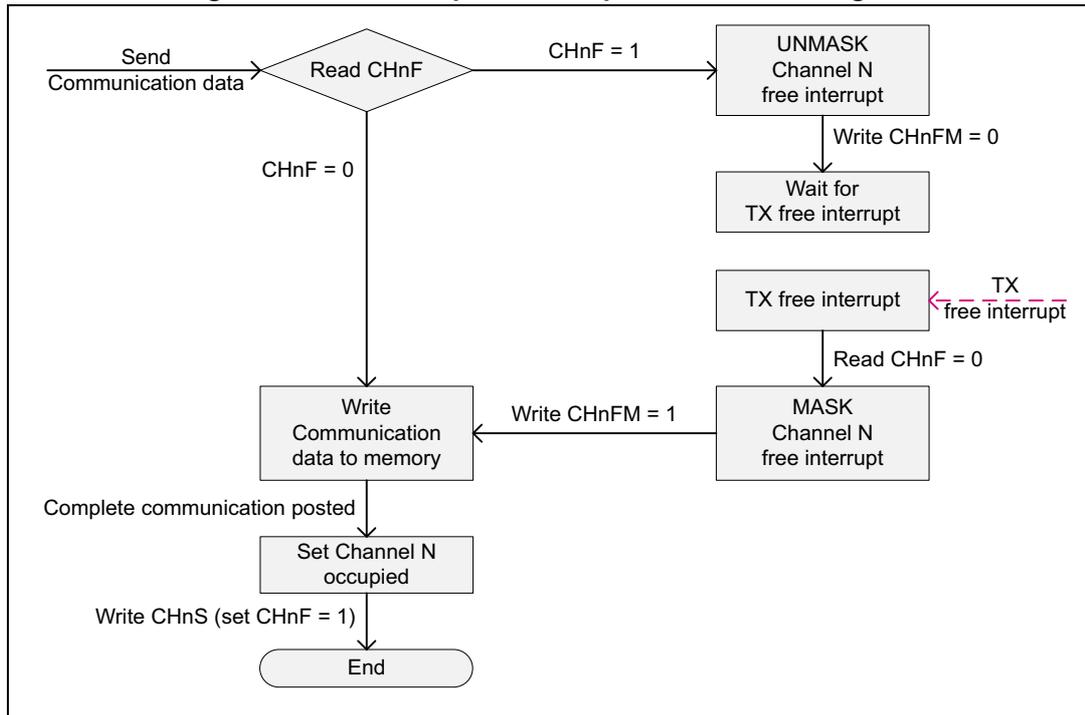

Figure 305. IPCC Simplex - Send procedure state diagram

graph TD; Start(( )) -- "Send Communication data" --> ReadCHnF{Read CHnF}; ReadCHnF -- "CHnF = 0" --> WriteData[Write Communication data to memory]; ReadCHnF -- "CHnF = 1" --> UNMASK[UNMASK Channel N free interrupt]; UNMASK -- "Write CHnFM = 0" --> WaitTX[Wait for TX free interrupt]; WaitTX --> TXFree[TX free interrupt]; TXFree -- "Read CHnF = 0" --> MASK[MASK Channel N free interrupt]; MASK -- "Write CHnFM = 1" --> WriteData; WriteData -- "Complete communication posted" --> SetOccupied[Set Channel N occupied]; SetOccupied -- "Write CHnS (set CHnF = 1)" --> End([End]);The state diagram illustrates the send procedure for the IPCC Simplex. It begins with an entry point labeled 'Send Communication data' leading to a decision diamond 'Read CHnF'. If 'CHnF = 0', the flow proceeds to 'Write Communication data to memory'. If 'CHnF = 1', the flow proceeds to 'UNMASK Channel N free interrupt', followed by 'Write CHnFM = 0', 'Wait for TX free interrupt', and 'TX free interrupt'. From 'TX free interrupt', the flow proceeds to 'Read CHnF = 0', which leads to 'MASK Channel N free interrupt', then 'Write CHnFM = 1', and finally 'Write Communication data to memory'. From 'Write Communication data to memory', the flow proceeds to 'Complete communication posted', then 'Set Channel N occupied', then 'Write CHnS (set CHnF = 1)', and finally 'End'.

To send communication data:

- • The sending processor checks the channel status flag CHnF:

- – When CHnF = 0, the channel is free (the last communication data is retrieved by the receiving processor), and the new communication data can be written.

- – When CHnF = 1, the channel is occupied (the last communication data is not retrieved by the receiving processor), and the sending processor unmask the channel free interrupt (CHnFM = 0).

- – On a TX free interrupt, the sending processor checks which channel became free and masks the channel free interrupt (CHnFM = 1). Then the new communication can take place.

- • Once the complete communication data is posted, the channel status is set to occupied with CHnS. This gives memory access to the receiving processor and generates the RX occupied interrupt.

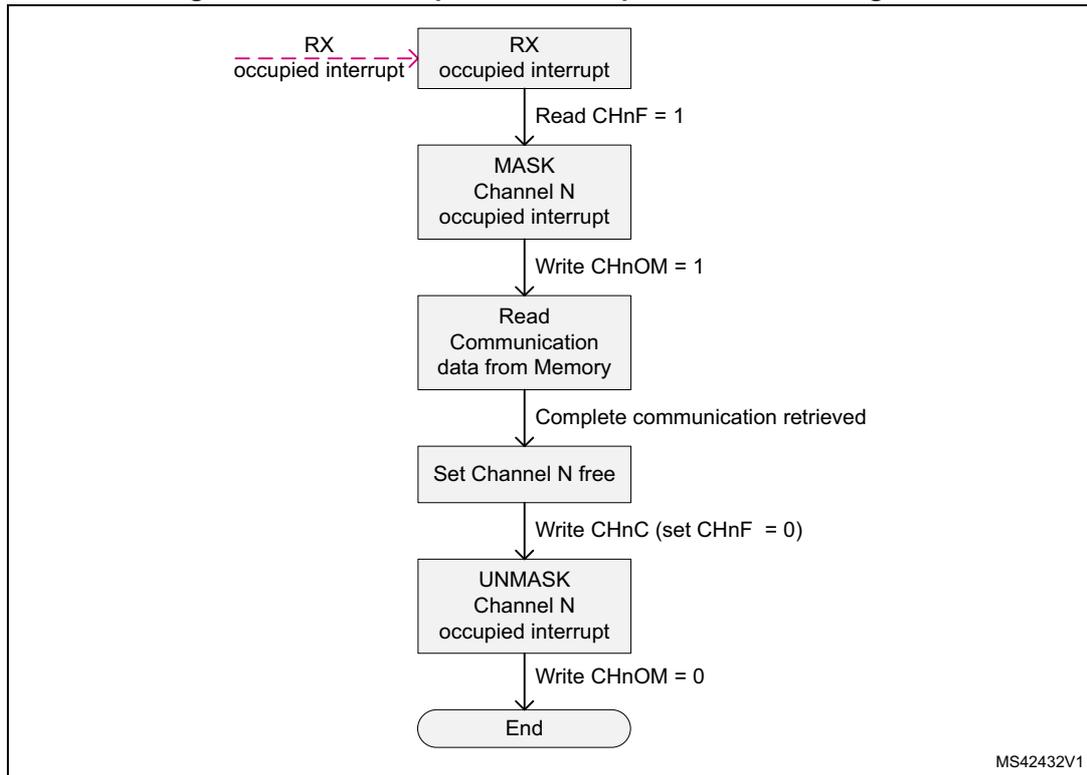

Figure 306. IPCC Simplex - Receive procedure state diagram

stateDiagram-v2

[*] --> RX_occupied_interrupt : RX occupied interrupt

RX_occupied_interrupt --> MASK_Channel_N_occupied_interrupt : Read CHnF = 1

MASK_Channel_N_occupied_interrupt --> Read_Communication_data_from_Memory : Write CHnOM = 1

Read_Communication_data_from_Memory --> Set_Channel_N_free : Complete communication retrieved

Set_Channel_N_free --> UNMASK_Channel_N_occupied_interrupt : Write CHnC (set CHnF = 0)

UNMASK_Channel_N_occupied_interrupt --> End : Write CHnOM = 0

End --> [*]

MS42432V1

To receive a communication, the channel occupied interrupt is unmasked ( \( CHnOM = 0 \) ):

- • On an RX occupied interrupt, the receiving processor checks which channel became occupied, masks the associated channel occupied interrupt ( \( CHnOM \) ) and reads the communication data from memory.

- • Once the complete communication data is retrieved, the channel status is cleared to free with \( CHnC \) . This gives memory access back to the sending processor and may generate the TX free interrupt.

- • Once the channel status is cleared, the channel occupied interrupt is unmasked ( \( CHnOM = 0 \) ).

31.3.3 IPCC Half-duplex channel mode

The Half-duplex channel mode is used when one processor sends a communication and the other processor sends a response to each communication (ping-pong).

In Half-duplex channel mode, a single dedicated memory location is assigned to communication data and response, and is used to transfer data in both directions. The sending processor channel status flag \( CHnF \) is assigned to the channel and used by both processors (see Table 199 ).

Once the processor A posts communication data into memory, it sets the processor A channel status flag \( CHnF \) to occupied with \( CHnS \) (giving memory access to processor B).

Once the processor B retrieves communication data from memory, it does not change the channel status flags. The memory access is kept by processor B for the response.

Once the processor B posts the response into memory, it clears the channel status flag \( CHnF \) to free with \( CHnC \) (giving memory access back to processor A).

Once the processor A retrieves the response from the memory, it does not change the channel status flags. The memory location access is kept by processor A for the next communication data.

Figure 307. IPCC Half-duplex channel mode transfer timing

The diagram illustrates the timing for a half-duplex channel mode transfer. It shows the sequence of events between Processor A, Processor B, and Memory. Processor A writes communication data to memory, then later reads the response. Processor B reads the communication data and writes the response. Interrupts (TX free and RX occupied) and channel flags (CHnF) are shown toggling at specific points in the sequence. Memory occupation is indicated for the communication data and response periods. Reference MS42435V1 is noted in the bottom right.

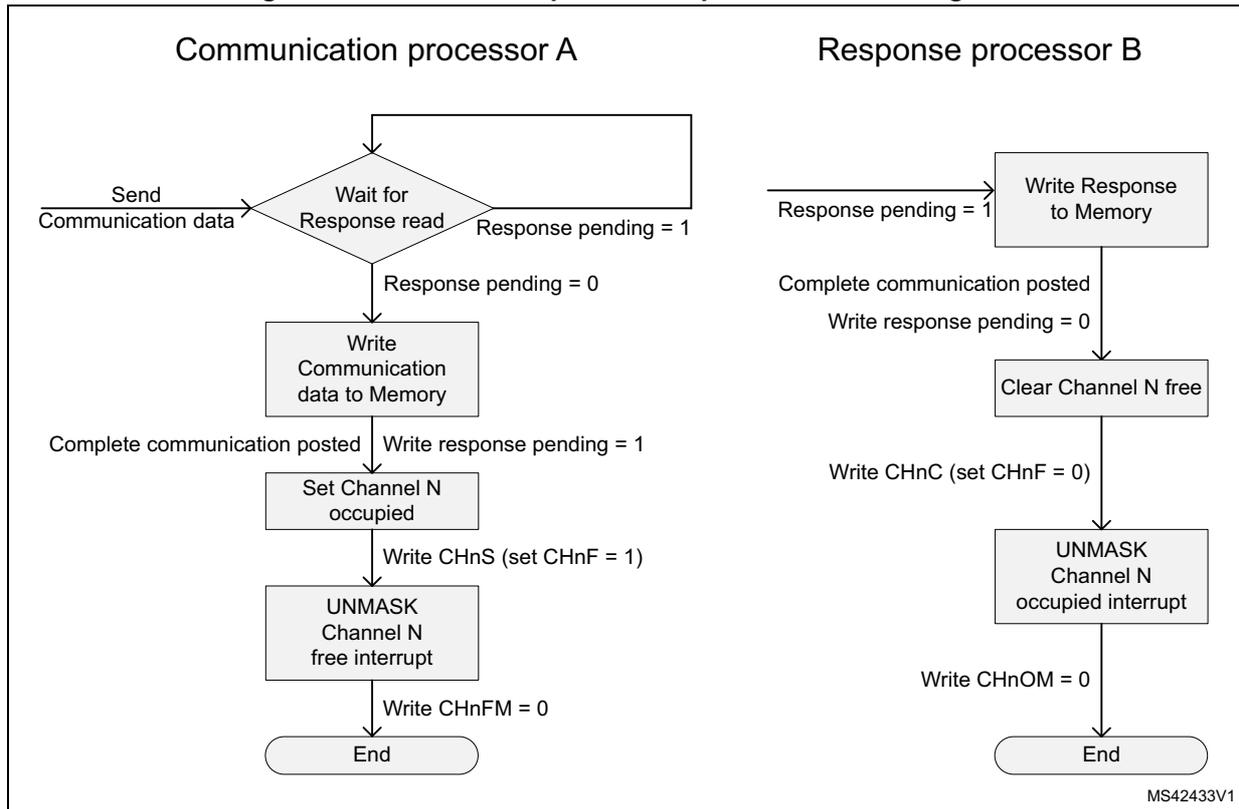

Figure 308. IPCC Half-duplex - Send procedure state diagram

This state diagram details the 'Send procedure' for the IPCC Half-duplex mode, split into two columns: 'Communication processor A' and 'Response processor B'. Processor A's flow starts with 'Send Communication data', leading to a decision 'Wait for Response read'. If 'Response pending = 1', it loops back. If 'Response pending = 0', it proceeds to 'Write Communication data to Memory', then 'Set Channel N occupied', 'UNMASK Channel N free interrupt', and finally 'End' after 'Write CHnFM = 0'. Processor B's flow starts with 'Response pending = 1', leading to 'Write Response to Memory', then 'Clear Channel N free', 'UNMASK Channel N occupied interrupt', and finally 'End' after 'Write CHnOM = 0'. Intermediate states like 'Complete communication posted' and 'Write response pending = 1' are shown between the main steps. Reference MS42433V1 is noted in the bottom right.

To send communication data:

- • The sending processor waits for its response pending software variable to get 0.

- – Once the response pending software variable is 0 the communication data is posted.

- • Once the complete communication data has been posted, the channel status flag CHnF is set to occupied with CHnS, and the response pending software variable is set to 1 (this gives memory access and generates the RX occupied interrupt to the receiving processor).

- • Once the channel status flag CHnF is set, the channel free interrupt is unmasked (CHnFM = 0).

To send a response:

- • The receiving processor waits for its response pending software variable to get 1.

- – Once the response pending software variable is 1, the response is posted.

- • Once the complete response is posted, the channel status flag CHnF is cleared to free with CHnC, and the response pending software variable is set to 0 (this gives memory access and generates the TX free interrupt to the sending processor).

- • Once the channel status flag CHnF is cleared, the channel occupied interrupt is unmasked (CHnOM = 0).

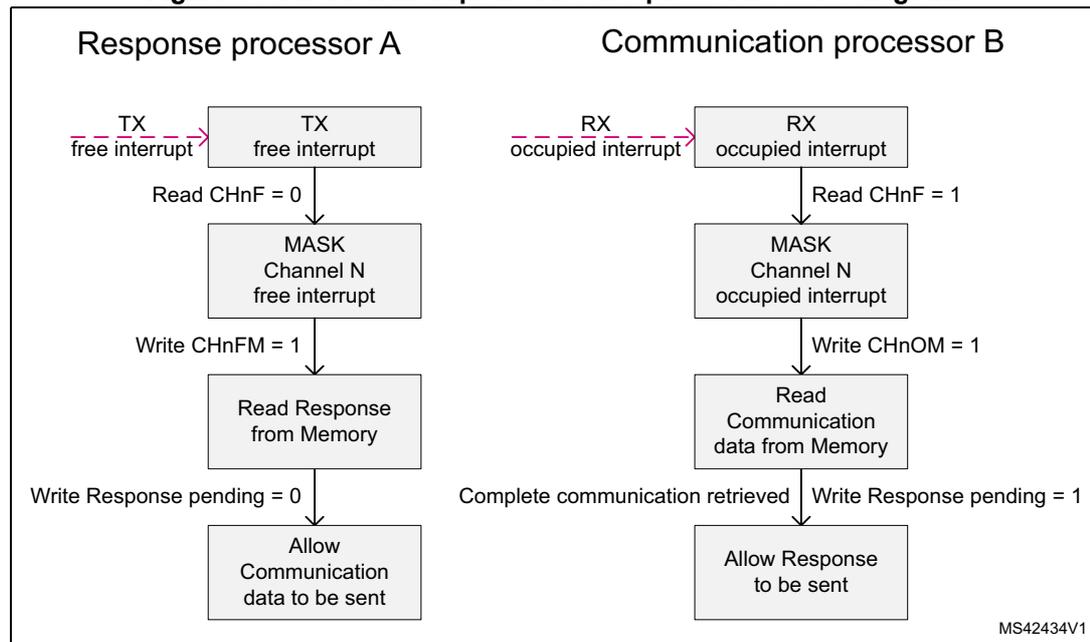

Figure 309. IPCC Half-duplex - Receive procedure state diagram

stateDiagram-v2

state "Response processor A" as A

state "Communication processor B" as B

state A {

[*] --> TX_free_interrupt_A: TX free interrupt

TX_free_interrupt_A --> Read_CHnF_0_A: Read CHnF = 0

Read_CHnF_0_A --> MASK_Channel_N_free_interrupt_A: MASK Channel N free interrupt

MASK_Channel_N_free_interrupt_A --> Write_CHnFM_1_A: Write CHnFM = 1

Write_CHnFM_1_A --> Read_Response_from_Memory_A: Read Response from Memory

Read_Response_from_Memory_A --> Write_Response_pending_0_A: Write Response pending = 0

Write_Response_pending_0_A --> Allow_Communication_data_to_be_sent_A: Allow Communication data to be sent

}

state B {

[*] --> RX_occupied_interrupt_B: RX occupied interrupt

RX_occupied_interrupt_B --> Read_CHnF_1_B: Read CHnF = 1

Read_CHnF_1_B --> MASK_Channel_N_occupied_interrupt_B: MASK Channel N occupied interrupt

MASK_Channel_N_occupied_interrupt_B --> Write_CHnOM_1_B: Write CHnOM = 1

Write_CHnOM_1_B --> Read_Communication_data_from_Memory_B: Read Communication data from Memory

Read_Communication_data_from_Memory_B --> Write_Response_pending_1_B: Write Response pending = 1

Write_Response_pending_1_B --> Allow_Response_to_be_sent_B: Allow Response to be sent

}

Allow_Communication_data_to_be_sent_A --> Read_Communication_data_from_Memory_B: Complete communication retrieved

Allow_Response_to_be_sent_B --> Read_Response_from_Memory_A: Complete communication retrieved

To receive communication data the channel occupied interrupt is unmasked (CHnOM = 0):

- • On an RX occupied interrupt, the receiving processor checks which channel became occupied, masks the associated channel occupied interrupt (CHnOM) and reads the communication data from the memory.

- • Once the complete communication data is retrieved, the response pending software variable is set. The channel status is not changed, access to the memory is kept to post the subsequent response.

To receive the response the channel free interrupt is unmasked (CHnFM = 0):

- • On a TX free interrupt, the sending processor checks which channel became free, masks the associated channel free interrupt (CHnFM) and reads the response from the memory.

- • Once the complete response is retrieved, the response pending software variable is cleared. The channel status is not changed, access to the memory is kept to post the subsequent communication data.

31.3.4 IPCC interrupts

There are four interrupt lines :

- • Two RX channel occupied interrupts, one for each processor:

- – Interrupt enable RXOIE per processor

- – Individual mask CHnOM per channel

- • Two TX channel free interrupts, one for each processor

- – Interrupt enable TXFIE per processor

- – Individual mask CHnFM per channel

The RX occupied interrupt is used by the receiving processor and indicates when an unmasked channel status indicates occupied (CHnF = 1).

The TX free interrupt is used by the sending processor, and indicates when an unmasked channel status indicates free (CHnF = 0).

A secure channel only generates a secure interrupt, and only in the case when the channel is secure unmasked and global secure enabled.

A nonsecure channel only generates a nonsecure interrupt, and only in the case when the channel is nonsecure unmasked and global nonsecure enabled.

31.4 IPCC registers

The peripheral registers must be accessed by words (32-bit). Byte (8-bit) and half-word (16-bit) accesses are not permitted and do not generate a bus error.

31.4.1 IPCC processor 1 control register (IPCC_C1CR)

Address offset: 0x000

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TXFIE |

| rw | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | RXOIE |

| rw |

Bits 31:17 Reserved, must be kept at reset value.

Bit 16 TXFIE : Processor 1 transmit channel free interrupt enable

Associated with IPCC_C1TOC2SR.

1: Enable an unmasked processor 1 transmit channel free to generate a TX free interrupt.

0: Processor 1 TX free interrupt disabled

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 RXOIE : Processor 1 receive channel occupied interrupt enable

Associated with IPCC_C2TOC1SR.

1: Enable an unmasked processor 1 receive channel occupied to generate an RX occupied interrupt.

0: Processor 1 RX occupied interrupt disabled

31.4.2 IPCC processor 1 mask register (IPCC_C1MR)

Address offset: 0x004

Reset value: 0xFFFF FFFF

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6 FM | CH5 FM | CH4 FM | CH3 FM | CH2 FM | CH1 FM |

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6 OM | CH5 OM | CH4 OM | CH3 OM | CH2 OM | CH1 OM |

| rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:16 CHnFM : Processor 1 transmit channel n status set, (n = 6 to 1).

Associated with IPCC_C1TOC2SR.CHnF

1: Transmit channel n free interrupt masked.

0: Transmit channel n free interrupt not masked.

Bits 15:6 Reserved, must be kept at reset value.

Bits 5:0 CHnOM : Processor 1 receive channel n status clear (n = 6 to 1).

Associated with IPCC_C2TOC1SR.CHnF

1: Receive channel n occupied interrupt masked.

0: Receive channel n occupied interrupt not masked.

31.4.3 IPCC processor 1 status set clear register (IPCC_C1SCR)

Address offset: 0x008

Reset value: 0x0000 0000

Reading this register always returns 0x0000 0000.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6S | CH5S | CH4S | CH3S | CH2S | CH1S |

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6C | CH5C | CH4C | CH3C | CH2C | CH1C |

| rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:16 CHnS : Processor 1 transmit channel n status set (n = 6 to 1).

Associated with IPCC_C1TOC2SR.CHnF

1: Processor 1 transmit channel n status bit set.

0: No action.

Bits 15:6 Reserved, must be kept at reset value.

Bits 5:0 CHnC : Processor 1 receive channel n status clear (n = 6 to 1).

Associated with IPCC_C2TOC1SR.CHnF

1: Processor 1 receive channel n status bit clear.

0: No action.

31.4.4 IPCC processor 1 to processor 2 status register (IPCC_C1TOC2SR)

Address offset: 0x00C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6F | CH5F | CH4F | CH3F | CH2F | CH1F |

| r | r | r | r | r | r |

Bits 31:6 Reserved, must be kept at reset value.

Bits 5:0 CHnF : Processor 1 transmit to processor 2 receive channel n status flag before masking (n = 6 to 1).

1: Channel occupied, data can be read by the receiving processor 2.

Generates a channel RX occupied interrupt to processor 2, when unmasked.

0: Channel free, data can be written by the sending processor 1.

Generates a channel TX free interrupt to processor 1, when unmasked.

31.4.5 IPCC processor 2 control register (IPCC_C2CR)

Address offset: 0x010

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TXFIE |

| nw | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | RXOIE |

| nw |

Bits 31:17 Reserved, must be kept at reset value.

Bit 16 TXFIE : Processor 2 transmit channel free interrupt enable

Associated with IPCC_C2TOC1SR.

1: Enable an unmasked processor 2 transmit channel free to generate a TX free interrupt.

0: Processor 2 TX free interrupt disabled

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 RXOIE : Processor 2 receive channel occupied interrupt enable

Associated with IPCC_C1TOC2SR.

1: Enable an unmasked processor 2 receive channel occupied to generate an RX occupied interrupt.

0: Processor 2 RX occupied interrupt disabled

31.4.6 IPCC processor 2 mask register (IPCC_C2MR)

Address offset: 0x014

Reset value: 0xFFFF FFFF

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6 FM | CH5 FM | CH4 FM | CH3 FM | CH2 FM | CH1 FM |

| rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6 OM | CH5 OM | CH4 OM | CH3 OM | CH2 OM | CH1 OM |

| rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:16 CHnFM : Processor 2 transmit channel n free interrupt mask (n = 6 to 1).

Associated with IPCC_C2TOC1SR.CHnF

1: Transmit channel n free interrupt masked.

0: Transmit channel n free interrupt not masked.

Bits 15:6 Reserved, must be kept at reset value.

Bits 5:0 CHnOM : Processor 2 receive channel n occupied interrupt mask (n = 6 to 1).

Associated with IPCC_C1TOC2SR.CHnF

1: Receive channel n occupied interrupt masked.

0: Receive channel n occupied interrupt not masked.

31.4.7 IPCC processor 2 status set clear register (IPCC_C2SCR)

Address offset: 0x018

Reset value: 0x0000 0000

Reading this register always returns 0x0000 0000.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6S | CH5S | CH4S | CH3S | CH2S | CH1S |

| rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6C | CH5C | CH4C | CH3C | CH2C | CH1C |

| rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:16 CHnS : Processor 2 transmit channel n status set (n = 6 to 1).

Associated with IPCC_C2TOC1SR.CHnF

1: Processor 2 transmit channel n status bit set.

0: No action.

Bits 15:6 Reserved, must be kept at reset value.

Bits 5:0 CHnC : Processor 2 receive channel n status clear (n = 6 to 1).

Associated with IPCC_C1TOC2SR.CHnF

1: Processor 2 receive channel n status bit clear.

0: No action.

31.4.8 IPCC processor 2 to processor 1 status register (IPCC_C2TOC1SR)

Address offset: 0x01C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6F | CH5F | CH4F | CH3F | CH2F | CH1F |

| r | r | r | r | r | r |

Bits 31:6 Reserved, must be kept at reset value.

Bits 5:0 CHnF : Processor 2 transmit to processor 1 receive channel n status flag before masking (n = 6 to 1)

1: Channel occupied, data can be read by the receiving processor 1.

Generates a channel RX occupied interrupt to processor 1, when unmasked.

0: Channel free, data can be written by the sending processor 2.

Generates a channel TX free interrupt to processor 2, when unmasked.

31.4.9 IPCC register map

Table 200. IPCC register map and reset values

| Offset | Register name Reset value | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x0000 | IPCC_C1CR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TXFIE | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | RXOIE |

| Reset value | 0 | 0 | ||||||||||||||||||||||||||||||||

| 0x0004 | IPCC_C1MR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6FM | CH5FM | CH4FM | CH3FM | CH2FM | CH1FM | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6OM | CH5OM | CH4OM | CH3OM | CH2OM | |

| Reset value | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||||||||||||||||||||||

| 0x0008 | IPCC_C1SCR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6S | CH5S | CH4S | CH3S | CH2S | CH1S | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6C | CH5C | CH4C | CH3C | CH2C | ||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||

| 0x000C | IPCC_C1TOC2SR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6F | CH5F | CH4F | CH3F | CH2F | ||

| Reset value | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||||

| 0x0010 | IPCC_C2CR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TXFIE | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | RXOIE | |

| Reset value | 0 | 0 | ||||||||||||||||||||||||||||||||

| 0x0014 | IPCC_C2MR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6FM | CH5FM | CH4FM | CH3FM | CH2FM | CH1FM | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6OM | CH5OM | CH4OM | CH3OM | CH2OM | |

| Reset value | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||||||||||||||||||||||

| 0x0018 | IPCC_C2SCR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6S | CH5S | CH4S | CH3S | CH2S | CH1S | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6C | CH5C | CH4C | CH3C | CH2C | ||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||

| 0x001C | IPCC_C2TOC1SR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CH6F | CH5F | CH4F | CH3F | CH2F | ||

| Reset value | 0 | 0 | 0 | 0 | 0 |

Refer to Section 2.2 on page 55 for the register boundary addresses.