24. Flexible memory controller (FMC)

The flexible memory controller (FMC) includes three memory controllers:

- • The NOR/PSRAM memory controller

- • The NAND memory controller

- • The Synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) controller

24.1 FMC main features

The FMC functional block makes the interface with: synchronous and asynchronous static memories, SDRAM memories, and NAND flash memory. Its main purposes are:

- • to translate AXI transactions into the appropriate external device protocol

- • to meet the access time requirements of the external memory devices

All external memories share the addresses, data and control signals with the controller. Each external device is accessed by means of a unique Chip Select. The FMC performs only one access at a time to an external device.

The main features of the FMC controller are the following:

- • Interface with static-memory mapped devices including:

- – Static random access memory (SRAM)

- – NOR Flash memory/OneNAND Flash memory

- – PSRAM (4 memory banks)

- – NAND Flash memory with ECC hardware to check up to 8 Kbytes of data

- • Interface with synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) memories

- • Burst mode support for faster access to synchronous devices such as NOR Flash memory, PSRAM and SDRAM

- • Programmable continuous clock output for asynchronous and synchronous accesses

- • 8-, 16- or 32-bit wide data bus

- • Independent Chip Select control for each memory bank

- • Independent configuration for each memory bank

- • Write enable and byte lane select outputs for use with PSRAM, SRAM and SDRAM devices

- • External asynchronous wait control

- • Write FIFO with 16 x32-bit depth

The Write FIFO is common to all memory controllers and consists of:

- – a Write Data FIFO which stores the data to be written to the memory

- – a Write Address FIFO which stores the address (up to 28 bits) plus the data size (up to 2 bits). When operating in Burst mode, only the start address is stored except when crossing a page boundary (for PSRAM and SDRAM). In this case, the burst is broken into two FIFO entries.

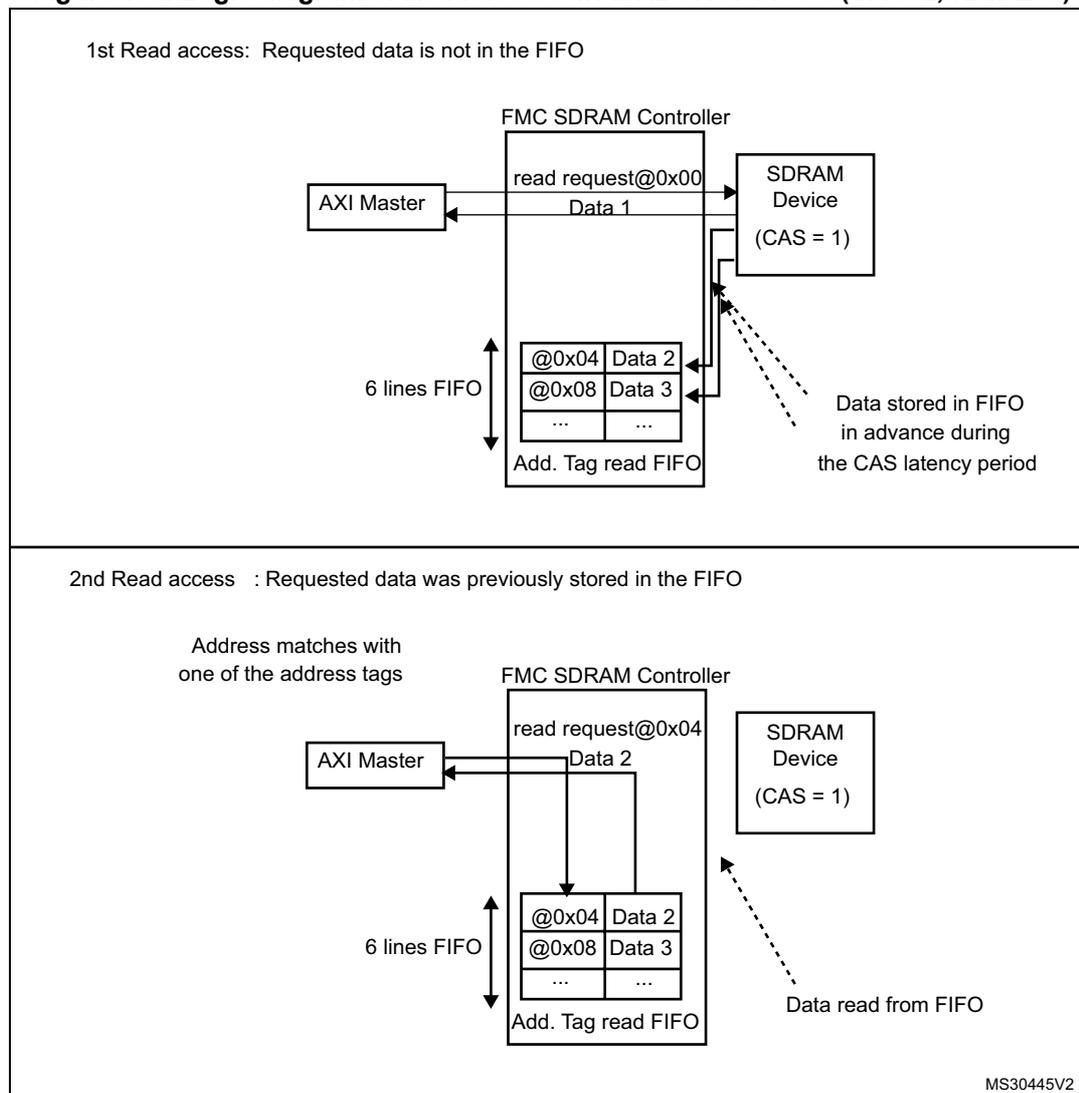

- • Cacheable Read FIFO with 6 x64-bit depth (6 x14-bit address tag) for SDRAM controller.

At startup the FMC pins must be configured by the user application. The FMC I/O pins which are not used by the application can be used for other purposes.

The FMC registers that define the external device type and associated characteristics are set at boot time and do not change until the next reset or power-up. However, only a few bits can be changed on-the-fly:

- • ECCEN and PBKEN bits in the FMC_PCR register

- • IFS, IRS and ILS bits in the FMC_SR register

- • MODE[2:0], CTB1/CTB2, NRFS and MRD bits in the FMC_SDCMR register

- • REIE and CRE bits in the FMC_SDRTR register.

Follow the below sequence to modify parameters while the FMC is enabled:

- 1. First disable the FMC controller to prevent further accesses to any memory controller while the register is modified.

- 2. Update all required configurations.

- 3. Enable the FMC controller again.

When the SDRAM controller is used, if the SDCLK Clock ratio or refresh rate has to be modified after initialization phase, the following procedure must be followed.

- 1. Put the SDRAM device in Self-refresh mode.

- 2. Disable the FMC controller by resetting the FMCEN bit in the FMC_BCR1 register.

- 3. Update the required parameters.

- 4. Enable the FMC controller once all parameters have been updated.

- 5. Then, send the Clock Configuration Enable command to exit Self-fresh mode.

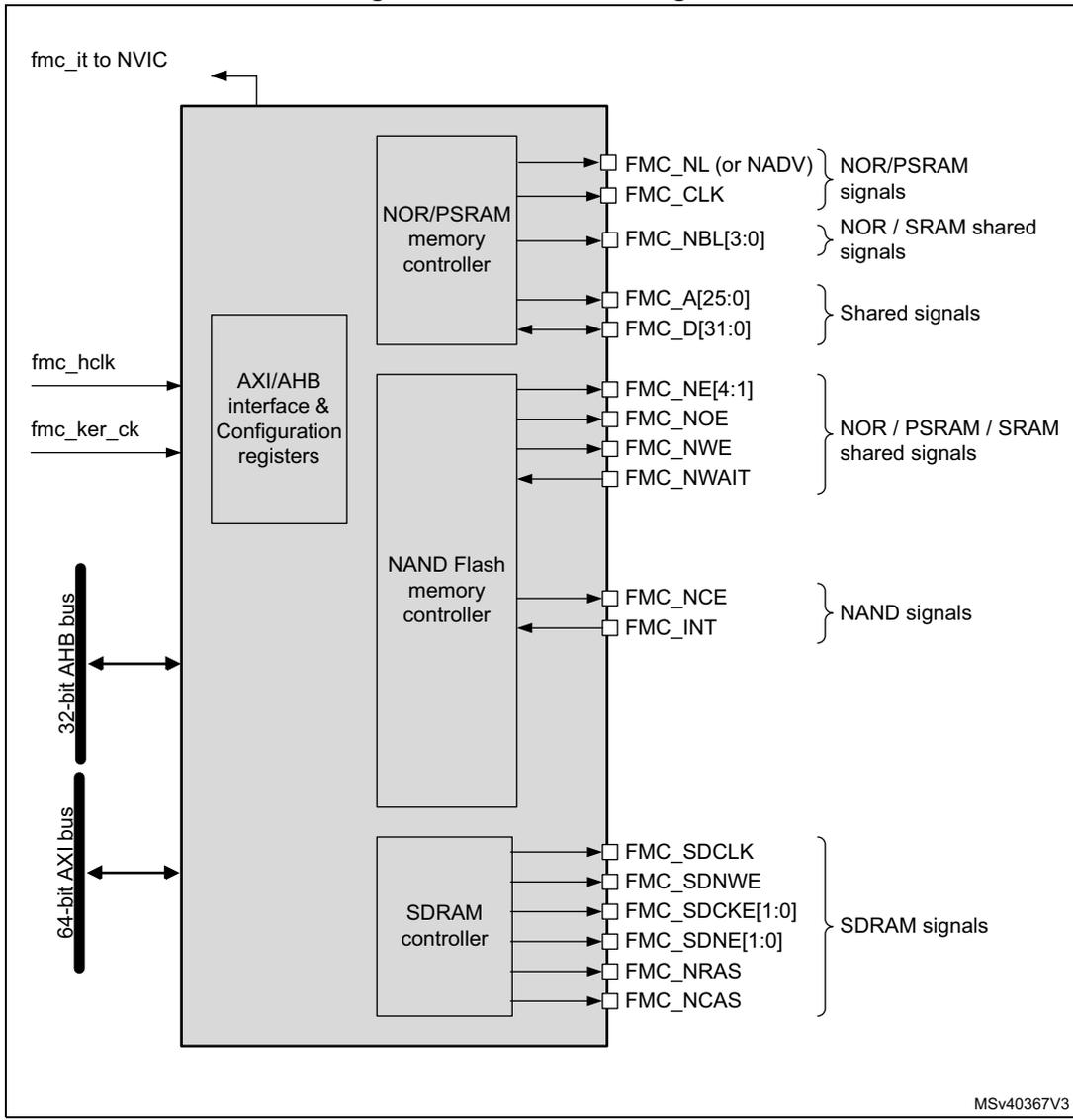

24.2 FMC block diagram

The FMC consists of the following main blocks:

- • The NOR Flash/PSRAM/SRAM controller

- • The NAND controller

- • The SDRAM controller

- • The AXI interface

- • The AHB interface (including the FMC configuration registers)

The block diagram is shown in the figure below.

Figure 112. FMC block diagram

graph TD

subgraph FMC

Registers[AXI/AHB interface & Configuration registers]

NOR_PSRAM[NOR/PSRAM memory controller]

NAND[NAND Flash memory controller]

SDRAM[SDRAM controller]

end

NVIC[NVIC] <-- fmc_it -- FMC

fmc_hclk --> Registers

fmc_ker_ck --> Registers

AHB_Bus[32-bit AHB bus] <--> Registers

AXI_Bus[64-bit AXI bus] <--> Registers

NOR_PSRAM --> NOR_Signals[FMC_NL (or NADV), FMC_CLK]

NOR_PSRAM --> Shared_SRAM[FMC_NBL[3:0]]

NOR_PSRAM --> Shared[FMC_A[25:0], FMC_D[31:0]]

NOR_PSRAM --> Shared_All[FMC_NE[4:1], FMC_NOE, FMC_NWE, FMC_NWAIT]

NAND --> NAND_Signals[FMC_NCE, FMC_INT]

SDRAM --> SDRAM_Signals[FMC_SDCLK, FMC_SDNWE, FMC_SDCKE[1:0], FMC_SDNE[1:0], FMC_NRAS, FMC_NCAS]

The diagram illustrates the internal architecture of the Flexible Memory Controller (FMC). At the top, an interrupt signal labeled 'fmc_it to NVIC' is shown. On the left, two input signals, 'fmc_hclk' and 'fmc_ker_ck', enter the controller. Below them, a vertical bar represents the '32-bit AHB bus' and the '64-bit AXI bus', both connected to the FMC's internal bus system. The central part of the FMC contains three main memory controllers: 'NOR/PSRAM memory controller', 'NAND Flash memory controller', and 'SDRAM controller'. To the left of these is a block for 'AXI/AHB interface & Configuration registers'. On the right, various signal groups are listed with their corresponding pins: 'NOR/PSRAM signals' (FMC_NL (or NADV), FMC_CLK), 'NOR / SRAM shared signals' (FMC_NBL[3:0]), 'Shared signals' (FMC_A[25:0], FMC_D[31:0]), 'NOR / PSRAM / SRAM shared signals' (FMC_NE[4:1], FMC_NOE, FMC_NWE, FMC_NWAIT), 'NAND signals' (FMC_NCE, FMC_INT), and 'SDRAM signals' (FMC_SDCLK, FMC_SDNWE, FMC_SDCKE[1:0], FMC_SDNE[1:0], FMC_NRAS, FMC_NCAS). The reference code 'MSv40367V3' is located in the bottom right corner.

24.3 FMC internal signals

Table 165 gives the list of FMC internal signals. FMC pins (or external signals) are described in Section 24.7.1: External memory interface signals .

Table 165. FMC pins

| Names | Signal type | Description |

|---|---|---|

| fmc_it | Digital output | FMC interrupt |

| fmc_ker_ck | Digital input | FMC kernel clock |

| fmc_hclk | Digital input | FMC interface clock |

24.4 AHB interface

The AHB slave interface allows internal CPUs to configure the FMC registers.

The AHB clock (fmc_hclk) is the reference clock for the FMC register accesses.

24.5 AXI interface

The AXI slave interface allows internal CPUs and other bus master peripherals to access the external memories.

AXI transactions are translated into the external device protocol. As the AXI data bus is 64-bit wide, the AXI transactions might be split into several consecutive 32-, 16- or 8-bit accesses according to data size accesses. The FMC Chip Select (FMC_NEx) does not toggle between consecutive accesses except in case of accesses in mode D when the Extended mode is enabled.

The FMC generates an AXI slave error when one of the following conditions is met:

- • Reading or writing to an FMC bank (Bank 1 to 4) which is not enabled.

- • Reading or writing to the NOR Flash bank while the FACCEN bit is reset in the FMC_BCRx register.

- • Writing to a write protected SDRAM bank (WP bit set in the FMC_SDCRx register).

- • Violation of the SDRAM address range (access to reserved address range)

- • Attempting to read/write access from/to SDRAM bank when it is not yet initialized

The FMC generates an AXI decoder error when ADDR[31:28] address bits are not supported by the FMC bank base address following the BMAP[1:0] bits configuration.

The kernel clock for the FMC controller is the asynchronous fmc_ker_ck clock (refer to Section 32: Reset and Clock Control (RCC) for fmc_ker_ck clock source selection).

24.5.1 Supported memories and transactions

General transaction rules

The requested AXI transaction data size can be 8-, 16-, 32- or 64-bit wide whereas the accessed external device has a fixed data width. The best performance is always achieved with aligned AXI transactions whose size matches the external device data width.

When AXI transaction data size is different from the device data width, the result depends on the following factors:

- • AXI transaction data size is greater than the device data width:

- – Read/Write transactions: the FMC splits the AXI transaction into smaller consecutive accesses matching the external device data width.

- • AXI transaction data size is smaller than the external device data width and the device supports byte selection (SRAM, PSRAM, SDRAM):

- – Write transactions, the FMC manages the transaction using the byte lane signals.

- – Read transactions, the FMC returns all bytes according to the external device data width. The useless bytes are discarded by the system.

- • AXI transaction data size is smaller than the external device data width and the device does not support byte selection (NOR and NAND Flash memories):

- – Write transactions: the FMC writes some irrelevant bytes which may corrupt the external device

- – Read transactions: the FMC returns all bytes according to the external device data width. The useless bytes are discarded by the system.

Caution: Address alignment

- • Read transactions with unaligned addresses (such as half-word starting at an odd address) are not supported by the FMC.

- • Write transactions with unaligned addresses

Their support depends on byte selection availability on the external device:- – If the device does not support byte selection (NOR and NAND Flash memories), narrow write transactions and/or unaligned write transaction are not supported since the FMC would write irrelevant bytes and corrupt the external device.

Wrap support for NOR Flash/PSRAM and SDRAM

The synchronous memories must be configured in Linear burst mode of undefined length as not all masters can issue wrap transactions.

If a master generates a wrap transaction:

- • The read is split into two linear burst transactions.

- • The write is split into two linear burst transactions if the write FIFO is enabled and into several linear burst transactions if the write FIFO is disabled.

Configuration registers

The FMC can be configured through a set of registers. Refer to Section 24.7.6 , for a detailed description of the NOR Flash/PSRAM controller registers. Refer to Section 24.8.7 , for a detailed description of the NAND Flash registers and to Section 24.9.5 for a detailed description of the SDRAM controller registers.

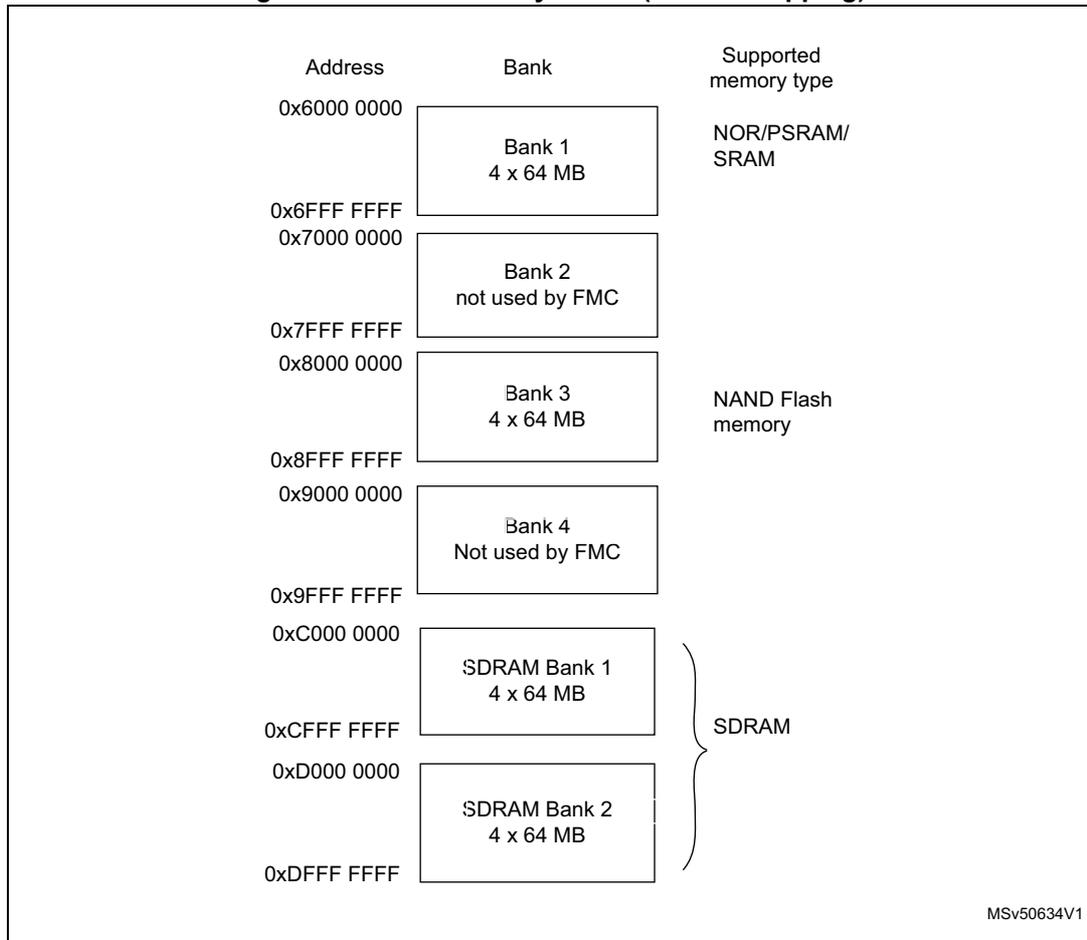

24.6 External device address mapping

From the FMC point of view, the external memory is divided into fixed-size banks of 256 Mbytes each (see Figure 113 ):

- • Bank 1 is used to address up to 4 NOR Flash memory or PSRAM devices. This bank is split into 4 NOR/PSRAM subbanks with 4 dedicated Chip Selects, as follows:

- – Bank 1 - NOR/PSRAM 1

- – Bank 1 - NOR/PSRAM 2

- – Bank 1 - NOR/PSRAM 3

- – Bank 1 - NOR/PSRAM 4

- • Bank 2 and Bank 4 are not used by the FMC.

- • Bank 3 is used to address NAND Flash memory devices. The MPU memory attribute for this space must be reconfigured by software to Device.

- • Bank 5 and 6 are used to address SDRAM devices (1 device per bank).

For each bank the type of memory to be used can be configured by the user application through the Configuration register.

Figure 113. FMC memory banks (default mapping)

| Address | Bank | Supported memory type |

|---|---|---|

| 0x6000 0000 | Bank 1 4 x 64 MB | NOR/PSRAM/ SRAM |

| 0x6FFF FFFF | ||

| 0x7000 0000 | Bank 2 not used by FMC | |

| 0x7FFF FFFF | ||

| 0x8000 0000 | Bank 3 4 x 64 MB | NAND Flash memory |

| 0x8FFF FFFF | ||

| 0x9000 0000 | Bank 4 Not used by FMC | |

| 0x9FFF FFFF | ||

| 0xC000 0000 | SDRAM Bank 1 4 x 64 MB | SDRAM |

| 0xCFFF FFFF | ||

| 0xD000 0000 | SDRAM Bank 2 4 x 64 MB | |

| 0xDFFF FFFF |

MSV50634V1

The FMC bank mapping can be modified through the BMAP[1:0] bits in the FMC_BCR1 register. Table 166 shows the configuration to swap the NOR/PSRAM bank with SDRAM banks.

Table 166. FMC bank mapping options

| Start -End address | BMAP[1:0]=00 (Default mapping) | BMAP[1:0]=01 NOR/PSRAM and SDRAM banks swapped |

|---|---|---|

| 0x6000 0000 - 0x6FFF FFFF | NOR/PSRAM bank | SDRAM bank1 |

| 0x7000 0000 - 0x7FFF FFFF | Not used by FMC | |

| 0x8000 0000 - 0x8FFF FFFF | NAND bank | NAND bank |

| 0x9000 0000 - 0x9FFF FFFF | Not used by FMC | |

| 0xC000 0000 - 0xCFFF FFFF | SDRAM bank1 | NOR/PSRAM bank |

| 0xD000 0000 - 0xDFFF FFFF | SDRAM bank2 | SDRAM bank2 |

24.6.1 NOR/PSRAM address mapping

ADDR[27:26] bits are used to select one of the four memory banks as shown in Table 167 .

Table 167. NOR/PSRAM bank selection

| ADDR[27:26] (1) | Selected bank |

|---|---|

| 00 | Bank 1 - NOR/PSRAM 1 |

| 01 | Bank 1 - NOR/PSRAM 2 |

| 10 | Bank 1 - NOR/PSRAM 3 |

| 11 | Bank 1 - NOR/PSRAM 4 |

- 1. ADDR are internal address lines that are translated to external memory.

The ADDR[25:0] bits contain the external memory address. Since ADDR is a byte address whereas the memory is addressed at word level, the address actually issued to the memory varies according to the memory data width, as shown in the following table.

Table 168. NOR/PSRAM External memory address

| Memory width (1) | Data address issued to the memory | Maximum memory capacity (bits) |

|---|---|---|

| 8-bit | ADDR[25:0] | 64 Mbytes x 8 = 512 Mbit |

| 16-bit | ADDR[25:1] >> 1 | 64 Mbytes/2 x 16 = 512 Mbit |

| 32-bit | ADDR[25:2] >> 2 | 64 Mbytes/4 x 32 = 512 Mbit |

- 1. In case of a 16-bit external memory width, the FMC will internally use ADDR[25:1] to generate the address for external memory FMC_A[24:0]. In case of a 32-bit memory width, the FMC will internally use ADDR[25:2] to generate the external address.

Whatever the external memory width, FMC_A[0] should be connected to external memory address A[0].

24.6.2 NAND Flash memory address mapping

The NAND bank is divided into memory areas as indicated in Table 169 .

Table 169. NAND memory mapping and timing registers| Start address | End address | FMC bank | Memory space | Timing register |

|---|---|---|---|---|

| 0x8800 0000 | 0x8BFF FFFF | Bank 3 - NAND Flash | Attribute | FMC_PATT (0x8C) |

| 0x8000 0000 | 0x83FF FFFF | Common | FMC_PMEM (0x88) |

For NAND Flash memory, the common and attribute memory spaces are subdivided into three sections (see in Table 170 below) located in the lower 256 Kbytes:

- • Data section (first 64 Kbytes in the common/attribute memory space)

- • Command section (second 64 Kbytes in the common / attribute memory space)

- • Address section (next 128 Kbytes in the common / attribute memory space)

| Section name | ADDR[17:16] | Address range |

|---|---|---|

| Address section | 1X | 0x020000-0x03FFFF |

| Command section | 01 | 0x010000-0x01FFFF |

| Data section | 00 | 0x000000-0x00FFFF |

The application software uses the 3 sections to access the NAND Flash memory:

- • To send a command to NAND Flash memory , the software must write the command value to any memory location in the command section.

- • To specify the NAND Flash address that must be read or written , the software must write the address value to any memory location in the address section. Since an address can be 4 or 5 bytes long (depending on the actual memory size), several consecutive write operations to the address section are required to specify the full address.

- • To read or write data , the software reads or writes the data from/to any memory location in the data section.

Since the NAND Flash memory automatically increments addresses, there is no need to increment the address of the data section to access consecutive memory locations.

24.6.3 SDRAM address mapping

Two SDRAM banks are available as indicated in Table 171 .

Table 171. SDRAM bank selection| Selected bank | Control register | Timing register |

|---|---|---|

| SDRAM Bank1 | FMC_SDCR1 | FMC_SDTR1 |

| SDRAM Bank2 | FMC_SDCR2 | FMC_SDTR2 |

Table 172 shows SDRAM mapping for a 13-bit row and an 11-bit column configuration.

Table 172. SDRAM address mapping

| Memory width (1) | Internal bank | Row address | Column address (2) | Maximum memory capacity (Mbytes) |

|---|---|---|---|---|

| 8-bit | ADDR[25:24] | ADDR[23:11] | ADDR[10:0] | 64 Mbytes: 4 x 8K x 2K |

| 16-bit | ADDR[26:25] | ADDR[24:12] | ADDR[11:1] | 128 Mbytes: 4 x 8K x 2K x 2 |

| 32-bit | ADDR[27:26] | ADDR[25:13] | ADDR[12:2] | 256 Mbytes: 4 x 8K x 2K x 4 |

- 1. When interfacing with a 16-bit memory, the FMC internally uses the ADDR[11:1] internal address lines to generate the external address. When interfacing with a 32-bit memory, the FMC internally uses ADDR[12:2] lines to generate the external address. Whatever the memory width, FMC_A[0] has to be connected to the external memory address A[0].

- 2. The AutoPrecharge is not supported. FMC_A[10] must be connected to the external memory address A[10] but it will be always driven low.

The ADDR[27:0] bits are translated into an external SDRAM address depending on the SDRAM controller configuration:

- • Data size: 8, 16 or 32 bits

- • Row size: 11, 12 or 13 bits

- • Column size: 8, 9, 10 or 11 bits

- • Number of internal banks: two or four internal banks

The following tables show the SDRAM address mapping versus the SDRAM controller configuration.

Table 173. SDRAM address mapping with 8-bit data bus width (1)(2)

| Row size configuration n | ADDR(Internal Address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 11-bit row size configuration | Res. | Bank [1:0] | Row[10:0] | Column[7:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[8:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[9:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[10:0] | |||||||||||||||||||||||||

| Row size configuration | ADDR(Internal Address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 12-bit row size configuration | Res. | Bank [1:0] | Row[11:0] | Column[7:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[8:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[9:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[10:0] | |||||||||||||||||||||||||

| 13-bit row size configuration | Res. | Bank [1:0] | Row[12:0] | Column[7:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[8:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[9:0] | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[10:0] | |||||||||||||||||||||||||

1. BANK[1:0] are the Bank Address BA[1:0]. When only 2 internal banks are used, BA1 must always be set to '0'.

2. Access to Reserved (Res.) address range generates an AXI slave error.

Table 174. SDRAM address mapping with 16-bit data bus width (1)(2)| Row size Configuration | ADDR(address Lines) | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| 11-bit row size configuration | Res. | Bank [1:0] | Row[10:0] | Column[7:0] | BM0 (3) | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[8:0] | BM0 | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[9:0] | BM0 | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[10:0] | BM0 | |||||||||||||||||||||||||

| 12-bit row size configuration | Res. | Bank [1:0] | Row[11:0] | Column[7:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[8:0] | BM0 | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[9:0] | BM0 | |||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[10:0] | BM0 | |||||||||||||||||||||||||

| Row size Configuration | ADDR(address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 13-bit row size configuration | Res. | Bank [1:0] | Row[12:0] | Column[7:0] | BM0 | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[8:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[9:0] | BM0 | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[10:0] | BM0 | ||||||||||||||||||||||||

- 1. BANK[1:0] are the Bank Address BA[1:0]. When only 2 internal banks are used, BA1 must always be set to '0'.

- 2. Access to Reserved space (Res.) generates an AXI Slave error.

- 3. BM0: is the byte mask for 16-bit access.

| Row size configuration | ADDR(address Lines) | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 11-bit row size configuration | Res. | Bank [1:0] | Row[10:0] | Column[7:0] | BM[1:0] (3) | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[8:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[9:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[10:0] | Column[10:0] | BM[1:0] | ||||||||||||||||||||||||

| 12-bit row size configuration | Res. | Bank [1:0] | Row[11:0] | Column[7:0] | BM[1:0] | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[8:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[9:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[11:0] | Column[10:0] | BM[1:0] | ||||||||||||||||||||||||

| 13-bit row size configuration | Res. | Bank [1:0] | Row[12:0] | Column[7:0] | BM[1:0] | |||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[8:0] | BM[1:0] | ||||||||||||||||||||||||

| Res. | Bank [1:0] | Row[12:0] | Column[9:0] | BM[1:0] | ||||||||||||||||||||||||

| Bank [1:0] | Row[12:0] | Column[10:0] | BM[1:0] | |||||||||||||||||||||||||

- 1. BANK[1:0] are the Bank Address BA[1:0]. When only 2 internal banks are used, BA1 must always be set to '0'.

- 2. Access to Reserved space (Res.) generates an AXI slave error.

- 3. BM[1:0]: is the byte mask for 32-bit access.

24.7 NOR Flash/PSRAM controller

The FMC generates the appropriate signal timings to drive the following types of memories:

- • Asynchronous SRAM and ROM

- – 8 bits

- – 16 bits

- – 32 bits

- • PSRAM (Cellular RAM)

- – Asynchronous mode

- – Burst mode for synchronous accesses with configurable option to split burst access when crossing boundary page for CDRAM 1.5.

- – Multiplexed or non-multiplexed

- • NOR Flash memory

- – Asynchronous mode

- – Burst mode for synchronous accesses

- – Multiplexed or non-multiplexed

The FMC outputs a unique Chip Select signal, NE[4:1], per bank. All the other signals (addresses, data and control) are shared.

The FMC supports a wide range of devices through a programmable timings among which:

- • Programmable wait states (up to 15)

- • Programmable bus turnaround cycles (up to 15)

- • Programmable output enable and write enable delays (up to 15)

- • Independent read and write timings and protocol to support the widest variety of memories and timings

- • Programmable continuous clock (FMC_CLK) output.

The FMC output Clock (FMC_CLK) is a sub-multiple of the fmc_ker_ck clock. It can be delivered to the selected external device either during synchronous accesses only or during asynchronous and synchronous accesses depending on the CCKEN bit configuration in the FMC_BCR1 register:

- • If the CCLKEN bit is reset, the FMC generates the clock (FMC_CLK) only during synchronous accesses (Read/write transactions).

- • If the CCLKEN bit is set, the FMC generates a continuous clock during asynchronous and synchronous accesses. To generate the FMC_CLK continuous clock, Bank 1 must be configured in Synchronous mode (see Section 24.7.6: NOR/PSRAM controller registers ). Since the same clock is used for all synchronous memories, when a continuous output clock is generated and synchronous accesses are performed, the AXI data size has to be the same as the memory data width (MWID) otherwise the FMC_CLK frequency will be changed depending on AXI data transaction (refer to Section 24.7.5: Synchronous transactions for FMC_CLK divider ratio formula).

The size of each bank is fixed and equal to 64 Mbytes. Each bank is configured through dedicated registers (see Section 24.7.6: NOR/PSRAM controller registers ).

The programmable memory parameters include access times (see Table 176 ) and support for wait management (for PSRAM and NOR Flash memory accessed in Burst mode).

Table 176. Programmable NOR/PSRAM access parameters| Parameter | Function | Access mode | Unit | Min. | Max. |

|---|---|---|---|---|---|

| Address setup | Duration of the address setup phase | Asynchronous | FMC clock cycle (fmc_ker_ck) | 0 | 15 |

| Address hold | Duration of the address hold phase | Asynchronous, muxed I/Os | FMC clock cycle (fmc_ker_ck) | 1 | 15 |

| Data setup | Duration of the data setup phase | Asynchronous | FMC clock cycle (fmc_ker_ck) | 1 | 256 |

| Bust turn | Duration of the bus turnaround phase | Asynchronous and synchronous read | FMC clock cycle (fmc_ker_ck) | 0 | 15 |

| Clock divide ratio | Number of FMC clock cycles (fmc_ker_ck) to build one memory clock cycle (CLK) | Synchronous | FMC clock cycle (fmc_ker_ck) | 2 | 16 |

| Data latency | Number of clock cycles to issue to the memory before the first data of the burst | Synchronous | Memory clock cycle (fmc_ker_ck) | 2 | 17 |

24.7.1 External memory interface signals

Table 177 , Table 178 and Table 179 list the signals that are typically used to interface with NOR Flash memory, SRAM and PSRAM.

Note: The prefix “N” identifies the signals which are active low.

NOR Flash memory, non-multiplexed I/Os

Table 177. Non-multiplexed I/O NOR Flash memory| FMC pin name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:0] | O | Address bus |

| D[31:0] | I/O | Bidirectional data bus |

| NE[x] | O | Chip Select, x = 1..4 |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(=NADV) | O | Latch enable (this signal is called address valid, NADV, by some NOR Flash devices) |

| NWAIT | I | NOR Flash wait input signal to the FMC |

The maximum capacity is 512 Mbits (26 address lines).

NOR Flash memory, 16-bit multiplexed I/Os Table 178. 16-bit multiplexed I/O NOR Flash memory| FMC pin name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:16] | O | Address bus |

| AD[15:0] | I/O | 16-bit multiplexed, bidirectional address/data bus (the 16-bit address A[15:0] and data D[15:0] are multiplexed on the databus) |

| NE[x] | O | Chip Select, x = 1..4 |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(=NADV) | O | Latch enable (this signal is called address valid, NADV, by some NOR Flash devices) |

| NWAIT | I | NOR Flash wait input signal to the FMC |

The maximum capacity is 512 Mbits.

PSRAM/SRAM, non-multiplexed I/Os Table 179. Non-multiplexed I/Os PSRAM/SRAM| FMC pin name | I/O | Function |

|---|---|---|

| CLK | O | Clock (only for PSRAM synchronous access) |

| A[25:0] | O | Address bus |

| D[31:0] | I/O | Data bidirectional bus |

| NE[x] | O | Chip Select, x = 1..4 (called NCE by PSRAM (Cellular RAM i.e. CDRAM)) |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(= NADV) | O | Address valid only for PSRAM input (memory signal name: NADV) |

| NWAIT | I | PSRAM wait input signal to the FMC |

| NBL[3:0] | O | Byte lane output. Byte 0 to Byte 3 control (Upper and lower byte enable) |

The maximum capacity is 512 Mbits.

PSRAM, 16-bit multiplexed I/Os Table 180. 16-Bit multiplexed I/O PSRAM| FMC pin name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:16] | O | Address bus |

| AD[15:0] | I/O | 16-bit multiplexed, bidirectional address/data bus (the 16-bit address A[15:0] and data D[15:0] are multiplexed on the databus) |

| FMC pin name | I/O | Function |

|---|---|---|

| NE[x] | O | Chip Select, x = 1..4 (called NCE by PSRAM (Cellular RAM i.e. CDRAM)) |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(= NADV) | O | Address valid PSRAM input (memory signal name: NADV) |

| NWAIT | I | PSRAM wait input signal to the FMC |

| NBL[1:0] | O | Byte lane output. Byte 0 and Byte 1 control (upper and lower byte enable) |

The maximum capacity is 512 Mbits (26 address lines).

24.7.2 Supported memories and transactions

Table 181 below shows an example of the supported devices, access modes and transactions when the memory data bus is 16-bit wide for NOR Flash memory, PSRAM and SRAM. The transactions not allowed (or not supported) by the FMC are shown in gray in this example.

Table 181. NOR Flash/PSRAM: Example of supported memories and transactions (1)| Device | Mode | R/W | AXI data size | Memory data size | Allowed/ not allowed | Comments |

|---|---|---|---|---|---|---|

| NOR Flash (muxed I/Os and non- multiplexed I/Os) | Asynchronous | R | 8 | 16 | Y | |

| Asynchronous | W | 8 | 16 | N | ||

| Asynchronous | R | 16 | 16 | Y | ||

| Asynchronous | W | 16 | 16 | Y | ||

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | R | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous | W | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous page | R | - | 16 | N | Mode is not supported | |

| Synchronous | R | 8 | 16 | N | ||

| Synchronous | R | 16 | 16 | Y | ||

| Synchronous | R | 32/64 | 16 | Y |

Table 181. NOR Flash/PSRAM: Example of supported memories and transactions (1) (continued)

| Device | Mode | R/W | AXI data size | Memory data size | Allowed/ not allowed | Comments |

|---|---|---|---|---|---|---|

| PSRAM (multiplexed I/Os and non- multiplexed I/Os) | Asynchronous | R | 8 | 16 | Y | |

| Asynchronous | W | 8 | 16 | Y | Use of byte lanes NBL[1:0] | |

| Asynchronous | R | 16 | 16 | Y | ||

| Asynchronous | W | 16 | 16 | Y | ||

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | R | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous | W | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous page | R | - | 16 | N | Mode is not supported | |

| Synchronous | R | 8 | 16 | N | ||

| Synchronous | R | 16 | 16 | Y | ||

| Synchronous | R | 32/64 | 16 | Y | ||

| Synchronous | W | 8 | 16 | Y | Use of byte lanes NBL[1:0] | |

| Synchronous | W | 16/32/64 | 16 | Y | ||

| SRAM and ROM | Asynchronous | R | 8/16 | 16 | Y | |

| Asynchronous | W | 8/16 | 16 | Y | Use of byte lanes NBL[1:0] | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses Use of byte lanes NBL[1:0] | |

| Asynchronous | R | 64 | 16 | Y | Split into 4 FMC accesses | |

| Asynchronous | W | 64 | 16 | Y | Split into 4 FMC accesses Use of byte lanes NBL[1:0] |

1. NBL[1:0] are also driven by AXI write strobes.

24.7.3 General timing rules

Signal synchronization is performed as follows:

- • All controller output signals change on the rising edge of the fmc_ker_ck clock.

- • In Synchronous read and write modes, all output signals change on the rising edge of fmc_ker_ck clock. Whatever the CLKDIV value, all outputs change as follows:

- – NOEL/NWEL/ NEL/NADVL/ NADVH /NBLL/ Address valid outputs change on the falling edge of FMC_CLK clock.

- – NOEH/ NWEH / NEH/ NOEH/NBLH/ Address invalid outputs change on the rising edge of FMC_CLK clock.

24.7.4 NOR Flash/PSRAM controller asynchronous transactions

Asynchronous transactions on static memories (NOR Flash memory, PSRAM, SRAM) are performed as follows:

- • Signals are synchronized by the internal clock. This clock is not issued to the memory.

- • The FMC always samples the data before deasserting the Chip Select signal. This guarantees that the memory data hold timing constraint is met (minimum Chip Enable high to data transition is usually 0 ns)

- • If the Extended mode is enabled (EXTMOD bit is set in the FMC_BCRx register), up to four extended modes (A, B, C and D) are available. It is possible to mix A, B, C and D modes for read and write operations. For example, read operation can be performed in mode A and write in mode B.

- • If the Extended mode is disabled (EXTMOD bit is reset in the FMC_BCRx register), the FMC can operate in Mode1 or Mode2 as follows:

- – Mode 1 is the default mode when SRAM/PSRAM memory type is selected (MTYP = 0x0 or 0x01 in the FMC_BCRx register)

- – Mode 2 is the default mode when NOR memory type is selected (MTYP = 0x10 in the FMC_BCRx register).

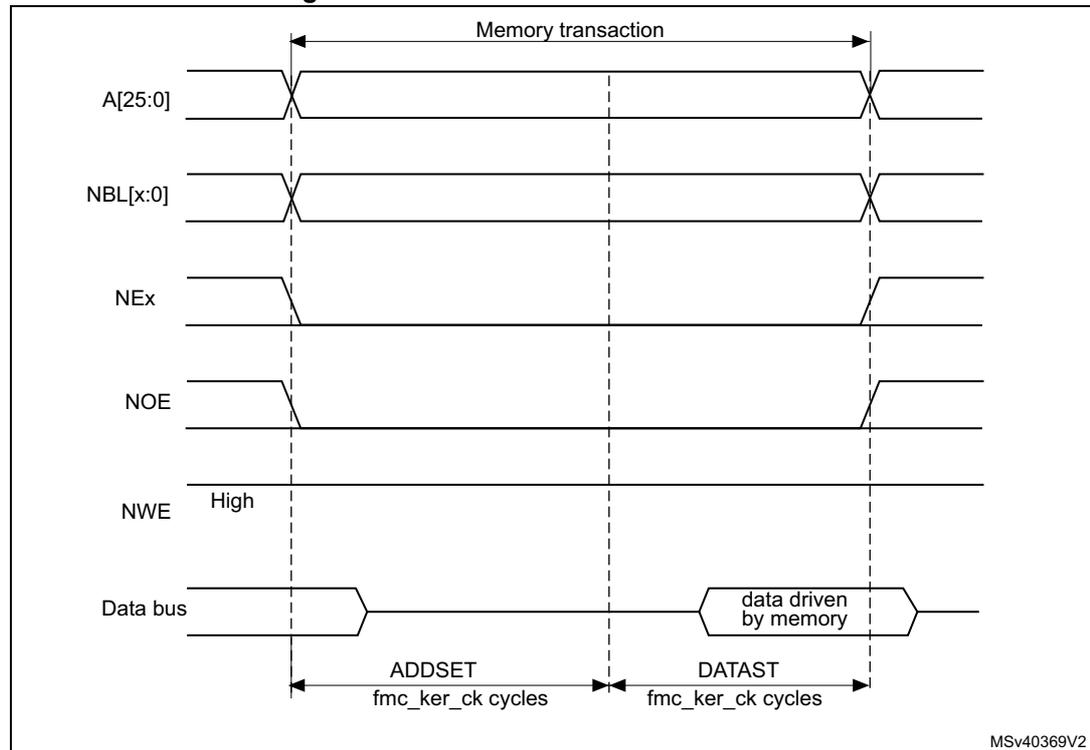

Mode 1 - SRAM/PSRAM (CRAM)

The next figures show the read and write transactions for the supported modes followed by the required configuration of FMC_BCRx, and FMC_BTRx/FMC_BWTRx registers.

Figure 114. Mode 1 read access waveforms

The diagram illustrates the timing for a Mode 1 read access. It shows the following signals over time:

- A[25:0] : Address bus, which is stable during the ADDSET and DATAST phases.

- NBL[x:0] : Byte Lane signals, which are active low and stable during the transaction.

- NEx : Chip Select signal, which is active low and goes low at the start of the transaction and high at the end.

- NOE : Output Enable signal, which is active low and goes low at the start of the transaction and high at the end.

- NWE : Write Enable signal, which is high (inactive) throughout the read transaction.

- Data bus : The data bus is shown in two states: initially high-impedance, and then "data driven by memory" during the DATAST phase.

The transaction is divided into two phases by vertical dashed lines:

- ADDSET : The first phase, labeled "fmc_ker_ck cycles", where the address and control signals are set.

- DATAST : The second phase, also labeled "fmc_ker_ck cycles", where the data is driven by the memory.

A horizontal double-headed arrow at the top indicates the total "Memory transaction" duration from the falling edge of NEx to its rising edge. The identifier MSV40369V2 is in the bottom right corner.

Figure 115. Mode 1 write access waveforms

![Timing diagram for Mode 1 write access waveforms. The diagram shows the relationship between address (A[25:0]), non-byte-lane (NBL[x:0]), chip select (NEx), output enable (NOE), write enable (NWE), and the data bus over a 'Memory transaction'. The transaction starts with address and NBL becoming valid, followed by NEx going low. NOE stays high throughout. NWE goes low to start the write pulse. The data bus is driven by the FSMC during the write pulse. Timing parameters include ADDSET (address setup time) and (DATAST + 1) (data setup time) measured in fmc_ker_ck cycles. A 1 fmc_ker_ck cycle is shown after the NWE rising edge to ensure address and data hold time.](/RM0468-STM32H723-733-725-735-730/7e54d2cbb4704f042a10b4e88cd92635_img.jpg)

MSV40370V2

The fmc_ker_ck cycle at the end of the write transaction helps guarantee the address and data hold time after the NWE rising edge. Due to the presence of this fmc_ker_ck cycle, the DATAST value must be greater than zero (DATAST > 0).

Table 182. FMC_BCRx bitfields (mode 1)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31 | FMCEN | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Don't care |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | As needed, exclude 0x2 (NOR Flash memory) |

| 1 | MUXE | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | Don't care |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST+1 fmc_ker_ck cycles for write accesses, DATAST fmc_ker_ck cycles for read accesses). |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles). Minimum value for ADDSET is 0. |

Mode A - SRAM/PSRAM (CRAM) OE toggling

Figure 116. Mode A read access waveforms

![Timing diagram for Mode A read access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over time. It includes labels for Memory transaction, ADDSET, and DATAST in fmc_ker_ck cycles.](/RM0468-STM32H723-733-725-735-730/5111fba4542d77a3b8d5fc60c4f4c305_img.jpg)

The diagram illustrates the timing for a Mode A read access. The signals shown are:

- A[25:0] : Address bus, stable during the memory transaction.

- NBL[x:0] : Byte Lane signals, driven low during the read access.

- NEx : Address Latch Enable, goes low to latch the address and returns high after.

- NOE : Output Enable, goes low to enable data output from the memory and returns high before the data transaction ends.

- NWE : Write Enable, remains high throughout the read access.

- Data bus : Bidirectional bus that is driven by the memory during the DATAST phase.

Timing parameters are defined in fmc_ker_ck cycles:

- ADDSET : Time from the falling edge of NEx to the start of the DATAST phase.

- DATAST : Time from the start of the DATAST phase to the rising edge of NOE.

Reference: MSV40371V2

- 1. NBL[3:0] are driven low during the read access

Figure 117. Mode A write access waveforms

![Timing diagram for Mode A write access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over a memory transaction. The diagram shows the relationship between address, bus cycle length, and data drive duration.](/RM0468-STM32H723-733-725-735-730/406967d4a821103d908424c824029635_img.jpg)

The diagram illustrates the timing for a Mode A write access. The 'Memory transaction' spans the entire active period of the NEx signal. Address lines A[25:0] and byte lane control lines NBL[x:0] are stable during this period. NEx (Chip Select) is active-low. NOE (Output Enable) toggles low then high during the write access. NWE (Write Enable) goes low after an initial setup time. The Data bus is driven by the FMC starting after the ADDSET period. The 'ADDSET' time is the duration from the start of the transaction to the falling edge of NWE, measured in fmc_ker_ck cycles. The 'data driven by FMC' duration is (DATAST + 1) fmc_ker_ck cycles, ending with the rising edge of NWE. A single fmc_ker_ck cycle is indicated at the end of the NWE low pulse.

MSV40372V3

The differences compared with Mode1 are the toggling of NOE and the independent read and write timings.

Table 184. FMC_BCRx bitfields (mode A)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31 | FMCEN | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

Table 184. FMC_BCRx bitfields (mode A) (continued)

| Bit number | Bit name | Value to set |

|---|---|---|

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Don't care |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | As needed, exclude 0x2 (NOR Flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

Table 185. FMC_BTRx bitfields (mode A)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 0. |

Table 186. FMC_BWTRx bitfields (mode A)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 0. |

Mode 2/B - NOR Flash

Figure 118. Mode 2 and mode B read access waveforms

![Timing diagram for Mode 2 and mode B read access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. The diagram shows a memory transaction with ADDSET and DATAST phases measured in fmc_ker_ck cycles. The data bus is driven by memory during the DATAST phase.](/RM0468-STM32H723-733-725-735-730/31534e3308fac1671bc8990208ec6f41_img.jpg)

Timing diagram for Mode 2 and mode B read access waveforms. The diagram shows the following signals and timing parameters:

- Signals:

- A[25:0]: Address bus, valid during the memory transaction.

- NADV: Address Valid signal, active low, goes low at the start of the transaction and high at the end.

- NEx: External memory signal, active low, goes low at the start and high at the end.

- NOE: Output Enable signal, active low, goes low at the start and high at the end.

- NWE: Write Enable signal, active low, remains high throughout the read transaction.

- Data bus: Bidirectional data bus, driven by memory during the DATAST phase.

- Timing Parameters:

- Memory transaction: The total duration of the read operation.

- ADDSET: Address setup time in fmc_ker_ck cycles.

- DATAST: Data setup time in fmc_ker_ck cycles.

Figure 119. Mode 2 write access waveforms

![Timing diagram for Mode 2 write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. The diagram shows a memory transaction with ADDSET and (DATAST + 1) phases measured in fmc_ker_ck cycles. The data bus is driven by FSMC during the (DATAST + 1) phase.](/RM0468-STM32H723-733-725-735-730/897b7f66d28ea4c22d5147b7f6b2a587_img.jpg)

Timing diagram for Mode 2 write access waveforms. The diagram shows the following signals and timing parameters:

- Signals:

- A[25:0]: Address bus, valid during the memory transaction.

- NADV: Address Valid signal, active low, goes low at the start and high at the end.

- NEx: External memory signal, active low, goes low at the start and high at the end.

- NOE: Output Enable signal, active low, goes low at the start and high at the end.

- NWE: Write Enable signal, active low, goes low at the start of the data phase and high at the end.

- Data bus: Bidirectional data bus, driven by FSMC during the (DATAST + 1) phase.

- Timing Parameters:

- Memory transaction: The total duration of the write operation.

- ADDSET: Address setup time in fmc_ker_ck cycles.

- (DATAST + 1): Data setup time in fmc_ker_ck cycles.

- 1 fmc_ker_ck: One clock cycle duration.

Figure 120. Mode B write access waveforms

![Timing diagram for Mode B write access waveforms. The diagram shows the relationship between address (A[25:0]), NADV, NEx, NOE, NWE, and the Data bus over time. A 'Memory transaction' is indicated by a double-headed arrow at the top. The address A[25:0] is stable during the transaction. NADV and NEx are active-low signals that go low at the start and high at the end. NOE is active-low and goes low at the start. NWE is active-low and goes low at the start, then high for '1 fmc_ker_ck' cycle, then low again. The Data bus is driven by FSMC and has two phases: 'ADDSET' (fmc_ker_ck cycles) and '(DATAST + 1)' (fmc_ker_ck cycles). The diagram is labeled MSv40375V2.](/RM0468-STM32H723-733-725-735-730/33af5a77acb1e2ba049ee80fc41d9f2c_img.jpg)

The differences with Mode1 are the toggling of NWE and the independent read and write timings when extended mode is set (mode B).

Table 187. FMC_BCRx bitfields (mode 2/B)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31 | FMCE | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 for mode B, 0x0 for mode 2 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | 0x1 |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x2 (NOR Flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x1 if Extended mode is set |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the access second phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the access first phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 0. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x1 if Extended mode is set |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the access second phase (DATAST fmc_ker_ck cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the access first phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 0. |

Note: The FMC_BWTRx register is valid only if the Extended mode is set (mode B), otherwise its content is don't care.

Mode C - NOR Flash - OE toggling

Figure 121. Mode C read access waveforms

![Timing diagram for Mode C read access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. It defines ADDSET and DATAST in fmc_ker_ck cycles.](/RM0468-STM32H723-733-725-735-730/0e7d27ad68db5e6a27b2fcfa7aab7823_img.jpg)

This timing diagram illustrates the signals for a read access in Mode C. The signals shown are address A[25:0], NADV, NEx, NOE, NWE, and the Data bus. The address is stable during the 'ADDSET' period. NADV and NEx are active-low signals that go low at the start of the transaction. NOE is active-low and goes low to enable data output from the memory. NWE is held high. The data bus is driven by the memory during the 'DATAST' period. The total 'Memory transaction' time is the sum of ADDSET and DATAST in fmc_ker_ck cycles. Reference MSV40376V2.

Figure 122. Mode C write access waveforms

![Timing diagram for Mode C write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time. It defines ADDSET and (DATAST + 1) in fmc_ker_ck cycles, with a 1 fmc_ker_ck cycle delay for NWE.](/RM0468-STM32H723-733-725-735-730/a36c8b9500e1b9fb5a39c35c57889f72_img.jpg)

This timing diagram illustrates the signals for a write access in Mode C. The signals shown are address A[25:0], NADV, NEx, NOE, NWE, and the Data bus. The address is stable during the 'ADDSET' period. NADV and NEx are active-low signals that go low at the start of the transaction. NOE is active-low and goes low to enable data output from the FSMC. NWE is active-low and goes low one fmc_ker_ck cycle after the data is driven. The data bus is driven by the FSMC during the '(DATAST + 1)' period. The total 'Memory transaction' time is the sum of ADDSET and (DATAST + 1) in fmc_ker_ck cycles. Reference MSV40377V2.

The differences compared with Mode1 are the toggling of NOE and the independent read and write timings.

Table 190. FMC_BCRx bitfields (mode C)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | FMCE N | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | 0x1 |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x02 (NOR Flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

Table 191. FMC_BTRx bitfields (mode C)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x2 |

| 27:24 | DATLAT | 0x0 |

| 23:20 | CLKDIV | 0x0 |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 0. |

Table 192. FMC_BWTRx bitfields (mode C)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x2 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 0. |

Mode D - asynchronous access with extended address

Figure 123. Mode D read access waveforms

![Timing diagram for Mode D read access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time relative to fmc_ker_ck clock.](/RM0468-STM32H723-733-725-735-730/ed99b530e6e6603875ca32134fdf86a2_img.jpg)

This timing diagram illustrates the signals for a Mode D read access. The signals shown are A[25:0] (address), NADV (address valid), NEx (external memory), NOE (output enable), NWE (write enable, held high), and the Data bus. The timing is relative to the fmc_ker_ck clock. The 'Memory transaction' starts when A[25:0] is set and NADV goes low. The address is latched on the rising edge of fmc_ker_ck (ADDSET). Data is driven by memory on the falling edge of fmc_ker_ck (DATAST). The transaction ends when NADV goes high and NEx goes high. MSV40378V2

Figure 124. Mode D write access waveforms

![Timing diagram for Mode D write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time relative to fmc_ker_ck clock.](/RM0468-STM32H723-733-725-735-730/82a90ab6b31e022e5b953afffcd07d0c_img.jpg)

This timing diagram illustrates the signals for a Mode D write access. The signals shown are A[25:0] (address), NADV (address valid), NEx (external memory), NOE (output enable), NWE (write enable), and the Data bus. The timing is relative to the fmc_ker_ck clock. The 'Memory transaction' starts when A[25:0] is set and NADV goes low. The address is latched on the rising edge of fmc_ker_ck (ADDSET). Data is driven by FMC on the falling edge of fmc_ker_ck (DATAST+1). The transaction ends when NADV goes high and NEx goes high. MSV40378V3

The differences with Mode1 are the toggling of NOE that goes on toggling after NADV changes and the independent read and write timings.

Table 193. FMC_BCRx bitfields (mode D)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | FMCEN | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Set according to memory support |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | As needed |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

Table 194. FMC_BTRx bitfields (mode D)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x3 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles) for read accesses. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 7:4 | ADDHLD | Duration of the middle phase of the read access (ADDHLD fmc_ker_ck cycles) |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for read accesses. Minimum value for ADDSET is 1. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x3 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST + 1 fmc_ker_ck cycles) for write accesses. |

| 7:4 | ADDHLD | Duration of the middle phase of the write access (ADDHLD fmc_ker_ck cycles) |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles) for write accesses. Minimum value for ADDSET is 1. |

Muxed mode - multiplexed asynchronous access to NOR Flash memory

Figure 125. Muxed read access waveforms

![Timing diagram for Figure 125: Muxed read access waveforms. It shows signals A[25:16], NADV, NEx, NOE, NWE, and AD[15:0] over time. The memory transaction starts with a falling edge of NADV and NEx. A[25:16] is stable during the transaction. AD[15:0] is used for 'Lower address' and 'data driven by memory'. Timing parameters include ADDSET, DATAST, and ADDHLD in fmc_ker_ck cycles. MSV40380V2 is noted at the bottom right.](/RM0468-STM32H723-733-725-735-730/946a221e4885c6ac32e0cc08ee4e847c_img.jpg)

Figure 126. Muxed write access waveforms

![Timing diagram for Figure 126: Muxed write access waveforms. It shows signals A[25:16], NADV, NEx, NOE, NWE, and AD[15:0] over time. The memory transaction starts with a falling edge of NADV and NEx. A[25:16] is stable. AD[15:0] is used for 'Lower address' and 'data driven by FSMC'. Timing parameters include ADDSET, (DATAST + 1), and ADDHLD in fmc_ker_ck cycles. A 1 fmc_ker_ck cycle is indicated for NWE. MSV40381V2 is noted at the bottom right.](/RM0468-STM32H723-733-725-735-730/4bc8020687a9b4d99685f0516609d98f_img.jpg)

The difference with Mode D is the drive of the lower address byte(s) on the data bus.

Table 196. FMC_BCRx bitfields (Muxed mode)| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | FMCCEN | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | 0x1 |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x2 (NOR Flash memory) |

| 1 | MUXEN | 0x1 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Duration of the second access phase (DATAST fmc_ker_ck cycles for read accesses and DATAST+1 fmc_ker_ck cycles for write accesses). |

Table 197. FMC_BTRx bitfields (Muxed mode) (continued)

| Bit number | Bit name | Value to set |

|---|---|---|

| 7:4 | ADDHLD | Duration of the middle phase of the access (ADDHLD fmc_ker_ck cycles). |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET fmc_ker_ck cycles). Minimum value for ADDSET is 1. |

WAIT management in asynchronous accesses

If the asynchronous memory asserts the WAIT signal to indicate that it is not yet ready to accept or to provide data, the ASYNCWAIT bit has to be set in FMC_BCRx register.

If the WAIT signal is active (high or low depending on the WAITPOL bit), the second access phase (Data setup phase), programmed by the DATAST bits, is extended until WAIT becomes inactive. Unlike the data setup phase, the first access phases (Address setup and Address hold phases), programmed by the ADDSET and ADDHLD bits, are not WAIT sensitive and so they are not prolonged.

The data setup phase must be programmed so that WAIT can be detected 4 fmc_ker_ck cycles before the end of the memory transaction. The following cases must be considered:

- 1. The memory asserts the WAIT signal aligned to NOE/NWE which toggles:

- 2. The memory asserts the WAIT signal aligned to NEx (or NOE/NWE not toggling):

if

then:

otherwise

where max_wait_assertion_time is the maximum time taken by the memory to assert the WAIT signal once NEx/NOE/NWE is low.

Figure 127 and Figure 128 show the number of fmc_ker_ck clock cycles that are added to the memory access phase after WAIT is released by the asynchronous memory (independently of the above cases).

Figure 127. Asynchronous wait during a read access waveforms

![Timing diagram for asynchronous wait during a read access. It shows signals A[25:0], NEx, NWAIT, NOE, and Data bus over time. The transaction is divided into address and data setup phases. NWAIT is shown as 'don't care' in both phases. Data is driven by memory, with a setup time of 4 fmc_ker_ck.](/RM0468-STM32H723-733-725-735-730/9e8b2e396781d01a2ec337a77ccd88d4_img.jpg)

The diagram illustrates the timing for an asynchronous read access with a wait state. The signals shown are:

- A[25:0] : Address bus, valid during the address phase and data setup phase.

- NEx : Address/Command Output Enable, active low signal.

- NWAIT : Asynchronous wait signal, labeled as 'don't care' in both the address and data setup phases.

- NOE : Output Enable for the data bus, active low signal.

- Data bus : Bidirectional data bus, driven by memory during the data setup phase.

The transaction is divided into two phases: address phase and data setup phase . The data setup time is specified as 4 fmc_ker_ck .

MSv40382V2

1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

Figure 128. Asynchronous wait during a write access waveforms

![Timing diagram for asynchronous wait during a write access. It shows signals A[25:0], NEx, NWAIT, NWE, and Data bus over time. The transaction is divided into address and data setup phases. NWAIT is shown as 'don't care' in both phases. Data is driven by FSMC, with a setup time of 3 fmc_ker_ck and a hold time of 1 fmc_ker_ck.](/RM0468-STM32H723-733-725-735-730/a8984a22e5c27a327ec23c33d358d3f3_img.jpg)

The diagram illustrates the timing for an asynchronous write access with a wait state. The signals shown are:

- A[25:0] : Address bus, valid during the address phase and data setup phase.

- NEx : Address/Command Output Enable, active low signal.

- NWAIT : Asynchronous wait signal, labeled as 'don't care' in both the address and data setup phases.

- NWE : Write Enable, active low signal.

- Data bus : Bidirectional data bus, driven by FSMC during the data setup phase.

The transaction is divided into two phases: address phase and data setup phase . The data setup time is specified as 3 fmc_ker_ck and the hold time as 1 fmc_ker_ck .

MSv40383V2

1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

24.7.5 Synchronous transactions

The memory clock, FMC_CLK, is a sub-multiple of fmc_ker_ck. It depends on the value of CLKDIV and the MWID/ AXI data size, following the formula given below:

If MWID is 16 or 8-bit, the FMC_CLK divider ratio is always defined by the programmed CLKDIV value.

If MWID is 32-bit, the FMC_CLK divider ratio depends also on AXI data size.

Example:

- • If CLKDIV=1, MWID = 32 bits, AXI data size=8 bits, FMC_CLK=fmc_ker_ck/4.

- • If CLKDIV=1, MWID = 16 bits, AXI data size=8 bits, FMC_CLK=fmc_ker_ck/2.

NOR Flash memories specify a minimum time from NADV assertion to FMC_CLK high. To meet this constraint, the FMC does not issue the clock to the memory during the first internal clock cycle of the synchronous access (before NADV assertion). This guarantees that the rising edge of the memory clock occurs in the middle of the NADV low pulse.

For some PSRAM memories which must be configured to Synchronous mode, during the BCR register writing, the memory attribute space must be configured to device or strongly-ordered. Once PSRAM BCR register is configured, the memory attribute of PSRAM address space can be programmed to cacheable.

Data latency versus NOR memory latency

The data latency is the number of cycles to wait before sampling the data. The DATLAT value must be consistent with the latency value specified in the NOR Flash configuration register. The FMC does not include the clock cycle when NADV is low in the data latency count.

Caution: Some NOR Flash memories include the NADV Low cycle in the data latency count, so that the exact relation between the NOR Flash latency and the FMC DATLAT parameter can be either:

- • NOR Flash latency = (DATLAT + 2) FMC_CLK clock cycles

- • or NOR Flash latency = (DATLAT + 3) FMC_CLK clock cycles

Some recent memories assert NWAIT during the latency phase. In such cases DATLAT can be set to its minimum value. As a result, the FMC samples the data and waits long enough to evaluate if the data are valid. Thus the FMC detects when the memory exits latency and real data are processed.

Other memories do not assert NWAIT during latency. In this case the latency must be set correctly for both the FMC and the memory, otherwise invalid data are mistaken for good data, or valid data are lost in the initial phase of the memory access.

Single-burst transfer

When the selected bank is configured in Burst mode for synchronous accesses, if for example a single-burst transaction is requested on 16-bit memories, the FMC performs a burst transaction of length 1 (if the AXI transfer is 16 bits), or length 2 (if the AXI transfer is 32 bits) and deassert the Chip Select signal when the last data is strobed.

Such transfers are not the most efficient in terms of cycles compared to asynchronous read operations. Nevertheless, a random asynchronous access would first require to re-program the memory access mode, which would altogether last longer.

Cross boundary page for Cellular RAM 1.5

Cellular RAM 1.5 does not allow burst access to cross the page boundary. The FMC controller allows to split automatically the burst access when the memory page size is reached by configuring the CPSIZE bits in the FMC_BCR1 register following the memory page size.

Wait management

For synchronous NOR Flash memories, NWAIT is evaluated after the programmed latency period, which corresponds to (DATLAT+2) FMC_CLK clock cycles.

If NWAIT is active (low level when WAITPOL = 0, high level when WAITPOL = 1), wait states are inserted until NWAIT is inactive (high level when WAITPOL = 0, low level when WAITPOL = 1).

When NWAIT is inactive, the data is considered valid either immediately (bit WAITCFG = 1) or on the next clock edge (bit WAITCFG = 0).

During wait-state insertion via the NWAIT signal, the controller continues to send clock pulses to the memory, keeping the Chip Select and output enable signals valid. It does not consider the data as valid.

In Burst mode, there are two timing configurations for the NOR Flash NWAIT signal:

- • The Flash memory asserts the NWAIT signal one data cycle before the wait state (default after reset).

- • The Flash memory asserts the NWAIT signal during the wait state

The FMC supports both NOR Flash wait state configurations, for each Chip Select, thanks to the WAITCFG bit in the FMC_BCRx registers (x = 0..3).

Figure 129. Wait configuration waveforms

![Figure 129. Wait configuration waveforms. Timing diagram showing signals fmc_ker_ck, FMC_CLK, A[25:16], NADV, NWAIT (WAITCFG = 0), NWAIT (WAITCFG = 1), and A/D[15:0] over a burst of 4 half words. The diagram illustrates the effect of inserting a wait state when WAITCFG is 1.](/RM0468-STM32H723-733-725-735-730/67d2d135b530f6655b3a5901a4c80063_img.jpg)

Memory transaction = burst of 4 half words

fmc_ker_ck

FMC_CLK

A[25:16] addr[25:16]

NADV

NWAIT (WAITCFG = 0)

NWAIT (WAITCFG = 1)

A/D[15:0] addr[15:0] data data data

inserted wait state

MSv40384V2

Figure 130. Synchronous multiplexed read mode waveforms - NOR, PSRAM (CRAM)

![Figure 130. Synchronous multiplexed read mode waveforms - NOR, PSRAM (CRAM). Timing diagram showing signals fmc_ker_ck, FMC_CLK, A[25:16], NEx, NOE, NWE, NADV, NWAIT (WAITCFG=0), and A/D[15:0] over a burst of 4 half words. The diagram shows address and data on the A/D bus, with data strobes and an inserted wait state.](/RM0468-STM32H723-733-725-735-730/40b5e0c03131e8c2f08f71aa3a08c727_img.jpg)

Memory transaction = burst of 4 half words

fmc_ker_ck

FMC_CLK

A[25:16] addr[25:16]

NEx

NOE

NWE High

NADV

NWAIT (WAITCFG=0)

A/D[15:0] Addr[15:0] cycles data data data data

(DATLAT + 2) fmc_ker_ck cycles

inserted wait state

clock clock cycle cycle

Data strobes

Data strobes

MSv40385V2

- 1. Byte lane outputs (NBL are not shown; for NOR access, they are held high, and for PSRAM (CRAM) access, they are held low).

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | MC | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | No effect on synchronous read |

| 18:16 | CPSIZE | As needed. (0x1 when using CRAM 1.5) |

| 15 | ASYNCWAIT | 0x0 |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | to be set to 1 if the memory supports this feature, to be kept at 0 otherwise |

| 12 | WREN | no effect on synchronous read |

| 11 | WAITCFG | to be set according to memory |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | to be set according to memory |

| 8 | BURSTEN | 0x1 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Set according to memory support (NOR Flash memory) |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x1 or 0x2 |

| 1 | MUXEN | As needed |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Data latency |

| 27:24 | DATLAT | Data latency |

| 23:20 | CLKDIV | 0x0 to get CLK = fmc_ker_ck 0x1 to get CLK = 2 × fmc_ker_ck .. |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Don't care |

Table 199. FMC_BTRx bitfields (Synchronous multiplexed read mode) (continued)

| Bit number | Bit name | Value to set |

|---|---|---|

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Don't care |

Figure 131. Synchronous multiplexed write mode waveforms - PSRAM (CRAM)

![Timing diagram for synchronous multiplexed write mode waveforms. It shows signals fmc_ker_ck, FMC_CLK, A[25:16], NEx, NOE, NWE, NADV, NWAIT, and A/D[15:0] over time. The diagram illustrates a memory transaction consisting of a burst of 2 half words. Address A[25:16] is shown as 'addr[25:16]'. Data A/D[15:0] is shown as 'Addr[15:0]', 'data', and 'data'. Timing parameters include (DATLAT + 2) fmc_ker_ck cycles and an inserted wait state. The diagram is labeled MSV40386V2.](/RM0468-STM32H723-733-725-735-730/c6907843fc8c6efa6f09afb20ccf1f93_img.jpg)

The timing diagram shows the following signals and timing parameters:

- fmc_ker_ck : Core clock signal, shown as a high-frequency square wave.

- FMC_CLK : Memory controller clock signal, shown as a lower-frequency square wave.

- A[25:16] : Address bus, shown as 'addr[25:16]' during the address phase.

- NEx : Memory address strobe signal, active low.

- NOE : Memory output enable signal, active low, shown as Hi-Z.

- NWE : Memory write enable signal, active low.

- NADV : Memory address valid signal, active low.

- NWAIT (WAITCFG = 0) : Memory wait signal, active low.

- A/D[15:0] : Data bus, shown as 'Addr[15:0]' during the address phase, and 'data' during the data phases.

Timing parameters and labels:

- Memory transaction = burst of 2 half words : Indicated by a double-headed arrow over the data phases.

- (DATLAT + 2) fmc_ker_ck cycles : Timing parameter for the address to data latency.

- inserted wait state : Indicated by a double-headed arrow over a period where the data bus is inactive.

- 1 clock cycle : Indicated by a double-headed arrow over one fmc_ker_ck period.

- MSV40386V2 : Diagram identifier.

- 1. The memory must issue NWAIT signal one cycle in advance, accordingly WAITCFG must be programmed to 0.

- 2. Byte Lane (NBL) outputs are not shown, they are held low while NEx is active.

Table 200. FMC_BCRx bitfields (Synchronous multiplexed write mode)

| Bit No. | Bit name | Value to set |

|---|---|---|

| 31 | FMCE | 0x1 |

| 30:26 | Reserved | 0x000 |

| 25:24 | BMAP | As needed |

| 23:22 | Reserved | 0x000 |

| 21 | WFDIS | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | No effect on synchronous read |

| Bit No. | Bit name | Value to set |

|---|---|---|

| 18:16 | CPSIZE | As needed. (0x1 when using CRAM 1.5) |

| 15 | ASYNCWAIT | 0x0 |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | to be set to 1 if the memory supports this feature, to be kept at 0 otherwise. |

| 12 | WREN | 0x1 |

| 11 | WAITCFG | 0x0 |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | to be set according to memory |

| 8 | BURSTEN | no effect on synchronous write |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Set according to memory support |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x1 |

| 1 | MUXEN | As needed |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | Reserved | 0x0 |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Data latency |

| 23:20 | CLKDIV | 0x0 to get CLK = fmc_ker_ck 0x1 to get CLK = 2 × fmc_ker_ck |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN fmc_ker_ck) |

| 15:8 | DATAST | Don't care |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Don't care |

24.7.6 NOR/PSRAM controller registers

SRAM/NOR-Flash chip-select control registers for bank x (FMC_BCRx)

Address offset: \( 8 * (x - 1) \) , ( \( x = 1 \) to \( 4 \) )

Reset value: Block 1: 0x0000 30DB

Reset value: Block 2: 0x0000 30D2

Reset value: Block 3: 0x0000 30D2

Reset value: Block 4: 0x0000 30D2

This register contains the control information of each memory bank, used for SRAMs, PSRAM and NOR Flash memories.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FMCEN | Res. | Res. | Res. | Res. | Res. | BMAP[1:0] | Res. | Res. | WFDIS | COLKEN | CBURSTRW | CPSIZE[2:0] | |||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | |||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ASYNCWAIT | EXTMOD | WAITEN | WREN | WAITCFG | Res. | WAITPOL | BURSTEN | Res. | FACCEN | MWID | MTYP | MUXEN | MBKEN | ||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

Bit 31 FMCEN : FMC controller Enable

This bit enables/disables the FMC controller.

0: Disable the FMC controller

1: Enable the FMC controller

Note: The FMCEN bit of the FMC_BCR2..4 registers is don't care. It is only enabled through the FMC_BCR1 register.

Bits 30:26 Reserved, must be kept at reset value.

Bits 25:24 BMAP[1:0] : FMC bank mapping

These bits allow different remap or swap of the FMC NOR/PSRAM and SDRAM banks (refer to Table 166 ).

00: Default mapping (refer to Figure 113 and Table 166 ).

01: NOR/PSRAM bank and SDRAM bank 1 are swapped.

10: Reserved

11: Reserved.

Note: The BMAP bits of the FMC_BCR2..4 registers are don't care. It is only enabled through the FMC_BCR1 register.

Bits 23:22 Reserved, must be kept at reset value.

Bit 21 WFDIS: Write FIFO DisableThis bit disables the Write FIFO used by the FMC controller.

0: Write FIFO enabled (Default after reset)

1: Write FIFO disabled

Note: The WFDIS bit of the FMC_BCR2..4 registers is don't care. It is only enabled through the FMC_BCR1 register.

Bit 20 CCLKEN: Continuous Clock EnableThis bit enables the FMC_CLK clock output to external memory devices.

0: The FMC_CLK is only generated during the synchronous memory access (read/write transaction). The FMC_CLK clock ratio is specified by the programmed CLKDIV value in the FMC_BCRx register (default after reset).