20. Extended interrupt and event controller (EXTI)

The Extended Interrupt and event controller (EXTI) manages wakeup through configurable and direct event inputs. It provides wakeup requests to the Power Control, and generates interrupt requests to the CPU NVIC and to the D3 domain DMAMUX2, and events to the CPU event input.

The EXTI wakeup requests allow the system to be woken up from Stop mode, and the CPU to be woken up from CStop mode.

Both the interrupt request and event request generation can also be used in Run modes.

20.1 EXTI main features

The EXTI main features are the following:

- • All Event inputs allow the CPU to wakeup and to generate a CPU interrupt and/or CPU event

- • Some Event inputs allow the user to wakeup the D3 domain for autonomous Run mode and generate an interrupt to the D3 domain, i.e. the DMAMUX2

The asynchronous event inputs are classified in 2 groups:

- • Configurable events (signals from I/Os or peripherals able to generate a pulse), they have the following features:

- – Selectable active trigger edge

- – Interrupt pending status register bit

- – Individual Interrupt and Event generation mask

- – SW trigger possibility

- – Configurable System D3 domain wakeup events have a D3 Pending mask and status register and may have a D3 interrupt signal.

- • Direct events (interrupt and wakeup sources from other peripherals, requiring to be cleared in the peripheral), they feature

- – Fixed rising edge active trigger

- – No interrupt pending status register bit in the EXTI (the interrupt pending status is provided by the peripheral generating the event)

- – Individual Interrupt and Event generation mask

- – No SW trigger possibility

- – Direct system D3 domain wakeup events have a D3 Pending mask and status register and may have a D3 interrupt signal

20.2 EXTI block diagram

As shown in Figure 91 , the EXTI consists of a Register block accessed via an APB interface, an Event input Trigger block, and a Masking block.

The Register block contains all EXTI registers.

The Event input trigger block provides Event input edge triggering logic.

The Masking block provides the Event input distribution to the different wakeup, interrupt and event outputs, and their masking.

Figure 91. EXTI block diagram

![Figure 91. EXTI block diagram. The diagram shows the internal structure of the EXTI block. On the left, 'Peripherals' are connected to the 'Event trigger' block via 'Configurable event(x)' and 'Direct event(x)' inputs. The 'Event trigger' block is connected to the 'Registers' block and the 'Masking' block. The 'Registers' block is connected to an 'APB interface'. The 'Masking' block is connected to the 'Registers' block and the 'Event trigger' block. The 'Masking' block outputs are connected to the 'CPU' (via 'cpu_it_exti_per(x)', 'cpu_event', and 'exti_cpu_wkup'), 'PWR' (via 'exti_d3_wkup'), and 'D3' (via 'd3_it_exti_per(x)' and 'd3_pendclear_in[3:0]'). The 'CPU' block contains 'nvic(n)' and 'rxev'. The 'PWR' and 'D3' blocks are also shown. The entire EXTI block is labeled 'EXTI' at the bottom left. A reference code 'MSv41947V1' is in the bottom right corner.](/RM0468-STM32H723-733-725-735-730/9343540fbb568aaaa5bdd259337839d2_img.jpg)

20.2.1 EXTI connections between peripherals, CPU, and D3 domain

The peripherals able to generate wakeup events when the system is in Stop mode or the CPU is in CStop mode are connected to an EXTI Configurable event input or Direct Event input:

- • Peripheral signals that generate a pulse are connected to an EXTI Configurable Event input. For these events the EXTI provides a CPU status pending bit that has to be cleared.

- • Peripheral Interrupt and Wakeup sources that have to be cleared in the peripheral are connected to an EXTI Direct Event input. There is no CPU status pending bit within the EXTI. The Interrupt or Wakeup is cleared by the CPU in the peripheral.

The Event inputs able to wakeup D3 for autonomous Run mode are provided with a D3 domain pending request function, that has to be cleared. This clearing request is taken care of by the signal selected by the Pending clear selection.

The CPU interrupts are connected to their respective CPU NVIC, and, similarly, the CPU event is connected to the CPU rxev input.

The EXTI Wakeup signals are connected to the PWR block, and are used to wakeup the D3 domain and/or the CPU.

The D3 domain interrupts allow the system to trigger events for D3 domain autonomous Run mode operation.

20.3 EXTI functional description

Depending on the EXTI Event input type and wakeup target(s), different logic implementations are used. The applicable features are controlled from register bits:

- • Active trigger edge enable, by EXTI rising trigger selection register (EXTI_RTSR1) , EXTI rising trigger selection register (EXTI_RTSR2) , EXTI rising trigger selection register (EXTI_RTSR3) , and EXTI falling trigger selection register (EXTI_FTSR1) , EXTI falling trigger selection register (EXTI_FTSR2) , EXTI falling trigger selection register (EXTI_FTSR3)

- • Software trigger, by EXTI software interrupt event register (EXTI_SWIER1) , EXTI software interrupt event register (EXTI_SWIER2) , EXTI software interrupt event register (EXTI_SWIER3)

- • CPU Interrupt enable, by EXTI interrupt mask register (EXTI_CPUIMR1) , EXTI interrupt mask register (EXTI_CPUIMR2) , EXTI interrupt mask register (EXTI_CPUIMR3)

- • CPU Event enable, by EXTI event mask register (EXTI_CPEUMR1) , EXTI event mask register (EXTI_CPEUMR2) , EXTI event mask register (EXTI_CPEUMR3)

- • D3 domain wakeup pending, by EXTI D3 pending mask register (EXTI_D3PMR1) , EXTI D3 pending mask register (EXTI_D3PMR2) , EXTI D3 pending mask register (EXTI_D3PMR3)

Table 141. EXTI Event input configurations and register control (1)

| Event input type | Wakeup target(s) | Logic implementation | EXTI_RTSR | EXTI_FTSR | EXTI_SWIER | EXTI_CPUIMR | EXTI_CPEUMR | EXTI_D3PMR |

|---|---|---|---|---|---|---|---|---|

| Configurable | CPU | Configurable event input, CPU wakeup logic | X | X | X | X | X | - |

| Any (2) | Configurable event input, Any wakeup logic | X | ||||||

| Direct | CPU | Direct event input, CPU wakeup logic | - | - | - | X | X | - |

| Any (2) | Direct event input, Any wakeup logic | X |

1. X indicates that functionality is available.

2. Waking-up D3 domain for autonomous Run mode, and/or CPU.

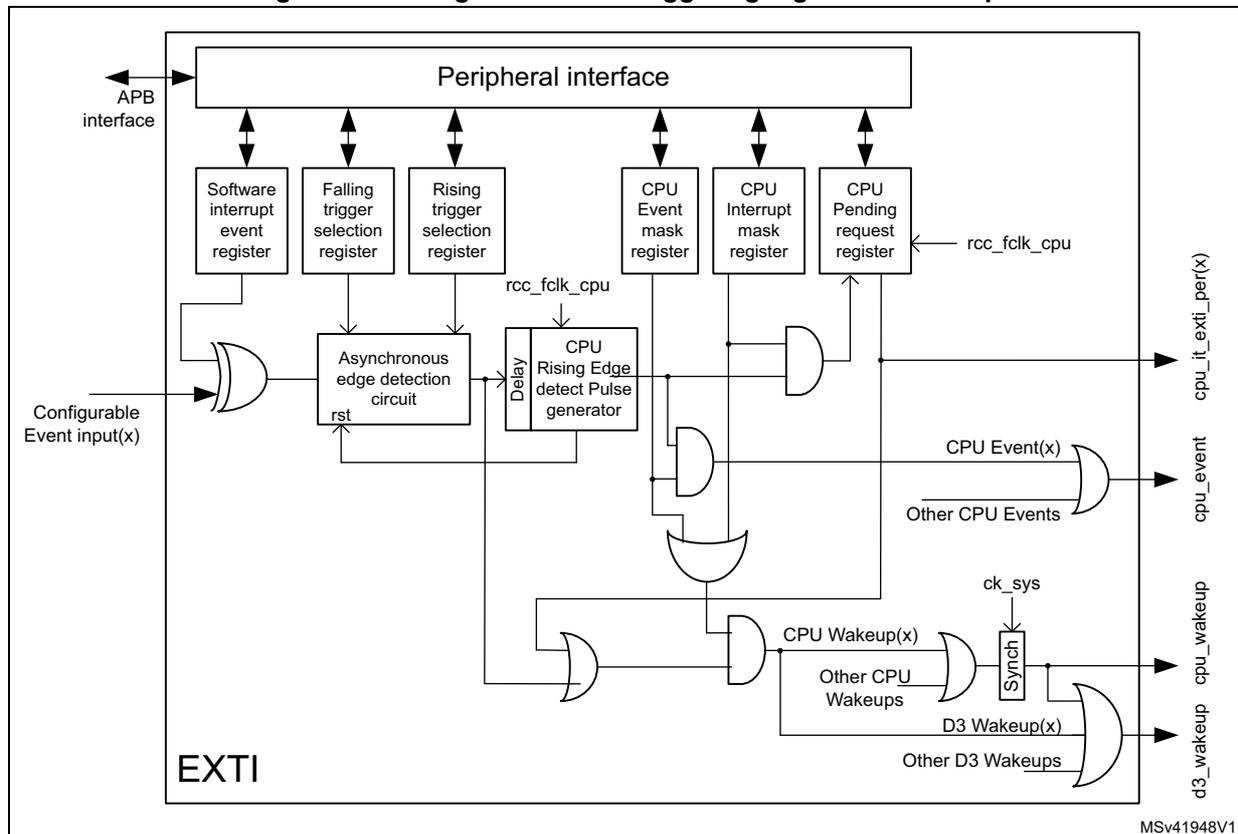

20.3.1 EXTI configurable event input - CPU wakeup

Figure 93 is a detailed representation of the logic associated with Configurable Event inputs which will always wake up the CPU.

Figure 92. Configurable event triggering logic CPU wakeup

The Software interrupt event register allows the system to trigger Configurable events by software, writing the EXTI software interrupt event register (EXTI_SWIER1) , the EXTI software interrupt event register (EXTI_SWIER2) , or the EXTI software interrupt event register (EXTI_SWIER3) register bit.

The rising edge EXTI rising trigger selection register (EXTI_RTSR1) , EXTI rising trigger selection register (EXTI_RTSR2) , EXTI rising trigger selection register (EXTI_RTSR3) , and falling edge EXTI falling trigger selection register (EXTI_FTSR1) , EXTI falling trigger selection register (EXTI_FTSR2) , EXTI falling trigger selection register (EXTI_FTSR3) selection registers allow the system to enable and select the Configurable event active trigger edge or both edges.

The devices feature dedicated interrupt mask registers, namely EXTI interrupt mask register (EXTI_CPUIMR1) and EXTI interrupt mask register (EXTI_CPUIMR2) , EXTI interrupt mask register (EXTI_CPUIMR3) , and EXTI pending register (EXTI_CPUPR1) , EXTI pending register (EXTI_CPUPR2) , EXTI pending register (EXTI_CPUPR3) for Configurable events pending request registers. The CPU pending register will only be set for an unmasks CPU interrupt. Each event provides a individual CPU interrupt to the CPU NVIC. The Configurable events interrupts need to be acknowledged by software in the EXTI_CPUPR register.

The devices feature dedicated event mask registers, i.e. EXTI event mask register (EXTI_CPUEMR1) , EXTI event mask register (EXTI_CPUEMR2) , and EXTI event mask register (EXTI_CPUEMR3) . The enabled event then generates an event on the CPU. All events for a CPU are OR-ed together into a single CPU event signal. The CPU Pending register (EXTI_CPUPR) will not be set for an unmasked CPU event.

When a CPU interrupt or CPU event is enabled, the Asynchronous edge detection circuit is reset by the clocked Delay and Rising edge detect pulse generator. This guarantees that the CPU clock is woken up before the Asynchronous edge detection circuit is reset.

Note: A detected Configurable event, enabled by the CPU, is only cleared when the CPU wakes up.

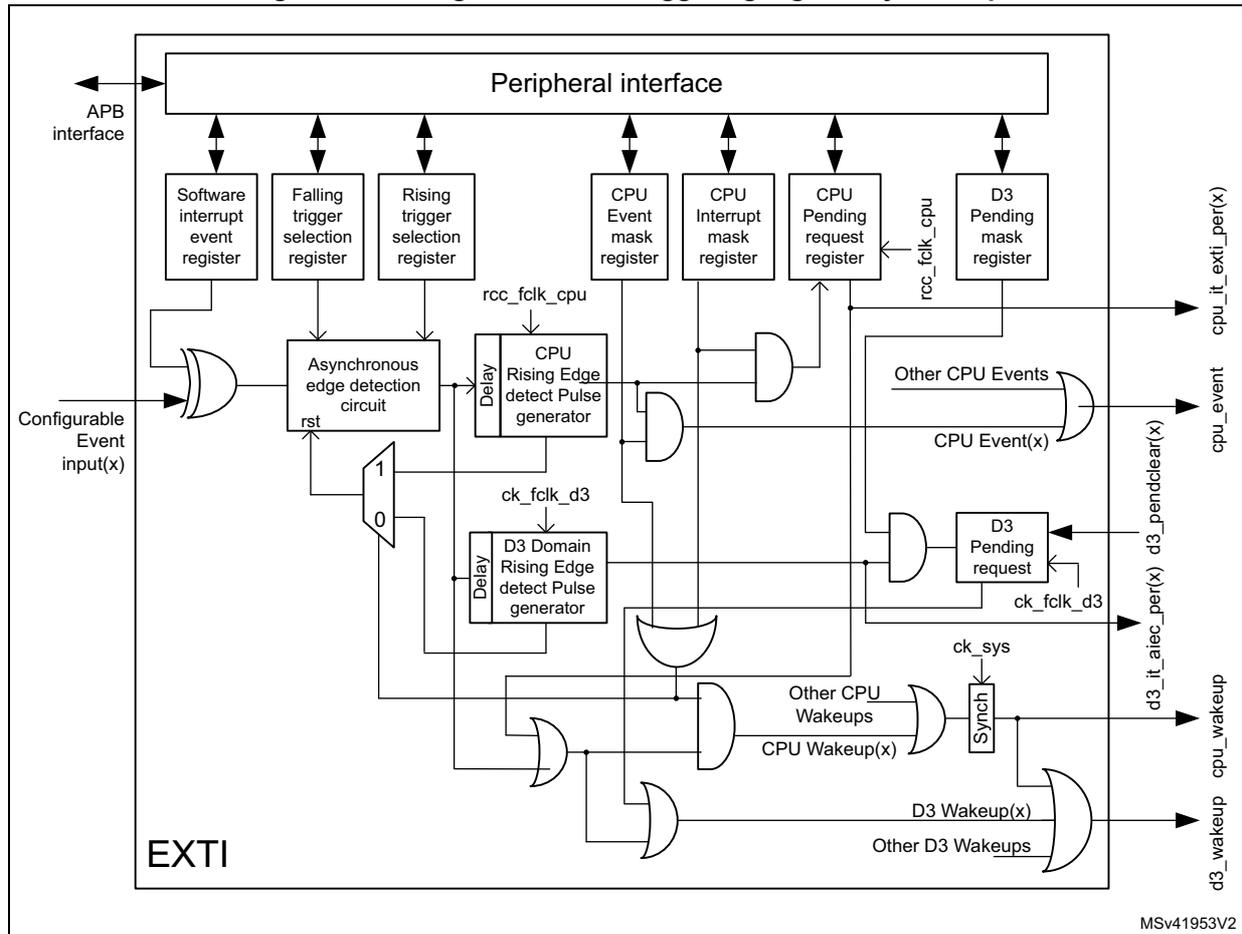

20.3.2 EXTI configurable event input - any wakeup

Figure 93 is a detailed representation of the logic associated with Configurable Event inputs that can wakeup D3 domain for autonomous Run mode and/or CPU (“Any” target). It provides the same functionality as the Configurable event input CPU wakeup, with additional functionality to wake up the D3 domain independently.

When all CPU interrupts and CPU events are disabled, the Asynchronous edge detection circuit is reset by the D3 domain clocked Delay and Rising edge detect pulse generator. This guarantees that the D3 domain clock is woken up before the Asynchronous edge detection circuit is reset.

Table 142. Configurable event input asynchronous edge detector reset

| EXTI_C1IMR | EXTI_C1EMR | Asynchronous edge detector reset by |

|---|---|---|

| Both = 0 | D3 domain clock rising edge detect pulse generator | |

| At least one = 1 | CPU clock rising edge detect pulse generator | |

Figure 93. Configurable event triggering logic - any wakeup

The diagram illustrates the internal architecture of the EXTI block for the 'any wakeup' target. At the top, a 'Peripheral interface' block is connected to an 'APB interface'. Below it, several registers are shown: 'Software interrupt event register', 'Falling trigger selection register', 'Rising trigger selection register', 'CPU Event mask register', 'CPU Interrupt mask register', 'CPU Pending request register', and 'D3 Pending mask register'. The 'CPU Pending request register' is connected to the 'D3 Pending mask register' via a signal labeled 'rcv_folk_cpu'. The 'Falling trigger selection register' and 'Rising trigger selection register' are connected to an 'Asynchronous edge detection circuit' which also receives 'Configurable Event input(x)'. The output of this circuit is connected to a 'Delay' block and a 'CPU Rising Edge detect Pulse generator'. The 'CPU Rising Edge detect Pulse generator' is connected to the 'CPU Event mask register' and the 'CPU Interrupt mask register'. The 'CPU Event mask register' and 'CPU Interrupt mask register' are connected to an AND gate. The output of this AND gate is connected to the 'CPU Pending request register' and the 'D3 Pending mask register'. The 'D3 Pending mask register' is connected to a 'D3 Pending request' block. The 'D3 Pending request' block is connected to the 'D3 Domain Rising Edge detect Pulse generator'. The 'D3 Domain Rising Edge detect Pulse generator' is connected to the 'CPU Pending request register' and the 'D3 Pending mask register'. The 'CPU Pending request register' and the 'D3 Pending request' block are connected to an OR gate labeled 'CPU Event(x)'. The output of this OR gate is connected to the 'cpu_event' output. The 'CPU Event(x)' output is connected to the 'cpu_it_exti_per(x)' output. The 'CPU Event(x)' output is also connected to an OR gate labeled 'CPU Wakeup(x)'. The output of this OR gate is connected to a 'Synch' block. The 'Synch' block is connected to the 'cpu_wakeup' output. The 'CPU Wakeup(x)' output is also connected to an OR gate labeled 'D3 Wakeup(x)'. The output of this OR gate is connected to the 'd3_wakeup' output. The 'D3 Wakeup(x)' output is also connected to an OR gate labeled 'Other D3 Wakeups'. The output of this OR gate is connected to the 'd3_it_aiec_per(x)' output. The 'd3_it_aiec_per(x)' output is also connected to the 'd3_pendclear(x)' output. The 'd3_pendclear(x)' output is connected to the 'D3 Pending request' block. The 'Synch' block is also connected to the 'ck_sys' clock signal. The 'CPU Rising Edge detect Pulse generator' is also connected to the 'rcv_folk_cpu' signal. The 'D3 Domain Rising Edge detect Pulse generator' is also connected to the 'ck_folk_d3' signal. The 'Synch' block is also connected to the 'ck_folk_d3' signal. The 'EXTI' label is at the bottom left of the diagram. The reference 'MSv41953V2' is at the bottom right.

The event triggering logic for “Any” target has additional D3 Pending mask register EXTI D3 pending mask register (EXTI_D3PMR1) , EXTI D3 pending mask register (EXTI_D3PMR2) , EXTI D3 pending mask register (EXTI_D3PMR3) and D3 Pending request logic. The D3 Pending request logic will only be set for unmasked D3 Pending events. The D3 Pending request logic keeps the D3 domain in Run mode until the D3 Pending request logic is cleared by the selected D3 domain pendclear source.

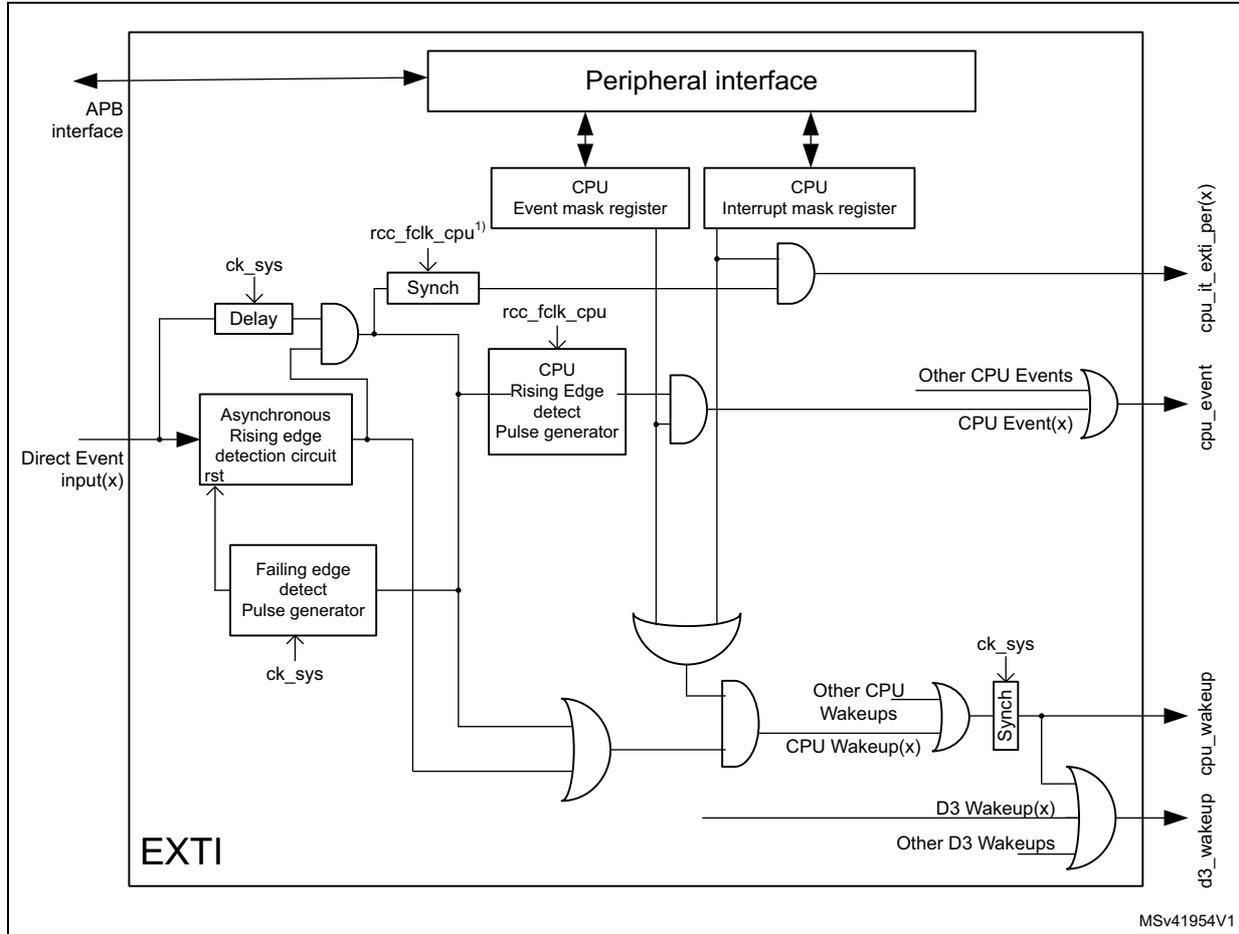

20.3.3 EXTI direct event input - CPU wakeup

Figure 94 is a detailed representation of the logic associated with Direct Event inputs waking up the CPU.

Direct events only provide CPU interrupt enable and CPU event enable functionality.

Figure 94. Direct event triggering logic CPU wakeup

- 1. The CPU interrupt for asynchronous Direct Event inputs (peripheral Wakeup signals) is synchronized with the CPU clock. The synchronous Direct Event inputs (peripheral interrupt signals), after the asynchronous edge detection, are directly sent to the CPU interrupt without resynchronization.

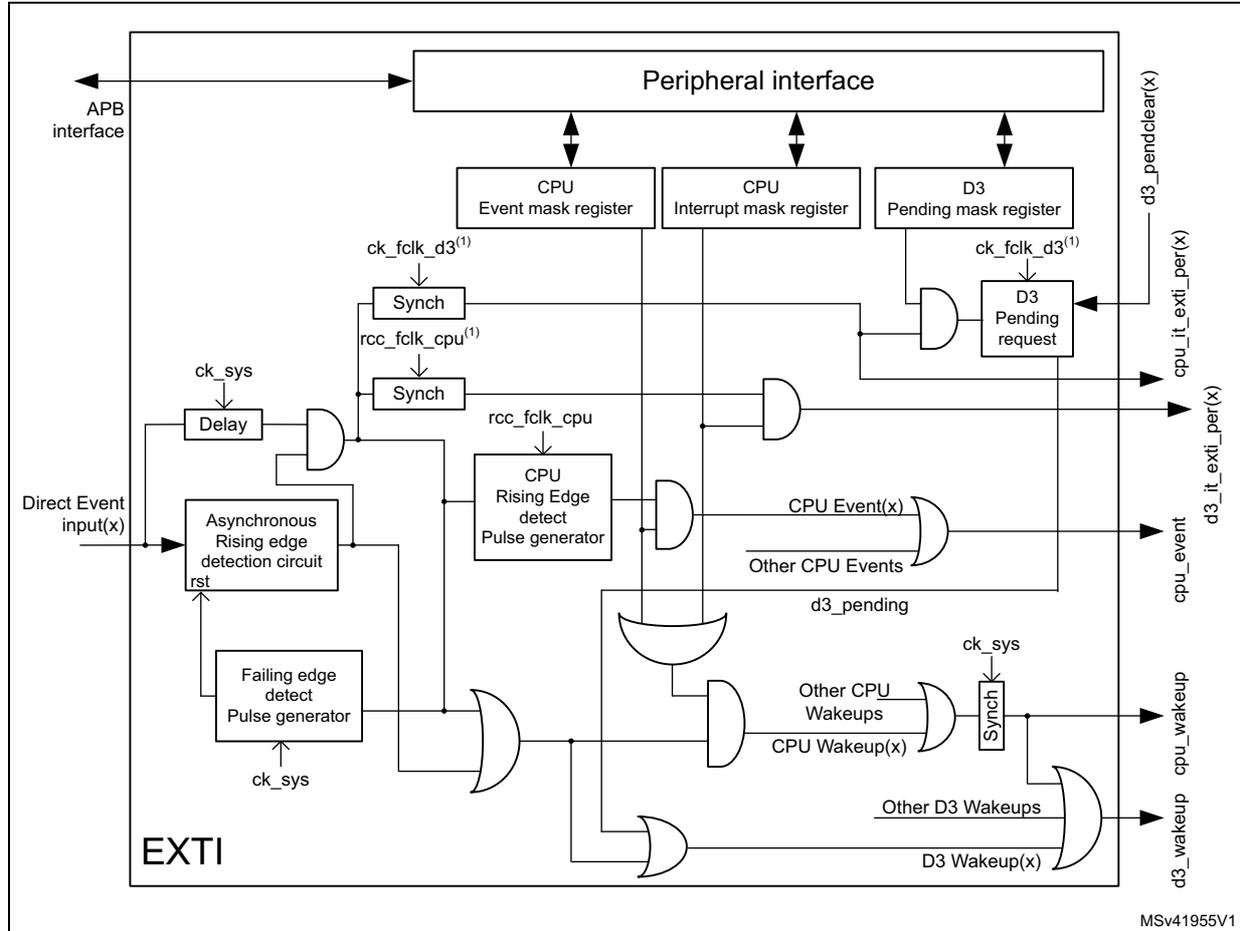

20.3.4 EXTI direct event input - any wakeup

Figure 95 is a detailed representation of the logic associated with Direct Event inputs waking up D3 domain for autonomous Run mode and/or CPU, (“Any” target). It provides the same functionality as the Direct event input CPU wakeup, plus additional functionality to wakeup the D3 domain independently.

Figure 95. Direct event triggering logic - any wakeup

- 1. The CPU interrupt and D3 domain interrupt for asynchronous Direct Event inputs (peripheral Wakeup signals) are synchronized, respectively, with the CPU clock and the D3 domain clock. The synchronous Direct Event inputs (peripheral interrupt signals), after the asynchronous edge detection, are directly sent to the CPU interrupt and the D3 domain interrupt without resynchronization in the EXTI.

20.3.5 EXTI D3 pending request clear selection

Event inputs able to wake up D3 domain for autonomous Run mode have D3 Pending request logic that can be cleared by the selected D3 pendclear source. For each D3 Pending request a D3 domain pendclear source can be selected from four different inputs.

Figure 96 is a detailed representation of the logic selecting the D3 pendclear source.

![Figure 96: D3 domain pending request clear logic diagram. The diagram shows an APB interface connected to a Peripheral interface. The Peripheral interface is connected to a D3 pending clear selection register. The register is connected to a multiplexer. The multiplexer has four inputs: d3_pendclear_in[0] (DMA_ch6_evt), d3_pendclear_in[1] (DMA_ch7_evt), d3_pendclear_in[2] (LPTIM4 out), and d3_pendclear_in[3] (LPTIM5 out). The output of the multiplexer is connected to a D3 pending request block. The D3 pending request block is connected to an Event(x) block. The Event(x) block is connected to the APB interface. The diagram is labeled MS40541V2.](/RM0468-STM32H723-733-725-735-730/33d9e32beba1c91457a1b240abc33809_img.jpg)

Figure 96. D3 domain pending request clear logic

The diagram illustrates the logic for clearing a D3 pending request. An APB interface connects to a Peripheral interface, which in turn connects to a D3 pending clear selection register. This register controls a multiplexer that selects from four potential sources: d3_pendclear_in[0] (DMA_ch6_evt), d3_pendclear_in[1] (DMA_ch7_evt), d3_pendclear_in[2] (LPTIM4 out), and d3_pendclear_in[3] (LPTIM5 out). The selected source is fed into a D3 pending request block, which is part of the EXTI logic and connected to Event(x) inputs. The entire logic block is labeled 'EXTI' and 'MS40541V2'.

The D3 Pending request clear selection registers EXTI D3 pending clear selection register low (EXTI_D3PCR1L) , EXTI D3 pending clear selection register high (EXTI_D3PCR1H) , EXTI D3 pending clear selection register low (EXTI_D3PCR2L) , EXTI D3 pending clear selection register high (EXTI_D3PCR2H) , EXTI D3 pending clear selection register low (EXTI_D3PCR2L) and EXTI D3 pending clear selection register high (EXTI_D3PCR3H) allow the system to select the source to reset the D3 Pending request.

20.4 EXTI event input mapping

For the sixteen GPIO Event inputs the associated IOPORT pin has to be selected in the SYSCFG register SYSCFG_EXTICRn. The same pin from each IOPORT maps to the corresponding EXTI Event input.

The wakeup capabilities of each Event input are detailed in Table 143 . An Event input can either wake up the CPU, and in the case of “Any” can also wake up D3 domain for autonomous Run mode.

The EXTI Event inputs with a connection to the CPU NVIC are indicated in the Connection to NVIC column. For the EXTI events not having a connection to the NVIC, the peripheral interrupt is directly connected to the NVIC in parallel with the connection to the EXTI.

All EXTI Event inputs are OR-ed together and connected to the CPU event input (rxev).

Table 143. EXTI Event input mapping

| Event input | Source | Event input type | Wakeup target(s) | Connection to NVIC |

|---|---|---|---|---|

| 0 - 15 | EXTI[15:0] | Configurable | Any | Yes |

| 16 | PVD and AVD (1) | Configurable | CPU only | Yes |

| 17 | RTC alarms | Configurable | CPU only | Yes |

| 18 | RTC tamper, RTC timestamp, RCC LSECSS (2) | Configurable | CPU only | Yes |

| 19 | RTC wakeup timer | Configurable | Any | Yes |

| 20 | COMP1 | Configurable | Any | Yes |

| 21 | COMP2 | Configurable | Any | Yes |

| 22 | I2C1 wakeup | Direct | CPU only | Yes |

| 23 | I2C2 wakeup | Direct | CPU only | Yes |

| 24 | I2C3 wakeup | Direct | CPU only | Yes |

| 25 | I2C4 wakeup | Direct | Any | Yes |

| 26 | USART1 wakeup | Direct | CPU only | Yes |

| 27 | USART2 wakeup | Direct | CPU only | Yes |

| 28 | USART3 wakeup | Direct | CPU only | Yes |

| 29 | USART6 wakeup | Direct | CPU only | Yes |

| 30 | UART4 wakeup | Direct | CPU only | Yes |

| 31 | UART5 wakeup | Direct | CPU only | Yes |

| 32 | UART7 wakeup | Direct | CPU only | Yes |

| 33 | UART8 wakeup | Direct | CPU only | Yes |

| 34 | LPUART1 RX wakeup | Direct | Any | Yes |

| 35 | LPUART1 TX wakeup | Direct | Any | Yes |

| 36 | SPI1 wakeup | Direct | CPU only | Yes |

| 37 | SPI2 wakeup | Direct | CPU only | Yes |

| 38 | SPI3 wakeup | Direct | CPU only | Yes |

| 39 | SPI4 wakeup | Direct | CPU only | Yes |

| 40 | SPI5 wakeup | Direct | CPU only | Yes |

| 41 | SPI6 wakeup | Direct | Any | Yes |

| 42 | MDIO wakeup | Direct | CPU only | Yes |

| 43 | USB1 wakeup | Direct | CPU only | Yes |

| 44 | Reserved | - | - | - |

| 45 | Reserved | - | - | - |

| 46 | Reserved | - | - | - |

| 47 | LPTIM1 wakeup | Direct | CPU only | Yes |

| 48 | LPTIM2 wakeup | Direct | Any | Yes |

Table 143. EXTI Event input mapping (continued)

| Event input | Source | Event input type | Wakeup target(s) | Connection to NVIC |

|---|---|---|---|---|

| 49 | LPTIM2 output | Configurable | Any | No (3) |

| 50 | LPTIM3 wakeup | Direct | Any | Yes |

| 51 | LPTIM3 output | Configurable | Any | No (3) |

| 52 | LPTIM4 wakeup | Direct | Any | Yes |

| 53 | LPTIM5 wakeup | Direct | Any | Yes |

| 54 | SWPMI wakeup | Direct | CPU only | Yes |

| 55 | WKUP1 | Direct | CPU only | Yes |

| 56 | WKUP2 | Direct | CPU only | Yes |

| 57 | Reserved | - | - | - |

| 58 | WKUP4 | Direct | CPU only | Yes |

| 59 | Reserved | - | - | - |

| 60 | WKUP6 | Direct | CPU only | Yes |

| 61 | RCC interrupt | Direct | CPU only | No (4) |

| 62 | I2C4 Event interrupt | Direct | CPU only | No (4) |

| 63 | I2C4 Error interrupt | Direct | CPU only | No (4) |

| 64 | LPUART1 global Interrupt | Direct | CPU only | No (4) |

| 65 | SPI6 interrupt | Direct | CPU only | No (4) |

| 66 | BDMA CH0 interrupt | Direct | CPU only | No (4) |

| 67 | BDMA CH1 interrupt | Direct | CPU only | No (4) |

| 68 | BDMA CH2 interrupt | Direct | CPU only | No (4) |

| 69 | BDMA CH3 interrupt | Direct | CPU only | No (4) |

| 70 | BDMA CH4 interrupt | Direct | CPU only | No (4) |

| 71 | BDMA CH5 interrupt | Direct | CPU only | No (4) |

| 72 | BDMA CH6 interrupt | Direct | CPU only | No (4) |

| 73 | BDMA CH7 interrupt | Direct | CPU only | No (4) |

| 74 | DMAMUX2 interrupt | Direct | CPU only | No (4) |

| 75 | ADC3 interrupt | Direct | CPU only | No (4) |

| 76 | SAI4 interrupt | Direct | CPU only | No (4) |

| 77 | HSEM0 interrupt | Direct | CPU only | No |

| 78 | Reserved | - | - | - |

| 79 | Reserved | - | - | - |

| 80 | Reserved | - | - | - |

| 81 | Reserved | - | - | - |

| 82 | Reserved | - | - | - |

| 83 | Reserved | - | - | - |

Table 143. EXTI Event input mapping (continued)

| Event input | Source | Event input type | Wakeup target(s) | Connection to NVIC |

|---|---|---|---|---|

| 84 | Reserved | - | - | - |

| 85 | HDMI-CEC wakeup | Configurable | CPU only | Yes |

| 86 | ETHERNET wakeup | Configurable | CPU only | Yes |

| 87 | HSECSS interrupt | Direct | CPU only | No (4) |

| 88 | TEMP wakeup | Direct | Any | Yes |

| 89 | UART9 wakeup | Direct | CPU only | Yes |

| 90 | USART10 wakeup | Direct | CPU only | Yes |

| 91 | I2C5 wakeup | Direct | CPU only | Yes |

- 1. PVD and AVD signals are OR-ed together on the same EXTI event input.

- 2. RTC Tamper, RTC timestamp and RCC LSECSS signals are OR-ed together on the same EXTI event input.

- 3. Not available on CPU NVIC, to be used for system wakeup only or CPU event input (rxev).

- 4. Available on CPU NVIC directly from the peripheral

20.5 EXTI functional behavior

The Direct event inputs are enabled in the respective peripheral generating the event. The Configurable events are enabled by enabling at least one of the trigger edges.

When in Stop mode an event will always wake up the D3 domain. In system Run and Stop modes an event will always generate an associated D3 domain interrupt. An event will only wake up the CPU when the event associated CPU interrupt is unmasked and/or the CPU event is unmasked.

Table 144. Masking functionality

| CPU | Configurable event inputs PRx bits of EXTI_CPUPR | CPU | D3 domain wakeup | |||

|---|---|---|---|---|---|---|

| Interrupt enable MRx bits of EXTI_CPUIMR | Event enable MRx bits of EXTI_CPUREMR | Interrupt | Event | Wakeup | ||

| 0 | 0 | No | Masked | Masked | Masked | Yes (1) / Masked (2) |

| 0 | 1 | No | Masked | Yes | Yes | Yes |

| 1 | 0 | Status latched | Yes | Masked | Yes | Yes |

| 1 | 1 | Status latched | Yes | Yes | Yes | Yes |

- 1. Only for Event inputs that allow the system to wakeup D3 domain for autonomous Run mode (Any target).

- 2. For Event inputs that will always wake up CPU.

For Configurable event inputs, when the enabled edge(s) occur on the event input, an event request is generated. When the associated CPU interrupt is unmasked, the corresponding pending PRx bit in EXTI_CPUPR is set and the CPU interrupt signal is activated. EXTI_CPUPR PRx pending bit shall be cleared by software writing it to '1'. This will clear the CPU interrupt.

For Direct event inputs, when enabled in the associated peripheral, an event request is generated on the rising edge only. There is no corresponding CPU pending bit. When the associated CPU interrupt is unmasked the corresponding CPU interrupt signal is activated.

The CPU event has to be unmasked to generate an event. When the enabled edge(s) occur on the Event input a CPU event pulse is generated. There is no CPU event pending bit.

Both a CPU interrupt and a CPU event may be enabled on the same Event input. They will both trigger the same Event input condition(s).

For the Configurable Event inputs an event input request can be generated by software when writing a '1' in the software interrupt/event register EXTI_SWIER.

Whenever an Event input is enabled and a CPU interrupt and/or CPU event is unmasked, the Event input will also generate a D3 domain wakeup next to the CPU wakeup.

Some Event inputs are able to wakeup the D3 domain autonomous Run mode, in this case the CPU interrupt and CPU event are masked, preventing the CPU to be woken up. Two D3 domain autonomous Run mode wakeup mechanisms are supported:

- • D3 domain wakeup without pending (EXTI_D3PMR = 0)

- – On a Configurable Event input this mechanism will wake up D3 domain and clear the D3 domain wakeup signal automatically after the Delay + Rising Edge detect Pulse generator.

- – On a Direct Event input this mechanism will wake up D3 domain and clear the D3 domain wakeup signal after the Direct Event input signal is cleared.

- • D3 domain wakeup with pending (EXTI_D3PMR = 1)

- – On a Configurable Event input this mechanism will wake up D3 domain and clear the D3 domain wakeup signal after the Delay + Rising Edge detect Pulse generator and when the D3 Pending request is cleared.

- – On a Direct Event input this mechanism will wake up D3 domain and clear the D3 domain wakeup signal after the Direct Event input signal is cleared and when the D3 Pending request is cleared.

20.5.1 EXTI CPU interrupt procedure

- • Unmask the Event input interrupt by setting the corresponding mask bits in the EXTI_CPUIMR register.

- • For Configurable Event inputs, enable the event input by setting either one or both the corresponding trigger edge enable bits in EXTI_RTSR and EXTI_FTSR registers.

- • Enable the associated interrupt source in the CPU NVIC or use the SEVONPEND, so that an interrupt coming from the CPU interrupt signal is detectable by the CPU after a WFI/WFE instruction.

- – For Configurable event inputs the associated EXTI pending bit needs to be cleared.

20.5.2 EXTI CPU event procedure

- • Unmask the Event input by setting the corresponding mask bits of the EXTI_CPUEMR register.

- • For Configurable Event inputs, enable the event input by setting either one or both the corresponding trigger edge enable bits in EXTI_RTSR and EXTI_FTSR registers.

- • The CPU event signal is detected by the CPU after a WFE instruction.

- – For Configurable event inputs there is no EXTI pending bit to clear.

20.5.3 EXTI CPU wakeup procedure

- • Unmask the Event input by setting at least one of the corresponding mask bits in the EXTI_CPUIMR and/or EXTI_CPUEMR registers. The CPU wakeup is generated at the same time as the unmasked CPU interrupt and/or CPU event.

- • For Configurable Event inputs, enable the event input by setting either one or both the corresponding trigger edge enable bits in EXTI_RTSR and EXTI_FTSR registers.

- • Direct Events will automatically generate a CPU wakeup.

20.5.4 EXTI D3 domain wakeup for autonomous Run mode procedure

- • Mask the Event input for waking up the CPU, by clearing both the corresponding mask bits in the EXTI_CPUIMR and/or EXTI_CPUEMR registers.

- • For Configurable Event inputs, enable the event input by setting either one or both the corresponding trigger edge enable bits in EXTI_RTSR and EXTI_FTSR registers.

- • Direct Events will automatically generate a D3 domain wakeup.

- • Select the D3 domain wakeup mechanism in EXTI_D3PMR.

- – When D3 domain wakeup without pending (EXTI_PMR = 0) is selected, the Wakeup will be cleared automatically following the clearing of the Event input.

- – When D3 domain wakeup with pending (EXTI_PMR = 1) is selected the Wakeup needs to be cleared by a selected D3 domain pendclear source.

A pending D3 domain wakeup signal can also be cleared by FW clearing the associated EXTI_D3PMR register bit.

- • After the D3 domain wakeup a D3 domain interrupt is generated.

- – Configurable Event inputs will generate a pulse on D3 domain interrupt.

- – Direct Event inputs will activate the D3 domain interrupt until the event input is cleared in the peripheral.

20.5.5 EXTI software interrupt/event trigger procedure

Any of the Configurable Event inputs can be triggered from the software interrupt/event register (the associated CPU interrupt and/or CPU event shall be enabled by their respective procedure).

- • Enable the Event input by setting at least one of the corresponding edge trigger bits in the EXTI_RTSR and/or EXTI_FTSR registers.

- • Unmask the software interrupt/event trigger by setting at least one of the corresponding mask bits in the EXTI_CPUIMR and/or EXTI_CPUEMR registers.

- • Trigger the software interrupt/event by writing “1” to the corresponding bit in the EXTI_SWIER register.

- • The Event input may be disabled by clearing the EXTI_RTSR and EXTI_FTSR register bits.

Note: An edge on the Configurable event input will also trigger an interrupt/event.

A software trigger can be used to set the D3 Pending request logic, keeping the D3 domain in Run until the D3 Pending request logic is cleared.

20.6 EXTI registers

Every register can only be accessed with 32-bit (word). A byte or half-word cannot be read or written.

20.6.1 EXTI rising trigger selection register (EXTI_RTSR1)

Address offset: 0x00

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR21 | TR20 | TR19 | TR18 | TR17 | TR16 |

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TR15 | TR14 | TR13 | TR12 | TR11 | TR10 | TR9 | TR8 | TR7 | TR6 | TR5 | TR4 | TR3 | TR2 | TR1 | TR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:0 TR[21:0] : Rising trigger event configuration bit of Configurable Event input x. (1)

0: Rising trigger disabled (for Event and Interrupt) for input line

1: Rising trigger enabled (for Event and Interrupt) for input line

- 1. The Configurable event inputs are edge triggered, no glitch must be generated on these inputs.

If a rising edge on the Configurable event input occurs during writing of the register, the associated pending bit will not be set.

Rising and falling edge triggers can be set for the same Configurable Event input. In this case, both edges generate a trigger.

20.6.2 EXTI falling trigger selection register (EXTI_FTSR1)

Address offset: 0x04

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR21 | TR20 | TR19 | TR18 | TR17 | TR16 |

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TR15 | TR14 | TR13 | TR12 | TR11 | TR10 | TR9 | TR8 | TR7 | TR6 | TR5 | TR4 | TR3 | TR2 | TR1 | TR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:0 TR[21:0] : Falling trigger event configuration bit of Configurable Event input x. (1)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line.

- 1. The Configurable event inputs are edge triggered, no glitch must be generated on these inputs.

If a falling edge on the Configurable event input occurs during writing of the register, the associated pending bit will not be set.

Rising and falling edge triggers can be set for the same Configurable Event input. In this case, both edges generate a trigger.

20.6.3 EXTI software interrupt event register (EXTI_SWIER1)

Address offset: 0x08

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SWIER 21 | SWIER 20 | SWIER 19 | SWIER 18 | SWIER 17 | SWIER 16 |

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SWIER 15 | SWIER 14 | SWIER 13 | SWIER 12 | SWIER 11 | SWIER 10 | SWIER 9 | SWIER 8 | SWIER 7 | SWIER 6 | SWIER 5 | SWIER 4 | SWIER 3 | SWIER 2 | SWIER 1 | SWIER 0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:0 SWIER[21:0] : Software interrupt on line x

This bitfield always returns 0 when read.

0: Writing 0 has no effect.

1: Writing a 1 to this bit will trigger an event on line x. This bit is auto cleared by HW.

20.6.4 EXTI D3 pending mask register (EXTI_D3PMR1)

Address offset: 0x0C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | MR25 | Res. | Res. | Res. | MR21 | MR20 | MR19 | Res. | Res. | Res. |

| rw | rw | rw | rw | ||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MR15 | MR14 | MR13 | MR12 | MR11 | MR10 | MR9 | MR8 | MR7 | MR6 | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:26 Reserved, must be kept at reset value.

Bit 25 MR25 : D3 Pending Mask on Event input x

0: D3 Pending request from Line x is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

Bits 24:22 Reserved, must be kept at reset value.

Bits 21:19 MR[21:19] : D3 Pending Mask on Event input x

0: D3 Pending request from Line x is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

Bits 18:16 Reserved, must be kept at reset value.

Bits 15:0 MR[15:0] : D3 Pending Mask on Event input x

0: D3 Pending request from Line x is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

20.6.5 EXTI D3 pending clear selection register low (EXTI_D3PCR1L)

Address offset: 0x10

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PCS15[1:0] | PCS14[1:0] | PCS13[1:0] | PCS12[1:0] | PCS11[1:0] | PCS10[1:0] | PCS9[1:0] | PCS8[1:0] | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PCS7[1:0] | PCS6[1:0] | PCS5[1:0] | PCS4[1:0] | PCS3[1:0] | PCS2[1:0] | PCS1[1:0] | PCS0[1:0] | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 PCS[15:0][1:0] : D3 Pending request clear input signal selection on Event input x = truncate (n/2)

00: DMA ch6 event selected as D3 domain pendclear source

01: DMA ch7 event selected as D3 domain pendclear source

10: LPTIM4 out selected as D3 domain pendclear source

11: LPTIM5 out selected as D3 domain pendclear source

20.6.6 EXTI D3 pending clear selection register high (EXTI_D3PCR1H)

Address offset: 0x14

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PCS25[1:0] | Res. | Res. | |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | PCS21[1:0] | PCS20[1:0] | PCS19[1:0] | Res. | Res. | Res. | Res. | Res. | Res. | |||

| rw | rw | rw | rw | rw | rw | ||||||||||

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:18 PCS25[1:0] : D3 Pending request clear input signal selection on Event input 25 = truncate \( ((n+32)/2) \)

- 00: DMA ch6 event selected as D3 domain pendclear source

- 01: DMA ch7 event selected as D3 domain pendclear source

- 10: LPTIM4 out selected as D3 domain pendclear source

- 11: LPTIM5 out selected as D3 domain pendclear source

Bits 17:12 Reserved, must be kept at reset value.

Bits 11:6 PCS[21:19][1:0] : D3 Pending request clear input signal selection on Event input x = truncate \( ((n+32)/2) \) (x = 21 to 19)

- 00: DMA ch6 event selected as D3 domain pendclear source

- 01: DMA ch7 event selected as D3 domain pendclear source

- 10: LPTIM4 out selected as D3 domain pendclear source

- 11: LPTIM5 out selected as D3 domain pendclear source

Bits 5:0 Reserved, must be kept at reset value.

20.6.7 EXTI rising trigger selection register (EXTI_RTSR2)

Address offset: 0x20

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR51 | Res. | TR49 | Res. |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:20 Reserved, must be kept at reset value.

Bit 19 TR51 : Rising trigger event configuration bit of Configurable Event input x+32. (1)

- 0: Rising trigger disabled (for Event and Interrupt) for input line

- 1: Rising trigger enabled (for Event and Interrupt) for input line

Bit 18 Reserved, must be kept at reset value.

Bit 17 TR49 : Rising trigger event configuration bit of Configurable Event input x+32. (1)

- 0: Rising trigger disabled (for Event and Interrupt) for input line

- 1: Rising trigger enabled (for Event and Interrupt) for input line

Bits 16:0 Reserved, must be kept at reset value.

- 1. The Configurable event inputs are edge triggered, no glitch must be generated on these inputs.

If a rising edge on the Configurable event input occurs during writing of the register, the associated pending bit will not be set.

Rising and falling edge triggers can be set for the same Configurable Event input. In this case, both edges generate a trigger.

20.6.8 EXTI falling trigger selection register (EXTI_FTSR2)

Address offset: 0x24

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR51 | Res. | TR49 | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:20 Reserved, must be kept at reset value.

Bit 19 TR51 : Falling trigger event configuration bit of Configurable Event input x+32. (1)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line

Bit 18 Reserved, must be kept at reset value.

Bit 17 TR49 : Falling trigger event configuration bit of Configurable Event input x+32. (1)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line

Bits 16:0 Reserved, must be kept at reset value.

- 1. The Configurable event inputs are edge triggered, no glitch must be generated on these inputs.

If a falling edge on the Configurable event input occurs during writing of the register, the associated pending bit will not be set.

Rising and falling edge triggers can be set for the same Configurable Event input. In this case, both edges generate a trigger.

20.6.9 EXTI software interrupt event register (EXTI_SWIER2)

Address offset: 0x28

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SWIER51 | Res. | SWIER49 | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:20 Reserved, must be kept at reset value.

Bit 19 SWIER51 : Software interrupt on line x+32

Will always return 0 when read.

0: Writing 0 has no effect.

1: Writing a 1 to this bit will trigger an event on line x. This bit is auto cleared by HW.

Bit 18 Reserved, must be kept at reset value.

Bit 17 SWIER49 : Software interrupt on line x+32

Will always return 0 when read.

0: Writing 0 has no effect.

1: Writing a 1 to this bit will trigger an event on line x. This bit is auto cleared by HW.

Bits 16:0 Reserved, must be kept at reset value.

20.6.10 EXTI D3 pending mask register (EXTI_D3PMR2)

Address offset: 0x2C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | MR53 | MR52 | MR51 | MR50 | MR49 | MR48 |

| rw | rw | rw | rw | rw | rw | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | MR41 | Res. | Res. | Res. | Res. | Res. | MR35 | MR34 | Res. | Res. |

| rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:16 MR[53:48] : D3 Pending Mask on Event input x+32

0: D3 Pending request from Line x+32 is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x+32 is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

Bits 15:10 Reserved, must be kept at reset value.

Bit 9 MR41 : D3 Pending Mask on Event input x+32

0: D3 Pending request from Line x+32 is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x+32 is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

Bits 8:4 Reserved, must be kept at reset value.

Bits 3:2 MR[35:34] : D3 Pending Mask on Event input x+32

0: D3 Pending request from Line x+32 is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x+32 is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

Bits 1:0 Reserved, must be kept at reset value.

20.6.11 EXTI D3 pending clear selection register low (EXTI_D3PCR2L)

Address offset: 0x30

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PCS41[1:0] | Res. | Res. | |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PCS35[1:0] | PCS34[1:0] | Res. | Res. | Res. | Res. | ||

| rw | rw | rw | rw | ||||||||||||

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:18 PCS41[1:0] : D3 Pending request clear input signal selection on Event input x = truncate \( ((n+64)/2) \)

- 00: DMA ch6 event selected as D3 domain pendclear source

- 01: DMA ch7 event selected as D3 domain pendclear source

- 10: LPTIM4 out selected as D3 domain pendclear source

- 11: LPTIM5 out selected as D3 domain pendclear source

Bits 17:8 Reserved, must be kept at reset value.

Bits 7:4 PCS[35:34][1:0] : D3 Pending request clear input signal selection on Event input x= truncate \( ((n+64)/2) \)

- 00: DMA ch6 event selected as D3 domain pendclear source

- 01: DMA ch7 event selected as D3 domain pendclear source

- 10: LPTIM4 out selected as D3 domain pendclear source

- 11: LPTIM5 out selected as D3 domain pendclear source

Bits 3:0 Reserved, must be kept at reset value.

20.6.12 EXTI D3 pending clear selection register high (EXTI_D3PCR2H)

Address offset: 0x34

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | PCS53[1:0] | PCS52[1:0] | PCS51[1:0] | PCS50[1:0] | PCS49[1:0] | PCS48[1:0] | ||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 PCS[53:48][1:0] : D3 Pending request clear input signal selection on Event input x= truncate \( ((n+96)/2) \)

00: DMA ch6 event selected as D3 domain pendclear source

01: DMA ch7 event selected as D3 domain pendclear source

10: LPTIM4 out selected as D3 domain pendclear source

11: LPTIM5 out selected as D3 domain pendclear source

20.6.13 EXTI rising trigger selection register (EXTI_RTSR3)

Address offset: 0x40

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR86 | TR85 | Res. | Res. | Res. | Res. | Res. |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:23 Reserved, must be kept at reset value.

Bits 22:21 TR[86:85] : Rising trigger event configuration bit of Configurable Event input x+64. (1)

0: Rising trigger disabled (for Event and Interrupt) for input line

1: Rising trigger enabled (for Event and Interrupt) for input line

Bits 20:0 Reserved, must be kept at reset value.

- The Configurable event inputs are edge triggered, no glitch must be generated on these inputs.

If a rising edge on the Configurable event input occurs during writing of the register, the associated pending bit will not be set.

Rising and falling edge triggers can be set for the same Configurable Event input. In this case, both edges generate a trigger.

20.6.14 EXTI falling trigger selection register (EXTI_FTSR3)

Address offset: 0x44

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR86 | TR85 | Res. | Res. | Res. | Res. | Res. |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:23 Reserved, must be kept at reset value.

Bits 22:21 TR[86:85] : Falling trigger event configuration bit of Configurable Event input x+64. (1)

0: Falling trigger disabled (for Event and Interrupt) for input line

1: Falling trigger enabled (for Event and Interrupt) for input line

Bits 20:0 Reserved, must be kept at reset value.

- 1. The Configurable event inputs are edge triggered, no glitch must be generated on these inputs.

If a falling edge on the Configurable event input occurs during writing of the register, the associated pending bit will not be set.

Rising and falling edge triggers can be set for the same Configurable Event input. In this case, both edges generate a trigger.

20.6.15 EXTI software interrupt event register (EXTI_SWIER3)

Address offset: 0x48

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SWIER 86 | SWIER 85 | Res. | Res. | Res. | Res. | Res. |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:23 Reserved, must be kept at reset value.

Bits 22:21 SWIER[86:85] : Software interrupt on line x+64

Will alway return 0 when read.

0: Writing 0 has no effect.

1: Writing a 1 to this bit will trigger an event on line x. This bit is auto cleared by HW.

Bits 20:0 Reserved, must be kept at reset value.

20.6.16 EXTI D3 pending mask register (EXTI_D3PMR3)

Address offset: 0x4C

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | MR88 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| rw | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:25 Reserved, must be kept at reset value.

Bit 24 MR88 : D3 Pending Mask on Event input x+64

0: D3 Pending request from Line x+64 is masked. Writing this bit to 0 will also clear the D3 Pending request.

1: D3 Pending request from Line x+64 is unmasked. The D3 domain pending signal when triggered will keep D3 domain wakeup active until cleared.

Bits 23:0 Reserved, must be kept at reset value.

20.6.17 EXTI D3 pending clear selection register high (EXTI_D3PCR3H)

Address offset: 0x54

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PCS88[1:0] | |

| rw | rw | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:18 Reserved, must be kept at reset value.

Bits 17:16 PCS88[1:0] : D3 Pending request clear input signal selection on Event input x= truncate \( \text{((n+160)/2)} \)

00: DMA ch6 event selected as D3 domain pendclear source

01: DMA ch7 event selected as D3 domain pendclear source

10: LPTIM4 out selected as D3 domain pendclear source

11: LPTIM5 out selected as D3 domain pendclear source

Bits 15:0 Reserved, must be kept at reset value.

20.6.18 EXTI interrupt mask register (EXTI_CPUIMR1)

Address offset: 0x80

Reset value: 0xFFC0 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MR31 | MR30 | MR29 | MR28 | MR27 | MR26 | MR25 | MR24 | MR23 | MR22 | MR21 | MR20 | MR19 | MR18 | MR17 | MR16 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MR15 | MR14 | MR13 | MR12 | MR11 | MR10 | MR9 | MR8 | MR7 | MR6 | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:22 MR[31:22] : CPU interrupt Mask on Direct Event input x (1)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

Bits 21:0 MR[21:0] : CPU interrupt Mask on Configurable Event input x (2)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

- 1. The reset value for Direct Event inputs is set to '1' in order to enable the interrupt by default.

- 2. The reset value for Configurable Event inputs is set to '0' in order to disable the interrupt by default.

20.6.19 EXTI event mask register (EXTI_CPUEMR1)

Address offset: 0x84

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MR31 | MR30 | MR29 | MR28 | MR27 | MR26 | MR25 | MR24 | MR23 | MR22 | MR21 | MR20 | MR19 | MR18 | MR17 | MR16 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MR15 | MR14 | MR13 | MR12 | MR11 | MR10 | MR9 | MR8 | MR7 | MR6 | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:0 MR[31:0] : CPU Event mask on Event input x

0: Event request from Line x is masked

1: Event request from Line x is unmasked

20.6.20 EXTI pending register (EXTI_CPUPR1)

Address offset: 0x88

Reset value: undefined

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PR21 | PR20 | PR19 | PR18 | PR17 | PR16 |

| rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PR15 | PR14 | PR13 | PR12 | PR11 | PR10 | PR9 | PR8 | PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

| rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 |

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:0 PR[21:0] : Configurable event inputs x Pending bit

0: No trigger request occurred

1: selected trigger request occurred

This bit is set when the selected edge event arrives on the external interrupt line. This bit is cleared by writing a 1 into the bit or by changing the sensitivity of the edge detector.

20.6.21 EXTI interrupt mask register (EXTI_CPUIMR2)

Address offset: 0x90

Reset value: 0xFFF5 FFFF

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MR63 | MR62 | MR61 | MR60 | Res. | MR58 | Res. | MR56 | MR55 | MR54 | MR53 | MR52 | MR51 | MR50 | MR49 | MR48 |

| rw | rw | rw | rw | rw | 1 | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MR47 | Res. | Res. | Res. | MR43 | MR42 | MR41 | MR40 | MR39 | MR38 | MR37 | MR36 | MR35 | MR34 | MR33 | MR32 |

| rw | 1 | 1 | 1 | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:28 MR[63:60] : CPU Interrupt Mask on Direct Event input x+32 (1) (x = 63 to 60)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

Bit 27 Reserved, must be kept at reset value (1) .

Bit 26 MR58 : CPU Interrupt Mask on Direct Event input 58+32 (1)

0: Interrupt request from Line 58 is masked

1: Interrupt request from Line 58 is unmasked

Bit 25 Reserved, must be kept at reset value (1) .

Bits 24:20 MR[56:52] : CPU Interrupt Mask on Direct Event input x+32 (1) (x = 56 to 52)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

Bit 19 MR51 : CPU interrupt Mask on Configurable Event input 51+32 (2)

0: Interrupt request from Line 51 is masked

1: Interrupt request from Line 51 is unmasked

Bit 18 MR50 : CPU Interrupt Mask on Direct Event input 50+32 (1)

0: Interrupt request from Line 50 is masked

1: Interrupt request from Line 50 is unmasked

Bit 17 MR49 : CPU interrupt Mask on Configurable Event input 49+32 (2)

0: Interrupt request from Line 49 is masked

1: Interrupt request from Line 49 is unmasked

Bits 16:15 MR[48:47] : CPU Interrupt Mask on Direct Event input x+32 (1) (x = 48 to 47)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

Bits 14:12 Reserved, must be kept at reset value (1) .

Bits 11:0 MR[43:32] : CPU Interrupt Mask on Direct Event input x+32 (1) (x = 43 to 32)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

- 1. The reset value for Direct Event inputs is set to '1' in order to enable the interrupt by default.

- 2. The reset value for Configurable Event inputs is set to '0' in order to disable the interrupt by default.

20.6.22 EXTI event mask register (EXTI_CPUEMR2)

Address offset: 0x94

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MR63 | MR62 | MR61 | MR60 | Res. | MR58 | Res. | MR56 | MR55 | MR54 | MR53 | MR52 | MR51 | MR50 | MR49 | MR48 |

| rw | rw | rw | rw | rw | 0 | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MR47 | Res. | Res. | Res. | MR43 | MR42 | MR41 | MR40 | MR39 | MR38 | MR37 | MR36 | MR35 | MR34 | MR33 | MR32 |

| rw | 0 | 0 | 0 | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:28 MR[63:60] : CPU Event mask on Event input x+32 (x = 63 to 60)

0: Event request from Line x is masked

1: Event request from Line x is unmasked

Bit 27 Reserved, must be kept at reset value.

Bit 26 MR[58] : CPU Event mask on Event input 58+32

0: Event request from Line 58 is masked

1: Event request from Line 58 is unmasked

Bit 25 Reserved, must be kept at reset value.

Bits 24:14 MR[56:47] : CPU Event mask on Event input x+32 (x = 56 to 47)

0: Event request from Line x is masked

1: Event request from Line x is unmasked

Bits 14:12 Reserved, must be kept at reset value.

Bits 11:0 MR[43:0] : CPU Event mask on Event input x+32 (x = 43 to 0)

0: Event request from Line x is masked

1: Event request from Line x is unmasked

20.6.23 EXTI pending register (EXTI_CPUPR2)

Address offset: 0x98

Reset value: undefined

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PR51 | Res. | PR49 | Res. |

| rc_w1 | rc_w1 | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:20 Reserved, must be kept at reset value.

Bit 19 PR51 : Configurable event inputs 51+32 Pending bit

0: No trigger request occurred

1: selected trigger request occurred

This bit is set when the selected edge event arrives on the external interrupt line. This bit is cleared by writing a 1 into the bit or by changing the sensitivity of the edge detector.

Bit 18 Reserved, must be kept at reset value.

Bit 17 PR49 : Configurable event inputs 49+32 Pending bit

0: No trigger request occurred

1: selected trigger request occurred

This bit is set when the selected edge event arrives on the external interrupt line. This bit is cleared by writing a 1 into the bit or by changing the sensitivity of the edge detector.

Bits 16:0 Reserved, must be kept at reset value.

20.6.24 EXTI interrupt mask register (EXTI_CPUIMR3)

Address offset: 0xA0

Reset value: 0x0F8B FFFF

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | MR91 | MR90 | MR89 | MR88 | MR87 | MR86 | MR85 | Res. | Res. | Res. | Res. | MR80 |

| rw | rw | rw | rw | rw | rw | rw | rw | ||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | MR78 | MR77 | MR76 | MR75 | MR74 | MR73 | MR72 | MR71 | MR70 | MR69 | MR68 | MR67 | MR66 | MR65 | MR64 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:23 MR[91:87] : CPU Interrupt Mask on Direct Event input x+64 (1) (x = 91 to 87)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

Bits 22:21 MR[86:85] : CPU interrupt Mask on Configurable Event input x+64 (2) (x = 86 to 85)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

Bits 20:17 Reserved, must be kept at reset value.

Bit 16 MR16 : CPU Interrupt Mask on Direct Event input 80+64 (1)

0: Interrupt request from Line 80 is masked

1: Interrupt request from Line 80 is unmasked

Bit 15 Reserved, must be kept at reset value.

Bits 14:0 MR[78: 64] : CPU Interrupt Mask on Direct Event input x+64 (1) (x = 78 to 64)

0: Interrupt request from Line x is masked

1: Interrupt request from Line x is unmasked

- 1. The reset value for Direct Event inputs is set to '1' in order to enable the interrupt by default.

- 2. The reset value for Configurable Event inputs is set to '0' in order to disable the interrupt by default.

20.6.25 EXTI event mask register (EXTI_CPUEMR3)

Address offset: 0xA4

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | MR91 | MR90 | MR89 | MR88 | MR87 | MR86 | MR85 | Res. | Res. | Res. | Res. | MR80 |

| rw | rw | rw | rw | rw | rw | rw | rw | ||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | MR78 | MR77 | MR76 | MR75 | MR74 | MR73 | MR72 | MR71 | MR70 | MR69 | MR68 | MR67 | MR66 | MR65 | MR64 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:21 MR[91:21] : CPU Event mask on Event input x+64 (x = 91 to 21)

0: Event request from Line x is masked

1: Event request from Line x is unmasked

Bits 20:17 Reserved, must be kept at reset value.

Bit 16 MR80 : CPU Event mask on Event input 80+64

0: Event request from Line 80 is masked

1: Event request from Line 80 is unmasked

Bit 15 Reserved, must be kept at reset value.

Bits 14:0 MR[78:64] : CPU Event mask on Event input x+64 (x = 78 to 64)

0: Event request from Line x is masked

1: Event request from Line x is unmasked

20.6.26 EXTI pending register (EXTI_CPUPR3)

Address offset: 0xA8

Reset value: undefined

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PR86 | PR85 | PR84 | Res. | Res. | Res. | Res. |

| rc_w1 | rc_w1 | rc_w1 | |||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Bits 31:23 Reserved, must be kept at reset value.

Bits 22:0 PR[86:84] : Configurable event inputs x+64 Pending bit (x = 86 to 84)

0: No trigger request occurred

1: selected trigger request occurred

This bit is set when the selected edge event arrives on the external interrupt line. This bit is cleared by writing a 1 into the bit or by changing the sensitivity of the edge detector.

20.6.27 EXTI register map

The following table gives the EXTI register map and the reset values.

Table 145. Asynchronous interrupt/event controller register map and reset values

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x00 | EXTI_RTSR1 | TR[21:0] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x04 | EXTI_FTSR1 | TR[21:0] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x08 | EXTI_SWIER1 | SWIER[21:0] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x0C | EXTI_D3PMR1 | MR[21:19] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0x10 | EXTI_D3PCR1L | PCS[15] | PCS[14] | PCS[13] | PCS[12] | PCS[11] | PCS[10] | PCS[9] | PCS[8] | PCS[7] | PCS[6] | PCS[5] | PCS[4] | PCS[3] | PCS[2] | PCS[1] | PCS[0] | |||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||||||||||||||

| 0x14 | EXTI_D3PCR1H | PCS[25] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x20 | EXTI_RTSR2 | TR[51] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x24 | EXTI_FTSR2 | TR[49] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x28 | EXTI_SWIER2 | SWIER[51] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x2C | EXTI_D3PMR2 | MR[53:48] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x30 | EXTI_D3PCR2L | PCS[41] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x34 | EXTI_D3PCR2H | PCS[53] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x40 | EXTI_RTSR3 | TR[85] | ||||||||||||||||||||||||||||||||

| Reset value | 0 | |||||||||||||||||||||||||||||||||

Table 145. Asynchronous interrupt/event controller register map and reset values (continued)

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x44 | EXTI_FTSR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TR[86] | TR[85] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | 0 | |||||||||||||||||||||||||||||||

| 0x48 | EXTI_SWIER3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SWIER[86] | SWIER[85] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | 0 | |||||||||||||||||||||||||||||||

| 0x4C | EXTI_D3PMR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | MR[88] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | ||||||||||||||||||||||||||||||||

| 0x50 | EXTI_D3PCR3L | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | |||||||||||||||||||||||||||||||||

| 0x54 | EXTI_D3PCR3H | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PCS[88] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | 0 | |||||||||||||||||||||||||||||||

| 0x58-0x7C | Reserved | ||||||||||||||||||||||||||||||||

| 0x80 | EXTI_CPUIMR1 | MR[31:22] | MR[21:0] | ||||||||||||||||||||||||||||||

| Reset value | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0x84 | EXTI_CPUCPUE MR1 | MR[31:0] | |||||||||||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0x88 | EXTI_CPUPR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PR[21:0] | |||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||

| 0x90 | EXTI_CPUIMR2 | MR[63:52] | Res. | MR[58] | Res. | MR[56:52] | MR[51] | MR[50] | MR[49] | MR[48:47] | Res. | Res. | Res. | MR[43:32] | |||||||||||||||||||

| Reset value | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | ||||||

| 0x94 | EXTI_CPUEMR2 | MR[63:60] | Res. | MR[58] | Res. | MR[56:47] | Res. | Res. | Res. | MR[43:32] | |||||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||||

| 0x98 | EXTI_CPUPR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PR[51] | Res. | PR[49] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | 0 | |||||||||||||||||||||||||||||||

| 0xA0 | EXTI_CPUIMR3 | Res. | Res. | Res. | Res. | MR[91:85] | Res. | Res. | Res. | MR[80] | Res. | MR[78:64] | |||||||||||||||||||||

| Reset value | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |||||||||

| 0xA4 | EXTI_CPUEMR3 | Res. | Res. | Res. | Res. | MR[91:85] | Res. | Res. | Res. | MR[80] | Res. | MR[78:64] | |||||||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||

Table 145. Asynchronous interrupt/event controller register map and reset values (continued)

| Offset | Register name | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0xA8 | EXTI_CPUPR3 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PR[86] | PR[85] | PR[84] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| Reset value | 0 | 0 | 0 | |||||||||||||||||||||||||||||||

| 0xAC-0xBC | Reserved | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

Refer to Section 2.3 on page 131 for the register boundary addresses.