6. Power control (PWR)

6.1 Introduction

The Power control section (PWR) provides an overview of the supply architecture for the different power domains and of the supply configuration controller.

It also describes the features of the power supply supervisors and explains how the \( V_{\text{CORE}} \) supply domain is configured depending on the operating modes, the selected performance (clock frequency) and the voltage scaling.

6.2 PWR main features

- • Power supplies and supply domains

- – Core domains ( \( V_{\text{CORE}} = V_{\text{CAP}} \) )

- – \( V_{\text{DD}} \) domain

- – Backup domain ( \( V_{\text{SW}}, V_{\text{BKP}} \) )

- – Analog domain ( \( V_{\text{DDA}} \) )

- • System supply voltage regulation

- – Switched-mode power supply power-efficient voltage down-converter (SMPS step-down converter)

- – Voltage regulator (LDO)

- • Peripheral supply regulation

- – USB regulator

- • Power supply supervision

- – POR/PDR monitor

- – BOR monitor

- – PVD monitor

- – AVD monitor

- – \( V_{\text{BAT}} \) thresholds

- – Temperature thresholds

- • Power management

- – \( V_{\text{BAT}} \) battery charging

- – Operating modes

- – Voltage scaling control

- – Low-power modes

6.3 PWR block diagram

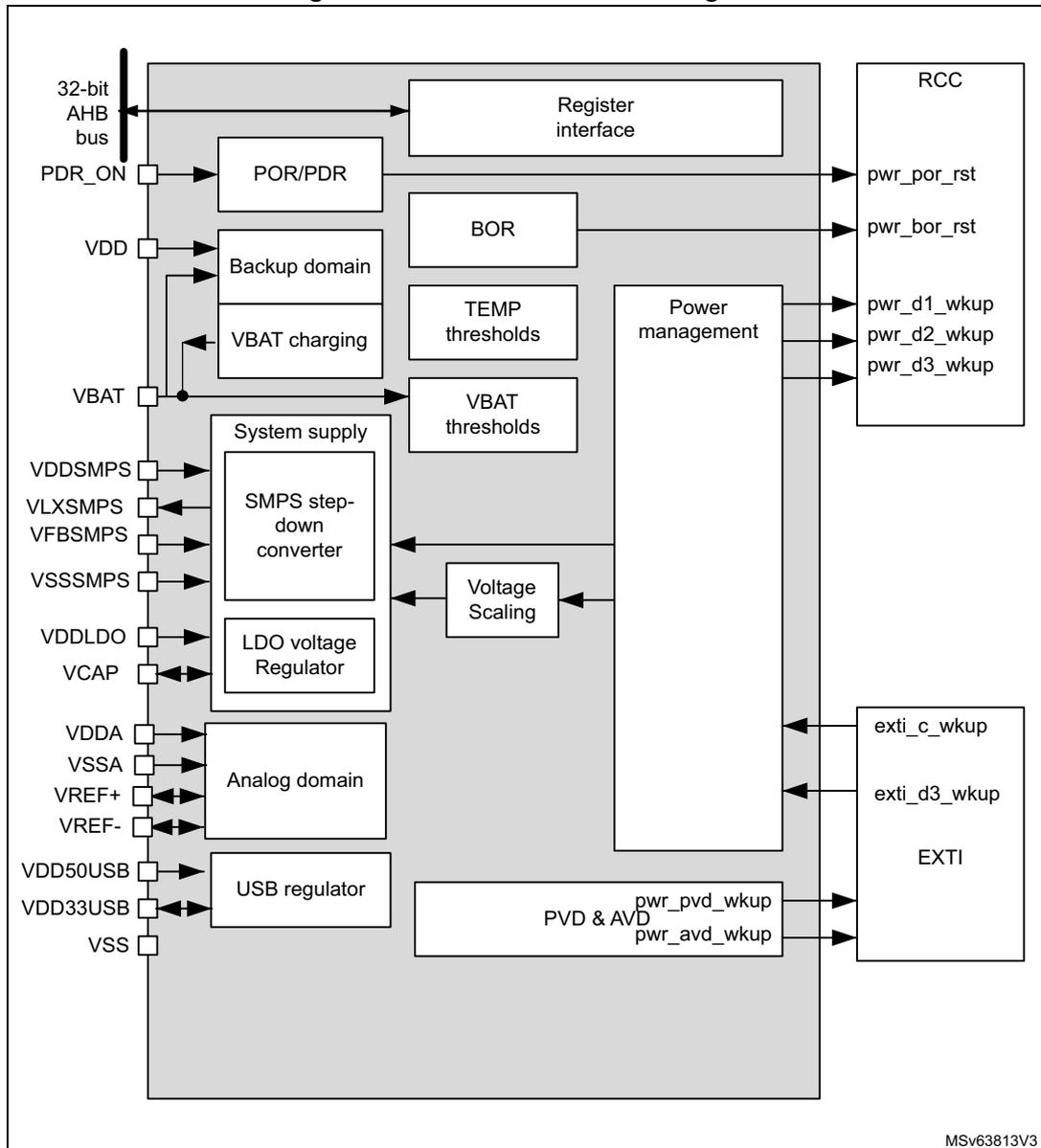

Figure 17. Power control block diagram

The diagram illustrates the internal architecture of the Power control (PWR) block. On the left, external pins are listed: PDR_ON, VDD, VBAT, VDDSMPS, VLXSMPS, VFBSMPS, VSSSMPS, VDDLDO, VCAP, VDDA, VSSA, VREF+, VREF-, VDD50USB, VDD33USB, and VSS. These pins connect to internal functional blocks:

- Register interface: Connected to the 32-bit AHB bus.

- POR/PDR: Receives PDR_ON and VDD signals.

- Backup domain: Receives VDD and VBAT signals, connected to BOR, TEMP thresholds, and VBAT charging.

- System supply: Contains an SMPS step-down converter (receiving VDDSMPS, VLXSMPS, VFBSMPS, VSSSMPS) and an LDO voltage Regulator (receiving VDDLDO, VCAP). It is controlled by Voltage Scaling and Power management.

- Analog domain: Receives VDDA, VSSA, VREF+, and VREF- signals.

- USB regulator: Receives VDD50USB, VDD33USB, and VSS signals.

- PVD & AVD: Monitors voltage levels and provides wake-up signals to Power management.

- RCC: Receives pwr_por_rst and pwr_bor_rst signals.

- Power management: Controls various power states and receives wake-up signals (pwr_d1_wkup, pwr_d2_wkup, pwr_d3_wkup, pwr_pvd_wkup, pwr_avd_wkup).

- EXT1: Receives exti_c_wkup and exti_d3_wkup signals from Power management.

6.3.1 PWR pins and internal signals

Table 28 lists the PWR inputs and output signals connected to package pins or balls, while Table 29 shows the internal PWR signals.

Table 28. PWR input/output signals connected to package pins or balls

| Pin name | Signal type | Description |

|---|---|---|

| VDD | Supply input | Main I/O and V DD domain supply input |

| VDDA | Supply input | External analog power supply for analog peripherals |

| VREF+,VREF- | Supply input/output | External reference voltage for ADCs and DAC |

| VBAT | Supply input/output | Backup battery supply input |

| VDDSMPS | Supply input | Step-down converter supply input |

| VLXSMPS | Supply output | Step-down converter supply output |

| VFBSMPS | Supply input | Step-down converter feedback voltage sense |

| VSSSMPS | Supply input | Step-down converter ground |

| VDDLDO (1) | Supply input | Voltage regulator supply input |

| VCAP | Supply Input/Outputs | Digital core domain supply |

| VDD50USB | Supply input | USB regulator supply input |

| VDD33USB | Supply Input/Outputs | USB regulator supply output or external USB supply input |

| VSS | Supply input | Main ground |

| AHB | Input/output | AHB register interface |

| PDR_ON | Input | Power Down Reset enable |

- 1. When LDO is available but VDDLDO pin is not present on the package, VDDLDO is internally connected to VDD.

Table 29. PWR internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| AHB | Input/output | AHB register interface |

| pwr_pvd_wkup | Output | Programmable voltage detector output |

| pwr_avd_wkup | Output | Analog voltage detector output |

| pwr_por_rst | Output | Power-on reset |

| pwr_bor_rst | Output | Brownout reset |

| exti_c_wkup | Input | CPU wakeup request |

| exti_d3_wkup | Input | D3 domain wakeup request |

| pwr_d1_wkup | Output | D1 domain bus matrix clock wakeup request |

Table 29. PWR internal input/output signals (continued)

| Signal name | Signal type | Description |

|---|---|---|

| pwr_d2_wkup | Output | D2 domain bus matrix clock wakeup request |

| pwr_d3_wkup | Output | D3 domain bus matrix clock wakeup request |

6.4 Power supplies

The device requires \( V_{DD} \) and \( V_{DDSMPS} \) power supplies as well as independent supplies for \( V_{DDLDO} \) , \( V_{DDA} \) , \( V_{DDUSB} \) , and \( V_{CAP} \) . It also provides regulated supplies for specific functions (step-down converter, voltage regulator, USB regulator).

- • \( V_{DD} \) : external power supply for I/Os and system analog blocks such as reset, power management and oscillators

- • \( V_{BAT} \) : optional external power supply for backup domain when \( V_{DD} \) is not present ( \( V_{BAT} \) mode)

This power supply must be connected to \( V_{DD} \) when no battery is used.

- •

\(

V_{DDSMPS}

\)

: external power supply for the SMPS step-down converter

\( V_{DDSMPS} \) must be connected to \( V_{DD} \) or tied to \( V_{SS} \) when the SMPS is not used.

- • \( V_{LXSMPS} \) : step-down converter supply output

- • \( V_{FBSMPS} \) : step-down converter sense feedback

- • \( V_{SSSMPS} \) : separate step-down converter ground

- • \( V_{DDLDO} \) : external power supply for voltage regulator

- • \( V_{CAP} \) : digital core domain supply

This power supply is independent from all the other power supplies:

- – When the voltage regulator is enabled, \( V_{CORE} \) is delivered by the internal voltage regulator.

- – When the voltage regulator is disabled, \( V_{CORE} \) is delivered by an external power supply through \( V_{CAP} \) pin, or by the SMPS step-down converter.

- • \( V_{DDA} \) : external analog power supply for ADCs, DACs, OPAMPS, comparators and voltage reference buffers

This power supply is independent from all the other power supplies.

- •

\(

V_{REF+}

\)

: external reference voltage for ADC and DAC.

- – When the voltage reference buffer is enabled, \( V_{REF+} \) and \( V_{REF-} \) are delivered by the internal voltage reference buffer.

- – When the voltage reference buffer is disabled, \( V_{REF+} \) is delivered by an independent external reference supply.

- • \( V_{SSA} \) : separate analog and reference voltage ground.

- • \( V_{DD50USB} \) : external power supply for USB regulator.

- •

\(

V_{DD33USB}

\)

: USB regulator supply output for USB interface.

- – When the USB regulator is enabled, \( V_{DD33USB} \) is delivered by the internal USB regulator.

- – When the USB regulator is disabled, \( V_{DD33USB} \) is delivered by an independent external supply input.

- • \( V_{SS} \) : common ground for all supplies except for step-down converter and analog peripherals.

Note: Depending on the operating power supply range, some peripherals might be used with limited features and performance. For more details, refer to section “General operating conditions” of the device datasheets.

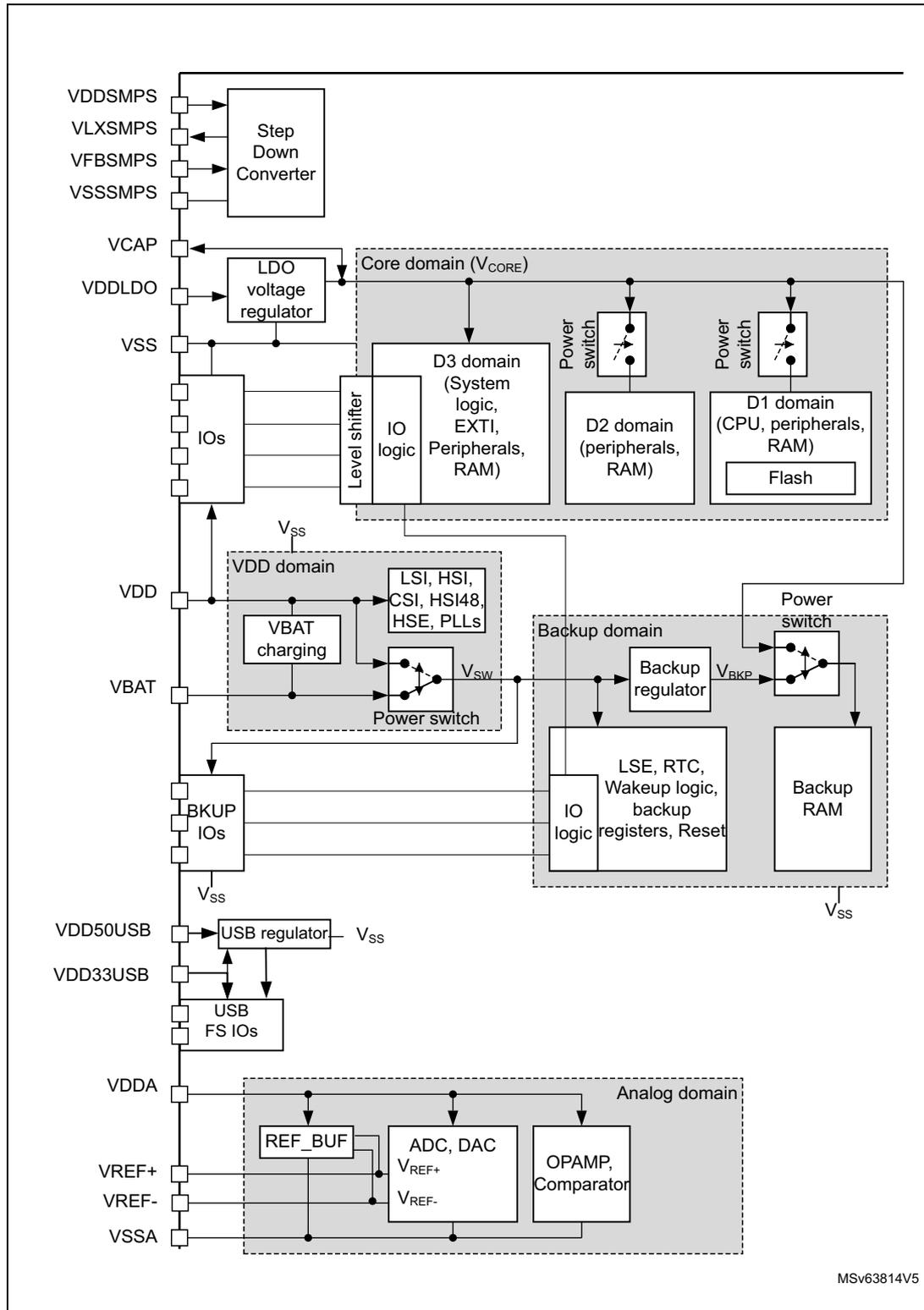

Figure 18. Power supply overview

The diagram illustrates the power supply architecture for the microcontroller, showing the flow of power from external pins through various regulators to different internal domains.

- External Pins: VDDSMPS, VLXSMPS, VFBSMPS, VSSSMPS, VCAP, VDDLDO, VSS, VDD, VBAT, BKUP IOs, VSS, VDD50USB, VDD33USB, VDDA, VREF+, VREF-, VSSA.

- Regulators:

- Step Down Converter: Receives VDDSMPS, VLXSMPS, VFBSMPS, and VSSSMPS. Output connects to VCAP and VDDLDO.

- LDO voltage regulator: Receives VDDLDO. Output connects to the Core domain (V CORE ).

- USB regulator: Receives VDD50USB and VDD33USB. Output connects to VSS and USB FS IOs.

- Backup regulator: Receives VBAT. Output connects to the Backup domain via a Power switch.

- Power Domains:

- Core domain (V CORE ): Contains D3 domain (System logic, EXTI, Peripherals, RAM), D2 domain (peripherals, RAM), and D1 domain (CPU, peripherals, RAM) with Flash. It includes Level shifter, IO logic, and Power switches.

- VDD domain: Contains LSI, HSI, CSI, HSI48, HSE, PLLs, VBAT charging, and a Power switch. It receives VDD and VBAT.

- Backup domain: Contains IO logic, LSE, RTC, Wakeup logic, backup registers, Reset, and Backup RAM. It receives VBAT and a Backup regulator output (V BKP ).

- Analog domain: Contains REF_BUF, ADC, DAC, and OPAMP, Comparator. It receives VDDA, VREF+, VREF-, and VSSA.

- Other Components:

- IOs: Connected to VSS and VDD.

- BKUP IOs: Connected to VSS and the Backup domain.

- USB FS IOs: Connected to the USB regulator.

MSv63814V5

By configuring the SMPS step-down converter and LDO voltage regulator, the supply configurations shown in Figure 19 are supported for the V CORE core domain and an external supply.

Note: The SMPS step-down converter is not available on all packages, and the Bypass mode is available only when the SMPS is available.

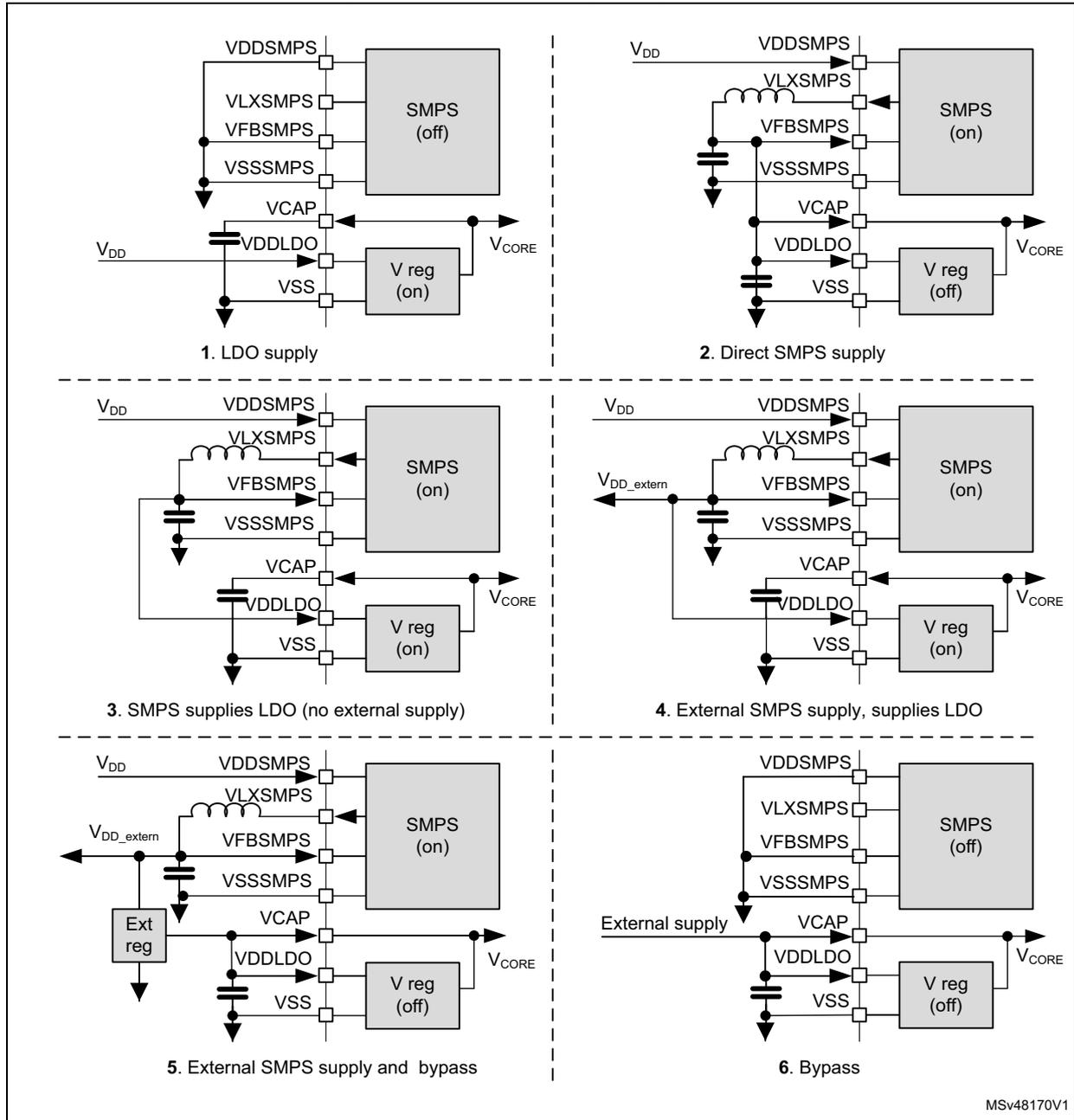

Figure 19. System supply configurations

The figure displays six system supply configurations for the V CORE domain, arranged in a 3x2 grid. Each configuration shows the internal components: SMPS (Step-Down Converter), V reg (Voltage Regulator/LDO), and their connections to V DD , V CORE , and V SS .

- 1. LDO supply: V DD is connected to the V reg (on). The SMPS is off. V reg outputs V CORE .

- 2. Direct SMPS supply: V DD is connected to the SMPS (on). The SMPS outputs V CORE . The V reg is off.

- 3. SMPS supplies LDO (no external supply): V DD is connected to the SMPS (on). The SMPS outputs are connected to the V reg (on). The V reg outputs V CORE .

- 4. External SMPS supply, supplies LDO: An external supply (V DD_extern ) is connected to the SMPS (on). The SMPS outputs are connected to the V reg (on). The V reg outputs V CORE .

- 5. External SMPS supply and bypass: An external supply (V DD_extern ) is connected to the SMPS (on). The SMPS outputs are connected to the V reg (off). The SMPS outputs also connect to the V reg's output (V CORE ) via a bypass capacitor (VCAP).

- 6. Bypass: An external supply is connected to the V reg (off). The SMPS is off. The V reg outputs V CORE .

MSV48170V1

The different supply configurations are controlled through the LDOEN, SDEN, SDEXTHP, SDLEVEL and BYPASS bits in PWR control register 3 (PWR_CR3) register according to Table 30 .

Table 30. Supply configuration control

| ID | Supply configuration | SDLEVEL | SDEXTHP | SDEN | LDOEN | BYPASS | Description |

|---|---|---|---|---|---|---|---|

| 0 | Default configuration | 00 | 0 | 1 | 1 | 0 |

|

| 1 | LDO supply | x | x | 0 | 1 | 0 |

|

| 2 | Direct SMPS step-down converter supply | x | 0 | 1 | 0 | 0 |

|

| 3 | SMPS step-down converter supplies LDO, | 01 or 10 | 0 | 1 | 1 | 0 |

|

| 4 | SMPS step-down converter supplies External and LDO | 01 or 10 | 1 | 1 | 1 | 0 |

|

| 5 | SMPS step-down converter supplies external. and LDO Bypass | 01 or 10 | 1 | 1 | 0 | 1 |

|

Table 30. Supply configuration control (continued)

| ID | Supply configuration | SDLEVEL | SDEXTHP | SDEN | LDOEN | BYPASS | Description |

|---|---|---|---|---|---|---|---|

| 6 | SMPS step-down converter disabled and LDO Bypass | x | x | 0 | 0 | 1 | – V

CORE

supplied from external source – SMPS step-down converter disabled and LDO bypassed, voltage monitoring still active. |

| NA | Illegal | x | x | 0 | 0 | 0 | – Illegal combination, the default configuration is kept. (write data will be ignored). |

| x | x | x | 1 | 1 | |||

| x | 0 | 1 | 0 | 1 | |||

| 00 | x | 1 | 1 | 0 | |||

| x | 1 | 1 | 0 | 0 | |||

| 00 | 1 | 1 | 0 | 1 |

6.4.1 System supply startup

The system startup sequence from power-on in different supply configurations is the following (see Figure 20 and Figure 21 for LDO supply and Direct SMPS supply, respectively):

- 1. When the system is powered on, the POR monitors V

DD

supply. Once V

DD

is above the POR threshold level, the SMPS step-down converter and voltage regulator are enabled in the default supply configuration:

- – The SMPS step-down converter output level is set at 1.36 V.

- – The voltage regulator output level is set at 1.0 V in accordance with the VOS3 level configured in PWR D3 domain control register (PWR_D3CR) .

- 2. The system is kept in reset mode as long as V CORE is not stable.

- 3. Once V CORE is stable, the system is taken out of reset and the HSI oscillator is enabled.

- 4. Once the oscillator is stable, the system is initialized: Flash memory and option bytes are loaded and the CPU starts in limited Run mode (Run*).

- 5. The software must then initialize the system including supply configuration programming in

PWR control register 3 (PWR_CR3)

. Once the supply configuration has been configured, the ACTVOSRDY bit in

PWR control status register 1 (PWR_CSR1)

must be checked to guarantee valid voltage levels:

- a) As long as ACTVOSRDY indicates that voltage levels are invalid, the system is in Run* mode, write operations to RAM are not allowed, and VOS must not be changed.

- b) Once ACTVOSRDY indicates that voltage levels are valid, the system is in normal Run mode, write accesses to RAMs are allowed and VOS can be changed.

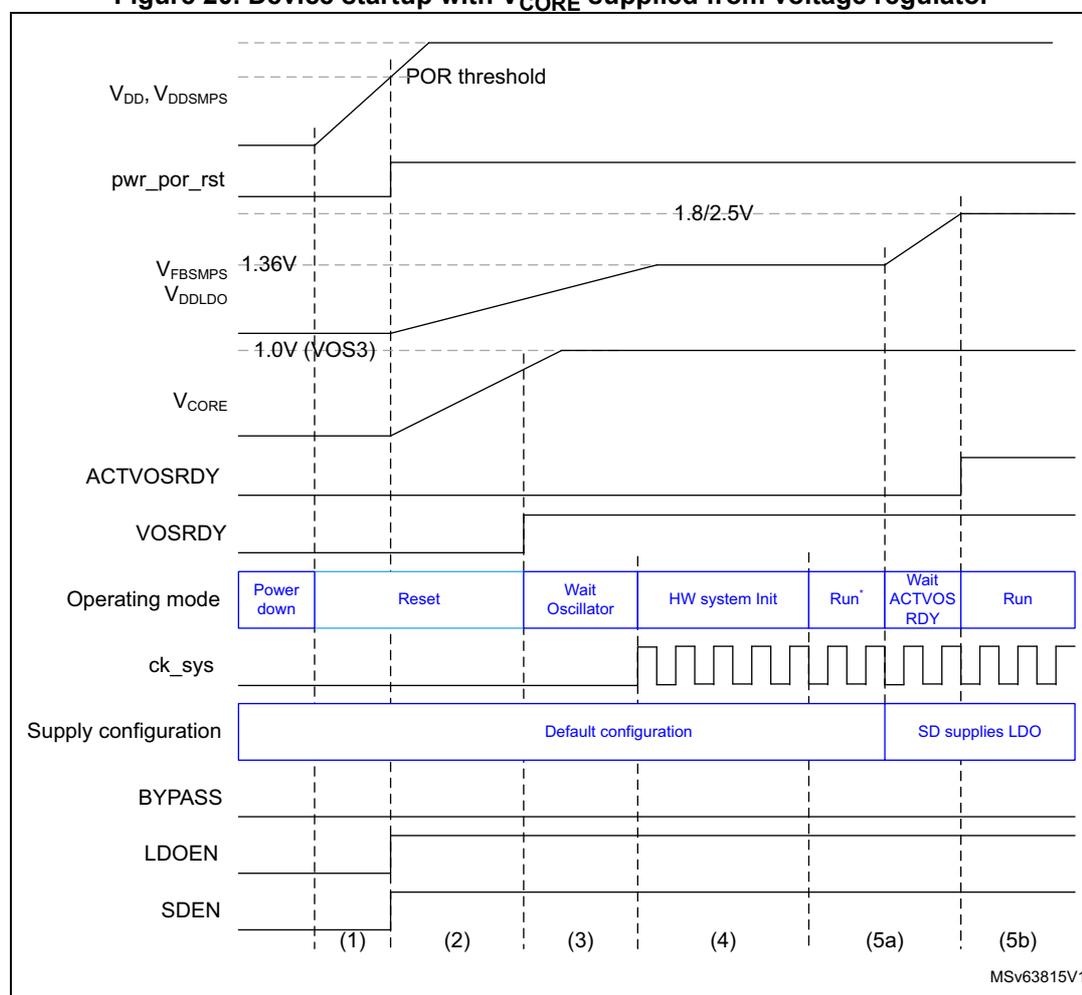

V CORE supplied from the voltage regulator (LDO)

When V CORE is supplied from the voltage regulator (LDO), the V CORE voltage settles directly at VOS3 level. However the SMPS step-down converter V FB SMPS output voltage is set at 1.36 V. ACTVOSRDY bit in PWR control status register 1 (PWR_CSR1) indicates that the voltage levels are invalid.

The software has to program the supply configuration in PWR control register 3 (PWR_CR3) . In addition, the V FB SMPS voltage level must reach the programmed SMPS step-down converter voltage output level (SDLEVEL) so that ACTVOSRDY indicates valid voltage levels (see Figure 20 ).

When exiting from Standby mode, the supply configuration is known by the system since the content of the PWR control register 3 (PWR_CR3) is retained. However the software must wait until ACTVOSRDY is set and ACTVOS reflects the awaited value in PWR control status register 1 (PWR_CSR1) to indicate V CORE voltage levels are valid, before performing write accesses to RAM or changing VOS level.

Figure 20. Device startup with V CORE supplied from voltage regulator

The timing diagram illustrates the sequence of events during device startup when V CORE is supplied from the LDO. The signals shown are:

- V DD , V DDSMPS : Supply voltage rising from 0V to a POR threshold.

- pwr_por_rst: Power-on reset signal, active low, going high after POR threshold is reached.

- V FB SMPS , V DDLDO : V FB SMPS rises to 1.36V. V DDLDO follows a ramp up to 1.8/2.5V.

- V CORE : Core voltage rising to 1.0V (VOS3).

- ACTVOSRDY: Active voltage ready signal, going high when V CORE reaches the programmed level at the end of phase (5a).

- VOSRDY: Voltage ready signal, going high during phase (3).

- Operating mode: Sequence of modes: Power down (1), Reset (2), Wait Oscillator (3), HW system Init (4), Run* (5a), Wait ACTVOS RDY (5a), Run (5b).

- ck sys : System clock, starting in the HW system Init phase (4).

- Supply configuration: Default configuration until phase (5a), then transitions to "SD supplies LDO".

- BYPASS, LDOEN, SDEN: Control signals for the voltage regulators. SDEN goes high at the start of phase (2). LDOEN goes high at the start of phase (3).

Phases are marked at the bottom: (1) Power down, (2) Reset, (3) Wait Oscillator, (4) HW system Init, (5a) Run*, (5b) Run. The transition from (5a) to (5b) occurs when ACTVOSRDY becomes valid.

- 1. In Run* mode, write operations to RAM are not allowed.

- 2. Write operations to RAM are allowed and VOS can be changed only when ACTVOSRDY is valid.

V CORE directly supplied from the SMPS step-down converter

When V CORE is directly supplied from the SMPS step-down converter, the V CORE voltage first settles at V FBSMPS default level (1.36 V). Due to a too high supply compared to the VOS3 level, the ACTVOSRDY bit in PWR control status register 1 (PWR_CSR1) indicates invalid voltage levels. V CORE settles at 1.0 V (VOS3 level) and ACTVODSRDY indicates valid voltage levels only when the supply configuration has been programmed in PWR control register 3 (PWR_CR3) (see Figure 21).

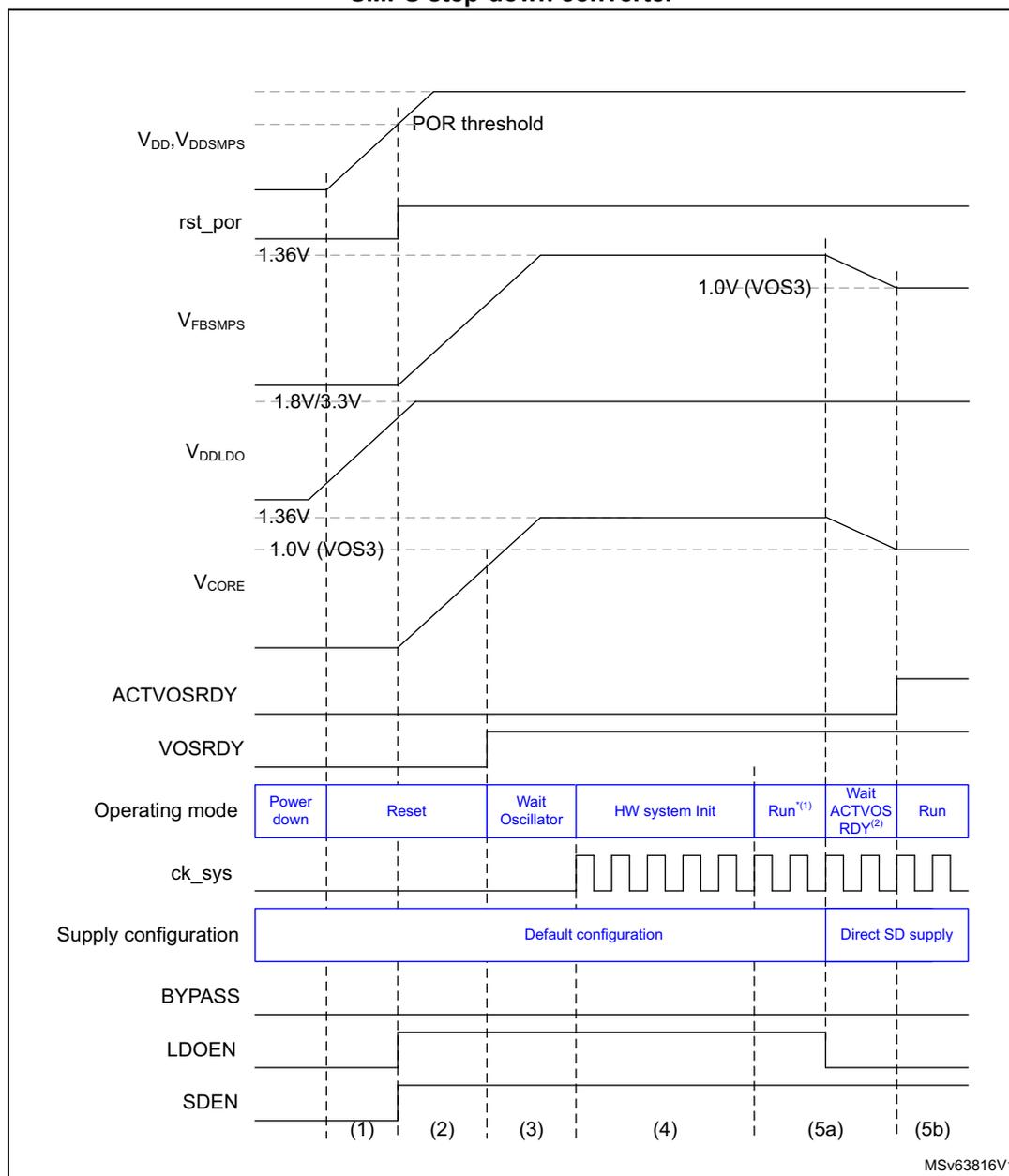

Figure 21. Device startup with V CORE supplied directly from SMPS step-down converter

The timing diagram illustrates the startup sequence of the device when V CORE is directly supplied from the SMPS step-down converter. The signals shown are:

- V DD , V DDSMPS : Supply voltage rising to the POR threshold.

- rst_por: Reset signal, active low, going high after POR threshold is reached.

- V FBSMPS : SMPS output voltage, starting at 1.36V and settling at 1.0V (VOS3).

- V DDLDO : LDO output voltage, starting at 1.36V and settling at 1.0V (VOS3).

- V CORE : Core voltage, following V FBSMPS and settling at 1.0V (VOS3).

- ACTVOSRDY: Active voltage status ready signal, going high when V CORE is valid.

- VOSRDY: Voltage status ready signal, going high when V CORE is valid.

- Operating mode: State transitions as follows:

- ck_sys: System clock, starting in Wait Oscillator mode and running in HW system Init and Run modes.

- Supply configuration: Default configuration (until 5a) → Direct SD supply (from 5a onwards).

- BYPASS: Bypass signal, active low, going high in Run mode.

- LDOEN: LDO enable signal, going high in Run mode.

- SDEN: SMPS enable signal, going high in Run mode.

| Power down | Reset | Wait Oscillator | HW system Init | Run (1) | Wait ACTVOS RDY (2) | Run |

Phases: (1) Power down, (2) Reset, (3) Wait Oscillator, (4) HW system Init, (5a) Run (1) , (5b) Run.

MSv63816V1

1. In Run* mode, write operations to RAM are not allowed.

2. Write operations to RAM are allowed and VOS can be changed only when ACTVOSRDY is valid.

When exiting from Standby mode, the supply configuration is known by the system since the content of PWR control register 3 (PWR_CR3) is retained. However the software must still wait for the ACTVOSRDY bit to be set in PWR control status register 1 (PWR_CSR1) to indicate \( V_{CORE} \) voltage levels are valid, before performing write accesses to RAM or changing VOS.

\( V_{CORE} \) supplied in Bypass mode (LDO and SMPS OFF)

The devices that feature the SMPS can also be used in Bypass mode.

When \( V_{CORE} \) is supplied in Bypass mode (LDO and SMPS OFF), the externally supplied \( V_{CORE} \) voltage must first settle at a default level higher than 1.1 V. Due to the LDO default state after power-up (enabled by default), the external \( V_{CORE} \) voltage must remain higher than 1.1 V until the LDO is disabled by software.

When the LDO is disabled, the external \( V_{CORE} \) voltage can be adjusted according to the user application needs (refer to section General operating conditions of the datasheet for details on \( V_{CORE} \) level versus the maximum operating frequency).

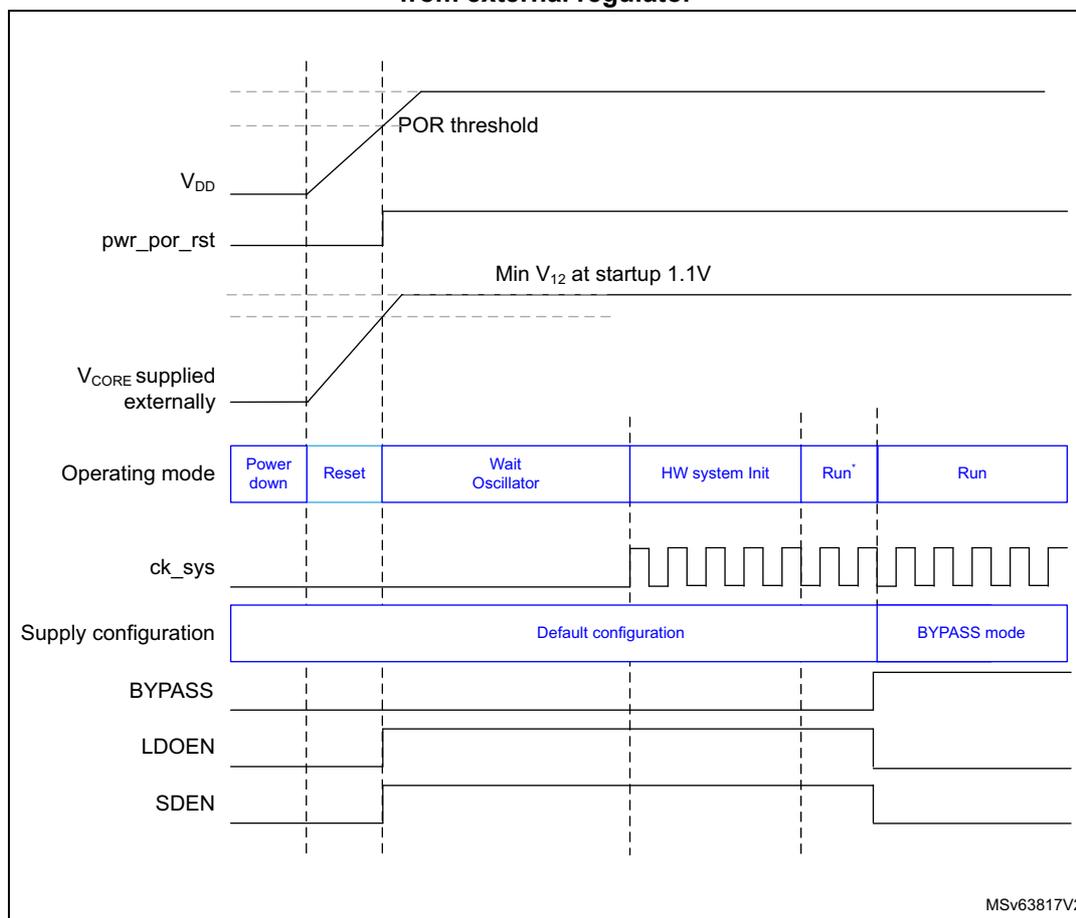

Figure 22. Device startup with \( V_{CORE} \) supplied in Bypass mode from external regulator

The timing diagram illustrates the sequence of events during device startup when \( V_{CORE} \) is supplied in bypass mode from an external regulator. The vertical axis represents various signals and states, while the horizontal axis represents time, divided into distinct phases by vertical dashed lines.

- \( V_{DD} \) : The main supply voltage rises from 0V to a level above the POR threshold.

- pwr_por_rst: A power-on reset signal that goes low (active low) when \( V_{DD} \) reaches the POR threshold.

- \( V_{CORE} \) supplied externally: The core supply voltage rises and settles at a minimum value of 1.1V ( \( Min V_{12} \) at startup 1.1V).

- Operating mode: The sequence of modes is: Power down → Reset → Wait Oscillator → HW system Init → Run* → Run.

- ck_sys: The system clock, which is a square wave starting during the HW system Init phase.

- Supply configuration: The system starts in Default configuration and switches to BYPASS mode upon entering Run* mode.

- BYPASS, LDOEN, SDEN: Control signals. BYPASS is high in Default configuration and low in BYPASS mode. LDOEN and SDEN are high in Default configuration and low in BYPASS mode.

MSv63817V2

How to exit from Run* mode

As the Run* mode does not allow accessing RAM, PWR configuration must be done in the startup file. Below an example of code for SMPS supply that can be adapted for any other mode:

;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

;;

;; Exit Run* mode to Direct SMPS mode

;;

THUMB

PUBWEAK ExitRun0ModeToDirectSMPSMode

SECTION .text:CODE:NOROOT:REORDER(1)

ExitRun0ModeToDirectSMPSMode

MOV R1, #0x4804

MOVT R1, #0x5802

LDR R0, [R1, #+8]

BIC R0, R0, #0x2

STR R0, [R1, #+8]

wait_actvosrdy:

LDR R2, [R1, #+0]

LSLS R0, R2, #+18

BPL.N wait_actvosrdy

BX LR

;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

;;

;; Default interrupt handlers.

;;

THUMB

PUBWEAK Reset_Handler

SECTION .text:CODE:NOROOT:REORDER(2)

Reset_Handler

LDR R0, =ExitRun0ModeToDirectSMPSMode

BLX R0

LDR R0, =SystemInit

BLX R0

LDR R0, =__iar_program_start

BX R0

6.4.2 Core domain

The \( V_{CORE} \) core domain supply can be provided by the SMPS step-down converter, LDO voltage regulator or by an external supply ( \( V_{CAP} \) ). \( V_{CORE} \) supplies all the digital circuitries

except for the backup domain and the Standby circuitry. The \( V_{CORE} \) domain is split into 3 sections:

- • D1 domain containing the CPU (Cortex®-M7), Flash memory and some peripherals.

- • D2 domain containing some peripherals

- • D3 domain containing the system control, I/O logic and low-power peripherals.

When a system reset occurs, the voltage regulator is enabled and supplies \( V_{CORE} \) . The SMPS step-down converter is also enabled to deliver 1.36 V. This allows the system to start up in any supply configurations (see Figure 19 ).

After a system reset, the software must configure the used supply configuration in PWR control register 3 (PWR_CR3) register before changing VOS in PWR D3 domain control register (PWR_D3CR) or the RCC ck_sys frequency. The different system supply configurations are controlled as shown in Table 30 .

Note: The SMPS step-down converter and the LDO are not available on all packages.

LDO voltage regulator

The embedded voltage regulator (LDO) requires external capacitors to be connected to VCAP pins.

The voltage regulator provides three different operating modes: Main (MR), Low-power (LP) or Off. These modes will be used depending on the system operating modes (Run, Stop and Standby).

- • Run and Autonomous modes

The LDO regulator is in Main mode and provides full power to the \( V_{CORE} \) domain (core, memories and digital peripherals). The regulator output voltage can be scaled by software to different voltage levels (VOS0, VOS1, VOS2, and VOS3) that are configured through VOS bits in PWR D3 domain control register (PWR_D3CR) . The VOS voltage scaling allows optimizing the power consumption when the system is clocked below the maximum frequency. By default VOS3 is selected after system reset. VOS can be changed on-the-fly to adapt to the required system performance.

- • Stop mode

The voltage regulator supplies the \( V_{CORE} \) domain to retain the content of registers and internal memories.

The regulator can be kept in Main mode to allow fast exit from Stop mode, or can be set in LP mode to obtain a lower \( V_{CORE} \) supply level and extend the exit-from-Stop latency. The regulator mode is selected through the SVOS and LPDS bits in PWR control register 1 (PWR_CR1) . Main mode and LP mode are allowed if SVOS3 voltage scaling is selected, while only LP mode is possible for SVOS4 and SVOS5 scaling. Due to a lower voltage level for SVOS4 and SVOS5 scaling, the Stop mode consumption can be further reduced.

- • Standby mode

The voltage regulator is OFF and the \( V_{CORE} \) domains are powered down. The content of the registers and memories is lost except for the Standby circuitry and the backup domain.

Note: The LDO is not available on all packages.

For more details, refer to the voltage regulator section in the datasheets.

SMPS step-down converter regulator

The SMPS step-down converter requires an external coil to be connected between the dedicated VLXSMPS pin and, via a capacitor, to VSS.

The SMPS step-down converter can be used in internal supply mode or external supply mode. The internal supply mode is used to directly supply the \( V_{CORE} \) domain, while the external supply mode is used to generate an intermediate supply level ( \( V_{DD\_extern} \) at 1.8 or 2.5 V) which can supply the voltage regulator and optionally an external circuitry.

The SMPS step-down converter works in three different power modes: Main (MR), Low-power (LP) or Off.

When the SMPS step-down converter is used in internal supply mode, the converter operating modes depend on the system modes (Run, Stop, Standby) and are configured through the associated VOS and SVOS levels:

- • Run mode

The SMPS step-down converter operates in MR mode and provides full power to the \( V_{CORE} \) domain (core, memories and digital peripherals). The regulator output voltage can be scaled by software to different voltage levels (VOS0, VOS1, VOS2, and VOS3) that are configured through VOS bits in PWR D3 domain control register (PWR_D3CR) . The VOS voltage scaling allows optimizing the power consumption when the system is clocked below the maximum frequency. By default VOS3 is selected after system reset. VOS can be changed on-the-fly to adapt to the required system performance. - • Stop mode

The SMPS step-down converter supplies the \( V_{CORE} \) domain to retain the content of registers and internal memories. The regulator can be kept in MR mode to allow fast exit from Stop mode, or can be set in LP mode to achieve a lower \( V_{CORE} \) supply level and extend the exit-from-Stop latency. The regulator mode is selected through the SVOS and LPDS bits in PWR control register 1 (PWR_CR1) . MR mode or LP mode are allowed if SVOS3 voltage scaling is selected, while only LP mode is possible for SVOS4 and SVOS5 scaling. Due to a lower voltage level for SVOS4 and SVOS5 scaling, the Stop mode consumption can be further reduced. - • Standby mode

The SMPS step-down converter is OFF and the \( V_{CORE} \) domains are powered down. The content of the registers and memories are lost except for the Standby circuitry and the backup domain.

When the SMPS step-down converter supplies an external circuitry by generating an intermediate voltage level, the converter is forced ON and operates in MR mode. The intermediate voltage level is selected through SDLEVEL bits in PWR control register 3 (PWR_CR3) . \( V_{DD\_extern} \) is supplied at all times with full power whatever the system modes (Run, Stop, Standby).

Note: The SMPS step-down converter and the LDO are not available on all packages. When the LDO is not available, the SMPS supplies the voltage regulator and optionally an external circuitry.

6.4.3 PWR external supply

When \( V_{CORE} \) is supplied from an external source (Bypass mode), different operating modes can be used depending on the system operating modes (Run, Autonomous, Stop or Standby):

- • In Run and D3 Autonomous modes

The external source supplies full power to the \( V_{CORE} \) domain (core, memories and digital peripherals). The external source output voltage is scalable through different voltage levels ( \( V_{OS0} \) , \( V_{OS1} \) , \( V_{OS2} \) and \( V_{OS3} \) ). The externally applied voltage level must be reflected in the \( V_{OS} \) bits of \( PWR\_D3CR \) register. The RAMs must only be accessed for write operations when the external applied voltage level matches \( V_{OS} \) settings.

- • In Stop mode

The external source supplies \( V_{CORE} \) domain to retain the content of registers and internal memories. The regulator can select a lower \( V_{CORE} \) supply level to reduce the consumption in Stop mode.

- • In Standby mode

The external source must be switched OFF and the \( V_{CORE} \) domains powered down. The content of registers and memories is lost except for the Standby circuitry and the backup domain. The external source must be switched ON when exiting Standby mode.

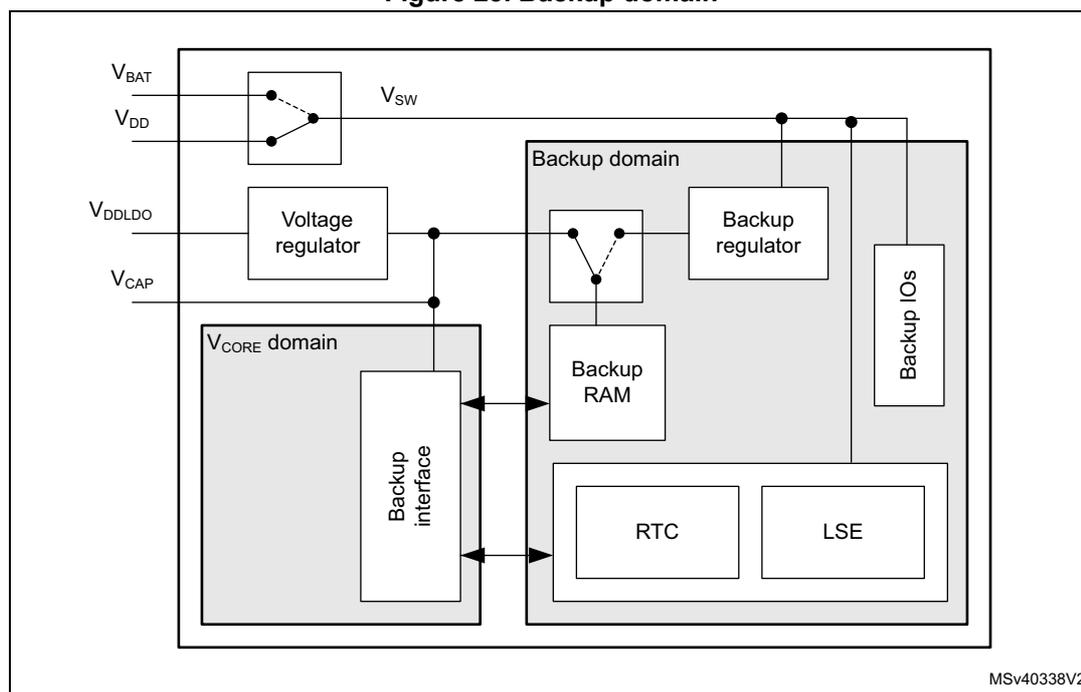

6.4.4 Backup domain

To retain the content of the backup domain (RTC, backup registers and backup RAM) when \( V_{DD} \) is turned off, \( V_{BAT} \) pin can be connected to an optional voltage which is supplied from a battery or from an another source.

The switching to \( V_{BAT} \) is controlled by the power-down reset embedded in the Reset block that monitors the \( V_{DD} \) supply.

Warning: During \( t_{RSTTEMPO} \) (temporization at \( V_{DD} \) startup) or after a PDR is detected, the power switch between \( V_{BAT} \) and \( V_{DD} \) remains connected to \( V_{BAT} \) .

During the startup phase, if \( V_{DD} \) is established in less than \( t_{RSTTEMPO} \) (see the datasheet for the value of \( t_{RSTTEMPO} \) ) and \( V_{DD} > V_{BAT} + 0.6\text{ V} \) , a current may be injected into \( V_{BAT} \) through an internal diode connected between \( V_{DD} \) and the power switch ( \( V_{BAT} \) ).

If the power supply/battery connected to the \( V_{BAT} \) pin cannot support this current injection, it is strongly recommended to connect an external low-drop diode between this power supply and the \( V_{BAT} \) pin.

When the \( V_{DD} \) supply is present, the backup domain is supplied from \( V_{DD} \) . This allows saving \( V_{BAT} \) power supply battery life time.

If no external battery is used in the application, it is recommended to connect \( V_{BAT} \) externally to \( V_{DD} \) , and add a 100 nF external ceramic capacitor between \( V_{BAT} \) and \( V_{SS} \) .

When the \( V_{DD} \) supply is present and higher than the PDR threshold, the backup domain is supplied by \( V_{DD} \) and the following functions are available:

- • PC14 and PC15 can be used either as GPIO or as LSE pins.

- • PC13 can be used either as GPIO or as RTC_AF1 or RTC_TAMP1 pin assuming they have been configured by the RTC.

- • PC1/RTC_TAMP3 when it is configured by the RTC as tamper pins. PC1 can be used either as GPIO or as TAMP_IN3 assuming they have been configured by the RTC tamper.

Note: Since the switch only sinks a limited amount of current, the use of PC13 and PC15 GPIOs is restricted: only one I/O can be used as an output at a time, at a speed limited to 2 MHz with a maximum load of 30 pF. These I/Os must not be used as current sources (e.g. to drive an LED).

In \( V_{BAT} \) mode, when the \( V_{DD} \) supply is absent and a supply is present on \( V_{BAT} \) , the backup domain is supplied by \( V_{BAT} \) and the following functions are available:

- • PC14 and PC15 can be used as LSE pins only.

- • PC13 can be used as RTC_AF1 or RTC_TAMP1 pin assuming they have been configured by the RTC.

- • PC1/RTC_TAMP3 when it is configured by the RTC as tamper pins. PC1 can be used as TAMP_IN3 assuming it has been configured by the RTC tamper.

Accessing the backup domain

After reset, the backup domain (RTC registers and RTC backup registers) is protected against possible unwanted write accesses. To enable access to the backup domain, set the DBP bit in the PWR control register 1 (PWR_CR1) .

For more detail on RTC and backup RAM access, refer to Section 8: Reset and clock control (RCC) .

Backup RAM

The backup domain includes 4 Kbytes of backup RAM accessible in 32-bit, 16-bit or 8-bit data mode. The backup RAM is supplied from the backup regulator in the backup domain. When the backup regulator is enabled through BREN bit in PWR control register 2 (PWR_CR2) , the backup RAM content is retained even in Standby and/or \( V_{BAT} \) mode (it can be considered as an internal EEPROM if \( V_{BAT} \) is always present.)

The backup regulator can be ON or OFF depending whether the application needs the backup RAM function in Standby or \( V_{BAT} \) modes.

After a tamper event, the backup RAM can no more be used until an erase is explicitly requested: reading the backup RAM returns 0x0, and any write different from 0 is not effective. The backup RAM can be erased:

- • through the Flash memory interface when an RDP level regression from level 1 to level 0 is requested (refer to Section 4.5.3: Readout protection (RDP) ) or

- • by performing a simple dummy write with zero as data to any address of the backup RAM (this action resets the whole backup RAM when it is performed after a tamper event).

Figure 23. Backup domain

The diagram illustrates the internal architecture of the backup domain. On the left, the V CORE domain contains a Backup interface . On the right, the Backup domain contains a Backup RAM , RTC , and LSE . A Voltage regulator is connected to V DD , V CAP , and V DDLO . A switch ( V sw ) connects V BAT and V DD . A Backup regulator is connected to the Backup RAM . Backup IOs are also shown. The diagram is labeled MSV40338V2.

6.4.5 V BAT battery charging

When V DD is present, the external battery connected to V BAT can be charged through an internal resistance.

V BAT charging can be performed either through a 5 k \( \Omega \) resistor or through a 1.5 k \( \Omega \) resistor, depending on the VBRS bit value in PWR control register 3 (PWR_CR3) .

The battery charging is enabled by setting the VBE bit in PWR control register 3 (PWR_CR3) . It is automatically disabled in V BAT mode.

6.4.6 Analog supply

Separate V DDA analog supply

The analog supply domain is powered by dedicated V DDA and V SSA pads that allow the supply to be filtered and shielded from noise on the PCB, thus improving ADC and DAC conversion accuracy:

- • The analog supply voltage input is available on a separate V DDA pin.

- • An isolated supply ground connection is provided on V SSA pin.

Analog reference voltage V REF+ /V REF-

To achieve better accuracy low-voltage signals, the ADC and DAC also have a separate reference voltage, available on V REF+ pin. The user can connect a separate external reference voltage on V REF+ .

The V REF+ controls the highest voltage, represented by the full scale value, the lower voltage reference ( V REF- ) being connected to V SSA .

When enabled by ENVR bit in the VREFBUF control and status register (see Section 32: Voltage reference buffer (VREFBUF) ), V REF+ is provided from the internal voltage reference buffer. The internal voltage reference buffer can also deliver a reference voltage to external components through VREF+/VREF- pins.

When the internal voltage reference buffer is disabled by ENVR, V REF+ is delivered by an independent external reference supply voltage.

Note: V REF+ and V REF- pins are not available on all packages (in this case they are connected internally respectively to VDDA and VSSA). Do not enable the internal voltage reference buffer when an external power supply is applied to the V REF+ pin.

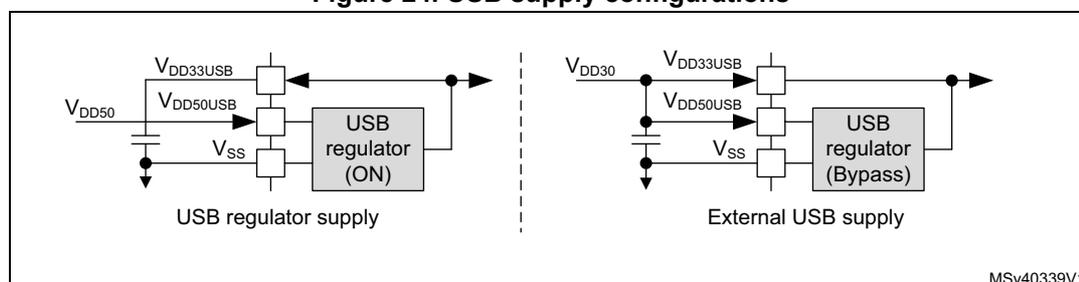

6.4.7 USB regulator

The USB transceivers are supplied from a dedicated V DD33USB supply that can be provided either by the integrated USB regulator, or by an external USB supply.

When enabled by USBREGEN bit in PWR control register 3 (PWR_CR3) , the V DD33USB is provided from the USB regulator, which is powered through the V DD50USB pin generally connected to the USB VBUS line. Before using V DD33USB , check that it is available by monitoring USB33RDY bit in PWR control register 3 (PWR_CR3) . The V DD33USB supply level detector must be enabled through USB33DEN bit in PWR_CR3 register.

When the USB regulator is disabled through USBREGEN bit, V DD33USB can be provided from an external supply. In this case V DD33USB and V DD50USB must be connected together. The V DD33USB supply level detector must be enabled through USB33DEN bit in PWR_CR3 register before using the USB transceivers.

For more information on the USB regulator (see Section 62: USB on-the-go high-speed (OTG_HS) ).

Figure 24. USB supply configurations

The diagram illustrates two power supply configurations for a USB transceiver. In the left configuration, labeled 'USB regulator supply', the transceiver's V DD33USB , V DD50USB , and V SS pins are connected to a 'USB regulator (ON)' block. The V DD50USB pin is connected to an external V DD50 supply. In the right configuration, labeled 'External USB supply', the transceiver's V DD33USB and V DD50USB pins are connected together and to an external V DD30 supply. The V SS pin is connected to V SS . The 'USB regulator (Bypass)' block is shown in this configuration, indicating it is disabled.

MSV40339V1

6.5 Power supply supervision

Power supply level monitoring is available on the following supplies:

- • \( V_{DD} \) ( \( V_{DDSMPS} \) ) can be monitored via POR/PDR (see Section 6.5.1 ), BOR (see Section 6.5.2 ) and PVD monitor (see Section 6.5.3 )

- • \( V_{DDA} \) can be monitored via AVD monitor (see Section 6.5.4 )

- • \( V_{BAT} \) can be monitored via VBAT threshold (see Section 6.5.5 )

- •

\(

V_{SW}

\)

can be monitored via

rst_vsw, which keeps \( V_{SW} \) domain in Reset mode as long as the level is not OK. - •

\(

V_{BKP}

\)

can be monitored via a

BRRDYbit in PWR control register 2 (PWR_CR2) . - •

\(

V_{FBSMPS}

\)

can be monitored via a

SDEXTRDYbit in PWR control register 3 (PWR_CR3) . - •

\(

V_{DD33USB}

\)

can be monitored via

USBRDYbit in PWR control register 3 (PWR_CR3) .

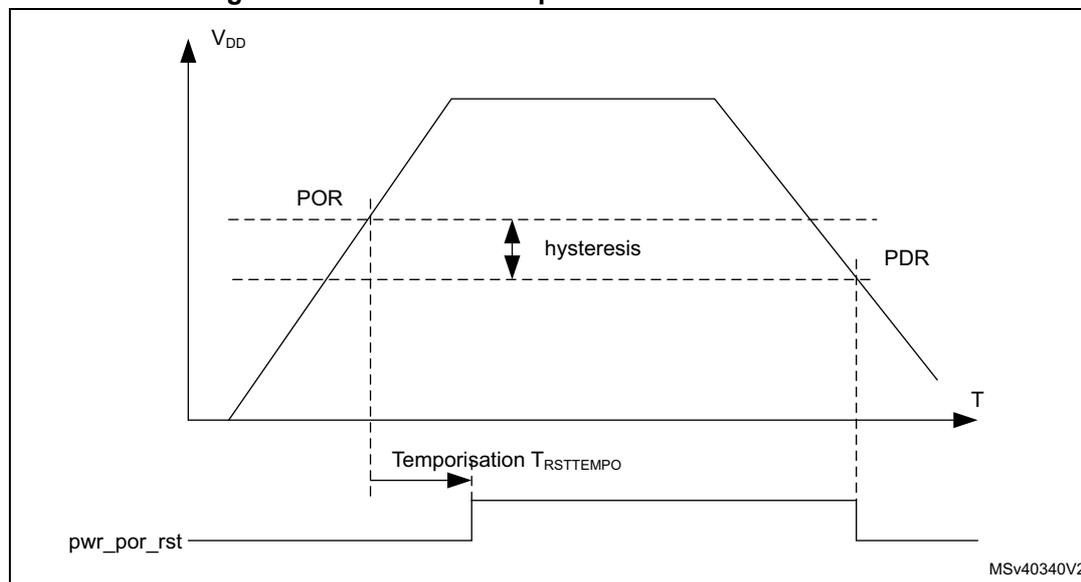

6.5.1 Power-on reset (POR)/power-down reset (PDR)

The system has an integrated POR/PDR circuitry that ensures proper startup operation.

The system remains in Reset mode when \( V_{DD} \) is below a specified \( V_{POR} \) threshold, without the need for an external reset circuit. Once the \( V_{DD} \) supply level is above the \( V_{POR} \) threshold, the system is taken out of reset (see Figure 25 ). For more details concerning the power-on/power-down reset threshold, refer to the electrical characteristics section of the datasheets.

The PDR can be enabled/disabled by the device

PDR_ON

input pin.

Figure 25. Power-on reset/power-down reset waveform

- 1. For thresholds and hysteresis values, refer to the datasheets.

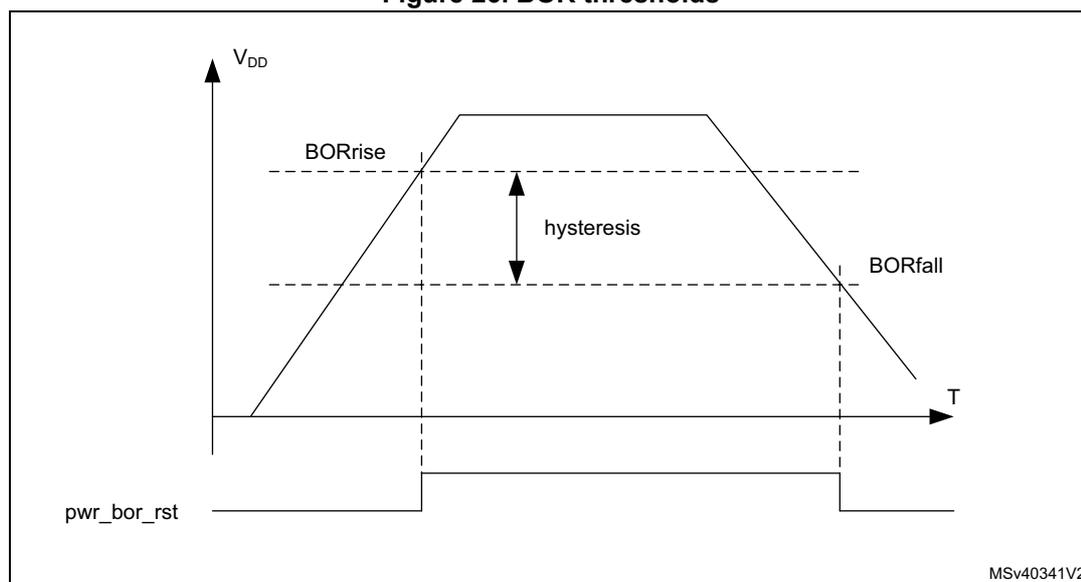

6.5.2 Brownout reset (BOR)

During power-on, the Brownout reset (BOR) keeps the system under reset until the \( V_{DD} \) supply voltage reaches the specified \( V_{BOR} \) threshold.

The \( V_{BOR} \) threshold is configured through system option bytes. By default, BOR is OFF. The following programmable \( V_{BOR} \) thresholds can be selected:

- • BOR OFF ( \( V_{BOR0} \) )

- • BOR Level 1 ( \( V_{BOR1} \) )

- • BOR Level 2 ( \( V_{BOR2} \) )

- • BOR Level 3 ( \( V_{BOR3} \) )

For more details on the brown-out reset thresholds, refer to the section “Electrical characteristics” of the product datasheets.

A system reset is generated when the BOR is enabled and \( V_{DD} \) supply voltage drops below the selected \( V_{BOR} \) threshold.

BOR can be disabled by programming the system option bytes. To disable the BOR function, \( V_{DD} \) must have been higher than \( V_{BOR0} \) to start the system option byte programming sequence. The power-down is then monitored by the PDR (see Section 6.5.1 ).

Figure 26. BOR thresholds

The figure is a graph showing the relationship between supply voltage \( V_{DD} \) (Y-axis) and Temperature \( T \) (X-axis). The graph illustrates the BOR threshold levels and hysteresis. The \( V_{DD} \) voltage is shown as a trapezoidal shape, starting at a low value, rising to a high value, and then falling back to a low value. The BORrise threshold is indicated by a horizontal dashed line at the rising edge of the \( V_{DD} \) curve. The BORfall threshold is indicated by a horizontal dashed line at the falling edge of the \( V_{DD} \) curve. The hysteresis is the vertical distance between the BORrise and BORfall thresholds. Below the graph, the pwr_bor_rst signal is shown as a horizontal line that goes low when \( V_{DD} \) drops below BORrise and goes high when \( V_{DD} \) rises above BORfall. The text MSv40341V2 is visible in the bottom right corner of the graph area.

- 1. For thresholds and hysteresis values, refer to the datasheets.

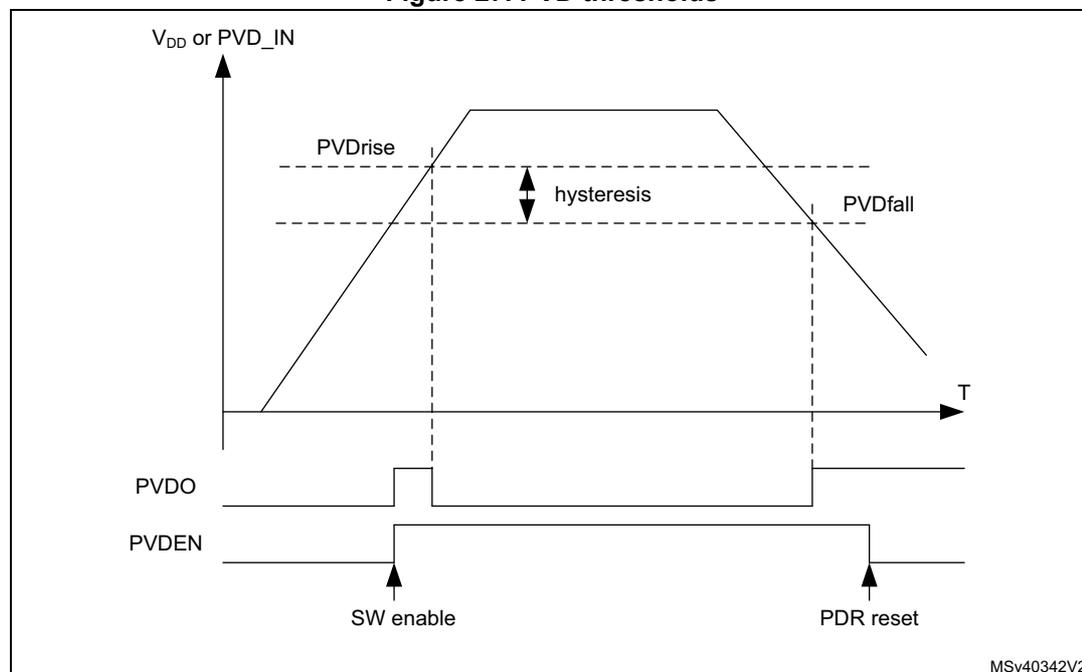

6.5.3 Programmable voltage detector (PVD)

The PVD can be used to monitor the \( V_{DD} \) power supply by comparing it to a threshold selected by the PLS[2:0] bits in the PWR control register 1 (PWR_CR1) . The PVD can also be used to monitor a voltage level on the PVD_IN pin. In this case PVD_IN voltage is compared to the internal \( V_{REFINT} \) level.

The PVD is enabled by setting the PVDE bit in PWR control register 1 (PWR_CR1) .

A PVDO flag is available in the PWR control status register 1 (PWR_CSR1) to indicate if \( V_{DD} \) or PVD_IN voltage is higher or lower than the PVD threshold. This event is internally connected to the EXTI and can generate an interrupt, assuming it has been enabled through the EXTI registers. The PVDO output interrupt can be generated when \( V_{DD} \) or PVD_IN voltage drops below the PVD threshold and/or when \( V_{DD} \) or PVD_IN voltage rises above the PVD threshold depending on EXTI rising/falling edge configuration. As an example the service routine could perform emergency shutdown tasks.

Figure 27. PVD thresholds

The figure illustrates the PVD thresholds and timing. The top graph shows the voltage ( \( V_{DD} \) or PVD_IN) over time (T). The voltage rises and falls, crossing two threshold levels: PVDrise (higher) and PVDfall (lower). The hysteresis is the voltage difference between these two thresholds. Below the graph, the PVDO output signal is shown. It is high when the voltage is above the PVDrise threshold and low when it is below the PVDfall threshold. The PVDEN signal is shown as a pulse that enables the PVD function. The diagram is labeled MSv40342V2.

- 1. For thresholds and hysteresis values, refer to the datasheets.

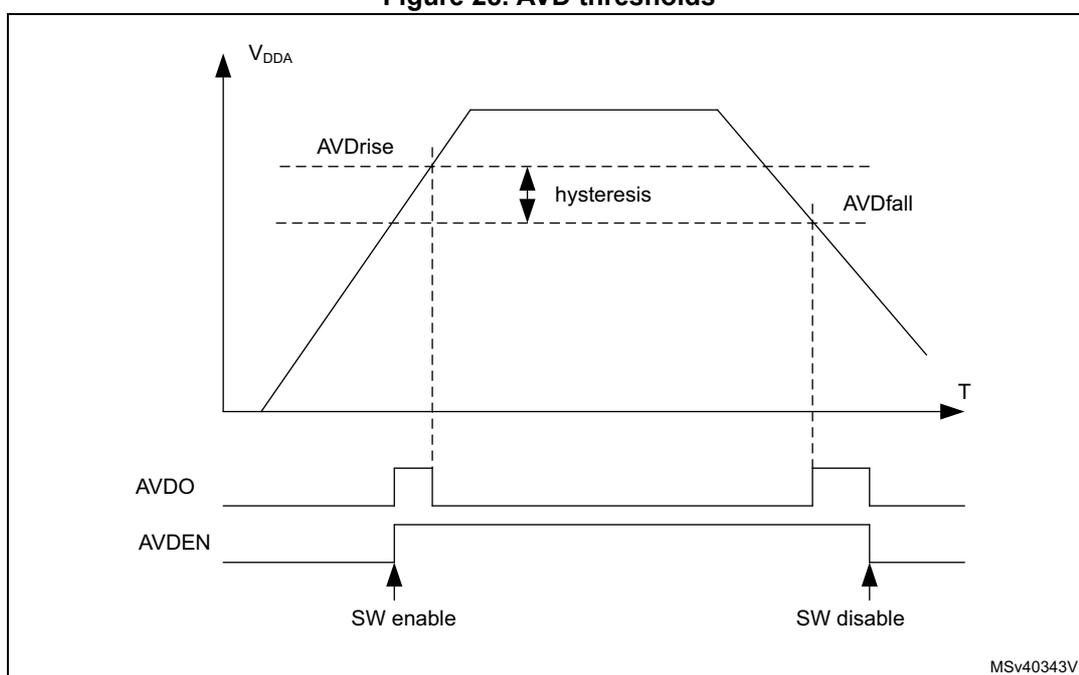

6.5.4 Analog voltage detector (AVD)

The AVD can be used to monitor the \( V_{DDA} \) supply by comparing it to a threshold selected by the ALS[1:0] bits in the PWR control register 1 (PWR_CR1) .

The AVD is enabled by setting the AVDEN bit in PWR control register 1 (PWR_CR1) .

An AVDO flag is available in the PWR control status register 1 (PWR_CSR1) to indicate whether \( V_{DDA} \) is higher or lower than the AVD threshold. This event is internally connected to the EXTI and can generate an interrupt if enabled through the EXTI registers. The AVDO interrupt can be generated when \( V_{DDA} \) drops below the AVD threshold and/or when \( V_{DDA} \) rises above the AVD threshold depending on EXTI rising/falling edge configuration. As an example the service routine could indicate when the \( V_{DDA} \) supply drops below a minimum level.

Figure 28. AVD thresholds

The figure illustrates the operation of the Analog Voltage Detector (AVD). The top graph plots the supply voltage \( V_{DDA} \) against time (T). The voltage rises to a peak and then falls. Two horizontal dashed lines represent the AVDrise (rising threshold) and AVDfall (falling threshold) levels. The vertical gap between these thresholds is labeled 'hysteresis'. Below the graph, two digital signals are shown: AVDO (Analog Voltage Detector Output) and AVDEN (Analog Voltage Detector Enable). AVDO is high when \( V_{DDA} \) is between the thresholds and low otherwise. AVDEN is high when the system is enabled ('SW enable') and low when disabled ('SW disable').

- 1. For thresholds and hysteresis values, refer to the datasheets.

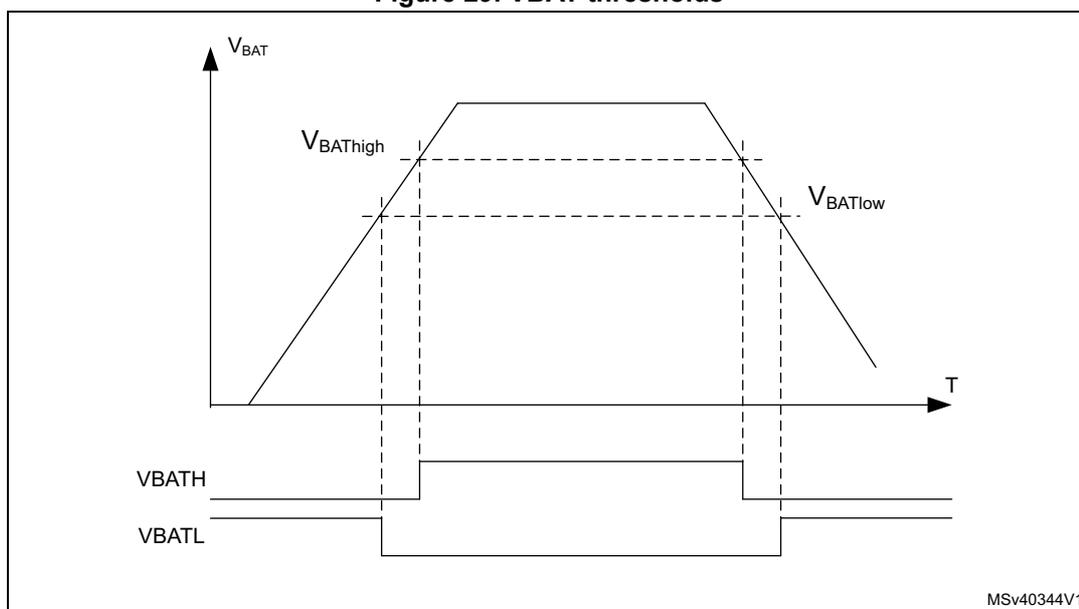

6.5.5 Battery voltage thresholds

The battery voltage supply monitors the backup domain \( V_{SW} \) level. \( V_{SW} \) is monitored by comparing it with two threshold levels: \( V_{BATHigh} \) and \( V_{BATLow} \) . \( VBATH \) and \( VBATL \) flags in the PWR control register 2 (PWR_CR2) , indicate if \( V_{SW} \) is higher or lower than the threshold.

The \( V_{BAT} \) supply monitoring can be enabled/disabled via \( MONEN \) bit in PWR control register 2 (PWR_CR2) . When it is enabled, the battery voltage thresholds increase power consumption. As an example the \( V_{SW} \) levels monitoring could be used to trigger a tamper event for an over or under voltage of the RTC power supply domain (available in \( VBAT \) mode).

\( VBATH \) and \( VBATL \) are connected to RTC tamper signals (see Section 51: Real-time clock (RTC) ).

Note: Battery voltage monitoring is only available when the backup regulator is enabled ( \( BREN \) bit set in PWR control register 2 (PWR_CR2) ).

When the device does not operate in \( VBAT \) mode, the battery voltage monitoring checks \( V_{DD} \) level. When \( V_{DD} \) is available, \( V_{SW} \) is connected to \( V_{DD} \) through the internal power switch (see Section 6.4.4: Backup domain ).

Figure 29. \( VBAT \) thresholds

The figure illustrates the battery voltage ( \( V_{BAT} \) ) monitoring process over time ( \( T \) ). The top graph shows \( V_{BAT} \) as a trapezoidal waveform. Two horizontal dashed lines represent the threshold levels \( V_{BATHigh} \) and \( V_{BATLow} \) . Below the graph, two digital signals are shown: \( VBATH \) and \( VBATL \) . \( VBATH \) is high when \( V_{BAT} > V_{BATHigh} \) and low otherwise. \( VBATL \) is low when \( V_{BAT} < V_{BATLow} \) and high otherwise. Vertical dashed lines indicate the transitions of these signals corresponding to the crossings of the voltage thresholds. The identifier MSv40344V1 is located in the bottom right corner of the diagram area.

- 1. For thresholds and hysteresis values, refer to the datasheets.

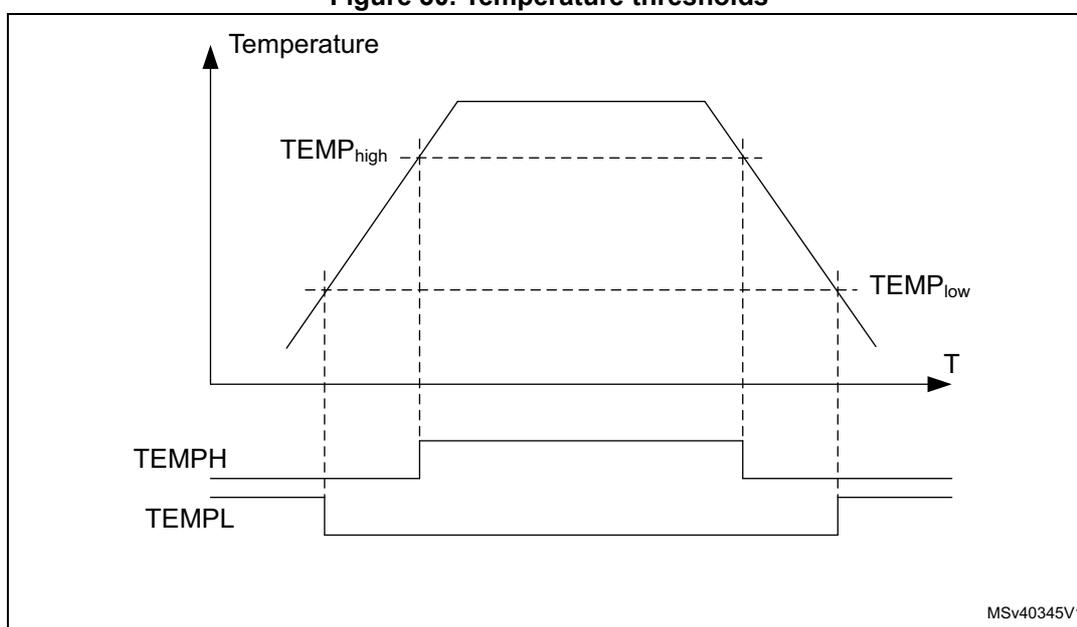

6.5.6 Temperature thresholds

The junction temperature can be monitored by comparing it with two threshold levels, \( TEMP_{high} \) and \( TEMP_{low} \) . \( TEMPH \) and \( TEMPL \) flags, in the PWR control register 2 (PWR_CR2) , indicate whether the device temperature is higher or lower than the threshold. The temperature monitoring can be enabled/disabled via \( MONEN \) bit in PWR control register 2 (PWR_CR2) . When enabled, the temperature thresholds increase power consumption. As an example the levels could be used to trigger a routine to perform temperature control tasks.

The temperature thresholds are available only when the backup regulator is enabled ( \( BREN \) bit set in the PWR_CR2 register).

\( TEMPH \) and \( TEMPL \) wakeup interrupts are available on the RTC tamper signals (see Section 51: Real-time clock (RTC) ).

Figure 30. Temperature thresholds

MSv40345V1

1. For thresholds and hysteresis values, refer to the datasheets.

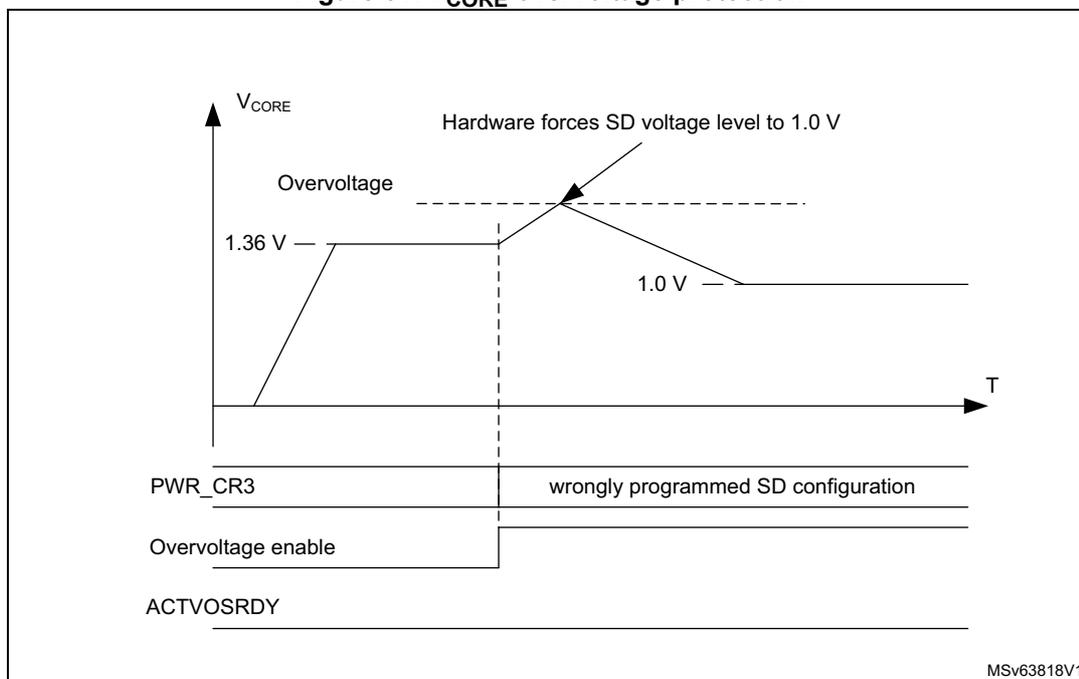

6.5.7 \( V_{CORE} \) maximum voltage level detector

\( V_{CORE} \) is protected against too high voltages in the direct SMPS step-down converter supply configuration. \( V_{CORE} \) overvoltage protection is enabled at startup by hardware once the SMPS step-down converter configuration has been programmed into PWR control register 3 (PWR_CR3) :

- •

\(

V_{CORE}

\)

voltage level stays within range:

- – \( ACTVOSRDY \) bit in PWR control status register 1 (PWR_CSR1) indicate valid voltage levels.

- – The system operates normally and \( V_{CORE} \) overvoltage protection is disabled.

- • \( V_{CORE} \) overvoltage (due to a wrongly programmed SMPS step-down converter configuration):

- – The hardware forces the SMPS step-down converter voltage level to 1.0 V.

- – The ACTVOSRDY goes on indicating invalid voltage levels. In this case the software must be corrected and re-loaded to program a correct SMPS step-down converter configuration that matches the application supply connections. The system must then be power cycled.

The figure illustrates the \( V_{CORE} \) overvoltage protection mechanism. The top graph plots \( V_{CORE} \) against time (T). The voltage rises to 1.36 V, labeled as 'Overvoltage', and then drops to 1.0 V. A label 'Hardware forces SD voltage level to 1.0 V' points to the 1.0 V level. Below the graph, three timing diagrams show: PWR_CR3 (labeled 'wrongly programmed SD configuration'), Overvoltage enable, and ACTVOSRDY. The MSV63818V1 code is in the bottom right.

6.6 Power management

The power management block controls the \( V_{CORE} \) supply in accordance with the system operation modes (see Section 6.6.1 ).

The \( V_{CORE} \) domain is split into the following power domains.

- • D1 domain containing some peripherals and the Cortex®-M7 Core.

- • D2 domain containing a large part of the peripherals.

- • D3 domain containing some peripherals and the system control.

The D1, D2 and system D3 power domains can operate in one of the following operating modes:

- • DRun/Run/Run* (power ON, clock ON)

- • DStop/Stop (power ON, clock OFF)

- • DStandby/Standby (Power OFF, clock OFF).

The operating modes for D1 domain and D2 domain are independent. However system D3 domain power modes depend on D1 and D2 domain modes:

- • For system D3 domain to operate in Stop mode, both D1 and D2 domains must be in DStop or DStandby mode.

- • For system D3 domain to operate in Standby mode, both D1 and D2 domains must be in DStandby too.

D1, D2 and system D3 domains are supplied from a single regulator at a common \( V_{CORE} \) level. The \( V_{CORE} \) supply level follows the system operating mode (Run, Stop, Standby). The D1 domain and/or D2 domain supply can be powered down individually when the domains are in DStandby mode.

The following voltage scaling features allow controlling the power with respect to the required system performance (see Section 6.6.2: Voltage scaling ):

- • To obtain a given system performance, the corresponding voltage scaling must be set in accordance with the system clock frequency. To do this, configure the VOS bits to the Run mode voltage scaling.

- • To obtain the best trade-off between power consumption and exit-from-Stop mode latency, configure the SVOS bits to Stop mode voltage scaling.

6.6.1 Operating modes

Several system operating modes are available to tune the system according to the performance required, i.e. when the CPU does not need to execute code and are waiting for an external event. It is up to the user to select the operating mode that gives the best compromise between low power consumption, short startup time and available wakeup sources.

The operating modes allow controlling the clock distribution to the different system blocks and powering them. The system operating mode is driven by the CPU subsystem, D2 subsystem and system D3 autonomous wakeup. A CPU subsystem can include multiple domains depending on its peripheral allocation (see Section 8.5.11: Peripheral clock gating control ).

The following operating modes are available for the different system blocks (see Table 31 ):

- • CPU subsystem modes:

- –

CRun

CPU and CPU subsystem peripheral allocated via RCC PERxEN bits are clocked. - –

CSleep

The CPU clock is stalled and the CPU subsystem allocated peripheral(s) clock operate according to RCC PERxLPEN. - –

CStop

CPU and CPU subsystem peripheral clocks are stalled.

- –

CRun

- • D1 domain mode:

- –

DRun

The domain bus matrix is clocked. The CPU subsystem operates in CRun or CSleep mode. - –

DStop

The domain bus matrix clock is stalled.

The CPU subsystem operates in CStop mode and the PDDS_D1 (a) bit selects DStop mode. - –

DStandby

The domain is powered down.

The CPU subsystem operates in CStop mode and the PDDS_D1 bit selects DStandby mode.

- –

DRun

- • D2 domain mode:

- –

DRun

The domain bus matrix is clocked.

The CPU subsystem has an allocated peripheral in the D2 domain and the CPU subsystem operates in CRun or CSleep mode.

- –

DRun

a. The PDDS_Dn bits belong to PWR CPU control register (PWR_CPUCR) .

- –

DStop

The domain bus matrix clock is stalled.

The CPU subsystem has no peripherals allocated in the D2 domain and PDDS_D2 (a) bit selects DStop mode,

or

the CPU subsystem has an allocated peripheral in D2 domain, the CPU subsystem operates in CStop mode and PDDS_D2 bit selects DStop mode. - –

DStandby

The domain is powered down.

The CPU subsystem has no peripherals allocated in the D2 domain and PDDS_D2 bit selects DStandby mode,

or

the CPU subsystem has an allocated peripheral in the D2 domain, the CPU subsystem operates in CStop mode and PDDS_D2 bit selects DStandby mode. - • System /D3 domain modes

- –

Run/Run*

The system clock and D3 domain bus matrix clock are running:- - The CPU subsystem is in CRun or CSleep mode

- or

- - A wakeup signal is active. (i.e. System D3 Autonomous mode)

- –

Stop

The system clock and D3 domain bus matrix clock is stalled:- - The CPU subsystem is in CStop mode.

- and

- - all wakeup signals are inactive.

- and

- - At least one PDDS_Dn (a) bit for any domain select Stop mode.

- –

Standby

The system is powered down:- - The CPU subsystem is in CStop mode

- and

- - all wakeup signals are inactive.

- and

- - All PDDS_Dn (a) bits for all domains select Standby mode.

- –

Run/Run*

In Run mode, power consumption can be reduced by one of the following means:

- • Lowering the system performance by slowing down the system clocks and reducing the V CORE supply level through VOS voltage scaling bits.

- • Gating the clocks to the APBx and AHBx peripherals when they are not used, through PERxEN bits.

Table 31. Summary of the operating mode

| System | Domain | CPU | Entry | Wakeup | System oscillator | System clock | Domain bus matrix clk | Peripheral clock | CPU clock | Voltage regulator | Domain supply |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Run | DRun (1) | CRun | - | - | ON | ON | ON | ON | ON | ON | ON |

| CSleep | WFI or return from ISR or WFE | Any interrupt or event | ON/OFF (2) | OFF | |||||||

| SLEEPDEEP bit + WFI or return from ISR or WFE | Any EXTI interrupt or event | ON/OFF (3) | |||||||||

| DStop | CStop | SLEEPDEEP bit + WFI or return from ISR or WFE | ON/OFF (6) | OFF | OFF | OFF | OFF | ON | OFF | ||

| DStandby | SLEEPDEEP bit + WFI or return from ISR or WFE or Wakeup source cleared (5) | ||||||||||

| Stop (4) | DStop | ON | |||||||||

| Stop (4) | DStandby | OFF | |||||||||

| Standby (7) | DStandby | All PDDS_Dn bit + SLEEPDEEP bit + WFI or return from ISR or WFE or Wakeup source cleared (5) | WKUP pins rising or falling edge, RTC alarm (Alarm A or Alarm B), RTC Wakeup event, RTC tamper events, RTC time stamp event, external reset in NRST pin, IWDG reset | OFF | OFF | OFF | |||||

1. In the D2 domain, the CPU subsystem has an allocated peripheral in the domain and operates in CRun or CSleep mode.

2. The CPU subsystem peripherals that have a PERxLPEN bit will operate accordingly.

3. The CPU subsystem peripherals located in the D3 domain that have a PERxAMEN bit operate accordingly.

4. All domains need to be in DStop Or DStandby.

5. When the CPU is in CStop and D3 domain in Autonomous mode, the last EXTI Wakeup source is cleared.

6. When the system oscillator HSI or CSI is used, the state is controlled by HSIKERON and CSICKERON, otherwise the system oscillator is OFF.

7. All domains are in DStandby mode.

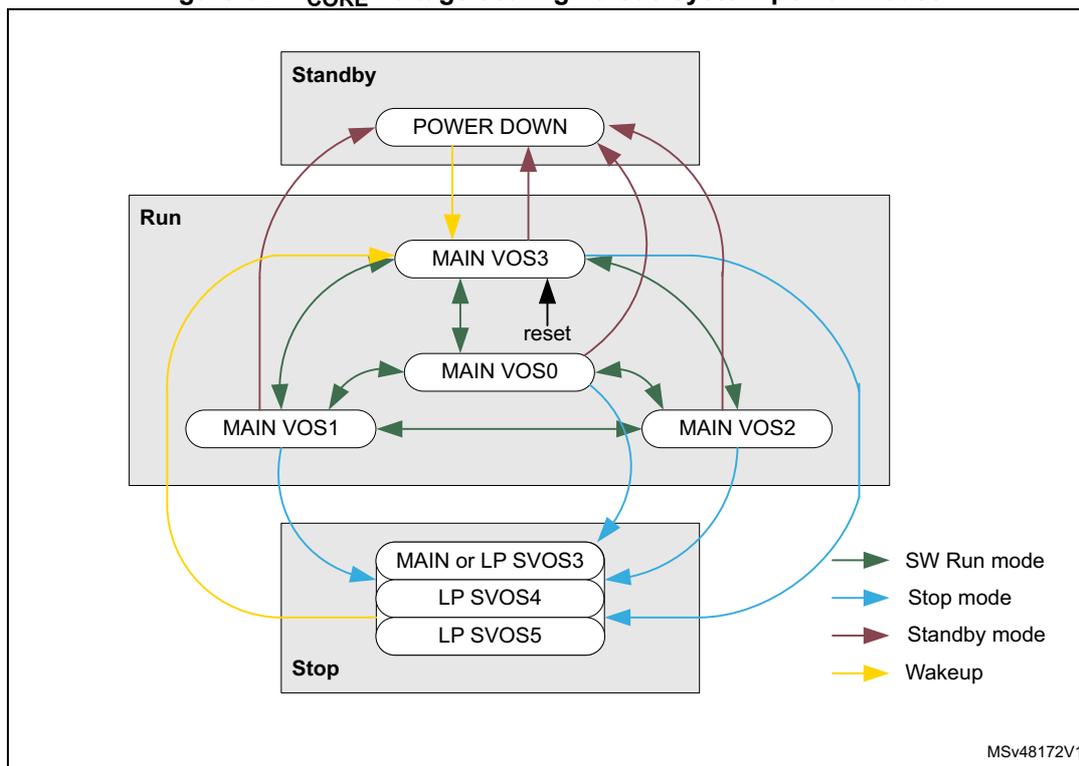

6.6.2 Voltage scaling

The D1, D2, and D3 domains are supplied from a single voltage regulator supporting voltage scaling with the following features:

- • Run mode voltage scaling

- – VOS0: Scale 0 ( \( V_{\text{CORE}} \) boost)

- – VOS1: Scale 1

- – VOS2: Scale 2

- – VOS3: Scale 3

- • Stop mode voltage scaling

- – SVOS3: Scale 3

- – LP-SVOS4: Scale 4

- – LP-SVOS5: Scale 5

For more details on voltage scaling values, refer to the product datasheets.

After reset, the system starts on the lowest Run mode voltage scaling (VOS3). The voltage scaling can then be changed on-the-fly by software by programming VOS bits in PWR D3 domain control register (PWR_D3CR) according to the required system performance. When exiting from Stop mode or Standby mode, the Run mode voltage scaling is reset to the default VOS3 value.

Before entering Stop mode, the software can preselect the SVOS level in PWR control register 1 (PWR_CR1) . The Stop mode voltage scaling for SVOS4 and SVOS5 also sets the voltage regulator in Low-power (LP) mode to further reduce power consumption. When preselecting SVOS3, the use of the voltage regulator low-power mode (LP) can be selected by LPDS register bit.

Figure 32.\( V_{CORE} \) voltage scaling versus system power modes

6.6.3 Power control modes

The power control block handles the \( V_{CORE} \) supply for system Run, Stop and Standby modes.

The system operating mode depends on the CPU subsystem modes (CRun, CSleep, CStop), on the domain modes (DRun, DStop, DStandby), and on the system D3 autonomous wakeup:

- • In Run mode and Autonomous mode, \( V_{CORE} \) is defined by the VOS voltage scaling. The CPU subsystem is in CRun or CSleep or an EXTI wakeup is active.

- • In Stop mode, \( V_{CORE} \) is defined by the SVOS voltage scaling. The CPU subsystem is in CStop mode and no EXTI wakeup is pending. The D1 domain and D2 domain are either in DStop or DStandby mode.

- • In Standby mode, \( V_{CORE} \) supply is switched off. The CPU subsystem is in CStop mode and no EXTI wakeup is pending. The D1 domain and D2 domain are both in DStandby mode.

The domain operating mode can depend on the CPU subsystem when peripherals are allocated in the corresponding domain. The domain mode selection between DStop and DStandby is configured via domain dedicated PDDS_Dn bits in PWR CPU control register (PWR_CPUCR) . The CPU can choose to keep a domain in DStop, or allow a domain to enter DStandby mode.

If a domain is in DStandby mode, the corresponding power is switched off.

All the domains can be configured for the system mode (Stop or Standby) through PDDS_Dn bits in PWR CPU control register (PWR_CPUCR) . The system enters Standby only when all PDDS_Dn bits for all domains have allowed it.

Table 32. PDDS_Dn low-power mode control

| PWR_CPUCR | D1 mode | D2 mode | D3 mode | ||

|---|---|---|---|---|---|

| PDDS_D1 | PDDS_D2 | PDDS_D3 | |||

| 0 | x | x | DStop | DStop or DStandby | Run or Stop |

| 1 | DStandby | DStop or DStandby | any | ||

| x | 0 | any | DStop | Run or Stop | |

| 1 | any | DStandby | any | ||

| at least one = 0 | DStop or DStandby | DStop or DStandby | Stop | ||

| 1 | 1 | 1 | DStandby | DStandby | Standby |

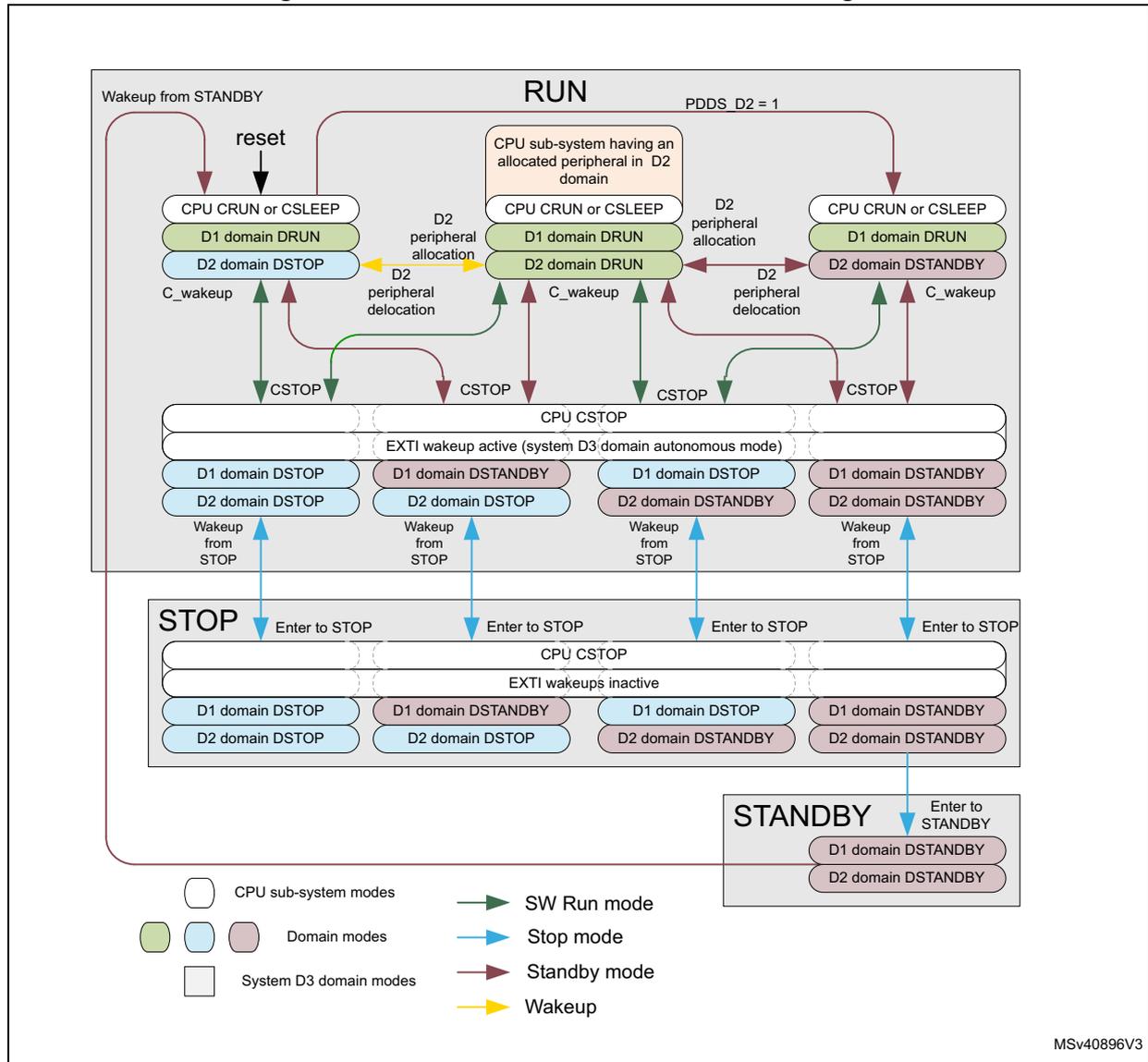

Figure 33. Power control modes detailed state diagram

The diagram illustrates the power control modes for a microcontroller, organized into three main states: RUN, STOP, and STANDBY.

- RUN State:

- Contains three CPU sub-system mode boxes: "CPU CRUN or CSLEEP".

- Each CPU box is associated with a "D1 domain DRUN" (green) and a "D2 domain" mode (blue or pink).

- Transitions between D1 and D2 modes are labeled "D2 peripheral allocation" (yellow arrow) and "D2 peripheral delocation" (red arrow).

- Transitions from D2 modes to "CPU CSTOP" (white) are labeled "CSTOP" (green arrow).

- Transitions from "CPU CSTOP" back to D2 modes are labeled "C_wakeup" (green arrow).

- A central box indicates "CPU sub-system having an allocated peripheral in D2 domain".

- A condition "PDDS_D2 = 1" is shown in the top right.

- A "reset" arrow points to the first CPU box.

- A "Wakeup from STANDBY" arrow points from the STANDBY state to the first CPU box.

- STOP State:

- Entered via "Enter to STOP" (blue arrow) from the RUN state.

- Contains a "CPU CSTOP" (white) mode.

- Below it, "EXTI wakeups inactive" (white).

- Associated with "D1 domain DSTOP" (blue) and "D2 domain DSTOP" (blue) modes.

- Transitions from these modes to "Wake up from STOP" (blue arrow) and back to "Enter to STOP" (blue arrow).

- STANDBY State:

- Entered via "Enter to STANDBY" (blue arrow) from the STOP state.

- Contains "D1 domain DSTANDBY" (pink) and "D2 domain DSTANDBY" (pink) modes.

Legend:

- White box: CPU sub-system modes

- Green box: D1 domain modes

- Blue box: D2 domain modes

- Pink box: System D3 domain modes

- Green arrow: SW Run mode

- Blue arrow: Stop mode

- Red arrow: Standby mode

- Yellow arrow: Wakeup

MSV40896V3

After a system reset, the CPU is in CRun mode.

Power control state transitions are initiated by the following events:

- • CPU going to CStop mode (state transitions in Run mode are marked in green and red)

- – Green transitions: CPU wakes up as from CSleep.

- – Red transitions: CPU wakes up with domain reset. The SBF_Dn is set.

- • Allocating or deallocating a peripheral in a domain (state transitions in Run mode are marked in orange and red)

- – Orange transitions: the domain wakes up from DStop

- – Red transitions: the domain wakes up from DStandby. The SBF_Dn is set.

- • The system enters or exits from Stop mode (state transitions marked in blue)

- – Blue transitions the system wakes up from Stop mode. The STOPF is set.

- • The system enters or exits from Standby mode (state transitions in Stop and Standby mode are marked in red).

- – When exiting from Standby mode, the SBF is set.

When a domain exits from DStandby, the domain peripherals are reset, while the domain SBF_Dn bit is set (state transitions causing a domain reset are marked in red).

Table 33 shows the flags that indicate from which mode the domain/system exits. The CPU features a set of flags which can be read from PWR CPU control register (PWR_CPUCR) .

Table 33. Low-power exit mode flags

| System mode | D1 domain mode | D2 domain mode | SBF_D1 | SBF_D2 | SBF | STOPF | Comment |

|---|---|---|---|---|---|---|---|

| Run | DRun or DStop | DRun or DStop | 0 | 0 | 0 | 0 | D1, D2 and system contents retained |

| Run | DStandby | DStop | 1 | 0 | 0 | 0 | D1 contents lost, D2 and system contents retained |

| Run | DRun or DStop | DStandby | 0 | 1 | 0 | 0 | D2 contents lost, D1 and system contents retained |

| Run | DStandby | DStandby | 1 | 1 | 0 | 0 | D1 and D2 contents lost, system contents retained |

| Stop | DStop | DStop | 0 | 0 | 0 | 1 | D1, D2 and system contents retained, clock system reset. |

| Stop | DStandby | DStop | 1 | 0 | 0 | 1 | D1 contents lost, D2 and system contents retained, clock system reset |

| Stop | DStop | DStandby | 0 | 1 | 0 | 1 | D2 contents lost, D1 and system contents retained, clock system reset |

| Stop | DStandby | DStandby | 1 | 1 | 0 | 1 | D1 and D2 contents lost, system contents retained, clock system reset |

| Standby | DStandby | DStandby | 0 (1) | 0 (1) | 1 | 0 | D1, D2 and system contents lost |

1. When returning from Standby, the SBF_D1 and SBF_D2 reflect the reset value.

6.6.4 Power management examples

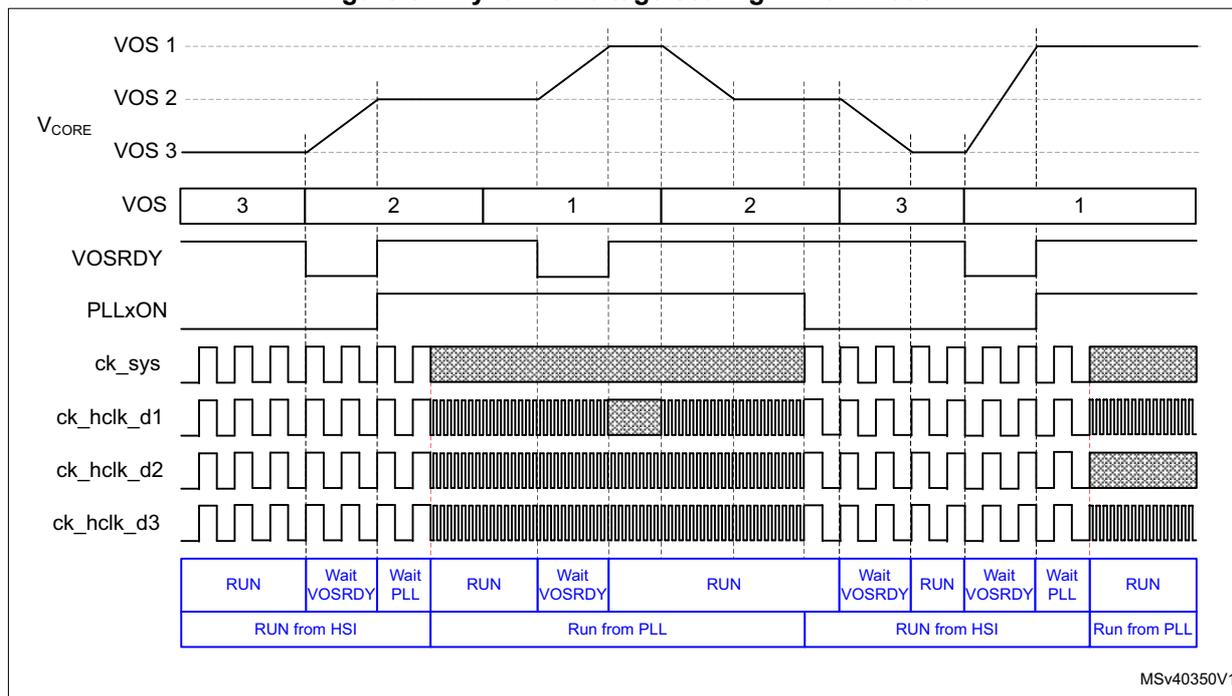

- • Figure 34 shows \( V_{CORE} \) voltage scaling behavior in Run mode.

- • Figure 35 shows \( V_{CORE} \) voltage scaling behavior in Stop mode.

- • Figure 36 shows \( V_{CORE} \) voltage regulator and voltage scaling behavior in Standby mode.

- • Figure 37 shows \( V_{CORE} \) voltage scaling behavior in Run mode with D1 and D2 domains are in DStandby mode

Example of \( V_{CORE} \) voltage scaling behavior in Run mode

Figure 34 illustrates the following system operation sequence example:

- 1. After reset, the system starts from HSI with VOS3.

- 2. The system performance is first increased to a medium-speed clock from the PLL with voltage scaling VOS2. To do this:

- a) Program the voltage scaling to VOS2.

- b) Once the \( V_{CORE} \) supply has reached the required level indicated by VOSRDY, increase the clock frequency by enabling the PLL.

- c) Once the PLL is locked, switch the system clock.

- 3. The system performance is then increased to high-speed clock from the PLL with voltage scaling VOS1. To do this:

- a) Program the voltage scaling to VOS1.

- b) Once the \( V_{CORE} \) supply has reached the required level indicated by VOSRDY, increase the clock frequency.

- 4. The system performance is then reduced to a medium-speed clock with voltage scaling VOS2. To do this:

- a) First decrease the system frequency.

- b) Then decrease the voltage scaling to VOS2.

- 5. The next step is to reduce the system performance to HSI clock with voltage scaling VOS3. To do this:

- a) Switch the clock to HSI.

- b) Disable the PLL.

- c) Decrease the voltage scaling to VOS3.

- 6. The system performance can then be increased to high-speed clock from the PLL. To do this:

- a) Program the voltage scaling to VOS1.

- b) Once the \( V_{CORE} \) supply has reached the required level indicated by VOSRDY, increase the clock frequency by enabling the PLL.

- c) Once the PLL is locked, switch the system clock.

When the system performance (clock frequency) is changed, VOS shall be set accordingly, otherwise the system might be unreliable.

Figure 34. Dynamic voltage scaling in Run mode

The diagram illustrates the timing of dynamic voltage scaling. The top section shows the V CORE voltage levels (VOS 1, 2, 3) and the VOSRDY signal. The bottom section shows the system clock (ck_sys) and domain clocks (ck_hclk_d1, d2, d3). The state transition table at the bottom details the sequence of states: RUN, Wait VOSRDY, and Wait PLL, indicating whether the system is running from HSI or PLL.

| RUN | Wait VOSRDY | Wait PLL | RUN | Wait VOSRDY | RUN | Wait VOSRDY | RUN | Wait VOSRDY | Wait PLL | RUN |

| RUN from HSI | Run from PLL | RUN from HSI | Run from PLL | |||||||

MSV40350V1

1. The status of the register bits at each step is shown in blue.

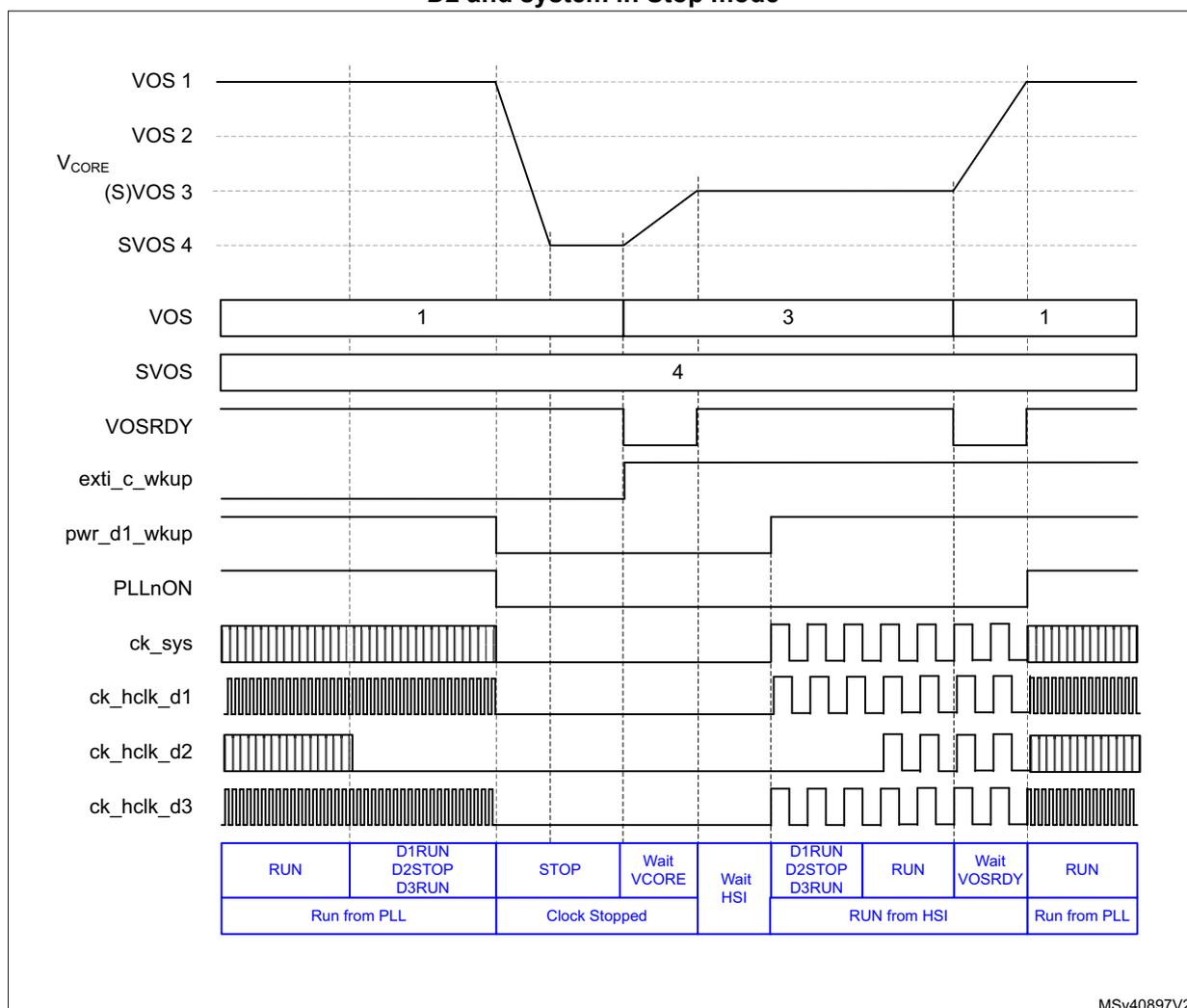

Example of V CORE voltage scaling behavior in Stop mode

Figure 35 illustrates the following system operation sequence example:

- 1. The system is running from the PLL in high-performance mode (VOS1 voltage scaling).

- 2. The CPU subsystem deallocates all the peripheral in the D2 domain that will first enter DStop mode. D2 system clock is stopped. The system still provides the high-performance system clock, hence the voltage scaling shall stay at VOS1 level.

- 3. In a second step, the CPU subsystem enters CStop mode, D1 domain enters DStop mode and the system enters Stop mode. The system clock is stopped and the hardware lowers the voltage scaling to the software preselected SVOS4 level.

- 4. The CPU subsystem is then woken up. The system exits from Stop mode, the D1 domain exits from DStop mode and the CPU subsystem exits from CStop mode. The hardware then sets the voltage scaling to VOS3 level and waits for the requested supply level to be reached before enabling the HSI clock. Once the HSI clock is stable, the system clock and the D1 system clock are enabled.

- 5. The CPU subsystem allocates a peripheral in the D2 domain. The D2 system clock is enabled.

- 6. The system performance is then increased. To do this:

- a) The software first sets the voltage scaling to VOS1.

- b) Once the V CORE supply has reached the required level indicated by VOSRDY, the clock frequency can be increased by enabling the PLL.

- c) Once the PLL is locked, the system clock can be switched.

Figure 35. Dynamic voltage scaling behavior with D1, D2 and system in Stop mode

| RUN | D1RUN D2STOP D3RUN | STOP | Wait VCORE | Wait HSI | D1RUN D2STOP D3RUN | RUN | Wait VOSRDY | RUN |

| Run from PLL | Clock Stopped | RUN from HSI | Run from PLL | |||||

MSv40897V2

- 1. The status of the register bits at each step is shown in blue.

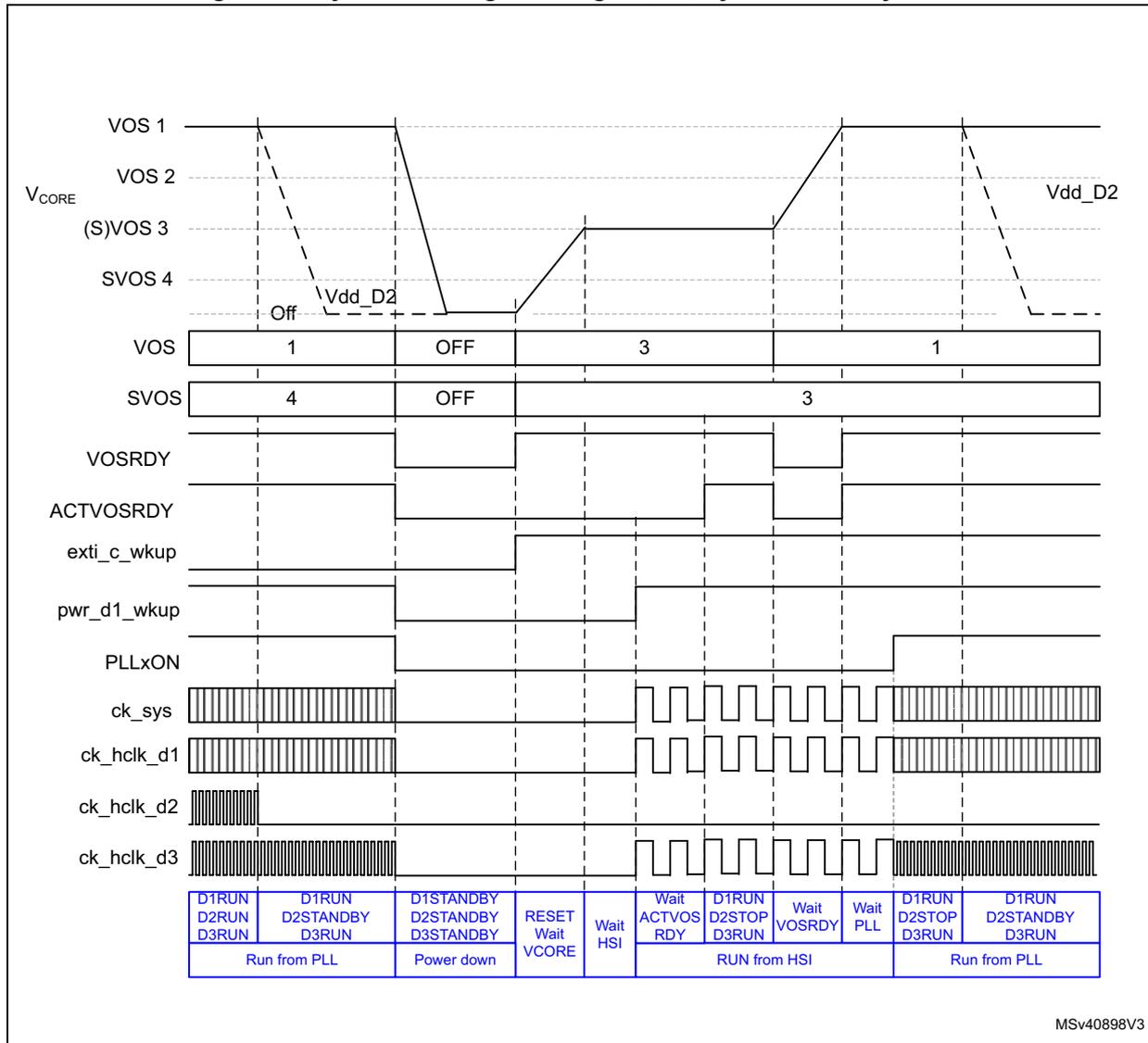

Example of V CORE voltage regulator and voltage scaling behavior in Standby mode

Figure 36 illustrates the following system operation sequence example:

- 1. The system is running from the PLL in high-performance mode (VOS1 voltage scaling).

- 2. The CPU subsystem deallocates all the peripherals in the D2 domain that will first enter DStandby mode. The D2 domain bus matrix clock is stopped and the power is switched off. The system performance is unchanged hence the voltage scaling does not change.

- 3. The CPU subsystem then enters CStop mode, D1 domain enters DStandby mode and the system enters Standby mode. The system clock is stopped and the voltage regulator switched off.

- 4. The system is then woken up by a wakeup source. The system exits from Standby mode. The hardware sets the voltage scaling to the default VOS3 level and waits for the requested supply level to be reached before enabling the default HSI oscillator. Once the HSI clock is stable, the system clock and D1 subsystem clock are enabled.

Since there are no allocated peripherals in the D2 domain, this domain remains in DStop mode. The software shall then check the ACTVOSRDY is valid before changing the system performance.

- 5. In a next step, increase the system performance. To do this:

- a) The software first increases the voltage scaling to VOS1 level

- b) Before enabling the PLL, it waits for the requested supply level to be reached by monitoring VOSRDY bit.

- c) Once the PLL is locked, the system clock can be switched.

- 6. The CPU subsystem puts the D2 domain in DStandby mode.

Figure 36. Dynamic Voltage Scaling D1, D2, system Standby mode

The diagram illustrates the sequence of events for dynamic voltage scaling and system clock management. The top section shows the voltage levels (VOS 1, VOS 2, (S)VOS 3, SVOS 4) and the V CORE supply. The middle section shows the status of control bits (VOS, SVOS, VOSRDY, ACTVOSRDY, exti_c_wkup, pwr_d1_wkup, PLLxON) and system clocks (ck_sys, ck_hclk_d1, ck_hclk_d2, ck_hclk_d3). The bottom section, highlighted in blue, shows the system states: 'Run from PLL', 'Power down', 'RUN from HSI', and 'Run from PLL'.

MSV40898V3

- 1. The status of the register bits at each step is shown in blue.

Example of \( V_{CORE} \) voltage scaling behavior in Run mode with D1 and D2 domains in DStandby mode

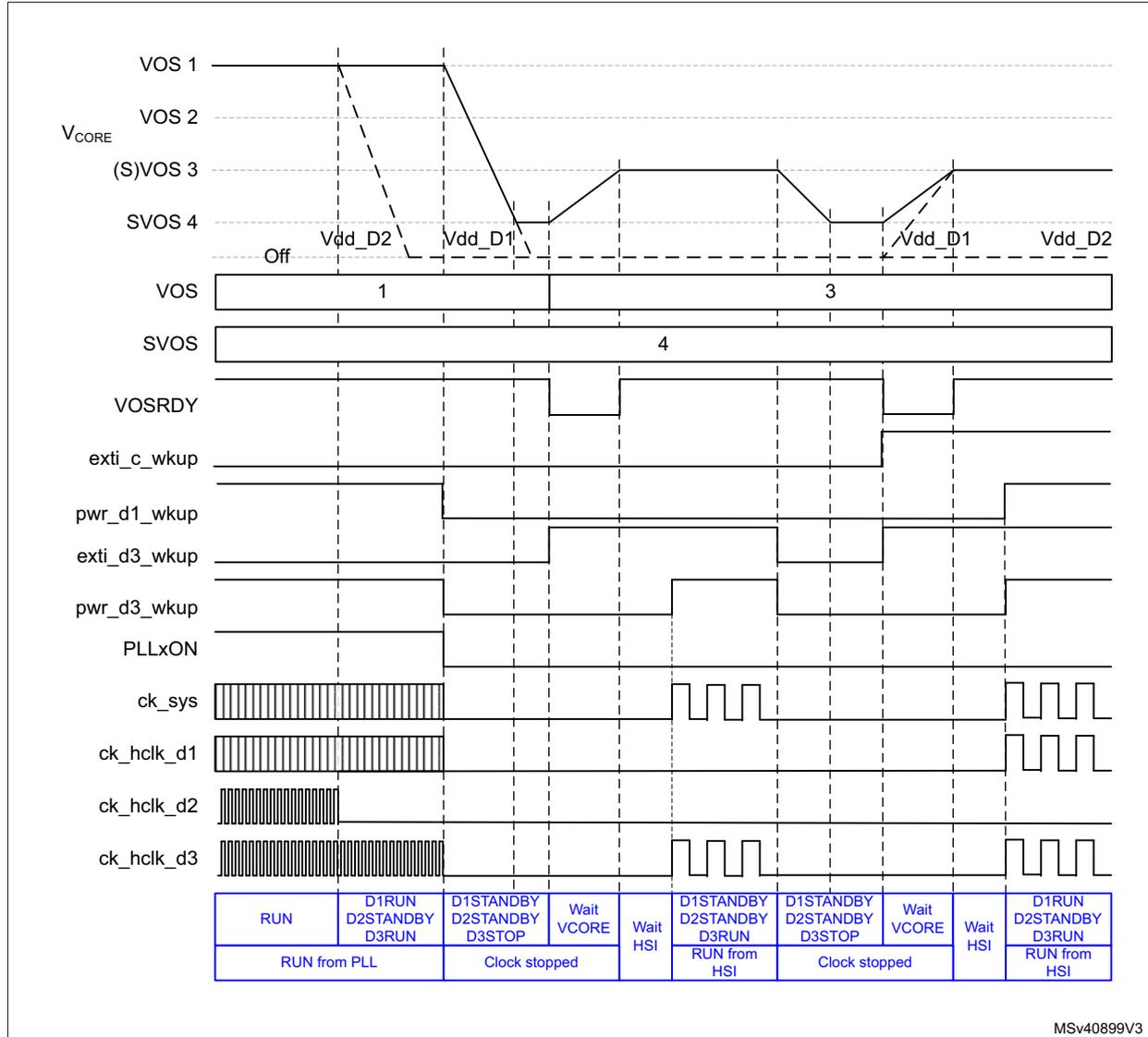

Figure 37 illustrates the following system operation sequence example:

- 1. The system is running from the PLL with system in high performance mode (VOS1 voltage scaling).

- 2. The CPU subsystem deallocates all the peripherals in the D2 domain that will first enter DStandby mode. The D2 domain bus matrix clock is stopped and its power switched off. The system performance is unchanged hence the voltage scaling does not change.

- 3. The CPU subsystem then enters CStop mode and the D1 domain enters DStandby mode. The D1 domain bus matrix clock is stopped and its power switched off. At the same time the system enters Stop mode. The system clock is stopped and the hardware lowers the voltage scaling to the software preselected SVOS4 level.

- 4. The system is then woken up by a D3 Autonomous mode wakeup event. The system exits from Stop mode. The hardware sets the voltage scaling to the default VOS3 level and waits for the requested supply level to be reached before enabling the HSI clock. Once the HSI clock is stable, the system clock is enabled. The system is running in D3 Autonomous mode.

- 5. The D3 Autonomous mode wakeup source is then cleared, causing the system to enter Stop mode. The system clock is stopped and the voltage scaling is lowered to the software preselected SVOS4 level.

- 6. The CPU subsystem is then woken up. The system exits from Stop mode, the D1 domain exits from DStandby mode and the CPU subsystem exits from CStop mode. The hardware sets the voltage scaling to the default VOS3 level and waits for the requested supply level to be reached before enabling the default HSI oscillator. Once the HSI clock is stable, the system clock and the D1 subsystem clock are enabled. The D2 domain remains in DStandby mode.

Figure 37. Dynamic voltage scaling behavior with D1 and D2 in DStandby mode and D3 in Autonomous mode

The figure is a timing diagram illustrating the dynamic voltage scaling (DVS) behavior of a microcontroller. It shows the relationship between voltage levels, system states, and clock signals over time.

Signal Levels:

- VOS 1, VOS 2, (S)VOS 3, SVOS 4: These signals represent voltage levels. The diagram shows transitions between Vdd_D2 and Vdd_D1 levels. VOS 1 and VOS 2 are shown as dashed lines, while (S)VOS 3 and SVOS 4 are solid lines.

- VOS: This signal is divided into two segments: 1 and 3 .

- SVOS: This signal is shown as a single segment labeled 4 .

- VOSRDY: This signal indicates the readiness of the voltage scaling. It is high during the RUN state and low during Wait VCORE and Wait HSI states.

- exti_c_wkup, pwr_d1_wkup, exti_d3_wkup, pwr_d3_wkup: These are wake-up signals. exti_c_wkup is high during Wait VCORE . pwr_d1_wkup and exti_d3_wkup are high during D1STANDBY and D2STANDBY states. pwr_d3_wkup is high during D3RUN and D3STOP states.

- PLLxON: This signal is high during the RUN state and low during other states.

- ck_sys, ck_hclk_d1, ck_hclk_d2, ck_hclk_d3: These are clock signals. ck_sys is a high-frequency clock. ck_hclk_d1 , ck_hclk_d2 , and ck_hclk_d3 are lower-frequency clocks. The diagram shows that ck_hclk_d1 and ck_hclk_d3 are active during RUN and D1RUN states, while ck_hclk_d2 is active during D1RUN and D2STANDBY states.

System States:

| RUN | D1RUN D2STANDBY D3RUN | D1STANDBY D2STANDBY D3STOP | Wait VCORE | Wait HSI | D1STANDBY D2STANDBY D3RUN | D1STANDBY D2STANDBY D3STOP | Wait VCORE | Wait HSI | D1RUN D2STANDBY D3RUN | |

| RUN from PLL | Clock stopped | RUN from HSI | Clock stopped | RUN from HSI | ||||||

MSV40899V3

- 1. The status of the register bits at each step is shown in blue.

6.7 Low-power modes

Several low-power modes are available to save power when the CPU does not need to execute code (i.e. when waiting for an external event). It is up to the user application to select the mode that gives the best compromise between low power consumption, short startup time and available wakeup sources:

- • Slowing down system clocks (see Section 8.5.6: System clock (sys_ck) )

- • Controlling individual peripheral clocks (see Section 8.5.11: Peripheral clock gating control )

- • Low-power modes

- – CSleep (CPU clock stopped)

- – CStop (CPU subsystem clock stopped)

- – DStop (Domain bus matrix clock stopped)

- – Stop (System clock stopped)

- – DStandby (Domain powered down)

- – Standby (System powered down)

6.7.1 Slowing down system clocks

In Run mode, the speed of the system clock

ck_sys

can be reduced. For more details refer to

Section 8.5.6: System clock (sys_ck)

.

6.7.2 Controlling peripheral clocks

In Run mode, the HCLKx and PCLKx for individual peripherals can be stopped by configuring at any time PERxEN bit in

RCC_C1_xxxxENR

or

RCC_xxxxENR

to reduce power consumption.

To reduce power consumption in CSleep mode, the individual peripheral clocks can be disabled by configuring PERxLPEN bit in

RCC_C1_xxxxLPENR

or

RCC_xxxxLPENR

. For the peripherals still receiving a clock in CSleep mode, their clock can be slowed down before entering CSleep mode.

6.7.3 Entering low-power modes

CPU subsystem CSleep and CStop low-power modes are entered by the MCU when executing the WFI (Wait For Interrupt) or WFE (Wait for Event) instructions, or when the SLEEPONEXIT bit in the Cortex ® -M System Control register is set on Return from ISR.

The D2 domain enters DStop or DStandby when the CPU subsystem has no peripheral allocated in the domain or is in CStop. The D1 domain enters DStop or DStandby when the CPU subsystem is in CStop.

The system can enter Stop or Standby low-power mode when all EXTI wakeup sources are cleared and the other domains are in DStop or DStandby mode.

6.7.4 Exiting from low-power modes

The CPU subsystem exits from CSleep mode through any interrupt or event depending on how the low-power mode was entered:

- • If the WFI instruction or Return from ISR was used to enter to low-power mode, any peripheral interrupt acknowledged by the NVIC can wake up the system.

- • If the WFE instruction is used to enter to low-power mode, the CPU exits from low-power mode as soon as an event occurs. The wakeup event can be generated either by:

- – An NVIC IRQ interrupt.

When SEVONPEND = 0 in the Cortex®-M7 System Control register, the interrupt must be enabled in the peripheral control register and in the NVIC.