4. Embedded Flash memory (FLASH)

4.1 Introduction

The embedded Flash memory (FLASH) manages the accesses of any master to the 1 Mbyte of embedded non-volatile memory. It implements the read, program and erase operations, error corrections as well as various integrity and confidentiality protection mechanisms.

The embedded Flash memory manages the automatic loading of non-volatile user option bytes at power-on reset, and implements the dynamic update of these options.

4.2 FLASH main features

- • Up to 1 Mbyte of non-volatile memory (one bank)

- • Flash memory read operations supporting multiple length (64 bits, 32bits, 16bits or one byte)

- • Flash memory programming by 256 bits

- • Sector erase, bank erase

- • Error Code Correction (ECC): one error detection/correction or two error detections per 256-bit Flash word using 10 ECC bits

- • Cyclic redundancy check (CRC) hardware module

- • User configurable non-volatile option bytes

- • Flash memory enhanced protections, activated by option bytes

- – Read protection (RDP), preventing unauthorized Flash memory dump to safeguard sensitive application code

- – Sector write-protection (128-Kbytes)

- – One proprietary code readout protection (PCROP) area. When enabled, this area is execute-only.

- – One secure-only area. When enabled this area is accessible only if the STM32 microcontroller operates in Secure access mode.

- • Read and write command queues to streamline Flash operations

4.3 FLASH functional description

4.3.1 FLASH block diagram

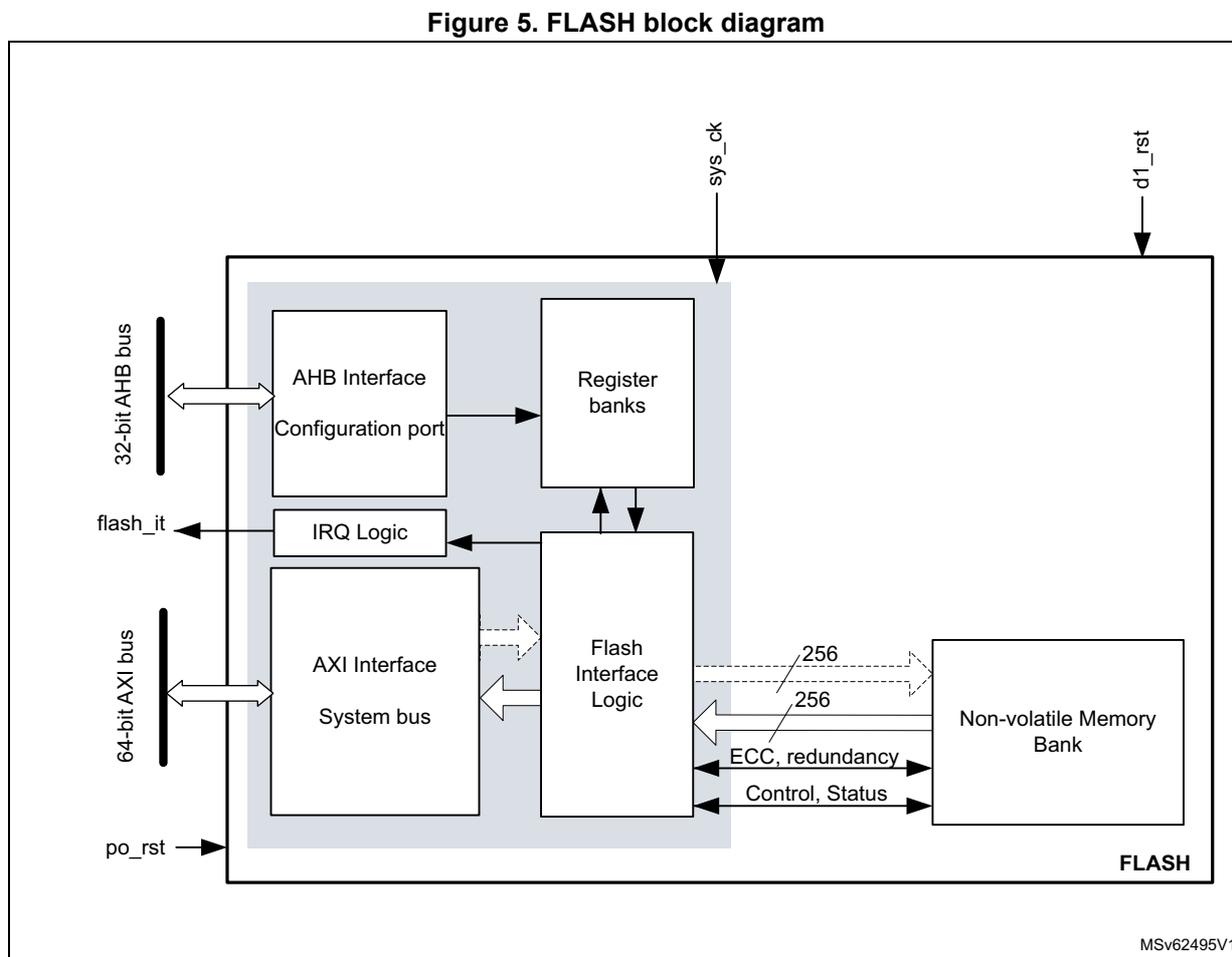

Figure 5 shows the embedded Flash memory block diagram.

Figure 5. FLASH block diagram

MSV62495V1

4.3.2 FLASH internal signals

Table 13 describes a list of the useful to know internal signals available at embedded Flash memory level. These signals are not available on the microcontroller pads.

Table 13. FLASH internal input/output signals

| Internal signal name | Signal type | Description |

|---|---|---|

| sys_ck | Input | D1 domain bus clock (embedded Flash memory AXI interface clock) |

| po_rst | Input | Power on reset |

| d1_rst | Input | D1 domain system reset |

| flash_it | Output | Embedded flash interface interrupt request |

4.3.3 FLASH architecture and integration in the system

The embedded Flash memory is a central resource for the whole microcontroller. It serves as an interface to one non-volatile memory bank, and organizes the memory in a very specific way. The embedded Flash memory also proposes a set of security features to protect the assets stored in the non-volatile memory at boot time, at run-time and during firmware and configuration upgrades.

The embedded Flash memory offers one 64-bit AXI slave ports for code and data accesses, plus a 32-bit AHB configuration slave port used for register bank accesses.

Note: The application can simultaneously request a read and a write operation through the AXI interface.

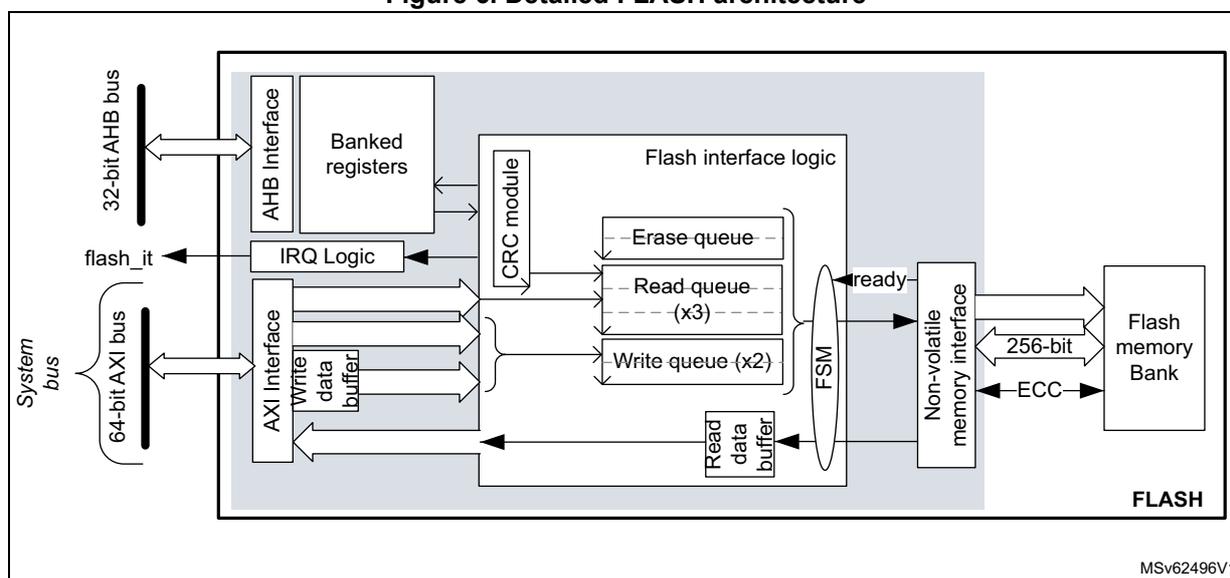

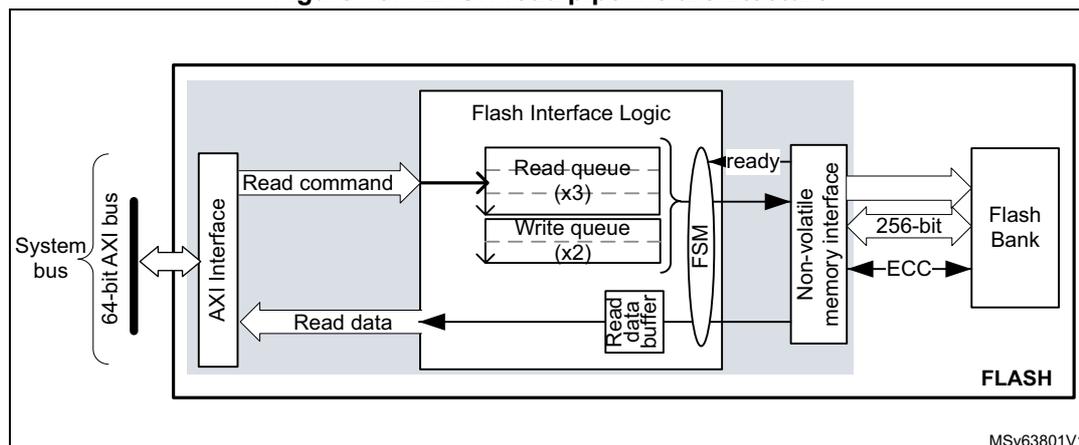

The embedded Flash microarchitecture is shown in Figure 6 .

Figure 6. Detailed FLASH architecture

Behind the system interfaces, the embedded Flash memory implements various command queues and buffers to perform Flash read, write and erase operations with maximum efficiency.

Thanks to the addition of a read and write data buffer, the AXI slave port handles the following access types:

- • Multiple length: 64 bits, 32 bits, 16 bits and 8 bits

- • Single or burst accesses

- • Write wrap burst must not cross 32-byte aligned address boundaries to target exactly one Flash word

The AHB configuration slave port supports 8-bit, 16-bit and 32-bit word accesses.

The embedded Flash memory is built in such a way that only one read or write operation can be executed at a time.

4.3.4 Flash memory architecture and usage

Flash memory architecture

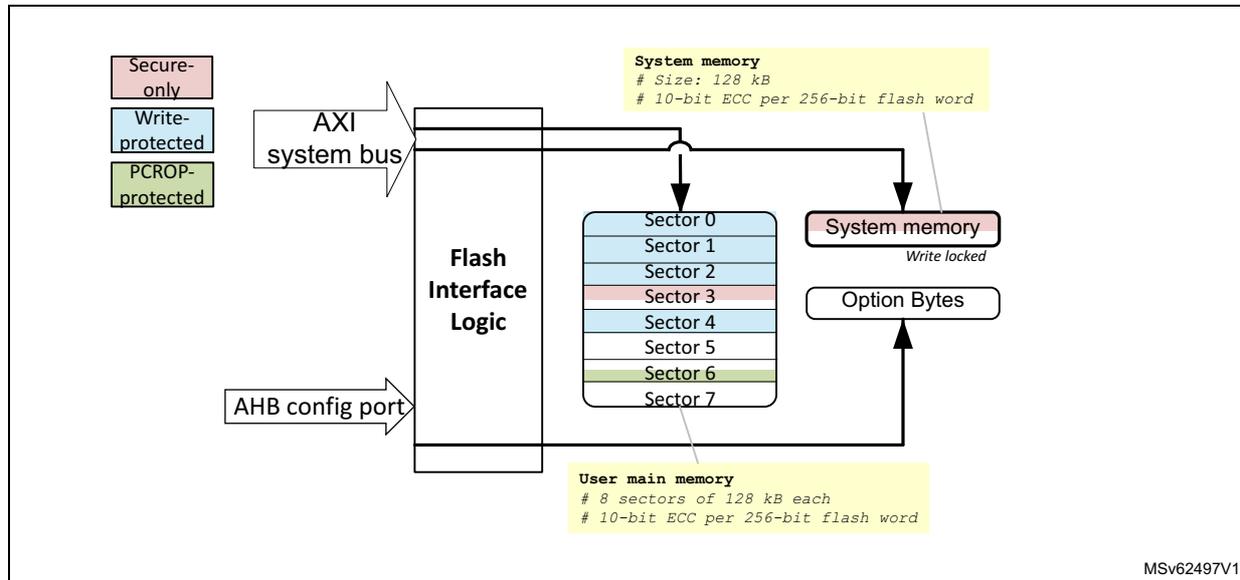

Figure 7 shows the non-volatile memory organization supported by the embedded Flash memory.

Figure 7. Embedded Flash memory organization

The diagram illustrates the internal architecture of the embedded Flash memory. On the left, a vertical bar represents the Flash Interface Logic . It is connected to an AXI system bus at the top and an AHB config port at the bottom. To the right of the interface logic, the memory is organized into three main regions:

- System memory : A yellow box at the top right, labeled "# Size: 128 kB" and "# 10-bit ECC per 256-bit flash word". It points to a pink box labeled "System memory" with a sub-label "Write locked".

- User main memory : A yellow box at the bottom right, labeled "# 8 sectors of 128 kB each" and "# 10-bit ECC per 256-bit flash word". It points to a stack of eight blue boxes labeled "Sector 0" through "Sector 7".

- Option Bytes : A white box in the middle right, which points to a pink box labeled "Option Bytes".

On the far left, three colored boxes indicate protection levels for the sectors: "Secure-only" (pink), "Write-protected" (blue), and "PCROP-protected" (green). The sectors are color-coded: Sector 0 (blue), Sector 1 (blue), Sector 2 (blue), Sector 3 (pink), Sector 4 (blue), Sector 5 (blue), Sector 6 (green), and Sector 7 (blue). The identifier "MSv62497V1" is located in the bottom right corner of the diagram.

The embedded Flash non-volatile memory is composed of:

- • A memory block of up to 1 Mbyte, with Flash-word rows of 256 bits + 10 bits of ECC per word

- • A system memory block of 128 Kbytes

- • A special region dedicated to option bytes storage

The embedded Flash memory interface logic supports the following architecture partitioning:

- • A user Flash memory mapped to the 1-Mbyte memory block. It is divided into eight sectors of 128 Kbytes. The user Flash memory is ECC protected.

- • A system Flash memory mapped to the 128-Kbyte system memory block. The system Flash memory is ECC protected

- • A set of non-volatile option bytes loaded at reset by the embedded Flash memory and accessible by the application software only through the AHB configuration register interface.

The overall Flash memory architecture is summarized in Table 15 .

Table 14. Flash memory organization (STM32H730 devices)

| Flash memory area | Address range | Size (bytes) | Region name | Access interface | SNB (1) |

|---|---|---|---|---|---|

| User main memory | 0x0800 0000- 0x0801 FFFF | 128 K | Sector 0 | AXI ports | 0x0 |

| System memory | 0x1FF0 0000- 0x1FF1 FFFF | 128 K | System Flash memory (read-only) | N/A (2) | |

| Option bytes | N/A | - | User option bytes | Registers only | N/A |

- 1. SNB contains the target sector number for an erase operation. See Section 4.3.10 for details.

- 2. Cannot be erased by software.

Table 15. Flash memory organization (STM32H723/733 and STM32H725/735 devices)

| Flash memory area | Address range | Size (bytes) | Region name (1) | Access interface | SNB (2) |

|---|---|---|---|---|---|

| User main memory | 0x0800 0000- 0x0801 FFFF | 128 K | Sector 0 | AXI ports | 0x0 |

| 0x0802 0000- 0x0803 FFFF | 128 K | Sector 1 | 0x1 | ||

| ... | ... | ... | ... | ||

| 0x080E 0000- 0x080F FFFF | 128 K | Sector 7 | 0x7 | ||

| System memory | 0x1FF0 0000- 0x1FF1 FFFF | 128 K | System Flash memory (read-only) | N/A (3) | |

| Option bytes | N/A | - | User option bytes | Registers only | N/A |

- 1. For devices with 512 Kbytes of Flash memory, only sectors 0 to 3 are available.

- 2. SNB contains the target sector number for an erase operation. See Section 4.3.10 for details.

- 3. Cannot be erased by software.

Partition usage

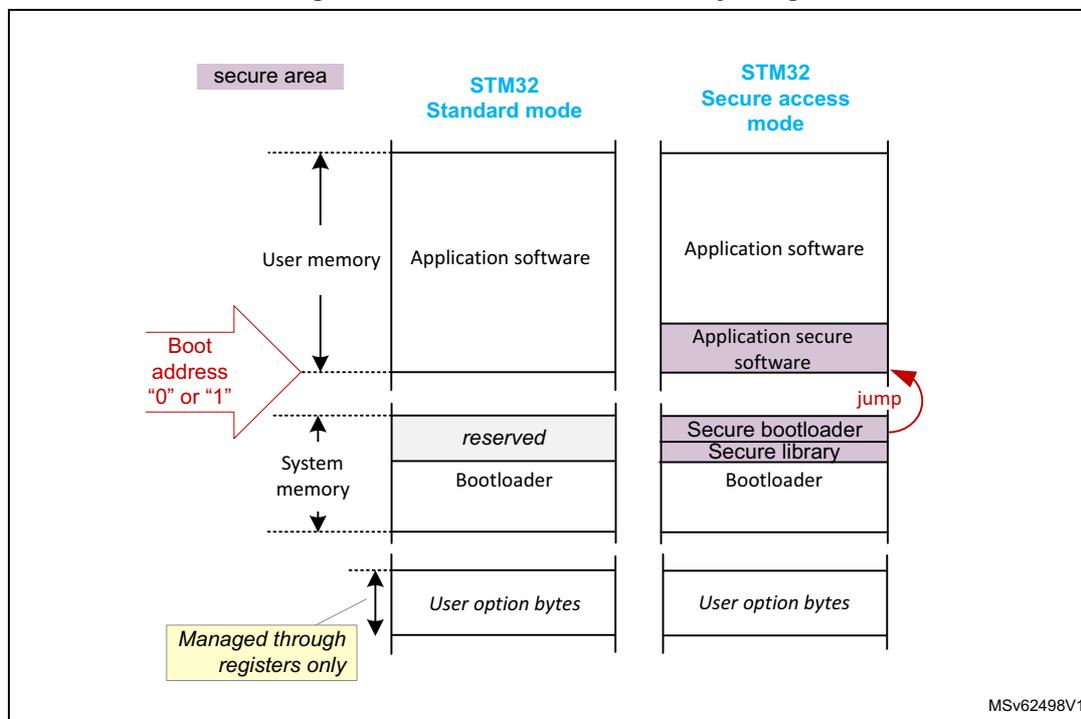

Figure 8 shows how the embedded Flash memory is used both by STMicroelectronics and the application software.

Figure 8. Embedded Flash memory usage

The diagram illustrates the memory layout for two STM32 modes: Standard mode and Secure access mode. A vertical axis on the left indicates memory addresses, with a 'secure area' at the top. The memory is divided into several regions:

- STM32 Standard mode:

- User memory: Contains 'Application software'.

- System memory: Contains 'reserved' space and 'Bootloader'.

- User option bytes: Located at the bottom, managed through registers only.

- STM32 Secure access mode:

- User memory: Contains 'Application software' and 'Application secure software'.

- System memory: Contains 'Secure bootloader', 'Secure library', and 'Bootloader'.

- User option bytes: Located at the bottom, managed through registers only.

A red arrow labeled 'Boot address "0" or "1"' points to the boundary between User memory and System memory. Another red arrow labeled 'jump' points from the 'Secure bootloader' to the 'Application secure software'.

User and system memories are used differently according to whether the microcontroller is configured by the application software in Standard mode or in Secure access mode. This selection is done through the SECURITY option bit (see Section 4.4.6 ):

- • In Standard mode, the user memory contains the application code and data, while the system memory is loaded with the STM32 bootloader. When a reset occurs, the core jumps to the boot address configured through the BOOT pin and the BOOT_CM_ADD0/1 option bytes.

- • In Secure access mode, dedicated libraries can be used for secure boot. They are located in user Flash and system Flash memory:

- – ST libraries in system Flash memory assist the application software boot with special features such as secure boot and secure firmware install (SFI).

- – Application secure libraries in user Flash memory are used for secure firmware update (SFU).

In Secure access mode, the microcontroller always boots into the secure bootloader code (unique entry point). Then, if no secure services are required, this code securely jumps to the requested boot address configured through the BOOT pin and the option bytes, as shown in Figure 8 (see Section 5: Secure memory management (SMM) for details).

Note: For more information on option byte setup for boot, refer to Section 4.4.7 .

Additional partition usage is the following:

- • The option bytes are used by STMicroelectronics and by the application software as non-volatile product options (e.g. boot address, protection configuration and reset behaviors).

Note: For further information on STM32 bootloader flashing by STMicroelectronics, refer to application note AN2606 “STM32 microcontroller system memory boot mode” available from http://www.st.com .

4.3.5 FLASH system performance enhancements

The embedded Flash memory uses read and write command queues in order to enhance Flash operations.

4.3.6 FLASH data protection schemes

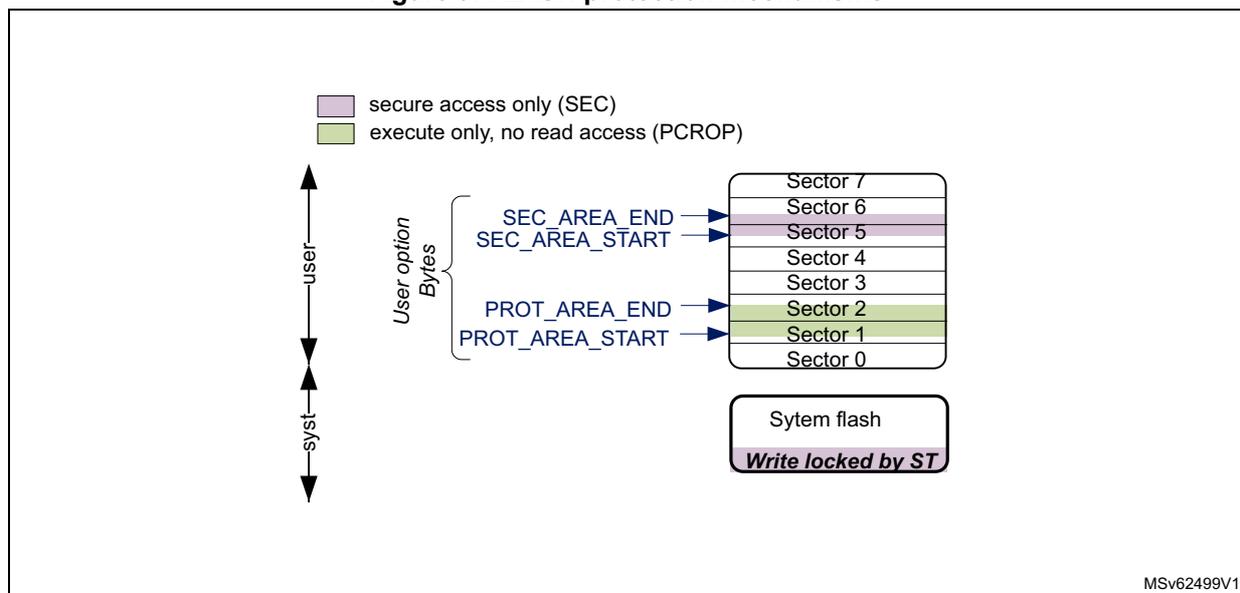

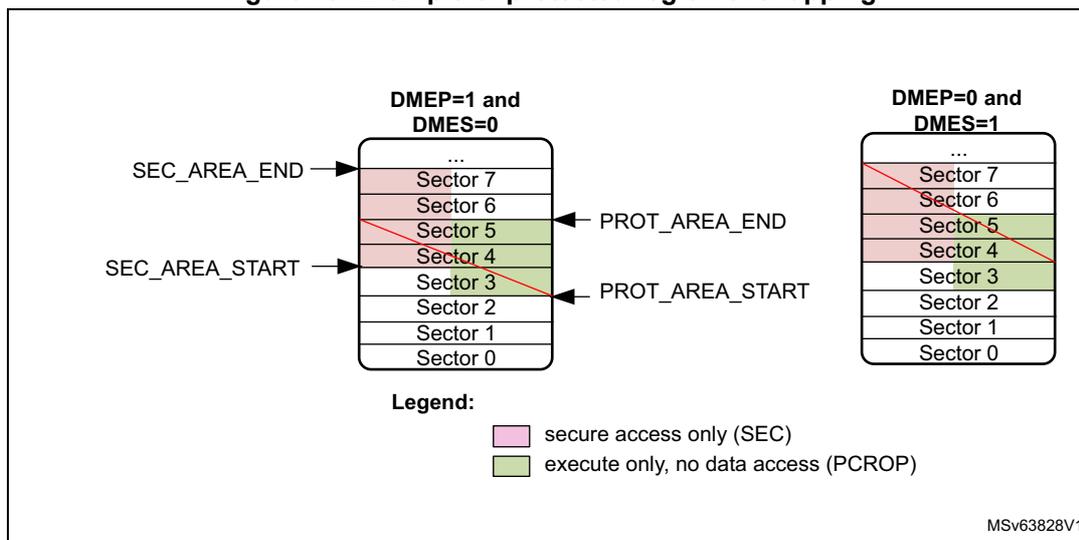

Figure 9 gives an overview of the protection mechanisms supported by the embedded Flash memory. A PCROP and a secure-only area can be defined in the Flash memory bank. The properties of these protected areas are detailed in Section 4.5 .

Figure 9. FLASH protection mechanisms

The diagram illustrates the memory layout and protection mechanisms. At the bottom, a box labeled 'System flash' is marked 'Write locked by ST'. Above it, memory is divided into 8 sectors (Sector 0 to Sector 7). Sector 0 is at the bottom, and Sector 7 is at the top. Two protection areas are defined by start and end addresses:

- SEC AREA

: Defined by

SEC_AREA_STARTandSEC_AREA_END. It covers Sector 5 (shaded purple, indicating 'secure access only (SEC)'). - PROT AREA

: Defined by

PROT_AREA_STARTandPROT_AREA_END. It covers Sectors 1 and 2 (shaded green, indicating 'execute only, no read access (PCROP)').

4.3.7 Overview of FLASH operations

Read operations

The embedded Flash memory can perform read operations on the whole non-volatile memory using various granularities: 64 bits, 32 bits, 16 bits or one byte. User and system Flash memories are read through the AXI interface, while the option bytes are read through the register interface.

To increase efficiency, the embedded Flash memory implements the buffering of consecutive read requests.

For more details on read operations, refer to Section 4.3.8: FLASH read operations .

Program/erase operations

The embedded Flash memory supports the following program and erase operations:

- • Single Flash word write (256-bit granularity), with the possibility for the application to force-write a user Flash word with less than 256 bits

- • Single sector erase

- • Bank erase

- • Option byte update

Note: Program and erase operations are subject to the various protection that could be set on the embedded Flash memory, such as write protection and global readout protection (see next sections for details).

To increase efficiency, the embedded Flash memory implements the buffering of consecutive write accesses.

For more details refer to Section 4.3.9: FLASH program operations and Section 4.3.10: FLASH erase operations .

Protection mechanisms

The embedded Flash memory supports different protection mechanisms:

- • Global readout protection (RDP)

- • Proprietary code readout protection (PCROP)

- • Write protection

- • Secure access only protection

For more details refer to Section 4.5: FLASH protection mechanisms .

Option byte loading

Under specific conditions, the embedded Flash memory reliably loads the non-volatile option bytes stored in non-volatile memory, thus enforcing boot and security options to the whole system when the embedded Flash memory becomes functional again. For more details refer to Section 4.4: FLASH option bytes .

4.3.8 FLASH read operations

Read operation overview

The embedded Flash memory supports the execution of one read command while two are waiting in the read command queue. Multiple read access types are also supported as defined in Section 4.3.3: FLASH architecture and integration in the system .

The read commands are associated with a 256-bit read data buffer.

Note: The embedded Flash memory can perform single error correction and double error detection while read operations are being executed (see Section 4.3.11: Flash memory error protections ).

The AXI interface read channel operates as follows:

- • When the read command queue is full, any new AXI read request stalls the bus read channel interface and consequently the master that issued that request.

- • If several consecutive read accesses request data that belong to the same Flash data word (256 bits), the data are read directly from the current data read buffer, without

triggering additional Flash read operations. This mechanism occurs each time a read access is granted. When a read access is rejected for security reasons (e.g. PCROP protected word), the corresponding read error response is issued by the embedded Flash memory and no read operation to Flash memory is triggered.

The Read pipeline architecture is summarized in Figure 10 .

For more information on bus interfaces, refer to Section 4.3.3: FLASH architecture and integration in the system .

Figure 10. FLASH read pipeline architecture

The diagram illustrates the internal architecture of the FLASH read pipeline. On the left, a 'System bus' (labeled '64-bit AXI bus') connects to an 'AXI Interface'. The 'AXI Interface' sends a 'Read command' to the 'Flash Interface Logic' and receives 'Read data' from a 'Read data buffer'. The 'Flash Interface Logic' contains a 'Read queue (x3)' and a 'Write queue (x2)'. A 'FSM' (Finite State Machine) is connected to the queues and the 'Non-volatile memory interface'. The 'Non-volatile memory interface' sends a 'ready' signal to the FSM and receives data from a 'Flash Bank' via a '256-bit' bus. The 'Flash Bank' also provides 'ECC' (Error Correction Code) data. The entire internal structure is labeled 'FLASH' at the bottom right. The identifier 'MSv63801V1' is present in the bottom right corner of the diagram.

Single read sequence

The recommended simple read sequence is the following:

- 1. Freely perform read accesses to any AXI-mapped area.

- 2. The embedded Flash memory effectively executes the read operation from the read command queue buffer as soon as the non-volatile memory is ready and the previously requested operations have been served.

Adjusting read timing constraints

The embedded Flash memory clock must be enabled and running before reading data from non-volatile memory.

To correctly read data from Flash memory, the number of wait states (LATENCY) must be correctly programmed in the Flash access control register (FLASH_ACR) according to the embedded Flash memory AXI interface clock frequency (sys_ck) and the internal voltage range of the device ( \( V_{core} \) ).

Table 16 shows the correspondence between the number of wait states (LATENCY), the programming delay parameter (WRHIGHFREQ), the embedded Flash memory clock frequency and its supply voltage ranges.

Table 16. FLASH recommended number of wait states and programming delay

| Number of wait states (LATENCY) | Programming delay (WRHIGHFREQ) | AXI Interface clock frequency vs V CORE range | |||

|---|---|---|---|---|---|

| VOS3 range 0.95 V - 1.05 V | VOS2 range 1.05 V - 1.15 V | VOS1 range 1.15 V - 1.26 V | VOS0 range 1.26 V - 1.40 V | ||

| 0 WS (1 FLASH clock cycle) | 00 | [0;35 MHz] | [0 MHz;50 MHz] | [0 MHz;67 MHz] | [0 MHz;70 MHz] |

| 1 WS (2 FLASH clock cycles) | 01 | ]35 MHz;70 MHz] | ]50 MHz;100 MHz] | ]67 MHz;133 MHz] | ]70 MHz;140 MHz] |

| 2 WS (3 FLASH clock cycles) | 10 | ]70 MHz;85 MHz] | ]100 MHz;150 MHz] | ]133 MHz;200 MHz] | ]140 MHz;210 MHz] |

| 3 WS (4 FLASH clock cycles) | 11 | - | - | - | ]210 MHz;275 MHz] |

Adjusting system frequency

After power-on, a default 7 wait-state latency is specified in FLASH_ACR register, in order to accommodate AXI interface clock frequencies with a safety margin (see Table 16 ).

When changing the AXI bus frequency, the application software must follow the below sequence in order to tune the number of wait states required to access the non-volatile memory.

To increase the embedded Flash memory clock source frequency:

- 1. If necessary, program the LATENCY and WRHIGHFREQ bits to the right value in the FLASH_ACR register, as described in Table 16 .

- 2. Check that the new number of wait states is taken into account by reading back the FLASH_ACR register.

- 3. Modify the embedded Flash memory clock source and/or the AXI bus clock prescaler in the RCC_CFGR register of the reset and clock controller (RCC).

- 4. Check that the new embedded Flash memory clock source and/or the new AXI bus clock prescaler value are taken in account by reading back the embedded Flash memory clock source status and/or the AXI bus prescaler value in the RCC_CFGR register of the reset and clock controller (RCC).

To decrease the embedded Flash memory clock source frequency:

- 1. Modify the embedded Flash memory clock source and/or the AXI bus clock prescaler in the RCC_CFGR register of reset and clock controller (RCC).

- 2. Check that the embedded Flash memory new clock source and/or the new AXI bus clock prescaler value are taken into account by reading back the embedded Flash

- memory clock source status and/or the AXI interface prescaler value in the RCC_CFGR register of reset and clock controller (RCC).

- 3. If necessary, program the LATENCY and WRHIGHFREQ bits to the right value in FLASH_ACR register, as described in Table 16 .

- 4. Check that the new number of wait states has been taken into account by reading back the FLASH_ACR register.

Error code correction (ECC)

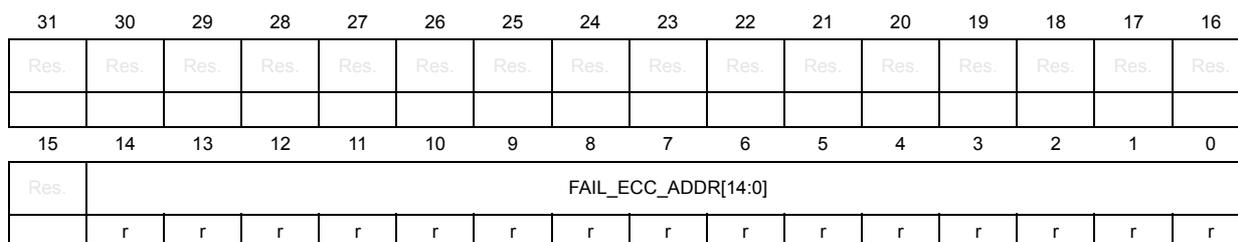

The embedded Flash memory embeds an error correction mechanism. Single error correction and double error detection are performed for each read operation. For more details, refer to Section 4.3.11: Flash memory error protections .

Read errors

When the ECC mechanism is not able to correct the read operation, the embedded Flash memory reports read errors as described in Section 4.7.7: Error correction code error (SNECCERR/DBECCERR) .

Read interrupts

See Section 4.8: FLASH interrupts for details.

4.3.9 FLASH program operations

Program operation overview

The virgin state of each non-volatile memory bitcell is 1. The embedded Flash memory supports programming operations that can change (reset) any memory bitcell to 0. However these operations do not support the return of a bit to its virgin state. In this case an erase operation of the entire sector is required.

A program operation consists in issuing write commands. The embedded Flash memory supports the execution of one write command while one command is waiting in the write command queue. Since a 10-bit ECC code is associated to each 256-bit data Flash word, only write operations by 256 bits are executed in the non-volatile memory.

Note: The application can decide to write as little as 8 bits to a Flash word. In this case, a force-write mechanism to the 256 bits + ECC is used (see FW bit of FLASH_CR register). System Flash memory cannot be written by the application software.

It is not recommended to overwrite a Flash word that is not virgin. The result may lead to an inconsistent ECC code that will be systematically reported by the embedded Flash memory, as described in Section 4.7.7: Error correction code error (SNECCERR/DBECCERR) .

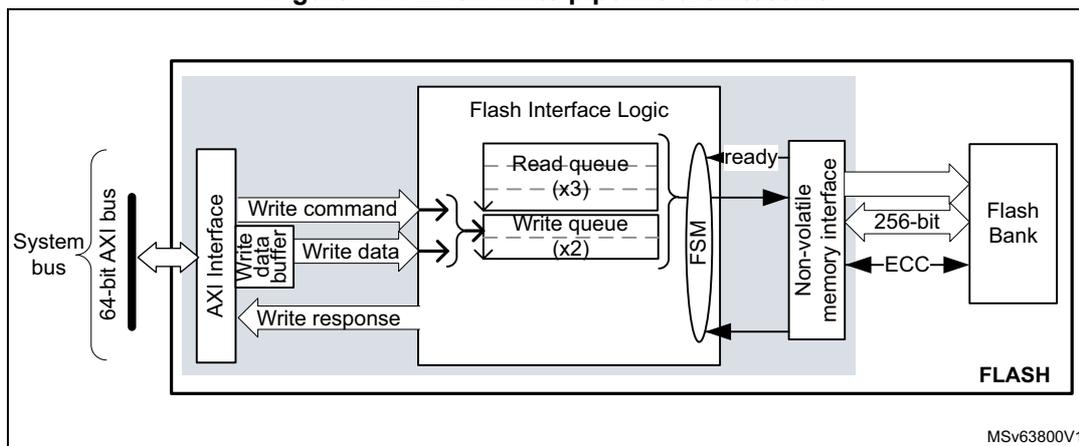

The AXI interface write channel operates as follows:

- • A 256-bit write data buffer is associated with the AXI interface. It supports multiple write access types (64 bits, 32 bits, 16 bits and 8 bits).

- • When the write queue is full, any new AXI write request stalls the bus write channel interface and consequently the master that issued that request.

The write pipeline architecture is described in Figure 11 .

For more information on bus interfaces, refer to Section 4.3.3: FLASH architecture and integration in the system .

Figure 11. FLASH write pipeline architecture

The diagram illustrates the FLASH write pipeline architecture. On the left, a 'System bus' (labeled '64-bit AXI bus') connects to an 'AXI Interface'. The AXI Interface sends 'Write command' and 'Write data' (via a 'Write data buffer') to 'Flash Interface Logic'. The Flash Interface Logic contains a 'Read queue (x3)' and a 'Write queue (x2)'. A 'FSM' (Finite State Machine) within the logic sends a 'ready' signal to the 'Non-volatile memory interface'. The AXI Interface also receives a 'Write response' from the Flash Interface Logic. The Non-volatile memory interface sends '256-bit' data and 'ECC' (Error Correction Code) to the 'Flash Bank'. The entire FLASH memory system is labeled 'FLASH' at the bottom right. A reference code 'MSV63800V1' is present in the bottom right corner of the diagram.

Managing write protections

Before programming a user sector, the application software must check the protection of the targeted Flash memory area.

The embedded Flash memory checks the protection properties of the write transaction target at the output of the write queue buffer, just before the effective write operation to the non-volatile memory:

- • If a write protection violation is detected, the write operation is canceled and write protection error (WRPERR) is raised in FLASH_SR register.

- • If the write operation is valid, the 10-bit ECC code is concatenated to the 256 bits of data and the write to non-volatile memory is effectively executed.

Note: No write protection check is performed when the embedded Flash memory accepts AXI write requests.

The write protection flag does not need to be cleared before performing a new programming operation.

Monitoring ongoing write operations

The application software can use three status flags located in FLASH_SR in order to monitor ongoing write operations.

- • BSY: this bit indicates that an effective write, erase or option byte change operation is ongoing to the non-volatile memory.

- • QW: this bit indicates that a write, erase or option byte change operation is pending in the write queue or command queue buffer. It remains high until the write operation is complete. It supersedes the BSY status bit.

- • WBNE: this bit indicates that the embedded Flash memory is waiting for new data to complete the 256-bit write buffer. In this state the write buffer is not empty. It is reset as soon as the application software fills the write buffer, force-writes the operation using FW bit in FLASH_CR, or disables all write operations.

Enabling write operations

Before programming the user flash, the application software must make sure that PG bit is set to 1 in FLASH_CR. If it is not the case, an unlock sequence must be used (see Section 4.5.1: FLASH configuration protection ) and the PG bit must be set.

When the option bytes need to be modified or a mass erase needs to be started, the application software must make sure that FLASH_OPTCR is unlocked. If it is not the case, an unlock sequence must be used (see Section 4.5.1: FLASH configuration protection ).

Note: The application software must not unlock a register that is already unlocked, otherwise this register will remain locked until next system reset.

If needed, the application software can update the programming delay and programming parallelism as described at the end of this section.

Single write sequence

The recommended single write sequence is the following:

- 1. Unlock the FLASH_CR register, as described in Section 4.5.1: FLASH configuration protection (only if register is not already unlocked).

- 2. Enable write operations by setting the PG bit in the FLASH_CR register.

- 3. Check the protection of the targeted memory area.

- 4. Write one Flash-word corresponding to 32-byte data starting at a 32-byte aligned address.

- 5. Check that QW has been raised and wait until it is reset to 0.

If step 4 is executed incrementally (e.g. byte per byte), the write buffer can become partially filled. In this case the application software can decide to force-write what is stored in the write buffer by using FW bit in FLASH_CR register. In this particular case, the unwritten bits are automatically set to 1. If no bit in the write buffer is set to 0, the FW bit has no effect.

Note: Using a force-write operation prevents the application from updating later the missing bits with a value different from 1, which is likely to lead to a permanent ECC error.

Any write access requested while the PG bit is set to 0 is rejected. In this case, no error is generated on the bus, but the PGSERR flag is raised.

Clearing the programming sequence error (PGSERR) and inconsistency error (INCERR) is mandatory before attempting a write operation (see Section 4.7: FLASH error management for details).

Adjusting programming timing constraints

Program operation timing constraints depend of the embedded Flash memory clock frequency, which directly impacts the performance. If timing constraints are too tight, the non-volatile memory will not operate correctly, if they are too lax, the programming speed will not be optimal.

The user must therefore trim the optimal programming delay through the WRHIGHFREQ parameter in the FLASH_ACR register. Refer to Table 16 in Section 4.3.8: FLASH read operations for the recommended programming delay depending on the embedded Flash memory clock frequency.

The application software must check that no program/erase operation is ongoing before modifying WRHIGHFREQ parameter.

Adjusting programming parallelism

The parallelism is the maximum number of bits that can be written to 0 in one shot during a write operation. The programming parallelism is also used during sector and bank erase.

There is no hardware limitation on programming parallelism. The user can select different parallelisms depending on the application requirements: the lower the parallelism, the lower the peak consumption during a programming operation, but the longer the execution time.

The parallelism is configured through the PSIZE1/2 bits in FLASH_CR1/2 register.

Table 17. FLASH parallelism parameter

| PSIZE | Parallelism |

|---|---|

| 00 | 8 bits (one byte) |

| 01 | 16 bits |

| 10 | 32 bits |

| 11 | 64 bits |

Programming errors

When a program operation fails, an error can be reported as described in Section 4.7: FLASH error management .

Programming interrupts

See Section 4.8: FLASH interrupts for details.

4.3.10 FLASH erase operations

Erase operation overview

The embedded Flash memory can perform erase operations on 128-Kbyte user sectors.

Note: System Flash cannot be erased by the application software.

The erase operation forces all non-volatile bit cells to high state, which corresponds to the virgin state. It clears existing data and corresponding ECC, allowing a new write operation to be performed. If the application software reads back a word that has been erased, all the bits will be read at 1, without ECC error.

Erase operations are similar to read or program operations except that the commands are queued in a special buffer (a two-command deep erase queue).

Erase commands are issued through the AHB configuration interface. If the embedded Flash memory receives simultaneously a write and an erase request, both operations are accepted but the write operation is executed first.

Erase and security

A user sector can be erased only if it does not contain PCROP, secure-only or write-protected data (see Section 4.5: FLASH protection mechanisms for details). In other words, if the application software attempts to erase a user sector with at least one Flash word that is protected, the sector erase operation is aborted and the WRPERR flag is raised in the FLASH_SR register, as described in Section 4.7.2: Write protection error (WRPERR) .

The embedded Flash memory allows the application software to perform an erase followed by an automatic protection removal (PCROP, secure-only area and write protection), as described hereafter.

Enabling erase operations

Before erasing a sector, the application software must make sure that FLASH_CR is unlocked. If it is not the case, an unlock sequence must be used (see Section 4.5.1: FLASH configuration protection ).

Note: The application software must not unlock a register that is already unlocked, otherwise this register will remain locked until next system reset.

Similar constraints apply to bank erase requests.

Flash sector erase sequence

To erase a 128-Kbyte user sector, proceed as follows:

- 1. Check and clear (optional) all the error flags due to previous programming/erase operation. Refer to Section 4.7: FLASH error management for details.

- 2. Unlock the FLASH_CR register, as described in Section 4.5.1: FLASH configuration protection (only if register is not already unlocked).

- 3. Set the SER bit and SNB bitfield in the corresponding FLASH_CR register. SER indicates a sector erase operation, while SNB contains the target sector number.

- 4. Set the START bit in the FLASH_CR register.

- 5. Wait for the QW bit to be cleared in the corresponding FLASH_SR register.

Note: If a bank erase is requested simultaneously to the sector erase (BER bit set), the bank erase operation supersedes the sector erase operation.

Standard Flash bank erase sequence

To erase all bank sectors except for those containing secure-only and protected data, proceed as follows:

- 1. Check and clear (optional) all the error flags due to previous program/erase operation. Refer to Section 4.7: FLASH error management for details.

- 2. Unlock the FLASH_CR register, as described in Section 4.5.1: FLASH configuration protection (only if the register is not already unlocked).

- 3. Set the BER bit in the FLASH_CR register.

- 4. Set the START bit in the FLASH_CR register to start the bank erase operation. Then wait until the QW bit is cleared in the corresponding FLASH_SR register.

Note: BER and START bits can be set together, so above steps 3 and 4 can be merged.

If a sector erase is requested simultaneously to the bank erase (SER bit set), the bank erase operation supersedes the sector erase operation.

Flash bank erase with automatic protection-removal sequence

To erase all bank sectors including those containing secure-only and protected data without performing an RDP regression (see Section 4.5.3 ), proceed as follows:

- 1. Check and clear (optional) all the error flags due to previous programming/erase operation. Refer to Section 4.7: FLASH error management for details.

- 2. Unlock FLASH_OPTCR register, as described in Section 4.5.1: FLASH configuration protection (only if register is not already unlocked).

- 3. If a PCROP-protected area exists set DMEP bit in FLASH_PRAR_PRG register. In addition, program the PCROP area end and start addresses so that the difference is negative, i.e. \( PROT\_AREA\_END < PROT\_AREA\_START \) .

- 4. If a secure-only area exists set DMES bit in FLASH_SCAR_PRG register. In addition, program the secure-only area end and start addresses so that the difference is negative, i.e. \( SEC\_AREA\_END < SEC\_AREA\_START \) .

- 5. Set all WRPSn1/2 bits in FLASH_WPSN_PRG to 1 to disable all sector write protection.

- 6. Unlock FLASH_CR register, only if register is not already unlocked.

- 7. Set the BER bit in the FLASH_CR register.

- 8. Set the START bit in the FLASH_CR register to start the bank erase with protection removal operation. Then wait until the QW bit is cleared in the corresponding FLASH_SR register. At that point a bank erase operation has erased the whole bank including the sectors containing PCROP-protected and/or secure-only data, and an option byte change has been automatically performed so that all the protections are disabled.

Note: BER and START bits can be set together, so above steps 8 and 9 can be merged.

Be aware of the following warnings regarding to above sequence:

- • No other option bytes than the one indicated above must be changed.

- • When the event above occurs, a simple bank erase is done, no option byte change is performed and no option change error is set.

4.3.11 Flash memory error protections

Error correction codes (ECC)

The embedded Flash memory supports an error correction code (ECC) mechanism. It is based on the SECDED algorithm in order to correct single errors and detects double errors.

This mechanism uses 10 ECC bits per 256-bit Flash word, and applies to user and system Flash memory.

More specifically, during each read operation from a 256-bit Flash word, the embedded Flash memory also retrieves the 10-bit ECC information, computes the ECC of the Flash word, and compares the result with the reference value. If they do not match, the corresponding ECC error is raised as described in Section 4.7.7: Error correction code error (SNECCERR/DBECCERR) .

During each program operation, a 10- bit ECC code is associated to each 256-bit data Flash word, and the resulting 266-bit Flash word information is written in non-volatile memory.

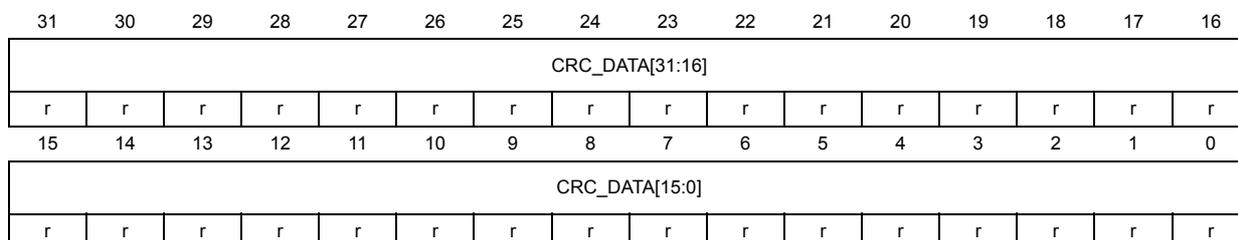

Cyclic redundancy codes (CRC)

The embedded Flash memory implements a cyclic redundancy check (CRC) hardware module. This module checks the integrity of a given user Flash memory area content (see Figure 6: Detailed FLASH architecture ).

The area processed by the CRC module can be defined either by sectors or by start/end addresses. It can also be defined as the whole bank (user Flash memory area only).

When enabled, the CRC hardware module performs multiple reads by chunks of 4, 16, 64 or 256 consecutive Flash-word (i.e. chunks of 128, 512, 2048 or 8192 bytes). These consecutive read operations are pushed by the CRC module into the required read command queue together with other AXI read requests, thus avoiding to deny AXI read commands.

CRC computation uses CRC-32 (Ethernet) polynomial 0x4C11DB7:

The CRC operation is concurrent with option byte change as the same hardware is used for both operations. To avoid the CRC computation from being corrupted, the application shall complete the option byte change (by reading the result of the change) before running a CRC operation, and vice-versa.

The sequence recommended to configure a CRC operation is the following:

- 1. Unlock FLASH_CR register, if not already unlocked.

- 2. Enable the CRC feature by setting the CRC_EN bit in FLASH_CR.

- 3. Program the desired data size in the CRC_BURST field of FLASH_CRCCR.

- 4. Define the user Flash area on which the CRC has to be computed. Two solutions are possible:

- – Define the area start and end addresses by programming FLASH_CRCSTARTADDR and FLASH_CRCENDADDR, respectively,

- – or select the targeted sectors by setting the CRC_BY_SECT bit in FLASH_CRCCR and by programming consecutively the target sector numbers in the CRC_SECT field of the FLASH_CRCCR register. Set ADD_SECT bit after each CRC_SECT programming.

- 5. Start the CRC operation by setting the START_CRC bit.

- 6. Wait until the CRC_BUSY flag is reset in FLASH_SR register.

- 7. Retrieve the CRC result in the FLASH_CRCDATAR register.

The CRC can be computed for the whole bank by setting the ALL_BANK bit in the FLASH_CRCCR register.

Note: The application should avoid running a CRC on PCROP- or secure-only user Flash area since it may alter the expected CRC value. A special error flag defined in Section 4.7.10: CRC read error (CRCRDERR) can be used to detect such a case.

CRC computation does not raise standard read error flags such as RDSERR, RDPERR and DBECCERR. Only CRCRDERR is raised.

4.3.12 FLASH reset and clocks

Reset management

The embedded Flash memory can be reset by a D1 domain reset (d1_rst), driven by the reset and clock control (RCC). The main effects of this reset are the following:

- • All registers, except for option byte registers, are cleared, including read and write latencies.

- • Most control registers are automatically protected against write operations. To unprotect them, new unlock sequences must be used as described in Section 4.5.1: FLASH configuration protection .

The embedded Flash memory can be reset by a power-on reset (po_rst), driven by the reset and clock control (RCC). When the reset falls, all option byte registers are reset. When the reset rises up, the option bytes are loaded, potentially applying new features. During this loading sequence, the device remains under reset and the embedded Flash memory is not accessible.

The Reset signal can have a critical impact on the embedded Flash memory:

- • The contents of the Flash memory are not guaranteed if a device reset occurs during a Flash memory write or erase operation.

- • If a reset occurs while the option byte modification is ongoing, the old option byte values are kept. When it occurs, a new option byte modification sequence is required to program the new values.

Clock management

The embedded Flash memory uses the microcontroller system clock (sys_ck), here the AXI interface clock.

Depending on the device clock and internal supply voltage, specific read and write latency settings usually need to be set in the Flash access control register (FLASH_ACR), as explained in Section 4.3.8: FLASH read operations and Section 4.3.9: FLASH program operations .

4.4 FLASH option bytes

4.4.1 About option bytes

The embedded Flash memory includes a set of non-volatile option bytes. They are loaded at power-on reset and can be read and modified only through configuration registers.

These option bytes are configured by the end-user depending on the application requirements. Some option bytes might have been initialized by STMicroelectronics during manufacturing stage.

This section documents:

- • When option bytes are loaded

- • How application software can modify them

- • What is the detailed list of option bytes, together with their default factory values (i.e. before the first option byte change).

4.4.2 Option byte loading

There are multiple ways of loading the option bytes into embedded Flash memory:

1. Power-on wakeup

When the device is first powered, the embedded Flash memory automatically loads all the option bytes. During the option byte loading sequence, the device remains under reset and the embedded Flash memory cannot be accessed.

2. Wakeup from system Standby

When the D1 power domain, which contains the embedded Flash memory, is switched from DStandby mode to DRun mode, the embedded Flash memory behaves as during a power-on sequence.

3. Ad-hoc option byte reloading by the application

When the user application successfully modifies the option byte content through the embedded Flash memory registers, the non-volatile option bytes are programmed and the embedded Flash memory automatically reloads all option bytes to update the option registers.

Note: The option bytes read sequence is enhanced thanks to a specific error correction code. In case of security issue, the option bytes may be loaded with default values (see Section 4.4.3: Option byte modification ).

4.4.3 Option byte modification

Changing user option bytes

A user option byte change operation can be used to modify the configuration and the protection settings saved in the non-volatile option byte area.

The embedded Flash memory features two sets of option byte registers:

- • The first register set contains the current values of the option bytes. Their names have the _CUR extension. All “_CUR” registers are read-only. Their values are automatically loaded from the non-volatile memory after power-on reset, wakeup from system standby or after an option byte change operation.

- • The second register set allows the modification of the option bytes. Their names contain the _PRG extension. All “_PRG” registers can be accessed in read/write mode.

When the OPTLOCK bit in FLASH_OPTCR register is set, modifying the _PRG registers is not possible.

When OPTSTART bit is set to 1, the embedded Flash memory checks if at least one option byte needs to be programmed by comparing the current values (_CUR) with the new ones (_PRG). If this is the case and all the other conditions are met (see Changing security option bytes ), the embedded Flash memory launches the option byte modification in its non-volatile memory and updates the option byte registers with _CUR extension.

If one of the condition described in Changing security option bytes is not respected, the embedded Flash memory sets the OPTCHANGEERR flag to 1 in the FLASH_OPTSR_CUR register and aborts the option byte change operation. In this case, the _PRG registers are not overwritten by current option value. The user application can check what was wrong in their configuration.

Unlocking the option byte modification

After reset, the OPTLOCK bit is set to 1 and the FLASH_OPTCR is locked. As a result, the application software must unlock the option configuration register before attempting to change the option bytes. The FLASH_OPTCR unlock sequence is described in Section 4.5.1: FLASH configuration protection .

Option byte modification sequence

To modify user option bytes, follow the sequence below:

- 1. Unlock FLASH_OPTCR register as described in Section 4.5.1: FLASH configuration protection , unless the register is already unlocked.

- 2. Write the desired new option byte values in the corresponding option registers (FLASH_XXX_PRG).

- 3. Set the option byte start change OPTSTART bit to 1 in the FLASH_OPTCR register.

- 4. Wait until OPT_BUSY bit is cleared.

Note: If a reset or a power-down occurs while the option byte modification is ongoing, the original option byte value is kept. A new option byte modification sequence is required to program the new value.

Changing security option bytes

On top of OPTLOCK bit, there is a second level of protection for security-sensitive option byte fields. Specific rules must be followed to update them:

- • Readout protection (RDP)

A detailed description of RDP option bits is given in Section 4.5.3 . The following rules must be respected to modify these option bits:

- – When RDP is set to level 2, no changes are allowed. As a result, if the user application attempts to reduce the RDP level, an option byte change error is raised (OPTCHANGEERR bit in FLASH_OPTSR_CUR register), and all the programmed changes are ignored.

- – When the RDP is set to level 1, requiring a change to level 2 is always allowed. When requiring a regression to level 0, an option byte change error can occur if some of the recommendations provided in this chapter have not been followed.

- – When the RDP is set to level 0, switching to level 1 or level 2 is possible without any restriction.

- • Sector write protection (WRPSn)

These option bytes manage sector write protection in FLASH_WPSN_CUR1/2R registers. They can be changed without any restriction when the RDP protection level is different from level 2.

- • PCROP area size (PROT_AREA_START and PROT_AREA_END)

These option bytes configure the size of the PCROP areas in FLASH_PRAR_CUR registers. They can be increased without any restriction by the Arm ® Cortex ® -M7 core. To remove or reduce a PCROP area, an RDP level 1 to 0 regression (see Section 4.5.3 ) or a bank erase with protection removal (see Section 4.3.10 ) must be

requested at the same time. DMEP must be set to 1 in either FLASH_PRAR_CUR or FLASH_PRAR_PRG, otherwise an option byte change error is raised.

- • DMEP

When this option bit is set, the content of the corresponding PCROP area is erased during a RDP level 1 to 0 regression (see Section 4.5.3 ) or a bank erase with protection removal (see Section 4.3.10 ). It is preserved otherwise.

There are no restrictions in setting DMEP bit. Resetting DMEP bit from 1 to 0 can only be done when an RDP level 1 to 0 regression or a bank erase with protection removal is requested at the same time.

- • Secure access mode (SECURITY)

The SECURITY option bit activates the secure access mode described in Section 4.5.5 . This option bit can be freely set by the application software if such mode is activated on the device. If at least one PCROP or secure-only area is defined as not null, the only way to deactivate the security option bit (from 1 to 0) is to perform an RDP level 1 to 0 regression, when DMEP is set to 1 in either FLASH_PRAR_CUR or FLASH_PRAR_PRG registers, and DMES is set to 1 in either FLASH_SCAR_CUR or FLASH_SCAR_PRG.

If no valid secure-only area and no valid PCROP area are currently defined, the SECURITY option bit can be freely reset.

Note: It is recommended to have both SEC_AREA_START > SEC_AREA_END and PROT_AREA_START > PROT_AREA_END programmed when deactivating the SECURITY option bit during an RDP level 1 to 0 regression.

- • Secure-only area size (SEC_AREA_START and SEC_AREA_END)

These option bytes configure the size of the secure-only areas in FLASH_SCAR_CUR registers. They can be changed without any restriction by the user secure application or by the ST secure library running on the device. For user non-secure application, the secure-only area size can be removed by performing a bank erase with protection removal (see Section 4.3.10 ), or an RDP level 1 to 0 regression when DMES set to 1 in either FLASH_SCAR_CUR or FLASH_SCAR_PRG (otherwise an option byte change error is raised).

- • DMES

When this option bit is set, the content of the corresponding secure-only area is erased during an RDP level 1 to 0 regression or a bank erase with protection removal, it is preserved otherwise.

DMES bits can be set without any restriction. Resetting DMES bit from 1 to 0 can only be performed when an RDP level 1 to 0 regression or a bank erase with protection removal is requested at the same time.

- • Secure DTCM size (ST_RAM_SIZE)

These bits selects the size of the secure DTCM, an option that is available only when SECURITY option bit is set. It can be modified only when the CPU is running the ST secure library.

4.4.4 Option bytes overview

Table 18 lists all the user option bytes managed through the embedded Flash memory registers, as well as their default values before the first option byte change (default factory value).

Table 18. Option byte organization

| Register | Bitfield | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | |

| FLASH_OPTSR_x[31:16] | Res. | OPTCHANGER | IO_HSLV | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SECURITY | ST_RAM_SIZE | IWDG_FZ_SDBY | IWDG_FZ_STOP | Res. | |

| Default factory value | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| FLASH_OPTSR_x[15:0] | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RDP[7:0] | NRST_STDY_D1 | NRST_STOP_D1 | Res. | IWDG1_SW | BOR_LEV | Res. | Res. | |||||||||

| Default factory value | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| FLASH_OPTSR2_x[15:0] | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CPUFREQ_BOOST | TOM_AXI_SHARED | ||

| Default factory value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| FLASH_BOOT_x[31:16] | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| BOOT_CM_ADD1[15:0] | ||||||||||||||||

| Default factory value | 0x1FF0 | |||||||||||||||

| FLASH_BOOT_x[15:0] | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BOOT_CM_ADD0[15:0] | ||||||||||||||||

| Default factory value | 0x0800 | |||||||||||||||

| FLASH_PRAR_x[31:16] | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| DMEP | Res. | Res. | Res. | PROT_AREA_END | ||||||||||||

Table 18. Option byte organization (continued)

| Register | Bitfield | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Default factory value | 0x000 | |||||||||||||||

| FLASH_PRAR_x[15:0] | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | PROT_AREA_START | ||||||||||||

| Default factory value | 0x0FF | |||||||||||||||

| FLASH_SCAR_x[31:16] | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| DMES | Res. | Res. | Res. | SEC_AREA_END | ||||||||||||

| Default factory value | 0x000 | |||||||||||||||

| FLASH_SCAR_x[15:0] | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | SEC_AREA_START | ||||||||||||

| Default factory value | 0x0FF | |||||||||||||||

| FLASH_WPSN_x[31:16] | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |

| Default factory value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| FLASH_WPSN_x[15:0] | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | WRPSn[7:0] | ||||||||

| Default factory value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

4.4.5 Description of user and system option bytes

Below the list of the general-purpose option bytes that can be used by the application:

- Watchdog management

- IWDG_FZ_STOP: independent watchdog (IWDG1) counter active in Stop mode if 1 (stop counting or freeze if 0)

- IWDG_FZ_SDBY: independent watchdog (IWDG1) counter active in Standby mode if 1 (stop counting or freeze if 0)

- IWDG1_SW: hardware (0) or software (1) IWDG1 watchdog control selection

Note: If the hardware watchdog “control selection” feature is enabled (set to 0), the watchdog is automatically enabled at power-on, thus generating a reset unless the watchdog key register is written to or the down-counter is reloaded before the end-of-count is reached. Depending on the configuration of IWDG_STOP and IWDG_STBY options, the IWDG can continue counting (1) or not (0) when the device is in Stop or Standby mode, respectively.

When the IWDG is kept running during Stop or Standby mode, it can wake up the device from these modes.

- • Reset management

- – BOR: Brownout level option, indicating the supply level threshold that activates/releases the reset

- – NRST_STDBY_D1: generates a reset when D1 domain enters DStandby mode. It is active low.

- – NRST_STOP_D1: generates a reset when D1 domain enters DStop mode. It is active low.

Note: Whenever a Standby (respectively Stop) mode entry sequence is successfully executed, the device is reset instead of entering Standby (respectively Stop) mode if NRST_STDBY (respectively NRST_STOP) is cleared to 0.

- • Device options

- – IO_HSLV: I/O speed optimization at low-voltage if set to 1.

When STMicroelectronics delivers the device, the values programmed in the general-purpose option bytes are the following:

- • Watchdog management

- – IWDG1 active in Standby and Stop modes (option byte value = 0x1)

- – IWDG1 not automatically enabled at power-on (option byte value = 0x1)

- • Reset management:

- – BOR: brownout level option (reset level) equals brownout reset threshold 0 (option byte value = 0x0)

- – A reset is not generated when D1 domain enters DStandby or DStop low-power mode (option byte value = 0x1)

- • Device working in the full voltage range with I/O speed optimization at low-voltage disabled (IO_HSLV=0)

Refer to Section 4.9: FLASH registers for details.

4.4.6 Description of data protection option bytes

Below the list of the option bytes that can be used to enhance data protection:

- • RDP[7:0]: Readout protection level (see Section 4.5.3 on page 179 for details).

- • WRPSn: sector write- protection (see Section 4.5.2 on page 178 for details).

- • PROT_AREAx: Proprietary code readout protection (refer to

Section 4.5.4 on page 183

for details)

- – PROT_AREA_START (respectively PROT_AREA_END) contains the first (respectively last) 256-byte block of the PCROP zone

- – DMEP: when set to 1, the PCROP area is erased during a RDP protection level regression (change from level 1 to 0) or a bank erase with protection removal.

- • SEC_AREAx: secure access only zones definition (refer to

Section 4.5.5 on page 184

for details).

- – SEC_AREA_START (respectively SEC_AREA_END) contains the first (respectively last) 256-byte block of the secure access only zone

- – DMES: when set to 1 the secure access only zone is erased during a RDP protection level regression (change from level 1 to 0), or a bank erase with protection removal.

- • SECURITY: this non-volatile option can be used by the application to manage secure access mode, as described in Section 4.5.5 .

- • ST_RAM_SIZE: this non-volatile option defines the amount of DTCM RAM root secure services (RSS) can use during execution when the SECURITY bit is set. The DTCM RAM is always fully available for the application whatever the option byte configuration.

When STMicroelectronics delivers the device, the values programmed in the data protection option bytes are the following:

- • RDP level 0 (option byte value = 0xAA)

- • Flash bank erase operations do not impact secure-only and PCROP data areas when enabled by the application (DMES=DMEP=0)

- • PCROP and secure-only zone protections disabled (start addresses higher than end addresses)

- • Write protection disabled (all option byte bits set to 1)

- • Secure access mode disabled (SECURITY option byte value= 0)

- • RSS can use the full DTCM RAM for executing its services (ST_RAM_SIZE = 11)

Refer to Section 4.9: FLASH registers for details.

4.4.7 Description of boot address option bytes

Below the list of option bytes that can be used to configure the appropriate boot address for your application:

- • BOOT_CM_ADD0/1: MSB of the Arm ® Cortex ® -M7 boot address when BOOT pin is low (respectively high)

When STMicroelectronics delivers the device, the values programmed in the boot address option bytes are the following:

- • Arm ® Cortex ® -M7 boot address (MSB): 0x0800 (BOOT pin low for user Flash memory) and 0x1FF0 (BOOT pin high for System Flash memory)

Refer to Section 4.9: FLASH registers for details.

4.5 FLASH protection mechanisms

Since sensitive information can be stored in the Flash memory, it is important to protect it against unwanted operations such as reading confidential areas, illegal programming of protected area, or illegal Flash memory erasing.

The embedded Flash memory implements the following protection mechanisms that can be used by end-user applications to manage the security of embedded non-volatile storage:

- • Configuration protection

- • Global device Readout protection (RDP)

- • Write protection

- • Proprietary code readout protection (PCROP)

- • Secure access mode areas

This section provides a detailed description of all these security mechanisms.

4.5.1 FLASH configuration protection

The embedded Flash memory uses hardware mechanisms to protect the following assets against unwanted or spurious modifications (e.g. software bugs):

- • Option bytes change

- • Write operations

- • Erase commands

- • Interrupt masking

More specifically, write operations to embedded Flash memory control registers (FLASH_CR and FLASH_OPTCR) are not allowed after reset.

The following sequence must be used to unlock FLASH_CR register:

- 1. Program KEY1 to 0x45670123 in FLASH_KEYR key register.

- 2. Program KEY2 to 0xCDEF89AB in FLASH_KEYR key register.

- 3. LOCK bit is now cleared and FLASH_CR is unlocked.

The following sequence must be used to unlock FLASH_OPTCR register:

- 1. Program OPTKEY1 to 0x08192A3B in FLASH_OPTKEYR option key register.

- 2. Program OPTKEY2 to 0x4C5D6E7F in FLASH_OPTKEYR option key register.

- 3. OPTLOCK bit is now cleared and FLASH_OPTCR register is unlocked.

Any wrong sequence locks up the corresponding register/bit until the next system reset, and generates a bus error.

The FLASH_CR (respectively FLASH_OPTCR) register can be locked again by software by setting the LOCK bit in FLASH_CR register (respectively OPTLOCK bit in FLASH_OPTCR register).

In addition the FLASH_CR register remains locked and a bus error is generated when the following operations are executed:

- • programming a third key value

- • writing to a different register than FLASH_KEYR before FLASH_CR has been completely unlocked (KEY1 programmed but KEY2 not yet programmed)

- • writing less than 32 bits to KEY1 or KEY2.

Similarly the FLASH_OPTCR register remains locked and a bus error is generated when the following operations are executed:

- • programming a third key value

- • writing to a different register before FLASH_OPTCR has been completely unlocked (OPTKEY1 programmed but OPTKEY2 not yet programmed)

- • writing less than 32 bits to OPTKEY1 or OPTKEY2.

The embedded Flash memory configuration registers protection is summarized in Table 19 .

Table 19. Flash interface register protection summary

| Register Name | Unlocking register | Protected asset |

|---|---|---|

| FLASH_ACR | N/A | - |

| FLASH_KEYR | N/A | - |

| FLASH_OPTKEYR | N/A | - |

| FLASH_CR | FLASH_KEYR | Write operations Erase commands Interrupt generation masking sources |

| FLASH_SR | N/A | - |

| FLASH_CCR | N/A | - |

| FLASH_OPTCR | FLASH_OPTKEYR | Option bytes change Mass erase |

| FLASH_OPTSR_PRG FLASH_OPTSR2_PRG | FLASH_OPTCR | Option bytes change |

| FLASH_OPTCCR | N/A | - |

| FLASH_PRAR_PRG | FLASH_OPTCR | Option bytes (PCROP) |

| FLASH_SCAR_PRG | FLASH_OPTCR | Option bytes (security) |

| FLASH_WPSN_PRG | FLASH_OPTCR | Option bytes (write protection) |

| FLASH_BOOT_PRG | FLASH_OPTCR | Option bytes (boot) |

| FLASH_CRCR | N/A | - |

| FLASH_CRCSADDR | - | |

| FLASH_CRCEADDR | - | |

| FLASH_CRCDATAR | - | |

| FLASH_ECC_FAR | N/A | - |

4.5.2 Write protection

The purpose of embedded Flash memory write protection is to protect the embedded Flash memory against unwanted modifications of the non-volatile code and/or data.

Any 128-Kbyte Flash sector can be independently write-protected or unprotected by clearing/setting the corresponding WRPSn bit in the FLASH_WPSN_PRG register.

A write-protected sector can neither be erased nor programmed. As a result, a bank erase cannot be performed if one sector is write-protected, unless a bank erase with automatic

protection removal or an RDP level 1 to 0 regression is executed (see Section : Flash bank erase with automatic protection-removal sequence for details).

The embedded Flash memory write-protection user option bits can be modified without any restriction when the RDP level is set to level 0 or level 1. When it is set to level 2, the write protection bitfield can no more be changed in the option bytes.

Note: PCROP or secure-only areas are write and erase protected.

Write protection errors are documented in Section 4.7: FLASH error management .

4.5.3 Readout protection (RDP)

The embedded Flash memory readout protection is global as it does not apply only to the embedded Flash memory, but also to the other secured regions. This is done by using dedicated security signals.

In this section other secured regions are defined as:

- • Backup SRAM

- • RTC backup registers

- • Encrypted regions protected by on-the-fly decryption engine (OTFDEC)

The global readout protection level is set by writing the values given in Table 20 into the readout protection (RDP) option byte (see Section 4.4.3: Option byte modification ).

Table 20. RDP value vs readout protection level

| RDP option byte value | Global Readout Protection Level |

|---|---|

| 0xAA | Level 0 |

| 0xCC | Level 2 |

| Any other value | Level 1 (1) |

1. Default protection level when RDP option byte is erased.

Definitions of RDP global protection level

RDP Level 0 (no protection)

When the global read protection level 0 is set, all read/program/erase operations from/to the user Flash memory are allowed (if no others protections are set). This is true whatever the boot configuration (boot from user or system flash memory, boot from RAM), and whether the debugger is connected to the device or not. Accesses to the other secured regions are also allowed.

RDP Level 1 (Flash memory content protection)

When the global read protection level 1 is set, the below properties apply:

- • The embedded flash memory content is protected against debugger and potential malicious code stored in RAM. Hence as soon as any debugger is connected or has been connected, or a boot is configured in embedded RAM (intrusion), the embedded Flash memory prevents any accesses to Flash memory.

- • When no intrusion is detected (no boot in RAM, no boot in System Flash memory and no debugger connected), all read/program/erase operations from/to the user Flash

memory are allowed (if no other protections are set). Accesses to the other secured regions are also allowed.

- • When an intrusion is detected, no accesses to the user Flash memory can be performed. A bus error is generated when a read access is requested to the Flash memory. In addition, no accesses to other secured regions (read or write) can be performed.

- • When performing an RDP level regression, i.e. programming the RDP protection to level 0, the user Flash memory and the other secured regions are mass erased, as described in RDP protection transitions .

- • When booting from STMicroelectronics non-secure bootloader, only the identification services are available (GET_ID_COMMAND, GET_VER_COMMAND and GET_CMD_COMMAND).

RDP Level 2 (device protection and intrusion prevention)

When the global read protection level 2 is set, the below rules apply:

- • All debugging features are disabled.

- • Like level 0, all read/write/erase operations from/to the user Flash memory are allowed since the debugger and the boot from RAM and System Flash memory are disabled. Accesses to the other secured regions are also allowed.

- • Booting from RAM is no more allowed.

- • The user option bits described in Section 4.4 can no longer be changed.

Caution: Memory read protection level 2 is an irreversible operation. When level 2 is activated, the level of protection cannot be changed back to level 0 or level 1.

Note: The JTAG port is permanently disabled when level 2 is active (acting as a JTAG fuse). As a consequence, STMicroelectronics is not able to perform analysis on defective parts on which the level 2 protection has been set.

Apply a power-on reset if the global read protection level 2 is set while the debugger is still connected.

The above RDP global protection is summarized in Table 21 .

Table 21. Protection vs RDP Level (1)

| Boot area | Inputs | Effects | Comment | ||||

|---|---|---|---|---|---|---|---|

| RDP | Debugger connected | User Flash memory access (2) | System Flash memory access (3) | Other secured regions | Option Bytes access | ||

| User Flash memory | Level 0 | Yes (4) /No | R/W/E | R | R/W | R/W | |

| Level 1 | Yes (3) | illegal access (5) | R | no access | R/W | - | |

| Level 1 | No | R/W/E | R | R/W | R/W | ||

| Level 2 | No | R/W/ E | R | R/W | R | ||

| Boot area | Inputs | Effects | Comment | ||||

|---|---|---|---|---|---|---|---|

| RDP | Debugger connected | User Flash memory access (2) | System Flash memory access (3) | Other secured regions | Option Bytes access | ||

| RAM or System Flash memory | Level 0 | Yes (3) /No | R/W/E | R | R/W | R/W | - |

| Level 1 | Yes (3) /No | illegal access (5) | R | no access | R/W | When selected, only ST basic bootloader is executed | |

| Level 2 | No | Not applicable | No boot from RAM or ST system Flash memory in RDP level 2 | ||||

- 1. R = read, W = write, E = erase.

- 2. PCROP (see Section 4.5.4 ) and secure-only access control (see Section 4.5.5 ) applies.

- 3. Read accesses to secure boot and secure libraries stored in system Flash possible only from STMicroelectronics code.

- 4. JTAG interface disabled while secure libraries are executed.

- 5. Read protection error (RDPERR) with bus error on read operations, Write protection error (WRPERR) on write/erase operations.

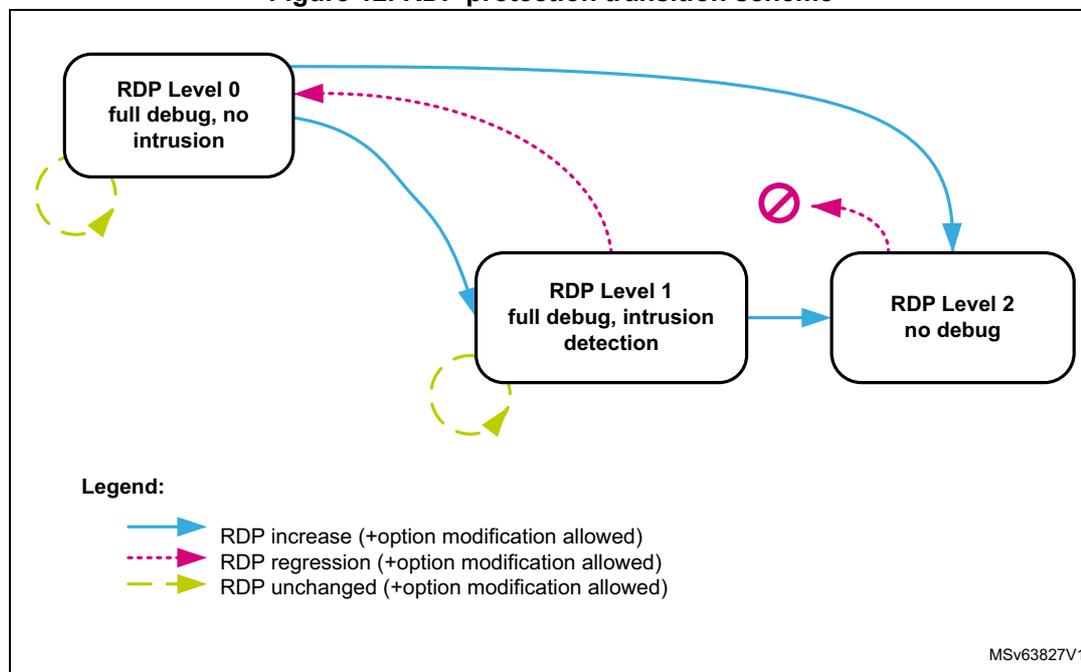

RDP protection transitions

Figure 12 shows how to switch from one RDP level to another. The transition is effective after successfully writing the option bytes including RDP (refer to Section 4.4.3 for details on how to change the option bytes).

Figure 12. RDP protection transition scheme

The diagram illustrates the RDP protection transition scheme between three levels: RDP Level 0 (full debug, no intrusion), RDP Level 1 (full debug, intrusion detection), and RDP Level 2 (no debug). Transitions are indicated by arrows:

- Solid blue arrows represent RDP increase (+option modification allowed). Transitions are from Level 0 to Level 1, Level 1 to Level 2, and Level 0 to Level 2.

- Dashed pink arrows represent RDP regression (+option modification allowed). Transitions are from Level 1 to Level 0 and from Level 2 to Level 0. The transition from Level 2 to Level 0 is marked with a red 'no' symbol (circle with a slash).

- Dashed yellow arrows represent RDP unchanged (+option modification allowed). These are self-loops on each level.

Table 22 details the RDP transitions and their effects on the product.

Table 22. RDP transition and effects

| RDP transition | RDP option update | Effect on device | |||

|---|---|---|---|---|---|

| Level before change | Level after change | Debugger disconnect | Option bytes change | Mass erase | |

| L0 | L1 | not 0xAA and not 0xCC | No | Allowed | No |

| L2 | 0xCC | Yes | Not allowed | No | |

| L1 | L2 | 0xCC | Yes | Not allowed | No |

| L0 | 0xAA | No | Allowed | Yes | |

| L0 | L0 | 0xAA | No | Allowed | No |

| L1 | L1 | not 0xAA and not 0xCC | |||

When the current RDP level is RDP level 1, requesting a new RDP level 0 causes a full mass erase:

- • The user Flash memory area of the embedded Flash memory is mass erased:

- – A partial sector erase occurs if PCROP (respectively secure-only) areas are preserved by the application. It happens when both DMEP bits (respectively DMES bits) are set to 0 in FLASH_PRAR_CUR and FLASH_PRAR_PRG (respectively FLASH_SCAR_CUR and FLASH_SCAR_PRG). The sectors belonging to the preserved area(s) are not erased.

- – A full bank erase occurs when at least one DMEP bit is set to 1 in FLASH_PRAR_CUR or FLASH_PRAR_PRG, and at least one DMES bit is set to 1 in FLASH_SCAR_CUR or FLASH_SCAR_PRG.

Note: Data in write protection area are not preserved during RDP regression.

- • The other secured regions are also erased.

During a level regression, if a PCROP area overlaps with a secure-only area, the embedded Flash memory performs the erase operation depending on the DMES/DMEP options bits (see strike-through areas in red in Figure 13). More specifically:

- • When DMEP is set in FLASH_PRAR_CUR or FLASH_PRAR_PRG, the PCROP area is erased (overlapped or not with secure-only area).

- • When DMES is set in FLASH_SCAR_CUR or FLASH_SCAR_PRG, the secure-only area is erased (overlapped or not with PCROP area).

Note: The sector protections (PCROP, secure-only) are removed only if the protected sector boundaries are modified by the user application.

Figure 13. Example of protected region overlapping

About RDP protection errors

Whatever the RDP level, the corresponding error flag is raised when an illegal read or write access is detected (see Section 4.7: FLASH error management ).

4.5.4 Proprietary code readout protection (PCROP)

The embedded Flash memory allows the definition of an “executable-only” area in the user area. In this area, only instruction fetch transactions from the system, i.e. no data access (data or literal pool) are allowed. This protection is particularly efficient to protect third party software intellectual property.

Note: Executable-only area usage requires the native code to be compiled accordingly using “execute-only” option.

PCROP area programming

One PCROP area can be defined by setting the PROT_AREA_END and PROT_AREA_START option bytes so that the END address is strictly higher than the START address. PROT_AREA_START and PROT_AREA_END are defined with a granularity of 256 bytes. This means that the actual PCROP area size (in bytes) is defined by:

As an example, to set a PCROP area on the first 4 Kbytes (i.e. from address 0x0800 0000 to address 0x0800 0FFF, both included), the embedded Flash memory must be configured as follows:

- • \( \text{PROT\_AREA\_START}[11:0] = 0x000 \)

- • \( \text{PROT\_AREA\_END}[11:0] = 0x00F \)

The protected area size defined above is equal to:

The minimum execute-only PCROP area that can be set is 16 Flash words (or 512 bytes). The maximum area is the whole user Flash memory, configured by setting to the same value the PCROP area START and END addresses.

Note: It is recommended to align the PCROP area size with the Flash sector granularity in order to avoid access right issues.

PCROP area properties

Each valid PCROP area has the following properties:

- • Arm ® Cortex ® -M7 debug events are ignored while executing code in this area.

- • Only the CPU can access it (Master ID filtering), using only instruction fetch transactions. In all other cases, accessing the PCROP area is illegal (see below).

- • Illegal transactions to a PCROP area (i.e. data read or write, not fetch) are managed as below:

- – Read operations return a zero, write operations are ignored.

- – No bus error is generated but an error flag is raised (RDPERR for read, WRPERR for write).

- • A valid PCROP area is erase-protected. As a result:

- – No erase operations to a sector located in this area is possible (including the sector containing the area start address and the end address)

- – No bank erase can be performed if a valid PCROP area is defined, except during regression level or erase with protection removal.

- • Only the CPU can modify the PCROP area definition and DMEP bit, as explained in Changing user option bytes in Section 4.4.3 .

- • During an RDP level 1 to 0 regression where the PCROP area is not null

- – The PCROP area content is not erased if the DMEP bits are both set to 0 in FLASH_PRRAR_CUR and FLASH_PRRAR_PRG registers.

- – The PCROP area content is erased if either of the corresponding DMEP bit is set to 1 in FLASH_PRRAR_CUR or FLASH_PRRAR_PRG register.

For more information on PCROP protection errors, refer to Section 4.7: FLASH error management .

4.5.5 Secure access mode

The embedded Flash memory allows the definition of a secure-only area in the user area. This area can be accessed only while the CPU executes secure application code. This feature is available only if the SECURITY option bit is set to 1.

Secure-only areas help isolating secure user code from application non-secure code. As an example, they can be used to protect a customer secure firmware upgrade code, a custom secure boot library or a third party secure library.

Secure-only area programming

One secure-only area can be defined by setting the SEC_AREA_END and SEC_AREA_START option bytes so that the END address is strictly higher than the START address. SEC_AREA_START and SEC_AREA_END are defined with a granularity of 256 bytes. This means that the actual secure-only area size (in bytes) is defined by:

As an example, to set a secure-only area on the first 8 Kbytes (i.e. from address 0x0800 0000 to address 0x0800 1FFF, both included), the embedded Flash memory must be configured as follows:

- • SEC_AREA_START[11:0] = 0x000

- • SEC_AREA_END[11:0] = 0x01F

The secure-only area size defined above is equal to:

Note: These option bytes can be modified only by the CPU running ST security library or application secure code, except during regression level or erase with protection removal.

The minimum secure-only area that can be set is 16 Flash words (or 512 bytes). The maximum area is the whole user Flash memory bank, configured by setting to the same value the secure-only area START and END addresses.

Note: It is recommended to align the secure-only area size with Flash sector granularity in order to avoid access right issues.

Secure-only access area properties

- • Arm ® Cortex ® -M7 debug events are ignored while executing code in this area.

- • Only the CPU executing ST secure library or user secure application can access it (Master ID filtering). In all other cases, accessing the secure-only area is illegal (see below).

- • Illegal transactions to a secure-only area are managed as follows:

- – Data read transactions return zero. Data write transactions are ignored. No bus error is generated but an error flag is raised (RDSERR for read, WRPERR for write).

- – Read instruction transactions generate a bus error and the RDSERR error flag is raised.

- • A valid secure-only area is erase-protected. As a result:

- – No erase operations to a sector located in this area are possible (including the sector containing the area start address and the end address), unless the application software is executed from a valid secure-only area.

- – No bank erase can be performed if a valid secure-only area is defined, except during regression level or erase with protection removal.

- • Only the CPU can modify the secure-only area definition and DMES bit, as explained in Changing user option bytes in Section 4.4.3 .

- • During an RDP level 1 to 0 regression where the secure-only area is not null:

- – the secure-only area content is not erased if the DMES bits are both set to 0 in FLASH_SCAR_CUR and FLASH_SCAR_PRG registers.

- – the secure-only area content is erased if either of the DMES bits is set to 1 in FLASH_SCAR_CUR or FLASH_SCAR_PRG register.

For more information on secure-only protection errors, refer to Section 4.7: FLASH error management .

4.6 FLASH low-power modes

4.6.1 Introduction

The table below summarizes the behavior of the embedded Flash memory in the microcontroller low-power modes. The embedded Flash memory belongs to the D1 domain.

Table 23. Effect of low-power modes on the embedded Flash memory

| System state | Power mode | D1 domain voltage range | Allowed if FLASH busy | FLASH power mode (in D1 domain) | |

|---|---|---|---|---|---|

| D1 domain | D2 domain | ||||

| Run | DRun | DRun, DStop or DStandby | VOS0/1/2/3 | Yes | Run |

| DStop | DStop or DStandby | VOS0/1/2/3 | No | Off | |

| DStandby | DStop or DStandby | Off | No | Off | |

| Stop | DStop | DStop or DStandby | SVOS3/4/5 | No | Clock gated or Stopped |

| DStandby | DStop or DStandby | Off | No | Off | |

| Standby (1) | DStandby | DStandby | No | ||

- 1. D3 domain must always be in DStandby mode. When all clocks are stopped and the CPU is in CStop, the VCORE domain is switched off.

When the system state changes or within a given system state, the embedded Flash memory might get a different voltage supply range (VOS) according to the application. The procedure to switch the embedded Flash memory into various power mode (run, clock gated, stopped, off) is described hereafter.

Note: For more information in the microcontroller power states, refer to the Power control section (PWR).

4.6.2 Managing the FLASH domain switching to DStop or DStandby