73. USB on-the-go high-speed (OTG_HS)

This section applies to STM32U59x/5Ax/5Fx/5Gx devices only.

73.1 OTG_HS introduction

Portions Copyright (c) Synopsys, Inc. All rights reserved. Used with permission.

This section presents the architecture and the programming model of the OTG_HS controller.

The following acronyms are used throughout the section:

| FS | Full-speed |

| LS | Low-speed |

| HS | High-speed |

| MAC | Media access controller |

| OTG | On-the-go |

| PFC | Packet FIFO controller |

| PHY | Physical layer |

| USB | Universal serial bus |

| UTMI | USB 2.0 Transceiver Macrocell interface (UTMI) |

| LPM | Link power management |

| BCD | Battery charging detector |

| HNP | Host negotiation protocol |

| SRP | Session request protocol |

References are made to the following documents:

- • USB On-The-Go Supplement, Revision 2.0

- • Universal Serial Bus Revision 2.0 Specification

- • USB 2.0 Link Power Management Addendum Engineering Change Notice to the USB 2.0 specification, July 16, 2007

- • Errata for USB 2.0 ECN: Link Power Management (LPM) - 7/2007

- • Battery Charging Specification, Revision 1.2

The USB OTG is a dual-role device (DRD) controller that supports both device and host functions and is fully compliant with the On-The-Go Supplement to the USB 2.0 Specification . It can also be configured as a host-only or device-only controller, fully compliant with the USB 2.0 Specification . OTG_HS supports the speeds defined in the Table 761: OTG_HS speeds supported below. The only external device required is a charge pump for V BUS in OTG mode.

Table 761. OTG_HS speeds supported

| - | HS (480 Mbit/s) | FS (12 Mbit/s) | LS (1.5 Mbit/s) |

|---|---|---|---|

| Host mode | X | X | X |

| Device mode | X | X | - |

73.2 OTG_HS main features

The main features can be divided into three categories: general, host-mode, and device-mode features.

73.2.1 General features

The OTG_HS interface general features are the following:

- • It is USB-IF certified to the Universal Serial Bus Specification Rev 2.0.

- • OTG_HS supports the following PHY interfaces:

- – A UTMI interface for internal HS PHY

- • It includes support (PHY) for the optional On-The-Go (OTG) protocol detailed in the On-The-Go Supplement Rev 2.0 specification

- – Integrated support for A-B device identification (ID line)

- – It allows host to turn \( V_{BUS} \) off to conserve battery power in OTG applications.

- – It supports OTG monitoring of \( V_{BUS} \) levels with internal comparators.

- • It is software-configurable to operate as:

- – USB On-The-Go Full-Speed Dual Role device

- • It supports HS SOF and LS Keep-alives with

- – SOF pulse PAD connectivity

- – SOF pulse internal connection to timer (TIMx)

- – Configurable framing period

- – Configurable end of frame interrupt

- • OTG_HS embeds an internal DMA with thresholding support and software selectable AHB burst type in DMA mode.

- • It includes power saving features such as system stop during USB suspend, switch-off of clock domains internal to the digital core, PHY and DFIFO power management.

- • It features a dedicated RAM of 4 Kbytes with advanced FIFO control:

- – Configurable partitioning of RAM space into different FIFOs for flexible and efficient use of RAM

- – Each FIFO can hold multiple packets.

- – Dynamic memory allocation

- – Configurable FIFO sizes that are not powers of 2 to allow the use of contiguous memory locations

- • It guarantees max USB bandwidth for up to one frame (1 ms) without system intervention.

- • It supports charging port detection as described in Battery Charging Specification Revision 1.2.

73.2.2 Host-mode features

The OTG_HS interface main features and requirements in host-mode are the following:

- • External charge pump for V BUS voltage generation

- • Up to 16 host channels (pipes): each channel is dynamically reconfigurable to allocate any type of USB transfer.

- • Built-in hardware scheduler holding:

- – Up to 16 interrupt plus isochronous transfer requests in the periodic hardware queue

- – Up to 16 control plus bulk transfer requests in the non-periodic hardware queue

- • Management of a shared Rx FIFO, a periodic Tx FIFO and a nonperiodic Tx FIFO for efficient usage of the USB data RAM.

73.2.3 Peripheral-mode features

The OTG_HS interface main features in peripheral-mode are the following:

- • 1 bidirectional control endpoint0

- • 8 IN endpoints (EPs) configurable to support bulk, interrupt or isochronous transfers

- • 8 OUT endpoints configurable to support bulk, interrupt or isochronous transfers

- • Management of a shared Rx FIFO and a Tx-OUT FIFO for efficient usage of the USB data RAM

- • Management of up to 9 dedicated Tx-IN FIFOs (one for each active IN EP) to put less load on the application

- • Support for the soft disconnect feature.

73.3 OTG_HS implementation

Table 762. OTG_HS implementation (1)

| USB features | OTG_HS for STM32U59x/5Ax/5Fx/5Gx |

|---|---|

| Device bidirectional endpoints (including EP0) | 9 |

| Host mode channels | 16 |

| Size of dedicated SRAM | 4 Kbytes |

| USB 2.0 link power management (LPM) support | X |

| OTG revision supported | 2.0 |

| Battery charging detection (BCD) support | X |

| Integrated PHY | HS |

| HNP and SRP support | - |

| SRP: OTG_DVBUSDIS register | - |

| SRP: OTG_DVBUSPULSE register | - |

| HNP: OTG_GOTGCTL bits 11:8 | - |

| SRP: OTG_GOTGCTL bits 1:0 | - |

| HNP/SRP: OTG_GOTGINT bits 19; 17; 9:8 | - |

| USB features | OTG_HS for STM32U59x/5Ax/5Fx/5Gx |

|---|---|

| HNP: OTG_GUSBCFG bit 9 | - |

| SRP: OTG_GUSBCFG bit 8 | - |

| OTG_PCGCTL1 register | X |

1. "X" = supported, "-" = not supported, "FS" = supported in FS mode, "HS" = supported in HS mode.

73.4 OTG_HS functional description

73.4.1 OTG_HS block diagram

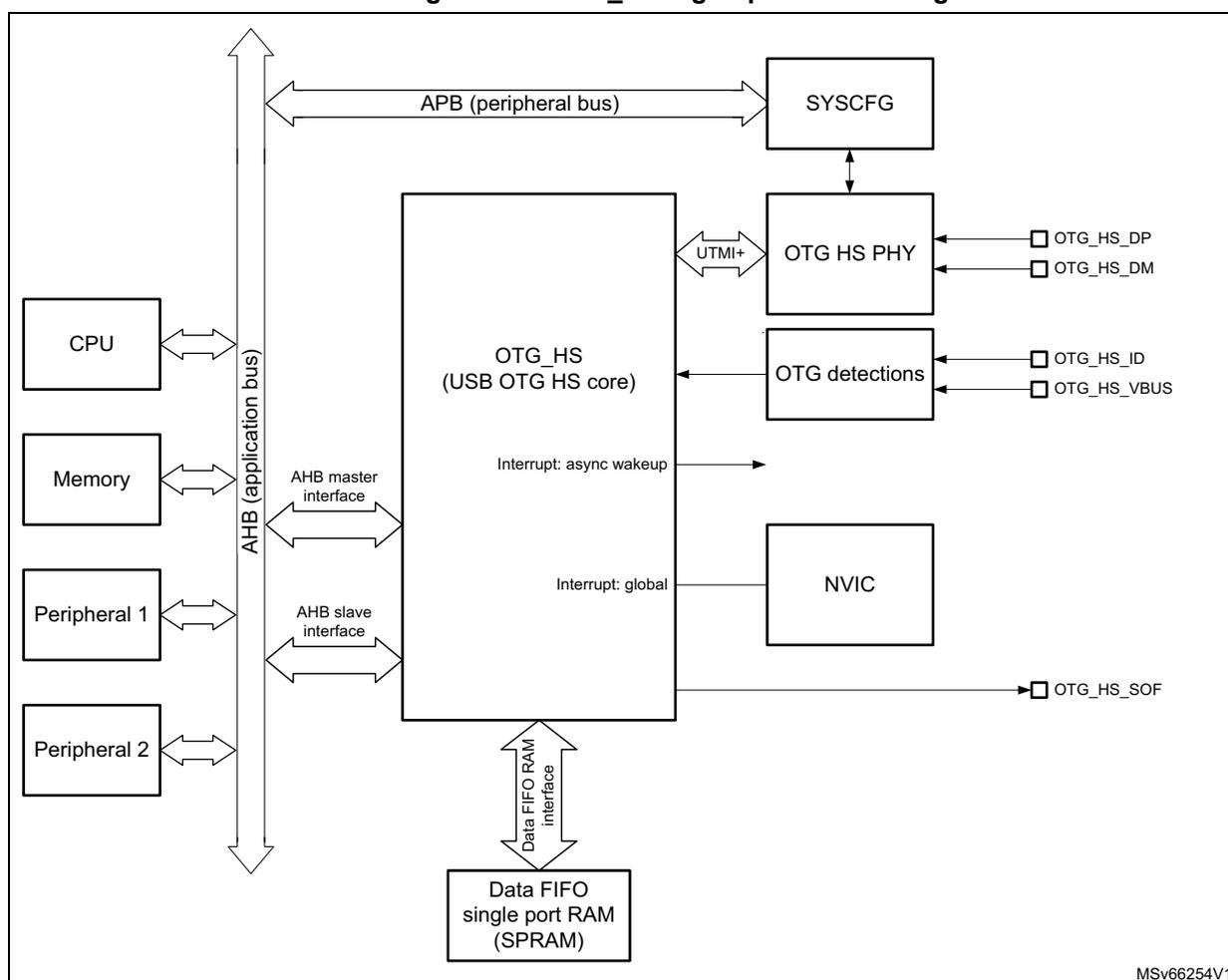

Figure 918. OTG_HS high-speed block diagram

The block diagram illustrates the internal architecture of the OTG_HS (USB OTG HS core) and its connections to various system components:

- CPU, Memory, Peripheral 1, and Peripheral 2 are connected to the AHB (application bus) .

- The AHB (application bus) is connected to the OTG_HS (USB OTG HS core) via an AHB master interface and an AHB slave interface .

- The OTG_HS (USB OTG HS core) is connected to the SYSCFG block via the APB (peripheral bus) .

- The OTG_HS (USB OTG HS core) is connected to the OTG HS PHY block via the UTMI+ interface.

- The OTG HS PHY block is connected to the external pins OTG_HS_DP and OTG_HS_DM .

- The OTG_HS (USB OTG HS core) is connected to the OTG detections block, which is connected to the external pins OTG_HS_ID and OTG_HS_VBUS .

- The OTG_HS (USB OTG HS core) is connected to the NVIC block via Interrupt: async wakeup and Interrupt: global lines.

- The OTG_HS (USB OTG HS core) is connected to the Data FIFO single port RAM (SPRAM) block via the Data FIFO RAM interface .

- An external pin OTG_HS_SOF is connected to the OTG_HS (USB OTG HS core) .

MSV66254V1

73.4.2 OTG_HS pin and internal signals

Table 763. OTG_HS input/output pins

| Signal name | Signal type | Description |

|---|---|---|

| OTG_HS_DP | Digital input/output | USB OTG D+ line |

| OTG_HS_DM | Digital input/output | USB OTG D- line |

| OTG_HS_ID | Digital input | USB OTG ID |

| OTG_HS_VBUS | Analog input | USB OTG VBUS |

| OTG_HS_SOF | Digital output | USB OTG Start Of Frame (visibility) |

Table 764. OTG_HS input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| usb_sof | Digital output | USB OTG start-of-frame event for on chip peripherals |

| usb_wkup | Digital output | USB OTG wake-up event output |

| usb_gbl_it | Digital output | USB OTG global interrupt |

73.4.3 OTG_HS core

The OTG_HS receives the 60 MHz clock from the reset and clock controller (RCC). This is typically generated in the PLL associated with the HS PHY and enabled in the RCC. This clock is used for driving the 60 MHz domain at high-speed (480 Mbit/s) and must be enabled prior to configuring the OTG core.

The CPU reads and writes from/to the OTG core registers through the AHB peripheral bus. It is informed of USB events through the single USB OTG interrupt line described in Section 73.12: OTG_HS interrupts .

The CPU submits data over the USB by writing 32-bit words to dedicated OTG locations (push registers). The data are then automatically stored into Tx-data FIFOs configured within the USB data RAM. There is one Tx FIFO push register for each in-endpoint (peripheral mode) or out-channel (host mode).

The CPU receives the data from the USB by reading 32-bit words from dedicated OTG addresses (pop registers). The data are then automatically retrieved from a shared Rx FIFO configured within the 4-Kbyte USB data RAM. There is one Rx FIFO pop register for each out-endpoint or in-channel.

The USB protocol layer is driven by the serial interface engine (SIE) and serialized over the USB by the transceiver module within the on-chip physical layer (PHY).

Caution: To guarantee a correct operation for the USB OTG_HS peripheral, the AHB frequency must be higher than 30 MHz.

73.4.4 OTG detections

Additionally the OTG_HS uses the following functions:

- • Integrated ID pull-up resistor used to sample the ID line for A/B device identification.

- • \( V_{BUS} \) sensing comparators with hysteresis used to detect \( V_{BUS} \) valid, A-B session valid and session-end voltage thresholds. They are used to detect valid startup and end-of-session conditions, and constantly monitor the \( V_{BUS} \) supply during USB operations.

73.4.5 High-speed OTG PHY connected to OTG_HS

Note: Refer to implementation table to determine if an HS PHY is embedded.

The USB OTG core includes an internal UTMI interface which is connected to the embedded HS PHY (see Section 73.4.1: OTG_HS block diagram ).

73.4.6 Battery charging detection

Support is available for the USB battery charging specification (v1.2).

The OTG_HS includes the necessary circuits to enable battery charging detection (portable device).

There is also a possibility to behave as a charging data port (the port advertises 1.5 A available on its VBUS pin).

Various fields control this functions and are implemented in register OTG_GCCFG.

73.5 OTG_HS dual role device (DRD)

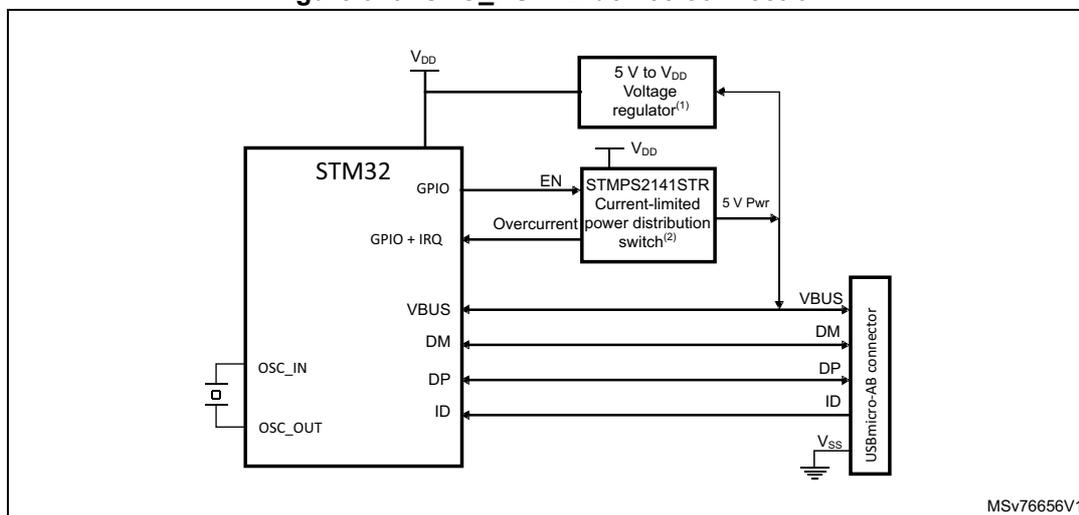

Figure 919. OTG_HS A-B device connection

1. External voltage regulator only needed when building a VBUS powered device.

2. STMP2141STR needed only if the application has to support a VBUS powered device. A basic power switch can be used if 5 V are available on the application board.

73.5.1 ID line detection

The host or peripheral (the default) role is assumed depending on the ID input pin. The ID line status is determined on plugging in the USB cable, depending on whether a MicroA or MicroB plug is connected to the micro-AB receptacle.

- • If the B-side of the USB cable is connected with a floating ID wire, the integrated pull-up resistor detects a high ID level and the default peripheral role is confirmed. In this configuration the OTG_HS complies with the standard FSM described in section 4.2.4: ID pin of the On-the-Go specification Rev2.0, supplement to the USB2.0.

- • If the A-side of the USB cable is connected with a grounded ID, the OTG_HS issues an ID line status change interrupt (CIDSCHG bit in OTG_GINTSTS) for host software initialization, and automatically switches to the host role. In this configuration the OTG_HS complies with the standard FSM described by section 4.2.4: ID pin of the On-the-Go specification Rev2.0, supplement to the USB2.0.

73.6 OTG_HS as a USB peripheral

This section gives the functional description of the OTG_HS in the USB peripheral mode. The OTG_HS works as an USB peripheral in the following circumstances:

- • OTG B-Peripheral

- – OTG B-device default state if B-side of USB cable is plugged in

- • B-device

- – If the ID line is present, functional and connected to the B-side of the USB cable.

- • Peripheral only

- – The force device mode bit (FDMOD) in the Section 73.14.4: OTG USB configuration register (OTG_GUSBFCFG) is set to 1, forcing the OTG_HS core to work as an USB peripheral-only. In this case, the ID line is ignored even if it is present on the USB connector.

Note: To build a bus-powered device implementation in case of the B-device or peripheral-only configuration, an external regulator has to be added, that generates the necessary power-supply from \( V_{BUS} \) .

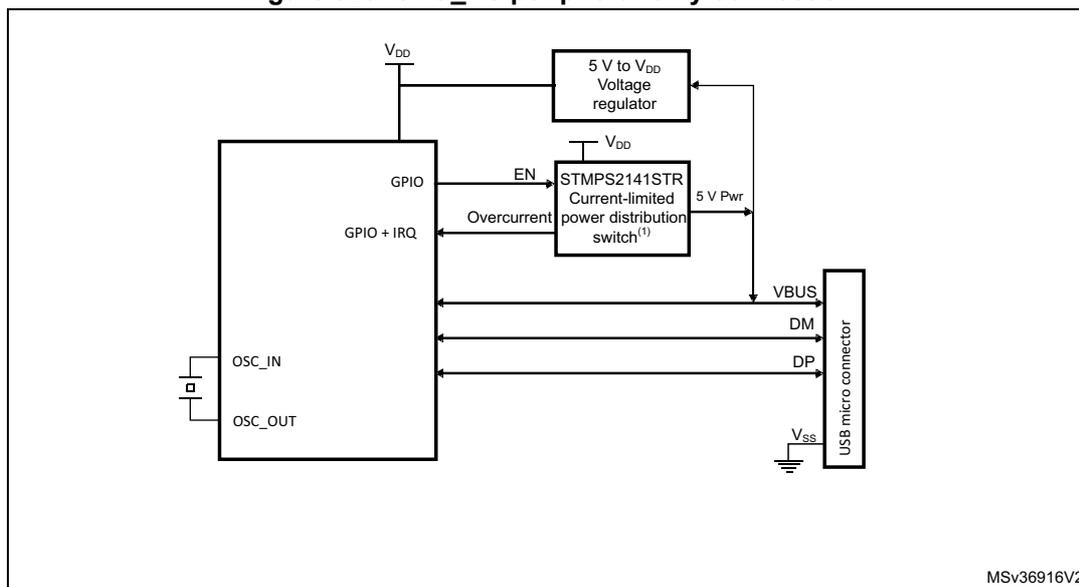

Figure 920. OTG_HS peripheral-only connection

- 1. Use a regulator to build a bus-powered device.

73.6.1 Peripheral states

Powered state

The \( V_{BUS} \) input detects the B-session valid voltage by which the USB peripheral is allowed to enter the powered state (see USB2.0 section 9.1). The OTG_HS then automatically connects the DP pull-up resistor to signal full-speed device connection to the host and generates the session request interrupt (SRQINT bit in OTG_GINTSTS) to notify the powered state.

The \( V_{BUS} \) input also ensures that valid \( V_{BUS} \) levels are supplied by the host during USB operations. If a drop in \( V_{BUS} \) below B-session valid happens to be detected (for instance because of a power disturbance or if the host port has been switched off), the OTG_HS automatically disconnects and the session end detected (SEDET bit in OTG_GOTGINT) interrupt is generated to notify that the OTG_HS has exited the powered state.

In the powered state, the OTG_HS expects to receive some reset signaling from the host. No other USB operation is possible. When a reset signaling is received the reset detected interrupt (USBRST in OTG_GINTSTS) is generated. When the reset signaling is complete, the enumeration done interrupt (ENUMDNE bit in OTG_GINTSTS) is generated and the OTG_HS enters the Default state.

Soft disconnect

The powered state can be exited by software with the soft disconnect feature. The DP pull-up resistor is removed by setting the soft disconnect bit in the device control register (SDIS bit in OTG_DCTL), causing a device disconnect detection interrupt on the host side even though the USB cable was not really removed from the host port.

Default state

In the Default state the OTG_HS expects to receive a SET_ADDRESS command from the host. No other USB operation is possible. When a valid SET_ADDRESS command is

decoded on the USB, the application writes the corresponding number into the device address field in the device configuration register (DAD bit in OTG_DCFG). The OTG_HS then enters the address state and is ready to answer host transactions at the configured USB address.

Suspended state

The OTG_HS peripheral constantly monitors the USB activity. After counting 3 ms of USB idleness, the early suspend interrupt (ESUSP bit in OTG_GINTSTS) is issued, and confirmed 3 ms later, if appropriate, by the suspend interrupt (USBSUSP bit in OTG_GINTSTS). The device suspend bit is then automatically set in the device status register (SUSPSTS bit in OTG_DSTS) and the OTG_HS enters the suspended state.

The suspended state may optionally be exited by the device itself. In this case the application sets the remote wake-up signaling bit in the device control register (RWUSIG bit in OTG_DCTL) and clears it after 1 to 15 ms.

When a resume signaling is detected from the host, the resume interrupt (WKUPINT bit in OTG_GINTSTS) is generated and the device suspend bit is automatically cleared.

73.6.2 Peripheral endpoints

The OTG_HS core instantiates the following USB endpoints:

- • Control endpoint 0:

- – Bidirectional and handles control messages only

- – Separate set of registers to handle in and out transactions

- – Dedicated control (OTG_DIEPCTL0/OTG_DOEPCTL0), transfer configuration (OTG_DIEPTSIZ0/OTG_DOEPTSIZ0), and status-interrupt (OTG_DIEPINT0/OTG_DOEPINT0) registers. The available set of bits inside the control and transfer size registers slightly differs from that of other endpoints

- • eight IN endpoints

- – Each of them can be configured to support the isochronous, bulk or interrupt transfer type

- – Each of them has dedicated control (OTG_DIEPCTLx), transfer configuration (OTG_DIEPTSIZx), and status-interrupt (OTG_DIEPINTx) registers

- – The device IN endpoints common interrupt mask register (OTG_DIEPMSK) is available to enable/disable a single kind of endpoint interrupt source on all of the IN endpoints (EP0 included)

- – Support for incomplete isochronous IN transfer interrupt (IISOIXFR bit in OTG_GINTSTS), asserted when there is at least one isochronous IN endpoint on

which the transfer is not completed in the current frame. This interrupt is asserted along with the end of periodic frame interrupt (OTG_GINTSTS/EOPF).

- • eight OUT endpoints

- – Each of them can be configured to support the isochronous, bulk or interrupt transfer type

- – Each of them has a dedicated control (OTG_DOEPCTLx), transfer configuration (OTG_DOEPTSIZx) and status-interrupt (OTG_DOEPINTx) register

- – Device OUT endpoints common interrupt mask register (OTG_DOEPMSK) is available to enable/disable a single kind of endpoint interrupt source on all of the OUT endpoints (EP0 included)

- – Support for incomplete isochronous OUT transfer interrupt (INCOMPISOOUT bit in OTG_GINTSTS), asserted when there is at least one isochronous OUT endpoint on which the transfer is not completed in the current frame. This interrupt is asserted along with the end of periodic frame interrupt (OTG_GINTSTS/EOPF).

Endpoint control

- • The following endpoint controls are available to the application through the device endpoint-x IN/OUT control register (OTG_DIEPCTLx/OTG_DOEPCTLx):

- – endpoint enable/disable

- – endpoint activate in current configuration

- – program USB transfer type (isochronous, bulk, interrupt)

- – program supported packet size

- – program Tx FIFO number associated with the IN endpoint

- – program the expected or transmitted data0/data1 PID (bulk/interrupt only)

- – program the even/odd frame during which the transaction is received or transmitted (isochronous only)

- – optionally program the NAK bit to always negative-acknowledge the host regardless of the FIFO status

- – optionally program the STALL bit to always stall host tokens to that endpoint

- – optionally program the SNOOP mode for OUT endpoint not to check the CRC field of received data

Endpoint transfer

The device endpoint-x transfer size registers (OTG_DIEPTSIZx/OTG_DOEPTSIZx) allow the application to program the transfer size parameters and read the transfer status. Programming must be done before setting the endpoint enable bit in the endpoint control register. Once the endpoint is enabled, these fields are read-only as the OTG_HS core updates them with the current transfer status.

The following transfer parameters can be programmed:

- • transfer size in bytes

- • number of packets that constitute the overall transfer size

Endpoint status/interrupt

The device endpoint-x interrupt registers (OTG_DIEPINTx/OTG_DOEPINTx) indicate the status of an endpoint with respect to USB- and AHB-related events. The application must read these registers when the OUT endpoint interrupt bit or the IN endpoint interrupt bit in

the core interrupt register (OEPINT bit in OTG_GINTSTS or IEPINT bit in OTG_GINTSTS, respectively) is set. Before the application can read these registers, it must first read the device all endpoints interrupt (OTG_DAINT) register to get the exact endpoint number for the device endpoint-x interrupt register. The application must clear the appropriate bit in this register to clear the corresponding bits in the OTG_DAINT and OTG_GINTSTS registers

The peripheral core provides the following status checks and interrupt generation:

- • transfer completed interrupt, indicating that data transfer was completed on both the application (AHB) and USB sides

- • setup stage has been done (control-out only)

- • associated transmit FIFO is half or completely empty (in endpoints)

- • NAK acknowledge has been transmitted to the host (isochronous-in only)

- • IN token received when Tx FIFO was empty (bulk-in/interrupt-in only)

- • Out token received when endpoint was not yet enabled

- • babble error condition has been detected

- • endpoint disable by application is effective

- • endpoint NAK by application is effective (isochronous-in only)

- • more than 3 back-to-back setup packets were received (control-out only)

- • timeout condition detected (control-in only)

- • isochronous out packet has been dropped, without generating an interrupt

73.7 OTG_HS as a USB host

This section gives the functional description of the OTG_HS in the USB host mode. The OTG_HS works as a USB host in the following circumstances:

Automatic host mode direct from ID pin:

The ID pin is not always available, refer to product datasheet for available pins.

- • Use cases:

- – Micro connector: A-Device with a Micro-A plug inserted, and connector ID pin connected to the STM32 ID pin which is then detected in a low state.

- • Note that the integrated pull-down resistors are automatically set on the DP/DM lines.

Manual forcing of host mode when not possible via ID pin:

The force host mode bit (FHMOD) in the OTG USB configuration register (OTG_GUSBCFG) forces the OTG_HS core to work as a USB host-only when required.

- • Use cases:

- – Standard-A connector which always implies Host mode.

- – Micro connector, so ID present on connector, but ID pin not available in pinout, at A-plug insertion (detected by another means, for example: GPIO).

- – A Type-C connector, when host functionality is determined at cable attachment or via power delivery messages.

- • Note that the integrated pull-down resistors are set on the DP/DM lines by setting bit FORCEHOSTPD.

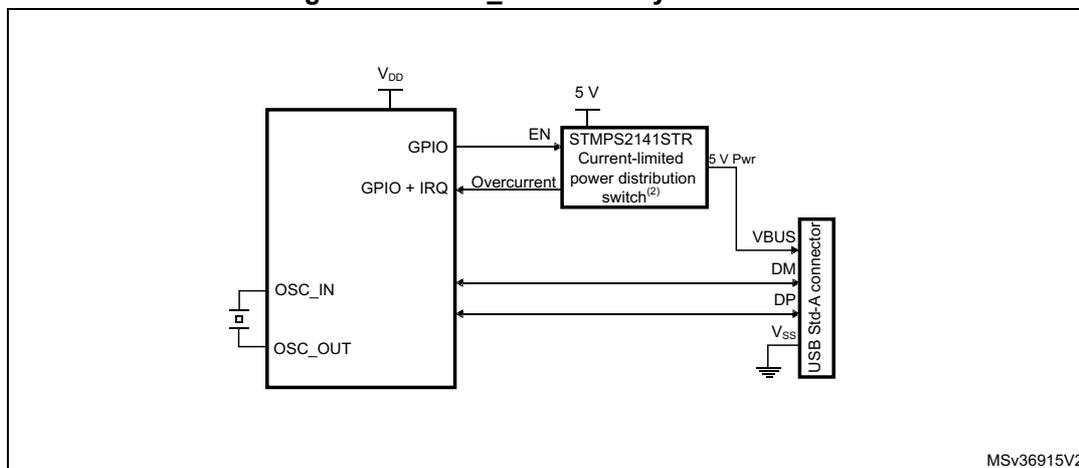

Note: On-chip 5 V \( V_{BUS} \) generation is not supported. For this reason, a charge pump or, if 5 V are available on the application board, a basic power switch must be added externally to drive

the 5 V \( V_{BUS} \) line. The external charge pump can be driven by any GPIO output. This is required for the OTG A-host, A-device and host-only configurations.

Figure 921. OTG_HS host-only connection

- 1. \( V_{DD} \) range is between 2 V and 3.6 V.

73.7.1 USB host states

Host port power

On-chip 5 V \( V_{BUS} \) generation is not supported. For this reason, a charge pump or, if 5 V are available on the application board, a basic power switch, must be added externally to drive the 5 V \( V_{BUS} \) line. The external charge pump can be driven by any GPIO output or via an I 2 C interface connected to an external PMIC (power management IC). When the application decides to power on \( V_{BUS} \) , it must also set the port power bit in the host port control and status register (PPWR bit in OTG_HPRT).

\( V_{BUS} \) valid

In Host mode, the VBUS sensing pin does not need to be connected to \( V_{BUS} \) .

The charge pump overcurrent flag can also be used to prevent electrical damage. Connect the overcurrent flag output from the charge pump to any GPIO input and configure it to generate a port interrupt on the active level. The overcurrent ISR must promptly disable the \( V_{BUS} \) generation and clear the port power bit.

Host detection of a peripheral connection

USB peripherals or B-device are detected as soon as they are connected. The OTG_HS core issues a host port interrupt triggered by the device connected bit in the host port control and status (PCDET bit in OTG_HPRT).

Host detection of peripheral a disconnection

The peripheral disconnection event triggers the disconnect detected interrupt (DISCINT bit in OTG_GINTSTS).

Host enumeration

After detecting a peripheral connection the host must start the enumeration process by sending USB reset and configuration commands to the new peripheral.

The application drives a USB reset signaling (single-ended zero) over the USB by keeping the port reset bit set in the host port control and status register (PRST bit in OTG_HPRT) for a minimum of 10 ms and a maximum of 20 ms. The application takes care of the timing count and then of clearing the port reset bit.

Once the USB reset sequence has completed, the host port interrupt is triggered by the port enable/disable change bit (PENCHNG bit in OTG_HPRT). This informs the application that the speed of the enumerated peripheral can be read from the port speed field in the host port control and status register (PSPD bit in OTG_HPRT) and that the host is starting to drive SOFs (FS) or Keep alives (LS). The host is now ready to complete the peripheral enumeration by sending peripheral configuration commands.

Host suspend

The application decides to suspend the USB activity by setting the port suspend bit in the host port control and status register (PSUSP bit in OTG_HPRT). The OTG_HS core stops sending SOFs and enters the suspended state.

The suspended state can be optionally exited on the remote device's initiative (remote wake-up). In this case the remote wake-up interrupt (WKUPINT bit in OTG_GINTSTS) is generated upon detection of a remote wake-up signaling, the port resume bit in the host port control and status register (PRES bit in OTG_HPRT) self-sets, and resume signaling is automatically driven over the USB. The application must time the resume window and then clear the port resume bit to exit the suspended state and restart the SOF.

If the suspended state is exited on the host initiative, the application must set the port resume bit to start resume signaling on the host port, time the resume window and finally clear the port resume bit.

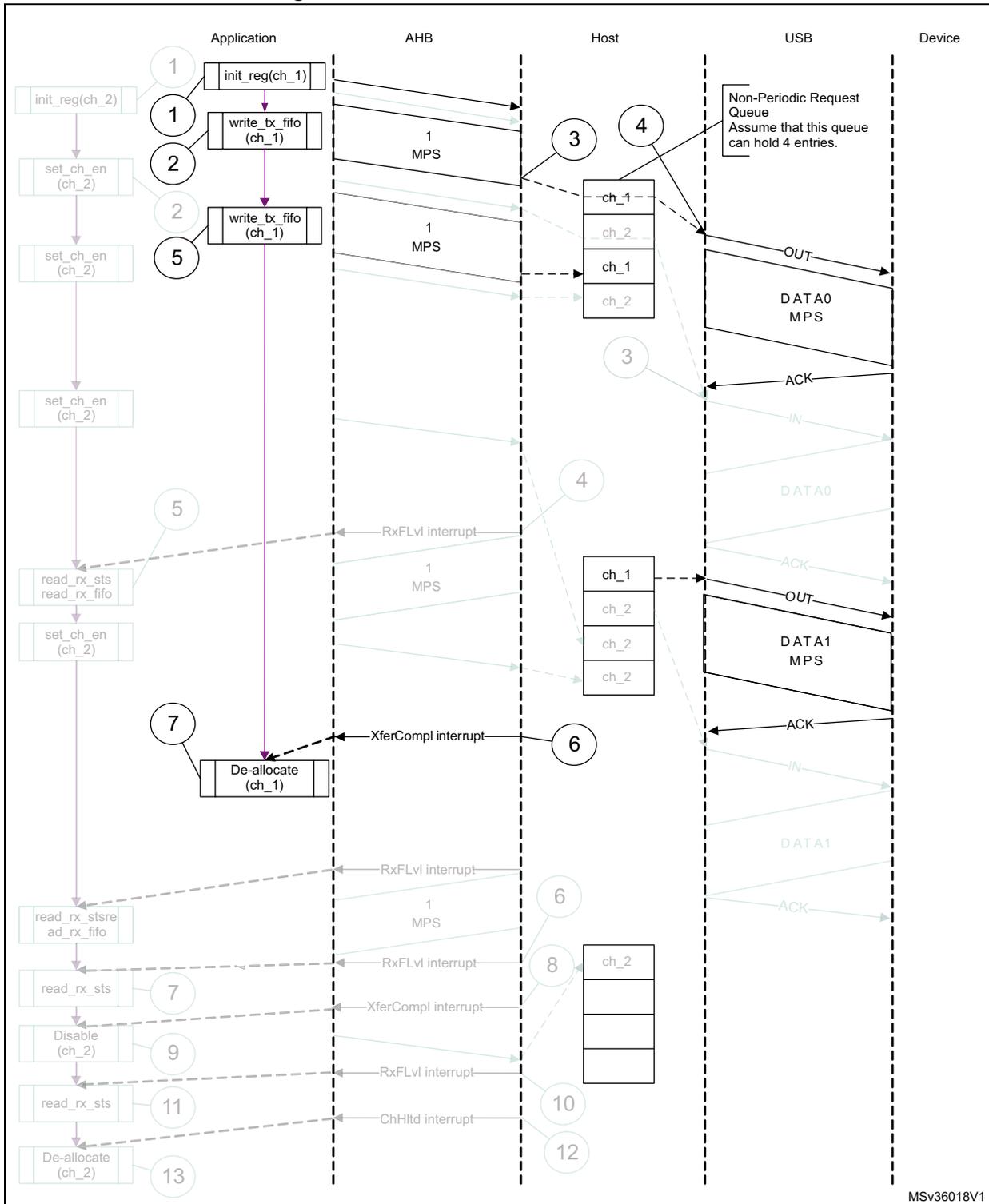

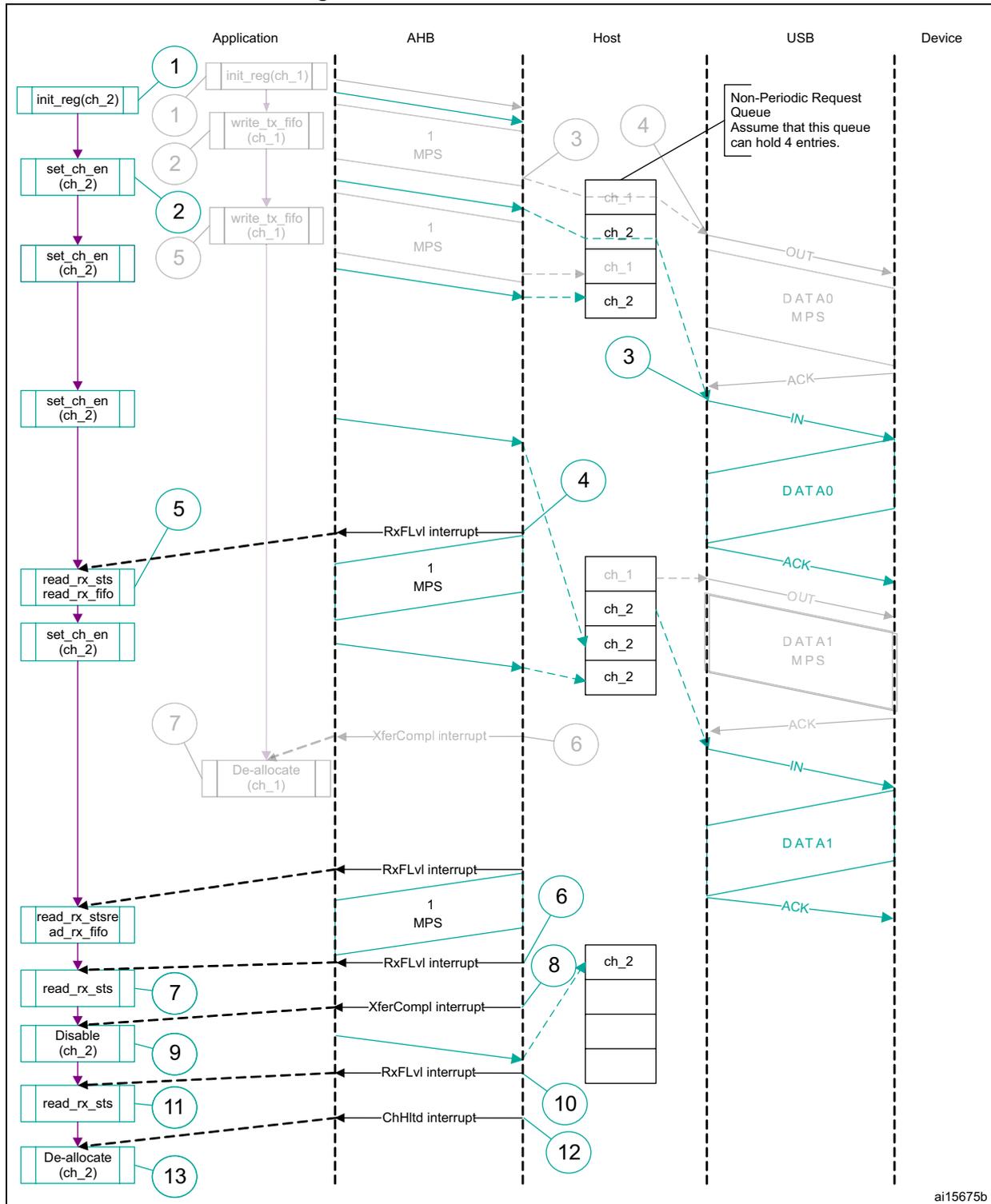

73.7.2 Host channels

The OTG_HS core instantiates 16 host channels. Each host channel supports an USB host transfer (USB pipe). The host is not able to support more than 16 transfer requests at the same time. If more than 16 transfer requests are pending from the application, the host controller driver (HCD) must re-allocate channels when they become available from previous duty, that is, after receiving the transfer completed and channel halted interrupts.

Each host channel can be configured to support in/out and any type of periodic/nonperiodic transaction. Each host channel makes use of dedicated control (OTG_HCCHARx), transfer configuration (OTG_HCTSIZx) and status/interrupt (OTG_HCINTx) registers with associated mask (OTG_HCINTMSKx) registers.

Host channel control

- • The following host channel controls are available to the application through the host channel-x characteristics register (OTG_HCCHARx):

- – Channel enable/disable

- – Program the HS/FS/LS speed of target USB peripheral

- – Program the address of target USB peripheral

- – Program the endpoint number of target USB peripheral

- – Program the transfer IN/OUT direction

- – Program the USB transfer type (control, bulk, interrupt, isochronous)

- – Program the maximum packet size (MPS)

- – Program the periodic transfer to be executed during odd/even frames

Host channel transfer

The host channel transfer size registers (OTG_HCTSIZx) allow the application to program the transfer size parameters, and read the transfer status. Programming must be done before setting the channel enable bit in the host channel characteristics register. Once the endpoint is enabled the packet count field is read-only as the OTG_HS core updates it according to the current transfer status.

- • The following transfer parameters can be programmed:

- – transfer size in bytes

- – number of packets making up the overall transfer size

- – initial data PID

Host channel status/interrupt

The host channel-x interrupt register (OTG_HCINTx) indicates the status of an endpoint with respect to USB- and AHB-related events. The application must read these registers when the host channels interrupt bit in the core interrupt register (HCINT bit in OTG_GINTSTS) is set. Before the application can read these registers, it must first read the host all channels interrupt (OTG_HAINT) register to get the exact channel number for the host channel-x interrupt register. The application must clear the appropriate bit in this register to clear the corresponding bits in the OTG_HAINT and OTG_GINTSTS registers.

The mask bits for each interrupt source of each channel are also available in the OTG_HCINTMSKx register.

- • The host core provides the following status checks and interrupt generation:

- – Transfer completed interrupt, indicating that the data transfer is complete on both the application (AHB) and USB sides

- – Channel has stopped due to transfer completed, USB transaction error or disable command from the application

- – Associated transmit FIFO is half or completely empty (IN endpoints)

- – ACK response received

- – NAK response received

- – STALL response received

- – USB transaction error due to CRC failure, timeout, bit stuff error, false EOP

- – Babble error

- – frame overrun

- – data toggle error

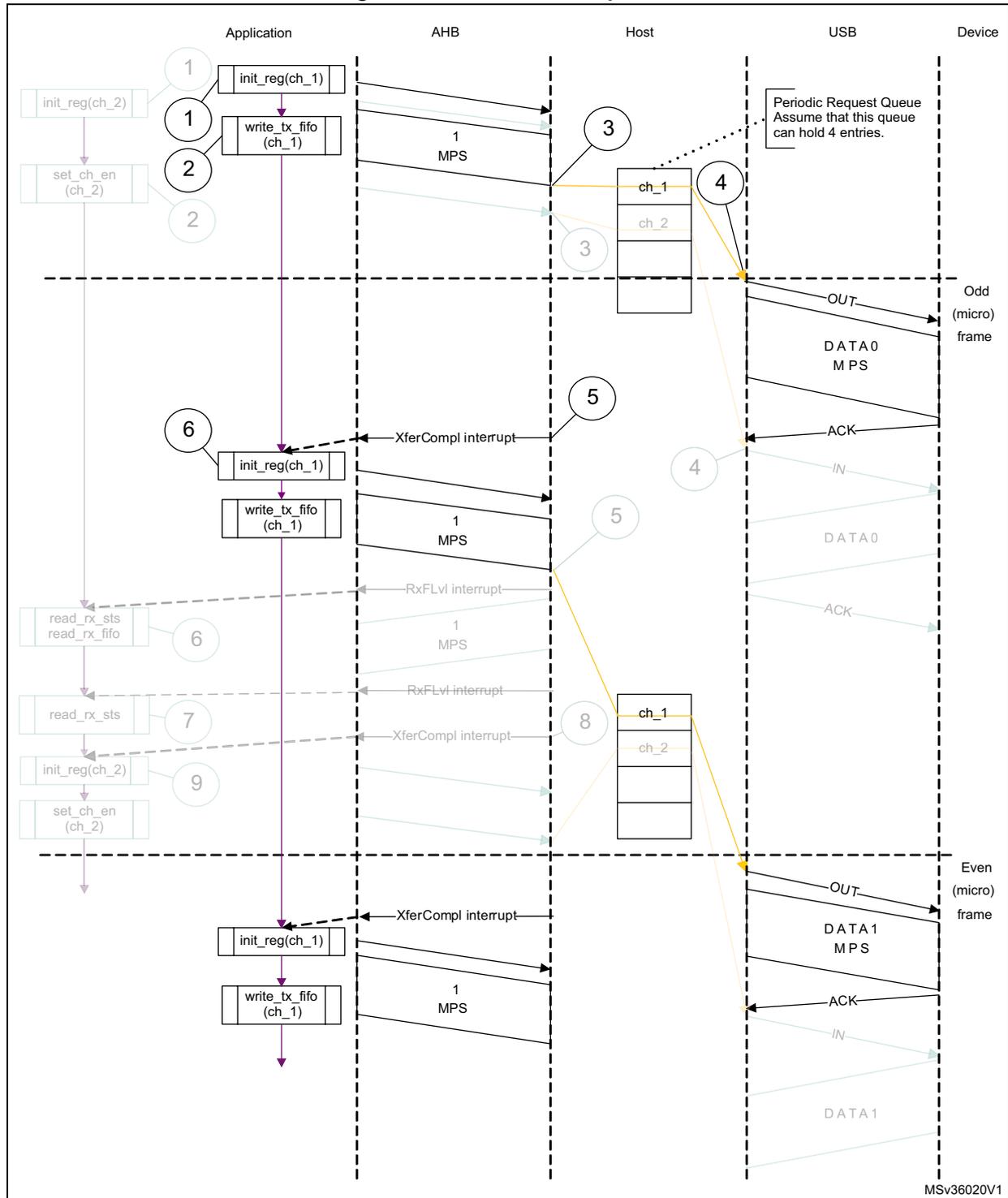

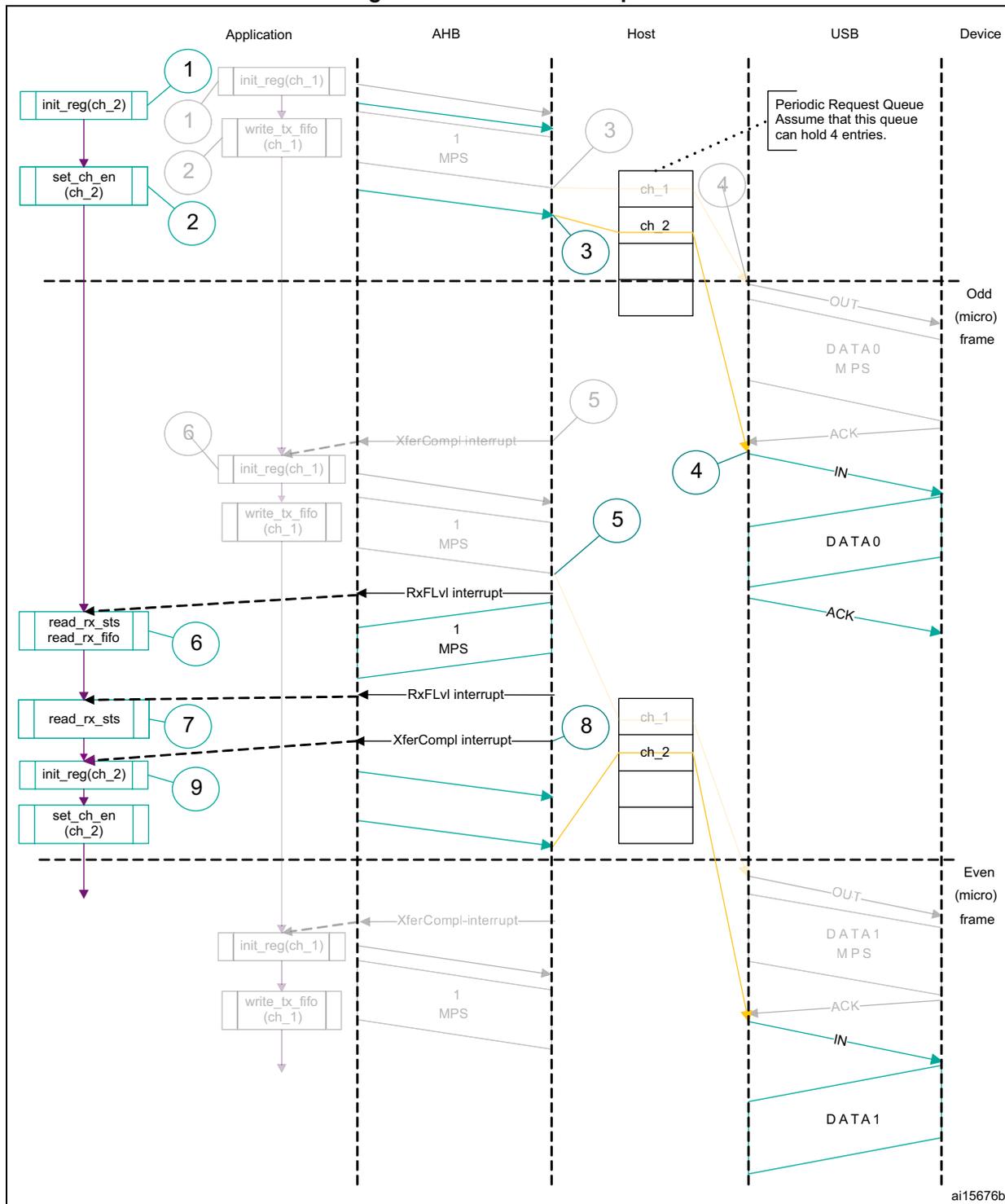

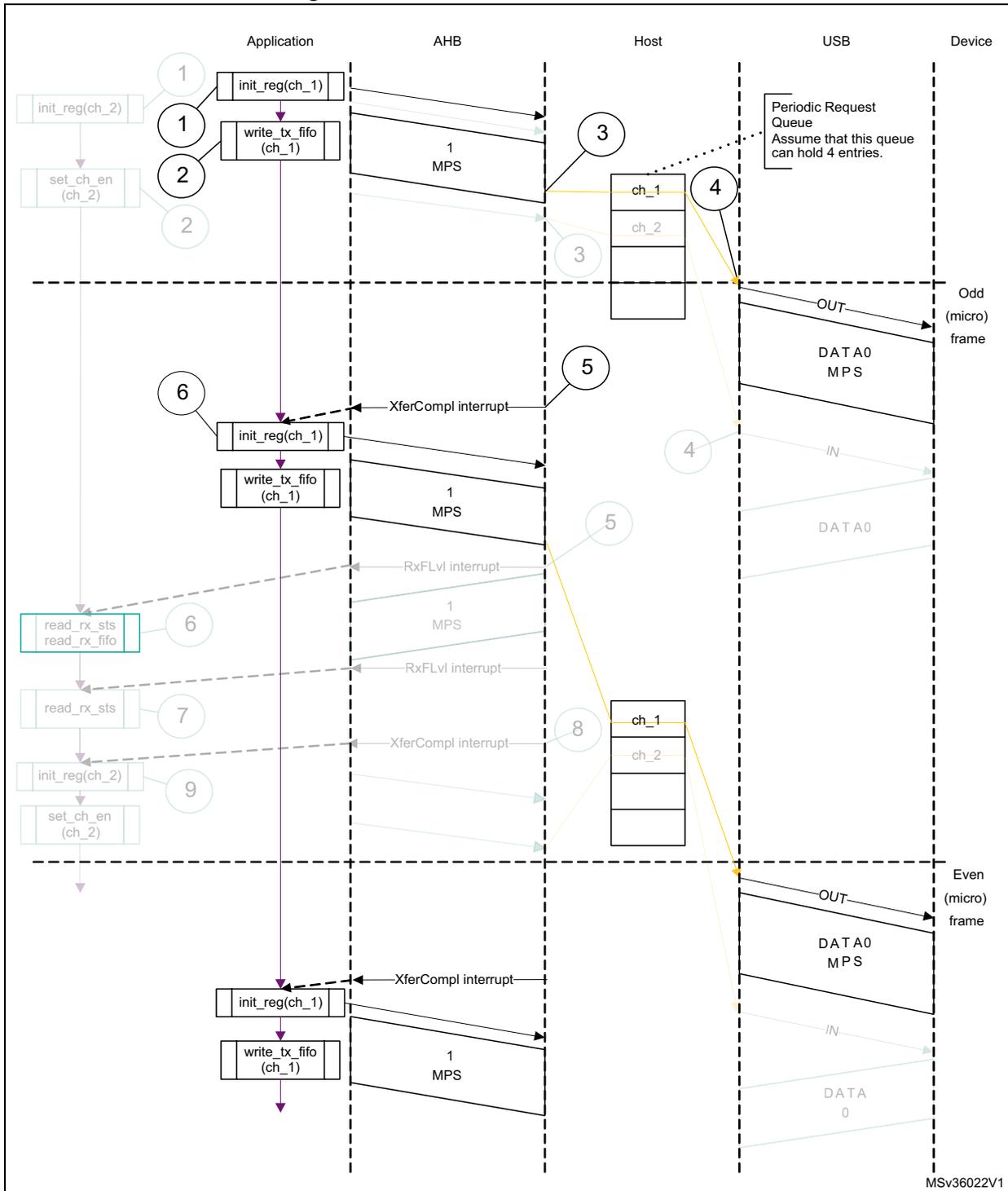

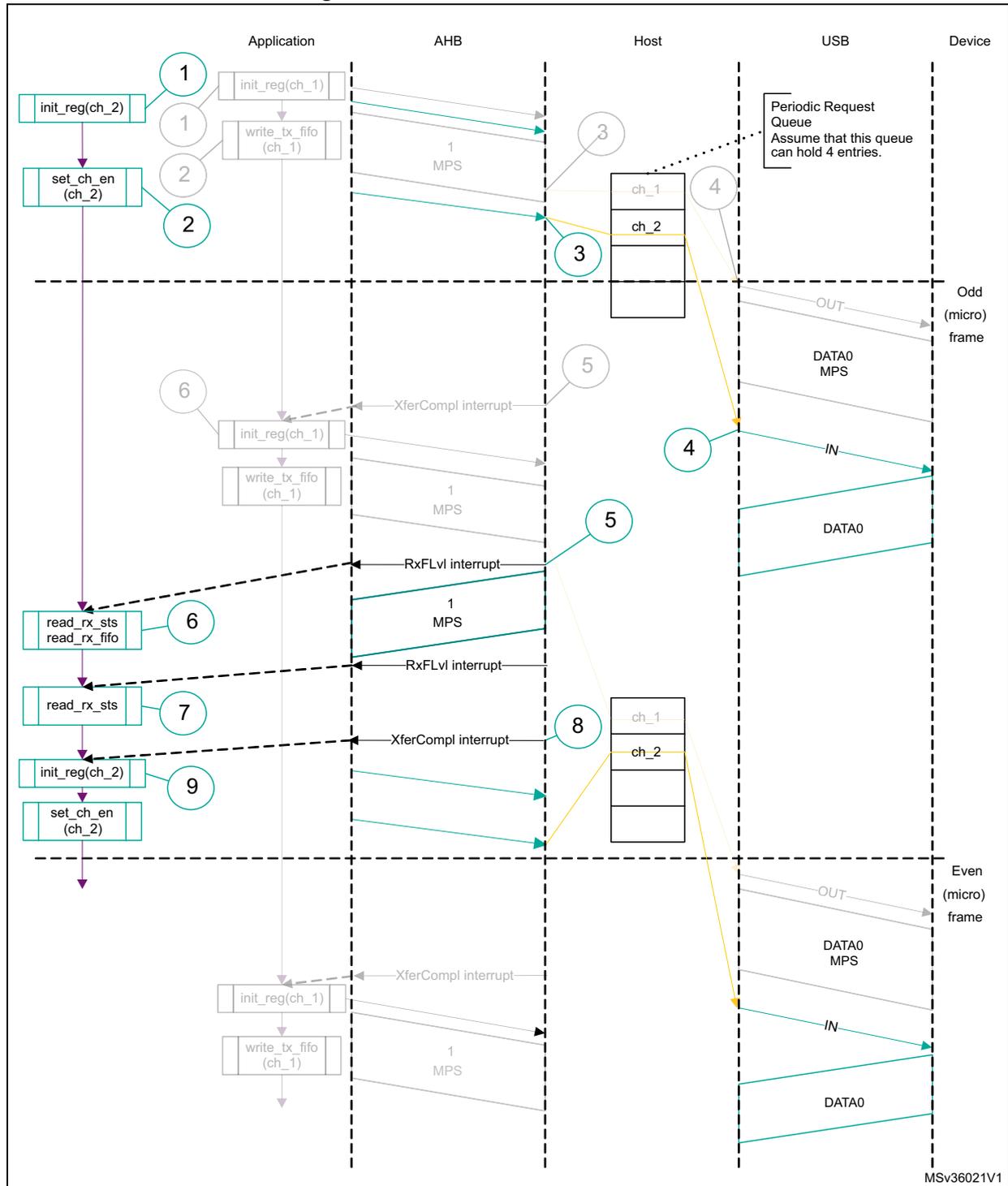

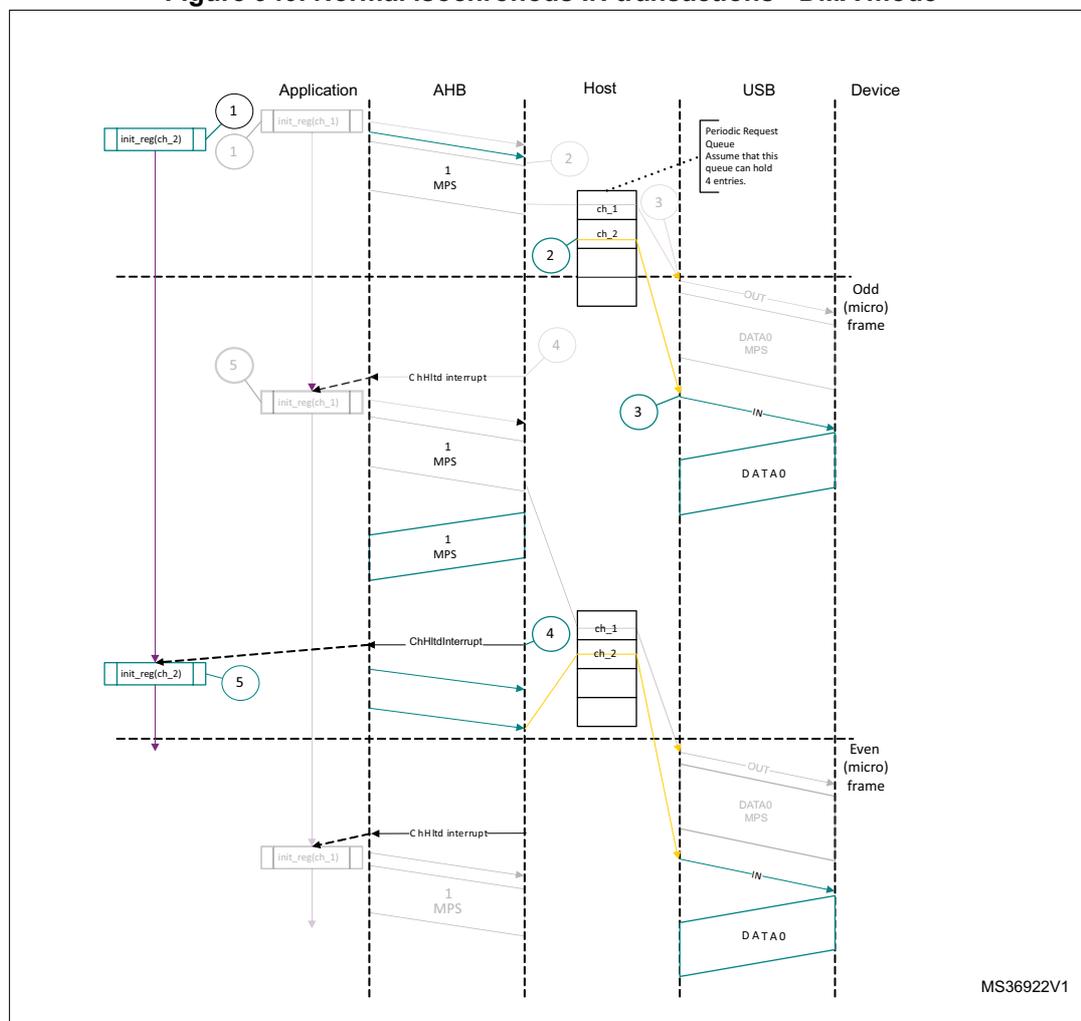

73.7.3 Host scheduler

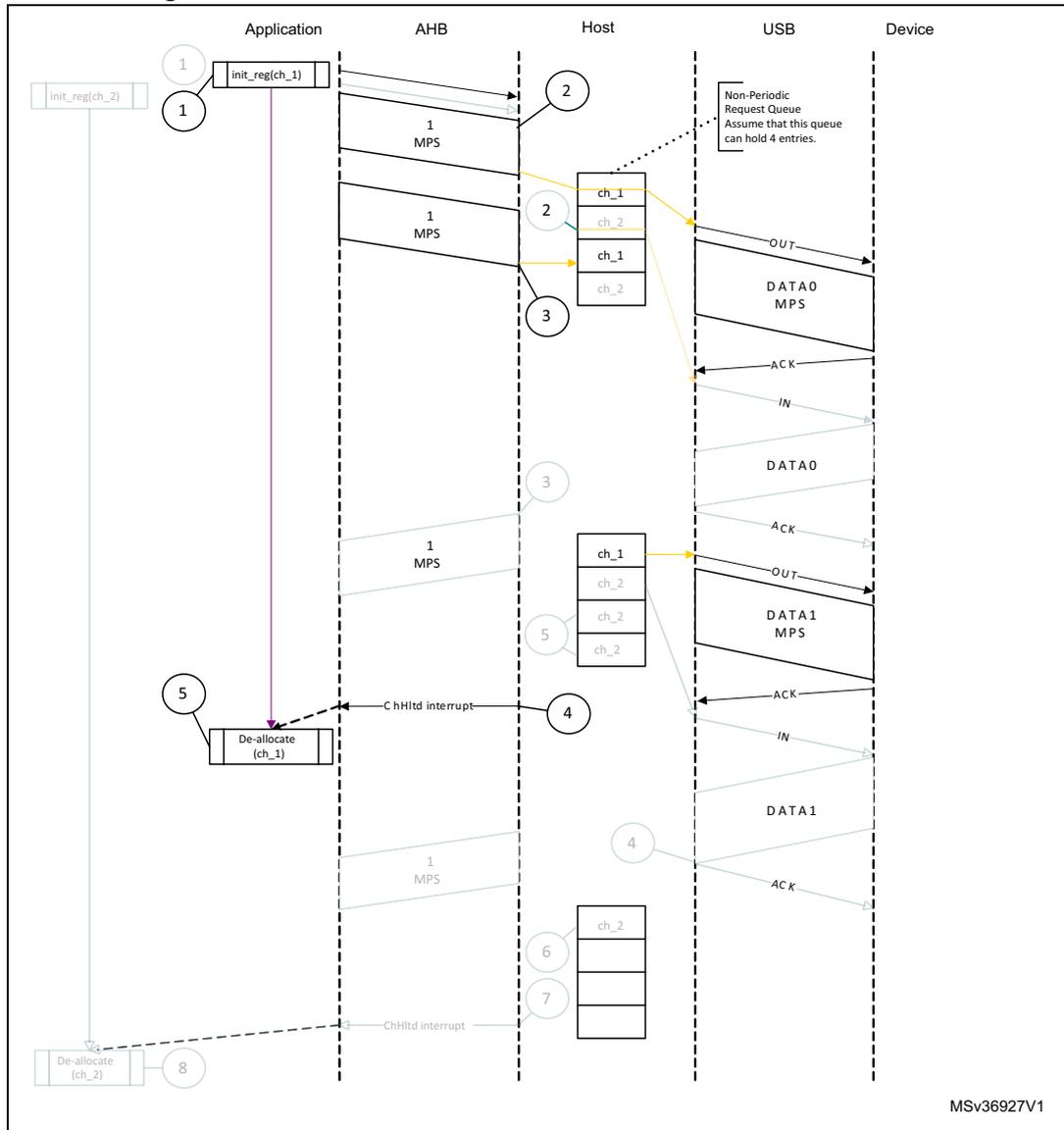

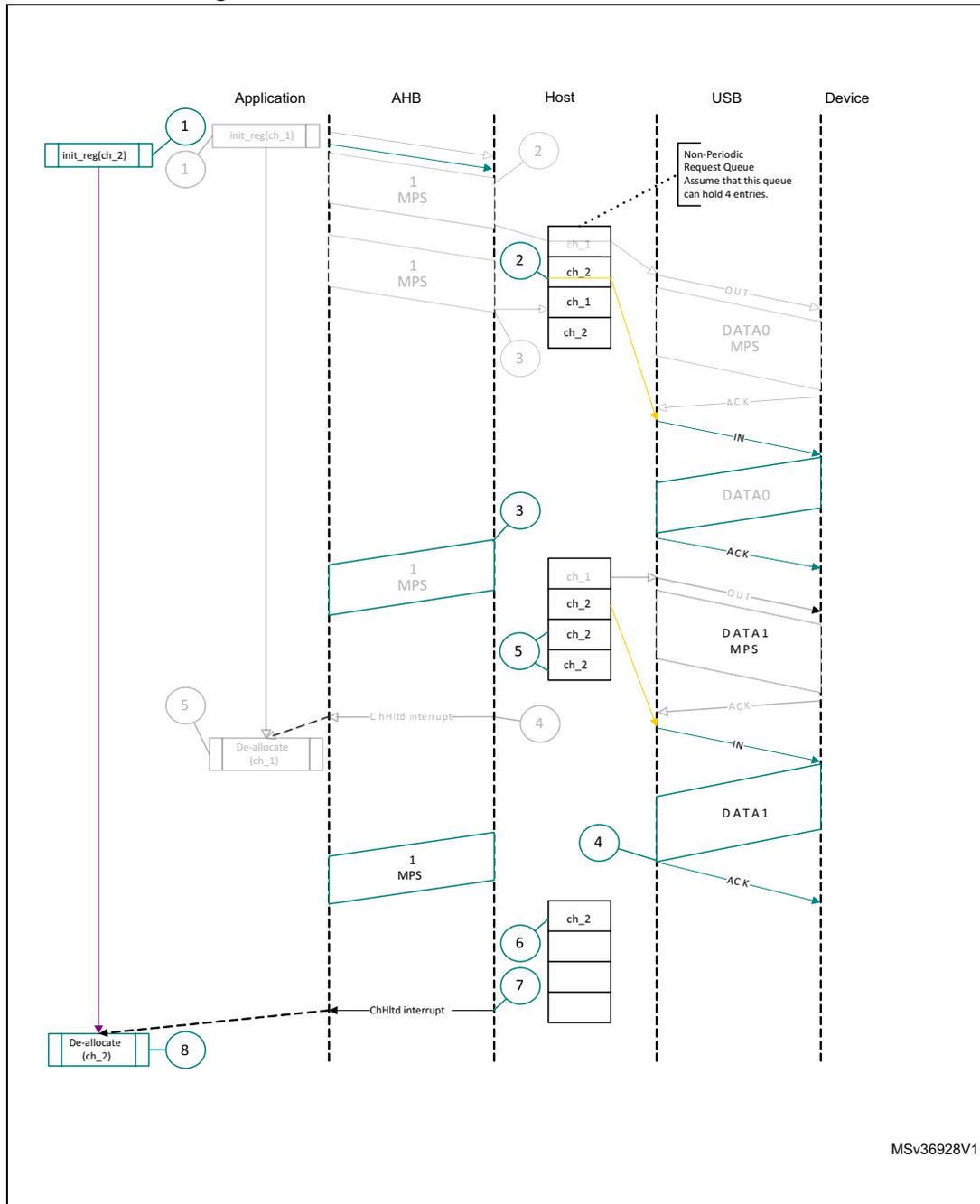

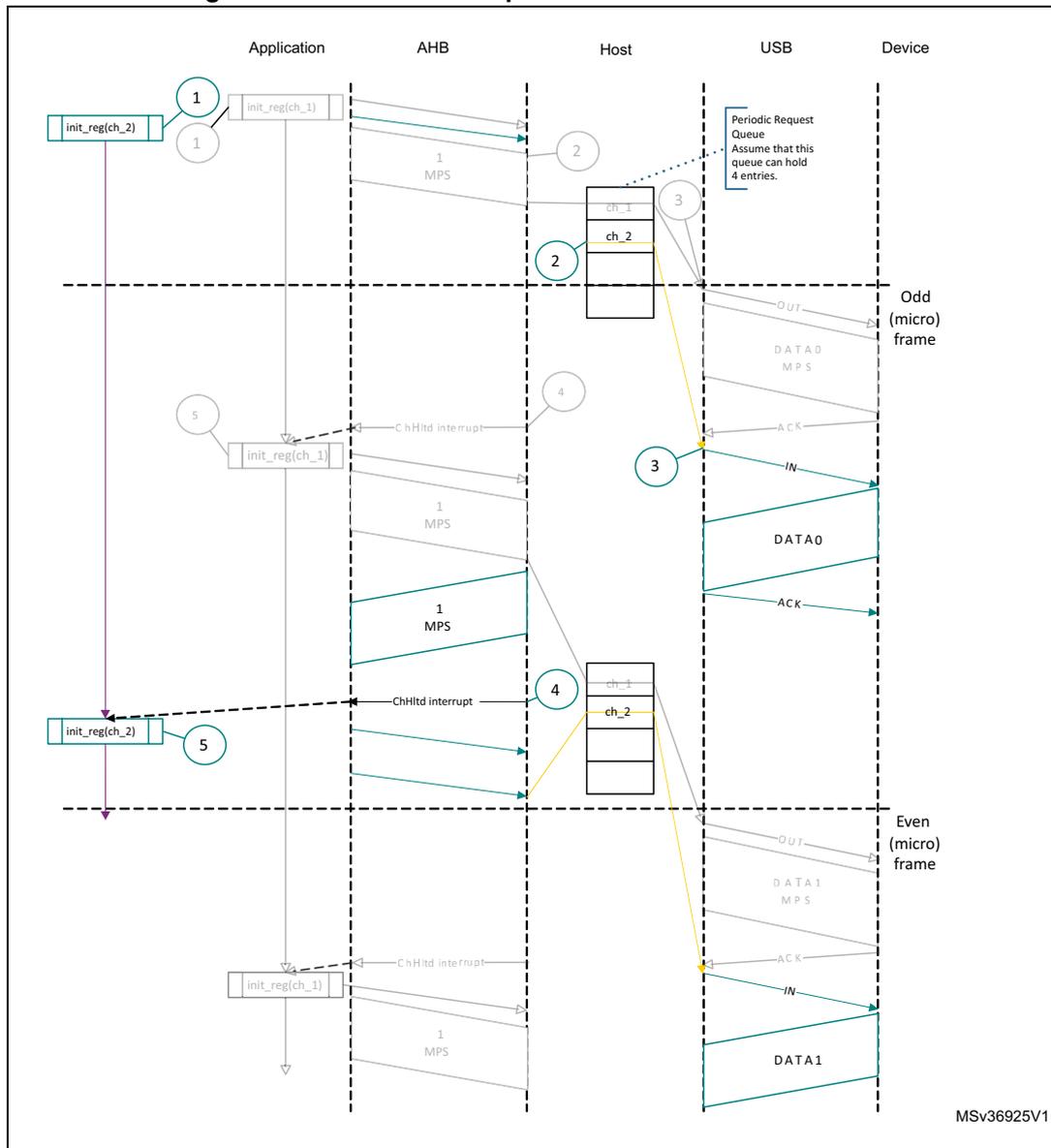

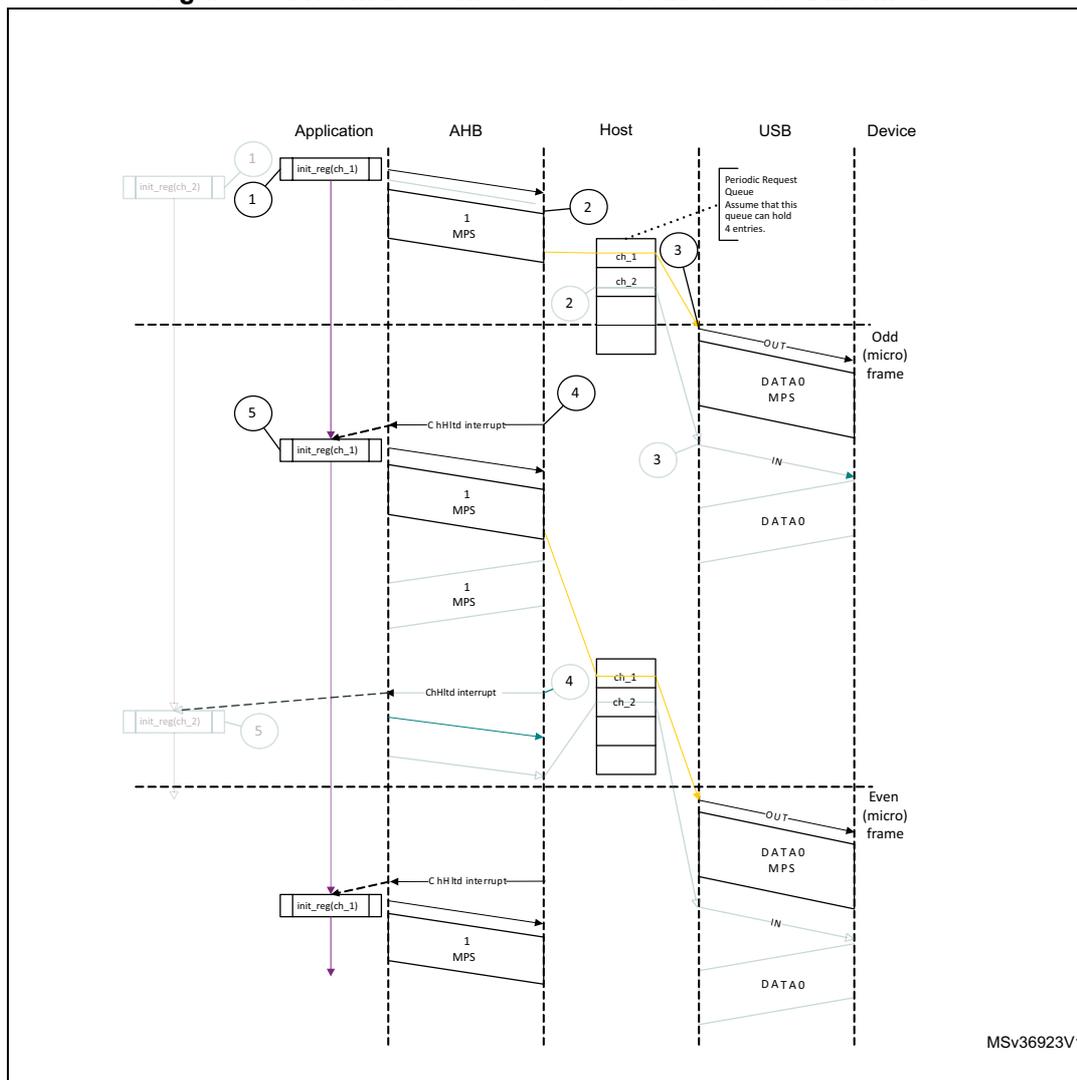

The host core features a built-in hardware scheduler which is able to autonomously re-order and manage the USB transaction requests posted by the application. At the beginning of each frame the host executes the periodic (isochronous and interrupt) transactions first, followed by the nonperiodic (control and bulk) transactions to achieve the higher level of priority granted to the isochronous and interrupt transfer types by the USB specification.

The host processes the USB transactions through request queues (one for periodic and one for nonperiodic). Each request queue can hold up to 8 entries. Each entry represents a pending transaction request from the application, and holds the IN or OUT channel number along with other information to perform a transaction on the USB. The order in which the requests are written to the queue determines the sequence of the transactions on the USB interface.

At the beginning of each frame, the host processes the periodic request queue first, followed by the nonperiodic request queue. The host issues an incomplete periodic transfer interrupt (IPXFR bit in OTG_GINTSTS) if an isochronous or interrupt transaction scheduled for the current frame is still pending at the end of the current frame. The OTG_HS core is fully responsible for the management of the periodic and nonperiodic request queues. The periodic transmit FIFO and queue status register (OTG_HPTXSTS) and nonperiodic transmit FIFO and queue status register (OTG_HNPTXSTS) are read-only registers which can be used by the application to read the status of each request queue. They contain:

- • The number of free entries currently available in the periodic (nonperiodic) request queue (8 max)

- • Free space currently available in the periodic (nonperiodic) Tx FIFO (out-transactions)

- • IN/OUT token, host channel number and other status information.

As request queues can hold a maximum of eight entries each, the application can push to schedule host transactions in advance with respect to the moment they physically reach the SB for a maximum of eight pending periodic transactions plus 8 pending non-periodic transactions.

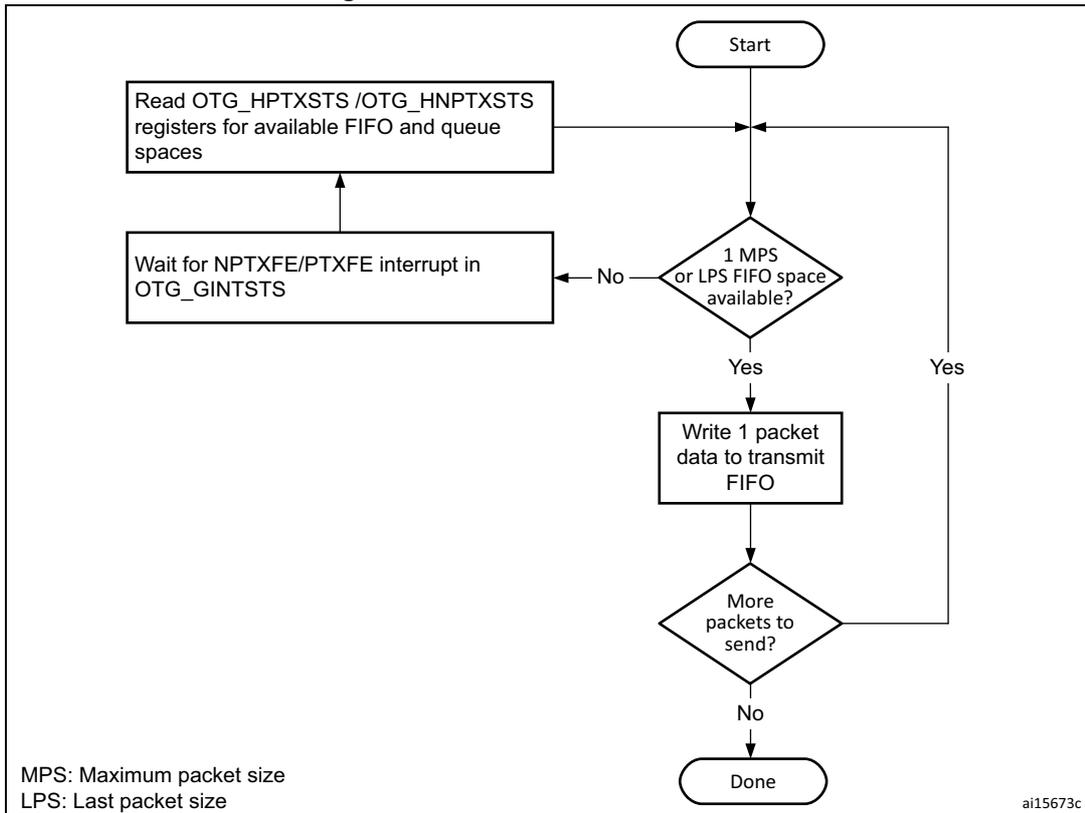

To post a transaction request to the host scheduler (queue) the application must check that there is at least 1 entry available in the periodic (nonperiodic) request queue by reading the

PTXQSAV bits in the OTG_HNPTXSTS register or NPTQXSAV bits in the OTG_HNPTXSTS register.

73.8 OTG_HS SOF trigger

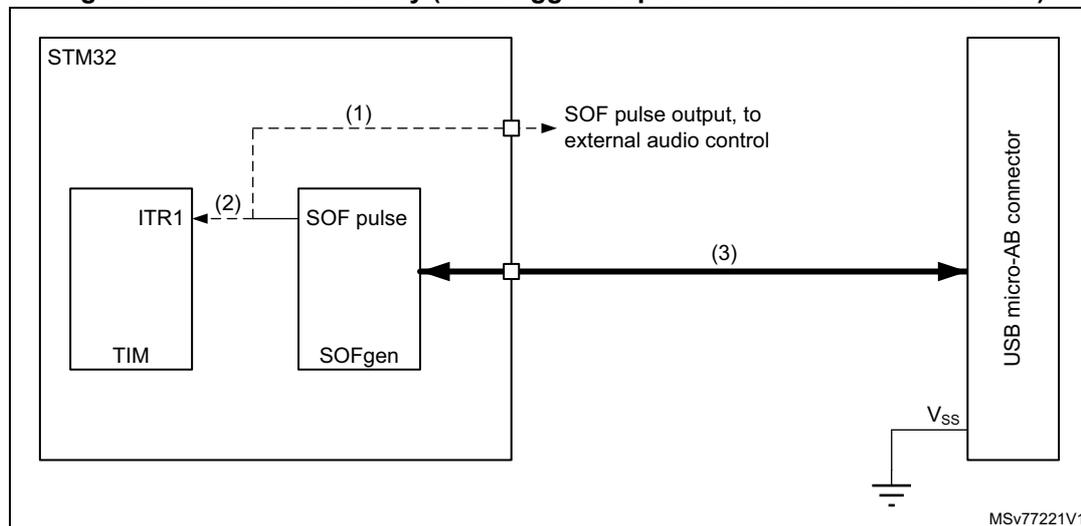

Figure 922. SOF connectivity (SOF trigger output to TIM and ITR1 connection)

The diagram illustrates the internal architecture of the STM32 microcontroller for SOF connectivity. It shows three main components: the STM32 core, the TIM (Timer) block, and the SOFgen (SOF generator) block. The connections are as follows:

- (1) A dashed line representing the SOF pulse output from the STM32 core to an external audio control.

- (2) A solid line representing the SOF pulse output from the SOFgen block to the ITR1 (Input Trigger) of the TIM block.

- (3) A solid line representing the SOF pulse input from the USB micro-AB connector to the SOFgen block.

The USB micro-AB connector is shown with a V SS pin connected to ground.

- 1. SOF pulse output is available on this product.

- 2. SOF timer connection is available on this product.

- 3. See Table 763: OTG_HS input/output pins for full pin list.

The OTG_HS core provides means to monitor, track and configure SOF framing in the host and peripheral, as well as an SOF pulse output connectivity feature.

Such utilities are especially useful for adaptive audio clock generation techniques, where the audio peripheral needs to synchronize to the isochronous stream provided by the PC, or the host needs to trim its framing rate according to the requirements of the audio peripheral.

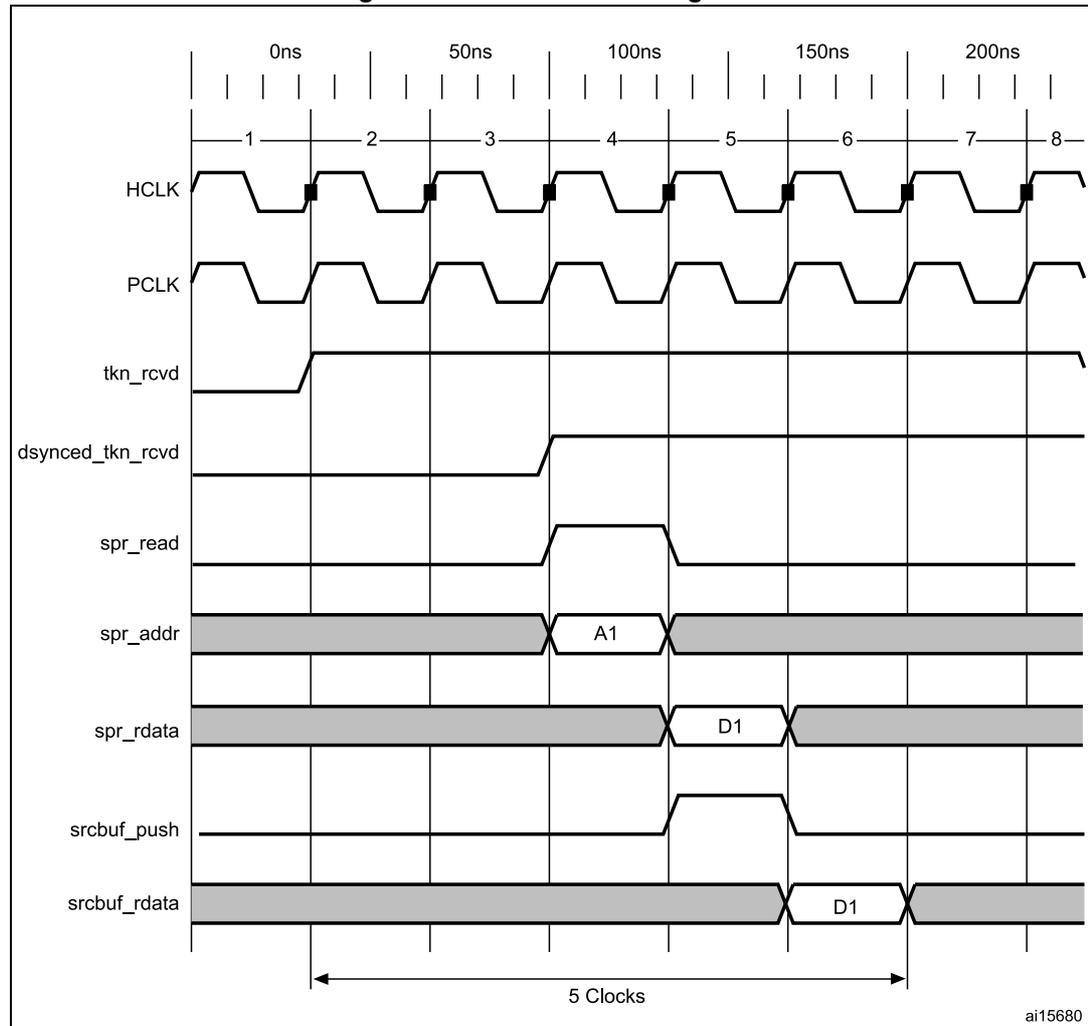

73.8.1 Host SOFs

In host mode the number of PHY clocks occurring between the generation of two consecutive SOF (HS/FS) or Keep-alive (LS) tokens is programmable in the host frame interval register (HFIR), thus providing application control over the SOF framing period. An interrupt is generated at any start of frame (SOF bit in OTG_GINTSTS). The current frame number and the time remaining until the next SOF are tracked in the host frame number register (HFNUM).

A SOF pulse signal, is generated at any SOF starting token and with a width of 20 HCLK cycles. The SOF pulse is also internally connected to the input trigger of the timer, so that the input capture feature, the output compare feature and the timer can be triggered by the SOF pulse.

73.8.2 Peripheral SOFs

In device mode, the start of frame interrupt is generated each time an SOF token is received on the USB (SOF bit in OTG_GINTSTS). The corresponding frame number can be read from the device status register (FNSOF bit in OTG_DSTS). A SOF pulse signal with a width

of 20 HCLK cycles is also generated. The SOF pulse signal is also internally connected to the TIM input trigger, so that the input capture feature, the output compare feature and the timer can be triggered by the SOF pulse.

The end of periodic frame interrupt (OTG_GINTSTS/EOPF) is used to notify the application when 80%, 85%, 90% or 95% of the time frame interval elapsed depending on the periodic frame interval field in the device configuration register (PFIVL bit in OTG_DCFG). This feature can be used to determine if all of the isochronous traffic for that frame is complete.

73.9 OTG_HS low-power modes

Table 765 below defines the STM32 low power modes and their compatibility with the OTG.

Table 765. Compatibility of STM32 low power modes with the OTG

| Mode | Description | USB compatibility |

|---|---|---|

| Run | MCU fully active | Required when USB not in suspend state. |

| Sleep | USB suspend exit causes the device to exit Sleep mode. Peripheral registers content is kept. | Available while USB is in suspend state. |

| Stop | USB suspend exit causes the device to exit Stop mode. Peripheral registers content is kept (1) . | Available while USB is in suspend state. |

| Standby | Powered-down. The peripheral must be reinitialized after exiting Standby mode. | Not compatible with USB applications. |

- 1. Within Stop mode there are different possible settings. Some restrictions may also exist, refer to Section 10: Power control (PWR) to understand which (if any) restrictions apply when using OTG.

The following bits and procedures reduce power consumption.

The power consumption of the OTG PHY is controlled by the following bit in the general core configuration register:

- •

\(

V_{BUS}

\)

detection enable (OTG_GCCFG/VBDEN)

It switches on/off the \( V_{BUS} \) sensing comparators associated with OTG operations

Power reduction techniques are available while in the USB suspended state, when the USB session is not yet valid or the device is disconnected.

- • Stop PHY clock (STPPCLK bit in OTG_PCGCTL)

When setting the stop PHY clock bit in the clock gating control register, most of the transceiver is disabled, and only the part in charge of detecting the asynchronous resume or remote wake-up event is kept alive. - • Gate HCLK (GATEHCLK bit in OTG_PCGCTL)

When setting the Gate HCLK bit in the clock gating control register, most of the system clock domain internal to the OTG_HS core is switched off by clock gating. Only the register read and write interface is kept alive. The dynamic power consumption due to the USB clock switching activity is cut even if the system clock is kept running by the application for other purposes. - • USB system stop

When the OTG_HS is in the USB suspended state, the application may decide to drastically reduce the overall power consumption by a complete shut down of all the

clock sources in the system. USB System Stop is activated by first setting the Stop PHY clock bit and then configuring the system deep sleep mode in the power control system module (PWR).

The OTG_HS core automatically reactivates both system and USB clocks by asynchronous detection of remote wake-up (as an host) or resume (as a device) signaling on the USB.

To save dynamic power, the USB data FIFO is clocked only when accessed by the OTG_HS core.

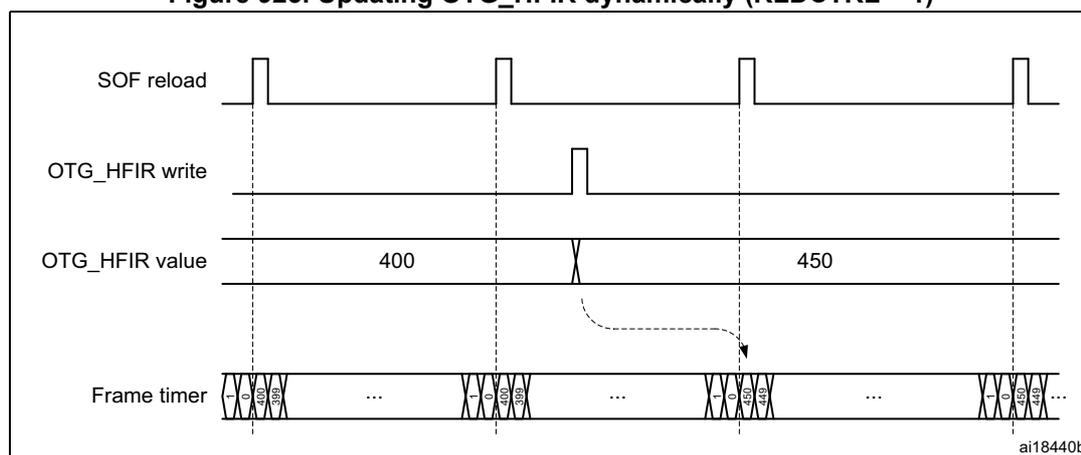

73.10 OTG_HS Dynamic update of the OTG_HFIR register

The USB core embeds a dynamic trimming capability of micro-SOF framing period in host mode allowing to synchronize an external device with the micro-SOF frames.

When the OTG_HFIR register is changed within a current micro-SOF frame, the SOF period correction is applied in the next frame as described in Figure 923 .

For a dynamic update, it is required to set RLDCTRL=1.

Figure 923. Updating OTG_HFIR dynamically (RLDCTRL = 1)

The figure is a timing diagram illustrating the dynamic update of the OTG_HFIR register. It consists of four horizontal signal lines. The top line, 'SOF reload', shows periodic pulses. The second line, 'OTG_HFIR write', shows a pulse that occurs during a SOF reload. The third line, 'OTG_HFIR value', shows a change from 400 to 450. The bottom line, 'Frame timer', shows a series of pulses, with the period between pulses decreasing after the OTG_HFIR value change. A dashed arrow indicates the transition from the old value (400) to the new value (450) in the OTG_HFIR register. The diagram is labeled ai18440b.

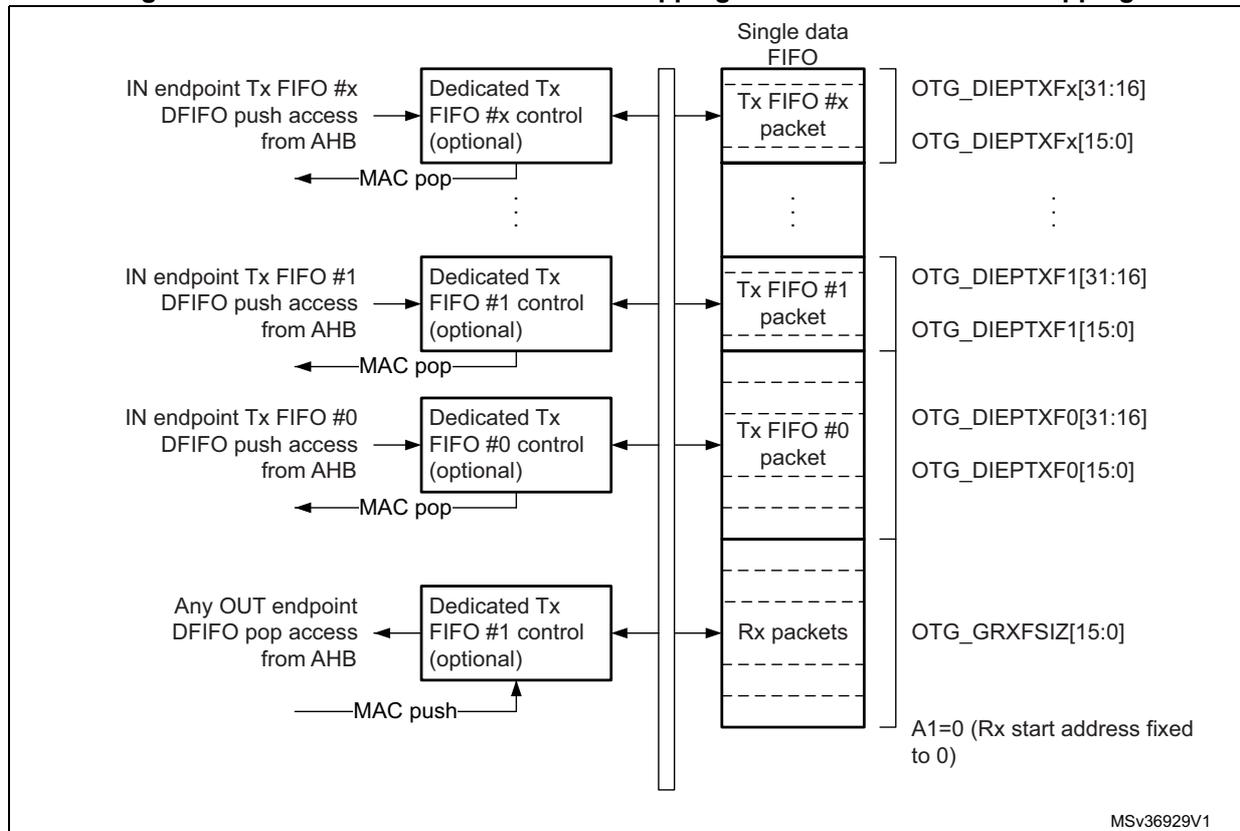

73.11 OTG_HS data FIFOs

The USB system features 4 Kbytes of dedicated RAM with a sophisticated FIFO control mechanism. The packet FIFO controller module in the OTG_HS core organizes RAM space into Tx FIFOs into which the application pushes the data to be temporarily stored before the USB transmission, and into a single Rx FIFO where the data received from the USB are temporarily stored before retrieval (popped) by the application. The number of instructed FIFOs and how these are organized inside the RAM depends on the device's role. In peripheral mode an additional Tx FIFO is instructed for each active IN endpoint. Any FIFO size is software configured to better meet the application requirements.

73.11.1 Peripheral FIFO architecture

Figure 924. Device-mode FIFO address mapping and AHB FIFO access mapping

The diagram illustrates the FIFO architecture for device mode. On the left, IN endpoint Tx FIFOs are shown. IN endpoint Tx FIFO #x, IN endpoint Tx FIFO #1, and IN endpoint Tx FIFO #0 each have a 'Dedicated Tx FIFO #x control (optional)' block. These are accessed via 'DFIFO push access from AHB' and 'MAC pop'. On the right, a 'Single data FIFO' contains 'Tx FIFO #x packet', 'Tx FIFO #1 packet', and 'Tx FIFO #0 packet'. These map to OTG registers: OTG_DIEPTXFx[31:16], OTG_DIEPTXFx[15:0], OTG_DIEPTXF1[31:16], OTG_DIEPTXF1[15:0], OTG_DIEPTXF0[31:16], and OTG_DIEPTXF0[15:0]. Below the Tx FIFOs is a section for 'Rx packets' which maps to OTG_GRXFSIZ[15:0]. This section is accessed via 'Dedicated Tx FIFO #1 control (optional)' with 'DFIFO pop access from AHB' and 'MAC push'. A note indicates 'A1=0 (Rx start address fixed to 0)'. The diagram is labeled MSv36929V1.

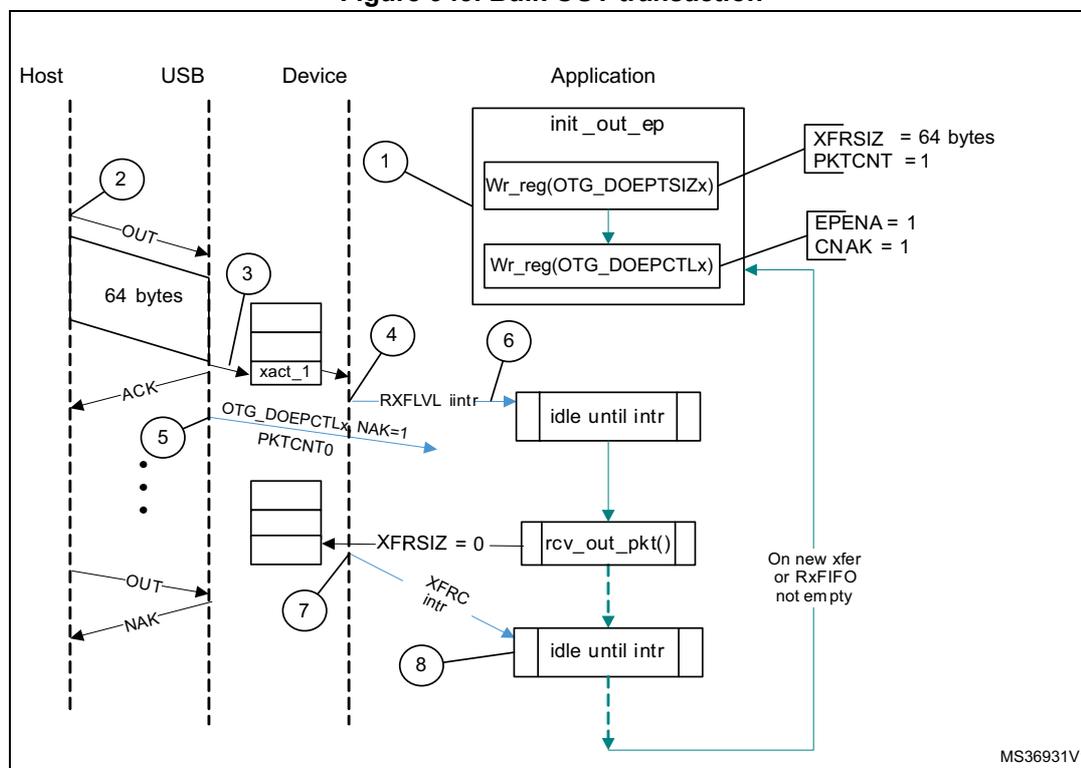

Peripheral Rx FIFO

The OTG peripheral uses a single receive FIFO that receives the data directed to all OUT endpoints. Received packets are stacked back-to-back until free space is available in the Rx FIFO. The status of the received packet (which contains the OUT endpoint destination number, the byte count, the data PID and the validity of the received data) is also stored by the core on top of the data payload. When no more space is available, host transactions are NACKed and an interrupt is received on the addressed endpoint. The size of the receive FIFO is configured in the receive FIFO size register (OTG_GRXFSIZ).

The single receive FIFO architecture makes it more efficient for the USB peripheral to fill in the receive RAM buffer:

- • All OUT endpoints share the same RAM buffer (shared FIFO)

- • The OTG_HS core can fill in the receive FIFO up to the limit for any host sequence of OUT tokens

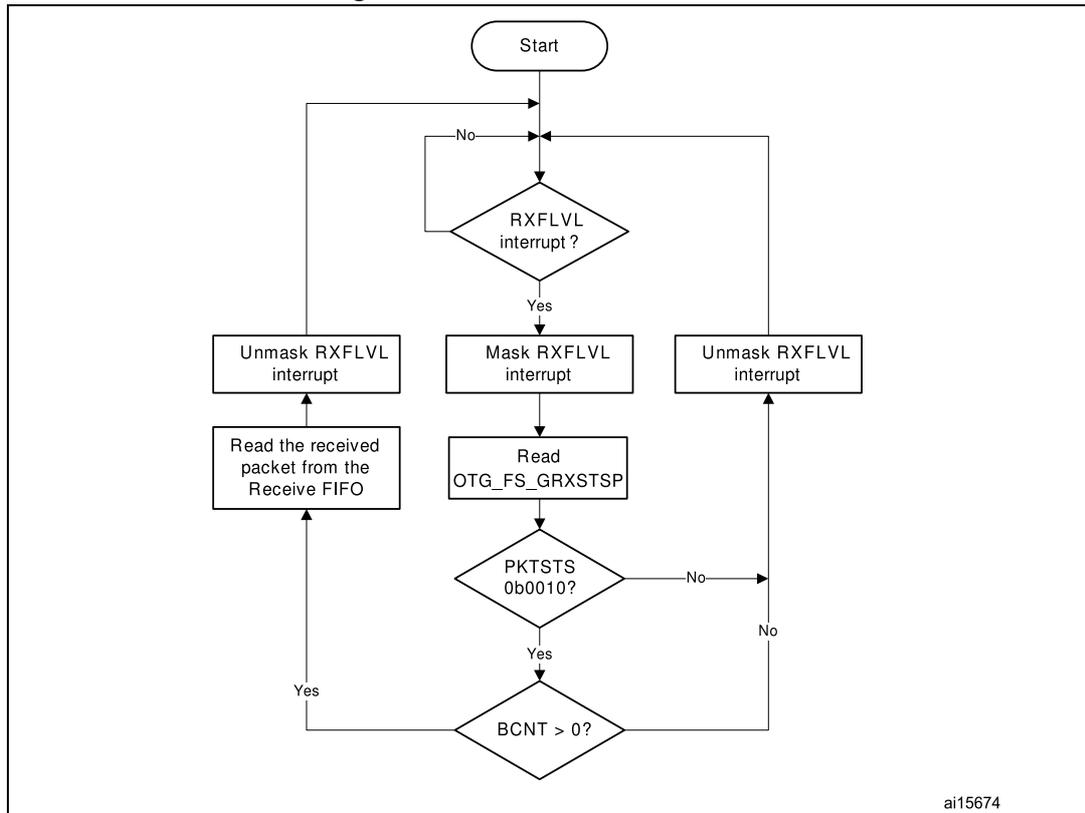

The application keeps receiving the Rx FIFO non-empty interrupt (RXFLVL bit in OTG_GINTSTS) as long as there is at least one packet available for download. It reads the packet information from the receive status read and pop register (OTG_GRXSTSP) and finally pops data off the receive FIFO by reading from the endpoint-related pop address.

Peripheral Tx FIFOs

The core has a dedicated FIFO for each IN endpoint. The application configures FIFO sizes by writing the endpoint 0 transmit FIFO size register (OTG_DIEPTXF0) for IN endpoint0 and the device IN endpoint transmit FIFOx registers (OTG_DIEPTXFx) for IN endpoint-x.

73.11.2 Host FIFO architecture

Figure 925. Host-mode FIFO address mapping and AHB FIFO access mapping

![Diagram of Host-mode FIFO address mapping and AHB FIFO access mapping. It shows a 'Single data FIFO' divided into three sections: 'Periodic Tx packets', 'Non-periodic Tx packets', and 'Rx packets'. On the left, 'Any periodic channel DFIFO push access from AHB' connects to 'Periodic Tx FIFO control (optional)', which connects to the 'Periodic Tx packets' section. 'Any non-periodic channel DFIFO push access from AHB' connects to 'Non-periodic Tx FIFO control', which connects to the 'Non-periodic Tx packets' section. 'Any channel DFIFO pop access from AHB' connects to 'Rx FIFO control', which connects to the 'Rx packets' section. 'MAC pop' arrows point from the control blocks to the AHB access. 'MAC push' arrows point from the AHB access to the control blocks. On the right, size registers are listed: OTG_HPTXFSIZ[31:16] and OTG_HPTXFSIZ[15:0] for periodic tx, OTG_HNPTXFSIZ[31:16] and OTG_HNPTXFSIZ[15:0] for non-periodic tx, and OTG_GRXFSIZ[15:0] for rx. A note indicates 'Rx start address fixed to 0 A1=0'. The diagram is labeled MSv36930V1.](/RM0456-STM32U5/8b22adac436d3af06de9d2700b3e40bd_img.jpg)

Host Rx FIFO

The host uses one receiver FIFO for all periodic and nonperiodic transactions. The FIFO is used as a receive buffer to hold the received data (payload of the received packet) from the USB until it is transferred to the system memory. Packets received from any remote IN endpoint are stacked back-to-back until free space is available. The status of each received packet with the host channel destination, byte count, data PID and validity of the received data are also stored into the FIFO. The size of the receive FIFO is configured in the receive FIFO size register (OTG_GRXFSIZ).

The single receive FIFO architecture makes it highly efficient for the USB host to fill in the receive data buffer:

- • All IN configured host channels share the same RAM buffer (shared FIFO)

- • The OTG_HS core can fill in the receive FIFO up to the limit for any sequence of IN tokens driven by the host software

The application receives the Rx FIFO not-empty interrupt as long as there is at least one packet available for download. It reads the packet information from the receive status read and pop register and finally pops the data off the receive FIFO.

Host Tx FIFOs

The host uses one transmit FIFO for all non-periodic (control and bulk) OUT transactions and one transmit FIFO for all periodic (isochronous and interrupt) OUT transactions. FIFOs are used as transmit buffers to hold the data (payload of the transmit packet) to be transmitted over the USB. The size of the periodic (nonperiodic) Tx FIFO is configured in the host periodic (nonperiodic) transmit FIFO size OTG_HPTXFSIZ / OTG_HNPTXFSIZ register.

The two Tx FIFO implementation derives from the higher priority granted to the periodic type of traffic over the USB frame. At the beginning of each frame, the built-in host scheduler processes the periodic request queue first, followed by the nonperiodic request queue.

The two transmit FIFO architecture provides the USB host with separate optimization for periodic and nonperiodic transmit data buffer management:

- • All host channels configured to support periodic (nonperiodic) transactions in the OUT direction share the same RAM buffer (shared FIFOs)

- • The OTG_HS core can fill in the periodic (nonperiodic) transmit FIFO up to the limit for any sequence of OUT tokens driven by the host software

The OTG_HS core issues the periodic Tx FIFO empty interrupt (PTXFE bit in OTG_GINTSTS) as long as the periodic Tx FIFO is half or completely empty, depending on the value of the periodic Tx FIFO empty level bit in the AHB configuration register (PTXFELVL bit in OTG_GAHBCFG). The application can push the transmission data in advance as long as free space is available in both the periodic Tx FIFO and the periodic request queue. The host periodic transmit FIFO and queue status register (OTG_HPTXSTS) can be read to know how much space is available in both.

OTG_HS core issues the non periodic Tx FIFO empty interrupt (NPTXFE bit in OTG_GINTSTS) as long as the nonperiodic Tx FIFO is half or completely empty depending on the non periodic Tx FIFO empty level bit in the AHB configuration register (TXFELVL bit in OTG_GAHBCFG). The application can push the transmission data as long as free space is available in both the nonperiodic Tx FIFO and nonperiodic request queue. The host nonperiodic transmit FIFO and queue status register (OTG_HNPTXSTS) can be read to know how much space is available in both.

73.11.3 FIFO RAM allocation

Device mode

Receive FIFO RAM allocation: the application must allocate RAM for SETUP packets:

- • 10 locations must be reserved in the receive FIFO to receive SETUP packets on control endpoint. The core does not use these locations, which are reserved for SETUP packets, to write any other data.

- • One location is to be allocated for Global OUT NAK.

- • Status information is written to the FIFO along with each received packet. Therefore, a minimum space of \( (\text{largest packet size} / 4) + 1 \) must be allocated to receive packets. If multiple isochronous endpoints are enabled, then at least two \( (\text{largest packet size} / 4) + 1 \) spaces must be allocated to receive back-to-back packets. Typically, two \( (\text{largest packet size} / 4) + 1 \) spaces are recommended so that when the previous packet is being transferred to the CPU, the USB can receive the subsequent packet.

- • Along with the last packet for each endpoint, transfer complete status information is also pushed to the FIFO. One location for each OUT endpoint is recommended.

Device RxFIFO =

\( (5 * \text{number of control endpoints} + 8) + ((\text{largest USB packet used} / 4) + 1 \text{ for status information}) + (2 * \text{number of OUT endpoints}) + 1 \text{ for Global NAK} \)

Example: The MPS is 1,024 bytes for a periodic USB packet and 512 bytes for a non-periodic USB packet. There are three OUT endpoints, three IN endpoints, one control endpoint, and three host channels.

Device RxFIFO = \( (5 * 1 + 8) + ((1,024 / 4) + 1) + (2 * 4) + 1 = 279 \)

Transmit FIFO RAM allocation:

the minimum RAM space required for each IN endpoint

Transmit FIFO is the maximum packet size for that particular IN endpoint.

Note: More space allocated in the transmit IN endpoint FIFO results in better performance on the USB.

Host mode

Receive FIFO RAM allocation:

Status information is written to the FIFO along with each received packet. Therefore, a minimum space of \( (\text{largest packet size} / 4) + 1 \) must be allocated to receive packets. If multiple isochronous channels are enabled, then at least two \( (\text{largest packet size} / 4) + 1 \) spaces must be allocated to receive back-to-back packets. Typically, two \( (\text{largest packet size} / 4) + 1 \) spaces are recommended so that when the previous packet is being transferred to the CPU, the USB can receive the subsequent packet.

Along with the last packet in the host channel, transfer complete status information is also pushed to the FIFO. So one location must be allocated for this.

Host RxFIFO = \( (\text{largest USB packet used} / 4) + 1 \text{ for status information} + 1 \text{ transfer complete} \)

Example: Host RxFIFO = \( ((1,024 / 4) + 1) + 1 = 258 \)

Transmit FIFO RAM allocation:

The minimum amount of RAM required for the host Non-periodic Transmit FIFO is the largest maximum packet size among all supported non-periodic OUT channels.

Typically, two largest packet sizes worth of space is recommended, so that when the current packet is under transfer to the USB, the CPU can get the next packet.

Non-Periodic TxFIFO = largest non-periodic USB packet used / 4

Example: Non-Periodic TxFIFO = \( (512 / 4) = 128 \)

The minimum amount of RAM required for host periodic Transmit FIFO is the largest maximum packet size out of all the supported periodic OUT channels. If there is at least one isochronous OUT endpoint, then the space must be at least two times the maximum packet size of that channel.

Host Periodic TxFIFO = largest periodic USB packet used / 4

Example: Host Periodic TxFIFO = \( (1,024 / 4) = 256 \)

Note: More space allocated in the Transmit Non-periodic FIFO results in better performance on the USB.

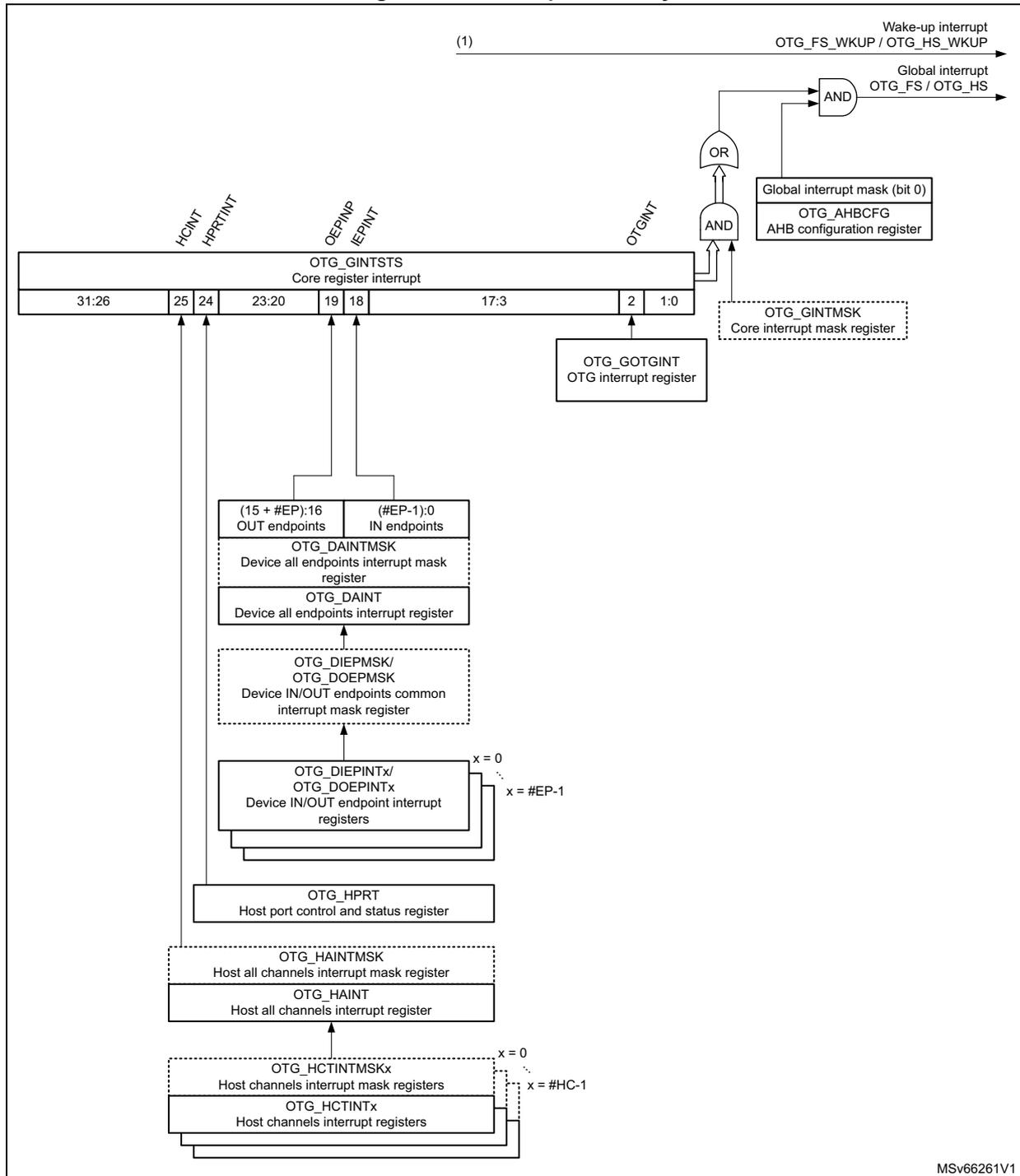

73.12 OTG_HS interrupts

When the OTG_HS controller is operating in one mode, either device or host, the application must not access registers from the other mode. If an illegal access occurs, a mode mismatch interrupt is generated and reflected in the core interrupt register (MMIS bit in the OTG_GINTSTS register). When the core switches from one mode to the other, the registers in the new mode of operation must be reprogrammed as they would be after a power-on reset.

Figure 926 shows the interrupt hierarchy.

Figure 926. Interrupt hierarchy

The diagram illustrates the interrupt hierarchy for the OTG_HS USB controller. At the top, the OTG_GINTSTS (Core register interrupt) is shown with its bit fields: 31:26, 25 (HCINT), 24 (HPRTINT), 23:20, 19 (OEPINT), 18 (IEPINT), 17:3, 2 (OTGINT), and 1:0. Below this, the hierarchy branches into Host and Device interrupt paths.

Host Path: The HCINT (bit 25) is generated from the OTG_HAINT (Host all channels interrupt register). The OTG_HAINT is derived from a stack of OTG_HCTINTx (Host channels interrupt registers) for \( x = 0 \) to \( x = \#HC-1 \) , which are masked by OTG_HCTINTMSKx (Host channels interrupt mask registers). These are further masked by the OTG_HAINTMSK (Host all channels interrupt mask register). The HPRTINT (bit 24) is generated from the OTG_HPRT (Host port control and status register).

Device Path: The OEPINT (bit 19) and IEPINT (bit 18) are generated from the OTG_DAINT (Device all endpoints interrupt register). The OTG_DAINT is derived from a stack of OTG_DIEPINTx/OTG_DOEPINTx (Device IN/OUT endpoint interrupt registers) for \( x = 0 \) to \( x = \#EP-1 \) , which are masked by OTG_DIEPMSK/OTG_DOEPMSK (Device IN/OUT endpoints common interrupt mask register). These are further masked by the OTG_DAINTMSK (Device all endpoints interrupt mask register).

OTG Path: The OTGINT (bit 2) is generated from the OTG_GOTINT (OTG interrupt register).

The signals from OTG_GINTSTS are ANDed with the OTG_GINTMSK (Core interrupt mask register) and then combined via an OR gate. This result is ANDed with the Global interrupt mask (bit 0) from the OTG_AHBCFG (AHB configuration register). The final output is the Global interrupt OTG_FS / OTG_HS . A separate Wake-up interrupt OTG_FS_WKUP / OTG_HS_WKUP is also shown.

1. OTG_HS_WKUP becomes active (high state) when resume condition occurs during L1 SLEEP or L2 SUSPEND states.

73.13 OTG_HS control and status registers

By reading from and writing to the control and status registers (CSRs) through the AHB slave interface, the application controls the OTG_HS controller. These registers are 32 bits wide, and the addresses are 32-bit block aligned. The OTG_HS registers must be accessed by words (32 bits).

CSRs are classified as follows:

- • Core global registers

- • Host-mode registers

- • Host global registers

- • Host port CSRs

- • Host channel-specific registers

- • Device-mode registers

- • Device global registers

- • Device endpoint-specific registers

- • Power and clock-gating registers

- • Data FIFO (DFIFO) access registers

Only the core global, power and clock-gating, data FIFO access, and host port control and status registers can be accessed in both host and device modes. When the OTG_HS controller is operating in one mode, either device or host, the application must not access registers from the other mode. If an illegal access occurs, a mode mismatch interrupt is generated and reflected in the core interrupt register (MMIS bit in the OTG_GINTSTS register). When the core switches from one mode to the other, the registers in the new mode of operation must be reprogrammed as they would be after a power-on reset.

73.13.1 CSR memory map

The host and device mode registers occupy different addresses. All registers are implemented in the AHB clock domain.

Global CSR map

These registers are available in both host and device modes.

Table 766. Core global control and status registers (CSRs)

| Acronym | Address offset | Register name |

|---|---|---|

| OTG_GOTGCTL | 0x000 | Section 73.14.1: OTG control and status register (OTG_GOTGCTL) |

| OTG_GOTGINT | 0x004 | Section 73.14.2: OTG interrupt register (OTG_GOTGINT) |

| OTG_GAHBCFG | 0x008 | Section 73.14.3: OTG AHB configuration register (OTG_GAHBCFG) |

| OTG_GUSBCFG | 0x00C | Section 73.14.4: OTG USB configuration register (OTG_GUSBCFG) |

| OTG_GRSTCTL | 0x010 | Section 73.14.5: OTG reset register (OTG_GRSTCTL) |

| OTG_GINTSTS | 0x014 | Section 73.14.6: OTG core interrupt register [alternate] (OTG_GINTSTS) Section 73.14.7: OTG core interrupt register [alternate] (OTG_GINTSTS) |

Table 766. Core global control and status registers (CSRs) (continued)

1. The general rule is to use OTG_HNPTXFSIZ for host mode and OTG_DIEPTXF0 for device mode.

Host-mode CSR map

These registers must be programmed every time the core changes to host mode.

Table 767. Host-mode control and status registers (CSRs)

| Acronym | Offset address | Register name |

|---|---|---|

| OTG_HCFG | 0x400 | Section 73.14.24: OTG host configuration register (OTG_HCFG) |

| OTG_HFIR | 0x404 | Section 73.14.25: OTG host frame interval register (OTG_HFIR) |

| OTG_HFNUM | 0x408 | Section 73.14.26: OTG host frame number/frame time remaining register (OTG_HFNUM) |

| OTG_HPTXSTS | 0x410 | Section 73.14.27: OTG Host periodic transmit FIFO/queue status register (OTG_HPTXSTS) |

Table 767. Host-mode control and status registers (CSRs) (continued)

| Acronym | Offset address | Register name |

|---|---|---|

| OTG_HAINT | 0x414 | Section 73.14.28: OTG host all channels interrupt register (OTG_HAINT) |

| OTG_HAINTMSK | 0x418 | Section 73.14.29: OTG host all channels interrupt mask register (OTG_HAINTMSK) |

| OTG_HPRT | 0x440 | Section 73.14.30: OTG host port control and status register (OTG_HPRT) |

| OTG_HCCHARx | 0x500 0x520 .... 0x6E0 | Section 73.14.31: OTG host channel x characteristics register (OTG_HCCHARx) |

| OTG_HCSPLTx | 0x504 0x524 .... 0x6E4 | Section 73.14.32: OTG host channel x split control register (OTG_HCSPLTx) |

| OTG_HCINTx | 0x508 0x528 .... 0x6E8 | Section 73.14.33: OTG host channel x interrupt register (OTG_HCINTx) |

| OTG_HCINTMSKx | 0x50C 0x52C .... 0x6EC | Section 73.14.34: OTG host channel x interrupt mask register (OTG_HCINTMSKx) |

| OTG_HCTSIZx | 0x510 0x530 .... 0x6F0 | Section 73.14.35: OTG host channel x transfer size register (OTG_HCTSIZx) |

| OTG_HCDMAx | 0x514 0x534 .... 0x6F4 | Section 73.14.36: OTG host channel x DMA address register(OTG_HCDMAx) |

Device-mode CSR map

These registers must be programmed every time the core changes to device mode.

Table 768. Device-mode control and status registers

| Acronym | Offset address | Register name |

|---|---|---|

| OTG_DCFG | 0x800 | Section 73.14.38: OTG device configuration register (OTG_DCFG) |

| OTG_DCTL | 0x804 | Section 73.14.39: OTG device control register (OTG_DCTL) |

| OTG_DSTS | 0x808 | Section 73.14.40: OTG device status register (OTG_DSTS) |

Table 768. Device-mode control and status registers (continued)

Table 768. Device-mode control and status registers (continued)

| Acronym | Offset address | Register name |

|---|---|---|

| OTG_DOEPTSIZ0 | 0xB10 | Section 73.14.56: OTG device OUT endpoint 0 transfer size register (OTG_DOEPTSIZ0) |

| OTG_DOEPDMAx | 0xB14 0xB34 ... 0xC14 | Section 73.14.57: OTG device OUT endpoint x DMA address register (OTG_DOEPDMAx) |

| OTG_DOEPCTLx | 0xB20 0xB40 ... 0xC00 | Section 73.14.58: OTG device OUT endpoint x control register [alternate] (OTG_DOEPCTLx) Section 73.14.59: OTG device OUT endpoint x control register [alternate] (OTG_DOEPCTLx) |

| OTG_DOEPTSIZx | 0xB30 0xB50 .. 0xBF0 | Section 73.14.60: OTG device OUT endpoint x transfer size register (OTG_DOEPTSIZx) |

Data FIFO (DFIFO) access register map

These registers, available in both host and device modes, are used to read or write the FIFO space for a specific endpoint or a channel, in a given direction. If a host channel is of type IN, the FIFO can only be read on the channel. Similarly, if a host channel is of type OUT, the FIFO can only be written on the channel.

Table 769. Data FIFO (DFIFO) access register map

| FIFO access register section | Offset address | Access |

|---|---|---|

| Device IN endpoint 0/Host OUT Channel 0: DFIFO write access Device OUT endpoint 0/Host IN Channel 0: DFIFO read access | 0x1000–0x1FFC | w r |

| Device IN endpoint 1/Host OUT Channel 1: DFIFO write access Device OUT endpoint 1/Host IN Channel 1: DFIFO read access | 0x2000–0x2FFC | w r |

| ... | ... | ... |

| Device IN endpoint x

(1)

/Host OUT Channel x

(1)

: DFIFO write access Device OUT endpoint x (1) /Host IN Channel x (1) : DFIFO read access | 0xX000–0xXFFC | w r |

1. Where x is 8 in device mode and 15 in host mode.

Power and clock gating CSR map

There is a single register for power and clock gating. It is available in both host and device modes.

Table 770. Power and clock gating control and status registers

| Acronym | Offset address | Register name |

|---|---|---|

| OTG_PCGCTL | 0xE00–0xE04 | Section 73.14.61: OTG power and clock gating control register (OTG_PCGCTL) |

73.14 OTG_HS registers

These registers are available in both host and device modes, and do not need to be reprogrammed when switching between these modes.

Bit values in the register descriptions are expressed in binary unless otherwise specified.

73.14.1 OTG control and status register (OTG_GOTGCTL)

The OTG_GOTGCTL register controls the behavior and reflects the status of the OTG function of the core.

Address offset: 0x000

Reset value: 0x0001 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CUR MOD | OTG VER | BSVLD | ASVLD | DBCT | CID STS |

| r | rw | r | r | r | r | ||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | EHEN | Res. | Res. | Res. | Res. | BVALO VAL | BVALO EN | AVALO VAL | AVALO EN | VBVAL OVAL | VBVAL OEN | Res. | Res. |

| rw | rw | rw | rw | rw | rw | rw |

Bits 31:22 Reserved, must be kept at reset value.

Bit 21 CURMOD : Current mode of operation

Indicates the current mode (host or device).

0: Device mode

1: Host mode

Bit 20 OTGVER : OTG version

Selects the OTG revision.

0:OTG Version 1.3. OTG1.3 is obsolete for new product development.

1:OTG Version 2.0. In this version the core supports only data line pulsing for SRP.

Bit 19 BSVLD : B-session valid

Indicates the device mode transceiver status.

0: B-session is not valid.

1: B-session is valid.

In OTG mode, the user can use this bit to determine if the device is connected or disconnected.

Note: Only accessible in device mode.

Bit 18 ASVLD : A-session validIndicates the host mode transceiver status.

0: A-session is not valid

1: A-session is valid

Note: Only accessible in host mode.

Bit 17 DBCT : Long/short debounce timeIndicates the debounce time of a detected connection.

0: Long debounce time, used for physical connections (100 ms + 2.5 µs)

1: Short debounce time, used for soft connections (2.5 µs)

Note: Only accessible in host mode.

Bit 16 CIDSTS : Connector ID statusIndicates the connector ID status on a connect event.

0: The OTG_HS controller is in A-device mode

1: The OTG_HS controller is in B-device mode

Note: Accessible in both device and host modes.

Bits 15:13 Reserved, must be kept at reset value.

Bit 12 EHEN : Embedded host enableIt is used to select between OTG A device state machine and embedded host state machine.

0: OTG A device state machine is selected

1: Embedded host state machine is selected

Bits 11:8 Reserved, must be kept at reset value.

Bit 7 BVALOVAL : B-peripheral session valid override valueThis bit is used to set override value for Bvalid signal when BVALOEN bit is set.

0: Bvalid value is '0' when BVALOEN = 1

1: Bvalid value is '1' when BVALOEN = 1

Note: Only accessible in device mode.

Bit 6 BVALOEN : B-peripheral session valid override enableThis bit is used to enable/disable the software to override the Bvalid signal using the BVALOVAL bit.

0: Override is disabled and Bvalid signal from the respective PHY selected is used internally by the core

1: Internally Bvalid received from the PHY is overridden with BVALOVAL bit value

Note: Only accessible in device mode.

Bit 5 AVALOVAL : A-peripheral session valid override valueThis bit is used to set override value for Avalid signal when AVALOEN bit is set.

0: Avalid value is '0' when AVALOEN = 1

1: Avalid value is '1' when AVALOEN = 1

Note: Only accessible in host mode.

Bit 4 AVALOEN : A-peripheral session valid override enableThis bit is used to enable/disable the software to override the Avalid signal using the AVALOVAL bit.

0: Override is disabled and Avalid signal from the respective PHY selected is used internally by the core

1: Internally Avalid received from the PHY is overridden with AVALOVAL bit value

Note: Only accessible in host mode.

Bit 3 VBVALOVAL : V BUS valid override value

This bit is used to set override value for vbusvalid signal when VBVALOEN bit is set.

0: vbusvalid value is '0' when VBVALOEN = 1

1: vbusvalid value is '1' when VBVALOEN = 1

Note: Only accessible in host mode.

Bit 2 VBVALOEN : V BUS valid override enable

This bit is used to enable/disable the software to override the vbusvalid signal using the VBVALOVAL bit.

0: Override is disabled and vbusvalid signal from the respective PHY selected is used internally by the core

1: Internally vbusvalid received from the PHY is overridden with VBVALOVAL bit value

Note: Only accessible in host mode.

Bits 1:0 Reserved, must be kept at reset value.

73.14.2 OTG interrupt register (OTG_GOTGINT)

The application reads this register whenever there is an OTG interrupt and clears the bits in this register to clear the OTG interrupt.

Address offset: 0x004

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ADTO CHG | Res. | Res. |

| rc_w1 | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | SEDET | Res. | Res. |

| rc_w1 |

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 ADTOCHG : A-device timeout change

The core sets this bit to indicate that the A-device has timed out while waiting for the B-device to connect.

Note: Accessible in both device and host modes.

Bits 17:3 Reserved, must be kept at reset value.

Bit 2 SEDET : Session end detected

The core sets this bit to indicate that the level of the voltage on V BUS is no longer valid for a B-Peripheral session when V BUS < 0.8 V.

Note: Accessible in both device and host modes.

Bits 1:0 Reserved, must be kept at reset value.

73.14.3 OTG AHB configuration register (OTG_GAHBCFG)

This register can be used to configure the core after power-on or a change in mode. This register mainly contains AHB system-related configuration parameters. Do not change this register after the initial programming. The application must program this register before starting any transactions on either the AHB or the USB.

Address offset: 0x008

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | PTXFE LVL | TXFE LVL | Res. | DMAEN | HBSTLEN[3:0] | GINT MSK | |||

| rw | rw | rw | rw | rw | rw | rw | rw | ||||||||

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 PTXFELVL : Periodic Tx FIFO empty level

Indicates when the periodic Tx FIFO empty interrupt bit in the OTG_GINTSTS register (PTXFE bit in OTG_GINTSTS) is triggered.

0: PTXFE (in OTG_GINTSTS) interrupt indicates that the Periodic Tx FIFO is half empty

1: PTXFE (in OTG_GINTSTS) interrupt indicates that the Periodic Tx FIFO is completely empty

Note: Only accessible in host mode.

Bit 7 TXFELVL : Tx FIFO empty level

Condition: device mode

This bit indicates when IN endpoint Transmit FIFO empty interrupt (TXFE in OTG_DIEPINTx) is triggered:

0: The TXFE (in OTG_DIEPINTx) interrupt indicates that the IN endpoint Tx FIFO is half empty

1: The TXFE (in OTG_DIEPINTx) interrupt indicates that the IN endpoint Tx FIFO is completely empty

Condition: host mode

This bit indicates when the nonperiodic Tx FIFO empty interrupt (NPTXFE bit in OTG_GINTSTS) is triggered:

0: The NPTXFE (in OTG_GINTSTS) interrupt indicates that the nonperiodic Tx FIFO is half empty

1: The NPTXFE (in OTG_GINTSTS) interrupt indicates that the nonperiodic Tx FIFO is completely empty

Bit 6 Reserved, must be kept at reset value.

Bit 5 DMAEN : DMA enabled

0: The core operates in slave mode

1: The core operates in DMA mode

Bits 4:1 HBSTLEN[3:0] : Burst length/type

0000 Single: Bus transactions use single 32 bit accesses (not recommended)

0001 INCR: Bus transactions use unspecified length accesses (not recommended, uses the INCR AHB bus command)

0011 INCR4: Bus transactions target 4x 32 bit accesses

0101 INCR8: Bus transactions target 8x 32 bit accesses

0111 INCR16: Bus transactions based on 16x 32 bit accesses

Others: Reserved

Bit 0 GINTMSK : Global interrupt mask

The application uses this bit to mask or unmask the interrupt line assertion to itself.

Irrespective of this bit setting, the interrupt status registers are updated by the core.

0: Mask the interrupt assertion to the application.

1: Unmask the interrupt assertion to the application.

Note: Accessible in both device and host modes.

73.14.4 OTG USB configuration register (OTG_GUSBCFG)

This register can be used to configure the core after power-on or a changing to host mode or device mode. It contains USB and USB-PHY related configuration parameters. The application must program this register before starting any transactions on either the AHB or the USB. Do not make changes to this register after the initial programming.

Address offset: 0x00C

Reset value: 0x0000 1400

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | FD MOD | FH MOD | Res. | Res. | Res. | Res. | Res. | Res. | TSDPS | Res. | Res. | Res. | Res. | Res. | Res. |

| rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PHYL PC | Res. | TRDT[3:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | TOCAL[2:0] | |||||

| rw | rw | rw | rw | rw | rw | rw | rw | ||||||||

Bit 31 Reserved, must be kept at reset value.

Bit 30 FDMOD : Force device mode

Writing a 1 to this bit, forces the core to device mode irrespective of the OTG_ID input pin.

0: Normal mode

1: Force device mode

After setting the force bit, the application must wait at least 25 ms before the change takes effect.

Note: Accessible in both device and host modes.

Bit 29 FHMOD : Force host mode

Writing a 1 to this bit, forces the core to host mode irrespective of the OTG_ID input pin.

0: Normal mode

1: Force host mode

After setting the force bit, the application must wait at least 25 ms before the change takes effect.

Note: Accessible in both device and host modes.

Bits 28:26 Reserved, must be kept at reset value.

Bits 25:23 Reserved, must be kept at reset value.

Bit 22 TSDPS : TermSel DLine pulsing selection

This bit selects utmi_termselect to drive the data line pulse during SRP (session request protocol).

0: Data line pulsing using utmi_txvalid (default)

1: Data line pulsing using utmi_termsel

Bits 21:16 Reserved, must be kept at reset value.

Bit 15 PHYLPC : PHY Low-power clock select

This bit selects either 480 MHz or 48 MHz (low-power) PHY mode. In FS and LS modes, the PHY can usually operate on a 48 MHz clock to save power.

0: 480 MHz internal PLL clock

1: 48 MHz external clock

In 480 MHz mode, the UTMI interface operates at either 60 or 30 MHz, depending on whether the 8- or 16-bit data width is selected. In 48 MHz mode, the UTMI interface operates at 48 MHz in FS and LS modes.

Bit 14 Reserved, must be kept at reset value.

Bits 13:10 TRDT[3:0] : USB turnaround time

These bits allows to set the turnaround time in PHY clocks. They must be configured according to Table 771: TRDT values , depending on the application AHB frequency. Higher TRDT values allow stretching the USB response time to IN tokens in order to compensate for longer AHB read access latency to the data FIFO.

Note: Only accessible in device mode.

Bits 9:8 Reserved, must be kept at reset value.

Bit 7 Reserved, must be kept at reset value.

Bit 6 Reserved, must be kept at reset value.

Bit 5 Reserved, must be kept at reset value.

Bit 4 Reserved, must be kept at reset value.

Bit 3 Reserved, must be kept at reset value.

Bits 2:0 TOCAL[2:0] : FS timeout calibration

The number of PHY clocks that the application programs in this field is added to the full-speed interpacket timeout duration in the core to account for any additional delays introduced by the PHY. This can be required, because the delay introduced by the PHY in generating the line state condition can vary from one PHY to another.

The USB standard timeout value for full-speed operation is 16 to 18 (inclusive) bit times. The application must program this field based on the speed of enumeration. The number of bit times added per PHY clock is 0.25 bit times.

Table 771. TRDT values

| AHB frequency range (MHz) | TRDT minimum value | |

|---|---|---|

| Min | Max | |

| 30 | - | 0x9 |

73.14.5 OTG reset register (OTG_GRSTCTL)

The application uses this register to reset various hardware features inside the core.

Address offset: 0x010

Reset value: 0x8000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| AHB IDL | DMAR EQ | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| r | r | ||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | TXFNUM[4:0] | TXF FLSH | RXF FLSH | Res. | FCRST | PSRST | CSRST | ||||

| rw | rw | rw | rw | rw | rs | rs | rs | rs | rs | ||||||

Bit 31 AHBIDL : AHB master idle

Indicates that the AHB master state machine is in the Idle condition.

Note: Accessible in both device and host modes.

Bit 30 DMAREQ : DMA request signal enabled

This bit indicates that the DMA request is in progress. Used for debug.

Bits 29:11 Reserved, must be kept at reset value.

Bits 10:6 TXFNUM[4:0] : Tx FIFO numberThis is the FIFO number that must be flushed using the Tx FIFO Flush bit. This field must not be changed until the core clears the Tx FIFO Flush bit.

Condition: host mode

00000: Non-periodic Tx FIFO flush

00001: Periodic Tx FIFO flush

10000: Flush all the transmit FIFOs

Condition: device mode

00000: Tx FIFO 0 flush

00001: Tx FIFO 1 flush

00010: Tx FIFO 2 flush

...

01111: Tx FIFO 15 flush

10000: Flush all the transmit FIFOs

Note: Accessible in both device and host modes.

Bit 5 TXFFLSH : Tx FIFO flushThis bit selectively flushes a single or all transmit FIFOs, but cannot do so if the core is in the midst of a transaction.

The application must write this bit only after checking that the core is neither writing to the Tx FIFO nor reading from the Tx FIFO. Verify using these registers:

Read—NAK Effective interrupt ensures the core is not reading from the FIFO

Write—AHBIDL bit in OTG_GRSTCTL ensures the core is not writing anything to the FIFO.

Flushing is normally recommended when FIFOs are reconfigured. FIFO flushing is also recommended during device endpoint disable. The application must wait until the core clears this bit before performing any operations. This bit takes eight clocks to clear, using the slower clock of phy_clk or hclk.

Note: Accessible in both device and host modes.

Bit 4 RXFFLSH : Rx FIFO flushThe application can flush the entire Rx FIFO using this bit, but must first ensure that the core is not in the middle of a transaction.

The application must only write to this bit after checking that the core is neither reading from the Rx FIFO nor writing to the Rx FIFO.

The application must wait until the bit is cleared before performing any other operations. This bit requires 8 clocks (slowest of PHY or AHB clock) to clear.

Note: Accessible in both device and host modes.

Bit 3 Reserved, must be kept at reset value.

Bit 2 FCRST: Host frame counter resetThe application writes this bit to reset the (micro-)frame number counter inside the core.

When the (micro-)frame counter is reset, the subsequent SOF sent out by the core has a frame number of 0.

When application writes '1' to the bit, it might not be able to read back the value as it gets cleared by the core in a few clock cycles.

Note: Only accessible in host mode.

Bit 1 PSRST: Partial soft resetResets the internal state machines but keeps the enumeration info. Can be used to recover some specific PHY errors.

Note: Accessible in both device and host modes.

Bit 0 CSRST: Core soft resetResets the HCLK and PHY clock domains as follows:

Clears the interrupts and all the CSR register bits except for the following bits:

- – GATEHCLK bit in OTG_PCGCCTL

- – STPPCLK bit in OTG_PCGCCTL

- – FSLSPCS bits in OTG_HCFG

- – DSPD bit in OTG_DCFG

- – SDIS bit in OTG_DCTL

- – OTG_GCCFG register

- – FDMOD bit in OTG_GUSBFG

- – FHMOD bit in OTG_GUSBFG

- – PHYLPC bit in OTG_GUSBFG

- – TSDPS bit in OTG_GUSBFG

All module state machines (except for the AHB slave unit) are reset to the Idle state, and all the transmit FIFOs and the receive FIFO are flushed.

Any transactions on the AHB Master are terminated as soon as possible, after completing the last data phase of an AHB transfer. Any transactions on the USB are terminated immediately.