39. Multi-function digital filter (MDF)

39.1 MDF introduction

The multi-function digital filter (MDF) is a high-performance module dedicated to the connection of external sigma-delta ( \( \Sigma\Delta \) ) modulators. It is mainly targeted for the following applications:

- • audio capture signals

- • motor control

- • metering

The MDF features up to 6 digital serial interfaces (SITFx) and digital filters (DFLTx) with flexible digital processing options to offer up to 24-bit final resolution.

The DFLTx of the MDF also include the filters of the audio digital filter (ADF).

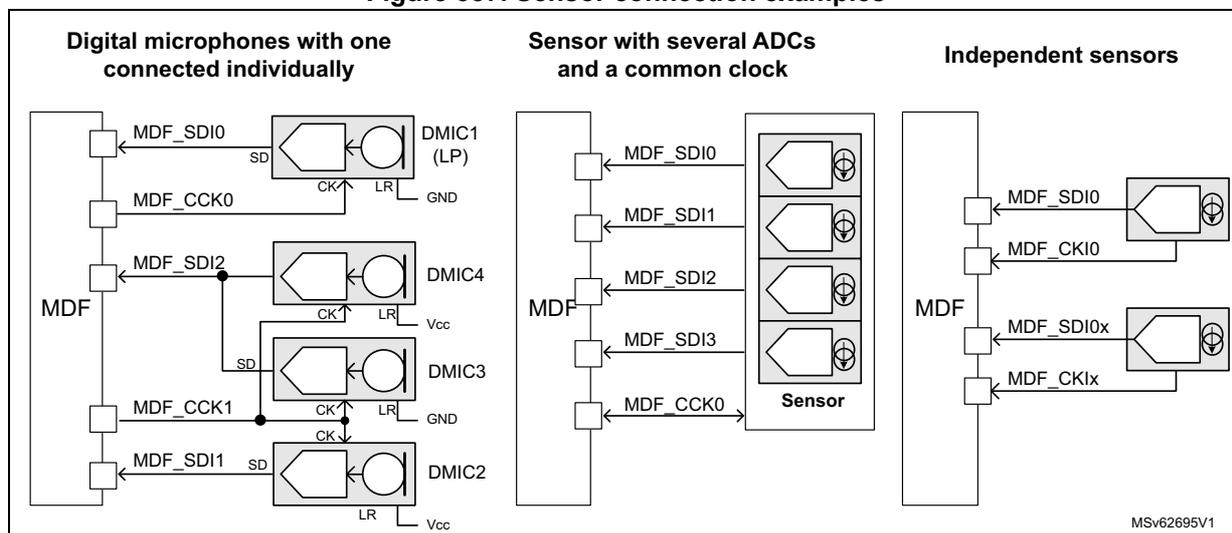

The MDF can receive, via its serial interfaces, streams coming from various digital sensors.

The MDF supports the following standards allowing the connection of various \( \Sigma\Delta \) modulator sensors:

- • SPI interface

- • Manchester coded 1-wire interface

- • PDM interface

A flexible bitstream matrix (BSMX) allows the connection of any incoming bitstream to any filter.

The MDF converts an input data stream into clean decimated digital data words. This conversion is done thanks to low-pass digital filters and decimation blocks. In addition it is possible to insert a high-pass filter or a DC offset correction block.

The conversion speed and resolution are adjustable according to configurable parameters for digital processing: filter type, filter order, decimation ratio, integrator length. The maximum output data resolution is up to 24 bits. There are two conversion modes: single conversion and continuous modes. The data can be automatically stored in a system RAM buffer through DMA, thus reducing the software overhead.

A flexible trigger interface can be used to control the conversion start. This timing control can trigger simultaneous conversions or insert a programmable delay between conversions.

The MDF features an out-of-limit detectors (OLD) function. There is one OLD for each digital filter chain. Independent programmable thresholds are available for each OLD, making it very suitable for over-current detection.

A short circuit detector (SCD) is also available for every selected bitstream. The SCD is able to detect a short-circuit condition with a very short latency. Independent programmable thresholds are offered in order to define the short circuit condition.

The digital processing is performed using only the kernel clock. The MDF requests the bus interface clock (AHB clock) only when data must be transferred or when a specific event requests the attention of the system processor.

39.2 MDF main features

- • AHB interface

- • up to 6 serial digital inputs:

- – configurable SPI interface to connect various digital sensors

- – configurable Manchester coded interface support

- – compatible with PDM interface to support digital microphones

- • 2 common clocks input/output for \( \Sigma\Delta \) modulators

- • Flexible matrix (BSMX) for connection between filters and digital inputs

- • 2 inputs to connect the internal ADCs

- • up to 6 flexible digital filter paths, including:

- – A configurable CIC filter:

- - Can be split into 2 CIC filters: high-resolution filter and out-off limit detector

- - Can be configured in Sinc 4 filter

- - Can be configured in Sinc 5 filter

- - Adjustable decimation ratio

- – A reshape filter to improve the out-off band rejection and in-band ripple

- – A high-pass filter to cancel the DC offset

- – An offset error cancellation

- – Gain control

- – Saturation blocks

- – An out-off limit detector

- – A configurable CIC filter:

- • Short-circuit detector

- • Clock absence detector

- • 16- or 24-bit signed output data resolution

- • Continuous or single conversion

- • Possibility to delay independently each bitstream

- • Various trigger possibilities

- • Break generation on out-of limit or short-circuit detector events

- • Autonomous functionality in Stop mode(s)

- • DMA can be used to read the conversion data

- • Interrupts services

39.3 MDF implementation

The devices embed one MDF instance and one ADF instance, both being digital filters with common features.

Table 367. ADF/MDF features (1)

| Mode or feature | ADF1 all devices | MDF1 STM32U535/545 | MDF1 STM32U575/585 | MDF1 STM32U59x/5Ax 5Fx/5Gx |

|---|---|---|---|---|

| Number of filters (DFLTx) and serial interfaces (SITFx) | 1 | 2 | 6 | |

| Mode or feature | ADF1 all devices | MDF1 STM32U535/545 | MDF1 STM32U575/585 | MDF1 STM32U59x/5Ax 5Fx/5Gx |

|---|---|---|---|---|

| MDF_CKly/ADF_CKl0 connected to pins | - | - | X | |

| Sound activity detection (SAD) | X | - | ||

| RXFIFO depth (number of 24-bit words) | 4 | 4 | ||

| ADC connected to ADCITF1 | - | ADC1 | ||

| ADC connected to ADCITF2 | - | - | ADC2 | |

| Motor dedicated features (SCD, OLD, OEC, INT, snapshot, break) | - | |||

| Main path with CIC4, CIC5 | X | X | ||

| Main path with CIC1,2, 3 or FastSinc | - | |||

| RSFLT, HPF, SAT, SCALE, DLY, Discard functions | X | |||

| Autonomous in Stop modes | X (2) | X (3) |

1. 'X' = supported, '-' = not supported.

2. Only Stop 0, Stop 1, and Stop 2 modes.

3. Only Stop 0 and Stop 1 modes.

39.4 MDF functional description

39.4.1 MDF block diagram

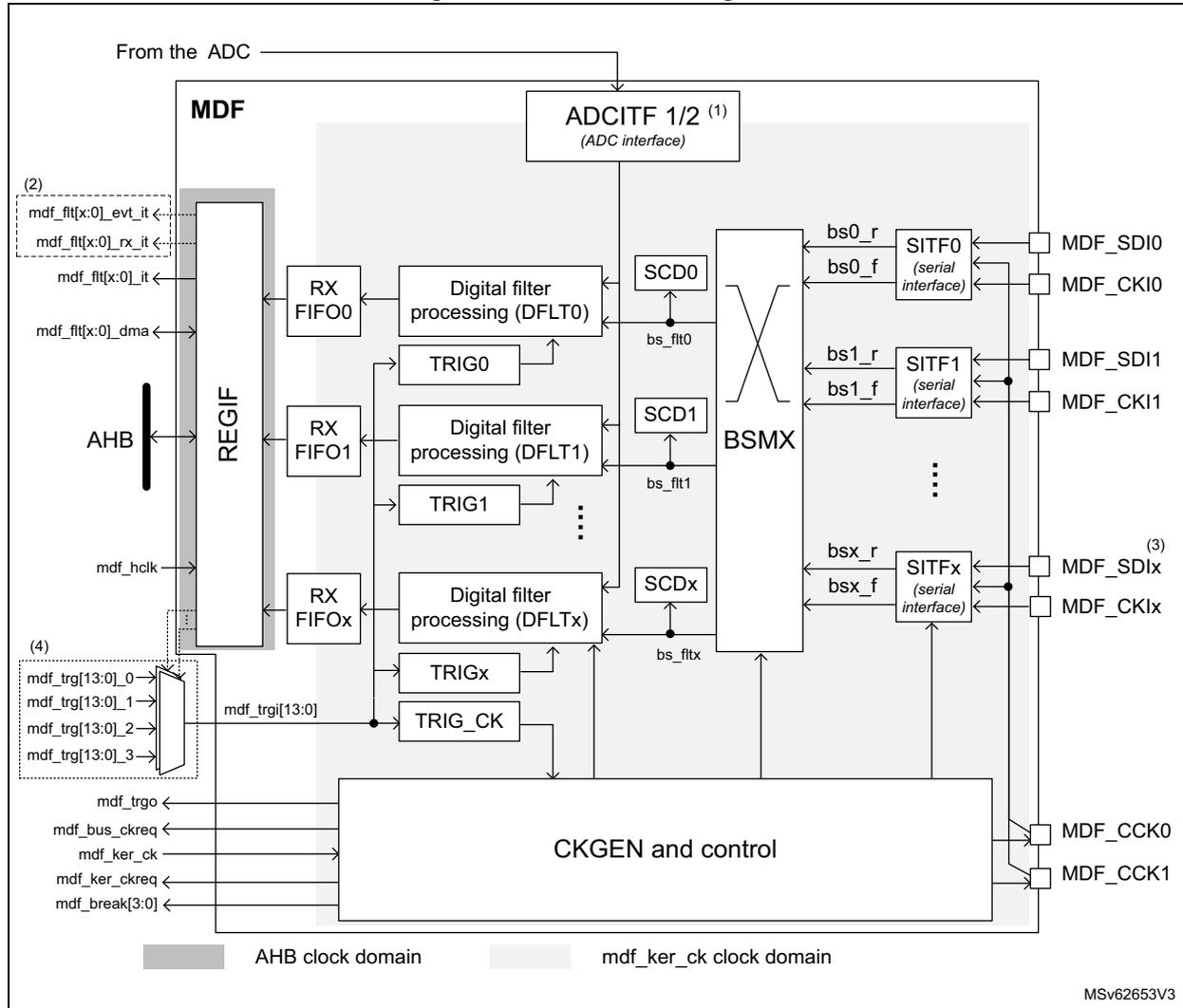

Figure 327. MDF block diagram

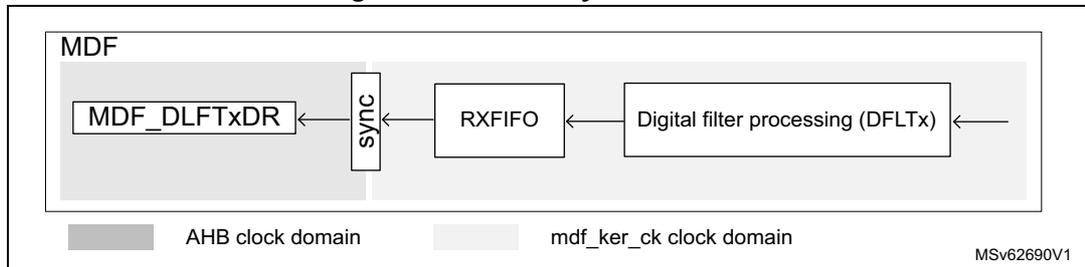

The block diagram illustrates the internal architecture of the Multi-function Digital Filter (MDF). It is divided into two clock domains: the AHB clock domain (shaded grey) and the mdf_ker_ck clock domain (shaded light grey). Key components include:

- REGIF: Interface to the AHB bus, connected to RX FIFOs and the AHB clock domain.

- RX FIFO0, RX FIFO1, RX FIFOx: Receive buffers for digital filter processing.

- Digital filter processing (DFLT0, DFLT1, DFLTx): Core processing blocks connected to RX FIFOs and SCD blocks.

- SCD0, SCD1, SCDx: Sample Control Data blocks that interface with the BSMX.

- BSMX: Bit Stream Multiplexer that routes data between SCD blocks and SITF blocks.

- SITF0, SITF1, SITFx: Serial Interface blocks connected to external pins (MDF_SDIO, MDF_CKIO, etc.).

- TRIG0, TRIG1, TRIGx, TRIG_CK: Trigger blocks connected to digital filter processing blocks and the CKGEN and control block.

- CKGEN and control: Clock generation and control block connected to various pins (MDF_CCK0, MDF_CCK1, etc.) and the TRIG blocks.

- ADCITF 1/2 (1) : ADC interface block connected to the ADC and the BSMX.

- From the ADC to ADCITF 1/2 (1) .

- External pins: MDF_SDIO, MDF_CKIO, MDF_SDI1, MDF_CKI1, MDF_SDIx, MDF_CKIx, MDF_CCK0, MDF_CCK1.

- Internal signals: mdf_flt[x:0]_evt_it, mdf_flt[x:0]_rx_it, mdf_flt[x:0]_it, mdf_flt[x:0]_dma, mdf_hclk, mdf_trg[13:0]_0 to _3, mdf_trgo, mdf_bus_ckreq, mdf_ker_ck, mdf_ker_ckreq, mdf_break[3:0].

- 1. Refer to Section 39.3: MDF implementation to check if the ADCITF is available, and which ADCs are connected.

- 2. Not always implemented, refer to the vector table of the product for details.

- 3. Refer to Section 39.3: MDF implementation to check the number of filter instances available.

- 4. The number of trigger inputs depends on the product. Refer to Section 39.3: MDF implementation for details.

39.4.2 MDF pins and internal signals

Table 368. MDF external pins

| Name | Signal type | Comment |

|---|---|---|

| MDF_CKly (y = 0 to 5) (1) | Input | Dedicated clock signals from external sensors |

| MDF_SDly (y = 0 to 5) (1) | Input | Data signal from external sensors |

| MDF_CCKy (y = 0, 1) | Input/output | Clock outputs for external sensor, or common clock input from external sensors |

1. The number of inputs available depends on the number of filters. Refer to Section 39.3 for details.

Table 369. MDF internal signals

| Name | Signal type | Comment |

|---|---|---|

| mdf_trgi[13:0] | Input | Trigger inputs in order to control the acquisition (see Table 370: MDF trigger connections for details) |

| mdf_trgo | Output | Trigger output for synchronizing several MDFs |

| mdf_break[3:0] | Output | Break signals event generation from over-current detector or short-circuit detector (see the next table for details) |

| mdf_fit[5:0]_dma (1) | Input/output | DMA request/acknowledge signals for each filter processing chain |

| mdf_fit[5:0]_it (1) | Output | Global interrupt signals, for each MDF filter |

| mdf_fit[5:0]_rx_it (1)(2) | Output | Receive interrupt signals, for each MDF filter. |

| mdf_fit[5:0]_evt_it (1)(2) | Output | Event interrupt signals, for each MDF filter. |

| mdf_bus_ckreq | Output | Bus interface clock request output |

| mdf_ker_ckreq | Output | Kernel clock request output |

| mdf_ker_ck | Input | Kernel clock input |

| mdf_hclk | Input | AHB bus interface clock input |

| mdf_adcitf1_dat[15:0] | Input | ADCITF1 data input |

| mdf_adcitf2_dat[15:0] | Input | ADCITF2 data input |

1. The number of signals available depends on the number of filters. Refer to Section 39.3 for details.

2. Not always connected. See the interrupt vector table for details.

The table below shows the way the trigger inputs of the MDF are connected.

Table 370. MDF trigger connections

| Trigger name | Trigger source |

|---|---|

| mdf_trgi0 | tim1_trgo |

| mdf_trgi1 | tim1_trgo2 |

| mdf_trgi2 | tim8_trgo |

| mdf_trgi3 | tim8_trgo2 |

| mdf_trgi4 | tim3_trgo |

| Trigger name | Trigger source |

|---|---|

| mdf_trgi5 | tim4_trgo |

| mdf_trgi6 | tim16_oc1 |

| mdf_trgi7 | tim6_trgo |

| mdf_trgi8 | tim7_trgo |

| mdf_trgi9 | adf1_sad_det (sound activity detection signal from ADF1) |

| mdf_trgi10 | exti11 |

| mdf_trgi11 | exti15 |

| mdf_trgi12 | lptim1_ch1 |

| mdf_trgi13 | adf1_trgo signal from ADF1 |

The table below shows the way the break outputs of the MDF are connected.

Table 371. MDF break connections| Trigger name | Trigger source |

|---|---|

| mdf_break0 | tim1_brk_cmp7 |

| mdf_break1 | tim1_brk2_cmp7 |

| mdf_break2 | tim8_brk_cmp7 |

| mdf_break3 | tim8_brk2_cmp7 |

The table below shows the way the ADC data are connected to the MDF.

Table 372. MDF ADC data connections| ADC data bus name | ADC source |

|---|---|

| mdf_adcitf1_dat[15:0] | adc1_dat |

| mdf_adcitf2_dat[15:0] | adc2_dat (1) |

1. Only available in STM32U59x/5Ax/5Fx/5Gx. It is not connected in STM32U535/545/575/585.

39.4.3 Serial input interfaces (SITF)

The SITFx input interfaces allow the connection of the external sensors to the digital filters, via the bitstream matrix (BSMX). The SITFx serial interface can be configured in the following modes:

- • LF_MASTER SPI mode (low-frequency)

- • normal SPI mode

- • Manchester mode

The amount of SITFx instances is equal to the amount of filters.

The data from each serial interface can be routed to any filter in order to perform:

- • the PDM to PCM conversion

- • the out-of limit detection

- • the short detection

The serial interfaces are enabled by setting the corresponding SITFEN bit to 1. Once the interface is enabled, it receives serial data from the external \( \Sigma\Delta \) modulator.

Note: Before enabling the serial interface, the user must insure that the mdf_proc_ck is already enabled (see Section 39.4.5 for details).

The SITFx are controlled via the MDF serial interface control register x (MDF_SITFxCxR) .

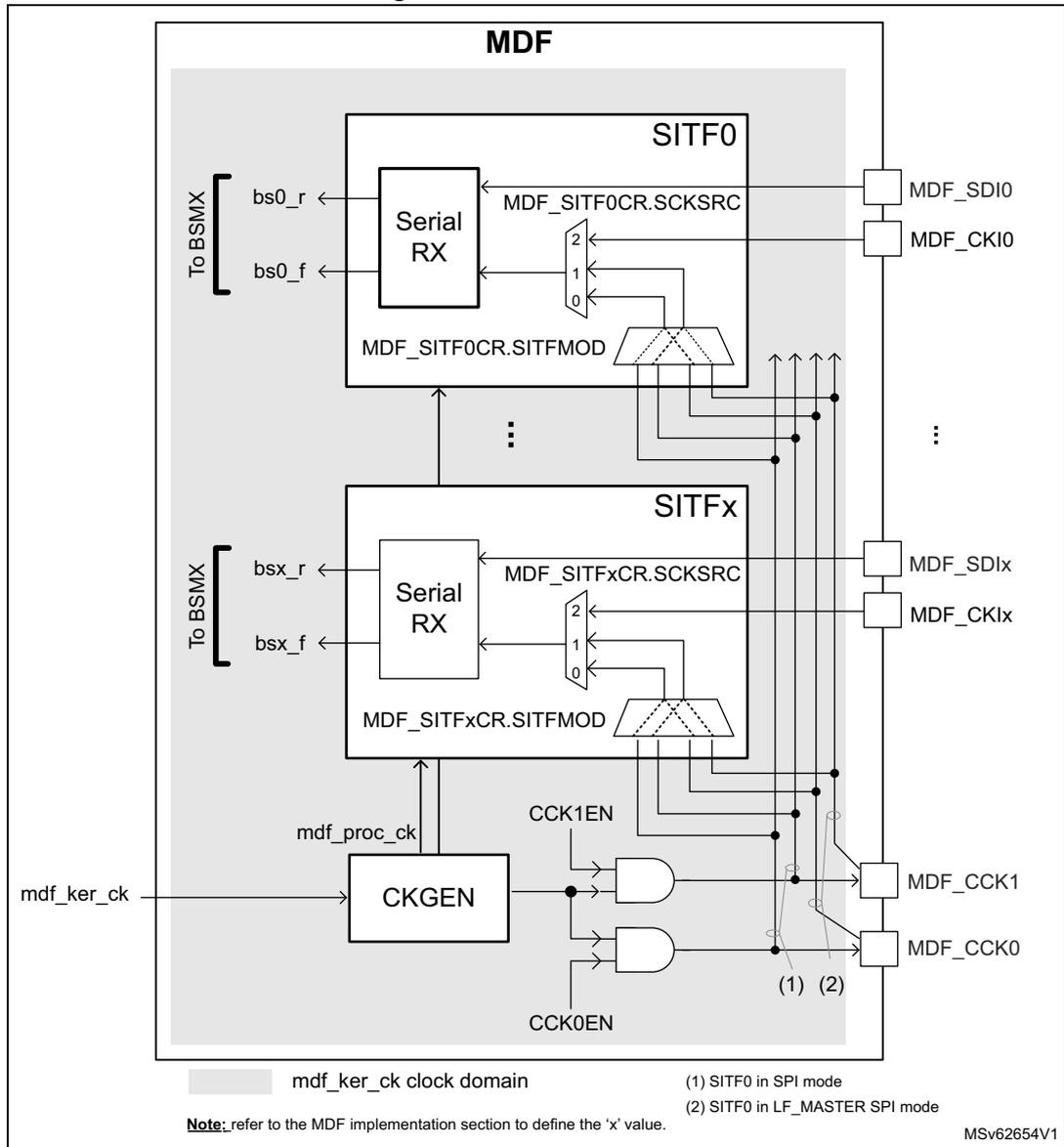

As shown in Figure 328 , for each SITF, there is a large choice of clocking possibilities:

- • If the serial interface is programmed in SPI mode, the selected clock source is a copy of the clock present on MDF_CCK0 or MDF_CCK1 or MDF_CKlx pin (see 2 in Figure 328 ).

- • If the serial interface is programmed in LF_MASTER SPI mode, the selected clock source must be the clock directly provided by the CCKDIV to the MDF_CCK0 or MDF_CCK1 pin (see 1 in Figure 328 ). In this case MDF_CKlx must not be selected.

See Table 373 for additional information.

Note: Using the common clock (MDF_CCK0 or MDF_CCK1) can be helpful to share the same clock between several SITFx.

Figure 328. SITFx overview

The diagram illustrates the internal architecture of the Multi-function digital filter (MDF). It features multiple Serial RX blocks labeled SITF0 and SITFx. Each block has a 'To BSMX' output and two internal outputs, bs0_r and bs0_f (or bsx_r and bsx_f). Each block is controlled by configuration registers: MDF_SITF0CR.SCKSRC and MDF_SITF0CR.SITFMOD (or MDF_SITFxCRC.SCKSRC and MDF_SITFxCRC.SITFMOD). The SCKSRC register has a 2-bit selector (0, 1, 2) that connects to external pins: MDF_SDI0, MDF_CKIO, MDF_SDIx, and MDF_CKIx. A central CKGEN block receives the mdf_ker_ck clock and generates two clock signals, CCK1EN and CCK0EN, which are ANDed with the SITF0 and SITFx blocks. The CKGEN block also has two outputs, MDF_CCK1 and MDF_CCK0, which are connected to external pins. The diagram is divided into two clock domains: mdf_ker_ck (shaded gray) and the rest of the MDF (white). A note at the bottom left refers to the MDF implementation section to define the 'x' value. A legend at the bottom right indicates: (1) SITF0 in SPI mode, (2) SITF0 in LF_MASTER SPI mode. The document code MSV62654V1 is shown in the bottom right corner.

LF_MASTER and normal SPI modes

The LF_MASTER SPI mode is a special mode allowing the usage of a mdf_proc_ck clock frequency, only two times higher than the sensor clock. This mode is dedicated to low-power use-cases, using low-speed sensors.

In LF_MASTER SPI mode, the MDF must provide the bitstream clock to the external sensors via MDF_CCK0 and MDF_CCK1 pins, and receives the bitstream data via the serial data input MDF_SDIx.

For each SITFx, the application must select the same clock than the one provided to the external sensor (MDF_CCK0 or MDF_CCK1), in order to guarantee optimal timing performances. This selection is done via SCKSRC[1:0].

Warning: The MDF_CKIx pin cannot be used in LF_MASTER SPI mode.

The normal SPI interface is a more flexible interface than the LF_MASTER SPI, but the mdf_proc_ck frequency must be at least four times higher than the sensor clock.

The application can select MDF_CCK0, MDF_CCK1 or MDF_CKIx clock for the capture of the data received via the MDF_SDIx pin.

The MDF can generate a clock to the sensors via MDF_CCK0 or MDF_CCK1 if needed.

For all SPI modes, all SITFs can share the same clock input (MDF_CCK0 or MDF_CCK1), in order to optimize the amount of requested I/Os.

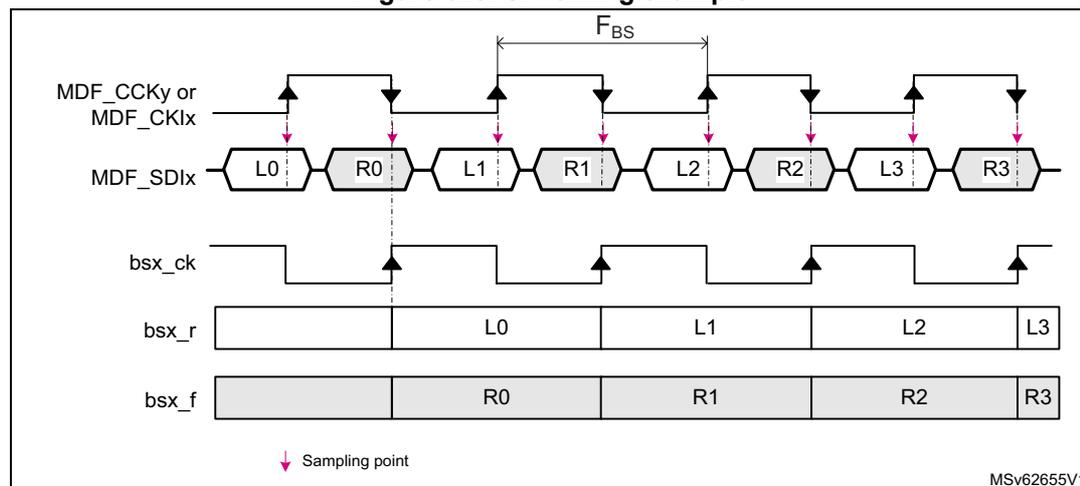

For all SPI modes, the serial data is captured using the rising and the falling edge of the selected clock. The SITFx always provides the following bitstreams:

- • bitstream received using the bitstream clock falling edge (bsx_f)

- • bitstream received using the bitstream clock rising edge (bsx_r)

According to the sensors connected, one of the two bitstreams may not be available.

The application can select the wanted stream via the BSMX matrix.

Figure 329. SPI timing example

The diagram illustrates the SPI timing for data capture. The top waveform shows the clock signal (MDF_CCKy or MDF_CKIx) and the data signal (MDF_SDIx). The data signal is a series of bits: L0, R0, L1, R1, L2, R2, L3, R3. The clock signal is a square wave. The bitstream bsx_r is captured on the rising edges of the clock, and the bitstream bsx_f is captured on the falling edges. The period between two consecutive rising edges is labeled F_BS. A legend indicates that a pink downward arrow represents a sampling point.

| bsx_r | L0 | L1 | L2 | L3 | |

|---|---|---|---|---|---|

| bsx_f | R0 | R1 | R2 | R3 |

To properly synchronize/receive the data stream, the frequency of the mdf_proc_ck clock must be adjusted according to the constraints listed in Table 374 .

Clock absence detection

A no-clock-transition period may be detected when the serial interface works in normal SPI mode. This feature can be used to detect a clock failure in the SPI link.

The application can program a timeout value via the STH[4:0] bitfield of the corresponding SITFx. If the MDF does not detect clock transitions for a duration of \( STH[4:0] \times T_{mdf\_proc\_ck} \) , then the CKABF flag is set.

An interrupt can be generated if CKABIE is set to 1. The STH[4:0] bitfield is in the MDF serial interface control register x (MDF_SITFxCN) .

When the serial interface is enabled, the CKABF flag remains to 1 until a first clock transition is detected.

To avoid spurious clock absence detection, the following sequence must be respected:

- 1. Configure the serial interface in normal SPI mode and enable it.

- 2. Clear the CKABF flag by writing CKABF bit to 1.

If no clock transition is detected on the serial interface, the hardware immediately sets the CKABF flag to 1. - 3. Read the CKABF flag:

- – If CKABF = 1, go back to step 2.

- – If CKABF = 0, a clock has been detected. The CKABIE bit can be set to 1 if the application wants an interrupt on detection of a clock absence.

Note: The clock absence detection feature is not available in the LF_MASTER SPI mode.

Manchester mode

In Manchester coded format, the MDF receives data stream from the external sensor via the MDF_SDlx pin only.

The MDF_CKlx pins are not needed in this mode.

Decoded data and clock signals are recovered from serial stream after Manchester decoding. They are available on bsx_r. There are two possible settings of Manchester codings:

- • signal rising edge decoded as 0 and signal falling edge decoded as 1

- • signal rising edge decoded as 1 and signal falling edge decoded as 0

Figure 330. Manchester timing example (SITFMOD = 11)

![Figure 330. Manchester timing example (SITFMOD = 11). This timing diagram shows the relationship between the Data transferred (bits 1, 1, 0, 0, 1), the Manchester encoded signal (MDF_SDix), the internal clock (mdf_proc_ck), the STH counter (STH[4:0] = 5), the Manchester counter (MCNT), the external clock (bsx_ck), the receive data (bsx_r), and the clock absence flag (CKABF). The diagram illustrates the timing parameters T_SYMB and the detection of long and short transitions based on the STH counter value. A legend at the bottom explains the background colors: green for signal absence, light blue for long transitions, and pink for short transitions.](/RM0456-STM32U5/7df1abe74d60173917cd2814777e4169_img.jpg)

To decode the incoming Manchester stream, the user must program the STH[4:0] bitfield in the MDF serial interface control register x (MDF_SITFxCN) . The STH[4:0] bitfield is used by the SITFx to estimate the Manchester symbol length and to detect a clock absence. An internal counter (MCNT) is restarted every time a transition is detected in the MDF_SDix input. It is used to detect short transitions, long transitions or clock absence. A long transition indicates that the data value changed. Figure 330 shows a case where the OVR is around height and STH[4:0] = 5.

The estimated Manchester symbol rate ( \( T_{SYMB} \) ) must respect the following formula:

It is recommended to compute STH as follows:

where OVR represents the ratio between the mdf_proc_ck frequency and the expected Manchester symbol frequency. OVR must be higher than five, and the mdf_proc_ck clock must be adjusted according to the constraints listed in Table 374 .

The clock absence flag CKABF is set to 1 when no transition is detected during more than \( 2 \times STH[4:0] \times T_{mdf\_proc\_ck} \) , or when the SITFx is not yet synchronized to the incoming Manchester stream. In addition, an interrupt can be generated if the bit CKABIE is set to 1.

When the serial interface is enabled, the MDF must first be synchronized to the incoming Manchester stream. The synchronization ends when a data transition from 0 to 1 or from 1 to 0 (pink circle in the Figure 330 ) is detected.

The end of the synchronization phase can be checked by following the software sequence:

- 1. Clear the CKABF flag in the MDF_DFLT \( x \) interrupt status register \( x \) (MDF_DFLT \( x \) ISR) by writing CKABF bit to 1. If the serial interface is not yet synchronized, the hardware immediately sets the CKABF flag to 1.

- 2. Read the CKABF flag.

- – If CKABF = 1, go back to step 1.

- – If CKABF = 0, the Manchester interface is synchronized and provides valid data.

Programming example

In the following example, the MDF kernel clock frequency ( \( F_{\text{mdf\_ker\_ck}} \) ) is 100 MHz and the received Manchester stream is at about 6 MHz ( \( F_{\text{SYMB}} \) ).

- 1. Provide a valid \( \text{mdf\_proc\_ck} \) to the SITF \( x \) .

The \( \text{mdf\_proc\_ck} \) frequency must be at least six times higher than the Manchester symbol frequency (means at least 36 MHz).

PROCDIV is programmed to 1 to perform a division by two of the kernel clock. In that case, \( F_{\text{mdf\_proc\_ck}} = 50 \) MHz (8.33 times higher than the Manchester symbol frequency).

- 2. Compute STH.

OVR is given by: \( \text{OVR} = F_{\text{mdf\_proc\_ck}} / F_{\text{SYMB}} = 50 \text{ MHz} / 6 \text{ MHz} = 8.33 \) .

The minimum allowed frequency for the Manchester stream is then:

The maximum allowed frequency for the Manchester stream is then:

39.4.4 ADC slave interface (ADCITF)

The ADCs are not always connected to the MDF. Refer to Section 39.3 to check the situation for this product.

The MDF allows the connection of up to two ADCs to the filter path. For each filter, the DATSRC[1:0] bitfield in the MDF digital filter configuration register \( x \) (MDF_DFLT \( x \) CICR) allows the application to select either data from the ADCs.

Warning: The MDF does not support receiving interleaved data from one of the ADCITF input.

39.4.5 Clock generator (CKGEN)

The RCC (reset and clock controller) provides the following clocks to the MDF:

- • AHB clock (mdf_hclk) used for the register interface

- • kernel clock (mdf_ker_ck) mainly used by all other parts of the circuit via the CKGEN

Those clocks are not supposed to be phase locked, so all signals crossing those clock domains are resynchronized.

The clock generator (CKGEN) is responsible of the generation of the processing clock, and the clock provided to the MDF_CCK0 and MDF_CCK1 pins. All those clocks are generated from the mdf_ker_ck.

The processing clock (mdf_proc_ck) is used to run all the signals processing and to re-sample the incoming serial or parallel stream.

Note: The reshape filter (RSFLT) needs up to 24 cycles of mdf_proc_ck clock to process a sample.

To adapt the kernel clock frequency provided by the RCC, the following dividers are available:

- • PROCDIV[6:0] used to adapt the kernel clock frequency to the constraints of the parallel and serial interfaces, and to the processing blocks

- • CCKDIV[3:0] used to adapt the frequency of the MDF_CCK0 and MDF_CCK1 clocks

PROCDIV[6:0] and CCKDIV[3:0] must be programmed when no clock is provided to the dividers (CKGDEN = 0).

The mdf_proc_ck generation is controlled by CKGDEN.

In addition, the CKGMOD bit allows the application to define the way to trigger the CCKDIV divider:

- • When CKGMOD = 0, the CCKDIV divider is started as soon as CKGDEN is set to 1.

- • When CKGMOD = 1, the CCKDIV divider is started when CKGDEN is set to 1 and the programmed trigger condition occurred.

All bits and fields controlling the CKGEN are in MDF_CKGCR.

Figure 331. CKGEN overview

![Figure 331. CKGEN overview diagram showing the internal clock generation logic of the MDF block. The diagram includes inputs mdf_ker_ck and cck_trg (from TRIG_CK). The cck_trg signal is ANDed with CKGDEN and then passed through a divider (+1 to 128) controlled by PROCODIV[6:0]. The output of this divider is ANDed with CKGMOD and then passed through another divider (+1 to 16) controlled by CCKDIV[3:0]. The output of the second divider is labeled mdf_proc_ck and is connected to TRIGx, Digital processing (DFLTx, SAD, OLD, SCD), and Interfaces (ADCITF[2:1], SITFx). The output of the second divider is also connected to two AND gates. The first AND gate takes CCK0DIR and CCK0EN as inputs and its output is connected to the MDF_CCK0 pin. The second AND gate takes CCK1DIR and CCK1EN as inputs and its output is connected to the MDF_CCK1 pin. The diagram is labeled MSv62657V1.](/RM0456-STM32U5/f46ffc5a39eefb97ff49e8ca32e608f3_img.jpg)

The trigger logic for CKGEN is handled by the TRG_CK block. As shown in Figure 340 , the CCKDIV divider can be triggered on the rising or falling edge of one of the 16 trigger sources. When the proper trigger condition occurs, the cck_trg signal goes to high, allowing the CCKDIV divider to start. The TRG_CK logic is reset when CKGDEN is set to 0.

This feature can be helpful to synchronize the MDF_CCKy (y = 0,1) clock of several MDF instances, or to synchronize the clock generation to a timer event.

The application can control the activation of the MDF_CCK0 or MDF_CCK1 pin CCK0EN/CCK1EN and CCK0DIR/CCK1DIR bits:

- • CCKyEN is used to enable the CCKDIV, and thus generates a clock for the external sensors.

- • CCKyDIR is used to control the direction of the ADF_CCKy pin (input or output)

| CCKyEN | CCKyDIR | Description |

|---|---|---|

| 0 | 0 | The MDF_CCKy pin is in input. An external clock can be connected to the MDF_CCKy pin and used by the SITFx in order to decode the serial stream |

| 0 | 1 | The MDF_CCKy pin is in output. No clock is generated, thus the MDF_CCKy pin is driven low. |

| 1 | 1 | The MDF_CCKy pin is in output. A clock is generated on the MDF_CCKy pin. The SITFx can use this pin as clock source in order to decode the serial stream |

1. The configuration with CCKyEN = 1 and CCKyDIR = 0 must be avoided (no interest).

When CCKyDIR = 1, as soon as the CCKyEN bit is set to 1, a clock is generated to the corresponding output without any spurs.

Note: The mdf_proc_ck must be enabled (by CKGDEN = 1) before enabling other blocks (such as SITFx or DFLT x ).

CKGEN activation sequence example- 1. Set CKGDEN to 0.

- 2. Wait for CKGACTIVE = 0. If CKGDEN was previously enabled, this phase can take two periods of mdf_hclk and two periods of mdf_proc_ck.

- 3. Program PROCDIV[6:0], CKGMOD, CCKDIV[3:0], TRGSRC[3:0] and TRGSENS.

- 4. Set CKGDEN to 1.

- 5. Set CCKxDIR to 1 (optional).

- 6. Set CCKxEN to 1 (optional).

When needed, at any moment, the CCK0EN or CCK1EN value can be changed without disabling the clock generator.

Clock frequency constraintsThe table below shows the frequency constraints to receive and process properly the samples.

Table 374. Clock constraints with respect to the incoming stream (1)

| SITFx mode | MDF clock constraints | |

|---|---|---|

| With RSFLT disabled | With RSFLT enabled | |

| LF_MASTER SPI | \( F_{MDF\_CCKy} \) max frequency limited to 5 MHz | |

| \(

F_{mdf\_proc\_ck} > 2 * F_{MDF\_CCKy}

\) and \( F_{mdf\_hclk} \geq F_{mdf\_proc\_ck} \) | \(

F_{mdf\_proc\_ck} > 24 * F_{MDF\_CCKy} / (MCICD+1)

\) and \( F_{mdf\_proc\_ck} > 2 * F_{MDF\_CCKy} \) and \( F_{mdf\_hclk} \geq F_{mdf\_proc\_ck} \) | |

| MASTER SPI SLAVE SPI | \( F_{MDF\_CKx} \) max frequency limited to 25 MHz | |

| \(

F_{mdf\_proc\_ck} > 4 * F_{MDF\_CCKy}

\) and \( F_{mdf\_hclk} \) higher or equal to \( F_{mdf\_proc\_ck} \) | \(

F_{mdf\_proc\_ck} > 24 * F_{MDF\_CCKy} / (MCICD+1)

\) and \( F_{mdf\_proc\_ck} \) higher than \( 4 * F_{MDF\_CCKy} \) and \( F_{mdf\_hclk} \) higher or equal to \( F_{mdf\_proc\_ck} \) | |

| Manchester | \( F_{SYMB} \) max frequency limited to 20 MHz | |

| \(

F_{mdf\_proc\_ck}

\)

higher than

\(

6 * F_{SYMB}

\) and \( F_{mdf\_hclk} \geq F_{mdf\_proc\_ck} \) | \(

F_{mdf\_proc\_ck}

\)

higher than

\(

24 * F_{MDF\_CCKy} / (MCICD+1)

\) and \( F_{mdf\_proc\_ck} > 6 * F_{SYMB} \) and \( F_{mdf\_hclk} \geq F_{mdf\_proc\_ck} \) | |

1. \( F_{MDF\_CCKy} \) represents the frequency of the clock received via MDF_CKIx and MDF_CCKy, or generated via MDF_CCKy. \( F_{SYMB} \) represents the frequency of the received symbol rate for Manchester mode.

39.4.6 Bitstream matrix (BSMX)The BSMX receives the bitstreams from all serial interfaces (SITFx) and provides the selected input to the digital filters (DFLTx) and to the short-circuit detectors (SCDx). For each filter path, any of the bitstream input can be selected.

As shown in the Figure 328 , each SITFx block provides two bitstreams (bsx_r and bsx_f) to the BSMX.

The application to select the wanted stream via the MDF bitstream matrix control register x (MDF_BSMXxCR) . This selection is intended to be static.

Figure 332. BSMX overview

![Figure 332. BSMX overview diagram showing the internal architecture of the Multi-function digital filter (MDF). The diagram illustrates the signal flow from the ADCITF[2,1] block through various filter paths (DFLT0, SCD0, BSMX, SITF0, etc.) to the output. The BSMX block is a central switching matrix that routes signals based on configuration registers (MDF_BSMX0CR.BSSEL, MDF_BSMX1CR.BSSEL, etc.).](/RM0456-STM32U5/bec8b98012e55a73ae5c115599a16c60_img.jpg)

The diagram shows the internal architecture of the Multi-function digital filter (MDF). At the top left, the ADCITF[2,1] block provides input signals. These signals are distributed to multiple filter paths. Each path consists of a DFLTx (Digital Filter) block, an SCDx (Short-Circuit Detector) block, and a SITFx (Signal Interface) block. The BSMX (Bitstream Matrix) block is a central switching matrix that routes the signals from the SCDx blocks to the SITFx blocks. The routing is controlled by configuration registers: MDF_BSMX0CR.BSSEL , MDF_BSMX1CR.BSSEL , and MDF_BSMX(N-1)CR.BSSEL . The BSMX block contains multiple multiplexers, each with inputs labeled bs0_r , bs0_f , bs1_r , bs1_f , ..., bs(N-1)_r , bs(N-1)_f . The outputs of these multiplexers are connected to the SITFx blocks, which are labeled bs0_r , bs0_f , bs1_r , bs1_f , ..., bs(N-1)_r , bs(N-1)_f . The diagram also shows the DFLTx blocks connected to the SCDx blocks, and the SCDx blocks connected to the BSMX blocks. The BSMX block is labeled with an 'X' symbol. The diagram is identified by the code MSV62658V1 in the bottom right corner.

BSMX programming sequence example

The BSSEL[4:0] bitfield cannot be changed if the corresponding SCDx, OLDx or DFLTx is enabled. The following steps are needed to change the value of BSMX, for filter path x:

- 1. Set SCDEN of SCDx to 0.

- 2. Set DFLTEN of DFLTx to 0.

- 3. Set OLDEN of OLDx to 0.

- 4. Wait for BSMXACTIVE = 0.

- 5. Program BSSEL[4:0] of filter path x.

- 6. Set SCDEN of SCDx to 1 (optional).

- 7. Set DFLTEN of DFLTx to 1 (optional).

- 8. Set OLDEN of OLDx block to 1 (optional).

39.4.7 Short-circuit detectors (SCD)

The SCDx detects, with a very fast response time, if an analog signal reached saturated values (out-of-full scale ranges) and remained on this value for a given time.

This behavior can detect short-circuit or open-circuit errors (such as over current or over voltage). An interrupt event or/and a break signal can be generated.

Figure 333. SCD functional view

![Figure 333. SCD functional view diagram showing the internal components of the Short Circuit Detector (SCD) within the MDF block. The SCD block contains a Transition detector, a Counter, and a Comparator. The Transition detector receives bs_fitx_dat and bs_fitx_ck from the BSMX and mdf_ker_ck. It sends a reset signal to the Counter. The Counter receives bs_fitx_ck and outputs scd_cnt[7:0] to the Comparator. The Comparator also receives MDF_SCDxCR.SCDT[7:0] and outputs scd_brkx (to break interface) and scd_evtX (to interrupts interface).](/RM0456-STM32U5/6e61932e746a7d8292252e91ed1e0e9a_img.jpg)

The diagram illustrates the functional architecture of the Short Circuit Detector (SCD) within the Multi-function Digital Filter (MDF). The SCD block is shown with the following internal components and connections:

- Inputs:

mdf_ker_ck: Clock signal for the SCD.bs_fitx_datandbs_fitx_ck: Data and clock signals from the BSMX (Break Signal Monitor) output.

- Internal Components:

- Transition detector:

Monitors the

bs_fitx_datsignal. When a transition is detected, it sends aresetsignal to the Counter. - Counter:

Counts consecutive zeros or ones based on the

bs_fitx_cksignal. It outputs the countscd_cnt[7:0]to the Comparator. - Comparator:

Compares the current count

scd_cnt[7:0]with the threshold valueMDF_SCDxCR.SCDT[7:0].

- Transition detector:

Monitors the

- Outputs:

scd_brkx: Break signal sent to the break interface.scd_evtX: Interrupt signal sent to the interrupts interface.

Reference: MSV62659V1

The SCDx is counting consecutive zeros or consecutive ones received from the serial interface (SITFx). A counter is restarted if there is a change in the data stream received. If this counter reaches a short-circuit threshold value (SCDT[7:0] in the

MDF short circuit detector control register x (MDF_SCDxCR)

), then a short-circuit event is invoked. Each BSMX output has its own short-circuit detector. Any BSMX output can be continuously monitored by setting the corresponding SCDEN bit to 1 in

MDF_SCDxCR

. Each SCD has its own threshold settings (SCDT) and its own status bit (SCDF).

The figure below shows an example where SCDT[7:0] is set to six. The break signal remains high as long as the short circuit condition is present.

No overrun event is generated when the interrupt event is pending while a new short-circuit condition is detected.

Figure 334. SCD timing example

![Figure 334. SCD timing example diagram showing the timing relationship between bs_fitx_dat, bs_fitx_ck, scd_cnt[7:0], mdf_ker_ck, scd_brkx, and mdf_evt_Itx/mdf_itx. The diagram shows a sequence of events where a short-circuit condition is detected and the break signal is asserted.](/RM0456-STM32U5/3922132e480e5a4f7fb9fdb78c79b999_img.jpg)

The timing diagram shows the following signals and their relationship over time:

bs_fitx_dat: Data signal from the BSMX. It shows a high level followed by a low level, then a high level again.bs_fitx_ck: Clock signal for the data. It is a periodic square wave.scd_cnt[7:0]: Counter output. The counter increments on rising edges ofbs_fitx_ckwhenbs_fitx_datis high. It resets to 1 on a transition ofbs_fitx_dat. The sequence shown is: 2, 3, 4, 1, 2, 3, 4, 1, 2, 3, 4, 5, 6, 1, 1, 2, 3, 4, 5, 6, 1, 2, 1.mdf_ker_ck: High-frequency clock signal for the MDF.scd_brkx: Break signal. It goes high when the counter reaches the threshold value of 6 and remains high as long as the short-circuit condition (highbs_fitx_dat) persists.mdf_evt_Itx/mdf_itx (due to scd_evtX): Interrupt signal. It is generated when the counter reaches the threshold value (6). The diagram shows a pulse followed by a high level, which returns to low after 'Writing 1 to SCDF'.

Reference: MSV62660V1

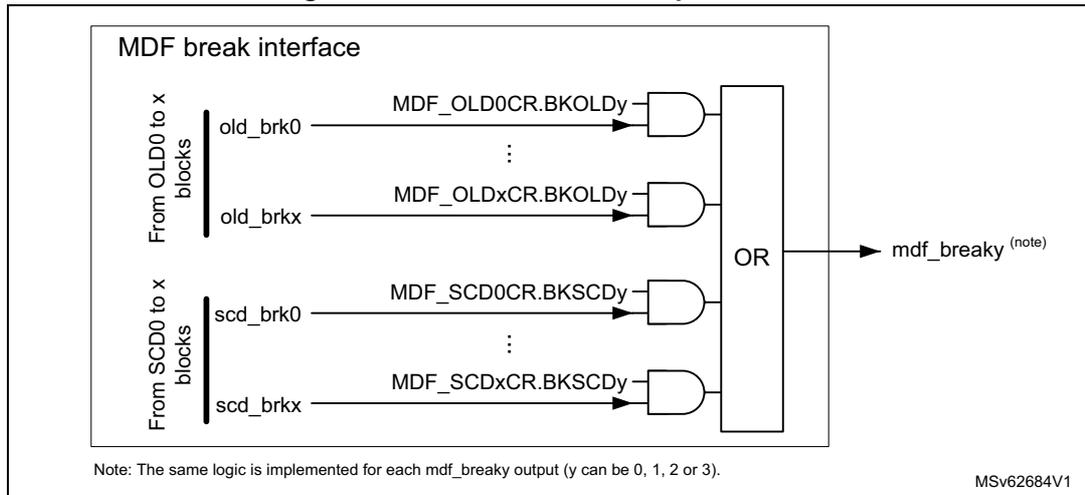

The SCDx event generated by the SCDx block can be assigned to break output signals mdf_break[3:0]. The break signal assignment to a given short-circuit detector event is done by BKSCD[3:0] in MDF_SCDxCR. The break outputs are shared with the over-current function.

Note: SCDs cannot be used to monitor the ADC data interface (ADCITF).

SCD activation sequence example

- 1. Enable and configure CKGEN to generate the mdf_proc_ck.

- 2. Set SCDEN to 0.

- 3. Wait for SCDACTIVE = 0. If SCDEN was previously enabled, this phase can take two periods of mdf_hclk, and two periods of mdf_proc_ck.

- 4. Program BKSCD[3:0] and SCDT[7:0].

- 5. Set SCDEN to 1.

Note: BKSCD[3:0] and SCDT[7:0] must not be changed when SCDACTIVE = 1.

39.4.8 Digital filter processing (DFLT)

The digital filter processing includes the following sub-blocks:

- • symbol remap (SBR)

- • source selector

- • clock skipper delay (DLY)

- • CIC decimation filter that can be configured:

- – in single Sinc 4 or Sinc 5 order CIC (MCIC)

- – in two CIC filters:

- - a main filter (MCIC), high resolution

- - an auxiliary filter (ACIC), low-latency, for the out-of-limit detector (OLD)

- - both MCIC and ACIC can be configured as Sinc 1 , Sinc 2 , Sinc 3 or FastSinc

- • gain control (SCALE)

- • signal saturation (SAT)

- • reshape filter (RSFLT)

- • high-pass filter (HPF)

- • integrator (INT)

- • receive RXFIFO

Figure 335 shows the filter-path configuration according to CICMOD[2:0]. Several configuration bits are available to configure the digital filter to the application needs.

Figure 335. DFLT overview

![Figure 335. DFLT overview block diagram showing the internal architecture of the Multi-function Digital Filter (MDF). The diagram is divided into three frequency domains: F_PCM (PCM frequency domain), F_RS (RS frequency domain), and F_BS (BS frequency domain), all within the mdf_proc_ck clock domain. The signal flow starts from RX FIFO (PCM[23:0]) through an INT block (controlled by INTERVAL), then through HPF (controlled by HPFBYP and HPFC), then through RSFLT (controlled by RSFLTBY and RSFLT). The signal then passes through a SCALE block, an OEC block, and an OFFSET block. The next stage is the CIC filter (MCIC1[3:1], MCIC4, MCIC5) controlled by CICMOD. The output of the CIC filter is then processed by a DLY (delay) block controlled by DATSRC. The DATSRC block selects between data from ADCITF2, ADCITF1, and BSMX. The output of the DLY block is then processed by a SBR (symbol remap) block, which outputs SCDx. An Out-of-limit detector (OLD) is also shown, consisting of a CMP block, D2, and ACICF[3:1] / ACICF blocks. The diagram also includes various control signals and internal data paths (e.g., 0xx, 100, 101, 0x, 1, -1, 0).](/RM0456-STM32U5/aa87e3ae9d2f19b4919e465af23e18df_img.jpg)

Symbol remap and source selection

The symbol remap (SBR) converts the bitstream selected by the BSMX into data usable by the filter path. More especially:

- • The high levels are converted into a 16-bit signed number + 1.

- • The low levels are converted into a 16-bit signed number - 1.

The signal source of the digital filter can be selected via DATSRC[1:0] between the two following:

- • data coming from the BSMX

- • data coming from one of the ADC interfaces (ADCITF2 or 1)

Programmable micro-delay control (DLY)

The digital filter has a delay line that allows the timing adjustment of each stream with the resolution of the bitstream clock.

This feature is particularly helpful in the case of microphone beam forming applications where delays smaller than the final sampling rate, must be applied to the incoming stream. This feature is helpful when the MDF is synchronized with other ADF or MDF blocks for a beam forming application for example.

The delay is performed by discarding a given number of samples from the selected input stream, before samples enter into the CIC filter. This data discarding is performed by skipping a given number of data strobe, preventing the CIC filter to take into account those data.

When the wanted amount of data strobe has been skipped, the next incoming samples are strobed normally.

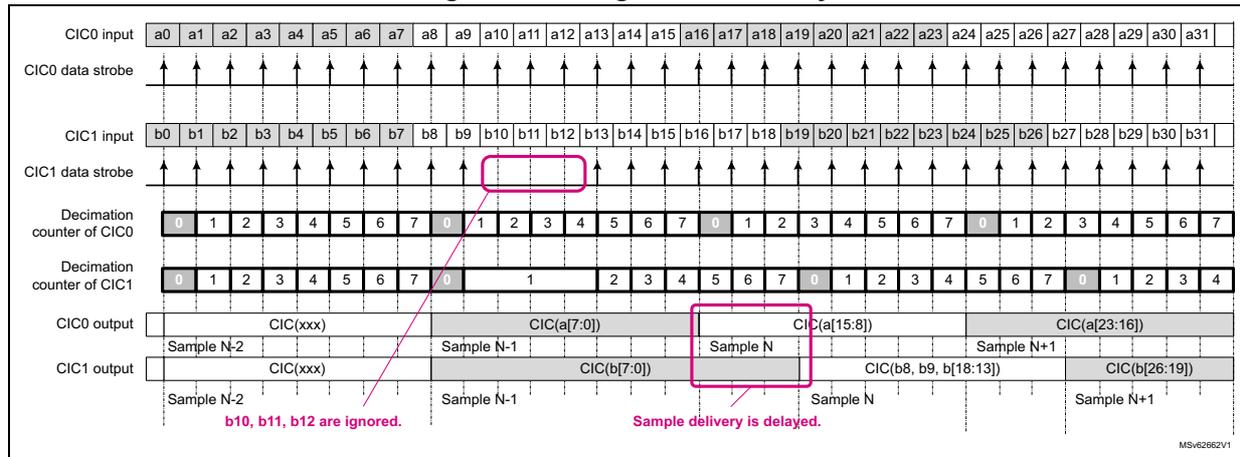

Figure 336 shows an example of how to apply dynamically small delay to an incoming stream. For simplification, the CIC filter performs a decimation by height in this example. CIC1 represents the CIC included in the ADF and CIC0 represents a filter from another ADF or MDF instance.

Figure 336. Programmable delay

The diagram illustrates the timing of two cascaded CIC filters, CIC0 and CIC1.

CIC0 input: A continuous stream of samples a0 through a31.

CIC0 data strobe: Pulses for every sample from a0 to a31.

CIC1 input: Receives samples from CIC0 output. It shows samples b0 through b31, but b10, b11, and b12 are missing (ignored).

CIC1 data strobe: Pulses for samples b0 through b9, then skips for three periods (corresponding to b10, b11, b12), then resumes for b13 through b31. A pink box highlights the skipped period.

Decimation counter of CIC0: Counts from 0 to 7 repeatedly.

Decimation counter of CIC1: Counts from 0 to 7, then when samples are skipped, the counter freezes at 0 for three clock periods before resuming its count from 1.

CIC0 output: Shows output samples N-2, N-1, N, and N+1. Sample N+1 is composed of input samples a[23:16].

CIC1 output: Shows output samples N-2, N-1, N, and N+1. Due to the skipping of b10, b11, and b12, the output stream is delayed. Sample N+1 is composed of input samples b[26:19].

Annotations: 'b10, b11, b12 are ignored.' and 'Sample delivery is delayed.' with arrows pointing to the relevant parts of the diagram.

The CIC of filter 1 (CIC1) receives a command in order to skip three incoming samples. So the input samples named b10, b11 and b12 are not processed by CIC1. As a consequence, the output sample N+1 generated by CIC0 is build from input samples a[23:16] while the sample N+1 of CIC1 is build from input samples b[26:19].

Finally, the non-skipped data stream looks delayed by three bitstream periods.

Note: When the input data strobes are skipped, the decimation counter remains frozen. As a consequence, the samples delivered by the CIC1 are a bit delayed.

Warning: It is not recommended to apply a delay bigger than the programmed decimation ratio (CIC + RSFLT decimation), especially if the MDF is programmed in interleaved acquisition mode. There is a strong risk of data misalignment inside the FIFOs.

The following steps are needed to program the amount of bitstream clock periods to be skipped:

- 1. Wait for SKPBF equal to 0.

- 2. Write SKPDLY[6:0] to the wanted number of bitstream clock periods to be skipped. The SKPBF flag goes immediately to 1, indicating that the delay value entered into SKPDLY[6:0] is under process.

- – If the corresponding DFLT x is not yet enabled (DFLTEN = 0), then the DLY logic waits for DFLTEN = 1. When the application sets DFLTEN to 1, the DLY logic starts to skip the amount of wanted data strobes.

- – If the corresponding digital filter is already enabled (DFLTEN = 1), then the DLY logic immediately starts to skip the amount of wanted data strobes.

When the MDF skipped the amount of wanted data strobes, then SKPBF goes back to 0.

- 3. If the application needs to skip more data strobes, then the operation must be restarted from step 1.

The effect of the delay performed with this mechanism is cumulative as long as the MDF is enabled. In a given filter, if the application performs a D1 delay, followed by a D2 delay, then all other active filters are delayed by D1 + D2.

Data coming from ADCs can also benefit of this feature.

In interleaved acquisition mode, it is up to the application to insure that the delay applied on the different microphones is in line with the depth of the RXFIFO buffers. If the relative delay between each activated filter is less than the decimation ratio, then it costs one FIFO location.

If the interleaved acquisition mode is not used, then the delay value has no impact on the RXFIFO buffering.

Note: If SKPDLY[6:0] is written when SKPBF = 1, the write operation is ignored.

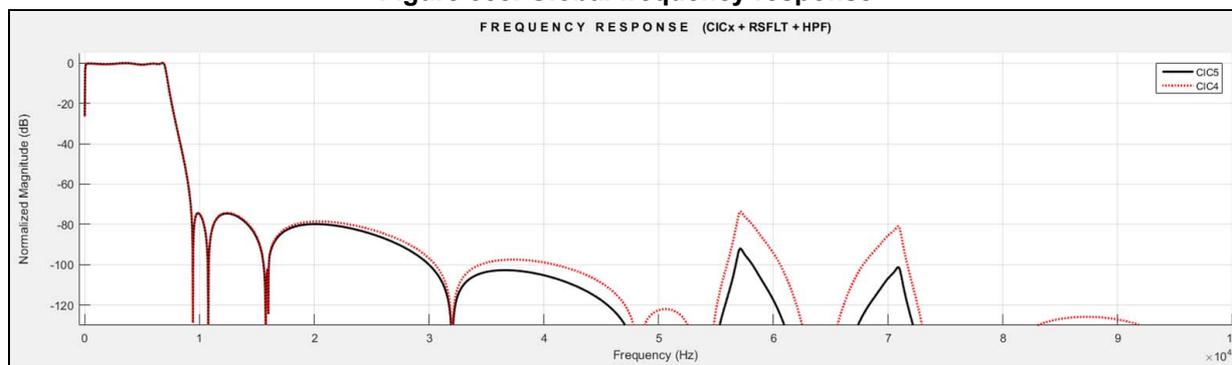

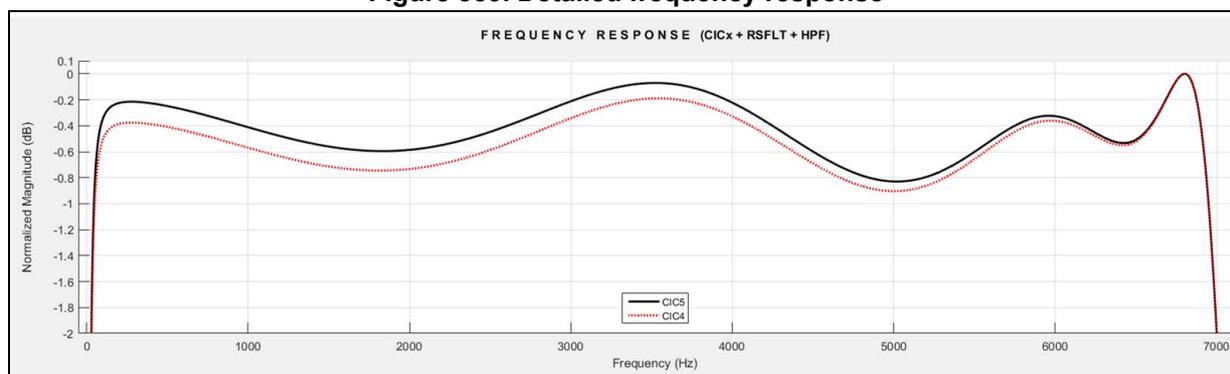

Cascaded-integrator-comb (CIC) filter

The CIC digital filters are an efficient implementation of low-pass filters, often used for decimation and interpolation. The CIC frequency response is equal to a \( \text{Sinc}^N \) function, this is why they are often called Sinc filters.

The \( \text{Sinc}^N \) digital filter embedded into the MDF is configurable according to the application targeted.

- • For audio applications, such as speech capture from digital microphones, the application can select a high-resolution low-pass decimation filter by setting CICMOD to 100 or 101.

- • If the targeted application is motor control or any other sensor capture, then the application can configure the CIC in order to offer a main filter path for acquisition (MCIC) and an auxiliary filter for fast-event generation (ACIC). This auxiliary filter can be used for example, to detect over-current conditions. This mode is selected by setting CICMOD[2:0] = 0xx.

When CICMOD[2:0] = 0xx, the following CIC filters are available:

- • main filter (MCIC)

- • auxiliary CIC filter (ACIC)

Both of them are configurable in FastSinc, \( \text{Sinc}^1 \) to \( \text{Sinc}^3 \) .

When CICMOD[2:0] = 100, the CIC is configured into a single \( \text{Sinc}^4 \) and when CICMOD[2:0] = 101, the CIC is configured into a single \( \text{Sinc}^5 \) filter.

The filters have the following transfer function (impulse response in z domain):

- •

\(

\text{Sinc}^N

\)

filter type:\[ H(z) = \left( \frac{1 - z^{-D}}{1 - z^{-1}} \right)^N \]

- • FastSinc filter type:\[ H(z) = \left( \frac{1 - z^{-D}}{1 - z^{-1}} \right)^2 \cdot (1 + z^{-(2 \cdot D)}) \]

where N can be 1, 2, 3, 4 or 5, and D is the decimation ratio.

D is equal to MCICD+1 or ACICD+1.

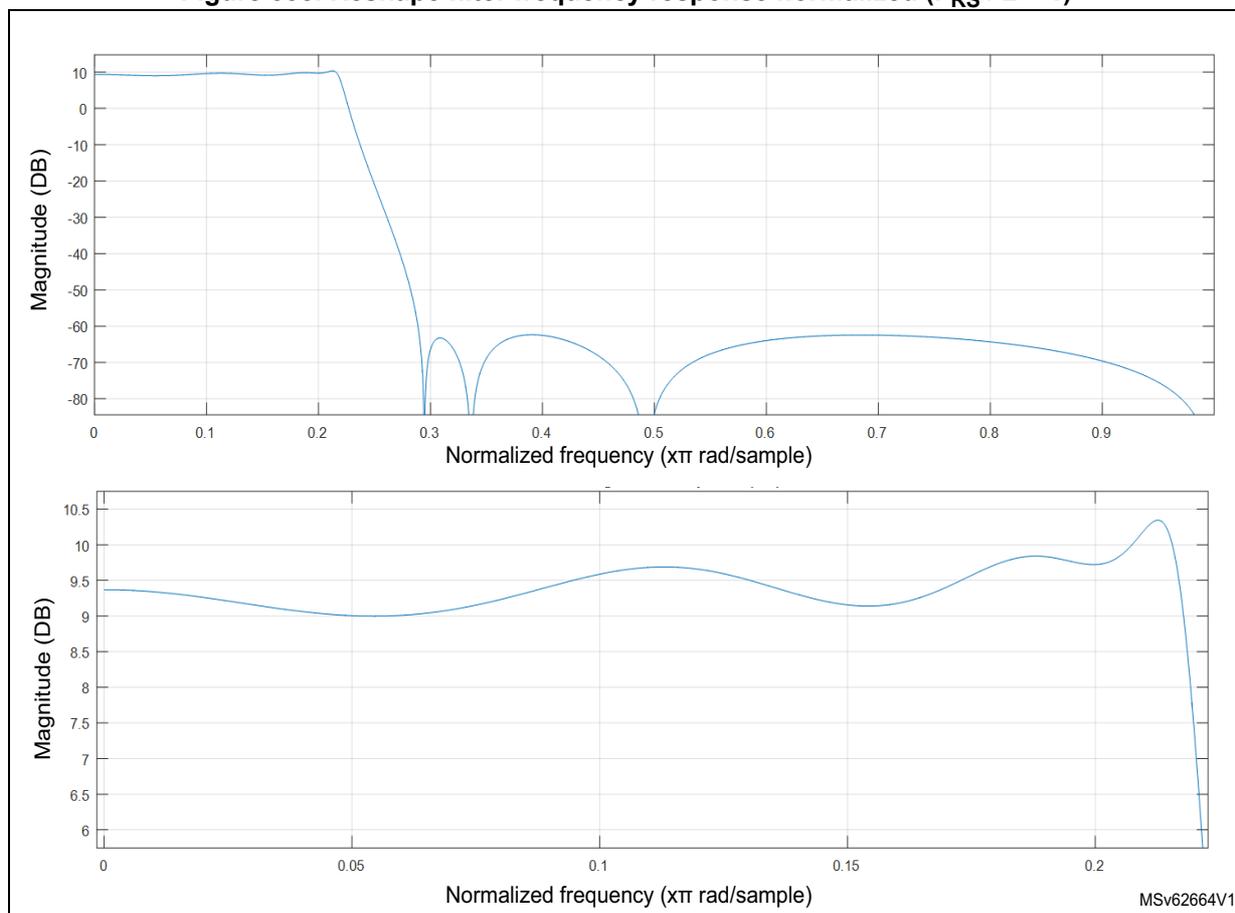

Figure 337. CIC3 and CIC5 frequency response with decimation ratio = 32

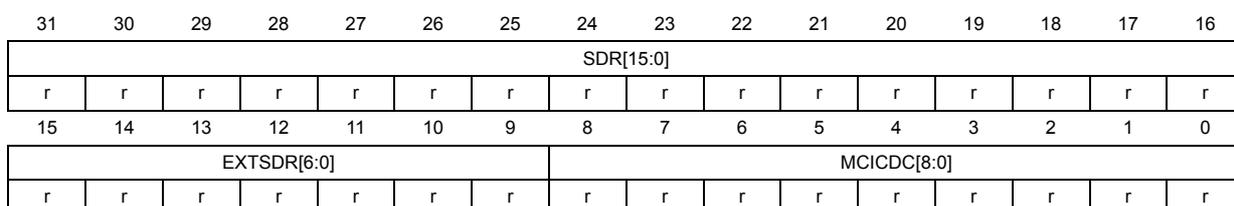

CIC output data size

The size of samples delivered by the CIC ( \( DS_{CIC} \) ) depends on the following parameters:

- • CIC order (N)

- • CIC decimation ratio (D)

- • data size of the input stream ( \( DS_{IN} \) )

The CIC order and decimation ratio must be programmed in order to insure that the data size does not exceed the 26-bit CIC capability.

The following formula gives the output data size ( \( DS_{CIC} \) ) according to the parameters above.

and the CIC gain is given by this formula:

The decimation ratio can be adjusted from 2 to 512 for the main CIC filter and from 1 to 32 for the auxiliary CIC filter.

The table below gives some data output size in bits for some decimation values, when the data source is a full-scale signal coming from the serial interface or from a 12-bit ADC.

Note: \( DS_{IN} = 1 \) bit for a serial bitstream but can be up to 16 bits when coming from the ADCITF.

Table 375. Data size according to CIC order and CIC decimation values

| Decimation | Data size (bits) when

\(

DS_{IN} = 1

\)

bit (data from SITFx) | Data size (bits) when

\(

DS_{IN} = 12

\)

bits (data from ADCITF) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Sinc 1 | Sinc 2 | FastSinc | Sinc 3 | Sinc 4 | Sinc 5 | Sinc 1 | Sinc 2 | FastSinc | Sinc 3 | Sinc 4 | Sinc 5 | |

| 4 | 3 | 5 | 6 | 7 | 9 | 11 | 14 | 16 | 17 | 18 | 20 | 22 |

| 8 | 4 | 7 | 8 | 10 | 13 | 16 | 15 | 18 | 19 | 21 | 24 | - |

| 12 | 5 | 9 | 9 | 12 | 16 | 19 | 16 | 20 | 21 | 23 | - | - |

| 16 | 5 | 9 | 10 | 13 | 17 | 21 | 16 | 20 | 21 | 24 | - | - |

| 24 | 6 | 11 | 12 | 15 | 20 | 24 | 17 | 22 | 23 | - | - | - |

| 32 | 6 | 11 | 12 | 16 | 21 | 26 | 17 | 22 | 23 | - | - | - |

| Decimation | Data size (bits) when DS

IN

= 1 bit (data from SITFx) | Data size (bits) when DS

IN

= 12 bits (data from ADCITF) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Sinc 1 | Sinc 2 | FastSinc | Sinc 3 | Sinc 4 | Sinc 5 | Sinc 1 | Sinc 2 | FastSinc | Sinc 3 | Sinc 4 | Sinc 5 | |

| 64 | 7 | 13 | 14 | 19 | 25 | - | 18 | 24 | 25 | - | - | - |

| 128 | 8 | 15 | 16 | 22 | - | - | 19 | 26 | - | - | - | - |

| 256 | 9 | 17 | 18 | 25 | - | - | 20 | - | - | - | - | - |

| 512 | 10 | 19 | 20 | - | - | - | 21 | - | - | - | - | - |

The LSB part of the data provided by the CIC is not necessarily significant: it depends on the sensor performances and the ability of the CIC to reject the out-of-band noise.

The sample size at CIC output can be adjusted thanks to the SCALE block.

The table below shows the maximum allowed decimation ratio for the CIC filter, depending on the input data size. Bigger decimation ratio causes a wrap-around of the signal at CIC output, for strong input signals.

Note: The MDF cannot detect or prevent a CIC wrap-around.

Table 376. Maximum decimation ratio versus order and input data size| Filter order | Max. decimation ratio when DS IN = 1 bit (SITFx) | Max. decimation ratio when DS IN = 12 bits (ADCITF) | Max. decimation ratio when DS IN = 16 bits (ADCITF) |

|---|---|---|---|

| Sinc 1 | 512 | 512 | 512 |

| Sinc 2 | 512 | 128 | 32 |

| FastSinc | 512 | 90 | 22 |

| Sinc 3 | 322 | 25 | 10 |

| Sinc 4 | 76 | 11 | 5 |

| Sinc 5 | 32 | 6 | 4 |

Scaling (SCALE) and saturation (SAT)

The SCALE block allows the application to adjust the amplitude of the signal provided by the CIC, by steps of 3 dB ( \( \pm 0.5 \) dB).

The signal amplitude can be decreased by up to 8 bits ( \( -48.2 \) dB) and can be increased by up to 12 bits ( \( +72.2 \) dB).

The gain is adjusted by the SCALE[5:0] bitfield in the MDF digital filter configuration register x (MDF_DFLTxCICR) .

SCALE[5:0] can be changed even if the corresponding DLFTx is enabled. During the gain transition, the signal provided by the filter is disturbed.

Due to internal resynchronization, there is a delay of some cycles of mdf_proc_ck clock between the moment where the application writes the new gain, and the moment where the gain is effectively applied to the samples. If the application attempts to write a new gain value while the previous one is not yet applied, this new gain value is ignored. Reading back SCALE[5:0] informs the application on the current gain value.

The table below shows the possible gain values.

Table 377. Possible gain values

| SCALE[5:0] | Gain (dB) | SCALE[5:0] | Gain (dB) | SCALE[5:0] | Gain (dB) | SCALE[5:0] | Gain (dB) |

|---|---|---|---|---|---|---|---|

| 0x20 | - 48.2 | 0x2B | - 14.5 | 0x06 | + 18.1 | 0x11 | + 51.7 |

| 0x21 | - 44.6 | 0x2C | - 12.0 | 0x07 | + 21.6 | 0x12 | + 54.2 |

| 0x22 | - 42.1 | 0x2D | - 8.5 | 0x08 | + 24.1 | 0x13 | + 57.7 |

| 0x23 | - 38.6 | 0x2E | - 6.0 | 0x09 | + 27.6 | 0x14 | + 60.2 |

| 0x24 | - 36.1 | 0x2F | - 2.5 | 0x0A | + 30.1 | 0x15 | + 63.7 |

| 0x25 | - 32.6 | 0x00 | 0.0 | 0x0B | + 33.6 | 0x16 | + 66.2 |

| 0x26 | - 30.1 | 0x01 | + 3.5 | 0x0C | + 36.1 | 0x17 | + 69.7 |

| 0x27 | - 26.6 | 0x02 | + 6.0 | 0x0D | + 39.6 | 0x18 | + 72.2 |

| 0x28 | - 24.1 | 0x03 | + 9.5 | 0x0E | + 42.1 | - | - |

| 0x29 | - 20.6 | 0x04 | + 12.0 | 0x0F | + 45.7 | - | - |

| 0x2A | - 18.1 | 0x05 | + 15.6 | 0x10 | + 48.2 | - | - |

The SAT blocks avoid having a wrap-around of the binary code when the code exceeds its maximal or minimal value.

The MDF performs saturation operations at the following levels:

- • after the SCALE block (performed by the SAT block). The signal is saturated at 24 bits.

- • inside the RSFLT, to insure a good filter behavior

- • at the output of the HPF, to insure that the output signal does not exceed 24 bits

The SATF bit informs the application that a saturation occurred either after the SCALE, inside the RSFLT or after the HPF. In addition, an interrupt can be generated if SATIE is set to 1. As soon as a saturation is detected, the SATF flag is set to 1. It is up to the application to clear this flag in order to be able to detect a new saturation.

Those bits are in the MDF DFLTx interrupt enable register x (MDF_DFLTxIER) and MDF DFLTx interrupt status register x (MDF_DFLTxISR) .

Gain adjustment policy

To get the best MDF performances, it is important to properly adjust the gain value via SCALE[5:0].

A usual way to adjust the gain is to select the SCALE[5:0] value that gives a final signal amplitude as close as possible to the 24-bit full scale, for the maximum input signal.

A way to select the optimal gain is detailed below:

- 1. Check that, for the expected input signal, the data size into the CIC filter does not exceed 26 bits. This can be checked using this formula:

where N represents the CIC order, D the decimation ratio and \( \text{SIN}_{\text{pp}} \) the maximum peak-to-peak amplitude of the input signal.

\( \text{SIN}_{\text{pp}} \) can take:

- – a maximum peak-to-peak amplitude of \( 2 (\pm 1) \) , for samples coming from SITF

- – a maximum peak-to-peak amplitude of 4095 (+ 2047, - 2048) for samples coming from a 12-bit ADC

Example: a \( \text{Sinc}^4 \) can be used with a decimation ratio of 96, if the maximum input signal does not exceed \( \pm 0.35 \) . Indeed:

- 2. Adjust the SCALE value.

To select the most appropriate SCALE value, the user must check if the RSFLT is used or not. If the RSFLT is used, the data size at SCALE output must not exceed 22 bits, otherwise the data size can be up to 24 bits.

The SCALE value in dB is selected using this formula:

where NB is equal to 22 if RSFLT is enabled, or 24 if RSFLT is bypassed. \( \text{SCALE}_{\text{dB}} \) represents the gain value selected by SCALE[5:0].

Example: for a \( \text{Sinc}^4 \) with a decimation ratio of 96 and a \( \text{SIN}_{\text{pp}} \) of 0.7:

- – If the RSFLT is bypassed:

\( \text{SCALE}_{\text{dB}} \) value must be lower than - 11 dB. The closest lower value is - 12dB (SCALE[5:0] = 0x2C).

- – If the RSFLT is enabled:

\( \text{SCALE}_{\text{dB}} \) value must be lower than - 23 dB, the closest lower value is - 24.1 dB (SCALE[5:0] = 0x28).

If SCALE[5:0] is set to a higher value, then a saturation may occur. An event flag informs the user if a saturation occurred.

The table below proposes gain values for different filter configurations, when the data comes from the SITFx, according to the CIC order, and the CIC decimation ratio. This table is not exhaustive, and considers a full-scale input signal (see Section 39.7.5 for details).

Table 378. Recommended maximum gain values versus CIC decimation ratios

| CIC decimation ratio | Gain settings (dB) for configuration SITF + CICx + RSFLT (+ HPF) | Gain settings (dB) for configuration SITF + CICx (+ HPF) | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| CIC5 | CIC4 | CIC3 | CIC2 | CIC1 | CIC5 | CIC4 | CIC3 | CIC2 | CIC1 | |

| 8 | 33.6 | 51.7 | 69.7 | 45.7 | 63.7 | |||||

| 12 | 18.1 | 39.6 | 60.2 | 72.2 | 30.1 | 51.7 | 72.2 | |||

| 16 | 3.5 | 27.6 | 51.7 | 15.6 | 39.6 | 63.7 | ||||

| 20 | - 6.0 | 21.6 | 48.2 | 6.0 | 33.6 | 60.2 | 72.2 | |||

| 24 | - 12.0 | 15.6 | 42.1 | 69.7 | 0 | 27.6 | 54.2 | |||

| 28 | - 20.6 | 9.5 | 36.1 | 66.2 | 72.2 | - 8.5 | 21.6 | 48.2 | 72.2 | |

| 32 | -26.6 | 3.5 | 33.6 | 63.7 | - 14.5 | 15.6 | 45.7 | |||

| 48 | - | - 8.5 | 24.1 | 57.7 | - | 3.5 | 31.6 | 69.7 | ||

| 64 | - | - 20.6 | 15.6 | 51.7 | - | -8.5 | 27.6 | 63.7 | ||

| 128 | - | - | - 2.5 | 39.6 | - | - | 9.5 | 51.7 | ||

| 256 | - | - | - 20.6 | 27.6 | - | - | -8.5 | 39.6 | ||

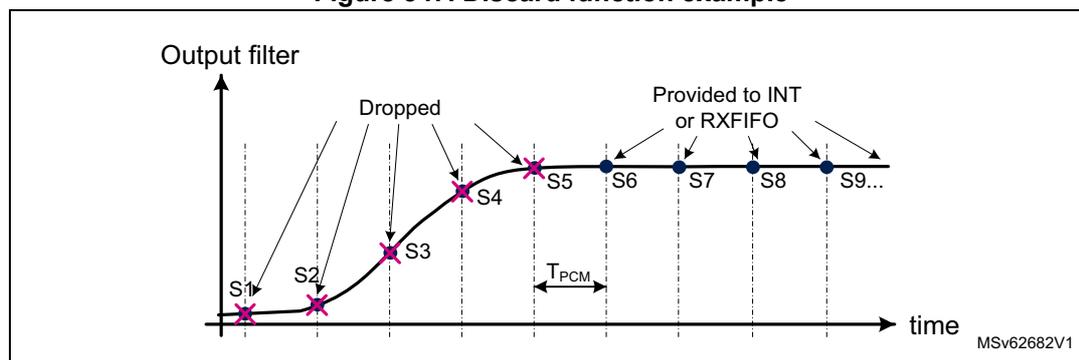

Reshaping filter (RSFLT)

In addition to the CIC, the MDF offers a reshaping IIR filter mainly dedicated to the audio application but also usable in other applications.

When the RSFLT is used, the sample size at its input must not exceed 22 bits.

The samples at the RSFLT output can be decimated by four or not according to the RSFLTD bit in the MDF reshape filter configuration register x (MDF_DFLTxRSFR) .

The RSFLT can be bypassed by setting RSFBYP to 1 in MDF_DFLTxRSFR .

The table below shows which sampling rate must be provided to the RSFLT in order to process the most common audio streams.

The RSFLT cutoff frequency ( \( F_C \) ) depends on the sample rates at its input ( \( F_{RS} \) ), and is given by the following formula:

Table 379. Most common microphone settings

| Sample rate (kHz) at RSFLT ( \( F_{RS} \) ) | Pass band (kHz) | D2 | PCM sampling rate (kHz) |

|---|---|---|---|

| 32 | 3.55 | 4 | 8 |

| 64 | 7.1 | 4 | 16 |

| 128 | 14.2 | 4 | 32 |

| 192 | 21.3 | 4 | 48 |

The figure below shows the frequency response of the reshape filter.

Figure 338. Reshape filter frequency response normalized ( \( F_{RS} / 2 = 1 \) )

The RSFLT gain is about 9.3 dB, so the output data size is a little bit lower than 24 bits for a 22-bit wide input signal.

The RSFLT takes 24 clock cycles of mdf_proc_ck clock to process one sample at \( F_{RS} \) . When the RSFLT is enabled, the application must insure that the mdf_proc_ck is at least 24 times faster \( F_{RS} \) .

The RSFLT generates an event (rfov_evt) and sets the RFOVRF flag, if the RSFLT receives a new sample while the previous one is still under processing.

When RFOVRF is set, the samples provided by the RSFLT are invalid. The application must then stop the data acquisition and provide a faster mdf_proc_ck clock to the RSFLT.

High-pass filter (HPF)

The high-pass filter suppresses the low-frequency content from the final output data stream in case of continuous conversion mode. The high-pass filter can be enabled or disabled via HPFBYP in the MDF reshape filter configuration register x (MDF_DFLTxRSFR) .

The HPF is useful when there is parasitic low-frequency noise (or DC signal) in the input data source and it must be removed from the final data.

The HPF is a first order IIR filter and the cut-off frequency can be selected via HPFC[1:0] in the MDF reshape filter configuration register x (MDF_DFLTxRSFR) , among the following values:

- • \( 0.000625 \times F_{PCM} \)

- • \( 0.00125 \times F_{PCM} \)

- • \( 0.00250 \times F_{PCM} \)

- • \( 0.00950 \times F_{PCM} \)

Table 380. HPF 3 dB cut-off frequencies examples

| HPFC | 3 dB cut-off frequency for common \( F_{PCM} \) frequencies (Hz) | ||

|---|---|---|---|

| \( F_{PCM} = 8 \) kHz | \( F_{PCM} = 16 \) kHz | \( F_{PCM} = 48 \) kHz | |

| 0 | 5 | 10 | 30 |

| 1 | 10 | 20 | 60 |

| 2 | 20 | 40 | 120 |

| 3 | 76 | 152 | 456 |

The HPF output is saturated at 24 bits. The SATF flag is set if a sample is saturated.

Offset error compensation (OEC)

Each digital filter has its own OEC. The offset correction is performed by subtracting to the signal provided by the CIC, the OFFSET[25:0] in the MDF offset error compensation control register x (MDF_OECxCR) .

Due to the internal resynchronization, there is a delay of some cycles of mdf_proc_ck clock between the moment where the application writes the new offset, and the moment where the new offset value is effectively applied to the samples. If the application attempts to write a new offset value while the previous one is not yet applied, this new offset value is ignored. Reading back OFFSET[25:0] informs the application on the current offset value.

Integrator (INT)

The INT performs additional decimation and a resolution increase of data coming from the digital filter. The INT simply performs the sum of data from a digital filter for a given number of data samples from a filter.

The INT is enabled by setting INTVAL[6:0] to a value different from 0.

The amount of integrated values can be defined by INTVAL[6:0] in the range of 2 to 128.

In order to control the data width at the integrator output, the resulting data can be divided by 1, 4, 32 or 128. This feature is controlled by INTDIV[1:0].

39.4.9 Out-of-limit detector (OLD)

The OLD triggers an event when a signal reaches or crosses given maximum and minimum threshold values. The generated event can drive an interrupt or break signals (mdf_break[3:0]) when conditions are met.

The OLD can be used only if the CIC filter is configured in motor and sensing mode (CICMOD[2:0] = 0xx).

The OLD takes the input signal selected by the main filter, process it using a Sinc N or FastSinc filter (ACIC), and compares the resulting signal to programmed thresholds.

The OLD is enabled via the OLDEN bit in MDF_OLD0CR. Once enabled, the input data are continuously monitored. There is no need to have the DFLT x enabled for using the OLD function.

The MDF offers a high- and low-threshold register that are compared with given data values.

The application can generate an event if the signal is inside or outside the boundary defined by those two thresholds. This behavior is controlled via THINB in the MDF_OLD0CR.

If the application only wants to generate an event when the input signal is higher than OLDTHH, then THINB and OLDTHL must both be cleared to 0.

If the application only wants to generate an event when the input signal is lower than OLDTHH, then THINB must be set to 1 and OLDTHL must be cleared to 0.

Note: It is not recommended to set a OLDTHL to a value bigger than OLDTHH.

The response time of the OLD depends on several parameters, the most important are listed hereafter:

- • sampling rate frequency used by the external sensor

- • ACIC decimation ratio

- • ACIC order

The OLD can be used for over-current detection but also as current limiter if the PWM signal is generated by a timer receiving a old_brk signal. Generally, to get a fast response time for over-current detection, it is recommended to use the ACIC with lowest order as possible and the minimum decimation ratio. FastSinc is also a good choice for over-current detection.

The application must perform a trade-off between the filter resolution and the response time.

Figure 339. Out-of-limit detector thresholds

![Figure 339: Out-of-limit detector thresholds. The diagram shows the internal logic of the Out-of-limit detector (OLD) and a timing diagram. The logic block includes a 'Logic' unit with inputs THINB, OLDTHH[25:0], and OLDTHL[25:0]. It outputs 'To interrupt' signals (old_thh, old_evt, old_thl) and 'To break' signals (old_brk). The 'To interrupt' signals pass through comparators and a D2 flip-flop with ACIC[3:1] and ACICF registers, receiving input from a DATSRC MUX. The timing diagram shows a signal fluctuating between +2^25 - 1 and -2^25. It highlights the OLDTHH[25:0] and OLDTHL[25:0] threshold levels. Below, it shows the THHF and THLF flags, the mdf_evt_it[x]/mdf_it[x] interrupt signal (due to old_evt[x]), and the old_brk[x] break signal. Two instances of 'Writing OLDF to 1' are shown at position A, where the interrupt is cleared but re-asserted because the signal remains outside the gray threshold area. The THINB signal is shown as active low (THINB = 0).](/RM0456-STM32U5/ab290ac0dc0882f537c98f6de0958aaa_img.jpg)

Status flags are available in order to inform the application that an OLD event is detected. Latched events are cleared by writing 1 into the OLDF bit.

As shown in Figure 339 , when THINB = 0, the interrupt signal remains active as long as the signal is outside the gray area. At position A, the application clears the interrupt, but the interrupt is re-asserted because the signal is still outside the gray area. When the application clears OLDF, THHF and THLF are cleared as well.

An OLD event can be assigned to one or several break output signals (mdf_break[3:0]). The break signal assignment to a given OLD event is done by BKOLD[3:0] in the MDF out-of limit detector control register x (MDF_OLDFxCR) .

Note: The generation of break signals is independent from the interrupts generation.

OLD activation sequence example

- 1. Enable and configure CKGEN.

- 2. Set OLDEN to 0.

- 3. Wait for OLDACTIVE = 0. If OLDEN was previously enabled, this phase can take two periods of mdf_hclk and two periods of mdf_proc_ck.

- 4. Program BKOLD[3:0], ACICN[1:0], ACICD[4:0], THINB, OLDTHL[25:0] and OLDTHH[25:0].

- 5. Set OLDEN to 1.

39.4.10 Digital filter acquisition modes

The MDF offers the following modes to perform a data capture:

- • asynchronous continuous acquisition mode

- • asynchronous single-shot acquisition mode

- • synchronous continuous acquisition mode

- • synchronous single-shot acquisition mode

- • window continuous acquisition mode

- • synchronous snapshot acquisition mode

For each filter, one of these modes can be selected independently.

Note: To perform a data capture, the filters, the interfaces providing the data (SITFx or ADCITF) and the CKGEN must be enabled. If needed, MDF_CCK0 or MDF_CCK1 must be enabled as well.

The filter can be stopped immediately when DFLTEN is set to 0. This resets the filters and flushes the RXFIFO of the corresponding filter path. The DFLTACTIVE flag also goes back to 0 when the RXFIFO and the filters are reset.

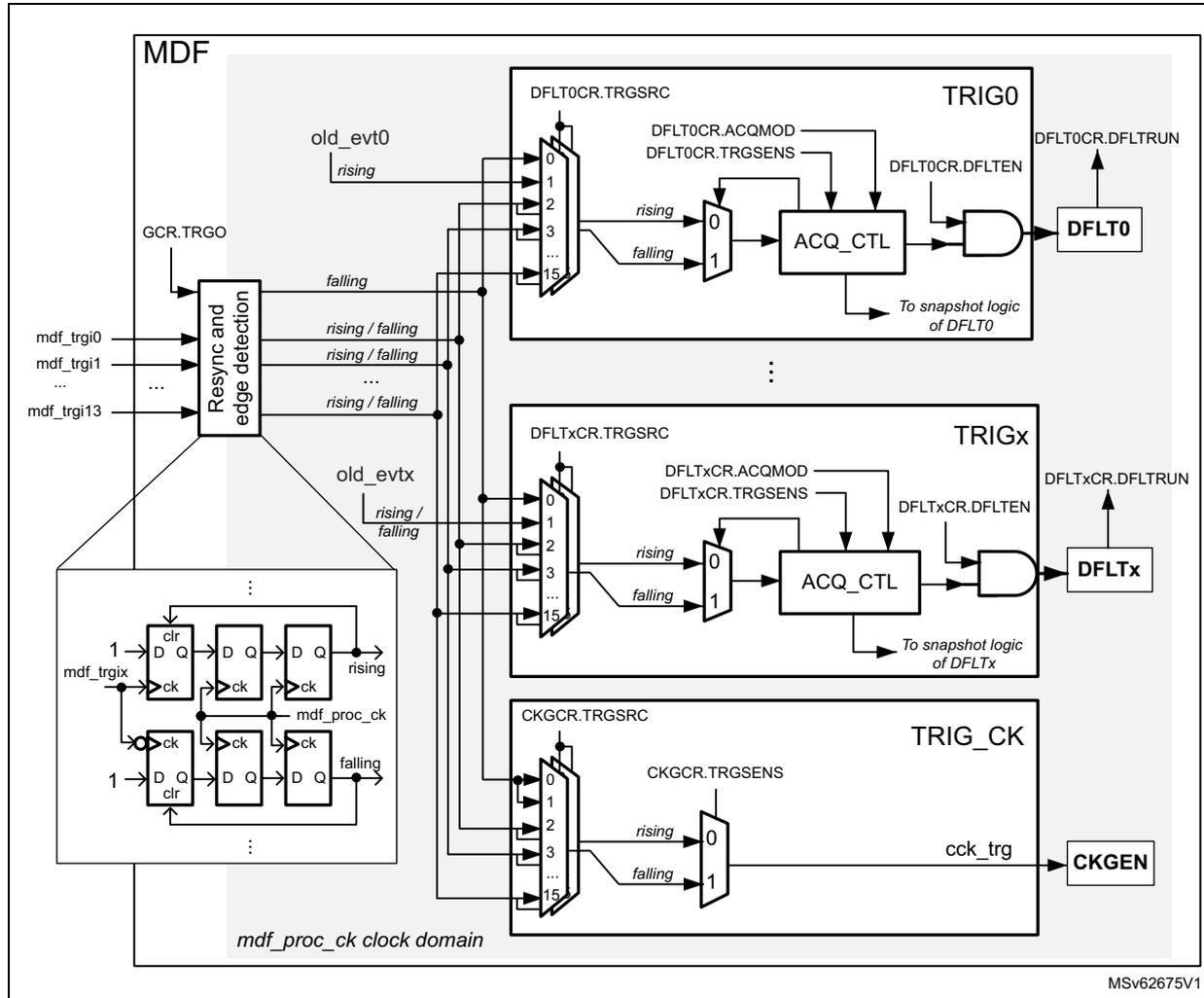

The figure below shows a simplified view of the trigger logic available for each filter and for the clock generator.

Figure 340. Trigger logic for DFLT and CKGEN

A block common to all TRIG blocks performs the rising and falling edges detection and the resynchronization of the input triggers to the mdf_ker_ck clock domain. This implementation allows the application to use triggers with pulse width smaller than the mdf_ker_ck period.

In synchronous modes, the TRIG block offers the possibility to select one of the following trigger sources:

- • mdf_trgi[13:0] signals (refer to Table 370 for the trigger connections)

- • TRGO bit in MDF_GCR

- • OLD event of each filter path

The edge sensitivity can also be selected, except for TRGO and OLD events.

Asynchronous continuous acquisition mode

This mode allows the application to start a continuous acquisition on one or several filters by simply writing their DFLTEN bits to 1.

The Asynchronous continuous acquisition mode is selected when ACQMOD[2:0] = 0.

The sequence below shows the most important programming steps (assuming that DFLTEN bits of the filters are set to 0):

- 1. Configure and enable the clock generator (CKGEN) so that the mdf_proc_ck frequency is compatible with the targeted application (see examples in Table 384 ).

- 2. Enable the CKGEN (CKGDEN = 1) and, if needed, enable the MDF_CCK0 and MDF_CCK1 clocks.

- 3. Program the filter configuration and set the ACQMOD[2:0] to 0.

- 4. Set to 1 the SITFEN bit of the requested data interfaces.

- 5. Before setting DFLTEN to 1, wait for DFLTACTIVE = 0: it insures that the previous filter deactivation sequence terminated properly.

- 6. When DFLTEN is set to 1 for the filters to enable, the acquisition sequence starts immediately.

The figure below shows a simplified example of the samples generated by the DFLT x .

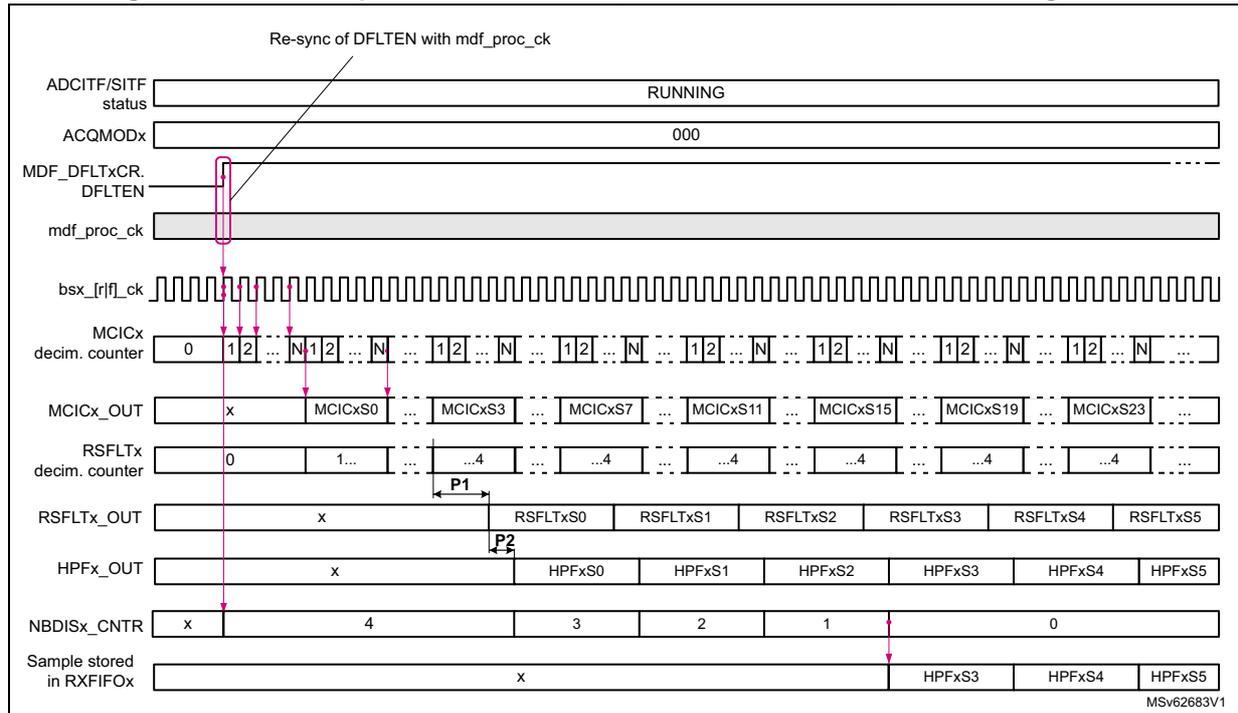

Figure 341. Asynchronous continuous mode (ACQMOD[2:0] = 0)

![Timing diagram for Asynchronous continuous mode (ACQMOD[2:0] = 0). The diagram shows five signal lines over time. 1. MDF_DFLTxC.R.DFLTEN: A control signal that goes high to start acquisition and low to stop it. 2. DFLTx output: Shows a 'Discard' phase (indicated by 'X' values) followed by valid samples S1, S2, ..., SN. When DFLTEN goes low, the output goes to 'OFF' and samples are 'Dropped!'. 3. MDF_DFLTxC.R.DFLTRUN: A signal that goes high when DFLTEN goes high and low when DFLTEN goes low. 4. MDF_DFLTxC.R.DFLTACTIVE: A signal that goes high when DFLTEN goes high and returns to low when the filter chain is reset. 5. MDF_CCK/CKI: A continuous clock signal. A note at the bottom left states 'Note: the discard phase is optional.' and a code 'MSv62676V1' is at the bottom right.](/RM0456-STM32U5/6aae23e438437495093d655eb75132c8_img.jpg)

Note: the discard phase is optional. MSv62676V1

Note: The acquisition can be stopped by setting DFLTEN back to 0. This resets the filter and flushes the RXFIFO, so the samples located into the RXFIFO are lost. The ongoing DMA transfer is properly terminated. DFLTACTIVE goes back to 0 when the filter chain is reset and the RXFIFO flushed.

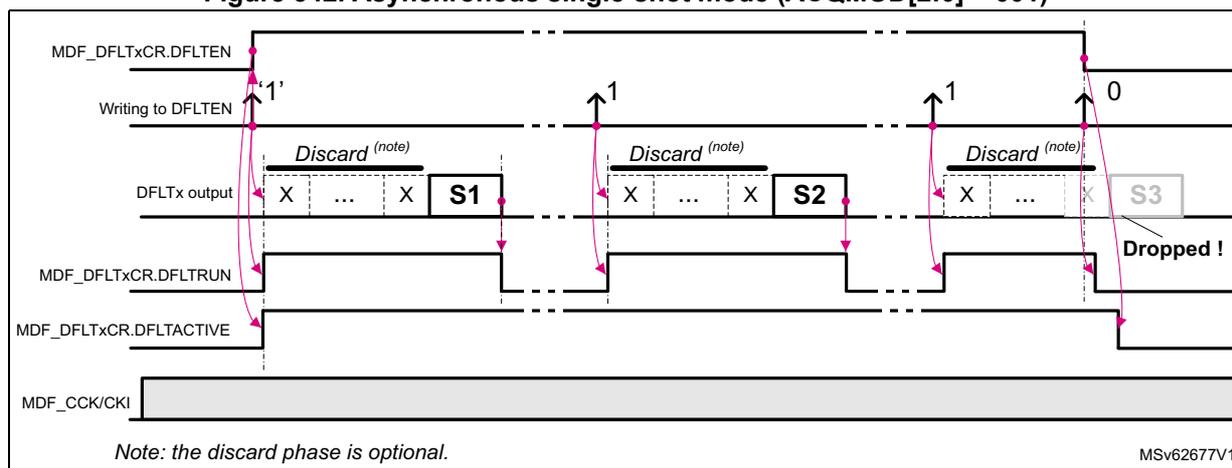

Asynchronous single-shot acquisition mode

This mode allows the application to start the acquisition of one sample on one or several filters by simply writing their DFLTEN bits to 1.

The Asynchronous single-shot acquisition mode is selected when ACQMOD[2:0] = 001.

The sequence below shows the most important programming steps (assuming that DFLTEN bits of the filters are cleared to 0):

- 1. Configure and enable the clock generator (CKGEN), so that the mdf_proc_ck frequency is compatible with the targeted application (see examples in Table 380 ).

- 2. Enable the CKGEN (CKGDEN = 1) and, if needed, enable the MDF_CCK0 and MDF_CCK1 clocks.

- 3. Program the filter configuration and set the ACQMOD[2:0] to 001.

- 4. Set to 1 the SITFEN bit of the requested data interfaces.

- 5. Before setting DFLTEN to 1, wait for DFLTACTIVE = 0: it insures that the previous filter deactivation sequence terminated properly.

- 6. When DFLTEN is set to 1 for the filters to enable, each selected filter provides one data to the RXFIFO and stops the acquisition.

To trigger a new acquisition, for each filter, the application must:

- 1. Check that the previous acquisition is completed, by waiting that DFLTRUN = 0.

- 2. Set again DFLTEN to 1.

This sequence can be repeated every time a new data must be converted.

As shown in the Figure 342 , every time DFLTEN is set to 1, an acquisition sequence is triggered. The first samples provided by the filter can be discarded if needed. At the end of each conversion, the decimation counters and filter taps are reset, and the filter is ready to start a new conversion.

If the DFLTEN is set to 0 while an acquisition is ongoing, the ongoing conversion is stopped (in the example, S3 is lost). This situation can be avoided with the following steps:

- 1. Wait for DFLTRUN = 0.

- 2. Read the sample from the RXFIFO.

- 3. Set DFLTEN to 0.

Figure 342. Asynchronous single-shot mode (ACQMOD[2:0] = 001)

Note: the discard phase is optional.

MSV62677V1

Note: The acquisition can be stopped by setting DFLTEN back to 0. This resets the filter and flushes the RXFIFO, so the samples located into the RXFIFO are lost. The ongoing DMA transfer is properly terminated. DFLTACTIVE goes back to 0 when the filter chain is reset and the RXFIFO flushed.

Synchronous continuous acquisition mode

This mode allows the application to start a continuous acquisition on one or several filters by using the following trigger sources:

- • one of the mdf_trg[13:0] signals

- • OLD event of the corresponding filter

- • TRGO bit

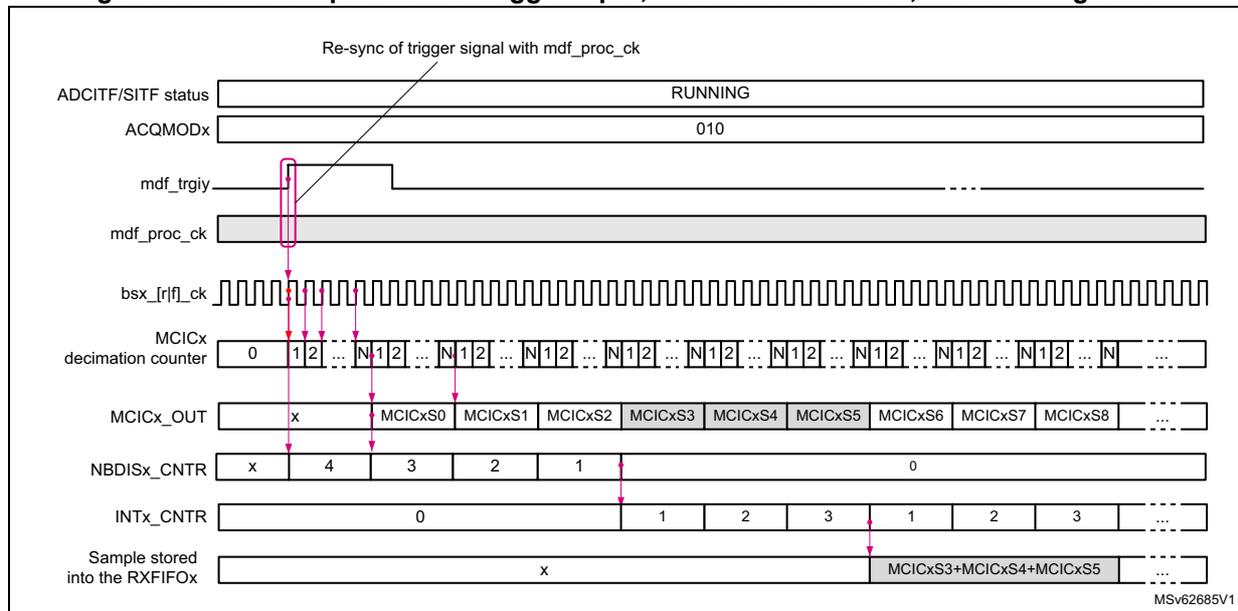

The Synchronous continuous acquisition mode is selected when ACQMOD[2:0] = 010.

The sequence below shows the most important programming steps (assuming that DFLTEN bits of the filters are set to 0):

- 1. Configure and enable the clock generator (CKGEN), so that the frequency of mdf_proc_ck clock is compatible with the targeted application (see examples in Table 380 ).

- 2. Enable the CKGEN (CKGDEN = 1) and, if needed, enable the MDF_CCK0 and MDF_CCK1 clocks.

- 3. Program the filter configuration, and set the ACQMOD[2:0] to 010.

- 4. Set to 1 the SITFEN bit of the requested data interfaces.

- 5. Select the proper trigger source and sensitivity for each filter.

- 6. Before setting DFLTEN to 1, wait for DFLTACTIVE = 0: it insures that the previous filter deactivation sequence terminated properly.

- 7. Set DFLTEN to 1 for the filters to enable.

- 8. When the trigger condition is met, the filters start the acquisition.

The TRGSENS bit allows the selection of the trigger edge (rising or falling). The trigger is ignored if an acquisition is ongoing or if DFLTEN is set to 0.

The figure below shows a simplified example where the trigger logic is sensitive to a rising edge trigger (TRGSENS = 0). The first rising edge of the trigger signal is ignored because DFLTEN = 0. The next rising edge is taken into account and starts the acquisition. All other rising edges are ignored. The trigger logic is re-initialized when DFLTRUN goes back to 0.

Figure 343. Synchronous continuous mode (ACQMOD[2:0] = 010)

![Timing diagram for synchronous continuous mode (ACQMOD[2:0] = 010). The diagram shows five signal lines over time. 1. MDF_DFLTxCR.DFLTEN: A control signal that is initially low, then goes high to start acquisition, and later goes low to stop it. 2. mdf_trg[y]: A trigger signal that is sensitive to rising edges. The first rising edge occurs while DFLTEN is low and is ignored. Subsequent rising edges while DFLTEN is high start the acquisition. 3. DFLTx output: Shows the filter's output sequence. It starts with a 'Discard' phase (indicated by 'X' and '...' symbols), followed by valid samples 'S1', 'S2', and so on, up to 'SN'. When DFLTEN goes low, the output becomes 'OFF'. 4. MDF_DFLTxCR.DFLTRUN: A signal that goes high when DFLTEN goes high and returns to low when DFLTEN goes low. 5. MDF_DFLTxCR.DFLTACTIVE: A signal that goes high when DFLTEN goes high and returns to low when DFLTRUN goes low. A note indicates that the discard phase is optional. A label 'Dropped !' points to a rising edge of the trigger signal that occurs while the filter is already active (DFLTACTIVE is high) and is therefore ignored. A reference code 'MSv62678V1' is in the bottom right corner.](/RM0456-STM32U5/b8208410ca7075da81993a58affe1175_img.jpg)

Note: The acquisition can be stopped by setting DFLTEN back to 0. This resets the filter and flushes the RXFIFO, so the samples located into the RXFIFO are lost. The ongoing DMA transfer is properly terminated. DFLTACTIVE goes back to 0 when the filter chain is reset and the RXFIFO flushed.

Synchronous single-shot acquisition mode

This mode allows the application to start a single acquisition on one or several filters by using the following trigger sources:

- • one of the mdf_trg[13:0] signals

- • OLD event of the corresponding filter

- • TRGO bit

The Synchronous single-shot acquisition mode is selected when ACQMOD[2:0] = 011.

The sequence below shows the most important programming steps (assuming that DFLTEN bits of the filters are set to 0):

- 1. Configure and enable the clock generator (CKGEN), so that the frequency of mdf_proc_ck clock is compatible with the targeted application (see examples in Table 380 ).

- 2. Enable the CKGEN and, if needed, enable the MDF_CCK0 and MDF_CCK1 clocks.

- 3. Program the wanted filter configuration and set the ACQMOD[2:0] to 011.

- 4. Set to 1 the SITFEN bit of the requested data interfaces.

- 5. Select the proper trigger source and sensitivity for each filter.

- 6. Before setting DFLTEN to 1, wait for DFLTACTIVE = 0: it insures that the previous filter deactivation sequence has been properly terminated.

- 7. Set DFLTEN to 1 for the filters to enable.

- 8. Then when the trigger condition is met, the filters start the acquisition and provide one data to the RXFIFO, then the filters are ready to accept a new trigger.

TRGSENS allows the selection of the trigger edge (rising or falling). The trigger is ignored if an acquisition is ongoing or if DFLTEN is set to 0.

The figure below shows a simplified example where the trigger logic is sensitive to a rising edge trigger (TRGSENS = 0). Every time a trigger rising edge is detected with DFLTEN = 1, an acquisition sequence is triggered. The first samples provided by the filter can be discarded if needed. At the end of each conversion, the decimation counters and filter taps are reset. DFLTRUN is set to 0 and the filter is ready to start a new conversion.

Figure 344. Synchronous single-shot mode (ACQMOD[2:0] = 011)

![Timing diagram for synchronous single-shot mode (ACQMOD[2:0] = 011). The diagram shows the relationship between several signals over time. 1. MDF_DFLTxC.R.DFLTEN: Control signal that enables the filter. It is set high before the first trigger and low before the second trigger. 2. mdf_trgi[y]: Trigger signal. It shows two rising edges. The first rising edge occurs while DFLTEN is high, initiating an acquisition. The second rising edge occurs while DFLTEN is low, and thus is ignored. 3. DFLTx output: Filter output. Following the first valid trigger, it outputs a series of samples labeled 'X', '...', 'X', followed by a valid sample 'S1'. A 'Discard (note)' phase is indicated for the initial 'X' samples. Following the second (invalid) trigger, it outputs 'X', '...', 'X', followed by 'S2', which is labeled 'Dropped !' because the trigger was invalid. 4. MDF_DFLTxC.R.DFLTRUN: Run signal. It goes high when a valid trigger occurs and returns to low when the acquisition is complete (after S1). 5. MDF_DFLTxC.R.DFLTACTIVE: Active signal. It goes high when DFLTEN is set high and returns to low when DFLTRUN goes low. 6. MDF_CCK/CKI: Clock signal, shown as a constant high-frequency signal. A note at the bottom states: 'Note: the discard phase is optional.' The diagram is labeled MSv62679V1.](/RM0456-STM32U5/9fc30839c2fb55513a615c48dcdfac40_img.jpg)

Note: The acquisition can be stopped by setting DFLTEN back to 0. This resets the filter and flushes the RXFIFO, so the samples located into the RXFIFO are lost. The ongoing DMA transfer is properly terminated. DFLTACTIVE goes back to 0 when the filter chain is reset and the RXFIFO flushed.

Figure 344 shows a case where DFLTEN is cleared to 0 while an acquisition is ongoing: thus the sample S2 is lost. This situation can be avoided with the following steps:

- 1. Wait for DFLTRUN = 0.

- 2. Read the sample from the RXFIFO.

- 3. Clear DFLTEN to 0.

Note: The ongoing DMA transfer is properly terminated.

Window continuous acquisition mode

This mode allows the application to start or stop a continuous acquisition on one or several filters controlled by consecutive edges of one of the following trigger sources:

- • one of the mdf_trg[13:0] signals

- • TRGO bit

The window continuous acquisition mode is selected when ACQMOD[2:0] = 100.

The sequence below shows the most important programming steps (assuming that DFLTEN bits of the filters are set to 0):

- 1. Configure and enable the clock generator (CKGEN), so that the frequency of mdf_proc_ck clock is compatible with the targeted application (see examples in Table 380 ).

- 2. Enable the CKGEN and, if needed, enable the MDF_CCK0 and MDF_CCK1 clocks.

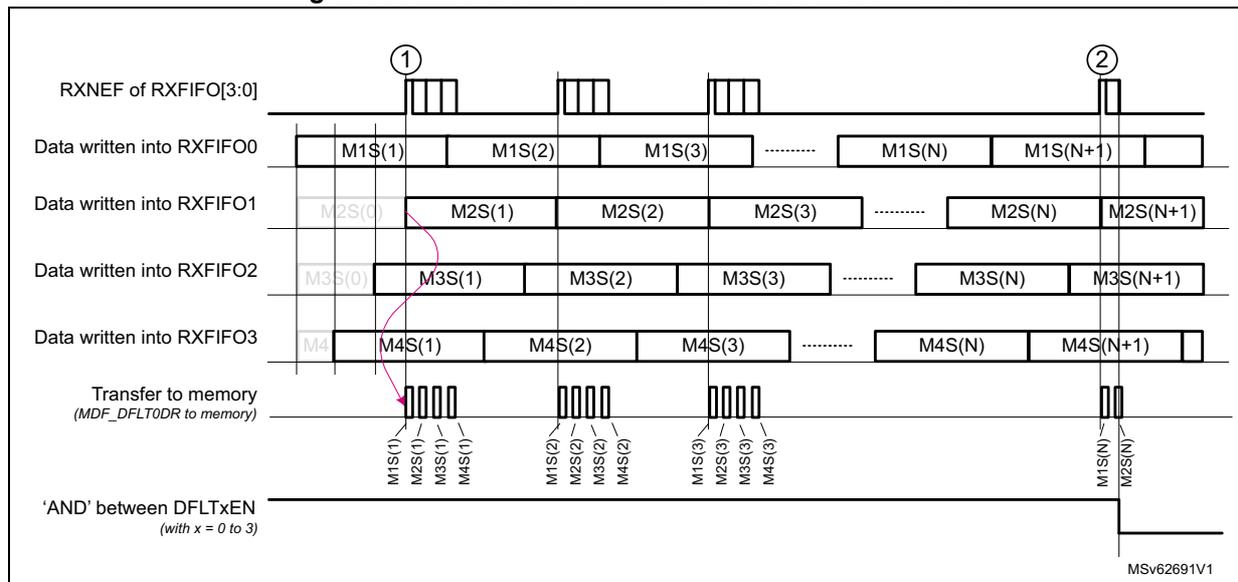

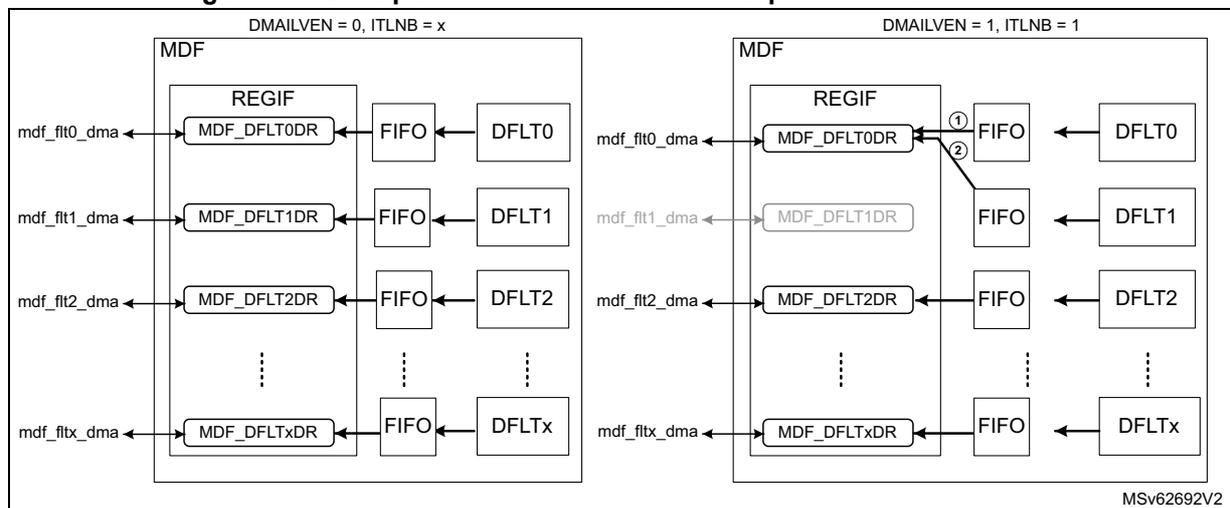

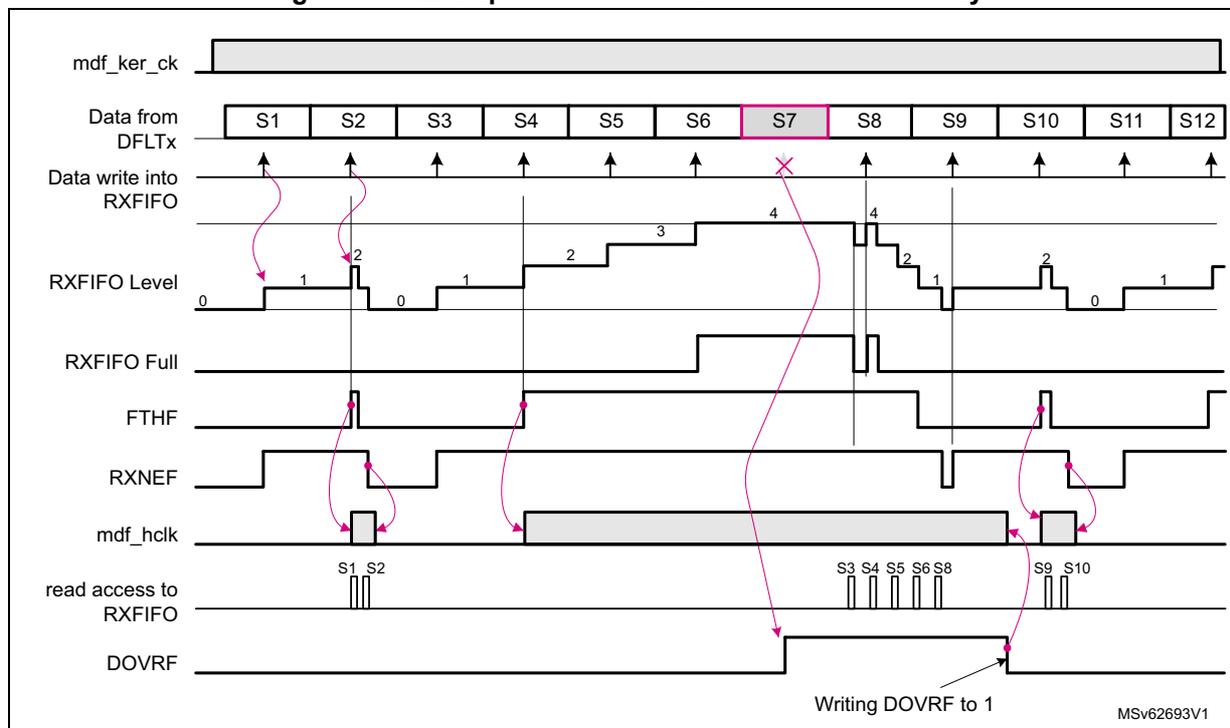

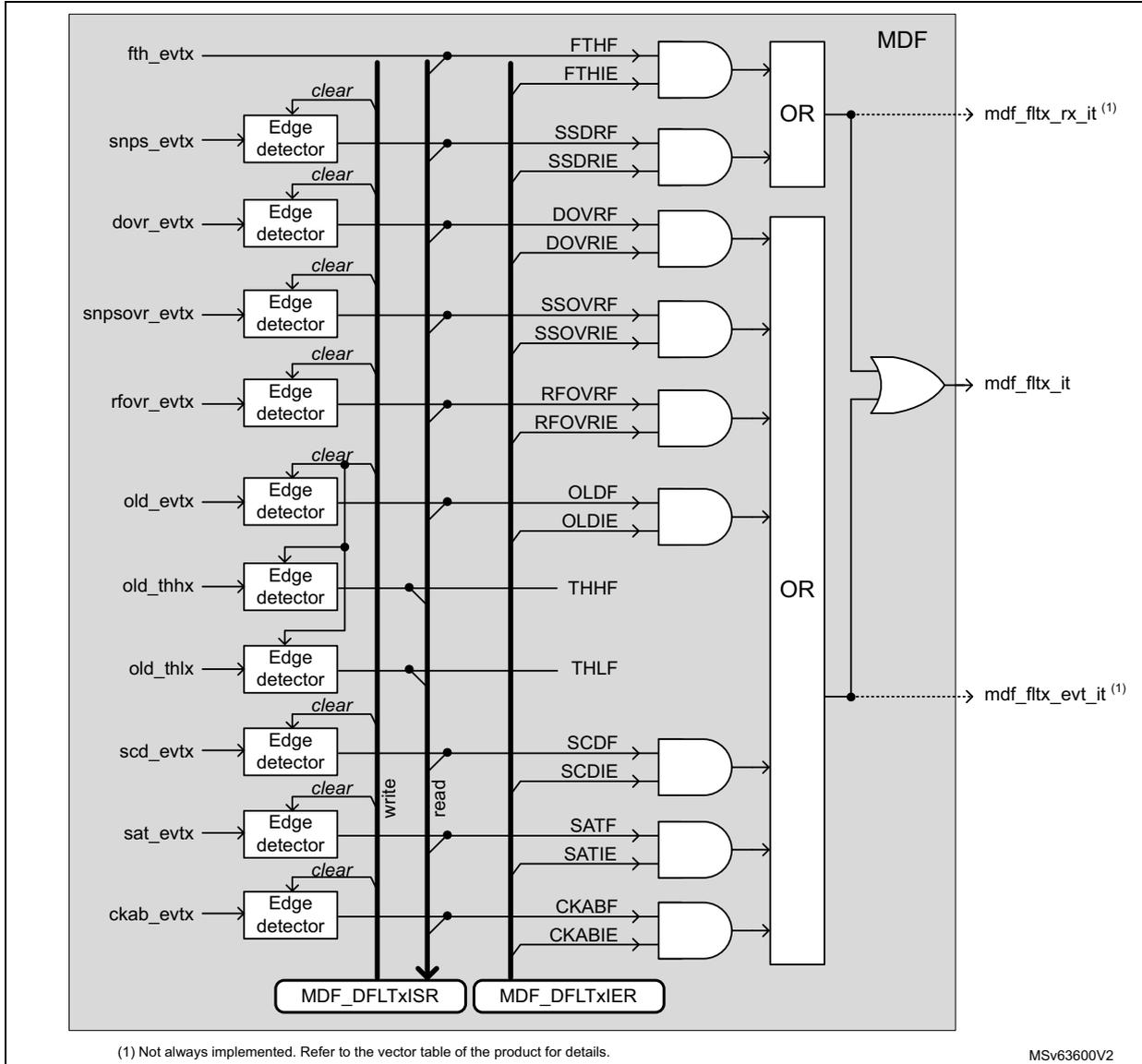

- 3. Program the wanted filter settings and set the ACQMOD[2:0] to 100.