28. Octo-SPI interface (OCTOSPI)

28.1 OCTOSPI introduction

The OCTOSPI supports most external serial memories such as serial PSRAMs, serial NAND and serial NOR flash memories, HyperRAM™ and HyperFlash™ memories, with the following functional modes:

- • indirect mode: all the operations are performed using the OCTOSPI registers to preset commands, addresses, data, and transfer parameters.

- • automatic status-polling mode: the external memory status register is periodically read and an interrupt can be generated in case of flag setting. This feature is only available in regular-command protocol.

- • memory-mapped mode: the external memory is memory mapped and it is seen by the system as if it was an internal memory, supporting both read and write operations.

The OCTOSPI supports the following protocols with associated frame formats:

- • the regular-command frame format with the command, address, alternate byte, dummy cycles, and data phase

- • the HyperBus™ frame format

28.2 OCTOSPI main features

- • Functional modes: indirect, automatic status-polling, and memory-mapped

- • Read and write support in memory-mapped mode

- • External (P)SRAM memory support

- • Support for single, dual, quad, and octal communication

- • Dual memory configuration, where eight bits can be sent/received simultaneously by accessing two quad memories in parallel

- • SDR (single-data rate) and DTR (double-transfer rate) support

- • Data strobe support

- • Fully programmable opcode

- • Fully programmable frame format

- • Support wrapped-type access to memory in read direction

- • HyperBus support

- • Integrated FIFO for reception and transmission

- • Asynchronous bus clock versus kernel clock support

- • 8-, 16-, and 32-bit data accesses allowed

- • DMA protocol support

- • DMA channel for indirect mode operations

- • Interrupt generation on FIFO threshold, timeout, operation complete, and access error

- • AHB interface with transaction acceptance limited to one: the interface accepts the next transfer on AHB bus only once the previous is completed on memory side.

28.3 OCTOSPI implementation

Table 249. Instances on STM32U5 Series devices

| Devices | OCTOSPI1 | OCTOSPI2 | OCTOSPIM | HSPI1 |

|---|---|---|---|---|

| STM32U535/545 | X | - | - | - |

| STM32U575/585 | X | X | X | - |

| STM32U59x/5Ax | X | X | X | X |

| STM32U5Fx/5Gx | X | X | X | X |

Table 250. OCTOSPI/HSPI implementation

| OCTOSPI feature | OCTOSPI1/2 | HSPI1 |

|---|---|---|

| HyperBus standard compliant | X | X |

| Xccela standard compliant | X | X |

| XSPI (JESD251C) standard compliant | X | X |

| AMBA ® AHB compliant data interface | X | X |

| Dual AHB interface | X | X |

| Asynchronous AHB clock versus kernel clock | X | X |

| Functional modes: indirect, automatic status-polling, and memory-mapped | X | X |

| Read and write support in memory-mapped mode | X | X |

| Dual-quad configuration | X | X |

| Dual-octal configuration | - | X |

| SDR (single-data rate) and DTR (double-transfer rate) | X | X |

| Data strobe (DS,DQS) | X | X |

| Fully programmable opcode | X | X |

| Fully programmable frame format | X | X |

| Integrated FIFO for reception and transmission | X | X |

| 8-, 16-, and 32-bit data accesses | X | X |

| Interrupt on FIFO threshold, timeout, operation complete, and access error | X | X |

| Bus error bit | - | - |

| Address offset | - | - |

| Compliant with dual-OCTOSPI arbiter (communication regulation) | X | - |

| Extended CSHT timeout | X | X |

| Memory-mapped write | X | X |

| Refresh counter | X | X |

| GPDMA interface | X | X |

| High-speed interface | - | X |

| Dual chip select | - | - |

Table 250. OCTOSPI/HSPI implementation (continued)

| OCTOSPI feature | OCTOSPI1/2 | HSPI1 |

|---|---|---|

| Extended external memory | - | - |

| Prefetch disable | - | - |

| Prefetch hardware software | - | - |

28.4 OCTOSPI functional description

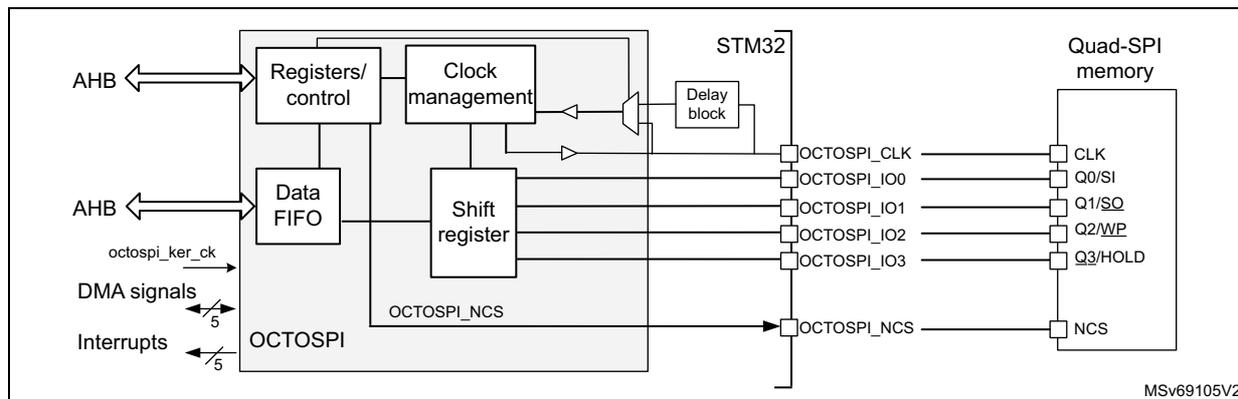

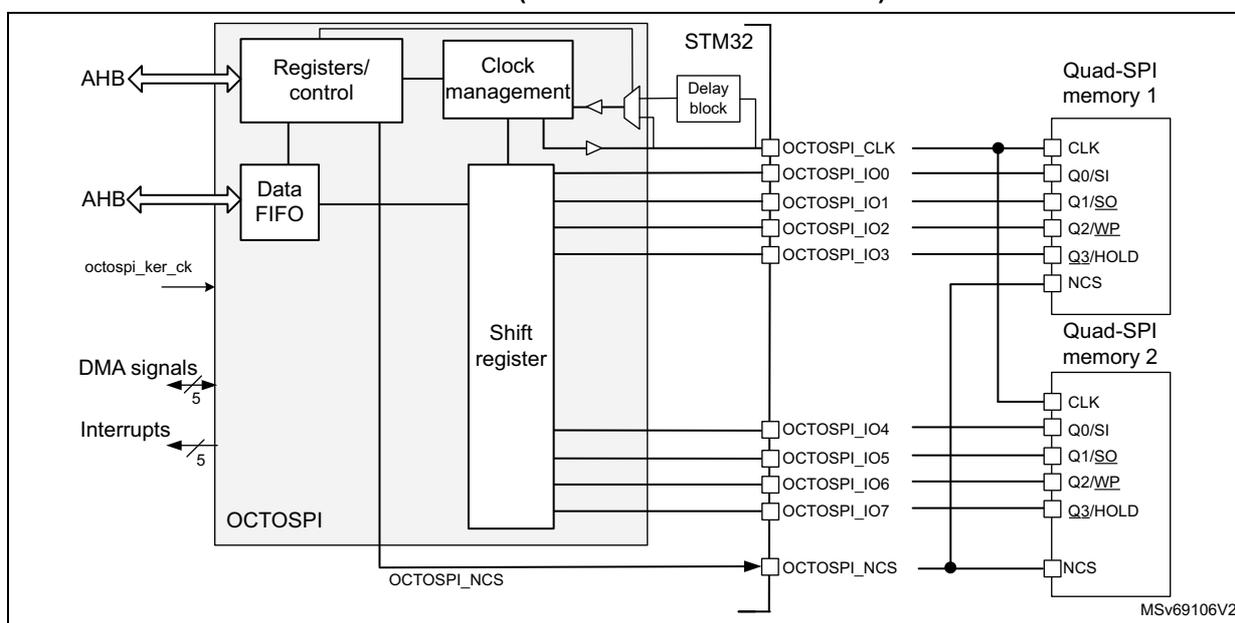

28.4.1 OCTOSPI block diagram

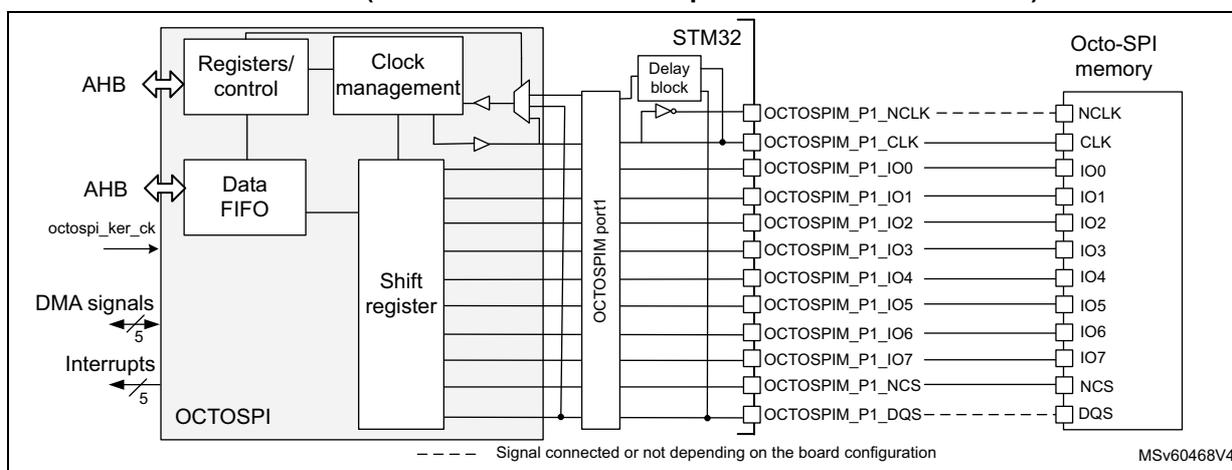

Figure 141. OCTOSPI block diagram in octal configuration

(for STM32U5 series except STM32U535/545 devices)

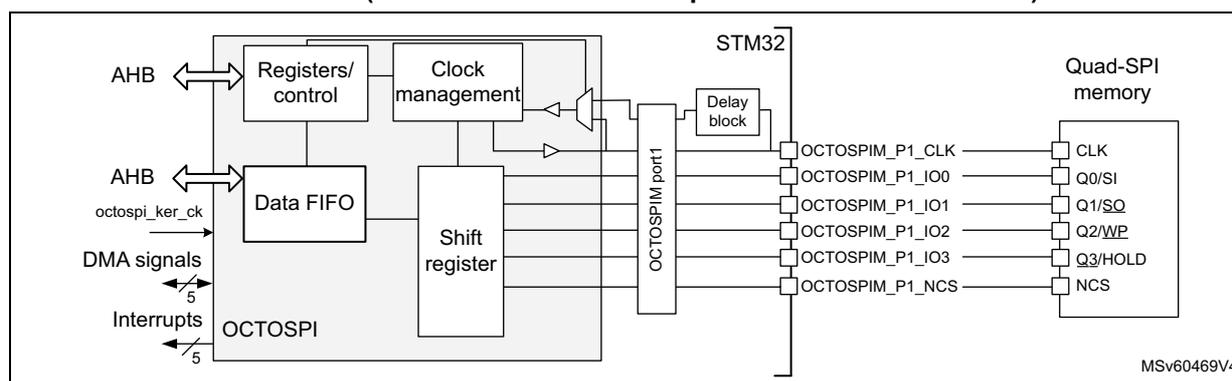

Figure 142. OCTOSPI block diagram in quad configuration

(for STM32U5 series except STM32U535/545 devices)

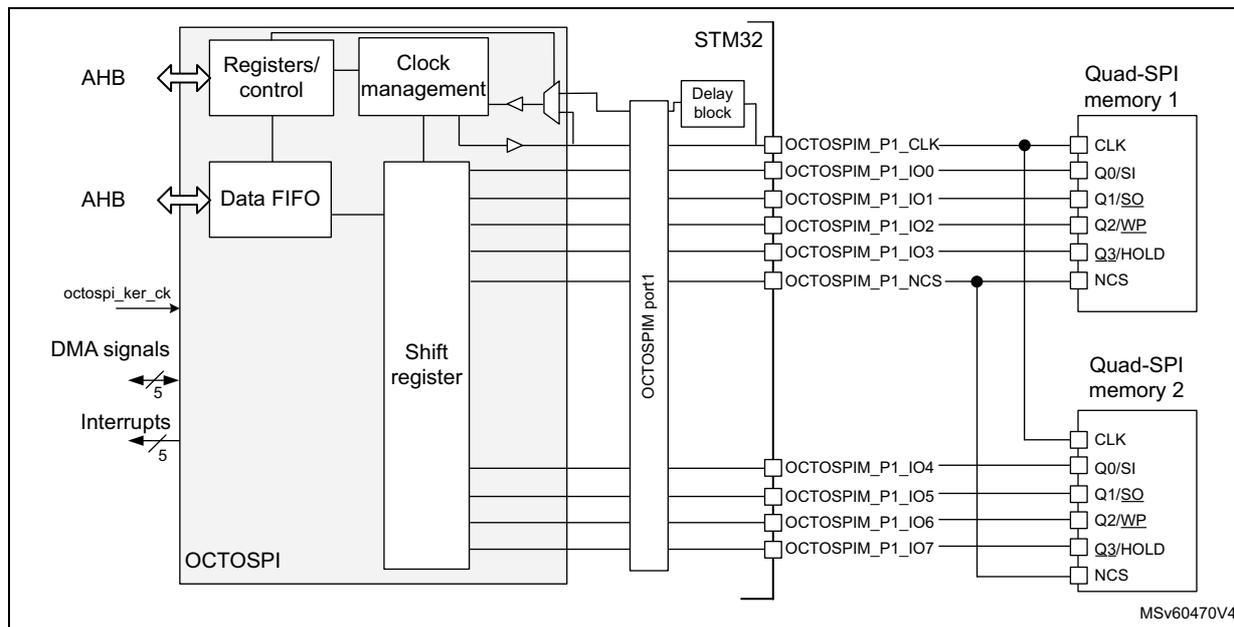

Figure 143. OCTOSPI block diagram in dual-quad configuration (for STM32U5 series except STM32U535/545 devices)

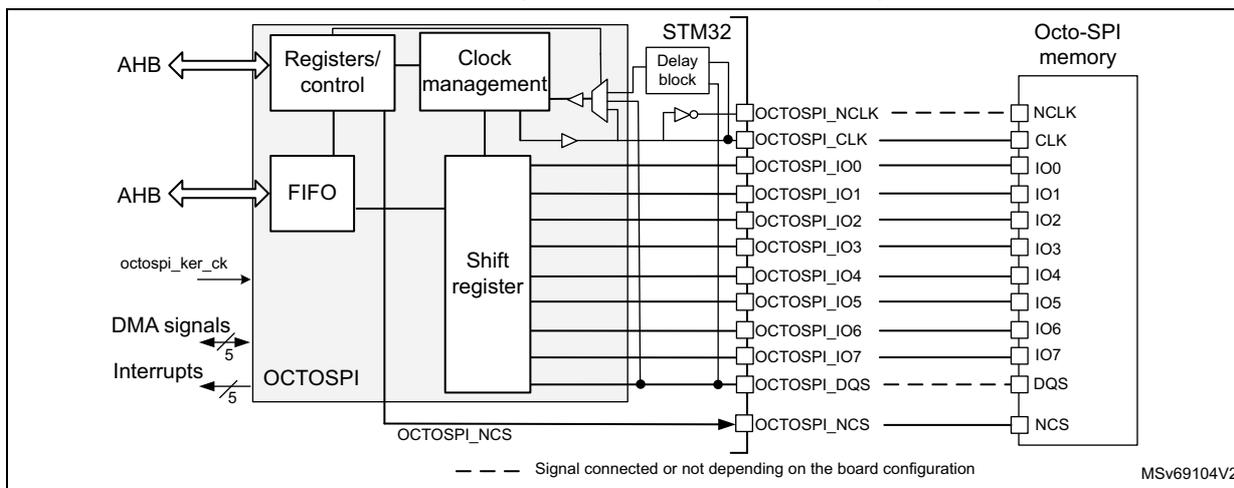

Figure 144. OCTOSPI block diagram in octal configuration (for STM32U535/545 devices)

Figure 145. OCTOSPI block diagram in quad configuration

(for STM32U535/545 devices)

Figure 146. OCTOSPI block diagram in dual-quad configuration

(for STM32U535/545 devices)

28.4.2 OCTOSPI pins and internal signals

Table 251. OCTOSPI input/output pins

(1)

(for STM32U5 Series except STM32U535/545 devices)

| Pin name | Type | Description |

|---|---|---|

| OCTOSPIM_Px_NCLK | Output | OCTOSPI inverted clock to support 1.8 V HyperBus protocol |

| OCTOSPIM_Px_CLK | OCTOSPI clock | |

| OCTOSPIM_Px_IO n (n = 0 to 7) | Input/output | OCTOSPI data pins |

| OCTOSPIM_Px_NCS | Output | Chip select for the memory |

| OCTOSPIM_Px_DQS | Input/output | Data strobe/write mask signal from/to the memory |

1. x = 1 to 2.

Caution: Use the same configuration (output speed, HSLV (a) ) for all OCTOSPI input/output pins to avoid any data corruption.

Table 252. OCTOSPI input/output pins (for STM32U535/545 devices)

| Pin name | Type | Description |

|---|---|---|

| OCTOSPI_NCLK | Output | OCTOSPI inverted clock to support 1.8 V HyperBus protocol |

| OCTOSPI_CLK | OCTOSPI clock | |

| OCTOSPI_IO n (n = 0 to 7) | Input/output | OCTOSPI data pins |

| OCTOSPI_NCS | Output | Chip select for the memory |

| OCTOSPI_DQS | Input/output | Data strobe/write mask signal from/to the memory |

Caution: Use the same configuration (output speed, HSLV (a) ) for all OCTOSPI input/output pins to avoid any data corruption.

Table 253. OCTOSPI internal signals

| Signal name | Type | Description |

|---|---|---|

| octospi_hclk | Input | OCTOSPI AHB clock |

| octospi_ker_ck | Input | OCTOSPI kernel clock |

| octospi_dma | N/A | DMA request signal |

| octospi_it | Output | Global interrupt line (see Table 257 for the multiple sources of interrupt) |

28.4.3 OCTOSPI interface to memory modes

The OCTOSPI supports the following protocols:

- • regular-command protocol

- • HyperBus protocol

The OCTOSPI uses from 6 to 12 signals to interface with a memory, depending on the functional mode:

- • NCS: chip-select

- • CLK: communication clock

- • NCLK: inverted clock used only in the 1.8 V HyperBus protocol

- • DQS: data strobe used only in regular-command protocol as input only

- • IO[3:0]: data bus LSB

- • IO[7:4]:

- – data bus MSB used in dual-quad and octal configurations

- – data bus can be used as possible remap for quad-SPI mode

a. When applicable.

28.4.4 OCTOSPI regular-command protocol

When in regular-command protocol, the OCTOSPI communicates with the external device using commands. Each command can include the following phases:

- • Instruction phase

- • Address phase

- • Alternate-byte phase

- • Dummy-cycle phase

- • Data phase

Any of these phases can be configured to be skipped but, in case of single-phase command, the only use case supported is instruction-phase-only.

The NCS falls before the start of each command and rises again after each command finishes.

In memory-mapped mode, both read and write operations are supported: as a consequence, some of the configuration registers are duplicated to specify write operations (read operations are configured using regular registers).

Figure 147. SDR read command in octal configuration

![Timing diagram for SDR read command in octal configuration. The diagram shows three signals: NCS (active-low chip select), CLK (clock), and IO[7:0] (data lines). NCS goes low at the start of the command and stays low until after the data phase. CLK is a square wave. IO[7:0] shows the data flow: an instruction (ECh), a 1-byte address (13h), a 4-byte address (A[31:24], A[23:16], A[15:8], A[7:0]), a dummy phase (Pre-drive), and four data bytes (D0, D1, D2, D3). The address and dummy phases are indicated by double-headed arrows below the signal line. The diagram is labeled MSv43488V1.](/RM0456-STM32U5/3d6a17f24abf67cf51341e386e8e676c_img.jpg)

The specific regular-command protocol features are configured through the registers in the 0x0100-0x01FC offset range.

Instruction phase

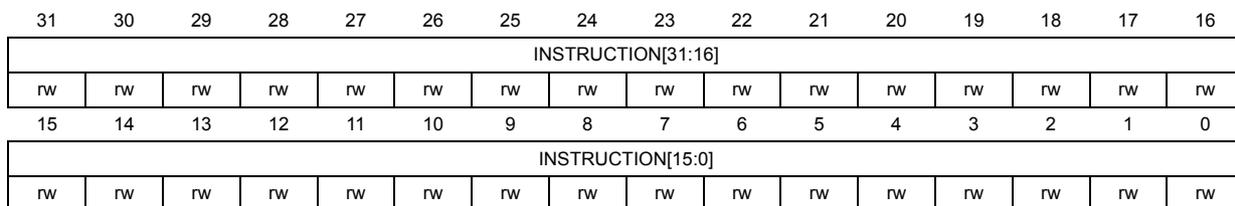

During this phase, a 1- to 4-byte instruction is sent to the external device specifying the type of operation to be performed. The size of the instruction to be sent is configured by ISIZE[1:0] in OCTOSPI_CCR and the instruction is programmed in INSTRUCTION[31:0] of OCTOSPI_IR.

The instruction phase can optionally send:

- • 1 bit at a time (over IO0, SO single in single-SPI mode)

- • 2 bits at a time (over IO0/IO1 in dual-SPI mode)

- • 4 bits at a time (over IO0 to IO3 in quad-SPI mode)

- • 8 bits at a time (over IO0 to IO7 in octal-SPI mode)

This can be configured using IMODE[2:0] of OCTOSPI_CCR.

The instruction can be sent in DTR mode on each rising and falling edge of the clock, by setting IDTR in OCTOSPI_CCR.

When IMODE[2:0] = 000 in OCTOSPI_CCR, the instruction phase is skipped, and the command sequence starts with the address phase, if present.

In memory-mapped mode, the instruction used for the write operation is specified in OCTOSPI_WIR, and the instruction format is specified in OCTOSPI_WCCR. The instruction used for the read operation and the instruction format are specified in OCTOSPI_IR and OCTOSPI_CCR.

Address phase

In the address phase, 1 to 4 bytes are sent to the external device, to indicate the address of the operation. The number of address bytes to be sent is configured by ADSIZE[1:0] in OCTOSPI_CCR.

In indirect and automatic status-polling modes, the address bytes to be sent are specified by ADDRESS[31:0] in OCTOSPI_AR. In memory-mapped mode, the address is given directly via the AHB (from any master in the system).

The address phase can send:

- • 1 bit at a time (over IO0, SO single in single-SPI mode)

- • 2 bits at a time (over IO0/IO1 in dual-SPI mode)

- • 4 bits at a time (over IO0 to IO3 in quad-SPI mode)

- • 8 bits at a time (over IO0 to IO7 in octal-SPI mode)

This can be configured using ADMODE[2:0] in OCTOSPI_CCR.

The address can be sent in DTR mode (on each rising and falling edge of the clock) setting ADDTR in OCTOSPI_CCR.

When ADMODE[2:0] = 000, the address phase is skipped and the command sequence proceeds directly to the next phase, if any.

In memory-mapped mode, the address format for the write operation is specified in OCTOSPI_WCCR. The address format for the read operation is specified in OCTOSPI_CCR.

Alternate-byte phase

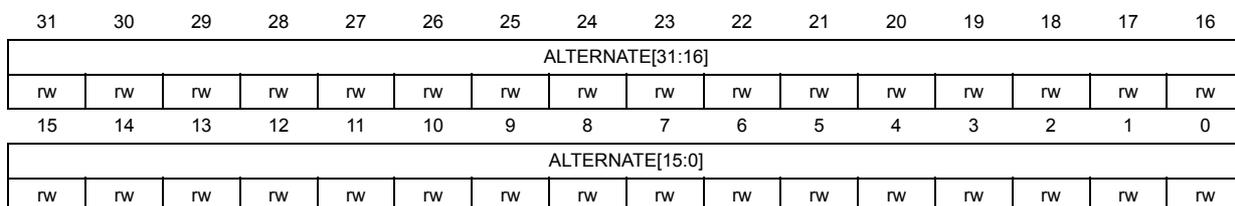

In the alternate-byte phase, 1 to 4 bytes are sent to the external device, generally to control the mode of operation. The number of alternate bytes to be sent is configured by ABSIZE[1:0] in OCTOSPI_CCR. The bytes to be sent are specified in OCTOSPI_ABR.

The alternate-byte phase can send:

- • 1 bit at a time (over IO0, SO single in single-SPI mode)

- • 2 bits at a time (over IO0/IO1 in dual-SPI mode)

- • 4 bits at a time (over IO0 to IO3 in quad-SPI mode)

- • 8 bits at a time (over IO0 to IO7 in octal-SPI mode)

This can be configured using ABMODE[2:0] in OCTOSPI_CCR.

The alternate bytes can be sent in DTR mode (on each rising and falling edge of the clock) setting ABDTR in OCTOSPI_CCR.

When ABMODE[2:0] = 000, the alternate-byte phase is skipped and the command sequence proceeds directly to the next phase, if any.

There may be times when only a single nibble needs to be sent during the alternate-byte phase rather than a full byte, such as when the dual-SPI mode is used and only two cycles are used for the alternate bytes.

In this case, the firmware can use the quad-SPI mode (ABMODE[2:0] = 011) and send a byte with bits 7 and 3 of ALTERNATE[31:0] set to 1 (keeping the IO3 line high), and bits 6 and 2 set to 0 (keeping the IO2 line low), in OCTOSPI_IR.

The upper two bits of the nibble to be sent are then placed in bits 5:4 of ALTERNATE[31:0] while the lower two bits are placed in bits 1:0. For example, if the nibble 2 (0010) is to be sent over IO0/IO1, then ALTERNATE[31:0] must be set to 0x8A (1000_1010).

In memory-mapped mode, the alternate bytes used for the write operation are specified in OCTOSPI_WABR, and the alternate byte format is specified in OCTOSPI_WCCR. The alternate bytes used for read operation and the alternate byte format are specified in OCTOSPI_ABR and OCTOSPI_CCR.

Dummy-cycle phase (memory latency)

In the dummy-cycle phase, 1 to 31 cycles are given without any data being sent or received, in order to give the external device, the time to prepare for the data phase when higher clock frequencies are used. The number of cycles given during this phase is specified by DCYC[4:0] in OCTOSPI_TCR. In both SDR and DTR modes, the duration is specified as a number of full CLK cycles.

When DCYC[4:0] = 00000, the dummy-cycle phase is skipped, and the command sequence proceeds directly to the data phase, if present.

In order to assure enough “turn-around” time for changing the data signals from the output mode to the input mode, there must be at least one dummy cycle when using the dual-SPI, the quad-SPI, or the octal-SPI mode, to receive data from the external device.

In memory-mapped mode, the dummy cycles for the write operations are specified in OCTOSPI_WTCR. The dummy cycles for the read operation are specified in OCTOSPI_TCR.

Data phase

During the data phase, any number of bytes can be sent to or received from the external device.

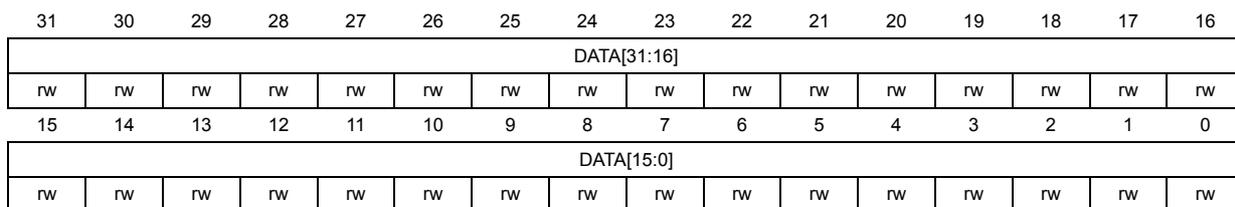

In indirect mode, the number of bytes to be sent/received is specified in OCTOSPI_DLR. In this mode, the data to be sent to the external device must be written to OCTOSPI_DR, while in indirect-read mode the data received from the external device is obtained by reading OCTOSPI_DR.

In automatic status-polling mode, the number of bytes to be received is specified in OCTOSPI_DLR, and the data received from the external device can be obtained by reading OCTOSPI_DR.

In memory-mapped mode, the data read or written, is sent or received directly over the AHB to the Cortex core or to a DMA.

The data phase can send/receive:

- • 1 bit at a time (over IO0/IO1 (SO/SI respectively) in single-SPI mode)

- • 2 bits at a time (over IO0/IO1 in dual-SPI mode)

- • 4 bits at a time (over IO0 to IO3 in quad-SPI mode)

- • 8 bits at a time (over IO0 to IO7 in octal-SPI mode)

This can be configured using DMODE[2:0] in OCTOSPI_CCR.

The data can be sent or received in DTR mode (on each rising and falling edge of the clock) setting DDTR in OCTOSPI_CCR.

When DMODE[2:0] = 000, the data phase is skipped, and the command sequence finishes immediately by raising the NCS. This configuration must be used only in indirect-write mode.

In memory-mapped mode, the data format for the write operation is specified in OCTOSPI_WCCR. The data format for the read operation is specified in OCTOSPI_CCR.

DQS use

The DQS signal can be used for data strobing during the read transactions when the device toggles the DQS aligned with the data.

The DQS management can be enabled by setting DQSE in OCTOSPI_CCR.

Figure 148. DTR read in octal-SPI mode with DQS (Macronix mode) example

![Timing diagram for DTR read in octal-SPI mode with DQS (Macronix mode) example. The diagram shows four signals: NCS (active low), CLK (square wave), DQS (data strobe), and IO[7:0] (data bus). The sequence starts with NCS going low, followed by CLK. IO[7:0] shows a series of bytes: EEh, 11h, A[31:24], A[23:16], A[15:8], A[7:0], which are grouped as 'Address'. This is followed by a 'Dummy' phase (shaded). Then, DQS toggles, and IO[7:0] shows data bytes D1, D0, D3, D2, which are grouped as 'Word unit'. The diagram ends with NCS going high.](/RM0456-STM32U5/1681d28bc068f08ab26bb5802715d2e9_img.jpg)

28.4.5 OCTOSPI regular-command protocol signal interface

Single-SPI mode

The legacy SPI mode allows just a single bit to be sent/received serially. In this mode, the data is sent to the external device over the SO signal (Single-SPI Output) (whose I/Os are shared with IO0). The data received from the external device arrives via SI (Single-SPI Input) (whose I/Os are shared with IO1).

Compared to the SPI legacy mode, IO0/SO and IO1/SI are respectively equivalent to MOSI and MISO, having the OCTOSPI generating the clock.

The different phases can each be configured separately to use this single-SPI mode by setting to 001 the IMODE, ADMODE, ABMODE, and DMODE fields in OCTOSPI_CCR and OCTOSPI_WCCR.

In each phase configured in single-SPI mode:

- • IO0 (SO) is in output mode.

- • IO1 (SI) is in input mode (high impedance).

- • IO2 is in output mode and forced to 0.

- • IO3 is in output mode and forced to 1 (to deactivate the “hold” function).

- • IO4 to IO7 are in output mode and forced to 0.

This is the case even for the dummy phase if DMODE[2:0] = 001.

Dual-SPI mode

In dual-SPI mode, two bits are sent/received simultaneously over the IO0/IO1 signals.

The different phases can each be configured separately to use dual-SPI mode by setting to 010 the IMODE, ADMODE, ABMODE, and DMODE fields in OCTOSPI_CCR and OCTOSPI_WCCR.

In each phase configured in dual-SPI mode:

- • IO0/IO1 are at high-impedance (input) during the data phase for the read operations, and outputs in all other cases.

- • IO2 is in output mode and forced to 0.

- • IO3 is in output mode and forced to 1.

- • IO4 to IO7 are in output mode and forced to 0.

In the dummy phase, when DMODE[2:0] = 010, IO0 and IO1 are in a high-impedance state during read transactions, and are forced to either high or low levels during write transactions.

Quad-SPI mode

In quad-SPI mode, four bits are sent/received simultaneously over the IO0/IO1/IO2/IO3 signals.

The different phases can each be configured separately to use the quad-SPI mode by setting to 011 the IMODE, ADMODE, ABMODE, and DMODE fields in OCTOSPI_CCR and OCTOSPI_WCCR.

In each phase configured in quad-SPI mode:

- • IO0 to IO3 are all at high-impedance (inputs) during the data phase for the read operations, and outputs in all other cases.

- • IO4 to IO7 are in output mode and forced to 0.

In the dummy phase, when DMODE[2:0] = 011, IO0 to IO3 are in a high-impedance state during read transactions, and are forced to either high or low levels during write transactions.

Octal-SPI mode

In regular octal-SPI mode, the eight bits are sent/received simultaneously over the IO[0:7] signals.

The different phases can each be configured separately to use the octal-SPI mode by setting to 100 the IMODE, ADMODE, ABMODE, and DMODE fields in OCTOSPI_CCR and OCTOSPI_WCCR.

In each phase that is configured in octal-SPI mode, IO[0:7] are all at high-impedance (input) during the data phase for read operations, and outputs in all other cases.

In the dummy phase, when DMODE[2:0] = 100, IO[0:7] are in a high-impedance state during read transactions, and are forced to either high or low levels during write transactions.

Single-data rate (SDR) mode

By default, all the phases operate in SDR mode.

In this mode, when the OCTOSPI drives the IO0/SO, IO1 to IO7 signals, these signals transition only with the falling edge of CLK.

When receiving data in SDR mode, the OCTOSPI assumes that the external devices also send the data using CLK falling edge. By default (when SSHIFT = 0 in OCTOSPI_TCR), the signals are sampled using the following (rising) edge of CLK.

Figure 149. SDR write command in octo-SPI mode example

![Timing diagram for SDR write command in octo-SPI mode. The diagram shows three signals: NCS (active low), CLK (square wave), and IO[7:0] (data bus). The sequence of data on the IO[7:0] bus is: 02h, FDh, A[31:24], A[23:16], A[15:8], A[7:0], D0, D1, D254, D255. The NCS signal is pulled low at the start of the command and goes high after the last data byte. The CLK signal is shown with multiple cycles, with data being transferred on the falling edges of CLK. The diagram is labeled MSV43490V1.](/RM0456-STM32U5/cab08800cad7d9617155adcc6beb7734_img.jpg)

Note: Due to internal synchronization, up to six extra dummy clock cycles may be generated by the Octo-SPI interface after the last data is read.

Double-transfer rate (DTR) mode

Each of the instruction, address, alternate-byte, and data phases can be configured to operate in DTR mode setting IDTR, ADDTR, ABDTR, and DDTR in OCTOSPI_CCR.

In memory-mapped mode, the DTR mode for each phase of the write operations is specified in OCTOSPI_WCCR. The DTR mode for each phase of the read operations is specified in OCTOSPI_CCR.

In DTR mode, when the OCTOSPI drives the IO0/SO and IO1 to IO7 signals in the instruction, address, and alternate-byte phases, a bit is sent or received on each of the falling and rising edges of CLK.

When receiving data in DTR mode, the OCTOSPI assumes that the external devices also send the data using both CLK rising and falling edges. When DDTR = 1 in OCTOSPI_CCR, the software must clear SSHIFT in OCTOSPI_TCR. Thus, the signals are sampled one half of a CLK cycle later (on the following, opposite edge).

In DTR mode, it is recommended to set DHQC of OCTOSPI_TCR, to shift the outputs by a quarter of cycle and avoid holding issues on the memory side.

Note: DHQC must not be set when the prescaler value is 0, as this action leads to unpredictable behavior.

Figure 150. DTR write in octal-SPI mode (Macronix mode) example

![Timing diagram for DTR write in octal-SPI mode (Macronix mode) example. The diagram shows three signals: NCS (Active Low Chip Select), CLK (Clock), and IO[7:0] (Data Bus). The NCS signal is initially high, then goes low to start the transaction, and returns high after the transaction. The CLK signal is a square wave. The IO[7:0] signal shows a sequence of data: a series of dummy cycles (indicated by diagonal hatching), followed by the instruction 02h, the address FDh, a 32-bit address split into four 8-bit bytes (A[31:24], A[23:16], A[15:8], A[7:0]), and then data D1, D0, D255, and D254. The data is transferred in 'Word Units' of 16 bits. The diagram is labeled MSV43491V1.](/RM0456-STM32U5/a374d4100e29c16e12cd44213d16039b_img.jpg)

Note: Due to internal synchronization, up to six extra dummy clock cycles may be generated by the Octo-SPI interface after the last data is read.

Dual-quad configuration

When DMM = 1 in OCTOSPI_CR, the OCTOSPI is in dual-memory configuration: if DMODE = 011, two external Quad-SPI devices (device A and device B) are used in order to send/receive eight bits (or 16 bits in DTR mode) every cycle, effectively doubling the throughput.

Each device (A or B) uses the same CLK and NCS signals, but each has separate IO0 to IO3 signals.

The dual-quad configuration can be used in conjunction with the single-SPI, dual-SPI, and quad-SPI modes, as well as with either the SDR or DTR mode.

The device size, as specified by DEVSIZE[4:0] in OCTOSPI_DCR1, must reflect the total external device capacity that is the double of the size of one individual component.

If address X is even, then the byte that the OCTOSPI gives for address X is the byte at the address X/2 of device A, and the byte that the OCTOSPI gives for address X + 1 is the byte at the address X/2 of device B. In other words, the bytes at even addresses are all stored in device A and the bytes at odd addresses are all stored in device B.

When reading the status registers of the devices in dual-quad configuration, twice as many bytes must be read compared to the same read in regular-command protocol: if each device gives eight valid bits after the instruction for fetching the status register, then the OCTOSPI must be configured with a data length of 2 bytes (16 bits), and the OCTOSPI receives one byte from each device.

If each device gives a status of 16 bits, then the OCTOSPI must be configured to read 4 bytes to get all the status bits of both devices in dual-quad configuration. The least-significant byte of the result (in the data register) is the least-significant byte of device A status register. The next byte is the least-significant byte of device B status register. Then, the third byte of the data register is the device A second byte. The fourth byte is the device B second byte (if devices have 16-bit status registers).

An even number of bytes must always be accessed in dual-quad configuration. For this reason, bit 0 of DL[31:0] in OCTOSPI_DLR is stuck at 1 when DMM = 1.

In dual-quad configuration, the behavior of device A interface signals is basically the same as in normal mode. Device B interface signals have exactly the same waveforms as device A ones during the instruction, address, alternate-byte, and dummy-cycle phases. In other words, each device always receives the same instruction and the same address.

Then, during the data phase, the AIOx and the BIOx buses both transfer data in parallel, but the data that is sent to (or received from) device A is distinct than the one from device B.

28.4.6 HyperBus protocol

The OCTOSPI can communicate with the external device using the HyperBus protocol.

The HyperBus uses 11 to 12 pins depending on the operating voltage:

- • IO[7:0] as bidirectional data bus

- • DQS for read and write data strobe and latency insertion

- • NCS

- • CLK

- • NCLK for 1.8 V operations (to support this mode, the device must be powered with 1.8 V)

The HyperBus does not require any command specification nor any alternate bytes. As a consequence, a separate register set is used to define the timing of the transaction.

The HyperBus frame is composed of the following phases:

- • Command/address phase

- • Data phase

The NCS falls before the start of a transaction and rises again after each transaction finishes.

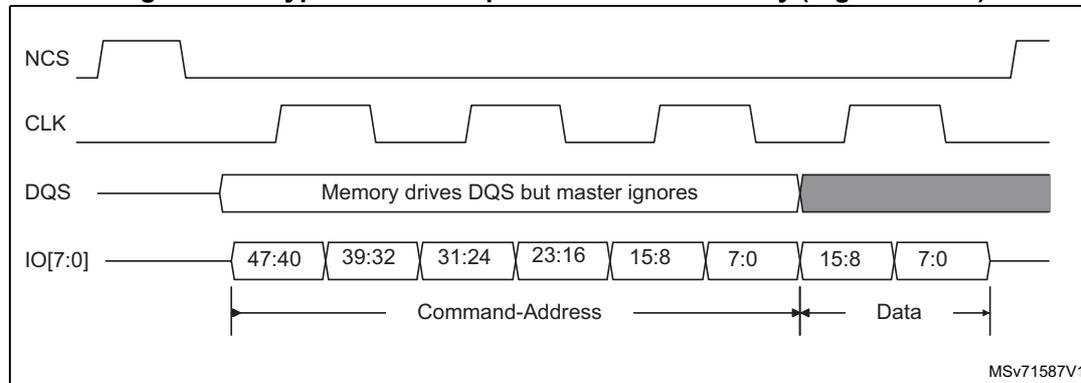

Figure 151. Example of HyperBus read operation

![Timing diagram for HyperBus read operation showing NCS, CLK, DQS, and IO[7:0] signals. The diagram illustrates the Command-Address phase followed by the Data phase. In the Command-Address phase, the host drives IO[7:0] and memory drives DQS. The Command-Address is split into six 8-bit nibbles: 47:40, 39:32, 31:24, 23:16, 15:8, and 7:0. The Data phase shows data being read from memory (Dn A, Dn B, Dn+1 A, Dn+1 B) with DQS and data being edge aligned. Timing parameters t_RWR (Read write recovery) and t_ACC (Initial access) are shown. A note indicates that up to six extra dummy clock cycles may be generated by the Octo-SPI interface after the last data is read.](/RM0456-STM32U5/f6a4506e4ae739e8c3d72b1c48f29e77_img.jpg)

Note: Due to internal synchronization, up to six extra dummy clock cycles may be generated by the Octo-SPI interface after the last data is read.

The specific HyperBus features are configured through the registers in the 0x0200-0x02FC offset range.

Command/address phase

During this initial phase, the OCTOSPI sends 48 bits over IO[7:0] to specify the operations to be performed with the external device.

Table 254. Command/address phase description

| CA bit | Bit name | Description |

|---|---|---|

| 47 | R/W# | Identifies the transaction as a read or a write. |

| 46 | Address space | Indicates if the transaction accesses the memory or the register space. |

| 45 | Burst type | Indicates if the burst is linear or wrapped. |

| 44-16 | Row and upper column address | Selects the row and the upper column addresses. |

| 15-3 | Reserved | - |

| 2-0 | Lower column address | Selects the starting 16-bit word within the half page. |

The address space is configured through the memory type MTYP[2:0] in OCTOSPI_DCR1. The total size of the device must be configured through DEVSIZE[4:0] of OCTOSPI_DCR1. In case of multi-chip product (MCP), the device size is the sum of all the sizes of all the MCP dies.

Read/write operation with initial latency

The HyperBus read and write operations need to respect two timings:

- • \( t_{RWR} \) : minimal read/write recovery time for the device (defined by TRWR[7:0] in OCTOSPI_HLCR)

- • \( t_{ACC} \) : access time for the device (defined by TACC[7:0] in OCTOSPI_HLCR) according to the memory latency

During the read operation, the DQS is used by the device, in two ways (see Figure 151):

- • during the command/address phase, to request an additional latency

- • during the data phase, for data strobing

During the write operation, the DQS is used:

- • by the device, during the command/address phase, to request an additional latency.

- • by the OCTOSPI, during the data phase, for write data masking.

Figure 152. HyperBus write operation with initial latency

![Timing diagram for HyperBus write operation with initial latency. The diagram shows four signals: NCS (active low), CLK (square wave), DQS (data strobe), and IO[7:0] (data bus). The sequence starts with NCS going low. The first phase is the Command-Address phase, where IO[7:0] is driven by the host and DQS is driven by memory. The command/address bits are 47:40, 39:32, 31:24, 23:16, 15:8, and 7:0. The DQS signal has a high level for 2x latency count and a low level for 1x latency count. The second phase is the data phase, where IO[7:0] and DQS are driven by the host. The data is Dn A, Dn B, Dn+1 A, and Dn+1 B. The timing parameters shown are t_RWR (Read Write Recovery) and t_ACC (Access). A note indicates that CLK and data are center aligned. The diagram is labeled MSV71584V1.](/RM0456-STM32U5/51efcff045cd212d9c1a8c9b92a98736_img.jpg)

Read/write operation with additional latency

If the device needs an additional latency (during refresh period of an SDRAM for example), DQS must be tied to one during one of the DQS signals, during the command/address phase.

An additional \( t_{ACC} \) duration is added by the OCTOSPI to meet the device request.

Figure 153. HyperBus read operation with additional latency

![Timing diagram for HyperBus read operation with additional latency. The diagram shows four signals: NCS (active low), CLK (clock), DQS (data strobe), and IO[7:0] (data bus). The sequence starts with a Command-Address phase (IO[7:0] driven by Host, DQS driven by Memory). This is followed by an 'Additional latency' period. Then, the read data phase begins, where memory drives IO[7:0] and DQS. The data is transferred in 8-bit chunks (47:40, 39:32, 31:24, 23:16, 15:8, 7:0). The DQS signal is high for 2x Latency count and low for 1x Latency count. The data is edge aligned with DQS. The diagram also shows t_RWR (Read write recovery) and t_ACC (Access) times. The memory drives IO[7:0] and DQS. The host drives IO[7:0] and memory drives DQS. The diagram is labeled MSV71585V1.](/RM0456-STM32U5/c363adbd37746818a793d323b033b356_img.jpg)

Figure 154. HyperBus write operation with additional latency

![Timing diagram for HyperBus write operation with additional latency. The diagram shows four signals: NCS (active low), CLK (clock), DQS (data strobe), and IO[7:0] (data bus). The sequence starts with a Command-Address phase (IO[7:0] driven by Host, DQS driven by Memory). This is followed by an 'Additional latency' period. Then, the write data phase begins, where host drives IO[7:0] and DQS. The data is transferred in 8-bit chunks (47:40, 39:32, 31:24, 23:16, 15:8, 7:0). The DQS signal is high for 2x Latency count and low for 1x Latency count. The data is center aligned with CLK. The diagram also shows t_RWR (Read write recovery) and t_ACC (Initial access) times. The host drives IO[7:0] and DQS. The memory drives DQS. The diagram is labeled MSV71586V1.](/RM0456-STM32U5/77c2a027d470dcf6114da716fa9b581d_img.jpg)

Fixed-latency mode

Some devices or some applications may not want to operate with a variable latency time as described above.

The latency can be forced to \( 2 \times t_{ACC} \) by setting LM in OCTOSPI_HLCR.

In this OCTOSPI latency mode, the state of the DQS signal is not taken into account by the OCTOSPI, and an additional latency is always added, leading to a fixed \( 2 \times t_{ACC} \) latency time.

Write operation with no latency

Some devices can also require a zero latency for the write operations. This write-zero latency can be forced by setting WZL in OCTOSPI_HLCR.

Figure 155. HyperBus write operation with no latency (register write)

The diagram shows the timing for a HyperBus write operation with no latency. The signals are NCS (active low), CLK (clock), DQS (data strobe), and IO[7:0] (data bus). During the Command-Address phase, IO[7:0] carries values: 47:40, 39:32, 31:24, 23:16, 15:8, and 7:0. This is followed immediately by the Data phase with values 15:8 and 7:0. DQS is driven by the memory but the master ignores it during this write operation. Diagram reference: MSv71587V1.

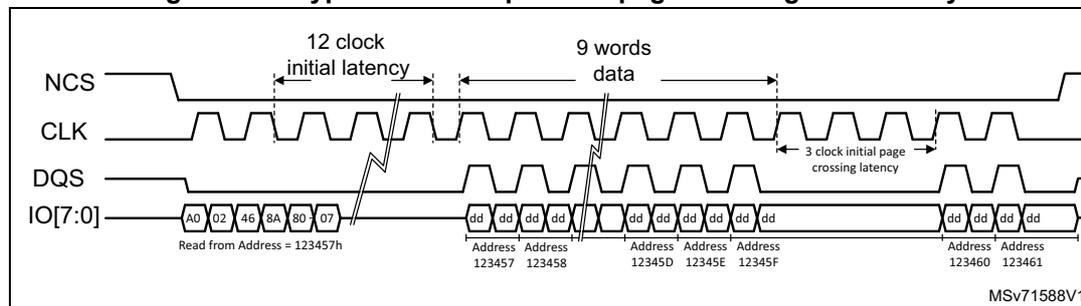

Latency on page-crossing during the read operations

An additional latency can be needed by some devices for the read operation when crossing pages.

The initial latency must be respected for any page access, as a consequence, when the first access is close to the page boundary, a latency is automatically added at the page crossing to respect the \( t_{ACC} \) time.

Figure 156. HyperBus read operation page crossing with latency

The diagram shows a HyperBus read operation with page crossing. Signals include NCS, CLK, DQS, and IO[7:0]. The operation starts with a Command-Address phase on IO[7:0] with values: A0, 02, 46, 8A, 80, 07, corresponding to 'Read from Address = 123457h'. This is followed by a '12 clock initial latency'. Then, '9 words data' are read (labeled dd), corresponding to addresses 123457, 123458, up to 12345D, 12345E, and 12345F. At the page boundary (after 12345F), a '3 clock initial page crossing latency' is inserted. Following this, data reading continues from addresses 123460 and 123461. DQS toggles during data phases. Diagram reference: MSv71588V1.

28.4.7 Specific features

The OCTOSPI supports some specific features, such as:

- • Wrap support

- • NCS boundary and refresh

- • Communication regulation

Wrap support

The OCTOSPI supports a hybrid wrap as defined by the HyperBus protocol. A hybrid wrap is also supported in the regular-command protocol.

In hybrid wrap, the transaction can continue after the initial wrap with an incremental access.

The wrap size supported by the target memory is configured by WRAPSIZE in OCTOSPI_DCR2.

Wrap is supported only in memory-read direction and only for data size = 4 bytes. Wrapped reads are supported for both HyperBus and regular-command protocols. To enable wrapped-read accesses, the dedicated OCTOSPI_WPxxx registers must be programmed according to the wrapped-read access characteristics. These registers apply for both HyperBus and regular-command protocols.

If the target memory is not supporting the hybrid wrap, WRAPSIZE must be set to 0.

Note: Hybrid wrap requires that the nonwrapped registers (OCTOSPI_CCR, OCTOSPI_TCR, OCTOSPI_IR) are set according to the memory configuration to satisfy its correct data prefetch (initiated after the wrap command).

The wrap operation cannot be interrupted by a refresh. The refresh event is only considered after the wrap completion.

NCS boundary and refresh

Two processes can be activated to regulate the OCTOSPI transactions:

- • NCS boundary

- • Refresh

The NCS boundary feature limits a transaction to a boundary of aligned addresses. The size of the address to be aligned with, is configured by CSBOUND[4:0] in OCTOSPI_DCR3: it is equal to \( 2^{\text{CSBOUND}} \) .

As an example, if CSBOUND[4:0] = 0x4, the boundary is set to \( 2^4 = 16 \) bytes. The NCS is then released each time the LSB address is equal to 0xF, and each time a new transaction is issued to address the next data.

If CSBOUND[4:0] = 0, the feature is disabled. A minimum value of three is recommended.

The NCS boundary feature cannot be used for flash memory devices in write mode since a command is necessary to program another page of the flash memory.

The refresh feature limits the duration of the transactions to the value programmed by REFRESH[31:0] in OCTOSPI_DCR4. The duration is expressed in number of cycles. This allows an external RAM to perform its internal refresh operation regularly.

The refresh value must be greater than the minimal transaction size in terms of number of cycles including the command/address/alternate/dummy phases.

If NCS boundary and refresh are enabled at the same time, the NCS is released on the first condition met.

Communication regulation

The communication regulation feature limits the maximum length of a transaction to the value programmed by MAXTRAN[7:0] in OCTOSPI_DCR3.

If the number of clock cycles reaches the MAXTRAN + 1 value, and if the second OCTOSPI requests access, the NCS is released and a new transaction is issued to address the next data. If the second OCTOSPI does not request an access, the transaction is not stopped and the NCS is not released.

If MAXTRAN[7:0] = 0, no limitation occurs.

The MAXTRAN[7:0] value must be greater than the minimal transaction size in terms of number of cycles including the command, address, alternate, and dummy phases.

Note: The communication regulation feature cannot be used in write mode for the flash memory devices that require extra command to reenable the write operation after the NCS is active again.

If NCS boundary, refresh, and communication regulation are enabled at the same time, the NCS is released on the first condition met.

Restarting after an interrupted transfer

When a read or write operation is interrupted by a timeout or communication regulation feature, the Octo-SPI interface, as soon as possible after getting back the port ownership, reissues the initial command sequence together with the address following the last address actually accessed before interruption. The transfer initially set goes on and ends seamlessly.

28.4.8 OCTOSPI operating mode introduction

The OCTOSPI has the following operating modes regardless of the low-level protocol used (either regular-command or HyperBus):

- • indirect mode (read or write)

- • automatic status-polling mode (only in regular-command protocol)

- • memory-mapped mode

28.4.9 OCTOSPI indirect mode

In indirect mode, the commands are started by writing to the OCTOSPI registers, and data are transferred by writing or reading the data register, in a similar way to other communication peripherals.

When FMODE[1:0] = 00 in OCTOSPI_CR, the OCTOSPI is in indirect-write mode: bytes are sent to the external device during the data phase. Data are provided by writing to OCTOSPI_DR.

When FMODE[1:0] = 01, the OCTOSPI is in indirect-read mode: bytes are received from the external device during the data phase. Data are recovered by reading OCTOSPI_DR.

In indirect mode, when the OCTOSPI is configured in DTR mode over eight lanes with DQS disabled, the given starting address and the data length must be even.

Note: The OCTOSPI_AR register must be updated even if the start address is the same as the start address of the previous indirect access.

The number of bytes to be read/written is specified in OCTOSPI_DLR:

- • If DL[31:0] = 0xFFFF FFFF, the data length is considered undefined and the OCTOSPI simply continues to transfer data until it reaches the end of the external device (as defined by DEVSIZE). If no bytes are to be transferred, DMODE[2:0] must be set to 0 in OCTOSPI_CCR.

- • If DL[31:0] = 0xFFFF FFFF and DEVSIZE[4:0] = 0x1F (its maximum value indicating at 4-Gbyte device), the transfers continue indefinitely, stopping only after an abort request or after the OCTOSPI is disabled. After the last memory address is read (at address 0xFFFF FFFF), reading continues with address = 0x0000 0000.

When the programmed number of bytes to be transmitted or received is reached, the TCF bit is set in OCTOSPI_SR, and an interrupt is generated if TCIE = 1 in OCTOSPI_CR. In the case of an undefined number of data, TCF is set when the limit of the external SPI memory is reached, according to the device size defined in OCTOSPI_DCR1.

Triggering the start of a transfer in regular-command protocol

Depending on the OCTOSPI configuration, there are three different ways to trigger the start of a transfer in indirect mode when using the regular-command protocol. In general, the start of transfer is triggered as soon as the software gives the last information that is necessary for the command. More specifically in indirect mode, a transfer starts when one of the following sequence of events occurs:

- • if no address is necessary (ADMODE[2:0] = 000) and if no data need to be provided by the software (FMODE[1:0] = 01 or DMODE[2:0] = 000), and at the moment when a write is performed to INSTRUCTION[31:0] in OCTOSPI_IR

- • if an address is necessary (when ADMODE[2:0] ≠ 000) and if no data need to be provided by the software (when FMODE[1:0] = 01 or DMODE[2:0] = 000), and at the moment when a write is performed to ADDRESS[31:0] in OCTOSPI_AR

- • if data need to be provided by the software (when FMODE[1:0] = 00 and DMODE[2:0] ≠ 000), and at the moment when a write is performed to DATA[31:0] in OCTOSPI_DR

A write to OCTOSPI_ABR never triggers the communication start. If alternate bytes are required, they must have been programmed before.

As soon as a command is started, the BUSY bit is automatically set in OCTOSPI_SR.

Triggering the start of a transfer in HyperBus protocol

Depending on the OCTOSPI configuration, there are different ways to trigger the start of a command in indirect mode. In general, it is triggered as soon as the firmware gives the last information that is necessary for the transfer to start, and more specifically, a communication in indirect mode is triggered by one of the following register settings, when it is the last one to be executed:

- • when a write is performed to ADDRESS[31:0] (OCTOSPI_AR) with ADMODE[2:0] ≠ 000 in indirect read mode (FMODE[1:0] = 01).

- • when a write is performed to DATA[31:0] (OCTOSPI_DR) in indirect-write mode (when FMODE = 00).

- • when a (dummy) write is performed to INSTRUCTION[31:0] (OCTOSPI_IR) for indirect read mode (with ADMODE[2:0] = 000 and FMODE = 01).

As soon as a transfer is started, the BUSY bit (OCTOSPI_SR[5]) is automatically set.

FIFO and data management

Data in indirect mode passes through a 32-byte FIFO that is internal to the OCTOSPI. FLEVEL in OCTOSPI_SR indicates how many bytes are currently being held in the FIFO.

AHB burst transactions are supported. Data of the burst are successively written in OCTOSPI_DR, and immediately transferred in the internal FIFO.

In indirect-write mode (FMODE[1:0] = 00), the software adds data to the FIFO when it writes in OCTOSPI_DR. A word write adds 4 bytes to the FIFO, a half-word write adds 2 bytes, and a byte write adds only 1 byte. If the software adds too many bytes to the FIFO (more

than indicated in DL[31:0]), the extra bytes are flushed from the FIFO at the end of the write operation (when TCF is set).

The byte/half-word accesses to OCTOSPI_DR must be done only to the least significant byte/halfword of the 32-bit register.

FTHRES is used to define a FIFO threshold after which point the FIFO threshold flag, FTF, gets set. In indirect-read mode, FTF is set when the number of valid bytes to be read from the FIFO is above the threshold. FTF is also set if there is any data left in the FIFO after the last byte is read from the external device, regardless of FTHRES setting. In indirect-write mode, the FTF is set when the number of empty bytes in the FIFO is above the threshold.

If FTIE = 1, there is an interrupt when the FTF is set. If DMAEN = 1, a DMA transfer is initiated when the FTF is set. The FTF is cleared by hardware as soon as the threshold condition is no longer true (after enough data has been transferred by the CPU or DMA).

The last data read in RX FIFO remains valid as long as there is no request for the next line. This means that, when the application reads several times in a row at the same location, the data is provided from the RX FIFO and not read again from the distant memory.

28.4.10 OCTOSPI automatic status-polling mode

In automatic status-polling mode, the OCTOSPI periodically starts a command to read a defined number of status bytes (up to four). The received bytes can be masked to isolate some status bits and an interrupt can be generated when the selected bits have a defined value. The automatic status-polling mode must be used only in regular-command protocol. For HyperBus protocol, it is not exploitable since the read status register into the HyperFlash memory must be performed in two steps (a write operation followed by a read operation).

The access to the device begins in the same manner as in indirect-read mode. BUSY in OCTOSPI_SR goes high at this point and stays high even between the periodic accesses.

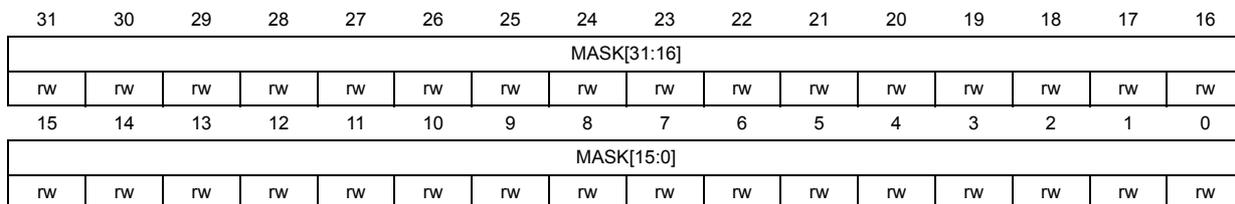

The content of MASK[31:0] in OCTOSPI_PSMAR is used to mask the data from the external device in automatic status-polling mode:

- • If the MASK[n] = 0, then bit n of the result is masked and not considered.

- • If MASK[n] = 1, and the content of bit[n] is the same as MATCH[n] in OCTOSPI_PSMAR, then there is a match for bit n.

If PMM = 0 in OCTOSPI_CR, the AND-match mode is activated: SMF is set in OCTOSPI_SR only when there is a match on all of the unmasked bits.

If PMM = 1 in OCTOSPI_CR, the OR-match mode is activated: SMF gets set if there is a match on any of the unmasked bits.

An interrupt is called when SMF = 1 if SMIE = 1.

If APMS is set in OCTOSPI_CR, the operation stops and BUSY goes to 0 as soon as a match is detected. Otherwise, BUSY stays at 1 and the periodic accesses continue until there is an abort or until the OCTOSPI is disabled (EN = 0).

OCTOSPI_DR contains the latest received status bytes (FIFO deactivated). The content of this register is not affected by the masking used in the matching logic. FTF in OCTOSPI_SR is set as soon as a new reading of the status is complete. FTF is cleared as soon as the data is read.

In automatic status-polling mode, variable latency is not supported. The memory must then be configured in fixed latency.

28.4.11 OCTOSPI memory-mapped mode

When configured in memory-mapped mode, the external SPI device is seen as an internal memory.

Note: No more than 256 Mbytes can be addressed even if the external device capacity is larger.

If an access is made to an address outside of the range defined by DEVSIZE[4:0] but still within the 256 Mbytes range, then an AHB error is given. The effect of this error depends on the AHB master that attempted the access:

- • If it is the Cortex CPU, a hard-fault interrupt is generated.

- • If it is a DMA, a DMA transfer error is generated, and the corresponding DMA channel is automatically disabled.

Byte, half-word, and word access types are all supported.

A support for execute in place (XIP) operation is implemented, where the OCTOSPI continues to load the bytes to the addresses following the most recent access. If subsequent accesses are continuous to the bytes that follow, then these operations end up quickly since their results were prefetched.

By default, the OCTOSPI never stops its prefetch operation. It either keeps the previous read operation active with the NCS maintained low or it relaunches a new transfer, even if no access to the external device occurs for a long time.

Since external devices tend to consume more power when the NCS is held low, the application may want to activate the timeout counter (TCEN = 1 in OCTOSPI_CR): the NCS is released after a period defined by TIMEOUT[15:0] in OCTOSPI_LPTR, when x cycles have elapsed without access since the clock is inactive.

BUSY goes high as soon as the first memory-mapped access occurs. Because of the prefetch operations, BUSY does not fall until there is an abort, or the peripheral is disabled.

It is not recommended to program the flash memory using the memory-mapped writes. The indirect-write mode fulfills this operation.

However, if the application requires the use of the MCE for encryption (check MCE product availability), the memory-mapped write mode may be used to program encrypted data to external flash memory under the following conditions:

- • Prefetch must be enabled.

- • In block cipher mode, the CPU must write a complete 128-bit data block to prevent the MCE from initiating read-modify-write operations when only a few bytes need to be programmed. This precaution avoids incorrect programming operations. There are no specific constraints to respect if the MCE is used in stream cipher mode.

- • Apply the abort sequence to exit memory-mapped mode when the data linked to the page has been written in the external memory buffers. The abort sequence triggers the start of the page programming.

- • Switch to the automatic status-polling mode to monitor the completion of the page programming phase.

- • Relaunch the write enable command in indirect mode, then switch back to the memory-mapped mode configuration to continue to program additional pages if any.

It is recommended to add a synchronization barrier between the end of the controller registers configuration and the first memory-mapped access to the external memory when the controller is configured in memory-mapped mode.

The controller can apply an automatic address offset to simplify memory area code switching, such as during a firmware update (if the address offset feature is available in the product implementation table). To enable this feature, set the ADOFFEN bit in the XSPI_CR register and configure the offset value in the ADOFF[4:0] bitfield of the XSPI_DCR1 register. The offset is modulo 256 bytes.

28.4.12 OCTOSPI configuration introduction

The OCTOSPI configuration is done in three steps:

- 1. OCTOSPI system configuration

- 2. OCTOSPI device configuration

- 3. OCTOSPI mode configuration

28.4.13 OCTOSPI system configuration

The OCTOSPI is configured using OCTOSPI_CR. The user must program:

- • the functional mode with FMODE[1:0]

- • the automatic status-polling mode behavior if needed with PMM and APMS

- • the FIFO level with FTHRES

- • the DMA use with DMAEN

- • the timeout counter use with TCEN

- • the dual-memory configuration, if needed, with DMM

In case of an interrupt use, the respective enable bit can also be set during this phase.

If the timeout counter is used, the timeout value is programmed in OCTOSPI_LPTR.

The DMA channel must not be enabled during the OCTOSPI configuration: it must be enabled only when the operation is fully configured, to avoid any unexpected request generation.

The DMA and OCTOSPI must be configured in a coherent manner regarding data length: FTHRES value must reflect the DMA burst size.

28.4.14 OCTOSPI device configuration

The parameters related to the external device targeted are configured through OCTOSPI_DCR1 and OCTOSPI_DCR2. The user must program:

- • the device size with DEVSIZE[4:0]

- • the chip-select minimum high time with CSHT[5:0]

- • the clock mode with FRCK and CKMODE

- • the device frequency with PRESCALER[7:0]

DEVSIZE[4:0] defines the size of external memory using the following formula:

where DEVSIZE+1 is the number of address bits required to address the external device. The external device capacity can go up to 4 Gbytes (addressed using 32 bits) in indirect mode, but the addressable space in memory-mapped mode is limited to 256 Mbytes.

If DMM = 1, DEVSIZE[4:0] must reflect the total capacity of the two devices together considering the above formula (DEVSIZE[4:0] value is so equal to one of the two memory capacities).

When the OCTOSPI executes two commands, one immediately after the other, it raises the chip-select signal (NCS) high between the two commands for only one CLK cycle by default.

If the external device requires more time between commands, the chip-select high time CSHT[5:0] can be used to specify the minimum number of CLK cycles for which the NCS must remain high.

CKMODE indicates the level that the CLK takes between commands (when NCS = 1).

In HyperBus protocol, the device timing ( \( t_{ACC} \) and \( t_{RWR} \) ) and the latency mode must be configured in OCTOSPI_HLCR.

Memory types

External memory providers may present some architecture and slight data formatting differences between them. The bitfield MTYP[2:0] into the OCTOSPI_CR register allows targeting the right controller configuration depending on the associated memory type selected in the application. This is the responsibility of the software developer to align the controller configuration to fit with the targeted memory type.

The memory types are grouped in a such way:

- • D0/D1 data ordering in octal-SPI data mode (DMODE[2:0] = 100) in DTR mode by configuring MTYP[2:0] = 000. For instance, Micron is using such data ordering. In this configuration, the DQS is sent with a polarity inverted respect to the clock polarity.

Figure 157. D0/D1 data ordering in octal-SPI DTR mode (Micron) - Read access

![Timing diagram for D0/D1 data ordering in octal-SPI DTR mode (Micron) - Read access. The diagram shows four signals: NCS (chip select), CLK (clock), DQS (data strobe), and IO[7:0] (data bus). NCS is active low. CLK is a periodic square wave. DQS is a data strobe signal that is inverted relative to CLK. IO[7:0] shows the data sequence: EEh, 11h, Address (A31:24, A23:16, A15:8, A7:0), Dummy, and then four word units (D0, D1, D2, D3). The address and dummy phases are indicated by double-headed arrows below the data bus. The diagram is labeled MSV71558V1.](/RM0456-STM32U5/8e4def2d60b117d0e3617d22d9bd9d7a_img.jpg)

- • D1/D0 data ordering in octal-SPI data mode (DMODE[2:0] = 100) in DTR mode by configuring MTYP[2:0] = 001. For instance, Macronix is using this reverse data ordering in its Octaflash portfolio (this configuration is not adapted to its OctaRAM™ memories). DQS is keeping the same polarity as the clock when reading data from the memory. Refer to Figure 148: DTR read in octal-SPI mode with DQS (Macronix mode) example .

- • D1/D0 data ordering in octal-SPI data mode (DMODE[2:0] = 100) in DTR mode by configuring MTYP[2:0] = 011 with specific address phase built with row and column to fit with Macronix OctaRAM™ memories requirement (refer to Table 255: OctaRAM command address bit assignment (based on 64-Mbyte OctaRAM) ). This is the controller which translates internally the targeted address provided by the software in row/column

address formatting to sent to the memory. DQS is keeping the same polarity as the clock one when reading data from the memory.

Figure 158. OctaRAM read operation with reverse data ordering D1/D0

![Timing diagram for OctaRAM read operation with reverse data ordering D1/D0. The diagram shows four signals: NCS (active low), CLK (clock), DQS (data strobe), and IO[7:0] (data bus). The sequence starts with NCS going low. CLK is a periodic square wave. DQS is initially low, then goes high to match CLK polarity. IO[7:0] shows a Command, followed by Row address and Column address, collectively labeled 'Command & Address'. After a break in the timeline, the data bus shows four data units: D1, D0, D3, and D2, grouped into two 'Word Unit' labels. The diagram is labeled MSV71560V1.](/RM0456-STM32U5/0990ab0153da596cb7e559fd7ac754c3_img.jpg)

Table 255. OctaRAM command address bit assignment

(based on 64-Mbyte

(1)

OctaRAM)

| Clock | 1st clock | 2nd clock | 3rd clock | ||

|---|---|---|---|---|---|

| Function | Command | Row address | Column address | ||

| SIO[7] | Command | Reserved | RA7 | CA9 | Reserved |

| SIO[6] | Reserved | RA6 | CA8 | Reserved | |

| SIO[5] | Reserved | RA5 | CA7 | Reserved | |

| SIO[4] | RA12 | RA4 | CA6 | Reserved | |

| SIO[3] | RA11 | RA3 | CA5 | CA3 | |

| SIO[2] | RA10 | RA2 | CA4 | CA2 | |

| SIO[1] | RA9 | RA1 | Reserved | CA1 | |

| SIO[0] | RA8 | RA0 | Reserved | CA0 (2) | |

1. Example of 64-Mbyte OctaRAM address assignment:

Row Address [RA12:RA0]: 8K. Column address [CA9:CA0]: 1K. 64-Mbyte density = 8K x 1K x 8 bits

2. Column address A0 must be always 0.

- HyperBus memories need to be selected when targeted by the application. The configuration to set depends on the access type:

- HyperBus memory mode: The protocol follows the HyperBus specification. MTYP[2:0] = 100 is the configuration to use to access the memory space.

- HyperBus register mode (addressing register space): the memory-mapped accesses in this mode must be noncacheable, or the indirect read/write modes must be used. The configuration to be set for this particular register space access is MTYP[2:0] = 101.

- Standard mode. It is the mode to use whenever the targeted memory is not corresponding to any others configurations described in this section. MTYP[2:0] = 010 for this standard mode.

28.4.15 OCTOSPI regular-command mode configuration

Indirect mode configuration

When FMODE[1:0] = 00, the indirect-write mode is selected and data can be sent to the external device. When FMODE[1:0] = 01, the indirect-read mode is selected, and data can be read from the external device.

When the OCTOSPI is used in indirect mode, the frames are constructed in the following way:

- 1. Specify a number of data bytes to read or write in OCTOSPI_DLR.

- 2. Specify the frame timing in OCTOSPI_TCR.

- 3. Specify the frame format in OCTOSPI_CCR.

- 4. Specify the instruction in OCTOSPI_IR.

- 5. Specify the optional alternate byte to be sent right after the address phase in OCTOSPI_ABR.

- 6. Specify the targeted address in OCTOSPI_AR.

- 7. Enable the DMA channel if needed.

- 8. Read/write the data from/to the FIFO through OCTOSPI_DR (if no DMA usage).

If neither the address register (OCTOSPI_AR) nor the data register (OCTOSPI_DR) need to be updated for a particular command, then the command sequence starts as soon as OCTOSPI_IR is written. This is the case when both ADMODE[2:0] and DMODE[2:0] equal 000, or if just ADMODE[2:0] = 000 when in indirect-read mode (FMODE[1:0] = 01).

When an address is required (ADMODE[2:0] ≠ 000) and the data register does not need to be written (FMODE[1:0] = 01 or DMODE[2:0] = 000), the command sequence starts as soon as the address is updated with a write to OCTOSPI_AR.

In case of data transmission (FMODE[1:0] = 00 and DMODE[2:0] ≠ 000), the communication start is triggered by a write in the FIFO through OCTOSPI_DR.

Automatic status-polling mode configuration

The automatic status-polling mode is enabled by setting FMODE[1:0] = 10. In this mode, the programmed frame is sent and data are retrieved periodically.

The maximum amount of data read in each frame is 4 bytes. If more data is requested in OCTOSPI_DLR, it is ignored, and only 4 bytes are read. The periodicity is specified in OCTOSPI_PIR.

Once the status data has been retrieved, the following can be processed:

- • Set SMF (an interrupt is generated if enabled).

- • Stop automatically the periodic retrieving of the status bytes.

The received value can be masked with the value stored in OCTOSPI_PSMKR, and can be ORed or ANDed with the value stored in OCTOSPI_PSMAR.

In case of a match, SMF is set and an interrupt is generated if enabled. The OCTOSPI can be automatically stopped if AMPS is set. In any case, the latest retrieved value is available in OCTOSPI_DR.

When the OCTOSPI is used in automatic status-polling mode, the frames are constructed in the following way:

- 1. Specify the input mask in OCTOSPI_PSMKR.

- 2. Specify the comparison value in OCTOSPI_PSMAR.

- 3. Specify the read period in OCTOSPI_PIR.

- 4. Specify a number of data bytes to read in OCTOSPI_DLR.

- 5. Specify the frame timing in OCTOSPI_TCR.

- 6. Specify the frame format in OCTOSPI_CCR.

- 7. Specify the instruction in OCTOSPI_IR.

- 8. Specify the optional alternate byte to be sent right after the address phase in OCTOSPI_ABR.

- 9. Specify the optional targeted address in OCTOSPI_AR.

If the address register (OCTOSPI_AR) does not need to be updated for a particular command, then the command sequence starts as soon as OCTOSPI_CCR is written. This is the case when ADMODE[2:0] = 000.

When an address is required (ADMODE[2:0] ≠ 000), the command sequence starts as soon as the address is updated with a write to OCTOSPI_AR.

Memory-mapped mode configuration

In memory-mapped mode, the external device is seen as an internal memory but with some latency during accesses. Read and write operations are allowed to the external device in this mode.

It is not recommended to program the flash memory using memory-mapped writes, as the internal flags for erase or programming status have to be polled. The indirect-write mode fulfills this operation, possibly in conjunction with the automatic status-polling mode.

The memory-mapped mode is entered by setting FMODE[1:0] = 11 in OCTOSPI_CR.

The programmed instruction and frame are sent when an AHB master accesses the memory-mapped space.

The FIFO is used as a prefetch buffer to anticipate any linear reads. Any access to OCTOSPI_DR in this mode returns zero.

The data length register (OCTOSPI_DLR) has no meaning in memory-mapped mode.

When the OCTOSPI is used in memory-mapped mode, the frames are constructed in the following way:

- 1. Specify the frame timing in OCTOSPI_TCR for read operation.

- 2. Specify the frame format in OCTOSPI_CCR for read operation.

- 3. Specify the instruction in OCTOSPI_IR.

- 4. Specify the optional alternate byte to be sent right after the address phase in OCTOSPI_ABR for read operation.

- 5. Specify the frame timing in OCTOSPI_WTCR for write operation.

- 6. Specify the frame format in OCTOSPI_WCCR for write operation.

- 7. Specify the instruction in OCTOSPI_WIR.

- 8. Specify the optional alternate byte to be sent right after the address phase in OCTOSPI_WABR for write operation.

All configuration operations must be completed (ensured by checking BUSY = 0) before the first access to the memory area: any register write operation when BUSY = 1 has no effect and is not signaled with an error response. On the first access, the OCTOSPI becomes

busy, and no further configuration is allowed. Then, the only way to get BUSY low is to clear the ENABLE bit or to abort by setting the ABORT bit.

OCTOSPI delayed data sampling when no DQS is used

By default, when no DQS is used, the OCTOSPI samples the data driven by the external device one half of a CLK cycle after the external device drives the signal.

In case of any external signal delays, it may be useful to sample the data later. Using SSHIFT in OCTOSPI_TCR, the sampling of the data can be shifted by half of a CLK cycle.

The firmware must clear SSHIFT when the data phase is configured in DTR mode (DDTR = 1).

OCTOSPI delayed data sampling when DQS is used

When external DQS is used as a sampling clock, it can be shifted in time to compensate the data propagation delay.

This shift is performed by a delay hardware element located outside of the controller into the RCC (RCC_DLYCFGR) or implemented on an external dedicated block delay peripheral depending on the product (refer to the product reference manual for information about how to manage and configure the delay).

In configurations where delay does not need to be compensated, the external delay block can be bypassed by setting DLYBYP in OCTOSPI_DCR1.

Sending the instruction only once (SIOO)

A flash memory can provide a mode where an instruction must be sent only with the first command sequence, while subsequent commands start directly with the address. The user can take advantage of this type of features using SIOO in OCTOSPI_CCR.

SIOO is valid for memory-mapped mode only. If this bit is set, the instruction is sent only for the first command following a write to OCTOSPI_CCR.

Subsequent command sequences skip the instruction phase, until there is a write to OCTOSPI_CCR. SIOO has no effect when IMODE[1:0] = 00 (no instruction).

The SIOO mode is not supported when any of the communication regulations, NCS boundary, or refresh features are used.

28.4.16 OCTOSPI HyperBus protocol configuration

Indirect mode configuration (HyperBus)

When FMODE[1:0] = 00, the indirect-write mode is selected and data can be sent to the external device. When FMODE[1:0] = 01, the indirect-read mode is selected where data can be read from the external device. ADMODE must be configured with a value different from 000 (for instance ADMODE = 100).

When the OCTOSPI is used in indirect mode, the frames are constructed in the following way:

- 1. Specify a number of data bytes to read or write in OCTOSPI_DLR.

- 2. Specify the targeted address in OCTOSPI_AR.

- 3. Enable the DMA channel if needed.

- 4. Read/write the data from/to the FIFO through OCTOSPI_DR (if no DMA usage).

In indirect-read mode, the command sequence starts as soon as the address is updated with a write to OCTOSPI_AR.

In indirect-write mode, the communication start is triggered by a write in the FIFO through OCTOSPI_DR.

Memory-mapped mode configuration (HyperBus)

In memory-mapped mode, the external device is seen as an internal memory but with some latency during the accesses. Read and write operations are allowed to the external device in this mode.

It is not recommended to program the flash memory using the memory-mapped writes: the indirect-write mode fulfills this operation.

The memory-mapped mode is entered by setting FMODE[1:0] = 11. The programmed instruction and frame is sent when an AHB master accesses the memory-mapped space.

The FIFO is used as a prefetch buffer to anticipate any linear reads. Any access to OCTOSPI_DR in this mode returns zero.

The data length register (OCTOSPI_DLR) has no meaning in memory-mapped mode.

All the configuration operation must be completed before the first access to the memory area. On the first access, the OCTOSPI becomes busy, and no configuration is allowed. Then, the only way to get BUSY low is to clear the ENABLE bit, or to abort by setting the ABORT bit.

28.4.17 OCTOSPI error management

The following errors set the TEF flag in OCTOSPI_SR and generates an interrupt if enabled (TEIE = 1 in OCTOSPI_CR):

- • in indirect or automatic status-polling mode, when a wrong address has been programmed in OCTOSPI_AR (according to the device size defined by DEVSIZE[4:0]).

- • in indirect mode, if the address plus the data length exceed the device size: TEF is set as soon as the access is triggered.

In memory-mapped mode, the OCTOSPI generates an AHB slave error in the following situations, setting the BERRF flag in XSPI_SR and generating an interrupt if enabled (BERRIE = 1 in XSPI_CR) (if the Bus error bit feature is available in the product implementation table, otherwise the Slave bus error response is generated at system level as transaction response with no dedicated bit into the controller status register):

- • The memory-mapped mode is disabled and an AHB read or write request occurs.

- • A read or write address (including the address offset if ADOFFEN bit is set) exceeds the size of the external memory.

- • An abort is received while a read or write burst is ongoing.

- • The OCTOSPI is disabled while a read or write burst is requested.

- • A write wrap burst is received.

- • A write request is received while DQSE = 0 in OCTOSPI_WCCR in octal DTR mode, in dual-memory configuration, in HyperBus mode.

- • A read or write request is received while DMODE[2:0] = 000 (no data phase), except when MTYP[2:0] is HyperBus.

- • Illegal access size when wrap read burst. This means that the AHB bus transfer size (HSIZE) is different from 4 bytes (only for memory-mapped mode).

- • Bit DMM is set in OCTOSPI_CR (dual-memory configuration) and octal mode is set.

28.4.18 OCTOSPI BUSY and ABORT

Once the OCTOSPI starts an operation with the external device, BUSY is automatically set in OCTOSPI_SR.

In indirect mode, BUSY is reset once the OCTOSPI has completed the requested command sequence and the FIFO is empty.

In automatic status-polling mode, BUSY goes low only after the last periodic access is complete, due to a match when APMS = 1 or due to an abort.

After the first access in memory-mapped mode, BUSY goes low only on an abort.

Any operation can be aborted by setting ABORT in OCTOSPI_CR. Once the abort is completed, BUSY and ABORT are automatically reset, and the FIFO is flushed.

Before setting ABORT, the software must ensure that all the current transactions are finished using the synchronization barriers. When DMA is enabled to handle the data read or write operations in OCTOSPI_DR, it is recommended to disable the DMA channel before aborting the OCTOSPI.

Note: Some devices may misbehave if a write operation to a status register is aborted.

28.4.19 OCTOSPI reconfiguration or deactivation

Before any OCTOSPI reconfiguration, the software must ensure that all the transactions are completed:

- • After a memory-mapped write, the software must perform a dummy read followed by a synchronization barrier, then an abort.

- • After a memory-mapped read, the software must perform a synchronization barrier than an abort.

28.4.20 NCS behavior

By default, NCS is high, deselecting the external device. NCS falls before an operation begins and rises as soon as it finishes.

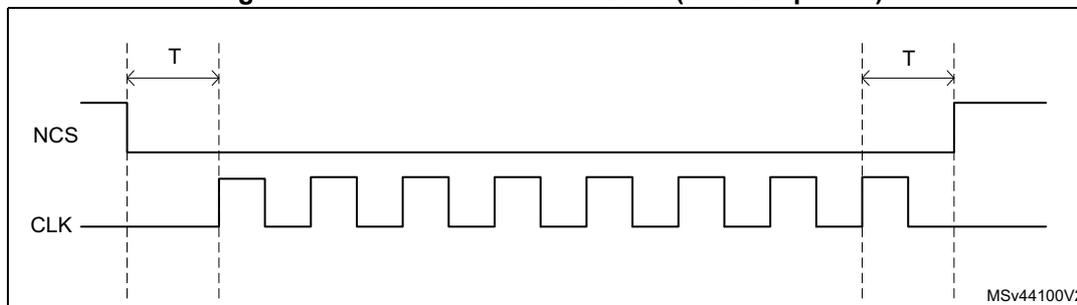

When CKMODE = 0 (clock mode 0: CLK stays low when no operation is in progress), NCS falls one CLK cycle before an operation first rising CLK edge, and NCS rises one CLK cycle after the operation final rising CLK edge (see the figure below).

Figure 159. NCS when CKMODE = 0 (T = CLK period)

The diagram shows two signal lines, NCS and CLK, over time. The NCS line starts at a high level. The CLK line is initially low and then begins a periodic square wave oscillation. Vertical dashed lines mark the rising edges of the CLK signal. The first rising edge of CLK is preceded by a falling edge of NCS. The NCS line remains low until after the last rising edge of CLK, at which point it rises back to its initial high level. The period between two consecutive rising edges of CLK is labeled 'T'.

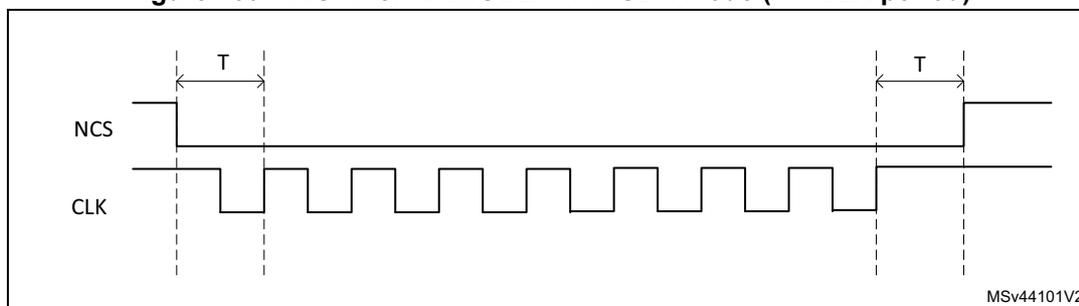

When CKMODE = 1 (clock mode 3: CLK goes high when no operation is in progress) and when in SDR mode, NCS falls one CLK cycle before an operation first rising CLK edge, and NCS rises one CLK cycle after the operation final rising CLK edge (see the figure below).

Figure 160. NCS when CKMODE = 1 in SDR mode ( \( T = \text{CLK period} \) )

The diagram shows two signals: NCS (top) and CLK (bottom). NCS is active-low. CLK is a square wave that is high when idle. The diagram illustrates that NCS falls exactly one clock period (T) before the first rising edge of the CLK signal. After the final rising edge of the CLK signal, NCS remains low for one full clock period (T) before returning high. The idle state for CLK is high.

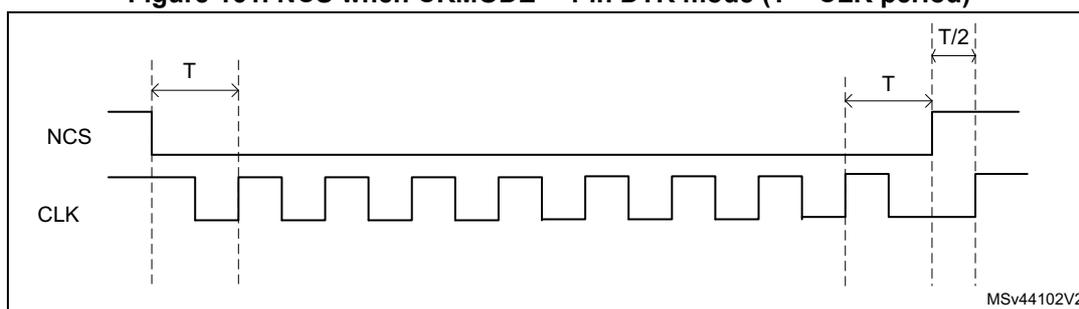

When the CKMODE = 1 (clock mode 3) and DDTR = 1 (data DTR mode), NCS falls one CLK cycle before an operation first rising CLK edge, and NCS rises one CLK cycle after the operation final active rising CLK edge (see the figure below). Because the DTR operations must finish with a falling edge, CLK is low when NCS rises, and CLK rises back up one half of a CLK cycle afterwards.

Figure 161. NCS when CKMODE = 1 in DTR mode ( \( T = \text{CLK period} \) )

The diagram shows NCS and CLK signals. NCS falls one clock period (T) before the first rising edge of CLK. In DTR mode, the operation ends on a falling edge of CLK. NCS rises one full clock period (T) after the final active rising edge of CLK. At the moment NCS rises, CLK is in a low state. CLK then returns to its high idle state one half-period ( \( T/2 \) ) after NCS has risen.

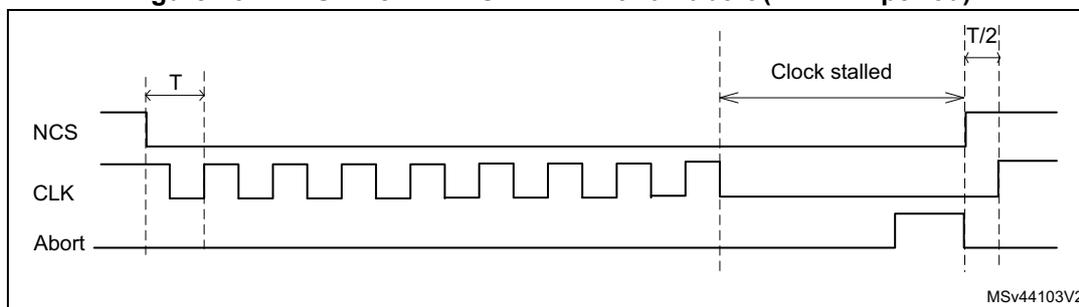

When the FIFO stays full during a read operation, or if the FIFO stays empty during a write operation, the operation stalls and CLK stays low until the software services the FIFO. If an abort occurs when an operation is stalled, NCS rises just after the abort is requested and then CLK rises one half of a CLK cycle later (see the figure below).

Figure 162. NCS when CKMODE = 1 with an abort ( \( T = \text{CLK period} \) )

The diagram shows three signals: NCS, CLK, and Abort. It begins with NCS falling one period (T) before the first CLK rising edge. During the operation, a 'Clock stalled' condition occurs where CLK remains low. While the clock is stalled, an Abort signal is asserted (goes high). Immediately following the abort request, NCS rises to its inactive high state. One half clock period ( \( T/2 \) ) after NCS rises, the CLK signal returns to its high idle state.

28.5 Address alignment and data number

The table below summarizes the effect of the address alignment and programmed data number depending on the use case.

Table 256. Address alignment cases

| Memory type | Transaction type | Constraint on address (1) | Impact if constraint on address not respected | Constraint on number of bytes (1) | Impact if constraint on bytes not respected |

|---|---|---|---|---|---|

| Single, dual, quad flash or SRAM (DMM = 0) | IND (2) read | None | None | None | None |

| MM (3) read | |||||

| IND write | |||||

| MM write | |||||

| Single, dual, quad flash or SRAM (DMM = 1) | IND read | Even | ADDR[0] is set to 0. (4) | Even | DLR[0] is set to 1. (5) |

| MM read | None | None | None | None | |

| IND write | Even | ADDR[0] is set to 0. (4) | Even | DLR[0] is set to 1. (5) | |

| MM write | Even | Slave error | Even | Last byte is lost. | |

| Octal flash in SDR mode | IND read | None | None | None | None |

| MM read | |||||

| IND write | |||||

| MM write | |||||

| Octal memory in DTR mode without WDM (6) or 8-bit HyperFLASH | IND read | Even | ADDR[0] is set to 0. (4) | Even | DLR[0] is set to 1. (5) |

| MM read | None | None | None | None | |

| IND write | Even | ADDR[0] is set to 0. (4) | Even | DLR[0] is set to 1. (5) | |

| MM write | Even | Slave error | Even | Last byte is lost. | |

| Octal flash or RAM in DTR mode with WDM | IND read | Even | ADDR[0] is set to 0. (4) | Even | DLR[0] is set to 1. (5) |

| MM read | None | None | None | None | |

| IND write (7) | |||||

| MM write | |||||

| 8-bit HyperRAM | IND read | Even | ADDR[0] is set to 0. (4) | Even | DLR[0] is set to 1. (5) |

| MM read | None | None | None | None | |

| IND write (7) | |||||

| MM write |

1. To be respected by the software.

2. IND = indirect mode.

3. MM = memory-mapped mode

4. Extra data at transfer start.

5. Extra data at transfer end.

6. WDM = write data mask.

- 7. If the FTHRES bitfield is set to the maximum value with DLR value greater than the data burst length, and if the DMA is enabled or the interrupt based on FIFO THRESHOLD Flag is enabled (FTF), the address must be modulo 2 aligned in DTR mode when the initiator (DMA, CPU, ...) is writing the data with a burst length equal to the FIFO size.

28.6 OCTOSPI interrupts

An interrupt can be produced on the following events:

- • Timeout

- • Status match

- • FIFO threshold

- • Transfer complete

- • Transfer error

Separate interrupt enable bits are available to provide more flexibility.

Table 257. OCTOSPI interrupt requests

| Interrupt event | Event flag | Enable control bit |

|---|---|---|

| Timeout | TOF | TOIE |

| Status match | SMF | SMIE |

| FIFO threshold | FTF | FTIE |

| Transfer complete | TCF | TCIE |

| Transfer error | TEF | TEIE |

28.7 OCTOSPI registers

28.7.1 OCTOSPI control register (OCTOSPI_CR)

Address offset: 0x0000

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | FMODE[1:0] | Res. | Res. | Res. | Res. | PMM | APMS | BERRIE | TOIE | SMIE | FTIE | TCIE | TEIE | |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | FTHRES[4:0] | MSEL | DMM | Res. | ADOFFEN | TCEN | DMAEN | ABORT | EN | ||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | w | rw | |||||

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:28 FMODE[1:0] : Functional mode

This bitfield defines the OCTOSPI functional mode of operation.

00: Indirect-write mode

01: Indirect-read mode

10: Automatic status-polling mode (relevant in regular-command protocol only)

11: Memory-mapped mode

If DMAEN = 1 already, then the DMA controller for the corresponding channel must be disabled before changing the FMODE[1:0] value.

Note: This bitfield can be modified only when BUSY = 0.

Bits 27:24 Reserved, must be kept at reset value.

Bit 23 PMM : Polling match mode

This bit indicates which method must be used to determine a match during the automatic status-polling mode.

0: AND-match mode, SMF is set if all the unmasked bits received from the device match the corresponding bits in the match register.