11. Reset and clock control (RCC)

11.1 RCC introduction

The reset and clock control (RCC) manages the different kind of reset, and generates all clocks for the bus and peripherals.

11.2 RCC pins and internal signals

The table below lists the RCC inputs and output signals connected to package pins or balls.

Table 112. RCC input/output signals connected to package pins or balls

| Signal name | Signal type | Description |

|---|---|---|

| NRST | I/O | System reset, can be used to provide reset to external devices |

| OSC32_IN | I | 32 kHz oscillator input |

| OSC32_OUT | O | 32 kHz oscillator output |

| OSC_IN | I | System oscillator input |

| OSC_OUT | O | System oscillator output |

| MCO | O | Output clock for external devices |

| LSCO | O | Low-speed output clock for external devices |

| AUDIOCLK | I | External kernel clock input for SAI1, SAI2, MDF1 and ADF1 |

11.3 RCC reset functional description

There are three types of reset:

- • a system reset

- • a power reset

- • a backup domain reset

11.3.1 Power reset

A power reset is generated when one of the following events occurs:

- • a brownout reset (BOR)

- • when exiting Standby mode

- • when exiting Shutdown mode

A BOR sets all registers to their reset values except the ones in the backup domain.

When exiting Standby mode, all registers in the core domain are set to their reset value. Registers outside the core domain (RTC, TAMP, WKUP, IWDG, and Standby/Shutdown mode control) are not impacted.

When exiting Shutdown mode, a brownout reset is generated, resetting all registers except those in the backup domain.

11.3.2 System reset

A system reset sets all registers to their reset values except the reset flags in RCC_CSR, and the registers in the backup domain.

A system reset is generated when one of the following events occurs:

- • a low level on the NRST pin (external reset)

- • a window watchdog event (WWDG reset)

- • an independent watchdog event (IWDG reset)

- • a software reset (SW reset) (see Software reset )

- • a low-power mode security reset (see Low-power mode security reset )

- • an option-byte loader reset (see Option byte loader reset )

- • a brownout reset

The reset source can be identified by checking the reset flags in RCC_CSR.

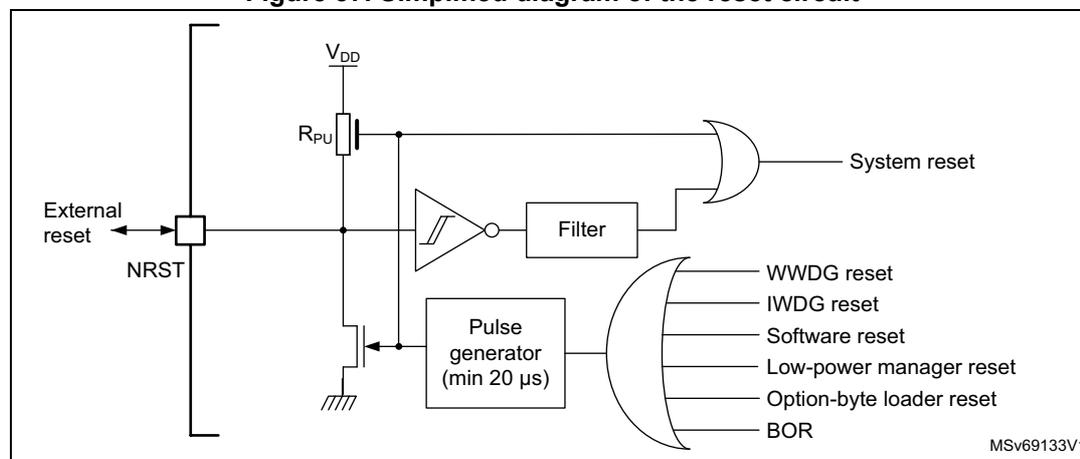

These sources act on the NRST pin and this pin is always kept low during the delay phase. The reset service routine vector is selected via the boot option bytes.

The system reset signal provided to the device is output on the NRST pin. The pulse generator guarantees a minimum reset pulse duration of 20 µs for each internal reset source. In case of an external reset, the reset pulse is generated while the NRST pin is asserted low.

In case of an internal reset, the internal pull-up \( R_{PU} \) is deactivated in order to save the power consumption through the pull-up resistor.

Figure 37. Simplified diagram of the reset circuit

Software reset

The SYSRESETREQ bit in Cortex-M33 application interrupt and reset control register must be set to force a software reset on the device.

Low-power mode security reset

To avoid that critical applications mistakenly enter a low-power mode, the following low-power mode security resets are available. If enabled in option bytes, the resets are generated in any of the following conditions:

- • Entering Standby mode: this type of reset is enabled by resetting NRST_STDBY bit in user option bytes. In this case, whenever a Standby mode entry sequence is successfully executed, the device is reset instead of entering Standby mode.

- • Entering Stop mode: this type of reset is enabled by resetting NRST_STOP bit in user option bytes. In this case, whenever a Stop mode entry sequence is successfully executed, the device is reset instead of entering Stop mode.

- • Entering Shutdown mode: this type of reset is enabled by resetting NRST_SHDW bit in user option bytes. In this case, whenever a Shutdown mode entry sequence is successfully executed, the device is reset instead of entering Shutdown mode.

For further information on the user option bytes, refer to Section 7.4.1: Option bytes description .

Option byte loader reset

The option byte loader reset is generated when the OBL_LAUNCH bit is set in the FLASH_NSCR register. This bit is used to launch the option byte loading by software.

11.3.3 Backup domain reset

The backup domain has two specific resets.

A backup domain reset is generated when one of the following events occurs:

- • a software reset, triggered by setting BDRST bit RCC_BDCR

- • a V DD or V BAT power on, if both supplies have previously been powered off

A backup domain reset affects the LSE oscillator, the RTC, the TAMP, the backup registers, RCC_BDCR, and PWR_BDCR1. The reset of PWR_BDCR1 affects the backup SRAM. Backup domain reset caused by power on resets SRAM2 to zero as it is corresponding to a tamper policy.

11.4 RCC clock functional description

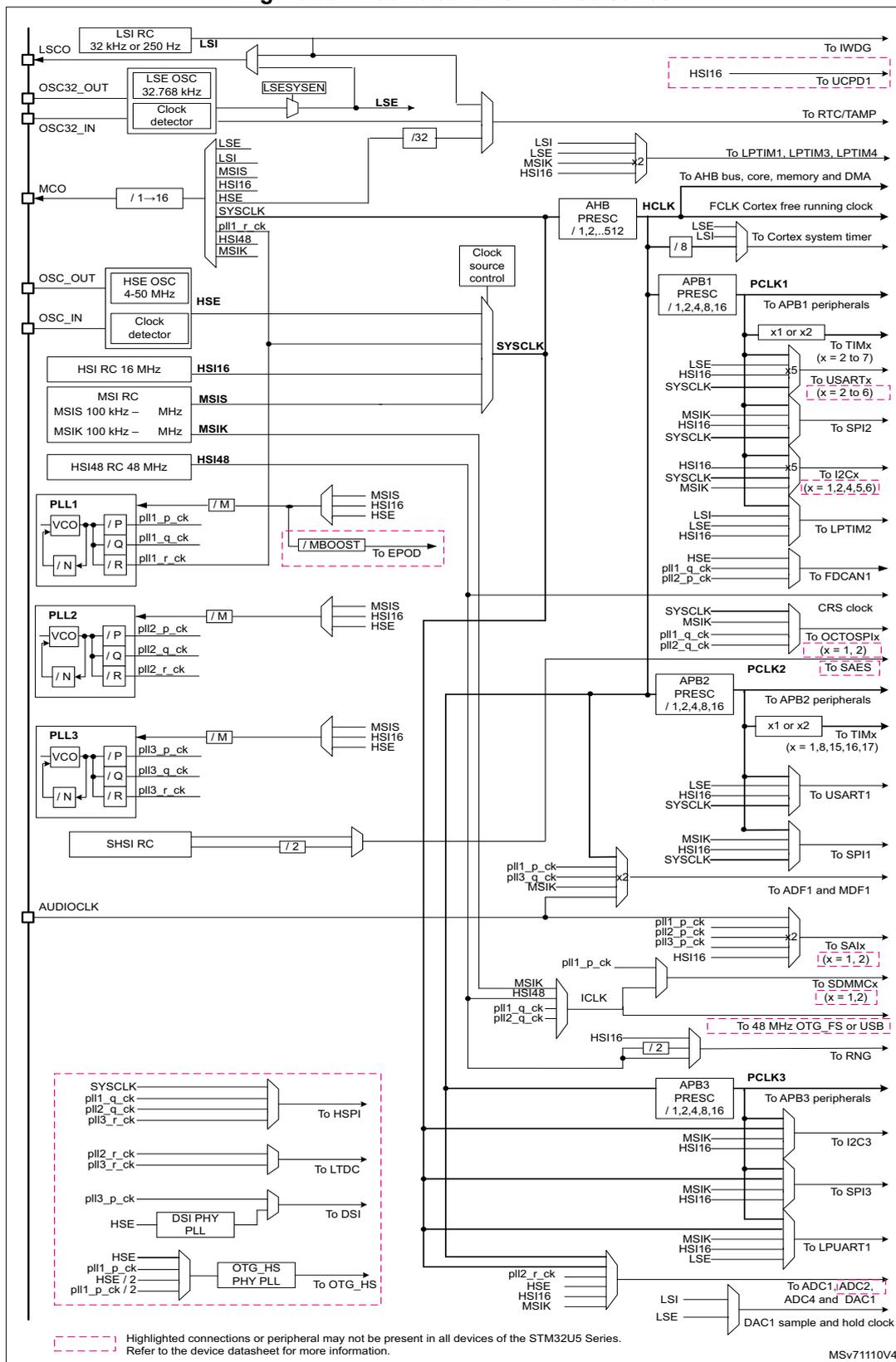

Four different clock sources can be used to drive the system clock (SYSCLK):

- • HSI16: high-speed internal 16 MHz RC oscillator clock

- • MSIS: multi-speed internal RC oscillator clock

- • HSE: high-speed external crystal or clock, from 4 to 50 MHz

- • PLL1 clock

The MSIS is used as system clock source after startup from reset, configured at 4 MHz.

The devices have the following additional clock sources:

- • MSIK: multi-speed internal RC oscillator clock used for peripherals kernel clocks

- • LSI: 32 kHz/250 Hz low-speed internal RC that drives the independent watchdog and optionally the RTC used for auto-wake-up from Stop and Standby modes

- • LSE: 32.768 kHz low-speed external crystal or clock that optionally drives the real-time clock (rtc_ck)

- • HSI48: internal 48 MHz RC that potentially drives the OTG_FS, the USB, the SDMMC, and the RNG

- • SHSI: secure high-speed internal 48 MHz RC that drives the SAES

- • PLL2 and PLL3 clocks

Each clock source can be switched on or off independently when it is not used, to optimize power consumption.

Several prescalers can be used to configure the AHB frequency, the APB1, APB2, and APB3 domains. The maximum frequency of the AHB and APB domains is 160 MHz.

All the peripheral clocks are derived from their bus clock (HCLK, PCLK1, PCLK2, or PCLK3) except the following ones that receive an independent kernel clock. This kernel clock can be selected by software between several sources thanks to RCC_CCIPRx registers ( \( x = 1, 2, 3 \) ): OTG_FS, USB, or OTG_HS, SDMMCx ( \( x = 1, 2 \) ), RNG, ADCx ( \( x = 1, 2, 4 \) ), DAC1, U(S)ARTx ( \( x = 1 \) to 6), LPUART1, I2Cx ( \( x = 1 \) to 6), SPIx ( \( x = 1 \) to 3), OCTOSPIx ( \( x = 1, 2 \) ), SAIx ( \( x = 1, 2 \) ), MDF1, ADF1, FDCAN1, LPTIMx ( \( x = 1 \) to 4), SAES, DSI, LTDC, HSPI1.

In addition, the RTC kernel clock is selected by software in RCC_BDCR. The IWDG clock is always the LSI 32 kHz clock.

The RCC feeds the Cortex system timer (SysTick) external clock with the AHB clock (HCLK) divided by eight, or LSE or LSI. The SysTick can work either with this clock or directly with the Cortex clock (HCLK), configurable in the SysTick control and status register.

FCLK acts as Cortex-M33 free-running clock.

Figure 38. Clock tree for STM32U5 series

The diagram illustrates the clock tree for the STM32U5 series. It shows the following components and connections:

- External Oscillators:

- LSI RC: 32 kHz or 250 Hz, connected to LSCO and LSI.

- LSE OSC: 32.768 kHz, connected to OSC32_IN, OSC32_OUT, and LSE.

- HSE OSC: 4-50 MHz, connected to OSC_IN, OSC_OUT, and HSE.

- Internal Oscillators:

- HSI RC: 16 MHz, connected to HSI16.

- MSI RC: 100 kHz – MHz, connected to MSIS.

- MSIK: 100 kHz – MHz, connected to MSIK.

- HSI48 RC: 48 MHz, connected to HSI48.

- SHSI RC: connected via /2 prescaler.

- PLLs:

- PLL1: VCO with /P, /Q, /N dividers. Outputs: pll1_p_ck, pll1_q_ck, pll1_r_ck. Includes a /M prescaler and a /MBOOST output to EPOD.

- PLL2: VCO with /P, /Q, /N dividers. Outputs: pll2_p_ck, pll2_q_ck, pll2_r_ck. Includes a /M prescaler.

- PLL3: VCO with /P, /Q, /N dividers. Outputs: pll3_p_ck, pll3_q_ck, pll3_r_ck. Includes a /M prescaler.

- Clock Source Control: Selects between LSE, LSI, MSIS, HSI16, HSE, SYSCLK, pll1_r_ck, HSI48, and MSIK.

- AHB Prescaler: /1,2,...,512, outputting HCLK to the AHB bus, core, memory, and DMA.

- APB1 Prescaler: /1,2,4,8,16, outputting PCLK1 to APB1 peripherals.

- APB2 Prescaler: /1,2,4,8,16, outputting PCLK2 to APB2 peripherals.

- APB3 Prescaler: /1,2,4,8,16, outputting PCLK3 to APB3 peripherals.

- Other Connections:

- Audio: AUDIOCLK, ICLK (from pll1_q_ck, pll2_q_ck, HSI16) to ADF1 and MDF1.

- Display/Interface: SYSCLK, pll1_q_ck, pll2_q_ck, pll3_r_ck to HSPI, LTDC, DSI (via DSI PHY PLL).

- USB: HSE, pll1_p_ck/2 to OTG_HS PHY PLL.

- ADCs: LSI, LSE to ADC1, ADC2, ADC4 and DAC1.

- Other Peripherals: Connections to IWDG, UCPD1, RTC/TAMP, LPTIM1, LPTIM3, LPTIM4, Cortex system timer, TIMx, USARTx, SPI2, I2Cx, LPTIM2, FDCAN1, CRS clock, OCTOSPIx, SAES, USART1, SPI1, SAix, SDMMCx, RNG, I2C3, SPI3, LPUART1.

Highlighted connections or peripheral may not be present in all devices of the STM32U5 Series.

Refer to the device datasheet for more information.

MSV71110V4

11.4.1 HSE clock

The high-speed external clock signal (HSE) can be generated from two possible clock sources:

- • HSE external crystal/ceramic resonator

- • HSE user external clock

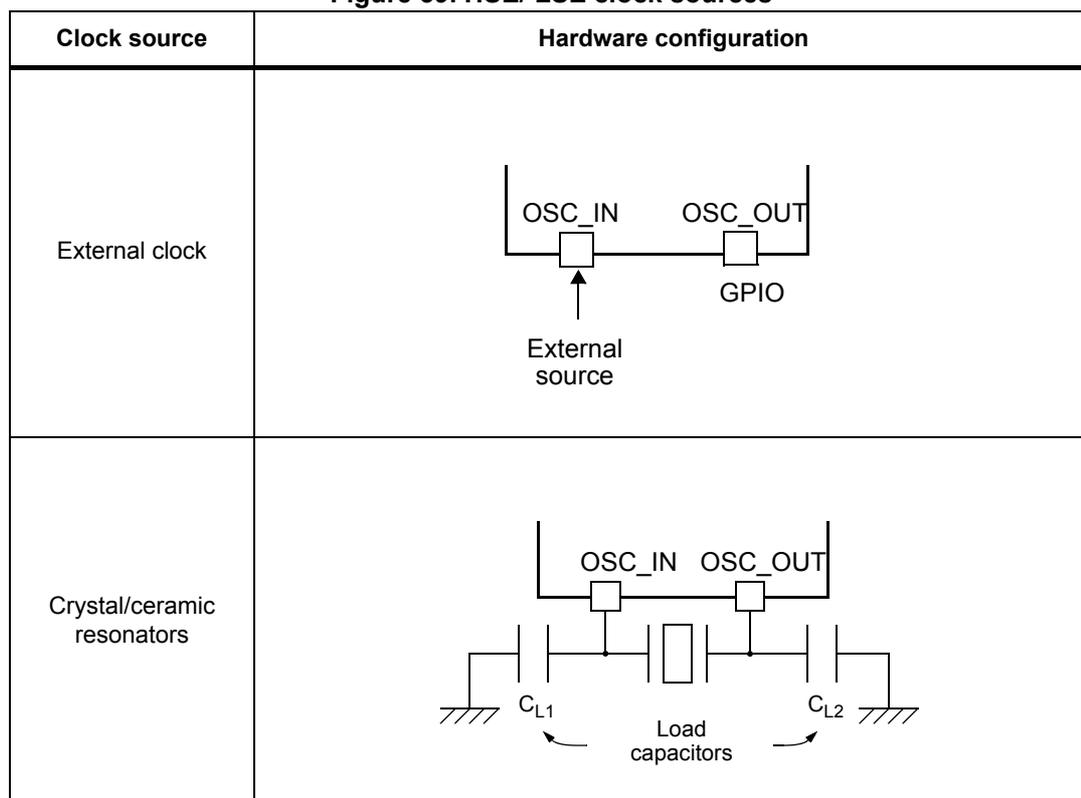

The resonator and the load capacitors must be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

Figure 39. HSE/ LSE clock sources

| Clock source | Hardware configuration |

|---|---|

| External clock | |

| Crystal/ceramic resonators |

External crystal/ceramic resonator (HSE crystal)

The 4 to 50 MHz external oscillator has the advantage of producing a very accurate rate on the main clock.

The associated hardware configuration is shown in Figure 39 . Refer to the electrical characteristics section of the datasheet for more details.

HSERDY in RCC_CR indicates if the HSE oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in RCC_CIER.

The HSE crystal can be switched on and off using HSEON in RCC_CR.

External source (HSE bypass)

In this mode, an external clock source must be provided. It can have a frequency of up to 50 MHz. This mode is selected by setting HSEBYP and HSEON in RCC_CR. The external clock signal (square, sinus, or triangle) with ~40-60 % duty cycle depending on the frequency (refer to the datasheet) must drive the OSC_IN pin while the OSC_OUT pin can be used a GPIO (see Figure 39 ).

11.4.2 HSI16 clock

The HSI16 clock signal is generated from an internal 16 MHz RC oscillator.

The HSI16 RC oscillator has the advantage of providing a clock source at low cost (no external components). It also has a faster startup time than the HSE crystal oscillator. However, even with calibration, the frequency is less accurate than an external crystal oscillator or ceramic resonator.

The HSI16 clock can be selected as system clock after wake-up from Stop modes. Refer to Section 11.8.6 . It can also be used as a backup clock source (auxiliary clock) if the HSE crystal oscillator fails. Refer to Section 11.4.11 .

Calibration

The RC oscillator frequencies may vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by ST for 1 % accuracy at \( T_A = 25^\circ\text{C} \) .

After reset, the factory calibration value is loaded in HSICAL[7:0] of RCC_ICSCR3.

If the application is subject to voltage or temperature variations, this may affect the RC oscillator speed. The HSI16 frequency can be trimmed in the application using HSITRIM[6:0] in RCC_ICSCR3.

For more details on how to measure the HSI16 frequency variation, refer to Section 11.4.23 .

HSIRDY in RCC_CR indicates if the HSI16 RC is stable or not. At startup, the HSI16 RC output clock is not released until this bit is set by hardware.

The HSI16 RC can be switched on and off using HSION in RCC_CR.

The HSI16 signal can also be used as a backup source (auxiliary clock) if the HSE crystal oscillator fails. Refer to Section 11.4.11 .

11.4.3 MSI (MSIS and MSIK) clocks

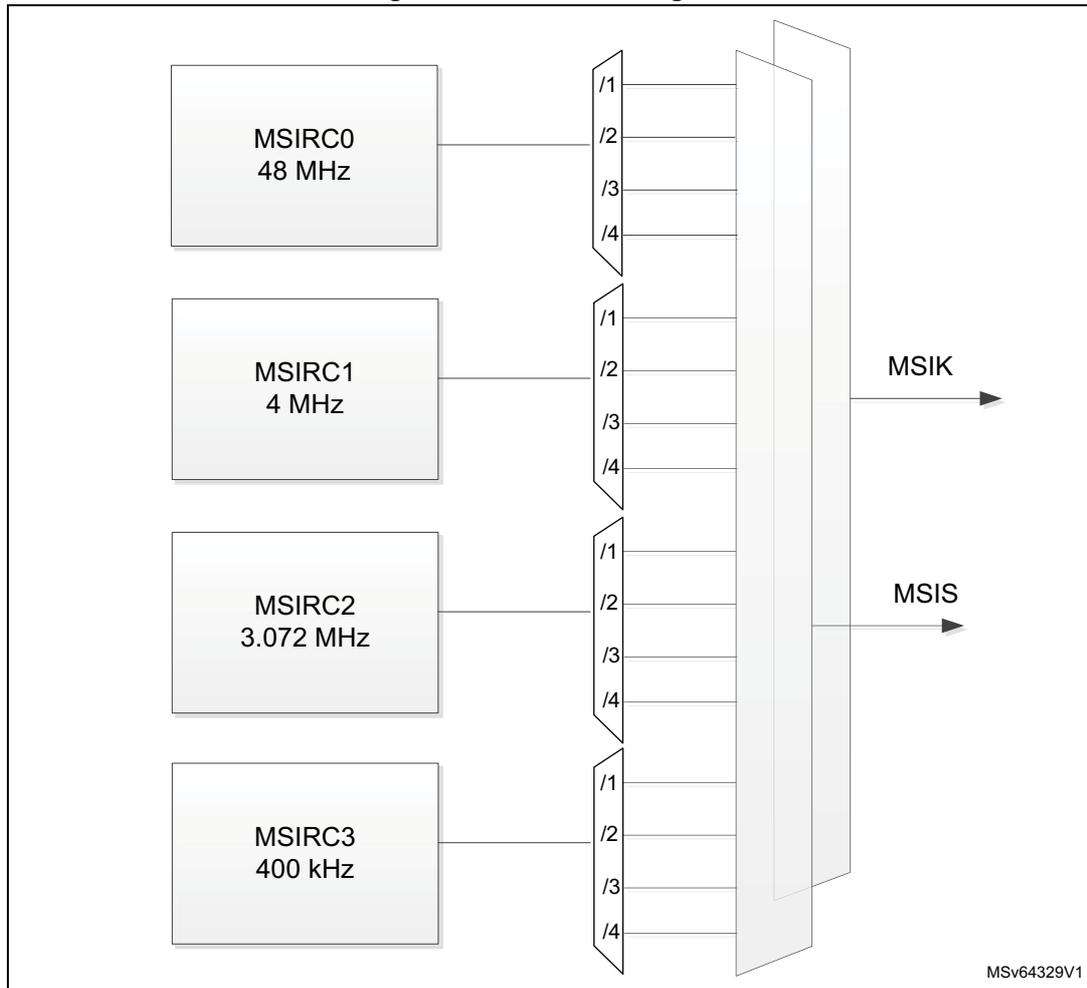

The MSI is made of four internal RC oscillators: MSIRC0 at 48 MHz, MSIRC1 at 4 MHz, MSIRC2 at 3.072 MHz, and MSIRC3 at 400 kHz. Each oscillator feeds a prescaler providing a division by 1, 2, 3, or 4. Two output clocks are generated from these divided oscillators: MSIS that can be selected as system clock, and MSIK that can be selected by some peripherals as kernel clock.

Figure 40. MSI block diagram

Refer to datasheet for complete MSI frequency characteristics in MSI-mode and in PLL-mode. MSIS and MSIK frequency ranges can be adjusted by software, by using respectively MSISRANGE[3:0] and MSIKRANGE[3:0] in RCC_ICSCR1, with MSIRGSEL = 1. Sixteen frequency ranges are available, generated from the four internal RCs, as shown in the table below.

Table 113. MSIS and MSIK ranges per internal MSIRCs (PLL_mode disabled) (1)

| MSIRC0 | MSIRC1 | MSIRC2 | MSIRC3 |

|---|---|---|---|

| Range 0: 48 MHz | Range 4: 4 MHz | Range 8: 3.072 MHz | Range 12: 400 kHz |

| Range 1: 24 MHz | Range 5: 2 MHz | Range 9: 1.536 MHz | Range 13: 200 kHz |

| Range 2: 16 MHz | Range 6: 1.33 MHz | Range 10: 1.024 MHz | Range 14: 133 kHz |

| Range 3: 12 MHz | Range 7: 1 MHz | Range 11: 0.768 MHz | Range 15: 100 kHz |

1. Refer to datasheet for complete MSI frequency characteristics in MSI-mode and in PLL-mode.

The MSIS clock is used as system clock after restart from reset, wake-up from Standby, and Shutdown low-power modes. After restart from reset or when exiting Shutdown mode, MSIS and MSIK frequencies are set to their default value 4 MHz. The frequency range at wake-up from Standby mode can be adjusted by software, using respectively MSISSRANGE[3:0] and MSIKSRANGE[3:0] with MSIRGSEL = 0 (refer to RCC_CSR).

The MSIS clock can be selected as system clock after a wake-up from Stop mode (Stop 0, Stop 1, Stop 2, or Stop 3) depending on STOPWUCK in RCC_CR. It can also be used as a backup clock source (auxiliary clock) if the HSE crystal oscillator fails. See Section 11.4.11 .

The MSI advantage is to provide a low-cost (no external components) low-power clock source. In addition, when used in PLL-mode with the LSE, the MSI provides a very accurate clock source that can be used by the OTG_FS, or the USB, and feeds the PLL.

MSISRDY and MSIKRDY in RCC_CR indicate whether the MSIS and MSIK RC are stable or not. At startup, MSIS and MSIK RC output clocks are not released until their respective bit is set by hardware. The MSIS and MSIK RC can be switched on and off by using MSISON and MSIKON in RCC_CR.

Hardware auto calibration with LSE (PLL-mode)

When a 32.768 kHz external oscillator is present in the application, it is possible to configure either the MSIS or the MSIK in a PLL-mode. This mode is enabled:

- • for MSIS by setting MSIPLLEN with MSIPLLSEL = 1 in RCC_CR

- • for MSIK by setting MSIPLLEN with MSIPLLSEL = 0

In case MSIS and MSIK ranges are generated from the same MSIRC source, the PLL-mode is applied on both MSIS and MSIK. When configured in PLL-mode, the MSIS or MSIK automatically calibrates itself thanks to the LSE. This mode is available for all MSI frequency ranges. At 48 MHz, the MSIK in PLL-mode can be used for the OTG_FS, or the USB, avoiding the need of an external high-speed crystal.

If LSE clocks pulses are stopped, the MSI PLL-mode is automatically unlocked, and the MSI accuracy is consequently degraded. On all STM32U5 devices except STM32U575/585 rev. X, the MSI PLL-mode unlock event is connected to an EXTI line: this is used to generate an event or interrupt supporting wake-up from Stop 0, Stop 1, or Stop 2 mode (see Table 118: Interrupt sources and control and Table 189: EXTI line connections ).

MSI PLL-mode stabilization time

When MSIPLLEN = 1, the final accuracy after enabling the MSI (by writing MSISON = 1 or MSIKON = 1 or following a peripheral clock request in Stop mode) is reached after a stabilization time \( t_{\text{STAB}}(\text{MSI}) \) when MSIPLLFAST = 0. This stabilization time is needed even if the LSE is kept enable. Refer to datasheet for \( t_{\text{STAB}}(\text{MSI}) \) value.

If MSIPLLEN = 1 with MSIPLLFAST = 1, the MSI oscillator is kept powered on when a request to switch it off is received (either by writing MSISON = 0 and MSIKON = 0, or because no peripheral requests this clock in Stop mode). In this case the MSI PLL-mode accuracy is kept when the MSI is switched on again, providing that the \( t_{\text{STAB}}(\text{MSI}) \) stabilization time is reached before switching off the MSI. This mode can be used for autonomous peripherals requiring accuracy in Stop mode, with an extra consumption as the oscillator remains powered on, but gated off when disabled.

Software calibration

The MSIRCx (x = 0 to 3) oscillators frequency may vary from one chip to another due to manufacturing process variations, this is why each device is factory calibrated by ST for 1 % accuracy at an ambient temperature, \( T_A = 25\text{ }^\circ\text{C} \) . After reset, the factory calibration value is loaded in MSICALx[4:0] (x = 0 to 3) in RCC_ICSCR1. If the application is subject to voltage or temperature variations, this may affect the RC oscillator speed. The MSIRCx frequency can be trimmed in the application by using MSITRIMx[4:0] (x = 0 to 3) in RCC_ICSCR.

Note: The final accuracy after applying the calibration value is reached after a stabilization time. This stabilization time is needed after reset of exiting Standby or Shutdown mode. It is also needed when switching from PLL-mode to normal mode.

The hardware auto calibration with LSE must not be used in conjunction with software calibration.

For more details on how to measure the MSI frequency variation, refer to Section 11.4.23 .

11.4.4 HSI48 clock

The HSI48 clock signal is generated from an internal 48 MHz RC oscillator and can be used directly for USB/OTG_FS, and for the RNG, as well as the SDMMC.

The internal 48 MHz RC oscillator is mainly dedicated to provide a high-precision clock to the OTG_FS and the USB by means of a special clock recovery system (CRS) circuitry. The CRS can use the USB SOF signal (only on STM32U535/545/575/585), the LSE, or an external signal to automatically and quickly adjust the oscillator frequency on-the-fly. It is disabled as soon as the system enters Stop or Standby mode. When the CRS is not used, the HSI48 RC oscillator runs on its default frequency that is subject to manufacturing process variations.

For more details on how to configure and use the CRS peripheral, refer to Section 12: Clock recovery system (CRS) .

The HSI48RDY flag in the RCC_CR register indicates whether the HSI48 RC oscillator is stable or not. At startup, the HSI48 RC oscillator output clock is not released until this bit is set by hardware.

The HSI48 can be switched on and off using the HSI48ON bit in the RCC_CR register.

11.4.5 SHSI clock

The SHSI is an internal securable RC oscillator dedicated to clock the SAES. SHSIRDY flag in RCC_CR indicates if the SHSI RC is stable or not. At startup, the SHSI RC output clock is not released until this bit is set by hardware.

The SHSI RC can be switched on and off using SHSION in RCC_CR.

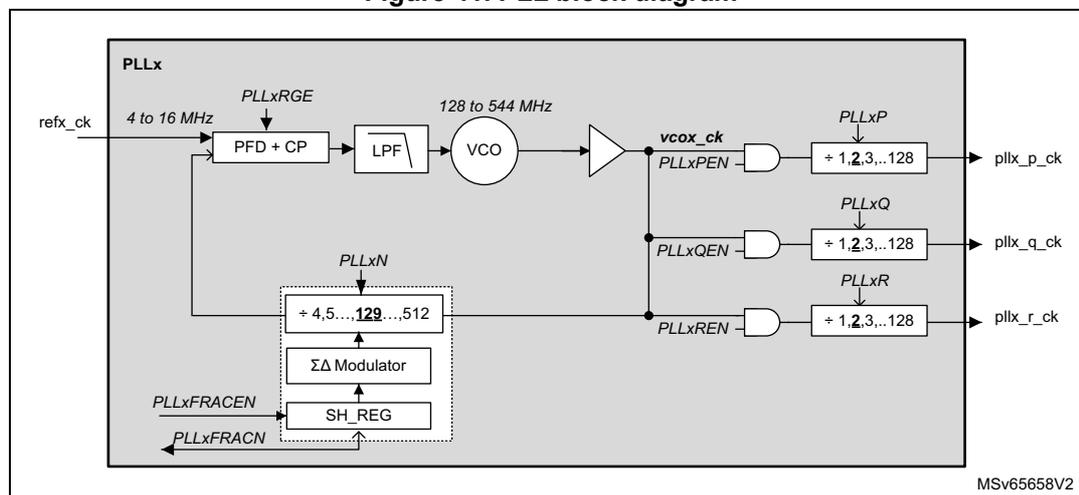

11.4.6 PLL

The RCC features three PLLs:

- • a main PLL, PLL1, that is generally used to provide clocks to the CPU and to some peripherals

- • two dedicated PLL2 and PLL3 that are used to generate the kernel clock for peripherals

The PLLs integrated into the RCC are completely independent. They offer the following features:

- • Input frequency range: 4 to 16 MHz

- • Capability to work either in integer or fractional mode

- • 13-bit sigma-delta ( \( \Sigma\Delta \) ) modulator, allowing to fine-tune the VCO frequency by steps of 11 to 0.3 ppm

- • The \( \Sigma\Delta \) modulator can be updated on-the-fly, without generating frequency overshoots on PLLs outputs.

- • Each PLL offers three outputs with post-dividers.

The PLLs are controlled via RCC_PLLxDIVR, RCC_PLLxFRACR, RCC_PLLxCFGR, and RCC_CR (x = 1, 2, 3).

The frequency of the reference clock provided to the PLLs (refx_ck) must range from 4 to 16 MHz. The user application must program properly the PLLxM (x = 1, 2, 3) dividers in RCC_PLL1CFGR, RCC_PLL2CFGR, and RCC_PLL3CFGR, in order to match this condition. In addition, PLLxRGE must be set according to the reference input frequency to guarantee an optimal performance of the PLL.

To reduce the power consumption, it is recommended to configure the VCOx output to the lowest frequency.

Figure 41. PLL block diagram

PLLxN loop divider must be programmed to achieve the expected frequency at VCO output. In addition, the VCO output range must be respected.

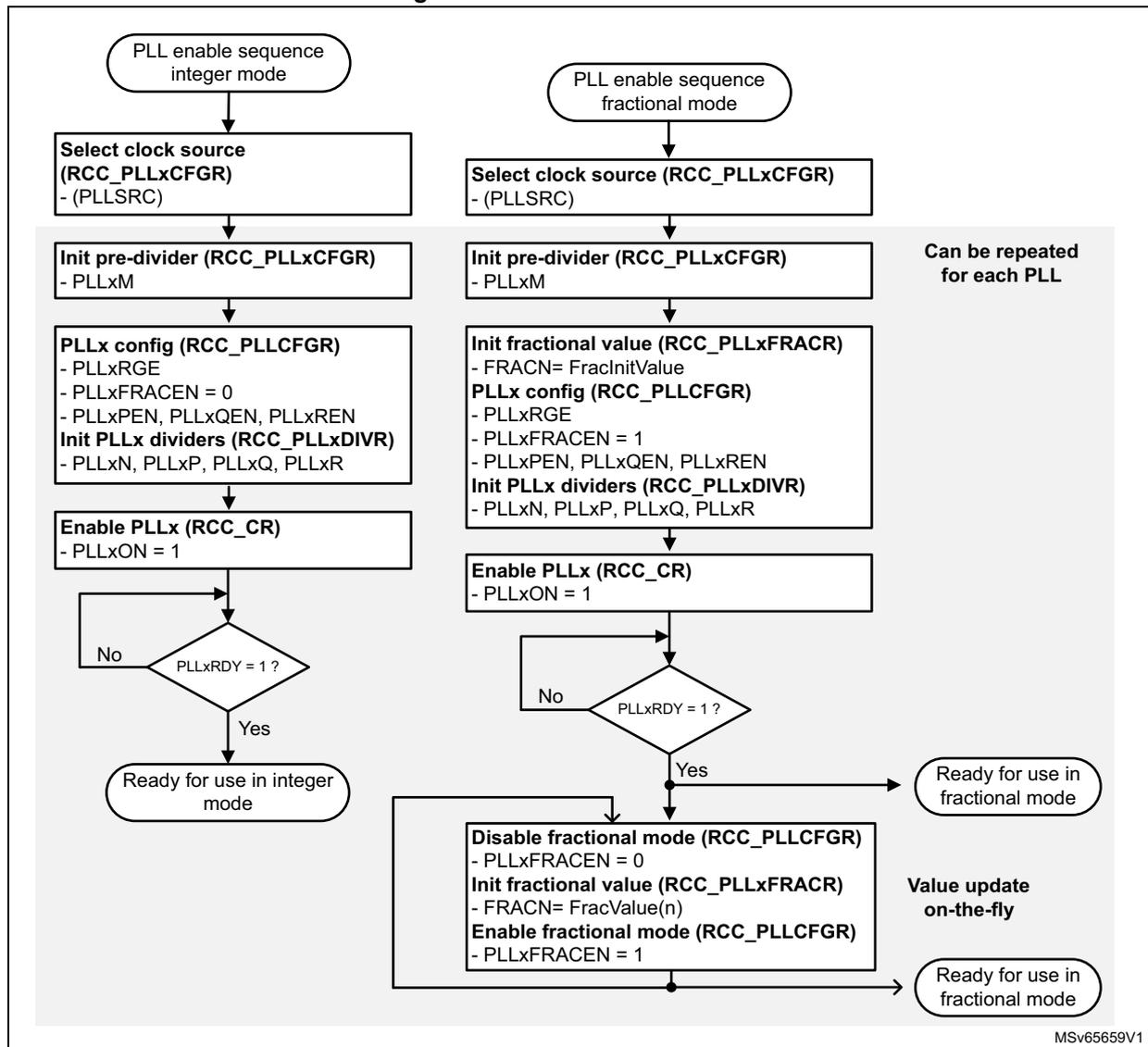

The PLLx operates in integer mode when PLLxFRACEN is 0, and the PLL is enabled with PLLxON. The fractional mode can be enabled at any time by setting PLL1FRACN to the

required value, and subsequently setting PLLxFRACEN from 0 to 1. The \( \Sigma\Delta \) modulator is designed to minimize the jitter impact while allowing very small step frequency adjustments. To update the fractional value, first set PLLxFRACEN to 0 before updating the PLLxFRACN value, and subsequently set PLLxFRACEN to 1. The old PLLxFRACN value is kept used until the new value is activated by setting PLLxFRACEN from 0 to 1. PLLxFRACN must only be updated by software when PLLxFRACEN is 0.

The PLLs can be enabled by setting PLLxON = 1 in RCC_CR. The PLLxRDY bit indicates that the PLL is ready (meaning locked).

Note: Before enabling the PLLs, make sure that the reference frequency (refx_ck) provided to the PLL is stable. The following PLLx parameters cannot be changed once the PLLx is enabled: PLLxSRC, PLLxN, PLLxRGE, PLLxP, PLLxQ, and PLLxR.

The hardware prevents writing PLL1ON to 0 if the PLL1 is currently used to deliver the system clock.

The following PLL parameters cannot be changed once the PLL is enabled: PLLxN, PLLxRGE, PLLxP, PLLxQ, and PLLxR.

To ensure an optimal behavior of the PLL when one of the post-dividers (PLLxP, PLLxQ, or PLLxR) is not used, the application must clear the enable bit (PLLxPEN, PLLxQEN, PLLxREN), and configure the corresponding post-dividers to their minimum value (PLLxR = 0, PLLxP = 0, or PLLxQ = 0).

If the above rules are not respected, the PLL output frequency is not guaranteed.

Output frequency computation

When the PLL operates in integer mode (SH_REG = 0), the VCO frequency ( \( F_{VCO} \) ) is given by the following formula ( \( x = 1, 2, 3 \) ):

When the PLL operates in fractional mode (SH_REG \( \neq \) 0), the PLLxN divider must be initialized before enabling the PLLs. However, the PLLxFRACN value can be changed on-the-fly without disturbing the PLL output.

This feature can be used either to generate a specific frequency from any crystal value with a good accuracy, or to fine-tune the frequency on-the-fly.

For each PLL, the VCO frequency is given by the following formula:

For both integer and fractional mode, the PLL1 output frequency is given by the following formula:

The PLLs are disabled by hardware:

- • when the system enters Stop or Standby mode

- • when an HSE failure occurs, when HSE or PLL (clocked by HSE) are used as system clock

The fractional information used by the PLL is reset when disabling the PLL.

PLL initialization phase

The following PLL initialization sequence in integer and fractional mode is recommended. The PLLx are supposed to be disabled at the start of the initialization sequence:

- 1. Initialize the PLLs registers according to the required frequency.

- – For integer mode, set PLLxFRACEN to 0 in RCC_PLL1CFGR, RCC_PLL2CFGR, and RCC_PLL3CFGR.

- – For fractional mode, set PLLxFRACN to the required initial value (FracInitValue), and then set PLLxFRACEN = 1.

- 2. Once PLLxON = 1, the application must wait until PLLxRDY = 1. As long as PLLxRDY = 0, PLLxFRACEN must not be altered.

- 3. Once PLLxRDY = 1, the PLLx is ready to be used.

- 4. If the application intends to tune the PLLx frequency on-the-fly, then:

- a) PLLxFRACEN must be set to 0 to update the PLLxFRACN value while keeping the PLL running.

- b) Wait at least 3 periods of the PLL reference clock (refx_ck).

- c) A new value can be uploaded into PLLxFRACN (FracValue(n)).

- d) PLLxFRACEN must be set to 1 to activate the new programed value in PLLxFRACN that is taken into account by the PLL.

Figure 42. PLL initialization flow

graph TD

subgraph IntegerMode [ ]

direction TB

I1([PLL enable sequence integer mode]) --> I2[Select clock source

(RCC_PLLxCFGR)

- (PLL_SRC)]

I2 --> I3[Init pre-divider (RCC_PLLxCFGR)

- PLLxM]

I3 --> I4[PLLx config (RCC_PLLxCFGR)

- PLLxRGE

- PLLxFRACEN = 0

- PLLxPEN, PLLxQEN, PLLxREN

Init PLLx dividers (RCC_PLLxDIVR)

- PLLxN, PLLxP, PLLxQ, PLLxR]

I4 --> I5[Enable PLLx (RCC_CR)

- PLLxON = 1]

I5 --> I6{PLLxRDY = 1?}

I6 -- No --> I5

I6 -- Yes --> I7([Ready for use in integer mode])

end

subgraph FractionalMode [ ]

direction TB

F1([PLL enable sequence fractional mode]) --> F2[Select clock source (RCC_PLLxCFGR)

- (PLL_SRC)]

F2 --> F3[Init pre-divider (RCC_PLLxCFGR)

- PLLxM]

F3 --> F4[Init fractional value (RCC_PLLxFRACR)

- FRACN= FracInitValue

PLLx config (RCC_PLLxCFGR)

- PLLxRGE

- PLLxFRACEN = 1

- PLLxPEN, PLLxQEN, PLLxREN

Init PLLx dividers (RCC_PLLxDIVR)

- PLLxN, PLLxP, PLLxQ, PLLxR]

F4 --> F5[Enable PLLx (RCC_CR)

- PLLxON = 1]

F5 --> F6{PLLxRDY = 1?}

F6 -- No --> F5

F6 -- Yes --> F7([Ready for use in fractional mode])

end

I7 --> F8[Disable fractional mode (RCC_PLLxCFGR)

- PLLxFRACEN = 0

Init fractional value (RCC_PLLxFRACR)

- FRACN= FracValue(n)

Enable fractional mode (RCC_PLLxCFGR)

- PLLxFRACEN = 1]

F7 --> F8

F8 --> F9([Ready for use in fractional mode])

style IntegerMode fill:none,stroke:none

style FractionalMode fill:none,stroke:none

style F3 fill:none,stroke:none

style F4 fill:none,stroke:none

style F8 fill:none,stroke:none

style F9 fill:none,stroke:none

style I3 fill:none,stroke:none

style I4 fill:none,stroke:none

style I7 fill:none,stroke:none

style I6 fill:none,stroke:none

style I5 fill:none,stroke:none

style I2 fill:none,stroke:none

style I1 fill:none,stroke:none

style F3 fill:none,stroke:none

style F4 fill:none,stroke:none

style F7 fill:none,stroke:none

style F6 fill:none,stroke:none

style F5 fill:none,stroke:none

style F2 fill:none,stroke:none

style F1 fill:none,stroke:none

style F8 fill:none,stroke:none

style F9 fill:none,stroke:none

The flowchart illustrates the PLL initialization process, starting with two entry points: "PLL enable sequence integer mode" and "PLL enable sequence fractional mode".

Integer Mode Path:

- Select clock source (RCC_PLLxCFGR) - (PLL_SRC)

- Init pre-divider (RCC_PLLxCFGR) - PLLxM

- PLLx config (RCC_PLLxCFGR):

- - PLLxRGE

- - PLLxFRACEN = 0

- - PLLxPEN, PLLxQEN, PLLxREN

- - PLLxN, PLLxP, PLLxQ, PLLxR

- Enable PLLx (RCC_CR) - PLLxON = 1

- Decision: PLLxRDY = 1?

- If No: Loop back to Enable PLLx.

- If Yes: Ready for use in integer mode.

Fractional Mode Path:

- Select clock source (RCC_PLLxCFGR) - (PLL_SRC)

- Init pre-divider (RCC_PLLxCFGR) - PLLxM

- Init fractional value (RCC_PLLxFRACR) - FRACN= FracInitValue

- PLLx config (RCC_PLLxCFGR):

- - PLLxRGE

- - PLLxFRACEN = 1

- - PLLxPEN, PLLxQEN, PLLxREN

- - PLLxN, PLLxP, PLLxQ, PLLxR

- Enable PLLx (RCC_CR) - PLLxON = 1

- Decision: PLLxRDY = 1?

- If No: Loop back to Enable PLLx.

- If Yes: Ready for use in fractional mode.

Value Update on-the-fly:

Both paths lead to a common block for "Value update on-the-fly":

- Disable fractional mode (RCC_PLLxCFGR) - PLLxFRACEN = 0

- Init fractional value (RCC_PLLxFRACR) - FRACN= FracValue(n)

- Enable fractional mode (RCC_PLLxCFGR) - PLLxFRACEN = 1

This sequence results in the system being "Ready for use in fractional mode".

A note indicates that the steps "Init pre-divider", "PLLx config", and "Init PLLx dividers" can be repeated for each PLL.

MSV65659V1

Note: When the PLLxRDY goes to 1, it means that the difference between the PLLx output frequency and the target value is lower than \( \pm 2\% \) .

11.4.7 LSE clock

The LSE crystal is a 32.768 kHz low-speed external crystal or ceramic resonator. It has the advantage of providing a low-power but highly accurate clock source to the real-time clock peripheral (RTC) for clock/calendar or other timing functions.

The LSE crystal is switched on and off using LSEON in RCC_BDCR. If the LSE is used by other peripherals or functions than RTC, TAMP, and LSECSS, the LSESYSEN bit must be also be set in RCC_BDCR (refer to LSE when used by peripherals other than RTC/TAMP, and RCC functions ).

The crystal oscillator driving strength is configured using the LSEDRV[1:0] bits, according to crystal specification, to obtain the best compromise between robustness and short startup

time on one side and low-power-consumption on the other side. The LSE drive must be programmed before enabling the LSE.

LSERDY in RCC_BDCR indicates whether the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by hardware. An interrupt can be generated if enabled in RCC_CIER.

External source (LSE bypass)

In this mode, an external clock source must be provided. This mode is selected by setting LSEBYP and LSEON in RCC_BDCR. The external clock signal (square, sinus, or triangle) with ~50 % duty cycle, must drive the OSC32_IN pin while the OSC32_OUT pin can be used as GPIO (see Figure 39 ).

LSE when used by peripherals other than RTC/TAMP, and RCC functions

By default, when enabled, the LSE is sent only to RTC and TAMP (assuming that RTCSEL = 01).

If the LSE is needed for other peripherals (such as peripheral clock or trigger source), or if the LSE is used by an RCC function (such as LSCO, MCO, MSI PLL mode), the sequence below must be done:

- 1. Set LSEON in RCC_BDCR, and wait for LSERD = 1 in RCC_BDCR.

- 2. Set LSESYSEN = 1 in RCC_BDCR.

- 3. Wait for LSESYSRDY = 1 in RCC_BDCR.

The LSE consumption is increased when LSESYSEN = 1.

11.4.8 LSI clock

The LSI RC acts as a low-power clock source that can be kept running in Stop and Standby modes for the independent watchdog (IWDG) and RTC. The clock frequency is either 32 kHz or 250 Hz depending on LSIPREDIV in RCC_BDCR. Setting LSIPREDIV allows a lower consumption (refer to the electrical characteristics section of the datasheet for more details).

When the IWDG is enabled or when the RTC or TAMP is clocked by the LSI, LSIPREDIV cannot be changed anymore.

The LSI RC can be switched on and off using LSION in RCC_BDCR.

LSIRDY in RCC_BDCR indicates if the LSI oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in RCC_CIER.

11.4.9 System clock (SYSCLK) selection

Four different clock sources can be used to drive the system clock (SYSCLK):

- • MSIS oscillator

- • HSI16 oscillator

- • HSE oscillator

- • PLL

The system clock maximum frequency is 160 MHz. After a system reset, the MSIS oscillator, at 4 MHz, is selected as system clock. When a clock source is used directly or through the PLL as a system clock, it is not possible to stop it.

A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay or PLL locked). If a clock source that is not yet ready is selected, the switch occurs when the clock source becomes ready. Status bits in RCC_CR indicate which clocks are ready and which clock is currently used as a system clock.

The table below gives the different bus frequencies depending on the product voltage range.

Table 114. Bus maximum frequency

| Product voltage range | AHB1/AHB2/AHB3/APB1/APB2/APB3 |

|---|---|

| Range 1 | 160 MHz |

| Range 2 | 110 MHz |

| Range 3 | 55 MHz |

| Range 4 | 25 MHz |

11.4.10 Clock source frequency versus voltage scaling

The table below gives the different clock source frequencies depending on the product voltage range.

Table 115. Clock source maximum frequency

| Voltage range | Clock frequency | |||||

|---|---|---|---|---|---|---|

| MSIS, MSIK | HSI16 | HSI48 | SHS1 | HSE | PLL outputs (VCO min to max) | |

| Range 1 | All ranges | Allowed | Allowed | Allowed | 50 MHz | 208 MHz (1) (128 to 544 MHz) |

| Range 2 | All ranges | Allowed | Allowed | Allowed | 50 MHz | 110 MHz (128 to 544 MHz) |

| Range 3 | All ranges | Allowed | Allowed | Allowed | 50 MHz | 55 MHz (128 to 330 MHz) |

| Range 4 | Up to 24 MHz range | Allowed | Allowed (divided by 2) | Allowed (divided by 2) | 25 MHz | Not allowed |

- 1. The maximum frequency depends on peripherals connected to PLL outputs.

11.4.11 Clock security system (CSS)

The CSS can be activated by software. In this case, the clock detector is enabled after the HSE oscillator wake-up time, and disabled when this oscillator is stopped.

If a failure is detected on the HSE clock, the HSE oscillator is automatically disabled. A clock failure event is sent to some timers break input and an interrupt is generated to inform the software about the failure (clock security system interrupt CSSI). This allows the MCU to perform rescue operations. The CSSI is linked to the Cortex-M33 NMI (nonmaskable interrupt) exception vector.

Note: Once the CSS is enabled and if the HSE clock fails, the CSSI occurs and an NMI is automatically generated. The NMI is executed indefinitely unless CSSI bit is cleared. As a consequence, in the NMI ISR, the user must clear the CSSI by setting CSSC in RCC_CICR.

If the HSE oscillator is used directly or indirectly as the system clock (indirectly means: it is used as PLL input clock and the PLL clock is used as system clock), a detected failure causes a switch of the system clock to the MSIS or the HSI16 oscillator depending on STOPWUCK configuration in RCC_CR, and the disabling of the HSE oscillator. If the HSE clock (divided or not) is the clock entry of the PLL used as system clock when the failure occurs, the PLL is disabled too.

11.4.12 Clock security system on LSE

A clock security system on LSE can be activated by software writing LSECSSON in RCC_BDCR. This bit can be disabled only by a hardware reset or RTC software reset, or after a failure detection on LSE. LSECSSON must be written after LSE is enabled (LSEON enabled) and ready (LSERDY set by hardware), and after the RTC clock has been selected by RTCSEL.

The CSS on LSE works in all modes, including V BAT mode. It works also under system reset (excluding power-on reset).

The CSS on LSE detects when the LSE disappears or in case of over frequency. In addition, the glitches on LSE can be filtered by setting LSEGFON. LSEGFON must be written when the LSE is disabled (LSEON = 0 and LSERDY = 0).

If a failure is detected on the external 32 kHz oscillator, the LSE clock is no longer supplied to the RTC, but no hardware action is made to the registers. If the MSI was in PLL-mode, this mode is disabled.

The CSS on LSE detection event is connected to the internal tamper 3 of the TAMP:

- • On STM32U575/585 rev. X devices, the internal tamper 3 must be enabled (ITAMP3E = 1 in TAMP_CR1) and the associated interrupt enabled (ITAMP3IE in TAMP_IER) in order to wake up from the low-power modes. This erases also the TAMP backup registers and backup SRAM unless ITAMP3NOER = 1 in TAMP_CR3 (see Section 64: Tamper and backup registers (TAMP) for more details).

- • On all other STM32U575/585 revisions, and the other STM32U5 devices, the CSS on LSE detection event is also connected to an EXTI line, allowing to generate an event or interrupt supporting wake-up from Stop 0, Stop 1, or Stop 2 mode, without requiring to enable tamper detection (see Table 118: Interrupt sources and control and Table 189: EXTI line connections ).

In case of CSS on LSE detection event (LSECSSD = 1 in RCC_BDCR), the software must then disable the LSECSSON bit, stop the defective 32 kHz oscillator (disabling LSEON), and change the RTC clock source (no clock or LSI or HSE, with RTCSEL), or take any required action to secure the application.

Refer to datasheet for CSS on LSE electrical characteristics.

11.4.13 ADC and DAC clocks

The ADC and DAC kernel clock source is selected thanks to ADCDACSEL[2:0] in RCC_CCIPR3. The ADC clock ratio must be around 50 %. For this reason, the AHB clock, when selected as ADC clock, must not be divided with HPRE prescaler. If pll2_r_ck is selected as ADC clock, the PLL2R division factor must be even (division by 2 or 4 for example).

If the application requires that the ADC or DAC is precisely triggered by a TIMx timer without any uncertainty, the HCLK must be selected as ADC and DAC kernel clock source.

The other clock sources are asynchronous to TIMx timers therefore an uncertainty of the trigger instant is added by the resynchronization between the two clock domains. LPTIMx timers are also asynchronous.

The DAC requires an additional low-power clock (LSI or LSE) to operate in sample and hold mode, available in Stop mode. This clock is selected with DAC1SEL in the RCC_CCIPR3.

11.4.14 RTC and TAMP clock

The RTCCLK clock source is used by RTC and TAMP, and can be either the HSE / 32, LSE, or LSI clock. It is selected by programming RTCSEL[1:0] in RCC_BDCR. This selection cannot be modified without resetting the backup domain. The system must always be configured so as to get a PCLK frequency greater than or equal to the RTCCLK frequency for a proper operation of the RTC. The TAMP does not require any kernel clock if only backup registers are used, with tamper in edge detection mode. All other tamper detection modes require a kernel clock (refer to Section 64: Tamper and backup registers (TAMP) for more details).

LSE and LSI clocks are in the backup domain, whereas the HSE clock is not. Consequently:

- • If LSE or LSI is selected as RTC and TAMP clock, these peripherals continue to work even if the \( V_{DD} \) supply is switched off, provided the \( V_{BAT} \) supply is maintained.

- • If the HSE clock divided by a prescaler is used as the RTC or TAMP clock, the RTC state is not guaranteed if the \( V_{DD} \) supply is powered off, or if the internal voltage regulator is powered off (removing power from the core domain). Depending on the TAMP configuration, this one can remain functional if used in a mode that does not need any kernel clock.

When the RTC and TAMP clock is LSE or LSI, the RTC remains clocked and functional under system reset.

If the LSE is needed only for the RTC or TAMP, LSESYSEN must be kept at reset value to get the lowest consumption.

11.4.15 Timer clock

The timer clock frequencies are automatically defined by hardware.

There are two cases:

- • If the APB prescaler equals 1, the timer clock frequencies are set to the APB domain frequency.

- • Otherwise, they are set to twice ( \( \times 2 \) ) the APB domain frequency.

11.4.16 Watchdog clock

If the independent watchdog (IWDG) is started by either hardware option or software access, the LSI oscillator is forced on and cannot be disabled. After the LSI oscillator temporization, the LSI 32 kHz clock is provided to the IWDG.

11.4.17 OCTOSPI clock

The OCTOSPIx kernel clock, selected by OCTOSPIxSEL[1:0], can be up to 200 MHz when pll1_q_ck or pll2_q_ck are used.

11.4.18 HSPI1 clock

The HSPI1 kernel clock, selected by HSPI1SEL[1:0], can be up to 200 MHz when pll1_q_ck, pll2_q_ck or pll3_r_ck are used.

11.4.19 OTG_HS clock

The OTG_HS kernel clock is generated by the OTG_HS PHY. This PHY can accept only frequencies of following list (16, 19.2, 20, 24, 26 or 32 MHz), with an accuracy of \( \pm 400 \) ppm. Those frequencies can be achieved using either HSE, HSE/2, PLL1_P or PLL1_P/2, and selected by the OTGHSSSEL[1:0] multiplexer. Refer to the OTGHSSSEL description concerning some limitations that apply when using the PLL as its input.

11.4.20 DSI clock

The DSI interface clock can be derived from the internal DSI PHY PLL or by the pll3_p_ck clocks, selected by DSISEL multiplexer.

11.4.21 LTDC clock

The LTDC interface clock can be derived from the pll2_r_ck or pll3_r_ck clocks, selected by LTDCSEL multiplexer.

11.4.22 Clock-out capability

- • MCO

The microcontroller clock output (MCO) capability allows the clock to be output onto the external MCO pin. One of the following clock signals can be selected as MCO clock.

- – LSI

- – LSE

- – SYSCLK

- – HSI16

- – HSI48

- – HSE

- – PLLCLK

- – MSIS

- – MSIK

This output remains available in Stop0, Stop1 and Stop2. In Stop modes, selection of available clock signals may be limited.

The selection is controlled by MCOSEL[3:0] in RCC_CR. The selected clock can be divided with MCOPRE[2:0] in RCC_CR.

- • LSCO

Another output (LSCO) allows one of the low-speed clocks below to be output onto the external LSCO pin:

- – LSI

- – LSE

This output remains available in all Stop modes, Standby, and Shutdown modes.

This output is not available in \( V_{BAT} \) mode. The selection is controlled by LSCOSEL bit and enabled with LSCOEN in RCC_BDCR.

The MCO clock output requires the corresponding alternate function selected on MCO pin.

11.4.23 Internal/external clock measurement with TIM15/TIM16/TIM17/LPTIM1/LPTIM2

The frequency of all on-board clock sources can be indirectly measured by means of the TIM15, TIM16, or TIM17 channel 1 input capture, and LPTIM1 or LPTIM2 channel 2 input capture.

HSI16 and MSI calibration using LSE

The primary purpose of connecting the LSE to the channel 1 input capture of TIM15, TIM16, and TIM17, and to the channel 2 input capture of LPTIM1, is to be able to precisely measure the HSI16 and MSI system clocks (for this, either HSI16 or MSIS must be used as system clock source). The number of HSI16 (MSIS respectively) clock counts between consecutive edges of the LSE signal provides a measure of the internal clock period. Taking advantage of the high precision of LSE crystals (typically a few tens of ppms), the internal clock frequency can be determined with the same resolution, and the source can be trimmed to compensate the manufacturing, process, temperature and/or voltage related frequency deviations.

The four oscillators of MSI and HSI16 oscillator have dedicated user-accessible calibration bits for this purpose.

The basic concept consists in providing a relative measurement (such as HSI16/LSE ratio). The precision is therefore closely related to the ratio between the two clock sources. The higher the ratio is, the better the measurement is.

Note: When the LSE is available, the MSI can be automatically trimmed by LSE using PLL-mode.

HSI16 and MSI calibration using HSE

If the HSE is available, it can be used as system clock, and the timer input capture must be connected either to MSI (divided by 1024 or by 4) or to HSI/256. TIM16 and TIM17 channel 1 input capture, as well and the LPTIM2 input capture 2, are connected to the divided oscillator only when TIMICSEL[2:0] \( \neq \) 0 in RCC_CCIPR1.

Considering that the timer counter is 16-bit, and that the ratio between HSE and the input capture signal must be the highest possible, a division by 1024 must be selected when MSIRC0, MSIRC1, or MSIRC2 is measured, and a division by 4 when MSIRC4 is measured.

LSI calibration

The calibration of the LSI follows the same principle, but changing the reference clock. The LSI clock must be connected to the channel 1 input capture of the TIM16 or TIM17, or to the channel 2 input capture of the LPTIM1. Then defining the HSE as system clock source, the number of its clock counts between consecutive edges of the LSI signal, provides a measure of the internal low-speed clock period.

The basic concept consists in providing a relative measurement (such as HSE/LSI ratio). The precision is therefore closely related to the ratio between the two clock sources. The higher the ratio is, the better the measurement is.

11.4.24 Peripherals clock gating and autonomous mode

Peripherals clock gating in Run mode

Each peripheral clock can be enabled by the corresponding EN bit in RCC_AHBxENR and RCC_APBxENR registers.

When the peripheral clock is not active, read or write accesses to the peripheral registers are not supported.

The enable bit has a synchronization mechanism to create a glitch-free clock for the peripheral. After the enable bit is set, there the clock is active after 2 cycles of the peripheral bus clock.

Caution: Just after enabling the clock for a peripheral, the software must wait for these two clock cycles before accessing the peripheral registers.

Peripherals clock gating in Sleep and Stop modes

When a peripheral is enabled, its clock can be automatically gated off when the device is in Sleep mode, by clearing the peripheral SMEN bit in RCC_AHBxSMENR and RCC_APBxSMENR. Both EN and SMEN of the peripheral must be set to keep the clock on in Sleep mode.

The SMEN bit of the peripheral is also used to allow peripheral clocking in Stop 0 and Stop 1 modes, upon peripheral request.

When the clock is requested by a peripheral, this clock is distributed to all enabled peripherals. Therefore, the SMEN bit must be cleared before entering Stop mode, if the peripheral is not used in Stop mode.

Caution: The SMEN bit of the peripheral must be set to allow the generation of an interrupt capable to wake up the device from Stop mode. This is not necessary when the peripheral wake-up interrupt is generated through the EXTI.

Peripherals clock gating and autonomous mode in Stop 0/1/2 modes

Some peripherals support autonomous mode (refer to Table 116 ). These peripherals are able to generate a kernel clock request and a AHB/APB bus clock request when they need, in order to operate and update their status register even in Stop mode. Depending on the peripheral configuration, either a DMA request or an interrupt can be associated to the peripheral event.

Upon an AHB or APB bus clock request from an autonomous peripheral, either MSI or HSI16 oscillator is woken up, depending on the oscillator selected by STOPWUCK in RCC_CFGR1.

If the autonomous peripheral is configured with DMA requests enabled, a data transfer is performed thanks to the AHB/APB clock. The bus clocks as well as the oscillator (HSI16 or MSI) are automatically switched off as soon as the transfer is finished, if no other peripheral requests it. The device automatically goes back in Stop mode.

If the autonomous peripheral is configured with interrupt enabled, the interrupt wakes up the device into Run mode.

The autonomous peripherals mapped on AHB3 or APB3 belong to the SmartRun domain and are autonomous in Stop 0, Stop 1, and Stop 2 with the LPDMA1 and SRAM4.

The autonomous peripherals mapped on AHB1, AHB2, APB1, and APB2, belong to the CPU domain, and are autonomous in Stop 0 and Stop 1 mode, only with GPDMA1 and SRAM1/2/3/4/5/6.

The table below shows the list of peripherals with autonomous mode capability.

Table 116. Autonomous peripherals

| Domain | Peripheral | Autonomous in Stop 0, 1 modes | Autonomous in Stop 2 mode | Associated DMA | Associated SRAM |

|---|---|---|---|---|---|

| CPU domain (CD) | U(S)ARTx (x = 1 to 6) | Yes (1) | No | GPDMA1 | SRAM1 SRAM2 SRAM3 SRAM4 (2) SRAM5 SRAM6 |

| SPIx (x = 1,2) | |||||

| I2Cx (x = 1,2,4,5,6) | |||||

| LPTIM2 | |||||

| MDF1 | |||||

| GPDMA1 | - | ||||

| SmartRun domain (SRD) | LPUART1 | Yes (3) | Yes (3) | LPDMA1 | SRAM4 |

| SPI3 | |||||

| I2C3 | |||||

| LPTIMx (x = 1,3,4) | |||||

| ADF1 | |||||

| DAC1 | |||||

| ADC4 | |||||

| LPDMA1 | - |

1. Enabled if both xxEN and xxSMEN bits of the peripheral are set (xx = instance name)

2. SRAM4 belongs to SmartRun domain (SRD) but can be addressed by GPDMA 1 in Stop 0 and Stop 1 modes.

3. Enabled if all xxEN, xxSMEN, and xxAMEN bits of the peripheral are set (xx = instance name)

For peripherals in the CPU domain, the autonomous mode is enabled in Stop 0 and Stop 1 modes if both xxEN and xxSMEN bits of the peripheral are set.

For peripherals in SmartRun domain, the autonomous mode is enabled in Stop 0, Stop 1, and Stop 2 modes if both xxEN and xxSMEN bits of the peripheral are set, plus xxAMEN bit of the peripheral in RCC_SRDRAMR.

If an autonomous peripheral requests its kernel clock in Stop 0, Stop 1, or Stop 2 mode, the internal oscillator (HSI16 or MSI) is woken up if it was off, and the kernel clock is propagated only to the peripheral requesting it. When the peripheral releases its kernel clock request, the HSI16 or MSI is switched off if no other peripheral requests it.

If an autonomous peripheral belonging to CPU domain requests its bus clock (AHB1, AHB2, APB1, or APB2 clock) in Stop 0 or Stop 1 mode, the internal oscillator (HSI16 or MSI depending on STOPWUCK value in RCC_CFGR1) is woken up if it was off, and the system clock is propagated to all peripherals configured with both xxEN = xxSMEN = 1.

If an autonomous peripheral belonging to SmartRun domain requests its bus clock (AHB3 or APB3 clock) in Stop 0, Stop 1, or Stop 2 mode, the internal oscillator (HSI16 or MSI depending on STOPWUCK value in RCC_CFGR1) is woken up if it was off, and

HCLK3/PCLK3 clocks are propagated to all peripherals of the SmartRun domain configured with xxEN = xxSMEN = xxAMEN = 1.

Caution: The AMEN bit of the peripheral must be set to allow the generation of an interrupt capable to wake up the device from Stop mode. This is not necessary when the peripheral wake-up interrupt is generated through the EXTI.

Note: MSI or HSI16 can be forced to remain on in Stop 0, Stop 1, or Stop 2 mode, by configuring MSIKERON or HSIKERON in RCC_CR. In this case, the oscillator is propagated only to the kernel clock of the enabled autonomous peripherals with this oscillator selected as kernel clock. This allows the peripheral baudrate or conversion rate increase, as there is no need to wait for the oscillator wake-up time when the peripheral requests its kernel clock.

The LSE or LSI selected as peripheral kernel clock remains always on in Stop modes.

AHB3 and APB3 clocks can be forced to remain on by setting SRDRUN in PWR_CR2. This allows the LPDMA1 latency to be improved as there is no need to wait for the oscillator wake-up time when the peripheral requests its bus clock.

11.5 RCC security and privilege functional description

11.5.1 RCC TrustZone security protection modes

When the TrustZone security is activated by TZEN option bit in FLASH_OPTR, the RCC is able to secure RCC configuration and status bits from being modified by nonsecure accesses.

This is configured through RCC_SECCFGR to prevent nonsecure access to read or modify the following features:

- • HSE, HSE-CSS, HSI, MSI, LSI, LSE, LSE-CSS, LSCO, HSI48 configuration and status bits

- • PLL1, PLL2, PLL3, AHB, and APB prescaler configuration and status bits

- • system clock (SYSCLK) and ICLK source clock selection and status bits

- • MCO clock output configuration, and STOPWUCK and STOPKERWUCK bit

- • Remove reset flag RMVF configuration

If SPRIV = 1 in RCC_PRIVCFGR, the RCC_SECCFGR register can be written only by secure and privileged access. If SPRIV = 0 in RCC_PRIVCFGR, RCC_SECCFGR can be written only by secure access, privileged or unprivileged.

RCC_SECCFGR can be read by secure, nonsecure, privileged and unprivileged access.

When a peripheral is configured as secure, its related clock, reset, clock source selection and clock enable during low-power modes control bits, are also secure in RCC_AHBxENR, RCC_APBxENR, RCC_AHBxSMEN, RCC_APBxSMEN, RCC_SRDAMEN, RCC_CCIPR1, RCC_CCIPR2, RCC_CCIPR3, and RCC_BDCR registers.

The SHSI configuration and status bits are secured when the SAES is configured as secure.

BDRST in RCC_BDCR is secure when at least one function is secure in RTC or TAMP.

A peripheral is secure when:

- • For securable peripherals by TZSC (TrustZone security controller), the SEC security bit corresponding to this peripheral is set in GTZC TZSC secure configuration registers.

- • For TrustZone-aware peripherals, a security feature of this peripheral is enabled through its dedicated bits.

Table 117 summarizes the RCC secured bits following the security configuration bit in RCC_SECCFGR register.

When one security configuration bit is set, some configuration and status bits are secured. The RCC registers may contain secure and nonsecure bits:

- • Secured bits: read and write operations are only allowed by a secure access. Nonsecure read returns 0 and write accesses are ignored. No illegal access event is generated.

- • Nonsecure bits: no restriction. Read and write operations are allowed by both secure and nonsecure accesses.

- • A nonsecure write access to RCC_SECCFGR is ignored and generates an illegal access event. An illegal access interrupt is generated if the RCC illegal access interrupt is enabled in the GTZC TZIC registers. RCC_SECCFGR can be read by secure or nonsecure access.

When the TrustZone security is disabled (TZEN = 0 in FLASH_OPTR), all registers are nonsecure. RCC_SECCFGR write accesses are ignored.

Table 117. RCC security configuration summary

| Configuration bit in RCC_SECCFGR | Secured bits | Corresponding register |

|---|---|---|

| HSISEC | HSION, HSIKERON, HSIRDY | RCC_CR |

| HSICAL[7:0], HSITRIM[6:0] | RCC_ICSCR3 | |

| HSIRDYIE | RCC_CIER | |

| HSIRDYIF | RCC_CIFR | |

| HSIRDYC | RCC_CICR | |

| HSESEC | HSEON, HSERDY, HSEBYP, CSSON, HSEEXT | RCC_CR |

| HSERDYIE | RCC_CIER | |

| HSERDYIF, CSSF | RCC_CIFR | |

| HSERDYC, CSSC | RCC_CICR | |

| MSISEC | MSISON, MSIKERON, MSISRDY, MSIPLLEN, MSIKON, MSIKRDY, MSIPLLSEL, MSIPLLFAST | RCC_CR |

| MISIRANGE[3:0], MISIKRANGE[3:0], MSIRGSEL, MSIBIAS, MSICAL0[4:0], MSICAL1[4:0], MSICAL2[4:0], MSICAL3[4:0] | RCC_ICSCR1 | |

| MSITRIM0[4:0], MSITRIM1[4:0], MSITRIM2[4:0], MSITRIM3[4:0] | RCC_ICSCR2 | |

| MSISRDYIE, MSIKRDYIE | RCC_CIER | |

| MSISRDYIF, MSIKRDYIF | RCC_CIFR | |

| MSISRDYIC, MSIKRDYIC | RCC_CICR | |

| MSISSRANGE[3:0], MSIKSRANGE[3:0] | RCC_CSR |

Table 117. RCC security configuration summary (continued)

| Configuration bit in RCC_SECCFGR | Secured bits | Corresponding register |

|---|---|---|

| LSISEC | LSION, LSIRDY, LSIPREDIV, LSCOSEL, LSCOEN | RCC_BDCR |

| LSIRDYIE | RCC_CIER | |

| LSIRDYIF | RCC_CIFR | |

| LSIRDYC | RCC_CICR | |

| LSESEC | LSECSSON, LSECSSD, LSEDRV[1:0], LSEBYP, LSERDY, LSEON, LSEGON, LSESYSRDY, LSESYSEN, LSCOSEL, LSCOEN | RCC_BDCR |

| LSERDYIE | RCC_CIER | |

| LSERDYF | RCC_CIFR | |

| LSERDYC | RCC_CICR | |

| SYSCLKSEC | SW[1:0], SWS[1:0], STOPWUCK, STOPKERWUCK, MCOSEL[3:0], MCOPRE[2:0] | RCC_CFGR1 |

| SYSTICKSEL[1:0] | RCC_CCIPR1 | |

| VOS[1:0] | PWR_VOSR | |

| PRESCSEC | HPRE[3:0], PPRE1[2:0], PPRE2[2:0] | RCC_CFGR2 |

| PPRE3[2:0] | RCC_CFGR3 | |

| PLL1SEC | PLL1SRC[1:0], PLL1RGE[1:0], PLL1FRACEN, PLL1M[3:0], PLL1MBOOST[3:0], PLL1PEN, PLL1QEN, PLL1REN | RCC_PLL1CFGR |

| PLL1N[8:0], PLL1P[6:0], PLL1Q[6:0], PLL1R[6:0] | RCC_PLL1DIVR | |

| PLL1FRACN[12:0] | RCC_PLL1FRACR | |

| PLL1RDY, PLL1ON | RCC_CR | |

| PLL1RDYIE | RCC_CIER | |

| PLL1RDYF | RCC_CIFR | |

| PLL1RDYC | RCC_CICR | |

| PLL2SEC | PLL2SRC[1:0], PLL2RGE[1:0], PLL2FRACEN, PLL2M[3:0], PLL2PEN, PLL2QEN, PLL2REN | RCC_PLL2CFGR |

| PLL2N[8:0], PLL2P[6:0], PLL2Q[6:0], PLL2R[6:0] | RCC_PLL2DIVR | |

| PLL2FRACN[12:0] | RCC_PLL2FRACR | |

| PLL2RDY, PLL2ON | RCC_CR | |

| PLL2RDYIE | RCC_CIER | |

| PLL2RDYF | RCC_CIFR | |

| PLL2RDYC | RCC_CICR |

Table 117. RCC security configuration summary (continued)

| Configuration bit in RCC_SECCFGR | Secured bits | Corresponding register |

|---|---|---|

| PLL3SEC | PLL3SRC[1:0], PLL3RGE[1:0], PLL3FRACEN, PLL3M[3:0], PLL3PEN, PLL3QEN, PLL3REN | RCC_PLL3CFGR |

| PLL3N[8:0], PLL3P[6:0], PLL3Q[6:0], PLL3R[6:0] | RCC_PLL3DIVR | |

| PLL3FRACN[12:0] | RCC_PLL3FRACR | |

| PLL3RDY, PLL3ON | RCC_CR | |

| PLL3RDYIE | RCC_CIER | |

| PLL3RDYF | RCC_CIFR | |

| PLL3RDYC | RCC_CICR | |

| HSI48SEC (1) | HSI48ON, HSI48RDY | RCC_CR |

| HSI48CAL[8:0] | RCC_CRRCR | |

| HSI48RDYE | RCC_CIER | |

| HSI48RDYF | RCC_CIFR | |

| HSI48RDYC | RCC_CICR | |

| ICLKSEL | ICLKSEL[1:0] | RCC_CCIPR1 |

| RMVFSEC | RMVF | RCC_CSR |

1. TRIM field of the HSI48 is located in CRS peripheral. Be sure to secure it using CRSSEC bit in GTZC1 TZSC secure configuration register 1.

11.5.2 RCC privilege protection modes

By default, after reset, all RCC registers can be read or written with both privileged and unprivileged access, except RCC_PRIVCFGR that can be written with privileged access only. RCC_PRIVCFGR can be read by secure and nonsecure, privileged and unprivileged access.

SPRIV in RCC_PRIVCFGR can be written with secure privileged access only. This bit configures the privileged access of all RCC secure functions (as defined by RCC_SECCFGR), or by the GTZC for securable peripherals, or by the peripheral itself in case of TrustZone-aware peripherals).

When SPRIV = 1 in RCC_PRIVCFGR:

- • Writing the RCC secure bits is possible only with privileged access, including RCC_SECCFGR.

- • The RCC secure bits can be read only with privileged access, except RCC_SECCFGR and RCC_PRIVCFGR that can be read by privileged or unprivileged access.

- • An unprivileged access to a privileged RCC bit or register is discarded: the bits are read as zero and the write to these bits is ignored (RAZ/WI).

NSPRIV in RCC_PRIVCFGR can be written with privileged access only, secure or nonsecure functions (as defined by RCC_SECCFGR, or by the GTZC for securable peripherals, or by the peripheral itself in case of TrustZone-aware peripherals).

When NSPRIV = 1 in RCC_PRIVCFGGR:

- • Writing the RCC nonsecure bits is possible only with privileged access.

- • The RCC nonsecure bits can be read only with privileged access except RCC_PRIVCFGGR that can be read by privileged or unprivileged access.

- • An unprivileged access to a privileged RCC bit or register is discarded: the bits are read as zero and the write to these bits is ignored (RAZ/WI).

11.6 RCC low-power modes

- • AHB and APB peripheral clocks, including DMA clock, can be disabled by software.

- • Sleep mode stops the CPU clock. The memory interface clocks (flash memory, caches, and all SRAM interfaces) can be stopped by software during Sleep mode. The AHB to APB bridge clocks are disabled by hardware during Sleep mode when all the clocks of the peripherals connected to them are disabled.

- • Stop modes (Stop 0, Stop 1, Stop 2, Stop 3) stop all the clocks in the core domain and disable the PLLs, HSI16, HSI48, SHSI, MSI, and HSE oscillators. However, HSI16 or MSI can be switched ON if the peripheral requests it for autonomous mode purpose, or to generate a wake-up interrupt (see Section 11.4.24 for more details). LSI and LSE remain active in Stop modes.

- • Standby and Shutdown modes stop all the clocks in the core domain and disable the PLLs, HSI16, HSI48, SHSI, MSI, and HSE oscillators.

The CPU deep-sleep mode can be overridden for debugging by setting the DBG_STOP or DBG_STANDBY bit in the DBGMCU_CR register.

When exiting Stop modes (Stop 0, Stop 1, Stop 2, or Stop 3), the system clock is either MSIS or HSI16, depending on STOPWUCK in RCC_CFGR1. The frequency (range and user trim) of MSIS and MSIK oscillators is the one configured before entering Stop mode, except if above 24 MHz. In this case, the MSIS or MSIK range is the 24 MHz range. The user trim of HSI16 is kept. If MSI is in PLL-mode before entering Stop mode with MSIPLLFAST = 0, the PLL-mode stabilization time must be waited for after wake-up even if the LSE was kept on during Stop mode. The PLL-mode accuracy is kept after wake-up from Stop 0, Stop 1, or Stop 2 mode without stabilization time if MSIPLLFAST = 1. MSIPLLFAST bit has no effect when exiting Stop 3 mode.

The other internal oscillator can be automatically woken up in addition to the one used by the system clock, in order to avoid waiting for the other oscillator wake-up time when the device is back in Run mode. This is done thanks to STOPKERWUCK in RCC_CFGR1.

When leaving the Standby and Shutdown modes, the system clock is MSIS. The MSIS and MSIK frequency at wake-up from Standby mode is configured with MSISSRANGE and MSIKSRANGE in RCC_CSR, from 1 to 4 MHz. The MSI frequency at wake-up from Shutdown mode is 4 MHz. The user trim is lost.

If a flash memory programming operation is ongoing, a Stop, Standby, or Shutdown mode entry is delayed until the flash memory interface access is finished. If an access to the APB domain is ongoing, a Stop, Standby, or Shutdown mode entry is delayed until the APB access is finished. If an autonomous peripheral generates a system clock request, a Stop, Standby, or Shutdown mode entry is delayed until the system clock request is released.

11.7 RCC interrupts

The table below summarizes the interrupt sources and the way to control them.

Table 118. Interrupt sources and control

| Interrupt vector | Interrupt event flag | Description | Enable control bit | Interrupt clear method | Exit Sleep mode | Exit Stop, Standby, Shutdown modes |

|---|---|---|---|---|---|---|

| RCC | LSIRDYF | LSI ready | LSIRDYIE and LSISEC = 0 | Set LSIRDYC to 1 | Yes | No |

| LSERDYF | LSE ready | LSERDYIE and LSESEC = 0 | Set LSERDYC to 1 | Yes | No | |

| HSIDRYF | HSI ready | HSIDRYIE and HSISEC = 0 | Set HSIRDYC to 1 | Yes | No | |

| HSERDYF | HSE ready | HSERDYIE and HSESEC = 0 | Set HSERDYC to 1 | Yes | No | |

| MSISRDYF | MSIS ready | MSISRDYIE and MSISEC = 0 | Set MSISRDYC to 1 | Yes | No | |

| MSIKRDYF | MSIK ready | MSIKRDYIE and MSISEC = 0 | Set MSIKRDYC to 1 | Yes | No | |

| SHSIRDYF | SHSI ready | SHSIRDYIE and SAESSEC = 0 (in GTZC) | Set SHSIRDYC to 1 | Yes | No | |

| HSI48RDYF | HSI48 ready | HSI48RDYIE and HSI48SEC = 0 | Set HSI48RDYC to 1 | Yes | No | |

| PLL1RDYF | PLL1 ready | PLL1RDYIE and PLL1SEC = 0 | Set PLL1RDYC to 1 | Yes | No | |

| PLL2RDYF | PLL2 ready | PLL2RDYIE and PLL2SEC = 0 | Set PLL2RDYC to 1 | Yes | No | |

| PLL3RDYF | PLL3 ready | PLL3RDYIE and PLL3SEC = 0 | Set PLL3DYC to 1 | Yes | No | |

| RCC_S (1) | LSIRDYF | LSI ready | LSIRDYIE and LSISEC = 1 | Set LSIRDYC to 1 | Yes | No |

| LSERDYF | LSE ready | LSERDYIE and LSESEC = 1 | Set LSERDYC to 1 | Yes | No | |

| HSIDRYF | HSI ready | HSIDRYIE and HSISEC = 1 | Set HSIRDYC to 1 | Yes | No | |

| HSERDYF | HSE ready | HSERDYIE and HSESEC = 1 | Set HSERDYC to 1 | Yes | No | |

| MSISRDYF | MSIS ready | MSISRDYIE and MSISEC = 1 | Set MSISRDYC to 1 | Yes | No | |

| MSIKRDYF | MSIK ready | MSIKRDYIE and MSISEC = 1 | Set MSIKRDYC to 1 | Yes | No |

Table 118. Interrupt sources and control (continued)

| Interrupt vector | Interrupt event flag | Description | Enable control bit | Interrupt clear method | Exit Sleep mode | Exit Stop, Standby, Shutdown modes |

|---|---|---|---|---|---|---|

| RCC_S (1) | SHSIRDYF | SHSI ready | SHSIRDYIE and SAESSEC (2) = 1 | Set SHSIRDYC to 1 | Yes | No |

| HSI48RDYF | HSI48 ready | HSI48RDYIE and HSI48SEC = 1 | Set HSI48RDYC to 1 | Yes | No | |

| PLL1RDYF | PLL1 ready | PLL1RDYIE and PLL1SEC = 1 | Set PLL1RDYC to 1 | Yes | No | |

| PLL2RDYF | PLL2 ready | PLL2RDYIE and PLL2SEC = 1 | Set PLL2RDYC to 1 | Yes | No | |

| PLL3RDYF | PLL3 ready | PLL3RDYIE and PLL3SEC = 1 | Set PLL3RDYC to 1 | Yes | No | |

| TAMP | ITAMP3F (3) | LSE CSS failure | LSECSSON and ITAMP3E (3) and ITAMP3IE (3) | Set CITAMP3F (3) to 1 | Yes | Yes |

| NMI | CSSF | HSE CSS failure | _(4) | Set CSSC to 1 | Yes | No |

| LSECSS (5) | Through EXTI | LSE CSS failure | Through EXTI | Through EXTI | Yes | Yes (6) /No |

| MSI_PLL_UNLOCK (5) | Through EXTI | MSI PLL-mode unlock (7) | Through EXTI | Through EXTI | Yes | Yes (6) /No |

1. The RCC secure interrupt vector is used only when TrustZone is enabled.

2. The SAESSEC bit is in the GTZC peripheral.

3. The LSE CSS failure event (LSECSSD) is connected to TAMP internal tamper 3. In order to get the interrupt associated to this event, the internal tamper 3 must be enabled, and the internal tamper 3 interrupt must be enabled. The ITAMP3F, ITAMP3E, ITAMP3IE, and CITAMP3F bits are in the TAMP peripheral. Consequently, the LSE CSS tamper interrupt erases or blocks the device secrets as described in Table 644: TAMP interconnection .

4. It is not possible to mask this interrupt when the security system feature is enabled (CSSON = 1).

5. Not available in STM32U575/585 rev. X devices. Available in all other STM32U575/585 revisions, and in the other STM32U5 Series devices.

6. This interrupt can wake up from Stop 0, Stop 1, and Stop 2 modes only.

7. This interrupt indicates that the MSI has left the PLL_mode, due to LSE missing pulses. As a consequence, the MSI frequency accuracy is degraded.

11.8 RCC registers

11.8.1 RCC clock control register (RCC_CR)

Address offset: 0x000

Reset value: 0x0000 0035

Access: no wait state; word, half-word, and byte access

HSEBYP and HSEEXT are cleared upon power-on reset. They are not affected upon other types of reset.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | PLL3R DY | PLL3O N | PLL2R DY | PLL2O N | PLL1R DY | PLL1O N | Res. | Res. | Res. | HSEEXT | CSSO N | HSEBY P | HSE RD Y | HSE O N |

| r | rw | r | rw | r | rw | rw | rs | rw | r | rw | |||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SHSIR DY | SHSIO N | HSI48R DY | HSI48 ON | Res. | HSIRD Y | HSIKE RON | HSION | MSIPL LFAST | MSIPL LSEL | MSIKR DY | MSIKO N | MSIPL LEN | MSISR DY | MSIKE RON | MSISO N |

| r | rw | r | rw | r | rw | rw | rw | rw | r | rw | rw | r | rw | rw |

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 PLL3RDY : PLL3 clock ready flag

This bit is set by hardware to indicate that the PLL3 is locked.

0: PLL3 unlocked

1: PLL3 locked

Bit 28 PLL3ON : PLL3 enable

This bit is set and cleared by software to enable PLL3. It is cleared by hardware when entering Stop, Standby, or Shutdown mode.

0: PLL3 OFF

1: PLL3 ON

Bit 27 PLL2RDY : PLL2 clock ready flag

This bit is set by hardware to indicate that the PLL2 is locked.

0: PLL2 unlocked

1: PLL2 locked

Bit 26 PLL2ON : PLL2 enable

This bit is set and cleared by software to enable PLL2. It is cleared by hardware when entering Stop, Standby, or Shutdown mode.

0: PLL2 OFF

1: PLL2 ON

Bit 25 PLL1RDY : PLL1 clock ready flag

This bit is set by hardware to indicate that the PLL1 is locked.

0: PLL1 unlocked

1: PLL1 locked

Bit 24 PLL1ON: PLL1 enableThis bit is set and cleared by software to enable the main PLL. It is cleared by hardware when entering Stop, Standby, or Shutdown mode. This bit cannot be reset if the PLL1 clock is used as the system clock.

0: PLL1 OFF

1: PLL1 ON

Bits 23:21 Reserved, must be kept at reset value.

Bit 20 HSEEXT: HSE external clock bypass modeThis bit is set and reset by software to select the external clock mode in bypass mode.

External clock mode must be configured with HSEON bit to be used by the device. This bit can be written only if the HSE oscillator is disabled. This bit is active only if the HSE bypass mode is enabled.

0: external HSE clock analog mode

1: external HSE clock digital mode (through I/O Schmitt trigger)

Bit 19 CSSON: Clock security system enableThis bit is set by software to enable the clock security system. When CSSON is set, the clock detector is enabled by hardware when the HSE oscillator is ready, and disabled by hardware if a HSE clock failure is detected. This bit is set only and is cleared by reset.

0: clock security system OFF (clock detector OFF)

1: clock security system ON (clock detector ON if the HSE oscillator is stable, OFF if not).

Bit 18 HSEBYP: HSE crystal oscillator bypassThis bit is set and cleared by software to bypass the oscillator with an external clock.

The external clock must be enabled with the HSEON bit set, to be used by the device.

This bit can be written only if the HSE oscillator is disabled.

0: HSE crystal oscillator not bypassed

1: HSE crystal oscillator bypassed with external clock

Bit 17 HSERDY: HSE clock ready flagThis bit is set by hardware to indicate that the HSE oscillator is stable.

0: HSE oscillator not ready

1: HSE oscillator ready

Note: Once the HSEON bit is cleared, HSERDY goes low after six HSE clock cycles.

Bit 16 HSEON: HSE clock enableThis bit is set and cleared by software. It is cleared by hardware to stop the HSE oscillator when entering Stop, Standby, or Shutdown mode. This bit cannot be reset if the HSE oscillator is used directly or indirectly as the system clock.

0: HSE oscillator off

1: HSE oscillator on

Bit 15 SHSIRDY: SHSI clock ready flagThis bit is set by hardware to indicate that the SHSI oscillator is stable. It is set only when SHSI is enabled by software (by setting SHSION).

0: SHSI oscillator not ready

1: SHSI oscillator ready

Note: Once the SHSION bit is cleared, SHSIRDY goes low after six SHSI clock cycles.

Bit 14 SHSION: SHSI clock enableThis bit is set and cleared by software. It is cleared by hardware to stop the SHSI when entering in Stop, Standby, or Shutdown modes.

0: SHSI oscillator off

1: SHSI oscillator on

Bit 13 HSI48RDY: HSI48 clock ready flagThis bit is set by hardware to indicate that HSI48 oscillator is stable. It is set only when HSI48 is enabled by software (by setting HSI48ON).

0: HSI48 oscillator not ready

1: HSI48 oscillator ready

Bit 12 HSI48ON: HSI48 clock enableThis bit is set and cleared by software. It is cleared by hardware to stop the HSI48 when entering in Stop, Standby, or Shutdown modes.

0: HSI48 oscillator off

1: HSI48 oscillator on

Bit 11 Reserved, must be kept at reset value. Bit 10 HSIRDY: HSI16 clock ready flagThis bit is set by hardware to indicate that HSI16 oscillator is stable. It is set only when HSI16 is enabled by software (by setting HSION).

0: HSI16 oscillator not ready

1: HSI16 oscillator ready

Note: Once the HSION bit is cleared, HSIRDY goes low after six HSI16 clock cycles.

Bit 9 HSIKERON: HSI16 enable for some peripheral kernelsThis bit is set and cleared by software to force HSI16 ON even in Stop modes. Keeping HSI16 on in Stop mode allows the communication speed not to be reduced by the HSI16 startup time. This bit has no effect on HSION value. Refer to Section 11.4.24 for more details. This bit must be configured at 0 before entering Stop 3 mode.

0: No effect on HSI16 oscillator

1: HSI16 oscillator forced on even in Stop mode

Bit 8 HSION: HSI16 clock enableThis bit is set and cleared by software. It is cleared by hardware to stop the HSI16 oscillator when entering Stop, Standby, or Shutdown mode. This bit is set by hardware to force the HSI16 oscillator on when STOPWUCK = 1 when leaving Stop modes, or in case of failure of the HSE crystal oscillator. This bit is set by hardware if the HSI16 is used directly or indirectly as system clock.

0: HSI16 oscillator off

1: HSI16 oscillator on

Bit 7 MSIPLLFAST: MSI PLL mode fast startupThis bit is set and reset by software to enable/disable the fast PLL mode start-up of the MSI clock source. This bit is used only if PLL mode is selected (MSIPLLEN = 1).

Caution: The fast start-up feature is not active the first time the PLL mode is selected.

The fast start-up is active when the MSI in PLL mode returns from switch off.

0: MSI PLL normal start-up

1: MSI PLL fast start-up

Bit 6 MSIPLLSEL: MSI clock with PLL mode selectionThis bit is set and cleared by software to select which MSI output clock uses the PLL mode. It can be written only when the MSI PLL mode is disabled (MSIPLLEN = 0).

0: PLL mode applied to MSIK (MSI kernel) clock output

1: PLL mode applied to MSIS (MSI system) clock output

Note: If the MSI kernel clock output uses the same oscillator source than the MSI system clock output, then the PLL mode is applied to both clock outputs.

Bit 5 MSIKRDY: MSIK clock ready flagThis bit is set by hardware to indicate that the MSIK is stable. It is set only when MSI kernel oscillator is enabled by software by setting MSIKON.

0: MSIK (MSI kernel) oscillator not ready

1: MSIK (MSI kernel) oscillator ready

Note: Once MSIKON bit is cleared, MSIKRDY goes low after six MSIK oscillator clock cycles.

Bit 4 MSIKON: MSIK clock enableThis bit is set and cleared by software. It is cleared by hardware to stop the MSIK when entering Stop, Standby, or Shutdown mode. This bit is set by hardware to force the MSIK oscillator ON when exiting Standby or Shutdown mode. It is set by hardware to force the MSIK oscillator on when STOPWUCK = 0 or STOPKERWUCK = 0 when exiting Stop modes, or in case of a failure of the HSE oscillator.

0: MSIK (MSI kernel) oscillator disabled

1: MSIK (MSI kernel) oscillator enabled

Bit 3 MSIPLLEN: MSI clock PLL-mode enableThis bit is set and cleared by software to enable/disable the PLL part of the MSI clock source. MSIPLLEN must be enabled after LSE is enabled (LSEON enabled) and ready (LSERDY set by hardware). A hardware protection prevents from enabling MSIPLLEN if LSE is not ready. This bit is cleared by hardware when LSE is disabled (LSEON = 0) or when the CSS on LSE detects a LSE failure (see RCC_CSR).

0: MSI PLL-mode OFF

1: MSI PLL-mode ON

Bit 2 MSISRDI: MSIS clock ready flagThis bit is set by hardware to indicate that the MSIS oscillator is stable. It is set only when MSIS is enabled by software (by setting MSISON).

0: MSIS (MSI system) oscillator not ready

1: MSIS (MSI system) oscillator ready

Note: Once the MSISON bit is cleared, MSISRDI goes low after six MSIS clock cycles.

Bit 1 MSIKERON: MSI enable for some peripheral kernelsThis bit is set and cleared by software to force MSI ON even in Stop modes. Keeping the MSI on in Stop mode allows the communication speed not to be reduced by the MSI startup time. This bit has no effect on MSISON and MSIKON values (see Section 11.4.24 for more details). This bit must be configured at 0 before entering Stop 3 mode.

0: No effect on MSI oscillator

1: MSI oscillator forced ON even in Stop mode

Bit 0 MSISON: MSIS clock enableThis bit is set and cleared by software. It is cleared by hardware to stop the MSIS oscillator when entering Stop, Standby or Shutdown mode. This bit is set by hardware to force the MSIS oscillator on when exiting Standby or Shutdown mode. It is set by hardware to force the MSIS oscillator ON when STOPWUCK = 0 when exiting Stop modes, or in case of a failure of the HSE oscillator.

Set by hardware when used directly or indirectly as system clock.

0: MSIS (MSI system) oscillator off

1: MSIS (MSI system) oscillator on

11.8.2 RCC internal clock sources calibration register 1 (RCC_ICSCR1)

Address offset: 0x008

Reset value: 0x440X XXXX

X is factory-programmed.

Access: no wait state; word, half-word, and byte access

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MSISRANGE[3:0] | MSIKRANGE[3:0] | MSIRG SEL | MSIBIA S | Res. | Res. | MSICAL0[4:1] | |||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rs | rw | r | r | r | r | ||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MSICAL L0[0] | MSICAL1[4:0] | MSICAL2[4:0] | MSICAL3[4:0] | ||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:28 MSISRANGE[3:0] : MSIS clock ranges

These bits are configured by software to choose the frequency range of MSIS oscillator when MSIRGSEL is set. 16 frequency ranges are available:

- 0000: range 0 around 48 MHz

- 0001: range 1 around 24 MHz

- 0010: range 2 around 16 MHz

- 0011: range 3 around 12 MHz

- 0100: range 4 around 4 MHz (reset value)

- 0101: range 5 around 2 MHz

- 0110: range 6 around 1.33 MHz

- 0111: range 7 around 1 MHz

- 1000: range 8 around 3.072 MHz

- 1001: range 9 around 1.536 MHz

- 1010: range 10 around 1.024 MHz

- 1011: range 11 around 768 kHz