21. Universal synchronous/asynchronous receiver transmitter (USART/UART)

21.1 Introduction

The universal synchronous asynchronous receiver transmitter (USART) offers a flexible means of Full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The USART offers a very wide range of baud rates using a programmable baud rate generator.

It supports synchronous one-way communication and Half-duplex Single-wire communication, as well as multiprocessor communications. It also supports the LIN (Local Interconnect Network), Smartcard protocol and IrDA (Infrared Data Association) SIR ENDEC specifications and Modem operations (CTS/RTS).

High speed data communication is possible by using the DMA (direct memory access) for multibuffer configuration.

21.2 USART main features

- • Full-duplex asynchronous communications

- • NRZ standard format (mark/space)

- • Configurable oversampling method by 16 or 8 to give flexibility between speed and clock tolerance

- • A common programmable transmit and receive baud rate of up to 4 Mbit/s when the clock frequency is 32 MHz and oversampling is by 8

- • Dual clock domain allowing:

- – USART functionality and wakeup from Stop mode

- – Convenient baud rate programming independent from the PCLK reprogramming

- • Auto baud rate detection

- • Programmable data word length (7, 8 or 9 bits)

- • Programmable data order with MSB-first or LSB-first shifting

- • Configurable stop bits (1 or 2 stop bits)

- • Synchronous mode and clock output for synchronous communications

- • Single-wire Half-duplex communications

- • Continuous communications using DMA

- • Received/transmitted bytes are buffered in reserved SRAM using centralized DMA

- • Separate enable bits for transmitter and receiver

- • Separate signal polarity control for transmission and reception

- • Swappable Tx/Rx pin configuration

- • Hardware flow control for modem and RS-485 transceiver

- • Communication control/error detection flags

- • Parity control:

- – Transmits parity bit

- – Checks parity of received data byte

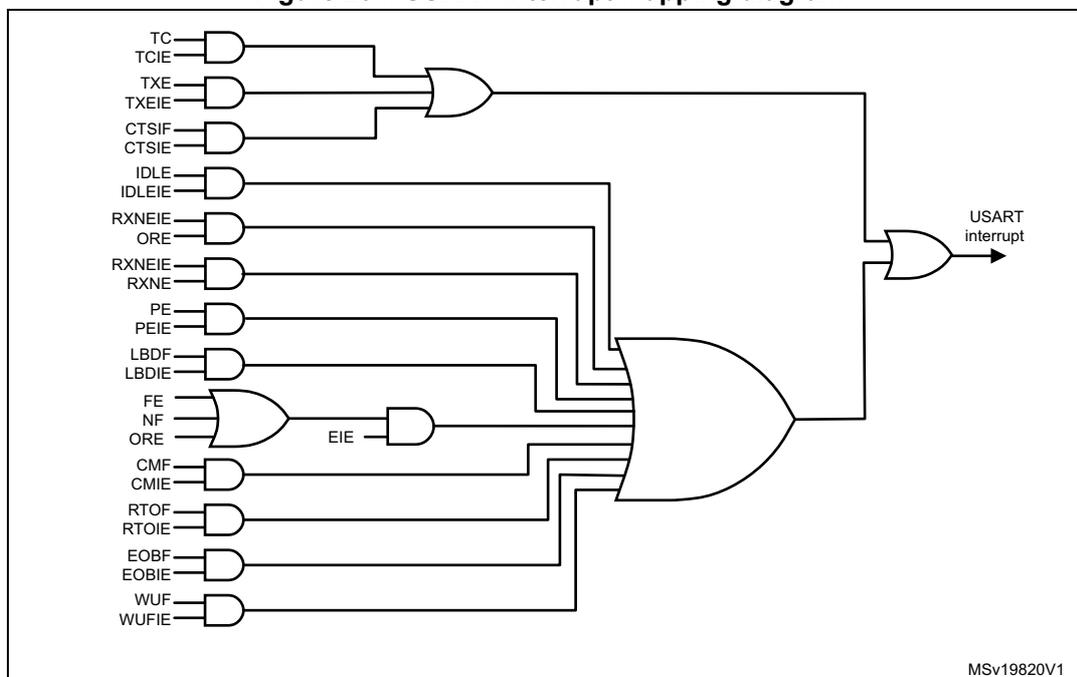

- • Fourteen interrupt sources with flags

- • Multiprocessor communications

The USART enters Mute mode if the address does not match. - • Wakeup from Mute mode (by idle line detection or address mark detection)

21.3 USART extended features

- • LIN master synchronous break send capability and LIN slave break detection capability

- – 13-bit break generation and 10/11-bit break detection when USART is hardware configured for LIN

- • IrDA SIR encoder decoder supporting 3/16 bit duration for normal mode

- • Smartcard mode

- – Supports the T=0 and T=1 asynchronous protocols for smartcards as defined in the ISO/IEC 7816-3 standard

- – 0.5 and 1.5 stop bits for smartcard operation

- • Support for ModBus communication

- – Timeout feature

- – CR/LF character recognition

21.4 USART implementation

Table 102. STM32L010x USART/LPUART features

| USART modes/features (1) | USART2 (category 1 and 2 devices) | USART2 (category 3 and 5) | LPUART1 |

|---|---|---|---|

| Hardware flow control for modem | X | X | X |

| Continuous communication using DMA | X | X | X |

| Multiprocessor communication | X | X | X |

| Synchronous mode | - | X | - |

| Smartcard mode | - | X | - |

| Single-wire Half-duplex communication | X | X | X |

| Ir SIR ENDEC block | - | X | - |

| LIN mode | - | X | - |

| Dual clock domain and wakeup from Stop mode | - | X | X |

| Receiver timeout interrupt | - | X | - |

| Modbus communication | - | X | - |

| Auto baud rate detection | - | X | - |

| Driver Enable | X | X | X |

| USART/LPUART data length | 7 (2) , 8 and 9 bits | ||

1. X = supported.

2. In 7-bit data length mode, Smartcard mode, LIN master mode and Auto baud rate (0x7F and 0x55 frame detection) are not supported.

21.5 USART functional description

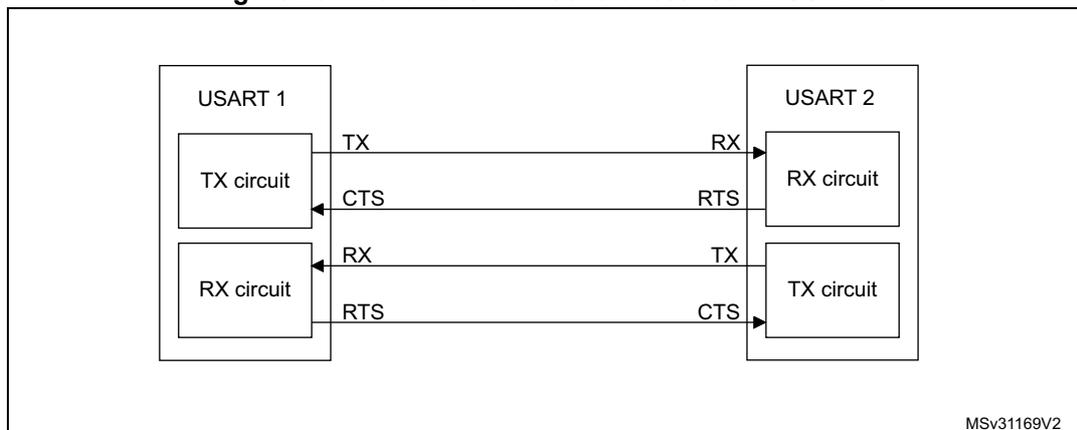

Any USART bidirectional communication requires a minimum of two pins: Receive data In (RX) and Transmit data Out (TX):

- • RX: Receive data Input.

This is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

- • TX: Transmit data Output.

When the transmitter is disabled, the output pin returns to its I/O port configuration. When the transmitter is enabled and nothing is to be transmitted, the TX pin is at high level. In Single-wire and Smartcard modes, this I/O is used to transmit and receive the data.

Serial data are transmitted and received through these pins in normal USART mode. The frames are comprised of:

- • An Idle Line prior to transmission or reception

- • A start bit

- • A data word (7, 8 or 9 bits) least significant bit first

- • 0.5, 1, 1.5, 2 stop bits indicating that the frame is complete

- • The USART interface uses a baud rate generator

- • A status register (USART_ISR)

- • Receive and transmit data registers (USART_RDR, USART_TDR)

- • A baud rate register (USART_BRR)

- • A guard-time register (USART_GTPR) in case of Smartcard mode.

Refer to Section 21.8: USART registers on page 617 for the definitions of each bit.

The following pin is required to interface in synchronous mode and Smartcard mode:

- • CK: Clock output. This pin outputs the transmitter data clock for synchronous transmission corresponding to SPI master mode (no clock pulses on start bit and stop bit, and a software option to send a clock pulse on the last data bit). In parallel, data can be received synchronously on RX. This can be used to control peripherals that have shift registers. The clock phase and polarity are software programmable. In Smartcard mode, CK output can provide the clock to the smartcard.

The following pins are required in RS232 Hardware flow control mode:

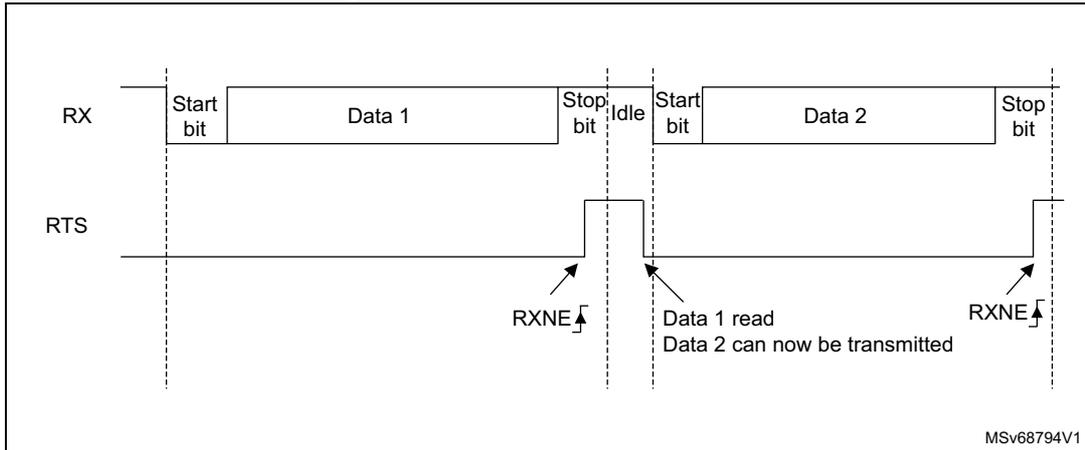

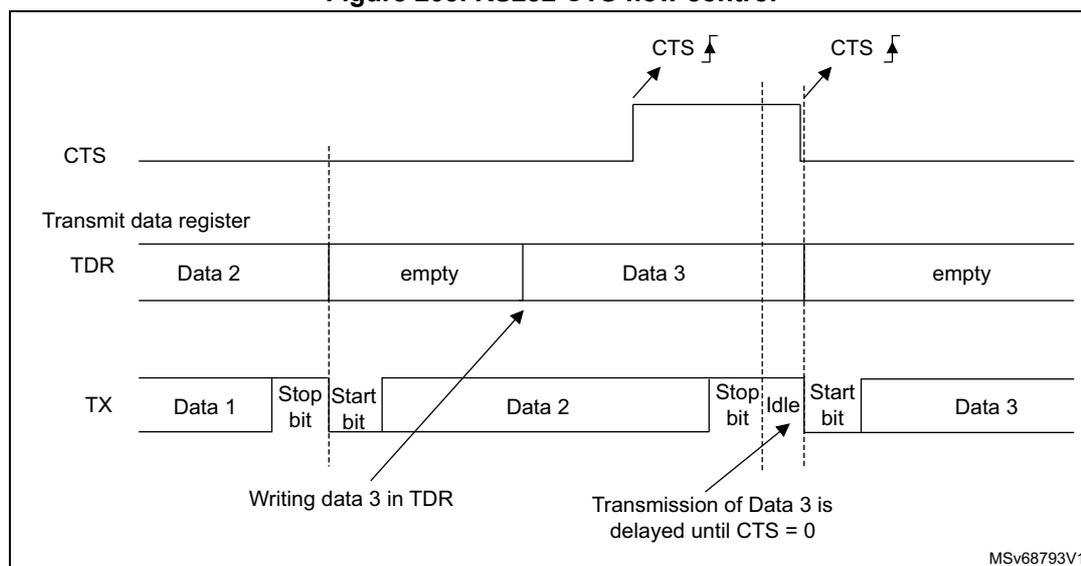

- • CTS: Clear To Send blocks the data transmission at the end of the current transfer (when high)

- • RTS: Request to send indicates that the USART is ready to receive data (when low).

The following pin is required in RS485 Hardware control mode:

- • DE: Driver Enable activates the transmission mode of the external transceiver.

Note: DE and RTS share the same pin.

Figure 180. USART block diagram

![Figure 180. USART block diagram. This is a detailed block diagram of the USART (Universal Synchronous/Asynchronous Receiver Transmitter) block. At the top, a 'PRDATA' bus is connected to a 'Write' block (CPU or DMA) which feeds into a 'Transmit shift register'. A 'Read' block (CPU or DMA) feeds into a 'Receive shift register', which is connected to a 'DR (data register)'. Below the shift registers are the 'Transmit data register (TDR)' and 'Receive data register (RDR)'. The 'IrDA SIR ENDEC block' is connected to the 'TX' and 'RX' pins and to the 'Transmit data register (TDR)'. The 'Hardware flow controller' is connected to the 'RTS/DE' and 'CTS' pins and to the 'Transmit control' and 'Receiver control' blocks. The 'USART_CR3 register' and 'USART_CR2 register' are connected to the 'IrDA SIR ENDEC block' and the 'Hardware flow controller'. The 'USART_CR1 register' is connected to the 'Transmit control', 'Wake-up unit', and 'Receiver control' blocks. The 'USART_GTPR register' contains 'GT' and 'PSC' fields, which are connected to the 'CK control' block. The 'CK control' block is connected to the 'CK' pin. The 'Transmit control' block is connected to the 'Transmit shift register', 'Transmit data register (TDR)', 'Wake-up unit', and 'USART_CR1 register'. The 'Wake-up unit' is connected to the 'Transmit control', 'Receiver control', and 'USART_CR1 register'. The 'Receiver control' block is connected to the 'Receive shift register', 'Receive data register (RDR)', 'Wake-up unit', 'USART_CR1 register', and 'USART_ISR register'. The 'USART_ISR register' is connected to the 'Receiver control' and 'USART interrupt control' blocks. The 'USART interrupt control' block is connected to the 'Transmit control', 'Wake-up unit', and 'Receiver control' blocks. The 'Transmitter clock' is connected to the '/USARTDIV or 2/USARTDIV (depending on the oversampling mode) (Note 1)' block. The 'fck (Note 2)' input is also connected to this block. The 'USART_BRR register' contains 'TE', 'BRR[15:0]', and 'RE' fields. The 'TE' field is connected to the 'Transmitter rate controller', which is connected to the '/USARTDIV or 2/USARTDIV' block. The 'BRR[15:0]' field is connected to the 'Transmitter rate controller' and the 'Receiver rate controller'. The 'RE' field is connected to the 'Receiver rate controller', which is connected to the '/USARTDIV or 2/USARTDIV' block. The 'Conventional baud rate generator' is connected to the 'Receiver rate controller'. The diagram is labeled 'MS19821V8' in the bottom right corner.](/RM0451-STM32L0x0/fa676d145fed4fc3621ea24c653c0299_img.jpg)

- 1. For details on coding USARTDIV in the USART_BRR register, refer to Section 21.5.4: USART baud rate generation .

- 2. \( f_{CK} \) can be \( f_{LSE} \) , \( f_{HSI} \) , \( f_{PCLK} \) , \( f_{SYS} \) .

21.5.1 USART character description

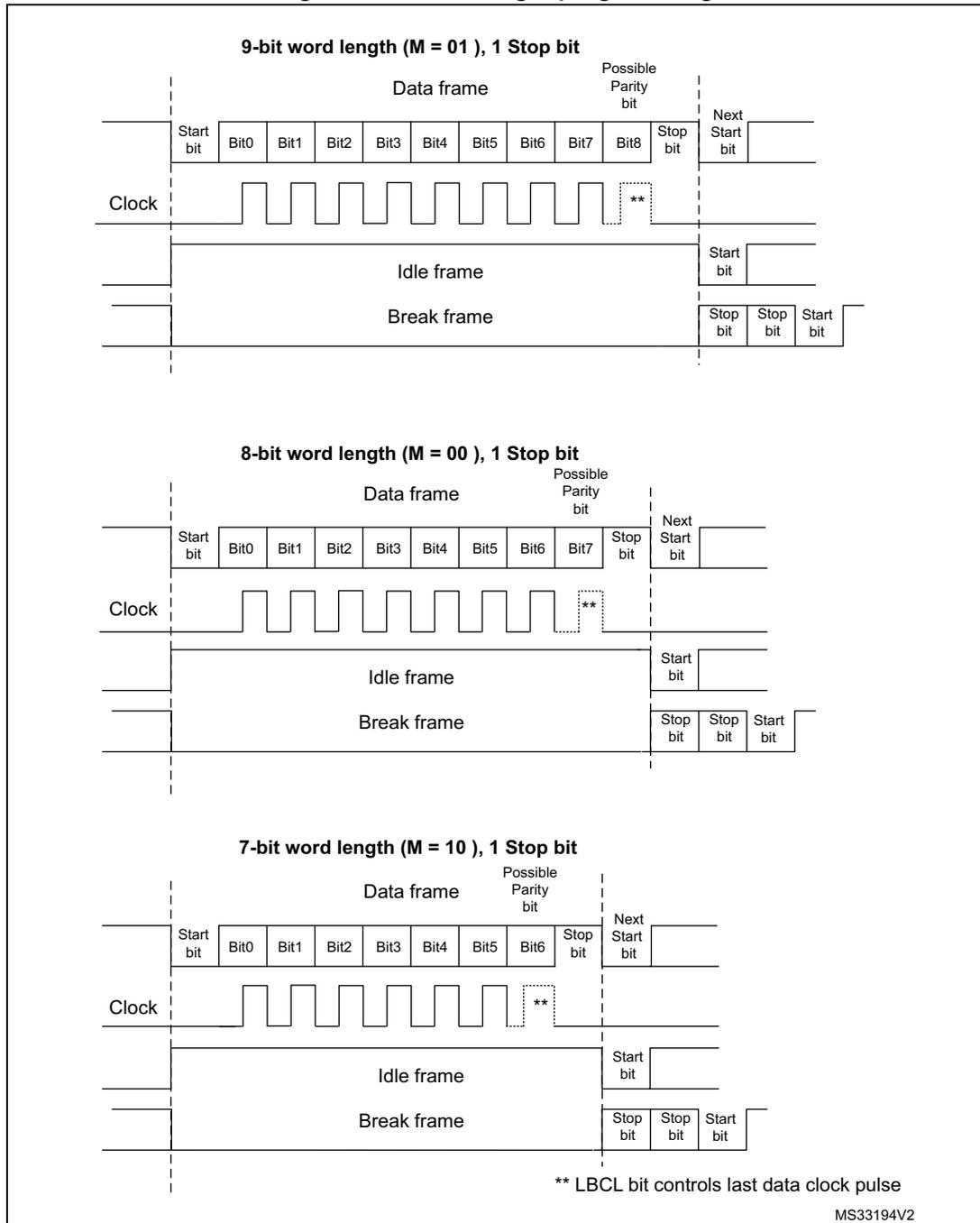

The word length can be selected as being either 7 or 8 or 9 bits by programming the M[1:0] bits in the USART_CR1 register (see Figure 181 ).

- • 7-bit character length: M[1:0] = 10

- • 8-bit character length: M[1:0] = 00

- • 9-bit character length: M[1:0] = 01

Note: The 7-bit mode is supported only on some USARTs. In addition, not all modes are supported in 7-bit data length mode. Refer to Section 21.4: USART implementation for additional information.

By default, the signal (TX or RX) is in low state during the start bit. It is in high state during the stop bit.

These values can be inverted, separately for each signal, through polarity configuration control.

An Idle character is interpreted as an entire frame of “1”s (the number of “1”s includes the number of stop bits).

A Break character is interpreted on receiving “0”s for a frame period. At the end of the break frame, the transmitter inserts 2 stop bits.

Transmission and reception are driven by a common baud rate generator, the clock for each is generated when the enable bit is set respectively for the transmitter and receiver.

The details of each block is given below.

Figure 181. Word length programming

The diagram illustrates the timing for three different word lengths in a USART/UART. Each section shows a 'Data frame', an 'Idle frame', and a 'Break frame' relative to a 'Clock' signal.

- 9-bit word length (M = 01), 1 Stop bit:

- Data frame: Start bit, Bit0, Bit1, Bit2, Bit3, Bit4, Bit5, Bit6, Bit7, Bit8, Possible Parity bit, Stop bit. The clock signal has 10 pulses, with the last one (LBCL) marked with '**'.

- Idle frame: A high level followed by a Start bit.

- Break frame: A low level followed by two Stop bits and a Start bit.

- 8-bit word length (M = 00), 1 Stop bit:

- Data frame: Start bit, Bit0, Bit1, Bit2, Bit3, Bit4, Bit5, Bit6, Bit7, Possible Parity bit, Stop bit. The clock signal has 9 pulses, with the last one (LBCL) marked with '**'.

- Idle frame: A high level followed by a Start bit.

- Break frame: A low level followed by two Stop bits and a Start bit.

- 7-bit word length (M = 10), 1 Stop bit:

- Data frame: Start bit, Bit0, Bit1, Bit2, Bit3, Bit4, Bit5, Bit6, Possible Parity bit, Stop bit. The clock signal has 8 pulses, with the last one (LBCL) marked with '**'.

- Idle frame: A high level followed by a Start bit.

- Break frame: A low level followed by two Stop bits and a Start bit.

** LBCL bit controls last data clock pulse

MS33194V2

21.5.2 USART transmitter

The transmitter can send data words of either 7, 8 or 9 bits depending on the M bits status. The Transmit Enable bit (TE) must be set in order to activate the transmitter function. The data in the transmit shift register is output on the TX pin and the corresponding clock pulses are output on the CK pin.

Character transmission

During an USART transmission, data shifts out least significant bit first (default configuration) on the TX pin. In this mode, the USART_TDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 180 ).

Every character is preceded by a start bit which is a logic level low for one bit period. The character is terminated by a configurable number of stop bits.

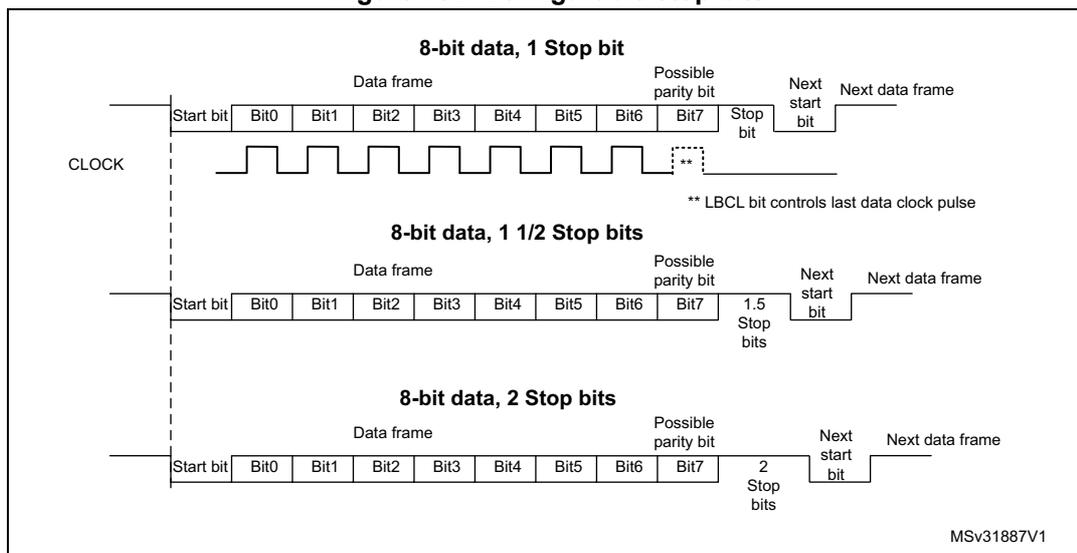

The following stop bits are supported by USART: 0.5, 1, 1.5 and 2 stop bits.

Note: The TE bit must be set before writing the data to be transmitted to the USART_TDR. The TE bit should not be reset during transmission of data. Resetting the TE bit during the transmission will corrupt the data on the TX pin as the baud rate counters will get frozen. The current data being transmitted will be lost. An idle frame will be sent after the TE bit is enabled.

Configurable stop bits

The number of stop bits to be transmitted with every character can be programmed in Control register 2, bits 13,12.

- • 1 stop bit: This is the default value of number of stop bits.

- • 2 stop bits: This will be supported by normal USART, Single-wire and Modem modes.

- • 1.5 stop bits: To be used in Smartcard mode.

- • 0.5 stop bit: To be used when receiving data in Smartcard mode.

An idle frame transmission will include the stop bits.

A break transmission will be 10 low bits (when M[1:0] = 00) or 11 low bits (when M[1:0] = 01) or 9 low bits (when M[1:0] = 10) followed by 2 stop bits (see Figure 182 ). It is not possible to transmit long breaks (break of length greater than 9/10/11 low bits).

Figure 182. Configurable stop bits

The diagram illustrates three data frame structures for 8-bit data transmission, showing the sequence of bits: Start bit, 8 data bits (Bit0 to Bit7), an optional parity bit, and stop bits. A CLOCK signal is shown above the frames, with a note that the LBCL bit controls the last data clock pulse.

- 8-bit data, 1 Stop bit: The frame consists of a Start bit, 8 data bits (Bit0 to Bit7), an optional parity bit, and 1 stop bit. The next data frame begins after the stop bit.

- 8-bit data, 1 1/2 Stop bits: The frame consists of a Start bit, 8 data bits (Bit0 to Bit7), an optional parity bit, and 1.5 stop bits. The next data frame begins after the stop bits.

- 8-bit data, 2 Stop bits: The frame consists of a Start bit, 8 data bits (Bit0 to Bit7), an optional parity bit, and 2 stop bits. The next data frame begins after the stop bits.

** LBCL bit controls last data clock pulse

MSv31887V1

Character transmission procedure

- 1. Program the M bits in USART_CR1 to define the word length.

- 2. Select the desired baud rate using the USART_BRR register.

- 3. Program the number of stop bits in USART_CR2.

- 4. Enable the USART by writing the UE bit in USART_CR1 register to 1.

- 5. Select DMA enable (DMAT) in USART_CR3 if multibuffer communication is to take place. Configure the DMA register as explained in multibuffer communication.

- 6. Set the TE bit in USART_CR1 to send an idle frame as first transmission.

- 7. Write the data to send in the USART_TDR register (this clears the TXE bit). Repeat this for each data to be transmitted in case of single buffer.

- 8. After writing the last data into the USART_TDR register, wait until TC=1. This indicates that the transmission of the last frame is complete. This is required for instance when the USART is disabled or enters the Halt mode to avoid corrupting the last transmission.

For code example, refer to A.15.1: USART transmitter configuration code example .

Single byte communication

Clearing the TXE bit is always performed by a write to the transmit data register.

The TXE bit is set by hardware and it indicates:

- • The data has been moved from the USART_TDR register to the shift register and the data transmission has started.

- • The USART_TDR register is empty.

- • The next data can be written in the USART_TDR register without overwriting the previous data.

For code example, refer to A.15.2: USART transmit byte code example .

This flag generates an interrupt if the TXEIE bit is set.

When a transmission is taking place, a write instruction to the USART_TDR register stores the data in the TDR register; next, the data is copied in the shift register at the end of the currently ongoing transmission.

When no transmission is taking place, a write instruction to the USART_TDR register places the data in the shift register, the data transmission starts, and the TXE bit is set.

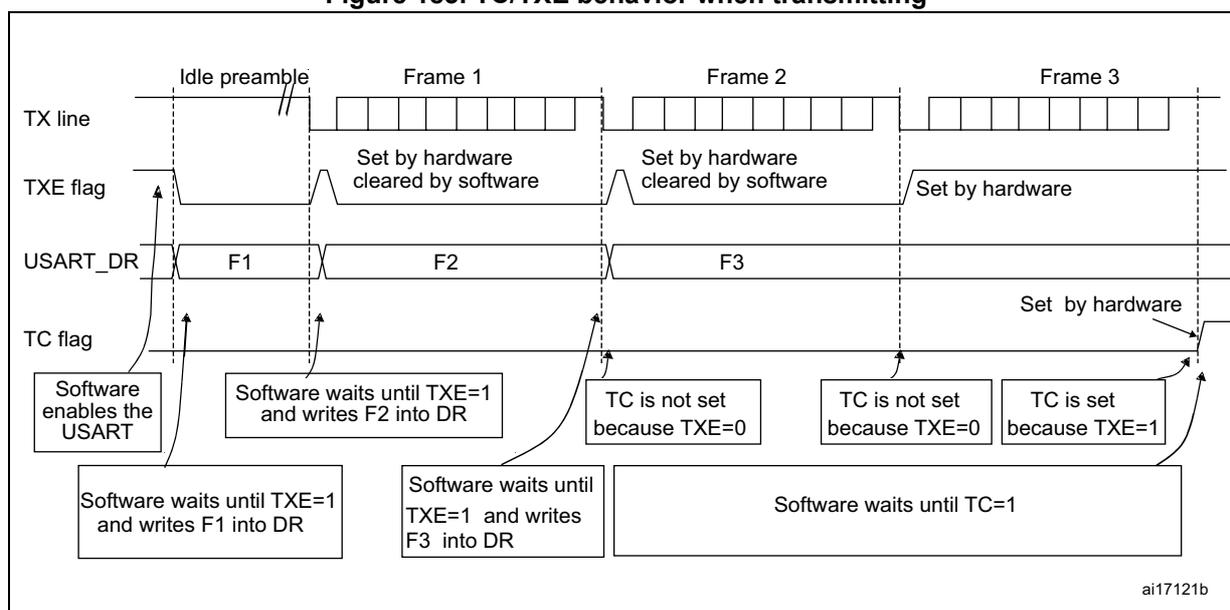

If a frame is transmitted (after the stop bit) and the TXE bit is set, the TC bit goes high. An interrupt is generated if the TCIE bit is set in the USART_CR1 register.

After writing the last data in the USART_TDR register, it is mandatory to wait for TC=1 before disabling the USART or causing the microcontroller to enter the low-power mode (see Figure 183: TC/TXE behavior when transmitting ).

Figure 183. TC/TXE behavior when transmitting

The diagram illustrates the timing and state of flags during the transmission of three frames (Frame 1, Frame 2, Frame 3) over a TX line. The sequence starts with an Idle preamble. The TX line shows the transmission of each frame. The TXE flag is set by hardware when the shift register is empty and cleared by software when a new character is written. The USART_DR register contains the data to be transmitted. The TC flag is set by hardware when the shift register is empty and the TXE flag is set. The diagram shows that the TC flag is not set while the TXE flag is set, and only becomes set after the TXE flag is cleared and the shift register is empty.

Key events and states shown in the diagram:

- Idle preamble: The initial state of the TX line.

- Frame 1: The first frame to be transmitted. The TXE flag is set by hardware. Software enables the USART and waits until TXE=1 to write F1 into DR. The TC flag is not set because TXE=0.

- Frame 2: The second frame to be transmitted. The TXE flag is set by hardware. Software waits until TXE=1 and writes F2 into DR. The TC flag is not set because TXE=0.

- Frame 3: The third frame to be transmitted. The TXE flag is set by hardware. Software waits until TXE=1 and writes F3 into DR. The TC flag is not set because TXE=0.

- End of transmission: After the last character (F3) is written, the TXE flag is cleared by software. The TC flag is set by hardware because TXE=1. Software waits until TC=1.

For code example, refer to A.15.3: USART transfer complete code example .

Break characters

Setting the SBKRQ bit transmits a break character. The break frame length depends on the M bits (see Figure 181 ).

If a '1' is written to the SBKRQ bit, a break character is sent on the TX line after completing the current character transmission. The SBKF bit is set by the write operation and it is reset by hardware when the break character is completed (during the stop bits after the break character). The USART inserts a logic 1 signal (STOP) for the duration of 2 bits at the end of the break frame to guarantee the recognition of the start bit of the next frame.

In the case the application needs to send the break character following all previously inserted data, including the ones not yet transmitted, the software should wait for the TXE flag assertion before setting the SBKRQ bit.

Idle characters

Setting the TE bit drives the USART to send an idle frame before the first data frame.

21.5.3 USART receiver

The USART can receive data words of either 7, 8 or 9 bits depending on the M bits in the USART_CR1 register.

Start bit detection

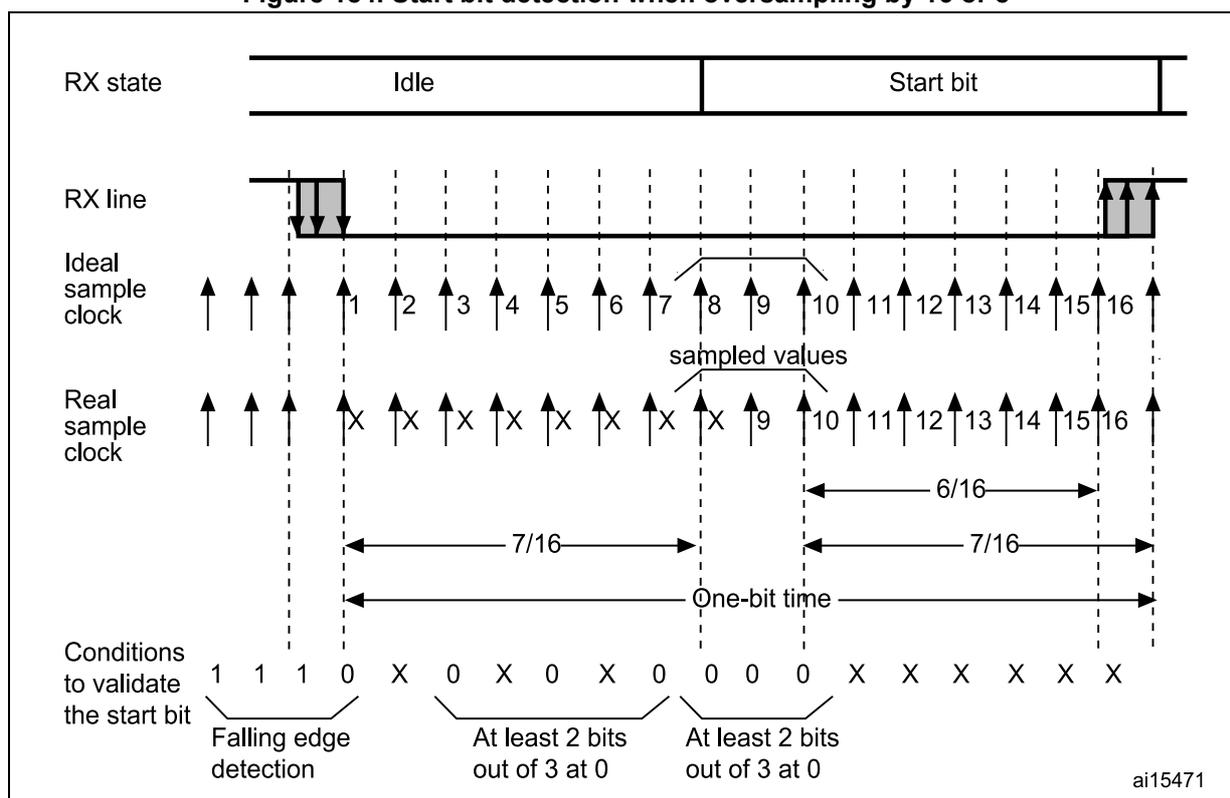

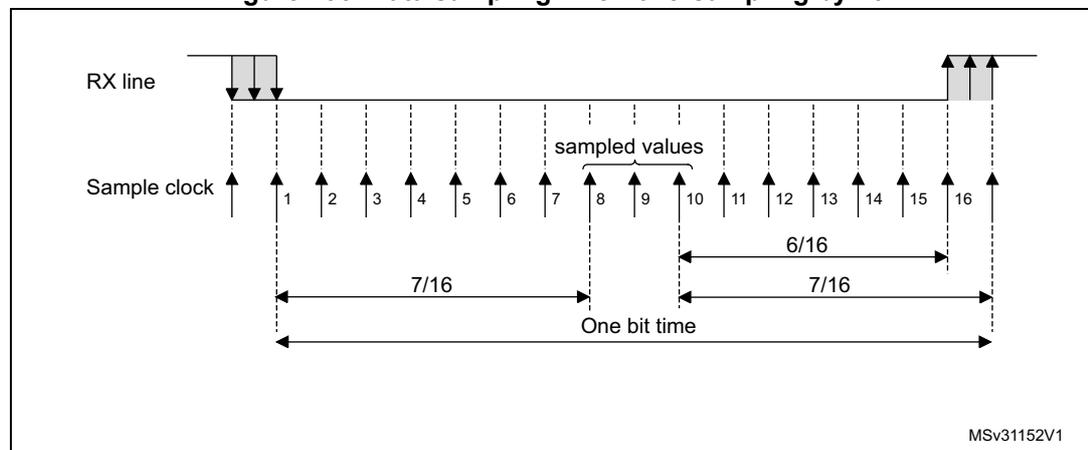

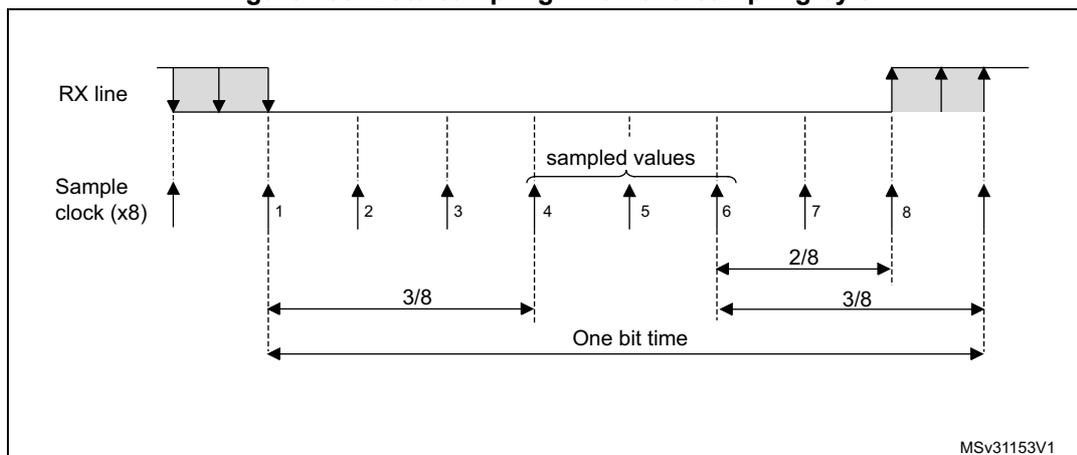

The start bit detection sequence is the same when oversampling by 16 or by 8.

In the USART, the start bit is detected when a specific sequence of samples is recognized. This sequence is: 1 1 1 0 X 0 X 0 X 0 X 0 X 0.

Figure 184. Start bit detection when oversampling by 16 or 8

The diagram illustrates the start bit detection process. The RX state transitions from Idle to Start bit. The RX line shows a falling edge for the start bit. Ideal sample clock has 16 samples per bit, while Real sample clock has 8 samples per bit. Sampling occurs at the 3rd, 5th, 7th, 8th, 9th, and 10th clock cycles. The sampled values are 1 1 1 0 X 0 X 0 X 0 X 0 X 0. Conditions to validate the start bit include falling edge detection and at least 2 bits out of 3 at 0 for two consecutive samplings. Timing markers show 7/16 and 6/16 bit times.

Note: If the sequence is not complete, the start bit detection aborts and the receiver returns to the idle state (no flag is set), where it waits for a falling edge.

The start bit is confirmed (RXNE flag set, interrupt generated if RXNEIE=1) if the 3 sampled bits are at 0 (first sampling on the 3rd, 5th and 7th bits finds the 3 bits at 0 and second sampling on the 8th, 9th and 10th bits also finds the 3 bits at 0).

The start bit is validated (RXNE flag set, interrupt generated if RXNEIE=1) but the NF noise flag is set if,

- for both samplings, 2 out of the 3 sampled bits are at 0 (sampling on the 3rd, 5th and 7th bits and sampling on the 8th, 9th and 10th bits)

- or

- for one of the samplings (sampling on the 3rd, 5th and 7th bits or sampling on the 8th, 9th and 10th bits), 2 out of the 3 bits are found at 0.

If neither conditions a. or b. are met, the start detection aborts and the receiver returns to the idle state (no flag is set).

Character reception

During an USART reception, data shifts in least significant bit first (default configuration) through the RX pin. In this mode, the USART_RDR register consists of a buffer (RDR) between the internal bus and the receive shift register.

Character reception procedure

- 1. Program the M bits in USART_CR1 to define the word length.

- 2. Select the desired baud rate using the baud rate register USART_BRR

- 3. Program the number of stop bits in USART_CR2.

- 4. Enable the USART by writing the UE bit in USART_CR1 register to 1.

- 5. Select DMA enable (DMAR) in USART_CR3 if multibuffer communication is to take place. Configure the DMA register as explained in multibuffer communication.

- 6. Set the RE bit USART_CR1. This enables the receiver which begins searching for a start bit.

For code example, refer to A.15.4: USART receiver configuration code example .

When a character is received:

- • The RXNE bit is set to indicate that the content of the shift register is transferred to the RDR. In other words, data has been received and can be read (as well as its associated error flags).

- • An interrupt is generated if the RXNEIE bit is set.

- • The error flags can be set if a frame error, noise or an overrun error has been detected during reception. PE flag can also be set with RXNE.

- • In multibuffer, RXNE is set after every byte received and is cleared by the DMA read of the Receive data Register.

- • In single buffer mode, clearing the RXNE bit is performed by a software read to the USART_RDR register. The RXNE flag can also be cleared by writing 1 to the RXFRQ in the USART_RQR register. The RXNE bit must be cleared before the end of the reception of the next character to avoid an overrun error.

For code example, refer to A.15.5: USART receive byte code example .

Break character

When a break character is received, the USART handles it as a framing error.

Idle character

When an idle frame is detected, there is the same procedure as for a received data character plus an interrupt if the IDLEIE bit is set.

Overrun error

An overrun error occurs when a character is received when RXNE has not been reset. Data can not be transferred from the shift register to the RDR register until the RXNE bit is cleared.

The RXNE flag is set after every byte received. An overrun error occurs if RXNE flag is set when the next data is received or the previous DMA request has not been serviced. When an overrun error occurs:

- • The ORE bit is set.

- • The RDR content will not be lost. The previous data is available when a read to USART_RDR is performed.

- • The shift register will be overwritten. After that point, any data received during overrun is lost.

- • An interrupt is generated if either the RXNEIE bit is set or EIE bit is set.

- • The ORE bit is reset by setting the ORECF bit in the ICR register.

Note: The ORE bit, when set, indicates that at least 1 data has been lost. There are two possibilities:

- - if RXNE=1, then the last valid data is stored in the receive register RDR and can be read,

- - if RXNE=0, then it means that the last valid data has already been read and thus there is nothing to be read in the RDR. This case can occur when the last valid data is read in the RDR at the same time as the new (and lost) data is received.

Selecting the proper oversampling method

When the dual clock domain with the wakeup from Stop mode is supported, the clock source can be one of the following sources: PCLK (default), LSE, HSI16 or SYSCLK. Otherwise, the USART clock source is PCLK.

Choosing LSE or HSI16 as clock source may allow the USART to receive data while the MCU is in low-power mode. Depending on the received data and wakeup mode selection, the USART wakes up the MCU, when needed, in order to transfer the received data by software reading the USART_RDR register or by DMA.

For the other clock sources, the system must be active in order to allow USART communication.

The receiver implements different user-configurable oversampling techniques for data recovery by discriminating between valid incoming data and noise. This allows a trade-off between the maximum communication speed and noise/clock inaccuracy immunity.

The oversampling method can be selected by programming the OVER8 bit in the USART_CR1 register and can be either 16 or 8 times the baud rate clock ( Figure 185 and Figure 186 ).

Depending on the application:

- • Select oversampling by 8 (OVER8=1) to achieve higher speed (up to \( f_{CK}/8 \) ). In this case the maximum receiver tolerance to clock deviation is reduced (refer to Section 21.5.5: Tolerance of the USART receiver to clock deviation on page 590 )

- • Select oversampling by 16 (OVER8=0) to increase the tolerance of the receiver to clock deviations. In this case, the maximum speed is limited to maximum \( f_{CK}/16 \) where \( f_{CK} \) is the clock source frequency.

Programming the ONEBIT bit in the USART_CR3 register selects the method used to evaluate the logic level. There are two options:

- • The majority vote of the three samples in the center of the received bit. In this case, when the 3 samples used for the majority vote are not equal, the NF bit is set

- • A single sample in the center of the received bit

Depending on the application:

- – select the three samples' majority vote method (ONEBIT=0) when operating in a noisy environment and reject the data when a noise is detected (refer to Figure 103 ) because this indicates that a glitch occurred during the sampling.

- – select the single sample method (ONEBIT=1) when the line is noise-free to increase the receiver's tolerance to clock deviations (see Section 21.5.5: Tolerance of the USART receiver to clock deviation on page 590 ). In this case the NF bit will never be set.

When noise is detected in a frame:

- • The NF bit is set at the rising edge of the RXNE bit.

- • The invalid data is transferred from the Shift register to the USART_RDR register.

- • No interrupt is generated in case of single byte communication. However this bit rises at the same time as the RXNE bit which itself generates an interrupt. In case of multibuffer communication an interrupt will be issued if the EIE bit is set in the USART_CR3 register.

The NF bit is reset by setting NFCF bit in ICR register.

Note: Oversampling by 8 is not available in LIN, Smartcard and IrDA modes. In those modes, the OVER8 bit is forced to '0' by hardware.

Figure 185. Data sampling when oversampling by 16

The diagram illustrates the timing for data sampling with 16x oversampling. A horizontal line represents the RX line, and a series of vertical arrows represents the Sample clock. The clock frequency is 16 times the bit rate. The first bit is sampled by the first 7 clock edges (labeled 1 to 7). The second bit is sampled by the next 7 clock edges (labeled 8 to 14). The third bit is sampled by the remaining 6 clock edges (labeled 15 to 16). A bracket labeled 'sampled values' covers the 8th, 9th, and 10th samples. Horizontal double-headed arrows indicate durations: '7/16' for the first bit, '6/16' for the third bit, and '7/16' for the second bit. A longer double-headed arrow at the bottom is labeled 'One bit time'. The diagram is identified by the code MSv31152V1 in the bottom right corner.

Figure 186. Data sampling when oversampling by 8

Table 103. Noise detection from sampled data

| Sampled value | NE status | Received bit value |

|---|---|---|

| 000 | 0 | 0 |

| 001 | 1 | 0 |

| 010 | 1 | 0 |

| 011 | 1 | 1 |

| 100 | 1 | 0 |

| 101 | 1 | 1 |

| 110 | 1 | 1 |

| 111 | 0 | 1 |

Framing error

A framing error is detected when the stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

When the framing error is detected:

- • The FE bit is set by hardware

- • The invalid data is transferred from the Shift register to the USART_RDR register.

- • No interrupt is generated in case of single byte communication. However this bit rises at the same time as the RXNE bit which itself generates an interrupt. In case of multibuffer communication an interrupt will be issued if the EIE bit is set in the USART_CR3 register.

The FE bit is reset by writing 1 to the FECF in the USART_ICR register.

Configurable stop bits during reception

The number of stop bits to be received can be configured through the control bits of Control Register 2 - it can be either 1 or 2 in normal mode and 0.5 or 1.5 in Smartcard mode.

- • 0.5 stop bit (reception in Smartcard mode): No sampling is done for 0.5 stop bit. As a consequence, no framing error and no break frame can be detected when 0.5 stop bit is selected.

- • 1 stop bit: Sampling for 1 stop Bit is done on the 8th, 9th and 10th samples.

- • 1.5 stop bits (Smartcard mode): When transmitting in Smartcard mode, the device must check that the data is correctly sent. Thus the receiver block must be enabled (RE =1 in the USART_CR1 register) and the stop bit is checked to test if the smartcard has detected a parity error. In the event of a parity error, the smartcard forces the data signal low during the sampling - NACK signal-, which is flagged as a framing error. Then, the FE flag is set with the RXNE at the end of the 1.5 stop bits. Sampling for 1.5 stop bits is done on the 16th, 17th and 18th samples (1 baud clock period after the beginning of the stop bit). The 1.5 stop bits can be decomposed into 2 parts: one 0.5 baud clock period during which nothing happens, followed by 1 normal stop bit period during which sampling occurs halfway through. Refer to Section 21.5.13: USART Smartcard mode on page 602 for more details.

- • 2 stop bits: Sampling for 2 stop bits is done on the 8th, 9th and 10th samples of the first stop bit. If a framing error is detected during the first stop bit the framing error flag will be set. The second stop bit is not checked for framing error. The RXNE flag will be set at the end of the first stop bit.

21.5.4 USART baud rate generation

The baud rate for the receiver and transmitter (Rx and Tx) are both set to the same value as programmed in the USART_BRR register.

Equation 1: Baud rate for standard USART (SPI mode included) (OVER8 = 0 or 1)

In case of oversampling by 16, the equation is:

In case of oversampling by 8, the equation is:

Equation 2: Baud rate in Smartcard, LIN and IrDA modes (OVER8 = 0)

In Smartcard, LIN and IrDA modes, only Oversampling by 16 is supported:

USARTDIV is an unsigned fixed point number that is coded on the USART_BRR register.

- • When OVER8 = 0, BRR = USARTDIV.

- • When OVER8 = 1

- – BRR[2:0] = USARTDIV[3:0] shifted 1 bit to the right.

- – BRR[3] must be kept cleared.

- – BRR[15:4] = USARTDIV[15:4]

Note: The baud counters are updated to the new value in the baud registers after a write operation to USART_BRR. Hence the baud rate register value should not be changed during communication.

In case of oversampling by 16 or 8, USARTDIV must be greater than or equal to 16d.

How to derive USARTDIV from USART_BRR register values

Example 1

To obtain 9600 baud with \( f_{CK} = 8 \) MHz.

- • In case of oversampling by 16:

USARTDIV = 8 000 000/9600

BRR = USARTDIV = 833d = 0341h - • In case of oversampling by 8:

USARTDIV = 2 * 8 000 000/9600

USARTDIV = 1666,66 (1667d = 683h)

BRR[3:0] = 3h >> 1 = 1h

BRR = 0x681

Example 2

To obtain 921.6 kbaud with \( f_{CK} = 32 \) MHz.

- • In case of oversampling by 16:

USARTDIV = 32 000 000/921 600

BRR = USARTDIV = 35d = 23h - • In case of oversampling by 8:

USARTDIV = 2 * 32 000 000/921 600

USARTDIV = 70d = 46h

BRR[3:0] = USARTDIV[3:0] >> 1 = 6h >> 1 = 3h

BRR = 0x43

| Baud rate | Oversampling by 16 (OVER8 = 0) | Oversampling by 8 (OVER8 = 1) | |||||

|---|---|---|---|---|---|---|---|

| S.No | Desired | Actual | BRR | % Error = (Calculated - Desired)B.Rate / Desired B.Rate | Actual | BRR | % Error |

| 1 | 2.4 kbaud | 2.4 kbaud | 0x3415 | 0 | 2.4 kbaud | 0x6825 | 0 |

| 2 | 9.6 kbaud | 9.6 kbaud | 0xD05 | 0 | 9.6 kbaud | 0x1A05 | 0 |

| 3 | 19.2 kbaud | 19.19 kbaud | 0x683 | 0.02 | 19.2 kbaud | 0xD02 | 0 |

| 4 | 38.4 kbaud | 38.41 kbaud | 0x341 | 0.04 | 38.39 kbaud | 0x681 | 0.02 |

| 5 | 57.6 kbaud | 57.55 kbaud | 0x22C | 0.08 | 57.6 kbaud | 0x453 | 0 |

| 6 | 115.2 kbaud | 115.1 kbaud | 0x116 | 0.08 | 115.11 kbaud | 0x226 | 0.08 |

| 7 | 230.4 kbaud | 230.21 kbaud | 0x8B | 0.08 | 230.21 kbaud | 0x113 | 0.08 |

| 8 | 460.8 kbaud | 463.76 kbaud | 0x045 | 0.64 | 460.06 kbaud | 0x85 | 0.08 |

| 9 | 921.6 kbaud | 914.28 kbaud | 0x23 | 0.79 | 927.5 kbaud | 0x42 | 0.79 |

| 10 | 2 Mbaud | 2 Mbaud | 0x10 | 0 | 2 Mbaud | 0x20 | 0 |

| 12 | 4Mbaud | 4Mbaud | NA | NA | 4Mbaud | 0x10 | 0 |

1. The lower the CPU clock the lower the accuracy for a particular baud rate. The upper limit of the achievable baud rate can be fixed with these data.

21.5.5 Tolerance of the USART receiver to clock deviation

The asynchronous receiver of the USART works correctly only if the total clock system deviation is less than the tolerance of the USART receiver. The causes which contribute to the total deviation are:

- • DTRA: Deviation due to the transmitter error (which also includes the deviation of the transmitter's local oscillator)

- • DQUANT: Error due to the baud rate quantization of the receiver

- • DREC: Deviation of the receiver's local oscillator

- • DTCL: Deviation due to the transmission line (generally due to the transceivers which can introduce an asymmetry between the low-to-high transition timing and the high-to-low transition timing)

where

DWU is the error due to sampling point deviation when the wakeup from Stop mode is used.

when M[1:0] = 01:

when M[1:0] = 00:

when M[1:0] = 10:

\( t_{\text{WUUSART}} \) is the time between:

- – The detection of start bit falling edge

- – The instant when clock (requested by the peripheral) is ready and reaching the peripheral and regulator is ready.

\( t_{\text{WUUSART}} \) corresponds to \( t_{\text{WUSTOP}} \) value provided in the datasheet.

The USART receiver can receive data correctly at up to the maximum tolerated deviation specified in Table 105 and Table 106 depending on the following choices:

- • 9-, 10- or 11-bit character length defined by the M bits in the USART_CR1 register

- • Oversampling by 8 or 16 defined by the OVER8 bit in the USART_CR1 register

- • Bits BRR[3:0] of USART_BRR register are equal to or different from 0000.

- • Use of 1 bit or 3 bits to sample the data, depending on the value of the ONEBIT bit in the USART_CR3 register.

Table 105. Tolerance of the USART receiver when BRR [3:0] = 0000

| M bits | OVER8 bit = 0 | OVER8 bit = 1 | ||

|---|---|---|---|---|

| ONEBIT=0 | ONEBIT=1 | ONEBIT=0 | ONEBIT=1 | |

| 00 | 3.75% | 4.375% | 2.50% | 3.75% |

| 01 | 3.41% | 3.97% | 2.27% | 3.41% |

| 10 | 4.16% | 4.86% | 2.77% | 4.16% |

Table 106. Tolerance of the USART receiver when BRR [3:0] is different from 0000

| M bits | OVER8 bit = 0 | OVER8 bit = 1 | ||

|---|---|---|---|---|

| ONEBIT=0 | ONEBIT=1 | ONEBIT=0 | ONEBIT=1 | |

| 00 | 3.33% | 3.88% | 2% | 3% |

| 01 | 3.03% | 3.53% | 1.82% | 2.73% |

| 10 | 3.7% | 4.31% | 2.22% | 3.33% |

Note: The data specified in Table 105 and Table 106 may slightly differ in the special case when the received frames contain some Idle frames of exactly 10-bit durations when M bits = 00 (11-bit durations when M bits = 01 or 9- bit durations when M bits = 10).

21.5.6 USART auto baud rate detection

The USART is able to detect and automatically set the USART_BRR register value based on the reception of one character. Automatic baud rate detection is useful under two circumstances:

- • The communication speed of the system is not known in advance

- • The system is using a relatively low accuracy clock source and this mechanism allows the correct baud rate to be obtained without measuring the clock deviation.

The clock source frequency must be compatible with the expected communication speed (when oversampling by 16, the baud rate is between \( f_{CK}/65535 \) and \( f_{CK}/16 \) . when oversampling by 8, the baud rate is between \( f_{CK}/65535 \) and \( f_{CK}/8 \) ).

Before activating the auto baud rate detection, the auto baud rate detection mode must be chosen. There are various modes based on different character patterns.

They can be chosen through the ABRMOD[1:0] field in the USART_CR2 register. In these auto baud rate modes, the baud rate is measured several times during the synchronization data reception and each measurement is compared to the previous one.

These modes are:

- • Mode 0: Any character starting with a bit at 1. In this case the USART measures the duration of the Start bit (falling edge to rising edge).

- • Mode 1: Any character starting with a 10xx bit pattern. In this case, the USART measures the duration of the Start and of the 1st data bit. The measurement is done falling edge to falling edge, ensuring better accuracy in the case of slow signal slopes.

- • Mode 2: A 0x7F character frame (it may be a 0x7F character in LSB first mode or a 0xFE in MSB first mode). In this case, the baud rate is updated first at the end of the start bit (BRs), then at the end of bit 6 (based on the measurement done from falling edge to falling edge: BR6). Bit 0 to bit 6 are sampled at BRs while further bits of the character are sampled at BR6.

- • Mode 3: A 0x55 character frame. In this case, the baud rate is updated first at the end of the start bit (BRs), then at the end of bit 0 (based on the measurement done from falling edge to falling edge: BR0), and finally at the end of bit 6 (BR6). Bit 0 is sampled at BRs, bit 1 to bit 6 are sampled at BR0, and further bits of the character are sampled at BR6.

In parallel, another check is performed for each intermediate transition of RX line. An error is generated if the transitions on RX are not sufficiently synchronized with the receiver (the receiver being based on the baud rate calculated on bit 0).

Prior to activating auto baud rate detection, the USART_BRR register must be initialized by writing a non-zero baud rate value.

The automatic baud rate detection is activated by setting the ABREN bit in the USART_CR2 register. The USART will then wait for the first character on the RX line. The auto baud rate operation completion is indicated by the setting of the ABRF flag in the USART_ISR register. If the line is noisy, the correct baud rate detection cannot be guaranteed. In this case the BRR value may be corrupted and the ABRE error flag will be set. This also happens if the communication speed is not compatible with the automatic baud rate

detection range (bit duration not between 16 and 65536 clock periods (oversampling by 16) and not between 8 and 65536 clock periods (oversampling by 8)).

The RXNE interrupt will signal the end of the operation.

At any later time, the auto baud rate detection may be relaunched by resetting the ABRF flag (by writing a 0).

Note: If the USART is disabled (UE=0) during an auto baud rate operation, the BRR value may be corrupted.

21.5.7 Multiprocessor communication using USART

In multiprocessor communication, the following bits are to be kept cleared:

- • LINEN bit in the USART_CR2 register,

- • HDSEL, IREN and SCEN bits in the USART_CR3 register.

It is possible to perform multiprocessor communication with the USART (with several USARTs connected in a network). For instance one of the USARTs can be the master, its TX output connected to the RX inputs of the other USARTs. The others are slaves, their respective TX outputs are logically ANDed together and connected to the RX input of the master.

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant USART service overhead for all non addressed receivers.

The non addressed devices may be placed in mute mode by means of the muting function. In order to use the mute mode feature, the MME bit must be set in the USART_CR1 register.

In mute mode:

- • None of the reception status bits can be set.

- • All the receive interrupts are inhibited.

- • The RWU bit in USART_ISR register is set to 1. RWU can be controlled automatically by hardware or by software, through the MMRQ bit in the USART_RQR register, under certain conditions.

The USART can enter or exit from mute mode using one of two methods, depending on the WAKE bit in the USART_CR1 register:

- • Idle Line detection if the WAKE bit is reset,

- • Address Mark detection if the WAKE bit is set.

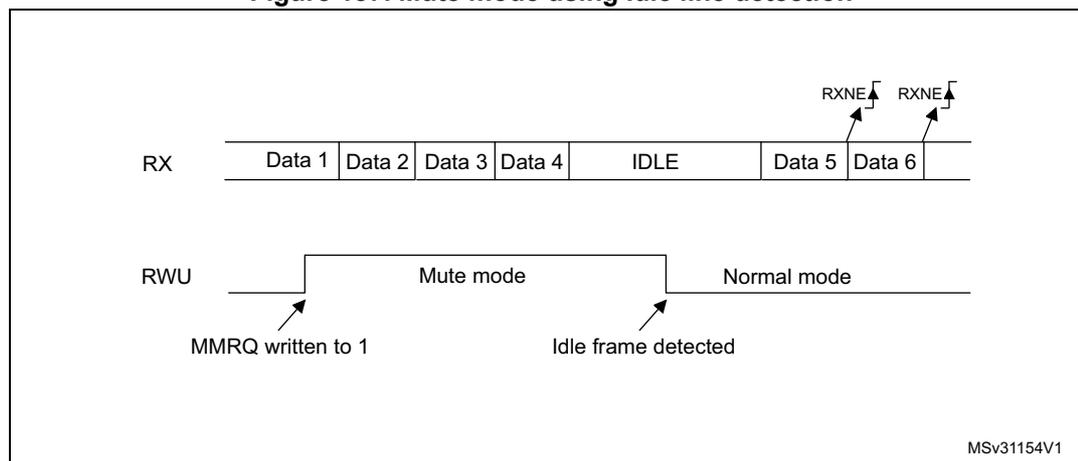

Idle line detection (WAKE=0)

The USART enters mute mode when the MMRQ bit is written to 1 and the RWU is automatically set.

It wakes up when an Idle frame is detected. Then the RWU bit is cleared by hardware but the IDLE bit is not set in the USART_ISR register. An example of mute mode behavior using Idle line detection is given in Figure 187 .

Figure 187. Mute mode using Idle line detection

The diagram illustrates the relationship between the RX (Receive) signal and the RWU (Receive Wakeup) signal during Idle line detection. The RX signal shows a sequence of data frames: Data 1, Data 2, Data 3, Data 4, followed by an IDLE state, then Data 5, and Data 6. The RWU signal is initially low. When the MMRQ bit is written to 1, the RWU signal goes high, entering 'Mute mode'. The RWU signal returns to low ('Normal mode') when an Idle frame is detected. RXNE (Receive Not Empty) flags are indicated by arrows pointing to the start of Data 5 and Data 6.

Note: If the MMRQ is set while the IDLE character has already elapsed, mute mode will not be entered (RWU is not set).

If the USART is activated while the line is IDLE, the idle state is detected after the duration of one IDLE frame (not only after the reception of one character frame).

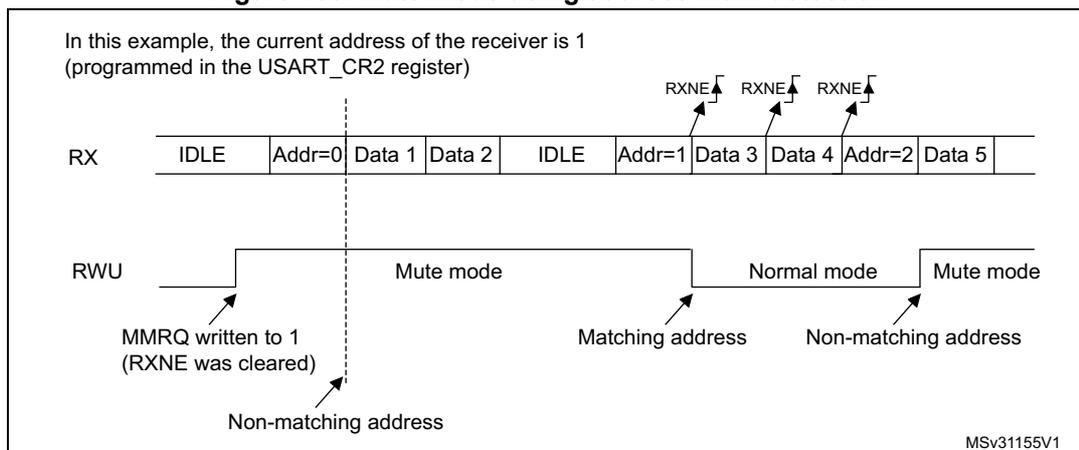

4-bit/7-bit address mark detection (WAKE=1)

In this mode, bytes are recognized as addresses if their MSB is a '1' otherwise they are considered as data. In an address byte, the address of the targeted receiver is put in the 4 or 7 LSBs. The choice of 7 or 4-bit address detection is done using the ADDM7 bit. This 4-bit/7-bit word is compared by the receiver with its own address which is programmed in the ADD bits in the USART_CR2 register.

Note: In 7-bit and 9-bit data modes, address detection is done on 6-bit and 8-bit addresses (ADD[5:0] and ADD[7:0]) respectively.

The USART enters mute mode when an address character is received which does not match its programmed address. In this case, the RWU bit is set by hardware. The RXNE flag is not set for this address byte and no interrupt or DMA request is issued when the USART enters mute mode.

The USART also enters mute mode when the MMRQ bit is written to 1. The RWU bit is also automatically set in this case.

The USART exits from mute mode when an address character is received which matches the programmed address. Then the RWU bit is cleared and subsequent bytes are received normally. The RXNE bit is set for the address character since the RWU bit has been cleared.

An example of mute mode behavior using address mark detection is given in Figure 188 .

Figure 188. Mute mode using address mark detection

In this example, the current address of the receiver is 1 (programmed in the USART_CR2 register)

The diagram illustrates the RX and RWU signals during mute mode using address mark detection. The RX signal shows a sequence of IDLE, Addr=0, Data 1, Data 2, IDLE, Addr=1, Data 3, Data 4, Addr=2, Data 5. The RWU signal shows transitions between Mute mode and Normal mode based on address matching. Address 0 is a non-matching address, Addr=1 is a matching address, and Addr=2 is a non-matching address. RXNE flags are shown for the matching address.

MSV31155V1

21.5.8 Modbus communication using USART

The USART offers basic support for the implementation of Modbus/RTU and Modbus/ASCII protocols. Modbus/RTU is a half duplex, block transfer protocol. The control part of the protocol (address recognition, block integrity control and command interpretation) must be implemented in software.

The USART offers basic support for the end of the block detection, without software overhead or other resources.

Modbus/RTU

In this mode, the end of one block is recognized by a “silence” (idle line) for more than 2 character times. This function is implemented through the programmable timeout function.

The timeout function and interrupt must be activated, through the RTOEN bit in the USART_CR2 register and the RTOIE in the USART_CR1 register. The value corresponding to a timeout of 2 character times (for example 22 x bit duration) must be programmed in the RTO register. When the receive line is idle for this duration, after the last stop bit is received, an interrupt is generated, informing the software that the current block reception is completed.

Modbus/ASCII

In this mode, the end of a block is recognized by a specific (CR/LF) character sequence. The USART manages this mechanism using the character match function.

By programming the LF ASCII code in the ADD[7:0] field and by activating the character match interrupt (CMIE=1), the software is informed when a LF has been received and can check the CR/LF in the DMA buffer.

21.5.9 USART parity control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the USART_CR1 register. Depending on the frame length defined by the M bits, the possible USART frame formats are as listed in Table 107 .

Table 107. Frame formats

| M bits | PCE bit | USART frame (1) |

|---|---|---|

| 00 | 0 | | SB | 8-bit data | STB | |

| 00 | 1 | | SB | 7-bit data | PB | STB | |

| 01 | 0 | | SB | 9-bit data | STB | |

| 01 | 1 | | SB | 8-bit data | PB | STB | |

| 10 | 0 | | SB | 7-bit data | STB | |

| 10 | 1 | | SB | 6-bit data | PB | STB | |

1. Legends: SB: start bit, STB: stop bit, PB: parity bit. In the data register, the PB is always taking the MSB position (9th, 8th or 7th, depending on the M bits value).

Even parity

The parity bit is calculated to obtain an even number of “1s” inside the frame of the 6, 7 or 8 LSB bits (depending on M bits values) and the parity bit.

As an example, if data=00110101, and 4 bits are set, then the parity bit will be 0 if even parity is selected (PS bit in USART_CR1 = 0).

Odd parity

The parity bit is calculated to obtain an odd number of “1s” inside the frame made of the 6, 7 or 8 LSB bits (depending on M bits values) and the parity bit.

As an example, if data=00110101 and 4 bits set, then the parity bit will be 1 if odd parity is selected (PS bit in USART_CR1 = 1).

Parity checking in reception

If the parity check fails, the PE flag is set in the USART_ISR register and an interrupt is generated if PEIE is set in the USART_CR1 register. The PE flag is cleared by software writing 1 to the PECF in the USART_ICR register.

Parity generation in transmission

If the PCE bit is set in USART_CR1, then the MSB bit of the data written in the data register is transmitted but is changed by the parity bit (even number of “1s” if even parity is selected (PS=0) or an odd number of “1s” if odd parity is selected (PS=1)).

21.5.10 USART LIN (local interconnection network) mode

This section is relevant only when LIN mode is supported. Please refer to Section 21.4: USART implementation on page 575 .

The LIN mode is selected by setting the LINEN bit in the USART_CR2 register. In LIN mode, the following bits must be kept cleared:

- • STOP[1:0] and CLKEN in the USART_CR2 register,

- • SCEN, HDSEL and IREN in the USART_CR3 register.

For code example, refer to A.15.6: USART LIN mode code example .

LIN transmission

The procedure explained in Section 21.5.2: USART transmitter has to be applied for LIN Master transmission. It must be the same as for normal USART transmission with the following differences:

- • Clear the M bits to configure 8-bit word length.

- • Set the LINEN bit to enter LIN mode. In this case, setting the SBKRQ bit sends 13 '0' bits as a break character. Then 2 bits of value '1' are sent to allow the next start detection.

LIN reception

When LIN mode is enabled, the break detection circuit is activated. The detection is totally independent from the normal USART receiver. A break can be detected whenever it occurs, during Idle state or during a frame.

When the receiver is enabled (RE=1 in USART_CR1), the circuit looks at the RX input for a start signal. The method for detecting start bits is the same when searching break characters or data. After a start bit has been detected, the circuit samples the next bits exactly like for the data (on the 8th, 9th and 10th samples). If 10 (when the LBDL = 0 in USART_CR2) or 11 (when LBDL=1 in USART_CR2) consecutive bits are detected as '0', and are followed by a delimiter character, the LBDF flag is set in USART_ISR. If the LBDIE bit=1, an interrupt is generated. Before validating the break, the delimiter is checked for as it signifies that the RX line has returned to a high level.

If a '1' is sampled before the 10 or 11 have occurred, the break detection circuit cancels the current detection and searches for a start bit again.

If the LIN mode is disabled (LINEN=0), the receiver continues working as normal USART, without taking into account the break detection.

If the LIN mode is enabled (LINEN=1), as soon as a framing error occurs (i.e. stop bit detected at '0', which will be the case for any break frame), the receiver stops until the break detection circuit receives either a '1', if the break word was not complete, or a delimiter character if a break has been detected.

The behavior of the break detector state machine and the break flag is shown on the Figure 189: Break detection in LIN mode (11-bit break length - LBDL bit is set) on page 598 .

Examples of break frames are given on Figure 190: Break detection in LIN mode vs. Framing error detection on page 599 .

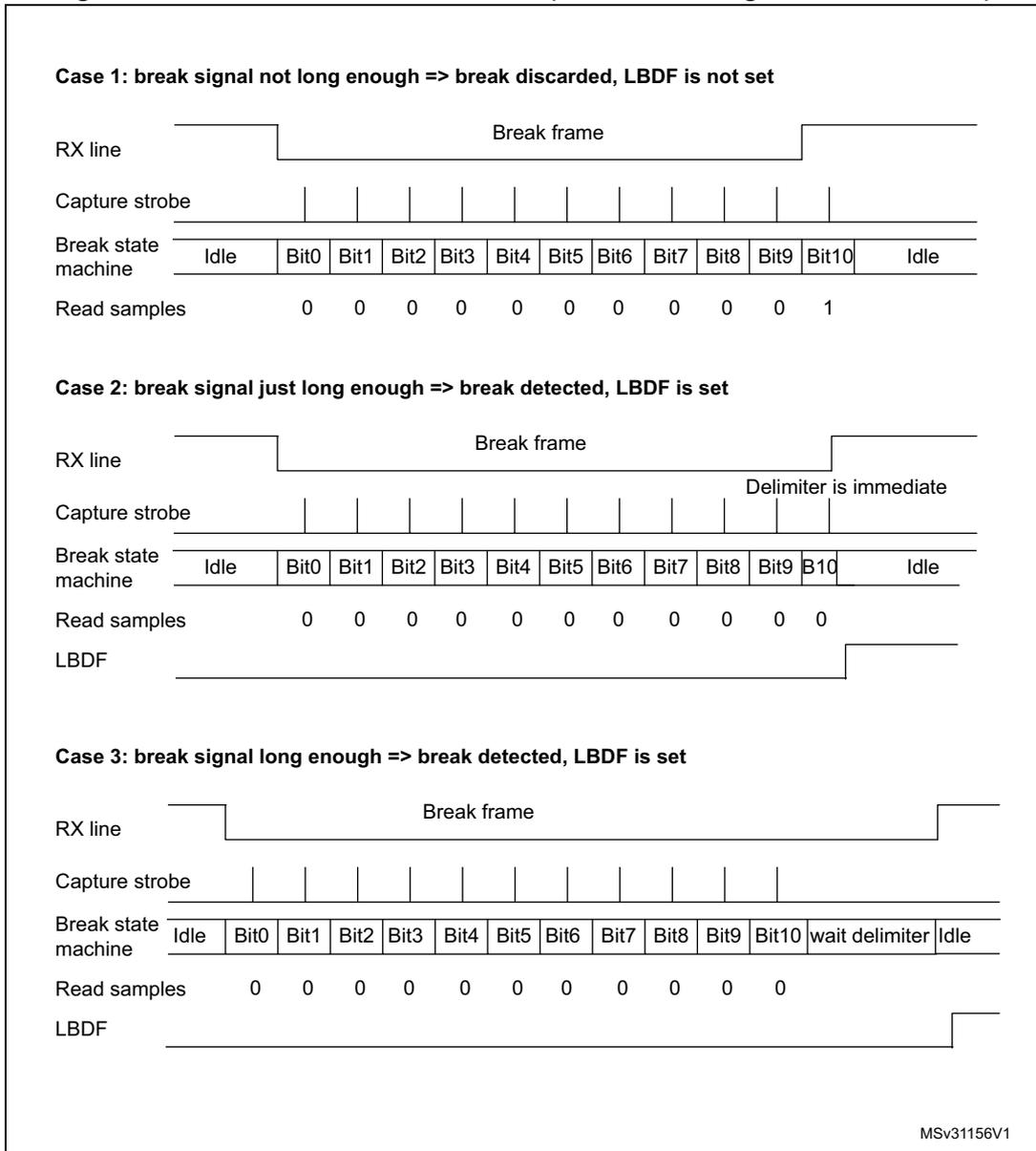

Figure 189. Break detection in LIN mode (11-bit break length - LBDL bit is set)

Case 1: break signal not long enough => break discarded, LBDF is not set

| RX line | Break frame | ||||||||||||

| Capture strobe | |||||||||||||

| Break state machine | Idle | Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 | Bit7 | Bit8 | Bit9 | Bit10 | Idle |

| Read samples | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | ||

Case 2: break signal just long enough => break detected, LBDF is set

| RX line | Break frame | ||||||||||||

| Capture strobe | |||||||||||||

| Break state machine | Idle | Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 | Bit7 | Bit8 | Bit9 | Bit10 | Idle |

| Read samples | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| LBDF | Delimiter is immediate | ||||||||||||

Case 3: break signal long enough => break detected, LBDF is set

| RX line | Break frame | |||||||||||||

| Capture strobe | ||||||||||||||

| Break state machine | Idle | Bit0 | Bit1 | Bit2 | Bit3 | Bit4 | Bit5 | Bit6 | Bit7 | Bit8 | Bit9 | Bit10 | wait delimiter | Idle |

| Read samples | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||

| LBDF | ||||||||||||||

MSv31156V1

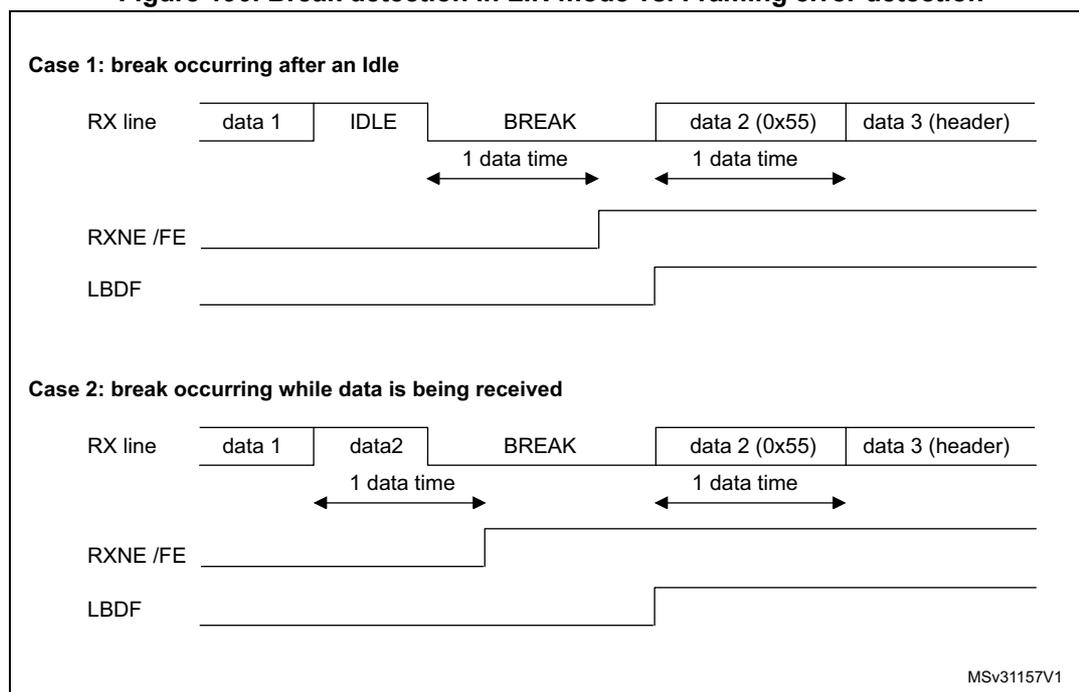

Figure 190. Break detection in LIN mode vs. Framing error detection

Case 1: break occurring after an Idle

The diagram shows the RX line transitioning from 'data 1' to 'IDLE', then to 'BREAK', then to 'data 2 (0x55)', and finally to 'data 3 (header)'. The 'BREAK' duration is marked as '1 data time'. The RXNE/FE signal goes high at the start of the 'BREAK' and stays high until the start of 'data 2 (0x55)'. The LBDF signal goes high at the start of the 'BREAK' and stays high until the start of 'data 2 (0x55)'.

Case 2: break occurring while data is being received

The diagram shows the RX line transitioning from 'data 1' to 'data2', then to 'BREAK', then to 'data 2 (0x55)', and finally to 'data 3 (header)'. The 'BREAK' duration is marked as '1 data time'. The RXNE/FE signal goes high at the start of the 'BREAK' and stays high until the start of 'data 2 (0x55)'. The LBDF signal goes high at the start of the 'BREAK' and stays high until the start of 'data 2 (0x55)'.

MSv31157V1

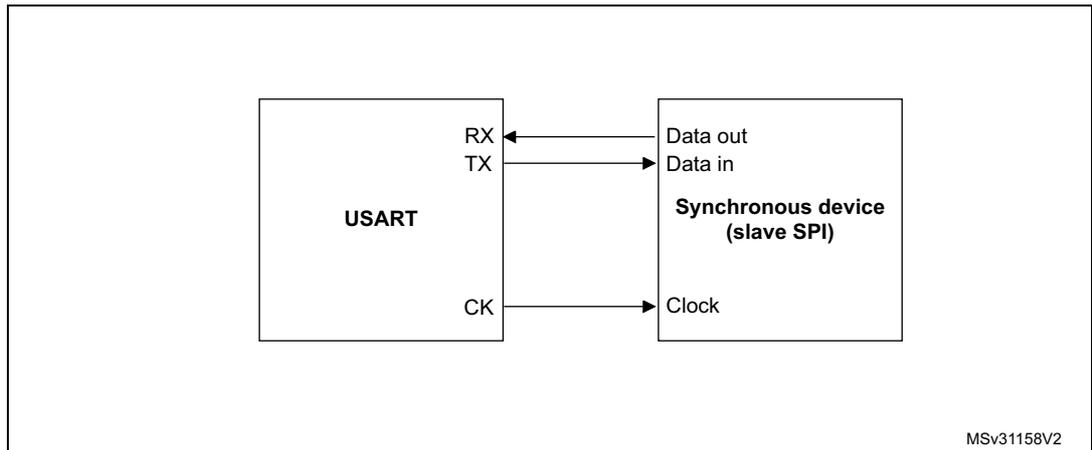

21.5.11 USART synchronous mode

The synchronous mode is selected by writing the CLKEN bit in the USART_CR2 register to 1. In synchronous mode, the following bits must be kept cleared:

- • LINEN bit in the USART_CR2 register,

- • SCEN, HDSEL and IREN bits in the USART_CR3 register.

In this mode, the USART can be used to control bidirectional synchronous serial communications in master mode. The CK pin is the output of the USART transmitter clock. No clock pulses are sent to the CK pin during start bit and stop bit. Depending on the state of the LBCL bit in the USART_CR2 register, clock pulses are, or are not, generated during the last valid data bit (address mark). The CPOL bit in the USART_CR2 register is used to select the clock polarity, and the CPHA bit in the USART_CR2 register is used to select the phase of the external clock (see Figure 191 , Figure 192 and Figure 193 ).

During the Idle state, preamble and send break, the external CK clock is not activated.

In synchronous mode the USART transmitter works exactly like in asynchronous mode. But as CK is synchronized with TX (according to CPOL and CPHA), the data on TX is synchronous.

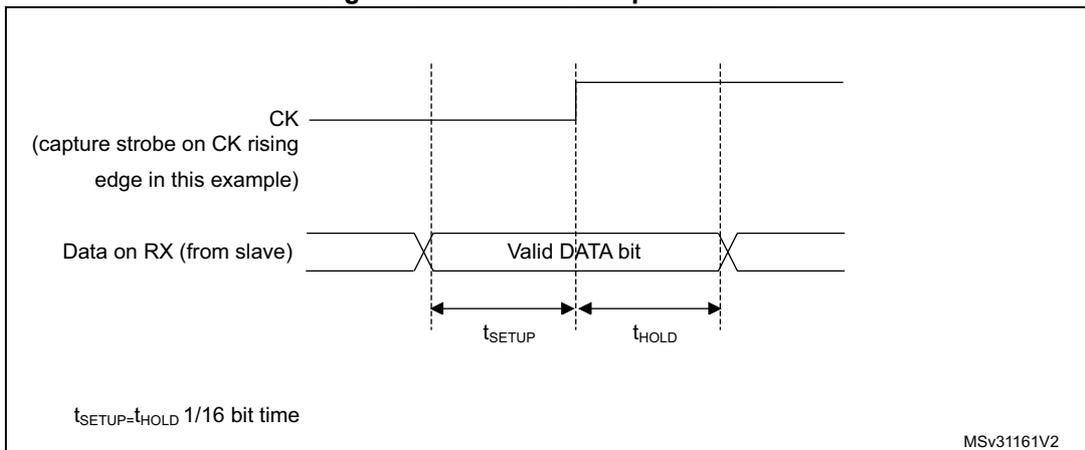

In this mode the USART receiver works in a different manner compared to the asynchronous mode. If RE=1, the data is sampled on CK (rising or falling edge, depending on CPOL and CPHA), without any oversampling. A setup and a hold time must be respected (which depends on the baud rate: 1/16 bit duration).

Note: The CK pin works in conjunction with the TX pin. Thus, the clock is provided only if the transmitter is enabled (TE=1) and data is being transmitted (the data register USART_TDR written). This means that it is not possible to receive synchronous data without transmitting data.

The LBCL, CPOL and CPHA bits have to be selected when the USART is disabled (UE=0) to ensure that the clock pulses function correctly.

For code example, refer to A.15.7: USART synchronous mode code example .

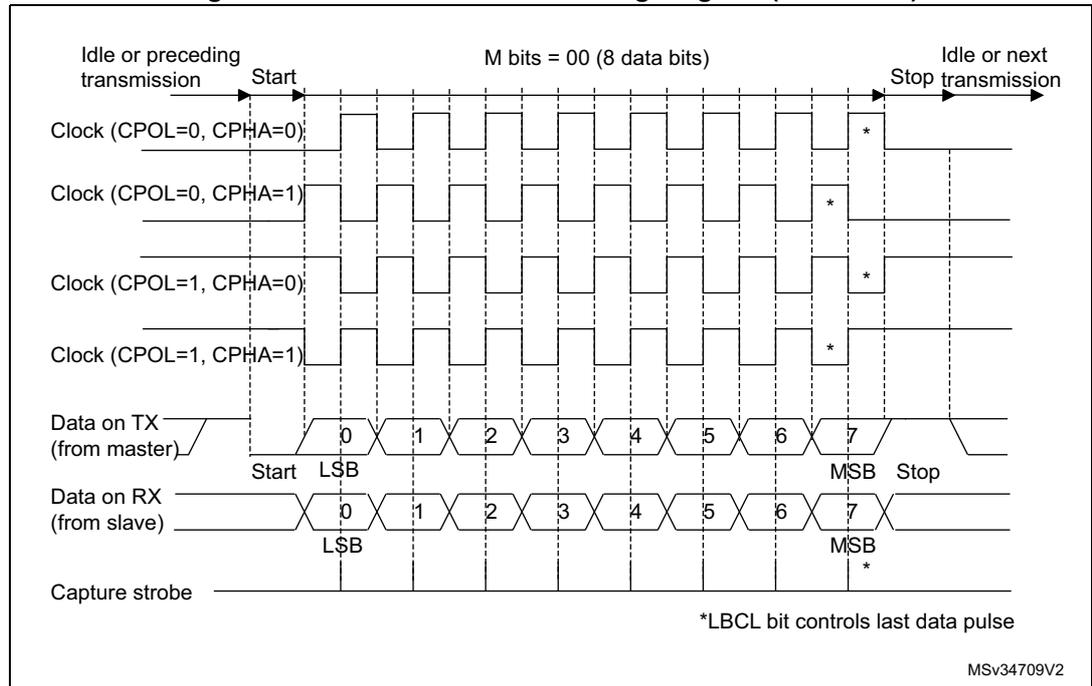

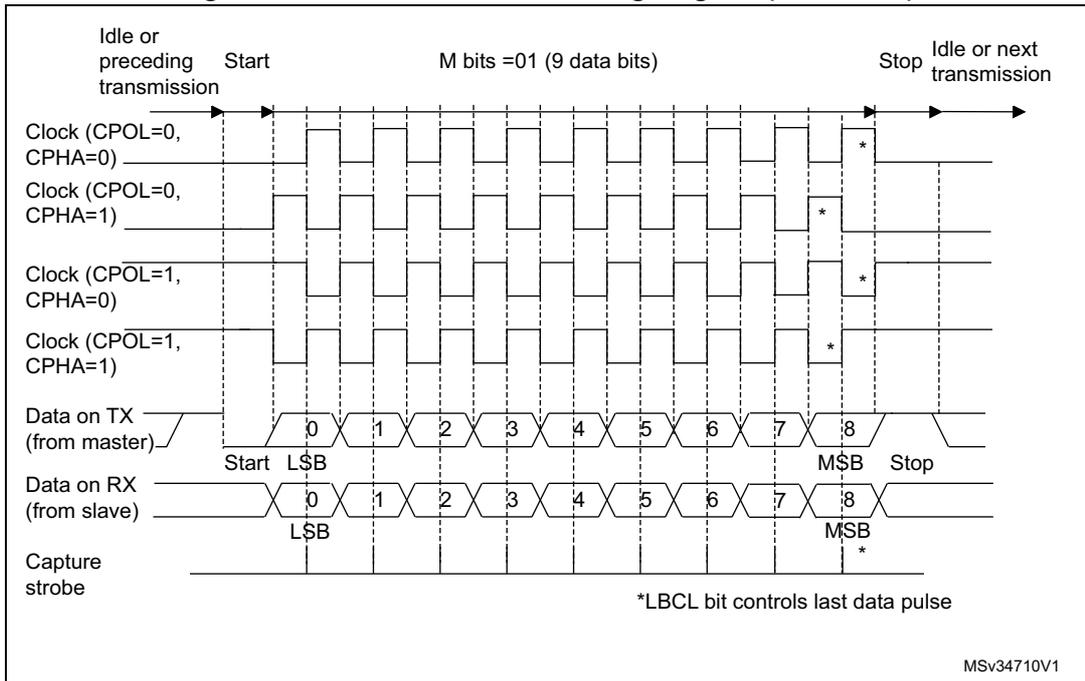

Figure 191. USART example of synchronous transmission

Figure 192. USART data clock timing diagram (M bits = 00)

Figure 193. USART data clock timing diagram (M bits = 01)

This timing diagram shows the relationship between the clock (CK) and data lines (TX and RX) for a 9-bit transmission. It illustrates four clock configurations based on CPOL (Clock Polarity) and CPHA (Clock Phase):

- Clock (CPOL=0, CPHA=0)

- Clock (CPOL=0, CPHA=1)

- Clock (CPOL=1, CPHA=0)

- Clock (CPOL=1, CPHA=1)

The sequence starts with an 'Idle or preceding transmission', followed by a 'Start' bit, then 9 data bits (0 to 8), and ends with a 'Stop' bit before returning to 'Idle or next transmission'. Bit 0 is labeled LSB and bit 8 is labeled MSB. A 'Capture strobe' line indicates sampling points. An asterisk (*) indicates that the LBCL bit controls the last data pulse. MSv34710V1

Figure 194. RX data setup/hold time

This diagram defines the timing requirements for receiving data. It shows the CK (capture strobe on CK rising edge in this example) and the 'Data on RX (from slave)'. The 'Valid DATA bit' must be stable for a duration of t

SETUP

before the clock edge and t

HOLD

after the clock edge.

\(

t_{SETUP} = t_{HOLD} = 1/16 \text{ bit time}

\)

MSv31161V2

Note: The function of CK is different in Smartcard mode. Refer to Section 21.5.13: USART Smartcard mode for more details.

21.5.12 USART Single-wire Half-duplex communication

Single-wire Half-duplex mode is selected by setting the HDSEL bit in the USART_CR3 register. In this mode, the following bits must be kept cleared:

- • LINEN and CLKEN bits in the USART_CR2 register,

- • SCEN and IREN bits in the USART_CR3 register.

The USART can be configured to follow a Single-wire Half-duplex protocol where the TX and RX lines are internally connected. The selection between half- and Full-duplex communication is made with a control bit HDSEL in USART_CR3.

As soon as HDSEL is written to 1:

- • The TX and RX lines are internally connected

- • The RX pin is no longer used

- • The TX pin is always released when no data is transmitted. Thus, it acts as a standard I/O in idle or in reception. It means that the I/O must be configured so that TX is configured as alternate function open-drain with an external pull-up.

Apart from this, the communication protocol is similar to normal USART mode. Any conflicts on the line must be managed by software (by the use of a centralized arbiter, for instance). In particular, the transmission is never blocked by hardware and continues as soon as data is written in the data register while the TE bit is set.

For code example, refer to A.15.8: USART single-wire half-duplex code example .

21.5.13 USART Smartcard mode

This section is relevant only when Smartcard mode is supported. Please refer to Section 21.4: USART implementation on page 575 .

Smartcard mode is selected by setting the SCEN bit in the USART_CR3 register. In Smartcard mode, the following bits must be kept cleared:

- • LINEN bit in the USART_CR2 register,

- • HDSEL and IREN bits in the USART_CR3 register.

Moreover, the CLKEN bit may be set in order to provide a clock to the smartcard.

The smartcard interface is designed to support asynchronous protocol for smartcards as defined in the ISO 7816-3 standard. Both T=0 (character mode) and T=1 (block mode) are supported.

The USART should be configured as:

- • 8 bits plus parity: where word length is set to 8 bits and PCE=1 in the USART_CR1 register

- • 1.5 stop bits when transmitting and receiving data: where STOP=11 in the USART_CR2 register. It is also possible to choose 0.5 stop bit for receiving.

For code example, refer to A.15.9: USART smartcard mode code example .

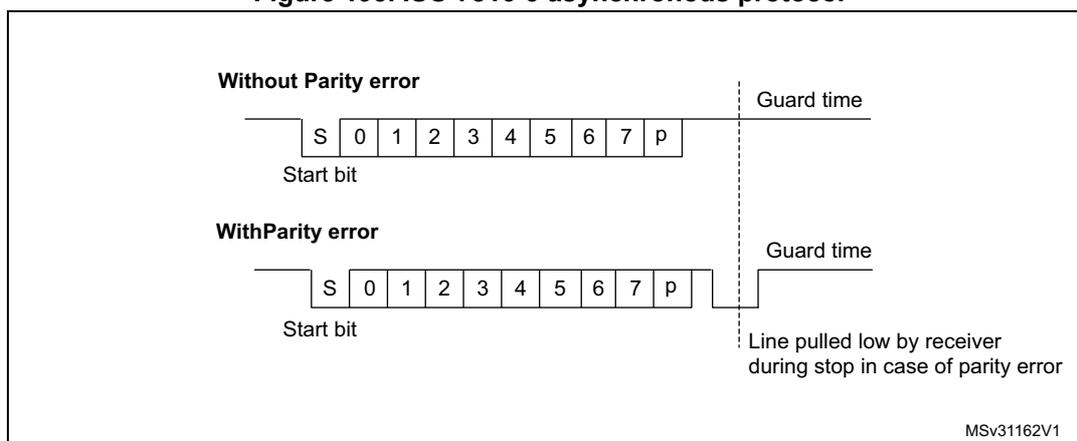

In T=0 (character) mode, the parity error is indicated at the end of each character during the guard time period.

Figure 195 shows examples of what can be seen on the data line with and without parity error.

Figure 195. ISO 7816-3 asynchronous protocol

The diagram illustrates two scenarios for character transmission according to the ISO 7816-3 asynchronous protocol. Both scenarios show a sequence of bits: a start bit 'S', data bits '0' through '7', and a parity bit 'p'. In the 'Without Parity error' scenario, the transmission ends with a 'Guard time'. In the 'With Parity error' scenario, the parity bit 'p' is followed by a 'Line pulled low by receiver during stop in case of parity error', which is then followed by a 'Guard time'. The diagram is labeled MSv31162V1.

When connected to a smartcard, the TX output of the USART drives a bidirectional line that is also driven by the smartcard. The TX pin must be configured as open drain.

Smartcard mode implements a single wire half duplex communication protocol.

- • Transmission of data from the transmit shift register is guaranteed to be delayed by a minimum of 1/2 baud clock. In normal operation a full transmit shift register starts shifting on the next baud clock edge. In Smartcard mode this transmission is further delayed by a guaranteed 1/2 baud clock.

- • In transmission, if the smartcard detects a parity error, it signals this condition to the USART by driving the line low (NACK). This NACK signal (pulling transmit line low for 1 baud clock) causes a framing error on the transmitter side (configured with 1.5 stop bits). The USART can handle automatic re-sending of data according to the protocol. The number of retries is programmed in the SCARCNT bit field. If the USART continues receiving the NACK after the programmed number of retries, it stops transmitting and signals the error as a framing error. The TXE bit can be set using the TXFRQ bit in the USART_RQR register.

- • Smartcard auto-retry in transmission: a delay of 2.5 baud periods is inserted between the NACK detection by the USART and the start bit of the repeated character. The TC bit is set immediately at the end of reception of the last repeated character (no guard-time). If the software wants to repeat it again, it must insure the minimum 2 baud periods required by the standard.

- • If a parity error is detected during reception of a frame programmed with a 1.5 stop bits period, the transmit line is pulled low for a baud clock period after the completion of the receive frame. This is to indicate to the smartcard that the data transmitted to the USART has not been correctly received. A parity error is NACKed by the receiver if the NACK control bit is set, otherwise a NACK is not transmitted (to be used in T=1 mode). If the received character is erroneous, the RXNE/receive DMA request is not activated. According to the protocol specification, the smartcard must resend the same character. If the received character is still erroneous after the maximum number of retries specified in the SCARCNT bit field, the USART stops transmitting the NACK and signals the error as a parity error.

- • Smartcard auto-retry in reception: the BUSY flag remains set if the USART NACKs the card but the card doesn't repeat the character.

- • In transmission, the USART inserts the Guard Time (as programmed in the Guard Time register) between two successive characters. As the Guard Time is measured after the stop bit of the previous character, the GT[7:0] register must be programmed to the desired CGT (Character Guard Time, as defined by the 7816-3 specification) minus 12 (the duration of one character).

- • The assertion of the TC flag can be delayed by programming the Guard Time register. In normal operation, TC is asserted when the transmit shift register is empty and no further transmit requests are outstanding. In Smartcard mode an empty transmit shift register triggers the Guard Time counter to count up to the programmed value in the Guard Time register. TC is forced low during this time. When the Guard Time counter reaches the programmed value TC is asserted high.

- • The TCBGT flag can be used to detect the end of data transfer without waiting for guard time completion. This flag is set just after the end of frame transmission and if no NACK has been received from the card.

- • The de-assertion of TC flag is unaffected by Smartcard mode.

- • If a framing error is detected on the transmitter end (due to a NACK from the receiver), the NACK is not detected as a start bit by the receive block of the transmitter. According to the ISO protocol, the duration of the received NACK can be 1 or 2 baud clock periods.

- • On the receiver side, if a parity error is detected and a NACK is transmitted the receiver does not detect the NACK as a start bit.

Note: A break character is not significant in Smartcard mode. A 0x00 data with a framing error is treated as data and not as a break.

No Idle frame is transmitted when toggling the TE bit. The Idle frame (as defined for the other configurations) is not defined by the ISO protocol.

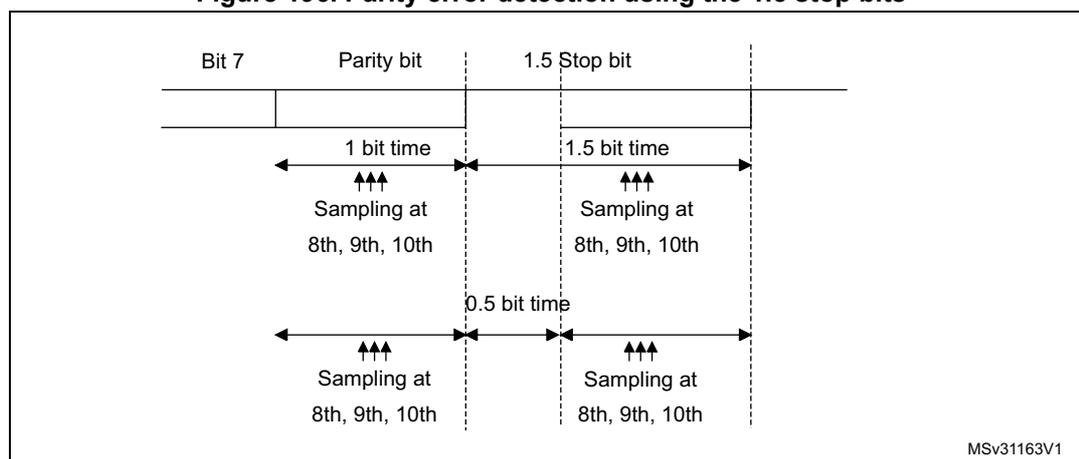

Figure 196 details how the NACK signal is sampled by the USART. In this example the USART is transmitting data and is configured with 1.5 stop bits. The receiver part of the USART is enabled in order to check the integrity of the data and the NACK signal.

Figure 196. Parity error detection using the 1.5 stop bits

The diagram illustrates the timing for parity error detection with 1.5 stop bits. It shows two rows of bit transmission. The top row shows Bit 7, Parity bit, and 1.5 Stop bit. The bottom row shows the same bits. Sampling points are indicated by arrows at the 8th, 9th, and 10th bit times. The 1.5 stop bit duration is shown as 1.5 bit time. The diagram is labeled MSv31163V1.

The USART can provide a clock to the smartcard through the CK output. In Smartcard mode, CK is not associated to the communication but is simply derived from the internal peripheral input clock through a 5-bit prescaler. The division ratio is configured in the prescaler register USART_GTPR. CK frequency can be programmed from \( f_{CK}/2 \) to \( f_{CK}/62 \) , where \( f_{CK} \) is the peripheral input clock.

Block mode (T=1)

In T=1 (block) mode, the parity error transmission is deactivated, by clearing the NACK bit in the USART_CR3 register.

When requesting a read from the smartcard, in block mode, the software must enable the receiver Timeout feature by setting the RTOEN bit in the USART_CR2 register and program the RTO bits field in the RTOR register to the BWT (block wait time) - 11 value. If no answer is received from the card before the expiration of this period, the RTOF flag will be set and a timeout interrupt will be generated (if RTOIE bit in the USART_CR1 register is set). If the first character is received before the expiration of the period, it is signaled by the RXNE interrupt.

Note: The RXNE interrupt must be enabled even when using the USART in DMA mode to read from the smartcard in block mode. In parallel, the DMA must be enabled only after the first received byte.

After the reception of the first character (RXNE interrupt), the RTO bit fields in the RTOR register must be programmed to the CWT (character wait time) - 11 value, in order to allow the automatic check of the maximum wait time between two consecutive characters. This time is expressed in baudtime units. If the smartcard does not send a new character in less than the CWT period after the end of the previous character, the USART signals this to the software through the RTOF flag and interrupt (when RTOIE bit is set).

Note: The RTO counter starts counting:

- - From the end of the stop bit in case STOP = 00.

- - From the end of the second stop bit in case of STOP = 10.

- - 1 bit duration after the beginning of the STOP bit in case STOP = 11.

- - From the beginning of the STOP bit in case STOP = 01.

As in the Smartcard protocol definition, the BWT/CWT values are defined from the beginning (start bit) of the last character. The RTO register must be programmed to BWT - 11 or CWT - 11, respectively, taking into account the length of the last character itself.

A block length counter is used to count all the characters received by the USART. This counter is reset when the USART is transmitting (TXE=0). The length of the block is communicated by the smartcard in the third byte of the block (prologue field). This value must be programmed to the BLEN field in the USART_RTOR register. When using DMA mode, before the start of the block, this register field must be programmed to the minimum value (0x0). With this value, an interrupt is generated after the 4th received character. The software must read the LEN field (third byte), its value must be read from the receive buffer.

In interrupt driven receive mode, the length of the block may be checked by software or by programming the BLEN value. However, before the start of the block, the maximum value of BLEN (0xFF) may be programmed. The real value will be programmed after the reception of the third character.

If the block is using the LRC longitudinal redundancy check (1 epilogue byte), the BLEN=LEN. If the block is using the CRC mechanism (2 epilogue bytes), BLEN=LEN+1 must be programmed. The total block length (including prologue, epilogue and information fields) equals BLEN+4. The end of the block is signaled to the software through the EOBF flag and interrupt (when EOBIE bit is set).

In case of an error in the block length, the end of the block is signaled by the RTO interrupt (Character wait Time overflow).

Note: The error checking code (LRC/CRC) must be computed/verified by software.

Direct and inverse convention

The Smartcard protocol defines two conventions: direct and inverse.

The direct convention is defined as: LSB first, logical bit value of 1 corresponds to a H state of the line and parity is even. In order to use this convention, the following control bits must be programmed: MSBFIRST=0, DATAINV=0 (default values).

The inverse convention is defined as: MSB first, logical bit value 1 corresponds to an L state on the signal line and parity is even. In order to use this convention, the following control bits must be programmed: MSBFIRST=1, DATAINV=1.

Note: When logical data values are inverted (0=H, 1=L), the parity bit is also inverted in the same way.

In order to recognize the card convention, the card sends the initial character, TS, as the first character of the ATR (Answer To Reset) frame. The two possible patterns for the TS are: LHHL LLL LLH and LHHL HHH LLH.

- • (H) LHHL LLL LLH sets up the inverse convention: state L encodes value 1 and moment 2 conveys the most significant bit (MSB first). when decoded by inverse convention, the conveyed byte is equal to '3F'.

- • (H) LHHL HHH LLH sets up the direct convention: state H encodes value 1 and moment 2 conveys the least significant bit (LSB first). when decoded by direct convention, the conveyed byte is equal to '3B'.

Character parity is correct when there is an even number of bits set to 1 in the nine moments 2 to 10.

As the USART does not know which convention is used by the card, it needs to be able to recognize either pattern and act accordingly. The pattern recognition is not done in hardware, but through a software sequence. Moreover, supposing that the USART is configured in direct convention (default) and the card answers with the inverse convention, TS = LHHL LLL LLH => the USART received character will be '03' and the parity will be odd.

Therefore, two methods are available for TS pattern recognition:

Method 1

The USART is programmed in standard Smartcard mode/direct convention. In this case, the TS pattern reception generates a parity error interrupt and error signal to the card.

- • The parity error interrupt informs the software that the card didn't answer correctly in direct convention. Software then reprograms the USART for inverse convention

- • In response to the error signal, the card retries the same TS character, and it will be correctly received this time, by the reprogrammed USART

Alternatively, in answer to the parity error interrupt, the software may decide to reprogram the USART and to also generate a new reset command to the card, then wait again for the TS.

Method 2

The USART is programmed in 9-bit/no-parity mode, no bit inversion. In this mode it receives any of the two TS patterns as:

(H) LHHL LLL LLH = 0x103 -> inverse convention to be chosen

(H) LHHL HHH LLH = 0x13B -> direct convention to be chosen

The software checks the received character against these two patterns and, if any of them match, then programs the USART accordingly for the next character reception.

If none of the two is recognized, a card reset may be generated in order to restart the negotiation.

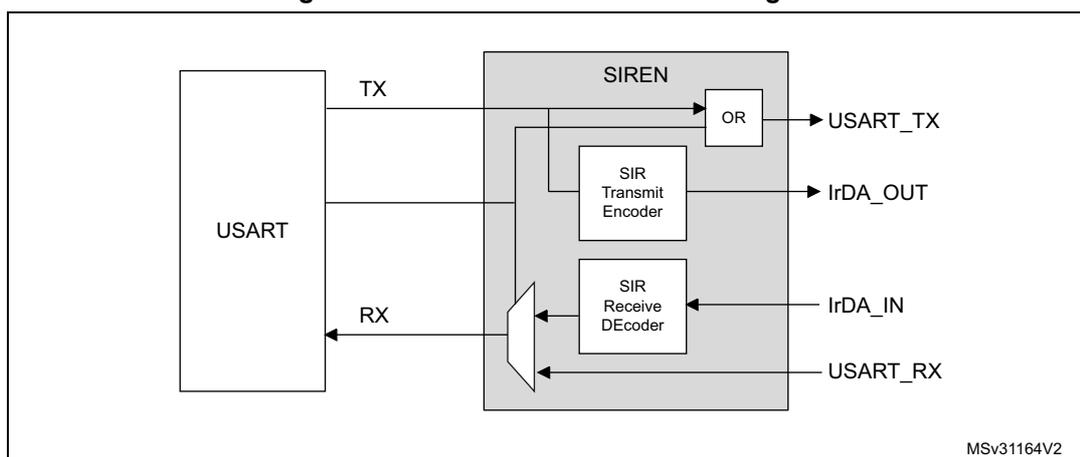

21.5.14 USART IrDA SIR ENDEC block

This section is relevant only when IrDA mode is supported. Please refer to Section 21.4: USART implementation on page 575 .

IrDA mode is selected by setting the IREN bit in the USART_CR3 register. In IrDA mode, the following bits must be kept cleared:

- • LINEN, STOP and CLKEN bits in the USART_CR2 register,

- • SCEN and HDSEL bits in the USART_CR3 register.

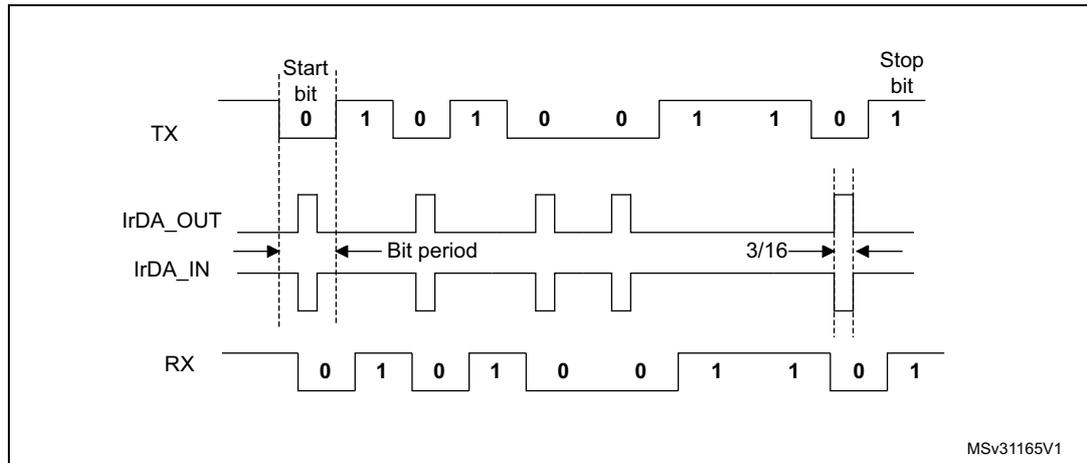

The IrDA SIR physical layer specifies use of a Return to Zero, Inverted (RZI) modulation scheme that represents logic 0 as an infrared light pulse (see Figure 197 ).

The SIR Transmit encoder modulates the Non Return to Zero (NRZ) transmit bit stream output from USART. The output pulse stream is transmitted to an external output driver and infrared LED. USART supports only bit rates up to 115.2 Kbps for the SIR ENDEC. In normal mode the transmitted pulse width is specified as 3/16 of a bit period.

The SIR receive decoder demodulates the return-to-zero bit stream from the infrared detector and outputs the received NRZ serial bit stream to the USART. The decoder input is normally high (marking state) in the Idle state. The transmit encoder output has the opposite polarity to the decoder input. A start bit is detected when the decoder input is low.

- • IrDA is a half duplex communication protocol. If the Transmitter is busy (when the USART is sending data to the IrDA encoder), any data on the IrDA receive line is ignored by the IrDA decoder and if the Receiver is busy (when the USART is receiving decoded data from the IrDA decoder), data on the TX from the USART to IrDA is not encoded. while receiving data, transmission should be avoided as the data to be transmitted could be corrupted.

- • A 0 is transmitted as a high pulse and a 1 is transmitted as a 0. The width of the pulse is specified as 3/16th of the selected bit period in normal mode (see Figure 198 ).

- • The SIR decoder converts the IrDA compliant receive signal into a bit stream for USART.

- • The SIR receive logic interprets a high state as a logic one and low pulses as logic zeros.

- • The transmit encoder output has the opposite polarity to the decoder input. The SIR output is in low state when Idle.

- • The IrDA specification requires the acceptance of pulses greater than 1.41 \( \mu\text{s} \) . The acceptable pulse width is programmable. Glitch detection logic on the receiver end filters out pulses of width less than 2 PSC periods (PSC is the prescaler value programmed in the USART_GTPR). Pulses of width less than 1 PSC period are always rejected, but those of width greater than one and less than two periods may be accepted or rejected, those greater than 2 periods will be accepted as a pulse. The IrDA encoder/decoder doesn't work when PSC=0.

- • The receiver can communicate with a low-power transmitter.

- • In IrDA mode, the STOP bits in the USART_CR2 register must be configured to "1 stop bit".

For code example, refer to A.15.11: USART IrDA mode code example .

IrDA low-power mode

Transmitter

In low-power mode the pulse width is not maintained at 3/16 of the bit period. Instead, the width of the pulse is 3 times the low-power baud rate which can be a minimum of 1.42 MHz.

Generally, this value is 1.8432 MHz ( \( 1.42 \text{ MHz} < \text{PSC} < 2.12 \text{ MHz} \) ). A low-power mode programmable divisor divides the system clock to achieve this value.

Receiver

Receiving in low-power mode is similar to receiving in normal mode. For glitch detection the USART should discard pulses of duration shorter than 1 PSC period. A valid low is accepted only if its duration is greater than 2 periods of the IrDA low-power Baud clock (PSC value in the USART_GTPR).

Note: A pulse of width less than two and greater than one PSC period(s) may or may not be rejected.

The receiver set up time should be managed by software. The IrDA physical layer specification specifies a minimum of 10 ms delay between transmission and reception (IrDA is a half duplex protocol).

Figure 197. IrDA SIR ENDEC- block diagram

graph LR

subgraph USART

TX

RX

end

subgraph SIREN

OR_GATE[OR]

MUX[Multiplexer]

SIR_TX[SIR Transmit Encoder]

SIR_RX[SIR Receive Decoder]

end

TX --> OR_GATE

TX --> SIR_TX

OR_GATE --> USART_TX

SIR_TX --> IrDA_OUT

IrDA_IN --> SIR_RX

SIR_RX --> MUX

RX --> MUX

MUX --> USART_RX

Figure 198. IrDA data modulation (3/16) -Normal Mode

The diagram illustrates the IrDA data modulation process. The TX line shows a start bit (0), followed by data bits (1, 0, 1, 0, 0, 1, 1, 0), and a stop bit (1). The IrDA_OUT line shows the modulated signal, which consists of short pulses corresponding to the '0' bits in the TX stream. The IrDA_IN line shows the received signal pulses. The RX line shows the demodulated signal, which reconstructs the original bit sequence. The bit period is indicated, and the IrDA_OUT signal is shown as a 3/16 duty cycle signal relative to the bit period. The diagram is labeled MSv31165V1.

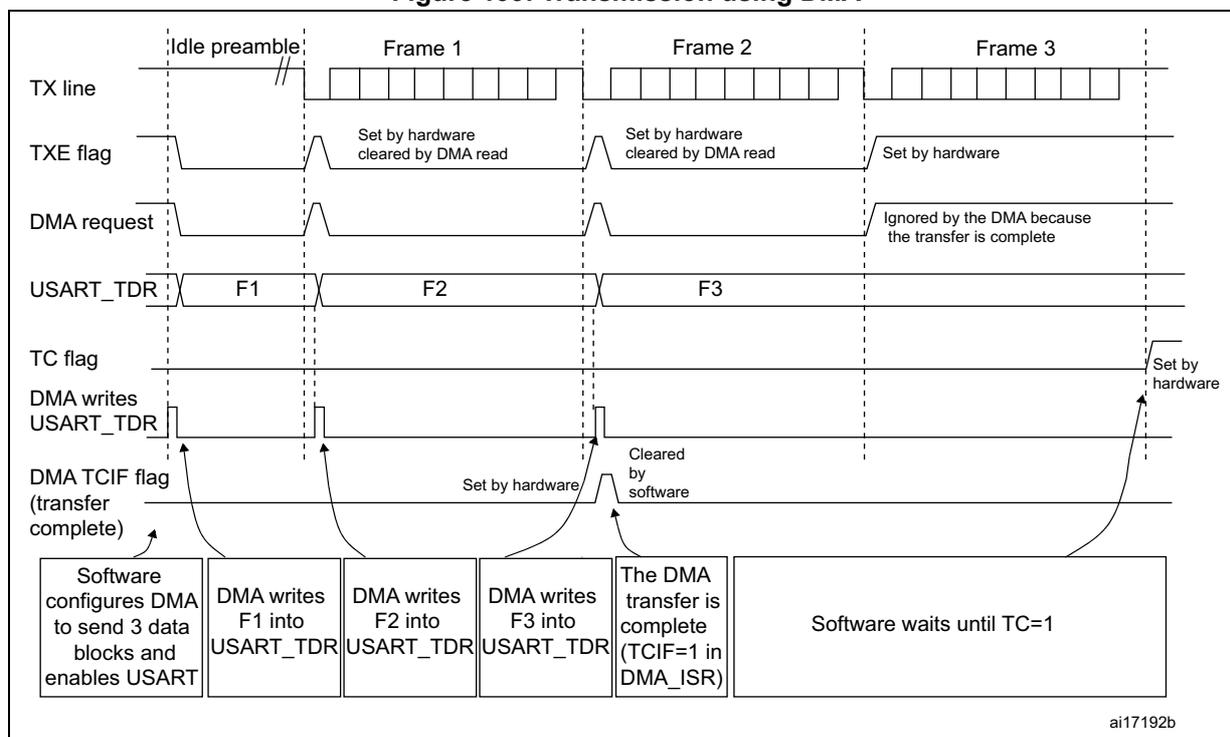

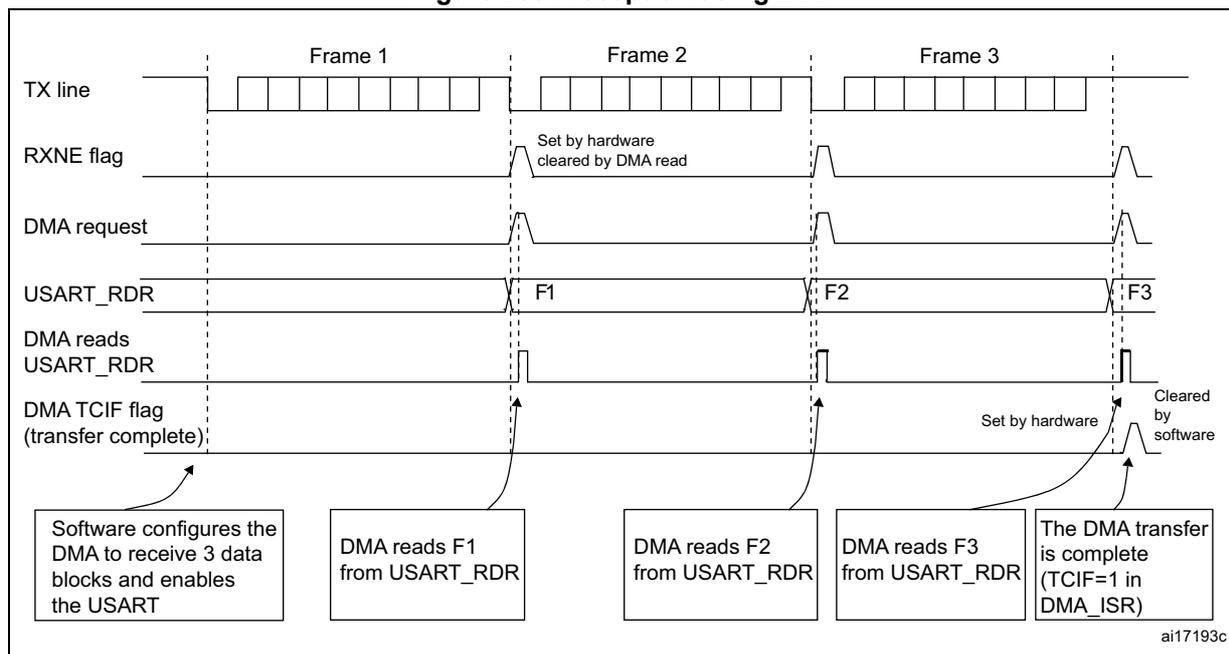

21.5.15 USART continuous communication in DMA mode