6. Power control (PWR)

6.1 Power supplies

The device requires a 1.8-to-3.6 V \( V_{DD} \) operating voltage supply.

An embedded linear voltage regulator is used to supply the internal digital power, ranging from 1.2 to 1.8 V.

- • \( V_{DD} = 1.8 \) to \( 3.6 \) V

\( V_{DD} \) is the external power supply for I/Os and internal regulator. It is provided externally through \( V_{DD} \) pins

- • \( V_{CORE} = 1.2 \) to \( 1.8 \) V

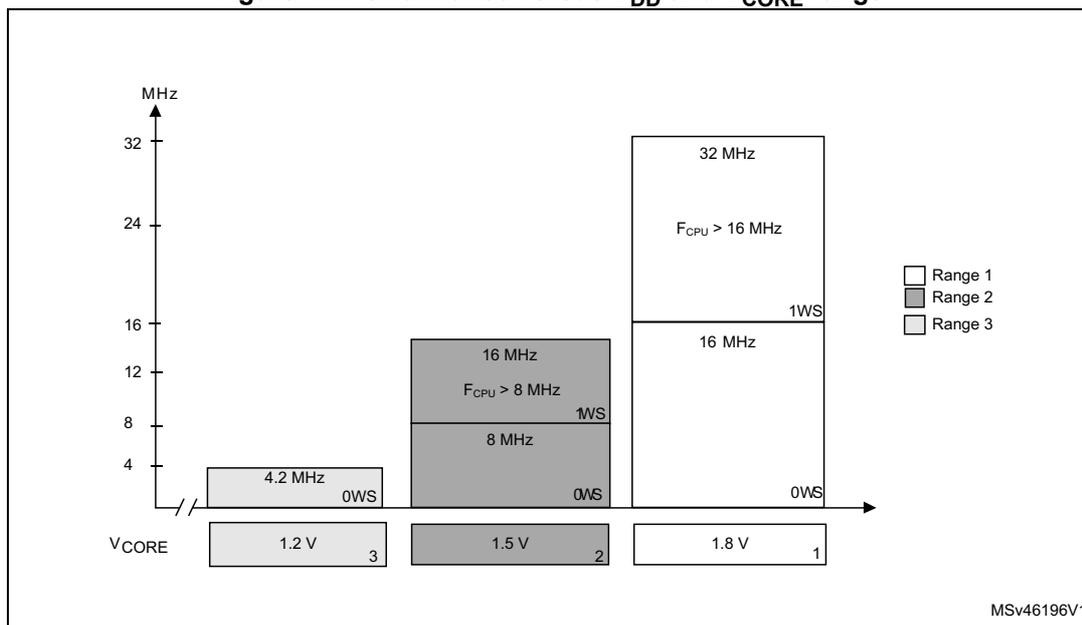

\( V_{CORE} \) is the power supply for digital peripherals, SRAM and Flash memory. It is generated by a internal voltage regulator. Three \( V_{CORE} \) ranges can be selected by software depending on \( V_{DD} \) (refer Figure 11 ).

- • \( V_{SSA}, V_{DDA} = 1.8 \) to \( 3.6 \) V

\( V_{DDA} \) is the external analog power supply for ADC, reset blocks, RC oscillators and PLL. For category 1 devices in low-pin count packages, \( V_{DDA} \) is bonded to \( V_{DD} \) (refer to the corresponding datasheets for more details).

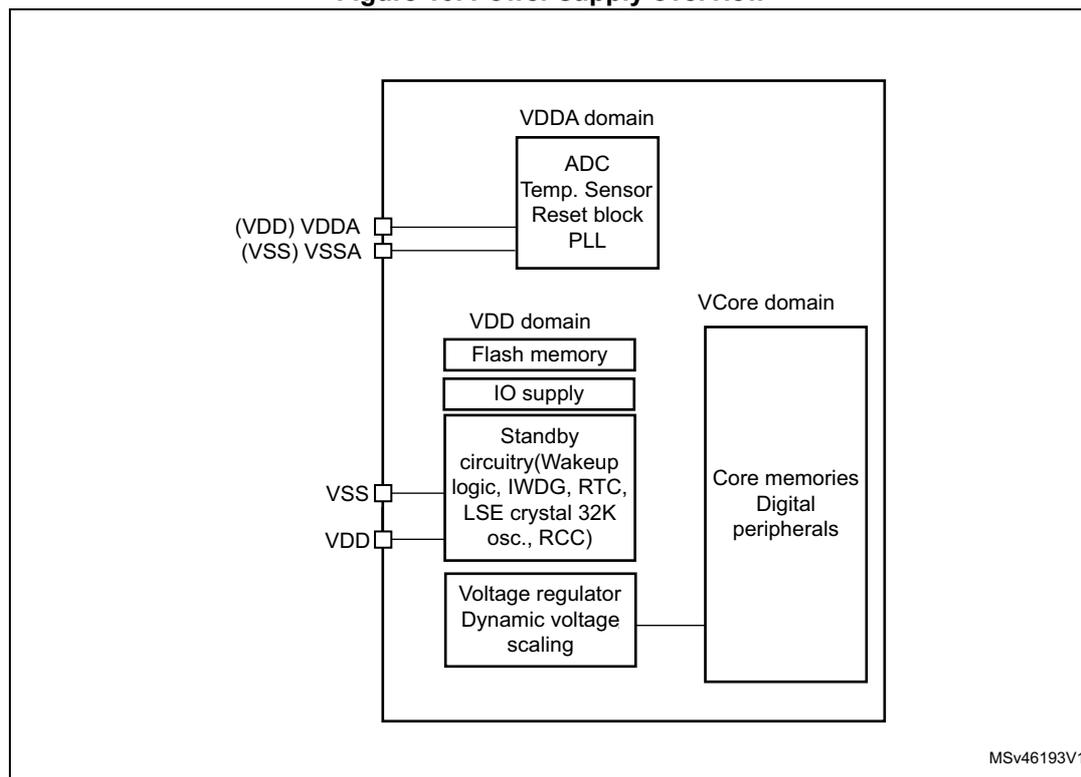

Figure 10. Power supply overview

The diagram illustrates the internal power supply architecture of the device. It shows three main power domains and their connections to external pins:

- VDDA domain: Contains the ADC, Temp. Sensor, Reset block, and PLL. It is connected to external pins \( (V_{DD}) V_{DDA} \) and \( (V_{SS}) V_{SSA} \) .

- VDD domain: Contains Flash memory, IO supply, Standby circuitry (Wakeup logic, IWDG, RTC, LSE crystal 32K osc., RCC), and a Voltage regulator with Dynamic voltage scaling. It is connected to external pins \( V_{SS} \) and \( V_{DD} \) .

- VCore domain: Contains Core memories and Digital peripherals. It is connected to the Voltage regulator.

The Voltage regulator is connected to the VDD domain and the VCore domain. The Standby circuitry is also connected to the VDD domain. The diagram is labeled with the code MSV46193V1.

- 1. \( V_{DDA} \) and \( V_{SSA} \) must be connected to \( V_{DD} \) and \( V_{SS} \) , respectively.

- 2. Depending on the operating power supply range used, some peripherals may be used with limited features or performance. For more details, please refer to section "General operating conditions" in STM32L010xx datasheets.

6.1.1 Independent A/D converter supply

To improve conversion accuracy, the ADC has an independent power supply that can be filtered separately, and shielded from noise on the PCB.

- • The ADC voltage supply input is available on a separate \( V_{DDA} \) pin

- • An isolated supply ground connection is provided on the \( V_{SSA} \) pin

Note: For category 1 devices in 14-pin package, \( V_{DDA} \) is internally connected to \( V_{DD} \) .

6.1.2 RTC and RTC backup registers

The real-time clock (RTC) is an independent BCD timer/counter. The RTC provides a time-of-day clock/calendar, two programmable alarm interrupts, and a periodic programmable wakeup flag with interrupt capability. The RTC contains 5 backup data registers (20 bytes). These backup registers are reset when a tamper detection event occurs. For more details refer to Real-time clock (RTC) section.

RTC registers access

After reset, the RTC Registers (RTC registers and RTC backup registers) are protected against possible stray write accesses. To enable access to the RTC Registers, proceed as follows:

- 1. Enable the power interface clock by setting the PWREN bits in the RCC_APB1ENR register.

- 2. Set the DBP bit in the PWR_CR register (see Section 6.4.1 ).

- 3. Select the RTC clock source through RTCSEL[1:0] bits in RCC_CSR register.

- 4. Enable the RTC clock by programming the RTCEN bit in the RCC_CSR register.

6.1.3 Voltage regulator

An embedded linear voltage regulator supplies all the digital circuitries except for the Standby circuitry. The regulator output voltage ( \( V_{CORE} \) ) can be programmed by software to three different ranges within 1.2 - 1.8 V (typical) (see Section 6.1.4 ).

The voltage regulator is always enabled after Reset. It works in three different modes: main (MR), low-power (LPR) and power-down, depending on the application modes.

- • In Run mode, the regulator is main (MR) mode and supplies full power to the \( V_{CORE} \) domain (core, memories and digital peripherals).

- • In Low-power run mode, the regulator is in low-power (LPR) mode and supplies low-power to the \( V_{CORE} \) domain, preserving the contents of the registers and internal SRAM.

- • In Sleep mode, the regulator is main (MR) mode and supplies full power to the \( V_{CORE} \) domain, preserving the contents of the registers and internal SRAM.

- • In Low-power sleep mode, the regulator is in low-power (LPR) mode and supplies low-power to the \( V_{CORE} \) domain, preserving the contents of the registers and internal SRAM.

- • In Stop mode the regulator supplies low power to the \( V_{CORE} \) domain, preserving the content of registers and internal SRAM.

- • In Standby mode, the regulator is powered off. The content of the registers and SRAM are lost except for the Standby circuitry.

6.1.4 Dynamic voltage scaling management

The dynamic voltage scaling is a power management technique which consists in increasing or decreasing the voltage used for the digital peripherals ( \( V_{CORE} \) ), according to the circumstances.

Dynamic voltage scaling to increase \( V_{CORE} \) is known as overvolting. It allows improving the device performance. Refer to Figure 11 for a description of the device operating conditions versus CPU performance and to the datasheet electrical characteristics for ADC clock frequency versus dynamic range.

Dynamic voltage scaling to decrease \( V_{CORE} \) is known as undervolting. It is performed to save power, particularly in laptops and other mobile devices where the energy comes from a battery and is thus limited.

Range 1

Range 1 is the “high performance” range.

The voltage regulator outputs a 1.8 V voltage (typical). Flash program and erase operations can be performed in this range.

When \( V_{DD} \) is below 2.0 V, the CPU frequency changes from initial to final state must respect the following conditions:

- • \( f_{CPUfinal} < 4 \times f_{CPUinitial} \)

- • In addition, a 5 µs delay must be respected between two changes. For example to switch from 4.2 to 32 MHz, switch from 4.2 to 16 MHz, wait for 5 µs, then switch from 16 to 32 MHz.

Range 2 and 3

The regulator can also be programmed to output a regulated 1.5 V (typical, range 2) or a 1.2 V (typical, range 3) without any limitations on \( V_{DD} \) (1.8 to 3.6 V).

- • At 1.5 V, the Flash memory is still functional but with medium read access time. This is the “medium performance” range. Program and erase operations on the Flash memory are still possible.

- • At 1.2 V, the Flash memory is still functional but with slow read access time. This is the “low performance” range. Program and erase operations on the Flash memory are not possible under these conditions.

Refer to Table 29 for details on the performance for each range.

Table 29. Performance versus \( V_{CORE} \) ranges

| CPU performance | Power performance | \( V_{CORE} \) range | Typical Value (V) | Max frequency (MHz) | \( V_{DD} \) range | |

|---|---|---|---|---|---|---|

| 1 WS | 0 WS | |||||

| High | Low | 1 | 1.8 | 32 | 16 | 1.8 - 3.6 |

| Medium | Medium | 2 | 1.5 | 16 | 8 | |

| Low | High | 3 | 1.2 | 4.2 | 4.2 | |

| VCORE (V) | Range | Max Frequency (MHz) | WS | Condition |

|---|---|---|---|---|

| 1.2 | Range 3 | 4.2 | 0WS | |

| 1.5 | Range 2 | 16 | 1WS | \( F_{CPU} > 8 \) MHz |

| 1.5 | Range 2 | 8 | 0WS | |

| 1.8 | Range 1 | 32 | 1WS | \( F_{CPU} > 16 \) MHz |

| 1.8 | Range 1 | 16 | 0WS |

6.1.5 Dynamic voltage scaling configuration

The following sequence is required to program the voltage regulator ranges:

- 1. Check \( V_{DD} \) to identify which ranges are allowed (see Figure 11: Performance versus \( V_{DD} \) and \( V_{CORE} \) range ).

- 2. Poll VOSF bit of in PWR_CSR. Wait until it is reset to 0.

- 3. Configure the voltage scaling range by setting the VOS[1:0] bits in the PWR_CR register.

- 4. Poll VOSF bit of in PWR_CSR register. Wait until it is reset to 0.

Note: During voltage scaling configuration, the system clock is stopped until the regulator is stabilized (VOSF=0). This must be taken into account during application development, in case a critical reaction time to interrupt is needed, and depending on peripheral used (timer, communication,...).

6.1.6 Voltage regulator and clock management when modifying the \( V_{CORE} \) range

When \( V_{DD} \) is above 1.8 V, any of the 3 voltage ranges can be selected:

- • When the voltage range is above the targeted voltage range (e.g. from range 1 to 2):

- a) Adapt the clock frequency to the lower voltage range that will be selected at next step.

- b) Select the required voltage range.

- • When the voltage range is below the targeted voltage range (e.g. from range 3 to 1):

- a) Select the required voltage range.

- b) Tune the clock frequency if needed.

6.1.7 Voltage range and limitations when \( V_{DD} \) ranges from 1.8 V to 2.0 V

The STM32L010xx voltage regulator is based on an architecture designed for Ultra-low-power. It does not use any external capacitor. Such regulator is sensitive to fast changes of load. In this case, the output voltage is reduced for a short period of time. Considering that the core voltage must be higher than 1.8 V to ensure a 32 MHz operation, this phenomenon is critical for very low \( V_{DD} \) voltages (e.g. 1.8 V \( V_{DD} \) minimum value).

To guarantee 32 MHz operation at \( V_{DD} = 1.8 \text{ V} \pm 5\% \) , with 1 wait state, and \( V_{CORE} \) range 1, the CPU frequency in run mode must be managed to prevent any changes exceeding a ratio of 4 in one shot. A delay of 5 \( \mu\text{s} \) must be respected between 2 changes. There is no limitation when waking up from low-power mode.

6.2 Power supply supervisor

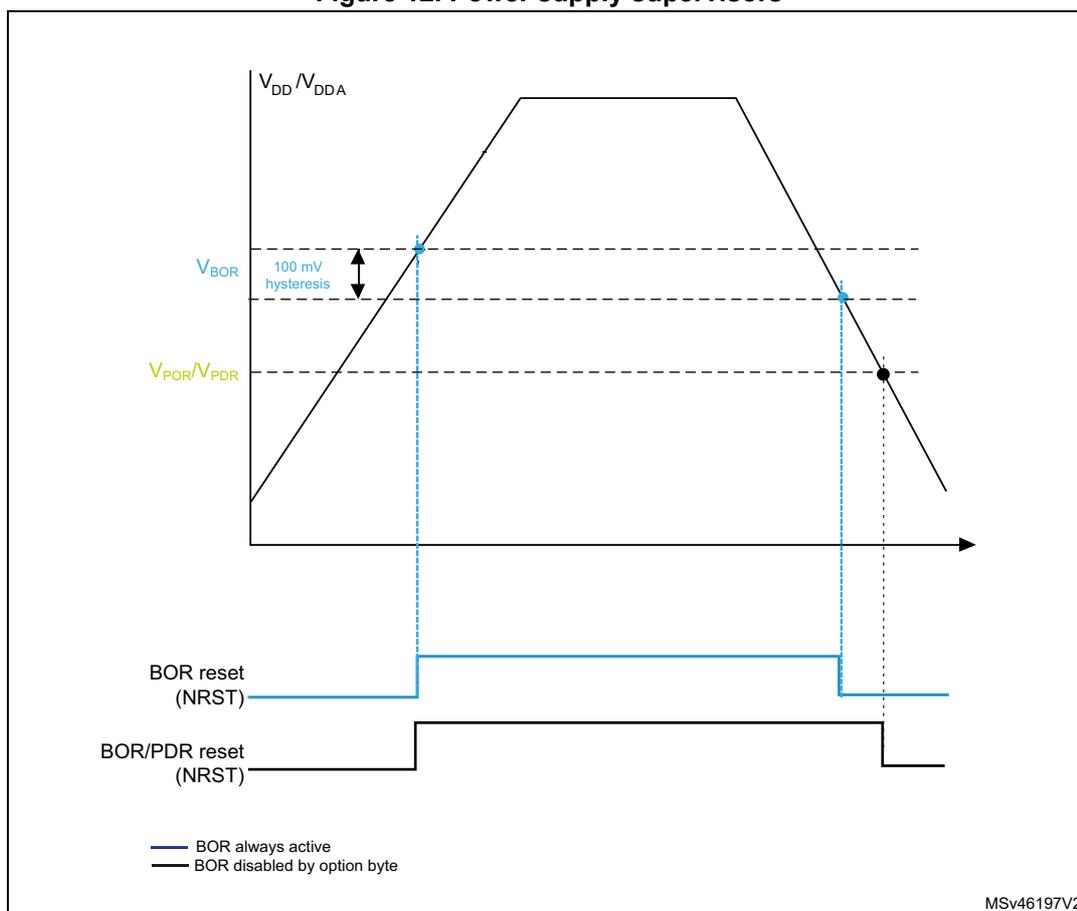

The device has an integrated zeropower power-on reset (POR)/power-down reset (PDR), coupled with a brownout reset (BOR) circuitry. The BOR is always active at power-on and ensures proper operation starting from 1.8 V. After the 1.8 V BOR threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently (in which case, the \( V_{DD} \) min value at power-down is set to \( V_{PDR} \) ).

Five BOR thresholds can be configured by option bytes, starting from 1.8 to 3 V. To reduce the power consumption in Stop mode, the internal voltage reference, \( V_{REFINT} \) , can be automatically switch off. The device remains in reset mode when \( V_{DD} \) is below a specified threshold, \( V_{POR} \) , \( V_{PDR} \) or \( V_{BOR} \) , without the need for any external reset circuit.

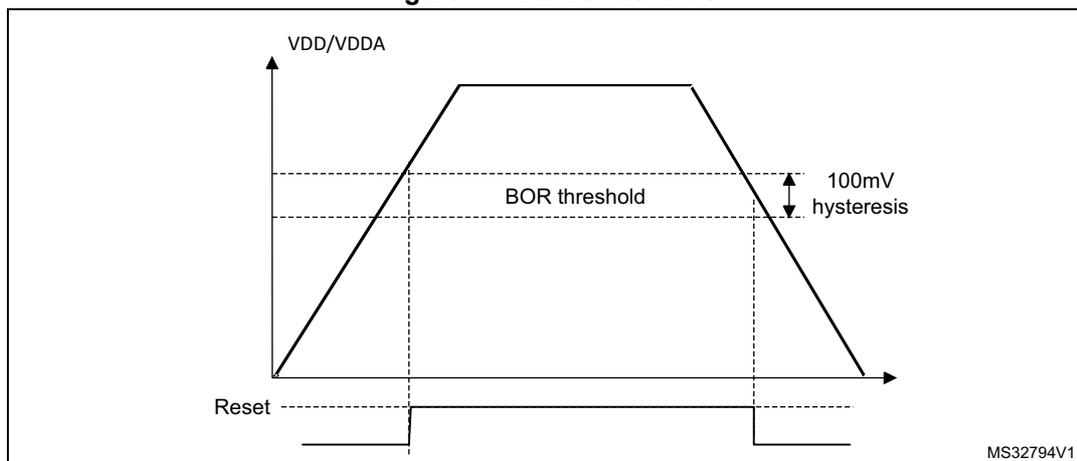

The different power supply supervisor (POR, PDR, BOR) are illustrated in Figure 12 .

Figure 12. Power supply supervisors

The figure illustrates the power supply supervisor behavior during a power cycle. The top graph shows the supply voltage \( V_{DD}/V_{DDA} \) rising from a low level to a peak and then falling. Two horizontal dashed lines represent the \( V_{BOR} \) threshold (with a 100 mV hysteresis band) and the \( V_{POR}/V_{PDR} \) threshold. Below the graph, two reset signal waveforms are shown. The \( BOR\ reset\ (NRST) \) signal is active (low) when the voltage is below \( V_{BOR} \) . The \( BOR/PDR\ reset\ (NRST) \) signal is active (low) when the voltage is below \( V_{POR}/V_{PDR} \) . A legend at the bottom indicates that the blue line represents 'BOR always active' and the black line represents 'BOR disabled by option byte'.

- 1. When the BOR is disabled by option byte, the reset is asserted when \( V_{DD} \) goes below PDR level

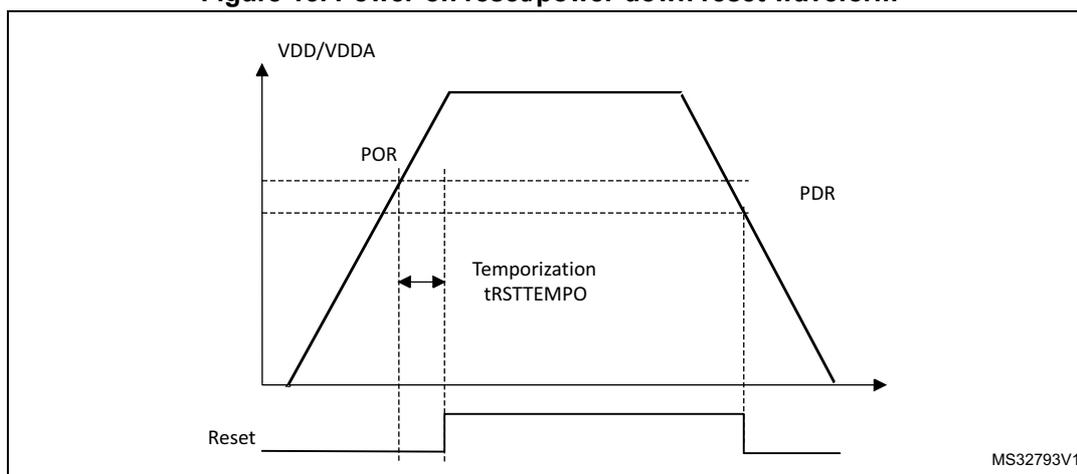

6.2.1 Power-on reset (POR)/power-down reset (PDR)

The device has an integrated POR/PDR circuitry that allows operation down to 1.5 V.

During power-on, the device remains in Reset mode when \( V_{DD}/V_{DDA} \) is below a specified threshold, \( V_{POR} \) , without the need for an external reset circuit. The POR feature is always enabled and the POR threshold is 1.5 V.

During power-down, the PDR keeps the device under reset when the supply voltage ( \( V_{DD} \) ) drops below the \( V_{PDR} \) threshold. The PDR feature is always enabled and the PDR threshold is 1.5 V.

The POR and PDR are used only when the BOR is disabled (see Section 6.2.2: Brownout reset (BOR) ). To insure the minimum operating voltage (1.8 V), the BOR should be configured to BOR Level 1. When the BOR is disabled, a “gray zone” exist between the minimum operating voltage (1.8 V) and the \( V_{POR}/V_{PDR} \) threshold. This means that \( V_{DD} \) can be lower than 1.8 V without device reset until the \( V_{PDR} \) threshold is reached.

For more details concerning the power-on/power-down reset threshold, refer to the electrical characteristics of the datasheet.

Figure 13. Power-on reset/power-down reset waveform

6.2.2 Brownout reset (BOR)

During power-on, the Brownout reset (BOR) keeps the device under reset until the supply voltage reaches the specified \( V_{BOR} \) threshold.

The BOR is always active at power-on and its threshold is 1.8 V.

Then when the system reset is released, the BOR level can be reconfigured or disabled by option byte loading.

If the BOR level is kept at the lowest level (1.8 V), the system reset is fully managed by the BOR and the product operating voltages are within safe ranges.

And when the BOR option is disabled by option byte, the power-down reset is controlled by the PDR and a “gray zone” exists between the 1.8 V and \( V_{PDR} \) .

\( V_{BOR} \) is configured through device option bytes. By default, the Level 4 threshold is activated. 5 programmable \( V_{BOR} \) thresholds can be selected.

- • BOR Level 1 ( \( V_{BOR0} \) ): reset threshold level for 1.69 to 1.80 V voltage range

- • BOR Level 2 ( \( V_{BOR1} \) ): reset threshold level for 1.94 to 2.1 V voltage range

- • BOR Level 3 ( \( V_{BOR2} \) ): reset threshold level for 2.3 to 2.49 V voltage range

- • BOR Level 4 ( \( V_{BOR3} \) ): reset threshold level for 2.54 to 2.74 V voltage range

- • BOR Level 5 ( \( V_{BOR4} \) ): reset threshold level for 2.77 to 3.0 V voltage range

When the supply voltage ( \( V_{DD} \) ) drops below the selected \( V_{BOR} \) threshold, a device reset is generated. When the \( V_{DD} \) is above the \( V_{BOR} \) upper limit the device reset is released and the system can start.

BOR can be disabled by programming the device option bytes. To disable the BOR function, \( V_{DD} \) must have been higher than \( V_{BOR0} \) to start the device option byte programming sequence. The power-on and power-down is then monitored by the POR and PDR (see Section 6.2.1: Power-on reset (POR)/power-down reset (PDR) )

The BOR threshold hysteresis is \( \sim 100 \) mV (between the rising and the falling edge of the supply voltage).

Figure 14. BOR thresholds

6.2.3 Internal voltage reference ( \( V_{REFINT} \) )

The internal reference ( \( V_{REFINT} \) ) provides stable voltage for analog peripherals. The functions managed through the internal voltage reference ( \( V_{REFINT} \) ) are BOR, ADC and comparators. The internal voltage reference ( \( V_{REFINT} \) ) is always enabled when one of these features is used.

The internal voltage reference consumption is not negligible, in particular in Stop and Standby mode. To reduce power consumption, the ULP bit (ultra-low-power) in the PWR_CR register can be set to disable the internal voltage reference. However, in this case, when exiting from the Stop/Standby mode, the functions managed through the internal voltage reference are not reliable during the internal voltage reference startup time (up to 3 ms).

To reduce the wakeup time, the device can exit from Stop/Standby mode without waiting for the internal voltage reference startup time. This is performed by setting the FWU bit (Fast wakeup) in the PWR_CR register before entering Stop/Standby mode.

If the ULP bit is set, the functions that were enabled before entering Stop/Standby mode will be disabled during these modes, and enabled again only after the end of the internal voltage reference startup time whatever FWU value. The VREFINTRDYF flag in the PWR_CSR register indicates that the internal voltage reference is ready.

When the device exits from low-power mode on an NRST pulse, it does not wait for internal voltage reference startup (even if ULP=1 and FWU=0). The application should check the VREFINTRDYF flag if necessary.

6.3 Low-power modes

By default, the microcontroller is in Run mode after a system or a power-on reset. In Run mode the CPU is clocked by HCLK and the program code is executed. Several low-power modes are available to save power when the CPU does not need to be kept running, for example when waiting for an external event. It is up to the user to select the mode that gives the best compromise between low-power consumption, performance, short startup time and available wakeup sources.

The devices feature five low-power modes:

- • Low-power run mode: regulator in low-power mode, limited clock frequency, limited number of peripherals running (refer to Section 6.3.4 )

- • Sleep mode: Cortex ® -M0+ core stopped, peripherals kept running (refer to Section 6.3.7 )

- • Low-power sleep mode: Cortex ® -M0+ core stopped, limited clock frequency, limited number of peripherals running, regulator in low-power mode, Flash stopped ((refer to Section 6.3.8 ))

- • Stop mode (all clocks are stopped, regulator running, regulator in low-power mode (refer to Section 6.3.9 ))

- • Standby mode: V CORE domain powered off ((refer to Section 6.3.10 ))

In addition, the power consumption in Run mode can be reduced by one of the following means:

- • Slowing down the system clocks

- • Gating the clocks to the APBx and AHBx peripherals when they are unused.

Table 30. Summary of low-power modes

| Mode name | Entry | Wakeup | Effect on V CORE domain clocks | Effect on V DD domain clocks | Voltage regulator |

|---|---|---|---|---|---|

| Low-power run | LPSDSR and LPRUN bits + Clock setting | The regulator is forced in Main regulator (1.8 V) | None | None | In low-power mode |

| Sleep (Sleep now or Sleep-on-exit) | WFI or Return from ISR | Any interrupt | CPU CLK OFF no effect on other clocks or analog clock sources | None | ON |

| WFE | Wakeup event | ||||

| Low-power sleep (Sleep now or Sleep-on-exit) | LPSDSR bits + WFI or Return from ISR | Any interrupt | CPU CLK OFF no effect on other clocks or analog clock sources, Flash CLK OFF | None | In low-power mode |

| LPSDSR bits + WFE | Wakeup event |

Table 30. Summary of low-power modes (continued)

| Mode name | Entry | Wakeup | Effect on V CORE domain clocks | Effect on V DD domain clocks | Voltage regulator |

|---|---|---|---|---|---|

| Stop | PDDS, LPDSR or LPDS bits + SLEEPDEEP bit + WFI, Return from ISR or WFE | Any EXTI line (configured in the EXTI registers, internal and external lines) | All V CORE domain clocks OFF | HSI16 (1) , HSE and MSI oscillators OFF | In low-power mode |

| Standby | PDDS bit + SLEEPDEEP bit + WFI, Return from ISR or WFE | WKUP pin rising edge, RTC alarm (Alarm A or Alarm B), RTC Wakeup event, RTC tamper event, RTC timestamp event, external reset in NRST pin, IWDG reset | OFF | ||

| Stop | PDDS, LPDS and LPDSR bits + SLEEPDEEP bit + WFI, Return from ISR or WFE | Any EXTI line (configured in the EXTI registers, internal and external lines) | All V CORE domain clocks OFF | HSI16 (1) , HSE and MSI oscillators OFF | In low-power mode |

| Standby | PDDS bit + SLEEPDEEP bit + WFI, Return from ISR or WFE | WKUP pin rising edge, RTC alarm (Alarm A or Alarm B), RTC Wakeup event, RTC tamper event, RTC timestamp event, external reset in NRST pin, IWDG reset | OFF |

1. HSI16 can run in Stop mode provided HSI16KERON is set in Clock control register (RCC_CR) .

6.3.1 Behavior of clocks in low-power modes

APB peripheral and DMA clocks can be disabled by software.

Sleep and Low-power sleep modes

The CPU clock is stopped in Sleep and Low-power sleep mode. The memory interface clocks (Flash memory and RAM interfaces) and all peripherals clocks can be stopped by software during Sleep. The memory interface clock is stopped and the RAM is in power-down when in Low-power sleep mode. The AHB to APB bridge clocks are disabled by hardware during Sleep/Low-power sleep mode when all the clocks of the peripherals connected to them are disabled.

Stop and Standby modes

The system clock and all high speed clocks are stopped in Stop and Standby modes:

- • PLL is disabled

- • Internal RC 16 MHz (HSI16) oscillator is disabled, except if HSI16KERON is set in Stop mode (see Section 7.3.1: Clock control register (RCC_CR) )

- • External 1-24 MHz (HSE) oscillator is disabled

- • Internal 65 kHz - 4.2 MHz (MSI) oscillator is disabled

When exiting this mode by an interrupt (Stop mode), the internal MSI or HSI16 can be selected as system clock. For both oscillators, their respective configuration (range and trimming) value is kept on Stop mode exit.

When exiting this mode by a reset (Standby mode), the internal MSI oscillator is selected as system clock. The range and the trimming value are reset to the default 2.1 MHz.

If a Flash program operation or an access to APB domain is ongoing, the Stop/Standby mode entry is delayed until the Flash memory or the APB access has completed.

6.3.2 Slowing down system clocks

In Run mode the speed of the system clocks (SYSCLK, HCLK, PCLK1, PCLK2) can be reduced by programming the prescaler registers. These prescalers can also be used to slow down peripherals before entering Sleep mode.

For more details refer to Section 7.3.3: Clock configuration register (RCC_CFGR) .

6.3.3 Peripheral clock gating

In Run mode, the HCLK and PCLKx for individual peripherals and memories can be stopped at any time to reduce power consumption.

To further reduce power consumption in Sleep mode the peripheral clocks can be disabled prior to executing the WFI or WFE instructions.

Peripheral clock gating is controlled by the AHB peripheral clock enable register (RCC_AHBENR), APB2 peripheral clock enable register (RCC_APB2ENR), APB1 peripheral clock enable register (RCC_APB1ENR) (see Section 7.3.12: AHB peripheral clock enable register (RCC_AHBENR) , Section 7.3.14: APB1 peripheral clock enable register (RCC_APB1ENR) and Section 7.3.13: APB2 peripheral clock enable register (RCC_APB2ENR) ).

Disabling the peripherals clocks in Sleep mode can be performed automatically by resetting the corresponding bit in RCC_AHBLPENR and RCC_APBxLPENR registers (x can 1 or 2).

6.3.4 Low-power run mode (LP run)

To further reduce the consumption when the system is in Run mode, the regulator can be configured in low-power mode. In this mode, the system frequency should not exceed f_MSI range1.

Please refer to the product datasheet for more details on voltage regulator and peripherals operating conditions.

Note: To be able to read the RTC calendar register when the APB1 clock frequency is less than seven times the RTC clock frequency ( \( 7 imes ext{RTCLCK} \) ), the software must read the calendar time and date registers twice.

If the second read of the RTC_TR gives the same result as the first read, this ensures that the data is correct. Otherwise a third read access must be done.

Low-power run mode can only be entered when V CORE is in range 2. In addition, the dynamic voltage scaling must not be used when Low-power run mode is selected. Only Stop and Sleep modes with regulator configured in low-power mode is allowed when Low-power run mode is selected.

Note: In Low-power run mode, all I/O pins keep the same state as in Run mode.

Entering Low-power run mode

To enter Low-power run mode proceed as follows:

- 1. Each digital IP clock must be enabled or disabled by using the RCC_APBxENR and RCC_AHBENR registers.

- 2. The frequency of the system clock must be decreased to not exceed the frequency of f_MSI range1.

- 3. The regulator is forced in low-power mode by software (LPRUN and LPSDSR bits set)

Exiting Low-power run mode

To exit Low-power run mode proceed as follows:

- 1. The regulator is forced in Main regulator mode by software.

- 2. The Flash memory is switched on, if needed.

- 3. The frequency of the clock system can be increased.

6.3.5 Entering low-power mode

Low-power modes (except for Low-power run mode) are entered by executing the WFI (Wait For Interrupt) or WFE (Wait for Event) instructions, or when the SLEEPONEXIT bit in Cortex ® -M0+ System Control register is set on Return from ISR.

Entering low-power mode through WFI or WFE will be executed only if no interrupt and no event is pending.

6.3.6 Exiting low-power mode

The microcontroller exits from Sleep and Stop mode depending on the way the mode was entered:

- • If the WFI instruction or Return from ISR was used to enter the low-power mode, any peripheral interrupt acknowledged by the NVIC can wake up the device. This includes EXTI lines and any GPIO toggle.

- • If the WFE instruction was used to enter low-power mode, the microcontroller exits the low-power mode as soon as an event occurs. The wakeup event can be generated either by:

- – An NVIC IRQ interrupt:

This is done by enabling an interrupt in the peripheral control register but not in the NVIC, and by enabling the SEVONPEND bit in the Cortex ® -M0+ System Control register. When the microcontroller resumes from WFE, the peripheral interrupt pending bit and the peripheral NVIC IRQ channel pending bit (in the NVIC interrupt clear pending register) have to be cleared. - – An event:

This is done by configuring an external or internal EXTI line in event mode. When the CPU resumes from WFE, it is not necessary to clear the peripheral interrupt pending bit or the NVIC IRQ channel pending bit as the pending bit corresponding to the event line is not set.

- – An NVIC IRQ interrupt:

6.3.7 Sleep mode

I/O states in Sleep mode

In Sleep mode, all I/O pins keep the same state as in Run mode.

Entering Sleep mode

The Sleep mode is entered according to Section 6.3.5: Entering low-power mode .

Refer to Table 31: Sleep-now and Table 32: Sleep-on-exit for details on how to enter Sleep mode.

Exiting Sleep mode

The Sleep mode is exited according to Section 6.3.6: Exiting low-power mode .

Refer to Table 31: Sleep-now and Table 32: Sleep-on-exit for more details on how to exit Sleep mode.

Table 31. Sleep-now

| Sleep-now mode | Description |

|---|---|

| Mode entry | WFI (Wait for Interrupt) or WFE (Wait for Event) while:

Refer to the Cortex®-M0+ System Control register (see PM0223 programming manual). On return from ISR while:

Refer to the Cortex®-M0+ System Control register (see PM0223 programming manual). |

| Mode exit | If WFI or return from ISR was used for entry: Interrupt: refer to Table 49: List of vectors If WFE was used for entry and SVONPEND = 0 Wakeup event: refer to Section 12.3.2: Wakeup event management If WFE was used for entry and SVONPEND = 1 Interrupt event when disabled in NVIC (refer to Table 49: List of vectors ) or wakeup event (refer to Section 12.3.2: Wakeup event management ) |

| Wakeup latency | None |

Table 32. Sleep-on-exit

| Sleep-on-exit | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) while:

Refer to the Cortex®-M0+ System Control register (see PM0223 programming manual). On return from ISR while:

Refer to the Cortex®-M0+ System Control register (see PM0223 programming manual). |

| Mode exit | Interrupt: refer to Table 49: List of vectors |

| Wakeup latency | None |

6.3.8 Low-power sleep mode (LP sleep)

I/O states in Low-power sleep mode

In Low-power sleep mode, all I/O pins keep the same state as in Run mode.

Entering Low-power sleep mode

To enter Low-power sleep mode, proceed as follows:

- 1. The Flash memory can be switched off by using the control bits (SLEEP_PD in the FLASH_ACR register. This reduces power consumption but increases the wake-up time.

- 2. Each digital IP clock must be enabled or disabled by using the RCC_APBxENR and RCC_AHBENR registers.

- 3. The frequency of the system clock must be decreased.

- 4. The regulator is forced in low-power mode by software (LPSDSR bits set).

- 5. Follow the steps described in Section 6.3.5: Entering low-power mode .

Refer to Table 33: Sleep-now (Low-power sleep) and Table 34: Sleep-on-exit (Low-power sleep) for details on how to enter Low-power sleep mode.

In Low-power sleep mode, the Flash memory can be switched off and the RAM memory remains available.

In this mode, the system frequency should not exceed f_MSI range1.

Please refer to product datasheet for more details on voltage regulator and peripherals operating conditions.

Low-power sleep mode can only be entered when V CORE is in range 2.

Note: To be able to read the RTC calendar register when the APB1 clock frequency is less than seven times the RTC clock frequency ( \( 7 \times \text{RTCLCK} \) ), the software must read the calendar time and date registers twice.

If the second read of the RTC_TR gives the same result as the first read, this ensures that the data is correct. Otherwise a third read access must be done.

Exiting Low-power sleep mode

The Low-power sleep mode is exited according to Section 6.3.6: Exiting low-power mode .

When exiting Low-power sleep mode by issuing an interrupt or a wakeup event, the regulator is configured in Main regulator mode, the Flash memory is switched on (if necessary), and the system clock can be increased.

When the voltage regulator operates in low-power mode, an additional startup delay is incurred when waking up from Low-power sleep mode.

Refer to Table 33: Sleep-now (Low-power sleep) and Table 34: Sleep-on-exit (Low-power sleep) for more details on how to exit Sleep low-power mode.

Table 33. Sleep-now (Low-power sleep)

| Sleep-now mode | Description |

|---|---|

| Mode entry | Voltage regulator in low-power mode and the Flash memory switched off

Refer to the Cortex ® -M0+ System Control register (see PM0223 programming manual). On return from ISR while:

Refer to the Cortex ® -M0+ System Control register (see PM0223 programming manual). |

| Mode exit | Voltage regulator in Main regulator mode and the Flash memory switched on If WFE was used for entry and SEVONPEND = 0 If WFE was used for entry and SVONPEND = 1 |

| Wakeup latency | Regulator wakeup time from low-power mode |

| Sleep-on-exit | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) while:

Refer to the Cortex®-M0+ System Control register (see PM0223 programming manual). On return from ISR while:

Refer to the Cortex®-M0+ System Control register (see PM0223 programming manual). |

| Mode exit | Interrupt: refer to Table 49: List of vectors . |

| Wakeup latency | regulator wakeup time from low-power mode |

6.3.9 Stop mode

The Stop mode is based on the Cortex®-M0+ DeepSleep mode combined with peripheral clock gating. The voltage regulator can be configured either in normal or low-power mode. In Stop mode, all clocks in the V CORE domain are stopped, the PLL, the MSI, the HSI16 (except if HSI16KERON is set in Stop mode, see Section 7.3.1: Clock control register (RCC_CR) ) and the HSE RC oscillators are disabled. Internal SRAM and register contents are preserved.

To get the lowest consumption in Stop mode, the internal Flash memory also enters low-power mode. When the Flash memory is in power-down mode, an additional startup delay is incurred when waking up from Stop mode.

To minimize the consumption In Stop mode, V REFINT and BOR can be switched off before entering Stop mode. This functionality is controlled by the ULP bit in the PWR_CR register. If the ULP bit is set, the reference is switched off on Stop mode entry and enabled again on wakeup. .

I/O states in Low-power sleep mode

In Stop mode, all I/O pins keep the same state as in Run mode.

Entering Stop mode

Refer to Section 6.3.5: Entering low-power mode and to Table 35 for details on how to enter the Stop mode.

If the application needs to disable the external clock before entering Stop mode, the HSEON bit must be first disabled and the system clock switched to HSI16.

Otherwise, if the HSEON bit is kept enabled while external clock (external oscillator) can be removed before entering Stop mode, the clock security system (CSS) feature must be enabled to detect any external oscillator failure and avoid a malfunction behavior when entering Stop mode.

To further reduce power consumption in Stop mode, the internal voltage regulator can be put in low-power mode. This is configured by the LPSDSR or LPDS bit in the PWR_CR register (see Section 6.4.1 ). The internal voltage regulator can also be kept in Main mode but the consumption will be much higher. As a result, it is always implicitly assumed that the regulator is in low-power mode during Stop mode. The only advantage of keeping the regulator in Main mode is that the wakeup time from Stop mode is shorter.

If Flash memory programming or an access to the APB domain is ongoing, the Stop mode entry is delayed until the memory or APB access has completed.

In Stop mode, the following features can be selected by programming individual control bits:

- • Independent watchdog (IWDG): the IWDG is started by writing to its Key register or by hardware option. Once started it cannot be stopped except by a Reset. Refer to Section 17.3: IWDG functional description in Section 17: Independent watchdog (IWDG) .

- • Real-time clock (RTC): this is configured by the RTCEN bit in the RCC_CSR register (see Section 7.3.20 ).

- • Internal RC oscillator (LSI RC): this is configured by the LSION bit in the RCC_CSR register.

- • External 32.768 kHz oscillator (LSE OSC): this is configured by the LSEON bit in the RCC_CSR register.

The ADC can also consume power in Stop mode, unless they are disabled before entering it. To disable them, the ADDIS bit in the ADC_CR register must be set to 1.

Exiting Stop mode

Refer to Section 6.3.6: Exiting low-power mode and to Table 35 for details on how to exit Stop mode.

When exiting Stop mode by issuing an interrupt or a wakeup event, the MSI or HSI16 RC oscillator is selected as system clock depending the bit STOPWUCK in the RCC_CFGR register.

When the voltage regulator operates in low-power mode, an additional startup delay is incurred when waking up from Stop mode. By keeping the internal regulator ON during Stop mode, the consumption is higher although the startup time is reduced.

Table 35. Stop mode

| Stop mode | Description |

|---|---|

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

Note: To enter the Stop mode, all EXTI Line pending bits (in Section 12.5.6: EXTI pending register (EXTI_PR) ), all peripherals interrupt pending bits, the RTC Alarm (Alarm A and Alarm B), RTC wakeup, RTC tamper, and RTC time-stamp flags, must be reset. Otherwise, the Stop mode entry procedure is ignored and program execution continues. | |

| Mode entry | On return from ISR while:

Note: To enter the Stop mode, all EXTI Line pending bits (in Section 12.5.6: EXTI pending register (EXTI_PR) ), all peripherals interrupt pending bits, the RTC Alarm (Alarm A and Alarm B), RTC wakeup, RTC tamper, and RTC time-stamp flags, must be reset. Otherwise, the Stop mode entry procedure is ignored and program execution continues. |

| Mode exit | If WFI or return from ISR was used for entry: Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). Refer to Table 49: List of vectors . If WFE was used for entry and SEVONPEND = 0 Any EXTI Line configured in event mode. Refer to Section 12.3.2: Wakeup event management on page 243 If WFE was used for entry and SEVONPEND = 1

|

| Wakeup latency | MSI or HSI16 RC wakeup time + regulator wakeup time from Low-power mode + FLASH wakeup time |

6.3.10 Standby mode

The Standby mode allows to achieve the lowest power consumption. It is based on the Cortex ® -M0+ DeepSleep mode, with the voltage regulator disabled. The V CORE domain is consequently powered off. The PLL, the MSI, the HSI16 oscillator and the HSE oscillator are also switched off. SRAM and register contents are lost except for the RTC registers, RTC backup registers and Standby circuitry (see Figure 10 ).

I/O states in Standby mode

In Standby mode, all I/O pins are high impedance except for:

- • Reset pad

- • Wakeup pins (WKUP1, WKUP2, WKUP3)

- • RTC functions (tamper, time-stamp, RTC Alarm out, RTC clock calibration out) on the following I/Os:

- – Category 1: PA0, PA2

- – Category 2: PC13, PA0, PA2

- – Category 3: PC13, PA0

- – Category 5: PC13, PA0, PE6

Entering Standby mode

Refer to Section 6.3.5: Entering low-power mode and to Table 36 for details on how to enter Standby mode.

In Standby mode, the following features can be selected by programming individual control bits:

- • Independent watchdog (IWDG): the IWDG is started by writing to its Key register or by hardware option. Once started it cannot be stopped except by a reset. Refer to Section 17.3: IWDG functional description on page 445 .

- • Real-time clock (RTC): this is configured by the RTCEN bit in the RCC_CSR register (see Section 7.3.20 ).

- • Internal RC oscillator (LSI RC): this is configured by the LSION bit in the RCC_CSR register.

- • External 32.768 kHz oscillator (LSE OSC): this is configured by the LSEON bit in the RCC_CSR register.

Exiting Standby mode

The microcontroller exits Standby mode when an external Reset (NRST pin), an IWDG Reset, a rising edge on WKUP pins (WKUP1, WKUP2 or WKUP3), an RTC alarm, a tamper event, or a time-stamp event is detected.

After waking up from Standby mode, program execution restarts in the same way as after a Reset (boot pins sampling, vector reset is fetched, etc.). The SBF status flag in the PWR_CSR register (see Section 6.4.2 ) indicates that the MCU was in Standby mode. All registers are reset to their default value after a system reset except for the register bits in the RTC domain (see Section 19.7: RTC registers , SBF status flag in the PWR power control/status register (PWR_CSR) , Control/status register (RCC_CSR) and Clock control register (RCC_CR) ).

Refer to Section 6.3.6: Exiting low-power mode and to Table 36 for more details on how to exit Standby mode.

Table 36. Standby mode

| Standby mode | Description |

|---|---|

| Mode entry | WFI (Wait for Interrupt) or WFE (Wait for Event) while:

On return from ISR while:

|

| Mode exit | WKUP pin rising edge, RTC alarm (Alarm A and Alarm B), RTC wakeup, tamper event, time-stamp event, external reset in NRST pin, IWDG reset. |

| Wakeup latency | Reset phase |

Debug mode

By default, the debug connection is lost if the application puts the MCU in Stop or Standby mode while the debug features are used. This is due to the fact that the Cortex®-M0+ core is no longer clocked.

However, by setting some configuration bits in the DBG_CR register, the software can be debugged even when using the low-power modes extensively. For more details, refer to Section 24.9.1: Debug support for low-power modes .

6.3.11 Waking up the device from Stop and Standby modes using the RTC

The MCU can be woken up from low-power mode by an RTC Alarm event, an RTC Wakeup event, a tamper event or a time-stamp event, without depending on an external interrupt (Auto-wakeup mode).

These RTC alternate functions can wake up the system from Stop and Standby low-power modes.

The system can also wake up from low-power modes without depending on an external interrupt (Auto-wakeup mode) by using the RTC alarm or the RTC wakeup events.

The RTC provides a programmable time base for waking up from Stop or Standby mode at regular intervals. For this purpose, two of the three alternative RTC clock sources can be selected by programming the RTCSEL[1:0] bits in the RCC_CSR register (see Section 7.3.20 ):

- • Low-power 32.768 kHz external crystal oscillator (LSE OSC).

This clock source provides a precise time base with very low-power consumption (less than 1 µA added consumption in typical conditions) - • Low-power internal RC oscillator (LSI RC)

This clock source has the advantage of saving the cost of the 32.768 kHz crystal. This internal RC Oscillator is designed to use minimum power consumption.

RTC auto-wakeup (AWU) from the Stop mode

- • To wake up from the Stop mode with an RTC alarm event, it is necessary to:

- a) Configure the EXTI Line 17 to be sensitive to rising edges (Interrupt or Event modes)

- b) Enable the RTC Alarm interrupt in the RTC_CR register

- c) Configure the RTC to generate the RTC alarm

- • To wake up from the Stop mode with an RTC Tamper or time stamp event, it is necessary to:

- a) Configure the EXTI Line 19 to be sensitive to rising edges (Interrupt or Event modes)

- b) Enable the RTC TimeStamp Interrupt in the RTC_CR register or the RTC Tamper Interrupt in the RTC_TCR register

- c) Configure the RTC to detect the tamper or time stamp event

- • To wake up from the Stop mode with an RTC Wakeup event, it is necessary to:

- a) Configure the EXTI Line 20 to be sensitive to rising edges (Interrupt or Event modes)

- b) Enable the RTC Wakeup Interrupt in the RTC_CR register

- c) Configure the RTC to generate the RTC Wakeup event

RTC auto-wakeup (AWU) from the Standby mode

- • To wake up from the Standby mode with an RTC alarm event, it is necessary to:

- a) Enable the RTC Alarm interrupt in the RTC_CR register

- b) Configure the RTC to generate the RTC alarm

- • To wake up from the Stop mode with an RTC Tamper or time stamp event, it is necessary to:

- a) Enable the RTC TimeStamp Interrupt in the RTC_CR register or the RTC Tamper Interrupt in the RTC_TCR register

- b) Configure the RTC to detect the tamper or time stamp event

- • To wake up from the Stop mode with an RTC Wakeup event, it is necessary to:

- a) Enable the RTC Wakeup Interrupt in the RTC_CR register

- b) Configure the RTC to generate the RTC Wakeup event

6.4 Power control registers

The peripheral registers have to be accessed by half-words (16-bit) or words (32-bit).

6.4.1 PWR power control register (PWR_CR)

Address offset: 0x00

Reset value: 0x0000 1000 (reset by wakeup from Standby mode)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | LPDS |

| rw | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | LPRUN | DS_EE_KOFF | VOS[1:0] | FWU | ULP | DBP | Res. | Res. | Res. | Res. | CSBF | CWUF | PDDS | LPSDSR | |

| rw | rw | rw | rw | rw | rw | rw | rc_w1 | rc_w1 | rw | rw | |||||

Bits 31:17 Reserved, always read as 0.

Bit 16 LPDS : Regulator in Low-power deepsleep mode

This bit allows switching the regulator to low-power mode when the CPU enters Stop mode. Its behavior depends on LPSDSR bit.

- – if LPSDSR = 1: bit has no effect.

- – if LPSDSR = 0:

0: Voltage regulator in Main mode during Deepsleep mode (Stop mode)

1: Voltage regulator switches to low-power mode when the CPU enters Deepsleep mode (Stop mode).

The regulator goes back to Main mode when the CPU exits from Deepsleep mode.

Note: The LPDS bit is available on category 1 devices only.

Bit 15 Reserved, always read as 0.

Bit 14 LPRUN : Low-power run mode

When LPRUN bit is set together with the LPSDSR bit, the regulator is switched from Main mode to low-power mode. Otherwise, it remains in Main mode. The regulator goes back to operate in Main mode when LPRUN is reset.

If this bit is set (with LPSDSR bit set) and the CPU enters sleep or Deepsleep mode (LP sleep or Stop mode), then, when the CPU wakes up from these modes, it enters Run mode but with LPRUN bit set. To enter again Low-power run mode, it is necessary to perform a reset and set LPRUN bit again.

It is forbidden to reset LPSDSR when the MCU is in Low-power run mode. LPSDSR is used as a prepositioning for the entry into low-power mode, indicating to the system which configuration of the regulator will be selected when entering low-power mode. The LPSDSR bit must be set before the LPRUN bit is set. LPSDSR can be reset only when LPRUN bit=0.

0: Voltage regulator in Main mode in Low-power run mode

1: Voltage regulator in low-power mode in Low-power run mode

Bit 13 DS_EE_KOFF : Deepsleep mode with non-volatile memory kept off

When entering low-power mode (Stop or Standby only), if DS_EE_KOFF and RUN_PD bits are both set in FLASH_ACR register (refer to Section 3.7.1: Access control register (FLASH_ACR) ), the non-volatile memory (Flash program memory and data EEPROM) will not be woken up when exiting from Deepsleep mode.

0: NVM woken up when exiting from Deepsleep mode even if the bit RUN_PD is set

1: NVM not woken up when exiting from low-power mode (if the bit RUN_PD is set)

Bits 12:11 VOS[1:0] : Voltage scaling range selectionThese bits are used to select the internal regulator voltage range.

Before resetting the power interface by resetting the PWRRST bit in the

RCC_APB1RSTR register, these bits have to be set to '10' and the frequency of the system has to be configured accordingly.

00: forbidden (bits are unchanged and keep the previous value, no voltage change occurs)

01: 1.8 V (range 1)

10: 1.5 V (range 2)

11: 1.2 V (range 3)

Bit 10 FWU : Fast wakeupThis bit works in conjunction with ULP bit.

If ULP = 0, FWU is ignored

If ULP = 1 and FWU = 1: V REFINT startup time is ignored when exiting from low-power mode. The VREFINTRDYF flag in the PWR_CSR register indicates when the V REFINT is ready again.

If ULP=1 and FWU = 0: Exiting from low-power mode occurs only when the V REFINT is ready (after its startup time). This bit is not reset by resetting the PWRRST bit in the RCC_APB1RSTR register.

0: Low-power modes exit occurs only when V REFINT is ready

1: V REFINT start up time is ignored when exiting low-power modes

Bit 9 ULP : Ultra-low-power modeWhen set, the V REFINT is switched off in low-power mode. The BOR also relies on the voltage reference. This bit is not reset by resetting the PWRRST bit in the RCC_APB1RSTR register.

0: V REFINT is on in low-power mode

1: V REFINT is off in low-power mode

Bit 8 DBP : Disable backup write protectionIn reset state, the RTC, RTC backup registers and RCC CSR register are protected against parasitic write access. This bit must be set to enable write access to these registers.

0: Access to RTC, RTC Backup and RCC CSR registers disabled

1: Access to RTC, RTC Backup and RCC CSR registers enabled

Note: If the HSE divided by 2, 4, 8 or 16 is used as the RTC clock, this bit must remain set to 1.

Bits 7:4 Reserved, always read as 0.

Bit 3 CSBF : Clear standby flagThis bit is always read as 0.

0: No effect

1: Clear the SBF Standby flag (write).

Bit 2 CWUF : Clear wakeup flagThis bit is always read as 0.

0: No effect

1: Clear the WUF Wakeup flag after 2 system clock cycles

Bit 1 PDDS : Power-down deepsleepThis bit is set and cleared by software.

0: Enter Stop mode when the CPU enters Deepsleep.

1: Enter Standby mode when the CPU enters Deepsleep.

Bit 0 LPDSR : Low-power deepsleep/Sleep/Low-power run– DeepSleep/Sleep modes

When this bit is set, the regulator switches in low-power mode when the CPU enters sleep or Deepsleep mode. The regulator goes back to Main mode when the CPU exits from these modes.

– Low-power run mode

When this bit is set, the regulator switches in low-power mode when the bit LPRUN is set. The regulator goes back to Main mode when the bit LPRUN is reset.

This bit is set and cleared by software.

0: Voltage regulator on during Deepsleep/Sleep/Low-power run mode

1: Voltage regulator in low-power mode during Deepsleep/Sleep/Low-power run mode

Note: If the sequence below is executed:

1) Low-power run

2) Low-power sleep

3) Run

4) Low-power run

after returning from Low-power deepsleep/Sleep mode (step 2), the regulator goes back to Main mode (step 3). Then to switch to Low-power run mode (step 4), it is necessary to perform a reset and set LPDSR bit again.

6.4.2 PWR power control/status register (PWR_CSR)

Address offset: 0x04

Reset value: 0x0000 0008 (not reset by wakeup from Standby mode)

Additional APB cycles are needed to read this register versus a standard APB read.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | Res. | EWUP3 | EWUP2 | EWUP1 | Res. | Res. | REG LPF | VOSF | VREFIN TRDYF | Res. | SBF | WUF |

| rw | rw | rw | r | r | r | r | r |

Bits 31:11 Reserved, must be kept at reset value.

Bit 10 EWUP3 : Enable WKUP pin 3

This bit is set and cleared by software.

0: WKUP pin 3 is used for general purpose I/Os. An event on the WKUP pin 3 does not wakeup the device from Standby mode.

1: WKUP pin 3 is used for wakeup from Standby mode and forced in input pull down configuration (rising edge on WKUP pin 3 wakes-up the system from Standby mode).

Note: This bit is reset by a system reset.

Bit 9 EWUP2 : Enable WKUP pin 2

This bit is set and cleared by software.

0: WKUP pin 2 is used for general purpose I/Os. An event on the WKUP pin 2 does not wakeup the device from Standby mode.

1: WKUP pin 2 is used for wakeup from Standby mode and forced in input pull down configuration (rising edge on WKUP pin 2 wakes-up the system from Standby mode).

Note: This bit is reset by a system reset.

Bit 8 EWUP1 : Enable WKUP pin 1

This bit is set and cleared by software.

0: WKUP pin 1 is used for general purpose I/Os. An event on the WKUP pin 1 does not wakeup the device from Standby mode.

1: WKUP pin 1 is used for wakeup from Standby mode and forced in input pull down configuration (rising edge on WKUP pin 1 wakes-up the system from Standby mode).

Note: This bit is reset by a system reset.

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 REGLPF : Regulator LP flag

This bit is set by hardware when the MCU is in Low-power run mode.

When the MCU exits from Low-power run mode, this bit stays at 1 until the regulator is ready in Main mode. A polling on this bit is recommended to wait for the regulator Main mode. This bit is reset by hardware when the regulator is ready.

0: Regulator is ready in Main mode

1: Regulator voltage is in low-power mode

Bit 4 VOSF : Voltage Scaling select flag

A delay is required for the internal regulator to be ready after the voltage range is changed. The VOSF bit indicates that the regulator has reached the voltage level defined with bits VOS of PWR_CR register.

This bit is set when \( VOS[1:0] \) in PWR_CR register change.

It is reset once the regulator is ready.

0: Regulator is ready in the selected voltage range

1: Regulator voltage output is changing to the required VOS level.

Bit 3 VREFINTRDYF : Internal voltage reference ( \( V_{REFINT} \) ) ready flag

This bit indicates the state of the internal voltage reference, \( V_{REFINT} \) .

0: \( V_{REFINT} \) is OFF

1: \( V_{REFINT} \) is ready

Bit 2 Reserved, must be kept at reset value.

Bit 1 SBF : Standby flag

This bit is set by hardware and cleared only by a POR/PDR (power-on reset/power-down reset) or by setting the CSBF bit in the PWR power control register (PWR_CR)

0: Device has not been in Standby mode

1: Device has been in Standby mode

Bit 0 WUF : Wakeup flag

This bit is set by hardware and cleared by a system reset or by setting the CWUF bit in the PWR power control register (PWR_CR)

0: No wakeup event occurred

1: A wakeup event was received from the WKUP pin or from the RTC alarm (Alarm A or Alarm B), RTC Tamper event, RTC Timestamp event or RTC Wakeup).

Note: An additional wakeup event is detected if the WKUP pins are enabled (by setting the EWUPx (x=1, 2, 3) bits) when the WKUP pin levels are already high.

6.4.3 PWR register map

The following table summarizes the PWR registers.

Table 37. PWR - register map and reset values

| Offset | Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x000 | PWR_CR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | LPDS | Res. | LPRUN | DS_EE_KOFF | VOS [1:0] | FWU | ULP | DBP | Res. | Res. | Res. | Res. | CSBF | CWUF | PDDS | LPDSR | |

| Reset value | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||

| 0x004 | PWR_CSR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | EWUP3 | EWUP2 | EWUP1 | Res. | Res. | REGLPF | VOSF | VREFINTRDYF | Res. | SBF | WUF | |

| Reset value | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

Refer to Section 2.2 on page 39 for the register boundary addresses.