34. Low-power universal asynchronous receiver transmitter (LPUART)

This section describes the low-power universal asynchronous receiver transmitter (LPUART).

34.1 LPUART introduction

The LPUART is an UART which enables bidirectional UART communications with a limited power consumption. Only 32.768 kHz LSE clock is required to enable UART communications up to 9600 baud. Higher baud rates can be reached when the LPUART is clocked by clock sources different from the LSE clock.

Even when the device is in low-power mode, the LPUART can wait for an incoming UART frame while having an extremely low energy consumption. The LPUART includes all necessary hardware support to make asynchronous serial communications possible with minimum power consumption.

It supports half-duplex single-wire communications and modem operations (CTS/RTS).

It also supports multiprocessor communications.

DMA (direct memory access) can be used for data transmission/reception.

34.2 LPUART main features

- • Full-duplex asynchronous communications

- • NRZ standard format (mark/space)

- • Programmable baud rate

- • From 300 baud to 9600 baud using a 32.768 kHz clock source.

- • Higher baud rates can be achieved by using a higher frequency clock source

- • Two internal FIFOs to transmit and receive data

Each FIFO can be enabled/disabled by software and come with status flags for FIFOs states. - • Dual clock domain with dedicated kernel clock for peripherals independent from PCLK.

- • Programmable data word length (7 or 8 or 9 bits)

- • Programmable data order with MSB-first or LSB-first shifting

- • Configurable stop bits (1 or 2 stop bits)

- • Single-wire half-duplex communications

- • Continuous communications using DMA

- • Received/transmitted bytes are buffered in reserved SRAM using centralized DMA.

- • Separate enable bits for transmitter and receiver

- • Separate signal polarity control for transmission and reception

- • Swappable Tx/Rx pin configuration

- • Hardware flow control for modem and RS-485 transceiver

- • Transfer detection flags:

- – Receive buffer full

- – Transmit buffer empty

- – Busy and end of transmission flags

- • Parity control:

- – Transmits parity bit

- – Checks parity of received data byte

- • Four error detection flags:

- – Overrun error

- – Noise detection

- – Frame error

- – Parity error

- • Interrupt sources with flags

- • Multiprocessor communications: wake-up from mute mode by idle line detection or address mark detection

34.3 LPUART implementation

The table(s) below describe(s) LPUART implementation. It(they) also include(s) USARTs for comparison.

Table 194. Instance implementation on STM32G0x1

| USART / LPUART instances | STM32G0x31xx, STM32G0x41xx, STM32G0x51xx, STM32G0x61xx | STM32G0x71xx, STM32G0x81xx | STM32G0xB1xx, STM32G0xC1xx |

|---|---|---|---|

| USART1 | FULL | FULL | FULL |

| USART2 | BASIC | FULL | FULL |

| USART3 | - | BASIC | FULL |

| USART4 | - | BASIC | BASIC |

| USART5 | - | - | BASIC |

| USART6 | - | - | BASIC |

| LPUART1 | LP | LP | LP |

| LPUART2 | - | - | LP |

Table 195. USART / LPUART features

| USART / LPUART modes/features (1) | Full feature set | Basic feature set | Low-power feature set |

|---|---|---|---|

| Hardware flow control for modem | X | X | X |

| Continuous communication using DMA | X | X | X |

| Multiprocessor communication | X | X | X |

| Synchronous mode (Master/Slave) | X | X | - |

| Smartcard mode | X | - | - |

| Single-wire half-duplex communication | X | X | X |

| IrDA SIR ENDEC block | X | - | - |

| LIN mode | X | - | - |

| Dual clock domain and wake-up from low-power mode | X | - | X |

| Receiver timeout interrupt | X | - | - |

| Modbus communication | X | - | - |

| Auto baud rate detection | X | - | - |

| Driver Enable | X | X | X |

| USART data length | 7, 8 and 9 bits | ||

| Tx/Rx FIFO | X | - | X |

| Tx/Rx FIFO size | 8 | - | 8 |

| Prescaler | X | - | X |

| Wake-up from low-power mode | X (2) | - | X (2) |

1. X = supported.

2. Wake-up supported from Stop 0 and Stop 1 modes.

34.4 LPUART functional description

34.4.1 LPUART block diagram

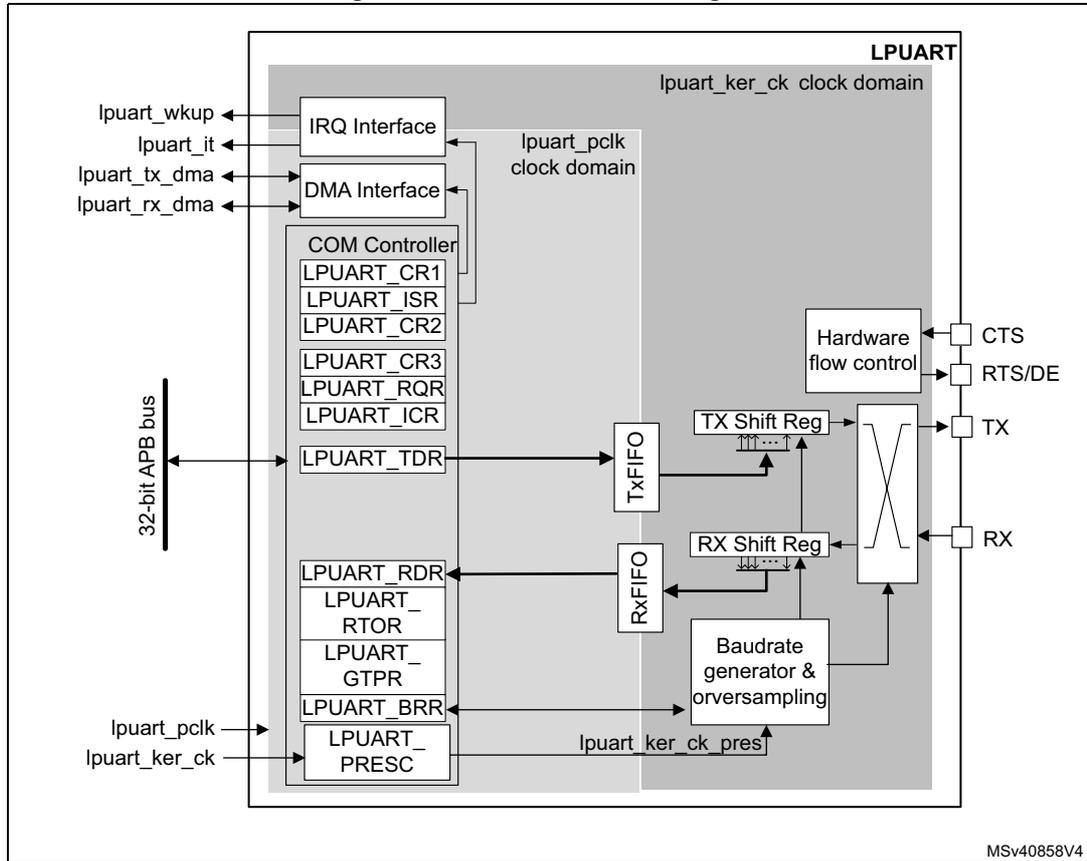

Figure 341. LPUART block diagram

The simplified block diagram given in Figure 341 shows two fully independent clock domains:

- • The lpuart_pclk clock domain

The lpuart_pclk clock signal feeds the peripheral bus interface. It must be active when accesses to the LPUART registers are required.

- • The lpuart_ker_ck kernel clock domain

The lpuart_ker_ck is the LPUART clock source. It is independent of the lpuart_pclk and delivered by the RCC. So, the LPUART registers can be written/read even when the lpuart_ker_ck is stopped.

When the dual clock domain feature is disabled, the lpuart_ker_ck is the same as the lpuart_pclk clock.

There is no constraint between lpuart_pclk and lpuart_ker_ck : lpuart_ker_ck can be faster or slower than lpuart_pclk , with no more limitation than the ability for the software to manage the communication fast enough.

34.4.2 LPUART signals

LPUART bidirectional communications requires a minimum of two pins: Receive Data In (RX) and Transmit Data Out (TX):

- •

RX

(Receive Data Input)

RX is the serial data input. - • TX (Transmit Data Output)

When the transmitter is disabled, the output pin returns to its I/O port configuration. When the transmitter is enabled and nothing is to be transmitted, the TX pin is at high level. In single-wire mode, this I/O is used to transmit and receive the data.

RS232 hardware flow control mode

The following pins are required in RS232 hardware flow control mode:

- •

CTS

(Clear To Send)

When driven high, this signal blocks the data transmission at the end of the current transfer. - •

RTS

(Request to send)

When it is low, this signal indicates that the USART is ready to receive data.

RS485 hardware flow control mode

The following pin is required in RS485 hardware control mode:

- •

DE

(Driver Enable)

This signal activates the transmission mode of the external transceiver.

Note: DE and RTS share the same pin.

Refer to Table 196 and Table 197 for the list of USART input/output pins and internal signals.

Table 196. LPUART input/output pins

| Pin name | Signal type | Description |

|---|---|---|

| LPUART_RX | Input | Serial data receive input |

| LPUART_TX | Output | Transmit data output |

| LPUART_CTS | Input | Clear to send |

| LPUART_RTS | Output | Request to send |

| LPUART_DE (1) | Output | Driver enable |

- 1. LPUART_DE and LPUART_RTS share the same pin.

Description of USART input/output signals

Table 197. LPUART internal input/output signals

| Pin name | Signal type | Description |

|---|---|---|

| lpuart_pclk | Input | APB clock |

| lpuart_ker_ck | Input | USART kernel clock |

Table 197. LPUART internal input/output signals (continued)

| Pin name | Signal type | Description |

|---|---|---|

| lpuart_wkup | Output | USART provides a wake-up interrupt |

| lpuart_it | Output | USART global interrupt |

| lpuart_tx_dma | Input/output | USART transmit DMA request |

| lpuart_rx_dma | Input/output | USART receive DMA request |

34.4.3 LPUART character description

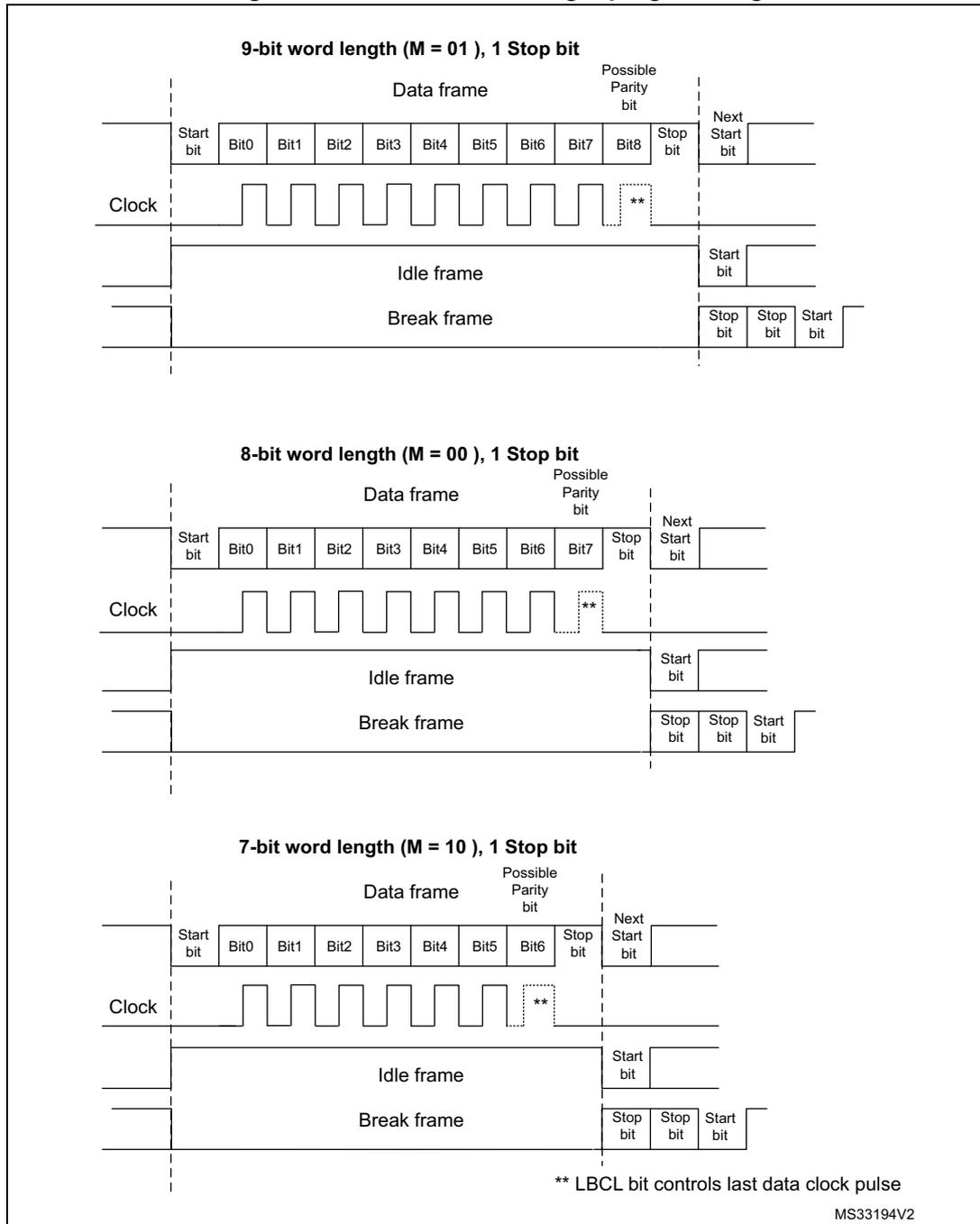

The word length can be set to 7 or 8 or 9 bits, by programming the M bits (M0: bit 12 and M1: bit 28) in the LPUART_CR1 register (see Figure 315 ).

- • 7-bit character length: M[1:0] = '10'

- • 8-bit character length: M[1:0] = '00'

- • 9-bit character length: M[1:0] = '01'

By default, the signal (TX or RX) is in low state during the start bit. It is in high state during the stop bit.

These values can be inverted, separately for each signal, through polarity configuration control.

An Idle character is interpreted as an entire frame of "1"s. (The number of "1" 's includes the number of stop bits).

A Break character is interpreted on receiving "0"s for a frame period. At the end of the break frame, the transmitter inserts 2 stop bits.

Transmission and reception are driven by a common baud rate generator. The transmission and reception clocks are generated when the enable bit is set for the transmitter and receiver, respectively.

The details of each block is given below.

Figure 342. LPUART word length programming

The diagram illustrates the timing for three different word lengths with one stop bit. Each section shows a 'Data frame', an 'Idle frame', and a 'Break frame' relative to a 'Clock' signal.

- 9-bit word length (M = 01), 1 Stop bit:

- Data frame: Start bit, Bit0 through Bit8, Possible Parity bit, Stop bit, followed by the Next Start bit.

- Idle frame: A high level followed by a Start bit.

- Break frame: Two Stop bits followed by a Start bit.

- 8-bit word length (M = 00), 1 Stop bit:

- Data frame: Start bit, Bit0 through Bit7, Possible Parity bit, Stop bit, followed by the Next Start bit.

- Idle frame: A high level followed by a Start bit.

- Break frame: Two Stop bits followed by a Start bit.

- 7-bit word length (M = 10), 1 Stop bit:

- Data frame: Start bit, Bit0 through Bit6, Possible Parity bit, Stop bit, followed by the Next Start bit.

- Idle frame: A high level followed by a Start bit.

- Break frame: Two Stop bits followed by a Start bit.

** LBCL bit controls last data clock pulse

MS33194V2

34.4.4 LPUART FIFOs and thresholds

The LPUART can operate in FIFO mode.

The LPUART comes with a Transmit FIFO (TXFIFO) and a Receive FIFO (RXFIFO). The FIFO mode is enabled by setting FIFOEN bit (bit 29) in LPUART_CR1 register.

Since the maximum data word length is 9 bits, the TXFIFO is 9-bit wide. However the RXFIFO default width is 12 bits. This is due to the fact that the receiver does not only store

the data in the FIFO, but also the error flags associated to each character (Parity error, Noise error and Framing error flags).

Note: The received data is stored in the RXFIFO together with the corresponding flags. However, only the data are read when reading the RDR.

The status flags are available in the LPUART_ISR register.

It is possible to define the TXFIFO and RXFIFO levels at which the Tx and RX interrupts are triggered. These thresholds are programmed through RXFTCFG and TXFTCFG bitfields in LPUART_CR3 control register.

In this case:

- • The RXFT flag is set in the LPUART_ISR register and the corresponding interrupt (if enabled) is generated, when the number of received data in the RXFIFO reaches the threshold programmed in the RXFTCFG bits fields.

This means that the RXFIFO is filled until the number of data in the RXFIFO is equal to the programmed threshold.

RXFTCFG data have been received: one data in LPUART_RDR and (RXFTCFG - 1) data in the RXFIFO. As an example, when the RXFTCFG is programmed to '101', the RXFT flag is set when a number of data corresponding to the FIFO size has been received: FIFO size - 1 data in the RXFIFO and 1 data in the LPUART_RDR. As a result, the next received data does not set the overrun flag.

- • The TXFT flag is set in the LPUART_ISR register and the corresponding interrupt (if enabled) is generated when the number of empty locations in the TXFIFO reaches the threshold programmed in the TXFTCFG bits fields.

This means that the TXFIFO is emptied until the number of empty locations in the TXFIFO is equal to the programmed threshold.

34.4.5 LPUART transmitter

The transmitter can send data words of either 7 or 8 or 9 bits, depending on the M bit status. The Transmit Enable bit (TE) must be set in order to activate the transmitter function. The data in the transmit shift register is output on the TX pin.

Character transmission

During an LPUART transmission, data shifts out least significant bit first (default configuration) on the TX pin. In this mode, the LPUART_TDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 341 ).

When FIFO mode is enabled, the data written to the LPUART_TDR register are queued in the TXFIFO.

Every character is preceded by a start bit which corresponds to a low logic level for one bit period. The character is terminated by a configurable number of stop bits.

The number of stop bits can be 1 or 2.

Note: The TE bit must be set before writing the data to be transmitted to the LPUART_TDR.

The TE bit should not be reset during data transmission. Resetting the TE bit during the transmission corrupts the data on the TX pin as the baud rate counters is frozen. The current data being transmitted are lost.

An idle frame is sent after the TE bit is enabled.

Configurable stop bits

The number of stop bits to be transmitted with every character can be programmed in LPUART_CR2 (bits 13,12).

- • 1 stop bit: This is the default value of number of stop bits.

- • 2 Stop bits: This is supported by normal LPUART, single-wire and modem modes.

An idle frame transmission includes the stop bits.

A break transmission is 10 low bits (when M[1:0] = '00') or 11 low bits (when M[1:0] = '01') or 9 low bits (when M[1:0] = '10') followed by 2 stop bits. It is not possible to transmit long breaks (break of length greater than 9/10/11 low bits).

Figure 343. Configurable stop bits

![Figure 343. Configurable stop bits. The diagram shows two timing diagrams for 8-bit word length (M[1:0]=00). Part (a) shows '1 Stop bit' configuration, where the frame consists of a Start bit, 8 Data bits (Bit0-Bit7), a Possible parity bit, a Stop bit, and a Next start bit. Part (b) shows '2 Stop bits' configuration, where the frame consists of a Start bit, 8 Data bits (Bit0-Bit7), a Possible parity bit, 2 Stop bits, and a Next start bit. Both diagrams include a CLOCK signal and a note that the LBCL bit controls the last data clock pulse. The diagram is labeled MS31885V1.](/RM0444-STM32G0x1/a2290c23188cf3e4efcf58a46d6f0396_img.jpg)

8-bit Word length (M[1:0]=00 bit is reset)

a) 1 Stop bit

CLOCK

Start bit Data frame (Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Bit7) Possible parity bit Stop bit Next start bit Next data frame

** LBCL bit controls last data clock pulse

b) 2 Stop bits

Start bit Data frame (Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Bit7) Possible parity bit 2 Stop bits Next start bit Next data frame

MS31885V1

Character transmission procedure

To transmit a character, follow the sequence below:

- 1. Program the M bits in LPUART_CR1 to define the word length.

- 2. Select the desired baud rate using the LPUART_BRR register.

- 3. Program the number of stop bits in LPUART_CR2.

- 4. Enable the LPUART by writing the UE bit in LPUART_CR1 register to '1'.

- 5. Select DMA enable (DMAT) in LPUART_CR3 if Multi buffer Communication is to take place. Configure the DMA register as explained in Section 34.4.12: Continuous communication using DMA and LPUART .

- 6. Set the TE bit in LPUART_CR1 to send an idle frame as first transmission.

- 7. Write the data to send in the LPUART_TDR register. Repeat this operation for each data to be transmitted in case of single buffer.

- – When FIFO mode is disabled, writing a data in the LPUART_TDR clears the TXE flag.

- – When FIFO mode is enabled, writing a data in the LPUART_TDR adds one data to the TXFIFO. Write operations to the LPUART_TDR are performed when TXFNF flag is set. This flag remains set until the TXFIFO is full.

- 8. When the last data is written to the LPUART_TDR register, wait until TC = 1. This indicates that the transmission of the last frame is complete.

- – When FIFO mode is disabled, this indicates that the transmission of the last frame is complete.

- – When FIFO mode is enabled, this indicates that both TXFIFO and shift register are empty.

This check is required to avoid corrupting the last transmission when the LPUART is disabled or enters Halt mode.

Single byte communication

- • When FIFO mode disabled:

Writing to the transmit data register always clears the TXE bit. The TXE flag is set by hardware to indicate that:

- – the data have been moved from the LPUART_TDR register to the shift register and data transmission has started;

- – the LPUART_TDR register is empty;

- – the next data can be written to the LPUART_TDR register without overwriting the previous data.

The TXE flag generates an interrupt if the TXEIE bit is set.

When a transmission is ongoing, a write instruction to the LPUART_TDR register stores the data in the TDR register, which is copied to the shift register at the end of the current transmission.

When no transmission is ongoing, a write instruction to the LPUART_TDR register places the data in the shift register, the data transmission starts, and the TXE bit is set.

- • When FIFO mode is enabled, the TXFNF (TXFIFO Not Full) flag is set by hardware to indicate that:

- – the TXFIFO is not full;

- – the LPUART_TDR register is empty;

- – the next data can be written to the LPUART_TDR register without overwriting the previous data. When a transmission is ongoing, a write operation to the LPUART_TDR register stores the data in the TXFIFO. Data are copied from the TXFIFO to the shift register at the end of the current transmission.

When the TXFIFO is not full, the TXFNF flag stays at '1' even after a write in LPUART_TDR. It is cleared when the TXFIFO is full. This flag generates an interrupt if TXFNEIE bit is set.

Alternatively, interrupts can be generated and data can be written to the TXFIFO when the TXFIFO threshold is reached. In this case, the CPU can write a block of data defined by the programmed threshold.

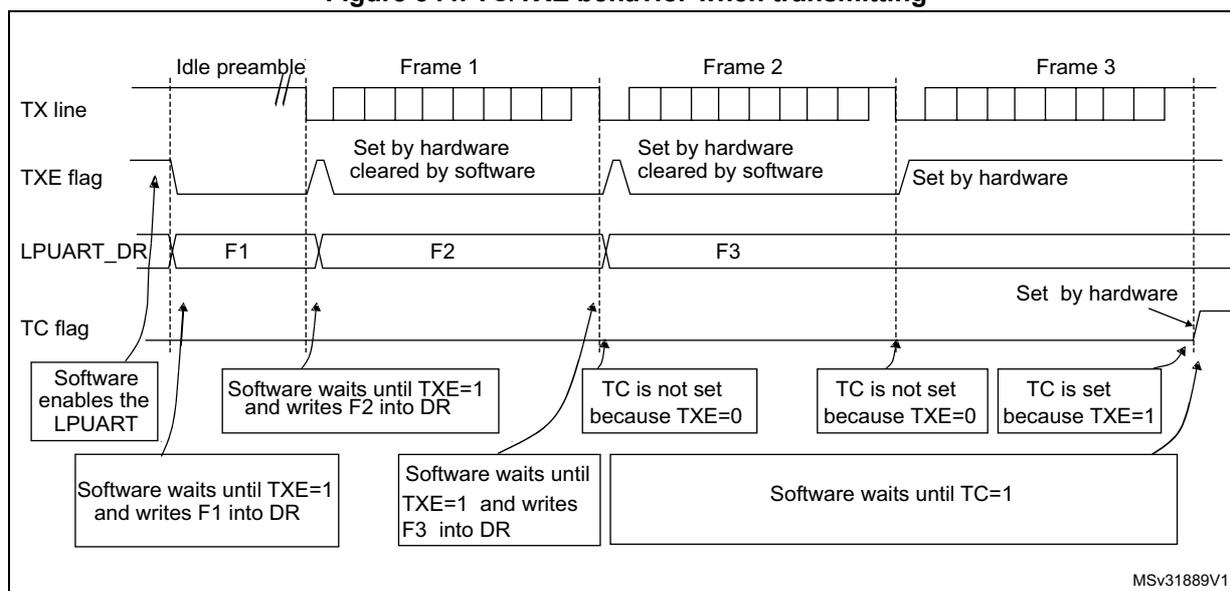

If a frame is transmitted (after the stop bit) and the TXE flag (TXFE is case of FIFO mode) is set, the TC bit goes high. An interrupt is generated if the TCIE bit is set in the LPUART_CR1 register.

After writing the last data in the LPUART_TDR register, it is mandatory to wait for TC = 1 before disabling the LPUART or causing the device to enter the low-power mode (see Figure 344: TC/TXE behavior when transmitting ).

Figure 344. TC/TXE behavior when transmitting

The diagram illustrates the timing and flag behavior for transmitting three frames (Frame 1, Frame 2, Frame 3) after an idle preamble. The signals shown are TX line, TXE flag, LPUART_DR, and TC flag.

- TX line: Shows the idle preamble followed by the transmission of Frame 1, Frame 2, and Frame 3.

- TXE flag:

- Is set by hardware when the LPUART_DR register is empty and cleared by software when a new data word is written.

- For Frame 1 and Frame 2, it is set by hardware when the register is empty and cleared by software when the next data word (F2 or F3) is written.

- For Frame 3, it is set by hardware when the register is empty and remains set until the transmission is complete.

- LPUART_DR: Shows the data words F1, F2, and F3 being written into the register.

- TC flag:

- Is set by hardware when the transmission is complete (TXE=1).

- For Frame 1, TC is not set because TXE=0 (F2 is being written).

- For Frame 2, TC is not set because TXE=0 (F3 is being written).

- For Frame 3, TC is set because TXE=1 (transmission complete).

Software interaction:

- Software enables the LPUART.

- Software waits until TXE=1 and writes F1 into DR.

- Software waits until TXE=1 and writes F2 into DR.

- Software waits until TXE=1 and writes F3 into DR.

- Software waits until TC=1 (after Frame 3 transmission complete).

MSv31889V1

Note: When FIFO management is enabled, the TXFNF flag is used for data transmission.

Break characters

Setting the SBKRQ bit transmits a break character. The break frame length depends on the M bits (see Figure 342 ).

If a '1' is written to the SBKRQ bit, a break character is sent on the TX line after completing the current character transmission. The SBKF bit is set by the write operation and it is reset by hardware when the break character is completed (during the stop bits after the break character). The LPUART inserts a logic 1 signal (STOP) for the duration of 2 bits at the end of the break frame to guarantee the recognition of the start bit of the next frame.

When the SBKRQ bit is set, the break character is sent at the end of the current transmission.

When FIFO mode is enabled, sending the break character has priority on sending data even if the TXFIFO is full.

Idle characters

Setting the TE bit drives the LPUART to send an idle frame before the first data frame.

34.4.6 LPUART receiver

The LPUART can receive data words of either 7 or 8 or 9 bits depending on the M bits in the LPUART_CR1 register.

Start bit detection

In the LPUART, the start bit is detected when a falling edge occurs on the Rx line, followed by a sample taken in the middle of the start bit to confirm that it is still '0'. If the start sample is at '1', then the noise error flag (NE) is set, then the start bit is discarded and the receiver waits for a new start bit. Else, the receiver continues to sample all incoming bits normally.

Character reception

During an LPUART reception, data are shifted in least significant bit first (default configuration) through the RX pin. In this mode, the LPUART_RDR register consists of a buffer (RDR) between the internal bus and the received shift register.

Character reception procedure

To receive a character, follow the sequence below:

- 1. Program the M bits in LPUART_CR1 to define the word length.

- 2. Select the desired baud rate using the baud rate register LPUART_BRR

- 3. Program the number of stop bits in LPUART_CR2.

- 4. Enable the LPUART by writing the UE bit in LPUART_CR1 register to '1'.

- 5. Select DMA enable (DMAR) in LPUART_CR3 if multibuffer communication is to take place. Configure the DMA register as explained in Section 34.4.12: Continuous communication using DMA and LPUART .

- 6. Set the RE bit LPUART_CR1. This enables the receiver which begins searching for a start bit.

When a character is received

- • When FIFO mode is disabled, the RXNE bit is set. It indicates that the content of the shift register is transferred to the RDR. In other words, data has been received and can be read (as well as its associated error flags).

- • When FIFO mode is enabled, the RXFNE bit is set indicating that the RXFIFO is not empty. Reading the LPUART_RDR returns the oldest data entered in the RXFIFO. When a data is received, it is stored in the RXFIFO, together with the corresponding error bits.

- • An interrupt is generated if the RXNEIE (RXFNEIE in case of FIFO mode) bit is set.

- • The error flags can be set if a frame error, noise or an overrun error has been detected during reception.

- • In multibuffer communication mode:

- – When FIFO mode is disabled, the RXNE flag is set after every byte received and is cleared by the DMA read of the Receive Data Register.

- – When FIFO mode is enabled, the RXFNE flag is set when the RXFIFO is not empty. After every DMA request, a data is retrieved from the RXFIFO. DMA request is triggered by RXFIFO is not empty i.e. there is a data in the RXFIFO to be read.

- • In single buffer mode:

- – When FIFO mode is disabled, clearing the RXNE flag is done by performing a software read from the LPUART_RDR register. The RXNE flag can also be cleared by writing 1 to the RXFRQ in the LPUART_RQR register. The RXNE bit must be cleared before the end of the reception of the next character to avoid an overrun error.

- – When FIFO mode is enabled, the RXFNE flag is set when the RXFIFO is not empty. After every read operation from the LPUART_RDR register, a data is retrieved from the RXFIFO. When the RXFIFO is empty, the RXFNE flag is cleared. The RXFNE flag can also be cleared by writing 1 to the RXFRQ bit in the LPUART_RQR register. When the RXFIFO is full, the first entry in the RXFIFO must be read before the end of the reception of the next character to avoid an overrun error. The RXFNE flag generates an interrupt if the RXFNEIE bit is set.

Alternatively, interrupts can be generated and data can be read from RXFIFO when the RXFIFO threshold is reached. In this case, the CPU can read a block of data defined by the programmed threshold.

Break character

When a break character is received, the LPUART handles it as a framing error.

Idle character

When an idle frame is detected, it is handled in the same way as a data character reception except that an interrupt is generated if the IDLEIE bit is set.

Overrun error

- • FIFO mode disabled

An overrun error occurs when a character is received when RXNE has not been reset. Data can not be transferred from the shift register to the RDR register until the RXNE bit is cleared. The RXNE flag is set after every byte received.

An overrun error occurs if RXNE flag is set when the next data is received or the previous DMA request has not been serviced. When an overrun error occurs:

- – the ORE bit is set;

- – the RDR content is not lost. The previous data is available when a read to LPUART_RDR is performed.;

- – the shift register is overwritten. After that, any data received during overrun is lost.

- – an interrupt is generated if either the RXNEIE bit or EIE bit is set.

- • FIFO mode enabled

An overrun error occurs when the shift register is ready to be transferred when the receive FIFO is full.

Data can not be transferred from the shift register to the LPUART_RDR register until there is one free location in the RXFIFO. The RXFNE flag is set when the RXFIFO is not empty.

An overrun error occurs if the RXFIFO is full and the shift register is ready to be transferred. When an overrun error occurs:

- – the ORE bit is set;

- – the first entry in the RXFIFO is not lost. It is available when a read to LPUART_RDR is performed.

- – the shift register is overwritten. After that, any data received during overrun is lost.

- – an interrupt is generated if either the RXFNEIE bit or EIE bit is set.

The ORE bit is reset by setting the ORECF bit in the ICR register.

Note: The ORE bit, when set, indicates that at least 1 data has been lost. T

When the FIFO mode is disabled, there are two possibilities

- • if RXNE = 1, then the last valid data is stored in the receive register (RDR) and can be read,

- • if RXNE = 0, then the last valid data has already been read and there is nothing left to be read in the RDR. This case can occur when the last valid data is read in the RDR at the same time as the new (and lost) data is received.

Selecting the clock source

The choice of the clock source is done through the Clock Control system (see Section Reset and clock controller (RCC) ). The clock source must be selected through the UE bit, before enabling the LPUART.

The clock source must be selected according to two criteria:

- • Possible use of the LPUART in low-power mode

- • Communication speed.

The clock source frequency is lpuart_ker_ck.

When the dual clock domain and the wake-up from low-power mode features are supported, the lpuart_ker_ck clock source can be configured in the RCC (see Section Reset and clock controller (RCC) ). Otherwise, the lpuart_ker_ck is the same as lpuart_pclk.

The lpuart_ker_ck can be divided by a programmable factor in the LPUART_PRESC register.

Figure 345. lpuart_ker_ck clock divider block diagram

![Block diagram of the lpuart_ker_ck clock divider. The input lpuart_ker_ck enters a block containing LPUARTx_PRESC[3:0] and LPUARTx_BRR register and oversampling. The output is lpuart_ker_ck_pres. The diagram is labeled MSv40859V1.](/RM0444-STM32G0x1/7c64823403d8f8d4a9c0c3ffaca812b4_img.jpg)

graph LR

subgraph Block [ ]

direction LR

A[LPUARTx_PRESC[3:0]] -- lpuart_ker_ck_pres --> B[LPUARTx_BRR register and oversampling]

end

lpuart_ker_ck --> A

style Block fill:none,stroke:none

style lpuart_ker_ck_pres stroke:none,stroke-width:0px

style MSv40859V1 fill:none,stroke:none

Some lpuart_ker_ck sources enable the LPUART to receive data while the MCU is in low-power mode. Depending on the received data and wake-up mode selection, the LPUART wakes up the MCU, when needed, in order to transfer the received data by software reading the LPUART_RDR register or by DMA.

For the other clock sources, the system must be active to enable LPUART communications.

The communication speed range (specially the maximum communication speed) is also determined by the clock source.

The receiver samples each incoming bit as close as possible to the middle of the bit-period. Only a single sample is taken of each of the incoming bits.

Note: There is no noise detection for data.

Framing error

A framing error is detected when the stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

When the framing error is detected:

- • the FE bit is set by hardware;

- • the invalid data is transferred from the Shift register to the LPUART_RDR register.

- • no interrupt is generated in case of single byte communication. However this bit rises at the same time as the RXNE bit which itself generates an interrupt. In case of

multibuffer communication, an interrupt is issued if the EIE bit is set in the LPUART_CR3 register.

The FE bit is reset by writing 1 to the FECF in the LPUART_ICR register.

Configurable stop bits during reception

The number of stop bits to be received can be configured through the control bits of LPUART_CR2: it can be either 1 or 2 in normal mode.

- • 1 stop bit: sampling for 1 stop bit is done on the 8th, 9th and 10th samples.

- • 2 stop bits: sampling for the 2 stop bits is done in the middle of the second stop bit. The RXNE and FE flags are set just after this sample i.e. during the second stop bit. The first stop bit is not checked for framing error.

34.4.7 LPUART baud rate generation

The baud rate for the receiver and transmitter (Rx and Tx) are both set to the value programmed in the LPUART_BRR register.

LPUARTDIV is defined in the LPUART_BRR register.

Note: The baud counters are updated to the new value in the baud registers after a write operation to LPUART_BRR. Hence the baud rate register value should not be changed during communication.

It is forbidden to write values lower than 0x300 in the LPUART_BRR register.

\( f_{CK} \) must range from 3 x baud rate to 4096 x baud rate.

The maximum baud rate that can be reached when the LPUART clock source is the LSE, is 9600 baud. Higher baud rates can be reached when the LPUART is clocked by clock sources different from the LSE clock. For example, if the LPUART clock source frequency is 100 MHz, the maximum baud rate that can be reached is about 33 Mbaud.

Table 198. Error calculation for programmed baud rates at lpuart_ker_ck_pres = 32.768 kHz

| Baud rate | lpuart_ker_ck_pres = 32.768 kHz | |||

|---|---|---|---|---|

| S.No | Desired | Actual | Value programmed in the baud rate register | % Error = (Calculated - Desired) B.rate / Desired B.rate |

| 1 | 300 bauds | 300 baud | 0x6D3A | 0 |

| 2 | 600 baud | 600 baud | 0x369D | 0 |

| 3 | 1200 baud | 1200.087 baud | 0x1B4E | 0.007 |

| 4 | 2400 baud | 2400.17 baud | 0xDA7 | 0.007 |

| 5 | 4800 baud | 4801.72 baud | 0x6D3 | 0.035 |

| 6 | 9600 baud | 9608.94 baud | 0x369 | 0.093 |

| Baud rate | \( f_{CK} = 100\text{MHz} \) | |||

|---|---|---|---|---|

| S.No | Desired | Actual | Value programmed in the baud rate register | % Error = (Calculated - Desired) B.rate / Desired B.rate |

| 1 | 38400 Baud | 38400,04 Baud | A2C2A | 0,0001 |

| 2 | 57600 Baud | 57600,06 Baud | 6C81C | 0,0001 |

| 3 | 115200 Baud | 115200,12 Baud | 3640E | 0,0001 |

| 4 | 230400 Baud | 230400,23 Baud | 1B207 | 0,0001 |

| 5 | 460800 Baud | 460804,61 Baud | D903 | 0,001 |

| 6 | 921600 Baud | 921625,81 Baud | 6C81 | 0,0028 |

| 7 | 4000 KBaud | 4000000,00 Baud | 1900 | 0 |

| 8 | 10000 Kbaud | 10000000,00 Baud | A00 | 0 |

| 9 | 20000 Kbaud | 20000000,00 Baud | 500 | 0 |

| 10 | 33000 Kbaud | 33032258,06 Baud | 307 | 0,1 |

34.4.8 Tolerance of the LPUART receiver to clock deviation

The asynchronous receiver of the LPUART works correctly only if the total clock system deviation is less than the tolerance of the LPUART receiver. The causes which contribute to the total deviation are:

- • DTRA: deviation due to the transmitter error (which also includes the deviation of the transmitter's local oscillator)

- • DQUANT: error due to the baud rate quantization of the receiver

- • DREC: deviation of the receiver local oscillator

- • DTCL: deviation due to the transmission line (generally due to the transceivers which can introduce an asymmetry between the low-to-high transition timing and the high-to-low transition timing)

where

DWU is the error due to sampling point deviation when the wake-up from low-power mode is used.

The LPUART receiver can receive data correctly at up to the maximum tolerated deviation specified in Table 200 :

- • Number of Stop bits defined through STOP[1:0] bits in the LPUART_CR2 register

- • LPUART_BRR register value.

Table 200. Tolerance of the LPUART receiver

| M bits | 768 < BRR < 1024 | 1024 < BRR < 2048 | 2048 < BRR < 4096 | 4096 ≤ BRR |

|---|---|---|---|---|

| 8 bits (M = '00'), 1 Stop bit | 1.82% | 2.56% | 3.90% | 4.42% |

| 9 bits (M = '01'), 1 Stop bit | 1.69% | 2.33% | 2.53% | 4.14% |

| 7 bits (M = '10'), 1 Stop bit | 2.08% | 2.86% | 4.35% | 4.42% |

| 8 bits (M = '00'), 2 Stop bit | 2.08% | 2.86% | 4.35% | 4.42% |

| 9 bits (M = '01'), 2 Stop bit | 1.82% | 2.56% | 3.90% | 4.42% |

| 7 bits (M = '10'), 2 Stop bit | 2.34% | 3.23% | 4.92% | 4.42% |

Note: The data specified in Table 200 may slightly differ in the special case when the received frames contain some Idle frames of exactly 10-bit times when M bits = '00' (11-bit times when M = '01' or 9- bit times when M = '10').

34.4.9 LPUART multiprocessor communication

It is possible to perform LPUART multiprocessor communications (with several LPUARTs connected in a network). For instance one of the LPUARTs can be the master, with its TX output connected to the RX inputs of the other LPUARTs. The others are slaves, with their respective TX outputs are logically ANDed together and connected to the RX input of the master.

In multiprocessor configurations it is often desirable that only the intended message recipient actively receives the full message contents, thus reducing redundant LPUART service overhead for all non addressed receivers.

The non addressed devices can be placed in mute mode by means of the muting function. To use the mute mode feature, the MME bit must be set in the LPUART_CR1 register.

Note: When FIFO management is enabled and MME is already set, MME bit must not be cleared and then set again quickly (within two lpuart_ker_ck cycles), otherwise mute mode might remain active.

When the mute mode is enabled:

- • none of the reception status bits can be set;

- • all the receive interrupts are inhibited;

- • the RWU bit in LPUART_ISR register is set to '1'. RWU can be controlled automatically by hardware or by software, through the MMRQ bit in the LPUART_RQR register, under certain conditions.

The LPUART can enter or exit from mute mode using one of two methods, depending on the WAKE bit in the LPUART_CR1 register:

- • Idle Line detection if the WAKE bit is reset,

- • Address Mark detection if the WAKE bit is set.

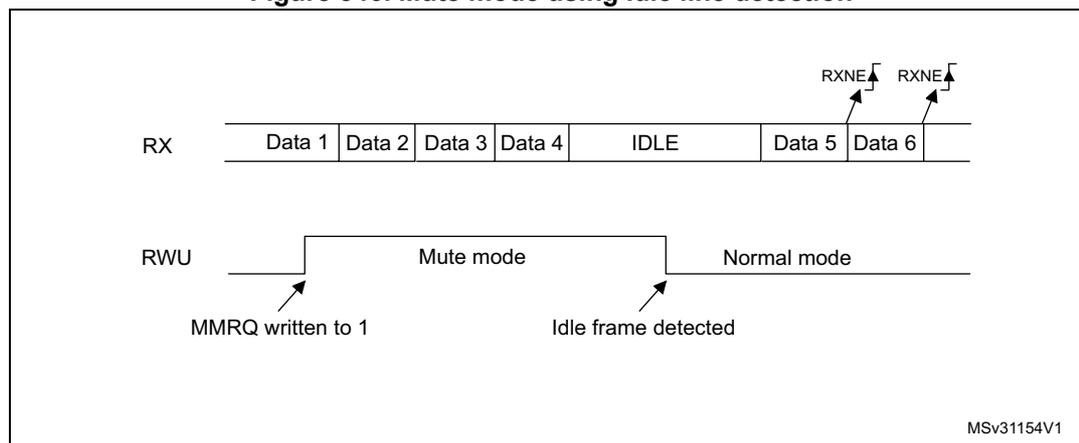

Idle line detection (WAKE = 0)

The LPUART enters mute mode when the MMRQ bit is written to 1 and the RWU is automatically set.

The LPUART wakes up when an Idle frame is detected. The RWU bit is then cleared by hardware but the IDLE bit is not set in the LPUART_ISR register. An example of mute mode behavior using Idle line detection is given in Figure 346 .

Figure 346. Mute mode using Idle line detection

The diagram shows two horizontal timelines. The top timeline, labeled 'RX', shows a sequence of data frames: 'Data 1', 'Data 2', 'Data 3', 'Data 4', followed by an 'IDLE' frame, then 'Data 5', and 'Data 6'. Above 'Data 5' and 'Data 6', there are arrows pointing to the RXNE flag, indicating that the RXNE flag is set for these frames. The bottom timeline, labeled 'RWU', shows the state of the RWU bit. It starts at a low level, then jumps to a high level when 'MMRQ written to 1' occurs, entering 'Mute mode'. It returns to a low level when 'Idle frame detected' occurs, returning to 'Normal mode'. The text 'MSv31154V1' is in the bottom right corner.

Note: If the MMRQ is set while the IDLE character has already elapsed, the mute mode is not entered (RWU is not set).

If the LPUART is activated while the line is IDLE, the idle state is detected after the duration of one IDLE frame (not only after the reception of one character frame).

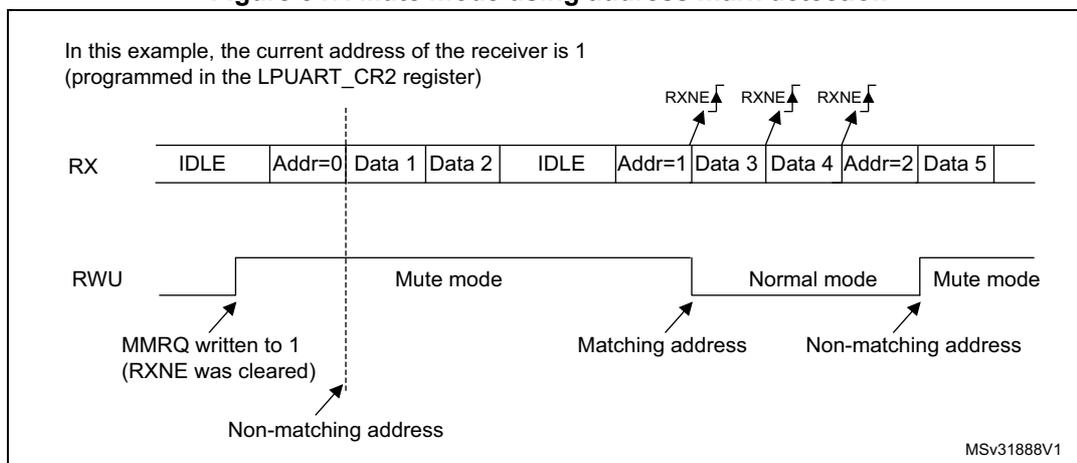

4-bit/7-bit address mark detection (WAKE = 1)

In this mode, bytes are recognized as addresses if their MSB is a '1' otherwise they are considered as data. In an address byte, the address of the targeted receiver is put in the 4 or 7 LSBs. The choice of 7 or 4 bit address detection is done using the ADDM7 bit. This 4-bit/7-bit word is compared by the receiver with its own address which is programmed in the ADD bits in the LPUART_CR2 register.

Note: In 7-bit and 9-bit data modes, address detection is done on 6-bit and 8-bit addresses (ADD[5:0] and ADD[7:0]) respectively.

The LPUART enters mute mode when an address character is received which does not match its programmed address. In this case, the RWU bit is set by hardware. The RXNE flag is not set for this address byte and no interrupt or DMA request is issued when the LPUART enters mute mode.

The LPUART also enters mute mode when the MMRQ bit is written to '1'. The RWU bit is also automatically set in this case.

The LPUART exits from mute mode when an address character is received which matches the programmed address. Then the RWU bit is cleared and subsequent bytes are received normally. The RXNE/RXFNE bit is set for the address character since the RWU bit has been cleared.

Note: When FIFO management is enabled, when MMRQ bit is set while the receiver is sampling the last bit of a data, this data may be received before effectively entering in mute mode.

An example of mute mode behavior using address mark detection is given in Figure 347 .

Figure 347. Mute mode using address mark detection

In this example, the current address of the receiver is 1 (programmed in the LPUART_CR2 register)

MSv31888V1

34.4.10 LPUART parity control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the LPUART_CR1 register. Depending on the frame length defined by the M bits, the possible LPUART frame formats are as listed in Table 201 .

Table 201: LPUART frame formats

| M bits | PCE bit | LPUART frame (1) |

|---|---|---|

| 00 | 0 | | SB | 8 bit data | STB | |

| 00 | 1 | | SB | 7-bit data | PB | STB | |

| 01 | 0 | | SB | 9-bit data | STB | |

| 01 | 1 | | SB | 8-bit data PB | STB | |

| 10 | 0 | | SB | 7bit data | STB | |

| 10 | 1 | | SB | 6-bit data | PB | STB | |

1. Legends: SB: start bit, STB: stop bit, PB: parity bit.

2. In the data register, the PB is always taking the MSB position (8th or 7th, depending on the M bit value).

Even parity

The parity bit is calculated to obtain an even number of “1s” inside the frame which is made of the 6, 7 or 8 LSB bits (depending on M bit values) and the parity bit.

As an example, if data equal 00110101, and 4 bits are set, then the parity bit is equal to 0 if even parity is selected (PS bit in LPUART_CR1 = 0).

Odd parity

The parity bit is calculated to obtain an odd number of “1s” inside the frame made of the 6, 7 or 8 LSB bits (depending on M bit values) and the parity bit.

As an example, if data equal 00110101 and 4 bits set, then the parity bit is equal to 1 if odd parity is selected (PS bit in LPUART_CR1 = 1).

Parity checking in reception

If the parity check fails, the PE flag is set in the LPUART_ISR register and an interrupt is generated if PEIE is set in the LPUART_CR1 register. The PE flag is cleared by software writing 1 to the PECF in the LPUART_ICR register.

Parity generation in transmission

If the PCE bit is set in LPUART_CR1, then the MSB bit of the data written in the data register is transmitted but is changed by the parity bit (even number of “1s” if even parity is selected (PS = 0) or an odd number of “1s” if odd parity is selected (PS = 1)).

34.4.11 LPUART single-wire half-duplex communication

Single-wire half-duplex mode is selected by setting the HDSEL bit in the LPUART_CR3 register. In this mode, the following bits must be kept cleared:

- • LINEN and CLKEN bits in the LPUART_CR2 register,

- • SCEN and IREN bits in the LPUART_CR3 register.

The LPUART can be configured to follow a single-wire half-duplex protocol where the TX and RX lines are internally connected. The selection between half- and Full-duplex communication is made with a control bit HDSEL in LPUART_CR3.

As soon as HDSEL is written to ‘1’:

- • The TX and RX lines are internally connected.

- • The RX pin is no longer used

- • The TX pin is always released when no data is transmitted. Thus, it acts as a standard I/O in idle or in reception. It means that the I/O must be configured so that TX is configured as alternate function open-drain with an external pull-up.

Apart from this, the communication protocol is similar to normal LPUART mode. Any conflict on the line must be managed by software (for instance by using a centralized arbiter). In particular, the transmission is never blocked by hardware and continues as soon as data is written in the data register while the TE bit is set.

Note: In LPUART communications, in the case of 1-stop bit configuration, the RXNE flag is set in the middle of the stop bit.

34.4.12 Continuous communication using DMA and LPUART

The LPUART is capable of performing continuous communication using the DMA. The DMA requests for Rx buffer and Tx buffer are generated independently.

Note: Refer to Section 33.4: USART implementation on page 986 to determine if the DMA mode is supported. If DMA is not supported, use the LPUSRT as explained in Section 33.5.6 . To perform continuous communication. When FIFO is disabled, you can clear the TXE/ RXNE flags in the LPUART_ISR register.

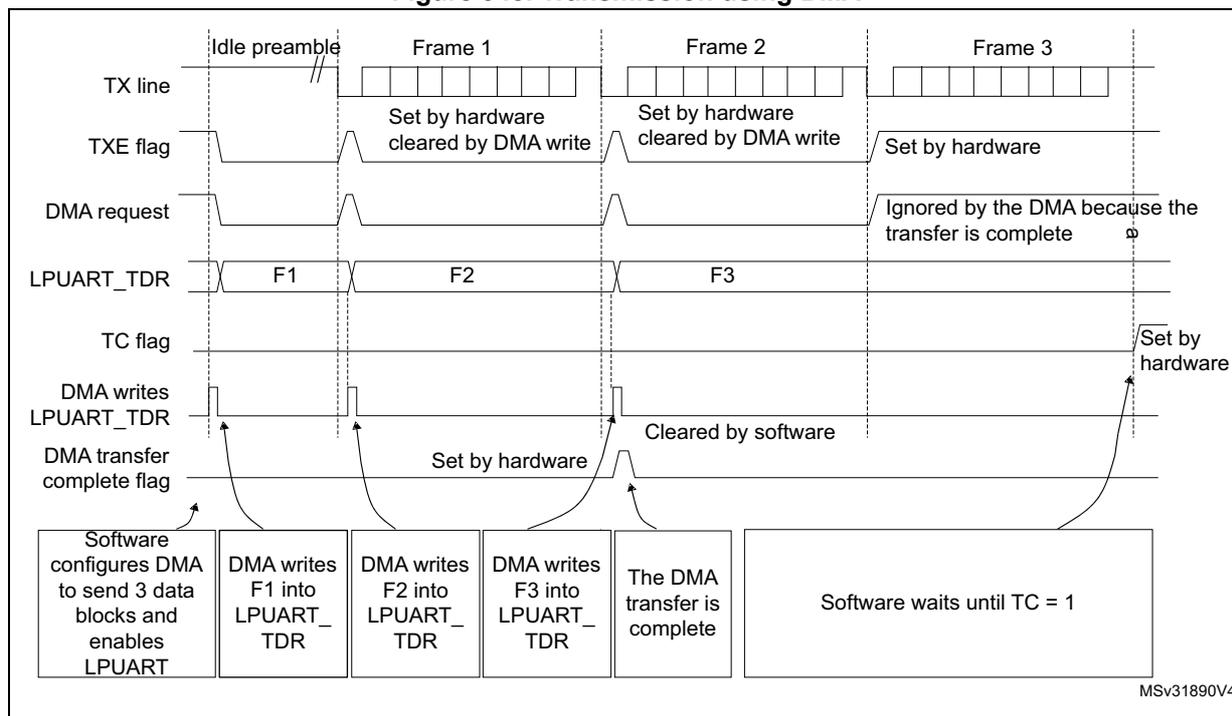

Transmission using DMA

DMA mode can be enabled for transmission by setting DMAT bit in the LPUART_CR3 register. Data are loaded from an SRAM area configured using the DMA peripheral (refer to the corresponding Direct memory access controller section ) to the LPUART_TDR register whenever the TXE flag (TXFNF flag if FIFO mode is enabled) is set. To map a DMA channel for LPUART transmission, use the following procedure (x denotes the channel number):

- 1. Write the LPUART_TDR register address in the DMA control register to configure it as the destination of the transfer. The data is moved to this address from memory after each TXE (or TXFNF if FIFO mode is enabled) event.

- 2. Write the memory address in the DMA control register to configure it as the source of the transfer. The data is loaded into the LPUART_TDR register from this memory area after each TXE (or TXFNF if FIFO mode is enabled) event.

- 3. Configure the total number of bytes to be transferred to the DMA control register.

- 4. Configure the channel priority in the DMA register

- 5. Configure DMA interrupt generation after half/ full transfer as required by the application.

- 6. Clear the TC flag in the LPUART_ISR register by setting the TCCF bit in the LPUART_ICR register.

- 7. Activate the channel in the DMA register.

When the number of data transfers programmed in the DMA Controller is reached, the DMA controller generates an interrupt on the DMA channel interrupt vector.

In transmission mode, once the DMA has written all the data to be transmitted (the TCIF flag is set in the DMA_ISR register), the TC flag can be monitored to make sure that the LPUART communication is complete. This is required to avoid corrupting the last transmission before disabling the LPUART or entering low-power mode. Software must wait until TC = 1. The TC flag remains cleared during all data transfers and it is set by hardware at the end of transmission of the last frame.

Figure 348. Transmission using DMA

The diagram illustrates the timing for DMA transmission of three frames (Frame 1, Frame 2, Frame 3) over an idle preamble. The signals shown are:

- TX line: Shows the idle preamble followed by the transmission of Frame 1, Frame 2, and Frame 3.

- TXE flag: Set by hardware when the LPUART_TDR is empty. It is cleared by a DMA write. For Frame 3, it is set by hardware but ignored by the DMA because the transfer is complete.

- DMA request: Triggered by the TXE flag. It is ignored by the DMA after the third frame because the transfer is complete.

- LPUART_TDR: The register where data is written. It contains F1, F2, and F3 for the three frames.

- TC flag: Set by hardware at the end of the last frame transmission (after Frame 3). It is cleared by software.

- DMA writes LPUART_TDR: Shows the DMA writing F1, F2, and F3 into the LPUART_TDR register.

- DMA transfer complete flag: Set by hardware when the DMA transfer is complete (after F3 is written). It is cleared by software.

Software actions shown at the bottom:

- Software configures DMA to send 3 data blocks and enables LPUART.

- DMA writes F1 into LPUART_TDR.

- DMA writes F2 into LPUART_TDR.

- DMA writes F3 into LPUART_TDR.

- The DMA transfer is complete.

- Software waits until TC = 1.

MSv31890V4

Note: When FIFO management is enabled, the DMA request is triggered by Transmit FIFO not full (i.e. TXFNF = 1).

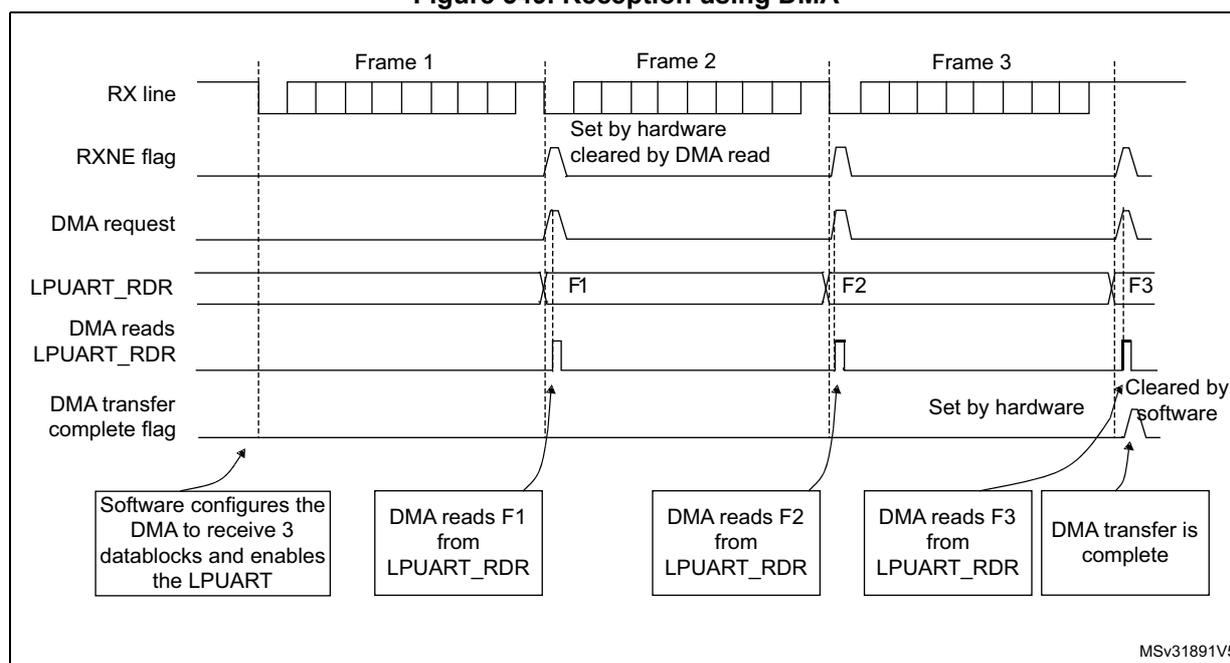

Reception using DMA

DMA mode can be enabled for reception by setting the DMAR bit in LPUART_CR3 register. Data are loaded from the LPUART_RDR register to a SRAM area configured using the DMA peripheral (refer to the corresponding Direct memory access controller (DMA) section ) whenever a data byte is received. To map a DMA channel for LPUART reception, use the following procedure:

- 1. Write the LPUART_RDR register address in the DMA control register to configure it as the source of the transfer. The data is moved from this address to the memory after each RXNE (RXFNE in case FIFO mode is enabled) event.

- 2. Write the memory address in the DMA control register to configure it as the destination of the transfer. The data is loaded from LPUART_RDR to this memory area after each RXNE (RXFNE in case FIFO mode is enabled) event.

- 3. Configure the total number of bytes to be transferred to the DMA control register.

- 4. Configure the channel priority in the DMA control register

- 5. Configure interrupt generation after half/ full transfer as required by the application.

- 6. Activate the channel in the DMA control register.

When the number of data transfers programmed in the DMA Controller is reached, the DMA controller generates an interrupt on the DMA channel interrupt vector.

Figure 349. Reception using DMA

The diagram illustrates the timing for reception using DMA across three frames (Frame 1, Frame 2, Frame 3). The signals shown are:

- RX line: Shows the incoming data for each frame. Frame 1 has 8 bytes, Frame 2 has 8 bytes, and Frame 3 has 8 bytes.

- RXNE flag: Set by hardware when a byte is received and cleared by a DMA read. It pulses high for each frame.

- DMA request: Triggered by the RXNE flag to initiate a data transfer from LPUART_RDR to memory.

- LPUART_RDR: The register containing the received data bytes (F1, F2, F3) which are read by the DMA.

- DMA reads LPUART_RDR: Shows the DMA reading the data bytes from the register.

- DMA transfer complete flag: Set by hardware when the DMA transfer is complete and cleared by software. It pulses high after the third frame.

Annotations at the bottom of the diagram:

- Software configures the DMA to receive 3 datablocks and enables the LPUART

- DMA reads F1 from LPUART_RDR

- DMA reads F2 from LPUART_RDR

- DMA reads F3 from LPUART_RDR

- DMA transfer is complete

MSV31891V5

Note: When FIFO management is enabled, the DMA request is triggered by Receive FIFO not empty (i.e. RXFNE = 1).

Error flagging and interrupt generation in multibuffer communication

If any error occurs during a transaction In multibuffer communication mode, the error flag is asserted after the current byte. An interrupt is generated if the interrupt enable flag is set. For framing error, overrun error and noise flag which are asserted with RXNE (RXFNE in case FIFO mode is enabled) in single byte reception, there is a separate error flag interrupt

enable bit (EIE bit in the LPUART_CR3 register), which, if set, enables an interrupt after the current byte if any of these errors occur.

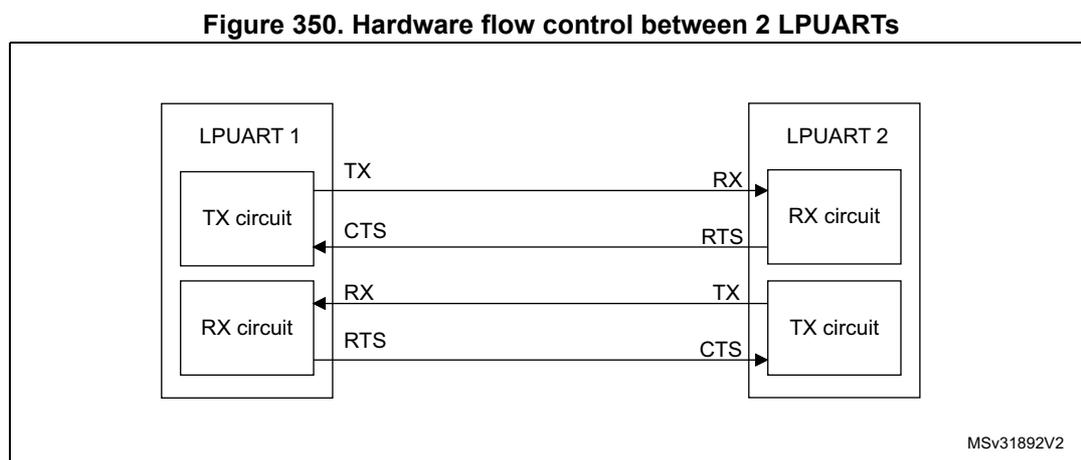

34.4.13 RS232 hardware flow control and RS485 Driver Enable

It is possible to control the serial data flow between 2 devices by using the CTS input and the RTS output. The Figure 336 shows how to connect 2 devices in this mode:

Figure 350. Hardware flow control between 2 LPUARTs

The diagram illustrates the connection between two LPUART modules, LPUART 1 and LPUART 2, for hardware flow control. LPUART 1 contains a TX circuit and an RX circuit. LPUART 2 contains an RX circuit and a TX circuit. The connections are as follows:

- The TX output of LPUART 1 is connected to the RX input of LPUART 2.

- The CTS input of LPUART 1 is connected to the RTS output of LPUART 2.

- The RX input of LPUART 1 is connected to the TX output of LPUART 2.

- The RTS output of LPUART 1 is connected to the CTS input of LPUART 2.

MSv31892V2

RS232 RTS and CTS flow control can be enabled independently by writing the RTSE and CTSE bits respectively to 1 (in the LPUART_CR3 register).

RS232 RTS flow control

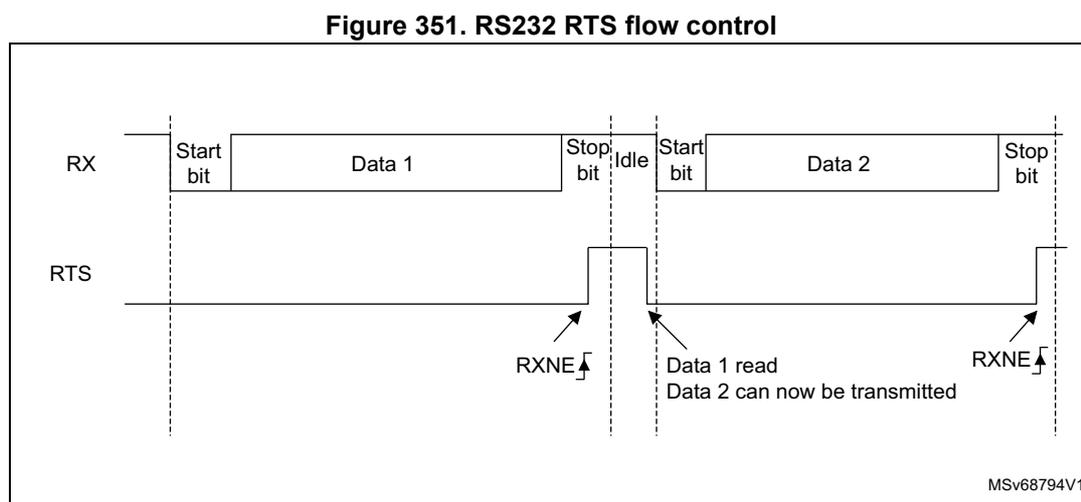

If the RTS flow control is enabled (RTSE = 1), then RTS is deasserted (tied low) as long as the LPUART receiver is ready to receive a new data. When the receive register is full, RTS is asserted, indicating that the transmission is expected to stop at the end of the current frame. Figure 351 shows an example of communication with RTS flow control enabled.

Figure 351. RS232 RTS flow control

The diagram shows the relationship between the RX (Receive) line and the RTS (Request to Send) line during two data transmissions. The RX line shows the sequence: Start bit, Data 1, Stop bit, Idle, Start bit, Data 2, Stop bit. The RTS line is initially low. When the first frame (Data 1) is received, the RXNE (Receive Not Empty) flag is set, and the RTS line goes high (asserted). When Data 1 is read from the receive register, the RXNE flag is reset, and the RTS line goes low (deasserted). When the second frame (Data 2) is received, the RXNE flag is set again, and the RTS line goes high. When Data 2 is read, the RTS line goes low again. The text "Data 1 read Data 2 can now be transmitted" is shown between the two frames when the RTS line is low.

MSv68794V1

Note: When FIFO mode is enabled, RTS is asserted only when RXFIFO is full.

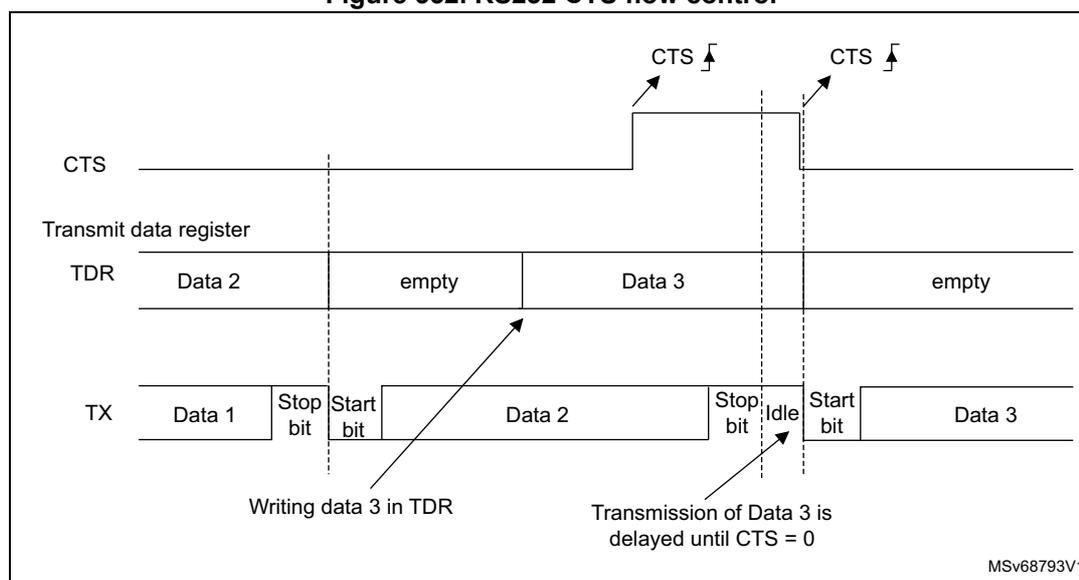

RS232 CTS flow control

If the CTS flow control is enabled (CTSE = 1), then the transmitter checks the CTS input before transmitting the next frame. If CTS is deasserted (tied low), then the next data is transmitted (assuming that data is to be transmitted, in other words, if TXE/TXFE = 0), else the transmission does not occur. When CTS is asserted during a transmission, the current transmission is completed before the transmitter stops.

When CTSE = 1, the CTSIF status bit is automatically set by hardware as soon as the CTS input toggles. It indicates when the receiver becomes ready or not ready for communication. An interrupt is generated if the CTSIE bit in the LPUART_CR3 register is set. Figure 352 shows an example of communication with CTS flow control enabled.

Figure 352. RS232 CTS flow control

The diagram illustrates the timing for RS232 CTS flow control. It consists of three horizontal timelines:

- CTS: Shows the Clear To Send signal. It starts low, goes high at the start of the second character transmission, and returns low before the start of the third character transmission. Two falling edges are marked with arrows and 'CTS'.

- Transmit data register (TDR): Shows the data to be transmitted. It contains 'Data 2', then an 'empty' state, then 'Data 3', and finally an 'empty' state. An arrow labeled 'Writing data 3 in TDR' points to the 'Data 3' entry.

- TX: Shows the actual transmitted data. It starts with 'Data 1' followed by a 'Stop bit'. Then, 'Start bit', 'Data 2', and 'Stop bit' are transmitted. An arrow from the 'empty' state of the TDR points to this sequence. After an 'Idle' state, the transmission of 'Data 3' (Start bit, Data 3, Stop bit) is delayed until the CTS signal goes low. Once CTS is low, the transmission of 'Data 3' begins. An arrow labeled 'Transmission of Data 3 is delayed until CTS = 0' points to the start of the 'Data 3' transmission.

The diagram is labeled with 'MSV68793V1' in the bottom right corner.

Note: For correct behavior, CTS must be deasserted at least 3 LPUART clock source periods before the end of the current character. In addition it should be noted that the CTSCF flag may not be set for pulses shorter than 2 x PCLK periods.

RS485 driver enable

The driver enable feature is enabled by setting bit DEM in the LPUART_CR3 control register. This enables activating the external transceiver control, through the DE (Driver Enable) signal. The assertion time is the time between the activation of the DE signal and the beginning of the start bit. It is programmed using the DEAT [4:0] bitfields in the LPUART_CR1 control register. The deassertion time is the time between the end of the last stop bit, in a transmitted message, and the de-activation of the DE signal. It is programmed using the DEDT [4:0] bitfields in the LPUART_CR1 control register. The polarity of the DE signal can be configured using the DEP bit in the LPUART_CR3 control register.

The LPUART DEAT and DEDT are expressed in LPUART clock source ( \( f_{CK} \) ) cycles:

- • The Driver enable assertion time equals

- – \( (1 + (DEAT \times P)) \times f_{CK} \) , if \( P \neq 0 \)

- – \( (1 + DEAT) \times f_{CK} \) , if \( P = 0 \)

- • The Driver enable deassertion time equals

- – \( (1 + (DEDT \times P)) \times f_{CK} \) , if \( P \neq 0 \)

- – \( (1 + DEDT) \times f_{CK} \) , if \( P = 0 \)

where \( P = BRR[20:11] \)

34.4.14 LPUART low-power management

The LPUART has advanced low-power mode functions that enable it to transfer properly data even when the lpuart_pclk clock is disabled.

The LPUART is able to wake up the MCU from low-power mode when the UESM bit is set. When the lpuart_pclk is gated, the LPUART provides a wake-up interrupt ( lpuart_wkup ) if a specific action requiring the activation of the lpuart_pclk clock is needed:

- • If FIFO mode is disabled

- –

lpuart_pclk

clock has to be activated to empty the LPUART data register.

In this case, the lpuart_wkup interrupt source is the RXNE set to '1'. The RXNEIE bit must be set before entering low-power mode.

- –

lpuart_pclk

clock has to be activated to empty the LPUART data register.

- • If FIFO mode is enabled

- –

lpuart_pclk

clock has to be activated

- – to fill the TXFIFO

- – or to empty the RXFIFO

- – RXFIFO not empty. In this case, the RXFNEIE bit must be set before entering low-power mode.

- – RXFIFO full. In this case, the RXFFIE bit must be set before entering low-power mode, the number of received data corresponds to the RXFIFO size, and the RXFF flag is not set.

- – TXFIFO empty. In this case, the TXFEIE bit must be set before entering low-power mode.

- –

lpuart_pclk

clock has to be activated

This enables sending/receiving the data in the TXFIFO/RXFIFO during low-power mode.

To avoid overrun/underrun errors and transmit/receive data in low-power mode, the lpuart_wkup interrupt source can be one of the following events:

- – TXFIFO threshold reached. In this case, the TXFTIE bit must be set before entering low-power mode.

- – RXFIFO threshold reached. In this case, the RXFTIE bit must be set before entering low-power mode.

For example, the application can set the threshold to the maximum RXFIFO size if the wake-up time is less than the time to receive a single byte across the line.

Using the RXFIFO full, TXFIFO empty, RXFIFO not empty and RXFIFO/TXFIFO threshold interrupts to wake up the MCU from low-power mode enables doing as many LPUART transfers as possible during low-power mode with the benefit of optimizing consumption.

Alternatively, a specific lpuart_wkup interrupt may be selected through the WUS bitfields.

When the wake-up event is detected, the WUF flag is set by hardware and lpuart_wkup interrupt is generated if the WUFIE bit is set.

Note: Before entering low-power mode, make sure that no LPUART transfer is ongoing. Checking the BUSY flag cannot ensure that low-power mode is never entered when data reception is ongoing.

The WUF flag is set when a wake-up event is detected, independently of whether the MCU is in low-power or in an active mode.

When entering low-power mode just after having initialized and enabled the receiver, the REACK bit must be checked to ensure the LPUART is actually enabled.

When DMA is used for reception, it must be disabled before entering low-power mode and re-enabled upon exit from low-power mode.

When FIFO is enabled, the wake-up from low-power mode on address match is only possible when mute mode is enabled.

Using mute mode with low-power mode

If the LPUART is put into mute mode before entering low-power mode:

- • Wake-up from mute mode on idle detection must not be used, because idle detection cannot work in low-power mode.

- • If the wake-up from mute mode on address match is used, then the low-power mode wake-up source must also be the address match. If the RXNE flag was set when entering the low-power mode, the interface remains in mute mode upon address match and wake up from low-power mode.

Note: When FIFO management is enabled, mute mode is used with wake-up from low-power mode without any constraints (i.e. the two points mentioned above about mute and low-power mode are valid only when FIFO management is disabled).

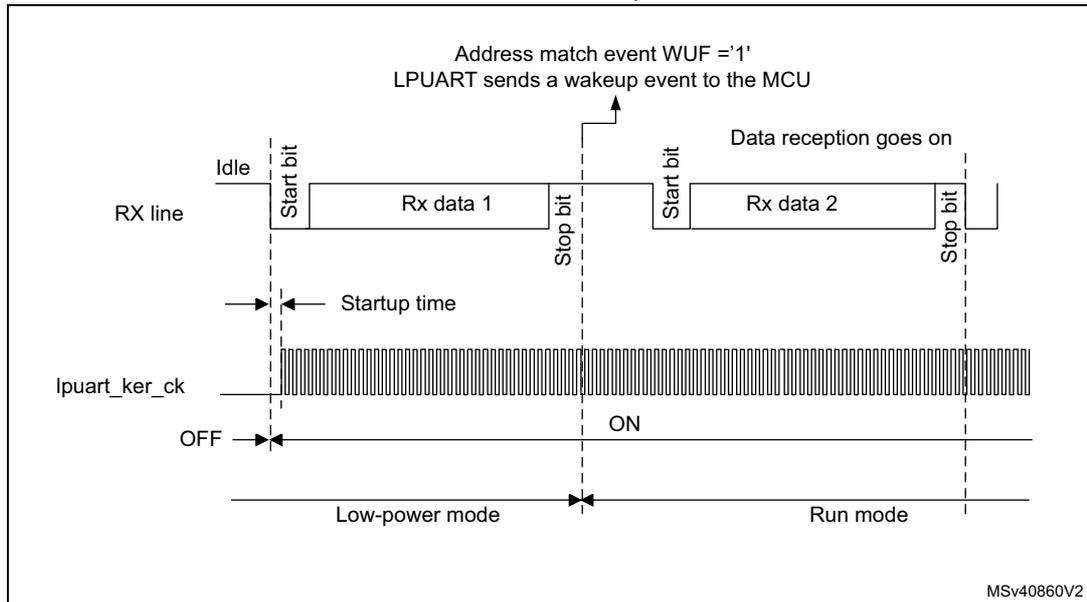

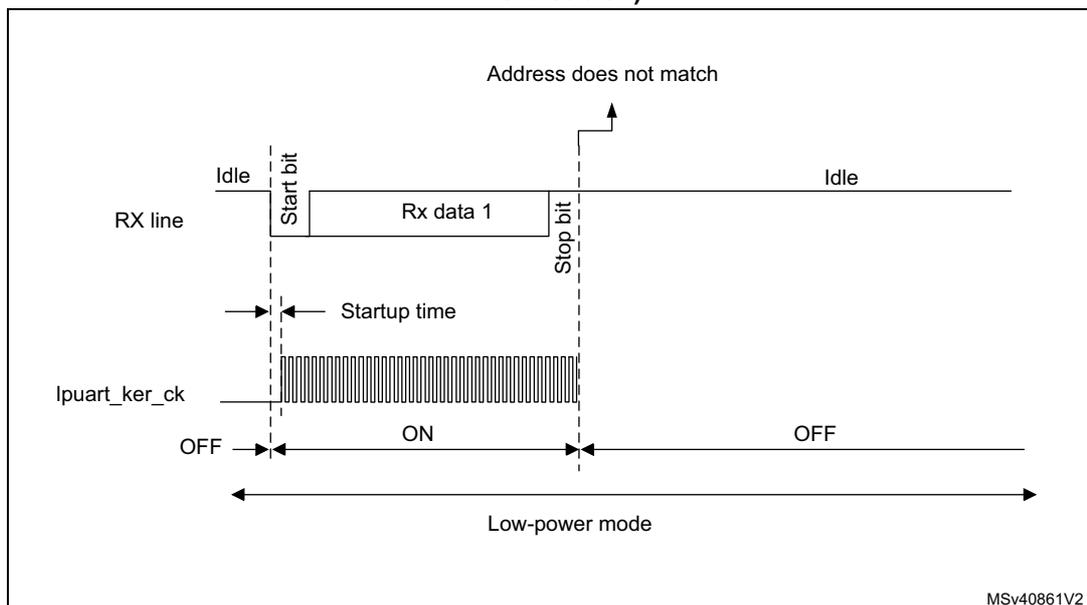

Wake-up from low-power mode when LPUART kernel clock lpuart_ker_ck is OFF in low-power mode

If during low-power mode, the lpuart_ker_ck clock is switched OFF, when a falling edge on the LPUART receive line is detected, the LPUART interface requests the lpuart_ker_ck clock to be switched ON thanks to the lpuart_ker_ck_req signal. The lpuart_ker_ck is then used for the frame reception.

If the wake-up event is verified, the MCU wakes up from low-power mode and data reception goes on normally.

If the wake-up event is not verified, the lpuart_ker_ck is switched OFF again, the MCU is not waken up and stays in low-power mode and the kernel clock request is released.

The example below shows the case of wake-up event programmed to “address match detection” and FIFO management disabled.

Figure 353 shows the behavior when the wake-up event is verified.

Figure 353. Wake-up event verified (wake-up event = address match, FIFO disabled)

Figure 354 shows the behavior when the wake-up event is not verified.

Figure 354. Wake-up event not verified (wake-up event = address match, FIFO disabled)

Note: The above figures are valid when address match or any received frame is used as wake-up event. In the case the wake-up event is the start bit detection, the LPUART sends the wake-up event to the MCU at the end of the start bit.

Determining the maximum LPUART baud rate that enables to correctly wake up the MCU from low-power mode

The maximum baud rate that enables to correctly wake up the MCU from low-power mode depends on the wake-up time parameter (refer to the device datasheet) and on the LPUART receiver tolerance (see Section 34.4.8: Tolerance of the LPUART receiver to clock deviation ).

Let us take the example of OVER8 = 0, M bits = '01', ONEBIT = 0 and BRR [3:0] = 0000.

In these conditions, according to Table 200: Tolerance of the LPUART receiver , the LPUART receiver tolerance equals 3.41%.

where \( t_{WULPUART} \) is the wake-up time from low-power mode.

If we consider the ideal case where DTRA, DQUANT, DREC and DTCL parameters are at 0%, the maximum value of DWU is 3.41%. In reality, we need to consider at least the

lpuart_ker_ck

inaccuracy.

For example, if HSI is used as

lpuart_ker_ck

, and the HSI inaccuracy is of 1%, then we obtain:

As a result, the maximum baud rate that enables to wake up correctly from low-power mode is: \( 1/11.32\ \mu\text{s} = 88.36\ \text{kbaud} \) .

34.5 LPUART in low-power modes

Table 202. Effect of low-power modes on the LPUART

| Mode | Description |

|---|---|

| Sleep | No effect. LPUART interrupts cause the device to exit Sleep mode. |

| Stop (1) | The content of the LPUART registers is kept. The LPUART is able to wake up the microcontroller from Stop mode when the LPUART is clocked by an oscillator available in Stop mode. |

| Standby | The LPUART peripheral is powered down and must be reinitialized after exiting Standby mode. |

- Refer to Section 34.3: LPUART implementation to know if the wake-up from Stop mode is supported for a given peripheral instance. If an instance is not functional in a given Stop mode, it must be disabled before entering this Stop mode.

34.6 LPUART interrupts

Refer to Table 203 for a detailed description of all LPUART interrupt requests.

Table 203. LPUART interrupt requests

| Interrupt vector | Interrupt event | Event flag | Enable Control bit | Interrupt clear method | Exit from Sleep mode | Exit from Stop (1) modes | Exit from Standby mode |

|---|---|---|---|---|---|---|---|

| LPUART | Transmit data register empty | TXE | TXEIE | Write TDR | Yes | No | No |

| Transmit FIFO Not Full | TXFNF | TXFNFIE | TXFIFO full | No | |||

| Transmit FIFO Empty | TXFE | TXFEIE | Write TDR or write 1 in TXFRQ | Yes | |||

| Transmit FIFO threshold reached | TXFT | TXFTIE | Write TDR | Yes | |||

| CTS interrupt | CTSIF | CTSIE | Write 1 in CTSCF | No | |||

| Transmission Complete | TC | TCIE | Write TDR or write 1 in TCCF | No | |||

| Receive data register not empty (data ready to be read) | RXNE | RXNEIE | Read RDR or write 1 in RXFRQ | Yes | Yes | ||

| Receive FIFO Not Empty | RXFNE | RXFNEIE | Read RDR until RXFIFO empty or write 1 in RXFRQ | Yes | |||

| Receive FIFO Full | RXFF (2) | RXFFIE | Read RDR | Yes | |||

| Receive FIFO threshold reached | RXFT | RXFTIE | Read RDR | Yes | |||

| Overrun error detected | ORE | RXNEIE/RXFNEIE | Write 1 in ORECF | No | |||

| Idle line detected | IDLE | IDLEIE | Write 1 in IDLECF | No | |||

| Parity error | PE | PEIE | Write 1 in PECF | No | |||

| Noise error in multibuffer communication. | NE | EIE | Write 1 in NFCF | No | |||

| Overrun error in multibuffer communication. | ORE (3) | Write 1 in ORECF | No | ||||

| Framing Error in multibuffer communication. | FE | Write 1 in FECF | No | ||||

| Character match | CMF | CMIE | Write 1 in CMCF | No | |||

| Wake-up from low-power mode | WUF | WUFIE | Write 1 in WUC | Yes |

- 1. The LPUART can wake up the device from Stop mode only if the peripheral instance supports the wake-up from Stop mode feature. Refer to Section 34.3: LPUART implementation for the list of supported Stop modes.

- 2. RXFF flag is asserted if the LPUART receives n+1 data (n being the RXFIFO size): n data in the RXFIFO and 1 data in LPUART_RDR. In Stop mode, LPUART_RDR is not clocked. As a result, this register is not written and once n data are received and written in the RXFIFO, the RXFF interrupt is asserted (RXFF flag is not set).

- 3. When OVRDIS = 0.

34.7 LPUART registers

Refer to Section 1.2 on page 55 for a list of abbreviations used in register descriptions.

The peripheral registers have to be accessed by words (32 bits).

34.7.1 LPUART control register 1 (LPUART_CR1)

Address offset: 0x00

Reset value: 0x0000 0000

The same register can be used in FIFO mode enabled (this section) and FIFO mode disabled (next section).

FIFO mode enabled

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| RXF FIE | TXFEIE | FIFO EN | M1 | Res. | Res. | DEAT[4:0] | DEDT[4:0] | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | CMIE | MME | M0 | WAKE | PCE | PS | PEIE | TXFN FIE | TCIE | RXFN EIE | IDLEIE | TE | RE | UESM | UE |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Bit 31 RXFIE :RXFIFO full interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated when RXFF = 1 in the LPUART_ISR register

Bit 30 TXFEIE :TXFIFO empty interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated when TXFE = 1 in the LPUART_ISR register

Bit 29 FIFOEN :FIFO mode enable

This bit is set and cleared by software.

0: FIFO mode is disabled.

1: FIFO mode is enabled.

Bit 28 M1: Word lengthThis bit must be used in conjunction with bit 12 (M0) to determine the word length. It is set or cleared by software.

M[1:0] = '00': 1 Start bit, 8 Data bits, n Stop bit

M[1:0] = '01': 1 Start bit, 9 Data bits, n Stop bit

M[1:0] = '10': 1 Start bit, 7 Data bits, n Stop bit

This bit can only be written when the LPUART is disabled (UE = 0).

Note: In 7-bit data length mode, the smartcard mode, LIN master mode and Auto baud rate (0x7F and 0x55 frames detection) are not supported.

Bits 27:26 Reserved, must be kept at reset value.

Bits 25:21 DEAT[4:0]: Driver enable assertion timeThis 5-bit value defines the time between the activation of the DE (Driver Enable) signal and the beginning of the start bit. It is expressed in lpuart_ker_ck clock cycles. For more details, refer Section 33.5.20: RS232 hardware flow control and RS485 Driver Enable .

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bits 20:16 DEDT[4:0]: Driver enable deassertion timeThis 5-bit value defines the time between the end of the last stop bit, in a transmitted message, and the de-activation of the DE (Driver Enable) signal. It is expressed in lpuart_ker_ck clock cycles. For more details, refer Section 34.4.13: RS232 hardware flow control and RS485 Driver Enable .

If the LPUART_TDR register is written during the DEDT time, the new data is transmitted only when the DEDT and DEAT times have both elapsed.

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 15 Reserved, must be kept at reset value.

Bit 14 CMIE: Character match interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: A LPUART interrupt is generated when the CMF bit is set in the LPUART_ISR register.

Bit 13 MME: Mute mode enableThis bit activates the mute mode function of the LPUART. When set, the LPUART can switch between the active and mute modes, as defined by the WAKE bit. It is set and cleared by software.

0: Receiver in active mode permanently

1: Receiver can switch between mute mode and active mode.

Bit 12 M0: Word lengthThis bit is used in conjunction with bit 28 (M1) to determine the word length. It is set or cleared by software (refer to bit 28 (M1) description).

This bit can only be written when the LPUART is disabled (UE = 0).

Bit 11 WAKE: Receiver wake-up methodThis bit determines the LPUART wake-up method from mute mode. It is set or cleared by software.

0: Idle line

1: Address mark

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 10 PCE: Parity control enableThis bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 9 PS: Parity selectionThis bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 8 PEIE: PE interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated whenever PE = 1 in the LPUART_ISR register

Bit 7 TXFNIE: TXFIFO not full interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: A LPUART interrupt is generated whenever TXE/TXFNF = 1 in the LPUART_ISR register

Bit 6 TCIE: Transmission complete interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated whenever TC = 1 in the LPUART_ISR register

Bit 5 RXFNIE: RXFIFO not empty interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: A LPUART interrupt is generated whenever ORE = 1 or RXNE/RXFNE = 1 in the LPUART_ISR register

Bit 4 IDLEIE: IDLE interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated whenever IDLE = 1 in the LPUART_ISR register

Bit 3 TE: Transmitter enableThis bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

Note: During transmission, a low pulse on the TE bit (“0” followed by “1”) sends a preamble (idle line) after the current word. In order to generate an idle character, the TE must not be immediately written to 1. In order to ensure the required duration, the software can poll the TEACK bit in the LPUART_ISR register.

When TE is set there is a 1 bit-time delay before the transmission starts.

Bit 2 RE : Receiver enableThis bit enables the receiver. It is set and cleared by software.

0: Receiver is disabled

1: Receiver is enabled and begins searching for a start bit

Bit 1 UESM : LPUART enable in Stop modeWhen this bit is cleared, the LPUART is not able to wake up the MCU from low-power mode.

When this bit is set, the LPUART is able to wake up the MCU from low-power mode, provided that the LPUART clock selection is HSI or LSE in the RCC.

This bit is set and cleared by software.

0: LPUART not able to wake up the MCU from low-power mode.

1: LPUART able to wake up the MCU from low-power mode. When this function is active, the clock source for the LPUART must be HSI or LSE (see RCC chapter)

Note: It is recommended to set the UESM bit just before entering low-power mode and clear it on exit from low-power mode.

Bit 0 UE : LPUART enableWhen this bit is cleared, the LPUART prescalers and outputs are stopped immediately, and current operations are discarded. The configuration of the LPUART is kept, but all the status flags, in the LPUART_ISR are reset. This bit is set and cleared by software.

0: LPUART prescaler and outputs disabled, low-power mode

1: LPUART enabled

Note: To enter low-power mode without generating errors on the line, the TE bit must be reset before and the software must wait for the TC bit in the LPUART_ISR to be set before resetting the UE bit.

The DMA requests are also reset when UE = 0 so the DMA channel must be disabled before resetting the UE bit.

34.7.2 LPUART control register 1 [alternate] (LPUART_CR1)

Address offset: 0x00

Reset value: 0x0000 0000

The same register can be used in FIFO mode enabled (previous section) and FIFO mode disabled (this section).

FIFO mode disabled

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | FIFO EN | M1 | Res. | Res. | DEAT[4:0] | DEDT[4:0] | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | CMIE | MME | M0 | WAKE | PCE | PS | PEIE | TXEIE | TCIE | RXNEIE | IDLEIE | TE | RE | UESM | UE |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 FIFOEN :FIFO mode enableThis bit is set and cleared by software.

0: FIFO mode is disabled.

1: FIFO mode is enabled.

Bit 28 M1: Word lengthThis bit must be used in conjunction with bit 12 (M0) to determine the word length. It is set or cleared by software.

M[1:0] = '00': 1 Start bit, 8 Data bits, n Stop bit

M[1:0] = '01': 1 Start bit, 9 Data bits, n Stop bit

M[1:0] = '10': 1 Start bit, 7 Data bits, n Stop bit

This bit can only be written when the LPUART is disabled (UE = 0).

Note: In 7-bit data length mode, the smartcard mode, LIN master mode and Auto baud rate (0x7F and 0x55 frames detection) are not supported.

Bits 27:26 Reserved, must be kept at reset value.

Bits 25:21 DEAT[4:0]: Driver enable assertion timeThis 5-bit value defines the time between the activation of the DE (Driver Enable) signal and the beginning of the start bit. It is expressed in lpuart_ker_ck clock cycles. For more details, refer Section 33.5.20: RS232 hardware flow control and RS485 Driver Enable .

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bits 20:16 DEDT[4:0]: Driver enable deassertion timeThis 5-bit value defines the time between the end of the last stop bit, in a transmitted message, and the de-activation of the DE (Driver Enable) signal. It is expressed in lpuart_ker_ck clock cycles. For more details, refer Section 34.4.13: RS232 hardware flow control and RS485 Driver Enable .

If the LPUART_TDR register is written during the DEDT time, the new data is transmitted only when the DEDT and DEAT times have both elapsed.

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 15 Reserved, must be kept at reset value.

Bit 14 CMIE: Character match interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: A LPUART interrupt is generated when the CMF bit is set in the LPUART_ISR register.

Bit 13 MME: Mute mode enableThis bit activates the mute mode function of the LPUART. When set, the LPUART can switch between the active and mute modes, as defined by the WAKE bit. It is set and cleared by software.

0: Receiver in active mode permanently

1: Receiver can switch between mute mode and active mode.

Bit 12 M0: Word lengthThis bit is used in conjunction with bit 28 (M1) to determine the word length. It is set or cleared by software (refer to bit 28 (M1) description).

This bit can only be written when the LPUART is disabled (UE = 0).

Bit 11 WAKE: Receiver wake-up methodThis bit determines the LPUART wake-up method from mute mode. It is set or cleared by software.

0: Idle line

1: Address mark

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 10 PCE: Parity control enableThis bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 9 PS: Parity selectionThis bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

This bitfield can only be written when the LPUART is disabled (UE = 0).

Bit 8 PEIE: PE interrupt enableThis bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated whenever PE = 1 in the LPUART_ISR register

Bit 7 TXEIE: Transmit data register emptyThis bit is set and cleared by software.

0: Interrupt is inhibited

1: A LPUART interrupt is generated whenever TXE/TXFNF = 1 in the LPUART_ISR register

Bit 6 TCIE: Transmission complete interrupt enableThis bit is set and cleared by software.