19. Flexible static memory controller (FSMC)

19.1 FMC introduction

The flexible static memory controller (FSMC) includes two memory controllers:

- The NOR/PSRAM memory controller

- The NAND memory controller

This memory controller is also named flexible memory controller (FMC).

19.2 FMC main features

The FMC functional block makes the interface with: synchronous and asynchronous static memories, and NAND flash memory. Its main purposes are:

- to translate AHB transactions into the appropriate external device protocol

- to meet the access time requirements of the external memory devices

All external memories share the addresses, data and control signals with the controller. Each external device is accessed by means of a unique chip select. The FMC performs only one access at a time to an external device.

The main features of the FMC controller are the following:

- Interface with static-memory mapped devices including:

- Static random access memory (SRAM)

- NOR flash memory/OneNAND flash memory

- PSRAM (4 memory banks)

- Ferroelectric RAM (FRAM)

- NAND flash memory with ECC hardware to check up to 8 Kbytes of data

- Interface with parallel LCD modules, supporting Intel 8080 and Motorola 6800 modes.

- Burst mode support for faster access to synchronous devices such as NOR flash memory, PSRAM)

- Programmable continuous clock output for asynchronous and synchronous accesses

- 8-,16-bit wide data bus

- Independent chip select control for each memory bank

- Independent configuration for each memory bank

- Write enable and byte lane select outputs for use with PSRAM, SRAM devices

- External asynchronous wait control

- Write FIFO with 16 x32-bit depth

The Write FIFO is common to all memory controllers and consists of:

- a Write Data FIFO which stores the AHB data to be written to the memory (up to 32 bits) plus one bit for the AHB transfer (burst or not sequential mode)

- a Write Address FIFO which stores the AHB address (up to 28 bits) plus the AHB data size (up to 2 bits). When operating in burst mode, only the start address is stored except when crossing a page boundary (for PSRAM). In this case, the AHB burst is broken into two FIFO entries.

At startup the FMC pins must be configured by the user application. The FMC I/O pins which are not used by the application can be used for other purposes.

The FMC registers that define the external device type and associated characteristics are usually set at boot time and do not change until the next reset or power-up. However, the settings can be changed at any time.

19.3 FMC block diagram

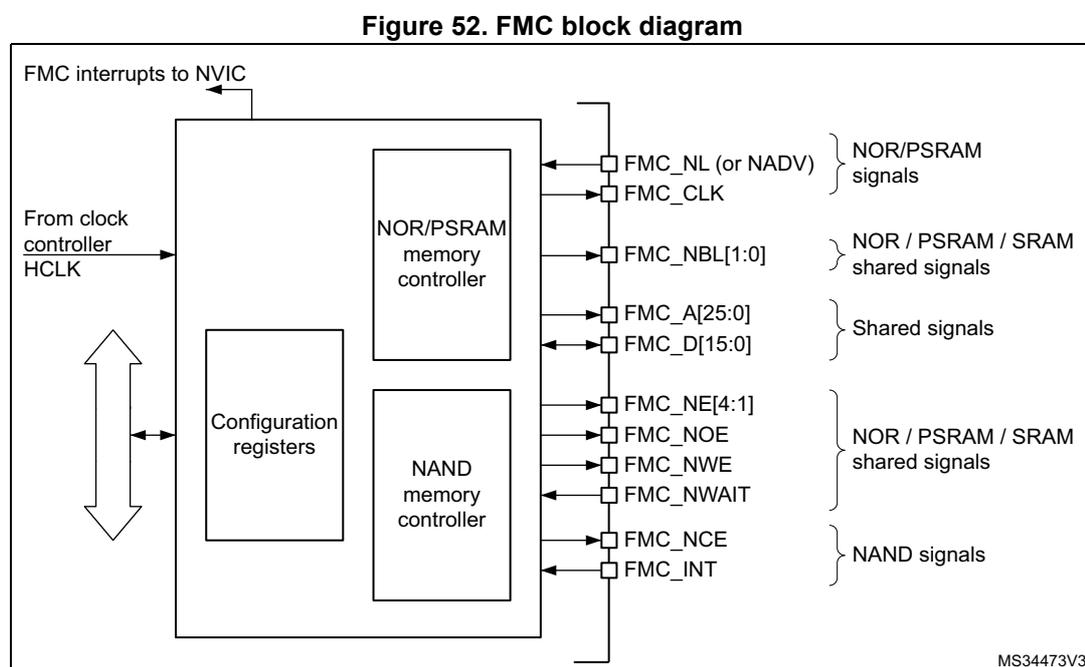

The FMC consists of the following main blocks:

- • The AHB interface (including the FMC configuration registers)

- • The NOR flash/PSRAM/SRAM controller

The block diagram is shown in the figure below.

Figure 52. FMC block diagram

The diagram illustrates the internal architecture of the FMC. On the left, an AHB interface connects to a 'Configuration registers' block and a 'NOR/PSRAM memory controller' block. The 'Configuration registers' block is connected to the AHB interface and the 'NAND memory controller' block. The 'NOR/PSRAM memory controller' block is connected to the 'NAND memory controller' block and the external pins. The 'NAND memory controller' block is connected to the 'Configuration registers' block and the external pins. The external pins are grouped into several signal sets:

- NOR/PSRAM signals: FMC_NL (or NADV), FMC_CLK

- NOR / PSRAM / SRAM shared signals: FMC_NBL[1:0]

- Shared signals: FMC_A[25:0], FMC_D[15:0]

- NOR / PSRAM / SRAM shared signals: FMC_NE[4:1], FMC_NOE, FMC_NWE, FMC_NWAIT

- NAND signals: FMC_NCE, FMC_INT

19.4 AHB interface

The AHB slave interface allows internal CPUs and other bus master peripherals to access the external memories.

AHB transactions are translated into the external device protocol. In particular, if the selected external memory is 16- or 8-bit wide, 32-bit wide transactions on the AHB are split into consecutive 16- or 8-bit accesses. The FMC chip select (FMC_NEx) does not toggle between the consecutive accesses except in case of Access mode D when the Extended mode is enabled.

The FMC generates an AHB error in the following conditions:

- • When reading or writing to a FMC bank (Bank 1 to 4) which is not enabled.

- • When reading or writing to the NOR flash bank while the FACCEN bit is reset in the FMC_BCRx register.

The effect of an AHB error depends on the AHB master which has attempted the R/W access:

- • If the access has been attempted by the Cortex ® -M33 CPU, a hard fault interrupt is generated.

- • If the access has been performed by a DMA controller, a DMA transfer error is generated and the corresponding DMA channel is automatically disabled.

The AHB clock (HCLK) is the reference clock for the FMC.

19.4.1 Supported memories and transactions

General transaction rules

The requested AHB transaction data size can be 8-, 16- or 32-bit wide whereas the accessed external device has a fixed data width. This may lead to inconsistent transfers.

Therefore, some simple transaction rules must be followed:

- • AHB transaction size and memory data size are equal

There is no issue in this case.

- • AHB transaction size is greater than the memory size:

In this case, the FMC splits the AHB transaction into smaller consecutive memory accesses to meet the external data width. The FMC chip select (FMC_NEx) does not toggle between the consecutive accesses. If the bus turnaround timings is configured to any other value than 0, the FMC chip select (FMC_NEx) toggles between the consecutive accesses. This feature is required when interfacing with FRAM memory.

- • AHB transaction size is smaller than the memory size:

The transfer may or not be consistent depending on the type of external device:

- – Accesses to devices that have the byte select feature (SRAM, ROM, PSRAM)

In this case, the FMC allows read/write transactions and accesses to the right data through its byte lanes NBL[1:0].

Bytes to be written are addressed by NBL[1:0].

All memory bytes are read (NBL[1:0] are driven low during read transaction) and the useless ones are discarded.

- – Accesses to devices that do not have the byte select feature (NOR and NAND flash memories)

This situation occurs when a byte access is requested to a 16-bit wide flash memory. Since the device cannot be accessed in Byte mode (only 16-bit words can be read/written from/to the flash memory), Write transactions and Read transactions are allowed (the controller reads the entire 16-bit memory word and uses only the required byte).

Wrap support for NOR flash/PSRAM

Wrap burst mode for synchronous memories is not supported. The memories must be configured in Linear burst mode of undefined length.

Configuration registers

The FMC can be configured through a set of registers. Refer to Section 19.6.6 , for a detailed description of the NOR flash/PSRAM controller registers. Refer to Section 19.7.7 , for a detailed description of the NAND flash registers.

19.5 External device address mapping

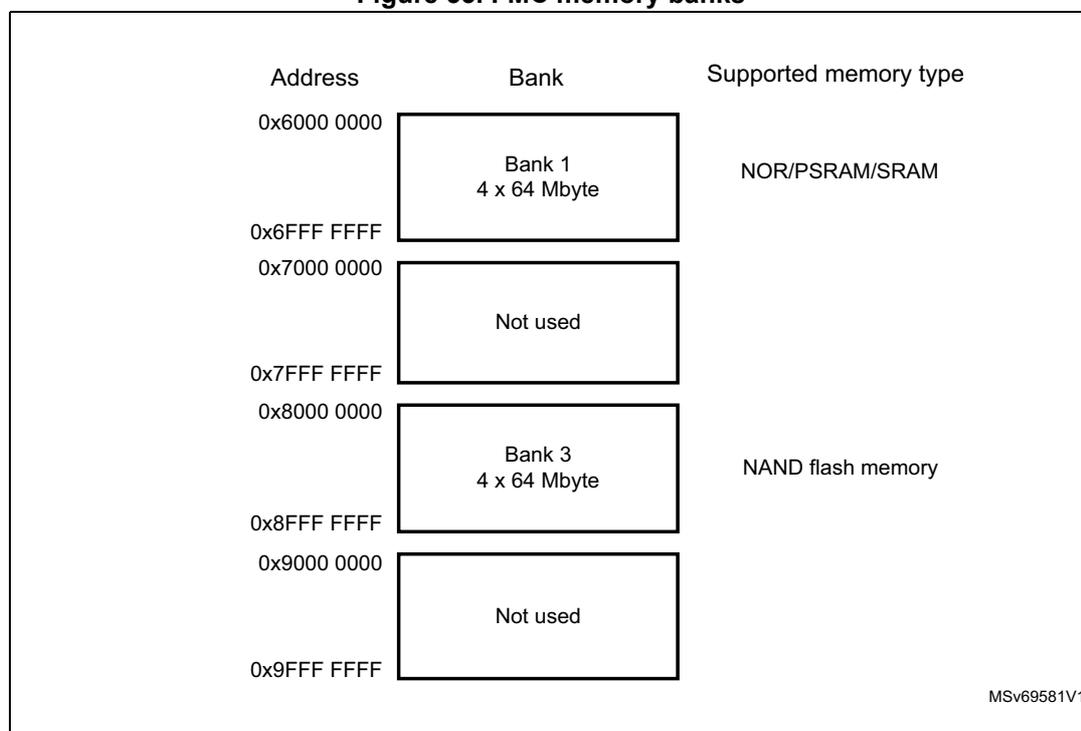

From the FMC point of view, the external memory is divided into fixed-size banks of 256 Mbytes each (see Figure 53 ):

- • Bank 1 used to address up to 4 NOR flash memory or PSRAM devices. This bank is split into 4 NOR/PSRAM subbanks with 4 dedicated chip selects, as follows:

- – Bank 1 - NOR/PSRAM 1

- – Bank 1 - NOR/PSRAM 2

- – Bank 1 - NOR/PSRAM 3

- – Bank 1 - NOR/PSRAM 4

- • Bank 3 used to address NAND flash memory devices. The MPU memory attribute for this space must be reconfigured by software to Device.

For each bank the type of memory to be used can be configured by the user application through the Configuration register.

Figure 53. FMC memory banks

The diagram illustrates the memory bank mapping for the FMC. It consists of three columns: Address, Bank, and Supported memory type. The address ranges are shown on the left, with start and end addresses for each bank. Bank 1 is shown as a 4 x 64 Mbyte block, supporting NOR/PSRAM/SRAM. Bank 3 is shown as a 4 x 64 Mbyte block, supporting NAND flash memory. The banks are separated by 'Not used' regions.

| Address | Bank | Supported memory type |

|---|---|---|

| 0x6000 0000 | Bank 1 4 x 64 Mbyte | NOR/PSRAM/SRAM |

| 0x6FFF FFFF | ||

| 0x7000 0000 | Not used | |

| 0x7FFF FFFF | ||

| 0x8000 0000 | Bank 3 4 x 64 Mbyte | NAND flash memory |

| 0x8FFF FFFF | ||

| 0x9000 0000 | Not used | |

| 0x9FFF FFFF |

MSv69581V1

19.5.1 NOR/PSRAM address mapping

HADDR[27:26] bits are used to select one of the four memory banks as shown in Table 120 .

Table 120. NOR/PSRAM bank selection

| HADDR[27:26] (1) | Selected bank |

|---|---|

| 00 | Bank 1 - NOR/PSRAM 1 |

| 01 | Bank 1 - NOR/PSRAM 2 |

| HADDR[27:26] (1) | Selected bank |

|---|---|

| 10 | Bank 1 - NOR/PSRAM 3 |

| 11 | Bank 1 - NOR/PSRAM 4 |

- 1. HADDR are internal AHB address lines that are translated to external memory.

The HADDR[25:0] bits contain the external memory address. Since HADDR is a byte address whereas the memory is addressed at word level, the address actually issued to the memory varies according to the memory data width, as shown in the following table.

Table 121. NOR/PSRAM External memory address| Memory width (1) | Data address issued to the memory | Maximum memory capacity (bits) |

|---|---|---|

| 8-bit | HADDR[25:0] | 64 Mbytes x 8 = 512 Mbits |

| 16-bit | HADDR[25:1] >> 1 | 64 Mbytes/2 x 16 = 512 Mbits |

- 1. In case of a 16-bit external memory width, the FMC internally uses HADDR[25:1] to generate the address for external memory FMC_A[24:0].

Whatever the external memory width, FMC_A[0] must be connected to external memory address A[0].

19.5.2 NAND flash memory address mapping

The NAND bank is divided into memory areas as indicated in Table 122 .

Table 122. NAND memory mapping and timing registers| Start address | End address | FMC bank | Memory space | Timing register |

|---|---|---|---|---|

| 0x8800 0000 | 0x8BFF FFFF | Bank 3 - NAND flash | Attribute | FMC_PATT (0x8C) |

| 0x8000 0000 | 0x83FF FFFF | Common | FMC_PMEM (0x88) |

For NAND flash memory, the common and attribute memory spaces are subdivided into three sections (see in Table 123 below) located in the lower 256 Kbytes:

- • Data section (first 64 Kbytes in the common/attribute memory space)

- • Command section (second 64 Kbytes in the common / attribute memory space)

- • Address section (next 128 Kbytes in the common / attribute memory space)

| Section name | HADDR[17:16] | Address range |

|---|---|---|

| Address section | 1X | 0x020000-0x03FFFF |

| Command section | 01 | 0x010000-0x01FFFF |

| Data section | 00 | 0x000000-0x0FFFF |

The application software uses the 3 sections to access the NAND flash memory:

- • To sending a command to NAND flash memory , the software must write the command value to any memory location in the command section.

- • To specify the NAND flash address that must be read or written , the software must write the address value to any memory location in the address section. Since an address can be 4 or 5 bytes long (depending on the actual memory size), several consecutive write operations to the address section are required to specify the full address.

- • To read or write data , the software reads or writes the data from/to any memory location in the data section.

Since the NAND flash memory automatically increments addresses, there is no need to increment the address of the data section to access consecutive memory locations.

19.6 NOR flash/PSRAM controller

The FMC generates the appropriate signal timings to drive the following types of memories:

- • Asynchronous SRAM, FRAM and ROM

- – 8 bits

- – 16 bits

- • PSRAM (CellularRAM™)

- – Asynchronous mode

- – Burst mode for synchronous accesses

- – Multiplexed or non-multiplexed

- • NOR flash memory

- – Asynchronous mode

- – Burst mode for synchronous accesses

- – Multiplexed or non-multiplexed

The FMC outputs a unique chip select signal, NE[4:1], per bank. All the other signals (addresses, data and control) are shared.

The FMC supports a wide range of devices through a programmable timings among which:

- • Programmable wait states (up to 15)

- • Programmable bus turnaround cycles (up to 15)

- • Programmable output enable and write enable delays (up to 15)

- • Independent read and write timings and protocol to support the widest variety of memories and timings

- • Programmable continuous clock (FMC_CLK) output.

The FMC Clock (FMC_CLK) is a submultiple of the HCLK clock. It can be delivered to the selected external device either during synchronous accesses only or during asynchronous and synchronous accesses depending on the CCKEN bit configuration in the FMC_BCR1 register:

- • If the CCKEN bit is reset, the FMC generates the clock (CLK) only during synchronous accesses (Read/write transactions).

- • If the CCKEN bit is set, the FMC generates a continuous clock during asynchronous and synchronous accesses. To generate the FMC_CLK continuous clock, Bank 1 must

be configured in Synchronous mode (see Section 19.6.6: NOR/PSRAM controller registers ). Since the same clock is used for all synchronous memories, when a continuous output clock is generated and synchronous accesses are performed, the AHB data size has to be the same as the memory data width (MWID) otherwise the FMC_CLK frequency is changed depending on AHB data transaction (refer to Section 19.6.5: Synchronous transactions for FMC_CLK divider ratio formula).

The size of each bank is fixed and equal to 64 Mbytes. Each bank is configured through dedicated registers (see Section 19.6.6: NOR/PSRAM controller registers ).

The programmable memory parameters include access times (see Table 124 ) and support for wait management (for PSRAM and NOR flash accessed in Burst mode).

Table 124. Programmable NOR/PSRAM access parameters

| Parameter | Function | Access mode | Unit | Min. | Max. |

|---|---|---|---|---|---|

| Address setup | Duration of the address setup phase | Asynchronous | AHB clock cycle (HCLK) | 0 | 15 |

| Address hold | Duration of the address hold phase | Asynchronous, muxed I/Os | AHB clock cycle (HCLK) | 1 | 15 |

| NBL setup | Duration of the byte lanes setup phase | Asynchronous | AHB clock cycle (HCLK) | 0 | 3 |

| Data setup | Duration of the data setup phase | Asynchronous | AHB clock cycle (HCLK) | 1 | 256 |

| Data hold | Duration of the data hold phase | Asynchronous | AHB clock cycle (HCLK) | 0 | 3 |

| Bust turn | Duration of the bus turnaround phase | Asynchronous and synchronous read / write | AHB clock cycle (HCLK) | 0 | 15 |

| Clock divide ratio | Number of AHB clock cycles (HCLK) to build one memory clock cycle (CLK) | Synchronous | AHB clock cycle (HCLK) | 2 | 16 |

| Data latency | Number of clock cycles to issue to the memory before the first data of the burst | Synchronous | Memory clock cycle (CLK) | 2 | 17 |

19.6.1 External memory interface signals

Table 125 , Table 126 and Table 127 list the signals that are typically used to interface with NOR flash memory, SRAM and PSRAM.

Note: The prefix “N” identifies the signals that are active low.

NOR flash memory, non-multiplexed I/Os

Table 125. Non-multiplexed I/O NOR flash memory

| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:0] | O | Address bus |

| FMC signal name | I/O | Function |

|---|---|---|

| D[15:0] | I/O | Bidirectional data bus |

| NE[x] | O | Chip select, x = 1..4 |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(=NADV) | O | Latch enable (this signal is called address valid, NADV, by some NOR flash devices) |

| NWAIT | I | NOR flash wait input signal to the FMC |

The maximum capacity is 512 Mbits (26 address lines).

NOR flash memory, 16-bit multiplexed I/Os

Table 126. 16-bit multiplexed I/O NOR flash memory| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:16] | O | Address bus |

| AD[15:0] | I/O | 16-bit multiplexed, bidirectional address/data bus (the 16-bit address A[15:0] and data D[15:0] are multiplexed on the databus) |

| NE[x] | O | Chip select, x = 1..4 |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(=NADV) | O | Latch enable (this signal is called address valid, NADV, by some NOR flash devices) |

| NWAIT | I | NOR flash wait input signal to the FMC |

The maximum capacity is 512 Mbits.

PSRAM/FRAM/SRAM, non-multiplexed I/Os

Table 127. Non-multiplexed I/Os PSRAM/SRAM| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (only for PSRAM synchronous access) |

| A[25:0] | O | Address bus |

| D[15:0] | I/O | Data bidirectional bus |

| NE[x] | O | Chip select, x = 1..4 (called NCE by PSRAM (CellularRAM™ i.e. CRAM)) |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(=NADV) | O | Address valid only for PSRAM input (memory signal name: NADV) |

| FMC signal name | I/O | Function |

|---|---|---|

| NWAIT | I | PSRAM wait input signal to the FMC |

| NBL[1:0] | O | Byte lane output. Byte 0 and Byte 1 control (upper and lower byte enable) |

The maximum capacity is 512 Mbits.

PSRAM, 16-bit multiplexed I/Os

Table 128. 16-Bit multiplexed I/O PSRAM| FMC signal name | I/O | Function |

|---|---|---|

| CLK | O | Clock (for synchronous access) |

| A[25:16] | O | Address bus |

| AD[15:0] | I/O | 16-bit multiplexed, bidirectional address/data bus (the 16-bit address A[15:0] and data D[15:0] are multiplexed on the databus) |

| NE[x] | O | Chip select, x = 1..4 (called NCE by PSRAM (CellularRAM™ i.e. CDRAM)) |

| NOE | O | Output enable |

| NWE | O | Write enable |

| NL(= NADV) | O | Address valid PSRAM input (memory signal name: NADV) |

| NWAIT | I | PSRAM wait input signal to the FMC |

| NBL[1:0] | O | Byte lane output. Byte 0 and Byte 1 control (upper and lower byte enable) |

The maximum capacity is 512 Mbits (26 address lines).

19.6.2 Supported memories and transactions

Table 129 below shows an example of the supported devices, access modes and transactions when the memory data bus is 16-bit wide for NOR flash memory, PSRAM and SRAM. The transactions not allowed (or not supported) by the FMC are shown in gray in this example.

Table 129. NOR flash/PSRAM: example of supported memories and transactions

| Device | Mode | R/W | AHB data size | Memory data size | Allowed/not allowed | Comments |

|---|---|---|---|---|---|---|

| NOR flash (muxed I/Os and nonmuxed I/Os) | Asynchronous | R | 8 | 16 | Y | - |

| Asynchronous | W | 8 | 16 | N | - | |

| Asynchronous | R | 16 | 16 | Y | - | |

| Asynchronous | W | 16 | 16 | Y | - | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous page | R | - | 16 | N | Mode is not supported | |

| Synchronous | R | 8 | 16 | N | - | |

| Synchronous | R | 16 | 16 | Y | - | |

| Synchronous | R | 32 | 16 | Y | - | |

| PSRAM (multiplexed I/Os and non-multiplexed I/Os) | Asynchronous | R | 8 | 16 | Y | - |

| Asynchronous | W | 8 | 16 | Y | Use of byte lanes NBL[1:0] | |

| Asynchronous | R | 16 | 16 | Y | - | |

| Asynchronous | W | 16 | 16 | Y | - | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous page | R | - | 16 | N | Mode is not supported | |

| Synchronous | R | 8 | 16 | N | - | |

| Synchronous | R | 16 | 16 | Y | - | |

| Synchronous | R | 32 | 16 | Y | - | |

| Synchronous | W | 8 | 16 | Y | Use of byte lanes NBL[1:0] | |

| Synchronous | W | 16/32 | 16 | Y | - | |

| SRAM and ROM | Asynchronous | R | 8 / 16 | 16 | Y | - |

| Asynchronous | W | 8 / 16 | 16 | Y | Use of byte lanes NBL[1:0] | |

| Asynchronous | R | 32 | 16 | Y | Split into 2 FMC accesses | |

| Asynchronous | W | 32 | 16 | Y | Split into 2 FMC accesses Use of byte lanes NBL[1:0] |

19.6.3 General timing rules

Signals synchronization

- • All controller output signals change on the rising edge of the internal clock (HCLK)

- • In Synchronous mode (read or write), all output signals change on the rising edge of HCLK. Whatever the CLKDIV value, all outputs change as follows:

- – NOEL/NWEL/ NEL/NADVL/ NADVH /NBLL/ Address valid outputs change on the falling edge of FMC_CLK clock.

- – NOEH/ NWEH / NEH/ NOEH/NBLH/ Address invalid outputs change on the rising edge of FMC_CLK clock.

19.6.4 NOR flash/PSRAM controller asynchronous transactions

Asynchronous static memories (NOR flash, PSRAM, SRAM, FRAM)

- • Signals are synchronized by the internal clock HCLK. This clock is not issued to the memory

- • The FMC always samples the data before de-asserting the NOE signal. This guarantees that the memory data hold timing constraint is met (minimum Chip Enable high to data transition is usually 0 ns)

- • If the Extended mode is enabled (EXTMOD bit is set in the FMC_BCRx register), up to four extended modes (A, B, C and D) are available. It is possible to mix A, B, C and D modes for read and write operations. For example, read operation can be performed in mode A and write in mode B.

- • If the Extended mode is disabled (EXTMOD bit is reset in the FMC_BCRx register), the FMC can operate in mode 1 or mode 2 as follows:

- – Mode 1 is the default mode when SRAM/PSRAM memory type is selected (MTYP = 0x0 or 0x01 in the FMC_BCRx register)

- – Mode 2 is the default mode when NOR memory type is selected (MTYP = 0x10 in the FMC_BCRx register).

Mode 1 - SRAM/FRAM/PSRAM (CRAM)

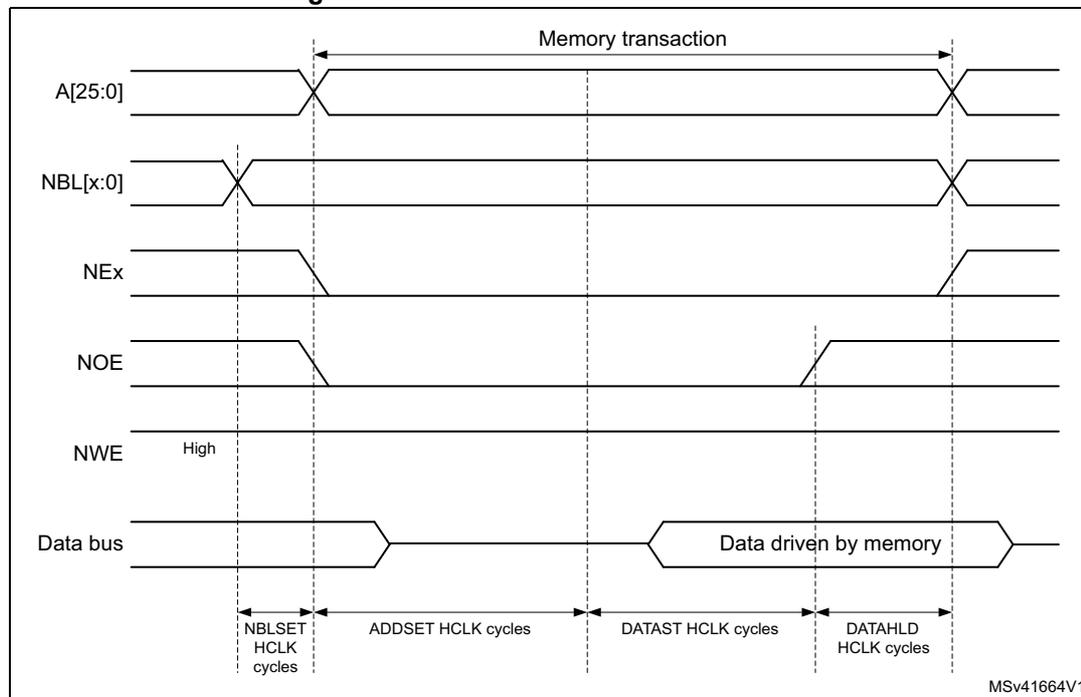

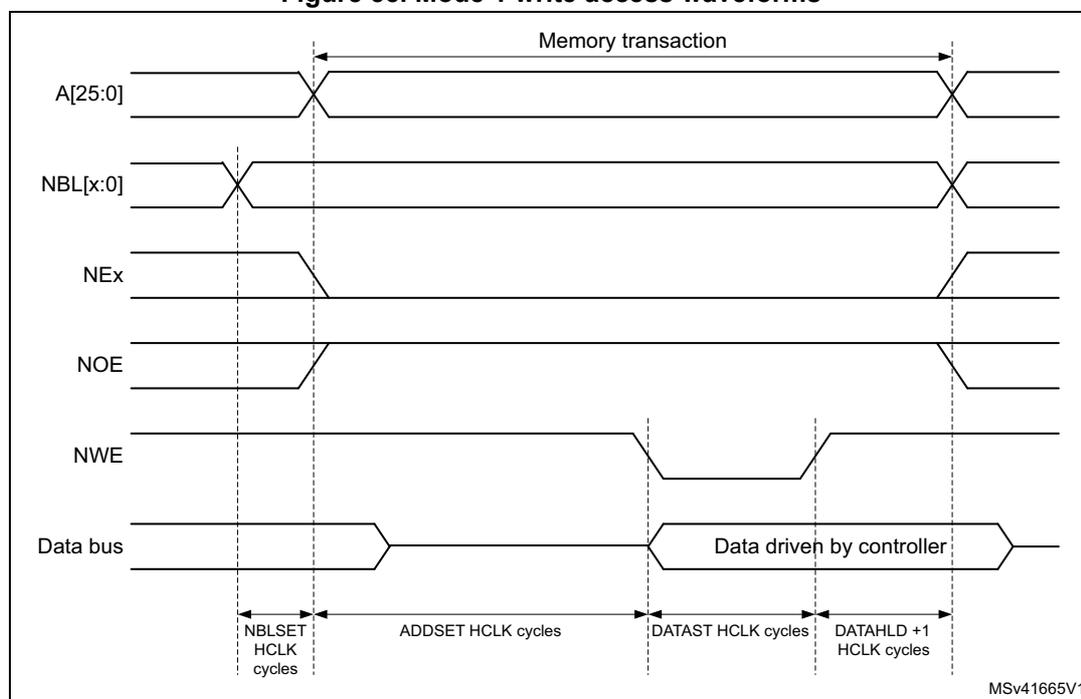

The next figures show the read and write transactions for the supported modes followed by the required configuration of FMC_BCRx, and FMC_BTRx/FMC_BWTRx registers.

Figure 54. Mode 1 read access waveforms

Timing diagram for Mode 1 read access waveforms. The diagram shows the relationship between address (A[25:0]), bus cycle (NBL[x:0]), and data (Data bus) signals during a read transaction. The memory transaction is indicated by a double-headed arrow at the top. The address (A[25:0]) is stable during the entire transaction. The bus cycle (NBL[x:0]) is active low and goes low at the start of the transaction. The NEx signal is active low and goes low at the start of the transaction. The NOE signal is active low and goes low at the start of the transaction. The NWE signal is active high and remains high throughout the transaction. The Data bus is driven by memory during the DATAST HCLK cycles. The timing parameters are defined as follows:

- NBLSET HCLK cycles: The time from the falling edge of NBL[x:0] to the start of the memory transaction.

- ADDSET HCLK cycles: The time from the start of the memory transaction to the start of the DATAST HCLK cycles.

- DATAST HCLK cycles: The duration of the data transfer phase.

- DATAHLD HCLK cycles: The time from the end of the DATAST HCLK cycles to the rising edge of NBL[x:0].

MSv41664V1

Figure 55. Mode 1 write access waveforms

Timing diagram for Mode 1 write access waveforms. The diagram shows the relationship between address (A[25:0]), bus cycle (NBL[x:0]), and data (Data bus) signals during a write transaction. The memory transaction is indicated by a double-headed arrow at the top. The address (A[25:0]) is stable during the entire transaction. The bus cycle (NBL[x:0]) is active low and goes low at the start of the transaction. The NEx signal is active low and goes low at the start of the transaction. The NOE signal is active low and goes low at the start of the transaction. The NWE signal is active low and goes low at the start of the transaction. The Data bus is driven by controller during the DATAST HCLK cycles. The timing parameters are defined as follows:

- NBLSET HCLK cycles: The time from the falling edge of NBL[x:0] to the start of the memory transaction.

- ADDSET HCLK cycles: The time from the start of the memory transaction to the start of the DATAST HCLK cycles.

- DATAST HCLK cycles: The duration of the data transfer phase.

- DATAHLD +1 HCLK cycles: The time from the end of the DATAST HCLK cycles to the rising edge of NBL[x:0].

MSv41665V1

The DATAHLD time at the end of the read and write transactions guarantee the address and data hold time after the NOE/NWE rising edge. The DATAST value must be greater than zero (DATAST > 0).

Table 130. FMC_BCRx bitfields (mode 1)| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Don't care |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | As needed, exclude 0x2 (NOR flash memory) |

| 1 | MUXE | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD HCLK cycles for read accesses, DATAHLD+1 HCLK cycles for write accesses). |

| 29:28 | ACCMOD | Don't care |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles). |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles). Minimum value for ADDSET is 0. |

Mode A - SRAM/FRAM/PSRAM (CRAM) OE toggling

Figure 56. Mode A read access waveforms

![Timing diagram for Mode A read access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over time. The diagram shows the sequence of events for a read operation, including address setup, data drive by memory, and data hold phases.](/RM0438-STM32L5/b59de7da6bab57b3ef901eb555cfcb69_img.jpg)

The diagram illustrates the timing for a read access in Mode A. The signals shown are:

- A[25:0] : Address bus, stable during the memory transaction.

- NBL[x:0] : Byte Lane signals, driven low during the read access.

- NEx : Address Latch Enable, active low signal.

- NOE : Output Enable, active low signal that toggles to enable data output from memory.

- NWE : Write Enable, active low signal, held high during read access.

- Data bus : Bidirectional data bus, driven by memory during the read phase.

Timing parameters are defined as follows:

- NBLSET HCLK cycles : Time from NEx falling edge to NBL[x:0] stable.

- ADDSET HCLK cycles : Time from NEx falling edge to A[25:0] stable.

- DATAST HCLK cycles : Time from NOE falling edge to Data bus driven by memory.

- DATAHLD HCLK cycles : Time from NOE rising edge to Data bus tri-stated.

Reference: MSV41681V1

- 1. NBL[1:0] are driven low during the read access

Figure 57. Mode A write access waveforms

![Timing diagram for Mode A write access waveforms showing signals A[25:0], NBL[x:0], NEx, NOE, NWE, and Data bus over time. The diagram shows the sequence of events for a write operation, including address setup, data drive by controller, and data hold phases.](/RM0438-STM32L5/2df6aabdaad4dcd06e7206f062ae89fb_img.jpg)

The diagram illustrates the timing for a write access in Mode A. The signals shown are:

- A[25:0] : Address bus, stable during the memory transaction.

- NBL[x:0] : Byte Lane signals, driven low during the write access.

- NEx : Address Latch Enable, active low signal.

- NOE : Output Enable, active low signal, held high during write access.

- NWE : Write Enable, active low signal that toggles to enable data input to memory.

- Data bus : Bidirectional data bus, driven by controller during the write phase.

Timing parameters are defined as follows:

- NBLSET HCLK cycles : Time from NEx falling edge to NBL[x:0] stable.

- ADDSET HCLK cycles : Time from NEx falling edge to A[25:0] stable.

- DATAST HCLK cycles : Time from NWE falling edge to Data bus driven by controller.

- DATAHLD +1 HCLK cycles : Time from NWE rising edge to Data bus tri-stated.

Reference: MSV41665V1

The differences compared with Mode 1 are the toggling of NOE and the independent read and write timings.

Table 132. FMC_BCRx bitfields (mode A)| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Don't care |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | As needed, exclude 0x2 (NOR flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD HCLK cycles for read accesses). |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles) for read accesses. Minimum value for ADDSET is 0. |

Table 134. FMC_BWTRx bitfields (mode A)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD+1 HCLK cycles for write accesses). |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles) for write accesses. Minimum value for ADDSET is 0. |

Mode 2/B - NOR flash

Figure 58. Mode 2 and mode B read access waveforms

![Timing diagram for Mode 2 and mode B read access waveforms. The diagram shows the relationship between address (A[25:0]), NADV, NEx, NOE, NWE, and data (D[15:0]) signals during a memory transaction. The transaction is divided into three phases: ADDSET HCLK cycles, DATAST HCLK cycles, and DATAHLD HCLK cycles. Data is driven by memory during the DATAST and DATAHLD phases.](/RM0438-STM32L5/97b5d0bcd48d1218e806ba336106b466_img.jpg)

The timing diagram illustrates the signals and phases for a read access in Mode 2 and Mode B. The signals shown are:

- A[25:0] : Address lines, which are stable during the memory transaction.

- NADV : Address Valid signal, which goes low at the start of the transaction and returns high at the end.

- NEx : Address and Data Valid signal, which goes low at the start and returns high at the end.

- NOE : Output Enable signal, which goes low to enable data output and returns high to disable it.

- NWE : Write Enable signal, which remains high throughout the read transaction.

- D[15:0] : Data lines, which are driven by the memory during the DATAST and DATAHLD phases.

The memory transaction is divided into three phases based on HCLK cycles:

- ADDSET HCLK cycles : The first phase where the address is set.

- DATAST HCLK cycles : The second phase where data is driven by memory.

- DATAHLD HCLK cycles : The third phase where data is held by memory.

The diagram is labeled MSV41678V1.

Figure 59. Mode 2 write access waveforms

![Timing diagram for Mode 2 write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time with labels for memory transaction, ADDSET, DATAST, and DATAHLD cycles.](/RM0438-STM32L5/4f290e7cecec9664303bd3097edbccd9_img.jpg)

This timing diagram illustrates the signals for a Mode 2 write access. The signals shown are A[25:0], NADV, NEx, NOE, NWE, and the Data bus. The diagram is divided into three main timing phases: ADDSET HCLK cycles, DATAST HCLK cycles, and DATAHLD + 1 HCLK cycles. The address A[25:0] is stable during the ADDSET phase. NADV and NEx are active-low signals that go low during the ADDSET phase and return high during the DATAST phase. NOE is active-low and goes low during the DATAST phase. NWE is active-low and goes low during the DATAST phase. The Data bus is driven by the controller during the DATAST phase. The entire sequence is labeled as a 'Memory transaction'.

MSv41679V1

Figure 60. Mode B write access waveforms

![Timing diagram for Mode B write access waveforms showing signals A[25:0], NADV, NEx, NOE, NWE, and Data bus over time with labels for memory transaction, ADDSET, DATAST, and DATAHLD cycles.](/RM0438-STM32L5/240e959690cb76eef7711c89395dee98_img.jpg)

This timing diagram illustrates the signals for a Mode B write access. The signals shown are A[25:0], NADV, NEx, NOE, NWE, and the Data bus. The diagram is divided into three main timing phases: ADDSET HCLK cycles, DATAST HCLK cycles, and DATAHLD + 1 HCLK cycles. The address A[25:0] is stable during the ADDSET phase. NADV and NEx are active-low signals that go low during the ADDSET phase and return high during the DATAST phase. NOE is active-low and goes low during the DATAST phase. NWE is active-low and goes low during the DATAST phase. The Data bus is driven by the controller during the DATAST phase. The entire sequence is labeled as a 'Memory transaction'.

MSv41680V1

The differences with mode 1 are the toggling of NWE and the independent read and write timings when extended mode is set (mode B).

Table 135. FMC_BCRx bitfields (mode 2/B)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | Don't care |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 for mode B, 0x0 for mode 2 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | 0x1 |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x2 (NOR flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

Table 136. FMC_BTRx bitfields (mode 2/B)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD HCLK cycles for read accesses and DATAHLD+1 HCLK cycles for write accesses when Extended mode is disabled). |

| 29:28 | ACCMOD | 0x1 if Extended mode is set |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the access second phase (DATAST HCLK cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the access first phase (ADDSET HCLK cycles) for read accesses. Minimum value for ADDSET is 0. |

Table 137. FMC_BWTRx bitfields (mode 2/B)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD+1 HCLK cycles for write accesses). |

| 29:28 | ACCMOD | 0x1 if Extended mode is set |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the access second phase (DATAST HCLK cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the access first phase (ADDSET HCLK cycles) for write accesses. Minimum value for ADDSET is 0. |

Note: The FMC_BWTRx register is valid only if the Extended mode is set (mode B), otherwise its content is don't care.

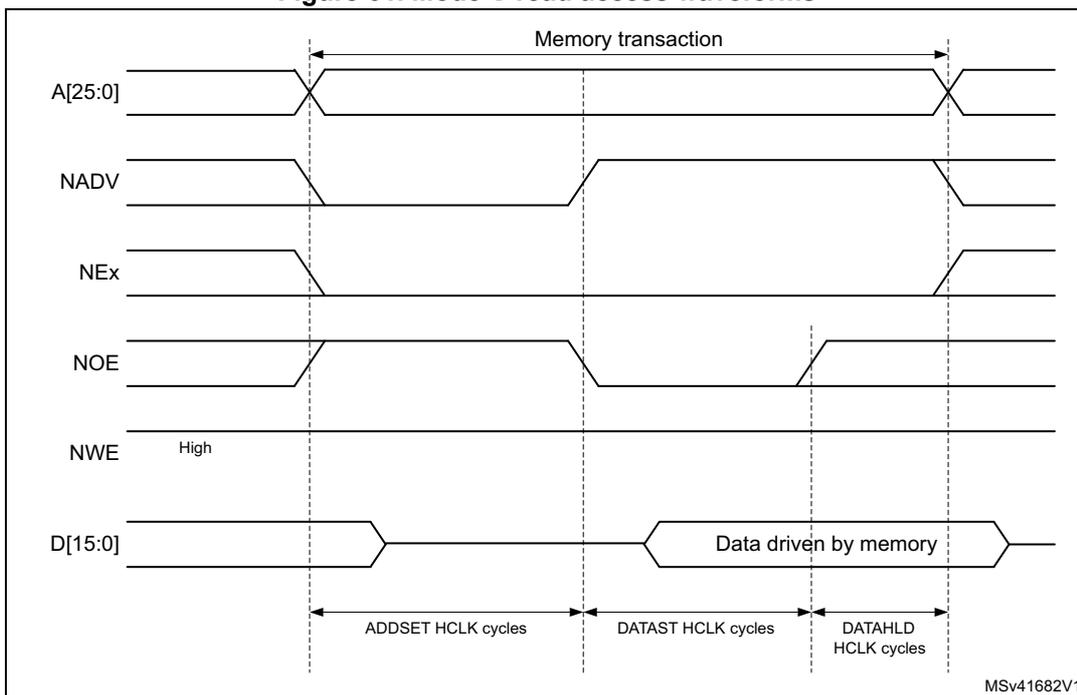

Mode C - NOR flash - OE toggling

Figure 61. Mode C read access waveforms

The diagram illustrates the timing for a read access in Mode C. The signals shown are:

- A[25:0] : Address lines, which are stable during the memory transaction.

- NADV : Address Valid signal, which goes low to indicate valid address and data, and returns high at the end of the transaction.

- NEx : Next Address signal, which goes low to indicate the start of the next address phase.

- NOE : Output Enable signal, which goes low to enable data output from the memory.

- NWE : Write Enable signal, which remains high throughout the read transaction.

- D[15:0] : Data lines, which are driven by the memory when NOE is low.

The timing is divided into three phases relative to the HCLK signal:

- ADDSET HCLK cycles : The duration of the access first phase.

- DATAST HCLK cycles : The duration of the access second phase.

- DATAHLD HCLK cycles : The duration of the data hold phase.

The entire sequence is labeled as a "Memory transaction". The diagram is identified by the code MSV41682V1.

Figure 62. Mode C write access waveforms

![Timing diagram for Mode C write access waveforms. The diagram shows the relationship between address (A[25:0]), NADV, NEx, NOE, NWE, and the Data bus over time. A 'Memory transaction' is indicated by a double-headed arrow spanning from the falling edge of NADV to the rising edge of NEx. The Data bus is driven by the controller during the 'DATAST HCLK cycles' and 'DATAHLD + 1 HCLK cycles' periods. The 'ADDSET HCLK cycles' period is shown between the falling edge of NADV and the start of the data drive. The Data bus is labeled 'Data driven by controller' during the active drive period. The diagram is labeled MSV41679V1.](/RM0438-STM32L5/ceb9783e4bf65d36aeec65c4c87cb832_img.jpg)

The differences compared with mode 1 are the toggling of NOE and the independent read and write timings.

Table 138. FMC_BCRx bitfields (mode C)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | Don't care |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | 0x1 |

| 5:4 | MWID | As needed |

| Bit number | Bit name | Value to set |

|---|---|---|

| 3:2 | MTYP | 0x02 (NOR flash memory) |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD HCLK cycles for read accesses). |

| 29:28 | ACCMOD | 0x2 |

| 27:24 | DATLAT | 0x0 |

| 23:20 | CLKDIV | 0x0 |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles) for read accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles) for read accesses. Minimum value for ADDSET is 0. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD+1 HCLK cycles for write accesses). |

| 29:28 | ACCMOD | 0x2 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles) for write accesses. |

| 7:4 | ADDHLD | Don't care |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles) for write accesses. Minimum value for ADDSET is 0. |

Mode D - asynchronous access with extended address

Figure 63. Mode D read access waveforms

![Timing diagram for Mode D read access waveforms showing signals A[25:0], NADV, NBL[x:0], NEx, NOE, NWE, and Data bus over time, with HCLK cycles and memory transaction phases.](/RM0438-STM32L5/481302913d06f34b34019d66547bde3c_img.jpg)

The diagram illustrates the timing for a Mode D read access. The signals shown are:

- A[25:0] : Address bus, which is latched at the first rising edge of HCLK (NBLSET) and remains stable until the second rising edge (ADDHLD).

- NADV : Address Valid signal, which goes low when the address is valid and returns high at the second rising edge of HCLK (ADDHLD).

- NBL[x:0] : Byte Lane signals, which are active-low and go low at the first rising edge of HCLK (NBLSET).

- NEx : External memory signal, which goes low at the first rising edge of HCLK (NBLSET) and returns high at the second rising edge (ADDHLD).

- NOE : Output Enable signal, which goes low at the second rising edge of HCLK (ADDHLD) to enable data output from the memory.

- NWE : Write Enable signal, which is held high throughout the read transaction.

- Data bus : The data bus is driven by the memory when NOE is low, starting at the second rising edge of HCLK (DATAST) and remaining valid until the third rising edge (DATAHLD).

The timing is defined by HCLK cycles:

- NBLSET HCLK cycles : Time from the first rising edge of HCLK to the start of the memory transaction.

- ADDSET HCLK cycles : Time from the first rising edge of HCLK to the second rising edge (ADDHLD).

- ADDHLD HCLK cycles : Time from the second rising edge (ADDHLD) to the start of data output.

- DATAST HCLK cycles : Time from the second rising edge (ADDHLD) to the third rising edge (DATAHLD).

- DATAHLD HCLK cycles : Time from the third rising edge (DATAHLD) to the end of the data output.

The entire sequence is labeled as a "Memory transaction" between the first and third rising edges of HCLK. The diagram is identified by the code MSV41683V1.

Figure 64. Mode D write access waveforms

![Timing diagram for Mode D write access waveforms showing signals A[25:0], NADV, NBL[x:0], NEx, NOE, NW E, and Data bus over time. The diagram shows the sequence of signals during a memory transaction, with specific timing parameters like NBLSET, ADDSET, ADDHLD, DATAST, and DATAHLD measured in HCLK cycles. The data bus is driven by the controller during the DATAST and DATAHLD phases.](/RM0438-STM32L5/c2c2c196e664610133685b180c6f3d8a_img.jpg)

The differences with mode 1 are the toggling of NOE that goes on toggling after NADV changes and the independent read and write timings.

Table 141. FMC_BCRx bitfields (mode D)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x1 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 6 | FACCEN | Set according to memory support |

| 5:4 | MWID | As needed |

| 3:2 | MTYP | As needed |

| 1 | MUXEN | 0x0 |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD HCLK cycles for read accesses). |

| 29:28 | ACCMOD | 0x3 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles) for read accesses. |

| 7:4 | ADDHLD | Duration of the middle phase of the read access (ADDHLD HCLK cycles) |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles) for read accesses. Minimum value for ADDSET is 1. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD+1 HCLK cycles for write accesses). |

| 29:28 | ACCMOD | 0x3 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles). |

| 7:4 | ADDHLD | Duration of the middle phase of the write access (ADDHLD HCLK cycles) |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles) for write accesses. Minimum value for ADDSET is 1. |

Muxed mode - multiplexed asynchronous access to NOR flash memory

Figure 65. Muxed read access waveforms

![Timing diagram for muxed read access waveforms showing signals A[25:16], NADV, NBL[x:0], NEx, NOE, NWE, and AD[15:0] over time, divided into memory transaction phases.](/RM0438-STM32L5/ae11c60feb544e83a0ef802bf234adc0_img.jpg)

The diagram illustrates the timing for a muxed read access to NOR flash memory. The signals shown are:

- A[25:16] : Address lines, stable during the address phase.

- NADV : Address Valid signal, active low, goes low at the start of the address phase and high at the start of the data phase.

- NBL[x:0] : Byte Lane signals, active low, shown toggling at the start and end of the transaction.

- NEx : External memory signal, active low, goes low at the start and high at the start of the data phase.

- NOE : Output Enable signal, active low, goes low at the start of the data phase and high at the end.

- NWE : Write Enable signal, active low, held high throughout the read transaction.

- AD[15:0] : Multiplexed address/data lines. They carry 'Lower address' during the first phase and are 'Data driven by memory' during the second phase.

The transaction is divided into several timing intervals relative to the HCLK signal:

- NBLSET HCLK cycles : Time from the falling edge of NBL to the start of the address phase.

- ADDSET HCLK cycles : Duration of the address phase, from the falling edge of NADV to the falling edge of NEx.

- ADDHLD HCLK cycles : Time from the falling edge of NEx to the start of the data phase.

- DATAST HCLK cycles : Duration of the data phase, from the falling edge of NOE to the falling edge of NADV.

- DATAHLD HCLK cycles : Time from the falling edge of NADV to the falling edge of NOE.

The entire sequence is labeled as a 'Memory transaction' at the top. The diagram is identified by the code MSV41685V1.

Figure 66. Muxed write access waveforms

![Timing diagram for muxed write access waveforms. The diagram shows the relationship between address, data, and control signals over time. Address lines A[25:16] are stable during the memory transaction. NADV (NAND Address Valid) is active low and goes low when the address is valid. NBL[x:0] (NAND Byte Lane) is active low and goes low when the data bus is valid. NEx (NAND External) is active low and goes low when the memory is selected. NOE (NAND Output Enable) is active low and goes low when data is being read. NW E (NAND Write Enable) is active low and goes low when data is being written. AD[15:0] (Address/Data) is multiplexed, showing 'Lower address' and 'Data driven by controller'. The timing is defined by HCLK cycles: NBLSET, ADDSET, ADDHLD, DATAST, and DATAHLD + 1.](/RM0438-STM32L5/6b74f92c0b63e1f3aadb1773646f7e92_img.jpg)

Timing diagram for muxed write access waveforms. The diagram shows the relationship between address, data, and control signals over time. Address lines A[25:16] are stable during the memory transaction. NADV (NAND Address Valid) is active low and goes low when the address is valid. NBL[x:0] (NAND Byte Lane) is active low and goes low when the data bus is valid. NEx (NAND External) is active low and goes low when the memory is selected. NOE (NAND Output Enable) is active low and goes low when data is being read. NW E (NAND Write Enable) is active low and goes low when data is being written. AD[15:0] (Address/Data) is multiplexed, showing 'Lower address' and 'Data driven by controller'. The timing is defined by HCLK cycles: NBLSET, ADDSET, ADDHLD, DATAST, and DATAHLD + 1.

The difference with mode D is the drive of the lower address byte(s) on the data bus.

Table 144. FMC_BCRx bitfields (Muxed mode)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | As needed |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x0 (no effect in Asynchronous mode) |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | Set to 1 if the memory supports this feature. Otherwise keep at 0. |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | 0x0 (no effect in Asynchronous mode) |

| 12 | WREN | As needed |

| 11 | WAITCFG | Don't care |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | Meaningful only if bit 15 is 1 |

| 8 | BURSTEN | 0x0 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | 0x1 |

Table 144. FMC_BCRx bitfields (Muxed mode) (continued)

| Bit number | Bit name | Value to set |

|---|---|---|

| 5:4 | MWID | As needed |

| 3:2 | MTYP | 0x2 (NOR flash memory) or 0x1(PSRAM) |

| 1 | MUXEN | 0x1 |

| 0 | MBKEN | 0x1 |

Table 145. FMC_BTRx bitfields (Muxed mode)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Duration of the data hold phase (DATAHLD HCLK cycles for read accesses, DATAHLD+1 HCLK cycles for write accesses). |

| 29:28 | ACCMOD | 0x0 |

| 27:24 | DATLAT | Don't care |

| 23:20 | CLKDIV | Don't care |

| 19:16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15:8 | DATAST | Duration of the second access phase (DATAST HCLK cycles). |

| 7:4 | ADDHLD | Duration of the middle phase of the access (ADDHLD HCLK cycles). |

| 3:0 | ADDSET | Duration of the first access phase (ADDSET HCLK cycles). Minimum value for ADDSET is 1. |

WAIT management in asynchronous accesses

If the asynchronous memory asserts the WAIT signal to indicate that it is not yet ready to accept or to provide data, the ASYNCWAIT bit has to be set in FMC_BCRx register.

If the WAIT signal is active (high or low depending on the WAITPOL bit), the second access phase (Data setup phase), programmed by the DATAST bits, is extended until WAIT becomes inactive. Unlike the data setup phase, the first access phases (Address setup and Address hold phases), programmed by the ADDSET and ADDHLD bits, are not WAIT sensitive and so they are not prolonged.

The data setup phase must be programmed so that WAIT can be detected 4 HCLK cycles before the end of the memory transaction. The following cases must be considered:

- 1. The memory asserts the WAIT signal aligned to NOE/NWE which toggles:

- 2. The memory asserts the WAIT signal aligned to NEx (or NOE/NWE not toggling):

if

then:

otherwise

where \( \text{max\_wait\_assertion\_time} \) is the maximum time taken by the memory to assert the WAIT signal once NEx/NOE/NWE is low.

Figure 67 and Figure 68 show the number of HCLK clock cycles that are added to the memory access phase after WAIT is released by the asynchronous memory (independently of the above cases).

Figure 67. Asynchronous wait during a read access waveforms

![Timing diagram for asynchronous wait during a read access. The diagram shows five signals over time: A[25:0] (Address), NEx (Next), NWAIT (Next Wait), NOE (Next Output Enable), and D[15:0] (Data). The 'Memory transaction' starts when A[25:0] is stable and NEx goes low. It is divided into 'address phase' (from NEx falling to NOE falling) and 'data setup phase' (from NOE falling to NEx rising). NWAIT is shown as 'don't care' during the address phase and data setup phase. NOE goes low at the start of the data setup phase. D[15:0] is driven by memory during the data setup phase. A '4HCLK' cycle duration is marked at the end of the data setup phase, just before NEx rises.](/RM0438-STM32L5/2576477d2bef80ebe31a7c9169392251_img.jpg)

- 1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

Figure 68. Asynchronous wait during a write access waveforms

![Timing diagram for asynchronous wait during a write access. The diagram shows five signal waveforms over time: A[25:0] (Address), NEx (Active-low chip select), NWAIT (Active-low wait signal), NWE (Active-low write enable), and D[15:0] (Data). The transaction is divided into an 'address phase' and a 'data setup phase'. NEx is low during the address phase. NWAIT is shown as 'don't care' during the address phase and 'don't care' during the data setup phase. NWE is low during the data setup phase. D[15:0] is driven by the FMC during the data setup phase. The diagram indicates a 'Memory transaction' duration, '1HCLK' (one system clock cycle) and '3HCLK' (three system clock cycles) intervals. The source 'MSV40168V1' is noted in the bottom right.](/RM0438-STM32L5/89a4e4f0ccbcfc3d57d98f7cdac00173_img.jpg)

- 1. NWAIT polarity depends on WAITPOL bit setting in FMC_BCRx register.

CellularRAM™ (PSRAM) refresh management

The CellularRAM™ does not enable maintaining the chip select signal (NE) low for longer than the \( t_{CEM} \) timing specified for the memory device. This timing can be programmed in the FMC_PSCSNTR register. It defines the maximum duration of the NE low pulse in HCLK cycles for asynchronous accesses and FMC_CLK cycles for synchronous accesses

19.6.5 Synchronous transactions

The memory clock, FMC_CLK, is a submultiple of HCLK. It depends on the value of CLKDIV and the MWID/ AHB data size, following the formula given below:

Whatever MWID size: 16 or 8-bit, the FMC_CLK divider ratio is always defined by the programmed CLKDIV value.

Example:

- • If CLKDIV=1, MWID = 16 bits, AHB data size=8 bits, FMC_CLK=HCLK/2.

NOR flash memories specify a minimum time from NADV assertion to CLK high. To meet this constraint, the FMC does not issue the clock to the memory during the first internal clock cycle of the synchronous access (before NADV assertion). This guarantees that the rising edge of the memory clock occurs in the middle of the NADV low pulse.

Data latency versus NOR memory latency

The data latency is the number of cycles to wait before sampling the data. The DATLAT value must be consistent with the latency value specified in the NOR flash configuration

register. The FMC does not include the clock cycle when NADV is low in the data latency count.

Caution: Some NOR flash memories include the NADV Low cycle in the data latency count, so that the exact relation between the NOR flash latency and the FMC DATLAT parameter can be either:

- • NOR flash latency = (DATLAT + 2) CLK clock cycles

- • or NOR flash latency = (DATLAT + 3) CLK clock cycles

Some recent memories assert NWAIT during the latency phase. In such cases DATLAT can be set to its minimum value. As a result, the FMC samples the data and waits long enough to evaluate if the data are valid. Thus the FMC detects when the memory exits latency and real data are processed.

Other memories do not assert NWAIT during latency. In this case the latency must be set correctly for both the FMC and the memory, otherwise invalid data are mistaken for good data, or valid data are lost in the initial phase of the memory access.

Single-burst transfer

When the selected bank is configured in Burst mode for synchronous accesses, if for example an AHB single-burst transaction is requested on 16-bit memories, the FMC performs a burst transaction of length 1 (if the AHB transfer is 16 bits), or length 2 (if the AHB transfer is 32 bits) and de-assert the chip select signal when the last data is strobed.

Such transfers are not the most efficient in terms of cycles compared to asynchronous read operations. Nevertheless, a random asynchronous access would first require to re-program the memory access mode, which would altogether last longer.

Cross boundary page for CellularRAM™ 1.5

CellularRAM™ 1.5 does not allow burst access to cross the page boundary. The FMC controller is used to split automatically the burst access when the memory page size is reached by configuring the CPSIZE bits in the FMC_BCR1 register following the memory page size.

Wait management

For synchronous NOR flash memories, NWAIT is evaluated after the programmed latency period, which corresponds to (DATLAT+2) CLK clock cycles.

If NWAIT is active (low level when WAITPOL = 0, high level when WAITPOL = 1), wait states are inserted until NWAIT is inactive (high level when WAITPOL = 0, low level when WAITPOL = 1).

When NWAIT is inactive, the data is considered valid either immediately (bit WAITCFG = 1) or on the next clock edge (bit WAITCFG = 0).

During wait-state insertion via the NWAIT signal, the controller continues to send clock pulses to the memory, keeping the chip select and output enable signals valid. It does not consider the data as valid.

In Burst mode, there are two timing configurations for the NOR flash NWAIT signal:

- • The flash memory asserts the NWAIT signal one data cycle before the wait state (default after reset).

- • The flash memory asserts the NWAIT signal during the wait state

The FMC supports both NOR flash wait state configurations, for each chip select, thanks to the WAITCFG bit in the FMC_BCRx registers (x = 0..3).

Figure 69. Wait configuration waveforms

![Timing diagram showing HCLK, CLK, A[25:16], NADV, NWAIT (WAITCFG=0), NWAIT (WAITCFG=1), and A/D[15:0] signals during a memory transaction. It illustrates the effect of the WAITCFG bit on the insertion of wait states.](/RM0438-STM32L5/a626dcaff2bc35e6d470d5bb3c28a2c7_img.jpg)

The diagram illustrates the timing of a memory transaction, defined as a burst of 4 half words. The signals shown are:

- HCLK : High-frequency system clock.

- CLK : Memory clock signal.

- A[25:16] : Address lines, showing addr[25:16] during the address phase.

- NADV : Address Valid signal, active low.

- NWAIT (WAITCFG = 0) : Wait signal when WAITCFG is 0. It goes low after the address phase and returns high before the data burst.

- NWAIT (WAITCFG = 1) : Wait signal when WAITCFG is 1. It goes low after the address phase and returns high after the third data word, effectively inserting a wait state.

- A/D[15:0] : Address/Data lines, showing addr[15:0] during the address phase and data during the data burst.

Vertical dashed lines mark the clock edges for the data burst. An arrow labeled "inserted wait state" indicates the extra clock cycle introduced when WAITCFG = 1. The diagram is labeled ai15798c in the bottom right corner.

Figure 70. Synchronous multiplexed read mode waveforms - NOR, PSRAM (CRAM)

![Timing diagram for synchronous multiplexed read mode. It shows signals HCLK, CLK, A[25:16], NEx, NOE, NWE, NADV, NWAIT, and A/D[15:0] over time. A memory transaction is shown as a burst of 4 half words (data1, data2, data3, data4). Addressing starts with addr[25:16] and Add[15:0]. Data strobes are indicated for each data word. An inserted wait state is shown between data1 and data2. The diagram is labeled ai17723g.](/RM0438-STM32L5/8255b46b37a64b2961ba900a691f0483_img.jpg)

- 1. Byte lane outputs (NBL are not shown; for NOR access, they are held high, and, for PSRAM (CRAM) access, they are held low.

Table 146. FMC_BCRx bitfields (Synchronous multiplexed read mode)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | Don't care |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | No effect on synchronous read |

| 18:16 | CPSIZE | 0x0 (no effect in Asynchronous mode) |

| 15 | ASYNCWAIT | 0x0 |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | To be set to 1 if the memory supports this feature, to be kept at 0 otherwise |

| 12 | WREN | No effect on synchronous read |

| Bit number | Bit name | Value to set |

|---|---|---|

| 11 | WAITCFG | To be set according to memory |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | To be set according to memory |

| 8 | BURSTEN | 0x1 |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Set according to memory support (NOR flash memory) |

| 5-4 | MWID | As needed |

| 3-2 | MTYP | 0x1 or 0x2 |

| 1 | MUXEN | As needed |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:30 | DATAHLD | Don't care |

| 29:28 | ACCMOD | 0x0 |

| 27-24 | DATLAT | Data latency |

| 27-24 | DATLAT | Data latency |

| 23-20 | CLKDIV | 0x0 to get CLK = HCLK 0x1 to get CLK = 2 × HCLK .. |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15-8 | DATAST | Don't care |

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Don't care |

Figure 71. Synchronous multiplexed write mode waveforms - PSRAM (CRAM)

![Timing diagram for synchronous multiplexed write mode waveforms. The diagram shows signals HCLK, CLK, A[25:16], NEx, NOE, NWE, NADV, NWAIT (WAITCFG = 0), and A/D[15:0] over time. A memory transaction is shown as a burst of 2 half words. The address is latched on the rising edge of CLK. Data1 and data2 are written on the rising edge of CLK. The diagram also shows the insertion of a wait state when NWAIT is asserted. The timing parameters (DATLAT + 2) CLK cycles and 1 clock cycle are indicated.](/RM0438-STM32L5/482fa2f59e158ce1214b65eab934c612_img.jpg)

Timing diagram for synchronous multiplexed write mode waveforms. The diagram shows signals HCLK, CLK, A[25:16], NEx, NOE, NWE, NADV, NWAIT (WAITCFG = 0), and A/D[15:0] over time. A memory transaction is shown as a burst of 2 half words. The address is latched on the rising edge of CLK. Data1 and data2 are written on the rising edge of CLK. The diagram also shows the insertion of a wait state when NWAIT is asserted. The timing parameters (DATLAT + 2) CLK cycles and 1 clock cycle are indicated.

- 1. The memory must issue NWAIT signal one cycle in advance, accordingly WAITCFG must be programmed to 0.

- 2. Byte Lane (NBL) outputs are not shown, they are held low while NEx is active.

Table 148. FMC_BCRx bitfields (Synchronous multiplexed write mode)

| Bit number | Bit name | Value to set |

|---|---|---|

| 31:24 | Reserved | 0x000 |

| 23:22 | NBLSET[1:0] | Don't care |

| 20 | CCLKEN | As needed |

| 19 | CBURSTRW | 0x1 |

| 18:16 | CPSIZE | As needed (0x1 for CRAM 1.5) |

| 15 | ASYNCWAIT | 0x0 |

| 14 | EXTMOD | 0x0 |

| 13 | WAITEN | To be set to 1 if the memory supports this feature, to be kept at 0 otherwise. |

| Bit number | Bit name | Value to set |

|---|---|---|

| 12 | WREN | 0x1 |

| 11 | WAITCFG | 0x0 |

| 10 | Reserved | 0x0 |

| 9 | WAITPOL | to be set according to memory |

| 8 | BURSTEN | no effect on synchronous write |

| 7 | Reserved | 0x1 |

| 6 | FACCEN | Set according to memory support |

| 5-4 | MWID | As needed |

| 3-2 | MTYP | 0x1 |

| 1 | MUXEN | As needed |

| 0 | MBKEN | 0x1 |

| Bit number | Bit name | Value to set |

|---|---|---|

| 31-30 | DATAHLD | Don't care |

| 29:28 | ACCMOD | 0x0 |

| 27-24 | DATLAT | Data latency |

| 23-20 | CLKDIV | 0x0 to get CLK = HCLK 0x1 to get CLK = 2 × HCLK |

| 19-16 | BUSTURN | Time between NEx high to NEx low (BUSTURN HCLK). |

| 15-8 | DATAST | Don't care |

| 7-4 | ADDHLD | Don't care |

| 3-0 | ADDSET | Don't care |

19.6.6 NOR/PSRAM controller registers

SRAM/NOR-flash chip-select control register for bank x (FMC_BCRx)

Address offset: 0x00 + 0x8 * (x - 1), (x = 1 to 4)

Reset value: 0x0000 30DB, 0x0000 30D2, 0x0000 30D2, 0x0000 30D2

This register contains the control information of each memory bank, used for SRAMs, PSRAM, FRAM and NOR flash memories.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | NBLSET[1:0] | WFDIS | CCLK EN | CBURST RW | CPSIZE[2:0] | |||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ASYNC WAIT | EXT MOD | WAIT EN | WREN | WAIT CFG | Res. | WAIT POL | BURST EN | Res. | FACC EN | MWID[1:0] | MTYP[1:0] | MUX EN | MBK EN | ||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:22 NBLSET[1:0] : Byte lane (NBL) setup

These bits configure the NBL setup timing from NBLx low to chip select NEx low.

00: NBL setup time is 0 AHB clock cycle

01: NBL setup time is 1 AHB clock cycle

10: NBL setup time is 2 AHB clock cycles

11: NBL setup time is 3 AHB clock cycles

Bit 21 WFDIS : Write FIFO disable

This bit disables the Write FIFO used by the FMC controller.

0: Write FIFO enabled (Default after reset)

1: Write FIFO disabled

Note: The WFDIS bit of the FMC_BCR2..4 registers is don't care. It is only enabled through the FMC_BCR1 register.

Bit 20 CCLKEN : Continuous clock enable

This bit enables the FMC_CLK clock output to external memory devices.

0: The FMC_CLK is only generated during the synchronous memory access (read/write transaction). The FMC_CLK clock ratio is specified by the programmed CLKDIV value in the FMC_BCRx register (default after reset).

1: The FMC_CLK is generated continuously during asynchronous and synchronous access. The FMC_CLK clock is activated when the CCLKEN is set.

Note: The CCLKEN bit of the FMC_BCR2..4 registers is don't care. It is only enabled through the FMC_BCR1 register. Bank 1 must be configured in Synchronous mode to generate the FMC_CLK continuous clock.

Note: If CCLKEN bit is set, the FMC_CLK clock ratio is specified by CLKDIV value in the FMC_BTR1 register. CLKDIV in FMC_BWTR1 is don't care.

Note: If the Synchronous mode is used and CCLKEN bit is set, the synchronous memories connected to other banks than Bank 1 are clocked by the same clock (the CLKDIV value in the FMC_BTR2..4 and FMC_BWTR2..4 registers for other banks has no effect.)

Bit 19 CBURSTRW: Write burst enableFor PSRAM (CRAM) operating in Burst mode, the bit enables synchronous accesses during write operations. The enable bit for synchronous read accesses is the BURSTEN bit in the FMC_BCRx register.

0: Write operations are always performed in Asynchronous mode.

1: Write operations are performed in Synchronous mode.

Bits 18:16 CPSIZE[2:0]: CRAM page sizeThese are used for CellularRAM™ 1.5 which does not allow burst access to cross the address boundaries between pages. When these bits are configured, the FMC controller splits automatically the burst access when the memory page size is reached (refer to memory datasheet for page size).

000: No burst split when crossing page boundary (default after reset)

001: 128 bytes

010: 256 bytes

011: 512 bytes

100: 1024 bytes

Others: Reserved, must not be used

Bit 15 ASYNCWAIT: Wait signal during asynchronous transfersThis bit enables/disables the FMC to use the wait signal even during an asynchronous protocol.

0: NWAIT signal is not taken in to account when running an asynchronous protocol (default after reset).

1: NWAIT signal is taken in to account when running an asynchronous protocol.

Bit 14 EXTMOD: Extended mode enableThis bit enables the FMC to program the write timings for non multiplexed asynchronous accesses inside the FMC_BWTR register, thus resulting in different timings for read and write operations.

0: values inside FMC_BWTR register are not taken into account (default after reset)

1: values inside FMC_BWTR register are taken into account

Note: When the Extended mode is disabled, the FMC can operate in mode 1 or mode 2 as follows:

- – Mode 1 is the default mode when the SRAM/PSRAM memory type is selected (MTYP = 0x0 or 0x01)

- – Mode 2 is the default mode when the NOR memory type is selected (MTYP = 0x10).

This bit enables/disables wait-state insertion via the NWAIT signal when accessing the memory in Synchronous mode.

0: NWAIT signal is disabled (its level not taken into account, no wait state inserted after the programmed flash latency period).

1: NWAIT signal is enabled (its level is taken into account after the programmed latency period to insert wait states if asserted) (default after reset).

Bit 12 WREN: Write enable bitThis bit indicates whether write operations are enabled/disabled in the bank by the FMC.

0: Write operations are disabled in the bank by the FMC, an AHB error is reported.

1: Write operations are enabled for the bank by the FMC (default after reset).

Bit 11 WAITCFG: Wait timing configurationThe NWAIT signal indicates whether the data from the memory are valid or if a wait state must be inserted when accessing the memory in Synchronous mode. This configuration bit determines if NWAIT is asserted by the memory one clock cycle before the wait state or during the wait state:

0: NWAIT signal is active one data cycle before wait state (default after reset).

1: NWAIT signal is active during wait state (not used for PSRAM).

Bit 10 Reserved, must be kept at reset value.Bit 9 WAITPOL : Wait signal polarity bitDefines the polarity of the wait signal from memory used for either in Synchronous or Asynchronous mode.

0: NWAIT active low (default after reset)

1: NWAIT active high

Bit 8 BURSTEN : Burst enable bitThis bit enables/disables synchronous accesses during read operations. It is valid only for synchronous memories operating in Burst mode.

0: Burst mode disabled (default after reset). Read accesses are performed in Asynchronous mode.

1: Burst mode enable. Read accesses are performed in Synchronous mode.

Bit 7 Reserved, must be kept at reset value.

Bit 6 FACCEN : Flash access enableEnables NOR flash memory access operations.

0: Corresponding NOR flash memory access is disabled.

1: Corresponding NOR flash memory access is enabled (default after reset).

Bits 5:4 MWID[1:0] : Memory data bus widthDefines the external memory device width, valid for all type of memories.

00: 8 bits

01: 16 bits (default after reset)

10: reserved

11: reserved

Bits 3:2 MTYP[1:0] : Memory typeDefines the type of external memory attached to the corresponding memory bank.

00: SRAM/FRAM (default after reset for Bank 2..4)

01: PSRAM (CRAM) / FRAM

10: NOR flash/OneNAND flash (default after reset for Bank 1)

11: reserved

Bit 1 MUXEN : Address/data multiplexing enable bitWhen this bit is set, the address and data values are multiplexed on the data bus, valid only with NOR and PSRAM memories:

0: Address/data non multiplexed

1: Address/data multiplexed on databus (default after reset)

Bit 0 MBKEN : Memory bank enable bitEnables the memory bank. After reset Bank1 is enabled, all others are disabled. Accessing a disabled bank causes an ERROR on AHB bus.

0: Corresponding memory bank is disabled.

1: Corresponding memory bank is enabled.

SRAM/NOR-flash chip-select timing register for bank x (FMC_BTRx)Address offset: 0x04 + 0x8 * (x - 1), (x = 1 to 4)

Reset value: 0x0FFF FFFF

This register contains the control information of each memory bank, used for SRAMs, PSRAM and NOR flash memories. If the EXTMOD bit is set in the FMC_BCRx register, then this register is partitioned for write and read access, that is, 2 registers are available: one to configure read accesses (this register) and one to configure write accesses (FMC_BWTRx registers).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| DATAHLD[1:0] | ACCMOD[1:0] | DATLAT[3:0] | CLKDIV[3:0] | BURSTURN[3:0] | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DATAST[7:0] | ADDHLD[3:0] | ADDSET[3:0] | |||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 31:30 DATAHLD[1:0] : Data hold phase duration

These bits are written by software to define the duration of the data hold phase in HCLK cycles (refer to Figure 54 to Figure 66 ), used in asynchronous accesses:

For read accesses

00: DATAHLD phase duration = 0 × HCLK clock cycle (default)

01: DATAHLD phase duration = 1 × HCLK clock cycle

10: DATAHLD phase duration = 2 × HCLK clock cycle

11: DATAHLD phase duration = 3 × HCLK clock cycle

For write accesses

00: DATAHLD phase duration = 1 × HCLK clock cycle (default)

01: DATAHLD phase duration = 2 × HCLK clock cycle

10: DATAHLD phase duration = 3 × HCLK clock cycle

11: DATAHLD phase duration = 4 × HCLK clock cycle

Bits 29:28 ACCMOD[1:0] : Access mode

Specifies the asynchronous access modes as shown in the timing diagrams. These bits are taken into account only when the EXTMOD bit in the FMC_BCRx register is 1.

00: Access mode A

01: Access mode B

10: Access mode C

11: Access mode D

Bits 27:24 DATLAT[3:0] : (see note below bit descriptions): Data latency for synchronous memory

For synchronous access with read/write Burst mode enabled (BURSTEN / CBURSTRW bits set), defines the number of memory clock cycles (+2) to issue to the memory before reading/writing the first data:

This timing parameter is not expressed in HCLK periods, but in FMC_CLK periods.

For asynchronous access, this value is don't care.

0000: Data latency of 2 CLK clock cycles for first burst access

1111: Data latency of 17 CLK clock cycles for first burst access (default value after reset)

Bits 23:20 CLKDIV[3:0] : Clock divide ratio (for FMC_CLK signal)

Defines the period of FMC_CLK clock output signal, expressed in number of HCLK cycles:

0000: FMC_CLK period= 1x HCLK period

0001: FMC_CLK period = 2 × HCLK periods

0010: FMC_CLK period = 3 × HCLK periods

1111: FMC_CLK period = 16 × HCLK periods (default value after reset)

In asynchronous NOR flash, SRAM or PSRAM accesses, this value is don't care.

Note: Refer to Section 19.6.5: Synchronous transactions for FMC_CLK divider ratio formula

Bits 19:16 BUSTURN[3:0] : Bus turnaround phase duration

These bits are written by software to add a delay at the end of current read or write transaction to next transaction on the same bank.

This delay is used to match the minimum time between consecutive transactions ( \( t_{\text{EHEL}} \) from NEx high to NEx low) and the maximum time needed by the memory to free the data bus after a read access ( \( t_{\text{EHQZ}} \) , chip enable high to output Hi-Z). This delay is recommended for mode D and muxed mode. For non-muxed memory, the bus turnaround delay can be set to minimum value.

For FRAM memories, the bus turnaround delay must be configured to match the minimum \( t_{\text{PC}} \) (precharge time) timings. The bus turnaround delay is inserted between any consecutive transactions on the same bank (read/read, write/write, read/write and write/read) to match the \( t_{\text{PC}} \) memory timing. The chip select is toggling between any consecutive accesses.

0000: BUSTURN phase duration = 1 HCLK clock cycle added

...

1111: BUSTURN phase duration = 16 x HCLK clock cycles added (default value after reset)

Bits 15:8 DATAST[7:0] : Data-phase duration

These bits are written by software to define the duration of the data phase (refer to Figure 54 to Figure 66 ), used in asynchronous accesses:

0000 0000: Reserved

0000 0001: DATAST phase duration = 1 x HCLK clock cycles