8. Power control (PWR)

The power controller (PWR) main features are:

- • Power supplies and supply domains

- – Core domains (VCORE)

- – VDD domain

- – Backup domain (VBAT)

- – Analog domain (VDDA)

- – Supply for the SMPS power stage (available on SMPS packages)

- – VDDIO2 domain on Port G

- – VDDUSB for USB transceiver

- • System supply voltage regulation

- – SMPS step down converter

- – Voltage regulator (LDO)

- – External SMPS mode

- • Power supply supervision

- – POR/PDR monitor

- – BOR monitor

- – PVD monitor

- – PWM monitor (VDDA, VDDUSB, VDDIO2)

- – Temperature threshold monitor

- – Upper VDD voltage threshold monitor

- • Power management

- – Operating modes

- – Voltage scaling control

- – Low-power modes

- • VBAT battery charging

- • TrustZone security

8.1 Power supplies and supply domains

The STM32L552xx and STM32L562xx devices require a 1.71 V to 3.6 V operating supply voltage ( \( V_{DD} \) ). Several peripherals are supplied through independent power domains: \( V_{DDA} \) , \( V_{DDIO2} \) , \( V_{DDUSB} \) . Those supplies must not be provided without a valid operating supply on the \( V_{DD} \) pin.

- •

\(

V_{DD} = 1.71 \text{ V to } 3.6 \text{ V}

\)

\( V_{DD} \) is the external power supply for the I/Os, the internal regulator (or the SMPS step down converter depending on the device) and the system analog such as reset, power management and internal clocks. It is provided externally through VDD pins. - •

\(

V_{DDA} = 1.62 \text{ V (ADCs/COMPs) / } 1.8 \text{ V (DACs/OPAMPs) / } 2.4 \text{ V (VREFBUF) to } 3.6 \text{ V}

\)

\( V_{DDA} \) is the external analog power supply for A/D converters, D/A converters, voltage reference buffer, operational amplifiers and comparators. The \( V_{DDA} \) voltage level is independent from the \( V_{DD} \) voltage. \( V_{DDA} \) should be preferably connected to \( V_{DD} \) when

these peripherals are not used.

- • \( V_{DDSMPS} = 2\text{ V to }3.6\text{ V} \)

\( V_{DDSMPS} \) is the external power supply for the SMPS step down converter. It is provided externally through \( V_{DDSMPS} \) supply pin, and shall be connected to the same supply as \( V_{DD} \) .

- • \( V_{LXSMPS} \) is the switched SMPS step down converter output.

- • \( V_{15SMPS} \) are the power supply for the system regulator. It is provided externally through the SMPS step down converter \( V_{LXSMPS} \) output.

Note: The SMPS power supply pins are available only on a specific package with SMPS step down converter option.

- • \( V_{DD12} = 1.05\text{ to }1.32\text{ V} \)

\( V_{DD12} \) is the external power supply bypassing the internal regulator when connected to an external SMPS. It is provided externally through \( V_{DD12} \) pins and only available on packages with the external SMPS supply option. \( V_{DD12} \) does not require any external decoupling capacitance and cannot support any external load.

Note: The \( V_{DD12} \) power supply pins are available only on a specific package with external SMPS option.

- • \( V_{DDUSB} = 3.0\text{ V to }3.6\text{ V} \)

\( V_{DDUSB} \) is the external independent power supply for USB transceivers. The \( V_{DDUSB} \) voltage level is independent from the \( V_{DD} \) voltage. \( V_{DDUSB} \) should be preferably connected to \( V_{DD} \) when the USB is not used.

The \( V_{DDUSB} \) power supply may not be present as a dedicated pin, but to be internally bonded to \( V_{DD} \) . For such devices, \( V_{DD} \) has to respect the \( V_{DDUSB} \) supply range when the USB is used.

- • \( V_{DDIO2} = 1.08\text{ V to }3.6\text{ V} \)

\( V_{DDIO2} \) is the external power supply for 14 I/Os (Port G[15:2]). The \( V_{DDIO2} \) voltage level is independent from the \( V_{DD} \) voltage and should preferably be connected to \( V_{DD} \) when PG[15:2] are not used.

- • \( V_{BAT} = 1.55\text{ V to }3.6\text{ V} \)

\( V_{BAT} \) is the power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when \( V_{DD} \) is not present. \( V_{BAT} \) is internally bonded to \( V_{DD} \) for small packages without dedicated pin.

- • \( V_{REF-} \) , \( V_{REF+} \)

\( V_{REF+} \) is the input reference voltage for ADCs and DACs. It is also the output of the internal voltage reference buffer when enabled.

When \( V_{DDA} < 2\text{ V} \) , \( V_{REF+} \) must be equal to \( V_{DDA} \) .

When \( V_{DDA} > 2\text{ V} \) , \( V_{REF+} \) must be between 2 V and \( V_{DDA} \) .

\( V_{REF+} \) can be grounded when ADC and DAC are not active.

The internal voltage reference buffer supports two output voltages, which are configured with VRS bit in the VREFBUF_CSR register:

- – \( V_{REF+} \) around 2.048 V. This requires \( V_{DDA} \) equal to or higher than 2.4 V.

- – \( V_{REF+} \) around 2.5 V. This requires \( V_{DDA} \) equal to or higher than 2.8 V.

On some packages, \( V_{REF-} \) and \( V_{REF+} \) pins are not available. When not available on the package, they are internally bonded to respectively \( V_{SSA} \) and \( V_{DDA} \) .

When the VREF+ is double-bonded with VDDA in a package, the internal voltage reference buffer is not available and must be kept disable (refer to related device datasheet for packages pinout description).

V REF- must always be equal to V SSA .

In the STM32L552xx and STM32L562xx devices, the I/Os, the embedded LDO regulator and the system analog peripherals (such as PLLs and reset block) are fed by V DD supply source. The embedded linear voltage regulator is used to supply the internal digital power V CORE . V CORE is the power supply for digital peripherals and memories.

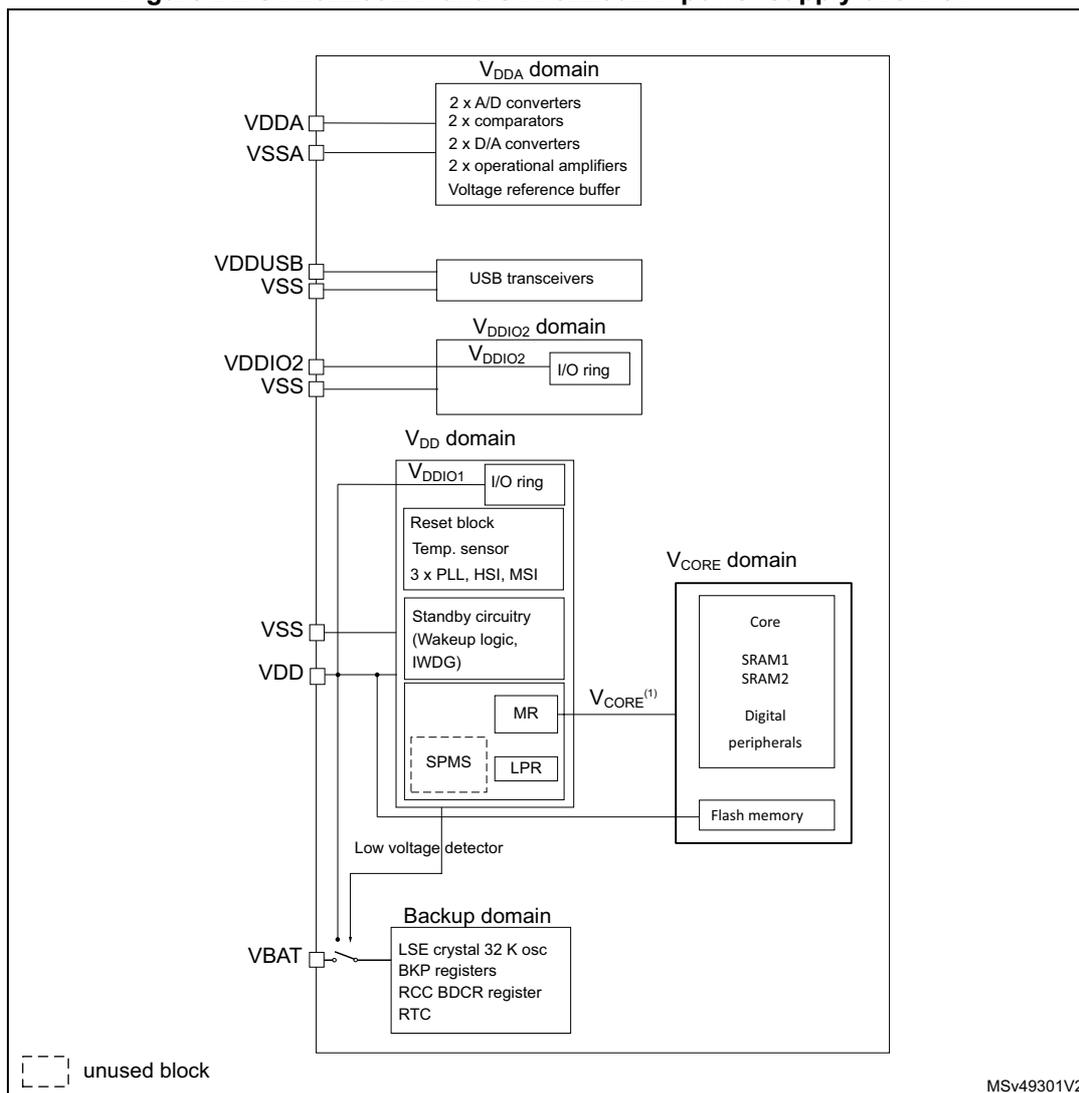

Figure 21. STM32L552xx and STM32L562xx power supply overview

The diagram illustrates the power supply architecture for STM32L552xx and STM32L562xx devices, organized into several power domains:

- V DDA domain: Connected to VDDA and VSSA pins. It contains 2 x A/D converters, 2 x comparators, 2 x D/A converters, 2 x operational amplifiers, and a Voltage reference buffer.

- USB transceivers: Connected to VDDUSB and VSS pins.

- V DDIO2 domain: Connected to VDDIO2 and VSS pins. It contains a V DDIO2 I/O ring.

- V

DD

domain:

Connected to VDD and VSS pins. It contains:

- V DDIO1 I/O ring

- Reset block, Temp. sensor, 3 x PLL, HSI, MSI

- Standby circuitry (Wakeup logic, IWDG)

- MR (Main Regulator)

- SPMS (unused block)

- LPR (Low Power Regulator)

- V CORE domain: Connected to V CORE (1) from the MR or LPR. It contains the Core, SRAM1, SRAM2, Digital peripherals, and Flash memory.

- Backup domain: Connected to VBAT pin. It contains an LSE crystal 32 K osc, BKP registers, RCC BDCR register, and RTC. A Low voltage detector is also connected to this domain.

A legend indicates that blocks with a dashed border (SPMS) are unused. The diagram is labeled MSV49301V2.

- 1. V CORE is provided by either MR or LPR, depending on the operating power mode.

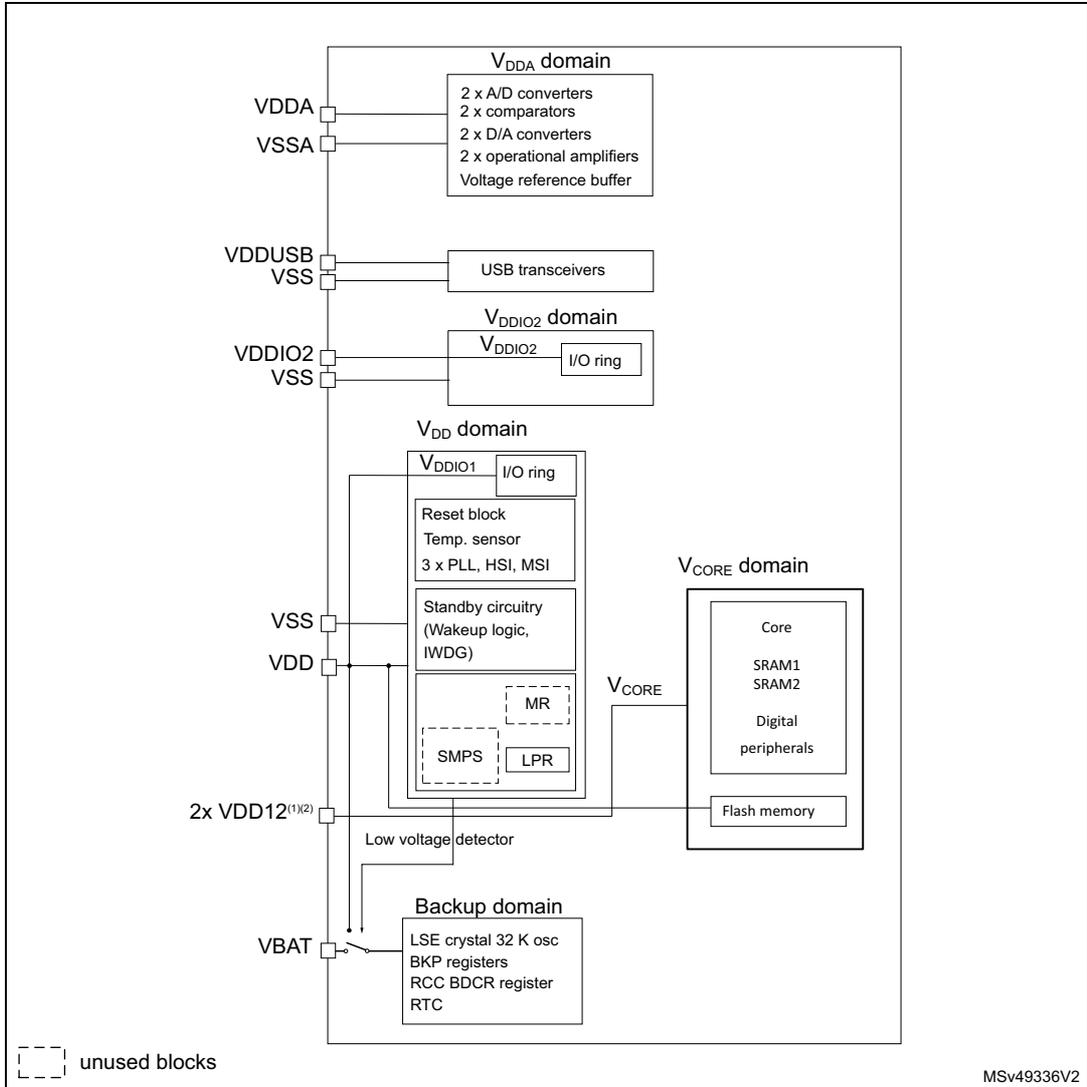

In the STM32L552xxxP and STM32L562xxxP devices, the I/Os and system analog peripherals (such as PLLs, and reset block) are fed by \( V_{DD} \) supply source. The \( V_{CORE} \) power supply for digital peripherals and memories is generated from external SMPS.

Figure 22. STM32L552xxxP and STM32L562xxxP power supply overview

- 1. If the selected package has the external SMPS option but no external SMPS is used by the application (the embedded LDO is used instead), the VDD12 pins are kept unconnected.

- 2. VDD12 is intended to be connected with external SMPS (switched-mode power supply) to generate the \( V_{CORE} \) logic supply in Run, Sleep and Stop 0 modes only.

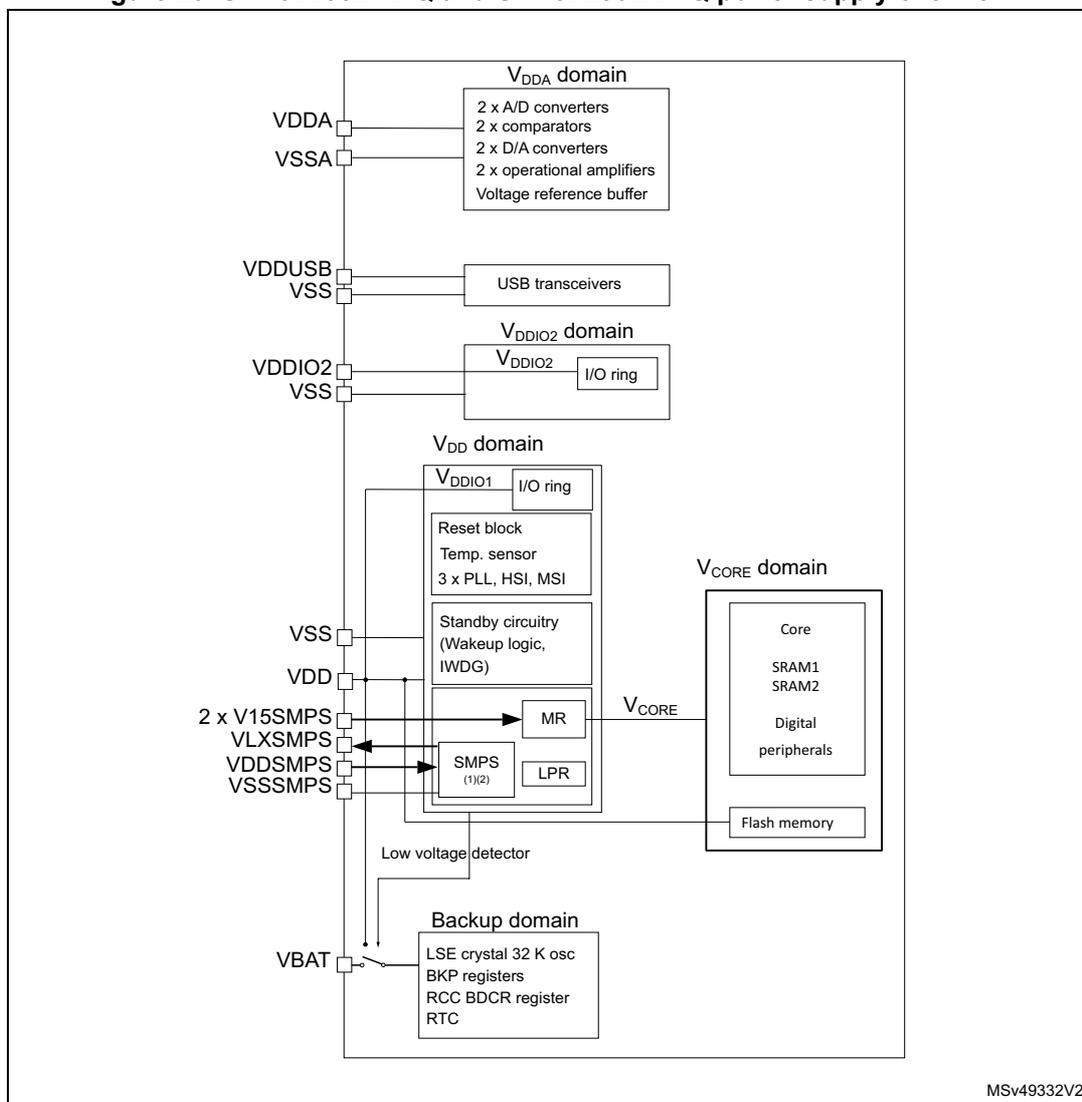

In the STM32L552xxxQ and STM32L562xxxQ devices, the I/Os, the embedded SMPS step down converter and the system analog peripherals (such as PLLs and reset block) are fed by \( V_{DD} \) supply source. The embedded linear main voltage regulator that provides the \( V_{CORE} \) supply for digital peripherals and memories is fed by the SMPS step down converter output.

Figure 23. STM32L552xxxQ and STM32L562xxxQ power supply overview

MSV49332V2

- 1. Refer to Figure 24 for SMPS step down converter power supply scheme.

- 2. During Low-power sleep, Low-power run, Stop 1, Stop 2, Standby and Shutdown modes, the SMPS step down converter is switched to Open mode. In Low-power sleep, Low-power run, Stop 1, Stop 2 and Standby with SRAM2 retention modes, the low-power regulator is used to provide the \( V_{CORE} \) . The SMPS is used in Run, Sleep and Stop 0 modes. It supplies the main regulator which provides the \( V_{CORE} \) .

Note: If the selected package has the SMPS step down converter option but the SMPS is not used by the application (and the embedded LDO is used instead), it is recommended to set the SMPS power supply pins as follows:

- - VDDSMPS and VLXSMPS connected to VSS

- - V15SMPS connected to VDD.

8.1.1 Independent analog peripherals supply

To improve ADC and DAC conversion accuracy and to extend the supply flexibility, the analog peripherals have an independent power supply which can be separately filtered and shielded from noise on the PCB.

- • The analog peripherals voltage supply input is available on a separate \( V_{DDA} \) pin.

- • An isolated supply ground connection is provided on \( V_{SSA} \) pin.

The \( V_{DDA} \) supply voltage can be different from \( V_{DD} \) . The presence of \( V_{DDA} \) must be checked before enabling any of the analog peripherals supplied by \( V_{DDA} \) (A/D converter, D/A converter, comparators, operational amplifiers, voltage reference buffer).

The \( V_{DDA} \) supply can be monitored by the peripheral voltage monitoring (PVM), and compared with two thresholds (1.65 V for PVM3 or 1.8 V for PVM4), refer to Section 8.3.3: Peripheral voltage monitoring (PVM) for more details.

When a single supply is used, \( V_{DDA} \) can be externally connected to \( V_{DD} \) through the external filtering circuit in order to ensure a noise-free \( V_{DDA} \) reference voltage.

ADC and DAC reference voltage

To ensure a better accuracy on low-voltage inputs and outputs, the user can connect to \( V_{REF+} \) a separate reference voltage lower than \( V_{DDA} \) . \( V_{REF+} \) is the highest voltage, represented by the full scale value, for an analog input (ADC) or output (DAC) signal.

\( V_{REF+} \) can be provided either by an external reference or by an internal buffered voltage reference (VREFBUF).

The internal voltage reference is enabled by setting the ENVR bit in the Section 23.4.1: VREFBUF control and status register (VREFBUF_CSR) . The voltage reference is set to 2.5 V when the VRS bit is set and to 2.048 V when the VRS bit is cleared. The internal voltage reference can also provide the voltage to external components through \( V_{REF+} \) pin. Refer to the device datasheet and to Section 23: Voltage reference buffer (VREFBUF) for further information.

8.1.2 Independent I/O supply rail

Some I/Os from port G (PG[15:2]) are supplied from a separate supply rail. The power supply for this rail can range from 1.08 V to 3.6 V and is provided externally through the \( V_{DDIO2} \) pin. The \( V_{DDIO2} \) voltage level is completely independent from \( V_{DD} \) or \( V_{DDA} \) . The \( V_{DDIO2} \) pin is available only for some packages. Refer to the pinout diagrams or tables in the related device datasheet(s) for I/O list(s).

After reset, the I/Os supplied by \( V_{DDIO2} \) are logically and electrically isolated and therefore are not available. The isolation must be removed before using any I/O from PG[15:2], by setting the IOSV bit in the PWR_CR2 register, once the \( V_{DDIO2} \) supply is present.

The \( V_{DDIO2} \) supply is monitored by the peripheral voltage monitoring (PVM2) and compared with the internal reference voltage ( \( 3/4 V_{REFINT} \) , around 0.9V), refer to Section 8.3.3: Peripheral voltage monitoring (PVM) for more details.

8.1.3 Independent USB transceivers supply

The USB transceivers are supplied from a separate \( V_{DDUSB} \) power supply pin. \( V_{DDUSB} \) range is from 3.0 V to 3.6 V and is completely independent from \( V_{DD} \) or \( V_{DDA} \) .

After reset, the USB features supplied by \( V_{DDUSB} \) are logically and electrically isolated and therefore are not available. The isolation must be removed before using the USB peripheral, by setting the USV bit in the PWR_CR2 register, once the \( V_{DDUSB} \) supply is present.

The \( V_{DDUSB} \) supply is monitored by the peripheral voltage monitoring (PVM1) and compared with the internal reference voltage ( \( V_{REFINT} \) , around 1.2 V), refer to Section 8.3.3: Peripheral voltage monitoring (PVM) for more details.

8.1.4 Battery backup domain

To retain the content of the backup registers and supply the RTC function when \( V_{DD} \) is turned off, the VBAT pin can be connected to an optional backup voltage supplied by a battery or by another source.

The VBAT pin powers the RTC unit, the LSE oscillator and the PC13 to PC15 I/Os, allowing the RTC to operate even when the main power supply is turned off. The switch to the \( V_{BAT} \) supply is controlled by the power-down reset embedded in the Reset block.

Warning:

During

\(

t_{RSTTEMPO}

\)

(temporization at

\(

V_{DD}

\)

startup) or after a PDR has been detected, the power switch between

\(

V_{BAT}

\)

and

\(

V_{DD}

\)

remains connected to

\(

V_{BAT}

\)

.

During the startup phase, if

\(

V_{DD}

\)

is established in less than

\(

t_{RSTTEMPO}

\)

(refer to the datasheet for the value of

\(

t_{RSTTEMPO}

\)

) and

\(

V_{DD} > V_{BAT} + 0.6

\)

V, a current may be injected into

\(

V_{BAT}

\)

through an internal diode connected between

\(

V_{DD}

\)

and the power switch (

\(

V_{BAT}

\)

).

If the power supply/battery connected to the VBAT pin cannot support this current injection, it is strongly recommended to connect an external low-drop diode between this power supply and the VBAT pin.

If no external battery is used in the application, it is recommended to connect \( V_{BAT} \) to \( V_{DD} \) supply and add a 100 nF ceramic decoupling capacitor on VBAT pin.

When the backup domain is supplied by \( V_{DD} \) (analog switch connected to \( V_{DD} \) ), the following pins are available:

- • PC13, PC14 and PC15, which can be used as GPIO pins

- • PC13, PC14 and PC15, which can be configured by RTC or LSE (refer to Section 41.3: RTC functional description on page 1396 )

- • PA0/TAMP_IN2/TAMP_OUT1 and PE6/TAMP_IN3/TAMP_OUT6 when they are configured by the tamper as tamper pins

Note: Due to the fact that the analog switch can transfer only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in Output mode is restricted: the speed has to be limited to 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (for example to drive a LED).

When the backup domain is supplied by \( V_{BAT} \) (analog switch connected to \( V_{BAT} \) because \( V_{DD} \) is not present), the following functions are available:

- • PC13, PC14 and PC15 can be controlled only by RTC or LSE (refer to Section 41.3:

- • PA0/TAMP_IN2 and PE6/TAMP_IN3 when they are configured by the tamper as tamper pins

After a system reset, the backup domain (RTC registers and backup registers) is protected against possible unwanted write accesses. To enable access to the backup domain, proceed as follows:

- 1. Enable the power interface clock by setting the PWREN bits in the Section 9.8.13: RCC APB1 peripheral reset register 1 (RCC_APB1RSTR1)

- 2. Set the DBP bit in the Power control register 1 (PWR_CR1) to enable access to the backup domain

- 3. Select the RTC clock source in the RCC Backup domain control register (RCC_BDCR) .

- 4. Enable the RTC clock by setting the RTCEN [15] bit in the RCC Backup domain control register (RCC_BDCR) .

When \( V_{DD} \) is present, It is possible to charge the external battery on VBAT through an internal resistance.

The VBAT charging is done either through a 5 k \( \Omega \) resistor or through a 1.5 k \( \Omega \) resistor depending on the VBRS bit value in the PWR_CR4 register.

The battery charging is enabled by setting VBE bit in the PWR_CR4 register. It is automatically disabled in VBAT mode.

8.2 System supply voltage regulation

8.2.1 Voltage regulator

Two embedded linear voltage regulators supply all the digital circuitries, except for the Standby circuitry and the backup domain. The main regulator output voltage ( \( V_{CORE} \) ) can be programmed by software to three different power ranges (Range 0, Range 1 and Range 2) in order to optimize the consumption depending on the system's maximum operating frequency (refer to Section 9.3.10: Clock source frequency versus voltage scaling and to Section 6.3.3: Read access latency ).

At power-on reset or a system reset, the main regulator voltage Range 2 is selected by default.

The voltage regulators are always enabled after a reset. Depending on the application modes, the \( V_{CORE} \) supply is provided either by the main regulator (MR) or by the low-power regulator (LPR).

- • In Run, Sleep and Stop 0 modes, both regulators are enabled and the main regulator (MR) supplies full power to the \( V_{CORE} \) domain (core, memories and digital peripherals).

- • In Low-power run and Low-power sleep modes, the main regulator is off and the low-power regulator (LPR) supplies low power to the \( V_{CORE} \) domain, preserving the contents of the registers, SRAM1 and SRAM2.

- • In Stop 1 and Stop 2 modes, the main regulator is off and the low-power regulator (LPR) supplies low-power to the \( V_{CORE} \) domain, preserving the contents of the

registers, SRAM1 and SRAM2.

- • In Standby mode, the SRAM2 content can be fully or partially (only 4 Kbytes) preserved (depending on RRS[1:0] bits in the PWR_CR3 register), the main regulator (MR) is off and the low-power regulator (LPR) provides the supply to SRAM2 only. The core, digital peripherals (except Standby circuitry and backup domain) and SRAM1 are powered off.

- • In Standby mode, both regulators are powered off. The contents of the registers, SRAM1 and SRAM2 is lost except for the Standby circuitry and the backup domain.

- • In Shutdown mode, both regulators are powered off. When exiting from Shutdown mode, a power-on reset is generated. Consequently, the contents of the registers, all SRAMs is lost, except for the backup domain.

8.2.2 Embedded SMPS step down converter

The built-in SMPS step down converter is a power-efficient DC/DC non-linear switching regulator that improves low-power performance when the V DD voltage is high enough. The SMPS step down converter automatically enters in Bypass mode when the V DD voltage falls below a V DD minimum value following the selected voltage range and switched back to the selected operating mode when V DD rises above the minimum value.

When the SMPS step down converter is enabled, it can be configured in:

- • High-power mode (HPM): achieving a high efficiency at high current load.

SMPS high-power mode is used in all ranges (0, 1 and 2).

It is the default selected mode after POR reset.

- • Low-power mode (LPM): achieving a high efficiency at low current load.

When enabled, the voltage scaling must not be modified. This mode shall be only selected in Range 2 and when power consumption does not exceed 30 mA.

- • Bypass mode:

When the Bypass mode is enabled, the SMPS step down converter is switched OFF and it is possible to change the voltage scaling. This mode can be forced by software by setting the SMPSBYP bit in PWR_CR4 register. The Bypass mode can be enabled or disabled on the fly at any time by the application software whatever the selected operation mode.

In Range 0 and Range 1, the SMPS Bypass mode is selected automatically when V DD drops below 2.05 V.

In Range 2, if V DD is less than 2.05 V, the SMPS Bypass mode must be forced by software. For this purpose, the PVD0 should monitor the V DD power supply and the software must force bypass mode by setting the SMPSBYP bit in PWR_CR4 register.

The following table summarizes the SMPS behavior depending on the main regulator range, V DD and consumption.

Table 62. SMPS modes summary

| Ranges | Max AHB clock | V CORE | SMPS mode | |

|---|---|---|---|---|

| V DD ≤ 2.05 V | V DD > 2.05 V | |||

| Range 0 | 110 MHz | 1.28 V | Automatic Bypass mode V 15SMPS = V DD | HP mode Max current consumption = 120 mA V 15SMPS = 1.6 V |

| Range 1 | 80 MHz | 1.2 V | Automatic Bypass mode V 15SMPS = V DD | HP mode Max current consumption = 80 mA V 15SMPS = 1.5 V |

| Range 2 | 26 MHz | 1.0 V | Software Bypass mode

(1) V 15SMPS = V DD | LP mode or HP mode Max current consumption = 30 mA V 15SMPS = 1.3 V |

- 1. There is no automatic SMPS bypass in Range 2. The user application should use PVD0 to monitor V DD supply and request the SMPS Bypass mode.

Refer to Table 63 for SMPS step down converter operating mode.

Table 63. SMPS step down converter operating mode

| SMPSBYP bit | SMPSLPEN bit | SMPSHPRDY flag | Description |

|---|---|---|---|

| 0 | 0 | 1 | High-power mode |

| 0 | 1 | 0 | Low-power mode |

| 1 | x | x | Bypass mode |

The sequence to go from Low-power to High-power mode is:

- 1. Clearing the SMPSLPEN bit in the PWR_CR4 register

- 2. Check that the SMPSHPRDY flag is set in PWR_SR1 register

The sequence to go from High-power to Low-power mode is:

- 1. Configure the system frequency and voltage scaling

- 2. Set the SMPSLPEN bit in the PWR_CR4 register

Note: If the Bypass mode is active and the SMPSLPEN bit is set, the switch to SMPS Low-power mode is delayed until the SMPS step down converter exits the Bypass mode.

Note: The SMPS step down converter operating mode and Voltage scaling range selection shall be changed only in RUN mode.

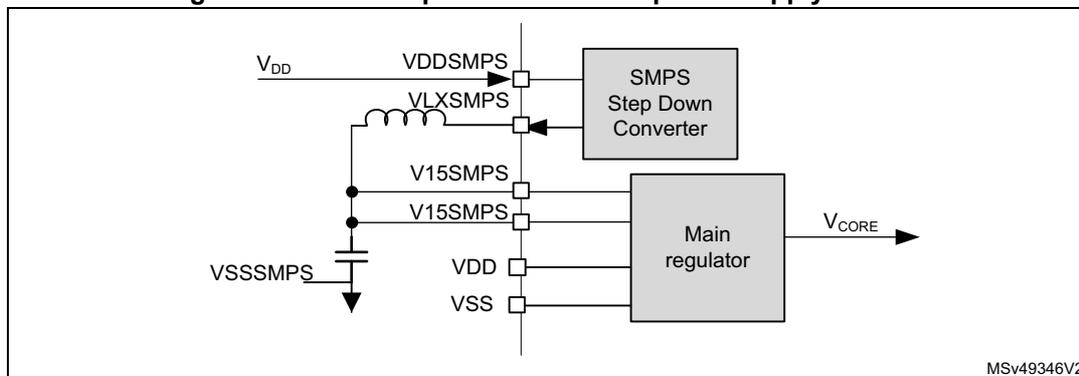

8.2.3 SMPS step down converter power supply scheme

The SMPS step down converter requires an external coil with typical value of 4.7 µH to be connected between the dedicated V LXSMPS pin to V SSSMPS via a capacitor of 4.7µF. It is switched OFF when:

- • LPREG is used

- or

- • SMPS is configured in Bypass mode by software in RUN/SLEEP modes (SMPSBYP bit set in PWR_CR4).

Thus, only main regulator is used by the application.

Refer to Figure 24 below.

Figure 24. SMPS step down converter power supply scheme

If the selected package is with the SMPS step down converter option but it is never used by the application, it is mandatory to set the SMPS power supply pins as follows:

- • \( V_{DDSMPS} \) and \( V_{LXSMPS} \) connected to VSS

- • \( V_{15SMPS} \) connected to VDD

8.2.4 SMPS step down converter versus low-power mode

The SMPS step down converter operating mode depends on the selected operating and upon the system operating modes (LP)Run, (LP)Sleep, Stop 0, Stop 1, Stop 2, Standby, and Shutdown.

During Stop 1, Stop 2, Standby and Shutdown modes the SMPS step down converter is switched to Open mode (see Table 64 ). When exiting from low-power modes (except Shutdown) the SMPS step down converter is set by hardware to the mode selected prior to the low-power mode selection. The SMPS step down converter mode configuration bits in PWR_CR4 (SMPSLEN or SMPSBYP) are retained in Standby mode.

After POR reset, the SMPS step down converter is in High-power mode.

Table 64. SMPS step down converter versus low-power modes

| System operating mode | SMPS step down converter state | Description |

|---|---|---|

| Run, Sleep | ON | SMPS in HPM or LPM mode and, in ranges 0/1 it switches to Bypass mode following VDD minimum value versus the selected voltage range |

| Stop 0 | ON | SMPS in HPM or LPM mode |

| Stop 1, Stop 2, Low power run, Low power sleep, Standby with SRAM2 retention | Open | SMPS is bypassed, LPR regulator is used |

| Standby and Shutdown | Open | SMPS is bypassed |

Note: It is recommended to enable the SMPS bypass mode prior entering Stop modes in order to reduce the wake up time.

Note: If the Bypass mode is requested, entering Stop 1 or Stop 2 or Low-power run or Low-power sleep modes shall be delayed until the SMPS BYPASS ready flag SMPSBYPRDY is set.

Note: In Low-power run mode, the following bits shall not be modified (PWR_CR4: SMPSLPEN, SMPSFSTEN, SMPSBYP).

SMPS step down converter fast startup

After POR reset, the SMPS step down converter starts in High-power mode and in Slow-startup mode. The low-startup feature is selected to limit the inrush current after power-on reset.

However, it is possible to configure a faster startup on the fly and it is applied for next SMPS startup (after a wakeup from low-power mode - except Shutdown and VBAT modes) or for next SMPS output voltage change (Bypass or VOS change). The fast startup is selected by setting the SMPSFSTEN bit in the PWR_CR4 register.

Note: Setting the SMPSFSTEN bit in the PWR_CR4 register allows also a faster switch to Bypass mode (i.e. \( V_{15\text{SMPS}} \) reaching \( V_{\text{DD}} \) ).

Note: The timing needed for Bypass mode to be effective (i.e. SMPSBYPRDY flag is set) is counted starting from \( V_{15} \) already at target value (1.3V (Range 2); 1.5V (Range 1); 1.6V (Range 0)). This timing is determined by the parameter \( V_{15} \) slew rate, depending itself on the fact that fast startup is enabled or disabled. Refer to the device datasheet.

8.2.5 Dynamic voltage scaling management

The dynamic voltage scaling is a power management technique which consists in increasing or decreasing the voltage used for the digital peripherals ( \( V_{\text{CORE}} \) ), according to the application performance and power consumption needs.

Dynamic voltage scaling to increase \( V_{\text{CORE}} \) is known as overvolting. It allows the device to improve its performance.

Dynamic voltage scaling to decrease \( V_{\text{CORE}} \) is known as undervolting. It is performed to save power, particularly in laptop and other mobile devices where the energy comes from a battery and is thus limited.

The main regulator operates in the following ranges:

- • Main regulator Range 0: high performance;

It provides a typical output voltage at 1.28 V. It is used when the system clock frequency is up to 110 MHz. The flash access time for read access is minimum, write and erase operations are possible. - • Main regulator Range 1: medium performance;

It provides a typical output voltage at 1.2 V. It is used when the system clock frequency is up to 80 MHz. The flash access time for read access is minimum, write and erase operations are possible. - • Main regulator Range 2: low-power range.

It provides a typical output voltage at 1.0 V. The system clock frequency can be up to 26 MHz. The flash access time for a read access is increased as compared to Range 1; write and erase operations are not possible.

Voltage scaling is selected through the VOS[1:0] bits in the PWR_CR1 register. The main regulator voltage Range 2 is selected by default.

Note: In Low-power run mode, the VOS[1:0] must not be modified.

Voltage scaling and SMPS step down converter

When the SMPS step down converter is selected, the VOS[1:0] bits must not be modified when the SMPS is in a low-power mode.

When the voltage scaling is updated, the SMPS step down converter output voltage is scaled automatically following the selected voltage range.

The sequence to go from Range 0 /Range 1 to Range 2 is:

- 1. In case of switching from Range 0 to Range 2, the system clock must be divided by 2 using the AHB prescaler before switching to a lower system frequency for at least 1 us and then reconfigure the AHB prescaler.

- 2. Reduce the system frequency to a value lower than 26 MHz.

- 3. Adjust number of wait states according new frequency target in Range 2 (LATENCY bits in the FLASH_ACR).

- 4. Program the VOS[1:0] bits to “10” in the PWR_CR1 register.

The sequence to go from Range 2 to Range 1/Range 0 is:

- 1. Program the VOS[1:0] bits to “01” in the PWR_CR1 register.

- 2. Wait until the VOSF flag is cleared in the PWR_SR2 register.

- 3. Adjust number of wait states according new frequency target in Range 0 or Range 1 (LATENCY bits in the FLASH_ACR).

- 4. Increase the system frequency by following below procedure:

- – If the system frequency is 26 MHz < SYSCLK <= 80 MHz:

- - Configure and switch to PLL for a new system frequency.

- – If the system frequency is SYSCLK > 80 MHz:

- - The system clock must be divided by 2 using the AHB prescaler before switching to a higher system frequency.

- - Configure and switch to PLL for a new system frequency.

- - Wait for at least 1us and then reconfigure the AHB prescaler to get the needed HCLK clock frequency.

- – If the system frequency is 26 MHz < SYSCLK <= 80 MHz:

The sequence to switch from Range 1 to Range 0 is:

- 1. The system clock must be divided by 2 using the AHB prescaler before switching to a higher system frequency.

- 2. Adjust the number of wait states according to the new frequency target in range1

- 3. Configure and switch to new system frequency.

- 4. Wait for at least 1us and then reconfigure the AHB prescaler to get the needed HCLK clock frequency.

The sequence to switch from Range 0 boost mode to Range 1 mode is:

- 1. Adjust the number of wait states according to the new frequency target in Range 0 default mode

- 2. Configure and switch to new system frequency.

8.2.6 VDD12 domain and external SMPS

VDD12 is intended to be connected with external SMPS (switched-mode power supply) to generate the V CORE logic supply in Run, Sleep and Stop 0 modes only.

VDD12 pins correspond to the internal \( V_{CORE} \) powering the digital part of Core, RAMs, FLASH and peripherals. This significantly improves the power consumption with a gain from 50% or more depending of the external SMPS performances.

The main benefit occurs in Run and Sleep modes whereas in Stop 0 mode, the gain is less significant.

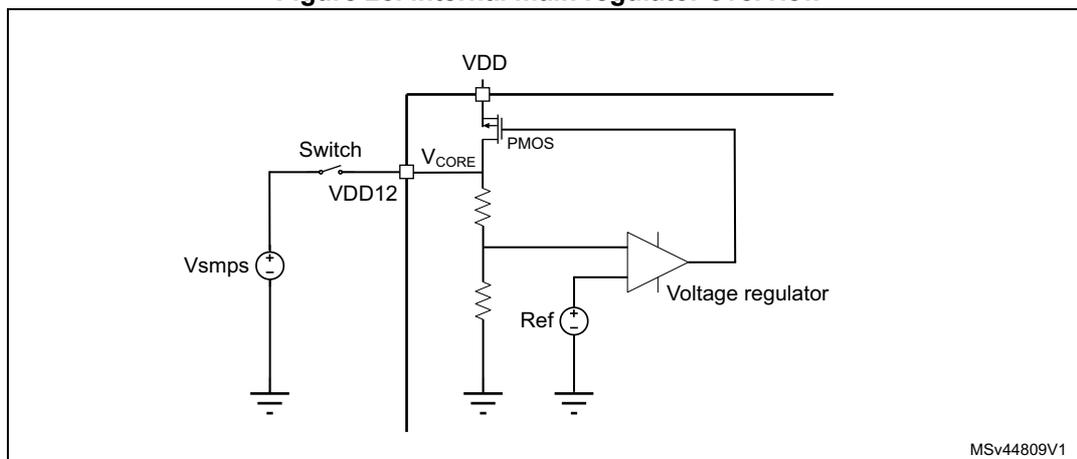

The figure below shows a schematic to understand how the internal regulator stops supplying \( V_{CORE} \) when an external voltage VDD12 is provided.

As VDD12 shares the same pin as output of the internal regulator, applying a slightly higher voltage (typically +50 mV) on the VDD12 blocks, the PMOS and the regulator consumption is negligible.

Figure 25. Internal main regulator overview

The diagram illustrates the internal power regulation circuit. An external voltage source \( V_{smps} \) is connected through a switch to the \( V_{DD12} \) and \( V_{CORE} \) pins. A PMOS transistor is used to switch the internal \( V_{CORE} \) supply. Its source is connected to \( V_{DD12} \) , and its drain is connected to the internal \( V_{DD} \) rail. The gate of the PMOS is driven by the output of an internal voltage regulator. This regulator compares the \( V_{CORE} \) voltage (via a resistive divider) against a reference voltage \( Ref \) . When the switch is closed, \( V_{DD12} \) is powered by the external SMPS. If \( V_{DD12} \) is at a slightly higher potential than the internal regulator's output, the PMOS is turned off, disconnecting the internal regulator from \( V_{CORE} \) and saving power.

A switch, controlled by the chosen GPIO, is inserted between the external SMPS output and VDD12.

There are two possible states:

- • Connected: Switch is closed so external SMPS powers VDD12

- • Disconnected: Switch is open and VDD12 is disconnected from external SMPS output

Proper software management through GPIOs to enable/disable external SMPS and to connect/disconnect external SMPS through the switch, is required to conform with the rules described below. See also Section 8.2.5: Dynamic voltage scaling management .

It is mandatory to respect the following rules to avoid any damage or instability on either digital parts or internal regulators:

- • In Run, Sleep and Stop 0 modes, VDD12 can be connected and should respect

- – \( V_{DD12} < 1.32\text{ V} \)

- –

\(

V_{DD12} \geq V_{CORE} + 50\text{ mV}

\)

giving for main regulator

Range 0, \( V_{CORE} = 1.28\text{ V} \) so VDD12 should be greater than 1.33 V, but this cannot match previous rule \( V_{DD12} < 1.32\text{ V} \) , so it is not a functional use case with an external SMPS.

Range 1, \( V_{CORE} = 1.2\text{ V} \) so VDD12 should be greater than 1.25 V.

Range 2, \( V_{CORE} = 1.0\text{ V} \) so VDD12 should be greater than 1.05 V - – \( V_{DD12} \geq 1.08\text{ V} \) in Range 1 when \( 80\text{ MHz} \geq \text{SYSCLK frequency} \geq 26\text{ MHz} \)

- – \( V_{DD12} \geq 1.14\text{ V} \) in Range 0 when \( \text{SYSCLK frequency} > 80\text{ MHz} \)

- • In all other modes, such as LPRun, LPSleep, Stop 1, Stop 2, Standby and Shutdown modes, VDD12 must be disconnected from external SMPS output. This means that the pin must be connected to a high impedance output:

- – VDD12 connected to HiZ (voltage is provided by internal regulators)

- • Transitions of VDD12 from connected to disconnected is only allowed when \( \text{SYSCLK frequency} \leq 26\text{ MHz} \) to avoid to big voltage drop on main regulator side.

Note: In case of asynchronous reset while having the \( V_{DD12} \leq 1.25\text{ V} \) , VDD12 should switch to HiZ in less than regulator switching time from Range 2 to Range 1 ( \( \sim 1\text{ }\mu\text{s} \) ).

Note:

\(

V_{DD12}

\)

Range 2 is extended down to 1.00 V for better efficiency, thus following formula applies when bit EXTSMPSSEN in the Power control register 4 (PWR_CR4) is set:

Range 2,

\(

V_{CORE} = 0.95\text{ V}

\)

so VDD12 should be greater than 1.00 V

Note: For more details on \( V_{DD12} \) management, refer to AN4978 “Design recommendations for STM32L4xxxx with external SMPS, for ultra-low-power applications with high performance”.

8.3 Power supply supervision

8.3.1 Power-on reset (POR) / power-down reset (PDR) / brown-out reset (BOR)

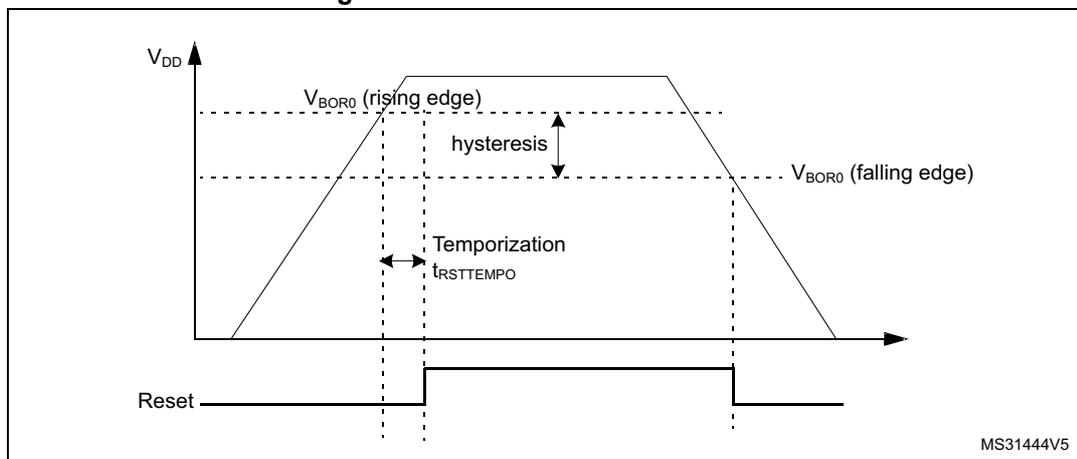

The device has an integrated power-on reset (POR) / power-down reset (PDR), coupled with a brown-out reset (BOR) circuitry. The BOR is active in all power modes except Shutdown mode, and cannot be disabled.

Five BOR thresholds can be selected through option bytes.

During power-on, the BOR keeps the device under reset until the supply voltage \( V_{DD} \) reaches the specified \( V_{BORx} \) threshold. When \( V_{DD} \) drops below the selected threshold, a device reset is generated. When \( V_{DD} \) is above the \( V_{BORx} \) upper limit, the device reset is released and the system can start.

For more details on the brown-out reset thresholds, refer to the electrical characteristics section in the datasheet.

During Stop 2 and Standby modes, it is possible to set the BOR in Ultra-low-power mode to further reduce the current consumption by setting the ULPMEN bit in PWR_CR3 register.

For Stop 2 mode, the BOR Ultra-low-power mode can be set if the BORH is set, otherwise there is no power consumption optimization.

Figure 26. Brown-out reset waveform

- 1. The reset temporization \( t_{RSTTEMPO} \) is present only for the BOR lowest threshold ( \( V_{BOR0} \) ).

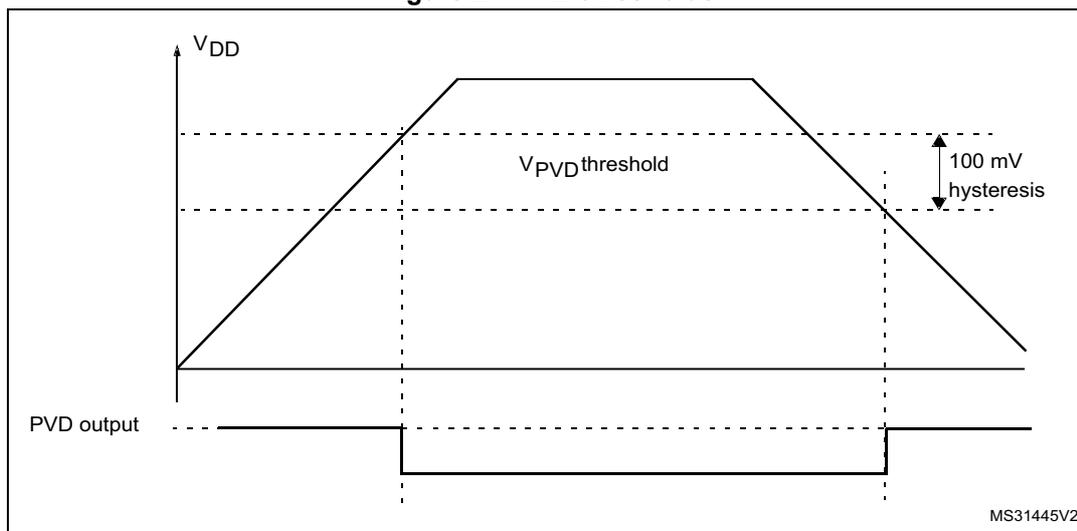

8.3.2 Programmable voltage detector (PVD)

The user can use the PVD to monitor the \( V_{DD} \) power supply by comparing it to a threshold selected by the PLS[2:0] bits in the Power control register 2 (PWR_CR2) .

The PVD is enabled by setting the PVDE bit.

A PVDO flag is available, in the Power status register 2 (PWR_SR2) , to indicate if \( V_{DD} \) is higher or lower than the PVD threshold. This event is internally connected to the EXTI line16 and can generate an interrupt if enabled through the EXTI registers. The rising/falling edge sensitivity of the EXTI line16 is configured to rising edge sensitivity, the interrupt is generated when \( V_{DD} \) drops below the PVD threshold. As an example, the service routine can perform emergency shutdown tasks.

Figure 27. PVD thresholds

8.3.3 Peripheral voltage monitoring (PVM)

Only \( V_{DD} \) is monitored by default, as it is the only supply required for all system-related functions. The other supplies ( \( V_{DDA} \) , \( V_{DDIO2} \) and \( V_{DDUSB} \) ) can be independent from \( V_{DD} \) and can be monitored with four peripheral voltage monitoring (PVM).

Each of the four PVMx (x=1, 2, 3, 4) is a comparator between a fixed threshold \( V_{PVMx} \) and the selected power supply. PVMOx flags indicate if the independent power supply is higher or lower than the PVMx threshold: PVMOx flag is cleared when the supply voltage is above the PVMx threshold, and is set when the supply voltage is below the PVMx threshold.

Each PVM output is connected to an EXTI line and can generate an interrupt if enabled through the EXTI registers. The PVMx output interrupt is generated when the independent power supply drops below the PVMx threshold and/or when it rises above the PVMx threshold, depending on EXTI line rising/falling edge configuration.

Each PVM can remain active in Stop 0, Stop 1 and Stop 2 modes, and the PVM interrupt can wake up from the Stop mode.

Table 65. PVM features

| PVM | Power supply | PVM threshold | EXTI line |

|---|---|---|---|

| PVM1 | \( V_{DDUSB} \) | \( V_{PVM1} \) (around 1.2 V) | 35 |

| PVM2 | \( V_{DDIO2} \) | \( V_{PVM2} \) (around 0.9 V) | 36 |

| PVM3 | \( V_{DDA} \) | \( V_{PVM3} \) (around 1.65 V) | 37 |

| PVM4 | \( V_{DDA} \) | \( V_{PVM4} \) (around 1.8 V) | 38 |

The independent supplies ( \( V_{DDA} \) , \( V_{DDIO2} \) and \( V_{DDUSB} \) ) are not considered as present by default, and a logical and electrical isolation is applied to ignore any information coming from the peripherals supplied by these dedicated supplies.

- • If these supplies are shorted externally to \( V_{DD} \) , the application should assume they are available without enabling any peripheral voltage monitoring.

- • If these supplies are independent from \( V_{DD} \) , the peripheral voltage monitoring (PVM) can be enabled to confirm whether the supply is present or not.

The following sequence must be done before using the USB peripheral:

- 1. If

\(

V_{DDUSB}

\)

is independent from

\(

V_{DD}

\)

:

- a) Enable the PVM1 by setting PVME1 bit in the Power control register 2 (PWR_CR2) .

- b) Wait for the PVM1 wakeup time.

- c) Wait until PVMO1 bit is cleared in the Power status register 2 (PWR_SR2) .

- d) Optional: Disable the PVM1 for consumption saving.

- 2. Set the USV bit in the Power control register 2 (PWR_CR2) to remove the \( V_{DDUSB} \) power isolation.

The following sequence must be done before using any I/O from PG[15:2]:

- 1. If

\(

V_{DDIO2}

\)

is independent from

\(

V_{DD}

\)

:

- a) Enable the PWM2 by setting PVME2 bit in the Power control register 2 (PWR_CR2) .

- b) Wait for the PWM2 wakeup time.

- c) Wait until PVMO2 bit is cleared in the Power control register 2 (PWR_CR2) .

- d) Optional: Disable the PWM2 for consumption saving.

- 2. Set the IOSV bit in the Power control register 2 (PWR_CR2) to remove the \( V_{DDIO2} \) power isolation.

The following sequence must be done before using any of these analog peripherals: analog to digital converters, digital to analog converters, comparators, operational amplifiers, voltage reference buffer:

- 1. If

\(

V_{DDA}

\)

is independent from

\(

V_{DD}

\)

:

- a) Enable the PWM3 (or PWM4) by setting PVME3 (or PVME4) bit in the Power control register 2 (PWR_CR2) .

- b) Wait for the PWM3 (or PWM4) wakeup time.

- c) Wait until PVMO3 (or PVMO4) bit is cleared in the Power status register 2 (PWR_SR2) .

- d) Optional: Disable the PWM3 (or PWM4) for consumption saving.

Enable the analog peripheral, which automatically removes the \( V_{DDA} \) isolation.

8.3.4 Upper voltage threshold monitoring

The upper VDD voltage monitoring is enabled by setting the bit VMONEN in the TAMP_CFGR register.

If the upper VDD voltage monitoring internal tamper is enabled in the TAMP peripheral (ITAMP1E=1 in the TAMP_CR1 register), a tamper event is generated when the VDD domain voltage is above the specified threshold.

The upper VDD monitoring can be periodical. This feature is enabled by setting the bit WUTMONEN in the TAMP configuration register TAMP_CFGR.

In this case, the monitoring is controlled by the RTC wakeup timer PWM resulting from the WUTF flag automatic clear and depending on the bitsfield WUTOCLR in the RTC_WUTR register. For more details, refer to the RTC section.

The monitoring is enabled during the PWM high level and disabled during the PWM low level.

Note: For threshold value, refer to the product datasheet.

Note: In case the VDD is below the functional range, a Brown-out reset is generated.

8.3.5 Temperature threshold monitoring

The temperature monitoring is enabled by setting the bit TMONEN in the TAMP_CFGR register.

If the temperature monitoring internal tamper is enabled in the TAMP peripheral (ITAMP2E=1 in the TAMP_CR1 register), a tamper event is generated when the temperature is above or below the specified thresholds.

The temperature monitoring can be periodical. This feature is enabled by setting the bit WUTMONEN in the TAMP configuration register TAMP_CFGR.

In this case, the monitoring is controlled by the RTC wakeup timer PWM resulting from the WUTF flag automatic clear and depending on the bitfield WUTOCLR in the RTC_WUTR register. For more details, refer to the RTC section.

The monitoring is enabled during the PWM high level and disabled during the PWM low level.

Note: For thresholds values, refer to the product datasheet.

8.4 Power management

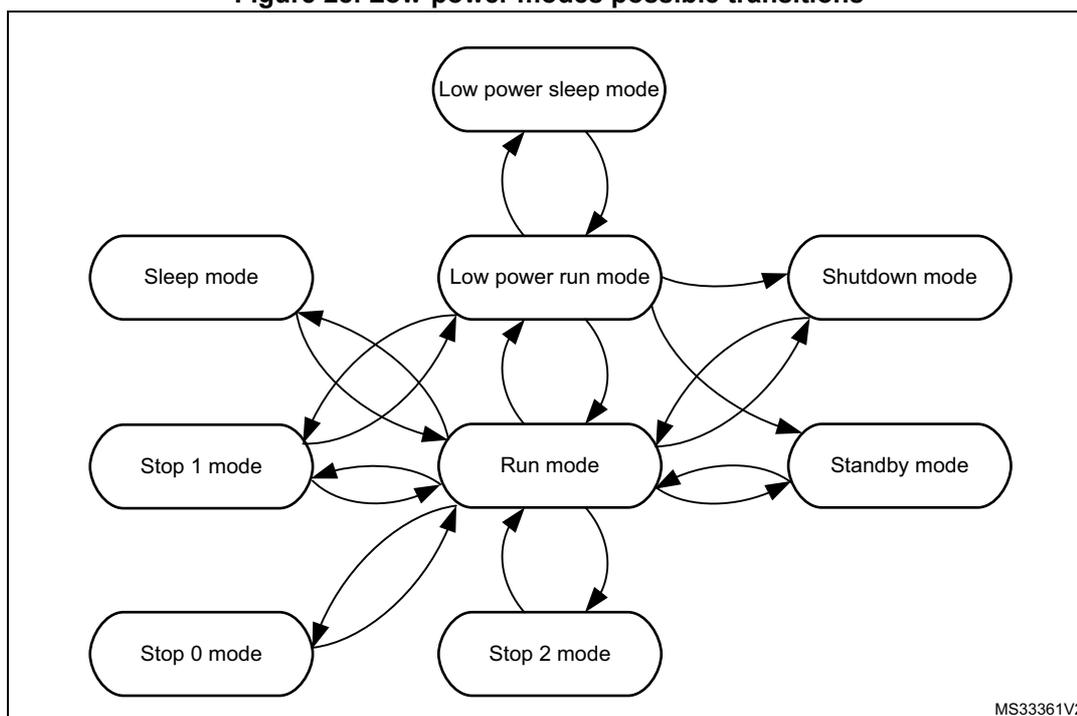

8.4.1 Power modes

By default, the microcontroller is in Run mode after a system or a power reset. Several low-power modes are available to save power when the CPU does not need to be kept running, for example when waiting for an external event. It is up to the user to select the mode that gives the best compromise between low-power consumption, short startup time and available wakeup sources.

The device features eight low-power modes:

- • Sleep mode: CPU clock off, all peripherals including Cortex ® -M33 core such as NVIC and SysTick can run and wake up the CPU when an interrupt or an event occurs. Refer to Section 8.4.5: Sleep mode .

- • Low-power run mode: This mode is achieved when the system clock frequency is reduced below 2 MHz. The code is executed from the SRAM or the flash memory. The regulator is in Low-power mode to minimize the regulator's operating current. Refer to Section 8.4.3: Low-power run mode (LP run) .

- • Low-power sleep mode: This mode is entered from the Low-power run mode: Cortex ® -M33 is off. Refer to Section 8.4.6: Low-power sleep mode (LP sleep) .

- • Stop 0, Stop 1 and Stop 2 modes: SRAM1, SRAM2 and all registers content are retained. All clocks in the V CORE domain are stopped, the PLL, the MSI, the HSI16 and the HSE are disabled. The LSI and the LSE can be kept running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with the wakeup capability can enable the HSI16 RC during the Stop mode to detect their wakeup condition.

In Stop 2 mode, most of the V CORE domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, which allows the fastest wakeup time but with much higher consumption. The active peripherals and wakeup sources are the same as in Stop 1 mode.

The system clock, when exiting from Stop 0, Stop 1 or Stop 2 mode, can be either MSI up to 48 MHz or HSI16, depending on the software configuration.

Refer to Section 8.4.7: Stop 0 mode and Section 8.4.9: Stop 2 mode .

- • Standby mode: V

CORE

domain is powered off. However, it is possible to preserve the full SRAM2 content or only 4 Kbytes:

- – Standby mode with full or only the upper 4 Kbytes of SRAM2 retention when the RRS[1:0] bits are set to '01' or '10' respectively in the PWR_CR3 register. In this

case, the SRAM2 is supplied by the low-power regulator.

- – Standby mode when the RRS[1:0] bits are cleared in PWR_CR3 register. In this case the main regulator and the low-power regulator are powered off.

All clocks in the \( V_{CORE} \) domain are stopped, the PLL, the MSI, the HSI16 and the HSE are disabled. The LSI and the LSE can be kept running.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The system clock, when exiting Standby modes, is MSI from 1 MHz up to 8 MHz.

Refer to Section 8.4.10: Standby mode .

- • Shutdown mode: \( V_{CORE} \) domain is powered off. All clocks in the \( V_{CORE} \) domain are stopped, the PLL, the MSI, the HSI16, the LSI and the HSE are disabled. The LSE can be kept running. The system clock, when exiting the Shutdown mode, is MSI at 4 MHz. In this mode, the supply voltage monitoring is disabled and the product behavior is not guaranteed in case of a power voltage drop. Refer to Section 8.4.11: Shutdown mode .

In addition, the power consumption in Run mode can be reduced by one of the following means:

- • Slowing down the system clocks

- • Gating the clocks to the APB and AHB peripherals when they are unused.

Figure 28. Low-power modes possible transitions

graph TD; Run[Run mode] <--> LPR[Low power run mode]; Run <--> S[Sleep mode]; Run <--> S1[Stop 1 mode]; Run <--> S0[Stop 0 mode]; Run <--> S2[Stop 2 mode]; Run <--> SD[Standby mode]; Run <--> SH[Shutdown mode]; LPR <--> S; LPR <--> S1; LPR <--> S0; LPR <--> S2; LPR <--> SD; LPR <--> SH; LPR <--> LPS[Low power sleep mode]; S <--> S1; S <--> S0; S <--> S2; S <--> SD; S <--> SH; S <--> LPS; S1 <--> S0; S1 <--> S2; S1 <--> SD; S1 <--> SH; S1 <--> LPS; S0 <--> S2; S0 <--> SD; S0 <--> SH; S0 <--> LPS; S2 <--> SD; S2 <--> SH; S2 <--> LPS; SD <--> SH; SD <--> LPS; SH <--> LPS;

Table 66. Low-power mode summary

| Mode name | Entry | Wakeup source (1) | Wakeup system clock | Effect on clocks | Voltage regulators | |

|---|---|---|---|---|---|---|

| MR | LPR | |||||

| Sleep (Sleep-now or Sleep-on-exit) | WFI or Return from ISR | Any interrupt | Same as before entering Sleep mode | CPU clock OFF no effect on other clocks or analog clock sources | ON | ON |

| WFE | Wakeup event | |||||

| Low-power run | Set LPR bit | Clear LPR bit | Same as low-power run clock | None | OFF | ON |

| Low-power sleep | Set LPR bit + WFI or Return from ISR | Any interrupt | Same as before entering Low-power sleep mode | CPU clock OFF no effect on other clocks or analog clock sources | OFF | ON |

| Set LPR bit + WFE | Wakeup event | |||||

| Stop 0 | LPMS="000" + SLEEPDEEP bit + WFI or Return from ISR or WFE | Any EXTI line (configured in the EXTI registers) Specific peripherals events | HSI16 when STOP- WUCK=1 in RCC_CFGR MSI with the frequency before entering the Stop mode when STOP- WUCK=0. | ON | ||

| Stop 1 | LPMS="001" + SLEEPDEEP bit + WFI or Return from ISR or WFE | |||||

| Stop 2 | LPMS="010" + SLEEPDEEP bit + WFI or Return from ISR or WFE | OFF | ||||

| Standby with SRAM2_4KB | LPMS="011" + Set RRS[1:0] bits to "10" + SLEEPDEEP bit + WFI or Return from ISR or WFE | WKUP pin edge, RTC event, external reset in NRST pin, IWDG reset | MSI from 1 MHz up to 8 MHz | All clocks OFF except LSI and LSE | ||

| Standby with SRAM2_Full | LPMS="011" + Set RRS bits to "01" + SLEEPDEEP bit + WFI or Return from ISR or WFE | |||||

| Standby | LPMS="011" + Clear RRS bits + SLEEPDEEP bit + WFI or Return from ISR or WFE | OFF | OFF | |||

| Shutdown | LPMS="1--" + SLEEPDEEP bit + WFI or Return from ISR or WFE | WKUP pin edge, RTC event, external reset in NRST pin | MSI 4 MHz | All clocks OFF except LSE | OFF | OFF |

1. Refer to Table 67: Functionalities depending on the working mode .

Table 67. Functionalities depending on the working mode (1)

| Peripheral | Run | Sleep | Low-power run | Low-power sleep | Stop 0/1 | Stop 2 | Standby | Shutdown | VBAT | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | Wakeup capability | - | Wakeup capability | - | Wakeup capability | - | Wakeup capability | ||||||

| CPU | Y | - | Y | - | - | - | - | - | - | - | - | - | - |

| Flash memory (2 Mbytes) | O (2) | O (2) | O (2) | O (2) | - | - | - | - | - | - | - | - | - |

| SRAM1 (192 Kbytes) | Y | Y (3) | Y | Y (3) | Y | - | Y | - | - | - | - | - | - |

| SRAM2 (64 Kbytes) | Y | Y (3) | Y | Y (3) | Y | - | Y | - | O (4) | - | - | - | - |

| FSMC | O | O | O | O | - | - | - | - | - | - | - | - | - |

| OctoSPI | O | O | O | O | - | - | - | - | - | - | - | - | - |

| OTFDEC | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Backup registers | Y | Y | Y | Y | Y | - | Y | - | Y | - | Y | - | Y |

| Brownout reset (BOR) | Y | Y | Y | Y | Y | Y | Y | Y | Y | Y | - | - | - |

| Programmable voltage detector (PVD) | O | O | O | O | O | O | O | O | - | - | - | - | - |

| Peripheral voltage monitor (PVMx; x=1,2,3,4) | O | O | O | O | O | O | O | O | - | - | - | - | - |

| DMA | O | O | O | O | - | - | - | - | - | - | - | - | - |

| High speed internal (HSI16) | O | O | O | O | (5) | - | (5) | - | - | - | - | - | - |

| Oscillator HSI48 | O | O | - | - | - | - | - | - | - | - | - | - | - |

| High speed external (HSE) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Low speed internal (LSI) | O | O | O | O | O | - | O | - | O | - | - | - | - |

| Low speed external (LSE) | O | O | O | O | O | - | O | - | O | - | O | - | O |

| Multi speed internal (MSI) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Clock security system (CSS) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Clock security system on LSE | O | O | O | O | O | O | O | O | O | O | - | - | - |

| Peripheral | Run | Sleep | Low-power run | Low-power sleep | Stop 0/1 | Stop 2 | Standby | Shutdown | VBAT | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | Wakeup capability | - | Wakeup capability | - | Wakeup capability | - | Wakeup capability | ||||||

| V DD voltage monitoring, temperature monitoring | O | O | O | O | O | O | O | O | O | O | - | - | - |

| RTC / TAMP | O | O | O | O | O | O | O | O | O | O | O | O | O |

| Number of RTC Tamper pins | 8 | 8 | 8 | 8 | 8 | O | 8 | O | 8 | O | 8 | O | 3 |

| USB, UCPD | O (8) | O (8) | - | - | - | O | - | - | - | - | - | - | - |

| USARTx (x=1,2,3,4,5) | O | O | O | O | O (6) | O (6) | - | - | - | - | - | - | - |

| Low-power UART (LPUART) | O | O | O | O | O (6) | O (6) | O (6) | O (6) | - | - | - | - | - |

| I2Cx (x=1,2,4) | O | O | O | O | O (7) | O (7) | - | - | - | - | - | - | - |

| I2C3 | O | O | O | O | O (7) | O (7) | O (7) | O (7) | - | - | - | - | - |

| SPIx (x=1,2,3) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| FDCAN1 | O | O | O | O | - | - | - | - | - | - | - | - | - |

| SDMMC1 | O | O | O | O | - | - | - | - | - | - | - | - | - |

| SAIx (x=1,2) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| DFSDM1 | O | O | O | O | - | - | - | - | - | - | - | - | - |

| ADCx (x=1,2) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| DACx (x=1,2) | O | O | O | O | O | - | - | - | - | - | - | - | - |

| VREFBUF | O | O | O | O | O | - | - | - | - | - | - | - | - |

| OPAMPx (x=1,2) | O | O | O | O | O | - | - | - | - | - | - | - | - |

| COMPx (x=1,2) | O | O | O | O | O | O | O | O | - | - | - | - | - |

| Temperature sensor | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Timers (TIMx) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Low-power timer 1, 3 (LPTIM1 and LPTIM3) | O | O | O | O | O | O | O | O | - | - | - | - | - |

| Low-power timer 2 (LPTIM2) | O | O | O | O | O | O | - | - | - | - | - | - | - |

| Independent watchdog (IWDG) | O | O | O | O | O | O | O | O | O | O | - | - | - |

| Peripheral | Run | Sleep | Low-power run | Low-power sleep | Stop 0/1 | Stop 2 | Standby | Shutdown | VBAT | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | - | Wake-up capability | ||||||

| Window watchdog (WWDG) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| SysTick timer | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Touch sensing controller (TSC) | O | O | O | O | - | - | - | - | - | - | - | - | - |

| Random number generator (RNG) | O (8) | O (8) | - | - | - | - | - | - | - | - | - | - | - |

| AES hardware accelerator | O | O | O | O | - | - | - | - | - | - | - | - | - |

| HASH hardware accelerator | O | O | O | O | - | - | - | - | - | - | - | - | - |

| PKA | O | O | O | O | - | - | - | - | - | - | - | - | - |

| CRC calculation unit | O | O | O | O | - | - | - | - | - | - | - | - | - |

| GPIOs | O | O | O | O | O | O | O | O | (9) 5 pins (10) | (11) 5 pins (10) | - | ||

1. Legend: Y = yes (enable). O = optional (disable by default, can be enabled by software). - = not available.

Gray cells highlight the wakeup capability in each mode.

2. The flash can be configured in Power-down mode. By default, it is not in Power-down mode.

3. The SRAM clock can be gated on or off.

4. 4 Kbytes or full SRAM2 content is preserved depending on RRS[1:0] bits configuration in PWR_CR3 register.

5. Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

8. Voltage scaling range 1 only.

9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

10. The I/Os with wakeup from standby/shutdown capability are: PA0, PC13, PE6, PA2, PC5.

11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

Debug mode

By default, the debug connection is lost if the application puts the MCU in Stop 0, Stop 1, Stop 2, Standby or Shutdown mode while the debug features are used. This is due to the fact that the Cortex ® -M33 core is no longer clocked.

However, by setting some configuration bits in the DBGMCU_CR register, the software can be debugged even when using the low-power modes extensively. For more details, refer to Section 52.2.5: Debug and low-power modes .

8.4.2 Run mode

Slowing down system clocks

In Run mode, the speed of the system clocks (SYSCLK, HCLK, PCLK) can be reduced by programming the prescaler registers. These prescalers can also be used to slow down the peripherals before entering the Sleep mode.

For more details, refer to Section 9.8.3: RCC clock configuration register (RCC_CFGR) .

Peripheral clock gating

In Run mode, the HCLK and PCLK for individual peripherals and memories can be stopped at any time to reduce the power consumption.

To further reduce the power consumption in Sleep mode, the peripheral clocks can be disabled prior to executing the WFI or WFE instructions.

The peripheral clock gating is controlled by the RCC_AHBxENR and RCC_APBxENR registers.

Disabling the peripherals clocks in Sleep mode can be performed automatically by resetting the corresponding bit in the RCC_AHBxSMENR and RCC_APBxSMENR registers.

8.4.3 Low-power run mode (LP run)

To further reduce the consumption when the system is in Run mode, the regulator can be configured in low-power mode. In this mode, the system frequency should not exceed 2 MHz.

Refer to the product datasheet for more details on voltage regulator and peripherals operating conditions.

I/O states in Low-power run mode

In Low-power run mode, all I/O pins keep the same state as in Run mode.

Entering the Low-power run mode

To enter the Low-power run mode, proceed as follows:

- 1. Optional: Jump into the SRAM and power-down the flash by setting the RUN_PD bit in the Flash access control register (FLASH_ACR) .

- 2. Decrease the system clock frequency below 2 MHz.

- 3. Force the regulator in Low-power mode by setting the LPR bit in the PWR_CR1 register.

Refer to Table 68: Low-power run on how to enter the Low-power run mode.

Exiting the Low-power run mode

To exit the Low-power run mode, proceed as follows:

- 1. Force the regulator in Main mode by clearing the LPR bit in the PWR_CR1 register.

- 2. Wait until REGLPF bit is cleared in the PWR_SR2 register.

- 3. Increase the system clock frequency.

Refer to Table 68: Low-power run on how to exit the Low-power run mode.

Table 68. Low-power run

| Low-power run mode | Description |

|---|---|

| Mode entry | Decrease the system clock frequency below 2 MHz LPR = 1 |

| Mode exit | LPR = 0 Wait until REGLPF = 0 Increase the system clock frequency |

| Wakeup latency | Regulator wakeup time from low-power mode |

8.4.4 Low-power modes

Entering into a low-power mode

Low-power modes are entered by the MCU by executing the WFI (wait for interrupt), or WFE (wait for event) instructions, or when the SLEEPONEXIT bit in the Cortex®-M33 system control register is set on Return from ISR .

Entering into a low-power mode through WFI or WFE is executed only if no interrupt is pending or no event is pending.

Exiting from a low-power mode

From Sleep mode and Stop mode the MCU exits the low-power mode depending on the way the low-power mode was entered:

- • If the WFI instruction or return from ISR was used to enter the low-power mode, any peripheral interrupt acknowledged by the NVIC can wake up the device.

- • If the WFE instruction is used to enter the low-power mode, the MCU exits the low-power mode as soon as an event occurs. The wakeup event can be generated either by:

- – NVIC IRQ interrupt.

- - When SEVONPEND = 0 in the Cortex®-M33 system control register. By enabling an interrupt in the peripheral control register and in the NVIC. When the MCU resumes from WFE, the peripheral interrupt pending bit and the NVIC peripheral IRQ channel pending bit (in the NVIC interrupt clear pending register) have to be cleared.

- – NVIC IRQ interrupt.

Only NVIC interrupts with sufficient priority wake up and interrupt the MCU.

- - When SEVONPEND = 1 in the Cortex®-M33 System Control register.

By enabling an interrupt in the peripheral control register and optionally in the NVIC. When the MCU resumes from WFE, the peripheral interrupt pending bit and

when enabled the NVIC peripheral IRQ channel pending bit (in the NVIC interrupt clear pending register) have to be cleared.

All NVIC interrupts wakes up the MCU, even the disabled ones. Only enabled NVIC interrupts with sufficient priority wake up and interrupt the MCU.

- – Event

Configuring a EXTI line in Event mode. When the CPU resumes from WFE, it is not necessary to clear the EXTI peripheral interrupt pending bit or the NVIC IRQ channel pending bit as the pending bits corresponding to the event line is not set. It may be necessary to clear the interrupt flag in the peripheral.

From Standby modes, and Shutdown modes the MCU exits the low-power mode through an external reset (NRST pin), an IWDG reset, a rising edge on one of the enabled WKUPx pins or a RTC event occurs (see Figure 398: RTC block diagram ).

After waking up from Standby or Shutdown mode, program execution restarts in the same way as after a Reset (boot pin sampling, option bytes loading, reset vector is fetched, etc.).

8.4.5 Sleep mode

I/O states in Sleep mode

In Sleep mode, all I/O pins keep the same state as in Run mode.

Entering the Sleep mode

The Sleep mode is entered according Section : Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex ® -M33 System Control register is clear.

Refer to Table 69: Sleep mode for details on how to enter the Sleep mode.

Exiting the Sleep mode

The Sleep mode is exit according Section : Exiting from a low-power mode .

Refer to Table 69: Sleep mode for more details on how to exit the Sleep mode.

Table 69. Sleep mode

| Sleep-now mode | Description |

|---|---|

| Mode entry | WFI (Wait for Interrupt) or WFE (Wait for Event) while:

Refer to the Cortex ® -M33 system control register. On return from ISR while:

Refer to the Cortex ® -M33 System Control register. |

Table 69. Sleep mode (continued)

| Sleep-now mode | Description |

|---|---|

| Mode exit | If WFI or return from ISR was used for entry If WFE was used for entry and SEVONPEND = 0: If WFE was used for entry and SEVONPEND = 1: |

| Wakeup latency | None |

8.4.6 Low-power sleep mode (LP sleep)

Refer to the product datasheet for more details on voltage regulator and peripherals operating conditions.

I/O states in Low-power sleep mode

In Low-power sleep mode, all I/O pins keep the same state as in Run mode.

Entering the Low-power sleep mode

The Low-power sleep mode is entered from Low-power run mode according to Section : Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex ® -M33 system control register is clear.

Refer to Table 70: Low-power sleep for details on how to enter the Low-power sleep mode.

Exiting the Low-power sleep mode

The Low-power sleep mode is exit according to Section : Exiting from a low-power mode . When exiting the Low-power sleep mode by issuing an interrupt or an event, the MCU is in Low-power run mode.

Refer to Table 70: Low-power sleep for details on how to exit the Low-power sleep mode.

Table 70. Low-power sleep

| Low-power sleep-now mode | Description |

|---|---|

| Low-power sleep mode is entered from the Low-power run mode. WFI (Wait for Interrupt) or WFE (Wait for Event) while: – SLEEPDEEP = 0 – No interrupt (for WFI) or event (for WFE) is pending Refer to the Cortex®-M33 System Control register. | |

| Mode entry | Low-power sleep mode is entered from the Low-power run mode. On return from ISR while: – SLEEPDEEP = 0 and – SLEEPONEXIT = 1 – No interrupt is pending Refer to the Cortex®-M33 System Control register. |

| Mode exit | If WFI or Return from ISR was used for entry Interrupt: refer to Table 109: STM32L552xx and STM32L562xx vector table If WFE was used for entry and SEVONPEND = 0: Wakeup event: refer to Section 17.3: EXTI functional description If WFE was used for entry and SEVONPEND = 1: Interrupt even when disabled in NVIC: refer to Table 109: STM32L552xx and STM32L562xx vector table Wakeup event: refer to Section 17.3: EXTI functional description After exiting the Low-power sleep mode, the MCU is in Low-power run mode. |

| Wakeup latency | None |

8.4.7 Stop 0 mode

The Stop 0 mode is based on the Cortex®-M33 Deepsleep mode combined with the peripheral clock gating. The voltage regulator is configured in Main regulator mode. In Stop 0 mode, all clocks in the V CORE domain are stopped; the PLL, the MSI, the HSI16 and the HSE oscillators are disabled. Some peripherals with the wakeup capability (I2Cx (x=1,2,3), U(S)ARTx(x=1,2...5) and LPUART) can switch on the HSI16 to receive a frame, and switch off the HSI16 after receiving the frame if it is not a wakeup frame. In this case, the HSI16 clock is propagated only to the peripheral requesting it.

SRAM1, SRAM2 and register contents are preserved.

The BOR is always available in Stop 0 mode. The consumption is increased when thresholds higher than V BOR0 are used.

I/O states in Stop 0 mode

In the Stop 0 mode, all I/O pins keep the same state as in the Run mode.

Entering the Stop 0 mode

The Stop 0 mode is entered according to Section : Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex®-M33 System Control register is set.

Refer to Table 71: Stop 0 mode for details on how to enter the Stop 0 mode.

If flash memory programming is ongoing, the Stop 0 mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, The Stop 0 mode entry is delayed until the APB access is finished.

In Stop 0 mode, the following features can be selected by programming individual control bits:

- • Independent watchdog (IWDG): the IWDG is started by writing to its key register or by hardware option. Once started, it cannot be stopped except by a reset. See Section 39.3: IWDG functional description .

- • Real-time clock (RTC): this is configured by the RTCEN bit in the RCC Backup domain control register (RCC_BDCR) .

- • Internal RC oscillator (LSI): LSI clock or LSI clock divided by 128, this is configured by the LSION and LSIPRE bits in the RCC control/status register (RCC_CSR) .

- • External 32.768 kHz oscillator (LSE): this is configured by the LSEON bit in the RCC Backup domain control register (RCC_BDCR) .

Several peripherals can be used in Stop 0 mode and can add consumption if they are enabled and clocked by LSI or LSE, or when they request the HSI16 clock: LPTIM1, LPTIM2, I2Cx (x=1,2,3,4) U(S)ARTx(x=1,2...5), LPUART.

The DACx (x=1,2), the OPAMPs and the comparators can be used in Stop 0 mode, the PVMx (x=1,2,3,4) and the PVD as well. If they are not needed, they must be disabled by software to save their power consumptions.

The ADCx (x=1,2,3), temperature sensor and VREFBUF buffer can consume power during the Stop 0 mode, unless they are disabled before entering this mode.

Exiting the Stop 0 mode

The Stop 0 mode is exit according Section : Entering into a low-power mode .

Refer to Table 71: Stop 0 mode for details on how to exit Stop 0 mode.

When exiting Stop 0 mode by issuing an interrupt or a wakeup event, the HSI16 oscillator is selected as system clock if the bit STOPWUCK is set in RCC clock configuration register (RCC_CFGR) . The MSI oscillator is selected as system clock if the bit STOPWUCK is cleared. The wakeup time is shorter when HSI16 is selected as wakeup system clock. The MSI selection allows wakeup at higher frequency, up to 48 MHz.

When exiting the Stop 0 mode, the MCU is either in Run mode (Range 0, Range 1 or Range 2) or in Low-power run mode if the bit LPR is set in the PWR_CR1 register.

Table 71. Stop 0 mode

| Stop 0 mode | Description |

|---|---|

| Mode entry | WFI (Wait for Interrupt) or WFE (Wait for Event) while:

On Return from ISR while:

Note: To enter Stop 0 mode, all EXTI Line pending bits (in EXTI rising edge pending register (EXTI_RPR2)), and the peripheral flags generating wakeup interrupts must be cleared. Otherwise, the Stop 0 mode entry procedure is ignored and program execution continues. |

| Mode exit | If WFI or Return from ISR was used for entry Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 109: STM32L552xx and STM32L562xx vector table . If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in Event mode. Refer to Section 17.3: EXTI functional description . If WFE was used for entry and SEVONPEND = 1: Any EXTI Line configured in Interrupt mode (even if the corresponding EXTI Interrupt vector is disabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 109: STM32L552xx and STM32L562xx vector table . Wakeup event: refer to Section 17.3: EXTI functional description |

| Wakeup latency | Longest wakeup time between: MSI or HSI16 wakeup time and flash wakeup time from Stop 0 mode. |

8.4.8 Stop 1 mode

The Stop 1 mode is the same as Stop 0 mode except that the main regulator is OFF, and only the low-power regulator is ON. Stop 1 mode can be entered from Run mode and from Low-power run mode.

Refer to Table 72: Stop 1 mode for details on how to enter and exit Stop 1 mode.

Table 72. Stop 1 mode

| Stop 1 mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On Return from ISR while:

Note: To enter Stop 1 mode, all EXTI Line pending bits (in EXTI rising edge pending register (EXTI_RPR1)), and the peripheral flags generating wakeup interrupts must be cleared. Otherwise, the Stop 1 mode entry procedure is ignored and program execution continues. |

| Mode exit | If WFI or Return from ISR was used for entry Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 109: STM32L552xx and STM32L562xx vector table . If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in Event mode. Refer to Section 17.3: EXTI functional description . If WFE was used for entry and SEVONPEND = 1: Any EXTI Line configured in Interrupt mode (even if the corresponding EXTI Interrupt vector is disabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 109: STM32L552xx and STM32L562xx vector table . Wakeup event: refer to Section 17.3: EXTI functional description |

| Wakeup latency | Longest wakeup time between: MSI or HSI16 wakeup time and regulator wakeup time from low-power mode + flash wakeup time from Stop 1 mode. |

8.4.9 Stop 2 mode

The Stop 2 mode is based on the Cortex®-M33 DeepSleep mode combined with peripheral clock gating. In Stop 2 mode, all clocks in the V CORE domain are stopped, the PLL, the MSI, the HSI16 and the HSE oscillators are disabled. Some peripherals with wakeup capability (I2C3 and LPUART) can switch on the HSI16 to receive a frame, and switch off the HSI16 after receiving the frame if it is not a wakeup frame. In this case the HSI16 clock is propagated only to the peripheral requesting it.

SRAM1, SRAM2 and register contents are preserved.

The BOR is always available in Stop 2 mode. The consumption is increased when thresholds higher than V BOR0 are used.

Note: The comparators outputs, the LPUART outputs and the LPTIM1 outputs are forced to low speed (OSPEEDy=00) during the Stop 2 mode.

I/O states in Stop 2 mode

In the Stop 2 mode, all I/O pins keep the same state as in the Run mode.

Entering Stop 2 mode

The Stop 2 mode is entered according Section : Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex®-M33 System Control register is set.

Refer to Table 73: Stop 2 mode for details on how to enter the Stop 2 mode.

Stop 2 mode can only be entered from Run mode. It is not possible to enter Stop 2 mode from the Low-power run mode.

If flash memory programming is ongoing, the Stop 2 mode entry is delayed until the memory access is finished.

If an access to the APB domain is ongoing, The Stop 2 mode entry is delayed until the APB access is finished.

In Stop 2 mode, the following features can be selected by programming individual control bits:

- • Independent watchdog (IWDG): the IWDG is started by writing to its key register or by hardware option. Once started it cannot be stopped except by a Reset. See Section 39.3: IWDG functional description in Section 39: Independent watchdog (IWDG) .

- • Real-time clock (RTC): this is configured by the RTCEN bit in the RCC Backup domain control register (RCC_BDCR) .

- • Internal RC oscillator (LSI): LSI clock or LSI clock divided by 128, this is configured by the LSION and LSIPRE bits in the RCC control/status register (RCC_CSR) .

- • External 32.768 kHz oscillator (LSE): this is configured by the LSEON bit in the RCC Backup domain control register (RCC_BDCR) .

Several peripherals can be used in Stop 2 mode and can add consumption if they are enabled and clocked by LSI or LSE, or when they request the HSI16 clock: LPTIM1, I2C3, LPUART.

The comparators can be used in Stop 2 mode, the PVMx (x=1,2,3,4) and the PVD as well. If they are not needed, they must be disabled by software to save their power consumptions.

The ADCx, OPAMPx, DACx, temperature sensor and VREFBUF buffer can consume power during Stop 2 mode, unless they are disabled before entering this mode.

All the peripherals which cannot be enabled in Stop 2 mode must be either disabled by clearing the enable bit in the peripheral itself, or put under reset state by setting the corresponding bit in the RCC AHB1 peripheral reset register (RCC_AHB1RSTR) , RCC AHB2 peripheral reset register (RCC_AHB2RSTR) , RCC AHB3 peripheral reset register (RCC_AHB3RSTR) , RCC APB1 peripheral reset register 1 (RCC_APB1RSTR1) , RCC APB1 peripheral reset register 2 (RCC_APB1RSTR2) , RCC APB2 peripheral reset register (RCC_APB2RSTR) .

Exiting Stop 2 mode

The Stop 2 mode is exit according to Section : Exiting from a low-power mode .

Refer to Table 73: Stop 2 mode for details on how to exit Stop 2 mode.

When exiting Stop 2 mode by issuing an interrupt or a wakeup event, the HSI16 oscillator is selected as system clock if the bit STOPWUCK is set in RCC clock configuration register (RCC_CFGR) . The MSI oscillator is selected as system clock if the bit STOPWUCK is cleared. The wakeup time is shorter when HSI16 is selected as wakeup system clock. The MSI selection allows wakeup at higher frequency, up to 48 MHz.

When exiting the Stop 2 mode, the MCU is in Run mode (Range 0, Range 1 or Range 2 depending on VOS bit in PWR_CR1).

Table 73. Stop 2 mode

| Stop 2 mode | Description |

|---|---|

| Mode entry | WFI (wait for interrupt) or WFE (wait for event) while:

On return from ISR while:

Note: To enter Stop 2 mode, all EXTI Line pending bits (in EXTI rising edge pending register (EXTI_RPR2) ), and the peripheral flags generating wakeup interrupts must be cleared. Otherwise, the Stop mode entry procedure is ignored and program execution continues. |

| Mode exit | If WFI or Return from ISR was used for entry: Any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 109: STM32L552xx and STM32L562xx vector table . If WFE was used for entry and SEVONPEND = 0: Any EXTI Line configured in Event mode. Refer to Section 17.3: EXTI functional description . If WFE was used for entry and SEVONPEND = 1: Any EXTI Line configured in Interrupt mode (even if the corresponding EXTI Interrupt vector is disabled in the NVIC). The interrupt source can be external interrupts or peripherals with wakeup capability. Refer to Table 109: STM32L552xx and STM32L562xx vector table . Any EXTI Line configured in Event mode. Refer to Section 17.3: EXTI functional description . |

| Wakeup latency | Longest wakeup time between: MSI or HSI16 wakeup time and regulator wakeup time from low-power mode + flash wakeup time from Stop 2 mode. |

8.4.10 Standby mode

The Standby mode permits the achievement of the lowest power consumption with BOR. It is based on the Cortex ® -M33 DeepSleep mode, with the voltage regulators disabled (except when SRAM2 content is preserved). The PLL, the HSI16, the MSI and the HSE oscillators are also switched off.

SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry (see Figure 21 ). SRAM2 content can be partially or fully preserved depending on RRS[1:0] bits configuration in PWR_CR3. In this case the Low-power regulator is ON and provides the supply to SRAM2 only.

The BOR is always available in Standby mode. The consumption is increased when thresholds higher than \( V_{BOR0} \) are used.

I/O states in Standby mode

In the Standby mode, the I/O's are by default in floating state. If the APC bit of PWR_CR3 register has been set, the I/Os can be configured either with a pull-up (refer to PWR_PUCRx registers ( \( x=A,B,C,D,E,F,G,H \) )), or with a pull-down (refer to PWR_PDCRx registers ( \( x=A,B,C,D,E,F,G,H \) )), or can be kept in analog state if none of the PWR_PUCRx or PWR_PDCRx register has been set. The pull-down configuration has highest priority over pull-up configuration in case both PWR_PUCRx and PWR_PDCRx are set for the same I/O.

Some I/Os (listed in Section 11.3.1: General-purpose I/O (GPIO) ) are used for JTAG/SW debug and can only be configured to their respective reset pull-up or pull-down state during Standby mode setting their respective bit in the PWR_PUCRx or PWR_PDCRx registers to '1', or to be configured to floating state if the bit is kept at '0'.

The RTC outputs on PC13 are functional in Standby mode. PC14 and PC15 used for LSE are also functional. 5 wakeup pins (WKUPx, \( x=1,2...5 \) ) and tamper inputs are available.

Entering Standby mode

The Standby mode is entered according to Section : Entering into a low-power mode , when the SLEEPDEEP bit in the Cortex ® -M33 System Control register is set.