37. High-Resolution Timer (HRTIM)

37.1 Introduction

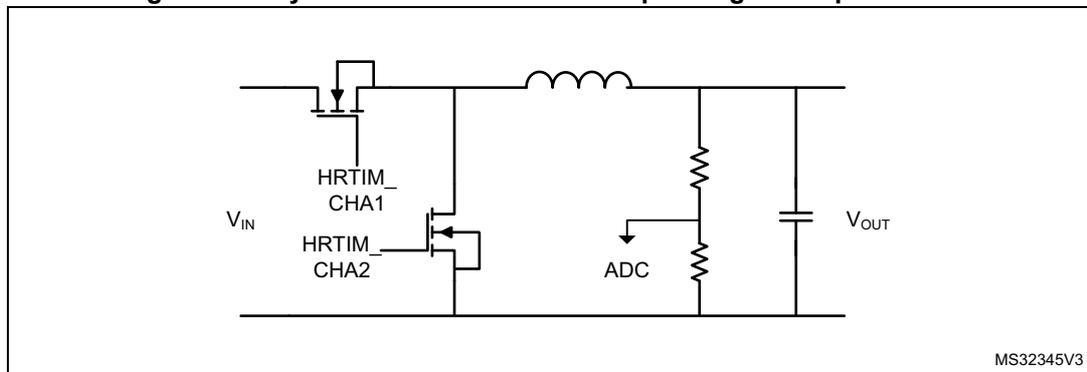

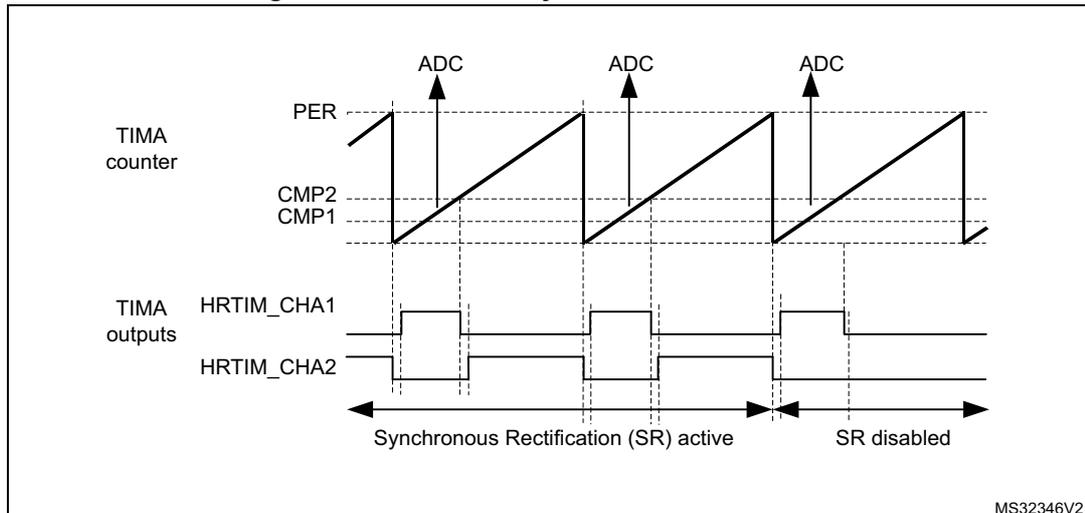

The high-resolution timer can generate up to 10 digital signals with highly accurate timings. It is primarily intended to drive power conversion systems such as switch mode power supplies or lighting systems, but can be of general purpose usage, whenever a very fine timing resolution is expected.

Its modular architecture allows to generate either independent or coupled waveforms. The wave-shape is defined by self-contained timings (using counters and compare units) and a broad range of external events, such as analog or digital feedbacks and synchronization signals. This allows to produce a large variety of control signal (PWM, phase-shifted, constant Ton,...) and address most of conversion topologies.

For control and monitoring purposes, the timer has also timing measure capabilities and links to built-in ADC and DAC converters. Last, it features light-load management mode and is able to handle various fault schemes for safe shut-down purposes.

37.2 Main features

- • Multiple timing units

- – Full-resolution available on all outputs, possibility to adjust duty-cycle, frequency and pulse width in triggered one-pulse mode

- – 6 16-bit timing units (each one with an independent counter and 4 compare units)

- – 10 outputs that can be controlled by any timing unit, up to 32 set/reset sources per channel

- – Modular architecture to address either multiple independent converters with 1 or 2 switches or few large multi-switch topologies

- • Up to 10 external events, available for any timing unit

- – Programmable polarity and edge sensitivity

- – 5 events with a fast asynchronous mode

- – 5 events with a programmable digital filter

- – Spurious events filtering with blanking and windowing modes

- • Multiple links to built-in analog peripherals

- – 4 triggers to ADC converters

- – 3 triggers to DAC converters

- – 3 comparators for analog signal conditioning

- • Versatile protection scheme

- – 5 fault inputs can be combined and associated to any timing unit

- – Programmable polarity, edge sensitivity, and programmable digital filter

- – dedicated delayed protections for resonant converters

- • Multiple HRTIM instances can be synchronized with external synchronization inputs/outputs

- • Versatile output stage

- – Full-resolution Deadtime insertion

- – Programmable output polarity

- – Chopper mode

- • Burst mode controller to handle light-load operation synchronously on multiple converters

- • 7 interrupt vectors, each one with up to 14 sources

- • 6 DMA requests with up to 14 sources, with a burst mode for multiple registers update

37.3 Functional description

37.3.1 General description

The HRTIM can be partitioned into several sub entities:

- • The master timer

- • The timing units (Timer A to Timer E)

- • The output stage

- • The burst mode controller

- • An external event and fault signal conditioning logic that is shared by all timers

- • The system interface

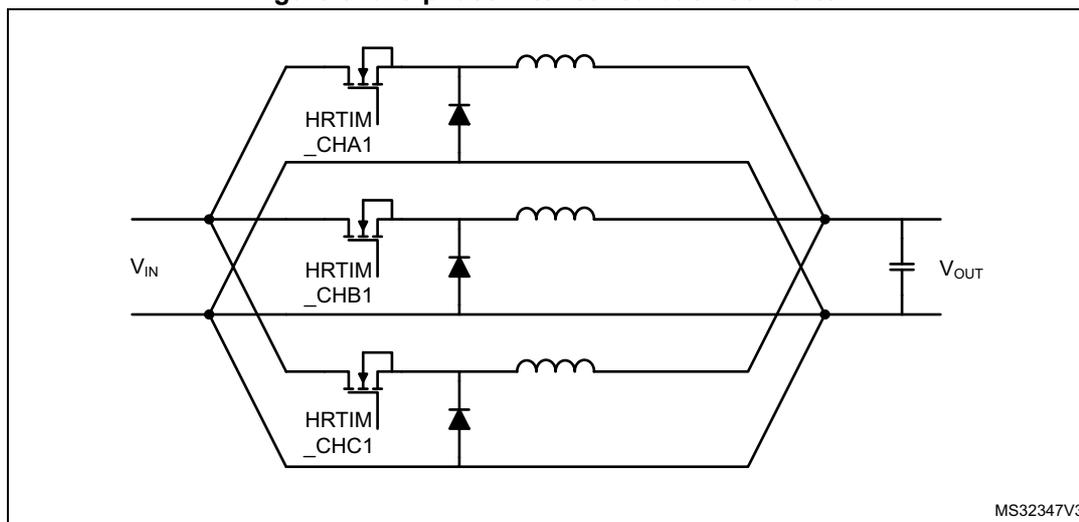

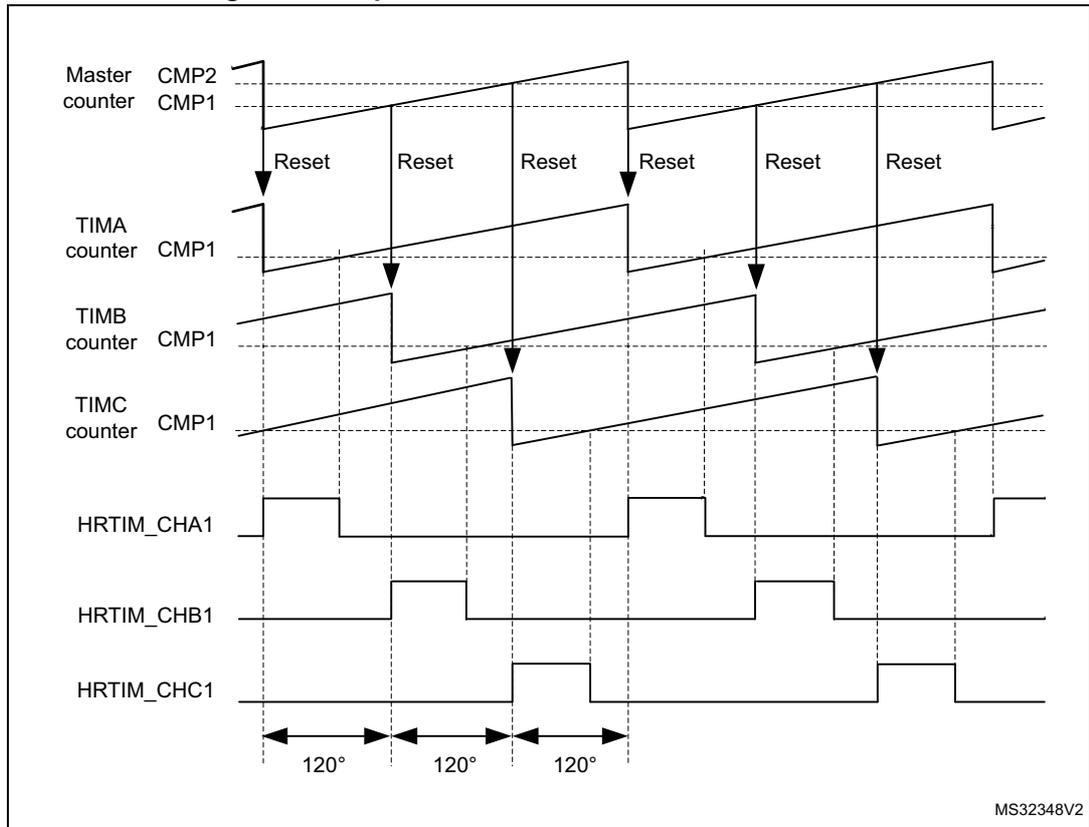

The master timer is based on a 16-bit up counter. It can set/reset any of the 10 outputs via 4 compare units and it provides synchronization signals to the 5 timer units. Its main purpose is to have the timer units controlled by a unique source. An interleaved buck converter is a typical application example where the master timer manages the phase-shifts between the multiple units.

The timer units are working either independently or coupled with the other timers including the master timer. Each timer contains the controls for two outputs. The outputs set/reset events are triggered either by the timing units compare registers or by events coming from the master timer, from the other timers or from external events.

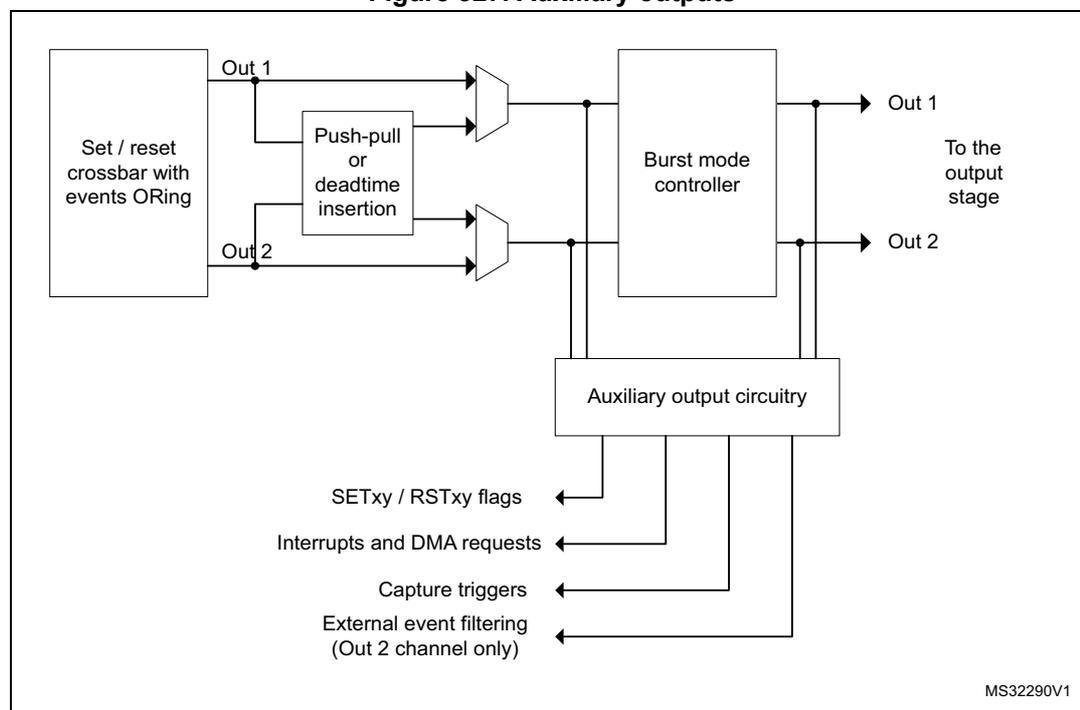

The output stage has several duties

- • Addition of deadtime when the 2 outputs are configured in complementary PWM mode

- • Addition of a carrier frequency on top of the modulating signal

- • Management of fault events, by asynchronously asserting the outputs to a predefined safe level

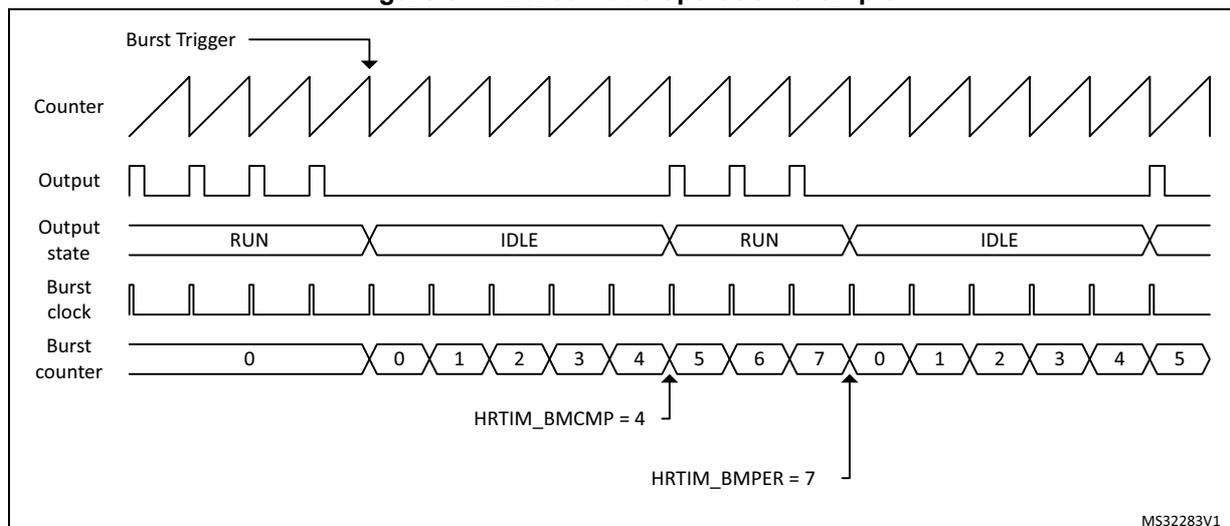

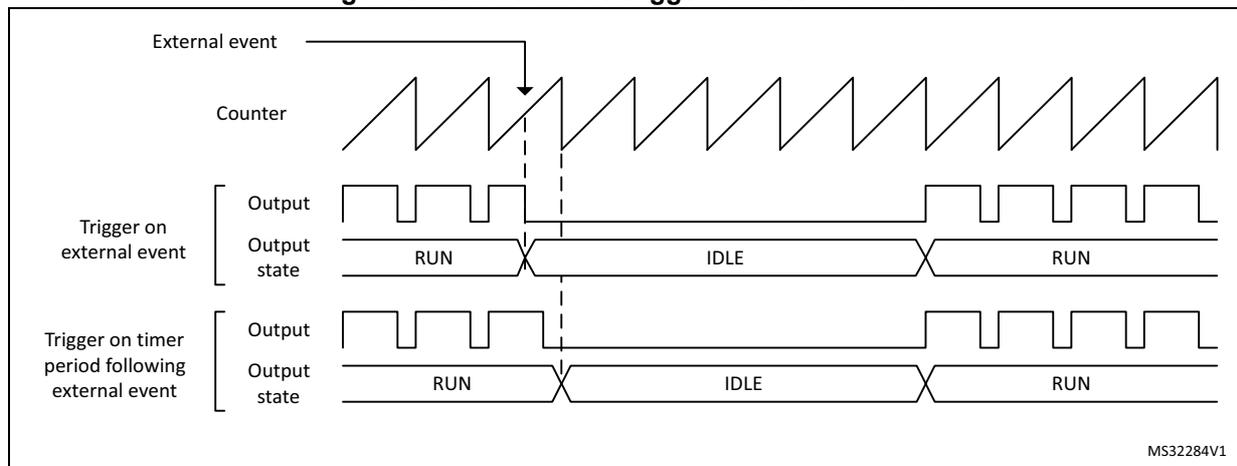

The burst mode controller can take over the control of one or multiple timers in case of light-load operation. The burst length and period can be programmed, as well as the idle state of the outputs.

The external event and fault signal conditioning logic includes:

- • The input selection MUXes (for instance for selecting a digital input or an on-chip source for a given external event channel)

- • Polarity and edge-sensitivity programming

- • Digital filtering (for 5 channels out of 10)

The system interface allows the HRTIM to interact with the rest of the MCU:

- • Interrupt requests to the CPU

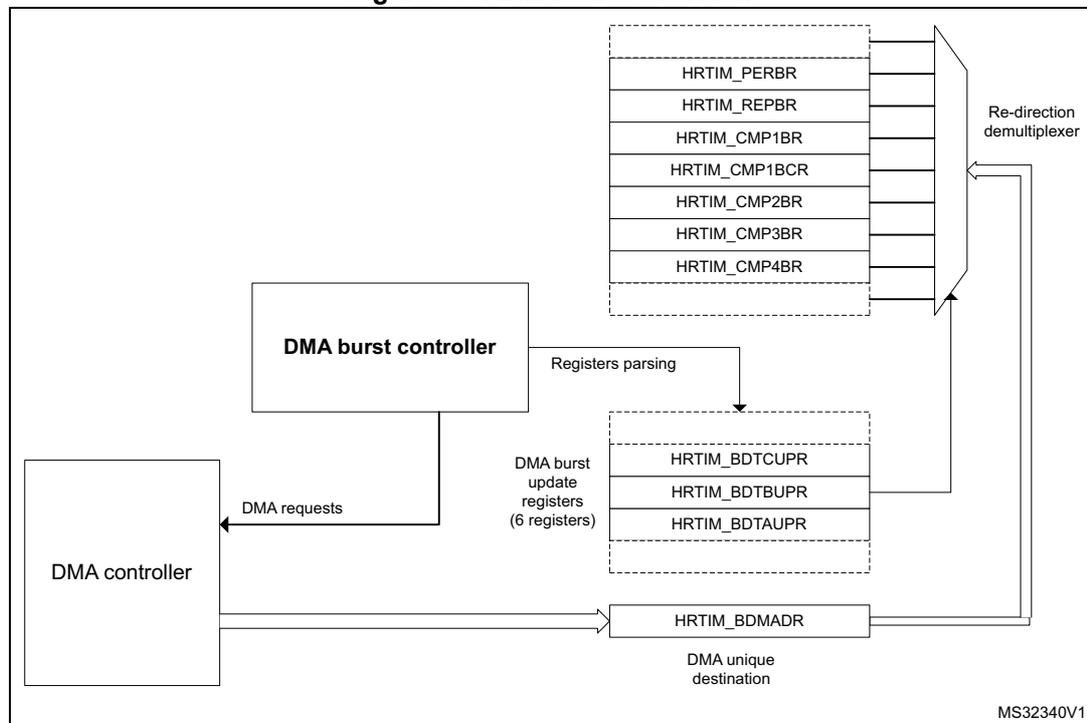

- • DMA controller for automatic accesses to/from the memories, including an HRTIM specific burst mode

- • Triggers for the ADC and DAC converters

The HRTIM registers are split into 7 groups:

- • Master timer registers

- • Timer A to Timer E registers

- • Common registers for features shared by all timer units

Note: As a writing convention, references to the 5 timing units in the text and in registers are generalized using the “x” letter, where x can be any value from A to E.

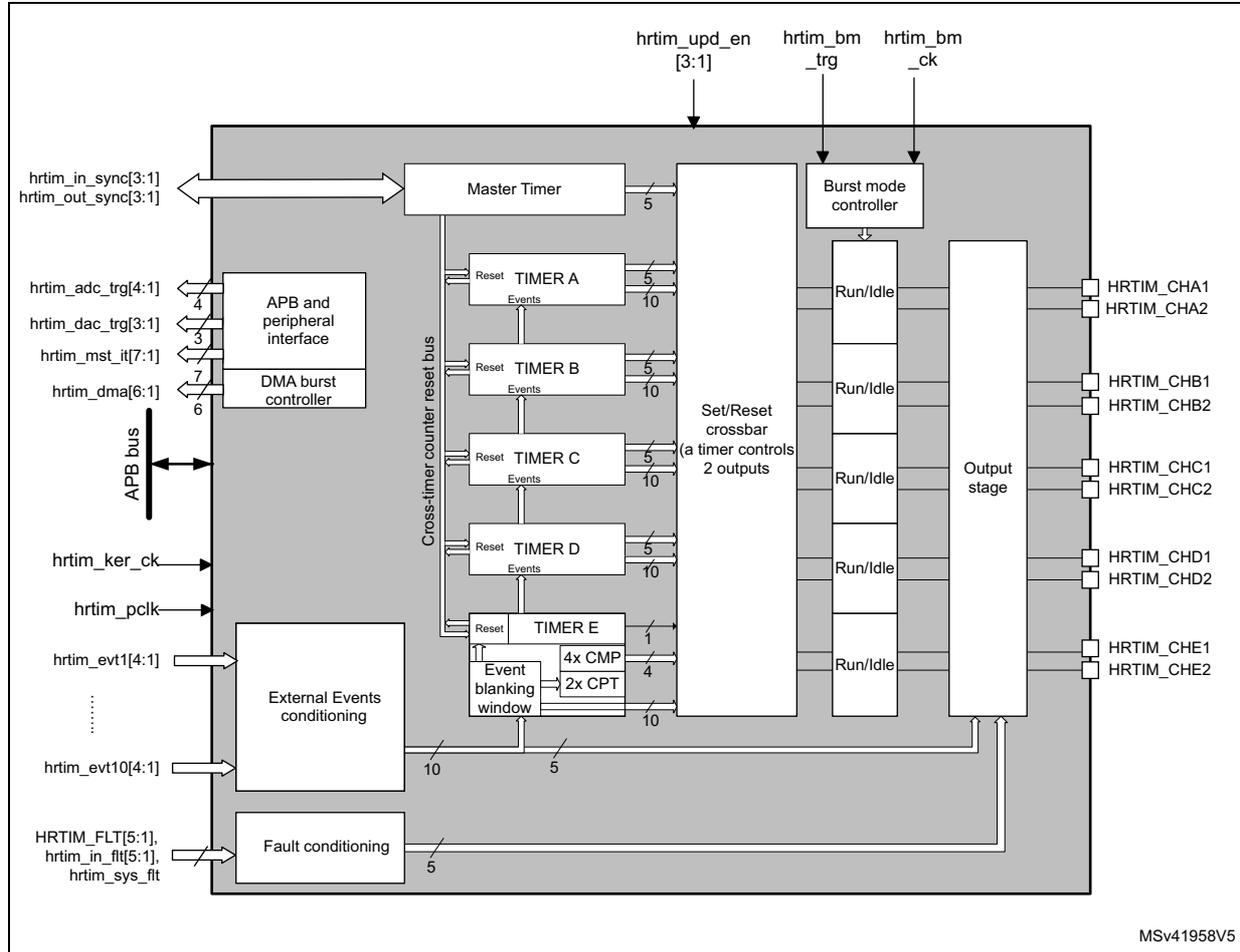

The block diagram of the timer is shown in Figure 281 .

Figure 281. High-resolution timer block diagram

The block diagram illustrates the internal architecture of the High-Resolution Timer (HRTIM). At the top, external signals

hrtim_upd_en[3:1]

,

hrtim_bm_trg

, and

hrtim_bm_ck

are inputs. The

hrtim_in_sync[3:1]

and

hrtim_out_sync[3:1]

signals connect to the Master Timer. The APB bus connects to the APB and peripheral interface and the DMA burst controller. External signals

hrtim_adc_trg[4:1]

,

hrtim_dac_trg[3:1]

,

hrtim_mst_it[7:1]

, and

hrtim_dma[6:1]

are also connected to the APB and peripheral interface. The Master Timer is connected to five timing units: TIMER A, TIMER B, TIMER C, TIMER D, and TIMER E. Each timer has a Reset input and an Events output. A cross-timer counter reset bus connects the Master Timer to all five timers. The Events outputs of the timers are connected to a Set/Reset crossbar, which has two outputs. The Set/Reset crossbar is connected to the Burst mode controller and the Output stage. The Burst mode controller is connected to the Run/Idle inputs of the Output stage. The Output stage has eight outputs:

HRTIM_CHA1

,

HRTIM_CHA2

,

HRTIM_CHB1

,

HRTIM_CHB2

,

HRTIM_CHC1

,

HRTIM_CHC2

,

HRTIM_CHD1

,

HRTIM_CHD2

,

HRTIM_CHE1

, and

HRTIM_CHE2

. The External Events conditioning block receives

hrtim_ker_ck

,

hrtim_pclk

,

hrtim_evt1[4:1]

, and

hrtim_evt10[4:1]

signals. The Fault conditioning block receives

HRTIM_FLT[5:1]

,

hrtim_in_flt[5:1]

, and

hrtim_sys_flt

signals. The External Events conditioning and Fault conditioning blocks are connected to the Output stage. The diagram is labeled MSv41958V5.

37.3.2 HRTIM pins and internal signals

The table here below summarizes the HRTIM inputs and outputs, both on-chip and off-chip.

Table 303. HRTIM Input/output summary

| Signal name | Signal type | Description |

|---|---|---|

| HRTIM_CHA1, HRTIM_CHA2, HRTIM_CHB1, HRTIM_CHB2, HRTIM_CHC1, HRTIM_CHC2, HRTIM_CHD1, HRTIM_CHD2, HRTIM_CHE1, HRTIM_CHE2 | Outputs | Main HRTIM timer outputs. They can be coupled by pairs (HRTIM_CHx1 & HRTIM_CHx2) with deadtime insertion or work independently. |

| HRTIM_FLT[5:1], hrtim_in_flt[5:1] | Digital input | Fault inputs: immediately disable the HRTIM outputs when asserted (5 on-chip inputs and 5 off-chip HRTIM_FLTx inputs). |

| hrtim_sys_flt | Digital input | System fault gathering MCU internal fault events (Clock security system, SRAM parity error, Cortex ® -M7 lockup (HardFault), PVD output). |

| hrtim_in_sync[3:1] | Digital Input | Synchronization inputs to synchronize the whole HRTIM with other internal or external timer resources: hrtim_in_sync1: reserved hrtim_in_sync2: the source is a regular TIMx timer (via on-chip interconnect) hrtim_in_sync3: the source is an external HRTIM (via the HRTIM_SCIN input pins) |

| hrtim_out_sync[2:1] | Digital output | The purpose of this output is to cascade or synchronize several HRTIM instances, either on-chip or off-chip: hrtim_out_sync1: reserved hrtim_out_sync2: the destination is an off-chip HRTIM or peripheral (via HRTIM_SCOUT output pins) |

| hrtim_evt1[4:1] | Digital input | External events. Each of the 10 events can be selected among 4 sources, either on-chip (from other built-in peripherals: comparator, ADC analog watchdog, TIMx timers, trigger outputs) or off-chip (HRTIM_EEVx input pins) |

| hrtim_evt2[4:1] | ||

| hrtim_evt3[4:1] | ||

| hrtim_evt4[4:1] | ||

| hrtim_evt5[4:1] | ||

| hrtim_evt6[4:1] | ||

| hrtim_evt7[4:1] | ||

| hrtim_evt8[4:1] | ||

| hrtim_evt9[4:1] | ||

| hrtim_evt10[4:1] | ||

| hrtim_upd_en[3:1] | Digital input | HRTIM register update enable inputs (on-chip interconnect) trigger the transfer from shadow to active registers |

Table 303. HRTIM Input/output summary (continued)

| Signal name | Signal type | Description |

|---|---|---|

| hrtim_bm_trg | Digital input | Burst mode trigger event (on-chip interconnect) |

| hrtim_bm_ck[4:1] | Digital input | Burst mode clock (on-chip interconnect) |

| hrtim_adc_trg[4:1] | Digital output | ADC start of conversion triggers |

| hrtim_dac_trg[3:1] | Digital output | DAC conversion update triggers |

| hrtim_mst_it[7:1] | Digital output | Interrupt requests |

| hrtim_dma[6:1] | Digital output | DMA requests |

| hrtim_pclk | Digital input | APB clock |

| hrtim_ker_ck | Digital input | HRTIM kernel clock (hereafter mentioned as \( f_{HRTIM} \) ). |

37.3.3 Clocks

The HRTIM must be supplied by the \( t_{HRTIM} \) system clock to offer a full resolution. All clocks present in the HRTIM are derived from this reference clock.

Definition of terms

\( f_{HRTIM} \) : main HRTIM clock (hrtim_ker_ck). All subsequent clocks are derived and synchronous with this source.

\( f_{DTG} \) : deadtime generator clock. For convenience, only the \( t_{DTG} \) period ( \( t_{DTG} = 1/f_{DTG} \) ) is used in this document.

\( f_{CHPFRQ} \) : chopper stage clock source.

\( f_{1STPW} \) : clock source defining the length of the initial pulse in chopper mode. For convenience, only the \( t_{1STPW} \) period ( \( t_{1STPW} = 1/f_{1STPW} \) ) is used in this document.

\( f_{BRST} \) : burst mode controller counter clock.

\( f_{SAMPLING} \) : clock needed to sample the fault or the external events inputs.

\( f_{FLTS} \) : clock derived from \( f_{HRTIM} \) which is used as a source for \( f_{SAMPLING} \) to filter fault events.

\( f_{EEVS} \) : clock derived from \( f_{HRTIM} \) which is used as a source for \( f_{SAMPLING} \) to filter external events.

\( f_{pclk} \) (hrtim_pclk): APB bus clock, needed for register read/write accesses

Timer clock and prescaler

Each timer in the HRTIM has its own individual clock prescaler, which allows you to adjust the timer resolution. (See Table 304 ).

Table 304. Timer resolution and min. PWM frequency for \( f_{HRTIM} = 400 \) MHz

| CKPSC[2:0] (1) | Prescaling ratio | \( f_{COUNTER} \) | Resolution | Min PWM frequency |

|---|---|---|---|---|

| 101 | 1 | 400 MHz | 2.5 ns | 6.1 kHz |

| 110 | 2 | 400/2 MHz = 200 MHz | 5 ns | 3.05 kHz |

| 111 | 4 | 400/4 MHz = 100 MHz | 10 ns | 1.5 kHz |

1. CKPSC[2:0] values from 000 to 100 are reserved.

The Full-resolution is available for edge positioning, PWM period adjustment and externally triggered pulse duration.

Initialization

At start-up, it is mandatory to initialize first the prescaler bitfields before writing the compare and period registers. Once the timer is enabled (MCEN or TxCEN bit set in the HRTIM_MCR register), the prescaler cannot be modified.

When multiple timers are enabled, the prescalers are synchronized with the prescaler of the timer that was started first.

Warning: It is possible to have different prescaling ratios in the master and TIMA..E timers only if the counter and output behavior does not depend on other timers' information and signals. It is mandatory to configure identical prescaling ratios in these timers when one of the following events is propagated from one timing unit (or master timer) to another: output set/reset event, counter reset event, update event, external event filter or capture triggers. Prescaler factors not equal will yield to unpredictable results.

Deadtime generator clock

The deadtime prescaler is supplied by \( f_{HRTIM} / 8 / 2^{(DTPRSC[2:0])} \) , programmed with DTPRSC[2:0] bits in the HRTIM_DTxR register.

\( t_{DTG} \) ranges from 2.5 ns to 20 ns for \( f_{HRTIM} = 400 \) MHz.

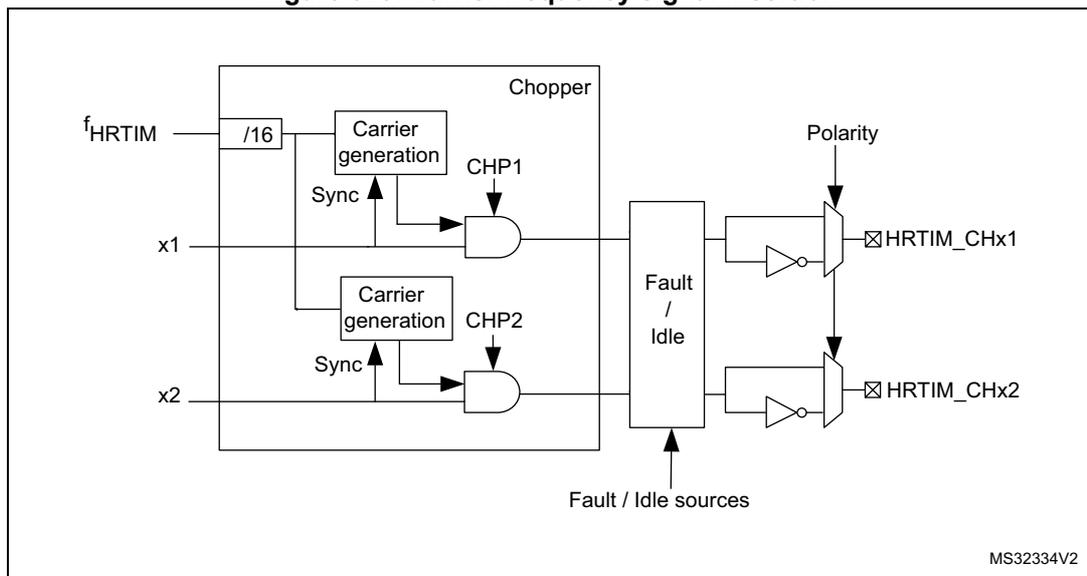

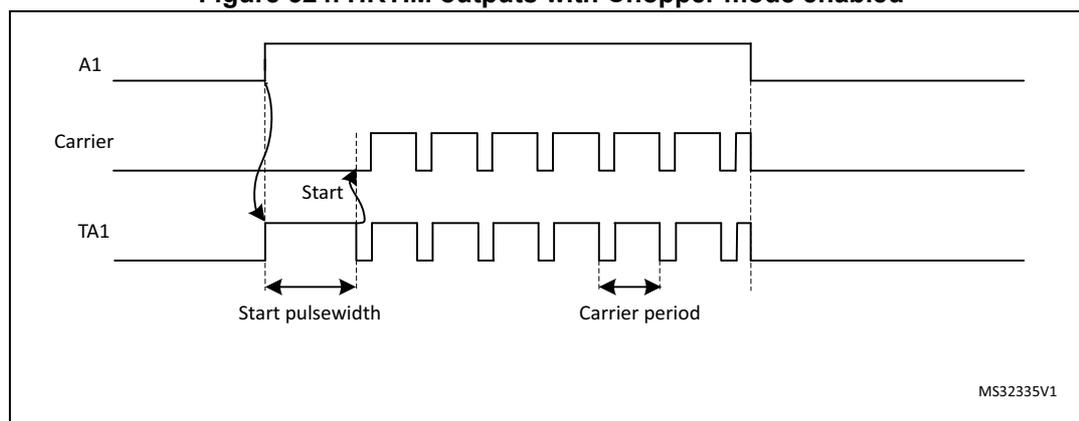

Chopper stage clock

The chopper stage clock source \( f_{\text{CHPFRQ}} \) is derived from \( f_{\text{HRTIM}} \) with a division factor ranging from 16 to 256, so that \( 1.56 \text{ MHz} \leq f_{\text{CHPFRQ}} \leq 25 \text{ MHz} \) for \( f_{\text{HRTIM}} = 400 \text{ MHz} \) .

\( t_{1\text{STPW}} \) is the length of the initial pulse in chopper mode, programmed with the STRPW[3:0] bits in the HRTIM_CHPxR register, as follows:

It uses \( f_{\text{HRTIM}} / 16 \) as clock source (25 MHz for \( f_{\text{HRTIM}} = 400 \text{ MHz} \) ).

Burst Mode Prescaler

The burst mode controller counter clock \( f_{\text{BRST}} \) can be supplied by several sources, among which one is derived from \( f_{\text{HRTIM}} \) .

In this case, \( f_{\text{BRST}} \) ranges from \( f_{\text{HRTIM}} \) to \( f_{\text{HRTIM}} / 32768 \) (12.2 kHz for \( f_{\text{HRTIM}} = 400 \text{ MHz} \) ).

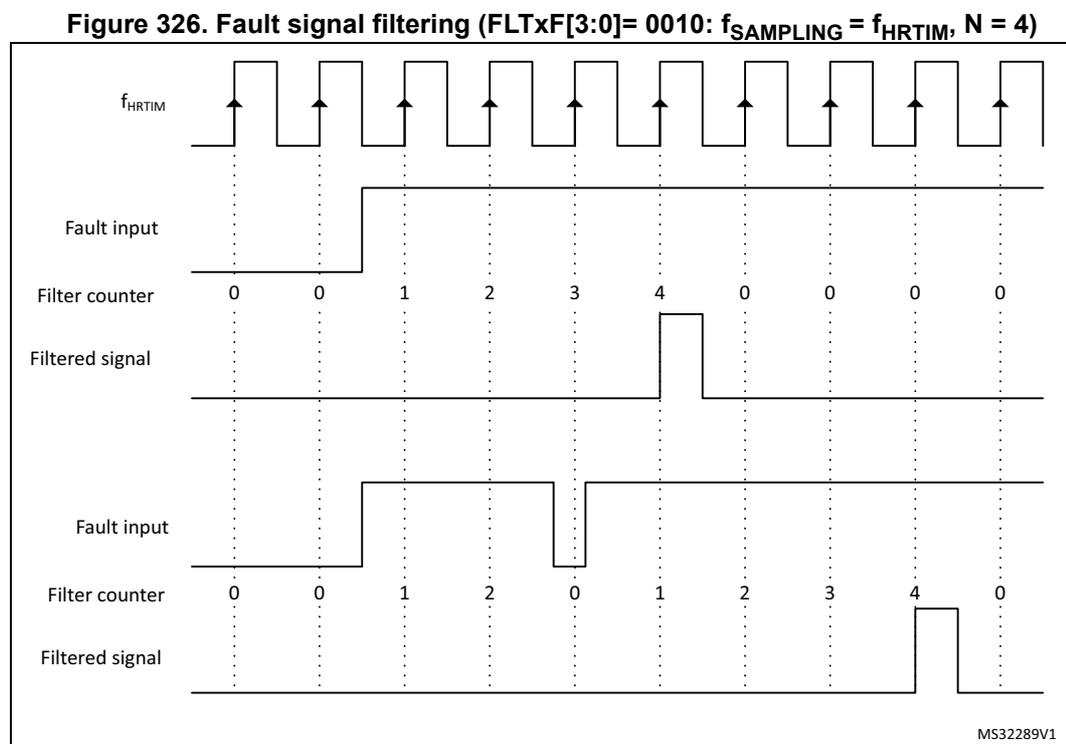

Fault input sampling clock

The fault input noise rejection filter has a time constant defined with \( f_{\text{SAMPLING}} \) which can be either \( f_{\text{HRTIM}} \) or \( f_{\text{FLTS}} \) .

\( f_{\text{FLTS}} \) is derived from \( f_{\text{HRTIM}} \) and ranges from 400 MHz to 50 MHz for \( f_{\text{HRTIM}} = 400 \text{ MHz} \) .

External Event input sampling clock

The fault input noise rejection filter has a time constant defined with \( f_{\text{SAMPLING}} \) which can be either \( f_{\text{HRTIM}} \) or \( f_{\text{EEVS}} \) .

\( f_{\text{EEVS}} \) is derived from \( f_{\text{HRTIM}} \) and ranges from 400 MHz to 50 MHz for \( f_{\text{HRTIM}} = 400 \text{ MHz} \) .

37.3.4 Timer A..E timing units

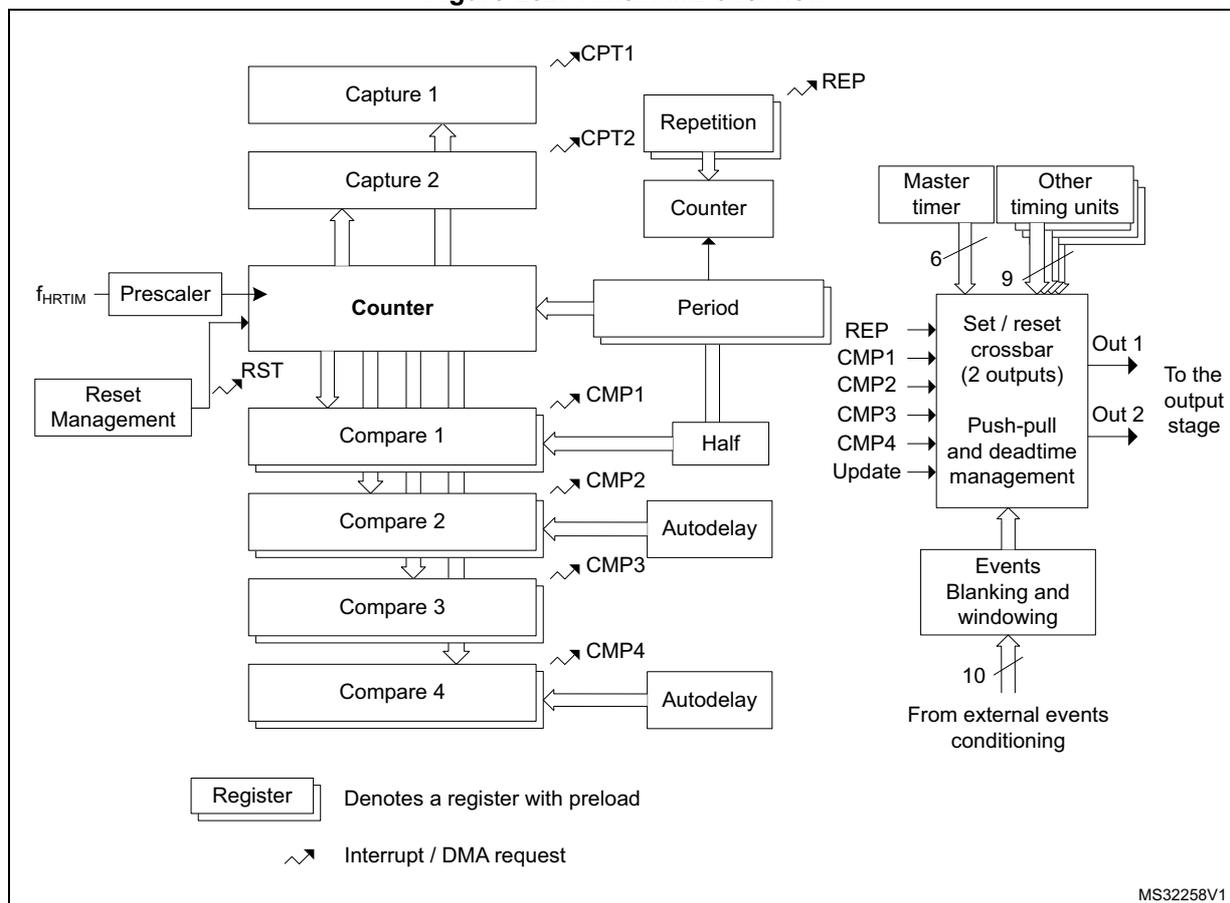

The HRTIM embeds 5 identical timing units made of a 16-bit up-counter with an auto-reload mechanism to define the counting period, 4 compare and 2 capture units, as per Figure 282. Each unit includes all control features for 2 outputs, so that it can operate as a standalone timer.

Figure 282. Timer A..E overview

The diagram illustrates the internal architecture of a Timer A..E timing unit. At the core is a Counter block. It receives input from a Prescaler (driven by \( f_{HRTIM} \) ) and a Reset Management block (RST). The Counter is connected to Capture 1 and Capture 2 blocks, which generate CPT1 and CPT2 interrupt/DMA requests. The Counter also feeds into a Period block, which generates a REP interrupt/DMA request. The Period block is connected to a Counter block, which in turn feeds into a Repetition block. The Counter also feeds into four Compare blocks: Compare 1 , Compare 2 , Compare 3 , and Compare 4 . These compare blocks generate CMP1 , CMP2 , CMP3 , and CMP4 interrupt/DMA requests. Compare 1 is connected to a Half block, Compare 2 to an Autodelay block, Compare 3 to another Autodelay block, and Compare 4 to a third Autodelay block. The Half , Autodelay , and Repetition blocks all feed into a Set / reset crossbar (2 outputs) block. This crossbar block also receives inputs from a Master timer (6 lines) and Other timing units (9 lines). It generates Out 1 and Out 2 signals to the output stage. The crossbar block is connected to a Push-pull and deadtime management block, which also receives inputs from CMP1 , CMP2 , CMP3 , CMP4 , and an Update signal. This management block is connected to an Events Blanking and windowing block, which receives inputs from From external events conditioning (10 lines). A legend indicates that a Register (represented by a double box) denotes a register with preload, and a jagged arrow represents an Interrupt / DMA request . The diagram is labeled MS32258V1.

The period and compare values must be within a lower and an upper limit related to the high-resolution implementation and listed in Table 305:

- • The minimum value must be greater than or equal to 3 periods of the \( f_{HRTIM} \) clock

- • The maximum value must be less than or equal to 0xFFFF - 1 periods of the \( f_{HRTIM} \) clock

Table 305. Period and Compare registers min and max values

| CKPSC[2:0] value (1) | Min | Max |

|---|---|---|

| ≥ 5 | 0x0003 | 0xFFFD |

1. CKPSC[2:0] values < 5 are reserved.

Note: A compare value greater than the period register value will not generate a compare match event.

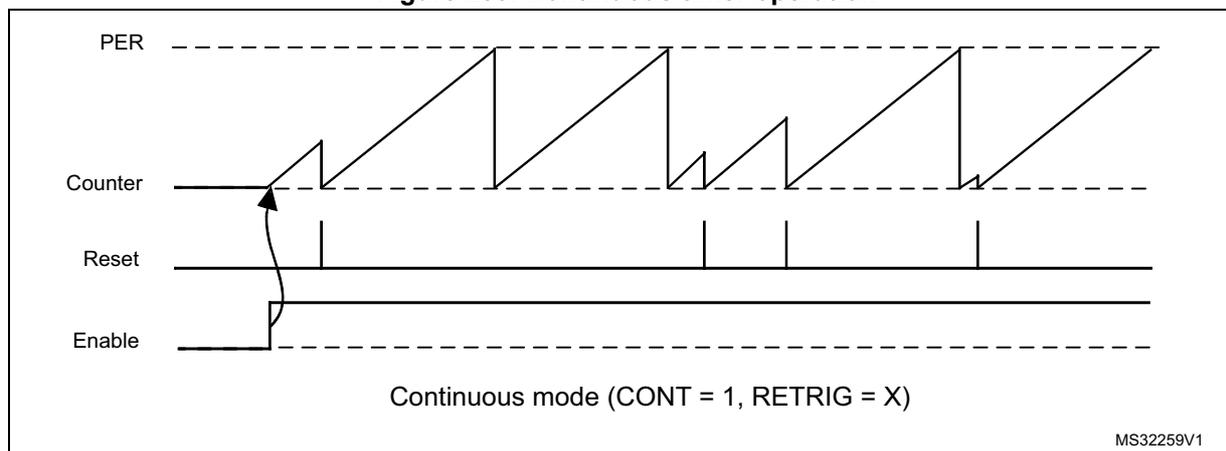

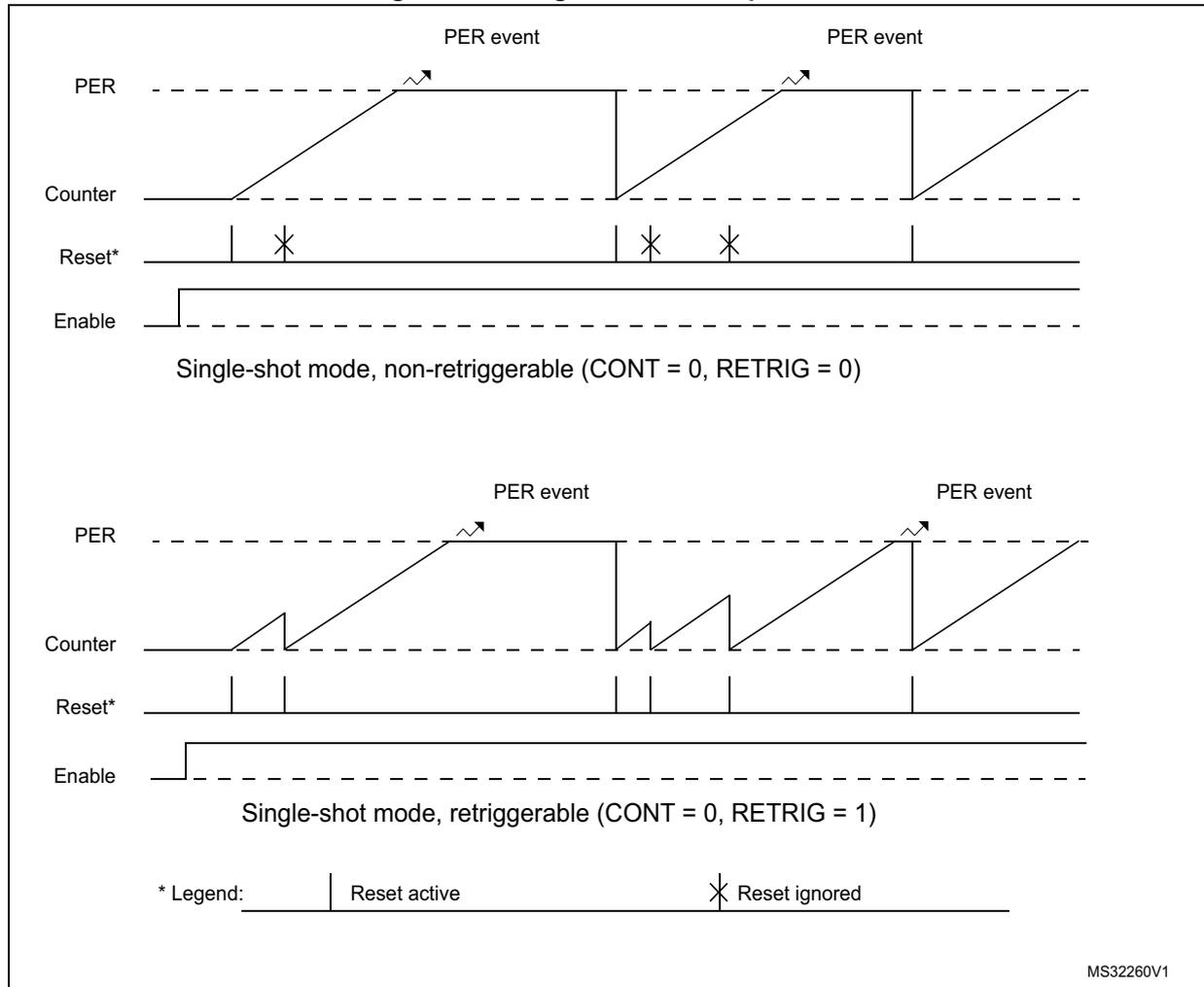

Counter operating mode

Timer A..E can operate in continuous (free-running) mode or in single-shot manner where counting is started by a reset event, using the CONT bit in the HRTIM_TIMxCR control register. An additional RETRIG bit allows you to select whether the single-shot operation is retriggerable or non-retriggerable. Details of operation are summarized on Table 306 and on Figure 283 and Figure 284 .

Table 306. Timer operating modes

| CONT | RETRIG | Operating mode | Start / Stop conditions |

|---|---|---|---|

| Clocking and event generation | |||

| 0 | 0 | Single-shot Non-retriggerable | Setting the TxEN bit enables the timer but does not start the counter. A first reset event starts the counting and any subsequent reset is ignored until the counter reaches the PER value. The PER event is then generated and the counter is stopped. A reset event re-starts the counting operation from 0x0000. |

| 0 | 1 | Single-shot Retriggerable | Setting the TxEN bit enables the timer but does not start the counter. A reset event starts the counting if the counter is stopped, otherwise it clears the counter. When the counter reaches the PER value, the PER event is generated and the counter is stopped. A reset event re-starts the counting operation from 0x0000. |

| 1 | X | Continuous mode | Setting the TxEN bit enables the timer and starts the counter simultaneously. When the counter reaches the PER value, it rolls-over to 0x0000 and resumes counting. The counter can be reset at any time. |

The TxEN bit can be cleared at any time to disable the timer and stop the counting.

Figure 283. Continuous timer operation

Continuous mode (CONT = 1, RETRIG = X)

MS32259V1

Figure 284. Single-shot timer operation

The figure consists of two timing diagrams illustrating single-shot timer operation. Both diagrams show four signals over time: PER (Period), Counter, Reset*, and Enable.

Top Diagram: Single-shot mode, non-retriggerable (CONT = 0, RETRIG = 0)

- PER: A dashed line representing the period. It shows two rising edges labeled "PER event".

- Counter: A solid line representing the counter value. It starts at 0 and increases linearly until it reaches the period value (PER), at which point it resets to 0. This reset occurs only if a "PER event" has occurred. If a reset signal is active during the count, the counter is ignored (marked with an 'X').

- Reset*: A solid line representing the active-low reset signal. It shows two active pulses. The first pulse occurs while the counter is still counting from the previous event, so it is ignored (marked with an 'X'). The second pulse occurs after the counter has reset, so it is active.

- Enable: A solid line that goes high to enable the timer and remains high throughout the sequence.

Bottom Diagram: Single-shot mode, retriggerable (CONT = 0, RETRIG = 1)

- PER: Similar to the top diagram, with two "PER event" rising edges.

- Counter: The counter starts at 0 and increases. If a new "PER event" occurs before the counter reaches the period value, the counter is reset to 0 and starts counting again. This retriggering is shown in the middle of the sequence.

- Reset*: Shows three active pulses. The first and third pulses occur after the counter has reached the period value and reset, so they are active. The second pulse occurs while the counter is still counting (retriggered by a PER event), so it is ignored (marked with an 'X').

- Enable: Similar to the top diagram, it remains high throughout the sequence.

* Legend:

- Reset active

- X Reset ignored

MS32260V1

Roll-over event

A counter roll-over event is generated when the counter goes back to 0 after having reached the period value set in the HRTIM_PERxR register in continuous mode.

This event is used for multiple purposes in the HRTIM:

- – To set/reset the outputs

- – To trigger the register content update (transfer from preload to active)

- – To trigger an IRQ or a DMA request

- – To serve as a burst mode clock source or a burst start trigger

- – as an ADC trigger

- – To decrement the repetition counter

If the initial counter value is above the period value when the timer is started, or if a new period is set while the counter is already above this value, the counter is not reset: it will overflow at the maximum period value and the repetition counter will not decrement.

Timer reset

The reset of the timing unit counter can be triggered by up to 30 events that can be selected simultaneously in the HRTIM_RSTxR register, among the following sources:

- • The timing unit: Compare 2, Compare 4 and Update (3 events)

- • The master timer: Reset and Compare 1..4 (5 events)

- • The external events EXTEVNT1..10 (10 events)

- • All other timing units (e.g. Timer B..E for timer A): Compare 1, 2 and 4 (12 events)

Several events can be selected simultaneously to handle multiple reset sources. In this case, the multiple reset requests are ORed. When 2 counter reset events are generated within the same \( f_{HRTIM} \) clock cycle, the last counter reset is taken into account.

Additionally, it is possible to do a software reset of the counter using the TxRST bits in the HRTIM_CR2 register. These control bits are grouped into a single register to allow the simultaneous reset of several counters.

The reset requests are taken into account only once the related counters are enabled (TxCEN bit set).

When the \( f_{HRTIM} \) clock prescaling ratio is above 1, the counter reset event is delayed to the next active edge of the prescaled clock. This allows to maintain a jitterless waveform generation when an output transition is synchronized to the reset event (typically a constant \( T_{on} \) time converter).

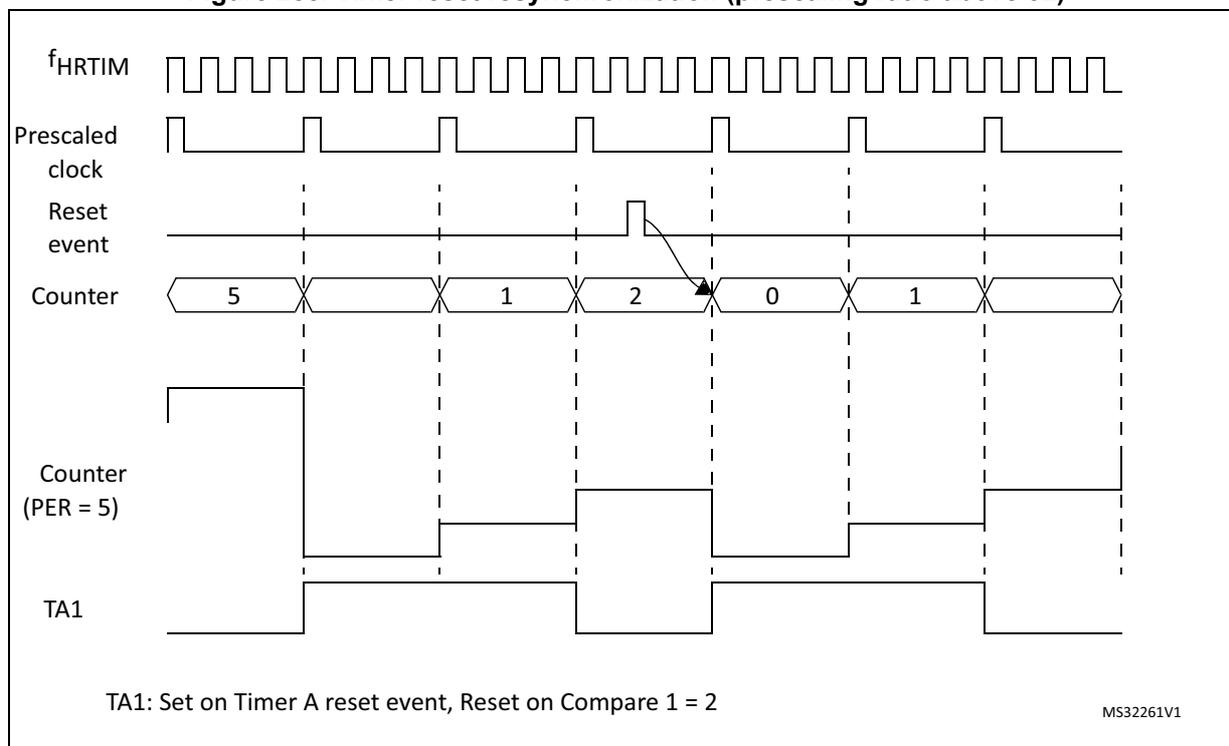

Figure 285 shows how the reset is handled for a clock prescaling ratio of 4 ( \( f_{HRTIM} \) divided by 4).

Figure 285. Timer reset resynchronization (prescaling ratio above 32)

TA1: Set on Timer A reset event, Reset on Compare 1 = 2

MS32261V1

Repetition counter

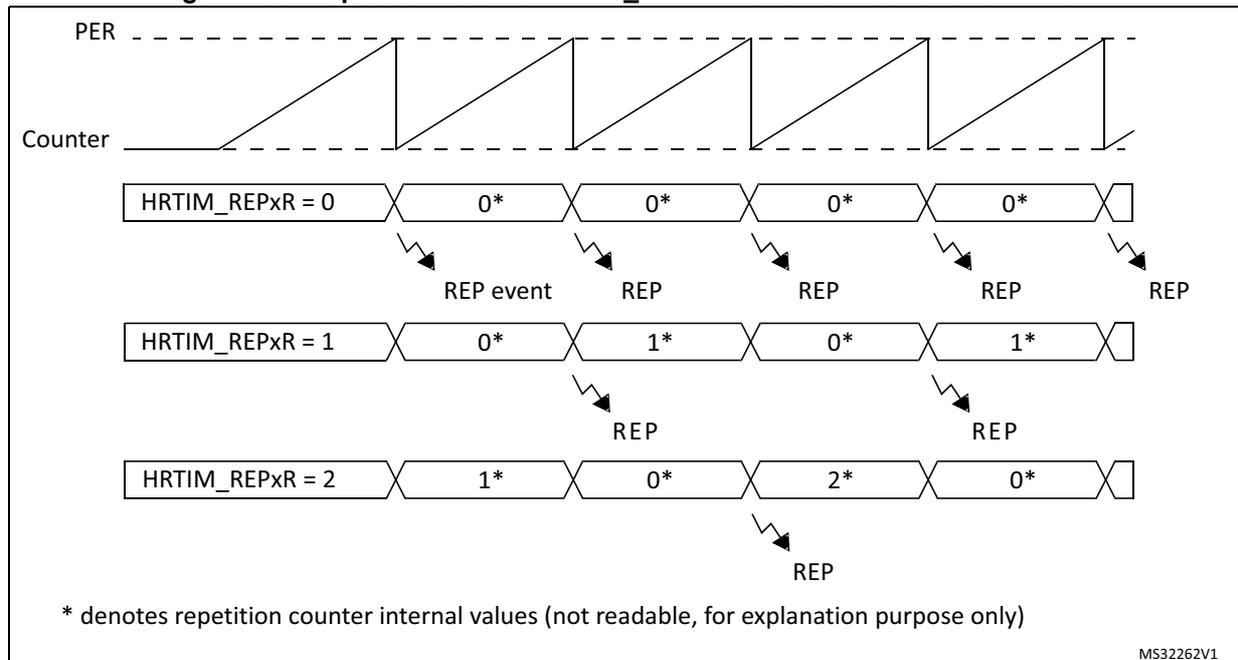

A common software practice is to have an interrupt generated when the period value is reached, so that the maximum amount of time is left for processing before the next period begins. The main purpose of the repetition counter is to adjust the period interrupt rate and off-load the CPU by decoupling the switching frequency and the interrupt frequency.

The timing units have a repetition counter. This counter cannot be read, but solely programmed with an auto-reload value in the HRTIM_REPxR register.

The repetition counter is initialized with the content of the HRTIM_REPxR register when the timer is enabled (TXCEN bit set). Once the timer has been enabled, any time the counter is cleared, either due to a reset event or due to a counter roll-over, the repetition counter is decreased. When it reaches zero, a REP interrupt or a DMA request is issued if enabled (REPIE and REPDE bits in the HRTIM_DIER register).

If the HRTIM_REPxR register is set to 0, an interrupt is generated for each and every period. For any value above 0, a REP interrupt is generated after (HRTIM_REPxR + 1) periods. Figure 286 presents the repetition counter operation for various values, in continuous mode.

Figure 286. Repetition rate vs HRTIM_REPxR content in continuous mode

The diagram illustrates the operation of the repetition counter in continuous mode. The top section shows the Period (PER) signal as a dashed line and the Counter as a sawtooth ramp. Below this, three rows show the internal values of the repetition counter for different HRTIM_REPxR settings:

- HRTIM_REPxR = 0: The internal counter value stays at 0*. A REP event (indicated by a lightning bolt and 'REP') is generated at every counter roll-over.

- HRTIM_REPxR = 1: The internal counter value alternates between 0* and 1*. A REP event is generated every two periods, specifically when the internal counter reaches 0 and rolls over.

- HRTIM_REPxR = 2: The internal counter value cycles through 1*, 0*, and 2*. A REP event is generated every three periods.

* denotes repetition counter internal values (not readable, for explanation purpose only)

MS32262V1

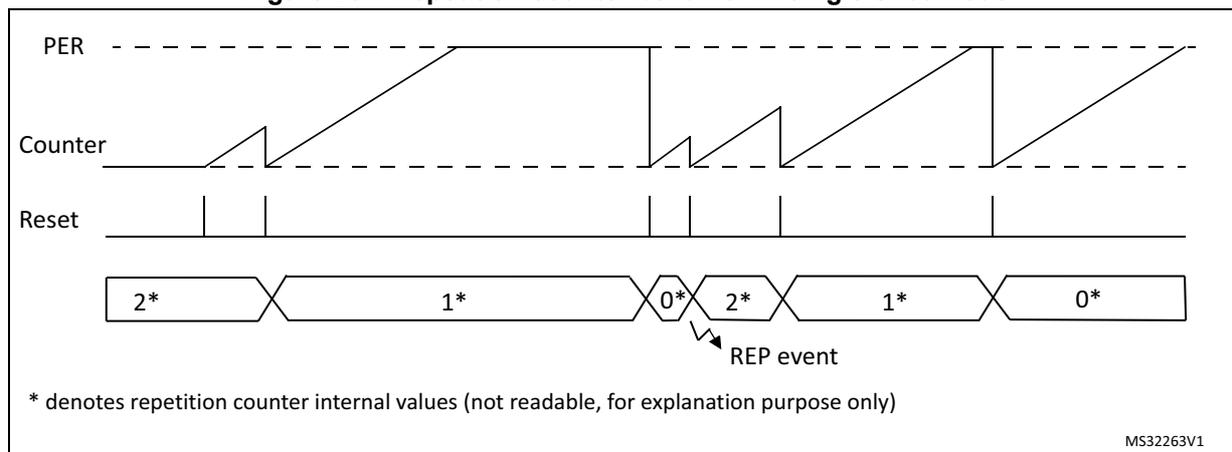

The repetition counter can also be used when the counter is reset before reaching the period value (variable frequency operation) either in continuous or in single-shot mode (Figure 287 here-below). The reset causes the repetition counter to be decremented, at the exception of the very first start following counter enable (TxCEN bit set).

Figure 287. Repetition counter behavior in single-shot mode

A reset or start event from the hrtim_in_sync[3:1] source causes the repetition to be decremented as any other reset. However, in SYNCIN-started single-shot mode (SYNCSTRTx bit set in the HRTIM_TIMxCR register), the repetition counter will be decremented only on the 1st reset event following the period. Any subsequent reset will not alter the repetition counter until the counter is re-started by a new request on hrtim_in_sync[3:1] inputs.

Set / reset crossbar

A “set” event correspond to a transition to the output active state, while a “reset” event corresponds to a transition to the output inactive state.

The polarity of the waveform is defined in the output stage to accommodate positive or negative logic external components: an active level corresponds to a logic level 1 for a positive polarity (POLx = 0), and to a logic level 0 for a negative polarity (POLx = 1).

Each of the timing units handles the set/reset crossbar for two outputs. These 2 outputs can be set, reset or toggled by up to 32 events that can be selected among the following sources:

- – The timing unit: Period, Compare 1..4, register update (6 events)

- – The master timer: Period, Compare 1..4, HRTIM synchronization (6 events)

- – All other timing units (e.g. Timer B..E for timer A): TIMEVNT1..9 (9 events described in Table 307 )

- – The external events EXTEVNT1..10 (10 events)

- – A software forcing (1 event)

The event sources are ORed and multiple events can be simultaneously selected.

Each output is controlled by two 32-bit registers, one coding for the set (HRTIM_SETxyR) and another one for the reset (HRTIM_RSTxyR), where x stands for the timing unit: A..E and y stands for the output 1or 2 (e.g. HRTIM_SETA1R, HRTIM_RSTC2R,...).

If the same event is selected for both set and reset, it will toggle the output. It is not possible to toggle the output state more than one time per \( t_{\text{HRTIM}} \) period: in case of two consecutive toggling events within the same cycle, only the first one is considered.

The set and reset requests are taken into account only once the counter is enabled (TxCEN bit set), except if the software is forcing a request to allow the prepositioning of the outputs at timer start-up.

Table 307 summarizes the events from other timing units that can be used to set and reset the outputs. The number corresponds to the timer events (such as TIMEVNTx) listed in the register, and empty locations are indicating non-available events.

For instance, Timer A outputs can be set or reset by the following events: Timer B Compare1, 2 and 4, Timer C Compare 2 and 3,... and Timer E Compare 3 will be listed as TIMEVNT8 in HRTIM_SETA1R.

Table 307. Events mapping across Timer A to E

| Source | Timer A | Timer B | Timer C | Timer D | Timer E | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CMP1 | CMP2 | CMP3 | CMP4 | CMP1 | CMP2 | CMP3 | CMP4 | CMP1 | CMP2 | CMP3 | CMP4 | CMP1 | CMP2 | CMP3 | CMP4 | CMP1 | CMP2 | CMP3 | CMP4 | ||

| Destination | Timer A | - | - | - | - | 1 | 2 | - | 3 | - | 4 | 5 | - | 6 | 7 | - | - | - | - | 8 | 9 |

| Timer B | 1 | 2 | - | 3 | - | - | - | - | - | - | 4 | 5 | - | - | 6 | 7 | 8 | 9 | - | - | |

| Timer C | - | 1 | 2 | - | - | 3 | 4 | - | - | - | - | - | - | 5 | - | 6 | - | 7 | 8 | 9 | |

| Timer D | 1 | - | - | 2 | - | 3 | - | 4 | 5 | - | 6 | 7 | - | - | - | - | 8 | - | - | 9 | |

| Timer E | - | - | 1 | 2 | - | - | 3 | 4 | 5 | 6 | - | - | 7 | 8 | - | 9 | - | - | - | - | |

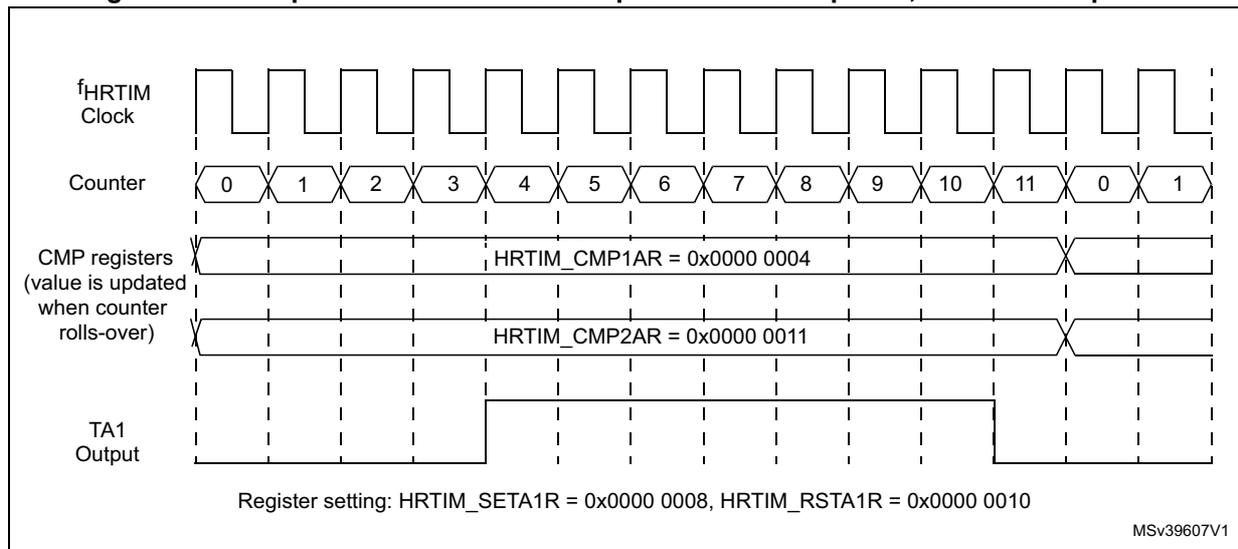

Figure 288 represents how a PWM signal is generated using two compare events.

Figure 288. Compare events action on outputs: set on compare 1, reset on compare 2

The figure is a timing diagram illustrating the generation of a PWM signal on the TA1 output using two compare events. The top row shows the fHRTIM Clock as a periodic square wave. The second row shows the Counter values from 0 to 11, which roll over from 11 back to 0. The third row shows the CMP registers, with HRTIM_CMP1AR set to 0x0000 0004 and HRTIM_CMP2AR set to 0x0000 0011. The bottom row shows the TA1 Output, which is set high at the compare event for CMP1 (counter value 4) and reset low at the compare event for CMP2 (counter value 11). The register settings for this configuration are HRTIM_SETA1R = 0x0000 0008 and HRTIM_RSTA1R = 0x0000 0010.

Set/Reset on Update events

Half mode

This mode aims at generating square signal with fixed 50% duty cycle and variable frequency (typically for converters using resonant topologies). It allows to have the duty cycle automatically forced to half of the period value when a new period is programmed.

This mode is enabled by writing HALF bit to 1 in the HRTIM_TIMxCR register. When the HRTIM_PERxR register is written, it causes an automatic update of the Compare 1 value with HRTIM_PERxR/2 value.

The output on which a square wave is generated must be programmed to have one transition on CMP1 event, and one transition on the period event, as follows:

- – HRTIM_SETxyR = 0x0000 0008, HRTIM_RSTxyR = 0x0000 0004, or

- – HRTIM_SETxyR = 0x0000 0004, HRTIM_RSTxyR = 0x0000 0008

The HALF mode overrides the content of the HRTIM_CMP1xR register. The access to the HRTIM_PERxR register only causes Compare 1 internal register to be updated. The user-accessible HRTIM_CMP1xR register is not updated with the HRTIM_PERxR / 2 value.

When the preload is enabled (PREEN = 1, MUDIS, TxUDIS), Compare 1 active register is refreshed on the Update event. If the preload is disabled (PREEN= 0), Compare 1 active register is updated as soon as HRTIM_PERxR is written.

The period must be greater than or equal to 6 periods of the \( f_{HRTIM} \) clock when the HALF mode is enabled.

Capture

The timing unit has the capability to capture the counter value, triggered by internal and external events. The purpose is to:

- • measure events arrival timings or occurrence intervals

- • update Compare 2 and Compare 4 values in auto-delayed mode (see Auto-delayed mode ).

The capture is done with \( f_{HRTIM} \) resolution.

The timer has 2 capture registers: HRTIM_CPT1xR and HRTIM_CPT2xR. The capture triggers are programmed in the HRTIM_CPT1xCR and HRTIM_CPT2xCR registers.

The capture of the timing unit counter can be triggered by up to 28 events that can be selected simultaneously in the HRTIM_CPT1xCR and HRTIM_CPT2xCR registers, among the following sources:

- • The external events, EXTEVNT1..10 (10 events)

- • All other timing units (e.g. Timer B..E for timer A): Compare 1, 2 and output 1 set/reset events (16 events)

- • The timing unit: Update (1 event)

- • A software capture (1 event)

Several events can be selected simultaneously to handle multiple capture triggers. In this case, the concurrent trigger requests are ORed. The capture can generate an interrupt or a DMA request when CPTxE and CPTxDE bits are set in the HRTIM_TIMxDIER register.

Over-capture is not prevented by the circuitry: a new capture is triggered even if the previous value was not read, or if the capture flag was not cleared.

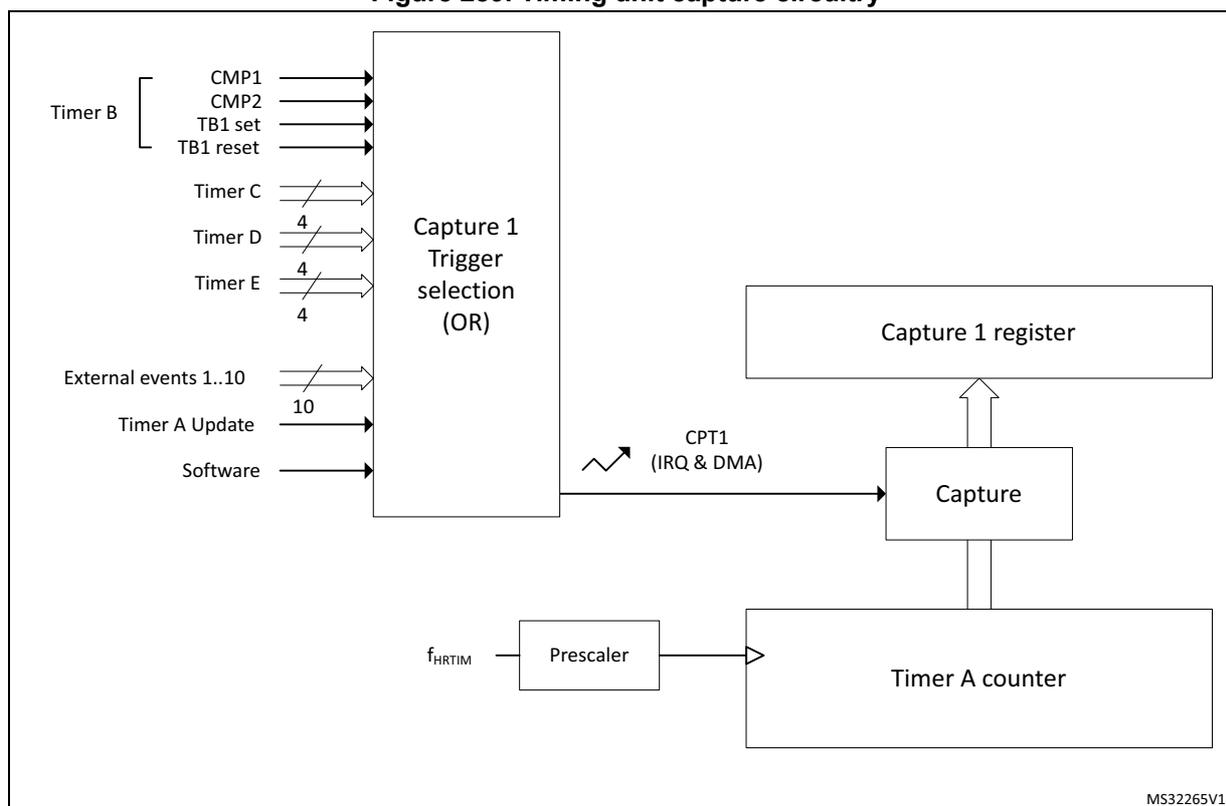

Figure 289. Timing unit capture circuitry

The diagram illustrates the timing unit capture circuitry. On the left, multiple input signals are shown entering a block labeled Capture 1 Trigger selection (OR) :

- Timer B : CMP1, CMP2, TB1 set, TB1 reset.

- Timer C : 4-bit bus input.

- Timer D : 4-bit bus input.

- Timer E : 4-bit bus input.

- External events 1..10 : 10-bit bus input.

- Timer A Update : Single line input.

- Software : Single line input.

Auto-delayed mode

This mode allows to have compare events generated relatively to capture events, so that for instance an output change can happen with a programmed timing following a capture. In this case, the compare match occurs independently from the timer counter value. It enables the generation of waveforms with timings synchronized to external events without the need of software computation and interrupt servicing.

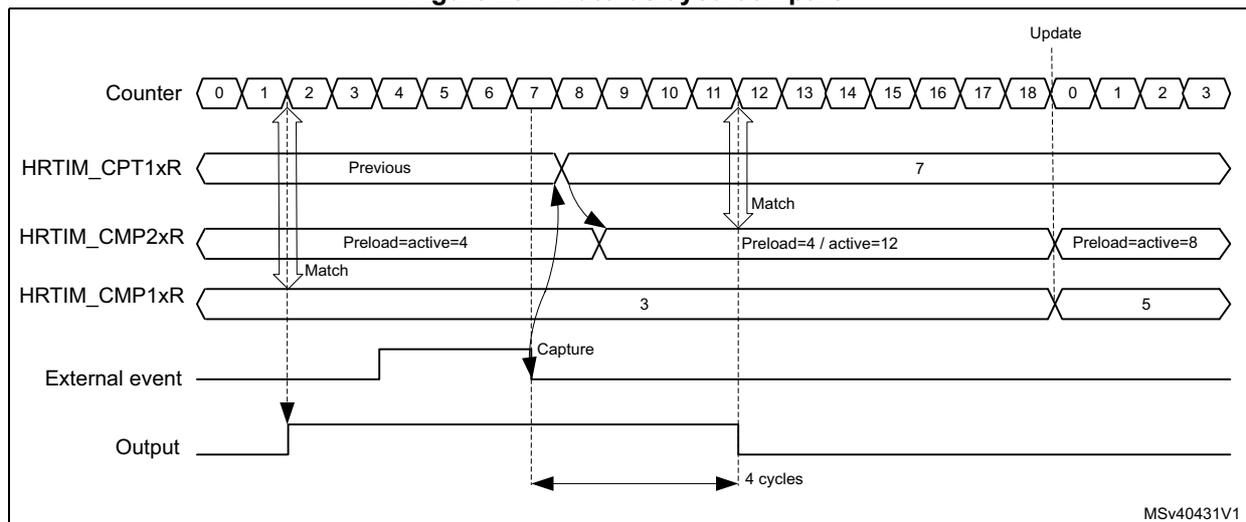

As long as no capture is triggered, the content of the HRTIM_CMPxR register is ignored (no compare event is generated when the counter value matches the Compare value). Once the capture is triggered, the compare value programmed in HRTIM_CMPxR is summed with the captured counter value in HRTIM_CPTxyR, and it updates the internal auto-delayed compare register, as seen on Figure 290. The auto-delayed compare register is internal to the timing unit and cannot be read. The HRTIM_CMPxR preload register is not modified after the calculation.

This feature is available only for Compare 2 and Compare 4 registers. Compare 2 is associated with capture 1, while Compare 4 is associated with capture 2. HRTIM_CMP2xR and HRTIM_CMP4xR Compares cannot be programmed with a value below 3 \( f_{HRTIM} \) clock periods, as in the regular mode.

Figure 290. Auto-delayed overview (Compare 2 only)

![Block diagram of the auto-delayed overview for Compare 2 in the HRTIM. The diagram shows a Counter connected to Capture 1, Compare 2, Compare 1, and Compare 3. Capture 1 is connected to an Adder. The Adder also receives inputs from Compare 2 and a 'Timeout feature if DELCMP2[1..0] = 1x'. The output of the Adder is connected to the 'Autodelayed Compare 2' block. The 'Autodelayed Compare 2' block is connected to a multiplexer (MUX) labeled 'DELCMP2[1..0]'. The MUX has inputs '00' and '100' from the Counter, and its output is connected to Compare 2. The MUX also has inputs '10' and '11' from Compare 1 and Compare 3 respectively. The 'Timeout feature if DELCMP2[1..0] = 1x' is connected to the MUX. The diagram is labeled 'MS32266V1' in the bottom right corner.](/RM0433-STM32H742-743-753-750/04fe9e8986c695db226c482352aacdb1_img.jpg)

The diagram illustrates the internal architecture of the HRTIM for the auto-delayed mode. At the top, a 'Capture 1' block receives a signal from the 'Counter'. The 'Counter' also feeds into a multiplexer (MUX) labeled 'DELCMP2[1..0]'. The MUX selects between '00' and '100' based on the counter value. The output of the MUX is connected to the 'Autodelayed Compare 2' block. The 'Autodelayed Compare 2' block also receives inputs from the 'Add' block and the 'Timeout feature if DELCMP2[1..0] = 1x'. The 'Add' block receives inputs from 'Capture 1', 'Compare 2', and the 'Timeout feature'. The output of the 'Add' block is connected to the 'Autodelayed Compare 2' block. The 'Autodelayed Compare 2' block is connected to a second MUX labeled 'DELCMP2[1..0]'. This MUX selects between '10' and '11' based on the output of the 'Autodelayed Compare 2' block. The output of this MUX is connected to 'Compare 2'. 'Compare 1' and 'Compare 3' are also connected to this MUX. The 'Timeout feature if DELCMP2[1..0] = 1x' is connected to the 'Add' block and the second MUX. The diagram is labeled 'MS32266V1' in the bottom right corner.

The auto-delayed Compare is only valid from the capture up to the period event: once the counter has reached the period value, the system is re-armed with Compare disabled until a capture occurs.

DELCMP2[1:0] and DELCMP4[1:0] bits in HRTIM_TIMxCR register allow to configure the auto-delayed mode as follows:

- • 00

Regular compare mode: HRTIM_CMP2xR and HRTIM_CMP4xR register contents are directly compared with the counter value. - • 01

Auto-delayed mode: Compare 2 and Compare 4 values are recomputed and used for comparison with the counter after a capture 1/2 event.

- • 1X

Auto-delayed mode with timeout: Compare 2 and Compare 4 values are recomputed and used for comparison with the counter after a capture 1/2 event or after a Compare 1 match ( \( DELCMPx[1:0]= 10 \) ) or a Compare 3 match ( \( DELCMPx[1:0]= 11 \) ) to have a timeout function if capture 1/2 event is missing.

When the capture occurs, the comparison is done with the \( (HRTIM\_CMP2/4xR + HRTIM\_CPT1/2xR) \) value. If no capture is triggered within the period, the behavior depends on the \( DELCMPx[1:0] \) value:

- • \( DELCMPx[1:0] = 01 \) : the compare event is not generated

- • \( DELCMPx[1:0] = 10 \) or \( 11 \) : the comparison is done with the sum of the 2 compares (for instance \( HRTIM\_CMP2xR + HRTIM\_CMP1xR \) ). The captures are not taken into account if they are triggered after \( CMPx + CMP1 \) (resp. \( CMPx + CMP3 \) ).

The captures are enabled again at the beginning of the next PWM period.

If the result of the auto-delayed summation is above 0xFFFF (overflow), the value is ignored and no compare event will be generated until a new period is started.

Note: \( DELCMPx[1:0] \) bitfield must be reset when reprogrammed from one value to the other to re-initialize properly the auto-delayed mechanism, for instance:

- • \( DELCMPx[1:0] = 10 \)

- • \( DELCMPx[1:0] = 00 \)

- • \( DELCMPx[1:0] = 11 \)

As an example, Figure 291 shows how the following signal can be generated:

- • Output set when the counter is equal to Compare 1 value

- • Output reset 4 cycles after a falling edge on a given external event

Note: To simplify the figure, the external event signal is shown without any resynchronization delay: practically, there is a delay of 1 to 2 \( f_{HRTIM} \) clock periods between the falling edge and the capture event due to an internal resynchronization stage which is necessary to process external input signals.

Figure 291. Auto-delayed compare

A regular compare channel (e.g. Compare 1) is used for the output set: as soon as the counter matches the content of the compare register, the output goes to its active state.

A delayed compare is used for the output reset: the compare event can be generated only if a capture event has occurred. No event is generated when the counter matches the delayed compare value (counter = 4). Once the capture event has been triggered by the external event, the content of the capture register is summed to the delayed compare value to have the new compare value. In the example, the auto-delayed value 4 is summed to the capture equal to 7 to give a value of 12 in the auto-delayed compare register. From this time on, the compare event can be generated and will happen when the counter is equal to 12, causing the output to be reset.

Overcapture management in auto-delayed mode

Overcapture is prevented when the auto-delayed mode is enabled (DEL CMPx[1:0] = 01, 10, 11).

When multiple capture requests occur within the same counting period, only the first capture is taken into account to compute the auto-delayed compare value. A new capture is possible only:

- • Once the auto-delayed compare has matched the counter value (compare event)

- • Once the counter has rolled over (period)

- • Once the timer has been reset

Changing auto-delayed compare values

When the auto-delayed compare value is preloaded (PREEN bit set), the new compare value is taken into account on the next coming update event (for instance on the period event), regardless of when the compare register was written and if the capture occurred (see Figure 291 , where the delay is changed when the counter rolls over).

When the preload is disabled (PREEN bit reset), the new compare value is taken into account immediately, even if it is modified after the capture event has occurred, as per the example below:

- 1. At t1, DEL CMP2 = 1.

- 2. At t2, CMP2_act = 0x40 => comparison disabled

- 3. At t3, a capture event occurs capturing the value CPTR1 = 0x20. => comparison enabled, compare value = 0x60

- 4. At t4, CMP2_act = 0x100 (before the counter reached value CPTR1 + 0x40) => comparison still enabled, new compare value = 0x120

- 5. At t5, the counter reaches the period value => comparison disabled, cmp2_act = 0x100

Similarly, if the CMP1(CMP3) value changes while DEL CMPx = 10 or 11, and preload is disabled:

- 1. At t1, DEL CMP2 = 2.

- 2. At t2, CMP2_act = 0x40 => comparison disabled

- 3. At t3, CMP3 event occurs - CMP3_act = 0x50 before capture 1 event occurs => comparison enabled, compare value = 0x90

- 4. At t4, CMP3_act = 0x100 (before the counter reached value 0x90) => comparison still enabled, Compare 2 event will occur at = 0x140

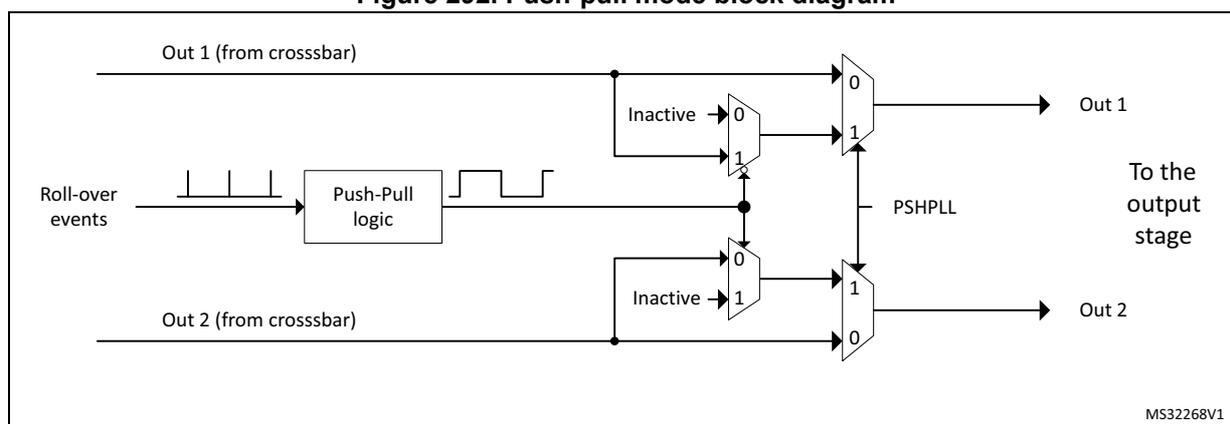

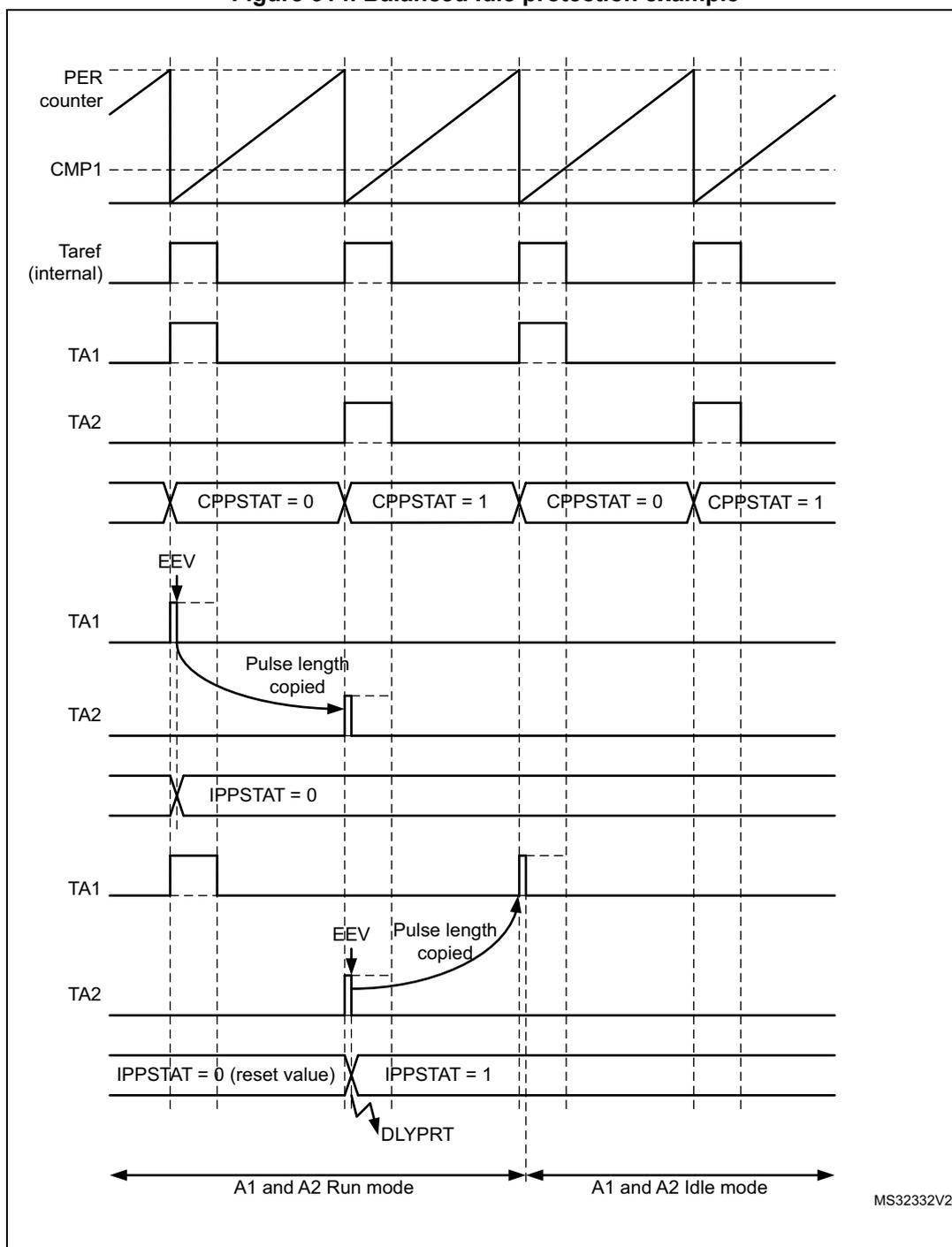

Push-pull mode

This mode primarily aims at driving converters using push-pull topologies. It also needs to be enabled when the delayed idle protection is required, typically for resonant converters (refer to Section 37.3.9: Delayed Protection ).

The push-pull mode is enabled by setting PSHPLL bit in the HRTIM_TIMxCR register.

It applies the signals generated by the crossbar to output 1 and output 2 alternatively, on the period basis, maintaining the other output to its inactive state. The redirection rate (push-pull frequency) is defined by the timer's period event, as shown on Figure 292 . The push-pull period is twice the timer counting period.

Figure 292. Push-pull mode block diagram

The push-pull mode is only available when the timer operates in continuous mode: the counter must not be reset once it has been enabled (TxCEN bit set). It is necessary to disable the timer to stop a push-pull operation and to reset the counter before re-enabling it.

The signal shape is defined using HRTIM_SETxyR and HRTIM_RSTxyR for both outputs. It is necessary to have HRTIM_SETx1R = HRTIM_SETx2R and HRTIM_RSTx1R = HRTIM_RSTx2R to have both outputs with identical waveforms and to achieve a balanced operation. Still, it is possible to have different programming on both outputs for other uses.

Note: The push-pull operation cannot be used when a deadtime is enabled (mutually exclusive functions).

The CPPSAT status bit in HRTIM_TIMxISR indicates on which output the signal is currently active. CPPSTAT is reset when the push-pull mode is disabled.

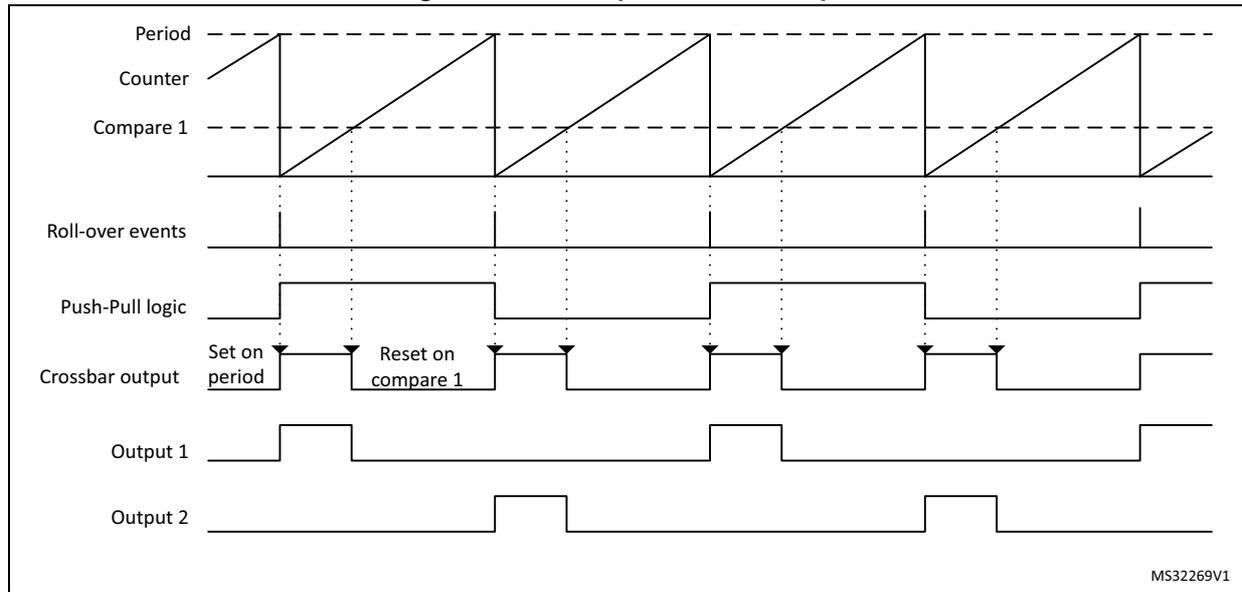

In the example given on Figure 293 , the timer internal waveform is defined as follows:

- • Output set on period event

- • Output reset on Compare 1 match event

Figure 293. Push-pull mode example

This timing diagram illustrates the push-pull mode operation. It shows the following signals over time:

- Period: A dashed horizontal line representing the timer period.

- Counter: A sawtooth waveform that increases linearly from 0 to the period value and then resets.

- Compare 1: A dashed horizontal line representing the compare value.

- Roll-over events: Pulses generated when the counter reaches the period value.

- Push-Pull logic: A signal that is high when the counter is between 0 and Compare 1, and low otherwise.

- Crossbar output: A signal that is set high on the rising edge of the counter (at 0) and reset low on the rising edge of Compare 1. It is labeled "Set on period" and "Reset on compare 1".

- Output 1: A pulse-width modulated (PWM) signal that is high when the crossbar output is high and the counter is below Compare 1.

- Output 2: The complementary PWM signal, which is high when the crossbar output is low and the counter is below Compare 1.

MS32269V1

Deadtime

A deadtime insertion unit allows to generate a couple of complementary signals from a single reference waveform, with programmable delays between active state transitions. This is commonly used for topologies using half-bridges or full bridges. It simplifies the software: only 1 waveform is programmed and controlled to drive two outputs.

The Dead time insertion is enabled by setting DTEN bit in HRTIM_OUTxR register. The complementary signals are built based on the reference waveform defined for output 1, using HRTIM_SETx1R and HRTIM_RSTx1R registers: HRTIM_SETx2R and HRTIM_RSTx2R registers are not significant when DTEN bit is set.

Note: The deadtime cannot be used simultaneously with the push-pull mode.

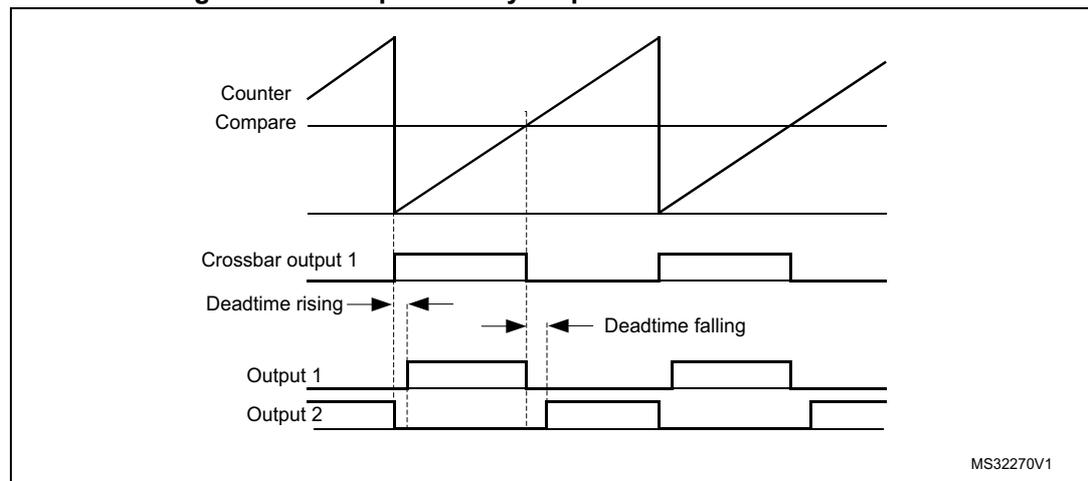

Two deadtimes can be defined in relationship with the rising edge and the falling edge of the reference waveform, as in Figure 294.

Figure 294. Complementary outputs with deadtime insertion

This timing diagram illustrates the operation with deadtime insertion. It shows the following signals over time:

- Counter: A sawtooth waveform.

- Compare: A dashed horizontal line representing the compare value.

- Crossbar output 1: The reference waveform that is set high at the counter's rising edge (0) and reset low at the compare value.

- Deadtime rising: The time interval between the rising edge of Crossbar output 1 and the rising edge of Output 1.

- Deadtime falling: The time interval between the falling edge of Crossbar output 1 and the falling edge of Output 2.

- Output 1: The primary output signal, which is a delayed version of Crossbar output 1.

- Output 2: The complementary output signal, which is a delayed version of the inverted Crossbar output 1.

MS32270V1

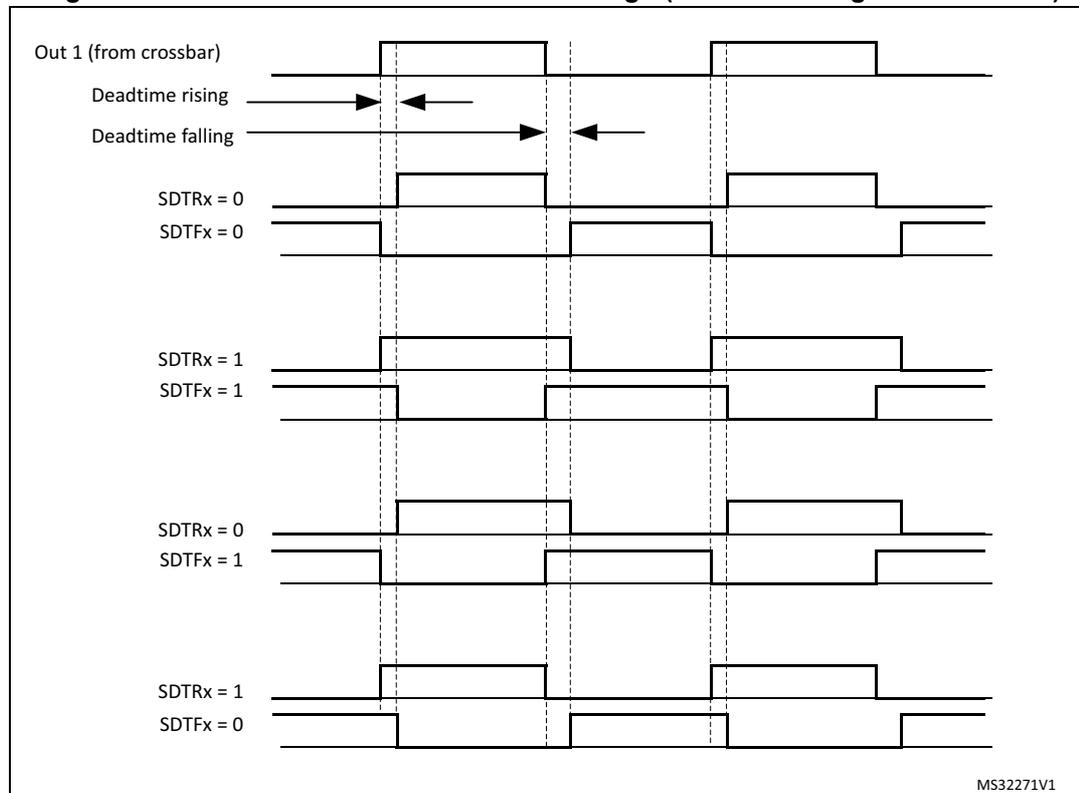

Negative deadtime values can be defined when some control overlap is required. This is done using the deadtime sign bits (SDTFx and SDTRx bits in HRTIM_DTxR register). Figure 295 shows complementary signal waveforms depending on respective signs.

Figure 295. Deadtime insertion vs deadtime sign (1 indicates negative deadtime)

The figure shows four sets of signal waveforms for Out 1 (from crossbar) and SDTRx/SDTFx bits. The top waveform shows Out 1 (from crossbar) with deadtime rising and falling intervals indicated by arrows. The subsequent waveforms show the SDTRx and SDTFx bit settings for different deadtime insertion scenarios:

- SDTRx = 0, SDTFx = 0: No deadtime insertion.

- SDTRx = 1, SDTFx = 1: Negative deadtime insertion.

- SDTRx = 0, SDTFx = 1: Negative deadtime insertion.

- SDTRx = 1, SDTFx = 0: Positive deadtime insertion.

MS32271V1

The deadtime values are defined with DTFx[8:0] and DTRx[8:0] bitfields and based on a specific clock prescaled according to DTPRSC[2:0] bits, as follows:

where x is either R or F and \( t_{DTG} = (2^{(DTPRSC[2:0])}) \times t_{HRTIM} \) .

Table 308 gives the resolution and maximum absolute values depending on the prescaler value.

Table 308. Deadtime resolution and max absolute values

| DTPRSC[2:0] (1) | \( t_{DTG} \) | \( t_{DTx} \max \) | \( f_{HRTIM} = 400 \text{ MHz} \) | |

|---|---|---|---|---|

| \( t_{DTG} \text{ (ns)} \) | \( |t_{DTx}| \max \text{ (}\mu\text{s)} \) | |||

| 011 | \( t_{HRTIM} \) | \( 511 \times t_{DTG} \) | 2.5 | 1.28 |

| 100 | \( 2 \times t_{HRTIM} \) | 5 | 2.56 | |

| 101 | \( 4 \times t_{HRTIM} \) | 10 | 5.11 | |

| 110 | \( 8 \times t_{HRTIM} \) | 20 | 10.22 | |

| 111 | \( 16 \times t_{HRTIM} \) | 40 | 20.44 | |

1. DTPRSC[2:0] values 000, 001, 010 are reserved.

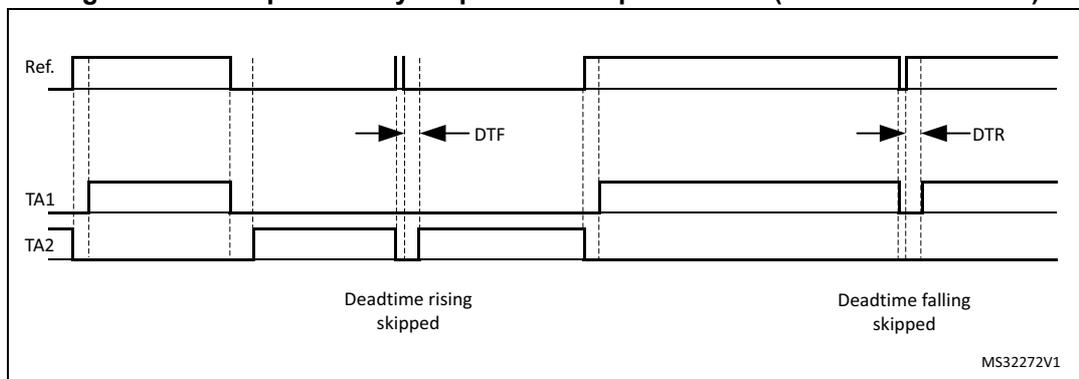

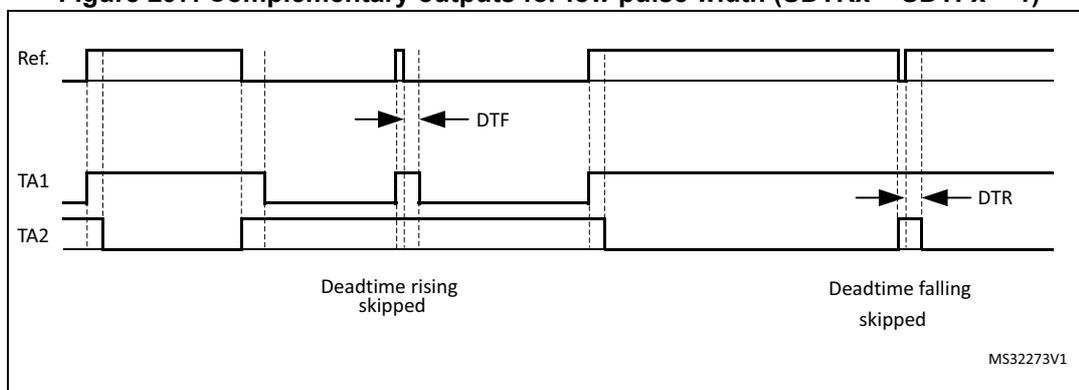

Figure 296 to Figure 299 present how the deadtime generator behaves for reference waveforms with pulsewidth below the deadtime values, for all deadtime configurations.

Figure 296. Complementary outputs for low pulse width (SDTRx = SDTFx = 0)

Timing diagram showing complementary outputs (TA1, TA2) for low pulse width (SDTRx = SDTFx = 0). The reference waveform (Ref.) has a pulse width below the deadtime values. The deadtime rising and falling are skipped. The diagram is labeled MS32272V1.

Figure 297. Complementary outputs for low pulse width (SDTRx = SDTFx = 1)

Timing diagram showing complementary outputs (TA1, TA2) for low pulse width (SDTRx = SDTFx = 1). The reference waveform (Ref.) has a pulse width below the deadtime values. The deadtime rising and falling are skipped. The diagram is labeled MS32273V1.

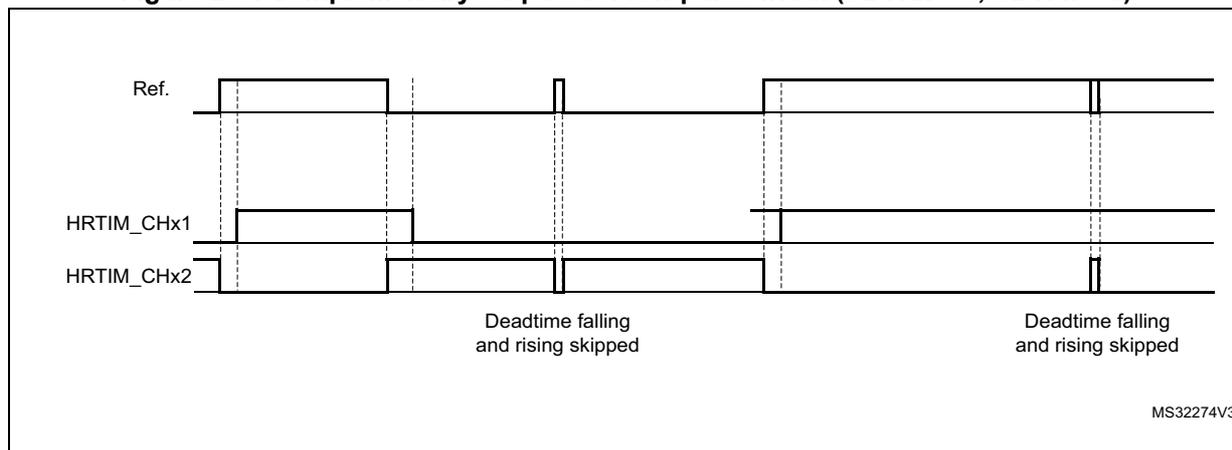

Figure 298. Complementary outputs for low pulse width (SDTRx = 0, SDTFx = 1)

Timing diagram showing complementary outputs (HRTIM_CHx1, HRTIM_CHx2) for low pulse width (SDTRx = 0, SDTFx = 1). The reference waveform (Ref.) has a pulse width below the deadtime values. The deadtime falling and rising are skipped. The diagram is labeled MS32274V3.

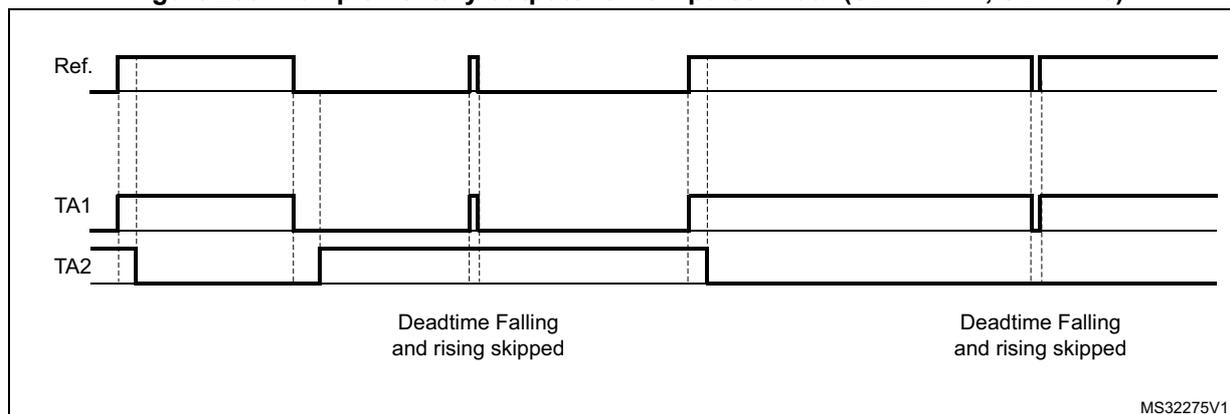

Figure 299. Complementary outputs for low pulse width (SDTRx = 1, SDTFx=0)

For safety purposes, it is possible to prevent any spurious write into the deadtime registers by locking the sign and/or the value of the deadtime using DTFLKx, DTRLKx, DTFSLKx and DTRSLKx. Once these bits are set, the related bits and bitfields are becoming read only until the next system reset.

Caution: DTEN bit must not be changed in the following cases:

- - When the timer is enabled (TxEN bit set)

- - When the timer outputs are set/reset by another timer (while TxEN is reset)

- Otherwise, an unpredictable behavior would result.

It is therefore necessary to disable the timer (TxCEN bit reset) and have the corresponding outputs disabled.

For the particular case where DTEN must be set while the burst mode is enabled with a deadtime upon entry (BME = 1, DIDL = 1, IDLEM = 1), it is necessary to force the two outputs in their IDLES state by software commands (SST, RST bits) before setting DTEN bit. This is to avoid any side effect resulting from a burst mode entry that would happen immediately before a deadtime enable.

37.3.5 Master timer

The main purpose of the master timer is to provide common signals to the 5 timing units, either for synchronization purpose or to set/reset outputs. It does not have direct control over any outputs, but still can be used indirectly by the set/reset crossbars.

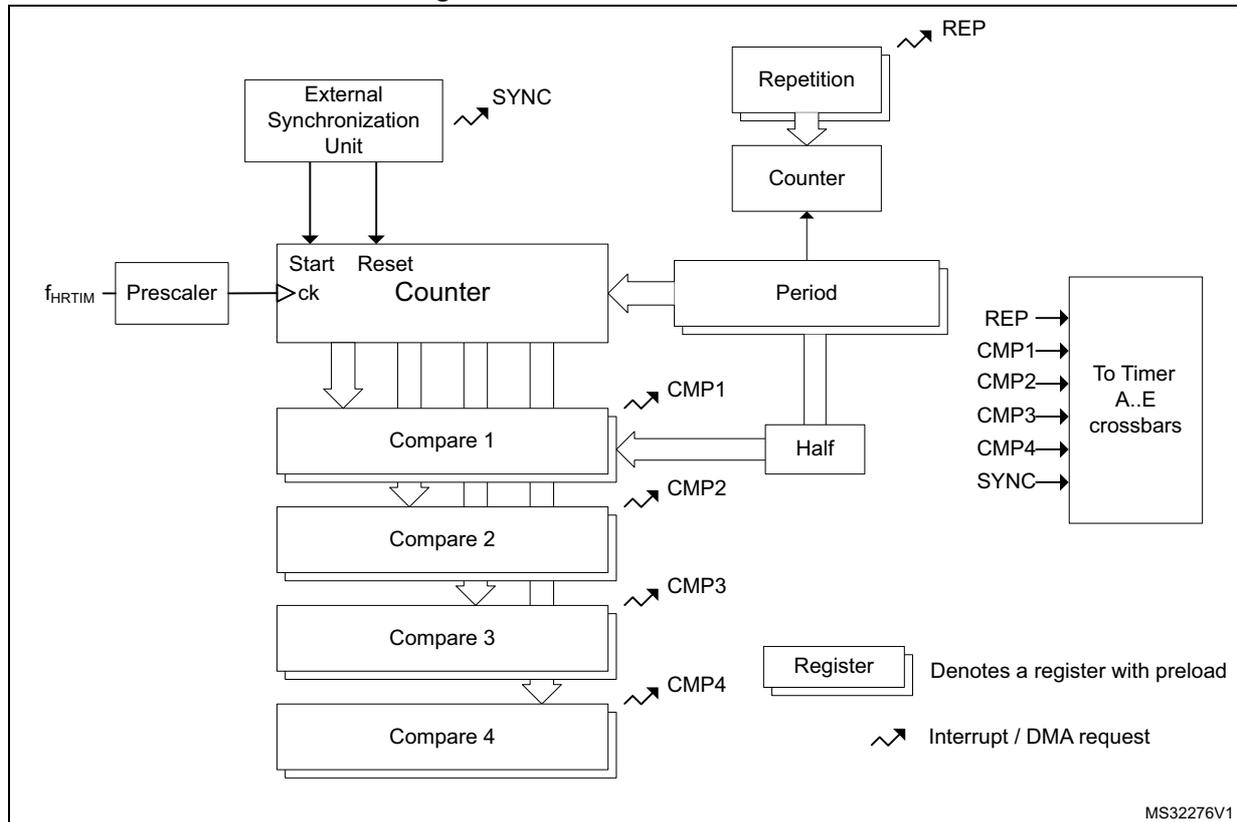

Figure 300 provides an overview of the master timer.

Figure 300. Master timer overview

MS32276V1

The master timer is based on the very same architecture as the timing units, with the following differences:

- • It does not have outputs associated with, nor output related control

- • It does not have its own crossbar unit, nor push-pull or deadtime mode

- • It can only be reset by the external synchronization circuitry

- • It does not have a capture unit, nor the auto-delayed mode

- • It does not include external event blanking and windowing circuitry

- • It has a limited set of interrupt / DMA requests: Compare 1..4, repetition, register update and external synchronization event.

The master timer control register includes all the timer enable bits, for the master and Timer A..E timing units. This allows to have all timer synchronously started with a single write access.

It also handles the external synchronization for the whole HRTIM timer (see Section 37.3.17: Synchronizing the HRTIM with other timers or HRTIM instances ), with both MCU internal and external (inputs/outputs) resources.

Master timer control registers are mapped with the same offset as the timing units' registers.

37.3.6 Set/reset events priorities and narrow pulses management

This section describes how the output waveform is generated when several set and/or reset requests are occurring within 3 consecutive \( t_{HRTIM} \) periods.

An arbitration is performed during each \( t_{HRTIM} \) period, in 2 steps:

- 1. For each active event, the desired output transition is determined (set, reset or toggle).

- 2. A predefined arbitration is performed among the active events (from highest to lowest priority \( CMP4 \rightarrow CMP3 \rightarrow CMP2 \rightarrow CMP1 \rightarrow PER \) , see Concurrent set request / Concurrent reset requests ).

When set and reset requests from two different sources are simultaneous, the reset action has the highest priority.

Concurrent set request / Concurrent reset requests

When multiple sources are selected for a set event, an arbitration is performed when the set requests occur within the same \( f_{HRTIM} \) clock period.

In case of multiple requests from adjacent timers (TIMEVNT1..9), the request which occurs first is taken into account. The arbitration is done in 2 steps, depending on the source (from the highest to the lowest priority): \( CMP4 \rightarrow CMP3 \rightarrow CMP2 \rightarrow CMP1 \) .

If multiple requests from the master timer occur within the same \( f_{HRTIM} \) clock period, a predefined arbitration is applied and a single request will be taken into account (from the highest to the lowest priority):

\( MSTCMP4 \rightarrow MSTCMP3 \rightarrow MSTCMP2 \rightarrow MSTCMP1 \rightarrow MSTCMPER \)

When multiple requests internal to the timer occur within the same \( f_{HRTIM} \) clock period, a predefined arbitration is applied and the requests are taken with the following priority, whatever the effective timing (from highest to lowest):

\( CMP4 \rightarrow CMP3 \rightarrow CMP2 \rightarrow CMP1 \rightarrow PER \)

Note: Practically, this is of a primary importance only when using auto-delayed Compare 2 and Compare 4 simultaneously (i.e. when the effective set/reset cannot be determined a priori because it is related to an external event). In this case, the highest priority signal must be affected to the CMP4 event.

Last, the highest priority is given to non timing-related: EXTEVNT1..10, RESYNC (coming from SYNC event if SYNCIRSTx or SYNCSTRTx is set or from a software reset), update and software set (SST).

As a summary, in case of simultaneous events, the effective set (reset) event will be arbitrated between:

- • Any TIMEVNT1..9 event

- • A single source from the master (as per the fixed arbitration given above)

- • A single source from the timer

- • The “non timing-related events”.

The same arbitration principle applies for concurrent reset requests. In this case, the reset request has the highest priority.

A set or reset event occurring within the prescaler clock cycle is delayed to the next active edge of the prescaled clock (as for a counter reset), even if the arbitration is still performed every \( t_{\text{HRTIM}} \) cycle.

If a reset event is followed by a set event within the same prescaler clock cycle, the latest event will be considered.

37.3.7 External events global conditioning

The HRTIM timer can handle events not generated within the timer, referred to as “external event”. These external events come from multiple sources, either on-chip or off-chip:

- • built-in comparators,

- • digital input pins (typically connected to off-chip comparators and zero-crossing detectors),

- • on-chip events for other peripheral (ADC’s analog watchdogs and general purpose timer trigger outputs).

The external events conditioning circuitry allows to select the signal source for a given channel (with a 4:1 multiplexer) and to convert it into an information that can be processed by the crossbar unit (for instance, to have an output reset triggered by a falling edge detection on an external event channel).

Up to 10 external event channels can be conditioned and are available simultaneously for any of the 5 timers. This conditioning is common to all timers, since this is usually dictated by external components (such as a zero-crossing detector) and environmental conditions (typically the filter set-up will be related to the applications noise level and signature).

Figure 301 presents an overview of the conditioning logic for a single channel.

Figure 301. External event conditioning overview (1 channel represented)

![Figure 301. External event conditioning overview (1 channel represented). The diagram shows the signal flow for an external event (hrtim_evtX) through various conditioning stages. It starts with source selection (EExSRC[1:0]) from four possible sources (hrtim_evtX[1] to [4]). This is followed by edge and polarity selection (EExPOL, EExSNS[1:0]) using multiplexers and inverters. Then, a filtering stage (Digital Filter and Prescaler) is applied, controlled by EExF[3:0] and EExVSD[1:0] bits. Finally, the signal is split into a synchronous path (EExFAST = 0) and a fast asynchronous path (EExFAST = 1) leading to the Timer A.E and Output stage. The diagram is divided into four functional blocks: Source selection, Edge and polarity, Filtering (hrtim_evt6..10 only), and Fast path (hrtim_evt1..5 only).](/RM0433-STM32H742-743-753-750/5cc3eef4b929bcec2d50febe8f8881de_img.jpg)

The diagram illustrates the external event conditioning for a single channel. It shows the following components and signal paths:

- Source selection: Four external event signals (hrtim_evtX[1] to [4]) are input to a multiplexer. The selection is controlled by the EExSRC[1:0] bits.

- Edge and polarity: The selected signal is then processed through a series of multiplexers and inverters. The EExPOL bit controls the polarity, and the EExSNS[1:0] bits control the sensitivity (level-sensitive or edge-sensitive).

- Filtering: The signal then passes through a Digital Filter and a Prescaler. The Digital Filter is controlled by the EExF[3:0] bits, and the Prescaler is controlled by the EExVSD[1:0] bits. This stage is only active for external events 6 to 10.

- Fast path: The signal is then split into two paths: a synchronous path (EExFAST = 0) and a fast asynchronous path (EExFAST = 1). The fast path is only active for external events 1 to 5.

- Output stage: Both paths lead to the Timer A.E and Output stage.

The diagram is divided into four functional blocks: Source selection, Edge and polarity, Filtering (hrtim_evt6..10 only), and Fast path (hrtim_evt1..5 only). The signal flow is from left to right, starting with the external event signals and ending at the Timer A.E and Output stage.

The 10 external events are initialized using the HRTIM_EECR1 and HRTIM_EECR2 registers:

- • to select up to 4 sources with the EExSRC[1:0] bits,

- • to select the sensitivity with EExSNS[1:0] bits, to be either level-sensitive or edge-sensitive (rising, falling or both),

- • to select the polarity, in case of a level sensitivity, with EExPOL bit,

- • to have a low latency mode, with EExFAST bits (see Latency to external events ), for external events 1 to 5.

Note: The external events used as triggers for reset, capture, burst mode, ADC triggers and delayed protection are edge-sensitive even if EExSNS bit is reset (level-sensitive selection): if POL = 0 the trigger is active on external event rising edge, while if POL = 1 the trigger is active on external event falling edge.

The external events are discarded as long as the counters are disabled (TxCEN bit reset) to prevent any output state change and counter reset, except if they are used as ADC triggers.

Additionally, it is possible to enable digital noise filters, for external events 6 to 10, using EExF[3:0] bits in the HRTIM_EECR3 register.

A digital filter is made of a counter in which a number N of valid samples is needed to validate a transition on the output. If the input value changes before the counter has

reached the value N, the counter is reset and the transition is discarded (considered as a spurious event). If the counter reaches N, the transition is considered as valid and transmitted as a correct external event. Consequently, the digital filter adds a latency to the external events being filtered, depending on the sampling clock and on the filter length (number of valid samples expected).

The sampling clock is either the \( f_{HRTIM} \) clock or a specific prescaled clock \( f_{EEV_{S}} \) derived from \( f_{HRTIM} \) , defined with EEVSD[1:0] bits in HRTIM_EECR3 register.

Table 309 summarizes the available sources and features associated with each of the 10 external events channels.

Table 309. External events mapping and associated features

| External event channel | Fast mode | Digital filter | Balanced fault timer A,B,C | Balanced fault timer D,E | Src1 | Src 2 | Src3 | Src4 |

|---|---|---|---|---|---|---|---|---|

| 1 | Yes | - | - | - | PC10 | COMP1 | TIM1_TRGO | ADC1_AWD1 |

| 2 | Yes | - | - | - | PC12 | COMP2 | TIM2_TRGO | ADC1_AWD2 |

| 3 | Yes | - | - | - | PD5 | - | TIM3_TRGO | ADC1_AWD3 |

| 4 | Yes | - | - | - | PG11 | OPAMP1 (1) | TIM7_TRGO | ADC2_AWD1 |

| 5 | Yes | - | - | - | PG12 | - | LPTIM1 OUT | ADC2_AWD2 |

| 6 | - | Yes | Yes | - | PB4 | COMP1 | TIM6_TRGO | ADC2_AWD3 |

| 7 | - | Yes | Yes | - | PB5 | COMP2 | TIM7_TRGO | - |

| 8 | - | Yes | - | Yes | PB6 | - | TIM6_TRGO | TTCAN_TMP |

| 9 | - | Yes | - | Yes | PB7 | OPAMP1 (1) | TIM15_TRGO | TTCAN_RTP |

| 10 | - | Yes | - | - | PG13 | - | LPTIM2 OUT | TTCAN_SOC |

- 1. OPAMP1_VOUT can be used as High-resolution timer internal event source. In this case, OPAMP1_VOUT (PC4) pin must be configured in input mode. The data from the GPIO pin is redirect to the HRTIM external events through the pin Schmitt trigger. If OPAMP1 is disabled, PC4 pin, configured in input mode, can be used as HRTIM external events.

Latency to external events

The external event conditioning gives the possibility to adjust the external event processing time (and associated latency) depending on performance expectations:

- • A regular operating mode, in which the external event is resampled with the clock before acting on the output crossbar. This adds some latency but gives access to all crossbar functionalities. It enables the generation of an externally triggered high-resolution pulse.

- • A fast operating mode, in which the latency between the external event and the action on the output is minimized. This mode is convenient for ultra-fast over-current protections, for instance.

EExFAST bits in the HRTIM_EECR1 register allow to define the operating for channels 1 to 5. This influences the latency and the jitter present on the output pulses, as summarized in the table below.

Table 310. Output set/reset latency and jitter vs external event operating mode| EExFAST | Response time latency | Response time jitter | Jitter on output pulse (counter reset by ext. event) |

|---|---|---|---|

| 0 | 5 to 6 cycles of \( f_{\text{HRTIM}} \) clock | 1 cycles of \( f_{\text{HRTIM}} \) clock | No jitter, pulse width maintained with high-resolution |

| 1 | Minimal latency (depends whether the comparator or digital input is used) | Minimal jitter | 1 cycle of \( f_{\text{HRTIM}} \) clock jitter pulse width resolution down to \( t_{\text{HRTIM}} \) |

The EExFAST mode is only available with level-sensitive programming (EExSNS[1:0] = 00); the edge-sensitivity cannot be programmed.

It is possible to apply event filtering to external events (both blanking and windowing with EExFLTR[3:0] != 0000, see Section 37.3.8 ). In this case, EExLTCHx bit must be reset: the postponed mode is not supported, neither the windowing timeout feature.

Note: The external event configuration (source and polarity) must not be modified once the related EExFAST bit is set.

A fast external event cannot be used to toggle an output: it must be enabled either in HRTIM_SETxyR or HRTIM_RSTxyR registers, not in both.

When a set and a reset event - from 2 independent fast external events - occur simultaneously, the reset has the highest priority in the crossbar and the output becomes inactive.

When EExFAST bit is set, the output cannot be changed during the 11 \( f_{\text{HRTIM}} \) clock periods following the external event.

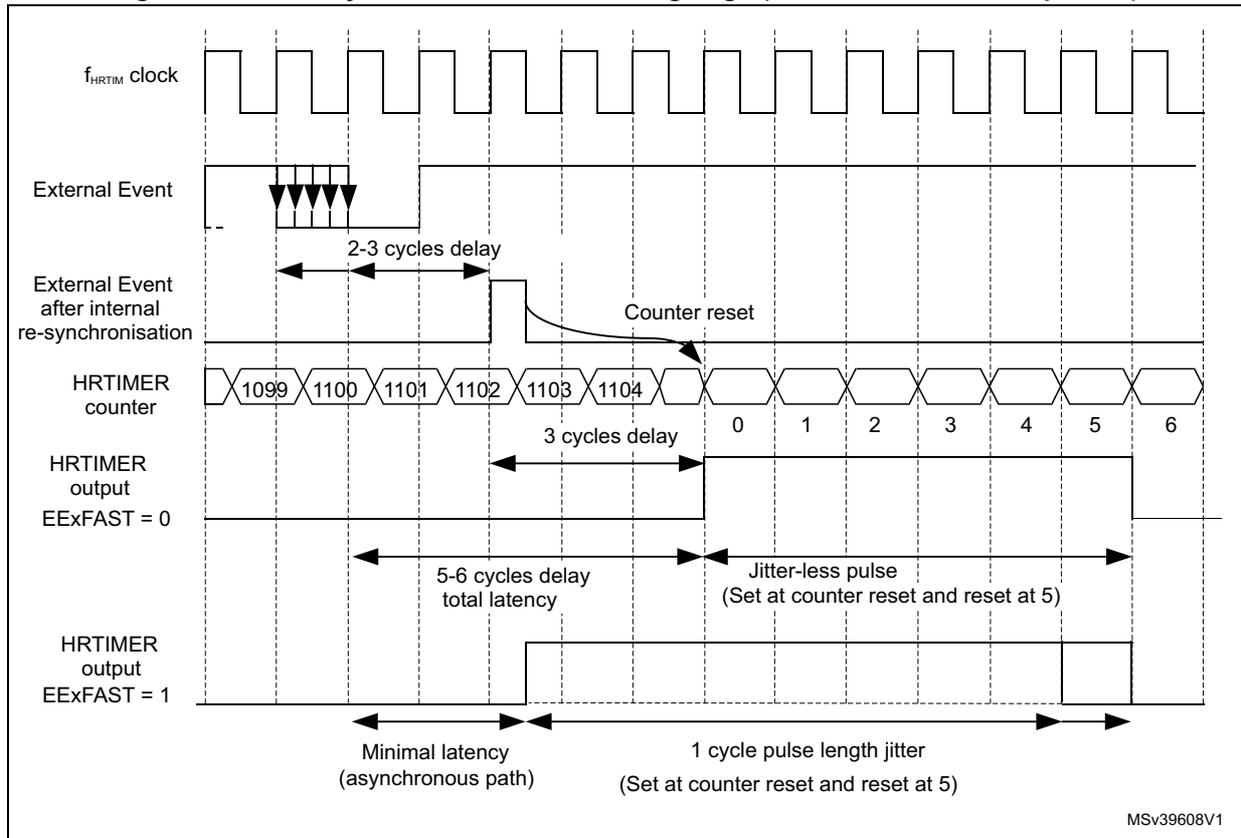

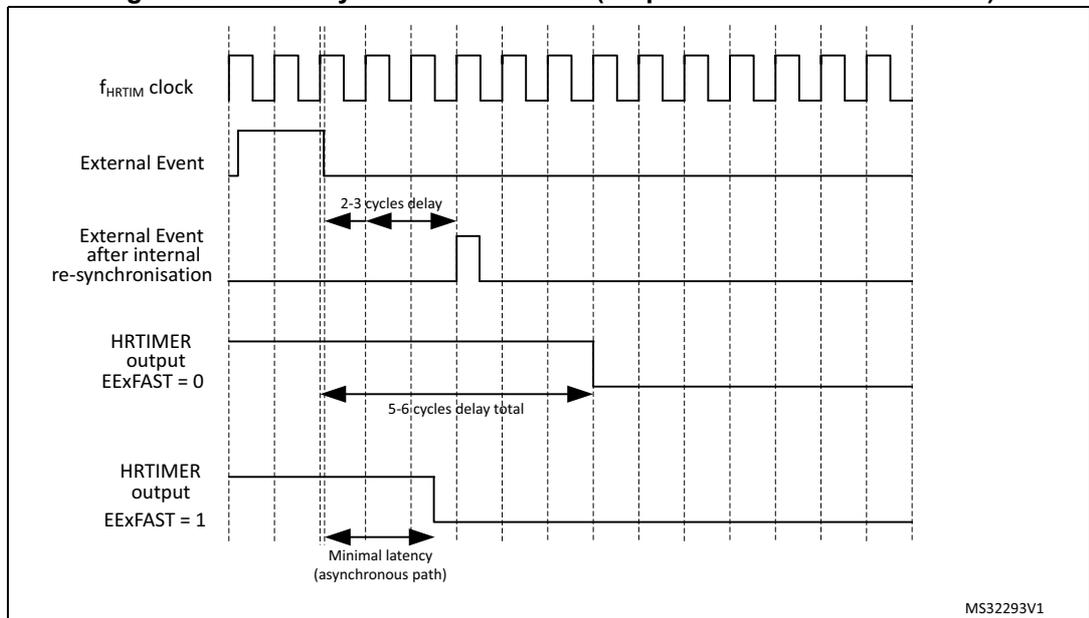

Figure 302 and Figure 303 give practical examples of the reaction time to external events, for output set/reset and counter reset.

Figure 302. Latency to external events falling edge (counter reset and output set)

The diagram shows the timing relationship between an external event and the HRTIMER counter and outputs. The f HRTIM clock is a periodic square wave. The External Event is a signal with a falling edge. The External Event after internal re-synchronisation is the event after it has been processed by the timer's internal logic. The HRTIMER counter shows a sequence of values: 1099, 1100, 1101, 1102, 1103, 1104, followed by a reset to 0, 1, 2, 3, 4, 5, 6. The HRTIMER output EExFAST = 0 is set at the counter reset and reset at counter value 5. The HRTIMER output EExFAST = 1 is set at the counter reset and reset at counter value 5. The diagram indicates a 2-3 cycles delay from the external event to the re-synchronised event. A Counter reset occurs at the re-synchronised event. A 3 cycles delay is shown from the counter reset to the output set. A 5-6 cycles delay total latency is indicated from the external event to the output set. A Jitter-less pulse is shown for EExFAST = 0, set at counter reset and reset at 5. Minimal latency (asynchronous path) and 1 cycle pulse length jitter are indicated for EExFAST = 1, set at counter reset and reset at 5. The identifier MSV39608V1 is present in the bottom right corner.

Figure 303. Latency to external events (output reset on external event)

The diagram shows the timing relationship between an external event and the HRTIMER outputs. The f HRTIM clock is a periodic square wave. The External Event is a signal with a falling edge. The External Event after internal re-synchronisation is the event after it has been processed by the timer's internal logic. The HRTIMER output EExFAST = 0 is reset on the external event. The HRTIMER output EExFAST = 1 is reset on the external event. The diagram indicates a 2-3 cycles delay from the external event to the re-synchronised event. A 5-6 cycles delay total is indicated from the external event to the output reset. Minimal latency (asynchronous path) is indicated for EExFAST = 1. The identifier MS32293V1 is present in the bottom right corner.

37.3.8 External event filtering in timing units

Once conditioned, the 10 external events are available for all timing units.

They can be used directly and are active as soon as the timing unit counter is enabled (TxCEN bit set).

They can also be filtered to have an action limited in time, usually related to the counting period. Two operations can be performed:

- • blanking, to mask external events during a defined time period,

- • windowing, to enable external events only during a defined time period.

These modes are enabled using HRTIM_EExFLTR[3:0] bits in the HRTIM_EEFxR1 and HRTIM_EEFxR2 registers. Each of the 5 TimerA..E timing units has its own programmable filter settings for the 10 external events.

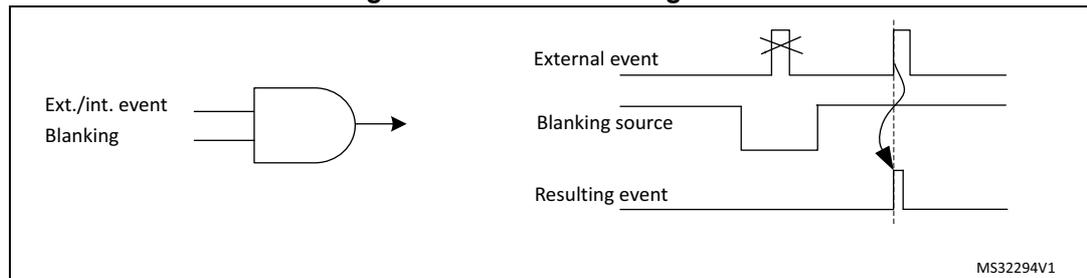

Blanking mode

In event blanking mode (see Figure 304 ), the external event is ignored if it happens during a given blanking period. This is convenient, for instance, to avoid a current limit to trip on switching noise at the beginning of a PWM period. This mode is active for EExFLTR[3:0] bitfield values ranging from 0001 to 1100.

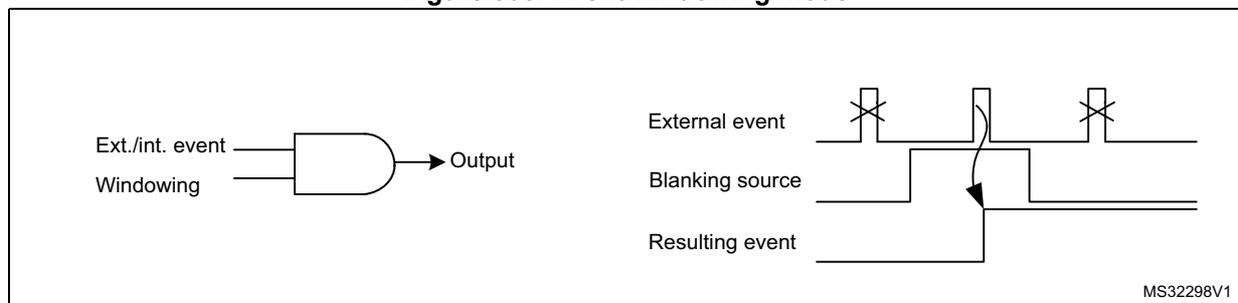

Figure 304. Event blanking mode

The diagram illustrates the event blanking mode. On the left, two inputs, 'Ext./int. event' and 'Blanking', are shown entering an AND gate. The output of the AND gate is labeled 'Resulting event'. To the right, three timing diagrams are shown. The 'External event' line shows a pulse that occurs while the 'Blanking source' line is high. The 'Resulting event' line shows that this pulse is ignored (remains low) during the blanking period. Once the blanking source goes low, a subsequent external event pulse is reflected as a pulse on the resulting event line. A small note 'MS32294V1' is in the bottom right corner.

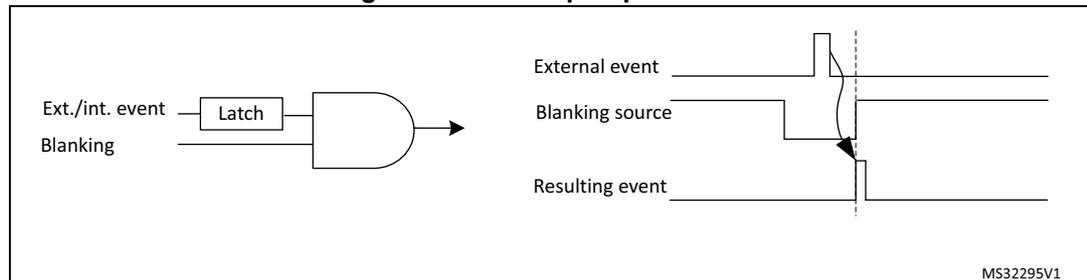

In event postpone mode, the external event is not taken into account immediately but is memorized (latched) and generated as soon as the blanking period is completed, as shown on Figure 305 . This mode is enabled by setting EExLTCH bit in HRTIM_EEFxR1 and HRTIM_EEFxR2 registers.

Figure 305. Event postpone mode

The diagram illustrates the event postpone mode. On the left, the 'Ext./int. event' input first passes through a 'Latch' block, and then its output and the 'Blanking' input enter an AND gate. The output of the AND gate is labeled 'Resulting event'. To the right, three timing diagrams are shown. The 'External event' line shows a pulse that occurs while the 'Blanking source' line is high. The 'Resulting event' line remains low during the blanking period but transitions to high immediately when the blanking source goes low, reflecting the state of the latched external event. A small note 'MS32295V1' is in the bottom right corner.

The blanking signal comes from several sources:

- the timer itself: the blanking lasts from the counter reset to the compare match (EExFLTR[3:0] = 0001 to 0100 for Compare 1 to Compare 4)

- from other timing units (EExFLTR[3:0] = 0101 to 1100): the blanking lasts from the selected timing unit counter reset to one of its compare match, or can be fully programmed as a waveform on Tx2 output. In this case, events are masked as long as the Tx2 signal is inactive (it is not necessary to have the output enabled, the signal is taken prior to the output stage).

The EExFLTR[3:0] configurations from 0101 to 1100 are referred to as TIMFLTR1 to TIMFLTR8 in the bit description, and differ from one timing unit to the other. Table 311 gives the 8 available options per timer: CMPx refers to blanking from counter reset to compare match, Tx2 refers to the timing unit TIMx output 2 waveform defined with HRTIM_SETx2 and HRTIM_RSTx2 registers. For instance, Timer B (TIMFLTR6) is Timer C output 2 waveform.

Table 311. Filtering signals mapping per time

| Source | Timer A | Timer B | Timer C | Timer D | Timer E | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CMP 1 | CMP 2 | CMP 4 | TA2 | CMP 1 | CMP 2 | CMP 4 | TB2 | CMP 1 | CMP 2 | CMP 4 | TC2 | CMP 1 | CMP 2 | CMP 4 | TD2 | CMP 1 | CMP 2 | CMP 4 | TE2 | ||

| Destination | Timer A | - | - | - | - | 1 | - | 2 | 3 | 4 | - | 5 | 6 | 7 | - | - | - | - | 8 | - | - |

| Timer B | 1 | - | 2 | 3 | - | - | - | - | 4 | 5 | - | 6 | - | 7 | - | - | 8 | - | - | - | |

| Timer C | - | 1 | - | - | 2 | - | 3 | 4 | - | - | - | - | 5 | - | 6 | 7 | - | - | 8 | - | |

| Timer D | 1 | - | - | - | - | 2 | - | - | 3 | 4 | - | 5 | - | - | - | - | 6 | - | 7 | 8 | |

| Timer E | - | 1 | - | - | 2 | - | - | - | 3 | - | 4 | 5 | 6 | - | 7 | 8 | - | - | - | - | |

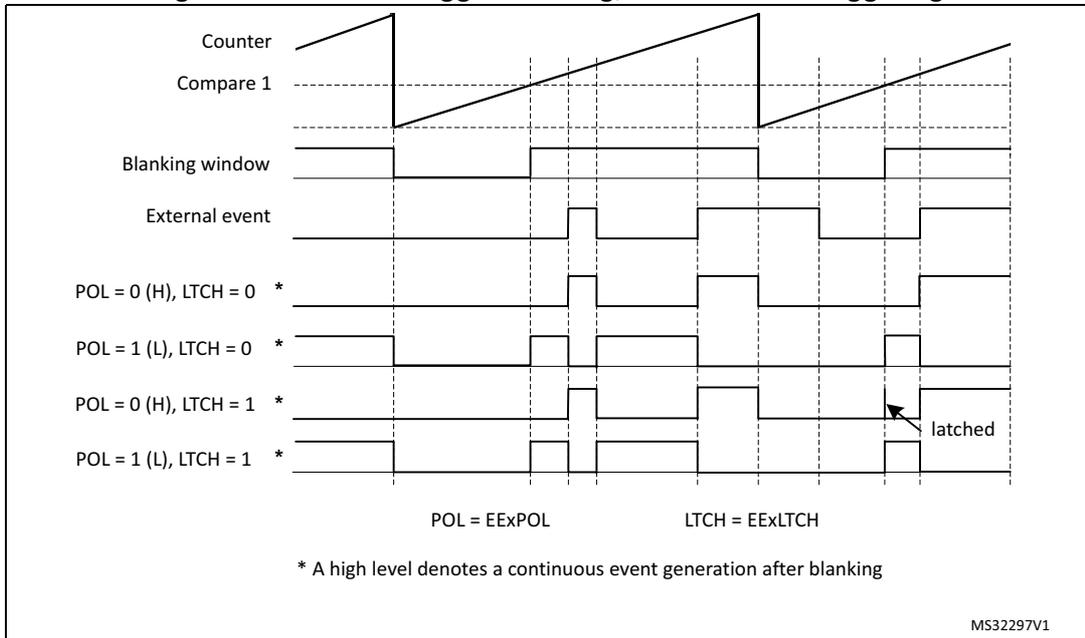

Figure 306 and Figure 307 give an example of external event blanking for all edge and level sensitivities, in regular and postponed modes.

Figure 306. External trigger blanking with edge-sensitive trigger

![Timing diagram for edge-sensitive external trigger blanking. It shows the Counter, Compare 1, Blanking window, External event, and two EExLTCH signal states (0 and 1) with corresponding edge-sensitive triggers. A legend defines EExSNS[1:0] settings: 01 (rising edge), 10 (falling edge), and 11 (both edges). An internal event is shown generated after the blanking window.](/RM0433-STM32H742-743-753-750/c4d06c605dd6b5837e94c19a11f1787d_img.jpg)

Counter

Compare 1

Blanking window

External event

EExLTCH = 0

EExLTCH = 1

▲ EExSNS[1:0] = 01 ▼ EExSNS[1:0] = 10 ▲▼ EExSNS[1:0] = 11

─┐ Internal event generated after blanking

MS32296V1

Figure 307. External trigger blanking, level sensitive triggering

Counter

Compare 1

Blanking window

External event

POL = 0 (H), LTCH = 0 *

POL = 1 (L), LTCH = 0 *

POL = 0 (H), LTCH = 1 *

POL = 1 (L), LTCH = 1 *

POL = EExPOL LTCH = EExLTCH

* A high level denotes a continuous event generation after blanking

latched

MS32297V1

Windowing mode

In event windowing mode, the event is taken into account only if it occurs within a given time window, otherwise it is ignored. This mode is active for EExFLTR[3:0] ranging from 1101 to 1111.

Figure 308. Event windowing mode

EExLTCH bit in EEFxR1 and EEFxR2 registers allows to latch the signal, if set to 1: in this case, an event is accepted if it occurs during the window but is delayed at the end of it.

- • If EExLTCH bit is reset and the signal occurs during the window, it is passed through directly.

- • If EExLTCH bit is reset and no signal occurs, a timeout event is generated at the end of the window.

A use case of the windowing mode is to filter synchronization signals. The timeout generation allows to force a default synchronization event, when the expected synchronization event is lacking (for instance during a converter start-up).

There are 3 sources for each external event windowing, coded as follows:

- • 1101 and 1110: the windowing lasts from the counter reset to the compare match (respectively Compare 2 and Compare 3)

- • 1111: the windowing is related to another timing unit and lasts from its counter reset to its Compare 2 match. The source is described as TIMWIN in the bit description and is given in Table 312 . As an example, the external events in timer B can be filtered by a window starting from timer A counter reset to timer A Compare 2.

Table 312. Windowing signals mapping per timer (EEFLTR[3:0] = 1111)

| Destination | Timer A | Timer B | Timer C | Timer D | Timer E |

|---|---|---|---|---|---|

| TIMWIN (source) | Timer B CMP2 | Timer A CMP2 | Timer D CMP2 | Timer C CMP2 | Timer D CMP2 |

Note: The timeout event generation is not supported if the external event is programmed in fast mode.

Figure 309 and Figure 310 present how the events are generated for the various edge and level sensitivities, as well as depending on EExLTCH bit setting. Timeout events are specifically mentioned for clarity reasons.

Figure 309. External trigger windowing with edge-sensitive trigger

![Timing diagram for Figure 309 showing Counter, Compare 1, Window, External event, and EExLTCH signals. It illustrates edge-sensitive triggering with EExSNS[1:0] settings 01, 10, and 11. The diagram shows how the external event is filtered through a window to generate an internal event. MS32299V1](/RM0433-STM32H742-743-753-750/22fa702f8cc85a08bd0b7263f0ddf9e0_img.jpg)

The diagram shows the following signals over time:

- Counter: A sawtooth waveform representing the timer's counter value.

- Compare 1: A horizontal dashed line representing the compare value.

- Window: A periodic square wave that defines the time intervals for external trigger acceptance.

- External event: A series of narrow pulses.

- EExLTCH = 0:

Output signals for different edge-sensitive settings:

- EExSNS[1:0] = 01: Rising edge sensitive. An output pulse occurs when a rising edge of the external event happens while the window is high. A timeout occurs if no event happens within the window.

- EExSNS[1:0] = 10: Falling edge sensitive. Similar behavior for falling edges.

- EExSNS[1:0] = 11: Both rising and falling edge sensitive. Output pulses occur for both edges within the window.

- EExLTCH = 1: Output signals for different edge-sensitive settings (mirrored logic to EExLTCH = 0).

- Internal event generated after windowing: A single pulse generated when the window is high and an external event edge is detected.

Legend for EExSNS[1:0]:

- EExSNS[1:0] = 01: Rising edge icon.

- EExSNS[1:0] = 10: Falling edge icon.

- EExSNS[1:0] = 11: Both rising and falling edge icons.

MS32299V1

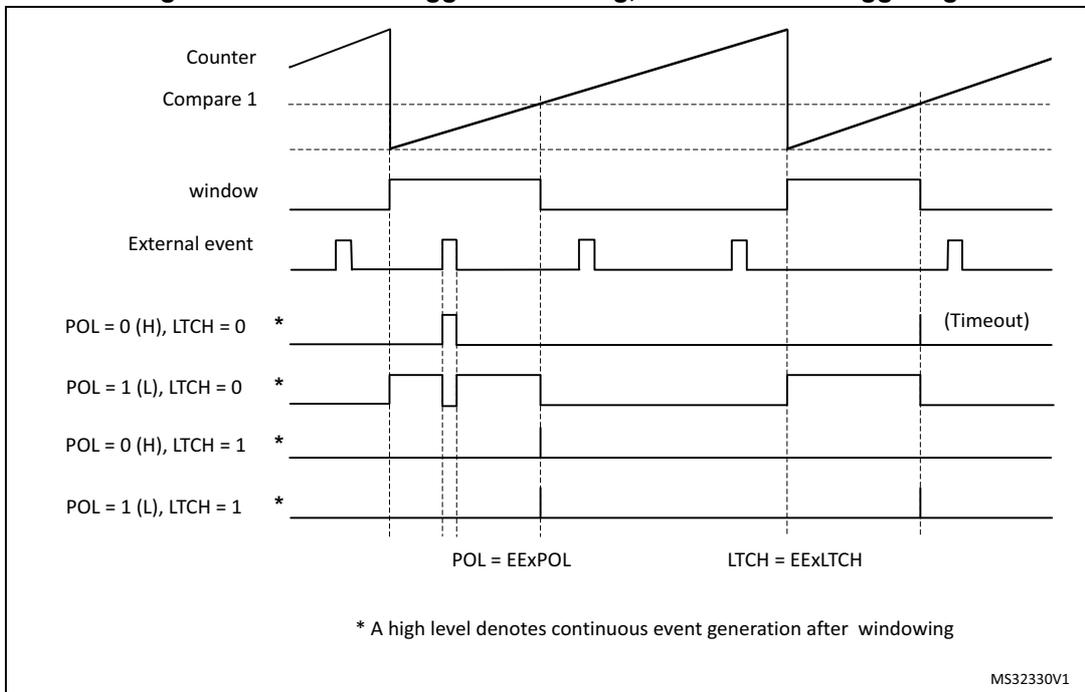

Figure 310. External trigger windowing, level sensitive triggering

The diagram shows the following signals over time:

- Counter: Sawtooth waveform.

- Compare 1: Horizontal dashed line.

- window: Periodic square wave.

- External event: Series of pulses.

- POL = 0 (H), LTCH = 0 (*): Output is high if the external event is high and the window is high.

- POL = 1 (L), LTCH = 0 (*): Output is high if the external event is low and the window is high.

- POL = 0 (H), LTCH = 1 (*): Output is high if the external event is high and the window is low.

- POL = 1 (L), LTCH = 1 (*): Output is high if the external event is low and the window is low.

Labels at the bottom:

- POL = EExPOL

- LTCH = EExLTCH

* A high level denotes continuous event generation after windowing

MS32330V1

37.3.9 Delayed Protection

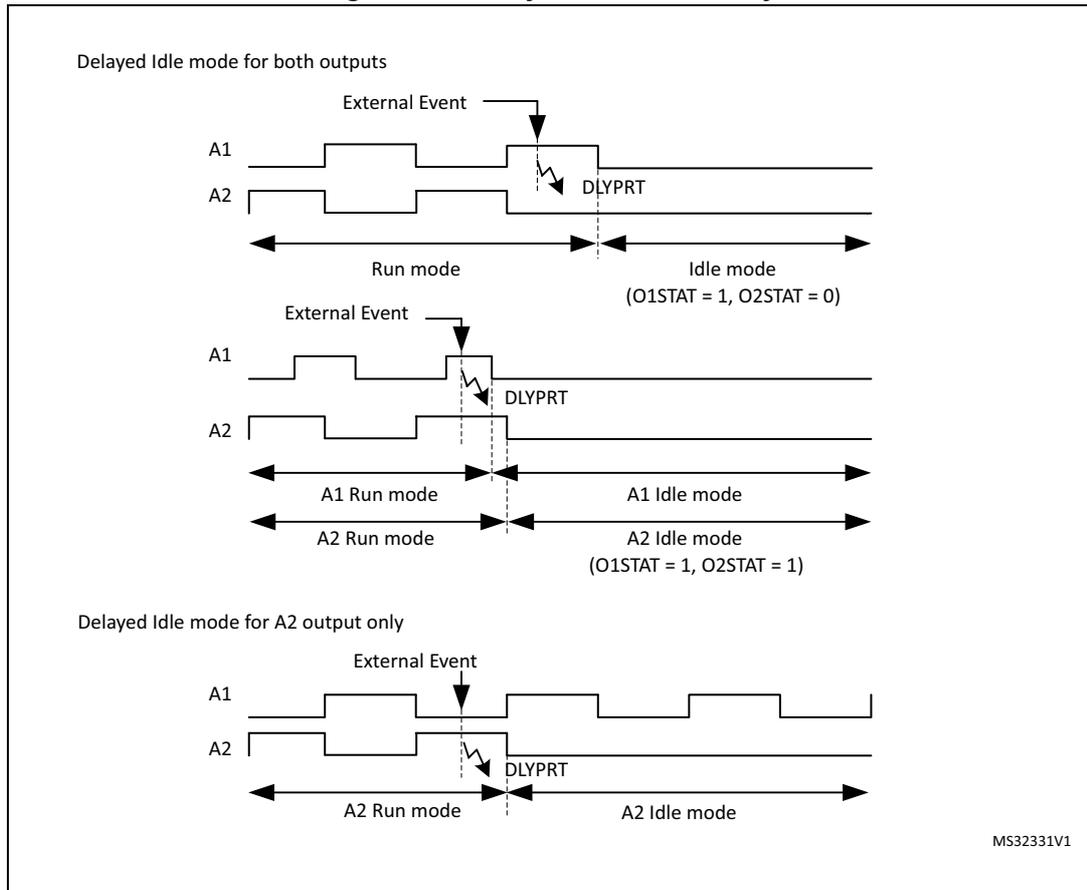

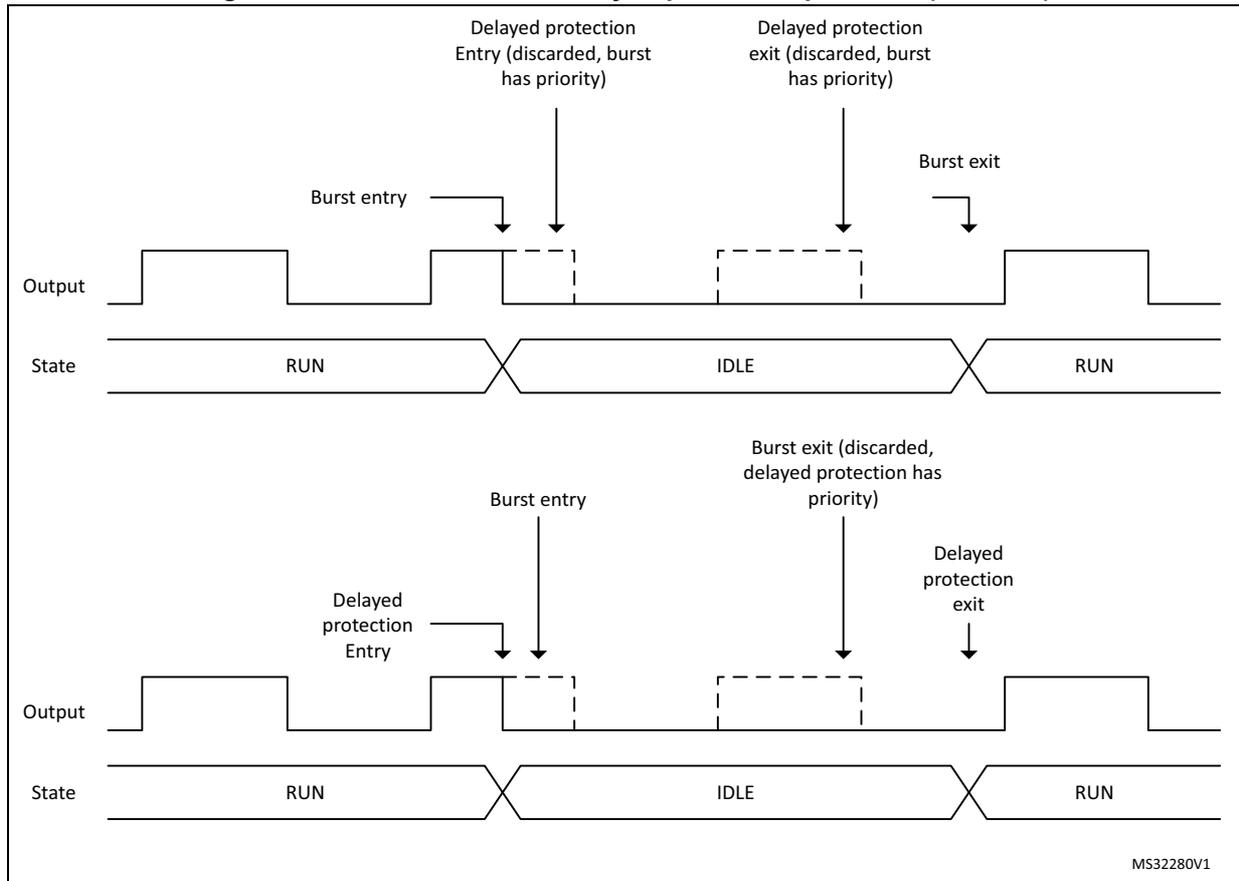

The HRTIM features specific protection schemes, typically for resonant converters when it is necessary to shut down the PWM outputs in a delayed manner, either once the active pulse is completed or once a push-pull period is completed. These features are enabled with DLYPRTEN bit in the HRTIM_OUTxR register, and are using specific external event channels.

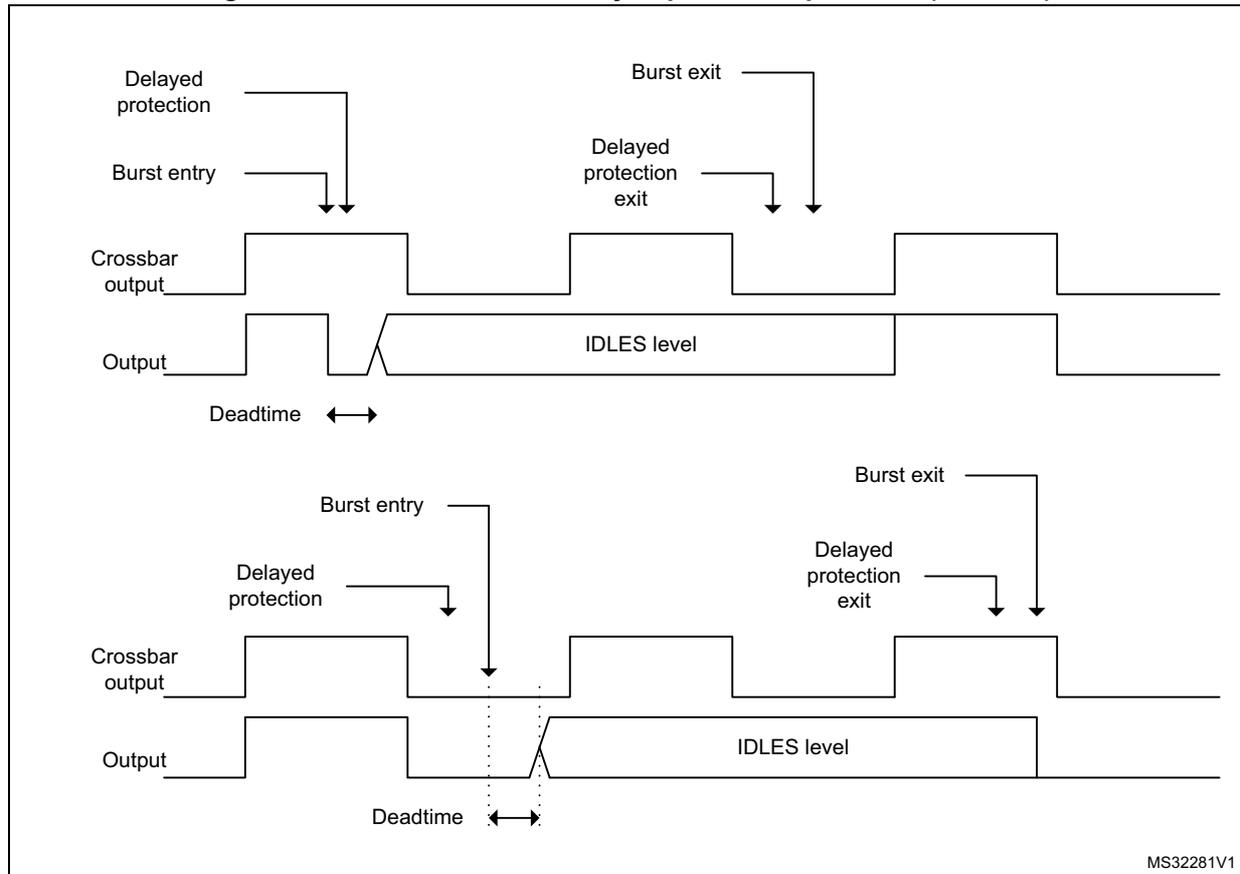

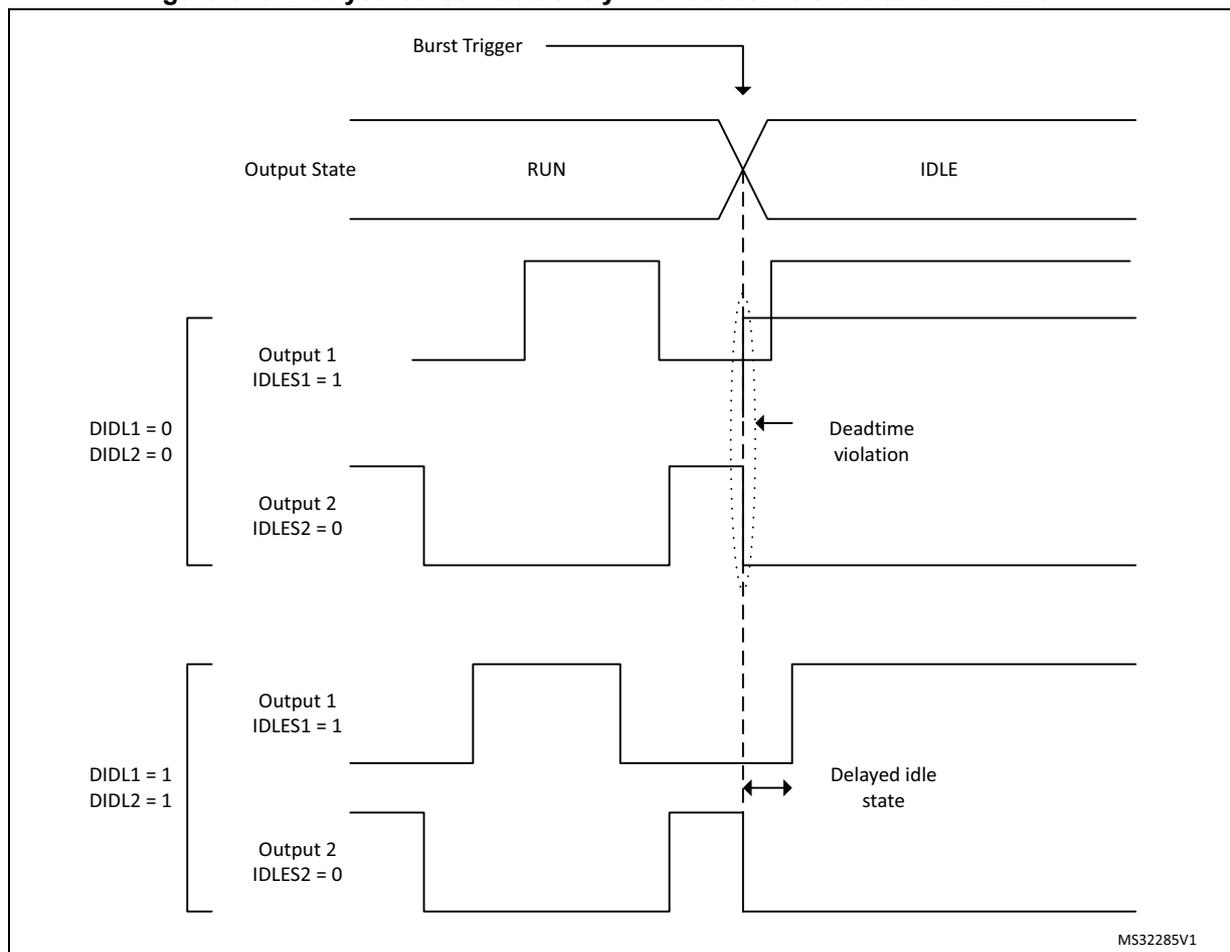

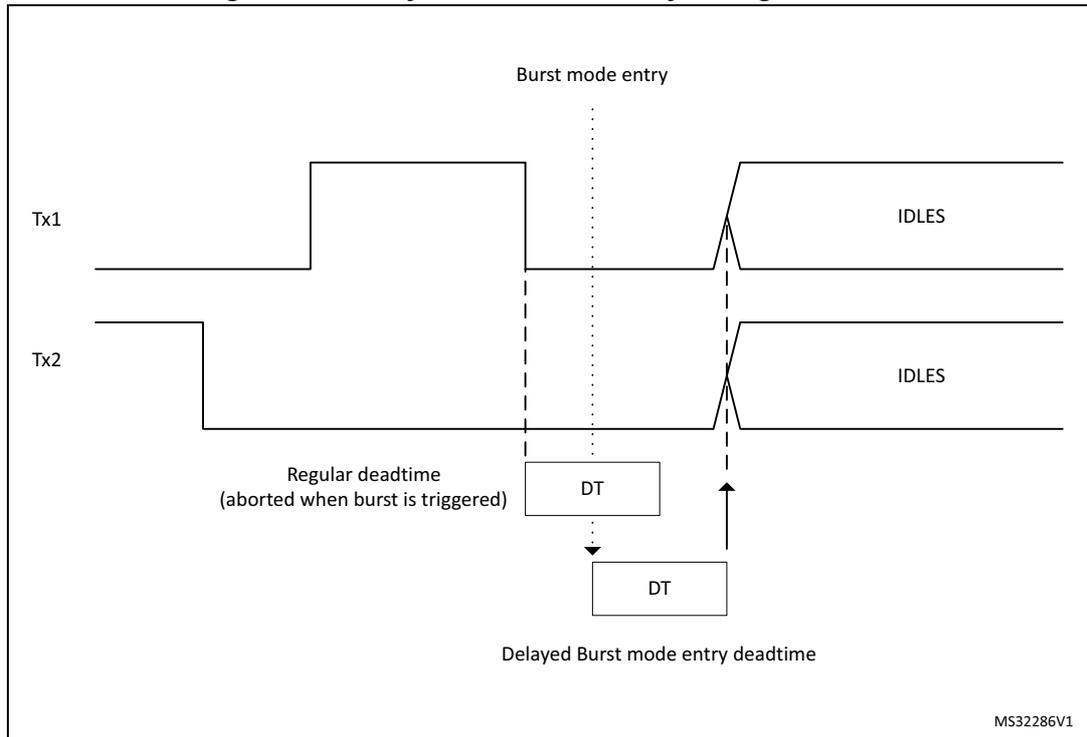

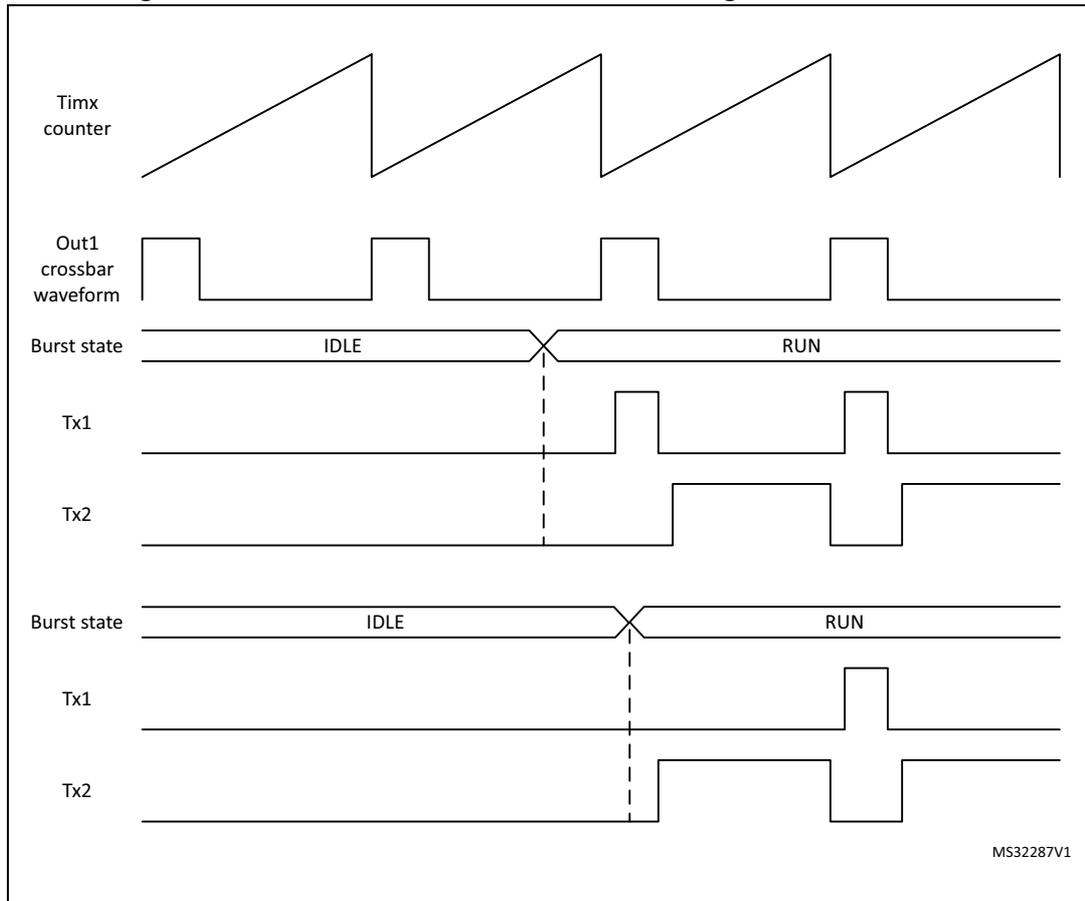

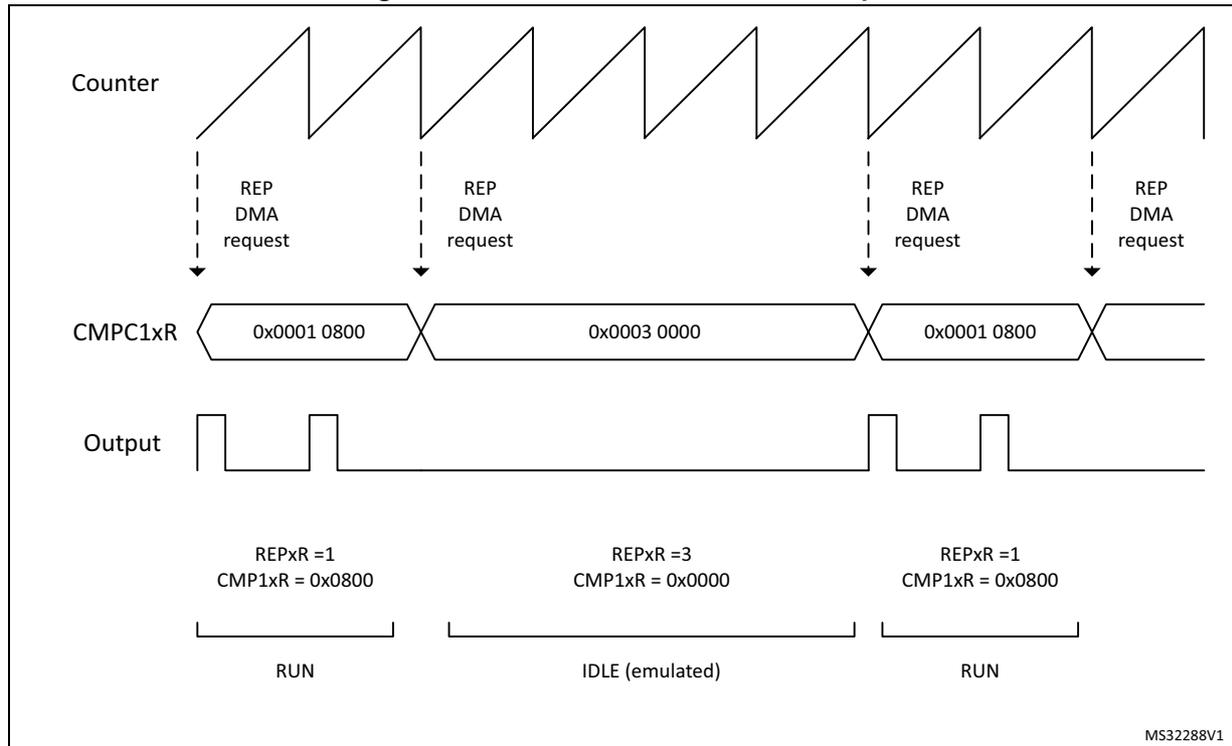

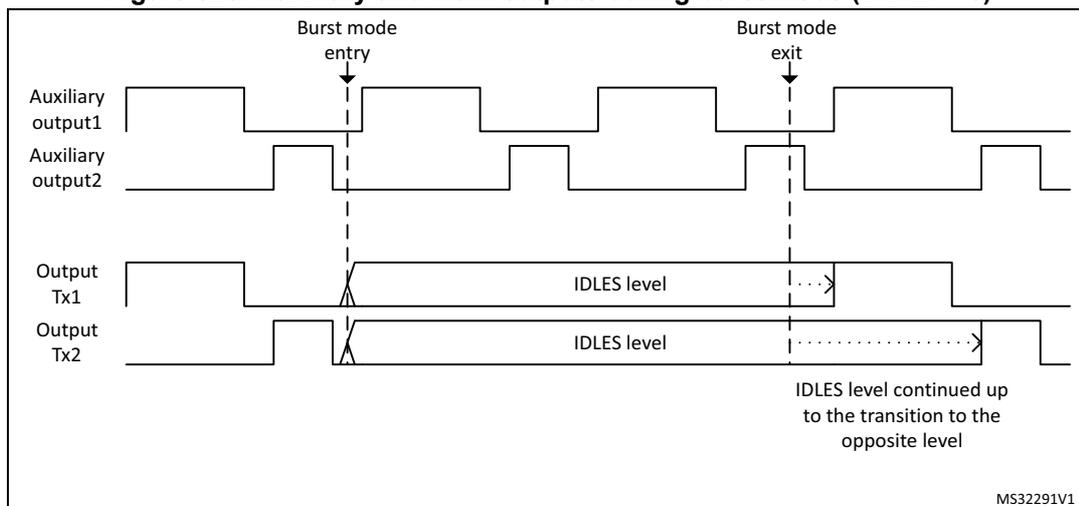

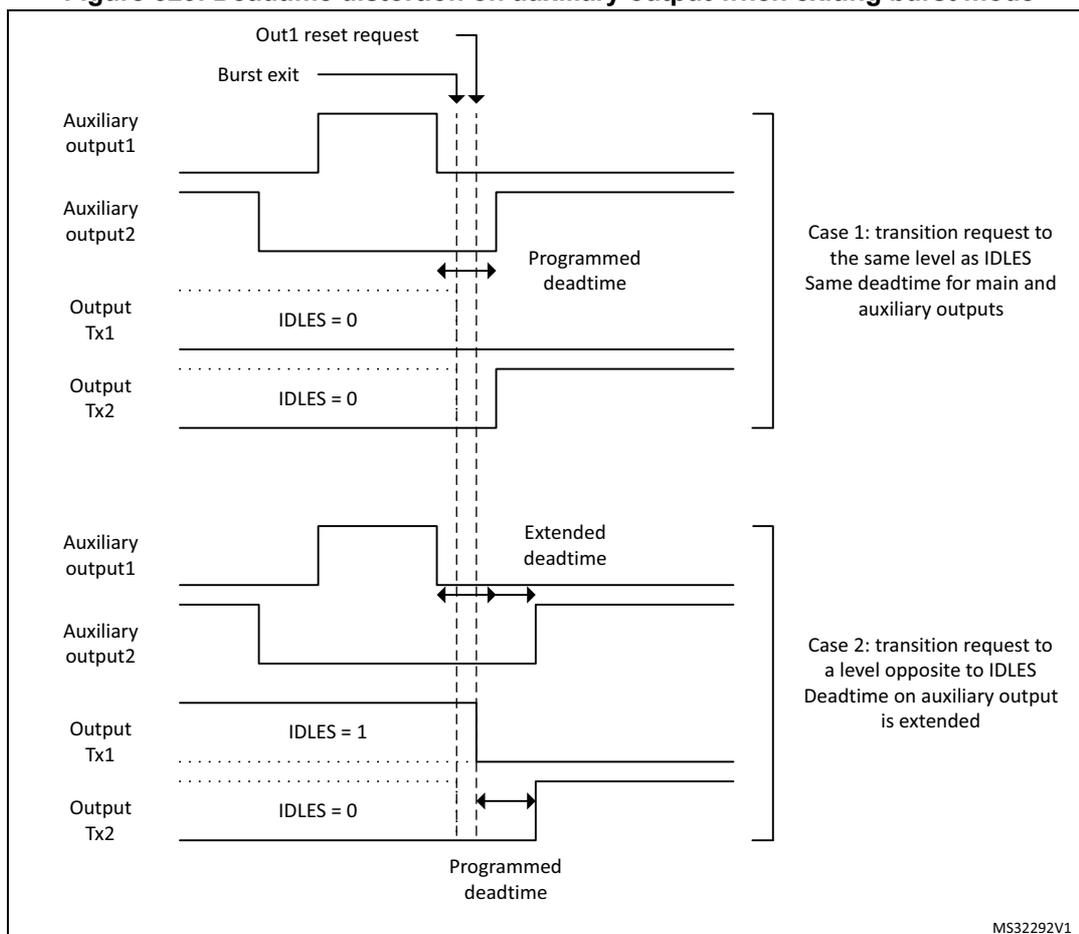

Delayed Idle

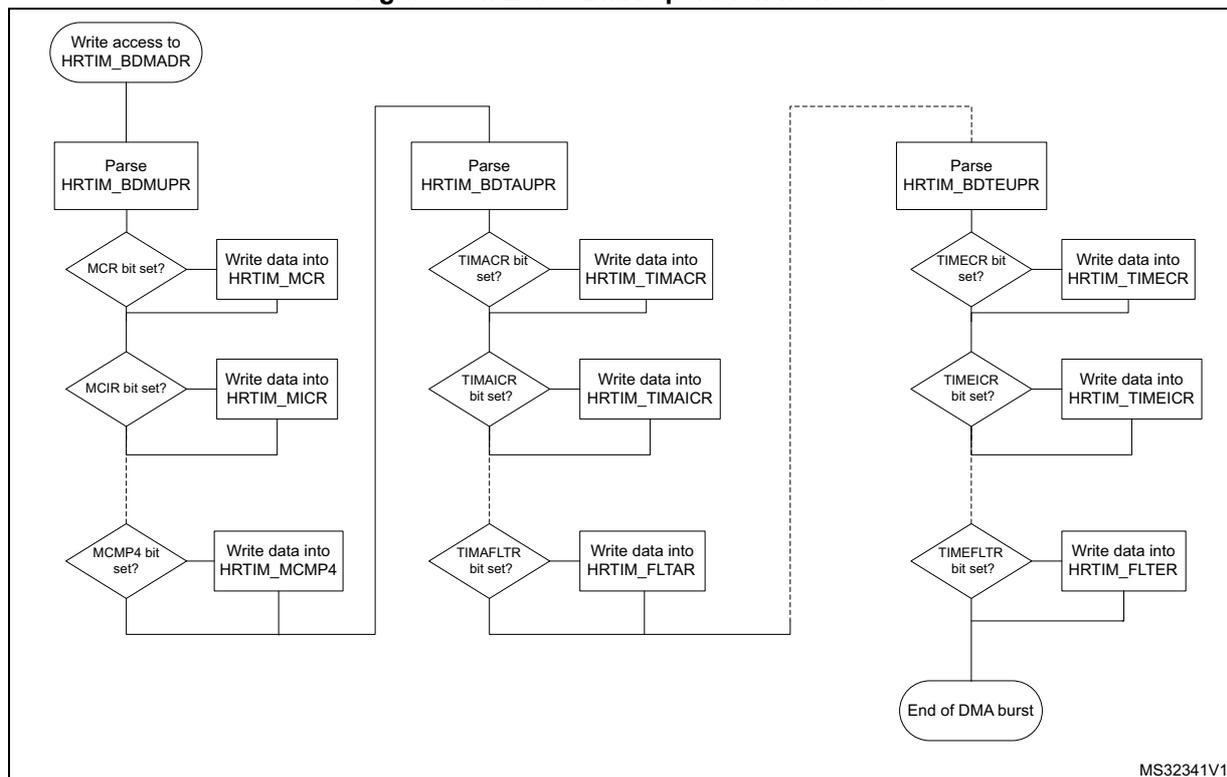

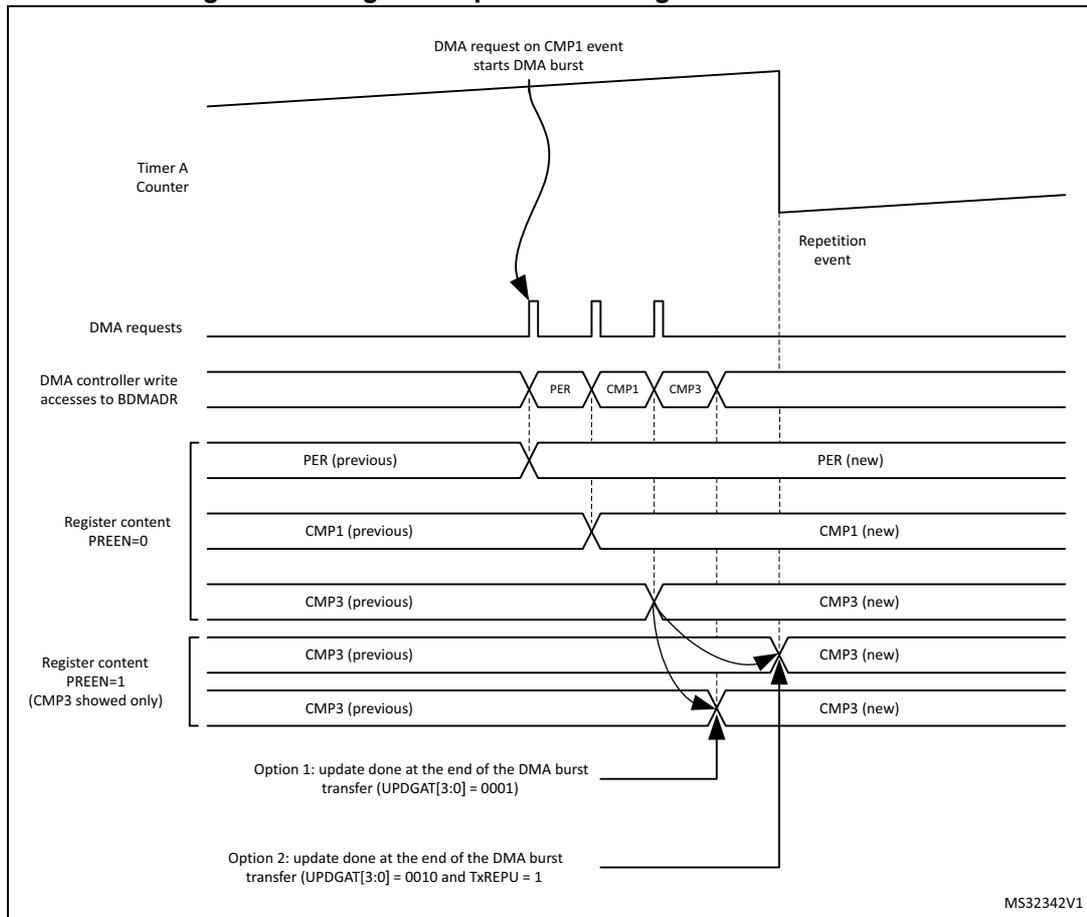

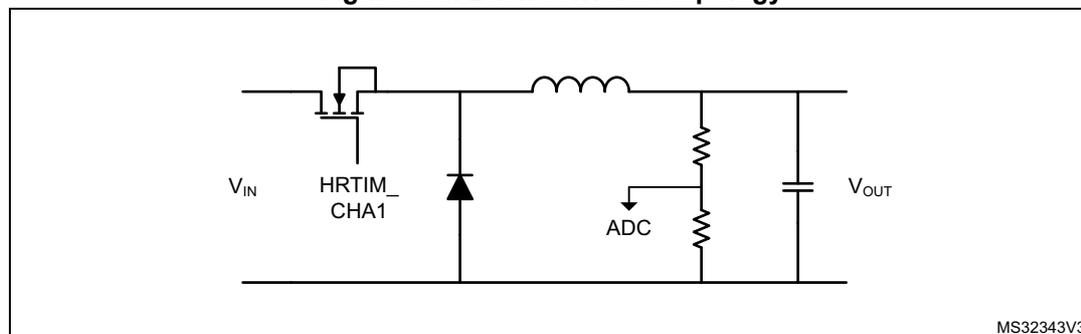

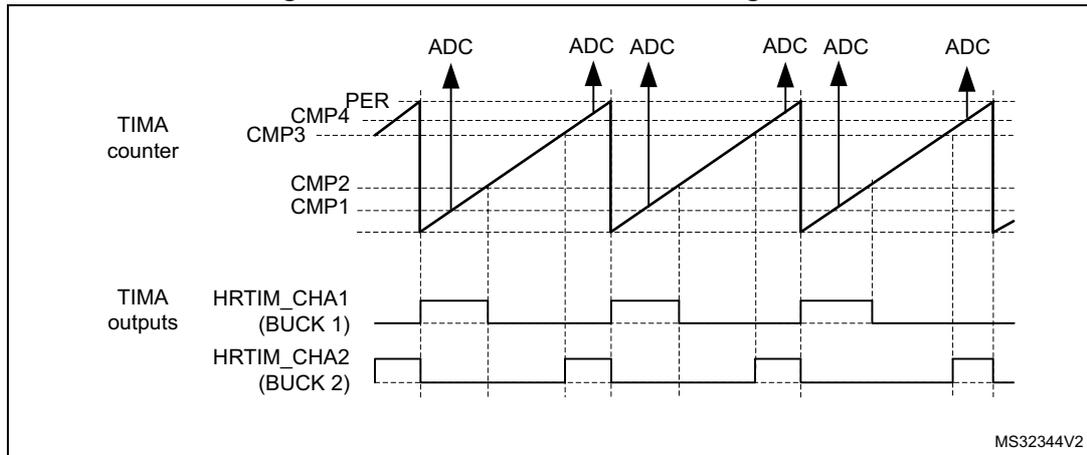

In this mode, the active pulse is completed before the protection is activated. The selected external event causes the output to enter in idle mode at the end of the active pulse (defined by an output reset event in HRTIM_RSTx1R or HRTIM_RSTx2R).