30. Digital filter for sigma delta modulators (DFSDM)

30.1 Introduction

Digital filter for sigma delta modulators (DFSDM) is a high-performance module dedicated to interface external \( \Sigma\Delta \) modulators. It is featuring up to 8 external digital serial interfaces (channels) and up to 4 digital filters with flexible Sigma Delta stream digital processing options to offer up to 24-bit final ADC resolution. DFSDM also features optional parallel data stream input from internal ADC peripherals or from device memory.

An external \( \Sigma\Delta \) modulator provides digital data stream of converted analog values from the external \( \Sigma\Delta \) modulator analog input. This digital data stream is sent into a DFSDM input channel through a serial interface. DFSDM supports several standards to connect various \( \Sigma\Delta \) modulator outputs: SPI interface and Manchester coded 1-wire interface (both with adjustable parameters). DFSDM module supports the connection of up to 8 multiplexed input digital serial channels which are shared with up to 4 DFSDM modules. DFSDM module also supports alternative parallel data inputs from up to 8 internal 16-bit data channels (from internal ADCs or from device memory).

DFSDM is converting an input data stream into a final digital data word which represents an analog input value on a \( \Sigma\Delta \) modulator analog input. The conversion is based on a configurable digital process: the digital filtering and decimation of the input serial data stream.

The conversion speed and resolution are adjustable according to configurable parameters for digital processing: filter type, filter order, length of filter, integrator length. The maximum output data resolution is up to 24 bits. There are two conversion modes: single conversion mode and continuous mode. The data can be automatically stored in a system RAM buffer through DMA, thus reducing the software overhead.

A flexible timer triggering system can be used to control the start of conversion of DFSDM. This timing control is capable of triggering simultaneous conversions or inserting a programmable delay between conversions.

DFSDM features an analog watchdog function. Analog watchdog can be assigned to any of the input channel data stream or to final output data. Analog watchdog has its own digital filtering of input data stream to reach the required speed and resolution of watched data.

To detect short-circuit in control applications, there is a short-circuit detector. This block watches each input channel data stream for occurrence of stable data for a defined time duration (several 0's or 1's in an input data stream).

An extremes detector block watches final output data and stores maximum and minimum values from the output data values. The extremes values stored can be restarted by software.

Two power modes are supported: normal mode and stop mode.

30.2 DFSDM main features

- • Up to 8 multiplexed input digital serial channels:

- – configurable SPI interface to connect various \( \Sigma\Delta \) modulators

- – configurable Manchester coded 1 wire interface support

- – clock output for \( \Sigma\Delta \) modulator(s)

- • Alternative inputs from up to 8 internal digital parallel channels:

- – inputs with up to 16 bit resolution

- – internal sources: ADCs data or memory (CPU/DMA write) data streams

- • Adjustable digital signal processing:

- – Sinc x filter: filter order/type (1..5), oversampling ratio (up to 1..1024)

- – integrator: oversampling ratio (1..256)

- • Up to 24-bit output data resolution:

- – right bit-shifter on final data (0..31 bits)

- • Signed output data format

- • Automatic data offset correction (offset stored in register by user)

- • Continuous or single conversion

- • Start-of-conversion synchronization with:

- – software trigger

- – internal timers

- – external events

- – start-of-conversion synchronously with first DFSDM filter (DFSDM_FLT0)

- • Analog watchdog feature:

- – low value and high value data threshold registers

- – own configurable Sinc x digital filter (order = 1..3, oversampling ratio = 1..32)

- – input from output data register or from one or more input digital serial channels

- – continuous monitoring independently from standard conversion

- • Short-circuit detector to detect saturated analog input values (bottom and top ranges):

- – up to 8-bit counter to detect 1..256 consecutive 0's or 1's on input data stream

- – monitoring continuously each channel (8 serial channel transceiver outputs)

- • Break generation on analog watchdog event or short-circuit detector event

- • Extremes detector:

- – store minimum and maximum values of output data values

- – refreshed by software

- • DMA may be used to read the conversion data

- • Interrupts: end of conversion, overrun, analog watchdog, short-circuit, channel clock absence

- • “regular” or “injected” conversions:

- – “regular” conversions can be requested at any time or even in continuous mode without having any impact on the timing of “injected” conversions

- – “injected” conversions for precise timing and with high conversion priority

30.3 DFSDM implementation

This section describes the configuration implemented in DFSDMx.

Table 247. DFSDM1 implementation

| DFSDM features | DFSDM1 |

|---|---|

| Number of channels | 8 |

| Number of filters | 4 |

| Input from internal ADC | X |

| Supported trigger sources | 32 (1) |

| Pulses skipper | - |

- 1. Refer to Table 250: DFSDM triggers connection for available trigger sources.

30.4 DFSDM functional description

30.4.1 DFSDM block diagram

Figure 229. Single DFSDM block diagram

![Figure 229. Single DFSDM block diagram. This block diagram illustrates the internal architecture of a DFSDM. At the top, an APB bus connects to a control unit and parallel input data registers (Sample 0 and Sample 1) for channels 0 and 7. These registers feed into a central Channel multiplexer. Below the multiplexer, four filter channels are shown (0, 1, 2, 3). Each channel consists of a Sinc* filter and an Integrator unit, with parameters for Filter order and Oversampling ratio. The output of the integrators goes to DFSDM data registers (0 and 3), which include a right bit-shift count and calibration data correction unit. These registers then connect to an APB bus via a Data output. The data from the registers also feeds into 8 watchdog filters and 8 watchdog comparators. Below this, there are 1's, 0's counter thresholds and Short circuit detectors (0 and 7). The Short circuit detectors have threshold and interrupt/break outputs. The watchdog comparators have High threshold and Low threshold settings, with Filter 0 config and Filter 3 config. They also have interrupt/break outputs. The Control unit at the bottom left contains Configuration registers and DMA, interrupt, break control, clock control. It generates Interrupts and events: 1) end of conversion, 2) analog watchdog, 3) short circuit detection, 4) overrun. It also connects to the Short circuit detectors and the watchdog comparators. The diagram also shows various input pins: EXTRG[1:0], CKOUT, DATIN0, CKIN0, DATIN7, CKIN7, and internal signals like Data in, Clock in, and Data output. The diagram is labeled MS35355V5.](/RM0433-STM32H742-743-753-750/16da89f5673e43efd969188695f556ad_img.jpg)

- 1. This example shows 4 DFSDM filters and 8 input channels (max. configuration).

30.4.2 DFSDM pins and internal signals

Table 248. DFSDM external pins

| Name | Signal Type | Remarks |

|---|---|---|

| VDD | Power supply | Digital power supply. |

| VSS | Power supply | Digital ground power supply. |

| CKIN[7:0] | Clock input | Clock signal provided from external \( \Sigma\Delta \) modulator. FT input. |

| DATIN[7:0] | Data input | Data signal provided from external \( \Sigma\Delta \) modulator. FT input. |

| CKOUT | Clock output | Clock output to provide clock signal into external \( \Sigma\Delta \) modulator. |

| EXTRG[1:0] | External trigger signal | Input trigger from two EXTI signals to start analog conversion (from GPIOs: EXTI11, EXTI15). |

Table 249. DFSDM internal signals

| Name | Signal Type | Remarks |

|---|---|---|

| dfsdm_jtrg[31:0] | Internal/external trigger signal | Input trigger from internal/external trigger sources in order to start analog conversion (from internal sources: synchronous input, from external sources: asynchronous input with synchronization). See Table 250 for details. |

| dfsdm_break[3:0] | break signal output | Break signals event generation from Analog watchdog or short-circuit detector |

| dfsdm_dma[3:0] | DMA request signal | DMA request signal from each DFSDM_FLTx (x=0..3): end of injected conversion event. |

| dfsdm_it[3:0] | Interrupt request signal | Interrupt signal for each DFSDM_FLTx (x=0..3) |

| dfsdm_dat_adc[15:0] | ADC input data | Up to 4 internal ADC data buses as parallel inputs. |

Table 250. DFSDM triggers connection

| Trigger name | Trigger source |

|---|---|

| dfsdm_jtrg0 | TIM1_TRGO |

| dfsdm_jtrg1 | TIM1_TRGO2 |

| dfsdm_jtrg2 | TIM8_TRGO |

| dfsdm_jtrg3 | TIM8_TRGO2 |

| dfsdm_jtrg4 | TIM3_TRGO |

| dfsdm_jtrg5 | TIM4_TRGO |

| dfsdm_jtrg6 | TIM16_OC1 |

| dfsdm_jtrg7 | TIM6_TRGO |

| dfsdm_jtrg8 | TIM7_TRGO |

| dfsdm_jtrg9 | HRTIM1_ADCTRG1 |

Table 250. DFSDM triggers connection (continued)

| Trigger name | Trigger source |

|---|---|

| dfsdm_jtrg10 | HRTIM1_ADCTRG3 |

| dfsdm_jtrg[23:11] | Reserved |

| dfsdm_jtrg24 | EXTI11 |

| dfsdm_jtrg25 | EXTI15 |

| dfsdm_jtrg26 | LPTIMER1 |

| dfsdm_jtrg27 | LPTIMER2 |

| dfsdm_jtrg28 | LPTIMER3 |

| dfsdm_jtrg[31:29] | Reserved |

Table 251. DFSDM break connection

| Break name | Break destination |

|---|---|

| dfsdm_break[0] | TIM1 break / TIM15 break |

| dfsdm_break[1] | TIM1 break2 / TIM16 break |

| dfsdm_break[2] | TIM8 break / TIM17 break |

| dfsdm_break[3] | TIM8 break2 |

30.4.3 DFSDM reset and clocks

DFSDM on-off control

The DFSDM interface is globally enabled by setting DFSDMEN=1 in the DFSDM_CH0CFGR1 register. Once DFSDM is globally enabled, all input channels (y=0..7) and digital filters DFSDM_FLTx (x=0..3) start to work if their enable bits are set (channel enable bit CHEN in DFSDM_CHyCFGR1 and DFSDM_FLTx enable bit DFEN in DFSDM_FLTxCR1).

Digital filter x DFSDM_FLTx (x=0..3) is enabled by setting DFEN=1 in the DFSDM_FLTxCR1 register. Once DFSDM_FLTx is enabled (DFEN=1), both Sinc x digital filter unit and integrator unit are reinitialized.

By clearing DFEN, any conversion which may be in progress is immediately stopped and DFSDM_FLTx is put into stop mode. All register settings remain unchanged except DFSDM_FLTxAWSR and DFSDM_FLTxISR (which are reset).

Channel y (y=0..7) is enabled by setting CHEN=1 in the DFSDM_CHyCFGR1 register. Once the channel is enabled, it receives serial data from the external \( \Sigma\Delta \) modulator or parallel internal data sources (ADCs or CPU/DMA wire from memory).

DFSDM must be globally disabled (by DFSDMEN=0 in DFSDM_CH0CFGR1) before stopping the system clock to enter in the STOP mode of the device.

DFSDM clocks

The internal DFSDM clock \( f_{\text{DFSDMCLK}} \) , which is used to drive the channel transceivers, digital processing blocks (digital filter, integrator) and next additional blocks (analog watchdog, short-circuit detector, extremes detector, control block) is generated by the RCC block and is derived from the system clock SYSCLK or peripheral clock PCLK2 (see Section 8.7.20: RCC domain 2 kernel clock configuration register (RCC_D2CCIP1R) ). The DFSDM clock is automatically stopped in stop mode (if DFEN = 0 for all DFSDM_FLTx, x=0..3).

The DFSDM serial channel transceivers can receive an external serial clock to sample an external serial data stream. The internal DFSDM clock must be at least 4 times faster than the external serial clock if standard SPI coding is used, and 6 times faster than the external serial clock if Manchester coding is used.

DFSDM can provide one external output clock signal to drive external \( \Sigma\Delta \) modulator(s) clock input(s). It is provided on CKOUT pin. This output clock signal must be in the range specified in given device datasheet and is derived from DFSDM clock or from audio clock (see CKOUTSRC bit in DFSDM_CH0CFGR1 register) by programmable divider in the range 2 - 256 (CKOUTDIV in DFSDM_CH0CFGR1 register). Audio clock source is SAI1 clock selected by SAI1SEL[1:0] field in RCC configuration (see Section 8.7.20: RCC domain 2 kernel clock configuration register (RCC_D2CCIP1R) ).

30.4.4 Serial channel transceivers

There are 8 multiplexed serial data channels which can be selected for conversion by each filter or Analog watchdog or Short-circuit detector. Those serial transceivers receive data stream from external \( \Sigma\Delta \) modulator. Data stream can be sent in SPI format or Manchester coded format (see SITP[1:0] bits in DFSDM_CHyCFGR1 register).

The channel is enabled for operation by setting CHEN=1 in DFSDM_CHyCFGR1 register.

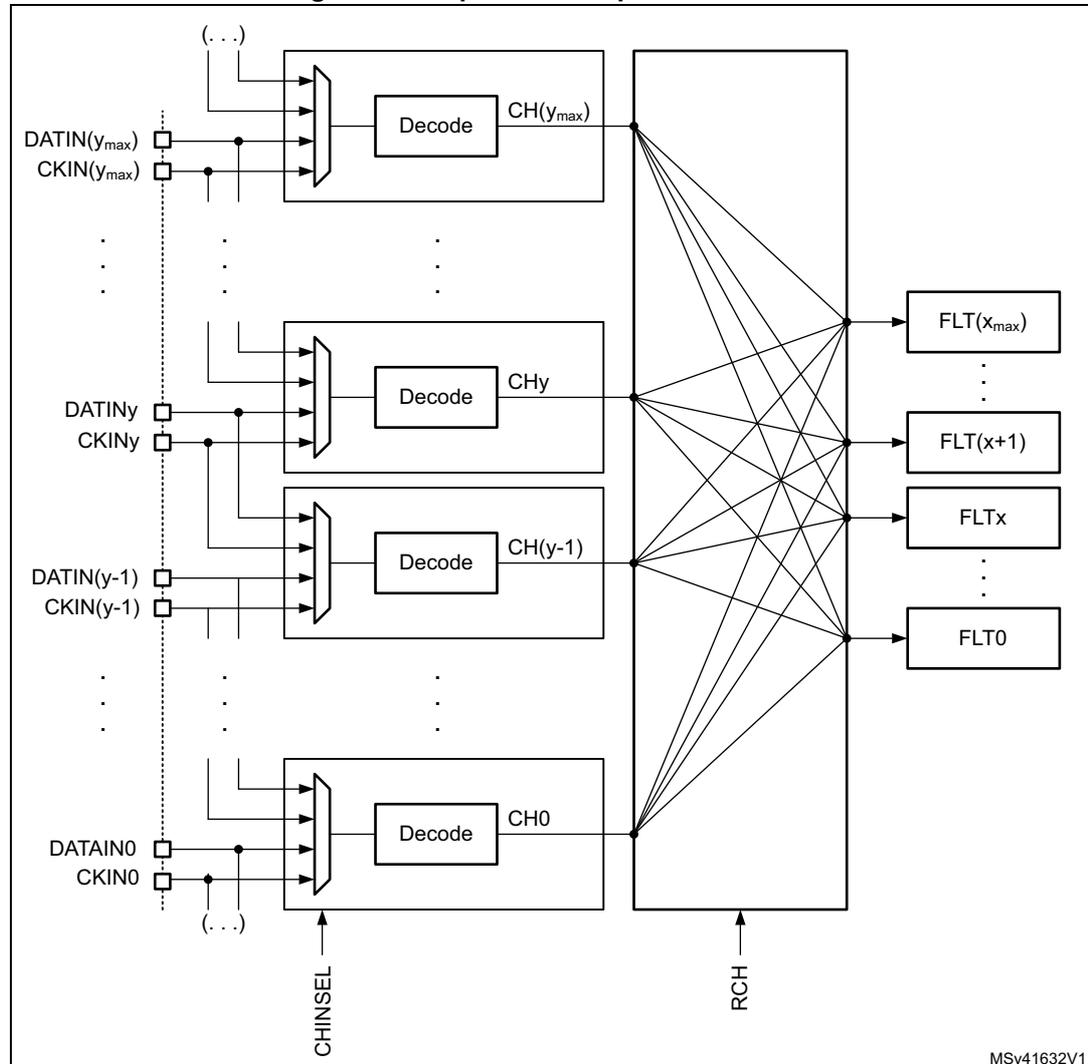

Channel inputs selection

Serial inputs (data and clock signals) from DATINy and CKINy pins can be redirected from the following channel pins. This serial input channel redirection is set by CHINSEL bit in DFSDM_CHyCFGR1 register.

Channel redirection can be used to collect audio data from PDM (pulse density modulation) stereo microphone type. PDM stereo microphone has one data and one clock signal. Data signal provides information for both left and right audio channel (rising clock edge samples for left channel and falling clock edge samples for right channel).

Configuration of serial channels for PDM microphone input:

- • PDM microphone signals (data, clock) will be connected to DFSDM input serial channel \( y \) (DATIN \( y \) , CKOUT) pins.

- • Channel \( y \) will be configured: CHINSEL = 0 (input from given channel pins: DATIN \( y \) , CKIN \( y \) ).

- • Channel \( (y-1) \) (modulo 8) will be configured: CHINSEL = 1 (input from the following channel \( ((y-1)+1) \) pins: DATIN \( y \) , CKIN \( y \) ).

- • Channel \( y \) : SITP[1:0] = 0 (rising edge to strobe data) => left audio channel on channel \( y \) .

- • Channel \( (y-1) \) : SITP[1:0] = 1 (falling edge to strobe data) => right audio channel on channel \( y-1 \) .

- • Two DFSDM filters will be assigned to channel \( y \) and channel \( (y-1) \) (to filter left and right channels from PDM microphone).

Figure 230. Input channel pins redirection

The diagram illustrates the internal architecture for input channel pin redirection in a DFSDM. On the left, multiple pairs of input pins are shown, labeled from top to bottom as DATIN \( (y_{max}) \) /CKIN \( (y_{max}) \) , DATIN \( y \) /CKIN \( y \) , DATIN \( (y-1) \) /CKIN \( (y-1) \) , and DATAIN0/CKIN0. Each pair is connected to a 'Decode' block. The 'Decode' blocks output signals labeled CH \( (y_{max}) \) , CH \( y \) , CH \( (y-1) \) , and CH0. These signals are then connected to a central switching matrix. The matrix is controlled by two inputs: CHINSEL and RCH. The outputs of the matrix are connected to a series of digital filters labeled FLT \( (x_{max}) \) , FLT \( (x+1) \) , FLTx, and FLT0. The diagram shows that the input pins are redirected through the matrix to the appropriate filters based on the configuration.

MSv41632V1

Output clock generation

A clock signal can be provided on CKOUT pin to drive external \( \Sigma\Delta \) modulator clock inputs. The frequency of this CKOUT signal is derived from DFSDM clock or from audio clock (see CKOUTSRC bit in DFSDM_CH0CFGR1 register) divided by a predivider (see CKOUTDIV bits in DFSDM_CH0CFGR1 register). If the output clock is stopped, then CKOUT signal is set to low state (output clock can be stopped by CKOUTDIV=0 in DFSDM_CHyCFGR1 register or by DFSDMEN=0 in DFSDM_CH0CFGR1 register). The output clock stopping is performed:

- • 4 system clocks after DFSDMEN is cleared (if CKOUTSRC=0)

- • 1 system clock and 3 audio clocks after DFSDMEN is cleared (if CKOUTSRC=1)

Before changing CKOUTSRC the software has to wait for CKOUT being stopped to avoid glitch on CKOUT pin. The output clock signal frequency must be in the range 0 - 20 MHz.

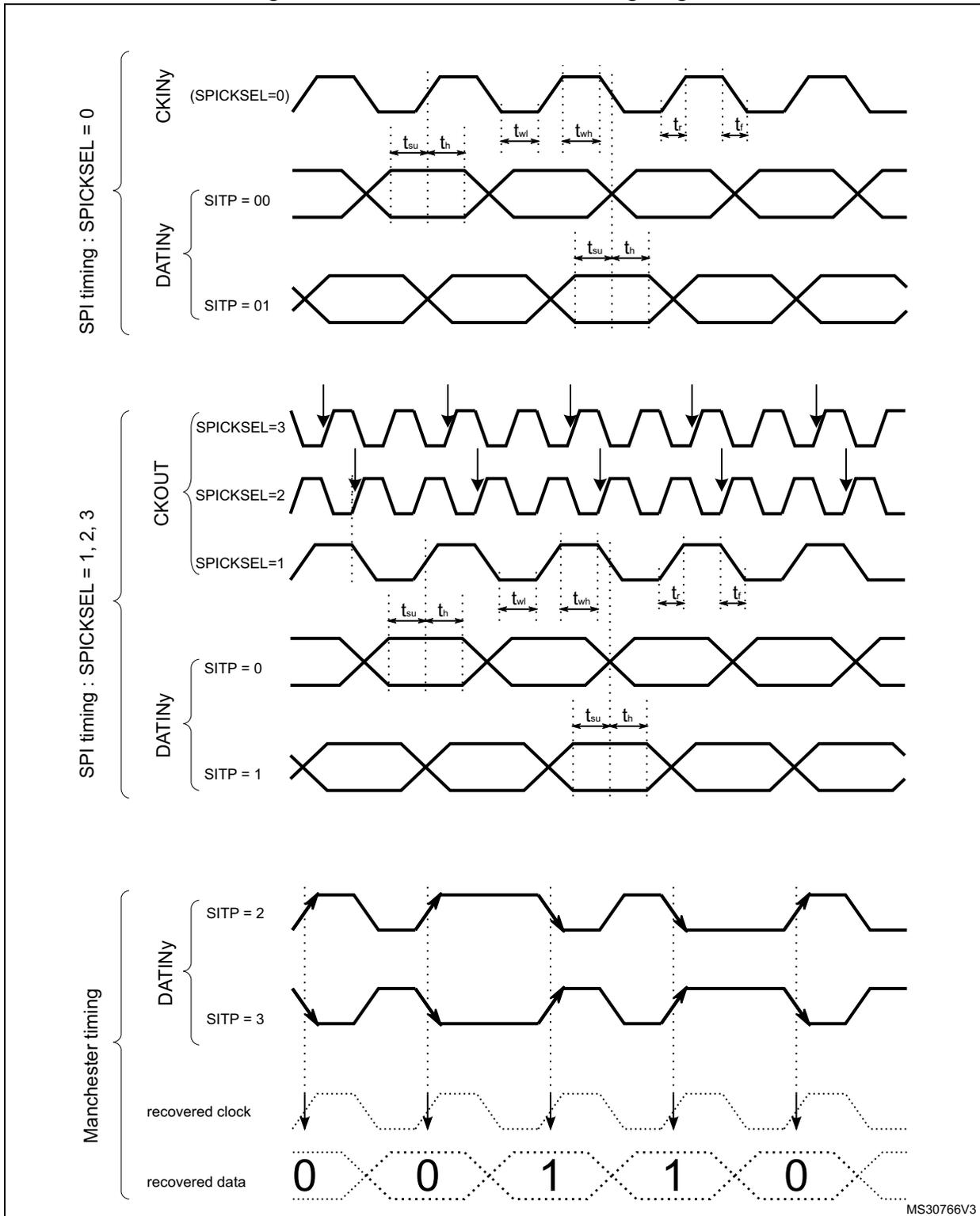

SPI data input format operation

In SPI format, the data stream is sent in serial format through data and clock signals. Data signal is always provided from DATINy pin. A clock signal can be provided externally from CKINy pin or internally from a signal derived from the CKOUT signal source.

In case of external clock source selection (SPICKSEL[1:0]=0) data signal (on DATINy pin) is sampled on rising or falling clock edge (of CKINy pin) according SITP[1:0] bits setting (in DFSDM_CHyCFGR1 register).

Internal clock sources - see SPICKSEL[1:0] in DFSDM_CHyCFGR1 register:

- • CKOUT signal:

- – For connection to external \( \Sigma\Delta \) modulator which uses directly its clock input (from CKOUT) to generate its output serial communication clock.

- – Sampling point: on rising/falling edge according SITP[1:0] setting.

- • CKOUT/2 signal (generated on CKOUT rising edge):

- – For connection to external \( \Sigma\Delta \) modulator which divides its clock input (from CKOUT) by 2 to generate its output serial communication clock (and this output clock change is active on each clock input rising edge).

- – Sampling point: on each second CKOUT falling edge.

- • CKOUT/2 signal (generated on CKOUT falling edge):

- – For connection to external \( \Sigma\Delta \) modulator which divides its clock input (from CKOUT) by 2 to generate its output serial communication clock (and this output clock change is active on each clock input falling edge).

- – Sampling point: on each second CKOUT rising edge.

Note: An internal clock source can only be used when the external \( \Sigma\Delta \) modulator uses CKOUT signal as a clock input (to have synchronous clock and data operation).

Internal clock source usage can save CKINy pin connection (CKINy pins can be used for other purpose).

The clock source signal frequency must be in the range 0 - 20 MHz for SPI coding and less than \( f_{\text{DFSDMCLK}}/4 \) .

Manchester coded data input format operation

In Manchester coded format, the data stream is sent in serial format through DATINy pin only. Decoded data and clock signal are recovered from serial stream after Manchester

decoding. There are two possible settings of Manchester codings (see SITP[1:0] bits in DFSDM_CHyCFGR1 register):

- • signal rising edge = log 0; signal falling edge = log 1

- • signal rising edge = log 1; signal falling edge = log 0

The recovered clock signal frequency for Manchester coding must be in the range 0 - 10 MHz and less than \( f_{\text{DFSDMCLK}}/6 \) .

To correctly receive Manchester coded data, the CKOUTDIV divider (in DFSDM_CH0CFGR1 register) must be set with respect to expected Manchester data rate according formula:

Figure 231. Channel transceiver timing diagrams

The figure illustrates timing diagrams for three main configurations:

SPI timing : SPICKSEL = 0

- CKINy (SPICKSEL=0): Input clock signal.

- DATINy

:

- SITP = 00: Data input signal.

- SITP = 01: Inverted data input signal.

- Timing parameters: \( t_{su} \) (setup time), \( t_h \) (hold time), \( t_{wl} \) (low pulse width), \( t_{wh} \) (high pulse width), \( t_r \) (rise time), \( t_f \) (fall time).

SPI timing : SPICKSEL = 1, 2, 3

- CKOUT

:

- SPICKSEL=3: Output clock signal with specific phase/polarity.

- SPICKSEL=2: Output clock signal with specific phase/polarity.

- SPICKSEL=1: Output clock signal with specific phase/polarity.

- DATINy

:

- SITP = 0: Data input signal.

- SITP = 1: Inverted data input signal.

- Timing parameters: \( t_{su} \) , \( t_h \) , \( t_{wl} \) , \( t_{wh} \) , \( t_r \) , \( t_f \) .

Manchester timing

- DATINy

:

- SITP = 2: Manchester encoded data input.

- SITP = 3: Inverted Manchester encoded data input.

- recovered clock : Clock signal extracted from the Manchester data.

- recovered data : Decoded bit sequence: 0, 0, 1, 1, 0.

MS30766V3

Clock absence detection

Channels serial clock inputs can be checked for clock absence/presence to ensure the correct operation of conversion and error reporting. Clock absence detection can be enabled or disabled on each input channel y by bit CKABEN in DFSDM_CHyCFGR1 register. If enabled, then this clock absence detection is performed continuously on a given channel. A clock absence flag is set (CKABF[y] = 1) and an interrupt can be invoked (if CKABIE=1) in case of an input clock error (see CKABF[7:0] in DFSDM_FLT0ISR register and CKABEN in DFSDM_CHyCFGR1). After a clock absence flag clearing (by CLRCKABF in DFSDM_FLT0ICR register), the clock absence flag is refreshed. Clock absence status bit CKABF[y] is set also by hardware when corresponding channel y is disabled (if CHEN[y] = 0 then CKABF[y] is held in set state).

When a clock absence event has occurred, the data conversion (and/or analog watchdog and short-circuit detector) provides incorrect data. The user should manage this event and discard given data while a clock absence is reported.

The clock absence feature is available only when the system clock is used for the CKOUT signal (CKOUTSRC=0 in DFSDM_CH0CFGR1 register).

When the transceiver is not yet synchronized, the clock absence flag is set and cannot be cleared by CLRCKABF[y] bit (in DFSDM_FLT0ICR register). The software sequence concerning clock absence detection feature should be:

- • Enable given channel by CHEN = 1

- • Try to clear the clock absence flag (by CLRCKABF = 1) until the clock absence flag is really cleared (CKABF = 0). At this time, the transceiver is synchronized (signal clock is valid) and is able to receive data.

- • Enable the clock absence feature CKABEN = 1 and the associated interrupt CKABIE = 1 to detect if the SPI clock is lost or Manchester data edges are missing.

If SPI data format is used, then the clock absence detection is based on the comparison of an external input clock with an output clock generation (CKOUT signal). The external input clock signal into the input channel must be changed at least once per 8 signal periods of CKOUT signal (which is controlled by CKOUTDIV field in DFSDM_CH0CFGR1 register).

Figure 232. Clock absence timing diagram for SPI

![Timing diagram for SPI clock absence detection. The diagram shows three signals: CKOUT (output clock), CKINy (input clock), and CKABF[y] (clock absence flag). CKOUT is a periodic square wave with periods labeled 2, 0, 1, 2, 3, 4, 5, 6, 7, 0. CKINy is a signal that is initially high and then goes low. A bracket on the left labeled 'SPI clock presence timing' groups CKOUT and CKINy. A horizontal double-headed arrow labeled 'max. 8 periods' spans from the first falling edge of CKOUT to the falling edge of CKINy. A dashed line labeled 'restart counting' points to the first falling edge of CKOUT. A dashed line labeled 'last clock change' points to the falling edge of CKINy. CKABF[y] is initially low and goes high at the falling edge of CKINy, labeled 'error reported'. The diagram is labeled MS30767V2.](/RM0433-STM32H742-743-753-750/595dd900916fdb33a8b5d09c1081159b_img.jpg)

If Manchester data format is used, then the clock absence means that the clock recovery is unable to perform from Manchester coded signal. For a correct clock recovery, it is first necessary to receive data with 1 to 0 or 0 to 1 transition (see Figure 234 for Manchester synchronization).

The detection of a clock absence in Manchester coding (after a first successful synchronization) is based on changes comparison of coded serial data input signal with output clock generation (CKOUT signal). There must be a voltage level change on DATINy pin during 2 periods of CKOUT signal (which is controlled by CKOUTDIV bits in DFSDM_CH0CFGR1 register). This condition also defines the minimum data rate to be able to correctly recover the Manchester coded data and clock signals.

The maximum data rate of Manchester coded data must be less than the CKOUT signal.

So to correctly receive Manchester coded data, the CKOUTDIV divider must be set according the formula:

A clock absence flag is set (CKABF[y] = 1) and an interrupt can be invoked (if CKABIE=1) in case of an input clock recovery error (see CKABF[7:0] in DFSDM_FLT0ISR register and CKABEN in DFSDM_CHyCFGR1). After a clock absence flag clearing (by CLRCKABF in DFSDM_FLT0ICR register), the clock absence flag is refreshed.

Figure 233. Clock absence timing diagram for Manchester coding

![Timing diagram for Manchester coding clock absence detection. The diagram shows five waveforms: CKOUT (output clock), DATINy (input data, with SITP=2 and SITP=3 paths), recovered clock, recovered data, and CKABF[y] (clock absence flag). CKOUT is a square wave with bits 0, 0, 0, 1, 0. DATINy shows Manchester-coded data. The recovered clock is derived from the data transitions. The recovered data shows bits 0, 0, 1, ?, ?. The CKABF[y] flag is low until a clock absence is detected, at which point it goes high, labeled 'error reported'. A 'max. 2 periods' timer is shown starting from the last data change. A 'restart counting' label is present near the third bit of CKOUT.](/RM0433-STM32H742-743-753-750/af0c5c71725814250ae26b2b186ad9e9_img.jpg)

Manchester/SPI code synchronization

The Manchester coded stream must be synchronized the first time after enabling the channel (CHEN=1 in DFSDM_CHyCFGR1 register). The synchronization ends when a data transition from 0 to 1 or from 1 to 0 (to be able to detect valid data edge) is received. The end of the synchronization can be checked by polling CKABF[y]=0 for a given channel after it has been cleared by CLRCKABF[y] in DFSDM_FLT0ICR, following the software sequence detailed hereafter:

CKABF[y] flag is cleared by setting CLRCKABF[y] bit. If channel y is not yet synchronized the hardware immediately set the CKABF[y] flag. Software is then reading back the CKABF[y] flag and if it is set then perform again clearing of this flag by setting CLRCKABF[y] bit. This software sequence (polling of CKABF[y] flag) continues until CKABF[y] flag is set (signalizing that Manchester stream is synchronized). To be able to synchronize/receive Manchester coded data the CKOUTDIV divider (in DFSDM_CH0CFGR1 register) must be set with respect to expected Manchester data rate according the formula below.

SPI coded stream is synchronized after first detection of clock input signal (valid rising/falling edge).

Note: When the transceiver is not yet synchronized, the clock absence flag is set and cannot be cleared by CLRCKABF[y] bit (in DFSDM_FLT0ICR register).

Figure 234. First conversion for Manchester coding (Manchester synchronization)

![Timing diagram for Manchester coding synchronization showing DATINy, recovered clock, data from modulator, CHEN, first conversion start trigger, recovered data, and CKABF[y] signals.](/RM0433-STM32H742-743-753-750/abe6145074c27d1a064c2abf5f3fa303_img.jpg)

The figure is a timing diagram illustrating the first conversion for Manchester coding. It consists of several signal traces:

- Manchester timing:

A bracket on the left groups the top two traces.

- DATINy: Two traces labeled SITP = 2 and SITP = 3 , showing Manchester-coded signals.

- recovered clock: A trace showing the clock signal recovered from the Manchester data.

- data from modulator: A trace showing the raw data bits: 0, 0, 1, 1, 0.

- CHEN: A signal line that goes high at the first conversion start trigger and returns low at the clearing of CKABF[y] flag by software polling .

- first conversion start trigger: A pulse that initiates the conversion.

- recovered data: A trace showing the data bits after conversion: ?, ?, 1, 1, 0. The first two bits are unknown due to synchronization issues.

- CKABF[y]: A flag signal that goes high when the conversion starts and is cleared by software.

Key timing points and annotations:

- real start of first conversion: Indicated by an arrow pointing to the rising edge of the recovered clock corresponding to the first '1' bit.

- first data bit toggle - end of Manchester synchronization: Indicated by an arrow pointing to the transition between the first and second bits.

- clearing of CKABF[y] flag by software polling: Indicated by a dashed line showing the software action to clear the flag.

Reference code: MS30769V2

External serial clock frequency measurement

The measuring of a channel serial clock input frequency provides a real data rate from an external \( \Sigma\Delta \) modulator, which is important for application purposes.

An external serial clock input frequency can be measured by a timer counting DFSDM clocks ( \( f_{\text{DFSDMCLK}} \) ) during one conversion duration. The counting starts at the first input data clock after a conversion trigger (regular or injected) and finishes by last input data clock before conversion ends (end of conversion flag is set). Each conversion duration (time between first serial sample and last serial sample) is updated in counter CNVCNT[27:0] in register DFSDM_FLTxCNVTIMR when the conversion finishes (JEOCF=1 or REOCF=1). The user can then compute the data rate according to the digital filter settings (FORD, FOSR, IOSR, FAST). The external serial frequency measurement is stopped only if the filter is bypassed (FOSR=0, only integrator is active, CNVCNT[27:0]=0 in DFSDM_FLTxCNVTIMR register).

In case of parallel data input ( Section 30.4.6: Parallel data inputs ) the measured frequency is the average input data rate during one conversion.

Note: When conversion is interrupted (e.g. by disabling/enabling the selected channel) the interruption time is also counted in CNVCNT[27:0]. Therefore it is recommended to not interrupt the conversion for correct conversion duration result.

Conversion times:

injected conversion or regular conversion with FAST = 0 (or first conversion if FAST=1):

for Sinc x filters (x=1..5):

for FastSinc filter:

regular conversion with FAST = 1 (except first conversion):

for Sinc x and FastSinc filters:

in case if \( F_{\text{OSR}} = F_{\text{OSR}}[9:0]+1 = 1 \) (filter bypassed, active only integrator):

where:

- • \( f_{\text{CKIN}} \) is the channel input clock frequency (on given channel CKINy pin) or input data rate (in case of parallel data input)

- • \( F_{\text{OSR}} \) is the filter oversampling ratio: \( F_{\text{OSR}} = F_{\text{OSR}}[9:0]+1 \) (see DFSDM_FLTxFCR register)

- • \( I_{\text{OSR}} \) is the integrator oversampling ratio: \( I_{\text{OSR}} = I_{\text{OSR}}[7:0]+1 \) (see DFSDM_FLTxFCR register)

- • \( F_{\text{ORD}} \) is the filter order: \( F_{\text{ORD}} = F_{\text{ORD}}[2:0] \) (see DFSDM_FLTxFCR register)

Channel offset setting

Each channel has its own offset setting (in register) which is finally subtracted from each conversion result (injected or regular) from a given channel. Offset correction is performed after the data right bit shift. The offset is stored as a 24-bit signed value in OFFSET[23:0] field in DFSDM_CHyCFGR2 register.

Data right bit shift

To have the result aligned to a 24-bit value, each channel defines a number of right bit shifts which will be applied on each conversion result (injected or regular) from a given channel. The data bit shift number is stored in DTRBS[4:0] bits in DFSDM_CHyCFGR2 register.

The right bit-shift is rounding the result to nearest integer value. The sign of shifted result is maintained, in order to have valid 24-bit signed format of result data.

30.4.5 Configuring the input serial interface

The following parameters must be configured for the input serial interface:

- • Output clock predivider. There is a programmable predivider to generate the output clock from DFSDM clock (2 - 256). It is defined by CKOUTDIV[7:0] bits in DFSDM_CH0CFGR1 register.

- • Serial interface type and input clock phase. Selection of SPI or Manchester coding and sampling edge of input clock. It is defined by SITP [1:0] bits in DFSDM_CHyCFGR1 register.

- • Input clock source. External source from CKINy pin or internal from CKOUT pin. It is defined by SPICKSEL[1:0] field in DFSDM_CHyCFGR1 register.

- • Final data right bit-shift. Defines the final data right bit shift to have the result aligned to a 24-bit value. It is defined by DTRBS[4:0] in DFSDM_CHyCFGR2 register.

- • Channel offset per channel. Defines the analog offset of a given serial channel (offset of connected external \( \Sigma\Delta \) modulator). It is defined by OFFSET[23:0] bits in DFSDM_CHyCFGR2 register.

- • short-circuit detector and clock absence per channel enable. To enable or disable the short-circuit detector (by SCDEN bit) and the clock absence monitoring (by CKABEN bit) on a given serial channel in register DFSDM_CHyCFGR1.

- • Analog watchdog filter and short-circuit detector threshold settings. To configure channel analog watchdog filter parameters and channel short-circuit detector parameters. Configurations are defined in DFSDM_CHyAWSCDR register.

30.4.6 Parallel data inputs

Each input channel provides a register for 16-bit parallel data input (besides serial data input). Each 16-bit parallel input can be sourced from internal data sources only:

- • internal ADC results

- • direct CPU/DMA writing.

The selection for using serial or parallel data input for a given channel is done by field DATMPX[1:0] of DFSDM_CHyCFGR1 register. In DATMPX[1:0] is also defined the parallel data source: internal ADC or direct write by CPU/DMA.

Each channel contains a 32-bit data input register DFSDM_CHyDATINR in which it can be written a 16-bit data. Data are in 16-bit signed format. Those data can be used as input to the digital filter which is accepting 16-bit parallel data.

If serial data input is selected (DATMPX[1:0] = 0), the DFSDM_CHyDATINR register is write protected.

Input from internal ADC

In case of ADC data parallel input (DATMPX[1:0]=1) the ADC[y+1] result is assigned to channel y input (ADC1 is filling DFSDM_CHDATIN0R register, ADC2 is filling DFSDM_CHDATIN1R register, ... , ADC8 is filling DFSDM_CHDATIN7R register). End of conversion event from ADC[y+1] causes update of channel y data (parallel data from ADC[y+1] are put as next sample to digital filter). Data from ADC[y+1] is written into DFSDM_CHyDATINR register (field INDAT0[15:0]) when end of conversion event occurred.

The setting of data packing mode (DATPACK[1:0] in the DFSDM_CHyCFGR1 register) has no effect in case of ADC data input.

Note: Extension of ADC specification: in case the internal ADC is configured in interleaved mode (e.g. ADC1 together with ADC2 - see ADC specification) then each result from ADC1 or from ADC2 will come to the same 16-bit bus - to the bus of ADC1 - which is coming into DFSDM channel 0 (fixed connection). So there will be double input data rate into DFSDM channel 0 (even samples come from ADC1 and odd samples from ADC2). Channel 1 associated with ADC2 will be free.

Input from memory (direct CPU/DMA write)

The direct data write into DFSDM_CHyDATINR register by CPU or DMA (DATMPX[1:0]=2) can be used as data input in order to process digital data streams from memory or peripherals.

Data can be written by CPU or DMA into DFSDM_CHyDATINR register:

1. CPU data write:

Input data are written directly by CPU into DFSDM_CHyDATINR register.

2. DMA data write:

The DMA should be configured in memory-to-memory transfer mode to transfer data from memory buffer into DFSDM_CHyDATINR register. The destination memory address is the address of DFSDM_CHyDATINR register. Data are transferred at DMA transfer speed from memory to DFSDM parallel input.

This DMA transfer is different from DMA used to read DFSDM conversion results. Both DMA can be used at the same time - first DMA (configured as memory-to-memory transfer) for input data writings and second DMA (configured as peripheral-to-memory transfer) for data results reading.

The accesses to DFSDM_CHyDATINR can be either 16-bit or 32-bit wide, allowing to load respectively one or two samples in one write operation. 32-bit input data register (DFSDM_CHyDATINR) can be filled with one or two 16-bit data samples, depending on the data packing operation mode defined in field DATPACK[1:0] of DFSDM_CHyCFGR1 register:

1. Standard mode (DATPACK[1:0]=0):

Only one sample is stored in field INDAT0[15:0] of DFSDM_CHyDATINR register which is used as input data for channel y. The upper 16 bits (INDAT1[15:0]) are ignored and write protected. The digital filter must perform one input sampling (from INDAT0[15:0]) to empty data register after it has been filled by CPU/DMA. This mode is used together with 16-bit CPU/DMA access to DFSDM_CHyDATINR register to load one sample per write operation.

2. Interleaved mode (DATPACK[1:0]=1):

DFSDM_CHyDATINR register is used as a two sample buffer. The first sample is stored in INDAT0[15:0] and the second sample is stored in INDAT1[15:0]. The digital filter must perform two input samplings from channel y to empty DFSDM_CHyDATINR register. This mode is used together with 32-bit CPU/DMA access to DFSDM_CHyDATINR register to load two samples per write operation.

3. Dual mode (DATPACK[1:0]=2):

Two samples are written into DFSDM_CHyDATINR register. The data INDAT0[15:0] is for channel y, the data in INDAT1[15:0] is for channel y+1. The data in INDAT1[15:0] is automatically copied INDAT0[15:0] of the following (y+1) channel data register (DFSDM_CH[y+1]DATINR). The digital filters must perform two samplings - one from

channel y and one from channel (y+1) - in order to empty DFSDM_CHyDATINR registers.

Dual mode setting (DATPACK[1:0]=2) is available only on even channel numbers (y = 0, 2, 4, 6). If odd channel (y = 1, 3, 5, 7) is set to Dual mode then both INDAT0[15:0] and INDAT1[15:0] parts are write protected for this channel. If even channel is set to Dual mode then the following odd channel must be set into Standard mode (DATPACK[1:0]=0) for correct cooperation with even channels.

See Figure 235 for DFSDM_CHyDATINR registers data modes and assignments of data samples to channels.

Figure 235. DFSDM_CHyDATINR registers operation modes and assignment

| Standard mode | Interleaved mode | Dual mode | ||||

|---|---|---|---|---|---|---|

| 31 | 16 15 0 | 31 | 16 15 0 | 31 | 16 15 0 | |

| Unused | Ch0 (sample 0) | Ch0 (sample 1) | Ch0 (sample 0) | Ch1 (sample 0) | Ch0 (sample 0) | y = 0 |

| Unused | Ch1 (sample 0) | Ch1 (sample 1) | Ch1 (sample 0) | Unused | Ch1 (sample 0) | y = 1 |

| Unused | Ch2 (sample 0) | Ch2 (sample 1) | Ch2 (sample 0) | Ch3 (sample 0) | Ch2 (sample 0) | y = 2 |

| Unused | Ch3 (sample 0) | Ch3 (sample 1) | Ch3 (sample 0) | Unused | Ch3 (sample 0) | y = 3 |

| Unused | Ch4 (sample 0) | Ch4 (sample 1) | Ch4 (sample 0) | Ch5 (sample 0) | Ch4 (sample 0) | y = 4 |

| Unused | Ch5 (sample 0) | Ch5 (sample 1) | Ch5 (sample 0) | Unused | Ch5 (sample 0) | y = 5 |

| Unused | Ch6 (sample 0) | Ch6 (sample 1) | Ch6 (sample 0) | Ch7 (sample 0) | Ch6 (sample 0) | y = 6 |

| Unused | Ch7 (sample 0) | Ch7 (sample 1) | Ch7 (sample 0) | Unused | Ch7 (sample 0) | y = 7 |

MS35354V3

The write into DFSDM_CHyDATINR register to load one or two samples must be performed after the selected input channel (channel y) is enabled for data collection (starting conversion for channel y). Otherwise written data are lost for next processing.

For example: for single conversion and interleaved mode, do not start writing pair of data samples into DFSDM_CHyDATINR before the single conversion is started (any data present in the DFSDM_CHyDATINR before starting a conversion is discarded).

30.4.7 Channel selection

There are 8 multiplexed channels which can be selected for conversion using the injected channel group and/or using the regular channel.

The injected channel group is a selection of any or all of the 8 channels. JCHG[7:0] in the DFSDM_FLTxJCHGR register selects the channels of the injected group, where JCHG[y]=1 means that channel y is selected.

Injected conversions can operate in scan mode (JSCAN=1) or single mode (JSCAN=0). In scan mode, each of the selected channels is converted, one after another. The lowest channel (channel 0, if selected) is converted first, followed immediately by the next higher channel until all the channels selected by JCHG[7:0] have been converted. In single mode (JSCAN=0), only one channel from the selected channels is converted, and the channel selection is moved to the next channel. Writing to JCHG[7:0] if JSCAN=0 resets the channel selection to the lowest selected channel.

Injected conversions can be launched by software or by a trigger. They are never interrupted by regular conversions.

The regular channel is a selection of just one of the 8 channels. RCH[2:0] in the DFSDM_FLTxCR1 register indicates the selected channel.

Regular conversions can be launched only by software (not by a trigger). A sequence of continuous regular conversions is temporarily interrupted when an injected conversion is requested.

Performing a conversion on a disabled channel (CHEN=0 in DFSDM_CHyCFGR1 register) causes that the conversion will never end - because no input data is provided (with no clock signal). In this case, it is necessary to enable a given channel (CHEN=1 in DFSDM_CHyCFGR1 register) or to stop the conversion by DFEN=0 in DFSDM_FLTxCR1 register.

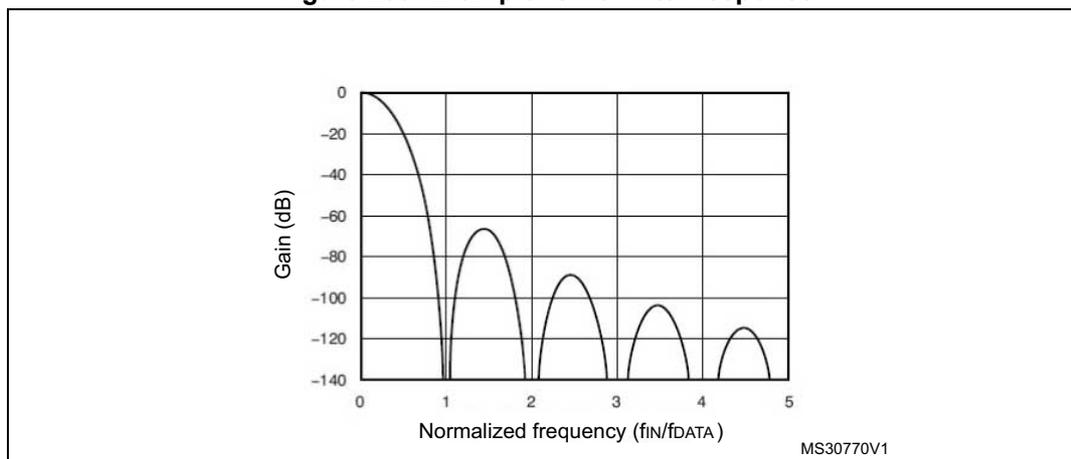

30.4.8 Digital filter configuration

DFSDM contains a Sinc x type digital filter implementation. This Sinc x filter performs an input digital data stream filtering, which results in decreasing the output data rate (decimation) and increasing the output data resolution. The Sinc x digital filter is configurable in order to reach the required output data rates and required output data resolution. The configurable parameters are:

- • Filter order/type: (see FORD[2:0] bits in DFSDM_FLTxFCR register):

- – FastSinc

- – Sinc 1

- – Sinc 2

- – Sinc 3

- – Sinc 4

- – Sinc 5

- • Filter oversampling/decimation ratio (see FOSR[9:0] bits in DFSDM_FLTxFCR register):

- – FOSR = 1-1024 - for FastSinc filter and Sinc x filter x = F ORD = 1..3

- – FOSR = 1-215 - for Sinc x filter x = F ORD = 4

- – FOSR = 1-73 - for Sinc x filter x = F ORD = 5

The filter has the following transfer function (impulse response in H domain):

- • Sinc

x

filter type:\[ H(z) = \left( \frac{1 - z^{-FOSR}}{1 - z^{-1}} \right)^x \]

- • FastSinc filter type:\[ H(z) = \left( \frac{1 - z^{-FOSR}}{1 - z^{-1}} \right)^2 \cdot (1 + z^{-(2 \cdot FOSR)}) \]

Table 252. Filter maximum output resolution (peak data values from filter output) for some FOSR values

| FOSR | Sinc 1 | Sinc 2 | FastSinc | Sinc 3 | Sinc 4 | Sinc 5 |

|---|---|---|---|---|---|---|

| x | +/- x | +/- x 2 | +/- 2x 2 | +/- x 3 | +/- x 4 | +/- x 5 |

| 4 | +/- 4 | +/- 16 | +/- 32 | +/- 64 | +/- 256 | +/- 1024 |

| 8 | +/- 8 | +/- 64 | +/- 128 | +/- 512 | +/- 4096 | - |

| 32 | +/- 32 | +/- 1024 | +/- 2048 | +/- 32768 | +/- 1048576 | +/- 33554432 |

| 64 | +/- 64 | +/- 4096 | +/- 8192 | +/- 262144 | +/- 16777216 | +/- 1073741824 |

| 128 | +/- 128 | +/- 16384 | +/- 32768 | +/- 2097152 | +/- 268435456 | |

| 256 | +/- 256 | +/- 65536 | +/- 131072 | +/- 16777216 | Result can overflow on full scale input (> 32-bit signed integer) | |

| 1024 | +/- 1024 | +/- 1048576 | +/- 2097152 | +/- 1073741824 | ||

For more information about Sinc filter type properties and usage, it is recommended to study the theory about digital filters (more resources can be downloaded from internet).

30.4.9 Integrator unit

The integrator performs additional decimation and a resolution increase of data coming from the digital filter. The integrator simply performs the sum of data from a digital filter for a given number of data samples from a filter.

The integrator oversampling ratio parameter defines how many data counts will be summed to one data output from the integrator. IOSR can be set in the range 1-256 (see IOSR[7:0] bits description in DFSDM_FLTxFCR register).

Table 253. Integrator maximum output resolution (peak data values from integrator output) for some IOSR values and FOSR = 256 and Sinc 3 filter type (largest data)| IOSR | Sinc 1 | Sinc 2 | FastSinc | Sinc 3 | Sinc 4 | Sinc 5 |

|---|---|---|---|---|---|---|

| x | +/- FOSR. x | +/- FOSR 2 . x | +/- 2.FOSR 2 . x | +/- FOSR 3 . x | +/- FOSR 4 . x | +/- FOSR 5 . x |

| 4 | - | - | - | +/- 67 108 864 | - | - |

| 32 | - | - | - | +/- 536 870 912 | - | - |

| 128 | - | - | - | +/- 2 147 483 648 | - | - |

| 256 | - | - | - | +/- 2 32 | - | - |

30.4.10 Analog watchdog

The analog watchdog purpose is to trigger an external signal (break or interrupt) when an analog signal reaches or crosses given maximum and minimum threshold values. An interrupt/event/break generation can then be invoked.

Each analog watchdog will supervise serial data receiver outputs (after the analog watchdog filter on each channel) or data output register (current injected or regular conversion result) according to AWFSEL bit setting (in DFSDM_FLTxCR1 register). The input channels to be monitored or not by the analog watchdog x will be selected by AWDCH[7:0] in DFSDM_FLTxCR2 register.

Analog watchdog conversions on input channels are independent from standard conversions. In this case, the analog watchdog uses its own filters and signal processing on each input channel independently from the main injected or regular conversions. Analog watchdog conversions are performed in a continuous mode on the selected input channels in order to watch channels also when main injected or regular conversions are paused (RCIP = 0, JCIP = 0).

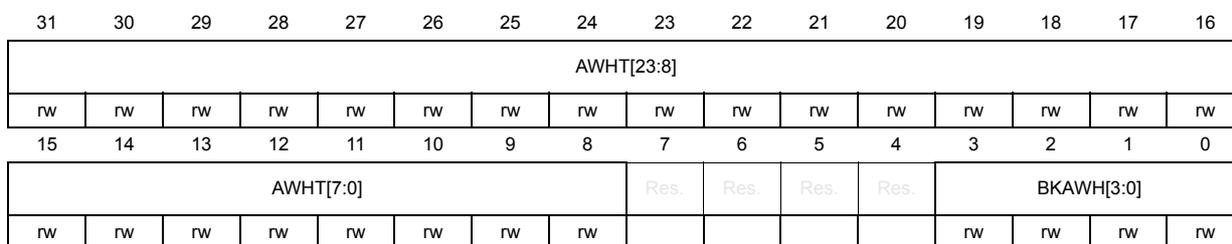

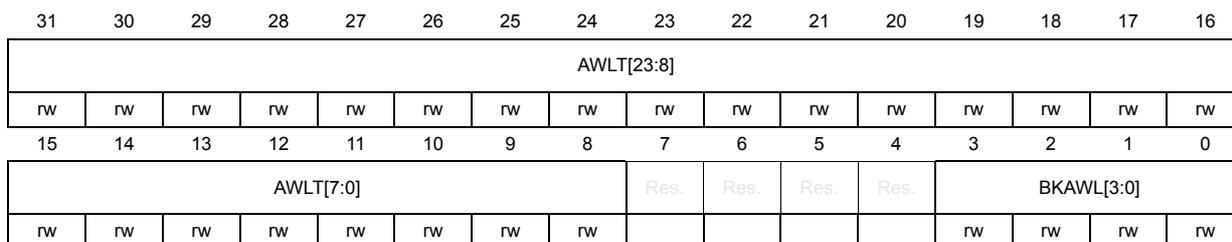

There are high and low threshold registers which are compared with given data values (set by AWHT[23:0] bits in DFSDM_FLTxAWHTR register and by AWLT[23:0] bits in DFSDM_FLTxAWLTR register).

There are 2 options for comparing the threshold registers with the data values

- • Option1: in this case, the input data are taken from final output data register (AWFSEL=0). This option is characterized by:

- – high input data resolution (up to 24-bits)

- – slow response time - inappropriate for fast response applications like overcurrent detection

- – for the comparison the final data are taken after bit shifting and offset data correction

- – final data are available only after main regular or injected conversions are performed

- – can be used in case of parallel input data source (DATMPX[1:0] ≠ 0 in DFSDM_CHyCFGR1 register)

- • Option2: in this case, the input data are taken from any serial data receivers output (AWFSEL=1). This option is characterized by:

- – input serial data are processed by dedicated analog watchdog Sinc x channel filters with configurable oversampling ratio (1..32) and filter order (1..3) (see AWFOISR[4:0] and AWFORR[1:0] bits setting in DFSDM_CHyAWSCDR register)

- – lower resolution (up to 16-bit)

- – fast response time - appropriate for applications which require a fast response like overcurrent/overvoltage detection)

- – data are available in continuous mode independently from main regular or injected conversions activity

In case of input channels monitoring (AWFSEL=1), the data for comparison to threshold is taken from channels selected by AWDCH[7:0] field (DFSDM_FLTxCR2 register). Each of the selected channels filter result is compared to one threshold value pair (AWHT[23:0] / AWLT[23:0]). In this case, only higher 16 bits (AWHT[23:8] / AWLT[23:8]) define the 16-bit threshold compared with the analog watchdog filter output because data coming from the analog watchdog filter is up to a 16-bit resolution. Bits AWHT[7:0] / AWLT[7:0] are not taken into comparison in this case (AWFSEL=1).

Parameters of the analog watchdog filter configuration for each input channel are set in DFSDM_CHyAWSCDR register (filter order AWFORR[1:0] and filter oversampling ratio AWFOISR[4:0]).

Each input channel has its own comparator which compares the analog watchdog data (from analog watchdog filter) with analog watchdog threshold values (AWHT/AWLT). When several channels are selected (field AWDCH[7:0] field of DFSDM_FLTxCR2 register), several comparison requests may be received simultaneously. In this case, the channel request with the lowest number is managed first and then continuing to higher selected channels. For each channel, the result can be recorded in a separate flag (fields AWHTF[7:0], AWLTF[7:0] of DFSDM_FLTxAWSR register). Each channel request is executed in 8 DFSDM clock cycles. So, the bandwidth from each channel is limited to 8 DFSDM clock cycles (if AWDCH[7:0] = 0xFF). Because the maximum input channel sampling clock frequency is the DFSDM clock frequency divided by 4, the configuration AWFOISR = 0 (analog watchdog filter is bypassed) cannot be used for analog watchdog feature at this input clock speed. Therefore user must properly configure the number of watched channels and analog watchdog filter parameters with respect to input sampling clock speed and DFSDM frequency.

Analog watchdog filter data for given channel y is available for reading by firmware on field WDATA[15:0] in DFSDM_CHyWDATR register. That analog watchdog filter data is converted continuously (if CHEN=1 in DFSDM_CHyCFGR1 register) with the data rate given by the analog watchdog filter setting and the channel input clock frequency.

The analog watchdog filter conversion works like a regular Fast Continuous Conversion without the integrator. The number of serial samples needed for one result from analog watchdog filter output (at channel input clock frequency \( f_{CKIN} \) ):

first conversion:

for Sinc x filters (x=1..5): number of samples = \( [F_{OSR} * F_{ORD} + F_{ORD} + 1] \)

for FastSinc filter: number of samples = \( [F_{OSR} * 4 + 2 + 1] \)

next conversions:

for Sinc x and FastSinc filters: number of samples = \( [F_{OSR} * I_{OSR}] \)

where:

\( F_{OSR} \) ..... filter oversampling ratio: \( F_{OSR} = AWFOSR[4:0]+1 \) (see DFSDM_CHyAWSCDR register)

\( F_{ORD} \) ..... the filter order: \( F_{ORD} = AWFORD[1:0] \) (see DFSDM_CHyAWSCDR register)

In case of output data register monitoring (AWFSEL=0), the comparison is done after a right bit shift and an offset correction of final data (see OFFSET[23:0] and DTRBS[4:0] fields in DFSDM_CHyCFGR2 register). A comparison is performed after each injected or regular end of conversion for the channels selected by AWDCH[7:0] field (in DFSDM_FLTxCR2 register).

The status of an analog watchdog event is signalized in DFSDM_FLTxAWSR register where a given event is latched. AWHTF[y]=1 flag signalizes crossing AWHT[23:0] value on channel y. AWLTF[y]=1 flag signalizes crossing AWLT[23:0] value on channel y. Latched events in DFSDM_FLTxAWSR register are cleared by writing '1' into the corresponding clearing bit CLRAWHTF[y] or CLRAWLTF[y] in DFSDM_FLTxAWCFR register.

The global status of an analog watchdog is signalized by the AWDF flag bit in DFSDM_FLTxISR register (it is used for the fast detection of an interrupt source). AWDF=1 signalizes that at least one watchdog occurred (AWHTF[y]=1 or AWLTF[y]=1 for at least one channel). AWDF bit is cleared when all AWHTF[7:0] and AWLTF[7:0] are cleared.

An analog watchdog event can be assigned to break output signal. There are four break outputs to be assigned to a high or low threshold crossing event (dfsdm_break[3:0]). The break signal assignment to a given analog watchdog event is done by BKAWH[3:0] and BKAWL[3:0] fields in DFSDM_FLTxAWHTR and DFSDM_FLTxAWLTR register.

30.4.11 Short-circuit detector

The purpose of a short-circuit detector is to signalize with a very fast response time if an analog signal reached saturated values (out of full scale ranges) and remained on this value given time. This behavior can detect short-circuit or open circuit errors (e.g. overcurrent or overvoltage). An interrupt/event/break generation can be invoked.

Input data into a short-circuit detector is taken from channel transceiver outputs.

There is an upcounting counter on each input channel which is counting consecutive 0's or 1's on serial data receiver outputs. A counter is restarted if there is a change in the data stream received - 1 to 0 or 0 to 1 change of data signal. If this counter reaches a short-circuit threshold register value (SCDT[7:0] bits in DFSDM_CHyAWSCDR register), then a short-

circuit event is invoked. Each input channel has its short-circuit detector. Any channel can be selected to be continuously monitored by setting the SCDEN bit (in DFSDM_CHyCFGR1 register) and it has its own short-circuit detector settings (threshold value in SCDT[7:0] bits, status bit SCDF[7:0], status clearing bits CLRSCDF[7:0]). Status flag SCDF[y] is cleared also by hardware when corresponding channel y is disabled (CHEN[y] = 0).

On each channel, a short-circuit detector event can be assigned to break output signal dfsdm_break[3:0]. There are four break outputs to be assigned to a short-circuit detector event. The break signal assignment to a given channel short-circuit detector event is done by BKSCD[3:0] field in DFSDM_CHyAWSCDR register.

Short circuit detector cannot be used in case of parallel input data channel selection (DATMPX[1:0] ≠ 0 in DFSDM_CHyCFGR1 register).

Four break outputs are totally available (shared with the analog watchdog function).

30.4.12 Extreme detector

The purpose of an extremes detector is to collect the minimum and maximum values of final output data words (peak to peak values).

If the output data word is higher than the value stored in the extremes detector maximum register (EXMAX[23:0] bits in DFSDM_FLTxEXMAX register), then this register is updated with the current output data word value and the channel from which the data is stored is in EXMAXCH[2:0] bits (in DFSDM_FLTxEXMAX register) .

If the output data word is lower than the value stored in the extremes detector minimum register (EXMIN[23:0] bits in DFSDM_FLTxEXMIN register), then this register is updated with the current output data word value and the channel from which the data is stored is in EXMINCH[2:0] bits (in DFSDM_FLTxEXMIN register).

The minimum and maximum register values can be refreshed by software (by reading given DFSDM_FLTxEXMAX or DFSDM_FLTxEXMIN register). After refresh, the extremes detector minimum data register DFSDM_FLTxEXMIN is filled with 0x7FFFFFF (maximum positive value) and the extremes detector maximum register DFSDM_FLTxEXMAX is filled with 0x800000 (minimum negative value).

The extremes detector performs a comparison after a right bit shift and an offset data correction. For each extremes detector, the input channels to be considered into computing the extremes value are selected in EXCH[7:0] bits (in DFSDM_FLTxCR2 register).

30.4.13 Data unit block

The data unit block is the last block of the whole processing path: External \( \Sigma\Delta \) modulators - Serial transceivers - Sinc filter - Integrator - Data unit block.

The output data rate depends on the serial data stream rate, and filter and integrator settings. The maximum output data rate is:

or

Maximum output data rate in case of parallel data input:

or

or

where: \( f_{\text{DATAIN\_RATE}} \) ...input data rate from ADC or from CPU/DMA

The right bit-shift of final data is performed in this module because the final data width is 24-bit and data coming from the processing path can be up to 32 bits. This right bit-shift is configurable in the range 0-31 bits for each selected input channel (see DTRBS[4:0] bits in DFSDM_CHyCFGR2 register). The right bit-shift is rounding the result to nearest integer value. The sign of shifted result is maintained - to have valid 24-bit signed format of result data.

In the next step, an offset correction of the result is performed. The offset correction value (OFFSET[23:0] stored in register DFSDM_CHyCFGR2) is subtracted from the output data for a given channel. Data in the OFFSET[23:0] field is set by software by the appropriate calibration routine.

Due to the fact that all operations in digital processing are performed on 32-bit signed registers, the following conditions must be fulfilled not to overflow the result:

Note:

In case of filter and integrator bypass (

\(

I_{\text{OSR}}[7:0]=0

\)

,

\(

F_{\text{OSR}}[9:0]=0

\)

), the input data rate (

\(

f_{\text{DATAIN\_RATE}}

\)

) must be limited to be able to read all output data:

\(

f_{\text{DATAIN\_RATE}} \leq f_{\text{APB}}

\)

where

\(

f_{\text{APB}}

\)

is the bus frequency to which the DFSDM peripheral is connected.

30.4.14 Signed data format

Each DFSDM input serial channel can be connected to one external \( \Sigma\Delta \) modulator. An external \( \Sigma\Delta \) modulator can have 2 differential inputs (positive and negative) which can be used for a differential or single-ended signal measurement.

A \( \Sigma\Delta \) modulator output is always assumed in a signed format (a data stream of zeros and ones from a \( \Sigma\Delta \) modulator represents values -1 and +1).

Signed data format in registers: Data is in a signed format in registers for final output data, analog watchdog, extremes detector, offset correction. The msb of output data word represents the sign of value (two's complement format).

30.4.15 Launching conversions

Injected conversions can be launched using the following methods:

- • Software: writing '1' to JSWSTART in the DFSDM_FLTxCR1 register.

- • Trigger: JEXTSEL[4:0] selects the trigger signal while JEXTEN activates the trigger and selects the active edge at the same time (see the DFSDM_FLTxCR1 register).

- • Synchronous with DFSDM_FLT0 if JSYNC=1: for DFSDM_FLTx (x>0), an injected conversion is automatically launched when in DFSDM_FLT0; the injected conversion is started by software (JSWSTART=1 in DFSDM_FLT0CR2 register). Each injected conversion in DFSDM_FLTx (x>0) is always executed according to its local configuration settings (JSCAN, JCHG, etc.).

If the scan conversion is enabled (bit JSCAN=1) then, each time an injected conversion is triggered, all of the selected channels in the injected group (JCHG[7:0] bits in DFSDM_FLTxJCHGR register) are converted sequentially, starting with the lowest channel (channel 0, if selected).

If the scan conversion is disabled (bit JSCAN=0) then, each time an injected conversion is triggered, only one of the selected channels in the injected group (JCHG[7:0] bits in DFSDM_FLTxJCHGR register) is converted and the channel selection is then moved to the next selected channel. Writing to the JCHG[7:0] bits when JSCAN=0 sets the channel selection to the lowest selected injected channel.

Only one injected conversion can be ongoing at a given time. Thus, any request to launch an injected conversion is ignored if another request for an injected conversion has already been issued but not yet completed.

Regular conversions can be launched using the following methods:

- • Software: by writing '1' to RSWSTART in the DFSDM_FLTxCR1 register.

- • Synchronous with DFSDM_FLT0 if RSYNC=1: for DFSDM_FLTx (x>0), a regular conversion is automatically launched when in DFSDM_FLT0; a regular conversion is started by software (RSWSTART=1 in DFSDM_FLT0CR2 register). Each regular conversion in DFSDM_FLTx (x>0) is always executed according to its local configuration settings (RCONT, RCH, etc.).

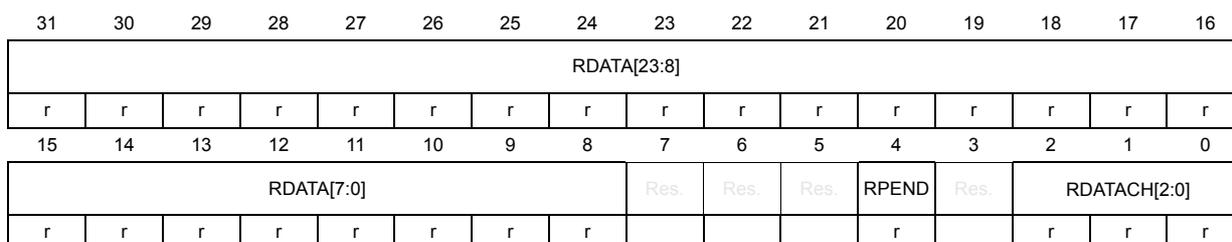

Only one regular conversion can be pending or ongoing at a given time. Thus, any request to launch a regular conversion is ignored if another request for a regular conversion has already been issued but not yet completed. A regular conversion can be pending if it was interrupted by an injected conversion or if it was started while an injected conversion was in progress. This pending regular conversion is then delayed and is performed when all injected conversion are finished. Any delayed regular conversion is signalized by RPEND bit in DFSDM_FLTxRDATA register.

30.4.16 Continuous and fast continuous modes

Setting RCONT in the DFSDM_FLTxCR1 register causes regular conversions to execute in continuous mode. RCONT=1 means that the channel selected by RCH[2:0] is converted repeatedly after '1' is written to RSWSTART.

The regular conversions executing in continuous mode can be stopped by writing '0' to RCONT. After clearing RCONT, the on-going conversion is stopped immediately.

In continuous mode, the data rate can be increased by setting the FAST bit in the DFSDM_FLTxCR1 register. In this case, the filter does not need to be refilled by new fresh data if converting continuously from one channel because data inside the filter is valid from previously sampled continuous data. The speed increase depends on the chosen filter order. The first conversion in fast mode (FAST=1) after starting a continuous conversion by RSWSTART=1 takes still full time (as when FAST=0), then each subsequent conversion is finished in shorter intervals.

Conversion time in continuous mode:

if FAST = 0 (or first conversion if FAST=1):

for Sinc x filters:

for FastSinc filter:

if FAST = 1 (except first conversion):

for Sinc x and FastSinc filters:

in case \( F_{\text{OSR}} = F_{\text{OSR}}[9:0]+1 = 1 \) (filter bypassed, only integrator active):

Continuous mode is not available for injected conversions. Injected conversions can be started by timer trigger to emulate the continuous mode with precise timing.

If a regular continuous conversion is in progress (RCONT=1) and if a write access to DFSDM_FLTxCR1 register requesting regular continuous conversion (RCONT=1) is performed, then regular continuous conversion is restarted from the next conversion cycle (like new regular continuous conversion is applied for new channel selection - even if there is no change in DFSDM_FLTxCR1 register).

30.4.17 Request precedence

An injected conversion has a higher precedence than a regular conversion. A regular conversion which is already in progress is immediately interrupted by the request of an injected conversion; this regular conversion is restarted after the injected conversion finishes.

An injected conversion cannot be launched if another injected conversion is pending or already in progress: any request to launch an injected conversion (either by JSWSTART or by a trigger) is ignored as long as bit JCP is '1' (in the DFSDM_FLTxISR register).

Similarly, a regular conversion cannot be launched if another regular conversion is pending or already in progress: any request to launch a regular conversion (using RSWSTART) is ignored as long as bit RCP is '1' (in the DFSDM_FLTxISR register).

However, if an injected conversion is requested while a regular conversion is already in progress, the regular conversion is immediately stopped and an injected conversion is launched. The regular conversion is then restarted and this delayed restart is signalized in bit RPEND.

Injected conversions have precedence over regular conversions in that a injected conversion can temporarily interrupt a sequence of continuous regular conversions. When

the sequence of injected conversions finishes, the continuous regular conversions start again if RCONT is still set (and RPEND bit will signalize the delayed start on the first regular conversion result).

Precedence also matters when actions are initiated by the same write to DFSDM, or if multiple actions are pending at the end of another action. For example, suppose that, while an injected conversion is in process (JCIP=1), a single write operation to DFSDM_FLTxCR1 writes '1' to RSWSTART, requesting a regular conversion. When the injected sequence finishes, the precedence dictates that the regular conversion is performed next and its delayed start is signalized in RPEND bit.

30.4.18 Power optimization in run mode

In order to reduce the consumption, the DFSDM filter and integrator are automatically put into idle when not used by conversions (RCIP=0, JCIP=0).

30.5 DFSDM interrupts

In order to increase the CPU performance, a set of interrupts related to the CPU event occurrence has been implemented:

- • End of injected conversion interrupt:

- – enabled by JEOCIE bit in DFSDM_FLTxCR2 register

- – indicated in JEOCF bit in DFSDM_FLTxISR register

- – cleared by reading DFSDM_FLTxJDATAR register (injected data)

- – indication of which channel end of conversion occurred, reported in JDATACH[2:0] bits in DFSDM_FLTxJDATAR register

- • End of regular conversion interrupt:

- – enabled by REOCIE bit in DFSDM_FLTxCR2 register

- – indicated in REOCF bit in DFSDM_FLTxISR register

- – cleared by reading DFSDM_FLTxRDATAR register (regular data)

- – indication of which channel end of conversion occurred, reported in RDATAACH[2:0] bits in DFSDM_FLTxRDATAR register

- • Data overrun interrupt for injected conversions:

- – occurred when injected converted data were not read from DFSDM_FLTxJDATAR register (by CPU or DMA) and were overwritten by a new injected conversion

- – enabled by JOVRIE bit in DFSDM_FLTxCR2 register

- – indicated in JOVRF bit in DFSDM_FLTxISR register

- – cleared by writing '1' into CLRJOVRF bit in DFSDM_FLTxICR register

- • Data overrun interrupt for regular conversions:

- – occurred when regular converted data were not read from DFSDM_FLTxRDATAR register (by CPU or DMA) and were overwritten by a new regular conversion

- – enabled by ROVRIE bit in DFSDM_FLTxCR2 register

- – indicated in ROVRF bit in DFSDM_FLTxISR register

- – cleared by writing '1' into CLRROVRF bit in DFSDM_FLTxICR register

- • Analog watchdog interrupt:

- – occurred when converted data (output data or data from analog watchdog filter - according to AWFSEL bit setting in DFSDM_FLTxCR1 register) crosses over/under high/low thresholds in DFSDM_FLTxAWHTR / DFSDM_FLTxAWLTR registers

- – enabled by AWDIE bit in DFSDM_FLTxCR2 register (on selected channels AWDCH[7:0])

- – indicated in AWDF bit in DFSDM_FLTxISR register

- – separate indication of high or low analog watchdog threshold error by AWHTF[7:0] and AWLTF[7:0] fields in DFSDM_FLTxAWSR register

- – cleared by writing '1' into corresponding CLRAWHTF[7:0] or CLRAWLTF[7:0] bits in DFSDM_FLTxAWCFR register

- • Short-circuit detector interrupt:

- – occurred when the number of stable data crosses over thresholds in DFSDM_CHyAWSCDR register

- – enabled by SCDIE bit in DFSDM_FLTxCR2 register (on channel selected by SCDEN bit in DFSDM_CHyCFGR1 register)

- – indicated in SCDF[7:0] bits in DFSDM_FLTxISR register (which also reports the channel on which the short-circuit detector event occurred)

- – cleared by writing '1' into the corresponding CLRSCDF[7:0] bit in DFSDM_FLTxICR register

- • Channel clock absence interrupt:

- – occurred when there is clock absence on CKINy pin (see Clock absence detection in Section 30.4.4: Serial channel transceivers )

- – enabled by CKABIE bit in DFSDM_FLTxCR2 register (on channels selected by CKABEN bit in DFSDM_CHyCFGR1 register)

- – indicated in CKABF[y] bit in DFSDM_FLTxISR register

- – cleared by writing '1' into CLRCKABF[y] bit in DFSDM_FLTxICR register

Table 254. DFSDM interrupt requests

| Interrupt event | Event flag | Event/Interrupt clearing method | Interrupt enable control bit |

|---|---|---|---|

| End of injected conversion | JEOCF | reading DFSDM_FLTxJDATAR | JEOCIE |

| End of regular conversion | REOCF | reading DFSDM_FLTxRDATAR | REOCIE |

| Injected data overrun | JOVRF | writing CLRJOVRF = 1 | JOVRIE |

| Regular data overrun | ROVRF | writing CLRROVRF = 1 | ROVRIE |

| Analog watchdog | AWDF, AWHTF[7:0], AWLTF[7:0] | writing CLRAWHTF[7:0] = 1 writing CLRAWLTF[7:0] = 1 | AWDIE, (AWDCH[7:0]) |

| short-circuit detector | SCDF[7:0] | writing CLRSCDF[7:0] = 1 | SCDIE, (SCDEN) |

| Channel clock absence | CKABF[7:0] | writing CLRCKABF[7:0] = 1 | CKABIE, (CKABEN) |

30.6 DFSDM DMA transfer

To decrease the CPU intervention, conversions can be transferred into memory using a DMA transfer. A DMA transfer for injected conversions is enabled by setting bit JDMAEN=1 in DFSDM_FLTxCR1 register. A DMA transfer for regular conversions is enabled by setting bit RDMAEN=1 in DFSDM_FLTxCR1 register.

Note: With a DMA transfer, the interrupt flag is automatically cleared at the end of the injected or regular conversion (JEOCF or REOCF bit in DFSDM_FLTxISR register) because DMA is reading DFSDM_FLTxJDATAR or DFSDM_FLTxRDATAR register.

30.7 DFSDM channel y registers (y=0..7)

Word access (32-bit) must be used for registers write access except DFSDM_CHyDATINR register. Write access to DFSDM_CHyDATINR register can be either word access (32-bit) or half-word access (16-bit).

30.7.1 DFSDM channel y configuration register (DFSDM_CHyCFGR1)

This register specifies the parameters used by channel y.

Address offset: 0x00 + 0x20 * y, (y = 0 to 7)

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| DFSDM EN | CKOUT SRC | Res. | Res. | Res. | Res. | Res. | Res. | CKOUTDIV[7:0] | |||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DATPACK[1:0] | DATMPX[1:0] | Res. | Res. | Res. | CHIN SEL | CHEN | CKAB EN | SCDEN | Res. | SPICKSEL[1:0] | SITP[1:0] | ||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

Bit 31 DFSDMEN : Global enable for DFSDM interface

0: DFSDM interface disabled

1: DFSDM interface enabled

If DFSDM interface is enabled, then it is started to operate according to enabled y channels and enabled x filters settings (CHEN bit in DFSDM_CHyCFGR1 and DFEN bit in DFSDM_FLTxCR1).

Data cleared by setting DFSDMEN=0:

–all registers DFSDM_FLTxISR are set to reset state (x = 0..3)

–all registers DFSDM_FLTxAWSR are set to reset state (x = 0..3)

Note: DFSDMEN is present only in DFSDM_CH0CFGR1 register (channel y=0)

Bit 30 CKOUTSRC : Output serial clock source selection

0: Source for output clock is from system clock

1: Source for output clock is from audio clock

This value can be modified only when DFSDMEN=0 (in DFSDM_CH0CFGR1 register).

Note: CKOUTSRC is present only in DFSDM_CH0CFGR1 register (channel y=0)

Bits 29:24 Reserved, must be kept at reset value.

Bits 23:16 CKOUTDIV[7:0] : Output serial clock divider

- 0: Output clock generation is disabled (CKOUT signal is set to low state)

- 1- 255: Defines the division of system clock for the serial clock output for CKOUT signal in range 2 - 256 (Divider = CKOUTDIV+1).

CKOUTDIV also defines the threshold for a clock absence detection.

This value can only be modified when DFSDMEN=0 (in DFSDM_CH0CFGR1 register).

If DFSDMEN=0 (in DFSDM_CH0CFGR1 register) then CKOUT signal is set to low state (setting is performed one DFSDM clock cycle after DFSDMEN=0).

Note: CKOUTDIV is present only in DFSDM_CH0CFGR1 register (channel y=0)

Bits 15:14 DATPACK[1:0] : Data packing mode in DFSDM_CHyDATINR register.

- 0: Standard: input data in DFSDM_CHyDATINR register are stored only in INDAT0[15:0]. To empty DFSDM_CHyDATINR register one sample must be read by the DFSDM filter from channel y.

- 1: Interleaved: input data in DFSDM_CHyDATINR register are stored as two samples:

- –first sample in INDAT0[15:0] (assigned to channel y)

- –second sample INDAT1[15:0] (assigned to channel y)

- 2: Dual: input data in DFSDM_CHyDATINR register are stored as two samples:

- –first sample INDAT0[15:0] (assigned to channel y)

- –second sample INDAT1[15:0] (assigned to channel y+1)

- 3: Reserved

This value can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Bits 13:12 DATMPX[1:0] : Input data multiplexer for channel y

- 0: Data to channel y are taken from external serial inputs as 1-bit values. DFSDM_CHyDATINR register is write protected.

- 1: Data to channel y are taken from internal analog to digital converter ADC y+1 output register update as 16-bit values (if ADC y+1 is available). Data from ADCs are written into INDAT0[15:0] part of DFSDM_CHyDATINR register.

- 2: Data to channel y are taken from internal DFSDM_CHyDATINR register by direct CPU/DMA write. There can be written one or two 16-bit data samples according DATPACK[1:0] bit field setting.

- 3: Reserved

This value can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Bits 11:9 Reserved, must be kept at reset value.

Bit 8 CHINSEL : Channel inputs selection

- 0: Channel inputs are taken from pins of the same channel y.

- 1: Channel inputs are taken from pins of the following channel (channel (y+1) modulo 8).

This value can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Bit 7 CHEN : Channel y enable

- 0: Channel y disabled

- 1: Channel y enabled

If channel y is enabled, then serial data receiving is started according to the given channel setting.

- Bit 6

CKABEN

: Clock absence detector enable on channel y

- 0: Clock absence detector disabled on channel y

- 1: Clock absence detector enabled on channel y

- Bit 5

SCDEN

: Short-circuit detector enable on channel y

- 0: Input channel y will not be guarded by the short-circuit detector

- 1: Input channel y will be continuously guarded by the short-circuit detector

- Bit 4 Reserved, must be kept at reset value.

- Bits 3:2

SPICKSEL[1:0]

: SPI clock select for channel y

- 0: clock coming from external CKINy input - sampling point according SITP[1:0]

- 1: clock coming from internal CKOUT output - sampling point according SITP[1:0]

- 2: clock coming from internal CKOUT - sampling point on each second CKOUT falling edge.

- For connection to external \( \Sigma\Delta \) modulator which divides its clock input (from CKOUT) by 2 to generate its output serial communication clock (and this output clock change is active on each clock input rising edge).

- 3: clock coming from internal CKOUT output - sampling point on each second CKOUT rising edge.

- For connection to external \( \Sigma\Delta \) modulator which divides its clock input (from CKOUT) by 2 to generate its output serial communication clock (and this output clock change is active on each clock input falling edge).

This value can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

- Bits 1:0

SITP[1:0]

: Serial interface type for channel y

- 00: SPI with rising edge to strobe data

- 01: SPI with falling edge to strobe data

- 10: Manchester coded input on DATINy pin: rising edge = logic 0, falling edge = logic 1

- 11: Manchester coded input on DATINy pin: rising edge = logic 1, falling edge = logic 0

This value can only be modified when CHEN=0 (in DFSDM_CHyCFGR1 register).

30.7.2 DFSDM channel y configuration register (DFSDM_CHyCFGR2)

This register specifies the parameters used by channel y.

Address offset: 0x04 + 0x20 * y, (y = 0 to 7)

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| OFFSET[23:8] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OFFSET[7:0] | DTRBS[4:0] | Res. | Res. | Res. | |||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |||

Bits 31:8 OFFSET[23:0] : 24-bit calibration offset for channel y

For channel y, OFFSET is applied to the results of each conversion from this channel.

This value is set by software.

Bits 7:3 DTRBS[4:0] : Data right bit-shift for channel y

0-31: Defines the shift of the data result coming from the integrator - how many bit shifts to the right will be performed to have final results. Bit-shift is performed before offset correction. The data shift is rounding the result to nearest integer value. The sign of shifted result is maintained (to have valid 24-bit signed format of result data).

This value can be modified only when CHEN=0 (in DFSDM_CHyCFGR1 register).

Bits 2:0 Reserved, must be kept at reset value.

30.7.3 DFSDM channel y analog watchdog and short-circuit detector register (DFSDM_CHyAWSCDR)

Short-circuit detector and analog watchdog settings for channel y.

Address offset: 0x08 + 0x20 * y, (y = 0 to 7)

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | AWFORD[1:0] | Res. | AWFOSR[4:0] | |||||

| rw | rw | rw | rw | rw | rw | rw | |||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| BKSCD[3:0] | Res. | Res. | Res. | Res. | SCDT[7:0] | ||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ||||

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:22 AWFORD[1:0] : Analog watchdog Sinc filter order on channel y

0: FastSinc filter type

1: Sinc 1 filter type

2: Sinc 2 filter type

3: Sinc 3 filter type