54. Secure digital input/output MultiMediaCard interface (SDMMC)

54.1 SDMMC main features

The SD/SDIO, embedded MultiMediaCard (e•MMC) host interface (SDMMC) provides an interface between the AHB bus and SD memory cards, SDIO cards and e•MMC devices.

The MultiMediaCard system specifications are available through the MultiMediaCard Association website at www.jedec.org , published by the MMCA technical committee.

SD memory card and SD I/O card system specifications are available through the SD card Association website at www.sdcard.org .

The SDMMC features include the following:

- Compliance with Embedded MultiMediaCard System Specification Version 4.51 . Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit.

- Full compatibility with previous versions of MultiMediaCards (backward compatibility).

- Full compliance with SD memory card specifications version 4.1 . (SPI mode and UHS-II mode not supported).

- Full compliance with SDIO card specification version 4.0 . Card support for two different databus modes: 1-bit (default) and 4-bit. (SPI mode and UHS-II mode not supported).

- Data transfer up to 104 Mbyte/s for the 8-bit mode. (depending maximum allowed I/O speed).

- Data and command output enable signals to control external bidirectional drivers.

The MultiMediaCard/SD bus connects cards to the host.

The current version of the SDMMC supports only one SD/SDIO/e•MMC card at any one time and a stack of e•MMC.

54.2 SDMMC implementation

Table 385. STM32L4Rxxx and STM32L4Sxxx SDMMC features

| SDMMC modes/features (1) | SDMMC1 |

|---|---|

| Variable delay (SDR104, HS200) | - |

| SDMMC_CKIN | X |

| SDMMC_CDIR, SDMMC_D0DIR | X |

| SDMMC_D123DIR | X |

1. X = supported.

Table 386. STM32L4P5xx and STM32L4Q5xx SDMMC features

| SDMMC modes/features (1) | SDMMC1 | SDMMC2 |

|---|---|---|

| Variable delay (SDR104, HS200) | - | - |

| SDMMC_CKIN | X | X |

Table 386. STM32L4P5xx and STM32L4Q5xx SDMMC features (continued)

| SDMMC modes/features (1) | SDMMC1 | SDMMC2 |

|---|---|---|

| SDMMC_CDIR, SDMMC_D0DIR | X | - |

| SDMMC_D123DIR | X | - |

1. X = supported.

54.3 SDMMC bus topology

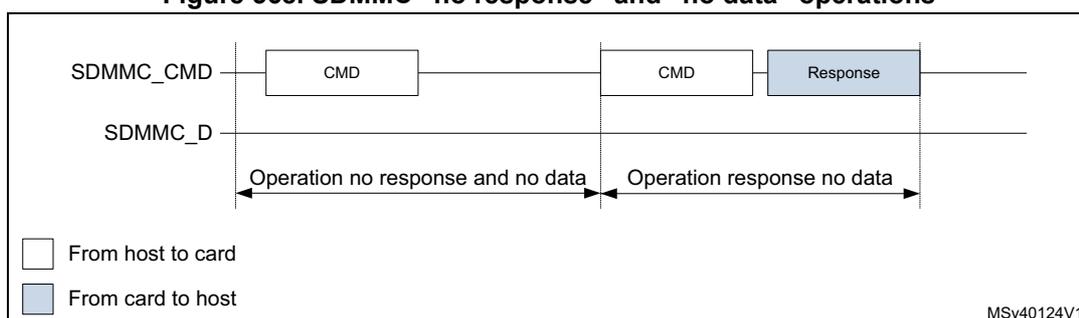

Communication over the bus is based on command/response and data transfers.

The basic transaction on the SD/SDIO/e•MMC bus is the command/response transaction. These types of bus transaction transfer their information directly within the command or response structure. In addition, some operations have a data token.

Data transfers are done in the following ways:

- • Block mode: data block(s) with block size \( 2^N \) bytes with N in the range 0-14.

- • SDIO multibyte mode: single data block with block size range 1-512 bytes

- • e•MMC Stream mode: continuous data stream

Data transfers to/from e•MMC cards are done in data blocks or streams.

Figure 568. SDMMC “no response” and “no data” operations

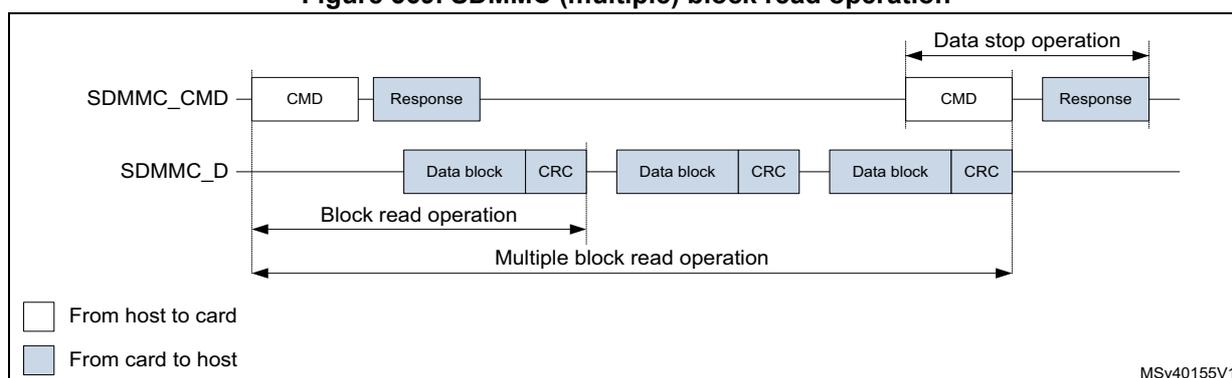

Figure 569. SDMMC (multiple) block read operation

Note: The Stop Transmission command is not required at the end of a e•MMC multiple block read with predefined block count.

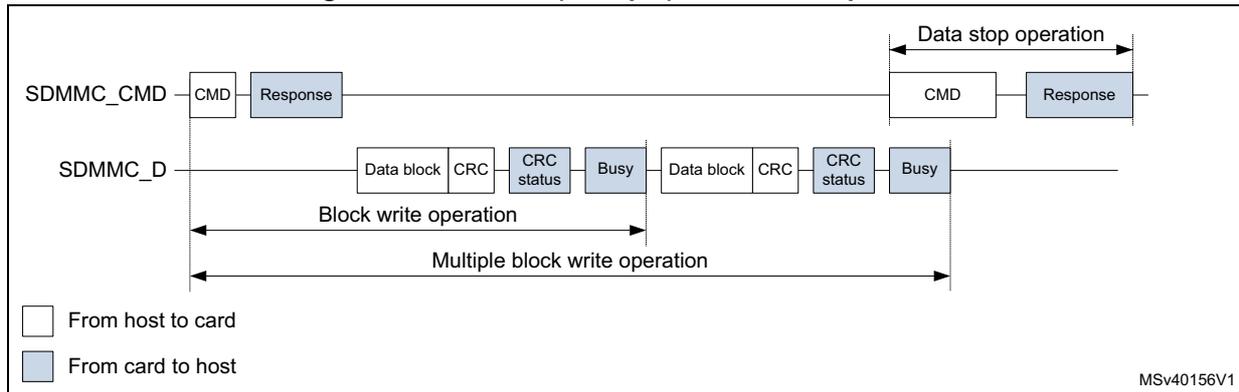

Figure 570. SDMMC (multiple) block write operation

Note: The Stop Transmission command is not required at the end of an e•MMC multiple block write with predefined block count.

Note: The SDMMC does not send any data as long as the Busy signal is asserted (SDMMC_D0 pulled low).

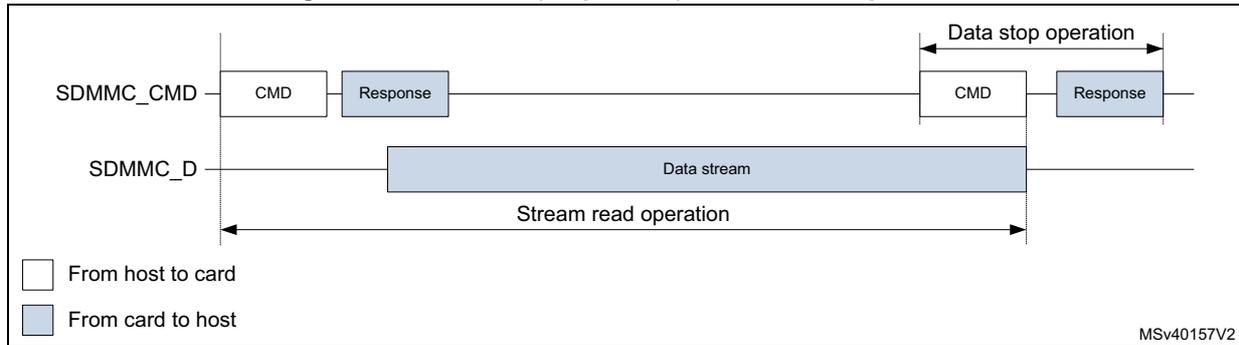

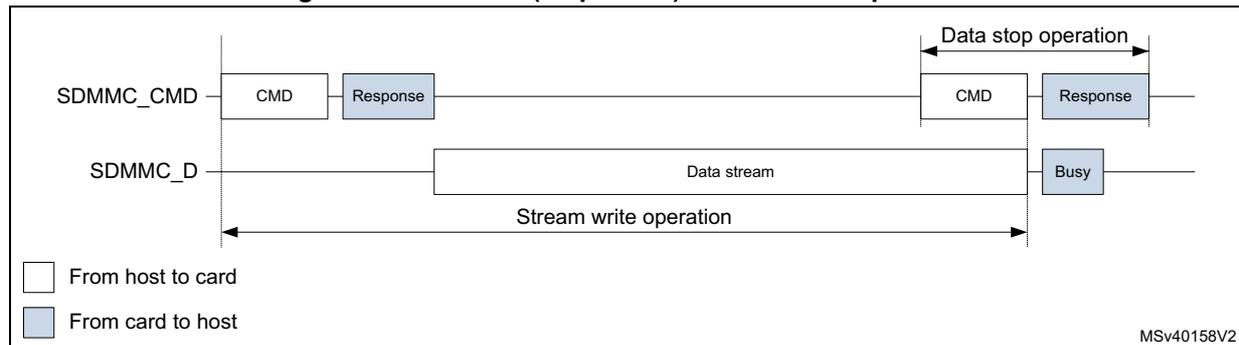

Figure 571. SDMMC (sequential) stream read operation

Figure 572. SDMMC (sequential) stream write operation

Stream data transfer operates only in a 1-bit wide bit bus configuration on SDMMC_D0 in single data rate modes (DS, HS, and SDR).

54.4 SDMMC operation modes

Table 387. SDMMC operation modes SD & SDIO

| SDIO Bus Speed modes (1)(2) | Max Bus Speed (3) [Mbyte/s] | Max Clock frequency [MHz] (4) | Signal Voltage [V] |

|---|---|---|---|

| DS (Default Speed) | 12.5 | 25 | 3.3 |

| HS (High Speed) | 25 | 50 | 3.3 |

| SDR12 | 12.5 | 25 | 1.8 |

| SDR25 | 25 | 50 | 1.8 |

| DDR50 | 50 | 50 | 1.8 |

| SDR50 | 50 | 100 | 1.8 |

- 1. SDR single data rate signaling.

- 2. DDR double data rate signaling. (data is sampled on both SDMMC_CK clock edges).

- 3. SDIO bus speed with 4bit bus width.

- 4. Maximum frequency depending on maximum allowed IO speed.

Table 388. SDMMC operation modes e•MMC

| e•MMC bus speed modes (1)(2) | Max bus speed (3) [Mbyte/s] | Max clock frequency [MHz] (4) | Signal voltage [V] |

|---|---|---|---|

| Legacy compatible | 26 | 26 | 3/1.8/1.2V |

| High speed SDR | 52 | 52 | 3/1.8/1.2V |

| High speed DDR | 104 | 52 | 3/1.8/1.2V |

- 1. SDR single data rate signaling.

- 2. DDR double data rate signaling. (data is sampled on both SDMMC_CK clock edges).

- 3. e•MMC bus speed with 8bit bus width.

- 4. Maximum frequency depending on maximum allowed IO speed.

54.5 SDMMC functional description

The SDMMC consists of three parts:

- • The AHB slave interface accesses the SDMMC adapter registers, and generates interrupt signals and IDMA control signals.

- • The SDMMC adapter block provides all functions specific to the e•MMC/SD/SD I/O card such as the clock generation unit, command and data transfer.

- • The internal DMA (IDMA) block with its AHB master interface.

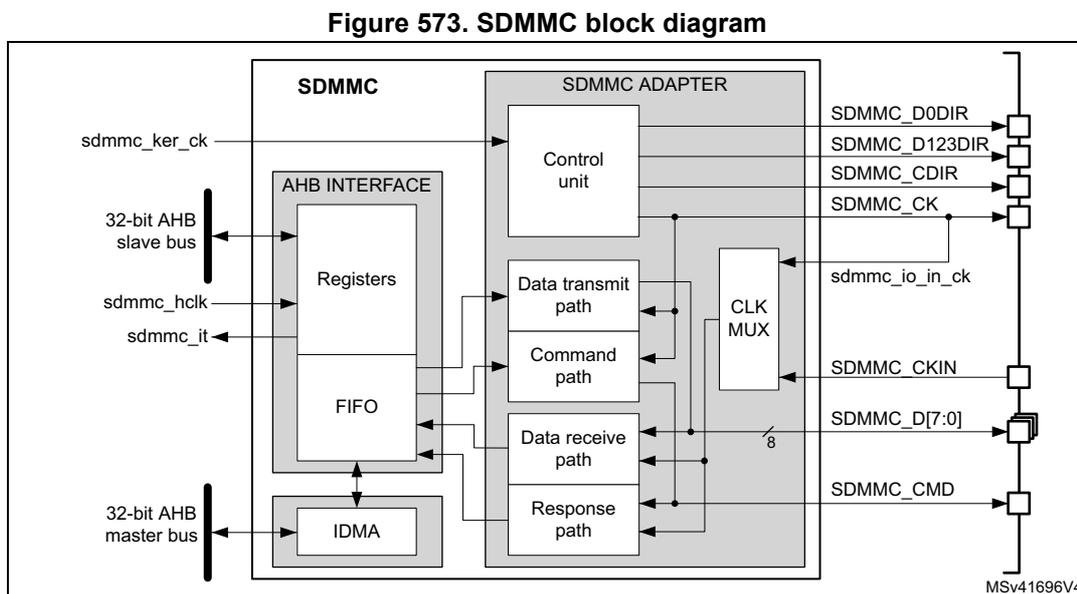

54.5.1 SDMMC block diagram

Figure 573 shows the SDMMC block diagram.

Figure 573. SDMMC block diagram

The diagram illustrates the internal architecture of the SDMMC interface. On the left, external signals include

sdmmc_ker_ck

(kernel clock),

sdmmc_hclk

(AHB clock), and

sdmmc_it

(interrupt). These connect to an

AHB INTERFACE

block containing

Registers

, a

FIFO

, and an

IDMA

unit. The

IDMA

is connected to a

32-bit AHB master bus

. The

AHB INTERFACE

connects to an

SDMMC ADAPTER

block. Inside the adapter, there is a

Control unit

, a

Data transmit path

, a

Command path

, a

Data receive path

, and a

Response path

. A

CLK MUX

block is also present in the adapter. The adapter connects to external pins on the right:

SDMMC_D0DIR

,

SDMMC_D123DIR

,

SDMMC_CDIR

,

SDMMC_CK

,

sdmmc_io_in_ck

,

SDMMC_CKIN

,

SDMMC_D[7:0]

(8-bit data bus), and

SDMMC_CMD

. A reference code

MSV41696V4

is shown in the bottom right corner.

54.5.2 SDMMC pins and internal signals

Table 389 lists the SDMMC internal input/output signals, Table 390 the SDMMC pins (alternate functions).

Table 389. SDMMC internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

sdmmc_ker_ck | Digital input | SDMMC kernel clock |

sdmmc_hclk | Digital input | AHB clock |

sdmmc_it | Digital output | SDMMC global interrupt |

sdmmc_io_in_ck | Digital input | SD/SDIO/e•MMC card feedback clock. This signal is internally connected to the

SDMMC_CK

pin (for DS and HS modes). |

Table 390. SDMMC pins

| Signal name | Signal type | Description |

|---|---|---|

SDMMC_CK | Digital output | Clock to SD/SDIO/e•MMC card |

SDMMC_CKIN | Digital input | Clock feedback from an external driver for SD/SDIO/e•MMC card. (for SDR12, SDR25, SDR50, DDR50) |

SDMMC_CMD | Digital input/output | SD/SDIO/e•MMC card bidirectional command/response signal. |

SDMMC_CDIR | Digital output | SD/SDIO/e•MMC card I/O direction indication for the

SDMMC_CMD

signal. |

Table 390. SDMMC pins (continued)

| Signal name | Signal type | Description |

|---|---|---|

| SDMMC_D[7:0] | Digital input/output | SD/SDIO/eMMC card bidirectional data lines. |

| SDMMC_D0DIR | Digital output | SD/SDIO/eMMC card I/O direction indication for the SDMMC_D0 data line. |

| SDMMC_D123DIR | Digital output | SD/SDIO/eMMC card I/O direction indication for the data lines SDMMC_D[3:1]. |

54.5.3 General description

The SDMMC_D[7:0] lines have different operating modes:

- By default, SDMMC_D0 line is used for data transfer. After initialization, the host can change the databus width.

- For an eMMC, 1-bit (SDMMC_D0), 4-bit (SDMMC_D[3:0]) or 8-bit (SDMMC_D[7:0]) data bus widths can be used.

- For an SD or an SDIO card, 1-bit (SDMMC_D0) or 4-bit (SDMMC_D[3:0]) can be used. All data lines operate in push-pull mode.

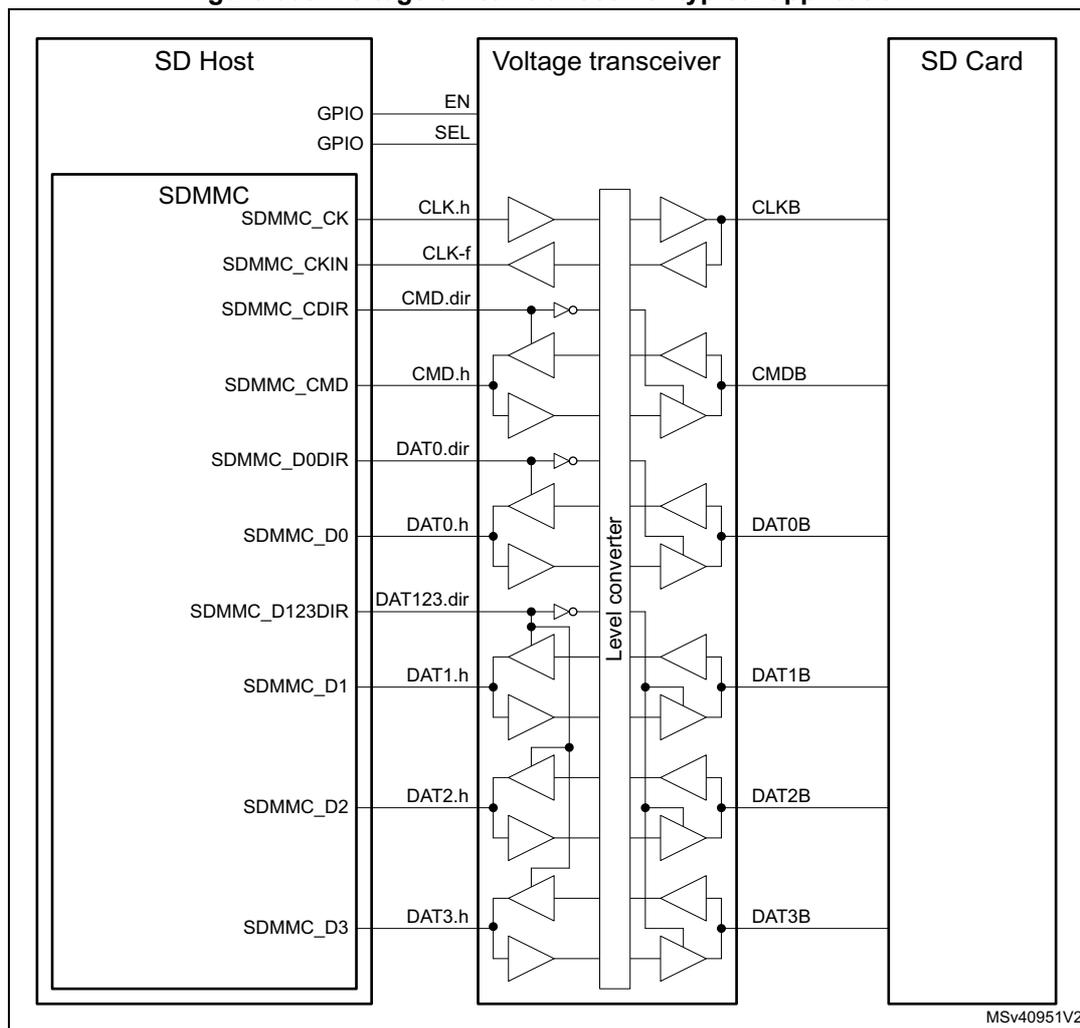

To allow the connection of an external driver (a voltage switch transceiver), the direction of data flow on the data lines is indicated with I/O direction signals. The SDMMC_D0DIR signal indicates the I/O direction for the SDMMC_D0 data line, the SDMMC_D123DIR for the SDMMC_D[3:1] data lines.

SDMMC_CMD only operates in push-pull mode:

To allow the connection of an external driver (a voltage switch transceiver), the direction of data flow on the SDMMC_CMD line is indicated with the I/O direction signal SDMMC_CDIR .

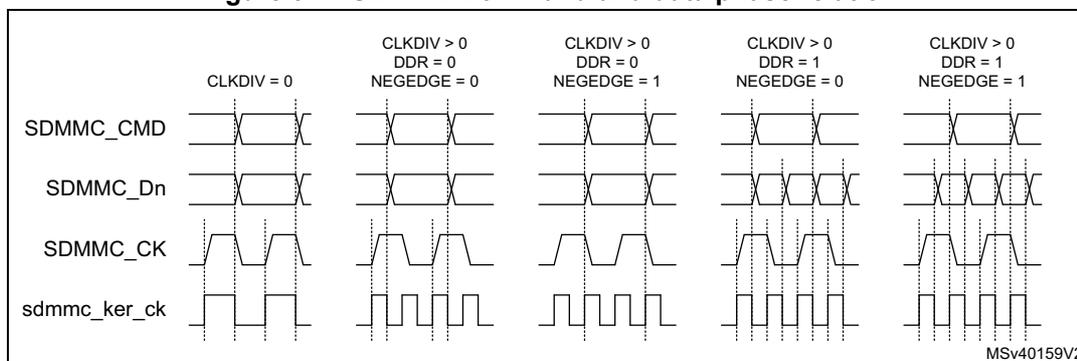

SDMMC_CK clock to the card originates from sdmmc_ker_ck :

- When the sdmmc_ker_ck clock has 50 % duty cycle, it can be used even in bypass mode (CLKDIV = 0).

- When the sdmmc_ker_ck duty cycle is not 50 %, the CLKDIV must be used to divide it by 2 or more (CLKDIV > 0).

- The phase relation between the SDMMC_CMD / SDMMC_D[7:0] outputs and the SDMMC_CK can be selected through the NEGEDGE bit. The phase relation depends on the CLKDIV, NEGEDGE, and DDR settings. See Figure 574 .

Figure 574. SDMMC Command and data phase relation

The figure is a timing diagram illustrating the phase relation between SDMMC_CMD, SDMMC_Dn, SDMMC_CK, and sdmmc_ker_ck signals across five different configurations. The configurations are: 1) CLKDIV = 0; 2) CLKDIV > 0, DDR = 0, NEGEDGE = 0; 3) CLKDIV > 0, DDR = 0, NEGEDGE = 1; 4) CLKDIV > 0, DDR = 1, NEGEDGE = 0; 5) CLKDIV > 0, DDR = 1, NEGEDGE = 1. The diagram shows the relative timing of the command, data, and clock signals for each case.

Table 391. SDMMC Command and data phase selection

| CLKDIV | DDR | NEGEDGE | SDMMC_CK | Command out | Data out |

|---|---|---|---|---|---|

| 0 | x | x | = sdmmc_ker_ck | generated on sdmmc_ker_ck falling edge | |

| >0 | 0 | 0 | generated on sdmmc_ker_ck rising edge | generated on sdmmc_ker_ck falling edge succeeding the SDMMC_CK rising edge. | generated on sdmmc_ker_ck falling edge succeeding a SDMMC_CK edge. |

| 1 | generated on the same sdmmc_ker_ck rising edge that generates the SDMMC_CK falling edge. | ||||

| 1 | 0 | generated on sdmmc_ker_ck falling edge succeeding the SDMMC_CK rising edge. | |||

| 1 | generated on the same sdmmc_ker_ck rising edge that generates the SDMMC_CK falling edge. |

By default, the sdmmc_io_in_ck feedback clock input is selected for sampling incoming data in the SDMMC receive path. It is derived from the SDMMC_CK pin.

When using an external driver (a voltage switch transceiver), the SDMMC_CKIN feedback clock input can be selected to sample the receive data.

For an SD/SDIO/e•MMC card, the clock frequency can vary between 0 and 208 MHz (limited by maximum I/O speed).

Depending on the selected bus mode (SDR or DDR), one bit or two bits are transferred on SDMMC_D[7:0] lines with each clock cycle. The SDMMC_CMD line transfers only one bit per clock cycle.

54.5.4 SDMMC adapter

The SDMMC adapter (see Figure 573: SDMMC block diagram ) is a multimedia/secure digital memory card bus master that provides an interface to a MultiMediaCard stack or to a secure digital memory card. It consists of the following subunits:

- • Control unit

- • Data transmit path

- • Command path

- • Data receive path

- • Response path

- • Receive data path clock multiplexer

- • Adapter register block

- • Data FIFO

- • Internal DMA (IDMA)

Note: The adapter registers and FIFO use the AHB clock domain (sdmmc_hclk). The control unit, command path and data transmit path use the SDMMC adapter clock domain (sdmmc_ker_ck). The response path and data receive path use the SDMMC adapter feedback clock domain from the sdmmc_io_in_ck, or SDMMC_CKIN.

Adapter register block

The adapter register block contains all system control registers, the SDMMC command and response registers and the data FIFO.

This block also generates the signals from the corresponding bit location in the SDMMC Clear register that clear the static flags in the SDMMC adapter.

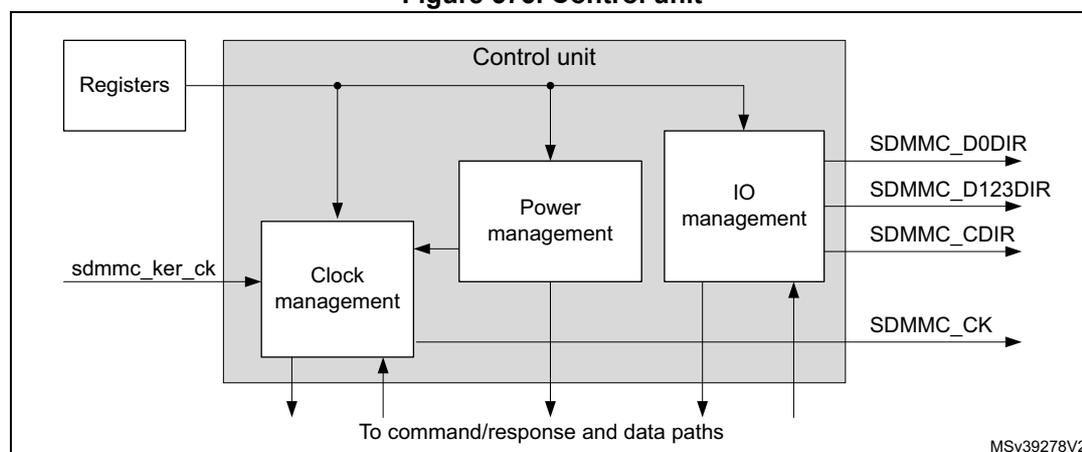

Control unit

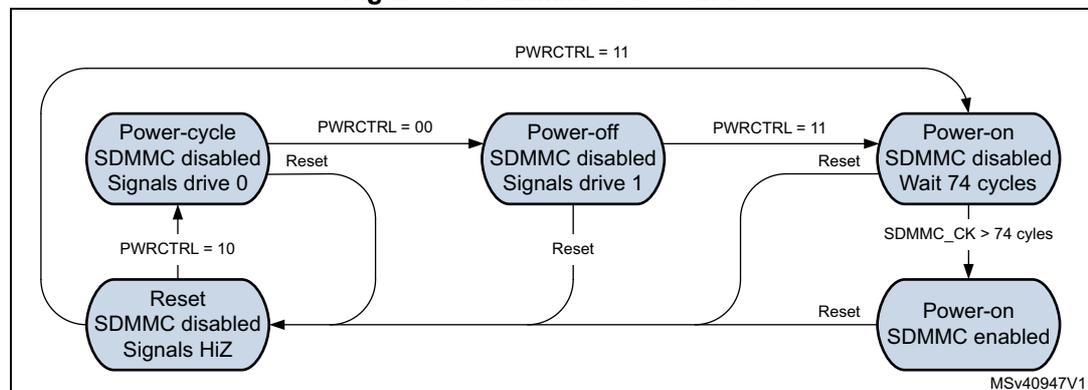

The control unit illustrated in Figure 575 , contains the power management functions, the SDMMC_CK clock management with divider, and the I/O direction management.

Figure 575. Control unit

graph LR

subgraph Control_unit [Control unit]

CM[Clock management]

PM[Power management]

IM[IO management]

end

R[Registers] --> CM

R --> PM

R --> IM

SKC[sdmmc_ker_ck] --> CM

CM --> SDCK[SDMMC_CK]

CM --> CRDP[To command/response and data paths]

PM --> SD0D[SDMMC_D0DIR]

PM --> SD12D[SDMMC_D123DIR]

PM --> SCD[SDMMC_CDIR]

PM --> CRDP

IM --> CRDP

MSV[MSV39278V2]

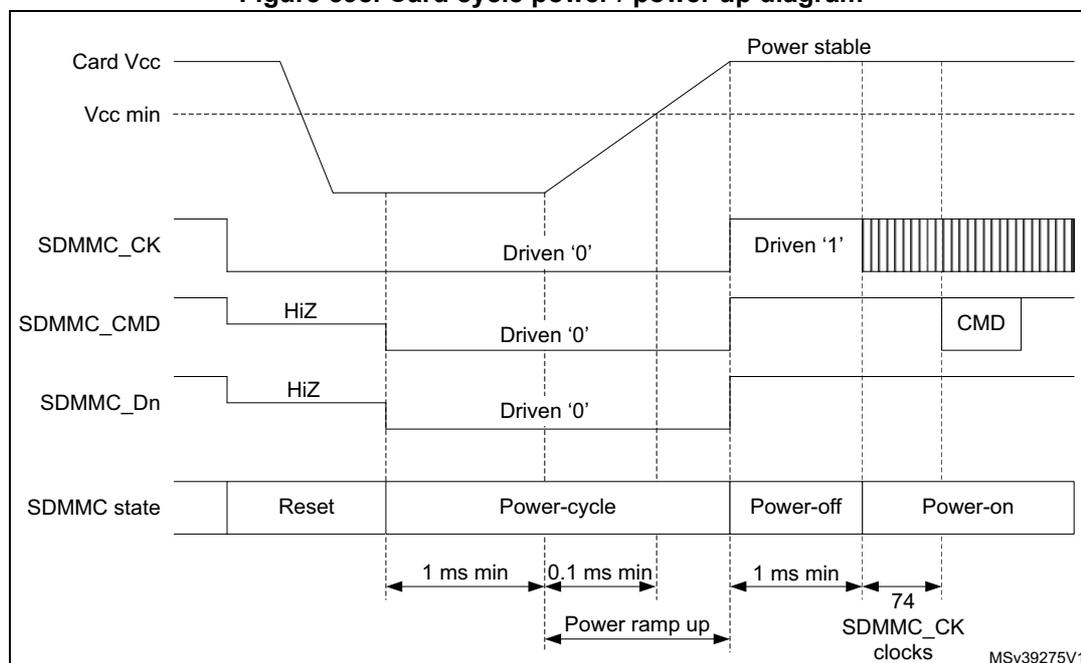

The power management subunit disables the card bus output signals during the power-off and power-up phases.

There are three power phases:

- • power-off

- • power-up

- • power-on

The clock management subunit uses the

sdmmc_ker_ck

to generate the

SDMMC_CK

and provides the division control. It also takes care of stopping the

SDMMC_CK

for i.e. flow control.

The clock outputs are inactive:

- • after reset

- • during the power-off or power-up phases

- • if the power saving mode (register bit

PWRSV) is enabled and the card bus is in the Idle state for eight clock periods. The clock is stopped eight cycles after both the command/response CPSM and data path DPSM subunits have entered the Idle phase. The clock is restarted when the command/response CPSM or data path DPSM is activated (enabled).

The I/O management subunit takes care of the

SDMMC_Dn

and

SDMMC_CMD

I/O direction signals, which controls the external voltage transceiver.

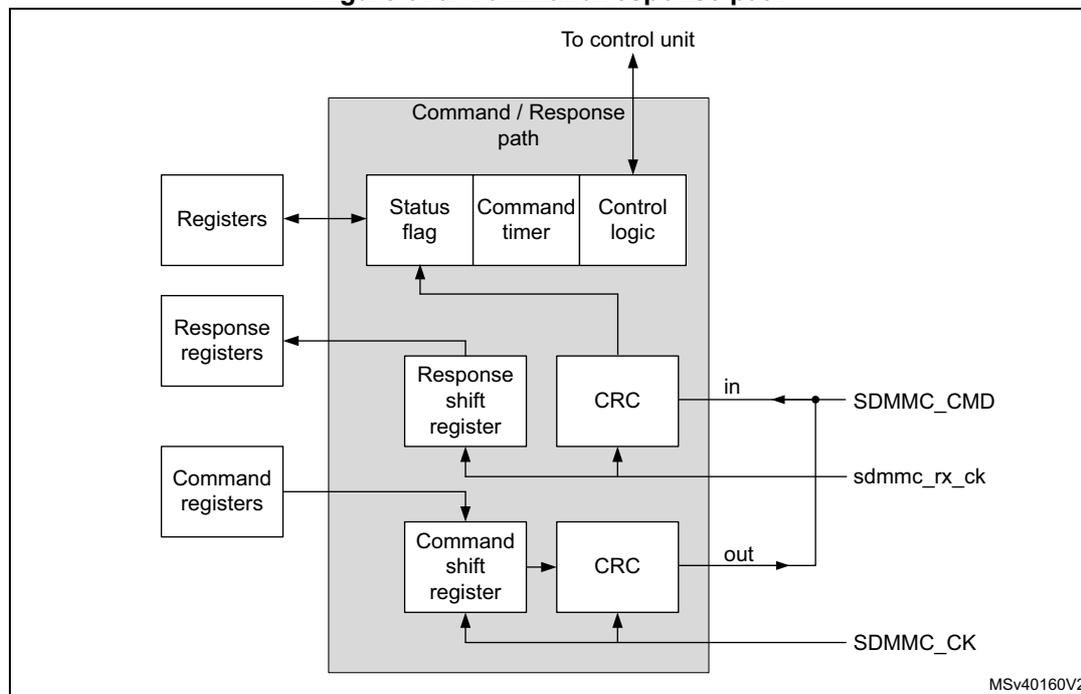

Command/response path

The command/response path subunit transfers commands and responses on the SDMMC_CMD line. The command path is clocked on the SDMMC_CK and sends commands to the card. The response path is clocked on the sdmmc_rx_ck and receives responses from the card.

Figure 576. Command/response path

The diagram illustrates the internal architecture of the Command/Response path subunit. A central grey box labeled 'Command / Response path' contains three sub-blocks: 'Status flag', 'Command timer', and 'Control logic'. The 'Control logic' is connected to an external 'To control unit' via a bidirectional arrow. It also has connections to three external register blocks: 'Registers', 'Response registers', and 'Command registers'. Inside the 'Command / Response path' box, the 'Status flag' and 'Command timer' are connected to the 'Control logic'. Below them, the 'Response path' includes a 'Response shift register' and a 'CRC' block. The 'Response shift register' is connected to the 'Control logic' and the 'CRC' block. The 'CRC' block is connected to the 'SDMMC_CMD' line (labeled 'in'). The 'Command path' includes a 'Command shift register' and a 'CRC' block. The 'Command shift register' is connected to the 'Control logic' and the 'CRC' block. The 'CRC' block is connected to the 'SDMMC_CMD' line (labeled 'out'). The 'Command shift register' is also connected to the 'SDMMC_CK' line. The 'Response shift register' is connected to the 'sdmmc_rx_ck' line. The diagram is labeled 'MSV40160V2' in the bottom right corner.

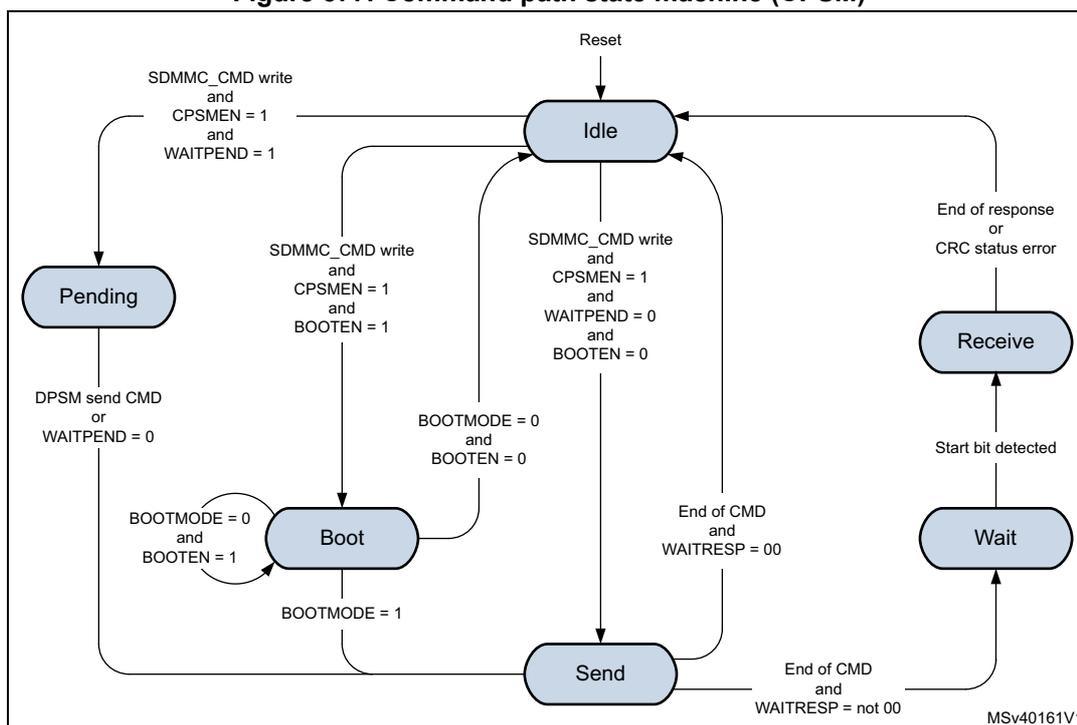

Command/response path state machine (CPSM)

- • When the command register is written to and the enable bit is set, command transfer starts. When the command has been sent the CRC is appended and the command path state machine (CPSM) sets the status flags and:

- – if a response is not required enters the Idle state.

- – If a response is required, it waits for the response.

- • When the response is received,

- – for a response with CRC, the received CRC code and the internally generated code are compared, and the appropriate status flag is set according the result.

- – for a response without CRC, no CRC is checked, and the appropriate status flag is not set.

When ever the CPSM is active, i.e. not in the Idle state, the CPSMACT bit is set.

Figure 577. Command path state machine (CPSM)

stateDiagram-v2

[*] --> Idle

Idle --> Pending: SDMMC_CMD write and CPSMEN = 1 and WAITPEND = 1

Idle --> Boot: SDMMC_CMD write and CPSMEN = 1 and BOOTEN = 1

Idle --> Send: SDMMC_CMD write and CPSMEN = 1 and WAITPEND = 0 and BOOTEN = 0

Pending --> Idle: DPSM send CMD or WAITPEND = 0

Pending --> Boot: BOOTMODE = 0 and BOOTEN = 1

Boot --> Idle: BOOTMODE = 0 and BOOTEN = 0

Boot --> Send: BOOTMODE = 1

Send --> Idle: End of CMD and WAITRESP = 00

Send --> Wait: End of CMD and WAITRESP = not 00

Wait --> Receive: Start bit detected

Receive --> Idle: End of response or CRC status error

- •

Idle:

The command path is inactive. When the command control register is written and the enable bit (CPSMEN) is set, the CPSM activates the SDMMC_CK clock (when stopped due to power save PWRSV bit) and moves

- – to the Send state when WAITPEND = 0 & BOOTEN = 0.

- – to the Pending state when WAITPEND = 1.

- – to the Boot state when BOOTEN = 1.

- •

Send:

The command is sent and the CRC is appended.

- – When CMDTRANS bit is set or when BOOTEN bit is set and BOOTMODE is alternative boot, and the DTDIR = receive, the CPSM DataEnable signal is issued to the DPSM at the end of the command.

- – When the CMDTRANS bit is set and the CMDSUSPEND bit is 0 the interrupt period is terminated at the end of the command.

- – When CMDSTOP bit is set the CPSM Abort signal is issued to the DPSM at the end of the command.

- – If no response is expected (WAITRESP = 00) the CPSM moves to the Idle state and the CMDSENT flag is set. When BOOTMODE = 1 & BOOTEN = 0 the CMDSENT flag is delayed 56 cycles after the command end bit, otherwise the

CMDSENT flag is generated immediately after the command end bit.

The RESPCMDR and RESPxR registers are not modified.

- – If a command response is expected (WAITRESP = not 00) the CPSM moves to the Wait state and start the response timeout.

- •

Wait:

The command path waits for a response.

- – When WAITINT bit is 0 the command timer starts running and the CPSM waits for a start bit.

- a) If a start bit is detected before the timeout the CPSM moves to the Receive state.

- b) If the timeout is reached before the CPSM detect a response start bit, the timeout flag (CTIMEOUT) is set and the CPSM moves to the Idle state.

The RESPCMDR and RESPxR registers are not modified.

- – When WAITINT bit is 1, the timer is disabled and the CPSM waits for an interrupt request (response start bit) from one of the cards.

- a) When a start bit is detected the CPSM moves to the Receive state.

- b) When writing WAITINT to 0 (interrupt mode abort), the host sends a response by its self and on detecting the start bit the CPSM move to the Receive state.

- – When WAITINT bit is 0 the command timer starts running and the CPSM waits for a start bit.

- •

Receive:

The command response is received. Depending the response mode bits WAITRESP in the command control register, the response can be either short or long, with CRC or without CRC. The received CRC code when present is verified against the internally generated CRC code.

- – When the CMDSUSPEND bit is set and the SDIO Response bit BS = 0 (response bit [39]), the interrupt period is started after the response.

When the CMDSUSPEND bit is cleared, or the CMDSUSPEND bit is 1 and the SDIO Response bit BS = 1 (response bit [39]), there is no interrupt period started. - – When the CMDTRANS bit is set and the CMDSUSPEND bit is set and the SDIO Response bit DF= 1 (response bit [32]) the interrupt period is terminated after the response.

- – When the CRC status passes or no CRC is present the CMDREND flag is set, the CPSM moves to the Idle state.

The RESPCMDR and RESPxR registers are updated with received response.- - When BOOTMODE = 1 & BOOTEN = 0 the CMDREND flag is delayed 56 cycles after the response end bit, otherwise the CMDREND flag is generated immediately after the response end bit.

- - When CMDTRANS bit is set and the DTDIR = transmit, the CPSM DataEnable signal is issued to the DPSM at the end of the command response.

- – When the CRC status fails the CCRCFAIL flag is set and the CPSM moves to the Idle state.

The RESPCMDR and RESPxR registers are updated with received response.

- – When the CMDSUSPEND bit is set and the SDIO Response bit BS = 0 (response bit [39]), the interrupt period is started after the response.

- •

Pending:

According the pending WAITPEND bit in the command register, the CPSM enters the pending state.

- – When DATALENGTH <= 5 bytes the CPSM moves to the Sent state and generates the DataEnable signal to start the data transfer aligned with the CMD12 Stop Transmission command.

- – When DATALENGTH > 5 bytes, the CPSM DataEnable signal is issued to the DPSM to start the data transfer. The CPSM waits for a send CMD signal from the

DPSM before moving to the Send state. This enables i.e. the CMD12 Stop Transmission command to be sent aligned with the data.

- – When writing WAITPEND to 0, the CPSM moves to the Send state.

- •

Boot:

If the BOOTEN bit is set in the command register, the CPSM enters the Boot state, and when:

- – BOOTMODE = 0 the SDMMC_CMD line is driven low and when CMDTRANS bit is set and the DTDIR = receive, the CPSM DataEnable signal is issued to the DPSM. This enables normal boot operation. This state is left at the end of the boot procedure by clearing the register bit BOOTEN, which cause the SDMMC_CMD line to be driven high and the CPSM Abort signal is issued to the DPSM, before moving to the Idle state. The CMDSENT flag is generated 56 cycles after SDMMC_CMD line is high.

- – BOOTMODE = 1, move to the Send state. This enables sending of the CMD0 (boot). Clearing BOOTEN has no effect.

Note: The CPSM remains in the Idle state for at least eight SDMMC_CK periods to meet the \( N_{CC} \) and \( N_{RC} \) timing constraints. \( N_{CC} \) is the minimum delay between two host commands, and \( N_{RC} \) is the minimum delay between the host command and the card response.

Note: The response timeout has a fixed value of 64 SDMMC_CK clock periods.

A command is a token that starts an operation. Commands are sent from the host to either a single card (addressed command) or all connected cards (broadcast command are available for e•MMC V3.31 or previous). Commands are transferred serially on the SDMMC_CMD line. All commands have a fixed length of 48 bits. The general format for a command token for SD-Memory cards, SDIO cards, and e•MMC cards is shown in Table 392 .

The command token data is taken from 2 registers, one containing a 32-bits argument and the other containing the 6-bits command index (six bits sent to a card).

Table 392. Command token format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 47 | 1 | 0 | Start bit |

| 46 | 1 | 1 | Transmission bit |

| [45:40] | 6 | x | Command index |

| [39:8] | 32 | x | Argument |

| [7:1] | 7 | x | CRC7 |

| 0 | 1 | 1 | End bit |

Next to the command data there are command type (WAITRESP) bits controlling the command path state machine (CPSM). These bits also determine whether the command requires a response, and whether the response is short (48 bit) or long (136 bits) long, and if a CRC is present or not.

A response is a token that is sent from an addressed card or synchronously from all connected cards to the host as an answer to a previous received command. All responses are sent via the command line SDMMC_CMD. The response transmission always starts with the left bit of the bit string corresponding to the response code word. The code length depends on the response type. Response tokens R1, R2, R3, R4, R5, and R6 have various

coding schemes, depending on their content. The general formats for the response tokens for SD-Memory cards, SDIO cards, and e•MMC cards are shown in Table 393 , Table 394 and Table 395 .

A response always starts with a start bit (always 0), followed by the bit indicating the direction of transmission (card = 0). A value denoted by x in the tables below indicates a variable entry. Most responses, except some, are protected by a CRC. Every command code word is terminated by the end bit (always 1).

The response token data is stored in 5 registers, four containing the 32-bits card status, OCR register, argument or 127-bits CID or CSD register including internal CRC, and one register containing the 6-bits command index.

Table 393. Short response with CRC token format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 47 | 1 | 0 | Start bit |

| 46 | 1 | 0 | Transmission bit |

| [45:40] | 6 | x | Command index (or reserved 111111) |

| [39:8] | 32 | x | Argument |

| [7:1] | 7 | x | CRC7 |

| 0 | 1 | 1 | End bit |

Table 394. Short response without CRC token format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 47 | 1 | 0 | Start bit |

| 46 | 1 | 0 | Transmission bit |

| [45:40] | 6 | x | Command index (or reserved 111111) |

| [39:8] | 32 | x | Argument |

| [7:1] | 7 | 1111111 | (reserved 1111111) |

| 0 | 1 | 1 | End bit |

Table 395. Long response with CRC token format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 135 | 1 | 0 | Start bit |

| 134 | 1 | 0 | Transmission bit |

| [133:128] | 6 | 111111 | Reserved |

| [127:1] | 127:8 | x | CID or CSD slices |

| 7:1 | x | CRC7 (included in CID or CSD) | |

| 0 | 1 | 1 | End bit |

The command/response path operates in a half-duplex mode, so that either commands can be sent or responses can be received. If the CPSM is not in the Send state, the

SDMMC_CMD output is in the Hi-Z state. Data sent on SDMMC_CMD are synchronous with the SDMMC_CK according the NEGEDGE register bit see Figure 574 .

The command and short response with CRC, the CRC generator calculates the CRC checksum for all 40 bits before the CRC code. This includes the start bit, transmission bit, command index, and command argument (or card status).

For the long response the CRC checksum is calculated only over the 120 bits of R2 CID or CSD. Note that the start bit, transmission bit and the six reserved bits are not used in the CRC calculation.

The CRC checksum is a 7-bit value:

Where \( n = 39 \) or \( 119 \) .

The CPSM allows to send a number of specific commands to handle various operating modes when CPSMEN is set, see Table 396 .

Table 396. Specific Commands overview

| VSWITCH | BOOTEN | BOOTMOD | CMDTRAN | WAITPEND | CMDSTOP | WAITINT | Description |

|---|---|---|---|---|---|---|---|

| 1 | x | x | x | x | x | x | Start Voltage Switch Sequence |

| 0 | 1 | x | x | x | x | x | Start normal boot |

| 0 | 1 | 1 | x | x | x | x | Start alternative boot |

| 0 | 0 | 1 | x | x | x | x | Stop alternative boot. |

| 0 | 0 | 0 | 1 | x | x | x | Send command with associated data transfer. |

| 0 | 0 | 0 | 0 | 1 | 1 | x | e•MMC stream data transfer, command (STOP_TRANSMISSION) pending until end of data transfer. |

| 0 | 0 | 0 | 0 | 1 | 0 | x | e•MMC stream data transfer, command different from (STOP_TRANSMISSION) pending until end of data transfer. |

| 0 | 0 | 0 | 0 | 0 | 1 | x | Send command (STOP_TRANSMISSION), stopping any ongoing data transmission. |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | Enter e•MMC wait interrupt (Wait-IRQ) mode. |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | Any other none specific command |

The command/response path implements the status flags and associated clear bits shown in Table 397 :

Table 397. Command path status flags

| Flag | Description |

|---|---|

| CMDSENT | Set at the end of the command without response. (CPSM moves from Send to Idle) |

| CMDREND | Set at the end of the command response when the CRC is OK. (CPSM moves from Receive to Idle) |

| CCRCFAIL | Set at the end of the command response when the CRC is FAIL. (CPSM moves from Receive to Idle) |

| CTIMEOUT | Set after the command when no response start bit received before the timeout. (CPSM moves from Wait to Idle) |

| CKSTOP | Set after the voltage switch (VSWITCHEN = 1) command response when the CRC is OK and the SDMMC_CK is stopped. (no impact on CPSM) |

| VSWEND | Set after the voltage switch (VSWITCH = 1) timeout of 5 ms + 1 ms. (no impact on CPSM) |

| CPSMACT | Command transfer in progress. (CPSM not in Idle state) |

The command path error handling is shown in Table 398 :

Table 398. Command path error handling

| Error | CPSM state | Cause | Card action | Host action | CPSM action |

|---|---|---|---|---|---|

| Timeout | Wait | No start bit in time | Unknown | Reset or cycle power card (1) | Move to Idle |

| CRC status | Receive | Negative status | Command ignored | Resend command (1) | Move to Idle |

| Transmission error | Command accepted | Resend command (1) |

- 1. When CMDTRANS is set, also a stop_transmission command must be sent to move the DPSM to Idle.

Data path

The data path subunit transfers data on the SDMMC_D[7:0] lines to and from cards. The data transmit path is clocked on the SDMMC_CK and sends data to the card. The data receive path is clocked on the sdmmc_rx_ck and receives data from the card. Figure 578 shows the data path block diagram.

Figure 578. Data path

![Figure 578. Data path diagram showing the internal architecture of the SDMMC interface. The diagram is divided into two main sections: 'Registers' and 'Data path'. The 'Registers' section includes a 'Registers' block and a 'FIFO' block. The 'Data path' section is a large grey box containing several sub-components: 'Status flag', 'Data timer', and 'Control logic' at the top, which connect to 'To control unit'. Below these are 'Odd receive shift register', 'Even receive shift register', 'Odd CRC', and 'Even CRC' for receiving data. At the bottom are 'Odd transmit shift register', 'Even transmit shift register', 'Odd CRC', 'Even CRC', and a 'Mux' for transmitting data. External connections include 'SDMMC_D[7:0]' (in/out), 'sdmmc_rx_ck' (in), and 'SDMMC_CK' (in/out). The diagram is labeled 'MSV40162V2' in the bottom right corner.](/RM0432-STM32L4+/4fcc6ebb614c9500a09e078fdf76f9d0_img.jpg)

The card data bus width can be programmed in the clock control register bits WIDBUS. The supported data bus width modes are:

- • If the wide bus mode is not enabled, only one bit is transferred over SDMMC_D0.

- • If the 4-bit wide bus mode is enabled, data is transferred at four bits over SDMMC_D[3:0].

- • If the 8-bit wide bus mode is enabled, data is transferred at eight bits over SDMMC_D[7:0].

Next to the data bus width the data sampling mode can be programmed in the clock control register bit DDR. The supported data sampling modes are:

- • Single data rate signaling (SDR), data is clocked on the rising edge of the clock.

- • Double data rate signaling (DDR), data is clocked on the both edges of the clock. DDR mode is only supported in wide bus mode (4-bit wide and 8-bit wide).

Note: The data sampling mode only applies to the SDMMC_D[7:0] lines. (not applicable to the SDMMC_CMD line.)

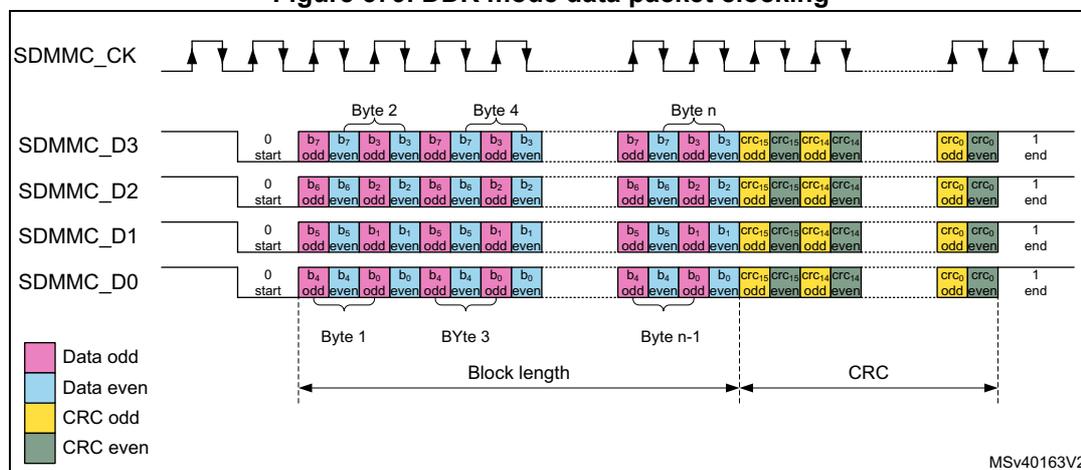

In DDR mode, data is sampled on both edges of the SDMMC_CK according the following rules, see also Figure 579 and Figure 580 :

- • On the rising edge of the clock odd bytes are sampled.

- • On the falling edge of the clock even bytes are sampled.

- • Data payload size is always a multiple of 2 Bytes.

- • Two CRC16 are computed per data line

- – Odd bits CRC16 clocked on the falling edge of the clock.

- – Even bits CRC16 clocked on the rising edge of the clock.

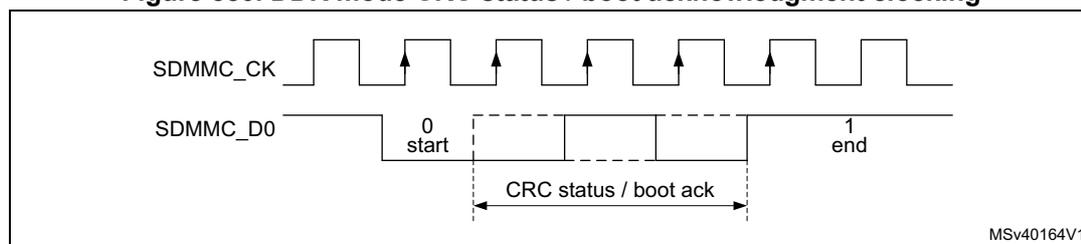

- • Start, end bits and idle conditions are full cycle.

- • CRC status / boot acknowledgment and busy signaling are full cycle and are only sampled on the rising edge of the clock.

In DDR mode the SDMMC_CK clock division must be \( \geq 2 \) .

Figure 579. DDR mode data packet clocking

Figure 580. DDR mode CRC status / boot acknowledgment clocking

Data path state machine (DPSM)

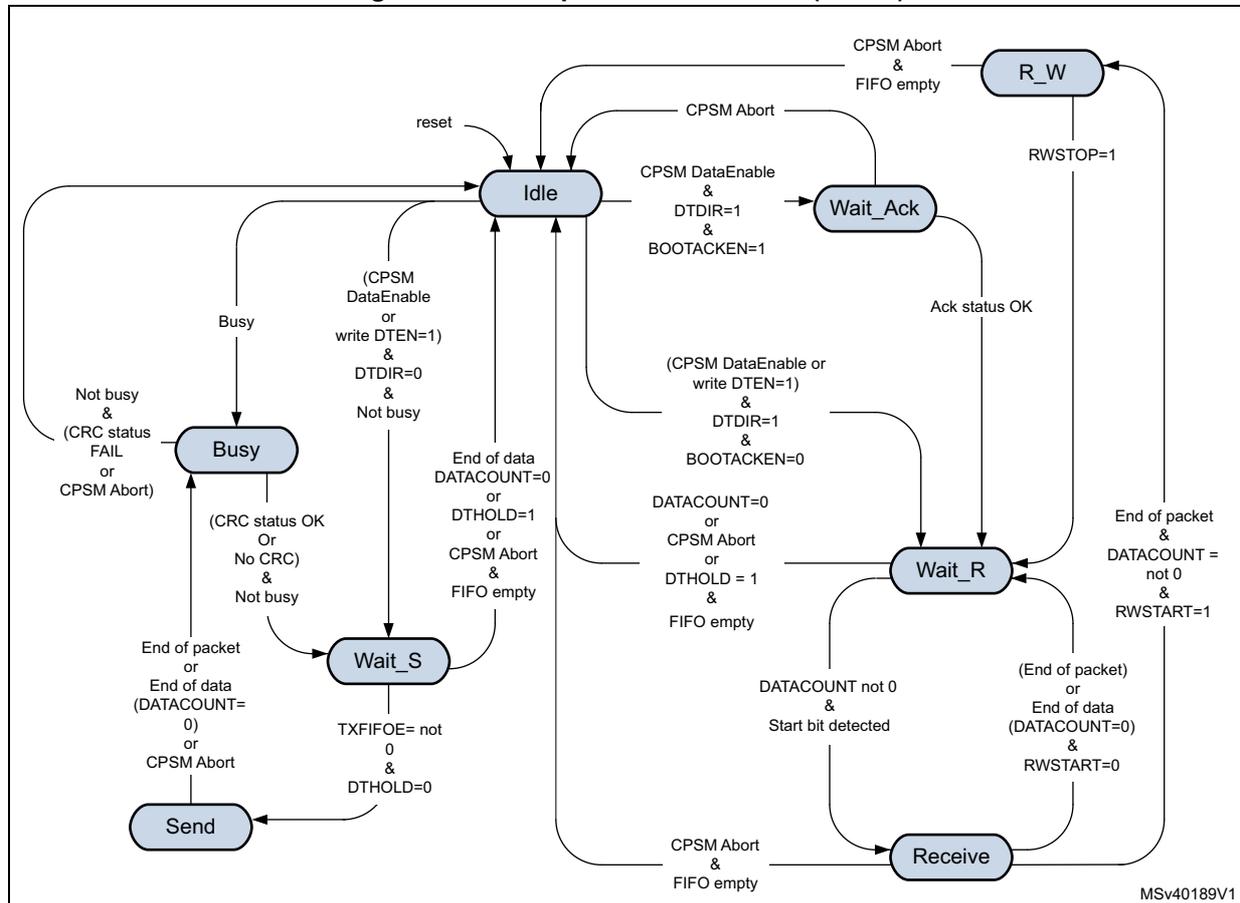

Depending on the transfer direction (send or receive), the data path state machine (DPSM) moves to the Wait_S or Wait_R state when it is enabled:

- • Send: the DPSM moves to the Wait_S state. If there is data in the transmit FIFO, the DPSM moves to the Send state, and the data path subunit starts sending data to a card.

- • Receive: the DPSM moves to the Wait_R state and waits for a start bit. When it receives a start bit, the DPSM moves to the Receive state, and the data path subunit starts receiving data from a card.

For boot operation with acknowledgment the DPSM moves to the Wait_Ack state and waits for the boot acknowledgment before moving to the Wait_R state.

The DPSM operates at SDMMC_CK. The DPSM has the following states, as shown in Figure 581. When ever the DPSM is active, i.e. not in the Idle state, the DPSMACT bit is set.

Figure 581. Data path state machine (DPSM)

stateDiagram-v2

[*] --> Idle

Idle --> Busy: Busy

Busy --> Idle: Not busy & (CRC status FAIL or CPSM Abort)

Busy --> Wait_S: (CRC status OK Or No CRC) & Not busy

Wait_S --> Idle: (CPSM DataEnable or write DTEN=1) & DTDIR=0 & Not busy

Wait_S --> Send: TXFIFOE= not 0 & DTHOLD=0

Send --> Idle: End of packet or End of data (DATACOUNT=0) or CPSM Abort

Send --> Wait_S: End of packet or End of data (DATACOUNT=0) or CPSM Abort

Idle --> Wait_S: (CPSM DataEnable or write DTEN=1) & DTDIR=0 & Not busy

Idle --> Wait_R: (CPSM DataEnable or write DTEN=1) & DTDIR=1 & BOOTACKEN=0

Idle --> Wait_Ack: (CPSM DataEnable & DTDIR=1 & BOOTACKEN=1)

Idle --> R_W: CPSM Abort & FIFO empty

Wait_S --> Idle: End of data DATACOUNT=0 or DTHOLD=1 or CPSM Abort & FIFO empty

Wait_S --> Send: TXFIFOE= not 0 & DTHOLD=0

Wait_S --> Wait_R: DATACOUNT=0 or CPSM Abort or DTHOLD=1 & FIFO empty

Wait_R --> Idle: DATACOUNT=0 or CPSM Abort or DTHOLD=1 & FIFO empty

Wait_R --> Send: DATACOUNT not 0 & Start bit detected

Wait_R --> Wait_Ack: (End of packet) or End of data (DATACOUNT=0) & RWSTART=0

Wait_R --> R_W: End of packet & DATACOUNT = not 0 & RWSTART=1

Wait_Ack --> Idle: CPSM Abort

Wait_Ack --> Wait_R: Ack status OK

Wait_Ack --> R_W: CPSM Abort & FIFO empty

- • Idle state: the data path is inactive, and the SDMMC_D[7:0] outputs are according the PWRCTRL setting. The DPSM is activated either by sending a command with CMDTRANS bit set or by setting the DTEN bit, or by detecting Busy on SDMMC_D0 (that is, after a command with R1b response).

When not busy, the DPSM activates the SDMMC_CK clock (when stopped due to power save PWRSV bit), loads the data counter with a new (DATALENGTH) value and:

- – When the data direction bit (DTDIR) indicates send, moves to the Wait_S.

- – When the data direction bit (DTDIR) indicates receive, moves to the

- - Wait_R when BOOTACKEN register bit is clear.

- - Wait_Ack when BOOTACKEN register bit is set and start the acknowledgment timeout.

When busy the DPSM keeps the SDMMC_CK clock active and move to the Busy state.

Note: DTEN must not be used to start data transfer with SD, SDIO and e•MMC cards.

- •

Wait_Ack

state: the data path waits for the boot acknowledgment token.

- – The DPSM moves to the Wait_R state if it receives an error free acknowledgment before a timeout.

- – When a pattern different from the acknowledgment is received an acknowledgment status error is generated, and the ack fail status flag (ACKFAIL) is set. The DPSM stays in Wait_Ack.

- – If it reaches a timeout (ACKTIME) before it detects a start bit, it sets the timeout status flag (ACKTIMEOUT). The DPSM stays in Wait_Ack.

- – When the CPSM Abort signal is set it moves to the Idle state and sets the DABORT flag.

- •

Wait_R

state: the data path, if the data counter is not zero and data is not hold, waits for a start bit on SDMMC_D[n:0]. If the data counter is zero or data is hold, wait for the FIFO to be empty.

- – In block mode, if a start bit is received before a timeout the DPSM moves to the Receive state and loads the data block counter with DBLOCKSIZE.

- – In SDIO multibyte mode, if a start bit is received before a timeout the DPSM moves to the Receive state and loads the data block counter with DATALENGTH.

- – In stream mode, if a start bit is received before a timeout the DPSM moves to the Receive state and loads the data counter with DATALENGTH.

- – if the data counter (DATACOUNT) equals zero (end of data) the DPSM moves to the Idle state when the receive FIFO is empty and the DATAEND flag is set.

- – If it reaches a timeout (DATETIME) before it detects a start bit, it sets the timeout status flag (DTIMEOUT) and the DPSM stays in the Wait_R state.

- – If the CPSM Abort signal is set:

If DATACOUNT > 0, the DPSM moves to the Idle state when the FIFO is empty and when IDMAEN = 0 reset with FIFOIRST, and sets the DABORT flag.

If DATACOUNT is zero normal operation is continued, there is no DABORT flag since the transfer has completed normally. - – if the DTHOLD bit is set:

- When DATACOUNT > 0, the DPSM moves to the Idle state when the receive FIFO is empty and when IDMAEN = 0 reset with FIFOIRST, and issues the DHOLD flag. When holding the timeout is disabled. When an CPSM Abort signal is received during holding, the transfer is aborted.

- - When DATACOUNT = 0, the transfer is completed normally and there is no DHOLD flag.

- - When DPSM has been started with DTEN, after an error (DTIMEOUT) the DPSM moves to the Idle state when the FIFO is empty and when IDMAEN = 0 reset with FIFORST.

- •

R_W

state: the data path Read Wait the bus.

- - The DPSM moves to the Wait_R state when the Read Wait stop bit (RWSTOP) is set, and start the receive timeout.

- - If the CPSM Abort signal is set, wait for the FIFO to be empty and when IDMAEN = 0 reset with FIFORST, then moves to the Idle state and sets the DABORT flag.

- •

Receive

state: the data path receives serial data from a card. Pack the data in bytes and written it to the data FIFO. Depending on the transfer mode selected in the data control register (DTMODE), the data transfer mode can be either block or stream:

- - In block mode, when the data block size (DBLOCKSIZE) number of data bytes are received, the DPSM waits until it receives the CRC code.

- - In SDIO multibyte mode, when the data block size (DATALENGTH) number of data bytes are received, the DPSM waits until it receives the CRC code.

- a) If the received CRC code matches the internally generated CRC code, the DPSM moves to the

- - R_W state when RWSTART = 1 and DATACOUNT > zero, the DBCKEND flag is set.

- - Wait_R state otherwise.

- b) If the received CRC code fails the internally generated CRC code any further data reception is prevented.

- - When not all data has been received (DATACOUNT > 0), the CRC fail status flag (DCRCFAIL) is set and the DPSM stays in the Receive state.

- - When all data has been received (DATACOUNT = 0), wait for the FIFO to be empty after which the CRC fail status flag (DCRCFAIL) is set and the DPSM moves to the Idle state.

- - In stream mode, the DPSM receives data while the data counter DATACOUNT > 0. When the counter is zero, the remaining data in the shift register is written to the data FIFO, and the DPSM moves to the Wait_R state.

- - When a FIFO overrun error occurs, the DPSM sets the FIFO overrun error flag (RXOVERR) and any further data reception is prevented. The DPSM stays in the Receive state.

- - When an CPSM Abort signal is received:

- - If the CPSM Abort signal is received before the 2 last bits of the data with DATACOUNT = 0, the transfer is aborted. The remaining data in the shift register is written to the data FIFO, wait for the FIFO to be empty and when IDMAEN = 0 reset with FIFORST, then the DPSM moves to the Idle state and the DABORT flag is set.

- - If the CPSM Abort signal is received during or after the 2 last bits of the transfer with DATACOUNT=0, the transfer is completed normally. The DPSM stays in the Receive state no DABORT flag is generated.

- - When DPSM has been started with DTEN, after an error (DCRCFAIL when DATACOUNT > 0, or RXOVERR) the DPSM moves to the Idle state when the FIFO is empty and when IDMAEN = 0 reset with FIFORST.

- •

Wait_S

state: the data path waits for data to be available from the FIFO.

- – If the data counter DATACOUNT > 0, waits until the data FIFO empty flag (TXFIFOE) is de-asserted and DTHOLD is not set, and moves to the Send state.

- – If the data counter (DATACOUNT) = 0 the DPSM moves to the Idle state.

- - When DTHOLD is disabled, the DATAEND flag is set.

- - When DTHOLD is enabled, the DHOLD flag is set.

- – When DTHOLD is set and the DATACOUNT > 0

- - When IDMA is enabled, the DBCKEND flag is set and subsequently the FIFO is flushed, furthermore the DPSM moves to the Idle state and the DHOLD flag is set.

- - When IDMA is disabled the DBCKEND flag is set. Wait for the FIFO to be reset by software with FIFOIRST, then DPSM moves to the Idle state and issues the DHOLD flag.

- – When DTHOLD is set and DATACOUNT = 0 the transfer is completed normally.

- – When receiving the CPSM Abort signal

- - If the CPSM Abort signal is received before the 2 last bits of the data with DATACOUNT = 0, the transfer is aborted, wait for the FIFO to be empty and when IDMAEN = 0 reset with FIFOIRST, then the DPSM moves to the Idle state and sets the DABORT flag.

- - If the CPSM Abort signal is received during or after the 2 last bits of the transfer with DATACOUNT=0, normal operation is continued, there is no DABORT flag since the transfer has completed normally.

Note: The DPSM remains in the Wait_S state for at least two clock periods to meet the \( N_{WR} \) timing requirements, where \( N_{WR} \) is the number of clock cycles between the reception of the card response and the start of the data transfer from the host.

- •

Send

state: the DPSM starts sending data to a card. Depending on the transfer mode bit in the data control register, the data transfer mode can be either block, SDIO multibyte or stream:

- – In block mode, when the data block size (DBLOCKSIZE) number of data bytes are sent, the DPSM sends an internally generated CRC code and end bit, and moves to the Busy state and start the transmit timeout.

- – In SDIO multibyte mode, when the data block size (DATALENGTH) number of data bytes are sent, the DPSM sends an internally generated CRC code and end bit, and moves to the Busy state and start the transmit timeout.

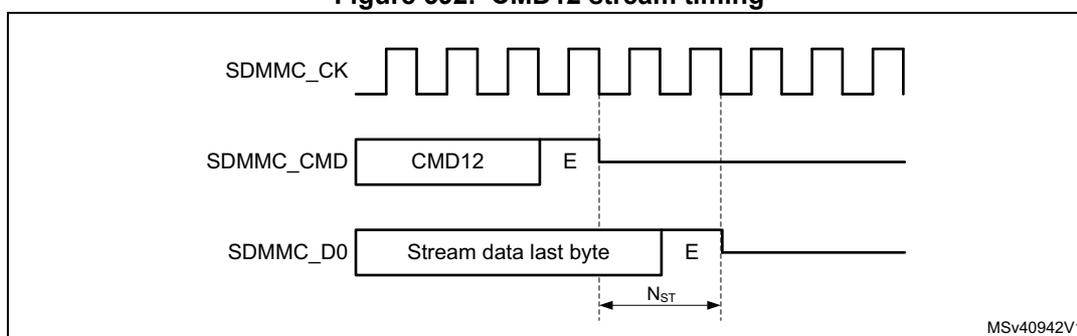

- – In stream mode, the DPSM sends data to a card while the data counter DATACOUNT > 0. When the data counter reaches zero moves to the Busy state and start the transmit timeout.

Before sending the last stream Byte according to DATACOUNT, the DPSM issues a trigger on the send CMD signal. This signal is used by the CPSM to sent any pending command. (i.e. CMD12 Stop Transmission command) - – If a FIFO underrun error occurs, the DPSM sets the FIFO underrun error flag (TXUNDERR). The DPSM stays in the Send state.

- – When receiving the CPSM Abort signal

- - If the CPSM Abort signal is received before the 2 last bits of the transfer with DATACOUNT=0, the transfer is aborted. The DPSM sends a last data bit followed by an end bit. The FIFO is disabled/flushed, and the DPSM moves to the Busy state to wait for not busy before setting the DABORT flag.

- - If the CPSM Abort signal is received during or after the 2 last bits of the transfer

with DATACOUNT=0, the transfer is completed normally, there is no DABORT flag.

- •

Busy

state: the DPSM waits for the CRC status token when expected, and wait for a not busy signal:

- – If a CRC status token is expected and indicate “non-erroneous transmission” or when there is no CRC expected:

- - it moves to the Wait_S state when SDMMC_D0 is not low (the card is not busy).

- - When the card is busy SDMMC_D0 is low it remains in the Busy state.

- – If a CRC status token is expected and indicates “erroneous transmission”.

- - When not all data has been send (DATACOUNT > 0). The DPSM waits for not busy after which the CRC fail status flag (DCRCFAIL) is set. The FIFO is disabled/flushed and the DPSM stays in the Busy state.

- - When all data has been send (DATACOUNT = 0). The DPSM waits for not busy after which the CRC fail status flag (DCRCFAIL) is set and the DPSM moves to the Idle state.

- – If a CRC status (Ncrc) timeout occurs while the DPSM is in the Busy state, it sets the data timeout flag (DTIMEOUT) and stays in the Busy state.

- – If a busy timeout occurs while the DPSM is in the Busy state, it sets the data timeout flag (DTIMEOUT) and stays in the Busy state.

- – When receiving the CPSM Abort signal in the Busy state:

- - If the CPSM Abort signal is received before the 2 last bits of the CRC response with DATACOUNT > 0, the data transfer is aborted. The DPSM waits for not busy and the FIFO to be disabled/flushed before moving to the Idle state and the DABORT flag is set.

- - If the CPSM Abort signal is received during or after the 2 last bits of the CRC response when DATACOUNT=0 or when no CRC is expected and DATACOUNT = 0 and there has been no DTIMEOUT error, the DPSM stays in the Busy state no DABORT flag is generated, since the transfer may completed normally.

- - If the CPSM Abort signal is received when a DTIMEOUT error has occurred the DPSM waits for not busy and the FIFO to be disabled/flushed before moving to the Idle state and the DABORT flag is set.

- – When entering the Busy state due to an abort in the Send state, the DPSM waits for not busy before moving to the Idle state and the DABORT flag is set.

- – When DPSM has been started with DTEN, after an error (DCRCFAIL when DATACOUNT > 0, or DTIMEOUT) the DPSM moves to the Idle state when the FIFO is reset.

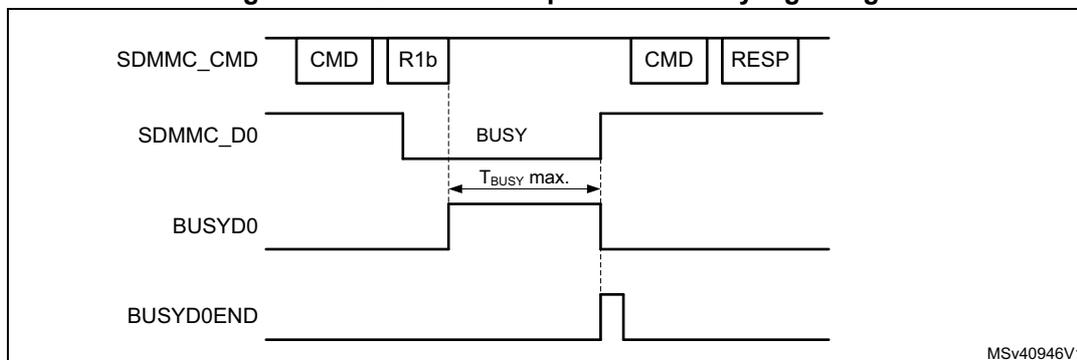

- – When the DPSM has been started due to Busy on SDMMC_D0, waits for not busy after which the Busy end status flag (BUSYD0END) is set and the DPSM moves to the Idle state.

- – If a CRC status token is expected and indicate “non-erroneous transmission” or when there is no CRC expected:

The data timer (DATATIME) is enabled when the DPSM is in the Wait_R or Busy state 2 cycles after the data block end bit, or data read command end bit, or R1b response, and generates the data timeout error (DTIMEOUT):

- • When transmitting data, the timeout occurs

- – when a CRC status is expected and no start bit is received within 8 SDMMC_CK cycles, the DTIMEOUT flag is set.

- – when the Busy state takes longer than the programmed timeout period., the DTIMEOUT flag is set.

- • When receiving data, the timeout occurs

- – when there is still data to be received DATACOUNT > 0 and no start bit is received before the programmed timeout period, the DTIMEOUT flag is set.

- • After a R1b response, the timeout occurs

- – when the Busy state takes longer than the programmed timeout period., the DTIMEOUT flag is set.

When DATATIME = 0,

- • In receive the start bit must be present 2 cycles after the data block end bit or data read command end bit.

- • In transmit busy is timed out 2 cycles after the CRC token end bit or stream data end bit.

- • After a R1b response busy is timed out 2 cycles after the response end bit.

Data can be transferred from the card to the host (transmit, send) or vice versa (receive). Data are transferred via the SDMMC_Dn data lines, they are stored in a FIFO.

Table 399. Data token format

| Description | Start bit | Data (1) | CRC16 | End bit | DTMODE |

|---|---|---|---|---|---|

| Block data | 0 | (DBLOCKSIZE, DATALENGTH) | yes | 1 | 00 |

| SDIO multibyte | 0 | (DATALENGTH) | yes | 1 | 01 |

| e•MMC stream | 0 | (DATALENGTH) | no | 1 | 10 |

- 1. The total amount of data to transfer is given by DATALENGTH. Where for Block data the amount of data in each block is given by DBLOCKSIZE.

The data token format is selected with register bits DTMODE according.

The data path implements the status flags and associated clear bits shown in Table 400 :

Table 400. Data path status flags and clear bits

| Flag | Description | |

|---|---|---|

| DATAEND | TX | Set at the end of the complete data transfer when the CRC is OK and busy has finished and both DTHOLD = 0 and DATACOUNT = 0. (DPSM moves from Wait_S to Idle) |

| RX | Set at the end of the complete data transfer when the CRC is OK and all data has been read, (DATACOUNT = 0 and FIFO is empty). (DPSM moves from Wait_R to Idle) | |

| Boot |

Table 400. Data path status flags and clear bits (continued)

| Flag | Description | |

|---|---|---|

| DCRCFAIL | TX | Set at the end of the CRC when FAIL and busy has finished. (DPSM stay in Busy when there is still data to send and wait for CPSM Abort) (DPSM moves from Busy to Idle when all data has been sent) or DPSM has been started with DTEN |

| RX | Set at the end of the CRC when FAIL and FIFO is empty. (DPSM stays in Receive when there is still data to be received and wait for CPSM Abort) (DPSM moves from Receive to Idle when all data has been received or DPSM has been started with DTEN) | |

| Boot | ||

| ACKFAIL | Boot | Set at the end of the boot acknowledgment when fail. (DPSM stays in Wait_Ack and wait for CPSM Abort) |

| DTIMEOUT | CMD R1b | Set after the command response no end of busy received before the timeout. (DPSM stays in Busy and wait for CPSM Abort) |

| TX | Set when no CRC token start bit received within Ncrc, or no end of busy received before the timeout. (DPSM stays in Busy and wait for CPSM Abort) (When DPSM has been started with DTEN move to Idle) Note: The DCRCFAIL flag may also be set when CRC failed before the busy timeout. | |

| RX | Set when no start bit received before the timeout. (DPSM stays in Wait_R and wait for CPSM Abort) (When DPSM has been started with DTEN move to Idle) | |

| Boot | ||

| ACKTIMEOUT | Boot | Set when no start bit received before the timeout. (DPSM stays in Wait_Ack and wait for CPSM Abort) |

| DBCKEND | TX | When DTHOLD = 1 and IDMAEN = 0: Set at the end of data block transfer when the CRC is OK and busy has finished, when data transfer is not complete (DATACOUNT >0). (DPSM moves from Busy to Wait_S) |

| RX | When RWSTART = 1: Set at the end of data block transfer when the CRC is OK, when data transfer is not complete (DATACOUNT > 0). (DPSM moves from Receive to R_W) | |

| Boot | ||

| DHOLD | TX | When DTHOLD = 1: Set at the end of data block transfer when the CRC is OK and busy has finished. (DPSM moves from Wait_S to Idle) |

| RX | When DTHOLD = 1: Set at the end of data block transfer when the CRC is OK and all data has been read (FIFO is empty), when data transfer is not complete (DATACOUNT >0). (DPSM moves from Wait_R to Idle) | |

| DABORT | CMD R1b | When CPSM Abort event has been sent by the CPSM and busy has finished. (DPSM moves from Busy to Idle) |

| TX | ||

| RX | When CPSM Abort event has been sent by the CPSM before the 2 last bits of the transfer. (DPSM moves from any state to Idle) | |

| Boot | ||

| BUSYD0END | CMD R1b | Set after the command response when end of busy before the timeout. (DPSM moves from Busy to Idle) |

| DPSMACT | Data transfer in progress. (DPSM not in Idle state) |

The data path error handling is shown in Table 401 :

Table 401. Data path error handling

| Error | DPSM state | Cause | Card action | Host action | DPSM action |

|---|---|---|---|---|---|

| Timeout | Wait_Ack | No Ack in time | unknown | Card cycle power | Stay in Wait_Ack (reset the SDMMC with the RCC.SDMMCxRST register bit) |

| Wait_R | No start bit in time | unknown | Stop data reception Send stop transmission command | ||

| unknown | Stop boot procedure | ||||

| Busy | Busy too long (due to data transfer) | unknown | Stop data reception Send stop transmission command | On CPSM Abort move to Idle | |

| Busy too long (due to R1b) | unknown | Send reset command | |||

| CRC | Receive | transmission error | Send further data | Stop data reception Send stop transmission command | On CPSM Abort move to Idle |

| CRC status | Busy | Negative status | Ignore further data | Stop data transmission Send stop transmission command | On CPSM Abort move to Idle |

| transmission error | wait for further data | ||||

| Ack status | Wait_Ack | transmission error | Send boot data | Stop boot procedure | On CPSM Abort move to Idle |

| Overrun | Receive | FIFO full | Send further data | Stop data reception Send stop transmission command | On CPSM Abort move to Idle |

| Underrun | Send | FIFO empty | Receive further data | Stop data transmission Send stop transmission command | On CPSM Abort move to Idle |

Data FIFO

The data FIFO (first-in-first-out) subunit contains the transmit and receive data buffer. A single FIFO is used for either transmit or receive as selected by the DTDIR bit. The FIFO contain a 32-bit wide, 16-word deep data buffer and control logic. Because the data FIFO operates in the AHB clock domain (sdmmc_hclk), all signals from the subunits in the SDMMC clock domain (SDMMC_CK/sdmmc_rx_ck) are resynchronized.

The FIFO can be in one of the following states:

- – The transmit FIFO refers to the transmit logic and data buffer when sending data out to the card. (DTDIR = 0)

- – The receive FIFO refers to the receive logic and data buffer when receiving data in from the card. (DTDIR = 1)

The end of a correctly completed SDMMC data transfer from the FIFO is indicated by the DATAEND flags driven by the data path subunit. Any incorrect (aborted) SDMMC data transfer from the FIFO is indicated by one of the error flags (DCRCFAIL, DTOUT, DABORT) driven by the data path subunit, or one of the FIFO error flags (TXUNDERR, RXOVERR) driven by the FIFO control.

The data FIFO can be accessed in the following ways, see Table 402 .

Table 402. Data FIFO access

| Data FIFO access | IDMAEN |

|---|---|

| From firmware via AHB slave interface | 0 |

| From IDMA via AHB master interface | 1 |

Transmit FIFO:

Data can be written to the transmit FIFO when the DPSM has been activated (DPSMACT = 1).

When IDMAEN = 1 the FIFO is fully handled by the IDMA.

When IDMAEN = 0 the FIFO is controlled by firmware via the AHB slave interface. The transmit FIFO is accessible via sequential addresses. The transmit FIFO contains a data output register that holds the data word pointed to by the read pointer. When the data path subunit has loaded its shift register, it increments the read pointer and drives new data out. The transmit FIFO is handled in the following way:

- 1. Write the data length into DATALENGTH and the block length in DBLOCKSIZE.

- – For block data transfer (DTMODE = 0), DATALENGTH must be an integer multiple of DBLOCKSIZE.

- 2. Set the SDMMC in transmit mode (DTDIR = 0).

- – Configures the FIFO in transmit mode.

- 3. Enable the data transfer

- – either by sending a command from the CPSM with the CMDTRANS bit set

- – or by setting DTEN bit

- 4. When (DPSMACT = 1) write data to the FIFO.

- – The DPSM stays in the Wait_S state until FIFO is full (TXFIFOF = 1), or the number indicated by DATALENGTH.

- - The SDMMC keeps sending data as long as FIFO is not empty, hardware flow control during data transfer is used to prevent FIFO underrun.

- 5. Write data to the FIFO.

- – When the FIFO is handled by software, wait until the FIFO is half empty (TXFIFOHE flag), write data to the FIFO until FIFO is full (TXFIFOF = 1), or last data has been written.

- – When the FIFO is handled by the IDMA, the IDMA transfers the FIFO data.

- 6. When last data has been written wait for end of data (DATAEND flag)

- – SDMMC has completely sent all data and the DPSM is disabled (DPSMACT = 0).

In case of a data transfer error or transfer hold when IDMAEN = 0, firmware must stop writing to the FIFO and flush and reset the FIFO with the FIFOIRST register bit.

The transmit FIFO status flags are listed in Table 403 .

Table 403. Transmit FIFO status flags

| Flag | Description |

|---|---|

| TXFIFOF | Set to high when all transmit FIFO words contain valid data. |

| TXFIFOE | Set to high when the transmit FIFO does not contain valid data. |

| TXFIFOHE | Set to high when half or more transmit FIFO words are empty. |

| TXUNDERR | Set to high when an underrun error occurs. This flag is cleared by writing to the SDMMC Clear register. |

Receive FIFO:

Data can be read from the receive FIFO when the DPSM is activated (DPSMACT = 1).

When IDMAEN = 1 the FIFO is fully handled by the IDMA.

When IDMAEN = 0 the FIFO is controlled by firmware via the AHB slave interface. When the data path subunit receives a word of data, it drives the data on the write databus. The write pointer is incremented after the write operation completes. On the read side, the contents of the FIFO word pointed to by the current value of the read pointer is driven onto the read databus. The receive FIFO is accessible via sequential addresses.

The receive FIFO is handled in the following way:

- 1. Write the data length into DATALENGTH and the block length in DBLOCKSIZE.

- – For block data transfer (DTMODE = 0), DATALENGTH must be an integer multiple of DBLOCKSIZE.

- 2. Set the SDMMC in receive mode (DTDIR = 1).

- – Configures the FIFO in receive mode.

- 3. Enable the DPSM transfer

- – either by sending a command from the CPSM with the CMDTRANS bit set

- – or by setting DTEN bit.

- 4. When (DPSMACT = 1) the FIFO is ready to receive data.

- – The DPSM writes the received data to the FIFO.

- - The SDMMC keeps receiving data as long as FIFO is not full, hardware flow control during the data transfer is used to prevent FIFO overrun.

- – The DPSM writes the received data to the FIFO.

- 5. Read data from the FIFO.

- – When the FIFO is handled by software, wait until the FIFO is half full (RXFIFOHF flag), read data from the FIFO until FIFO is empty (RXFIFOE = 1).

- - When last data has been received end of data (DATAEND flag), read data from the FIFO until FIFO is empty (RXFIFOE = 1).

- – When the FIFO is handled by the IDMA, the IDMA transfers the FIFO date.

- – When the FIFO is handled by software, wait until the FIFO is half full (RXFIFOHF flag), read data from the FIFO until FIFO is empty (RXFIFOE = 1).

- 6. SDMMC has completely received all data and the DPSM is disabled (DPSMACT = 0).

In case of a data transfer hold when IDMAEN = 0, the firmware must read the remaining data until the FIFO is empty and reset the FIFO with the FIFORST register bit. This causes the DPSM to go to the Idle state (DPSMACT = 0).

In case of a data transfer error when IDMAEN = 0, the firmware must stop reading the FIFO and flush and reset the FIFO with the FIFORST register bit. This causes the DPSM to go to the Idle state (DPSMACT = 0).

The receive FIFO status flags are listed in Table 404 .

Table 404. Receive FIFO status flags

| Flag | Description |

|---|---|

| RXFIFOF | Set to high when all receive FIFO words contain valid data |

| RXFIFOE | Set to high when the receive FIFO does not contain valid data. |

| RXFIFOHF | Set to high when half or more receive FIFO words contain valid data. |

| RXOVERR | Set to high when an overrun error occurs. This flag is cleared by writing to the SDMMC Clear register. |

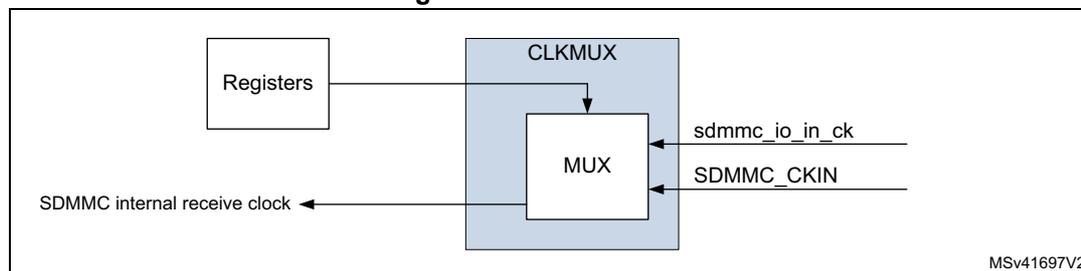

CLKMUX unit

The CLKMUX selects the source for clock sdmmc_rx_ck to be used with the received data and command response. The receive data clock source can be selected by the clock control register bit SELCLKRX, between:

- • sdmmc_io_in_ck bus master main feedback clock.

- • SDMMC_CKIN external bus feedback clock.

The sdmmc_io_in_ck is selected when there is no external driver, with DS and HS.

The SDMMC_CKIN is selected when there is an external driver with SDR12, SDR25, SDR50 and DDR50.

Figure 582. CLKMUX unit

The sdmmc_rx_ck source must be changed when the CPSM and DPSM are in the Idle state.

54.5.5 SDMMC AHB slave interface

The AHB slave interface generates the interrupt requests, and accesses the SDMMC adapter registers and the data FIFO. It consists of a data path, register decoder, and interrupt logic.

SDMMC FIFO

The FIFO access is restricted to word access only:

- • In transmit FIFO mode

- – Data are written to the FIFO in words (32-bits) until all data according DATALNGTH has been transfered. When the DATALNGTH is not an integer multiple of 4, the last remaining data (1, 2 or 3 bytes) are written with a word transfer.

- • In receive FIFO mode

- – Data are read from the FIFO in words (32-bits) until all data according DATALNGTH has been transfered. When the DATALNGTH is not an integer multiple of 4, the last remaining data (1, 2 or 3 bytes) are read with a word transfer padded with 0 value bytes.

When accessing the FIFO with half word or byte accesses an AHB bus fault is generated.

SDMMC interrupts

The interrupt logic generates an interrupt request signal that is asserted when at least one of the unmasked status flags is active. A mask register is provided to allow selection of the conditions that generate an interrupt. A status flag generates the interrupt request if a corresponding mask flag is set. Some status flags require an implicit clear in the clear register.

54.5.6 SDMMC AHB master interface

The AHB master interface is used to transfer the data between a memory and the FIFO using the SDMMC IDMA.

SDMMC IDMA

Direct memory access (DMA) is used to provide high-speed transfer between the SDMMC FIFO and the memory. The AHB master optimizes the bandwidth of the system bus. The SDMMC internal DMA (IDMA) provides one channel to be used either for transmit or receive.

The IDMA is enabled by the IDMAEN bit and supports burst transfers of 8 beats.

- • In transmit burst transfer mode:

- – Data are fetched in burst from memory whenever the FIFO is empty for the number of burst transfers, until all data according DATALNGTH has been transferred. When the DATALNGTH is not an integer multiple of the burst size the remaining, smaller than burst size data is transferred using single transfer mode. When the DATALNGTH is not an integer multiple of 4, the last remaining data (1, 2 or 3 bytes) are fetched with a word transfer.

- • In receive burst transfer mode:

- – Data are stored in burst in to memory whenever the FIFO contains the number of burst transfers, until all data according DATALNGTH has been transferred. When the DATALNGTH is not an integer multiple of the burst transfer the remaining, smaller than burst size data, is transferred using single transfer mode. When the DATALNGTH is not an integer multiple of 4, the last remaining data (1, 2 or 3 bytes) are stored with halfword and or byte transfers.

In addition the IDMA provides the following channel configurations selected by bit IDMABMODE:

- • single buffered channel

- • double buffered channel

Single buffered channel

In single buffer configuration the data at the memory side is accessed in a linear matter starting from the base address IDMABASE0. When the IDMA has finished transferring all data the and the DPSM has completed the transfer the DATAEND flag is set.

Double buffered channel

In double buffer configuration the data at the memory side is subsequently accessed from 2 buffers, one located from base address IDMABASE0 and a second located from base address IDMABASE1. This allows firmware to process one memory buffer while the IDMA is accessing the other memory buffer. The size of the memory buffers is defined by IDMABSIZE. The buffer size must be an integer multiple of the burst size. It is possible to update the base address of the buffers on-the-fly when the channel is enabled, the following rule apply:

- • When IDMABACT bit is '0' the IDMA hardware uses the IDMABASE0 to access memory. When attempting to write to this register by Firmware the write is discarded, IDMABASE0 data is not changed. Firmware is allowed to write IDMABASE1.

- • When IDMABACT bit is '1' the IDMA hardware uses the IDMABASE1 to access memory. When attempting to write to this register by Firmware the write is discarded, IDMABASE1 data is not changed. Firmware is allowed to write IDMABASE0.

When the IDMA has finished transferring the data of one buffer the buffer transfer complete flag (IDMABTC) is set and the IDMABACT bit toggles where after the IDMA continues

transferring data from the other buffer. When the IDMA has finished transferring all data and the DPSM has completed the transfer the DATAEND flag is set.

The IDMABASEn address must be word aligned.

IDMA transfer error management

An IDMA transfer error can occur:

- • When reading or writing a reserved address space.

On a IDMA transfer error subsequent IDMA transfers are disabled and an IDMATE flag is set. Depending when the IDMA transfer error occurs, it normally causes the generation of a TXUNDERR or RXOVERR error.

The behavior of the IDMATE flag depend on when the IDMA transfer error occurs during the SDMMC transfer:

- • An IDMA transfer error is detected before any SDMMC transfer error (TXUNDERR, RXOVERR, DCRCFAIL, or DTIMEOUT):

- – The IDMATE flag is set at the same time as the SDMMC transfer error flag.

- – The TXUNDERR, RXOVERR, DCRCFAIL, or DTIMEOUT interrupt is generated.

- • An IDMA transfer error is detected during a STOP_TRANSMISSION command:

- – The IDMATE flag is set at the same time as the DABORT flag.

- – The DABORT interrupt is generated.

- • An IDMA transfer error is detected at the end of the SDMMC transfer (DHOLD, or DATAEND).

- – The IDMATE flag is set at the end of the SDMMC transfer.

- – A SDMMC transfer end interrupt is generated and a DHOLD or DATAEND flag is set.

The IDMATE is generated on an other SDMMC transfer interrupt (TXUNDERR, RXOVERR, DCRCFAIL, DTIMEOUT, DABORT, DHOLD, or DATAEND).

54.5.7 AHB and SDMMC_CK clock relation

The AHB must at least have 3x more bandwidth than the SDMMC bus bandwidth i.e. for SDR50 4-bit mode (50 Mbyte/s) the minimum sdmmc_hclk frequency is 37.5 MHz (150 Mbyte/s).

Table 405. AHB and SDMMC_CK clock frequency relation

| SDMMC bus mode | SDMMC bus width | Maximum SDMMC_CK [MHz] | Minimum AHB clock [MHz] |

|---|---|---|---|

| e•MMC DS | 8 | 26 | 19.5 |

| e•MMC HS | 8 | 52 | 39 |

| e•MMC DDR52 | 8 | 52 | 78 |

| SD DS / SDR12 | 4 | 25 | 9.4 |

| SD HS / SDR25 | 4 | 50 | 18.8 |

| SD DDR50 | 4 | 50 | 37.5 |

| SD SDR50 | 4 | 100 | 37.5 |

54.6 Card functional description

54.6.1 SD I/O mode

The following features are SDMMC specific operations:

- • SDIO interrupts

- • SDIO suspend/resume operation (write and read suspend)

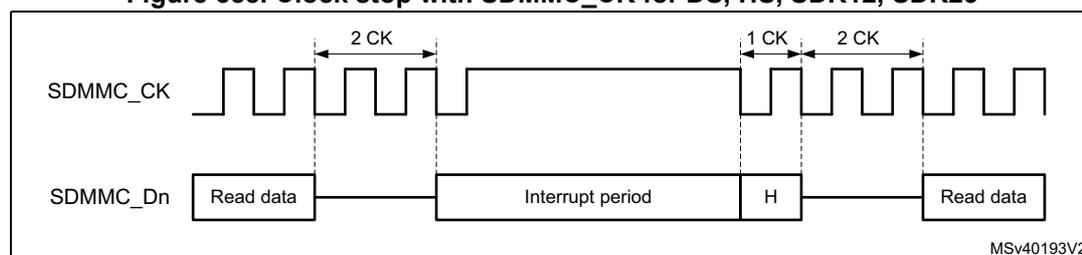

- • SDIO Read Wait operation by stopping the clock

- • SDIO Read Wait operation by SDMMC_D2 signaling

Table 406. SDIO special operation control

| Operation mode | SDIOEN | RWMOD | RWSTOP | RWSTART | DTDIR |

|---|---|---|---|---|---|

| Interrupt detection | 1 | X | X | X | X |

| Suspend/Resume operation | X | X | X | X | X |

| Read Wait SDMMC_CK clock stop (START) | X | 1 | 0 | 1 | 1 |

| Read Wait SDMMC_CK clock stop (STOP) | X | 1 | 1 | 1 | 1 |

| Read Wait SDMMC_D2 signaling (START) | X | 0 | 0 | 1 | 1 |

| Read Wait SDMMC_D2 signaling (STOP) | X | 0 | 1 | 1 | 1 |

SD I/O interrupts

To allow the SD I/O card to interrupt the host, an interrupt function is available on pin 8 (shared with SDMMC_D1 in 4-bit mode) on the SD interface. The use of the interrupt is optional for each card or function within a card. The SD I/O interrupt is level-sensitive, which means that the interrupt line must be held active (low) until it is either recognized and acted upon by the host or deasserted due to the end of the interrupt period. After the host has serviced the interrupt, the interrupt status bit is cleared via an I/O write to the appropriate bit in the SD I/O card internal registers. The interrupt output of all SD I/O cards is active low and the application must provide external pull-up resistors on all data lines (SDMMC_D[3:0]).

In SD 1-bit mode pin 8 is dedicated to the interrupt function (IRQ), and there are no timing constraints on interrupts.

In SD 4-bit mode the host samples the level of pin 8 (SDMMC_D1/IRQ) into the interrupt detector only during the interrupt period. At all other times, the host interrupt ignores this value. The interrupt period begins when interrupts are enabled at the card and SDIOEN bit is set see register settings in Table 406 .

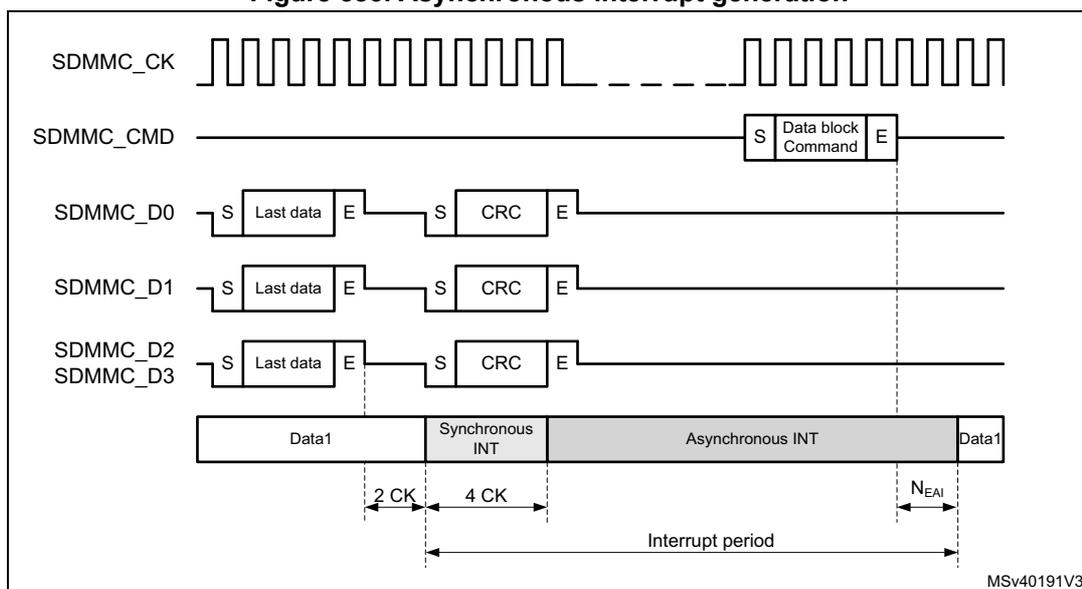

In 4-bit mode the card can generate a synchronous or asynchronous interrupt as indicated by the card CCCR register SAI and EAI bits.

- • Synchronous interrupt, require the SDMMC_CK to be active.

- • Asynchronous interrupt, can be generated when the SDMMC_CK is stopped, 4 cycles after the start of the card interrupt period following the last data block.

Figure 583. Asynchronous interrupt generation

The diagram illustrates the timing for asynchronous interrupt generation. It shows the following signals:

- SDMMC_CK : A continuous clock signal.

- SDMMC_CMD : Shows a 'Data block Command' with start (S) and end (E) bits.

- SDMMC_D0, SDMMC_D1, SDMMC_D2, SDMMC_D3 : Data lines showing 'Last data' (with S and E bits) followed by 'CRC' (with S and E bits).

- Interrupt period : A shaded timeline below the signals. It transitions from 'Data1' to 'Synchronous INT' (lasting 2 CK + 4 CK), then to 'Asynchronous INT', and finally back to 'Data1'. The 'Asynchronous INT' period ends at the start of the 'Data block Command' on the CMD line. A timing parameter N EA1 is shown at the end of the Asynchronous INT period.

The timing of the interrupt period is depended on the bus speed mode:

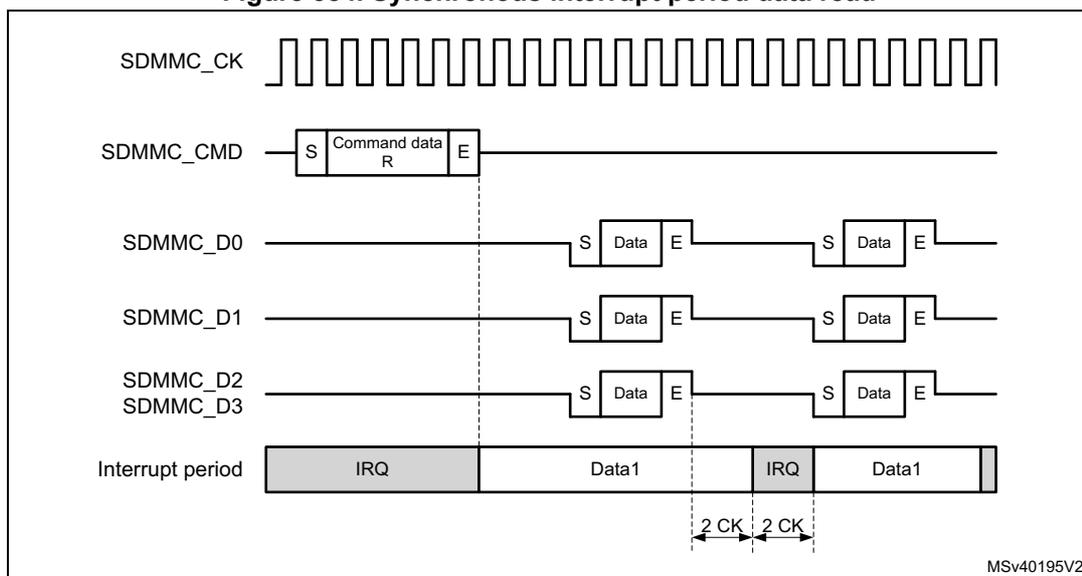

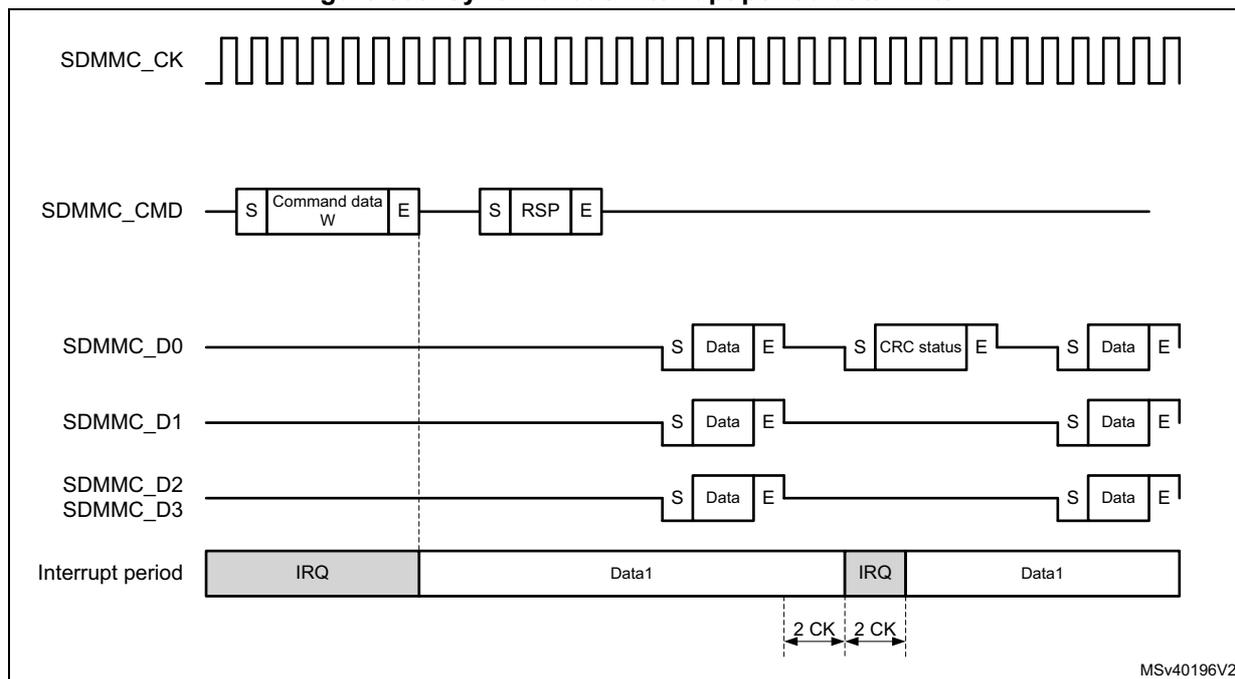

In DS, HS, SDR12, and SDR25 mode, selected by register bit BUSSPEED, the interrupt period is synchronous to the SD clock.

- • The interrupt period ends at the next clock from the end bit of a command that transfers data block(s) (Command sent with the CMDTRANS bit is set), or when the DTEN bit is set.

- • The interrupt period resumes 2 SDMMC_CK after the completion of the data block.

- • At the data block gap the interrupt period is limited to 2 SDMMC_CK cycles.

Note: DTEN must not be used to start data transfer with SD and e•MMC cards.

Figure 584. Synchronous interrupt period data read

The diagram illustrates the timing for synchronous interrupt period data read. It shows the following signals:

- SDMMC_CK : A continuous clock signal.

- SDMMC_CMD : Shows a 'Command data R' with start (S) and end (E) bits.

- SDMMC_D0, SDMMC_D1, SDMMC_D2, SDMMC_D3 : Data lines showing 'Data' blocks with start (S) and end (E) bits.

- Interrupt period : A shaded timeline showing 'IRQ' periods alternating with 'Data1' blocks. The IRQ period starts after the end of the command on the CMD line. Between two 'Data1' blocks, there is an IRQ period lasting 2 CK + 2 CK.

Figure 585. Synchronous interrupt period data write

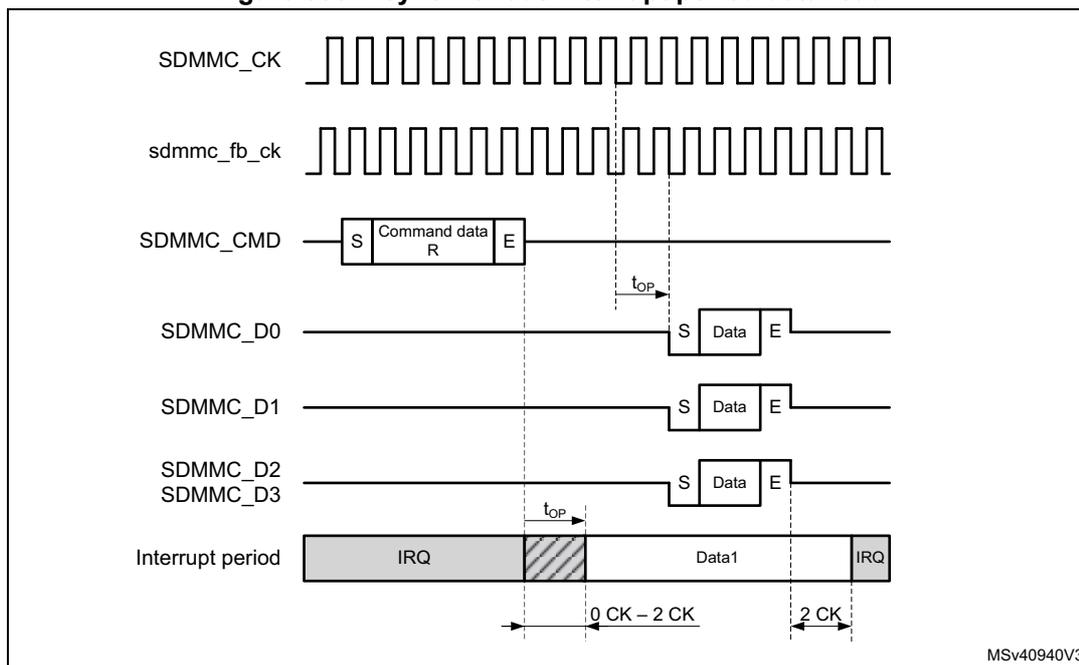

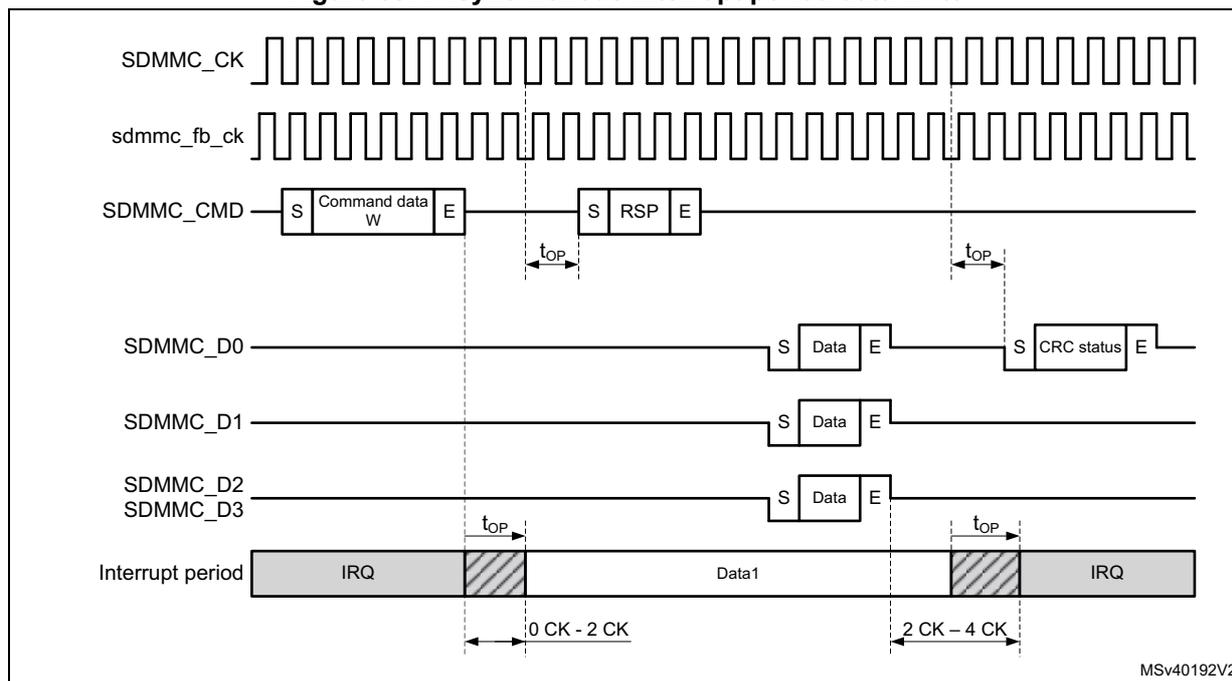

In SDR50 and DDR50, selected by register bit BUSSPEED, due to propagation delay from the card to host, the interrupt period is asynchronous.

- • The card interrupt period ends after 0 to 2 SDMMC_CLK cycles after the end bit of a command that transfers data block(s) (Command sent with the CMDTRANS bit is set), or when the DTEN bit is set. At the host the interrupt period ends after the end bit of a command that transfers data block(s). A card interrupt issued in the 1 to 2 cycles after the command end bit are not detected by the host during this interrupt period.

- • The card interrupt period resumes 2 to 4 SDMMC_CLK after the completion of the last data block. The host resumes the interrupt period always 2 cycles after the last data block.

- • There is NO interrupt period at the data block gap.

Note: DTEN must not be used to start data transfer with SD and e•MMC cards.

Figure 586. Asynchronous interrupt period data read

Figure 586 shows the timing diagram for an asynchronous interrupt period during a data read operation. The signals shown are SDMMC_CLK, sdmmc_fb_ck, SDMMC_CMD, SDMMC_D0, SDMMC_D1, SDMMC_D2/SDMMC_D3, and the Interrupt period. The SDMMC_CMD signal shows a Command data R block. The SDMMC_D0, SDMMC_D1, and SDMMC_D2/SDMMC_D3 signals show Data blocks. The Interrupt period signal shows an IRQ signal. The setup time (t op ) is indicated as 0 CK - 2 CK, and the hold time is indicated as 2 CK. The diagram is labeled MSV40940V3.

Figure 587. Asynchronous interrupt period data write

Figure 587 shows the timing diagram for an asynchronous interrupt period during a data write operation. The signals shown are SDMMC_CLK, sdmmc_fb_ck, SDMMC_CMD, SDMMC_D0, SDMMC_D1, SDMMC_D2/SDMMC_D3, and the Interrupt period. The SDMMC_CMD signal shows a Command data W block and an RSP block. The SDMMC_D0, SDMMC_D1, and SDMMC_D2/SDMMC_D3 signals show Data blocks. The SDMMC_D0 signal also shows a CRC status block. The Interrupt period signal shows an IRQ signal. The setup time (t op ) is indicated as 0 CK - 2 CK, and the hold time is indicated as 2 CK - 4 CK. The diagram is labeled MSV40192V2.

When transferring Open-ended multiple block data and using DTMODE “block data transfer ending with STOP_TRANSMISSION command”, the SDMMC masks the interrupt period after the last data block until the end of the CMD12 STOP_TRANSMISSION command.

The interrupt period is applicable for both memory and I/O operations.

In 4-bit mode interrupts can be differentiated from other signaling according Table 407 .

Table 407. 4-bit mode Start, interrupt, and CRC-status Signaling detection

| SDMMC data line | Start | Interrupt | CRC-status |

|---|---|---|---|

| SDMMC_D0 | 0 | 1 or CRC-status | 0 |

| SDMMC_D1 | 0 | 0 | X |

| SDMMC_D2 | 0 | 1 or Read Wait | X |

| SDMMC_D3 | 0 | 1 | X |

SD I/O suspend and resume

This function is NOT supported in SDIO version 4.00 or later.

Within a multifunction SD I/O or a card with both I/O and memory functions, there are multiple devices (I/O and memory) that share access to the e•MMC/SD bus. To share access to the host among multiple devices, SD I/O and combo cards optionally implement the concept of suspend/resume. When a card supports suspend/resume, the host can temporarily halt (suspend) a data transfer operation to one function or memory to free the bus for a higher-priority transfer to a different function or memory. After this higher-priority transfer is complete, the original transfer is restarted (resume) where it left off.

To perform the suspend/resume operation on the bus, the host performs the following steps:

- 1. Determines the function currently using the SDMMC_D[3:0] line(s)

- 2. Requests the lower-priority or slower transaction to suspend

- 3. Waits for the transaction suspension to complete

- 4. Begins the higher-priority transaction

- 5. Waits for the completion of the higher priority transaction

- 6. Restores the suspended transaction

The card receiving a suspend command responds with its current bus status. Only when the bus has been suspended by the card the bus status indicates suspension completed.

There are different suspend cases conditions:

- • Suspend request accepted prior to the start of data transfer.

- • Suspend request not accepted, (due to data being transfered at the same time), the host keeps checking the request until it is accepted. (data transfer has suspended)

- • Suspend request during write busy.

- • Suspend request with write multiple.

- • Suspend request during Read Wait.

For the host to know if the bus has been released it must check the status of the suspend request, suspension completed.

When the bus status of the suspend request response indicates suspension completed, the card has released the bus. At this time the state of the suspended operation must be saved where after an other operation can start.

The suspend command must be sent with the CMDSUSPEND bit set. This allows to start the interrupt period after the suspend command response when the bus is suspended (response bit BS = 0).

The hardware does not save the number of remaining data to be transferred when resuming the suspended operation. It is up to firmware to determine the data that has been transferred and resume with the correct remaining number of data bytes.

While receiving data from the card, the SDMMC can suspend the read operation after the read data block end (DPSM in Wait_R). After receiving the suspend acknowledgment response from the card the following steps must be taken by firmware:

- 1. The normal receive process must be stopped by setting DTHOLD bit.

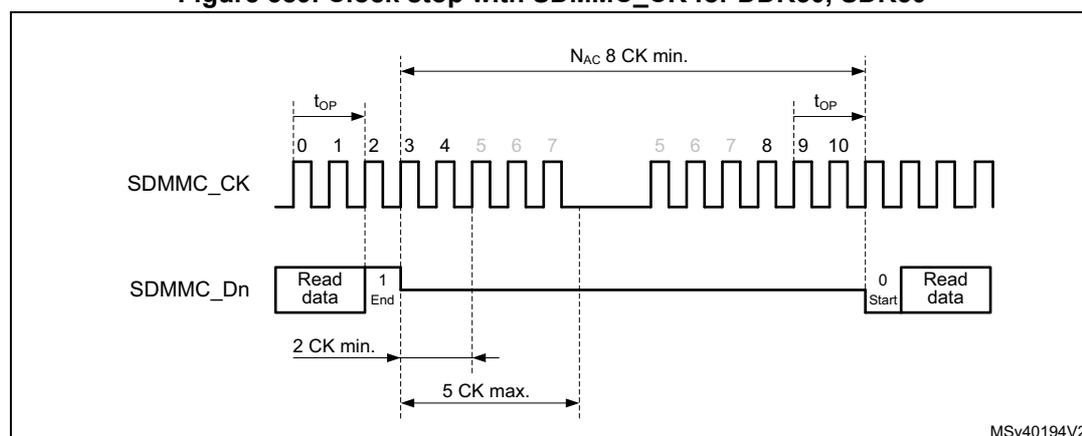

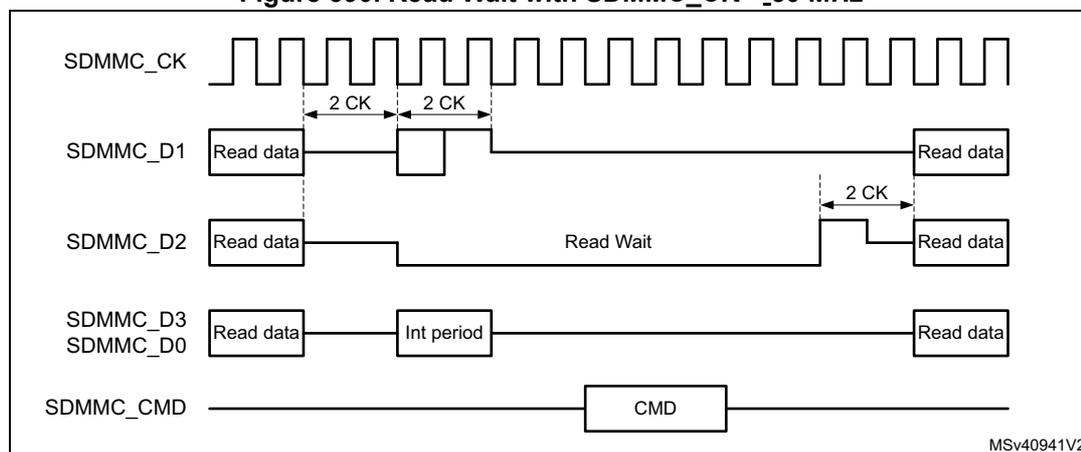

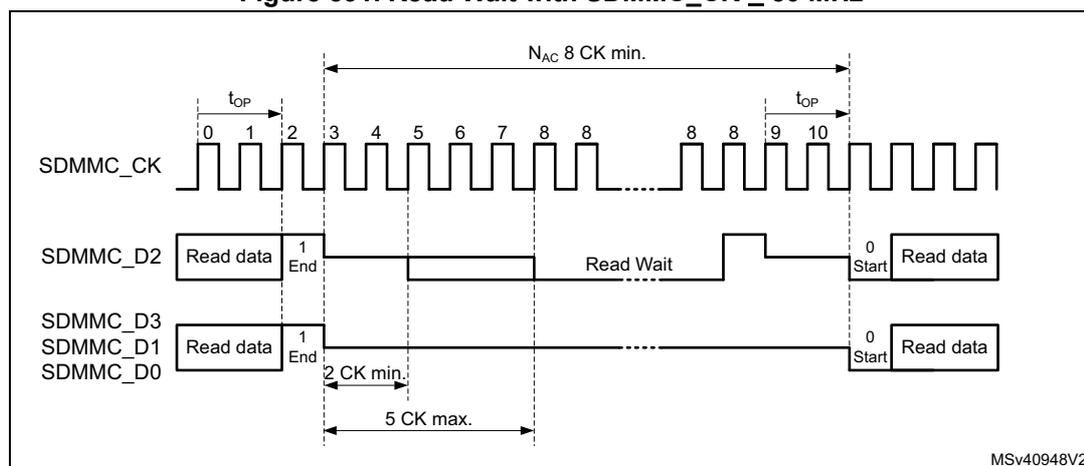

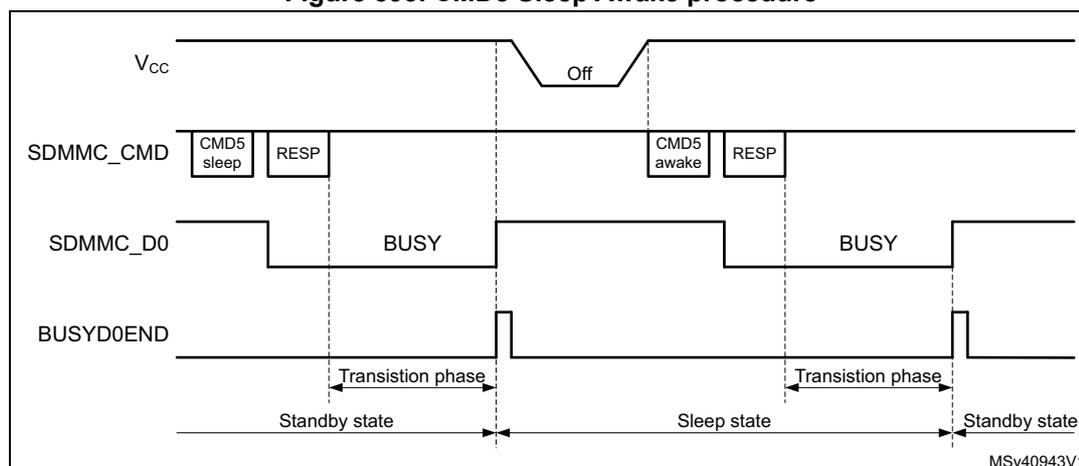

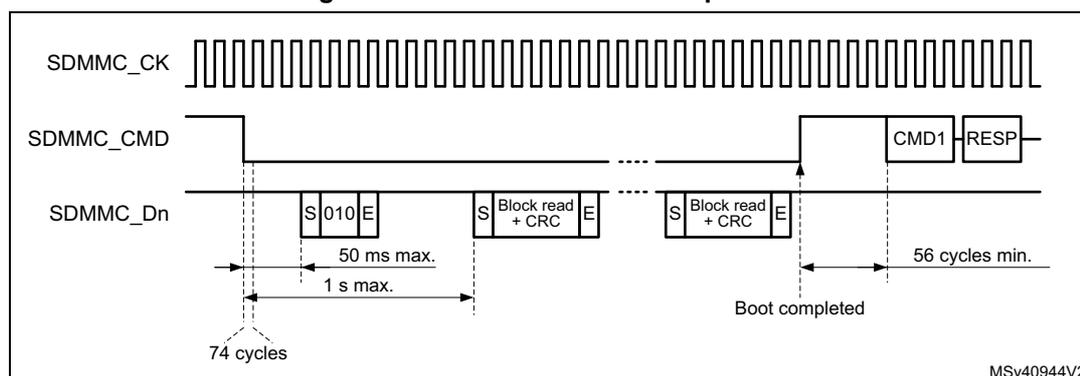

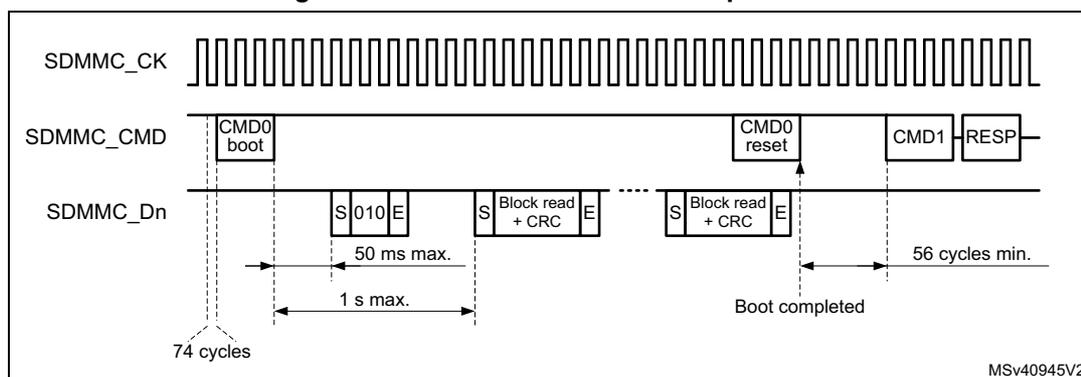

- a) The remaining number of data bytes in the FIFO must be read until the receive FIFO is empty (RXFIFOE flag is set), and when IDMAEN = 0 the FIFO must be reset with FIFORST.