30. SD/SDIO/MMC card host interface (SDMMC)

30.1 SDMMC main features

The SD/SDIO MMC card host interface (SDMMC) provides an interface between the APB2 peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The MultiMediaCard system specifications are available through the MultiMediaCard Association website, published by the MMCA technical committee.

SD memory card and SD I/O card system specifications are available through the SD card Association website.

The SDMMC features include the following:

- • Full compliance with MultiMediaCard System Specification Version 4.2 . Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- • Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- • Full compliance with SD Memory Card Specifications Version 2.0

- • Full compliance with SD I/O Card Specification Version 2.0 : card support for two different databus modes: 1-bit (default) and 4-bit

- • Data transfer up to 50 MHz for the 8 bit mode

- • Data and command output enable signals to control external bidirectional drivers.

- Note:

- 1 The SDMMC does not have an SPI-compatible communication mode.

- 2 The SD memory card protocol is a superset of the MultiMediaCard protocol as defined in the MultiMediaCard system specification V2.11 . Several commands required for SD memory devices are not supported by either SD I/O-only cards or the I/O portion of combo cards. Some of these commands have no use in SD I/O devices, such as erase commands, and thus are not supported in the SDIO protocol. In addition, several commands are different between SD memory cards and SD I/O cards and thus are not supported in the SDIO protocol. For details refer to SD I/O card Specification Version 1.0 .

The MultiMediaCard/SD bus connects cards to the controller.

The current version of the SDMMC supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

30.2 SDMMC bus topology

Communication over the bus is based on command and data transfers.

The basic transaction on the MultiMediaCard/SD/SD I/O bus is the command/response transaction. These types of bus transaction transfer their information directly within the command or response structure. In addition, some operations have a data token.

Data transfers to/from SD/SDIO memory cards are done in data blocks. Data transfers to/from MMC are done data blocks or streams.

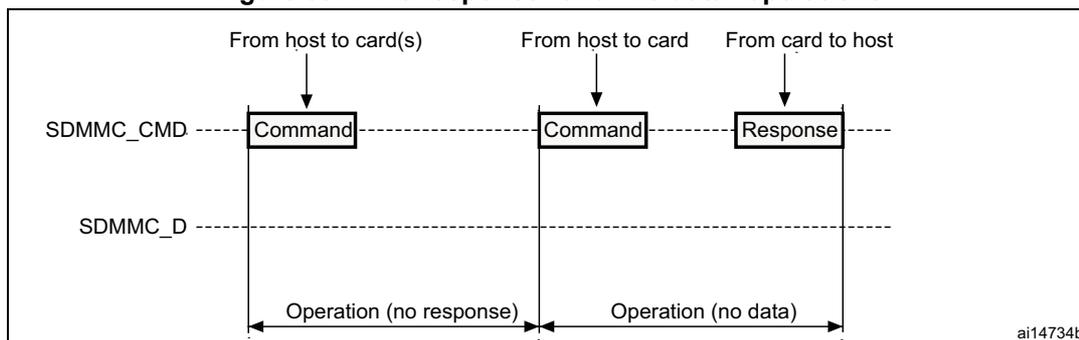

Figure 397. “No response” and “no data” operations

Figure 397 illustrates two types of operations on the SDMMC interface. The first operation, labeled "Operation (no response)", shows a command being sent from the host to the card(s) via the SDMMC_CMD line, but no response is received. The second operation, labeled "Operation (no data)", shows a command being sent from the host to the card via the SDMMC_CMD line, a response is received from the card to the host, but no data is transferred on the SDMMC_D line.

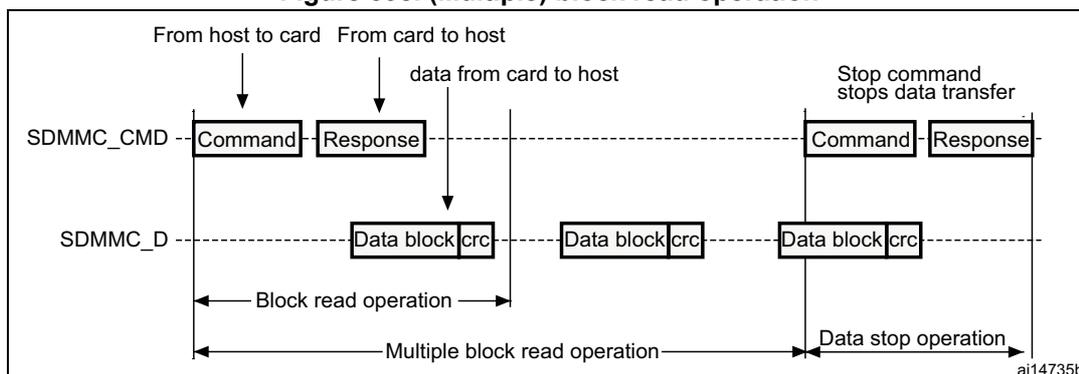

Figure 398. (Multiple) block read operation

Figure 398 illustrates a multiple block read operation. It starts with a "Block read operation" where a command is sent from the host to the card via the SDMMC_CMD line, a response is received from the card to the host, and multiple data blocks (each consisting of a data block and a CRC) are transferred from the card to the host via the SDMMC_D line. This is followed by a "Multiple block read operation" which includes a "Stop command" sent from the host to the card via the SDMMC_CMD line, a response is received from the card to the host, and a final data block (consisting of a data block and a CRC) is transferred from the card to the host via the SDMMC_D line. A note indicates that the stop command stops data transfer.

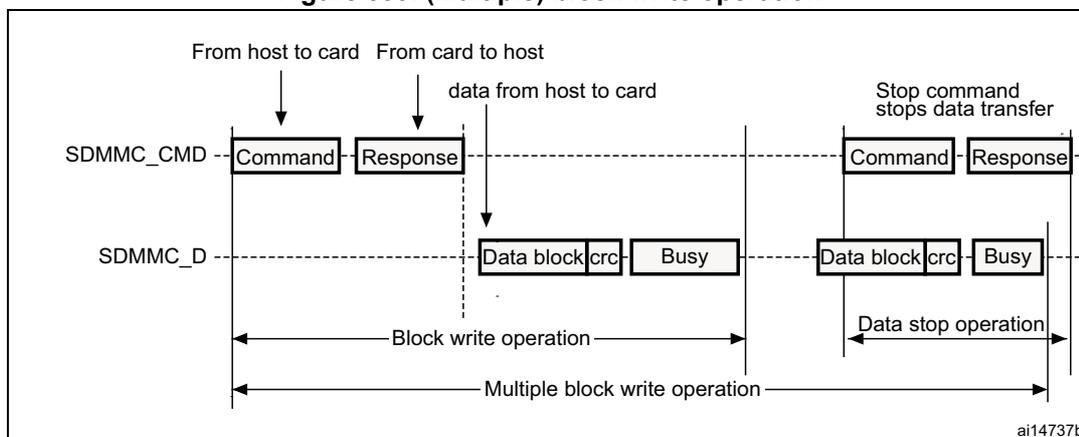

Figure 399. (Multiple) block write operation

Figure 399 illustrates a multiple block write operation. It starts with a "Block write operation" where a command is sent from the host to the card via the SDMMC_CMD line, a response is received from the card to the host, and a data block (consisting of a data block and a CRC) is transferred from the host to the card via the SDMMC_D line, followed by a "Busy" signal from the card. This is followed by a "Multiple block write operation" which includes a "Stop command" sent from the host to the card via the SDMMC_CMD line, a response is received from the card to the host, another data block (consisting of a data block and a CRC) is transferred from the host to the card via the SDMMC_D line, and another "Busy" signal from the card. A note indicates that the stop command stops data transfer.

Note: The SDMMC will not send any data as long as the Busy signal is asserted (SDMMC_D0 pulled low).

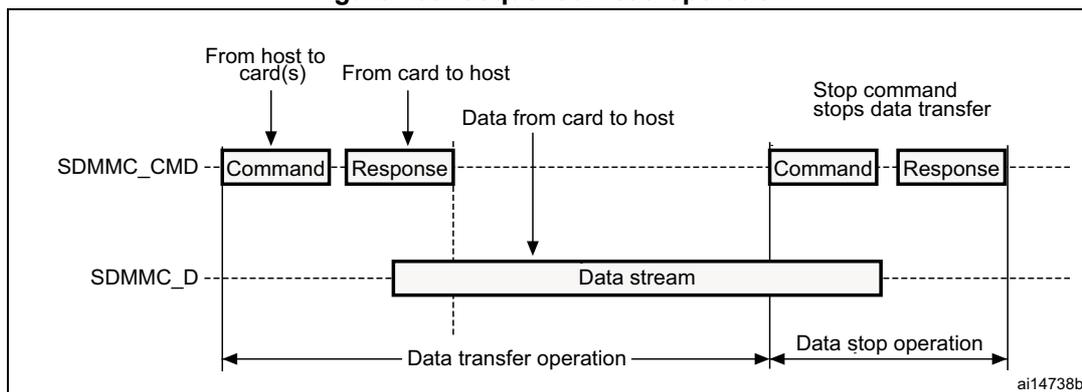

Figure 400. Sequential read operation

The diagram illustrates the timing for a sequential read operation. On the SDMMC_CMD line, a 'Command' is sent 'From host to card(s)', followed by a 'Response' 'From card to host'. On the SDMMC_D line, a 'Data stream' is sent 'Data from card to host'. This entire phase is labeled 'Data transfer operation'. To end the transfer, a 'Stop command' is sent 'From host to card(s)' on the SDMMC_CMD line, followed by a 'Response'. This final phase is labeled 'Data stop operation' with the note 'Stop command stops data transfer'. Diagram reference: ai14738b.

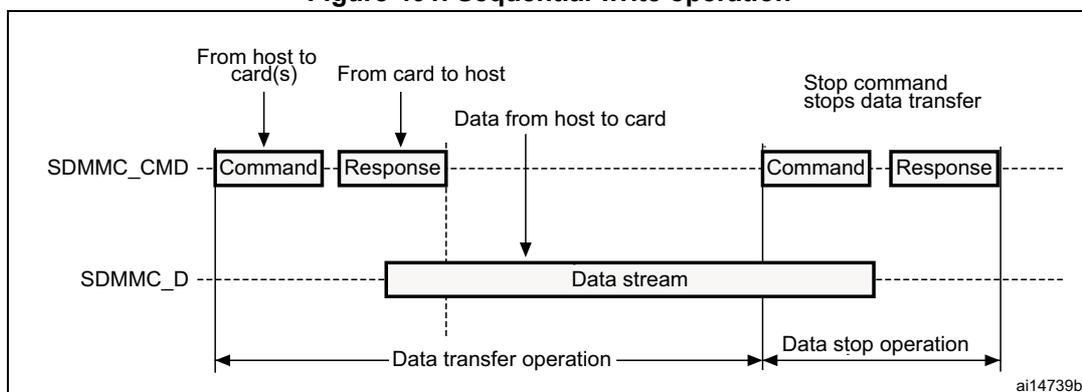

Figure 401. Sequential write operation

The diagram illustrates the timing for a sequential write operation. On the SDMMC_CMD line, a 'Command' is sent 'From host to card(s)', followed by a 'Response' 'From card to host'. On the SDMMC_D line, a 'Data stream' is sent 'Data from host to card'. This phase is labeled 'Data transfer operation'. To end the transfer, a 'Stop command' is sent 'From host to card(s)' on the SDMMC_CMD line, followed by a 'Response'. This final phase is labeled 'Data stop operation' with the note 'Stop command stops data transfer'. Diagram reference: ai14739b.

30.3 SDMMC functional description

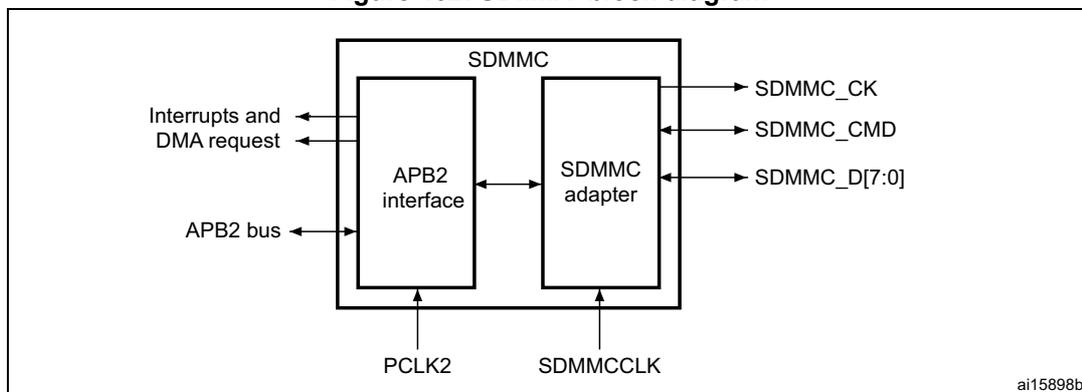

The SDMMC consists of two parts:

- • The SDMMC adapter block provides all functions specific to the MMC/SD/SD I/O card such as the clock generation unit, command and data transfer.

- • The APB2 interface accesses the SDMMC adapter registers, and generates interrupt and DMA request signals.

Figure 402. SDMMC block diagram

The block diagram shows the internal structure of the SDMMC. It contains an APB2 interface block and an SDMMC adapter block. The APB2 interface connects to the 'APB2 bus' and outputs 'Interrupts and DMA request'. The SDMMC adapter connects to external signals: 'SDMMC_CK', 'SDMMC_CMD', and 'SDMMC_D[7:0]'. The entire block is clocked by 'PCLK2' and 'SDMMCCLK'. Diagram reference: ai15898b.

By default SDMMC_D0 is used for data transfer. After initialization, the host can change the databus width.

If a MultiMediaCard is connected to the bus, SDMMC_D0, SDMMC_D[3:0] or SDMMC_D[7:0] can be used for data transfer. MMC V3.31 or previous, supports only 1 bit of data so only SDMMC_D0 can be used.

If an SD or SD I/O card is connected to the bus, data transfer can be configured by the host to use SDMMC_D0 or SDMMC_D[3:0]. All data lines are operating in push-pull mode.

SDMMC_CMD has two operational modes:

- • Open-drain for initialization (only for MMCV3.31 or previous)

- • Push-pull for command transfer (SD/SD I/O card MMC4.2 use push-pull drivers also for initialization)

SDMMC_CK is the clock to the card: one bit is transferred on both command and data lines with each clock cycle.

The SDMMC uses two clock signals:

- • SDMMC adapter clock SDMMCCLK = 50 MHz)

- • APB2 bus clock (PCLK2)

PCLK2 and SDMMC_CK clock frequencies must respect the following condition:

The signals shown in Table 187 are used on the MultiMediaCard/SD/SD I/O card bus.

Table 187. SDMMC I/O definitions

| Pin | Direction | Description |

|---|---|---|

| SDMMC_CK | Output | MultiMediaCard/SD/SDIO card clock. This pin is the clock from host to card. |

| SDMMC_CMD | Bidirectional | MultiMediaCard/SD/SDIO card command. This pin is the bidirectional command/response signal. |

| SDMMC_D[7:0] | Bidirectional | MultiMediaCard/SD/SDIO card data. These pins are the bidirectional databus. |

30.3.1 SDMMC adapter

Figure 403 shows a simplified block diagram of an SDMMC adapter.

![Figure 403. SDMMC adapter block diagram. The diagram shows the internal structure of the SDMMC adapter. It includes an 'Adapter registers' block and a 'FIFO' block connected to an 'APB2 interface'. These are connected to a 'Control unit', 'Command path', and 'Data path' block. The 'Control unit' is connected to 'SDMMC_CK', 'SDMMC_CMD', and 'SDMMC_D[7:0]' signals, which are part of the 'Card bus'. The 'Data path' is also connected to 'SDMMC_D[7:0]'. The 'Control unit', 'Command path', and 'Data path' are powered by 'SDMMCCLK'. The 'Adapter registers' and 'FIFO' are powered by 'PCLK2'. The diagram is labeled 'ai15899b'.](/RM0431-STM32F72-73/2a51469975ba30e3f2fed3f4335c3ad1_img.jpg)

Figure 403. SDMMC adapter

The SDMMC adapter is a multimedia/secure digital memory card bus master that provides an interface to a multimedia card stack or to a secure digital memory card. It consists of five subunits:

- • Adapter register block

- • Control unit

- • Command path

- • Data path

- • Data FIFO

Note: The adapter registers and FIFO use the APB2 bus clock domain (PCLK2). The control unit, command path and data path use the SDMMC adapter clock domain (SDMMCCLK).

Adapter register block

The adapter register block contains all system registers. This block also generates the signals that clear the static flags in the multimedia card. The clear signals are generated when 1 is written into the corresponding bit location in the SDMMC Clear register.

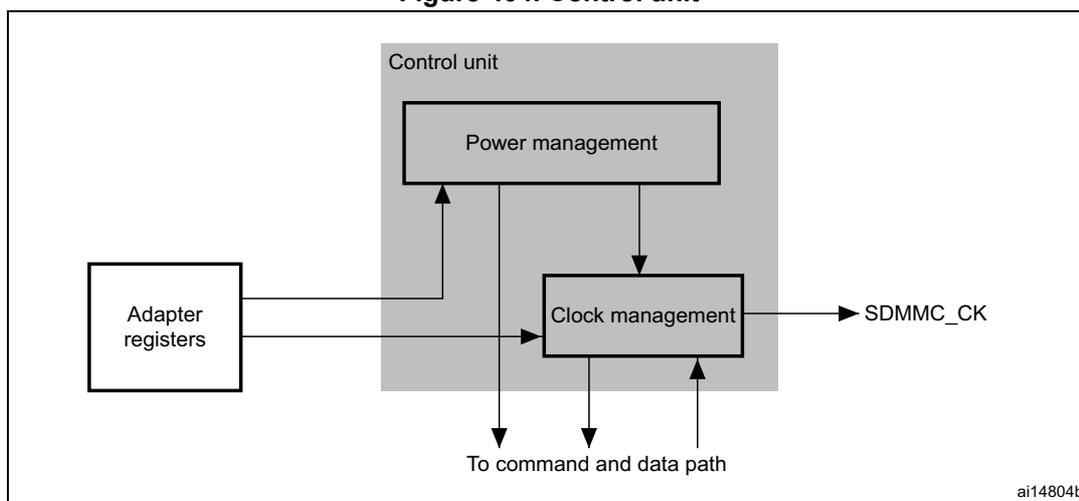

Control unit

The control unit contains the power management functions and the clock divider for the memory card clock.

There are three power phases:

- • power-off

- • power-up

- • power-on

Figure 404. Control unit

graph TD

subgraph Control_unit [Control unit]

PM[Power management]

CM[Clock management]

PM --> CM

end

AR[Adapter registers] --> PM

AR --> CM

CM --> SDMMC_CK[SDMMC_CK]

CM --> To_command_and_data_path[To command and data path]

To_command_and_data_path --> CM

ai14804b

The control unit is illustrated in Figure 404 . It consists of a power management subunit and a clock management subunit.

The power management subunit disables the card bus output signals during the power-off and power-up phases.

The clock management subunit generates and controls the SDMMC_CK signal. The SDMMC_CK output can use either the clock divide or the clock bypass mode. The clock output is inactive:

- • after reset

- • during the power-off or power-up phases

- • if the power saving mode is enabled and the card bus is in the Idle state (eight clock periods after both the command and data path subunits enter the Idle phase)

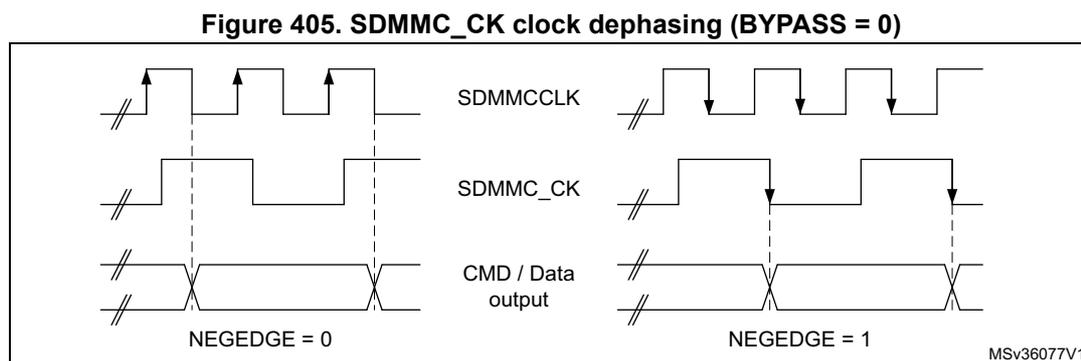

The clock management subunit controls SDMMC_CK dephasing. When not in bypass mode the SDMMC command and data output are generated on the SDMMCCLK falling edge succeeding the rising edge of SDMMC_CK. (SDMMC_CK rising edge occurs on SDMMCCLK rising edge) when SDMMC_CLKCR[13] bit is reset (NEGEDGE = 0). When SDMMC_CLKCR[13] bit is set (NEGEDGE = 1) SDMMC command and data changed on the SDMMC_CK falling edge.

When SDMMC_CLKCR[10] is set (BYPASS = 1), SDMMC_CK rising edge occurs on SDMMCCLK rising edge. The data and the command change on SDMMCCLK falling edge whatever NEGEDGE value.

The data and command responses are latched using SDMMC_CK rising edge.

Figure 405. SDMMC_CK clock dephasing (BYPASS = 0)

Command path

The command path unit sends commands to and receives responses from the cards.

Figure 406. SDMMC adapter command path

- • Command path state machine (CPSM)

- – When the command register is written to and the enable bit is set, command transfer starts. When the command has been sent, the command path state machine (CPSM) sets the status flags and enters the Idle state if a response is not required. If a response is required, it waits for the response (see Figure 407 on page 1073 ). When the response is received, the received CRC code and the internally generated code are compared, and the appropriate status flags are set.

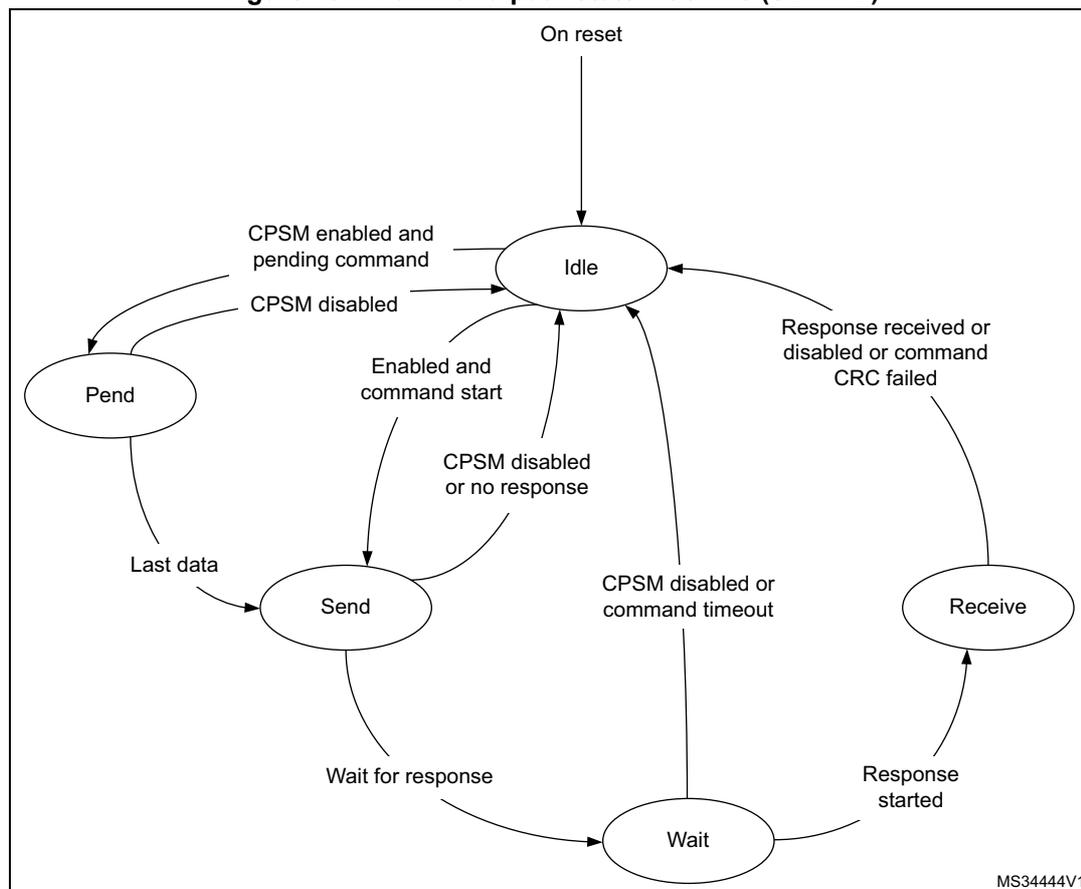

Figure 407. Command path state machine (SDMMC)

stateDiagram-v2

[*] --> Idle : On reset

Idle --> Pend : CPSM enabled and pending command

Idle --> Send : Enabled and command start

Idle --> Idle : CPSM disabled

Pend --> Idle : CPSM disabled

Pend --> Send : Last data

Send --> Idle : CPSM disabled or no response

Send --> Wait : Wait for response

Wait --> Idle : CPSM disabled or command timeout

Wait --> Receive : Response started

Receive --> Idle : Response received or disabled or command CRC failed

When the Wait state is entered, the command timer starts running. If the timeout is reached before the CPSM moves to the Receive state, the timeout flag is set and the Idle state is entered.

Note: The command timeout has a fixed value of 64 SDMMC_CK clock periods.

If the interrupt bit is set in the command register, the timer is disabled and the CPSM waits for an interrupt request from one of the cards. If a pending bit is set in the command register, the CPSM enters the Pend state, and waits for a CmdPend signal from the data path subunit. When CmdPend is detected, the CPSM moves to the Send state. This enables the data counter to trigger the stop command transmission.

Note: The CPSM remains in the Idle state for at least eight SDMMC_CK periods to meet the \( N_{CC} \) and \( N_{RC} \) timing constraints. \( N_{CC} \) is the minimum delay between two host commands, and \( N_{RC} \) is the minimum delay between the host command and the card response.

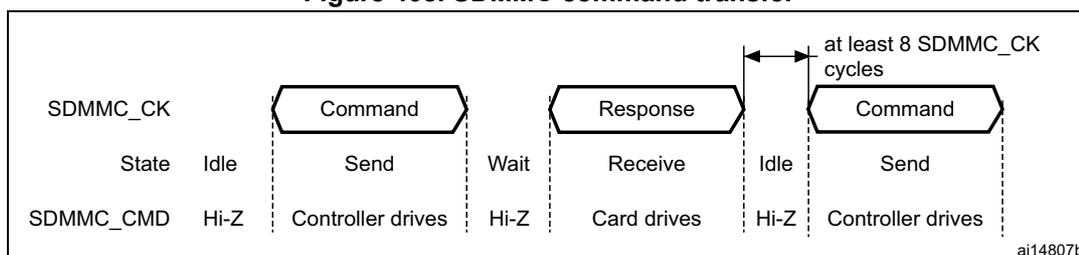

Figure 408. SDMMC command transfer

The diagram shows the timing of SDMMC command transfers. The top signal, SDMMC_CK, is a periodic clock. The bottom signal, SDMMC_CMD, is a command line. The sequence of events is:

- Idle: SDMMC_CMD is in Hi-Z state.

- Command (Send): The controller drives the SDMMC_CMD line with a 48-bit command token.

- Wait: SDMMC_CMD returns to Hi-Z state.

- Response (Receive): The card drives the SDMMC_CMD line with a response token.

- Idle: SDMMC_CMD returns to Hi-Z state.

- Command (Send): The controller drives the SDMMC_CMD line with another 48-bit command token.

- • Command format

- – Command: a command is a token that starts an operation. Command are sent from the host either to a single card (addressed command) or to all connected cards (broadcast command are available for MMC V3.31 or previous). Commands are transferred serially on the CMD line. All commands have a fixed length of 48 bits. The general format for a command token for MultiMediaCards, SD-Memory cards and SDIO-Cards is shown in Table 188 .

The command path operates in a half-duplex mode, so that commands and responses can either be sent or received. If the CPSM is not in the Send state, the SDMMC_CMD output is in the Hi-Z state, as shown in Figure 408 on page 1074 . Data on SDMMC_CMD are synchronous with the rising edge of SDMMC_CK. Table 188 shows the command format.

Table 188. Command format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 47 | 1 | 0 | Start bit |

| 46 | 1 | 1 | Transmission bit |

| [45:40] | 6 | - | Command index |

| [39:8] | 32 | - | Argument |

| [7:1] | 7 | - | CRC7 |

| 0 | 1 | 1 | End bit |

- – Response: a response is a token that is sent from an addressed card (or synchronously from all connected cards for MMC V3.31 or previous), to the host as an answer to a previously received command. Responses are transferred serially on the CMD line.

The SDMMC supports two response types. Both use CRC error checking:

- • 48 bit short response

- • 136 bit long response

Note: If the response does not contain a CRC (CMD1 response), the device driver must ignore the CRC failed status.

Table 189. Short response format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 47 | 1 | 0 | Start bit |

| 46 | 1 | 0 | Transmission bit |

| [45:40] | 6 | - | Command index |

| [39:8] | 32 | - | Argument |

| [7:1] | 7 | - | CRC7(or 1111111) |

| 0 | 1 | 1 | End bit |

Table 190. Long response format

| Bit position | Width | Value | Description |

|---|---|---|---|

| 135 | 1 | 0 | Start bit |

| 134 | 1 | 0 | Transmission bit |

| [133:128] | 6 | 111111 | Reserved |

| [127:1] | 127 | - | CID or CSD (including internal CRC7) |

| 0 | 1 | 1 | End bit |

The command register contains the command index (six bits sent to a card) and the command type. These determine whether the command requires a response, and whether the response is 48 or 136 bits long (see Section 30.8.4 on page 1111 ). The command path implements the status flags shown in Table 191 :

Table 191. Command path status flags

| Flag | Description |

|---|---|

| CMDREND | Set if response CRC is OK. |

| CCRCFAIL | Set if response CRC fails. |

| CMDSENT | Set when command (that does not require response) is sent |

| CTIMEOUT | Response timeout. |

| CMDACT | Command transfer in progress. |

The CRC generator calculates the CRC checksum for all bits before the CRC code. This includes the start bit, transmitter bit, command index, and command argument (or card status). The CRC checksum is calculated for the first 120 bits of CID or CSD for the long response format. Note that the start bit, transmitter bit and the six reserved bits are not used in the CRC calculation.

The CRC checksum is a 7-bit value:

Data path

The data path subunit transfers data to and from cards. Figure 409 shows a block diagram of the data path.

Figure 409. Data path

![Block diagram of the Data path subunit. The diagram shows a 'Data path' block containing 'Status flag', 'Control logic', and 'Data timer' connected to a 'To control unit'. Below this, a 'Data FIFO' contains 'Transmit' and 'Receive' blocks. The 'Transmit' block connects to a 'Shift register', which then connects to a 'CRC' block. The 'CRC' block outputs to 'SDMMC_Dout[7:0]'. The 'Receive' block also connects to the 'Shift register'. The 'Shift register' also receives input from 'SDMMC_Din[7:0]'. The 'Data path' block also has connections to the 'Shift register' and the 'CRC' block. The diagram is labeled 'ai14808b' in the bottom right corner.](/RM0431-STM32F72-73/415cf8e0a104a0e37bffeccc5d83e83d_img.jpg)

The card databus width can be programmed using the clock control register. If the 4-bit wide bus mode is enabled, data is transferred at four bits per clock cycle over all four data signals (SDMMC_D[3:0]). If the 8-bit wide bus mode is enabled, data is transferred at eight bits per clock cycle over all eight data signals (SDMMC_D[7:0]). If the wide bus mode is not enabled, only one bit per clock cycle is transferred over SDMMC_D0.

Depending on the transfer direction (send or receive), the data path state machine (DPSM) moves to the Wait_S or Wait_R state when it is enabled:

- • Send: the DPSM moves to the Wait_S state. If there is data in the transmit FIFO, the DPSM moves to the Send state, and the data path subunit starts sending data to a card.

- • Receive: the DPSM moves to the Wait_R state and waits for a start bit. When it receives a start bit, the DPSM moves to the Receive state, and the data path subunit starts receiving data from a card.

Data path state machine (DPSM)

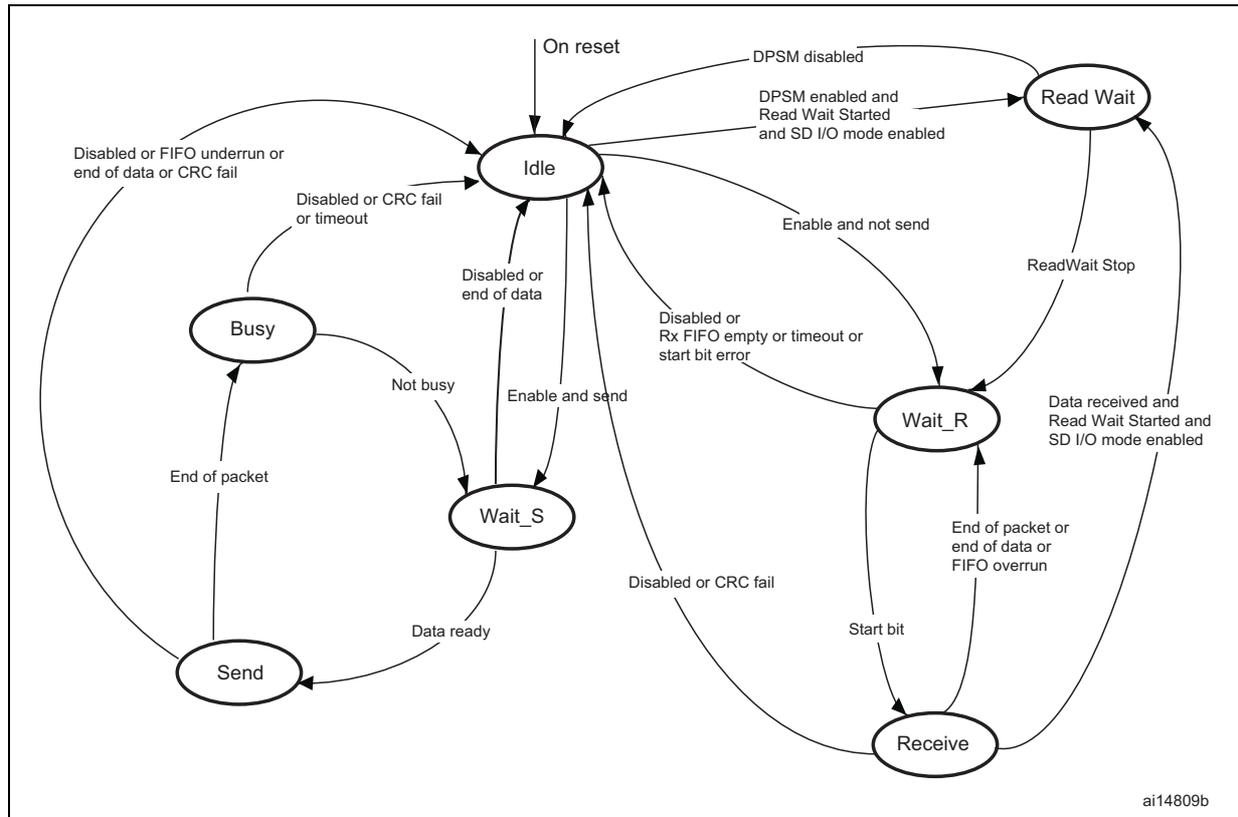

The DPSM operates at SDMMC_CK frequency. Data on the card bus signals is synchronous to the rising edge of SDMMC_CK. The DPSM has six states, as shown in Figure 410: Data path state machine (DPSM) .

Figure 410. Data path state machine (DPSM)

stateDiagram-v2

[*] --> Idle : On reset

Idle --> Idle : Disabled or FIFO underrun or

end of data or CRC fail

Idle --> Idle : Disabled or CRC fail

or timeout

Idle --> Idle : Disabled or

end of data

Idle --> Read Wait : DPSM disabled

Idle --> Read Wait : DPSM enabled and

Read Wait Started

and SD I/O mode enabled

Idle --> Wait_S : Enable and send

Idle --> Wait_R : Enable and not send

Busy --> Idle : Disabled or CRC fail

or timeout

Busy --> Send : End of packet

Wait_S --> Idle : Data ready

Wait_S --> Send : Not busy

Send --> Idle : Data ready

Send --> Busy : End of packet

Wait_R --> Idle : Disabled or CRC fail

Wait_R --> Receive : Start bit

Wait_R --> Idle : Disabled or

Rx FIFO empty or timeout or

start bit error

Receive --> Wait_R : End of packet or

end of data or

FIFO overrun

Receive --> Idle : Disabled or CRC fail

Read Wait --> Idle : ReadWait Stop

Read Wait --> Wait_R : Data received and

Read Wait Started and

SD I/O mode enabled

- • Idle : the data path is inactive, and the SDMMC_D[7:0] outputs are in Hi-Z. When the data control register is written and the enable bit is set, the DPSM loads the data counter with a new value and, depending on the data direction bit, moves to either the Wait_S or the Wait_R state.

- • Wait_R : if the data counter equals zero, the DPSM moves to the Idle state when the receive FIFO is empty. If the data counter is not zero, the DPSM waits for a start bit on SDMMC_D. The DPSM moves to the Receive state if it receives a start bit before a timeout, and loads the data block counter. If it reaches a timeout before it detects a start bit, it moves to the Idle state and sets the timeout status flag.

- •

Receive

: serial data received from a card is packed in bytes and written to the data FIFO. Depending on the transfer mode bit in the data control register, the data transfer mode can be either block or stream:

- – In block mode, when the data block counter reaches zero, the DPSM waits until it receives the CRC code. If the received code matches the internally generated CRC code, the DPSM moves to the Wait_R state. If not, the CRC fail status flag is set and the DPSM moves to the Idle state.

- – In stream mode, the DPSM receives data while the data counter is not zero. When the counter is zero, the remaining data in the shift register is written to the data FIFO, and the DPSM moves to the Wait_R state.

- • Wait_S : the DPSM moves to the Idle state if the data counter is zero. If not, it waits until the data FIFO empty flag is deasserted, and moves to the Send state.

Note: The DPSM remains in the Wait_S state for at least two clock periods to meet the \( N_{WR} \) timing requirements, where \( N_{WR} \) is the number of clock cycles between the reception of the card response and the start of the data transfer from the host.

- • Send: the DPSM starts sending data to a card. Depending on the transfer mode bit in the data control register, the data transfer mode can be either block or stream:

- – In block mode, when the data block counter reaches zero, the DPSM sends an internally generated CRC code and end bit, and moves to the Busy state.

- – In stream mode, the DPSM sends data to a card while the enable bit is high and the data counter is not zero. It then moves to the Idle state.

If a FIFO underrun error occurs, the DPSM sets the FIFO error flag and moves to the Idle state.

- • Busy: the DPSM waits for the CRC status flag:

- – If it does not receive a positive CRC status, it moves to the Idle state and sets the CRC fail status flag.

- – If it receives a positive CRC status, it moves to the Wait_S state if SDMMC_D0 is not low (the card is not busy).

If a timeout occurs while the DPSM is in the Busy state, it sets the data timeout flag and moves to the Idle state.

The data timer is enabled when the DPSM is in the Wait_R or Busy state, and generates the data timeout error:

- – When transmitting data, the timeout occurs if the DPSM stays in the Busy state for longer than the programmed timeout period

- – When receiving data, the timeout occurs if the end of the data is not true, and if the DPSM stays in the Wait_R state for longer than the programmed timeout period.

- • Data: data can be transferred from the card to the host or vice versa. Data is transferred via the data lines. They are stored in a FIFO of 32 words, each word is 32 bits wide.

Table 192. Data token format

| Description | Start bit | Data | CRC16 | End bit |

|---|---|---|---|---|

| Block Data | 0 | - | yes | 1 |

| Stream Data | 0 | - | no | 1 |

DPSM Flags

The status of the data path subunit transfer is reported by several status flags

Table 193. DPSM flags

| Flag | Description |

|---|---|

| DBCKEND | Set to high when data block send/receive CRC check is passed. In SDIO multibyte transfer mode this flag is set at the end of the transfer (a multibyte transfer is considered as a single block transfer by the host). |

| DATAEND | Set to high when SDMMC_DCOUNT register decrements and reaches 0. DATAEND indicates the end of a transfer on SDMMC data line. |

| DTIMEOUT | Set to high when data timeout period is reached. When data timer reaches zero while DPSM is in Wait_R or Busy state, timeout is set. DTIMEOUT can be set after DATAEND if DPSM remains in busy state for longer than the programmed period. |

| DCRCFAIL | Set to high when data block send/receive CRC check fails. |

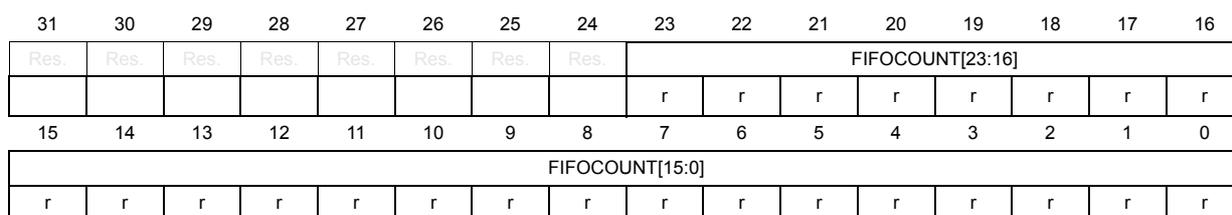

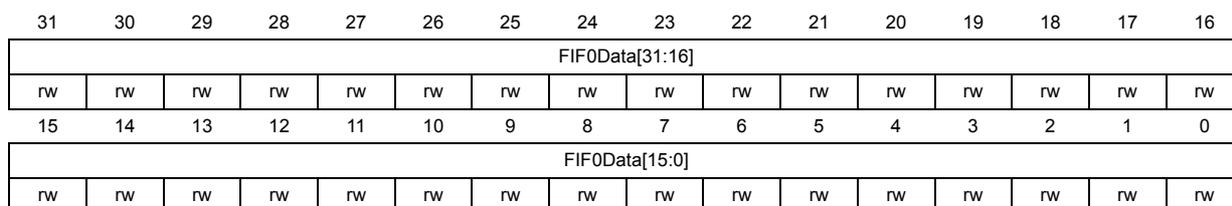

Data FIFO

The data FIFO (first-in-first-out) subunit is a data buffer with a transmit and receive unit.

The FIFO contains a 32-bit wide, 32-word deep data buffer, and transmit and receive logic. Because the data FIFO operates in the APB2 clock domain (PCLK2), all signals from the subunits in the SDMMC clock domain (SDMMCCLK) are resynchronized.

Depending on the TXACT and RXACT flags, the FIFO can be disabled, transmit enabled, or receive enabled. TXACT and RXACT are driven by the data path subunit and are mutually exclusive:

- – The transmit FIFO refers to the transmit logic and data buffer when TXACT is asserted

- – The receive FIFO refers to the receive logic and data buffer when RXACT is asserted

- • Transmit FIFO:

Data can be written to the transmit FIFO through the APB2 interface when the SDMMC is enabled for transmission.

The transmit FIFO is accessible via 32 sequential addresses. The transmit FIFO contains a data output register that holds the data word pointed to by the read pointer. When the data path subunit has loaded its shift register, it increments the read pointer and drives new data out.

If the transmit FIFO is disabled, all status flags are deasserted. The data path subunit asserts TXACT when it transmits data.

Table 194. Transmit FIFO status flags| Flag | Description |

|---|---|

| TXFIFOE | Set to high when the transmit FIFO does not contain valid data. |

| TXFIFOH | Set to high when 8 or more transmit FIFO words are empty. This flag can be used as a DMA request. |

| TXDAVL | Set to high when the transmit FIFO contains valid data. This flag is the inverse of the TXFIFOE flag. |

| TXUNDERR | Set to high when an underrun error occurs. This flag is cleared by writing to the SDMMC Clear register. Note: In case of TXUNDERR, and DMA is used to fill SDMMC FIFO, user software should disable DMA stream, and then write DMAEN bit in SDMMC_DCTRL with '0' (to disable DMA request generation). |

- • Receive FIFO

When the data path subunit receives a word of data, it drives the data on the write databus. The write pointer is incremented after the write operation completes. On the read side, the contents of the FIFO word pointed to by the current value of the read pointer is driven onto the read databus. If the receive FIFO is disabled, all status flags are deasserted, and the read and write pointers are reset. The data path subunit asserts RXACT when it receives data. Table 195 lists the receive FIFO status flags. The receive FIFO is accessible via 32 sequential addresses.

Table 195. Receive FIFO status flags| Flag | Description |

|---|---|

| RXFIFOE | Set to high when the receive FIFO does not contain valid data. |

| RXFIFOH | Set to high when 8 or more receive FIFO words contain valid data. This flag can be used as a DMA request. |

| RXDAVL | Set to high when the receive FIFO is not empty. This flag is the inverse of the RXFIFOE flag. |

| RXOVERR | Set to high when an overrun error occurs. This flag is cleared by writing to the SDMMC Clear register. Note: In case of RXOVERR, and DMA is used to read SDMMC FIFO, user software should disable DMA stream, and then write DMAEN bit in SDMMC_DCTRL with '0' (to disable DMA request generation). |

30.3.2 SDMMC APB2 interface

The APB2 interface generates the interrupt and DMA requests, and accesses the SDMMC adapter registers and the data FIFO. It consists of a data path, register decoder, and interrupt/DMA logic.

SDMMC interrupts

The interrupt logic generates an interrupt request signal that is asserted when at least one of the selected status flags is high. A mask register is provided to allow selection of the conditions that will generate an interrupt. A status flag generates the interrupt request if a corresponding mask flag is set.

SDMMC/DMA interface

SDMMC APB interface controls all subunit to perform transfers between the host and card

Example of read procedure using DMA

Send CMD17 (READ_BLOCK) as follows:

- a) Program the SDMMC data length register (SDMMC data timer register should be already programmed before the card identification process)

- b) Program DMA channel (refer to DMA configuration for SDMMC controller )

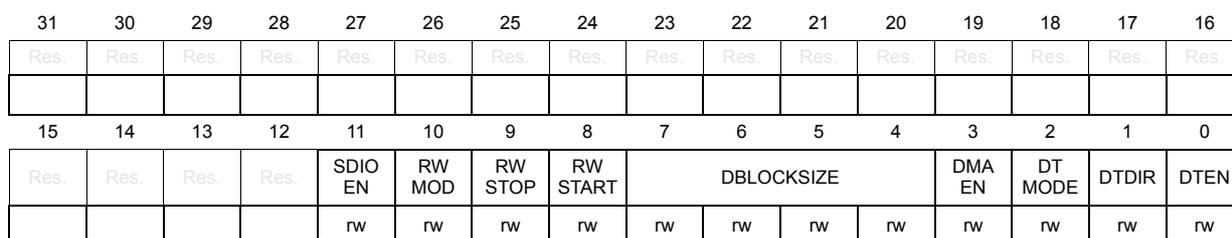

- c) Program the SDMMC data control register: DTEN with '1' (SDMMC card host enabled to send data); DTDIR with '1' (from card to controller); DTMODE with '0' (block data transfer); DMAEN with '1' (DMA enabled); DBLOCKSIZE with 0x9 (512 bytes). Other fields are don't care.

- d) Program the SDMMC argument register with the address location of the card from where data is to be transferred

- e) Program the SDMMC command register: CmdIndex with 17(READ_BLOCK); WaitResp with '1' (SDMMC card host waits for a response); CPSMEN with '1' (SDMMC card host enabled to send a command). Other fields are at their reset value.

- f) Wait for SDMMC_STA[6] = CMDREND interrupt, (CMDREND is set if there is no error on command path).

- g) Wait for SDMMC_STA[10] = DBCKEND, (DBCKEND is set in case of no errors until the CRC check is passed)

- h) Wait until the FIFO is empty, when FIFO is empty the SDMMC_STA[5] = RXOVERR value has to be checked to guarantee that read succeeded

Note: When FIFO overrun error occurs with last 1-4 bytes, it may happen that RXOVERR flag is set 2 APB clock cycles after DATAEND flag is set. To guarantee success of read operation RXOVERR must be checked after FIFO is empty.

Example of write procedure using DMA

Send CMD24 (WRITE_BLOCK) as follows:

- Program the SDMMC data length register (SDMMC data timer register should be already programmed before the card identification process)

- Program DMA channel (refer to DMA configuration for SDMMC controller )

- Program the SDMMC argument register with the address location of the card from where data is to be transferred

- Program the SDMMC command register: CmdIndex with 24(WRITE_BLOCK); WaitResp with '1' (SDMMC card host waits for a response); CPSMEN with '1' (SDMMC card host enabled to send a command). Other fields are at their reset value.

- Wait for SDMMC_STA[6] = CMDREND interrupt, then Program the SDMMC data control register: DTEN with '1' (SDMMC card host enabled to send data); DTDIR with '0' (from controller to card); DTMODE with '0' (block data transfer); DMAEN with '1' (DMA enabled); DBLOCKSIZE with 0x9 (512 bytes). Other fields are don't care.

- Wait for SDMMC_STA[10] = DBCKEND, (DBCKEND is set in case of no errors)

DMA configuration for SDMMC controller

- Enable DMA2 controller and clear any pending interrupts.

- Program the DMA2_Stream3 (or DMA2_Stream6) Channel4 source address register with the memory location base address and DMA2_Stream3 (or DMA2_Stream6) Channel4 destination address register with the SDMMC_FIFO register address.

- Program DMA2_Stream3 (or DMA2_Stream6) Channel4 control register (memory increment, not peripheral increment, peripheral and source width is word size).

- Program DMA2_Stream3 (or DMA2_Stream6) Channel4 to select the peripheral as flow controller (set PFCTRL bit in DMA_S3CR (or DMA_S6CR) configuration register).

- Configure the incremental burst transfer to 4 beats (at least from peripheral side) in DMA2_Stream3 (or DMA2_Stream6) Channel4.

- Enable DMA2_Stream3 (or DMA2_Stream6) Channel4

Note: SDMMC host allows only to use the DMA in peripheral flow controller mode. DMA stream used to serve SDMMC must be configured in peripheral flow controller mode

SDMMC generates only DMA burst requests to DMA controller. DMA must be configured in incremental burst mode on peripheral side.

30.4 Card functional description

30.4.1 Card identification mode

While in card identification mode the host resets all cards, validates the operation voltage range, identifies cards and sets a relative card address (RCA) for each card on the bus. All data communications in the card identification mode use the command line (CMD) only.

30.4.2 Card reset

The GO_IDLE_STATE command (CMD0) is the software reset command and it puts the MultiMediaCard and SD memory in the Idle state. The IO_RW_DIRECT command (CMD52) resets the SD I/O card. After power-up or CMD0, all cards output bus drivers are in the high-impedance state and the cards are initialized with a default relative card address (RCA=0x0001) and with a default driver stage register setting (lowest speed, highest driving current capability).

30.4.3 Operating voltage range validation

All cards can communicate with the SDMMC card host using any operating voltage within the specification range. The supported minimum and maximum \( V_{DD} \) values are defined in the operation conditions register (OCR) on the card.

Cards that store the card identification number (CID) and card specific data (CSD) in the payload memory are able to communicate this information only under data-transfer \( V_{DD} \) conditions. When the SDMMC card host module and the card have incompatible \( V_{DD} \) ranges, the card is not able to complete the identification cycle and cannot send CSD data. For this purpose, the special commands, SEND_OP_COND (CMD1), SD_APP_OP_COND (ACMD41 for SD Memory), and IO_SEND_OP_COND (CMD5 for SD I/O), are designed to provide a mechanism to identify and reject cards that do not match the \( V_{DD} \) range desired by the SDMMC card host. The SDMMC card host sends the required \( V_{DD} \) voltage window as the operand of these commands. Cards that cannot perform data transfer in the specified range disconnect from the bus and go to the inactive state.

By using these commands without including the voltage range as the operand, the SDMMC card host can query each card and determine the common voltage range before placing out-of-range cards in the inactive state. This query is used when the SDMMC card host is able to select a common voltage range or when the user requires notification that cards are not usable.

30.4.4 Card identification process

The card identification process differs for MultiMediaCards and SD cards. For MultiMediaCard cards, the identification process starts at clock rate \( F_{od} \) . The SDMMC_CMD line output drivers are open-drain and allow parallel card operation during this process. The registration process is accomplished as follows:

- 1. The bus is activated.

- 2. The SDMMC card host broadcasts SEND_OP_COND (CMD1) to receive operation conditions.

- 3. The response is the wired AND operation of the operation condition registers from all cards.

- 4. Incompatible cards are placed in the inactive state.

- 5. The SDMMC card host broadcasts ALL_SEND_CID (CMD2) to all active cards.

- 6. The active cards simultaneously send their CID numbers serially. Cards with outgoing CID bits that do not match the bits on the command line stop transmitting and must wait for the next identification cycle. One card successfully transmits a full CID to the SDMMC card host and enters the Identification state.

- 7. The SDMMC card host issues SET_RELATIVE_ADDR (CMD3) to that card. This new address is called the relative card address (RCA); it is shorter than the CID and

addresses the card. The assigned card changes to the Standby state, it does not react to further identification cycles, and its output switches from open-drain to push-pull.

- 8. The SDMMC card host repeats steps 5 through 7 until it receives a timeout condition.

For the SD card, the identification process starts at clock rate \( F_{od} \) , and the SDMMC_CMD line output drives are push-pull drivers instead of open-drain. The registration process is accomplished as follows:

- 1. The bus is activated.

- 2. The SDMMC card host broadcasts SD_APP_OP_COND (ACMD41).

- 3. The cards respond with the contents of their operation condition registers.

- 4. The incompatible cards are placed in the inactive state.

- 5. The SDMMC card host broadcasts ALL_SEND_CID (CMD2) to all active cards.

- 6. The cards send back their unique card identification numbers (CIDs) and enter the Identification state.

- 7. The SDMMC card host issues SET_RELATIVE_ADDR (CMD3) to an active card with an address. This new address is called the relative card address (RCA); it is shorter than the CID and addresses the card. The assigned card changes to the Standby state. The SDMMC card host can reissue this command to change the RCA. The RCA of the card is the last assigned value.

- 8. The SDMMC card host repeats steps 5 through 7 with all active cards.

For the SD I/O card, the registration process is accomplished as follows:

- 1. The bus is activated.

- 2. The SDMMC card host sends IO_SEND_OP_COND (CMD5).

- 3. The cards respond with the contents of their operation condition registers.

- 4. The incompatible cards are set to the inactive state.

- 5. The SDMMC card host issues SET_RELATIVE_ADDR (CMD3) to an active card with an address. This new address is called the relative card address (RCA); it is shorter than the CID and addresses the card. The assigned card changes to the Standby state. The SDMMC card host can reissue this command to change the RCA. The RCA of the card is the last assigned value.

30.4.5 Block write

During block write (CMD24 - 27) one or more blocks of data are transferred from the host to the card with a CRC appended to the end of each block by the host. A card supporting block write is always able to accept a block of data defined by WRITE_BL_LEN. If the CRC fails, the card indicates the failure on the SDMMC_D line and the transferred data are discarded and not written, and all further transmitted blocks (in multiple block write mode) are ignored.

If the host uses partial blocks whose accumulated length is not block aligned and, block misalignment is not allowed (CSD parameter WRITE_BLK_MISALIGN is not set), the card will detect the block misalignment error before the beginning of the first misaligned block. (ADDRESS_ERROR error bit is set in the status register). The write operation will also be aborted if the host tries to write over a write-protected area. In this case, however, the card will set the WP_VIOLATION bit.

Programming of the CID and CSD registers does not require a previous block length setting. The transferred data is also CRC protected. If a part of the CSD or CID register is stored in ROM, then this unchangeable part must match the corresponding part of the receive buffer. If this match fails, then the card reports an error and does not change any register contents.

Some cards may require long and unpredictable times to write a block of data. After receiving a block of data and completing the CRC check, the card begins writing and holds the SDMMC_D line low if its write buffer is full and unable to accept new data from a new WRITE_BLOCK command. The host may poll the status of the card with a SEND_STATUS command (CMD13) at any time, and the card will respond with its status. The READY_FOR_DATA status bit indicates whether the card can accept new data or whether the write process is still in progress. The host may deselect the card by issuing CMD7 (to select a different card), which will place the card in the Disconnect state and release the SDMMC_D line(s) without interrupting the write operation. When reselecting the card, it will reactivate busy indication by pulling SDMMC_D to low if programming is still in progress and the write buffer is unavailable.

30.4.6 Block read

In Block read mode the basic unit of data transfer is a block whose maximum size is defined in the CSD (READ_BL_LEN). If READ_BL_PARTIAL is set, smaller blocks whose start and end addresses are entirely contained within one physical block (as defined by READ_BL_LEN) may also be transmitted. A CRC is appended to the end of each block, ensuring data transfer integrity. CMD17 (READ_SINGLE_BLOCK) initiates a block read and after completing the transfer, the card returns to the Transfer state.

CMD18 (READ_MULTIPLE_BLOCK) starts a transfer of several consecutive blocks.

The host can abort reading at any time, within a multiple block operation, regardless of its type. Transaction abort is done by sending the stop transmission command.

If the card detects an error (for example, out of range, address misalignment or internal error) during a multiple block read operation (both types) it stops the data transmission and remains in the data state. The host must then abort the operation by sending the stop transmission command. The read error is reported in the response to the stop transmission command.

If the host sends a stop transmission command after the card transmits the last block of a multiple block operation with a predefined number of blocks, it is responded to as an illegal command, since the card is no longer in the data state. If the host uses partial blocks whose accumulated length is not block-aligned and block misalignment is not allowed, the card detects a block misalignment error condition at the beginning of the first misaligned block (ADDRESS_ERROR error bit is set in the status register).

30.4.7 Stream access, stream write and stream read (MultiMediaCard only)

In stream mode, data is transferred in bytes and no CRC is appended at the end of each block.

Stream write (MultiMediaCard only)

WRITE_DAT_UNTIL_STOP (CMD20) starts the data transfer from the SDMMC card host to the card, beginning at the specified address and continuing until the SDMMC card host issues a stop command. When partial blocks are allowed (CSD parameter WRITE_BL_PARTIAL is set), the data stream can start and stop at any address within the card address space, otherwise it can only start and stop at block boundaries. Because the amount of data to be transferred is not determined in advance, a CRC cannot be used. When the end of the memory range is reached while sending data and no stop command is sent by the SDMMC card host, any additional transferred data are discarded.

The maximum clock frequency for a stream write operation is given by the following equation fields of the card-specific data register:

- • Maximumspeed = maximum write frequency

- • TRANSPEED = maximum data transfer rate

- • writeblalen = maximum write data block length

- • NSAC = data read access time 2 in CLK cycles

- • TAAC = data read access time 1

- • R2WFACTOR = write speed factor

If the host attempts to use a higher frequency, the card may not be able to process the data and stop programming, set the OVERRUN error bit in the status register, and while ignoring all further data transfer, wait (in the receive data state) for a stop command. The write operation is also aborted if the host tries to write over a write-protected area. In this case, however, the card sets the WP_VIOLATION bit.

Stream read (MultiMediaCard only)

READ_DAT_UNTIL_STOP (CMD11) controls a stream-oriented data transfer.

This command instructs the card to send its data, starting at a specified address, until the SDMMC card host sends STOP_TRANSMISSION (CMD12). The stop command has an execution delay due to the serial command transmission and the data transfer stops after the end bit of the stop command. When the end of the memory range is reached while sending data and no stop command is sent by the SDMMC card host, any subsequent data sent are considered undefined.

The maximum clock frequency for a stream read operation is given by the following equation and uses fields of the card specific data register.

- • Maximumspeed = maximum read frequency

- • TRANSPEED = maximum data transfer rate

- • readblalen = maximum read data block length

- • writeblalen = maximum write data block length

- • NSAC = data read access time 2 in CLK cycles

- • TAAC = data read access time 1

- • R2WFACTOR = write speed factor

If the host attempts to use a higher frequency, the card is not able to sustain data transfer. If this happens, the card sets the UNDERRUN error bit in the status register, aborts the transmission and waits in the data state for a stop command.

30.4.8 Erase: group erase and sector erase

The erasable unit of the MultiMediaCard is the erase group. The erase group is measured in write blocks, which are the basic writable units of the card. The size of the erase group is a card-specific parameter and defined in the CSD.

The host can erase a contiguous range of Erase Groups. Starting the erase process is a three-step sequence.

First the host defines the start address of the range using the ERASE_GROUP_START (CMD35) command, next it defines the last address of the range using the ERASE_GROUP_END (CMD36) command and, finally, it starts the erase process by issuing the ERASE (CMD38) command. The address field in the erase commands is an Erase Group address in byte units. The card ignores all LSBs below the Erase Group size, effectively rounding the address down to the Erase Group boundary.

If an erase command is received out of sequence, the card sets the ERASE_SEQ_ERROR bit in the status register and resets the whole sequence.

If an out-of-sequence (neither of the erase commands, except SEND_STATUS) command received, the card sets the ERASE_RESET status bit in the status register, resets the erase sequence and executes the last command.

If the erase range includes write protected blocks, they are left intact and only nonprotected blocks are erased. The WP_ERASE_SKIP status bit in the status register is set.

The card indicates that an erase is in progress by holding SDMMC_D low. The actual erase time may be quite long, and the host may issue CMD7 to deselect the card.

30.4.9 Wide bus selection or deselection

Wide bus (4-bit bus width) operation mode is selected or deselected using SET_BUS_WIDTH (ACMD6). The default bus width after power-up or GO_IDLE_STATE (CMD0) is 1 bit. SET_BUS_WIDTH (ACMD6) is only valid in a transfer state, which means that the bus width can be changed only after a card is selected by SELECT/DESELECT_CARD (CMD7).

30.4.10 Protection management

Three write protection methods for the cards are supported in the SDMMC card host module:

- 1. internal card write protection (card responsibility)

- 2. mechanical write protection switch (SDMMC card host module responsibility only)

- 3. password-protected card lock operation

Internal card write protection

Card data can be protected against write and erase. By setting the permanent or temporary write-protect bits in the CSD, the entire card can be permanently write-protected by the manufacturer or content provider. For cards that support write protection of groups of sectors by setting the WP_GRP_ENABLE bit in the CSD, portions of the data can be protected, and the write protection can be changed by the application. The write protection is in units of WP_GRP_SIZE sectors as specified in the CSD. The SET_WRITE_PROT and CLR_WRITE_PROT commands control the protection of the addressed group. The SEND_WRITE_PROT command is similar to a single block read command. The card sends

a data block containing 32 write protection bits (representing 32 write protect groups starting at the specified address) followed by 16 CRC bits. The address field in the write protect commands is a group address in byte units.

The card ignores all LSBs below the group size.

Mechanical write protect switch

A mechanical sliding tab on the side of the card allows the user to set or clear the write protection on a card. When the sliding tab is positioned with the window open, the card is write-protected, and when the window is closed, the card contents can be changed. A matched switch on the socket side indicates to the SDMMC card host module that the card is write-protected. The SDMMC card host module is responsible for protecting the card. The position of the write protect switch is unknown to the internal circuitry of the card.

Password protect

The password protection feature enables the SDMMC card host module to lock and unlock a card with a password. The password is stored in the 128-bit PWD register and its size is set in the 8-bit PWD_LEN register. These registers are nonvolatile so that a power cycle does not erase them. Locked cards respond to and execute certain commands. This means that the SDMMC card host module is allowed to reset, initialize, select, and query for status, however it is not allowed to access data on the card. When the password is set (as indicated by a nonzero value of PWD_LEN), the card is locked automatically after power-up. As with the CSD and CID register write commands, the lock/unlock commands are available in the transfer state only. In this state, the command does not include an address argument and the card must be selected before using it. The card lock/unlock commands have the structure and bus transaction types of a regular single-block write command. The transferred data block includes all of the required information for the command (the password setting mode, the PWD itself, and card lock/unlock). The command data block size is defined by the SDMMC card host module before it sends the card lock/unlock command, and has the structure shown in Table 209 .

The bit settings are as follows:

- • ERASE: setting it forces an erase operation. All other bits must be zero, and only the command byte is sent

- • LOCK_UNLOCK: setting it locks the card. LOCK_UNLOCK can be set simultaneously with SET_PWD, however not with CLR_PWD

- • CLR_PWD: setting it clears the password data

- • SET_PWD: setting it saves the password data to memory

- • PWD_LEN: it defines the length of the password in bytes

- • PWD: the password (new or currently used, depending on the command)

The following sections list the command sequences to set/reset a password, lock/unlock the card, and force an erase.

Setting the password

- 1. Select a card (SELECT/DESELECT_CARD, CMD7), if none is already selected.

- 2. Define the block length (SET_BLOCKLEN, CMD16) to send, given by the 8-bit card lock/unlock mode, the 8-bit PWD_LEN, and the number of bytes of the new password.

When a password replacement is done, the block size must take into account that both the old and the new passwords are sent with the command.

- 3. Send LOCK/UNLOCK (CMD42) with the appropriate data block size on the data line including the 16-bit CRC. The data block indicates the mode (SET_PWD = 1), the length (PWD_LEN), and the password (PWD) itself. When a password replacement is done, the length value (PWD_LEN) includes the length of both passwords, the old and the new one, and the PWD field includes the old password (currently used) followed by the new password.

- 4. When the password is matched, the new password and its size are saved into the PWD and PWD_LEN fields, respectively. When the old password sent does not correspond (in size and/or content) to the expected password, the LOCK_UNLOCK_FAILED error bit is set in the card status register, and the password is not changed.

The password length field (PWD_LEN) indicates whether a password is currently set. When this field is nonzero, there is a password set and the card locks itself after power-up. It is possible to lock the card immediately in the current power session by setting the LOCK_UNLOCK bit (while setting the password) or sending an additional command for card locking.

Resetting the password

- 1. Select a card (SELECT/DESELECT_CARD, CMD7), if none is already selected.

- 2. Define the block length (SET_BLOCKLEN, CMD16) to send, given by the 8-bit card lock/unlock mode, the 8-bit PWD_LEN, and the number of bytes in the currently used password.

- 3. Send LOCK/UNLOCK (CMD42) with the appropriate data block size on the data line including the 16-bit CRC. The data block indicates the mode (CLR_PWD = 1), the length (PWD_LEN) and the password (PWD) itself. The LOCK_UNLOCK bit is ignored.

- 4. When the password is matched, the PWD field is cleared and PWD_LEN is set to 0. When the password sent does not correspond (in size and/or content) to the expected password, the LOCK_UNLOCK_FAILED error bit is set in the card status register, and the password is not changed.

Locking a card

- 1. Select a card (SELECT/DESELECT_CARD, CMD7), if none is already selected.

- 2. Define the block length (SET_BLOCKLEN, CMD16) to send, given by the 8-bit card lock/unlock mode (byte 0 in Table 209 ), the 8-bit PWD_LEN, and the number of bytes of the current password.

- 3. Send LOCK/UNLOCK (CMD42) with the appropriate data block size on the data line including the 16-bit CRC. The data block indicates the mode (LOCK_UNLOCK = 1), the length (PWD_LEN), and the password (PWD) itself.

- 4. When the password is matched, the card is locked and the CARD_IS_LOCKED status bit is set in the card status register. When the password sent does not correspond (in size and/or content) to the expected password, the LOCK_UNLOCK_FAILED error bit is set in the card status register, and the lock fails.

It is possible to set the password and to lock the card in the same sequence. In this case, the SDMMC card host module performs all the required steps for setting the password (see Setting the password on page 1088 ), however it is necessary to set the LOCK_UNLOCK bit in Step 3 when the new password command is sent.

When the password is previously set (PWD_LEN is not 0), the card is locked automatically after power on reset. An attempt to lock a locked card or to lock a card that does not have a password fails and the LOCK_UNLOCK_FAILED error bit is set in the card status register.

Unlocking the card

- 1. Select a card (SELECT/DESELECT_CARD, CMD7), if none is already selected.

- 2. Define the block length (SET_BLOCKLEN, CMD16) to send, given by the 8-bit cardlock/unlock mode (byte 0 in Table 209 ), the 8-bit PWD_LEN, and the number of bytes of the current password.

- 3. Send LOCK/UNLOCK (CMD42) with the appropriate data block size on the data line including the 16-bit CRC. The data block indicates the mode (LOCK_UNLOCK = 0), the length (PWD_LEN), and the password (PWD) itself.

- 4. When the password is matched, the card is unlocked and the CARD_IS_LOCKED status bit is cleared in the card status register. When the password sent is not correct in size and/or content and does not correspond to the expected password, the LOCK_UNLOCK_FAILED error bit is set in the card status register, and the card remains locked.

The unlocking function is only valid for the current power session. When the PWD field is not clear, the card is locked automatically on the next power-up.

An attempt to unlock an unlocked card fails and the LOCK_UNLOCK_FAILED error bit is set in the card status register.

Forcing erase

If the user has forgotten the password (PWD content), it is possible to access the card after clearing all the data on the card. This forced erase operation erases all card data and all password data.

- 1. Select a card (SELECT/DESELECT_CARD, CMD7), if none is already selected.

- 2. Set the block length (SET_BLOCKLEN, CMD16) to 1 byte. Only the 8-bit card lock/unlock byte (byte 0 in Table 209 ) is sent.

- 3. Send LOCK/UNLOCK (CMD42) with the appropriate data byte on the data line including the 16-bit CRC. The data block indicates the mode (ERASE = 1). All other bits must be zero.

- 4. When the ERASE bit is the only bit set in the data field, all card contents are erased, including the PWD and PWD_LEN fields, and the card is no longer locked. When any other bits are set, the LOCK_UNLOCK_FAILED error bit is set in the card status register and the card retains all of its data, and remains locked.

An attempt to use a force erase on an unlocked card fails and the LOCK_UNLOCK_FAILED error bit is set in the card status register.

30.4.11 Card status register

The response format R1 contains a 32-bit field named card status. This field is intended to transmit the card status information (which may be stored in a local status register) to the host. If not specified otherwise, the status entries are always related to the previously issued command.

Table 196 defines the different entries of the status. The type and clear condition fields in the table are abbreviated as follows:

Type:

- • E: error bit

- • S: status bit

- • R: detected and set for the actual command response

- • X: detected and set during command execution. The SDMMC card host must poll the card by issuing the status command to read these bits.

Clear condition:

- • A: according to the card current state

- • B: always related to the previous command. Reception of a valid command clears it (with a delay of one command)

- • C: clear by read

Table 196. Card status

| Bits | Identifier | Type | Value | Description | Clear condition |

|---|---|---|---|---|---|

| 31 | ADDRESS_OUT_OF_RANGE | E R X | '0'= no error '1'= error | The command address argument was out of the allowed range for this card. A multiple block or stream read/write operation is (although started in a valid address) attempting to read or write beyond the card capacity. | C |

| 30 | ADDRESS_MISALIGN | - | '0'= no error '1'= error | The commands address argument (in accordance with the currently set block length) positions the first data block misaligned to the card physical blocks. A multiple block read/write operation (although started with a valid address/block-length combination) is attempting to read or write a data block which is not aligned with the physical blocks of the card. | C |

| 29 | BLOCK_LEN_ERROR | - | '0'= no error '1'= error | Either the argument of a SET_BLOCKLEN command exceeds the maximum value allowed for the card, or the previously defined block length is illegal for the current command (e.g. the host issues a write command, the current block length is smaller than the maximum allowed value for the card and it is not allowed to write partial blocks) | C |

Table 196. Card status (continued)

| Bits | Identifier | Type | Value | Description | Clear condition |

|---|---|---|---|---|---|

| 28 | ERASE_SEQ_ERROR | - | '0'= no error '1'= error | An error in the sequence of erase commands occurred. | C |

| 27 | ERASE_PARAM | E X | '0'= no error '1'= error | An invalid selection of erase groups for erase occurred. | C |

| 26 | WP_VIOLATION | E X | '0'= no error '1'= error | Attempt to program a write-protected block. | C |

| 25 | CARD_IS_LOCKED | S R | '0'= card unlocked '1'= card locked | When set, signals that the card is locked by the host | A |

| 24 | LOCK_UNLOCK_FAILED | E X | '0'= no error '1'= error | Set when a sequence or password error has been detected in lock/unlock card command | C |

| 23 | COM_CRC_ERROR | E R | '0'= no error '1'= error | The CRC check of the previous command failed. | B |

| 22 | ILLEGAL_COMMAND | E R | '0'= no error '1'= error | Command not legal for the card state | B |

| 21 | CARD_ECC_FAILED | E X | '0'= success '1'= failure | Card internal ECC was applied but failed to correct the data. | C |

| 20 | CC_ERROR | E R | '0'= no error '1'= error | (Undefined by the standard) A card error occurred, which is not related to the host command. | C |

| 19 | ERROR | E X | '0'= no error '1'= error | (Undefined by the standard) A generic card error related to the (and detected during) execution of the last host command (e.g. read or write failures). | C |

| 18 | Reserved | ||||

| 17 | Reserved | ||||

| 16 | CID/CSD_OVERWRITE | E X | '0'= no error '1'= error | Can be either of the following errors: – The CID register has already been written and cannot be overwritten – The read-only section of the CSD does not match the card contents – An attempt to reverse the copy (set as original) or permanent WP (unprotected) bits was made | C |

| 15 | WP_ERASE_SKIP | E X | '0'= not protected '1'= protected | Set when only partial address space was erased due to existing write | C |

| 14 | CARD_ECC_DISABLED | S X | '0'= enabled '1'= disabled | The command has been executed without using the internal ECC. | A |

Table 196. Card status (continued)

| Bits | Identifier | Type | Value | Description | Clear condition |

|---|---|---|---|---|---|

| 13 | ERASE_RESET | - | '0'= cleared '1'= set | An erase sequence was cleared before executing because an out of erase sequence command was received (commands other than CMD35, CMD36, CMD38 or CMD13) | C |

| 12:9 | CURRENT_STATE | S R | 0 = Idle 1 = Ready 2 = Ident 3 = Stby 4 = Tran 5 = Data 6 = Rcv 7 = Prg 8 = Dis 9 = Btst 10-15 = reserved | The state of the card when receiving the command. If the command execution causes a state change, it will be visible to the host in the response on the next command. The four bits are interpreted as a binary number between 0 and 15. | B |

| 8 | READY_FOR_DATA | S R | '0'= not ready '1'= ready | Corresponds to buffer empty signalling on the bus | - |

| 7 | SWITCH_ERROR | E X | '0'= no error '1'= switch error | If set, the card did not switch to the expected mode as requested by the SWITCH command | B |

| 6 | Reserved | ||||

| 5 | APP_CMD | S R | '0' = Disabled '1' = Enabled | The card will expect ACMD, or an indication that the command has been interpreted as ACMD | C |

| 4 | Reserved for SD I/O Card | ||||

| 3 | AKE_SEQ_ERROR | E R | '0'= no error '1'= error | Error in the sequence of the authentication process | C |

| 2 | Reserved for application specific commands | ||||

| 1 | Reserved for manufacturer test mode | ||||

| 0 | |||||

30.4.12 SD status register

The SD status contains status bits that are related to the SD memory card proprietary features and may be used for future application-specific usage. The size of the SD Status is one data block of 512 bits. The contents of this register are transmitted to the SDMMC card host if ACMD13 is sent (CMD55 followed with CMD13). ACMD13 can be sent to a card in transfer state only (card is selected).

Table 197 defines the different entries of the SD status register. The type and clear condition fields in the table are abbreviated as follows:

Type:

- • E: error bit

- • S: status bit

- • R: detected and set for the actual command response

- • X: detected and set during command execution. The SDMMC card Host must poll the card by issuing the status command to read these bits

Clear condition:

- • A: according to the card current state

- • B: always related to the previous command. Reception of a valid command clears it (with a delay of one command)

- • C: clear by read

Table 197. SD status

| Bits | Identifier | Type | Value | Description | Clear condition |

|---|---|---|---|---|---|

| 511: 510 | DAT_BUS_WIDTH | S R | '00'= 1 (default) '01'= reserved '10'= 4 bit width '11'= reserved | Shows the currently defined databus width that was defined by SET_BUS_WIDTH command | A |

| 509 | SECURED_MODE | S R | '0'= Not in the mode '1'= In Secured Mode | Card is in Secured Mode of operation (refer to the “SD Security Specification”). | A |

| 508: 496 | Reserved | ||||

| 495: 480 | SD_CARD_TYPE | S R | '00xxh'= SD Memory Cards as defined in Physical Spec Ver1.01-2.00 ('x'= don't care). The following cards are currently defined: '0000'= Regular SD RD/WR Card. '0001'= SD ROM Card | In the future, the 8 LSBs will be used to define different variations of an SD memory card (each bit will define different SD types). The 8 MSBs will be used to define SD Cards that do not comply with current SD physical layer specification. | A |

| 479: 448 | SIZE_OF_PROTECTED_AREA | S R | Size of protected area (See below) | (See below) | A |

| 447: 440 | SPEED_CLASS | S R | Speed Class of the card (See below) | (See below) | A |

Table 197. SD status (continued)

| Bits | Identifier | Type | Value | Description | Clear condition |

|---|---|---|---|---|---|

| 439: 432 | PERFORMANCE_MOVE | S R | Performance of move indicated by 1 [MB/s] step. (See below) | (See below) | A |

| 431:428 | AU_SIZE | S R | Size of AU (See below) | (See below) | A |

| 427:424 | Reserved | ||||

| 423:408 | ERASE_SIZE | S R | Number of AUs to be erased at a time | (See below) | A |

| 407:402 | ERASE_TIMEOUT | S R | Timeout value for erasing areas specified by UNIT_OF_ERASE_AU | (See below) | A |

| 401:400 | ERASE_OFFSET | S R | Fixed offset value added to erase time. | (See below) | A |

| 399:312 | Reserved | ||||

| 311:0 | Reserved for Manufacturer | ||||

SIZE_OF_PROTECTED_AREA

Setting this field differs between standard- and high-capacity cards. In the case of a standard-capacity card, the capacity of protected area is calculated as follows:

SIZE_OF_PROTECTED_AREA is specified by the unit in MULT*BLOCK_LEN.

In the case of a high-capacity card, the capacity of protected area is specified in this field:

SIZE_OF_PROTECTED_AREA is specified by the unit in bytes.

SPEED_CLASS

This 8-bit field indicates the speed class and the value can be calculated by \( P_W/2 \) (where \( P_W \) is the write performance).

Table 198. Speed class code field

| SPEED_CLASS | Value definition |

|---|---|

| 00h | Class 0 |

| 01h | Class 2 |

| 02h | Class 4 |

| 03h | Class 6 |

| 04h – FFh | Reserved |

PERFORMANCE_MOVE

This 8-bit field indicates Pm (performance move) and the value can be set by 1 [MB/sec] steps. If the card does not move used RUs (recording units), Pm should be considered as infinity. Setting the field to FFh means infinity.

Table 199. Performance move field

| PERFORMANCE_MOVE | Value definition |

|---|---|

| 00h | Not defined |

| 01h | 1 [MB/sec] |

| 02h | 02h 2 [MB/sec] |

| ----- | ----- |

| FEh | 254 [MB/sec] |

| FFh | Infinity |

AU_SIZE

This 4-bit field indicates the AU size and the value can be selected in the power of 2 base from 16 KB.

Table 200. AU_SIZE field

| AU_SIZE | Value definition |

|---|---|

| 00h | Not defined |

| 01h | 16 KB |

| 02h | 32 KB |

| 03h | 64 KB |

| 04h | 128 KB |

| 05h | 256 KB |

| 06h | 512 KB |

| 07h | 1 MB |

| 08h | 2 MB |

| 09h | 4 MB |

| Ah – Fh | Reserved |

The maximum AU size, which depends on the card capacity, is defined in Table 201 . The card can be set to any AU size between RU size and maximum AU size.

Table 201. Maximum AU size

| Capacity | 16 MB-64 MB | 128 MB-256 MB | 512 MB | 1 GB-32 GB |

|---|---|---|---|---|

| Maximum AU Size | 512 KB | 1 MB | 2 MB | 4 MB |

ERASE_SIZE

This 16-bit field indicates NERASE . When NERASE numbers of AUs are erased, the timeout value is specified by ERASE_TIMEOUT (Refer to ERASE_TIMEOUT ). The host should determine the proper number of AUs to be erased in one operation so that the host can show the progress of the erase operation. If this field is set to 0, the erase timeout calculation is not supported.

Table 202. Erase size field

| ERASE_SIZE | Value definition |

|---|---|

| 0000h | Erase timeout calculation is not supported. |

| 0001h | 1 AU |

| 0002h | 2 AU |

| 0003h | 3 AU |

| ----- | ----- |

| FFFFh | 65535 AU |

ERASE_TIMEOUT

This 6-bit field indicates TERASE and the value indicates the erase timeout from offset when multiple AUs are being erased as specified by ERASE_SIZE . The range of ERASE_TIMEOUT can be defined as up to 63 seconds and the card manufacturer can choose any combination of ERASE_SIZE and ERASE_TIMEOUT depending on the implementation. Determining ERASE_TIMEOUT determines the ERASE_SIZE .

Table 203. Erase timeout field

| ERASE_TIMEOUT | Value definition |

|---|---|

| 00 | Erase timeout calculation is not supported. |

| 01 | 1 [sec] |

| 02 | 2 [sec] |

| 03 | 3 [sec] |

| ----- | ----- |

| 63 | 63 [sec] |

ERASE_OFFSET

This 2-bit field indicates TOFFSET and one of four values can be selected. This field is meaningless if the ERASE_SIZE and ERASE_TIMEOUT fields are set to 0.

Table 204. Erase offset field

| ERASE_OFFSET | Value definition |

|---|---|

| 0h | 0 [sec] |

| 1h | 1 [sec] |

Table 204. Erase offset field (continued)

| ERASE_OFFSET | Value definition |

|---|---|

| 2h | 2 [sec] |

| 3h | 3 [sec] |

30.4.13 SD I/O mode

SD I/O interrupts

To allow the SD I/O card to interrupt the MultiMediaCard/SD module, an interrupt function is available on a pin on the SD interface. Pin 8, used as SDMMC_D1 when operating in the 4-bit SD mode, signals the cards interrupt to the MultiMediaCard/SD module. The use of the interrupt is optional for each card or function within a card. The SD I/O interrupt is level-sensitive, which means that the interrupt line must be held active (low) until it is either recognized and acted upon by the MultiMediaCard/SD module or deasserted due to the end of the interrupt period. After the MultiMediaCard/SD module has serviced the interrupt, the interrupt status bit is cleared via an I/O write to the appropriate bit in the SD I/O card's internal registers. The interrupt output of all SD I/O cards is active low and the application must provide pull-up resistors externally on all data lines (SDMMC_D[3:0]). The MultiMediaCard/SD module samples the level of pin 8 (SDMMC_D/IRQ) into the interrupt detector only during the interrupt period. At all other times, the MultiMediaCard/SD module ignores this value.

The interrupt period is applicable for both memory and I/O operations. The definition of the interrupt period for operations with single blocks is different from the definition for multiple-block data transfers.

SD I/O suspend and resume

Within a multifunction SD I/O or a card with both I/O and memory functions, there are multiple devices (I/O and memory) that share access to the MMC/SD bus. To share access to the MMC/SD module among multiple devices, SD I/O and combo cards optionally implement the concept of suspend/resume. When a card supports suspend/resume, the MMC/SD module can temporarily halt a data transfer operation to one function or memory (suspend) to free the bus for a higher-priority transfer to a different function or memory. After this higher-priority transfer is complete, the original transfer is resumed (restarted) where it left off. Support of suspend/resume is optional on a per-card basis. To perform the suspend/resume operation on the MMC/SD bus, the MMC/SD module performs the following steps:

- 1. Determines the function currently using the SDMMC_D [3:0] line(s)

- 2. Requests the lower-priority or slower transaction to suspend

- 3. Waits for the transaction suspension to complete

- 4. Begins the higher-priority transaction

- 5. Waits for the completion of the higher priority transaction

- 6. Restores the suspended transaction

SD I/O ReadWait

The optional ReadWait (RW) operation is defined only for the SD 1-bit and 4-bit modes. The ReadWait operation allows the MMC/SD module to signal a card that it is reading multiple

registers (IO_RW_EXTENDED, CMD53) to temporarily stall the data transfer while allowing the MMC/SD module to send commands to any function within the SD I/O device. To determine when a card supports the ReadWait protocol, the MMC/SD module must test capability bits in the internal card registers. The timing for ReadWait is based on the interrupt period.

30.4.14 Commands and responses

Application-specific and general commands

The SDMMC card host module system is designed to provide a standard interface for a variety of applications types. In this environment, there is a need for specific customer/application features. To implement these features, two types of generic commands are defined in the standard: application-specific commands (ACMD) and general commands (GEN_CMD).

When the card receives the APP_CMD (CMD55) command, the card expects the next command to be an application-specific command. ACMDs have the same structure as regular MultiMediaCard commands and can have the same CMD number. The card recognizes it as ACMD because it appears after APP_CMD (CMD55). When the command immediately following the APP_CMD (CMD55) is not a defined application-specific command, the standard command is used. For example, when the card has a definition for SD_STATUS (ACMD13), and receives CMD13 immediately following APP_CMD (CMD55), this is interpreted as SD_STATUS (ACMD13). However, when the card receives CMD7 immediately following APP_CMD (CMD55) and the card does not have a definition for ACMD7, this is interpreted as the standard (SELECT/DESELECT_CARD) CMD7.

To use one of the manufacturer-specific ACMDs the SD card Host must perform the following steps:

- 1. Send APP_CMD (CMD55)

The card responds to the MultiMediaCard/SD module, indicating that the APP_CMD bit is set and an ACMD is now expected. - 2. Send the required ACMD

The card responds to the MultiMediaCard/SD module, indicating that the APP_CMD bit is set and that the accepted command is interpreted as an ACMD. When a nonACMD is sent, it is handled by the card as a normal MultiMediaCard command and the APP_CMD bit in the card status register stays clear.

When an invalid command is sent (neither ACMD nor CMD) it is handled as a standard MultiMediaCard illegal command error.

The bus transaction for a GEN_CMD is the same as the single-block read or write commands (WRITE_BLOCK, CMD24 or READ_SINGLE_BLOCK, CMD17). In this case, the argument denotes the direction of the data transfer rather than the address, and the data block has vendor-specific format and meaning.

The card must be selected (in transfer state) before sending GEN_CMD (CMD56). The data block size is defined by SET_BLOCKLEN (CMD16). The response to GEN_CMD (CMD56) is in R1b format.

Command types

Both application-specific and general commands are divided into the four following types:

- • broadcast command (BC) : sent to all cards; no responses returned.

- • broadcast command with response (BCR) : sent to all cards; responses received from all cards simultaneously.

- • addressed (point-to-point) command (AC) : sent to the card that is selected; does not include a data transfer on the SDMMC_D line(s).

- • addressed (point-to-point) data transfer command (ADTC) : sent to the card that is selected; includes a data transfer on the SDMMC_D line(s).

Command formats

See Table 188 on page 1074 for command formats.

Commands for the MultiMediaCard/SD module

Table 205. Block-oriented write commands

| CMD index | Type | Argument | Response format | Abbreviation | Description |

|---|---|---|---|---|---|

| CMD23 | ac | [31:16] set to 0 [15:0] number of blocks | R1 | SET_BLOCK_COUNT | Defines the number of blocks which are going to be transferred in the multiple-block read or write command that follows. |

| CMD24 | adtc | [31:0] data address | R1 | WRITE_BLOCK | Writes a block of the size selected by the SET_BLOCKLEN command. |

| CMD25 | adtc | [31:0] data address | R1 | WRITE_MULTIPLE_BLOCK | Continuously writes blocks of data until a STOP_TRANSMISSION follows or the requested number of blocks has been received. |

| CMD26 | adtc | [31:0] stuff bits | R1 | PROGRAM_CID | Programming of the card identification register. This command must be issued only once per card. The card contains hardware to prevent this operation after the first programming. Normally this command is reserved for manufacturer. |

| CMD27 | adtc | [31:0] stuff bits | R1 | PROGRAM_CSD | Programming of the programmable bits of the CSD. |

Table 206. Block-oriented write protection commands

| CMD index | Type | Argument | Response format | Abbreviation | Description |

|---|---|---|---|---|---|

| CMD28 | ac | [31:0] data address | R1b | SET_WRITE_PROT | If the card has write protection features, this command sets the write protection bit of the addressed group. The properties of write protection are coded in the card-specific data (WP_GRP_SIZE). |

| CMD29 | ac | [31:0] data address | R1b | CLR_WRITE_PROT | If the card provides write protection features, this command clears the write protection bit of the addressed group. |

| CMD30 | adtc | [31:0] write protect data address | R1 | SEND_WRITE_PROT | If the card provides write protection features, this command asks the card to send the status of the write protection bits. |

| CMD31 | Reserved | ||||

Table 207. Erase commands

| CMD index | Type | Argument | Response format | Abbreviation | Description |

|---|---|---|---|---|---|