28. Serial peripheral interface / integrated interchip sound (SPI/I2S)

28.1 Introduction

The SPI/I 2 S interface can be used to communicate with external devices using the SPI protocol or the I 2 S audio protocol. SPI or I 2 S mode is selectable by software. SPI Motorola mode is selected by default after a device reset.

The serial peripheral interface (SPI) protocol supports half-duplex, full-duplex and simplex synchronous, serial communication with external devices. The interface can be configured as master and in this case it provides the communication clock (SCK) to the external slave device. The interface is also capable of operating in multimaster configuration.

The integrated interchip sound (I 2 S) protocol is also a synchronous serial communication interface. It can operate in slave or master mode with half-duplex communication. Full-duplex operations are possible by combining two I2S blocks. It can address four different audio standards including the Philips I 2 S standard, the MSB- and LSB-justified standards and the PCM standard.

28.2 SPI main features

- • Master or slave operation

- • Full-duplex synchronous transfers on three lines

- • Half-duplex synchronous transfer on two lines (with bidirectional data line)

- • Simplex synchronous transfers on two lines (with unidirectional data line)

- • 4 to 16-bit data size selection

- • Multimaster mode capability

- • 8 master mode baud rate prescalers up to \( f_{PCLK}/2 \)

- • Slave mode frequency up to \( f_{PCLK}/2 \)

- • NSS management by hardware or software for both master and slave: dynamic change of master/slave operations

- • Programmable clock polarity and phase

- • Programmable data order with MSB-first or LSB-first shifting

- • Dedicated transmission and reception flags with interrupt capability

- • SPI bus busy status flag

- • SPI Motorola support

- • Hardware CRC feature for reliable communication:

- – CRC value can be transmitted as last byte in Tx mode

- – Automatic CRC error checking for last received byte

- • Master mode fault, overrun flags with interrupt capability

- • CRC Error flag

- • Two 32-bit embedded Rx and Tx FIFOs with DMA capability

- • Enhanced TI and NSS pulse modes support

28.3 I2S main features

- • Half-duplex communication (only transmitter or receiver)

- • Master or slave operations

- • 8-bit programmable linear prescaler to reach accurate audio sample frequencies (from 8 kHz to 192 kHz)

- • Data format may be 16-bit, 24-bit, or 32-bit

- • Packet frame is fixed to 16-bit (16-bit data frame) or 32-bit (16-bit, 24-bit, 32-bit data frame) by audio channel

- • Programmable clock polarity (steady state)

- • Underrun flag in slave transmission mode, overrun flag in reception mode (master and slave) and Frame Error Flag in reception and transmitter mode (slave only)

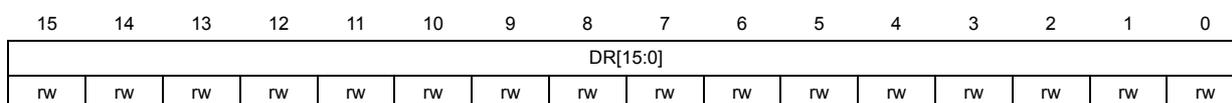

- • 16-bit register for transmission and reception with one data register for both channel sides

- • Supported I

2

S protocols:

- – I 2 S Philips standard

- – MSB-justified standard (left-justified)

- – LSB-justified standard (right-justified)

- – PCM standard (with short and long frame synchronization on 16-bit channel frame or 16-bit data frame extended to 32-bit channel frame)

- • Data direction is always MSB first

- • DMA capability for transmission and reception (16-bit wide)

- • Master clock can be output to drive an external audio component. The ratio is fixed at \( 256 \times f_s \) for all I2S modes, and to \( 128 \times f_s \) for all PCM modes (where \( f_s \) is the audio sampling frequency).

28.4 SPI/I2S implementation

The following table describes all the SPI instances and their features embedded in the devices.

Table 173. STM32F72xxx and STM32F73xxx SPI and SPI/I2S implementation

| SPI Features | SPI2S1 | SPI2S2 | SPI2S3 | SPI4 | SPI5 |

|---|---|---|---|---|---|

| Enhanced NSSP & TI modes | Yes | Yes | Yes | Yes | Yes |

| Hardware CRC calculation | Yes | Yes | Yes | Yes | Yes |

| I 2 S support | Yes | Yes | Yes | No | No |

| Data size configurable | from 4 to 16 bits | from 4 to 16 bits | from 4 to 16 bits | from 4 to 16 bits | from 4 to 16 bits |

| Rx/Tx FIFO size | 32 bits | 32 bits | 32 bits | 32 bits | 32 bits |

| Wake-up capability from Low-power Sleep | Yes | Yes | Yes | Yes | Yes |

28.5 SPI functional description

28.5.1 General description

The SPI allows synchronous, serial communication between the MCU and external devices. Application software can manage the communication by polling the status flag or using dedicated SPI interrupt. The main elements of SPI and their interactions are shown in the following block diagram Figure 343 .

Figure 343. SPI block diagram

![Figure 343. SPI block diagram. The diagram shows the internal architecture of an SPI interface. On the left, four pins are shown: MOSI, MISO, SCK, and NSS. The MOSI and MISO pins are connected to a bidirectional shift register. Data is written to the shift register from a 'Tx FIFO' and read from the shift register to an 'Rx FIFO'. The 'Rx FIFO' is connected to an 'Address and data bus'. The 'Tx FIFO' is connected to a 'Communication controller'. The 'Communication controller' is connected to the 'Address and data bus', a 'CRC controller', and the 'NSS logic'. The 'CRC controller' is connected to the 'Communication controller' and the 'Address and data bus'. The 'NSS logic' is connected to the 'Communication controller' and the 'NSS pin'. The 'Communication controller' is also connected to a 'Baud rate generator', which is connected to the 'SCK pin'. The 'Communication controller' has several control inputs: RXONLY, CPOL, CPHA, DS[0:3], BIDIOE, and BR[2:0]. The 'CRC controller' has control inputs: CRCEN, CRCNEXT, and CRCL. The 'NSS logic' has an 'Internal NSS' input. The diagram is labeled MS30117V1 in the bottom right corner.](/RM0431-STM32F72-73/dd0387b748fea5bcd5dfe597425b0afb_img.jpg)

Four I/O pins are dedicated to SPI communication with external devices.

- • MISO: Master In / Slave Out data. In the general case, this pin is used to transmit data in slave mode and receive data in master mode.

- • MOSI: Master Out / Slave In data. In the general case, this pin is used to transmit data in master mode and receive data in slave mode.

- • SCK: Serial Clock output pin for SPI masters and input pin for SPI slaves.

- •

NSS:

Slave select pin. Depending on the SPI and NSS settings, this pin can be used to either:

- – select an individual slave device for communication

- – synchronize the data frame or

- – detect a conflict between multiple masters

See Section 28.5.5: Slave select (NSS) pin management for details.

The SPI bus allows the communication between one master device and one or more slave devices. The bus consists of at least two wires - one for the clock signal and the other for synchronous data transfer. Other signals can be added depending on the data exchange between SPI nodes and their slave select signal management.

28.5.2 Communications between one master and one slave

The SPI allows the MCU to communicate using different configurations, depending on the device targeted and the application requirements. These configurations use 2 or 3 wires (with software NSS management) or 3 or 4 wires (with hardware NSS management). Communication is always initiated by the master.

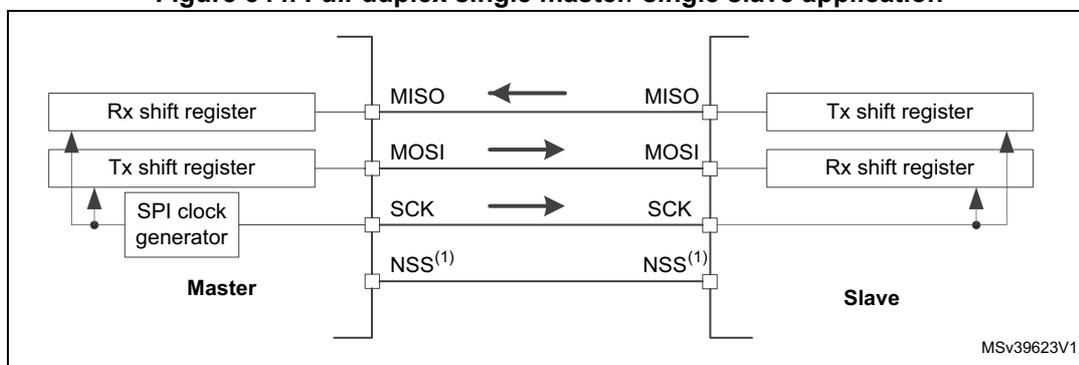

Full-duplex communication

By default, the SPI is configured for full-duplex communication. In this configuration, the shift registers of the master and slave are linked using two unidirectional lines between the MOSI and the MISO pins. During SPI communication, data is shifted synchronously on the SCK clock edges provided by the master. The master transmits the data to be sent to the slave via the MOSI line and receives data from the slave via the MISO line. When the data frame transfer is complete (all the bits are shifted) the information between the master and slave is exchanged.

Figure 344. Full-duplex single master/ single slave application

- 1. The NSS pins can be used to provide a hardware control flow between master and slave. Optionally, the pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and slave. For more details see Section 28.5.5: Slave select (NSS) pin management .

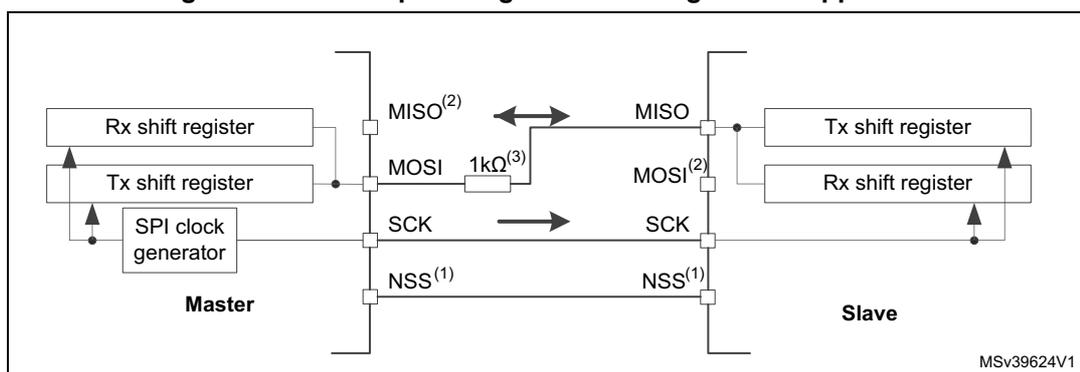

Half-duplex communication

The SPI can communicate in half-duplex mode by setting the BIDIMODE bit in the SPIx_CR1 register. In this configuration, one single cross connection line is used to link the shift registers of the master and slave together. During this communication, the data is synchronously shifted between the shift registers on the SCK clock edge in the transfer direction selected reciprocally by both master and slave with the BDIOE bit in their SPIx_CR1 registers. In this configuration, the master's MISO pin and the slave's MOSI pin are free for other application uses and act as GPIOs.

Figure 345. Half-duplex single master/ single slave application

- 1. The NSS pins can be used to provide a hardware control flow between master and slave. Optionally, the pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and slave. For more details see Section 28.5.5: Slave select (NSS) pin management .

- 2. In this configuration, the master's MISO pin and the slave's MOSI pin can be used as GPIOs.

- 3. A critical situation can happen when communication direction is changed not synchronously between two nodes working at bidirectional mode and new transmitter accesses the common data line while former transmitter still keeps an opposite value on the line (the value depends on SPI configuration and communication data). Both nodes then fight while providing opposite output levels on the common line temporary till next node changes its direction settings correspondingly, too. It is suggested to insert a serial resistance between MISO and MOSI pins at this mode to protect the outputs and limit the current blowing between them at this situation.

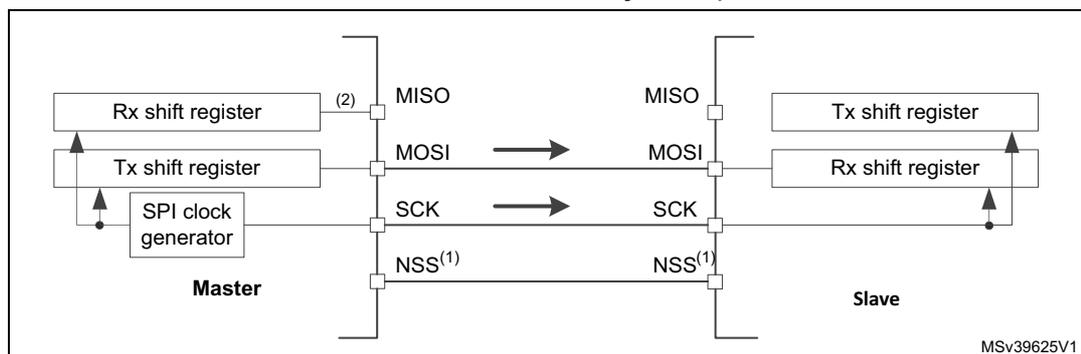

Simplex communications

The SPI can communicate in simplex mode by setting the SPI in transmit-only or in receive-only using the RXONLY bit in the SPIx_CR1 register. In this configuration, only one line is used for the transfer between the shift registers of the master and slave. The remaining MISO and MOSI pins pair is not used for communication and can be used as standard GPIOs.

- • Transmit-only mode (RXONLY=0): The configuration settings are the same as for full-duplex. The application has to ignore the information captured on the unused input pin. This pin can be used as a standard GPIO.

- • Receive-only mode (RXONLY=1): The application can disable the SPI output function by setting the RXONLY bit. In slave configuration, the MISO output is disabled and the pin can be used as a GPIO. The slave continues to receive data from the MOSI pin while its slave select signal is active (see 28.5.5: Slave select (NSS) pin management ). Received data events appear depending on the data buffer configuration. In the master configuration, the MOSI output is disabled and the pin can be used as a GPIO. The clock signal is generated continuously as long as the SPI is enabled. The only way to stop the clock is to clear the RXONLY bit or the SPE bit and wait until the incoming pattern from the MISO pin is finished and fills the data buffer structure, depending on its configuration.

Figure 346. Simplex single master/single slave application (master in transmit-only/ slave in receive-only mode)

The diagram illustrates a simplex single master/single slave application. On the left, the Master block contains an Rx shift register, a Tx shift register, and an SPI clock generator. On the right, the Slave block contains a Tx shift register and an Rx shift register. The connections are as follows:

- The Master's MISO pin (labeled (2)) is connected to the Slave's MISO pin.

- The Master's MOSI pin is connected to the Slave's MOSI pin.

- The Master's SCK pin is connected to the Slave's SCK pin.

- The Master's NSS (1) pin is connected to the Slave's NSS (1) pin.

- 1. The NSS pins can be used to provide a hardware control flow between master and slave. Optionally, the pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and slave. For more details see Section 28.5.5: Slave select (NSS) pin management .

- 2. An accidental input information is captured at the input of transmitter Rx shift register. All the events associated with the transmitter receive flow must be ignored in standard transmit only mode (e.g. OVR flag).

- 3. In this configuration, both the MISO pins can be used as GPIOs.

Note: Any simplex communication can be alternatively replaced by a variant of the half-duplex communication with a constant setting of the transaction direction (bidirectional mode is enabled while BDIO bit is not changed).

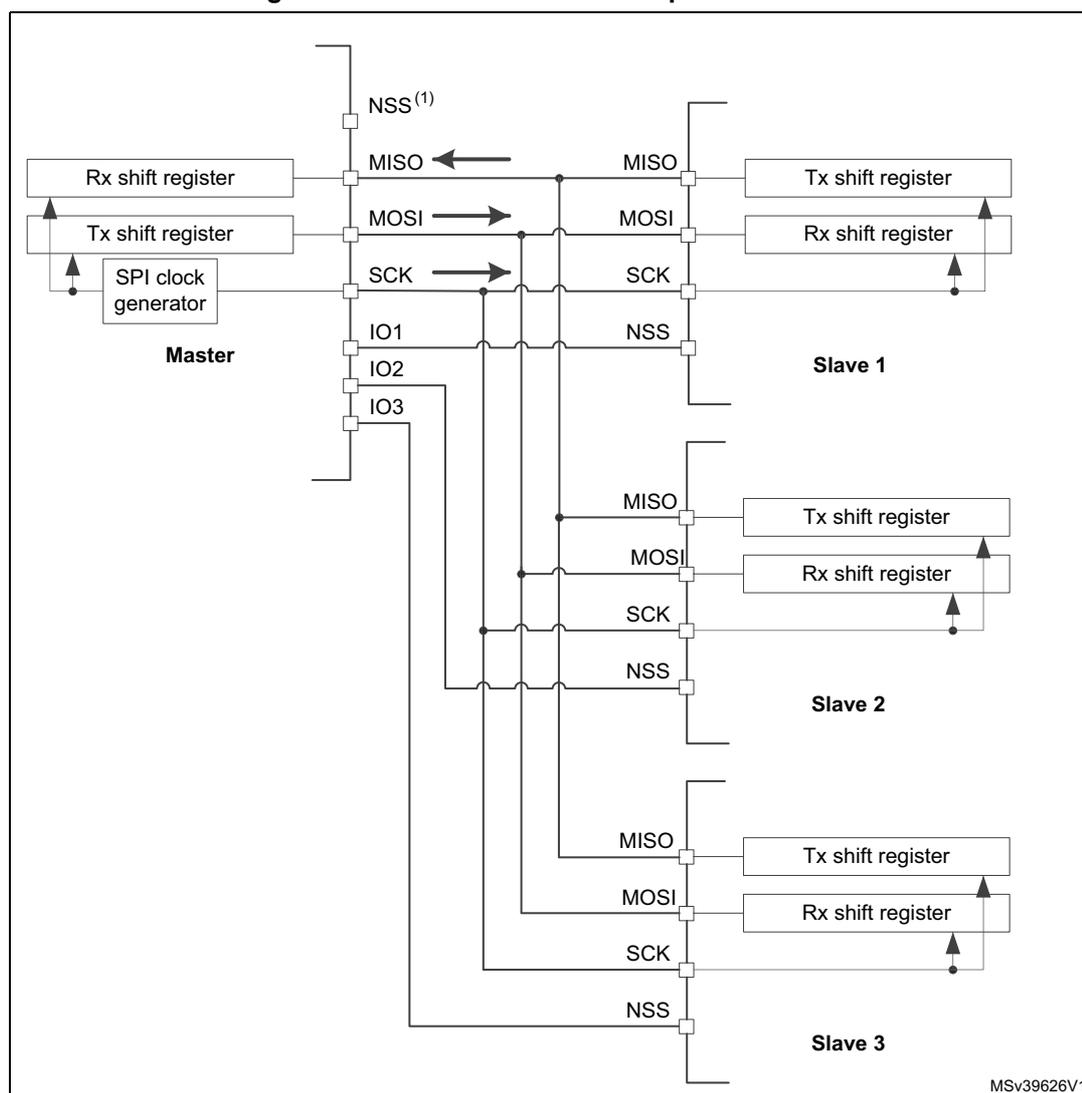

28.5.3 Standard multislave communication

In a configuration with two or more independent slaves, the master uses GPIO pins to manage the chip select lines for each slave (see Figure 347 ). The master must select one of the slaves individually by pulling low the GPIO connected to the slave NSS input. When this is done, a standard master and dedicated slave communication is established.

Figure 347. Master and three independent slaves

- 1. NSS pin is not used on master side at this configuration. It has to be managed internally (SSM=1, SSI=1) to prevent any MODF error.

- 2. As MISO pins of the slaves are connected together, all slaves must have the GPIO configuration of their MISO pin set as alternate function open-drain (see I/O alternate function input/output section (GPIO)).

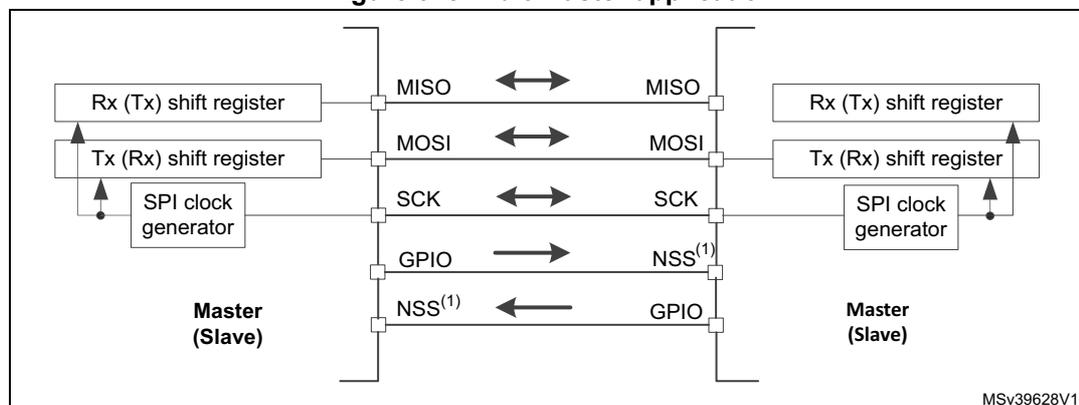

28.5.4 Multimaster communication

Unless SPI bus is not designed for a multimaster capability primarily, the user can use built-in feature which detects a potential conflict between two nodes trying to master the bus at the same time. For this detection, NSS pin is used configured at hardware input mode.

The connection of more than two SPI nodes working at this mode is impossible as only one node can apply its output on a common data line at time.

When nodes are non active, both stay at slave mode by default. Once one node wants to overtake control on the bus, it switches itself into master mode and applies active level on the slave select input of the other node via dedicated GPIO pin. After the session is completed, the active slave select signal is released and the node mastering the bus temporarily returns back to passive slave mode waiting for next session start.

If potentially both nodes raised their mastering request at the same time a bus conflict event appears (see mode fault MODF event). Then the user can apply some simple arbitration process (e.g. to postpone next attempt by predefined different time-outs applied at both nodes).

Figure 348. Multimaster application

- 1. The NSS pin is configured at hardware input mode at both nodes. Its active level enables the MISO line output control as the passive node is configured as a slave.

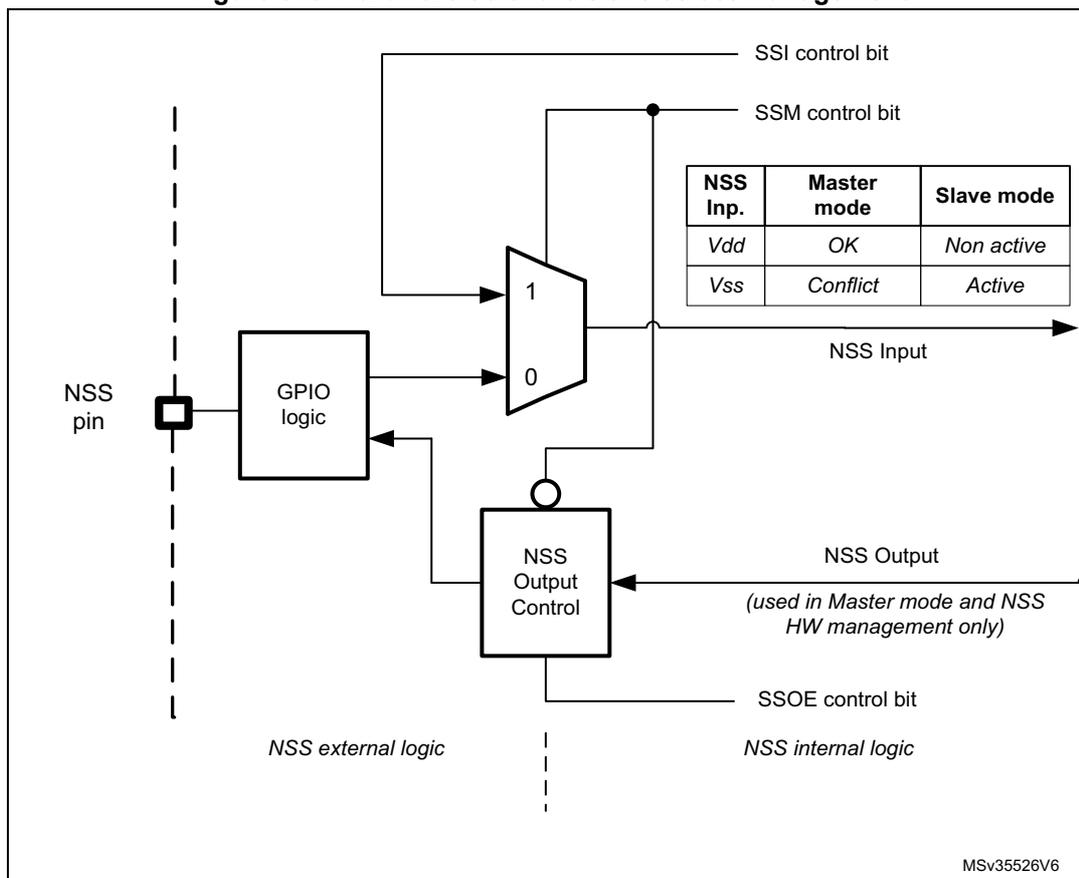

28.5.5 Slave select (NSS) pin management

In slave mode, the NSS works as a standard “chip select” input and lets the slave communicate with the master. In master mode, NSS can be used either as output or input. As an input it can prevent multimaster bus collision, and as an output it can drive a slave select signal of a single slave.

Hardware or software slave select management can be set using the SSM bit in the SPIx_CR1 register:

- • Software NSS management (SSM = 1) : in this configuration, slave select information is driven internally by the SSI bit value in register SPIx_CR1. The external NSS pin is free for other application uses.

- •

Hardware NSS management (SSM = 0)

: in this case, there are two possible configurations. The configuration used depends on the NSS output configuration (SSOE bit in register SPIx_CR1).

- – NSS output enable (SSM=0,SSOE = 1) : this configuration is only used when the MCU is set as master. The NSS pin is managed by the hardware. The NSS signal is driven low as soon as the SPI is enabled in master mode (SPE=1), and is kept low until the SPI is disabled (SPE =0). A pulse can be generated between continuous communications if NSS pulse mode is activated (NSSP=1). The SPI cannot work in multimaster configuration with this NSS setting.

- – NSS output disable (SSM=0, SSOE = 0) : if the microcontroller is acting as the master on the bus, this configuration allows multimaster capability. If the NSS pin is pulled low in this mode, the SPI enters master mode fault state and the device is automatically reconfigured in slave mode. In slave mode, the NSS pin works as a standard “chip select” input and the slave is selected while NSS line is at low level.

Figure 349. Hardware/software slave select management

The diagram illustrates the internal logic for slave select (NSS) management. On the left, the 'NSS pin' is connected to 'GPIO logic'. This logic feeds into a 2-to-1 multiplexer. The multiplexer's inputs are labeled '1' and '0'. Input '1' is connected to the 'SSI control bit', and input '0' is connected to the 'SSM control bit'. The output of the multiplexer is the 'NSS Input'. Below the multiplexer, there is an 'NSS Output Control' block. This block receives the 'NSS Input' and the 'SSOE control bit' as inputs and produces the 'NSS Output'. A note indicates that the 'NSS Output' is 'used in Master mode and NSS HW management only'. The diagram is divided into 'NSS external logic' (left of the dashed line) and 'NSS internal logic' (right of the dashed line). A table on the right provides settings for the 'NSS Inp.'.

| NSS Inp. | Master mode | Slave mode |

|---|---|---|

| Vdd | OK | Non active |

| Vss | Conflict | Active |

MSv35526V6

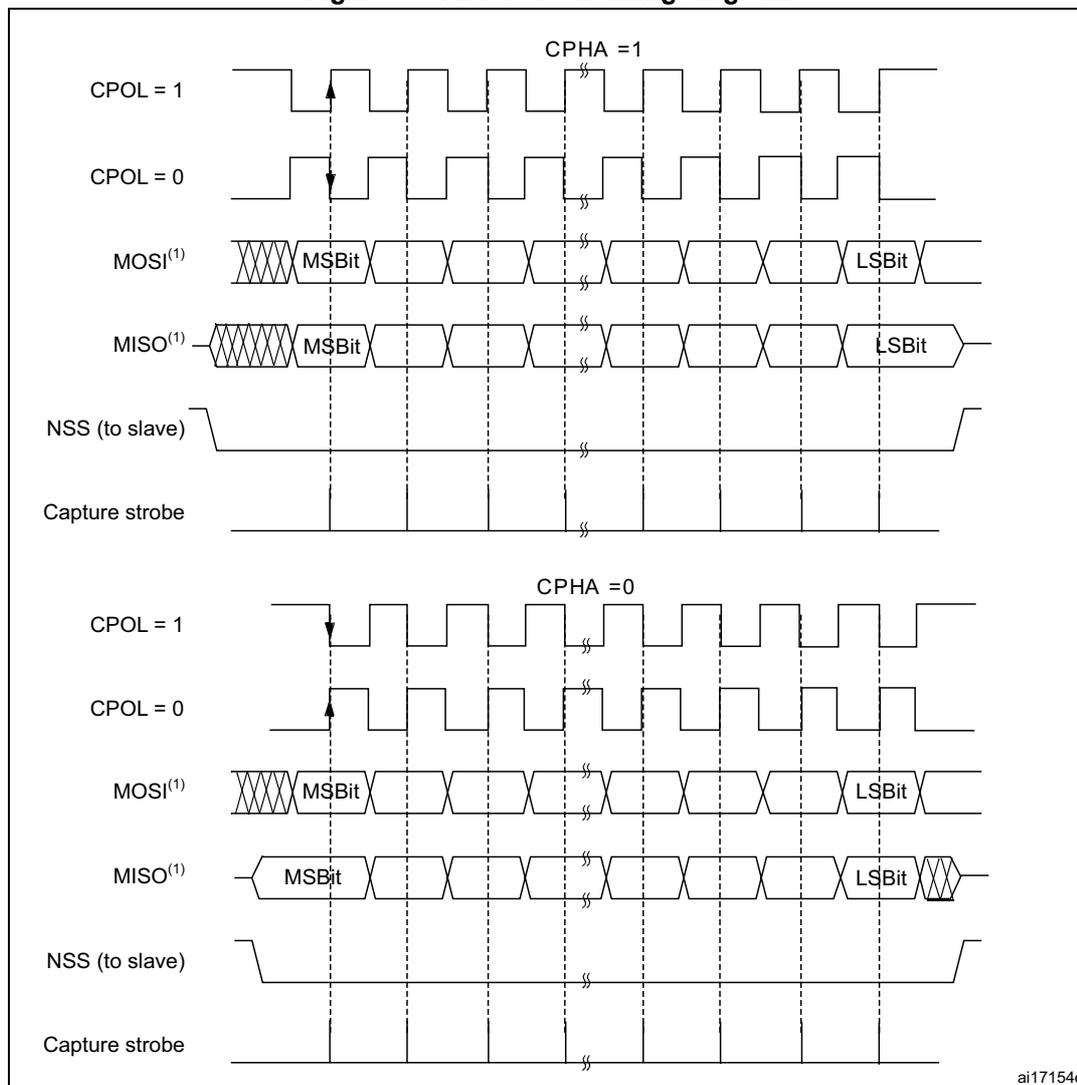

28.5.6 Communication formats

During SPI communication, receive and transmit operations are performed simultaneously. The serial clock (SCK) synchronizes the shifting and sampling of the information on the data lines. The communication format depends on the clock phase, the clock polarity and the data frame format. To be able to communicate together, the master and slaves devices must follow the same communication format.

Clock phase and polarity controls

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits in the SPIx_CR1 register. The CPOL (clock polarity) bit controls the idle state value of the clock when no data is being transferred. This bit affects both master and slave modes. If CPOL is reset, the SCK pin has a low-level idle state. If CPOL is set, the SCK pin has a high-level idle state.

If the CPHA bit is set, the second edge on the SCK pin captures the first data bit transacted (falling edge if the CPOL bit is reset, rising edge if the CPOL bit is set). Data are latched on each occurrence of this clock transition type. If the CPHA bit is reset, the first edge on the SCK pin captures the first data bit transacted (falling edge if the CPOL bit is set, rising edge if the CPOL bit is reset). Data are latched on each occurrence of this clock transition type.

The combination of CPOL (clock polarity) and CPHA (clock phase) bits selects the data capture clock edge.

Figure 350, shows an SPI full-duplex transfer with the four combinations of the CPHA and CPOL bits.

Note: Prior to changing the CPOL/CPHA bits the SPI must be disabled by resetting the SPE bit. The idle state of SCK must correspond to the polarity selected in the SPIx_CR1 register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

Figure 350. Data clock timing diagram

The figure shows two timing diagrams for SPI full-duplex transfer. The top diagram is for CPHA = 1, and the bottom diagram is for CPHA = 0. Each diagram shows the relationship between the clock (SCK), master output slave input (MOSI), master input slave output (MISO), and the capture strobe. The clock polarity (CPOL) can be 1 or 0. In the CPHA = 1 diagram, data is captured on the rising edge of the clock. In the CPHA = 0 diagram, data is captured on the falling edge of the clock. The MOSI and MISO lines show the transfer of multiple bits, with the most significant bit (MSB) and least significant bit (LSB) indicated. The capture strobe is a pulse that is active during the data capture edge. The NSS (to slave) line is shown as a low-active signal. The diagrams are labeled with 'ai17154e' in the bottom right corner.

- 1. The order of data bits depends on LSBFIRST bit setting.

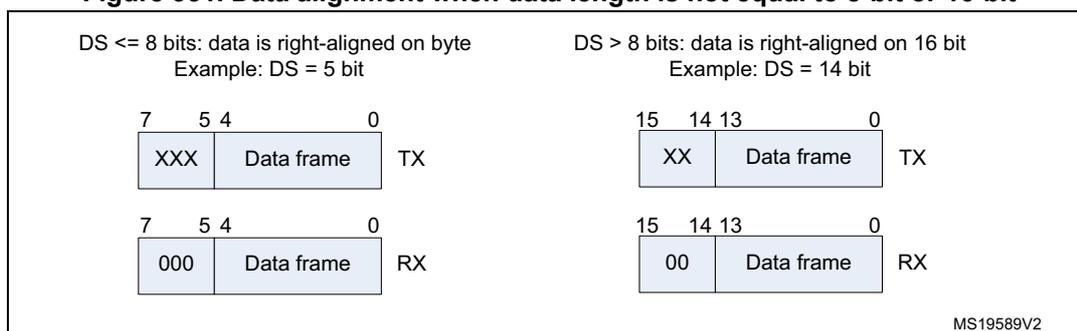

Data frame format

The SPI shift register can be set up to shift out MSB-first or LSB-first, depending on the value of the LSBFIRST bit. The data frame size is chosen by using the DS bits. It can be set from 4-bit up to 16-bit length and the setting applies for both transmission and reception. Whatever the selected data frame size, read access to the FIFO must be aligned with the FRXTH level. When the SPIx_DR register is accessed, data frames are always right-aligned into either a byte (if the data fits into a byte) or a half-word (see Figure 351). During communication, only bits within the data frame are clocked and transferred.

Figure 351. Data alignment when data length is not equal to 8-bit or 16-bit

| DS ≤ 8 bits: data is right-aligned on byte Example: DS = 5 bit | DS > 8 bits: data is right-aligned on 16 bit Example: DS = 14 bit | ||||

|---|---|---|---|---|---|

| 7 | 5 4 | 0 | 15 | 14 13 | 0 |

| XXX | Data frame | TX | XX | Data frame TX | |

| 7 | 5 4 | 0 | 15 | 14 13 | 0 |

| 000 | Data frame | RX | 00 | Data frame RX | |

MS19589V2

Note: The minimum data length is 4 bits. If a data length of less than 4 bits is selected, it is forced to an 8-bit data frame size.

28.5.7 Configuration of SPI

The configuration procedure is almost the same for master and slave. For specific mode setups, follow the dedicated sections. When a standard communication is to be initialized, perform these steps:

- Write proper GPIO registers: Configure GPIO for MOSI, MISO and SCK pins.

- Write to the SPI_CR1 register:

- Configure the serial clock baud rate using the BR[2:0] bits (Note: 4).

- Configure the CPOL and CPHA bits combination to define one of the four relationships between the data transfer and the serial clock (CPHA must be cleared in NSSP mode). (Note: 2 - except the case when CRC is enabled at TI mode).

- Select simplex or half-duplex mode by configuring RXONLY or BIDIMODE and BIDIOE (RXONLY and BIDIMODE cannot be set at the same time).

- Configure the LSBFIRST bit to define the frame format (Note: 2).

- Configure the CRCL and CRCEN bits if CRC is needed (while SCK clock signal is at idle state).

- Configure SSM and SSI (Notes: 2 & 3).

- Configure the MSTR bit (in multimaster NSS configuration, avoid conflict state on NSS if master is configured to prevent MODF error).

- Write to SPI_CR2 register:

- Configure the DS[3:0] bits to select the data length for the transfer.

- Configure SSOE (Notes: 1 & 2 & 3).

- Set the FRF bit if the TI protocol is required (keep NSSP bit cleared in TI mode).

- Set the NSSP bit if the NSS pulse mode between two data units is required (keep CHPA and TI bits cleared in NSSP mode).

- Configure the FRXTH bit. The RXFIFO threshold must be aligned to the read access size for the SPIx_DR register.

- Initialize LDMA_TX and LDMA_RX bits if DMA is used in packed mode.

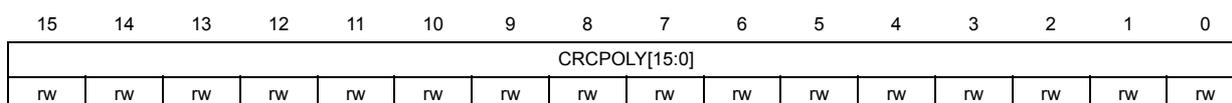

- Write to SPI_CRCPR register: Configure the CRC polynomial if needed.

- Write proper DMA registers: Configure DMA streams dedicated for SPI Tx and Rx in DMA registers if the DMA streams are used.

- Note:

- (1) Step is not required in slave mode.

- (2) Step is not required in TI mode.

- (3) Step is not required in NSSP mode.

- (4) The step is not required in slave mode except slave working at TI mode

28.5.8 Procedure for enabling SPI

It is recommended to enable the SPI slave before the master sends the clock. If not, undesired data transmission might occur. The data register of the slave must already contain data to be sent before starting communication with the master (either on the first edge of the communication clock, or before the end of the ongoing communication if the clock signal is continuous). The SCK signal must be settled at an idle state level corresponding to the selected polarity before the SPI slave is enabled.

The master at full-duplex (or in any transmit-only mode) starts to communicate when the SPI is enabled and TXFIFO is not empty, or with the next write to TXFIFO.

In any master receive only mode (RXONLY = 1 or BIDIMODE = 1 & BIDIOE = 0), master starts to communicate and the clock starts running immediately after SPI is enabled.

For handling DMA, follow the dedicated section.

28.5.9 Data transmission and reception procedures

RXFIFO and TXFIFO

All SPI data transactions pass through the 32-bit embedded FIFOs. This enables the SPI to work in a continuous flow, and prevents overruns when the data frame size is short. Each direction has its own FIFO called TXFIFO and RXFIFO. These FIFOs are used in all SPI modes except for receiver-only mode (slave or master) with CRC calculation enabled (see Section 28.5.14: CRC calculation ).

The handling of FIFOs depends on the data exchange mode (duplex, simplex), data frame format (number of bits in the frame), access size performed on the FIFO data registers (8-bit or 16-bit), and whether or not data packing is used when accessing the FIFOs (see Section 28.5.13: TI mode ).

A read access to the SPIx_DR register returns the oldest value stored in RXFIFO that has not been read yet. A write access to the SPIx_DR stores the written data in the TXFIFO at the end of a send queue. The read access must be always aligned with the RXFIFO threshold configured by the FRXTH bit in SPIx_CR2 register. FTLVL[1:0] and FRLVL[1:0] bits indicate the current occupancy level of both FIFOs.

A read access to the SPIx_DR register must be managed by the RXNE event. This event is triggered when data is stored in RXFIFO and the threshold (defined by FRXTH bit) is reached. When RXNE is cleared, RXFIFO is considered to be empty. In a similar way, write access of a data frame to be transmitted is managed by the TXE event. This event is triggered when the TXFIFO level is less than or equal to half of its capacity. Otherwise TXE is cleared and the TXFIFO is considered as full. In this way, RXFIFO can store up to four data frames, whereas TXFIFO can only store up to three when the data frame format is not greater than 8 bits. This difference prevents possible corruption of 3x 8-bit data frames already stored in the TXFIFO when software tries to write more data in 16-bit mode into TXFIFO. Both TXE and RXNE events can be polled or handled by interrupts. See Figure 353 through Figure 356 .

Another way to manage the data exchange is to use DMA (see Communication using DMA (direct memory addressing) ).

If the next data is received when the RXFIFO is full, an overrun event occurs (see description of OVR flag at Section 28.5.10: SPI status flags ). An overrun event can be polled or handled by an interrupt.

The BSY bit being set indicates ongoing transaction of a current data frame. When the clock signal runs continuously, the BSY flag stays set between data frames at master but becomes low for a minimum duration of one SPI clock at slave between each data frame transfer.

Sequence handling

A few data frames can be passed at single sequence to complete a message. When transmission is enabled, a sequence begins and continues while any data is present in the TXFIFO of the master. The clock signal is provided continuously by the master until TXFIFO becomes empty, then it stops waiting for additional data.

In receive-only modes, half-duplex (BIDIMODE=1, BIDIOE=0) or simplex (BIDIMODE=0, RXONLY=1) the master starts the sequence immediately when both SPI is enabled and receive-only mode is activated. The clock signal is provided by the master and it does not stop until either SPI or receive-only mode is disabled by the master. The master receives data frames continuously up to this moment.

While the master can provide all the transactions in continuous mode (SCK signal is continuous) it has to respect slave capability to handle data flow and its content at anytime. When necessary, the master must slow down the communication and provide either a slower clock or separate frames or data sessions with sufficient delays. Be aware there is no underflow error signal for master or slave in SPI mode, and data from the slave is always transacted and processed by the master even if the slave could not prepare it correctly in time. It is preferable for the slave to use DMA, especially when data frames are shorter and bus rate is high.

Each sequence must be encased by the NSS pulse in parallel with the multislave system to select just one of the slaves for communication. In a single slave system it is not necessary to control the slave with NSS, but it is often better to provide the pulse here too, to synchronize the slave with the beginning of each data sequence. NSS can be managed by both software and hardware (see Section 28.5.5: Slave select (NSS) pin management ).

When the BSY bit is set it signifies an ongoing data frame transaction. When the dedicated frame transaction is finished, the RXNE flag is raised. The last bit is just sampled and the complete data frame is stored in the RXFIFO.

Procedure for disabling the SPI

When SPI is disabled, it is mandatory to follow the disable procedures described in this paragraph. It is important to do this before the system enters a low-power mode when the peripheral clock is stopped. Ongoing transactions can be corrupted in this case. In some modes the disable procedure is the only way to stop continuous communication running.

Master in full-duplex or transmit only mode can finish any transaction when it stops providing data for transmission. In this case, the clock stops after the last data transaction. Special care must be taken in packing mode when an odd number of data frames are transacted to prevent some dummy byte exchange (refer to Data packing section). Before the SPI is disabled in these modes, the user must follow standard disable procedure. When

the SPI is disabled at the master transmitter while a frame transaction is ongoing or next data frame is stored in TXFIFO, the SPI behavior is not guaranteed.

When the master is in any receive only mode, the only way to stop the continuous clock is to disable the peripheral by SPE=0. This must occur in specific time window within last data frame transaction just between the sampling time of its first bit and before its last bit transfer starts (in order to receive a complete number of expected data frames and to prevent any additional “dummy” data reading after the last valid data frame). Specific procedure must be followed when disabling SPI in this mode.

Data received but not read remains stored in RXFIFO when the SPI is disabled, and must be processed the next time the SPI is enabled, before starting a new sequence. To prevent having unread data, ensure that RXFIFO is empty when disabling the SPI, by using the correct disabling procedure, or by initializing all the SPI registers with a software reset via the control of a specific register dedicated to peripheral reset (see the SPIIRST bits in the RCC_APBIRSTR registers).

Standard disable procedure is based on pulling BSY status together with FTLVL[1:0] to check if a transmission session is fully completed. This check can be done in specific cases, too, when it is necessary to identify the end of ongoing transactions, for example:

- • When NSS signal is managed by software and master has to provide proper end of NSS pulse for slave, or

- • When transactions' streams from DMA or FIFO are completed while the last data frame or CRC frame transaction is still ongoing in the peripheral bus.

The correct disable procedure is (except when receive only mode is used):

- 1. Wait until FTLVL[1:0] = 00 (no more data to transmit).

- 2. Wait until BSY=0 (the last data frame is processed).

- 3. Disable the SPI (SPE=0).

- 4. Read data until FRLVL[1:0] = 00 (read all the received data).

The correct disable procedure for certain receive only modes is:

- 1. Interrupt the receive flow by disabling SPI (SPE=0) in the specific time window while the last data frame is ongoing.

- 2. Wait until BSY=0 (the last data frame is processed).

- 3. Read data until FRLVL[1:0] = 00 (read all the received data).

Note: If packing mode is used and an odd number of data frames with a format less than or equal to 8 bits (fitting into one byte) has to be received, FRXTH must be set when FRLVL[1:0] = 01, in order to generate the RXNE event to read the last odd data frame and to keep good FIFO pointer alignment.

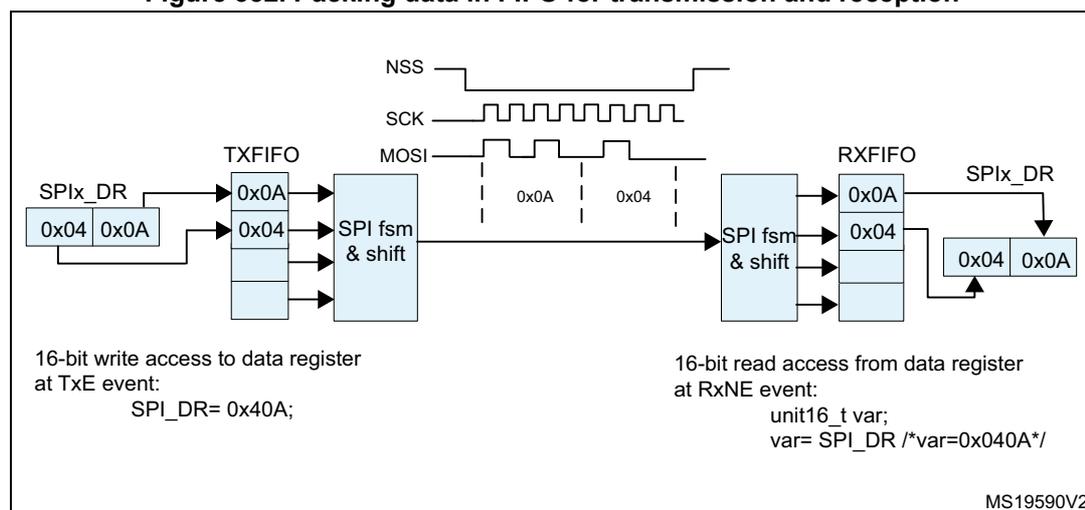

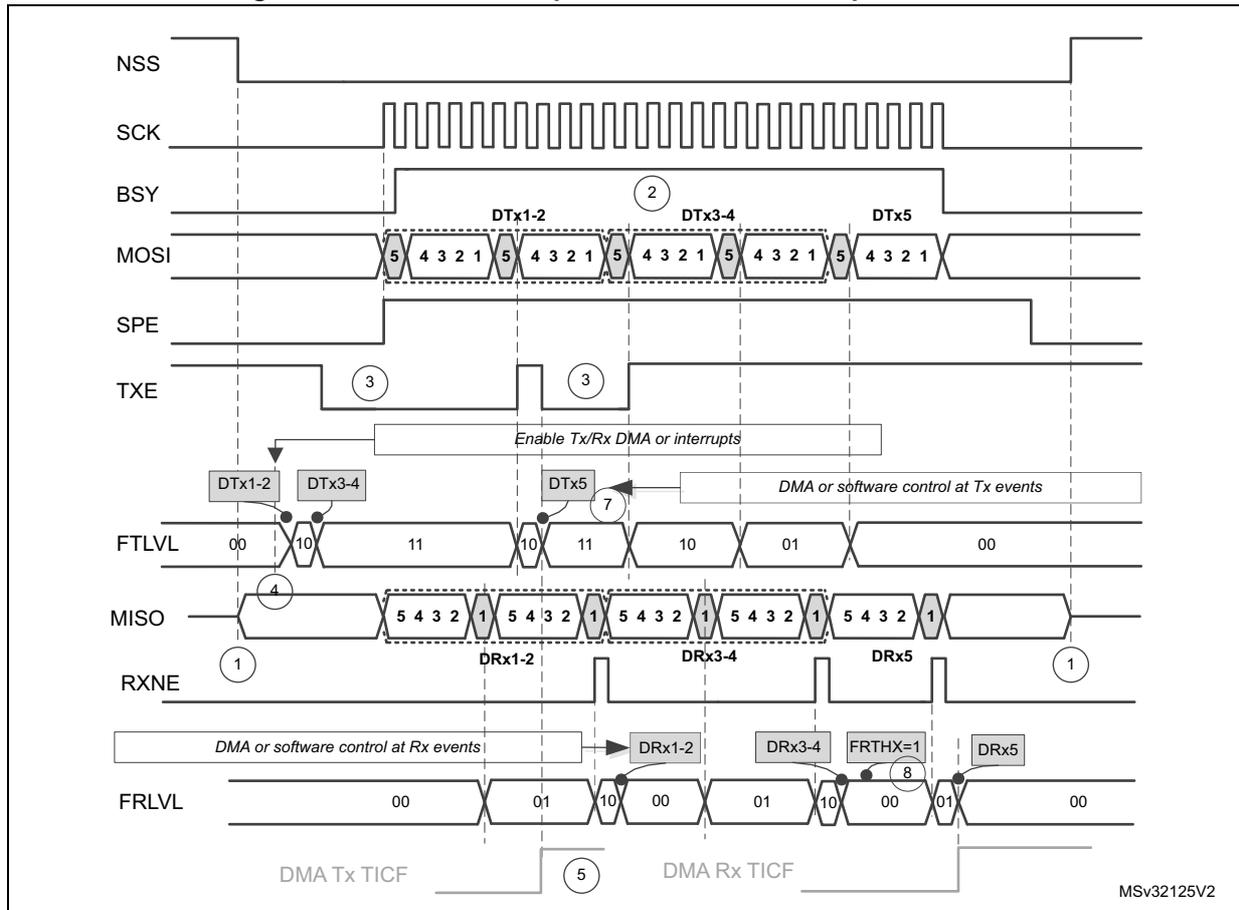

Data packing

When the data frame size fits into one byte (less than or equal to 8 bits), data packing is used automatically when any read or write 16-bit access is performed on the SPIx_DR register. The double data frame pattern is handled in parallel in this case. At first, the SPI operates using the pattern stored in the LSB of the accessed word, then with the other half stored in the MSB. Figure 352 provides an example of data packing mode sequence handling. Two data frames are sent after the single 16-bit access the SPIx_DR register of the transmitter. This sequence can generate just one RXNE event in the receiver if the RXFIFO threshold is set to 16 bits (FRXTH=0). The receiver then has to access both data frames by a single 16-bit read of SPIx_DR as a response to this single RXNE event. The

RxFIFO threshold setting and the following read access must be always kept aligned at the receiver side, as data can be lost if it is not in line.

A specific problem appears if an odd number of such “fit into one byte” data frames must be handled. On the transmitter side, writing the last data frame of any odd sequence with an 8-bit access to SPIx_DR is enough. The receiver has to change the Rx_FIFO threshold level for the last data frame received in the odd sequence of frames in order to generate the RXNE event.

Figure 352. Packing data in FIFO for transmission and reception

- 1. In this example: Data size DS[3:0] is 4-bit configured, CPOL=0, CPHA=1 and LSBFIRST =0. The Data storage is always right aligned while the valid bits are performed on the bus only, the content of LSB byte goes first on the bus, the unused bits are not taken into account on the transmitter side and padded by zeros at the receiver side.

Communication using DMA (direct memory addressing)

To operate at its maximum speed and to facilitate the data register read/write process required to avoid overrun, the SPI features a DMA capability, which implements a simple request/acknowledge protocol.

A DMA access is requested when the TXDMAEN or RXDMAEN enable bit in the SPIx_CR2 register is set. Separate requests must be issued to the Tx and Rx buffers.

- • In transmission, a DMA request is issued each time TXE is set to 1. The DMA then writes to the SPIx_DR register.

- • In reception, a DMA request is issued each time RXNE is set to 1. The DMA then reads the SPIx_DR register.

See Figure 353 through Figure 356 .

When the SPI is used only to transmit data, it is possible to enable only the SPI Tx DMA channel. In this case, the OVR flag is set because the data received is not read. When the SPI is used only to receive data, it is possible to enable only the SPI Rx DMA channel.

In transmission mode, when the DMA has written all the data to be transmitted (the TCIF flag is set in the DMA_ISR register), the BSY flag can be monitored to ensure that the SPI communication is complete. This is required to avoid corrupting the last transmission before disabling the SPI or entering the Stop mode. The software must first wait until FTLVL[1:0]=00 and then until BSY=0.

When starting communication using DMA, to prevent DMA channel management raising error events, these steps must be followed in order:

- 1. Enable DMA Rx buffer in the RXDMAEN bit in the SPI_CR2 register, if DMA Rx is used.

- 2. Enable DMA streams for Tx and Rx in DMA registers, if the streams are used.

- 3. Enable DMA Tx buffer in the TXDMAEN bit in the SPI_CR2 register, if DMA Tx is used.

- 4. Enable the SPI by setting the SPE bit.

To close communication it is mandatory to follow these steps in order:

- 1. Disable DMA streams for Tx and Rx in the DMA registers, if the streams are used.

- 2. Disable the SPI by following the SPI disable procedure.

- 3. Disable DMA Tx and Rx buffers by clearing the TXDMAEN and RXDMAEN bits in the SPI_CR2 register, if DMA Tx and/or DMA Rx are used.

Packing with DMA

If the transfers are managed by DMA (TXDMAEN and RXDMAEN set in the SPIx_CR2 register) packing mode is enabled/disabled automatically depending on the PSIZE value configured for SPI TX and the SPI RX DMA channel. If the DMA channel PSIZE value is equal to 16-bit and SPI data size is less than or equal to 8-bit, then packing mode is enabled. The DMA then automatically manages the write operations to the SPIx_DR register.

If data packing mode is used and the number of data to transfer is not a multiple of two, the LDMA_TX/LDMA_RX bits must be set. The SPI then considers only one data for the transmission or reception to serve the last DMA transfer (for more details refer to Data packing on page 965 .)

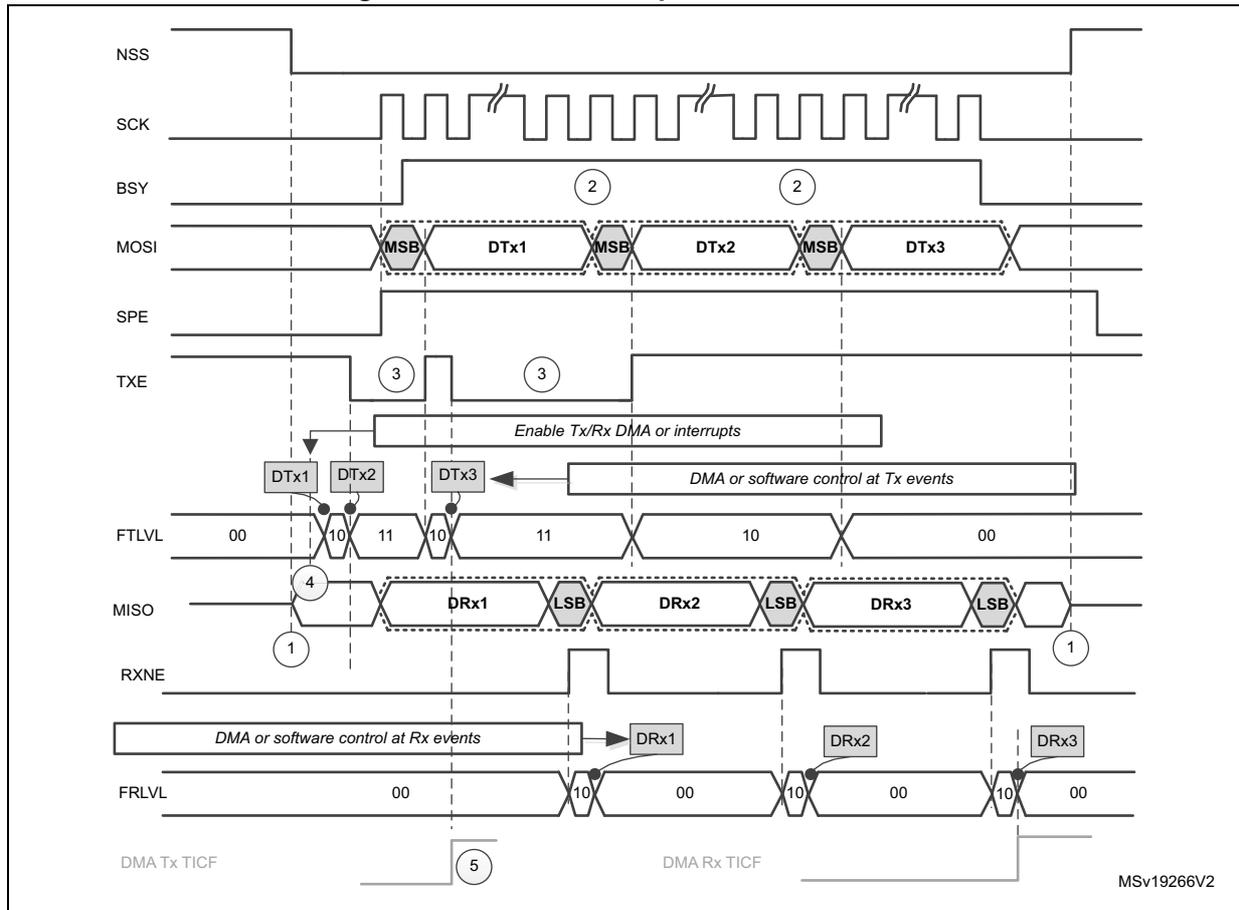

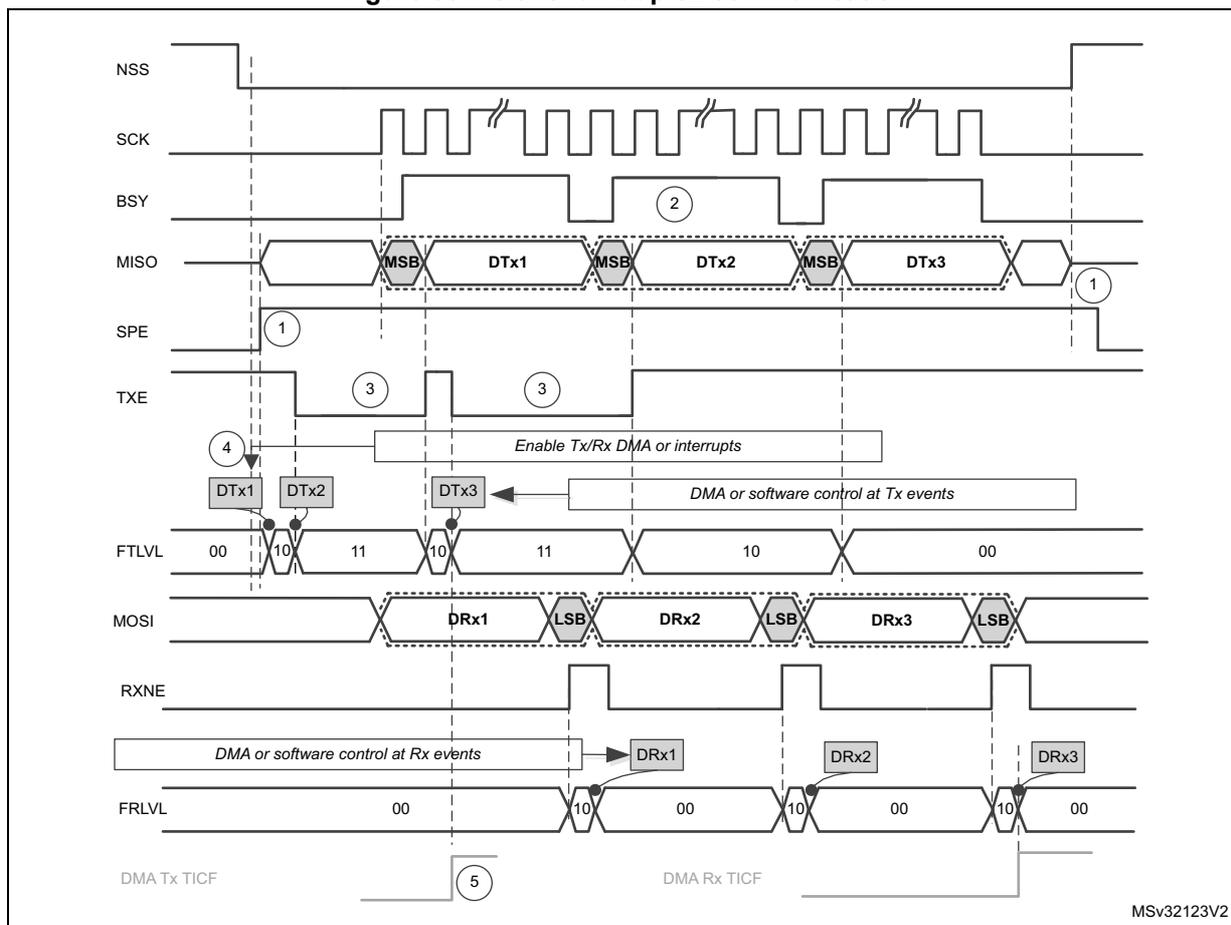

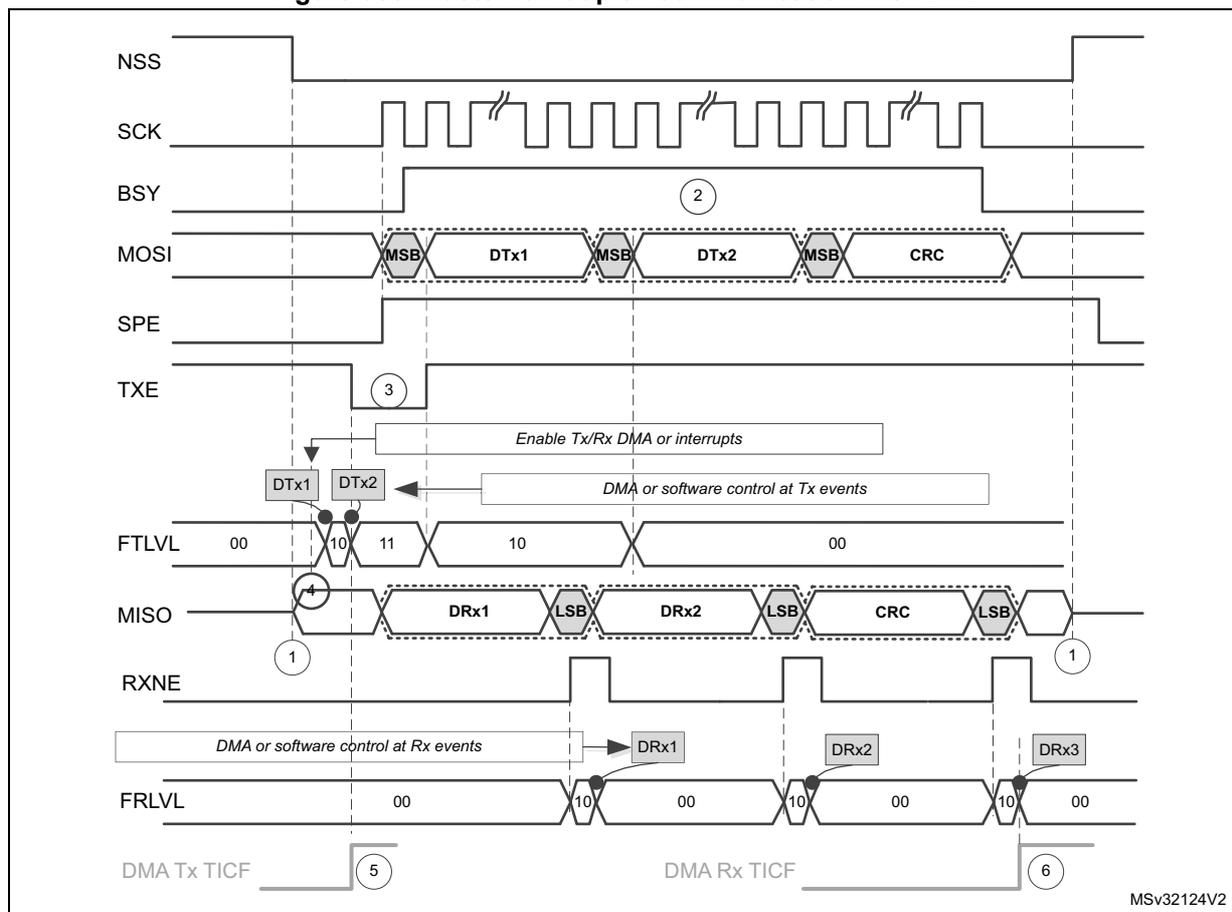

Communication diagrams

Some typical timing schemes are explained in this section. These schemes are valid no matter if the SPI events are handled by polling, interrupts or DMA. For simplicity, the LSBFIRST=0, CPOL=0 and CPHA=1 setting is used as a common assumption here. No complete configuration of DMA streams is provided.

The following numbered notes are common for Figure 353 on page 969 through Figure 356 on page 972 :

- 1. The slave starts to control MISO line as NSS is active and SPI is enabled, and is disconnected from the line when one of them is released. Sufficient time must be provided for the slave to prepare data dedicated to the master in advance before its transaction starts.

At the master, the SPI peripheral takes control at MOSI and SCK signals (occasionally at NSS signal as well) only if SPI is enabled. If SPI is disabled the SPI peripheral is disconnected from GPIO logic, so the levels at these lines depends on GPIO setting exclusively. - 2. At the master, BSY stays active between frames if the communication (clock signal) is continuous. At the slave, BSY signal always goes down for at least one clock cycle between data frames.

- 3. The TXE signal is cleared only if TXFIFO is full.

- 4. The DMA arbitration process starts just after the TXDMAEN bit is set. The TXE interrupt is generated just after the TXEIE is set. As the TXE signal is at an active level, data transfers to TxFIFO start, until TxFIFO becomes full or the DMA transfer completes.

- 5. If all the data to be sent can fit into TxFIFO, the DMA Tx TCIF flag can be raised even before communication on the SPI bus starts. This flag always rises before the SPI transaction is completed.

- 6. The CRC value for a package is calculated continuously frame by frame in the SPIx_TXCRCR and SPIx_RXCRCR registers. The CRC information is processed after the entire data package has completed, either automatically by DMA (Tx channel must be set to the number of data frames to be processed) or by SW (the user must handle CRCNEXT bit during the last data frame processing).

While the CRC value calculated in SPIx_TXCRCR is simply sent out by transmitter, received CRC information is loaded into RxFIFO and then compared with the SPIx_RXCRCR register content (CRC error flag can be raised here if any difference). This is why the user must take care to flush this information from the FIFO, either by software reading out all the stored content of RxFIFO, or by DMA when the proper number of data frames is preset for Rx channel (number of data frames + number of CRC frames) (see the settings at the example assumption). - 7. In data packed mode, TxE and RxNE events are paired and each read/write access to the FIFO is 16 bits wide until the number of data frames are even. If the TxFIFO is \( \frac{3}{4} \) full FTLVL status stays at FIFO full level. That is why the last odd data frame cannot be stored before the TxFIFO becomes \( \frac{1}{2} \) full. This frame is stored into TxFIFO with an 8-bit access either by software or automatically by DMA when LDMA_TX control is set.

- 8. To receive the last odd data frame in packed mode, the Rx threshold must be changed to 8-bit when the last data frame is processed, either by software setting FRXTH=1 or automatically by a DMA internal signal when LDMA_RX is set.

Figure 353. Master full-duplex communication

The diagram illustrates the timing for master full-duplex communication across three data frames. The signals shown are:

- NSS (Slave Select): Active low signal, held high throughout the communication.

- SCK (Serial Clock): Generated by the master, shown as a continuous square wave.

- BSY (Busy): Goes high when the first frame starts and returns low when the last frame ends. It is labeled with '2' during the active period.

- MOSI (Master Out Slave In): Transmits data from master to slave. It shows three frames: DTx1, DTx2, and DTx3. Each frame starts with MSB (Most Significant Bit) and ends with LSB (Least Significant Bit).

- SPE (Serial Peripheral Enable): Active low signal, held high.

- TXE (Transmit Buffer Empty): Goes high when the transmit buffer is empty, allowing new data to be written. It is labeled with '3' during the active period.

- FTLVL (Fill Threshold Level): Shows the level of data in the transmit buffer. It starts at 00, goes to 10 when DTx1 is written, 11 when DTx2 is written, 10 when DTx3 is written, and returns to 00 after the third clock edge.

- MISO (Master In Slave Out): Receives data from slave to master. It shows three frames: DRx1, DRx2, and DRx3. Each frame starts with MSB and ends with LSB.

- RXNE (Receive Buffer Not Empty): Goes high when new data is received. It is labeled with '1' at the start and end of the sequence.

- FRLVL (Fill Level): Shows the level of data in the receive buffer. It starts at 00, goes to 10 when DRx1 is received, 00 when DRx2 is received, 10 when DRx3 is received, and returns to 00 after the third clock edge.

- DMA Tx TICF (Transmit Interrupt Call Flag): Generated when the transmit buffer is empty. It is labeled with '5' at the start.

- DMA Rx TICF (Receive Interrupt Call Flag): Generated when new data is received.

Control signals and events:

- Enable Tx/Rx DMA or interrupts: A signal that enables DMA or interrupts for both transmission and reception.

- DMA or software control at Tx events: Control signal for transmission events, triggered when the transmit buffer is empty.

- DMA or software control at Rx events: Control signal for reception events, triggered when new data is received.

Numbered circles indicate key events:

- 1: RXNE goes high at the start and end of the sequence.

- 2: BSY goes high at the start and low at the end of the sequence.

- 3: TXE goes high when the transmit buffer is empty.

- 4: FTLVL goes high when the first data byte (DTx1) is written.

- 5: DMA Tx TICF goes high when the transmit buffer is empty.

MSv19266V2

Assumptions for master full-duplex communication example:

- • Data size > 8 bit

If DMA is used:

- • Number of Tx frames transacted by DMA is set to 3

- • Number of Rx frames transacted by DMA is set to 3

See also : Communication diagrams on page 968 for details about common assumptions and notes.

Figure 354. Slave full-duplex communication

The diagram illustrates the timing for slave full-duplex communication. The signals shown are:

- NSS : Slave Select, active low.

- SCK : Serial Clock.

- BSY : Busy signal, goes high when communication starts and low when it ends.

- MISO : Master In Slave Out data lines, showing transmitted data DTx1, DTx2, and DTx3 with MSB (Most Significant Bit) and LSB (Least Significant Bit) markers.

- SPE : SPI Enable, goes high to enable the SPI and low to disable it.

- TXE : Transmit Buffer Empty flag, pulses high when the data register is empty and ready for new data.

- FTLVL : FIFO Level, shows levels 00, 10, 11, 10, 11, 10, 00.

- MOSI : Master Out Slave In data lines, showing received data DRx1, DRx2, and DRx3 with MSB and LSB markers.

- RXNE : Receive Buffer Not Empty flag, goes high when data is received and low when the buffer is empty.

- FRLVL : FIFO Level, shows levels 00, 10, 00, 10, 00, 10, 00.

- SPE goes high and NSS goes low to start communication.

- BSY goes high.

- TXE goes high, indicating the buffer is empty. Data DTx1, DTx2, and DTx3 are loaded into the buffer (event 4).

- Data is transmitted and received simultaneously. RXNE goes high when data is received (event 5).

- Communication ends when NSS goes high and SPE goes low. BSY goes low.

MSv32123V2

Assumptions for slave full-duplex communication example:

- • Data size > 8 bit

If DMA is used:

- • Number of Tx frames transacted by DMA is set to 3

- • Number of Rx frames transacted by DMA is set to 3

See also Communication diagrams on page 968 for details about common assumptions and notes.

Figure 355. Master full-duplex communication with CRC

The diagram illustrates the timing for master full-duplex communication with CRC. The signals shown are:

- NSS : Slave Select, active low.

- SCK : Serial Clock.

- BSY : Busy flag, goes high when the SPI is active.

- MOSI : Master Out Slave In. Shows two transmitted frames, DTx1 and DTx2, each with MSB (Most Significant Bit) and CRC fields.

- SPE : SPI Enable.

- TXE : Transmit Buffer Empty flag. Goes high when the buffer is empty and low when it contains data.

- FTLVL : FIFO Level. Shows levels 00, 10, 11, 10, 00, indicating the number of data frames in the transmit buffer.

- MISO : Master In Slave Out. Shows three received frames, DRx1, DRx2, and DRx3, each with MSB, LSB (Least Significant Bit), and CRC fields.

- RXNE : Receive Buffer Not Empty flag. Goes high when the buffer is not empty and low when it is empty.

- FRLVL : FIFO Level. Shows levels 00, 10, 00, 10, 00, indicating the number of data frames in the receive buffer.

- DMA Tx TICF : DMA Transmit Transfer Interrupt Flag. Goes high when the last data frame is transmitted (point 5).

- DMA Rx TICF : DMA Receive Transfer Interrupt Flag. Goes high when the last data frame is received (point 6).

Annotations in the diagram:

- (1) RXNE flag transitions.

- (2) BSY flag duration.

- (3) TXE flag transition at the start of transmission.

- (4) First bit of the first received frame (DRx1).

- (5) DMA Tx TICF flag transition.

- (6) DMA Rx TICF flag transition.

- Enable Tx/Rx DMA or interrupts: A block indicating when DMA or interrupts are enabled.

- DMA or software control at Tx events: Arrows pointing to DTx1 and DTx2 in the FTLVL register.

- DMA or software control at Rx events: Arrows pointing to DRx1, DRx2, and DRx3 in the FRLVL register.

MSv32124V2

Assumptions for master full-duplex communication with CRC example:

- • Data size = 16 bit

- • CRC enabled

If DMA is used:

- • Number of Tx frames transacted by DMA is set to 2

- • Number of Rx frames transacted by DMA is set to 3

See also : Communication diagrams on page 968 for details about common assumptions and notes.

Figure 356. Master full-duplex communication in packed mode

Assumptions for master full-duplex communication in packed mode example:

- • Data size = 5 bit

- • Read/write FIFO is performed mostly by 16-bit access

- • FRXTH=0

If DMA is used:

- • Number of Tx frames to be transacted by DMA is set to 3

- • Number of Rx frames to be transacted by DMA is set to 3

- • PSIZE for both Tx and Rx DMA channel is set to 16-bit

- • LDMA_TX=1 and LDMA_RX=1

See also : Communication diagrams on page 968 for details about common assumptions and notes.

28.5.10 SPI status flags

Three status flags are provided for the application to completely monitor the state of the SPI bus.

Tx buffer empty flag (TXE)

The TXE flag is set when transmission TXFIFO has enough space to store data to send. TXE flag is linked to the TXFIFO level. The flag goes high and stays high until the TXFIFO level is lower or equal to 1/2 of the FIFO depth. An interrupt can be generated if the TXEIE bit in the SPIx_CR2 register is set. The bit is cleared automatically when the TXFIFO level becomes greater than 1/2.

Rx buffer not empty (RXNE)

The RXNE flag is set depending on the FRXTH bit value in the SPIx_CR2 register:

- • If FRXTH is set, RXNE goes high and stays high until the RXFIFO level is greater or equal to 1/4 (8-bit).

- • If FRXTH is cleared, RXNE goes high and stays high until the RXFIFO level is greater than or equal to 1/2 (16-bit).

An interrupt can be generated if the RXNEIE bit in the SPIx_CR2 register is set.

The RXNE is cleared by hardware automatically when the above conditions are no longer true.

Busy flag (BSY)

The BSY flag is set and cleared by hardware (writing to this flag has no effect).

When BSY is set, it indicates that a data transfer is in progress on the SPI (the SPI bus is busy).

The BSY flag can be used in certain modes to detect the end of a transfer so that the software can disable the SPI or its peripheral clock before entering a low-power mode which does not provide a clock for the peripheral. This avoids corrupting the last transfer.

The BSY flag is also useful for preventing write collisions in a multimaster system.

The BSY flag is cleared under any one of the following conditions:

- • When the SPI is correctly disabled

- • When a fault is detected in Master mode (MODF bit set to 1)

- • In Master mode, when it finishes a data transmission and no new data is ready to be sent

- • In Slave mode, when the BSY flag is set to '0' for at least one SPI clock cycle between each data transfer.

Note: When the next transmission can be handled immediately by the master (e.g. if the master is in Receive-only mode or its Transmit FIFO is not empty), communication is continuous and the BSY flag remains set to '1' between transfers on the master side. Although this is not the case with a slave, it is recommended to use always the TXE and RXNE flags (instead of the BSY flags) to handle data transmission or reception operations.

28.5.11 SPI error flags

An SPI interrupt is generated if one of the following error flags is set and interrupt is enabled by setting the ERRIE bit.

Overrun flag (OVR)

An overrun condition occurs when data is received by a master or slave and the RXFIFO has not enough space to store this received data. This can happen if the software or the DMA did not have enough time to read the previously received data (stored in the RXFIFO) or when space for data storage is limited e.g. the RXFIFO is not available when CRC is enabled in receive only mode so in this case the reception buffer is limited into a single data frame buffer (see Section 28.5.14: CRC calculation ).

When an overrun condition occurs, the newly received value does not overwrite the previous one in the RXFIFO. The newly received value is discarded and all data transmitted subsequently is lost. Clearing the OVR bit is done by a read access to the SPI_DR register followed by a read access to the SPI_SR register.

Mode fault (MODF)

Mode fault occurs when the master device has its internal NSS signal (NSS pin in NSS hardware mode, or SSI bit in NSS software mode) pulled low. This automatically sets the MODF bit. Master mode fault affects the SPI interface in the following ways:

- • The MODF bit is set and an SPI interrupt is generated if the ERRIE bit is set.

- • The SPE bit is cleared. This blocks all output from the device and disables the SPI interface.

- • The MSTR bit is cleared, thus forcing the device into slave mode.

Use the following software sequence to clear the MODF bit:

- 1. Make a read or write access to the SPIx_SR register while the MODF bit is set.

- 2. Then write to the SPIx_CR1 register.

To avoid any multiple slave conflicts in a system comprising several MCUs, the NSS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits can be restored to their original state after this clearing sequence. As a security, hardware does not allow the SPE and MSTR bits to be set while the MODF bit is set. In a slave device the MODF bit cannot be set except as the result of a previous multimaster conflict.

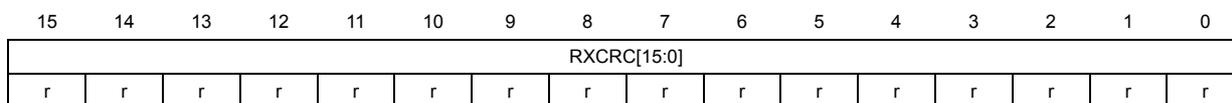

CRC error (CRCERR)

This flag is used to verify the validity of the value received when the CRCEN bit in the SPIx_CR1 register is set. The CRCERR flag in the SPIx_SR register is set if the value received in the shift register does not match the receiver SPIx_RXCRCR value. The flag is cleared by the software.

TI mode frame format error (FRE)

A TI mode frame format error is detected when an NSS pulse occurs during an ongoing communication when the SPI is operating in slave mode and configured to conform to the TI mode protocol. When this error occurs, the FRE flag is set in the SPIx_SR register. The SPI is not disabled when an error occurs, the NSS pulse is ignored, and the SPI waits for the next NSS pulse before starting a new transfer. The data may be corrupted since the error detection may result in the loss of two data bytes.

The FRE flag is cleared when SPIx_SR register is read. If the ERRRIE bit is set, an interrupt is generated on the NSS error detection. In this case, the SPI should be disabled because data consistency is no longer guaranteed and communications should be reinitiated by the master when the slave SPI is enabled again.

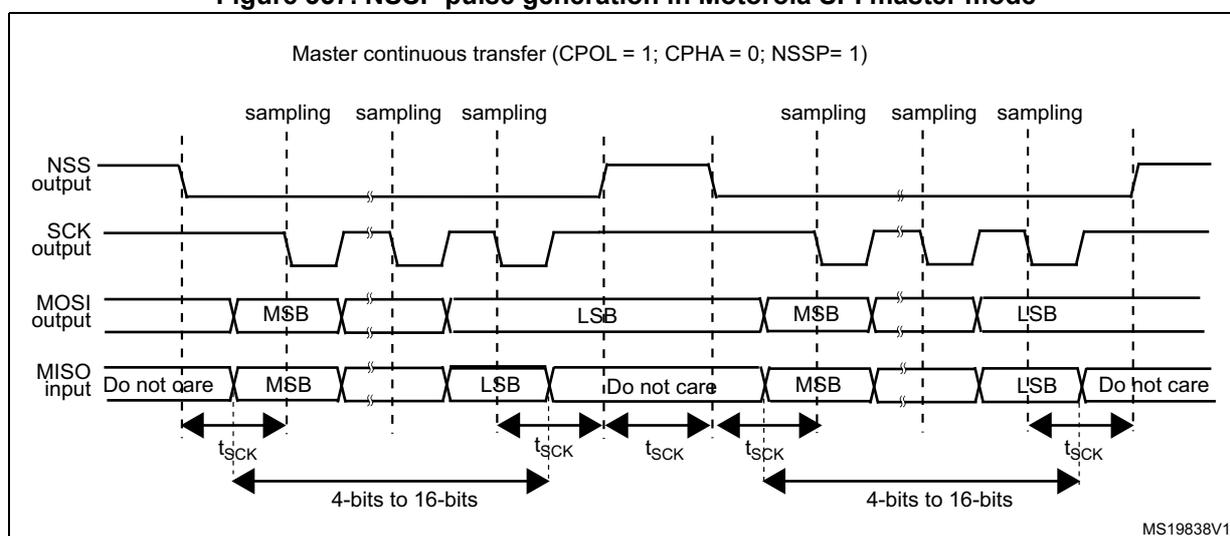

28.5.12 NSS pulse mode

This mode is activated by the NSSP bit in the SPIx_CR2 register and it takes effect only if the SPI interface is configured as Motorola SPI master (FRF=0) with capture on the first edge (SPIx_CR1 CPHA = 0, CPOL setting is ignored). When activated, an NSS pulse is generated between two consecutive data frame transfers when NSS stays at high level for the duration of one clock period at least. This mode allows the slave to latch data. NSSP pulse mode is designed for applications with a single master-slave pair.

Figure 357 illustrates NSS pin management when NSSP pulse mode is enabled.

Figure 357. NSSP pulse generation in Motorola SPI master mode

Master continuous transfer (CPOL = 1; CPHA = 0; NSSP= 1)

The diagram illustrates the timing for a master continuous transfer in Motorola SPI mode with NSSP enabled. The NSS output is high before the first SCK edge and goes low when the first data frame starts, returning high after the last data frame. The SCK output is a continuous square wave. The MOSI output shows data frames (MSB and LSB) being transmitted. The MISO input shows 'Do not care' periods at the beginning and end of each data frame, with data being received during the MSB and LSB periods. Sampling edges are marked on the SCK waveform. Timing parameters \( t_{sck} \) and frame lengths (4-bits to 16-bits) are indicated.

MS19838V1

Note: Similar behavior is encountered when CPOL = 0. In this case the sampling edge is the rising edge of SCK, and NSS assertion and deassertion refer to this sampling edge.

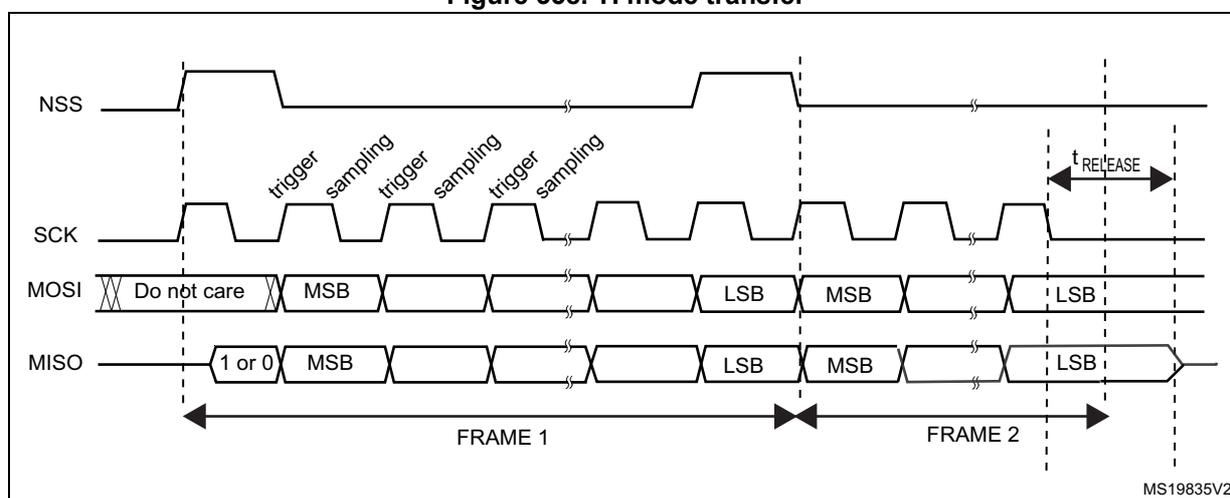

28.5.13 TI mode

TI protocol in master mode

The SPI interface is compatible with the TI protocol. The FRF bit of the SPIx_CR2 register can be used to configure the SPI to be compliant with this protocol.

The clock polarity and phase are forced to conform to the TI protocol requirements whatever the values set in the SPIx_CR1 register. NSS management is also specific to the TI protocol which makes the configuration of NSS management through the SPIx_CR1 and SPIx_CR2 registers (SSM, SSI, SSOE) impossible in this case.

In slave mode, the SPI baud rate prescaler is used to control the moment when the MISO pin state changes to HiZ when the current transaction finishes (see Figure 358). Any baud rate can be used, making it possible to determine this moment with optimal flexibility. However, the baud rate is generally set to the external master clock baud rate. The delay for the MISO signal to become HiZ ( \( t_{release} \) ) depends on internal resynchronization and on the

baud rate value set in through the BR[2:0] bits in the SPIx_CR1 register. It is given by the formula:

If the slave detects a misplaced NSS pulse during a data frame transaction the TIFRE flag is set.

If the data size is equal to 4-bits or 5-bits, the master in full-duplex mode or transmit-only mode uses a protocol with one more dummy data bit added after LSB. TI NSS pulse is generated above this dummy bit clock cycle instead of the LSB in each period.

This feature is not available for Motorola SPI communications (FRF bit set to 0).

Figure 358: TI mode transfer shows the SPI communication waveforms when TI mode is selected.

Figure 358. TI mode transfer

The diagram shows the timing for TI mode transfer. The top signal is NSS (Slave Select), which goes low to initiate a transfer and high to release it. Below it is SCK (Serial Clock), a square wave. The third signal is MOSI (Master Out Slave In), showing data bits being sent. The bottom signal is MISO (Master In Slave Out), showing data bits being received. The diagram is divided into two frames, FRAME 1 and FRAME 2. Each frame consists of multiple bits. Labels 'trigger' and 'sampling' are placed above the SCK signal to indicate the clock edges used for data transfer. The MOSI signal shows 'Do not care' for the first bit, followed by MSB (Most Significant Bit) and LSB (Least Significant Bit) for subsequent bits. The MISO signal shows '1 or 0' for the first bit, followed by MSB and LSB. A time interval 't_RELEASE' is indicated between the end of FRAME 2 and the start of the next frame. The diagram is labeled MS19835V2 in the bottom right corner.

28.5.14 CRC calculation

Two separate CRC calculators are implemented in order to check the reliability of transmitted and received data. The SPI offers CRC8 or CRC16 calculation independently of the frame data length, which can be fixed to 8-bit or 16-bit. For all the other data frame lengths, no CRC is available.

CRC principle

CRC calculation is enabled by setting the CRCEN bit in the SPIx_CR1 register before the SPI is enabled (SPE = 1). The CRC value is calculated using an odd programmable polynomial on each bit. The calculation is processed on the sampling clock edge defined by the CPHA and CPOL bits in the SPIx_CR1 register. The calculated CRC value is checked automatically at the end of the data block as well as for transfer managed by CPU or by the DMA. When a mismatch is detected between the CRC calculated internally on the received data and the CRC sent by the transmitter, a CRCERR flag is set to indicate a data corruption error. The right procedure for handling the CRC calculation depends on the SPI configuration and the chosen transfer management.

Note: The polynomial value should only be odd. No even values are supported.

CRC transfer managed by CPU

Communication starts and continues normally until the last data frame has to be sent or received in the SPIx_DR register. Then CRCNEXT bit has to be set in the SPIx_CR1 register to indicate that the CRC frame transaction follows after the transaction of the currently processed data frame. The CRCNEXT bit must be set before the end of the last data frame transaction. CRC calculation is frozen during CRC transaction.

The received CRC is stored in the RXFIFO like a data byte or word. That is why in CRC mode only, the reception buffer has to be considered as a single 16-bit buffer used to receive only one data frame at a time.

A CRC-format transaction usually takes one more data frame to communicate at the end of data sequence. However, when setting an 8-bit data frame checked by 16-bit CRC, two more frames are necessary to send the complete CRC.

When the last CRC data is received, an automatic check is performed comparing the received value and the value in the SPIx_RXCRC register. Software has to check the CRCERR flag in the SPIx_SR register to determine if the data transfers were corrupted or not. Software clears the CRCERR flag by writing '0' to it.

After the CRC reception, the CRC value is stored in the RXFIFO and must be read in the SPIx_DR register in order to clear the RXNE flag.

CRC transfer managed by DMA

When SPI communication is enabled with CRC communication and DMA mode, the transmission and reception of the CRC at the end of communication is automatic (with the exception of reading CRC data in receive only mode). The CRCNEXT bit does not have to be handled by the software. The counter for the SPI transmission DMA channel has to be set to the number of data frames to transmit excluding the CRC frame. On the receiver side, the received CRC value is handled automatically by DMA at the end of the transaction but user must take care to flush out received CRC information from RXFIFO as it is always loaded into it. In full-duplex mode, the counter of the reception DMA channel can be set to the number of data frames to receive including the CRC, which means, for example, in the specific case of an 8-bit data frame checked by 16-bit CRC:

In receive only mode, the DMA reception channel counter should contain only the amount of data transferred, excluding the CRC calculation. Then based on the complete transfer from DMA, all the CRC values must be read back by software from FIFO as it works as a single buffer in this mode.

At the end of the data and CRC transfers, the CRCERR flag in the SPIx_SR register is set if corruption occurred during the transfer.

If packing mode is used, the LDMA_RX bit needs managing if the number of data is odd.

Resetting the SPIx_TXCRC and SPIx_RXCRC values

The SPIx_TXCRC and SPIx_RXCRC values are cleared automatically when new data is sampled after a CRC phase. This allows the use of DMA circular mode (not available in receive-only mode) in order to transfer data without any interruption, (several data blocks covered by intermediate CRC checking phases).

If the SPI is disabled during a communication the following sequence must be followed:

- 1. Disable the SPI

- 2. Clear the CRCEN bit

- 3. Enable the CRCEN bit

- 4. Enable the SPI

Note: When the SPI interface is configured as a slave, the NSS internal signal needs to be kept low during transaction of the CRC phase once the CRCNEXT signal is released. That is why the CRC calculation cannot be used at NSS Pulse mode when NSS hardware mode should be applied at slave normally.

At TI mode, despite the fact that clock phase and clock polarity setting is fixed and independent on SPIx_CR1 register, the corresponding setting CPOL=0 CPHA=1 has to be kept at the SPIx_CR1 register anyway if CRC is applied. In addition, the CRC calculation has to be reset between sessions by SPI disable sequence with re-enable the CRCEN bit described above at both master and slave side, else CRC calculation can be corrupted at this specific mode.

28.6 SPI interrupts

During SPI communication an interrupt can be generated by the following events:

- • Transmit TXFIFO ready to be loaded

- • Data received in Receive RXFIFO

- • Master mode fault

- • Overrun error

- • TI frame format error

- • CRC protocol error

Interrupts can be enabled and disabled separately.

Table 174. SPI interrupt requests

| Interrupt event | Event flag | Enable Control bit |

|---|---|---|

| Transmit TXFIFO ready to be loaded | TXE | TXEIE |

| Data received in RXFIFO | RXNE | RXNEIE |

| Master Mode fault event | MODF | ERRIE |

| Overrun error | OVR | |

| TI frame format error | FRE | |

| CRC protocol error | CRCERR |

28.7 I2S functional description

28.7.1 I2S general description

The block diagram of the I2S is shown in Figure 359 .

Figure 359. I2S block diagram

![Figure 359. I2S block diagram. This is a detailed functional block diagram of the I2S interface. At the top, an 'Address and data bus' connects to a 'Tx buffer' and a 'Communication control' block. The 'Tx buffer' is a 16-bit buffer connected to a 'Shift register', which is also 16-bit and configured for 'LSB first'. The 'Shift register' connects to an 'Rx buffer', which in turn connects to the 'Address and data bus'. The 'Communication control' block is connected to the 'Tx buffer', 'Shift register', 'Rx buffer', and several configuration registers. On the left, pins are labeled 'MOSI/SD', 'MISO', 'NSS/WS', 'CK', and 'MCK'. 'MOSI/SD' and 'MISO' are connected to a bidirectional switch. 'NSS/WS' is connected to the 'Communication control'. 'CK' is connected to a multiplexer that selects between 'I2S_CK' and 'SPI' output. 'MCK' is connected to the 'I2S clock generator'. The 'Master control logic' block is connected to the 'Communication control' and the 'SPI baud rate generator'. The 'SPI baud rate generator' is connected to a set of registers including 'LSB First', 'SPE', 'BR2', 'BR1', 'BR0', 'MSTR', 'CPOL', and 'CPHA'. Below the baud rate generator is the 'I2S clock generator', which is connected to registers 'MCKOE', 'ODD', and 'I2SDIV[7:0]'. The 'I2S clock generator' outputs 'I2SxCLK' to the 'Communication control'. There are two rows of configuration registers: the top row includes 'I2SCFG [1:0]', 'I2SSTD [1:0]', 'CK POL', 'DATLEN [1:0]', 'CH LEN', 'I2S MOD', and 'I2SE'; the bottom row includes 'BSY', 'OVR', 'MODF', 'CRC ERR', 'UDR', 'CH SIDE', 'TxE', 'RxNE', and 'FRE'. Another set of registers includes 'Bidi mode', 'Bidi OE', 'CRC EN', 'CRC Next', 'DFF', 'Rx only', 'SSM', and 'SSI'.](/RM0431-STM32F72-73/72803bce7664d2c898bcc9d23b15046d_img.jpg)

- 1. MCK is mapped on the MISO pin.

The SPI can function as an audio I2S interface when the I2S capability is enabled (by setting the I2SMOD bit in the SPIx_I2SCFGR register). This interface mainly uses the same pins, flags and interrupts as the SPI.

The I2S shares three common pins with the SPI:

- • SD: Serial Data (mapped on the MOSI pin) to transmit or receive the two time-multiplexed data channels (in half-duplex mode only).

- • WS: Word Select (mapped on the NSS pin) is the data control signal output in master mode and input in slave mode.

- • CK: Serial Clock (mapped on the SCK pin) is the serial clock output in master mode and serial clock input in slave mode.

An additional pin can be used when a master clock output is needed for some external audio devices:

- • MCK: Master Clock (mapped separately) is used, when the I2S is configured in master mode (and when the MCKOE bit in the SPIx_I2SPR register is set), to output this additional clock generated at a preconfigured frequency rate equal to \( 256 \times f_S \) for all I2S modes, and to \( 128 \times f_S \) for all PCM modes, where \( f_S \) is the audio sampling frequency.

The I2S uses its own clock generator to produce the communication clock when it is set in master mode. This clock generator is also the source of the master clock output. Two additional registers are available in I 2 S mode. One is linked to the clock generator configuration SPIx_I2SPR and the other one is a generic I2S configuration register SPIx_I2SCFG (audio standard, slave/master mode, data format, packet frame, clock polarity, etc.).

The SPIx_CR1 register and all CRC registers are not used in the I 2 S mode. Likewise, the SSOE bit in the SPIx_CR2 register and the MODF and CRCERR bits in the SPIx_SR are not used.

The I2S uses the same SPI register for data transfer (SPIx_DR) in 16-bit wide mode.

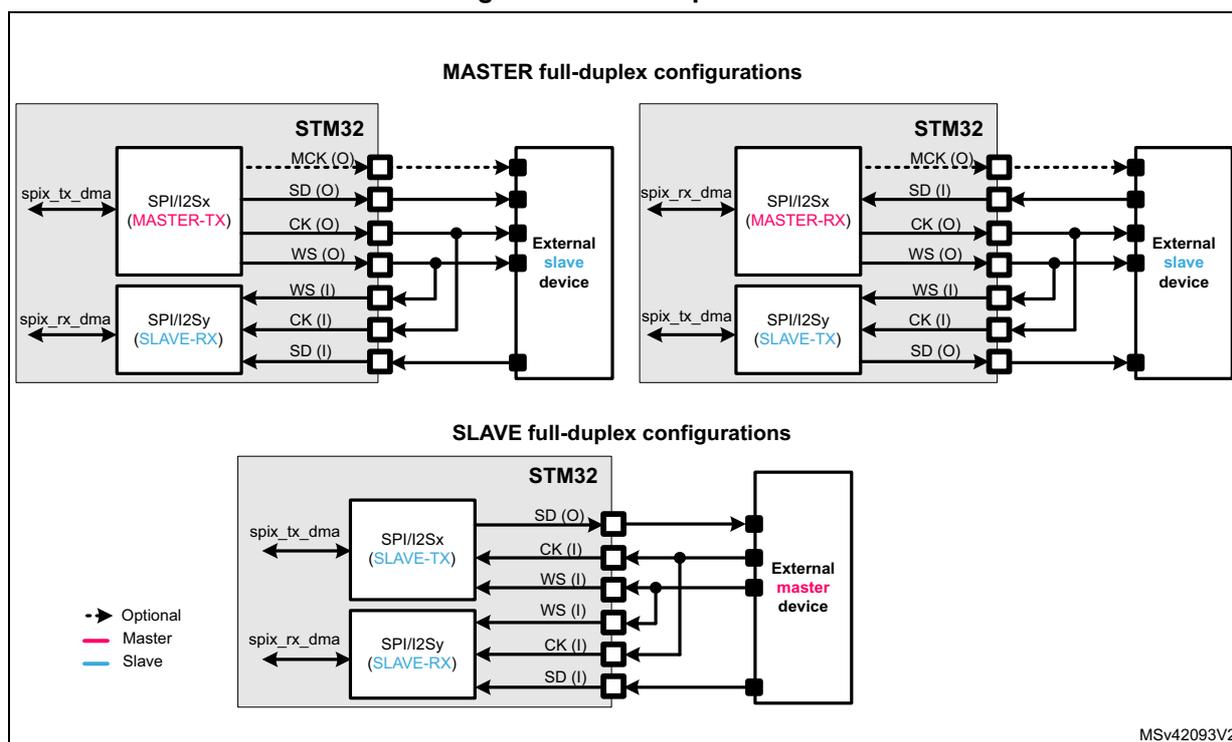

28.7.2 I2S full duplex

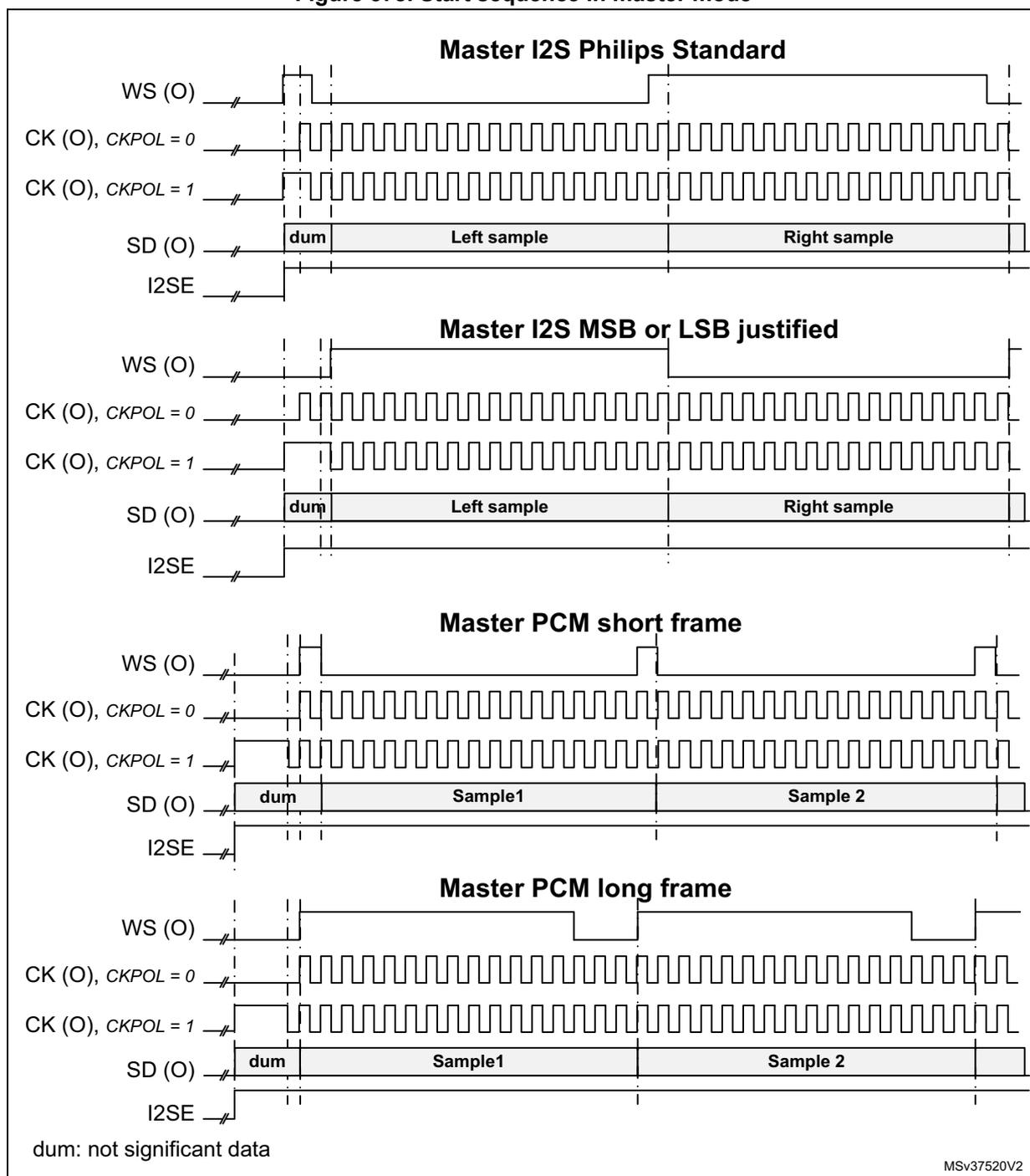

Figure 360 shows how to perform full-duplex communications using two SPI/I2S instances. In this case, the WS and CK IOs of both SPI/I2S must be connected together.

For the master full-duplex mode, one of the SPI/I2S block must be programmed in master (I2SCFG = '10' or '11'), and the other SPI/I2S block must be programmed in slave (I2SCFG = '00' or '01'). The MCK can be generated or not, depending on the application needs.

For the slave full-duplex mode, both SPI/I2S blocks must be programmed in slave. One of them in the slave receiver (I2SCFG = '01'), and the other in the slave transmitter (I2SCFG = '00'). The master external device then provides the bit clock (CK) and the frame synchronization (WS).

Note that the full-duplex mode can be used for all the supported standards: I 2 S Philips, MSB-justified, LSB-justified and PCM.

For the full-duplex mode, both SPI/I2S instances must use the same standard, with the same parameters: I2SMOD, I2SSTD, CKPOL, PCMSYNC, DATLEN and CHLEN must contain the same value on both instances.

Figure 360. Full-duplex communication

28.7.3 Supported audio protocols

The three-line bus has to handle only audio data generally time-multiplexed on two channels: the right channel and the left channel. However there is only one 16-bit register for transmission or reception. So, it is up to the software to write into the data register the appropriate value corresponding to each channel side, or to read the data from the data register and to identify the corresponding channel by checking the CHSIDE bit in the SPIx_SR register. Channel left is always sent first followed by the channel right (CHSIDE has no meaning for the PCM protocol).

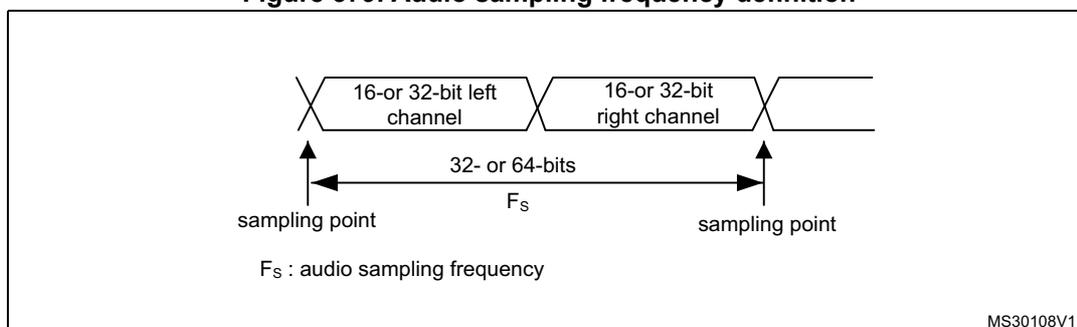

Four data and packet frames are available. Data may be sent with a format of:

- • 16-bit data packed in a 16-bit frame

- • 16-bit data packed in a 32-bit frame

- • 24-bit data packed in a 32-bit frame

- • 32-bit data packed in a 32-bit frame

When using 16-bit data extended on 32-bit packet, the first 16 bits (MSB) are the significant bits, the 16-bit LSB is forced to 0 without any need for software action or DMA request (only one read/write operation).

The 24-bit and 32-bit data frames need two CPU read or write operations to/from the SPIx_DR register or two DMA operations if the DMA is preferred for the application. For 24-bit data frame specifically, the 8 non-significant bits are extended to 32 bits with 0-bits (by hardware).

For all data formats and communication standards, the most significant bit is always sent first (MSB first).

The I 2 S interface supports four audio standards, configurable using the I2SSTD[1:0] and PCMSYNC bits in the SPIx_I2SCFGR register.

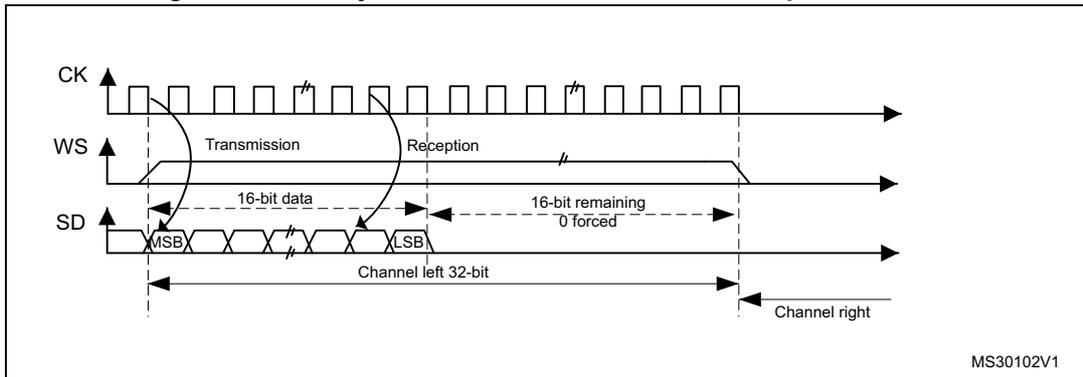

I 2 S Philips standard

For this standard, the WS signal is used to indicate which channel is being transmitted. It is activated one CK clock cycle before the first bit (MSB) is available.

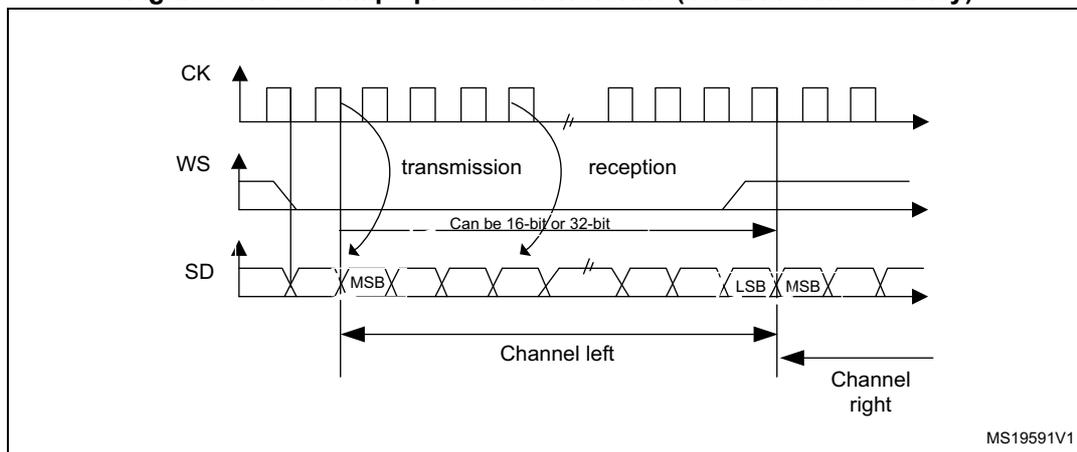

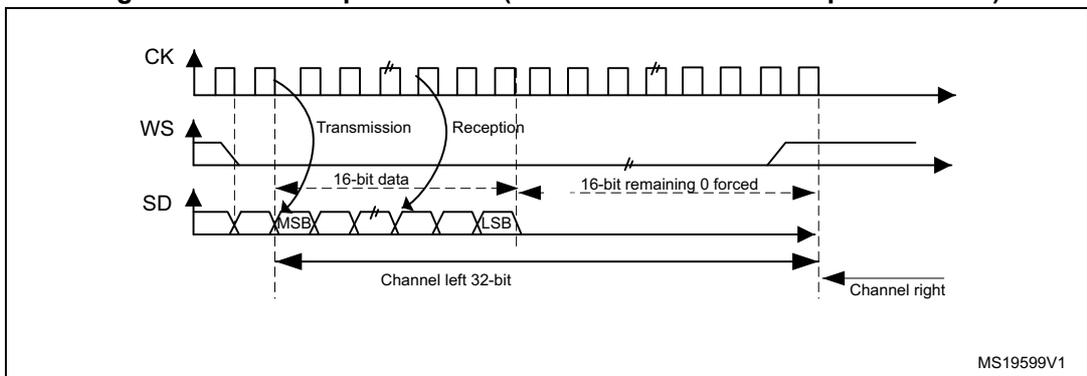

Figure 361. I 2 S Philips protocol waveforms (16/32-bit full accuracy)

Data are latched on the falling edge of CK (for the transmitter) and are read on the rising edge (for the receiver). The WS signal is also latched on the falling edge of CK.

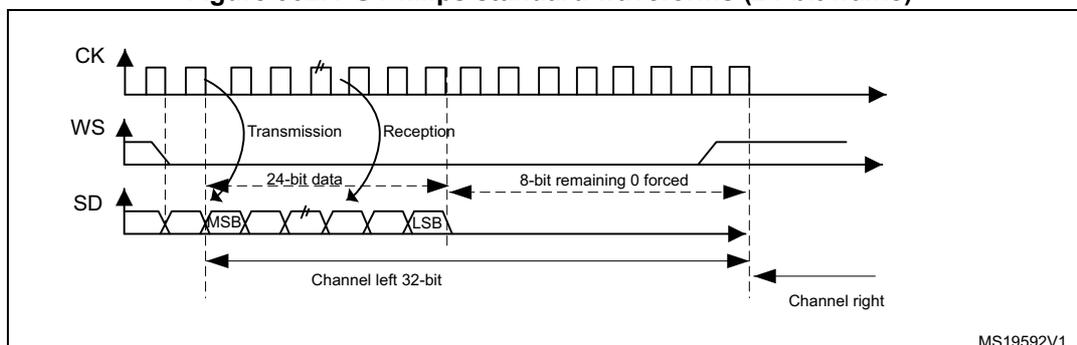

Figure 362. I 2 S Philips standard waveforms (24-bit frame)

This mode needs two write or read operations to/from the SPIx_DR register.

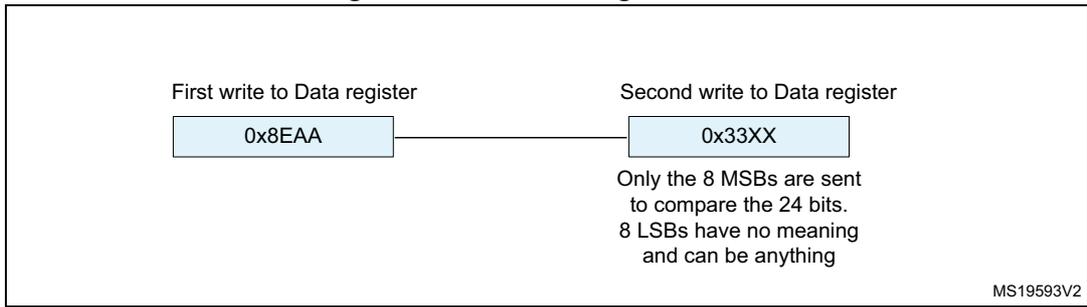

- • In transmission mode:

If 0x8EAA33 has to be sent (24-bit):

Figure 363. Transmitting 0x8EAA33

First write to Data register

0x8EAA

Second write to Data register

0x33XX

Only the 8 MSBs are sent to compare the 24 bits.

8 LSBs have no meaning and can be anything

MS19593V2

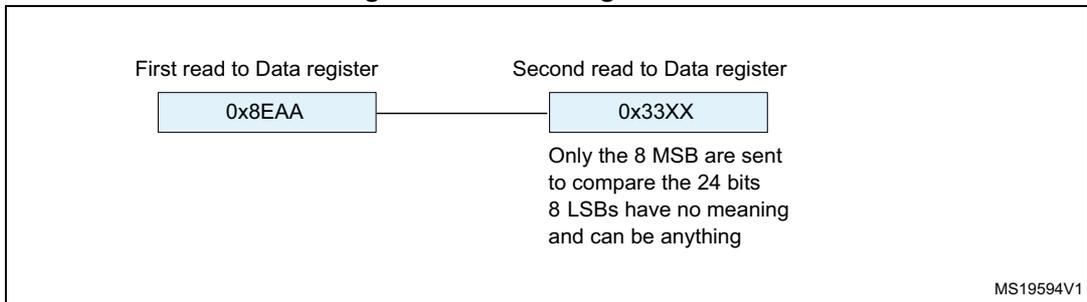

- • In reception mode:

If data 0x8EAA33 is received:

Figure 364. Receiving 0x8EAA33

First read to Data register

0x8EAA

Second read to Data register

0x33XX

Only the 8 MSB are sent to compare the 24 bits

8 LSBs have no meaning and can be anything

MS19594V1

Figure 365. I 2 S Philips standard (16-bit extended to 32-bit packet frame)

CK

WS

SD

Transmission Reception

16-bit data

16-bit remaining 0 forced

MSB

LSB

Channel left 32-bit

Channel right

MS19599V1

When 16-bit data frame extended to 32-bit channel frame is selected during the I2S configuration phase, only one access to the SPIx_DR register is required. The 16 remaining bits are forced by hardware to 0x0000 to extend the data to 32-bit format.

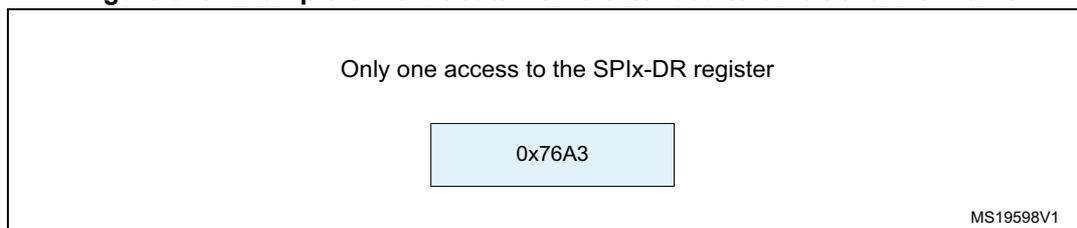

If the data to transmit or the received data are 0x76A3 (0x76A30000 extended to 32-bit), the operation shown in Figure 366 is required.

Figure 366. Example of 16-bit data frame extended to 32-bit channel frame

Only one access to SPIx_DR

0x76A3

MS19595V1

For transmission, each time an MSB is written to SPIx_DR, the TXE flag is set and its interrupt, if allowed, is generated to load the SPIx_DR register with the new value to send. This takes place even if 0x0000 have not yet been sent because it is done by hardware.

For reception, the RXNE flag is set and its interrupt, if allowed, is generated when the first 16 MSB half-word is received.

In this way, more time is provided between two write or read operations, which prevents underrun or overrun conditions (depending on the direction of the data transfer).

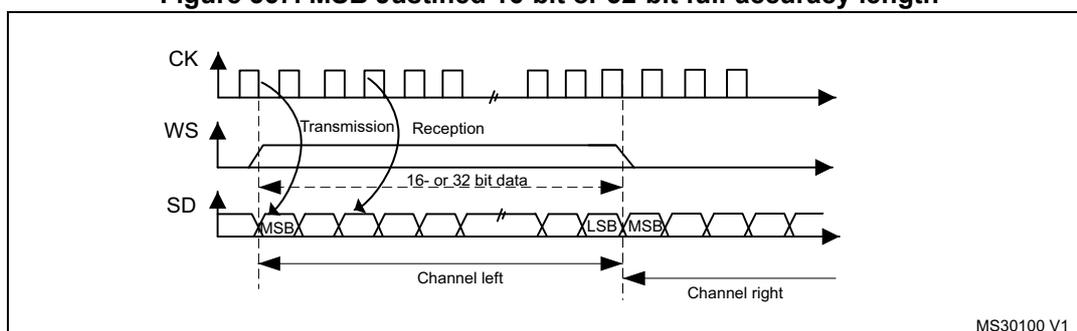

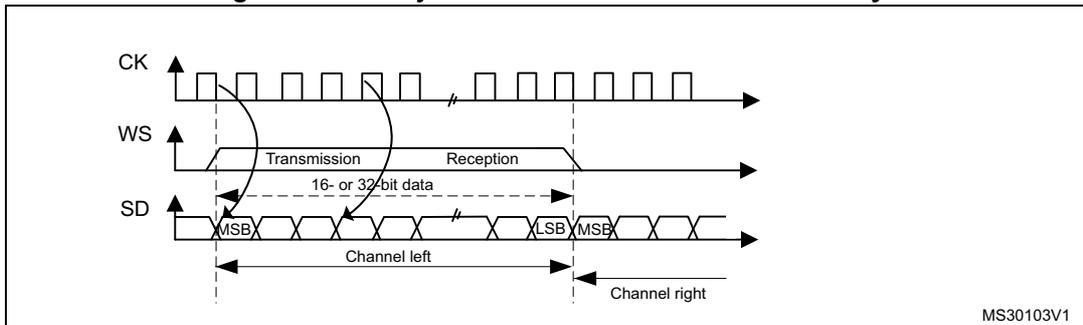

MSB justified standard

For this standard, the WS signal is generated at the same time as the first data bit, which is the MSB.

Figure 367. MSB Justified 16-bit or 32-bit full-accuracy length

Data are latched on the falling edge of CK (for transmitter) and are read on the rising edge (for the receiver).

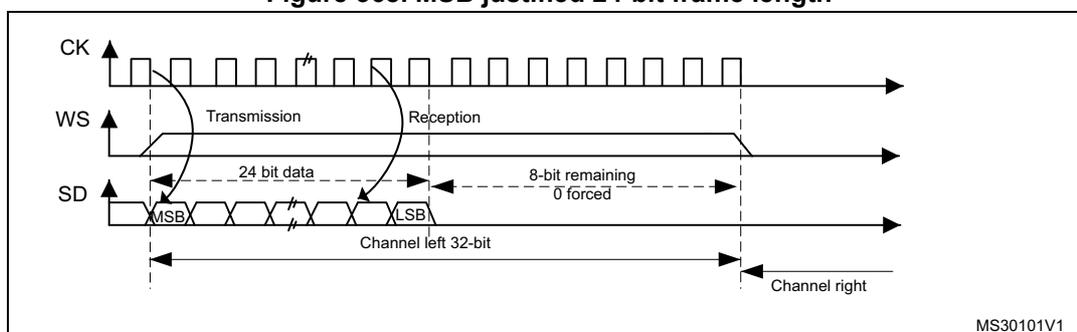

Figure 368. MSB justified 24-bit frame length

Figure 369. MSB justified 16-bit extended to 32-bit packet frame

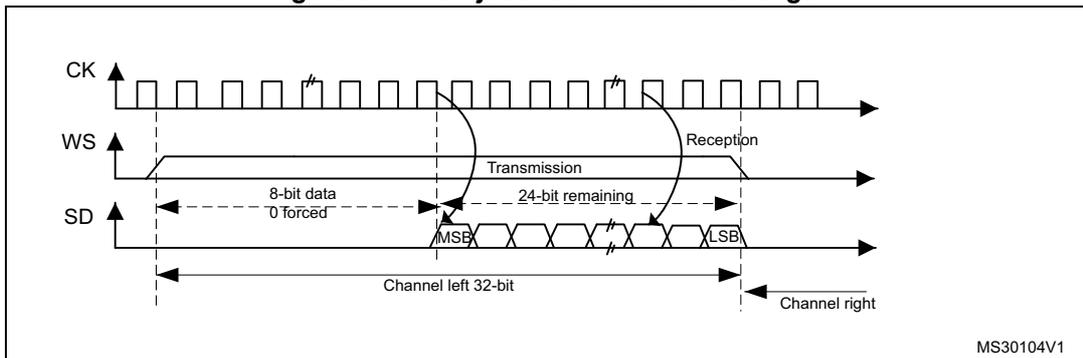

LSB justified standard

This standard is similar to the MSB justified standard (no difference for the 16-bit and 32-bit full-accuracy frame formats).

The sampling of the input and output signals is the same as for the I 2 S Philips standard.

Figure 370. LSB justified 16-bit or 32-bit full-accuracy

Figure 371. LSB justified 24-bit frame length

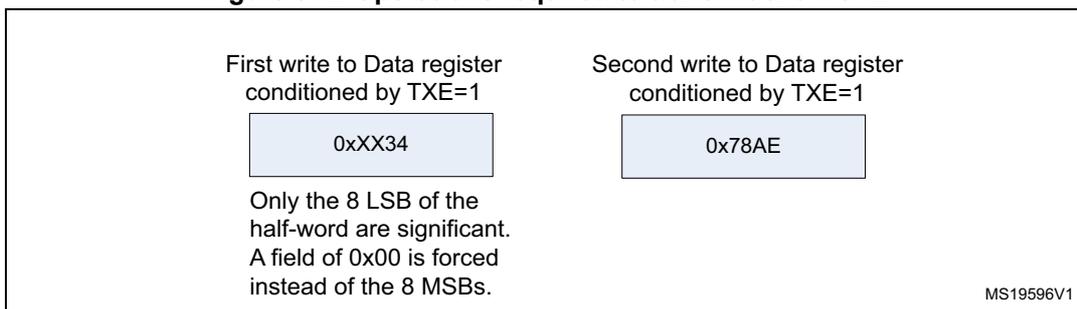

- • In transmission mode:

If data 0x3478AE have to be transmitted, two write operations to the SPIx_DR register are required by software or by DMA. The operations are shown below.

Figure 372. Operations required to transmit 0x3478AE

First write to Data register conditioned by TXE=1

0xxx34

Only the 8 LSB of the half-word are significant. A field of 0x00 is forced instead of the 8 MSBs.

Second write to Data register conditioned by TXE=1

0x78AE

MS19596V1

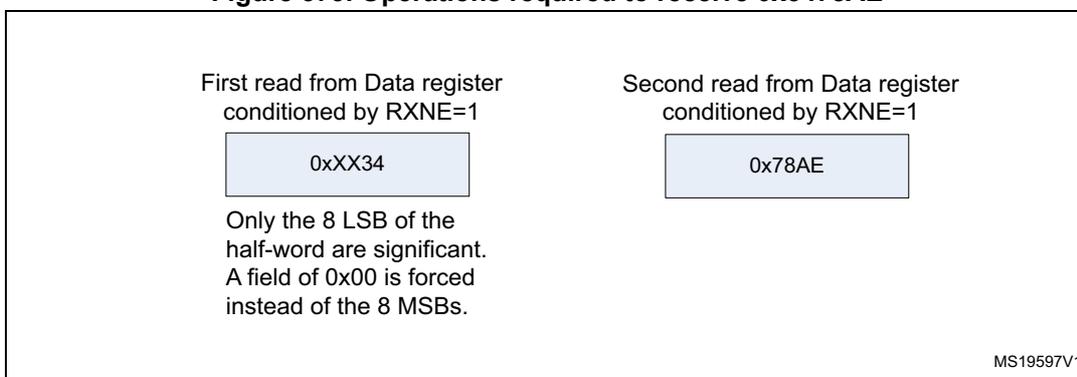

- • In reception mode:

If data 0x3478AE are received, two successive read operations from the SPIx_DR register are required on each RXNE event.

Figure 373. Operations required to receive 0x3478AE

First read from Data register conditioned by RXNE=1

0xxx34

Only the 8 LSB of the half-word are significant. A field of 0x00 is forced instead of the 8 MSBs.

Second read from Data register conditioned by RXNE=1

0x78AE

MS19597V1

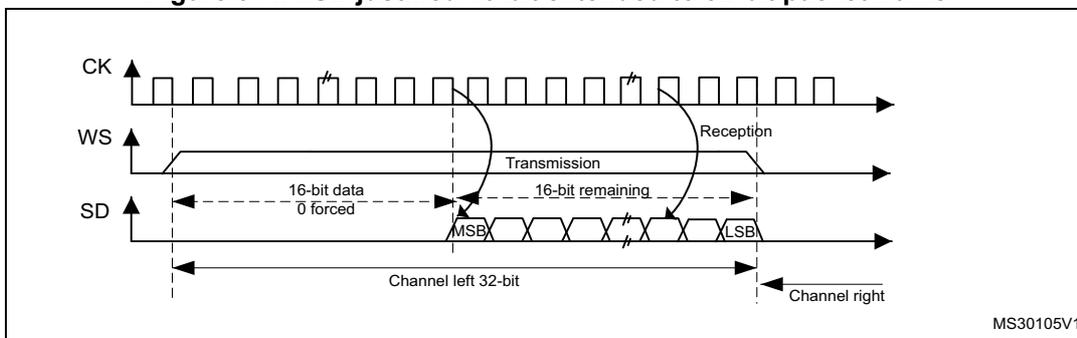

Figure 374. LSB justified 16-bit extended to 32-bit packet frame

CK

WS

SD

Transmission

Reception

16-bit data 0 forced

16-bit remaining

MSB

LSB

Channel left 32-bit

Channel right

MS30105V1

When 16-bit data frame extended to 32-bit channel frame is selected during the I2S configuration phase, Only one access to the SPIx_DR register is required. The 16 remaining bits are forced by hardware to 0x0000 to extend the data to 32-bit format. In this case it corresponds to the half-word MSB.

If the data to transmit or the received data are 0x76A3 (0x0000 76A3 extended to 32-bit), the operation shown in Figure 375 is required.

Figure 375. Example of 16-bit data frame extended to 32-bit channel frame

Only one access to the SPIx-DR register

0x76A3

MS19598V1

In transmission mode, when a TXE event occurs, the application has to write the data to be transmitted (in this case 0x76A3). The 0x000 field is transmitted first (extension on 32-bit). The TXE flag is set again as soon as the effective data (0x76A3) is sent on SD.

In reception mode, RXNE is asserted as soon as the significant half-word is received (and not the 0x0000 field).

In this way, more time is provided between two write or read operations to prevent underrun or overrun conditions.

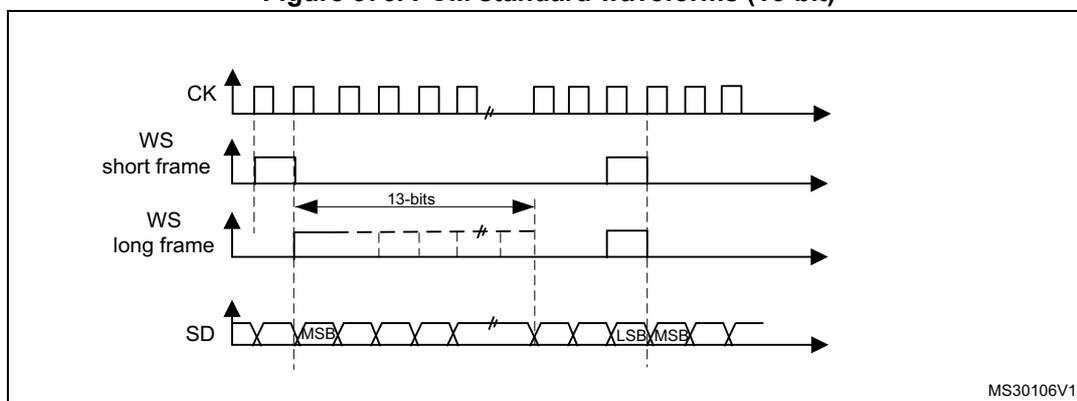

PCM standard

For the PCM standard, there is no need to use channel-side information. The two PCM modes (short and long frame) are available and configurable using the PCMSYNC bit in SPIx_I2SCFGR register.

In PCM mode, the output signals (WS, SD) are sampled on the rising edge of CK signal. The input signals (WS, SD) are captured on the falling edge of CK.

Note that CK and WS are configured as output in MASTER mode.

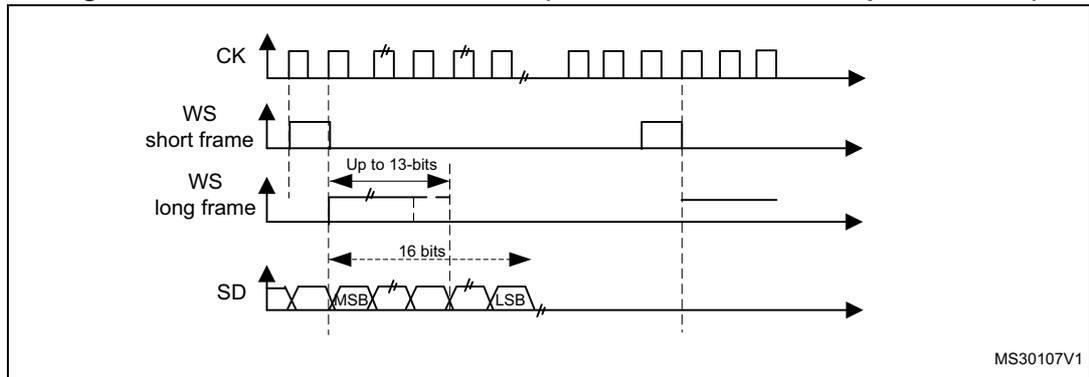

Figure 376. PCM standard waveforms (16-bit)

MS30106V1

For long frame synchronization, the WS signal assertion time is fixed to 13 bits in master mode.

For short frame synchronization, the WS synchronization signal is only one cycle long.

Figure 377. PCM standard waveforms (16-bit extended to 32-bit packet frame)

The diagram illustrates the timing relationships for PCM standard waveforms. The CK (clock) signal is a continuous square wave. The WS (word synchronization) signal is shown in two modes: 'short frame', where it is high for one clock period, and 'long frame', where it is high for up to 13 bits. The SD (serial data) signal is shown as a 16-bit packet, with the MSB (Most Significant Bit) and LSB (Least Significant Bit) clearly marked. The diagram is labeled MS30107V1.

Note: For both modes (master and slave) and for both synchronizations (short and long), the number of bits between two consecutive pieces of data (and so two synchronization signals) needs to be specified (DATLEN and CHLEN bits in the SPIx_I2SCFGR register) even in slave mode.

28.7.4 Start-up description