24. AES hardware accelerator (AES)

24.1 Introduction

The AES hardware accelerator (AES) encrypts or decrypts data, using an algorithm and implementation fully compliant with the advanced encryption standard (AES) defined in Federal information processing standards (FIPS) publication 197.

Multiple chaining modes are supported (ECB, CBC, CTR, GCM, GMAC, CCM), for key sizes of 128 or 256 bits.

The AES accelerator is a 32-bit AHB peripheral. It supports DMA single transfers for incoming and outgoing data (two DMA channels required).

The AES peripheral provides hardware acceleration to AES cryptographic algorithms packaged in STM32 cryptographic library.

AES is an AMBA AHB slave peripheral, accessible through 32-bit word single accesses only (otherwise an AHB bus error is generated and write accesses are ignored).

24.2 AES main features

- • Compliance with NIST “ Advanced encryption standard (AES), FIPS publication 197 ” from November 2001

- • 128-bit data block processing

- • Support for cipher key lengths of 128-bit and 256-bit

- • Encryption and decryption with multiple chaining modes:

- – Electronic codebook (ECB) mode

- – Cipher block chaining (CBC) mode

- – Counter (CTR) mode

- – Galois counter mode (GCM)

- – Galois message authentication code (GMAC) mode

- – Counter with CBC-MAC (CCM) mode

- • 51 or 75 clock cycle latency in ECB mode for processing one 128-bit block of data with, respectively, 128-bit or 256-bit key

- • Integrated key scheduler with its key derivation stage (ECB or CBC decryption only)

- • AMBA AHB slave peripheral, accessible through 32-bit word single accesses only

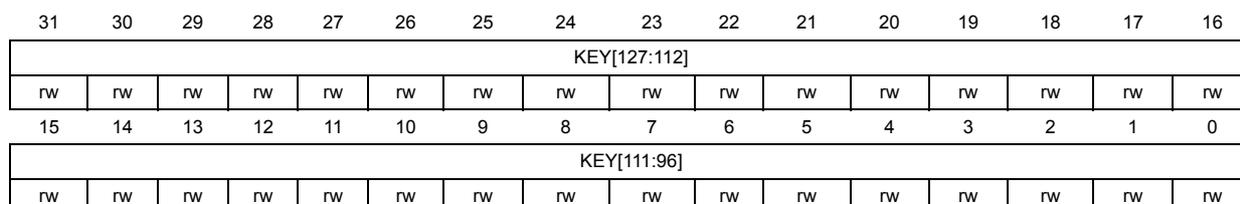

- • 256-bit register for storing the cryptographic key (eight 32-bit registers)

- • 128-bit register for storing initialization vector (four 32-bit registers)

- • 32-bit buffer for data input and output

- • Automatic data flow control with support of single-transfer direct memory access (DMA) using two channels (one for incoming data, one for processed data)

- • Data-swapping logic to support 1-, 8-, 16- or 32-bit data

- • Possibility for software to suspend a message if AES needs to process another message with a higher priority, then resume the original message

24.3 AES implementation

The device has a single instance of AES peripheral.

24.4 AES functional description

24.4.1 AES block diagram

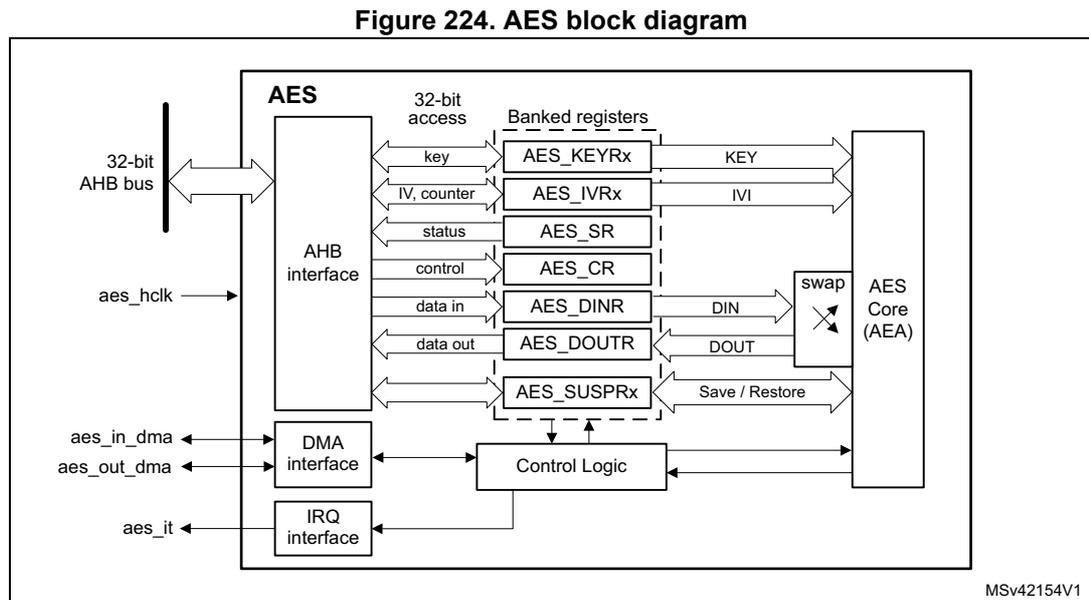

Figure 224 shows the block diagram of AES.

Figure 224. AES block diagram

MSv42154V1

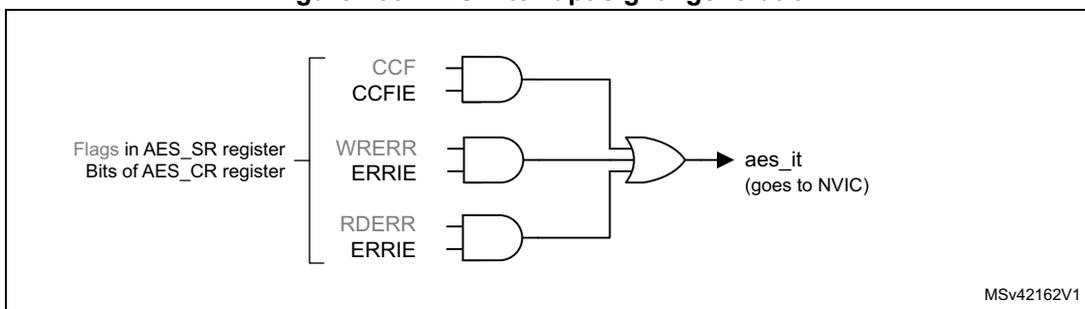

24.4.2 AES internal signals

Table 125 describes the user relevant internal signals interfacing the AES peripheral.

Table 125. AES internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| aes_hclk | digital input | AHB bus clock |

| aes_it | digital output | AES interrupt request |

| aes_in_dma | digital input/output | Input DMA single request/acknowledge |

| aes_out_dma | digital input/output | Output DMA single request/acknowledge |

24.4.3 AES cryptographic core

Overview

The AES cryptographic core consists of the following components:

- • AES algorithm (AEA)

- • multiplier over a binary Galois field (GF2mul)

- • key input

- • initialization vector (IV) input

- • chaining algorithm logic (XOR, feedback/counter, mask)

The AES core works on 128-bit data blocks (four words) with 128-bit or 256-bit key length. Depending on the chaining mode, the AES requires zero or one 96-bit initialization vector IV (and a 32-bit counter field).

The AES features the following modes of operation:

- •

Mode 1:

Plaintext encryption using a key stored in the AES_KEYRx registers - •

Mode 2:

ECB or CBC decryption key preparation. It must be used prior to selecting Mode 3 with ECB or CBC chaining modes. The key prepared for decryption is stored automatically in the AES_KEYRx registers. Now the AES peripheral is ready to switch to Mode 3 for executing data decryption. - •

Mode 3:

Ciphertext decryption using a key stored in the AES_KEYRx registers. When ECB and CBC chaining modes are selected, the key must be prepared beforehand, through Mode 2. - •

Mode 4:

ECB or CBC ciphertext single decryption using the key stored in the AES_KEYRx registers (the initial key is derived automatically).

Note: Mode 2 and mode 4 are only used when performing ECB and CBC decryption. When Mode 4 is selected only one decryption can be done, therefore usage of Mode 2 and Mode 3 is recommended instead.

The operating mode is selected by programming the MODE[1:0] bitfield of the AES_CR register. It may be done only when the AES peripheral is disabled.

Typical data processing

Typical usage of the AES is described in Section 24.4.4: AES procedure to perform a cipher operation on page 695 .

Note: The outputs of the intermediate AEA stages are never revealed outside the cryptographic boundary, with the exclusion of the IVI bitfield.

Chaining modes

The following chaining modes are supported by AES, selected through the CHMOD[2:0] bitfield of the AES_CR register:

- • Electronic code book (ECB)

- • Cipher block chaining (CBC)

- • Counter (CTR)

- • Galois counter mode (GCM)

- • Galois message authentication code (GMAC)

- • Counter with CBC-MAC (CCM)

Note: The chaining mode may be changed only when AES is disabled (bit EN of the AES_CR register set).

Principle of each AES chaining mode is provided in the following subsections.

Detailed information is in dedicated sections, starting from Section 24.4.8: AES basic chaining modes (ECB, CBC) .

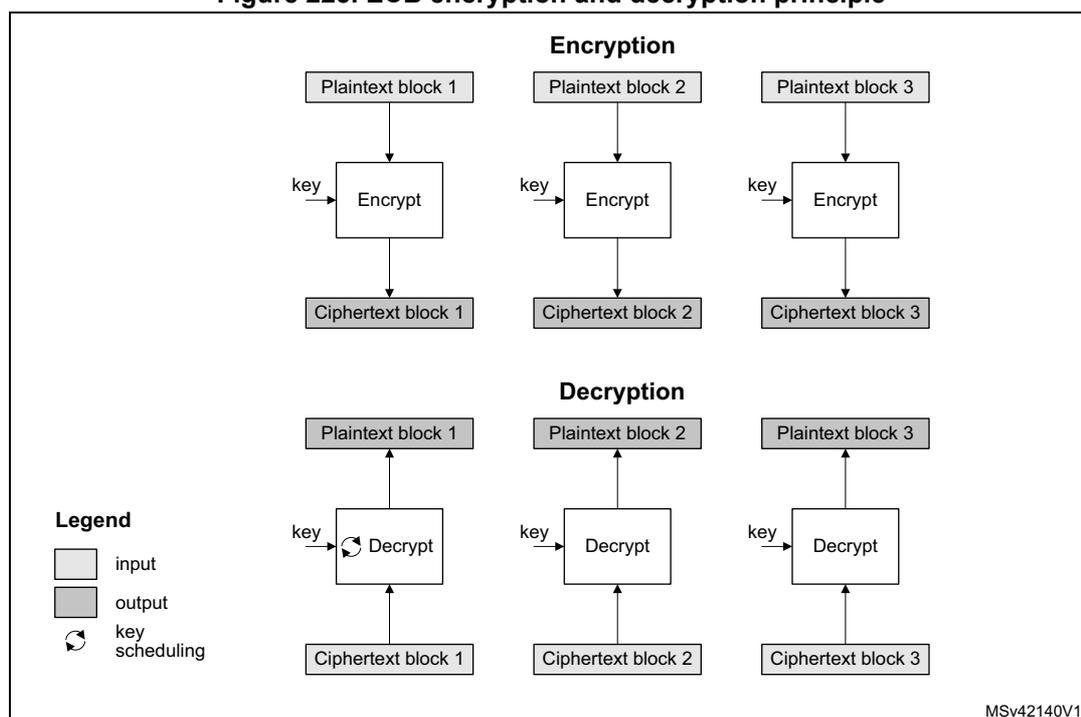

Electronic codebook (ECB) mode

Figure 225. ECB encryption and decryption principle

The diagram illustrates the ECB encryption and decryption process. It is divided into two horizontal sections:

Encryption

and

Decryption

.

Encryption:

Three 'Plaintext block' boxes (1, 2, and 3) are at the top. Below each is an 'Encrypt' box. Arrows point from each plaintext block to its corresponding 'Encrypt' box. A 'key' input arrow points to each 'Encrypt' box. Arrows point from each 'Encrypt' box to a 'Ciphertext block' box (1, 2, and 3) at the bottom.

Decryption:

Three 'Ciphertext block' boxes (1, 2, and 3) are at the bottom. Above each is a 'Decrypt' box. Arrows point from each ciphertext block to its corresponding 'Decrypt' box. A 'key' input arrow points to each 'Decrypt' box. Arrows point from each 'Decrypt' box to a 'Plaintext block' box (1, 2, and 3) at the top.

Legend:

A light gray box is labeled 'input', a dark gray box is labeled 'output', and a circular arrow is labeled 'key scheduling'.

ECB is the simplest mode of operation. There are no chaining operations, and no special initialization stage. The message is divided into blocks and each block is encrypted or decrypted separately.

Note: For decryption, a special key scheduling is required before processing the first block.

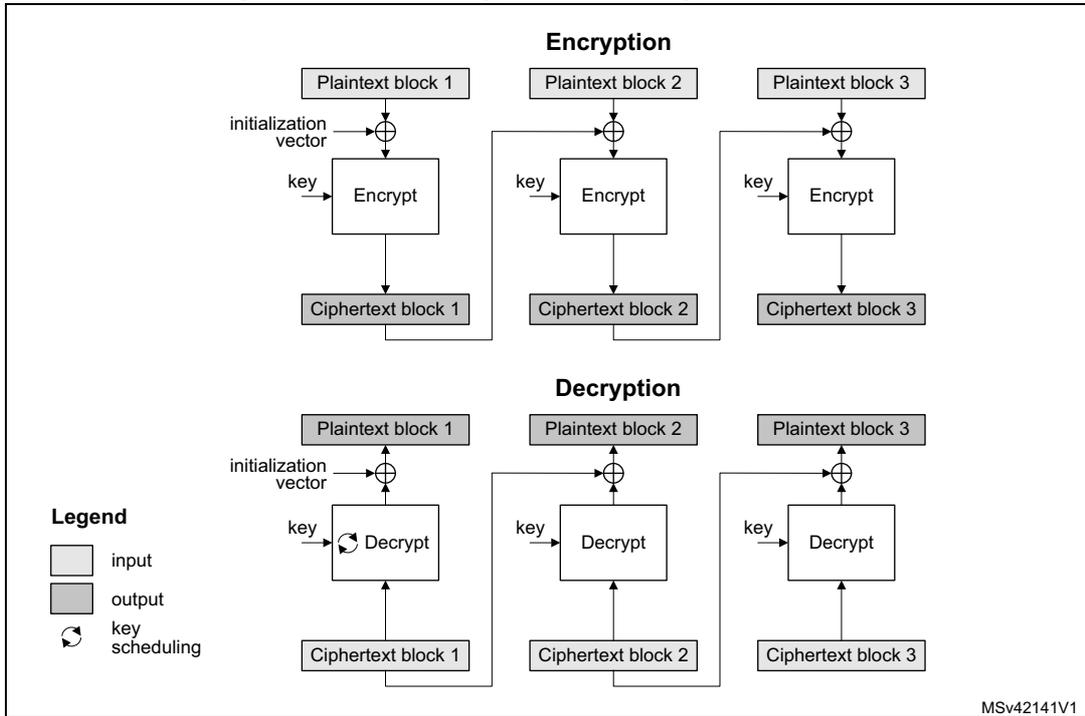

Cipher block chaining (CBC) mode

Figure 226. CBC encryption and decryption principle

The diagram illustrates the CBC encryption and decryption process across three blocks. In the Encryption section, 'Plaintext block 1', 'Plaintext block 2', and 'Plaintext block 3' are shown as white boxes. An 'initialization vector' is XORed with 'Plaintext block 1'. The result is input to an 'Encrypt' block along with a 'key'. The output is 'Ciphertext block 1' (grey box). 'Ciphertext block 1' is XORed with 'Plaintext block 2' and input to the second 'Encrypt' block. The output is 'Ciphertext block 2' (grey box). 'Ciphertext block 2' is XORed with 'Plaintext block 3' and input to the third 'Encrypt' block. The output is 'Ciphertext block 3' (grey box). In the Decryption section, 'Ciphertext block 1', 'Ciphertext block 2', and 'Ciphertext block 3' are shown as grey boxes. 'Ciphertext block 1' is input to a 'Decrypt' block along with a 'key'. The output is XORed with the 'initialization vector' to produce 'Plaintext block 1' (white box). 'Ciphertext block 2' is input to a 'Decrypt' block. The output is XORed with 'Ciphertext block 1' to produce 'Plaintext block 2' (white box). 'Ciphertext block 3' is input to a 'Decrypt' block. The output is XORed with 'Ciphertext block 2' to produce 'Plaintext block 3' (white box). A Legend indicates: white box = input, grey box = output, and a circular arrow = key scheduling.

MSv42141V1

In CBC mode the output of each block chains with the input of the following block. To make each message unique, an initialization vector is used during the first block processing.

Note: For decryption, a special key scheduling is required before processing the first block.

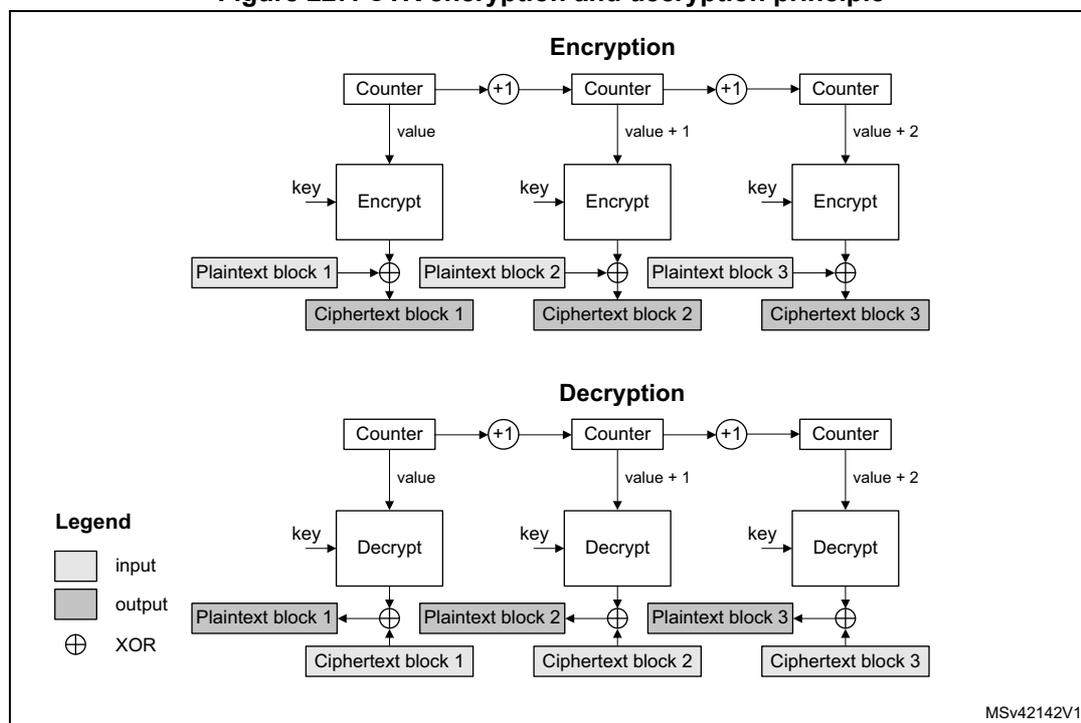

Counter (CTR) mode Figure 227. CTR encryption and decryption principle

Encryption

Counter → (+1) → Counter → (+1) → Counter

value value + 1 value + 2

key → Encrypt key → Encrypt key → Encrypt

Plaintext block 1 → ⊕ → Plaintext block 2 → ⊕ → Plaintext block 3

Ciphertext block 1 Ciphertext block 2 Ciphertext block 3

Decryption

Counter → (+1) → Counter → (+1) → Counter

value value + 1 value + 2

key → Decrypt key → Decrypt key → Decrypt

Plaintext block 1 ← ⊕ ← Plaintext block 2 ← ⊕ ← Plaintext block 3

Ciphertext block 1 Ciphertext block 2 Ciphertext block 3

Legend

input

output

⊕ XOR

MSv42142V1

The CTR mode uses the AES core to generate a key stream. The keys are then XORed with the plaintext to obtain the ciphertext as specified in NIST Special Publication 800-38A, Recommendation for Block Cipher Modes of Operation .

Note: Unlike with ECB and CBC modes, no key scheduling is required for the CTR decryption, since in this chaining scheme the AES core is always used in encryption mode for producing the key stream, or counter blocks.

Galois/counter mode (GCM)

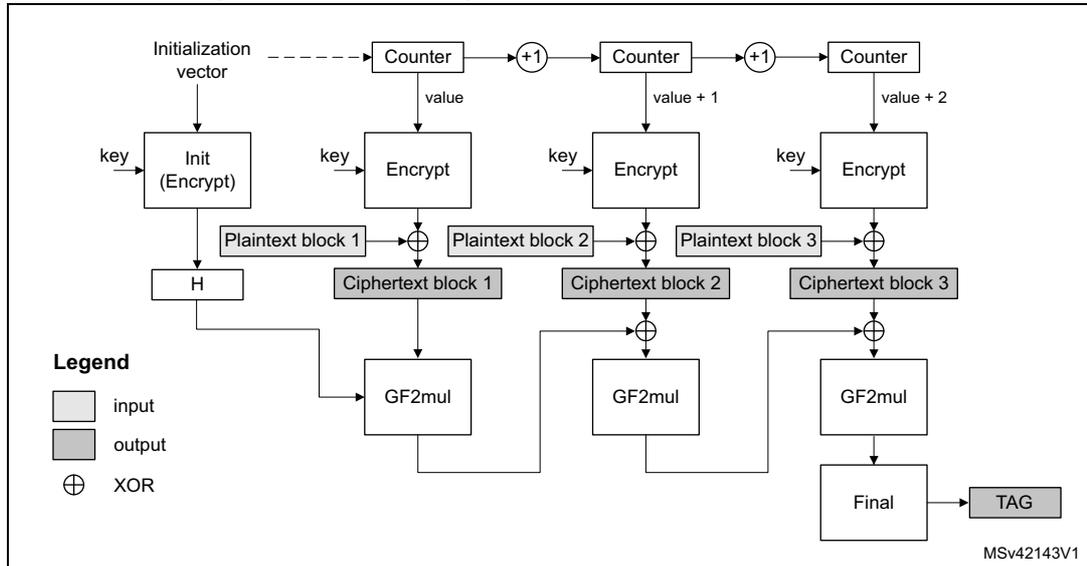

Figure 228. GCM encryption and authentication principle

The diagram illustrates the GCM encryption and authentication process. It starts with an Initialization vector and a key being input to an Init (Encrypt) block, which outputs an H value. Simultaneously, the Initialization vector is passed to a Counter block. The key is also input to a series of Encrypt blocks. The Counter blocks are chained, with each outputting a value ( value , value + 1 , value + 2 ) to the corresponding Encrypt block. The Encrypt blocks take the key and the counter value as input and produce Ciphertext block 1 , Ciphertext block 2 , and Ciphertext block 3 . These ciphertext blocks are XORed ( \( \oplus \) ) with Plaintext block 1 , Plaintext block 2 , and Plaintext block 3 respectively. The resulting XOR outputs are then passed through GF2mul blocks. The H value from the Init block is also input to the first GF2mul block. The outputs of the GF2mul blocks are chained and passed through a Final block to produce the TAG . A legend indicates that light gray boxes represent input , dark gray boxes represent output , and the \( \oplus \) symbol represents XOR . The diagram is labeled MSv42143V1.

In Galois/counter mode (GCM), the plaintext message is encrypted while a message authentication code (MAC) is computed in parallel, thus generating the corresponding ciphertext and its MAC (also known as authentication tag). It is defined in NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation - Galois/Counter Mode (GCM) and GMAC .

GCM mode is based on AES in counter mode for confidentiality. It uses a multiplier over a fixed finite field for computing the message authentication code. It requires an initial value and a particular 128-bit block at the end of the message.

Galois message authentication code (GMAC) principle

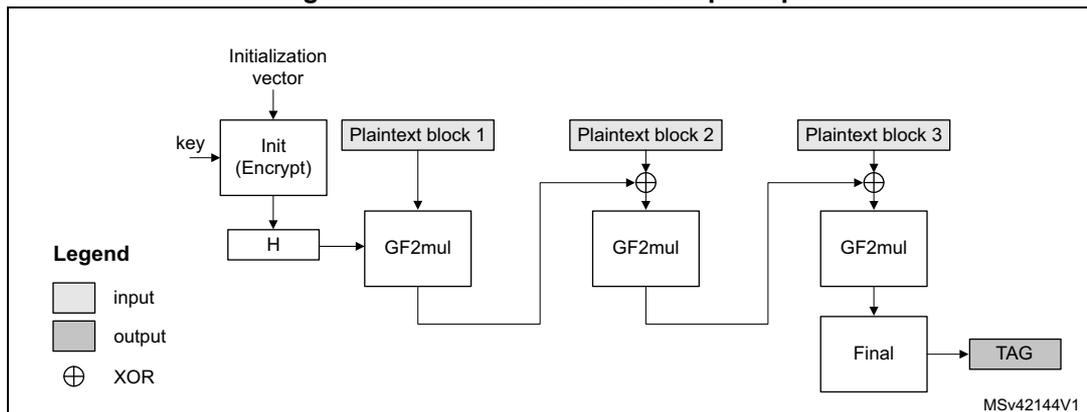

Figure 229. GMAC authentication principle

The diagram illustrates the GMAC authentication process. It starts with an Initialization vector and a key being input to an Init (Encrypt) block, which outputs an H value. The key is also input to a series of GF2mul blocks. The H value is input to the first GF2mul block. The GF2mul blocks take the key and the previous output (or H for the first block) as input and produce an output. This output is XORed ( \( \oplus \) ) with Plaintext block 1 , Plaintext block 2 , and Plaintext block 3 respectively. The resulting XOR outputs are then passed through the next GF2mul block. The final output is passed through a Final block to produce the TAG . A legend indicates that light gray boxes represent input , dark gray boxes represent output , and the \( \oplus \) symbol represents XOR . The diagram is labeled MSv42144V1.

Galois message authentication code (GMAC) allows authenticating a message and generating the corresponding message authentication code (MAC). It is defined in NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation - Galois/Counter Mode (GCM) and GMAC .

GMAC is similar to GCM, except that it is applied on a message composed only by plaintext authenticated data (that is, only header, no payload).

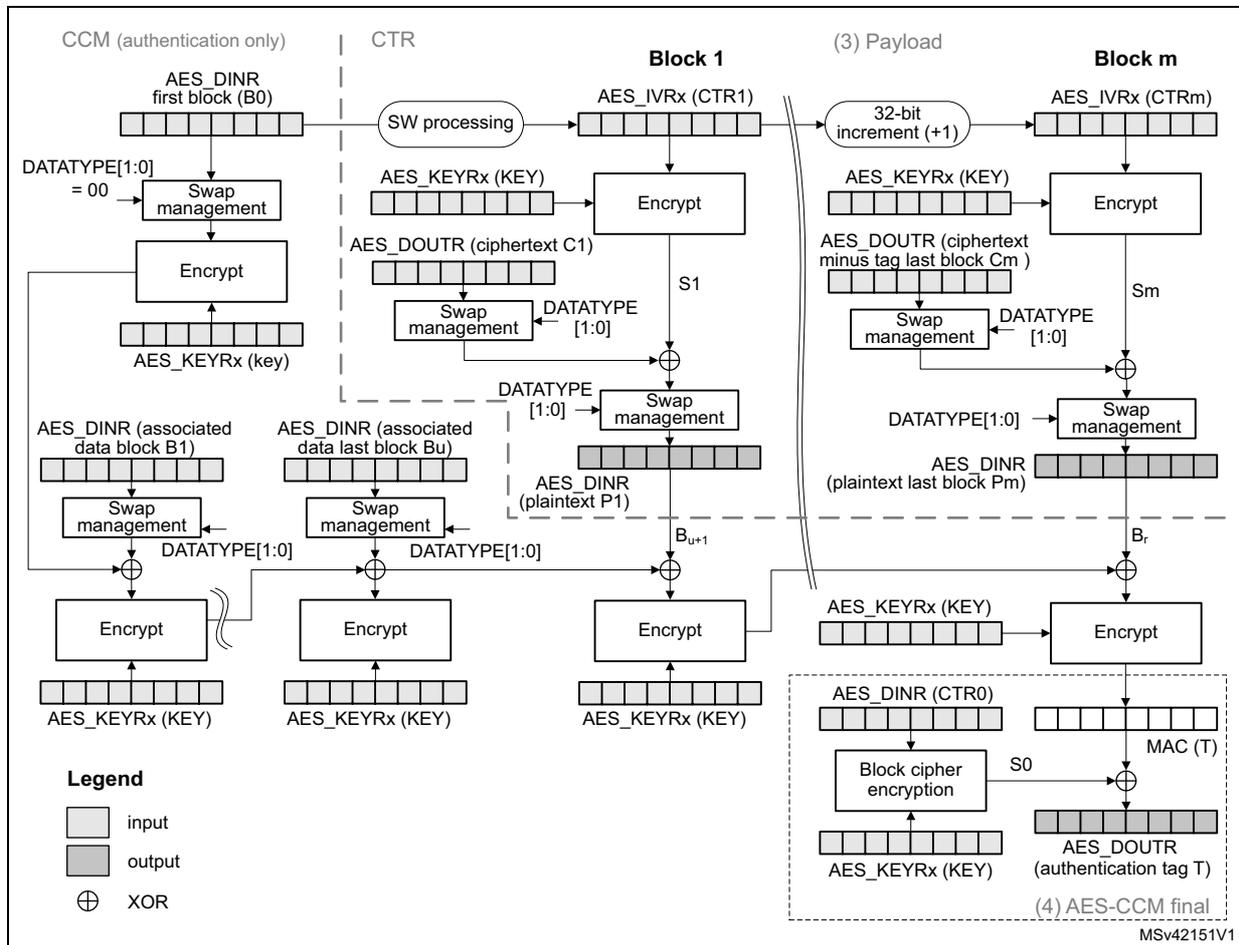

Counter with CBC-MAC (CCM) principle

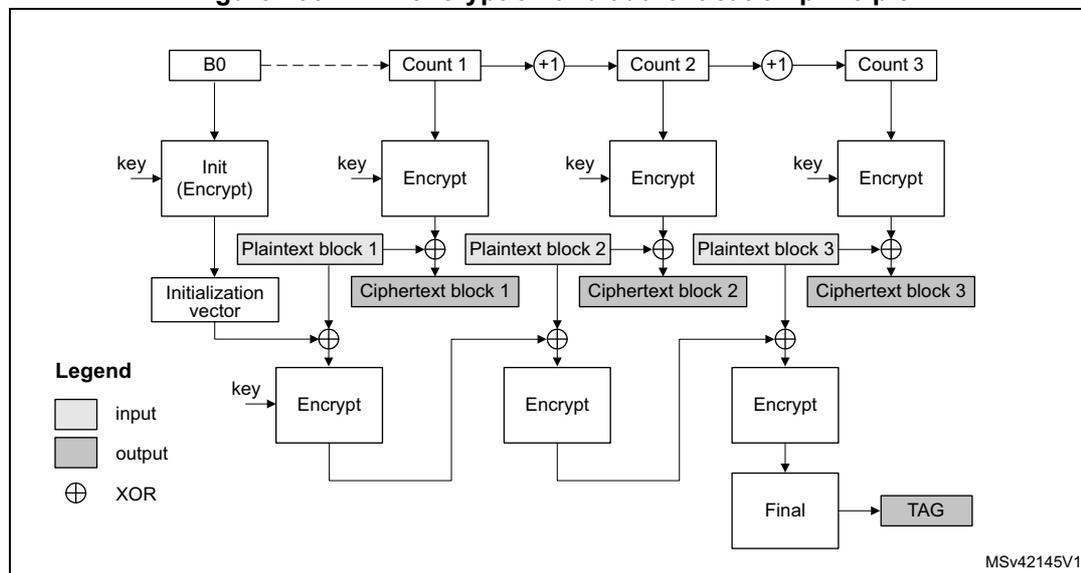

Figure 230. CCM encryption and authentication principle

In Counter with cipher block chaining-message authentication code (CCM) mode, the plaintext message is encrypted while a message authentication code (MAC) is computed in parallel, thus generating the corresponding ciphertext and the corresponding MAC (also known as tag). It is described by NIST in Special Publication 800-38C, Recommendation for Block Cipher Modes of Operation - The CCM Mode for Authentication and Confidentiality .

CCM mode is based on AES in counter mode for confidentiality and it uses CBC for computing the message authentication code. It requires an initial value.

Like GCM, the CCM chaining mode can be applied on a message composed only by plaintext authenticated data (that is, only header, no payload). Note that this way of using CCM is not called CMAC (it is not similar to GCM/GMAC), and its usage is not recommended by NIST.

24.4.4 AES procedure to perform a cipher operation

Introduction

A typical cipher operation is explained below. Detailed information is provided in sections starting from Section 24.4.8: AES basic chaining modes (ECB, CBC) .

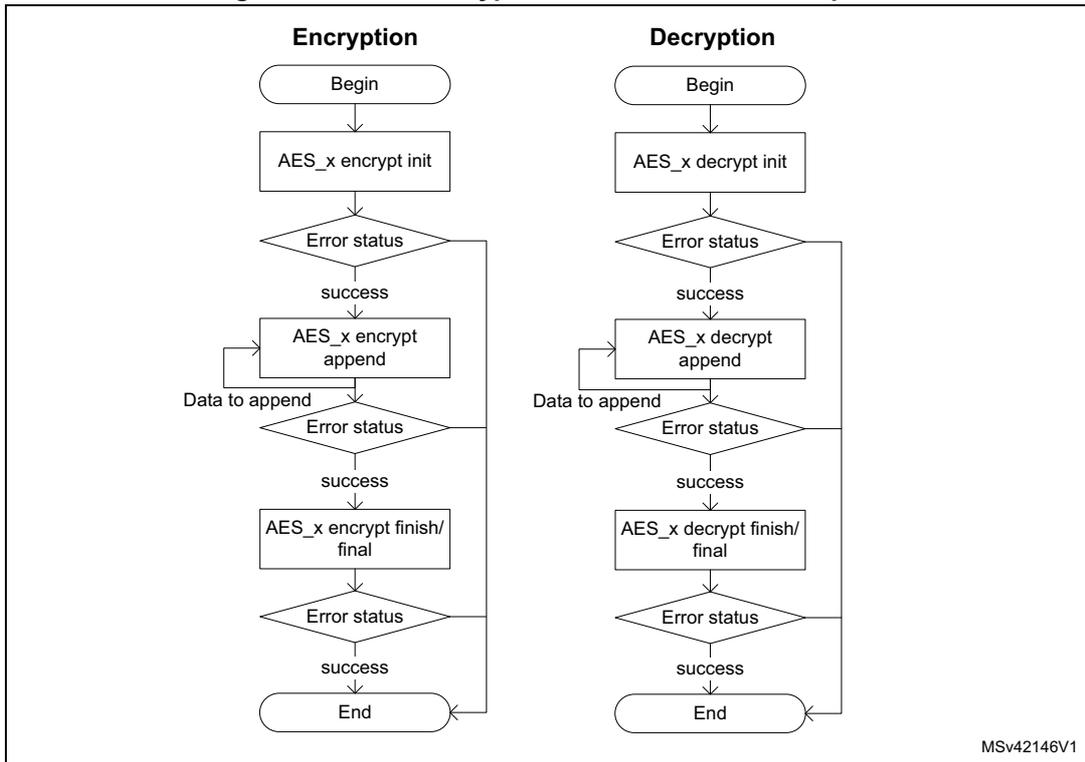

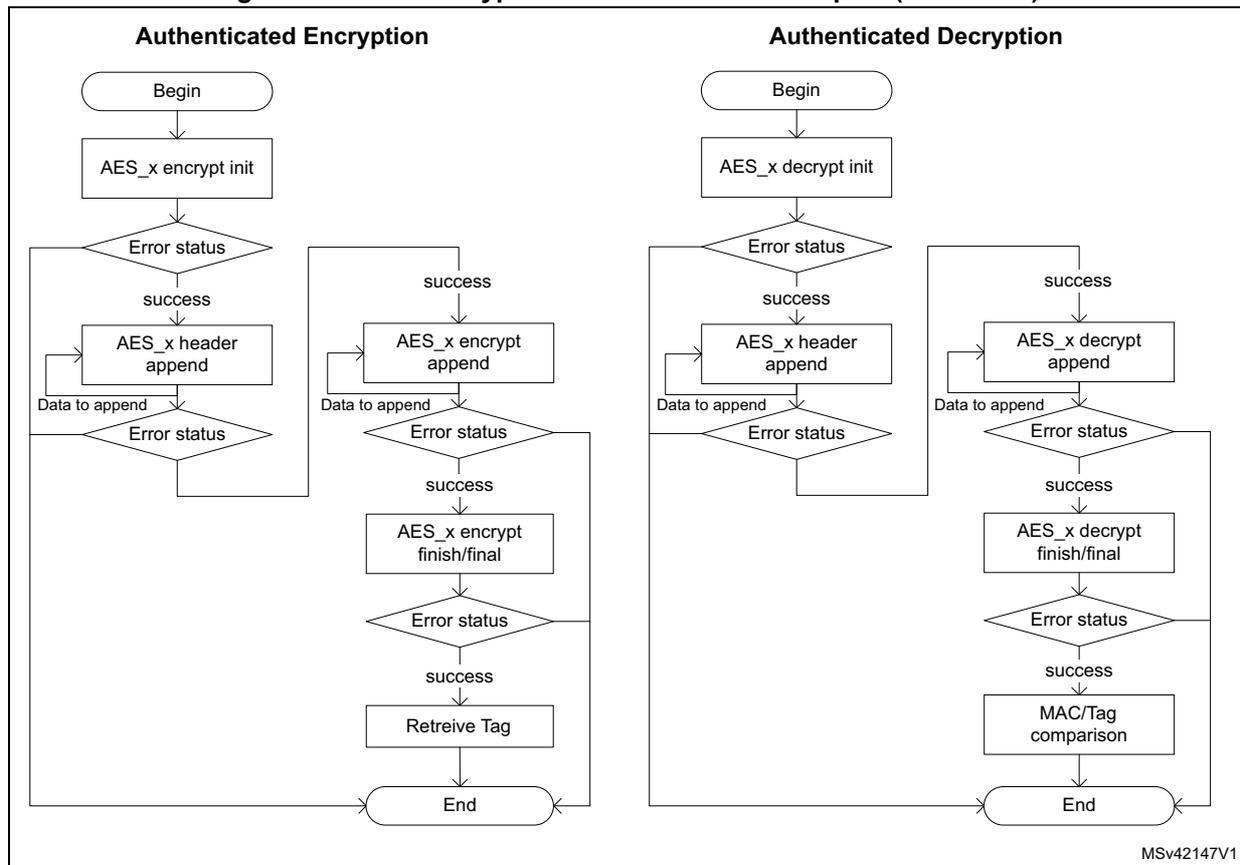

The flowcharts shown in Figure 231 and Figure 232 describe the way STM32 cryptographic library implements the AES algorithm. AES accelerates the execution of the AES-128 and AES-256 cryptographic algorithms in ECB, CBC, CTR, CCM, and GCM operating modes.

Note: For more details on the cryptographic library, refer to the UM1924 user manual “STM32 crypto library” available from www.st.com .

Figure 231. STM32 cryptolib AES flowchart examples

graph TD

subgraph Encryption

E1([Begin]) --> E2[AES_x encrypt init]

E2 --> E3{Error status}

E3 -- success --> E4[AES_x encrypt append]

E4 --> E5{Data to append}

E5 --> E6{Error status}

E6 -- success --> E7[AES_x encrypt finish/final]

E7 --> E8{Error status}

E8 -- success --> E9([End])

E3 -- bypass --> E9

E6 -- bypass --> E9

E8 -- bypass --> E9

end

subgraph Decryption

D1([Begin]) --> D2[AES_x decrypt init]

D2 --> D3{Error status}

D3 -- success --> D4[AES_x decrypt append]

D4 --> D5{Data to append}

D5 --> D6{Error status}

D6 -- success --> D7[AES_x decrypt finish/final]

D7 --> D8{Error status}

D8 -- success --> D9([End])

D3 -- bypass --> D9

D6 -- bypass --> D9

D8 -- bypass --> D9

endMSv42146V1

Figure 232. STM32 cryptolib AES flowchart examples (continued)

graph TD

subgraph Authenticated Encryption

AE_Beg[Begin] --> AE_Init[AES_x encrypt init]

AE_Init --> AE_Err1{Error status}

AE_Err1 -- success --> AE_Head[AES_x header append]

AE_Head --> AE_Data{Data to append}

AE_Data -- success --> AE_Fin[AES_x encrypt finish/final]

AE_Data -- not success --> AE_Err1

AE_Fin --> AE_Err2{Error status}

AE_Err2 -- success --> AE_Tag[Retreive Tag]

AE_Tag --> AE_End[End]

end

subgraph Authenticated Decryption

AD_Beg[Begin] --> AD_Init[AES_x decrypt init]

AD_Init --> AD_Err1{Error status}

AD_Err1 -- success --> AD_Head[AES_x header append]

AD_Head --> AD_Data{Data to append}

AD_Data -- success --> AD_Fin[AES_x decrypt finish/final]

AD_Data -- not success --> AD_Err1

AD_Fin --> AD_Err2{Error status}

AD_Err2 -- success --> AD_Mac[MAC/Tag comparison]

AD_Mac --> AD_End[End]

end

MSV42147V1

Initialization of AES

To initialize AES, first disable it by clearing the EN bit of the AES_CR register. Then perform the following steps in any order:

- • Configure the AES mode, by programming the MODE[1:0] bitfield of the AES_CR register.

- – For encryption, Mode 1 must be selected (MODE[1:0] = 00).

- – For decryption, Mode 3 must be selected (MODE[1:0] = 10), unless ECB or CBC chaining modes are used. In this latter case, an initial key derivation of the encryption key must be performed, as described in Section 24.4.5: AES decryption key preparation .

- • Select the chaining mode, by programming the CHMOD[2:0] bitfield of the AES_CR register

- • Configure the key size (128-bit or 256-bit), with the KEYSIZE bitfield of the AES_CR register.

- • Write a symmetric key into the AES_KEYRx registers (4 or 8 registers depending on the key size).

- • Configure the data type (1-, 8-, 16- or 32-bit), with the DATATYPE[1:0] bitfield in the AES_CR register.

- • When it is required (for example in CBC or CTR chaining modes), write the initialization vectors into the AES_IVRx register.

Data append

This section describes different ways of appending data for processing, where the size of data to process is not a multiple of 128 bits.

For ECB, CBC and GCM encryption mode, refer to Section 24.4.6: AES ciphertext stealing and data padding . The second-last and the last block management in these cases is more complex than in the sequence described in this section.

Data append through polling

This method uses flag polling to control the data append.

For all other cases, the data is appended through the following sequence:

- 1. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 2. Repeat the following sub-sequence until the payload is entirely processed:

- a) Write four input data words into the AES_DINR register.

- b) Wait until the status flag CCF is set in the AES_SR, then read the four data words from the AES_DOUTR register.

- c) Clear the CCF flag, by setting the CCFC bit of the AES_CR register.

- d) If the data block just processed is the second-last block of the message and the significant data in the last block to process is inferior to 128 bits, pad the remainder of the last block with zeros

- 3. Discard the data that is not part of the payload, then disable the AES peripheral by clearing the EN bit of the AES_CR register.

Note: Up to three wait cycles are automatically inserted between two consecutive writes to the AES_DINR register, to allow sending the key to the AES processor.

Data append using interrupt

The method uses interrupt from the AES peripheral to control the data append, through the following sequence:

- 1. Enable interrupts from AES by setting the CCFIE bit of the AES_CR register.

- 2. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 3. Write first four input data words into the AES_DINR register.

- 4. Handle the data in the AES interrupt service routine, upon interrupt:

- a) Read four output data words from the AES_DOUTR register.

- b) Clear the CCF flag and thus the pending interrupt, by setting the CCFC bit of the AES_CR register

- c) If the data block just processed is the second-last block of an message and the significant data in the last block to process is inferior to 128 bits, pad the remainder of the last block with zeros. Then proceed with point 4e).

- d) If the data block just processed is the last block of the message, discard the data that is not part of the payload, then disable the AES peripheral by clearing the EN bit of the AES_CR register and quit the interrupt service routine.

- e) Write next four input data words into the AES_DINR register and quit the interrupt service routine.

Note: AES is tolerant of delays between consecutive read or write operations, which allows, for example, an interrupt from another peripheral to be served between two AES computations.

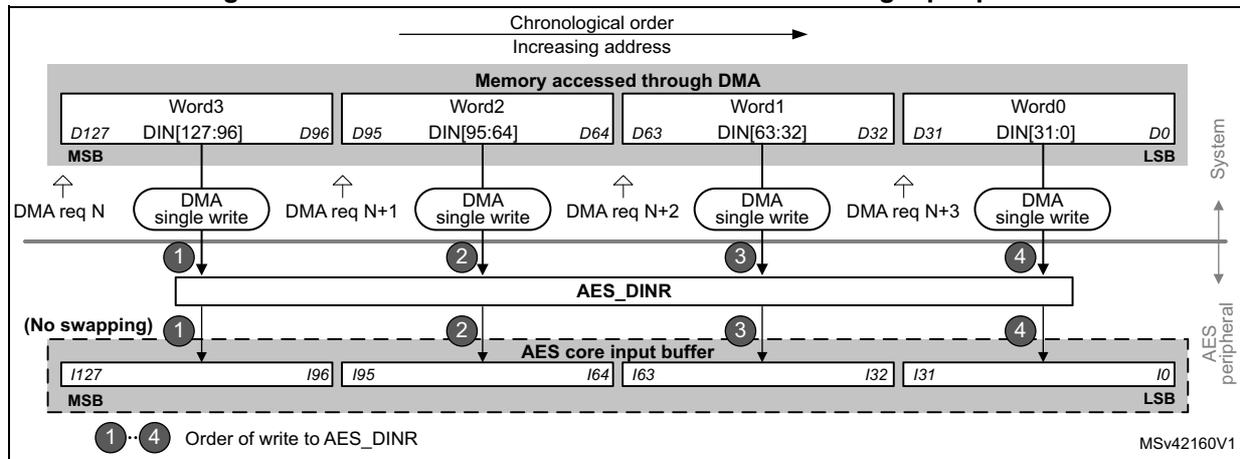

Data append using DMA

With this method, all the transfers and processing are managed by DMA and AES. To use the method, proceed as follows:

- 1. Prepare the last four-word data block (if the data to process does not fill it completely), by padding the remainder of the block with zeros.

- 2. Configure the DMA controller so as to transfer the data to process from the memory to the AES peripheral input and the processed data from the AES peripheral output to the memory, as described in Section 24.4.16: AES DMA interface . Configure the DMA controller so as to generate an interrupt on transfer completion.

- 3. Enable the AES peripheral by setting the EN bit of the AES_CR register

- 4. Enable DMA requests by setting the DMAINEN and DMAOUTEN bits of the AES_CR register.

- 5. Upon DMA interrupt indicating the transfer completion, get the AES-processed data from the memory.

Note: The CCF flag has no use with this method, because the reading of the AES_DOUTR register is managed by DMA automatically, without any software action, at the end of the computation phase.

24.4.5 AES decryption key preparation

For an ECB or CBC decryption, a key for the first round of decryption must be derived from the key of the last round of encryption. This is why a complete key schedule of encryption is required before performing the decryption. This key preparation is not required for AES decryption in modes other than ECB or CBC.

Recommended method is to select the Mode 2 by setting to 01 the MODE[1:0] bitfield of the AES_CR (key process only), then proceed with the decryption by setting MODE[1:0] to 10 (Mode 3, decryption only). Mode 2 usage is described below:

- 1. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

- 2. Select Mode 2 by setting to 01 the MODE[1:0] bitfield of the AES_CR. The CHMOD[2:0] bitfield is not significant in this case because this key derivation mode is independent of the chaining algorithm selected.

- 3. Set key length to 128 or 256 bits, via KEYSIZE bit of AES_CR register.

- 4. Write the AES_KEYRx registers (128 or 256 bits) with encryption key, as shown in Figure 233 . Writes to the AES_IVRx registers have no effect.

- 5. Enable the AES peripheral, by setting the EN bit of the AES_CR register.

- 6. Wait until the CCF flag is set in the AES_SR register.

- 7. Derived key is available in AES core, ready to use for decryption. Application can also read the AES_KEYRx register to obtain the derived key if needed, as shown in Figure 233 (the processed key is loaded automatically into the AES_KEYRx registers).

Note: The AES is disabled by hardware when the derivation key is available.

To restart a derivation key computation, repeat steps 4, 5, 6 and 7.

Figure 233. Encryption key derivation for ECB/CBC decryption (Mode 2)

![Figure 233. Encryption key derivation for ECB/CBC decryption (Mode 2). The diagram shows a sequence of operations: Input phase (4 write operations into AES_KEYRx[31:0] with WR EK3, WR EK2, WR EK1, WR EK0), Computation phase (Wait until flag CCF = 1, with EN = 1 into AES_CR), and Output phase (optional, 4 read operations of AES_KEYRx[31:0] with RD DK3, RD DK2, RD DK1, RD DK0). The input phase is labeled MSB to LSB, and the output phase is also labeled MSB to LSB. A legend at the bottom defines EK as encryption key (4 words EK3, ..., EK0) and DK as decryption key (4 words DK3, ..., DK0). The diagram is labeled MS18937V2.](/RM0430-STM32F413-423/4286d6102bce8b0903b7ad79cd772959_img.jpg)

Diagram illustrating the encryption key derivation for ECB/CBC decryption (Mode 2). The process is divided into three phases:

- Input phase:

4 write operations into

AES_KEYRx[31:0](MSB to LSB):WR EK3,WR EK2,WR EK1,WR EK0. - Computation phase:

Wait until flag

CCF = 1. This phase is initiated by settingEN = 1intoAES_CR. - Output phase (optional):

4 read operations of

AES_KEYRx[31:0](MSB to LSB):RD DK3,RD DK2,RD DK1,RD DK0. This results in a 128-bit derivation key stored intoAES_KEYRx.

Legend:

- EK = encryption key = 4 words (EK3, ..., EK0)

- DK = decryption key = 4 words (DK3, ..., DK0)

MS18937V2

If the software stores the initial key prepared for decryption, it is enough to do the key schedule operation only once for all the data to be decrypted with a given cipher key.

Note: The operation of the key preparation lasts 80 or 109 clock cycles, depending on the key size (128- or 256-bit).

Note:

Alternative key preparation is to select Mode 4 by setting to 11 the

MODE[1:0]

bitfield of the

AES_CR

register. In this case Mode 3 cannot be used.

24.4.6 AES ciphertext stealing and data padding

When using AES in ECB or CBC modes to manage messages the size of which is not a multiple of the block size (128 bits), ciphertext stealing techniques are used, such as those described in NIST Special Publication 800-38A, Recommendation for Block Cipher Modes of Operation: Three Variants of Ciphertext Stealing for CBC Mode . Since the AES peripheral on the device does not support such techniques, the last two blocks of input data must be handled in a special way by the application.

Note: Ciphertext stealing techniques are not documented in this reference manual.

Similarly, when AES is used in other modes than ECB or CBC, an incomplete input data block (that is, block with input data shorter than 128 bits) must be padded with zeros prior to encryption (that is, extra bits must be appended to the trailing end of the data string). After decryption, the extra bits must be discarded. As AES does not implement automatic data padding operation to the last block , the application must follow the recommendation given in Section 24.4.4: AES procedure to perform a cipher operation on page 695 to manage messages the size of which is not a multiple of 128 bits.

Note:

Padding data are swapped in a similar way as normal data, according to the

DATATYPE[1:0]

field of the

AES_CR

register (see

Section 24.4.13: .AES data registers and data swapping on page 721

for details).

A workaround is required in order to properly compute authentication tags for GCM encryption , when the input data in the last block is inferior to 128 bits . During GCM encryption payload phase and before inserting a last plaintext block smaller than 128 bits, then application must apply the following steps:

- 1. Disable the AES peripheral by clearing the EN bit of the AES_CR register

- 2. Change the mode to CTR by writing 010 to the CHMOD[2:0] bitfield of the AES_CR register.

- 3. Pad the last block (smaller than 128 bits) with zeros to have a complete block of 128 bits, then write it into AES_DINR register.

- 4. Upon encryption completion, read the 128-bit ciphertext from the AES_DOUTR register and store it as intermediate data.

- 5. Change again the mode to GCM by writing 011 to the CHMOD[2:0] bitfield of the AES_CR register.

- 6. Select Final phase by writing 11 to the GCMPH[1:0] bitfield of the AES_CR register.

- 7. In the intermediate data, set to zero the bits corresponding to the padded bits of the last block of payload, then insert the resulting data into AES_DINR register.

- 8. Wait for operation completion, and read data on AES_DOUTR. This data is to be discarded.

- 9. Apply the normal Final phase as described in Section 24.4.10: AES Galois/counter mode (GCM) on page 709

24.4.7 AES task suspend and resume

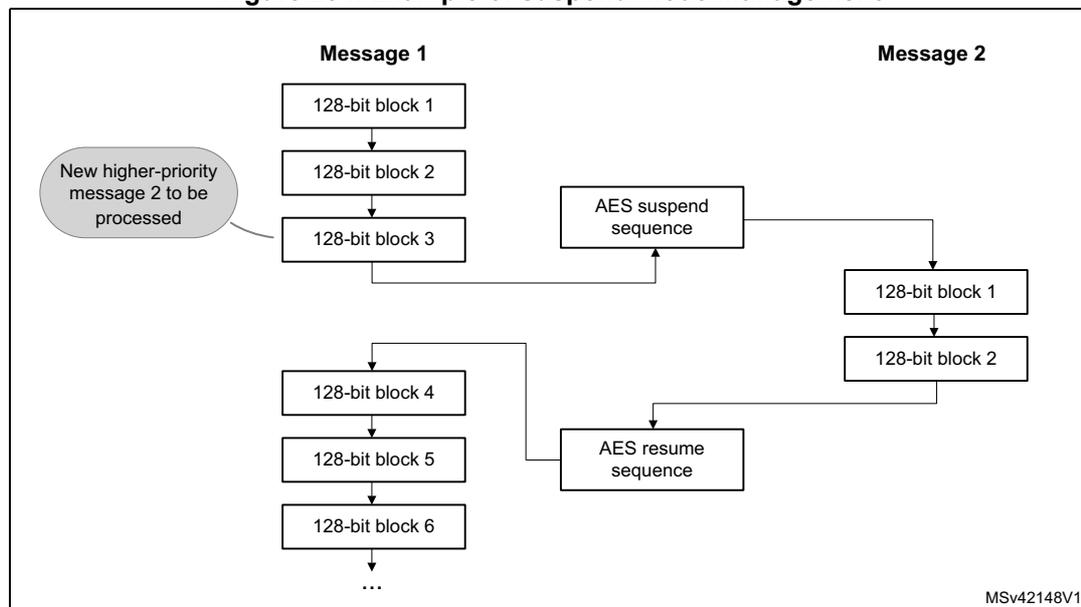

A message can be suspended if another message with a higher priority must be processed. When this highest priority message is sent, the suspended message can resume in both encryption or decryption mode.

Suspend/resume operations do not break the chaining operation and the message processing can resume as soon as AES is enabled again to receive the next data block.

Figure 234 gives an example of suspend/resume operation: Message 1 is suspended in order to send a shorter and higher-priority Message 2.

Figure 234. Example of suspend mode management

The diagram shows two message processing paths. Message 1 starts with '128-bit block 1', followed by '128-bit block 2', and '128-bit block 3'. A callout bubble indicates 'New higher-priority message 2 to be processed'. At this point, an 'AES suspend sequence' box is shown, with an arrow pointing from Message 1's flow to it. Message 2 then begins with '128-bit block 1' and '128-bit block 2'. After Message 2, an 'AES resume sequence' box is shown, with an arrow pointing from it back to Message 1's flow. Message 1 then resumes with '128-bit block 4', '128-bit block 5', and '128-bit block 6', followed by an ellipsis. The diagram is labeled 'MSv42148V1' in the bottom right corner.

A detailed description of suspend/resume operations is in the sections dedicated to each AES mode.

24.4.8 AES basic chaining modes (ECB, CBC)

Overview

This section gives a brief explanation of the four basic operation modes provided by the AES computing core: ECB encryption, ECB decryption, CBC encryption and CBC decryption. For detailed information, refer to the FIPS publication 197 from November 26, 2001.

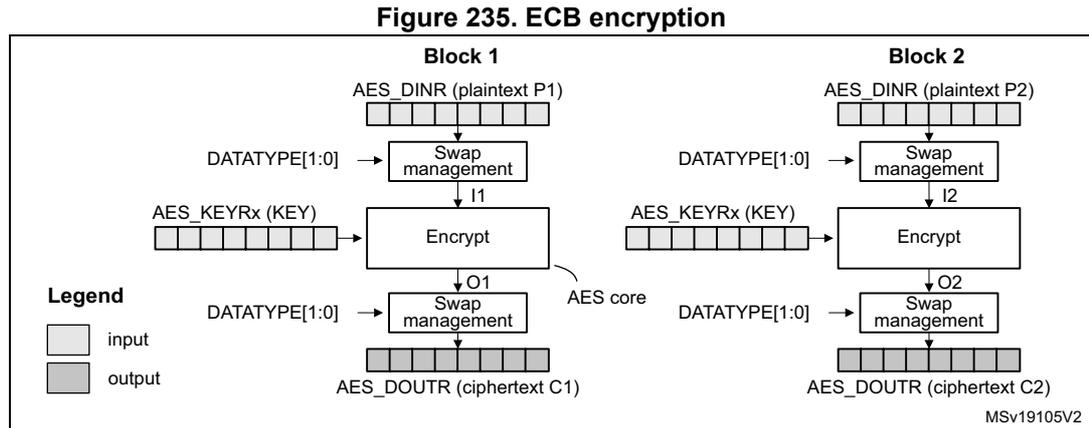

Figure 235 illustrates the electronic codebook (ECB) encryption.

Figure 235. ECB encryption

The diagram illustrates the ECB encryption process for two blocks, Block 1 and Block 2. Each block follows a similar flow:

- Block 1: The 128-bit plaintext input data block P1 in the AES_DINR register is processed by a 'Swap management' block (controlled by DATATYPE[1:0]) to produce an intermediate result I1. I1 is then processed by the 'Encrypt' block of the AES core using the AES_KEYRx (KEY) to produce an intermediate result O1. O1 is then processed by another 'Swap management' block (controlled by DATATYPE[1:0]) to produce the 128-bit ciphertext output data block C1 in the AES_DOUTR register.

- Block 2: The 128-bit plaintext input data block P2 in the AES_DINR register is processed by a 'Swap management' block (controlled by DATATYPE[1:0]) to produce an intermediate result I2. I2 is then processed by the 'Encrypt' block of the AES core using the AES_KEYRx (KEY) to produce an intermediate result O2. O2 is then processed by another 'Swap management' block (controlled by DATATYPE[1:0]) to produce the 128-bit ciphertext output data block C2 in the AES_DOUTR register.

In ECB encrypt mode, the 128-bit plaintext input data block Px in the AES_DINR register first goes through bit/byte/half-word swapping. The swap result Ix is processed with the AES core set in encrypt mode, using a 128- or 256-bit key. The encryption result Ox goes through bit/byte/half-word swapping, then is stored in the AES_DOUTR register as 128-bit ciphertext output data block Cx. The ECB encryption continues in this way until the last complete plaintext block is encrypted.

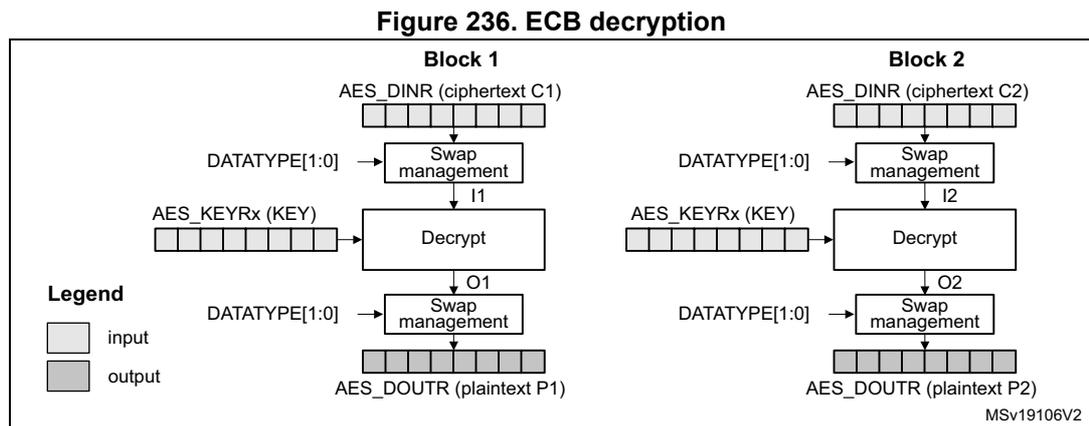

Figure 236 illustrates the electronic codebook (ECB) decryption.

Figure 236. ECB decryption

The diagram illustrates the ECB decryption process for two blocks, Block 1 and Block 2. Each block follows a similar flow:

- Block 1: The 128-bit ciphertext input data block C1 in the AES_DINR register is processed by a 'Swap management' block (controlled by DATATYPE[1:0]) to produce an intermediate result I1. I1 is then processed by the 'Decrypt' block of the AES core using the AES_KEYRx (KEY) to produce an intermediate result O1. O1 is then processed by another 'Swap management' block (controlled by DATATYPE[1:0]) to produce the 128-bit plaintext output data block P1 in the AES_DOUTR register.

- Block 2: The 128-bit ciphertext input data block C2 in the AES_DINR register is processed by a 'Swap management' block (controlled by DATATYPE[1:0]) to produce an intermediate result I2. I2 is then processed by the 'Decrypt' block of the AES core using the AES_KEYRx (KEY) to produce an intermediate result O2. O2 is then processed by another 'Swap management' block (controlled by DATATYPE[1:0]) to produce the 128-bit plaintext output data block P2 in the AES_DOUTR register.

To perform an AES decryption in the ECB mode, the secret key has to be prepared by collecting the last-round encryption key (which requires to first execute the complete key schedule for encryption), and using it as the first-round key for the decryption of the ciphertext. This preparation is supported by the AES core.

In ECB decrypt mode, the 128-bit ciphertext input data block C1 in the AES_DINR register first goes through bit/byte/half-word swapping. The keying sequence is reversed compared to that of the ECB encryption. The swap result I1 is processed with the AES core set in decrypt mode, using the formerly prepared decryption key. The decryption result goes through bit/byte/half-word swapping, then is stored in the AES_DOUTR register as 128-bit plaintext output data block P1. The ECB decryption continues in this way until the last complete ciphertext block is decrypted.

Figure 237 illustrates the cipher block chaining (CBC) encryption mode.

Figure 237. CBC encryption

![Figure 237. CBC encryption diagram showing the flow of data through two blocks. Block 1: AES_DINR (plaintext P1) is processed by Swap management (controlled by DATATYPE[1:0]) to produce P1'. P1' is XOR-ed with the IVI (from AES_IVRx) to produce I1. I1 is processed by Block cipher encryption (using AES_KEYRx) to produce O1. O1 is processed by Swap management to produce AES_DOUTR (ciphertext C1). Block 2: AES_DINR (plaintext P2) is processed by Swap management to produce P2'. P2' is XOR-ed with O1 to produce I2. I2 is processed by Block cipher encryption to produce O2. O2 is processed by Swap management to produce AES_DOUTR (ciphertext C2). A legend indicates that white boxes are input, grey boxes are output, and a circle with a cross is XOR.](/RM0430-STM32F413-423/e48db73ff288c71367cb9c901a48f657_img.jpg)

In CBC encrypt mode, the first plaintext input block, after bit/byte/half-word swapping (P1'), is XOR-ed with a 128-bit IVI bitfield (initialization vector and counter), producing the I1 input data for encrypt with the AES core, using a 128- or 256-bit key. The resulting 128-bit output block O1, after swapping operation, is used as ciphertext C1. The O1 data is then XOR-ed with the second-block plaintext data P2' to produce the I2 input data for the AES core to produce the second block of ciphertext data. The chaining of data blocks continues in this way until the last plaintext block in the message is encrypted.

If the message size is not a multiple of 128 bits, the final partial data block is encrypted in the way explained in Section 24.4.6: AES ciphertext stealing and data padding .

Figure 238 illustrates the cipher block chaining (CBC) decryption mode.

Figure 238. CBC decryption

![Figure 238. CBC decryption diagram showing the flow of data through two blocks. Block 1: AES_DINR (ciphertext C1) is processed by Swap management (controlled by DATATYPE[1:0]) to produce I1. I1 is processed by Decrypt (using AES_KEYRx) to produce O1. O1 is XOR-ed with the IVI (from AES_IVRx) to produce P1'. P1' is processed by Swap management to produce AES_DOUTR (plaintext P1). Block 2: AES_DINR (ciphertext C2) is processed by Swap management to produce I2. I2 is processed by Decrypt to produce O2. O2 is XOR-ed with O1 to produce P2'. P2' is processed by Swap management to produce AES_DOUTR (plaintext P2). A legend indicates that white boxes are input, grey boxes are output, and a circle with a cross is XOR.](/RM0430-STM32F413-423/5287c0601abe43814411c68da92c467b_img.jpg)

In CBC decrypt mode, like in ECB decrypt mode, the secret key must be prepared to perform an AES decryption.

After the key preparation process, the decryption goes as follows: the first 128-bit ciphertext block (after the swap operation) is used directly as the AES core input block I1 for decrypt operation, using the 128-bit or 256-bit key. Its output O1 is XOR-ed with the 128-bit IVI field (that must be identical to that used during encryption) to produce the first plaintext block P1.

The second ciphertext block is processed in the same way as the first block, except that the I1 data from the first block is used in place of the initialization vector.

The decryption continues in this way until the last complete ciphertext block is decrypted.

If the message size is not a multiple of 128 bits, the final partial data block is decrypted in the way explained in Section 24.4.6: AES ciphertext stealing and data padding .

For more information on data swapping, refer to Section 24.4.13: .AES data registers and data swapping .

ECB/CBC encryption sequence

The sequence of events to perform an ECB/CBC encryption (more detail in Section 24.4.4 ):

- 1. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

- 2. Select the Mode 1 by to 00 the MODE[1:0] bitfield of the AES_CR register and select ECB or CBC chaining mode by setting the CHMOD[2:0] bitfield of the AES_CR register to 000 or 001, respectively. Data type can also be defined, using DATATYPE[1:0] bitfield.

- 3. Select 128- or 256-bit key length through the KEYSIZE bit of the AES_CR register.

- 4. Write the AES_KEYRx registers (128 or 256 bits) with encryption key. Fill the AES_IVRx registers with the initialization vector data if CBC mode has been selected.

- 5. Enable the AES peripheral by setting the EN bit of the AES_CR register.

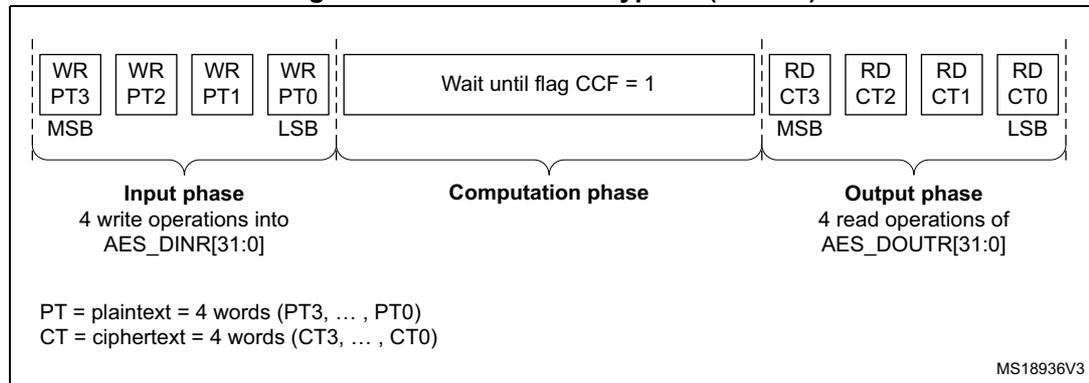

- 6. Write the AES_DINR register four times to input the plaintext (MSB first), as shown in Figure 239 .

- 7. Wait until the CCF flag is set in the AES_SR register.

- 8. Read the AES_DOUTR register four times to get the ciphertext (MSB first) as shown in Figure 239 . Then clear the CCF flag by setting the CCFC bit of the AES_CR register.

- 9. Repeat steps 6,7,8 to process all the blocks with the same encryption key.

Figure 239. ECB/CBC encryption (Mode 1)

The diagram illustrates the sequence of operations for ECB/CBC encryption in Mode 1. It is divided into three main phases:

- Input phase: Four write operations into the AES_DINR register. The data is written in four words (PT3, PT2, PT1, PT0) from MSB to LSB. The label "Input phase" and "4 write operations into AES_DINR[31:0]" is present.

- Computation phase: A period where the user must "Wait until flag CCF = 1".

- Output phase: Four read operations from the AES_DOUTR register. The data is read in four words (CT3, CT2, CT1, CT0) from MSB to LSB. The label "Output phase" and "4 read operations of AES_DOUTR[31:0]" is present.

Legend:

PT = plaintext = 4 words (PT3, ... , PT0)

CT = ciphertext = 4 words (CT3, ... , CT0)

Reference code: MS18936V3

ECB/CBC decryption sequence

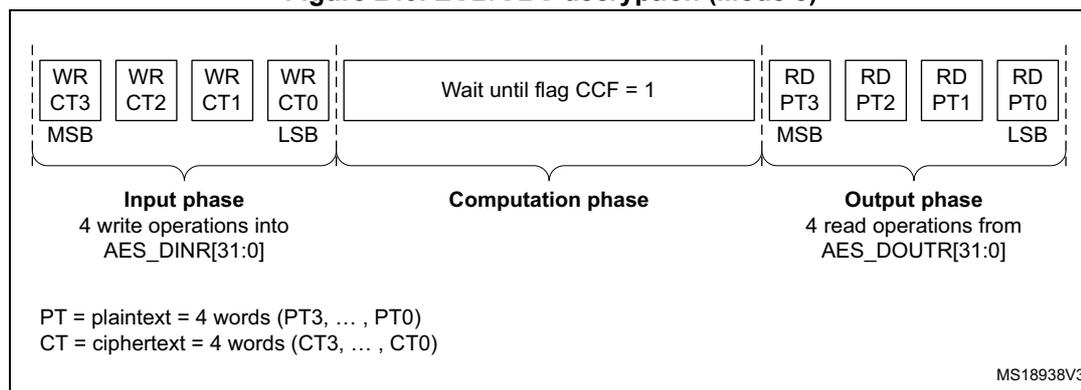

The sequence of events to perform an AES ECB/CBC decryption is as follows (more detail in Section 24.4.4 ):

- 1. Follow the steps described in Section 24.4.5: AES decryption key preparation on page 699 , in order to prepare the decryption key in AES core.

- 2. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

- 3. Select the Mode 3 by setting to 10 the MODE[1:0] bitfield of the AES_CR register and select ECB or CBC chaining mode by setting the CHMOD[2:0] bitfield of the AES_CR register to 000 or 001, respectively. Data type can also be defined, using DATATYPE[1:0] bitfield.

- 4. Select key length of 128 or 256 bits via KEYSIZE bitfield of the AES_CR register.

- 5. Write the AES_IVRx registers with the initialization vector (required in CBC mode only).

- 6. Enable AES by setting the EN bit of the AES_CR register.

- 7. Write the AES_DINR register four times to input the cipher text (MSB first), as shown in Figure 240 .

- 8. Wait until the CCF flag is set in the AES_SR register.

- 9. Read the AES_DOUTR register four times to get the plain text (MSB first), as shown in Figure 240 . Then clear the CCF flag by setting the CCFC bit of the AES_CR register.

- 10. Repeat steps 7,8,9 to process all the blocks encrypted with the same key.

Figure 240. ECB/CBC decryption (Mode 3)

The diagram illustrates the ECB/CBC decryption process in Mode 3, divided into three phases:

- Input phase: 4 write operations into AES_DINR[31:0]. The data is written in four words (CT3, CT2, CT1, CT0) from MSB to LSB.

- Computation phase: Wait until flag CCF = 1.

- Output phase: 4 read operations from AES_DOUTR[31:0]. The data is read in four words (PT3, PT2, PT1, PT0) from MSB to LSB.

Legend:

PT = plaintext = 4 words (PT3, ... , PT0)

CT = ciphertext = 4 words (CT3, ... , CT0)

MS18938V3

Suspend/resume operations in ECB/CBC modes

To suspend the processing of a message, proceed as follows:

- 1. If DMA is used, stop the AES DMA transfers to the IN FIFO by clearing the MAINEN bit of the AES_CR register.

- 2. If DMA is not used, read four times the AES_DOUTR register to save the last processed block. If DMA is used, wait until the CCF flag is set in the AES_SR register.

then stop the DMA transfers from the OUT FIFO by clearing the DMAOUTEN bit of the AES_CR register.

- 3. If DMA is not used, poll the CCF flag of the AES_SR register until it becomes 1 (computation completed).

- 4. Clear the CCF flag by setting the CCFC bit of the AES_CR register.

- 5. Save initialization vector registers (only required in CBC mode as AES_IVRx registers are altered during the data processing).

- 6. Disable the AES peripheral by clearing the bit EN of the AES_CR register.

- 7. Save the current AES configuration in the memory (except AES initialization vector values).

- 8. If DMA is used, save the DMA controller status (pointers for IN and OUT data transfers, number of remaining bytes, and so on).

Note: In point 7, the derived key information stored in AES_KEYRx registers can optionally be saved in memory if the interrupted process is a decryption. Otherwise those registers do not need to be saved as the original key value is known by the application

To resume the processing of a message , proceed as follows:

- 1. If DMA is used, configure the DMA controller so as to complete the rest of the FIFO IN and FIFO OUT transfers.

- 2. Ensure that AES is disabled (the EN bit of the AES_CR must be 0).

- 3. Restore the AES_CR and AES_KEYRx register setting, using the values of the saved configuration. In case of decryption, derived key information can be written in AES_KEYRx register instead of the original key value.

- 4. Prepare the decryption key as described in Section 24.4.5: AES decryption key preparation (only required for ECB or CBC decryption). This step is not necessary if derived key information has been loaded in AES_KEYRx registers.

- 5. Restore AES_IVRx registers using the saved configuration (only required in CBC mode).

- 6. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 7. If DMA is used, enable AES DMA transfers by setting the DMAINEN and DMAOUTEN bits of the AES_CR register.

Alternative single ECB/CBC decryption using Mode 4

The sequence of events to perform a single round of ECB/CBC decryption using Mode 4 is:

- 1. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

- 2. Select the Mode 4 by setting to 11 the MODE[1:0] bitfield of the AES_CR register and select ECB or CBC chaining mode by setting the CHMOD[2:0] bitfield of the AES_CR register to 000 or 001, respectively.

- 3. Select key length of 128 or 256 bits via KEYSIZE bitfield of the AES_CR register.

- 4. Write the AES_KEYRx registers with the encryption key. Write the AES_IVRx registers if the CBC mode is selected.

- 5. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 6. Write the AES_DINR register four times to input the cipher text (MSB first).

- 7. Wait until the CCF flag is set in the AES_SR register.

- 8. Read the AES_DOUTR register four times to get the plain text (MSB first). Then clear the CCF flag by setting the CCFC bit of the AES_CR register.

Note: When mode 4 is selected mode 3 cannot be used.

In mode 4, the AES_KEYRx registers contain the encryption key during all phases of the processing. No derivation key is stored in these registers. It is stored internally in AES.

24.4.9 AES counter (CTR) mode

Overview

The counter mode (CTR) uses AES as a key-stream generator. The generated keys are then XOR-ed with the plaintext to obtain the ciphertext.

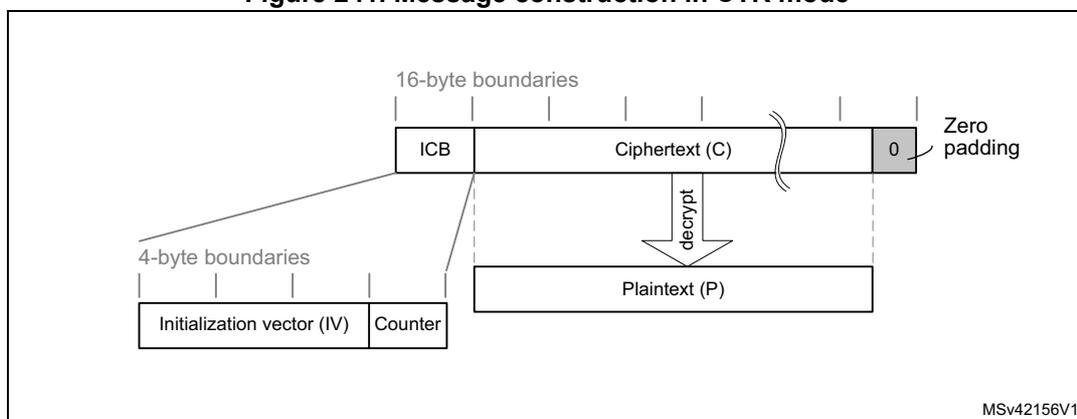

CTR chaining is defined in NIST Special Publication 800-38A, Recommendation for Block Cipher Modes of Operation . A typical message construction in CTR mode is given in Figure 241.

Figure 241. Message construction in CTR mode

The diagram illustrates the message construction in CTR mode. At the top, a horizontal bar represents the message structure. It starts with a 16-byte Initial Counter Block (ICB), which is further divided into a 4-byte Initialization vector (IV) and a 12-byte Counter. This is followed by the Ciphertext (C), which is shown as a series of 16-byte blocks. The last block of ciphertext is followed by a 0, labeled 'Zero padding'. Below the ICB, a box shows the 'Initialization vector (IV)' and 'Counter' fields, with lines connecting them to the ICB. Below the Ciphertext (C), a box shows the 'Plaintext (P)' field, with a 'decrypt' arrow pointing from the ciphertext to the plaintext. Vertical dashed lines indicate '16-byte boundaries' for the ciphertext and '4-byte boundaries' for the IV and Counter. The diagram is labeled 'MSv42156V1' in the bottom right corner.

The structure of this message is:

- • A 16-byte initial counter block (ICB), composed of two distinct fields:

- – Initialization vector (IV) : a 96-bit value that must be unique for each encryption cycle with a given key.

- – Counter : a 32-bit big-endian integer that is incremented each time a block processing is completed. The initial value of the counter should be set to 1.

- • The plaintext P is encrypted as ciphertext C, with a known length. This length can be non-multiple of 16 bytes, in which case a plaintext padding is required.

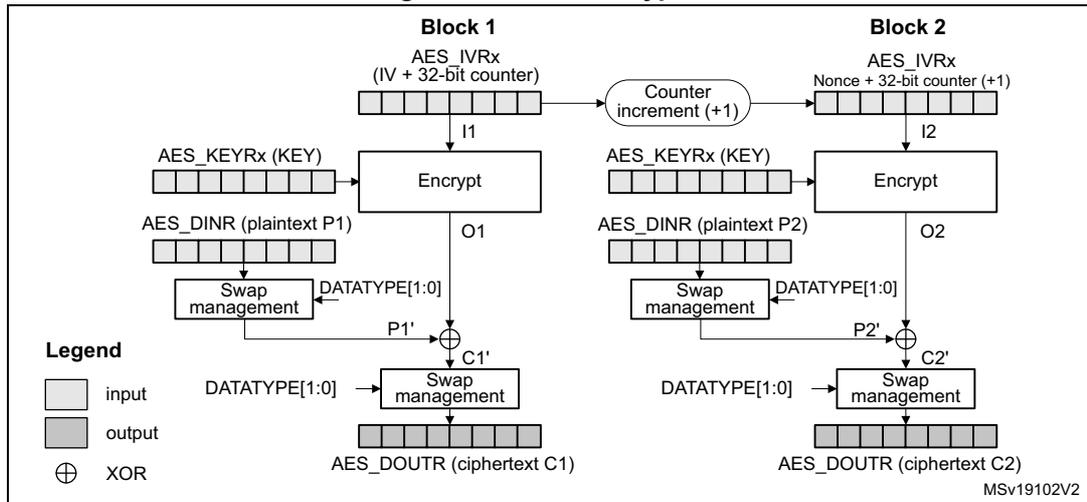

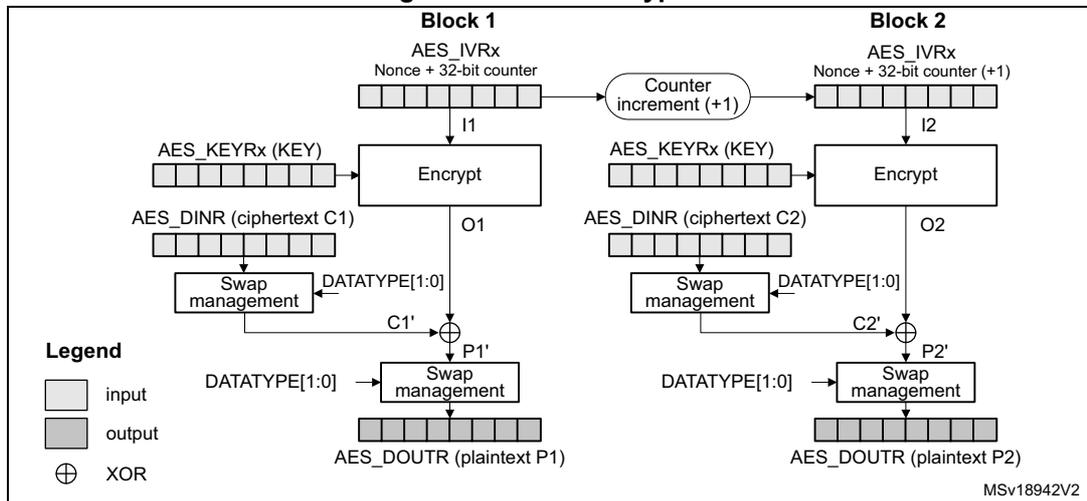

CTR encryption and decryption

Figure 242 and Figure 243 describe the CTR encryption and decryption process, respectively, as implemented in the AES peripheral. The CTR mode is selected by writing 010 to the CHMOD[2:0] bitfield of AES_CR register.

Figure 242. CTR encryption

Figure 243. CTR decryption

In CTR mode, the cryptographic core output (also called keystream) \( O_x \) is XOR-ed with relevant input block ( \( P_x' \) for encryption, \( C_x' \) for decryption), to produce the correct output block ( \( C_x' \) for encryption, \( P_x' \) for decryption). Initialization vectors in AES must be initialized as shown in Table 126.

Table 126. CTR mode initialization vector definition

| AES_IVR3[31:0] | AES_IVR2[31:0] | AES_IVR1[31:0] | AES_IVR0[31:0] |

|---|---|---|---|

| Nonce[31:0] | Nonce[63:32] | Nonce[95:64] | 32-bit counter = 0x0001 |

Unlike in CBC mode that uses the AES_IVRx registers only once when processing the first data block, in CTR mode AES_IVRx registers are used for processing each data block, and the AES peripheral increments the counter bits of the initialization vector (leaving the nonce bits unchanged).

CTR decryption does not differ from CTR encryption, since the core always encrypts the current counter block to produce the key stream that is then XOR-ed with the plaintext (CTR

encryption) or ciphertext (CTR decryption) input. In CTR mode, the MODE[1:0] bitfield settings 11, 10 or 00 default all to encryption mode, and the setting 01 (key derivation) is forbidden.

The sequence of events to perform an encryption or a decryption in CTR chaining mode:

- 1. Ensure that AES is disabled (the EN bit of the AES_CR must be 0).

- 2. Select CTR chaining mode by setting to 010 the CHMOD[2:0] bitfield of the AES_CR register. Set MODE[1:0] bitfield to any value other than 01.

- 3. Initialize the AES_KEYRx registers, and load the AES_IVRx registers as described in Table 126 .

- 4. Set the EN bit of the AES_CR register, to start encrypting the current counter (EN is automatically reset when the calculation finishes).

- 5. If it is the last block, pad the data with zeros to have a complete block, if needed.

- 6. Append data in AES, and read the result. The three possible scenarios are described in Section 24.4.4: AES procedure to perform a cipher operation .

- 7. Repeat the previous step till the second-last block is processed. For the last block, apply the two previous steps and discard the bits that are not part of the payload (if the size of the significant data in the last input block is less than 16 bytes).

Suspend/resume operations in CTR mode

Like for the CBC mode, it is possible to interrupt a message to send a higher priority message, and resume the message that was interrupted. Detailed CBC suspend/resume sequence is described in Section 24.4.8: AES basic chaining modes (ECB, CBC) .

Note: Like for CBC mode, the AES_IVRx registers must be reloaded during the resume operation.

24.4.10 AES Galois/counter mode (GCM)

Overview

The AES Galois/counter mode (GCM) allows encrypting and authenticating a plaintext message into the corresponding ciphertext and tag (also known as message authentication code). To ensure confidentiality, GCM algorithm is based on AES counter mode. It uses a multiplier over a fixed finite field to generate the tag.

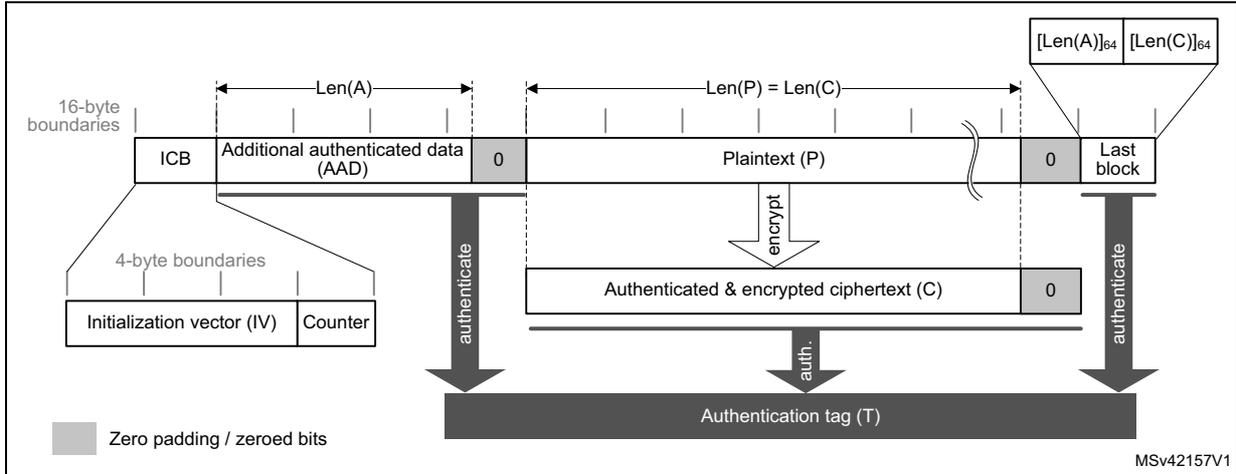

GCM chaining is defined in NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation - Galois/Counter Mode (GCM) and GMAC . A typical message construction in GCM mode is given in Figure 244 .

Figure 244. Message construction in GCM

The diagram illustrates the message construction in GCM. It shows the flow from the Initialization vector (IV) and Counter to the Initial Counter Block (ICB), then through Additional Authenticated Data (AAD) and Plaintext (P) to generate the Authenticated & encrypted ciphertext (C), and finally the Authentication tag (T). The ICB is composed of a 96-bit IV and a 32-bit Counter. The AAD and Plaintext are processed to generate the ciphertext and the authentication tag. The last block contains the AAD header length and the payload length. Zero padding / zeroed bits are indicated by grey boxes.

The message has the following structure:

- •

16-byte initial counter block (ICB)

, composed of two distinct fields:

- – Initialization vector (IV) : a 96-bit value that must be unique for each encryption cycle with a given key. Note that the GCM standard supports IVs with less than 96 bits, but in this case strict rules apply.

- – Counter : a 32-bit big-endian integer that is incremented each time a block processing is completed. According to NIST specification, the counter value is 0x2 when processing the first block of payload.

- • Authenticated header AAD (also known as additional authentication data) has a known length \( Len(A) \) that may be a non-multiple of 16 bytes, and must not exceed \( 2^{64} - 1 \) bits. This part of the message is only authenticated, not encrypted.

- • Plaintext message P is both authenticated and encrypted as ciphertext C, with a known length \( Len(P) \) that may be non-multiple of 16 bytes, and cannot exceed \( 2^{32} - 2 \) 128-bit blocks.

- • Last block contains the AAD header length (bits [32:63]) and the payload length (bits [96:127]) information, as shown in Table 127 .

The GCM standard specifies that ciphertext C has the same bit length as the plaintext P.

When a part of the message (AAD or P) has a length that is a non-multiple of 16-bytes a special padding scheme is required.

Table 127. GCM last block definition

| Endianness | Bit[0] ----- Bit[31] | Bit[32]----- Bit[63] | Bit[64] ----- Bit[95] | Bit[96] ----- Bit[127] |

|---|---|---|---|---|

| Input data | 0x0 | AAD length[31:0] | 0x0 | Payload length[31:0] |

GCM processing

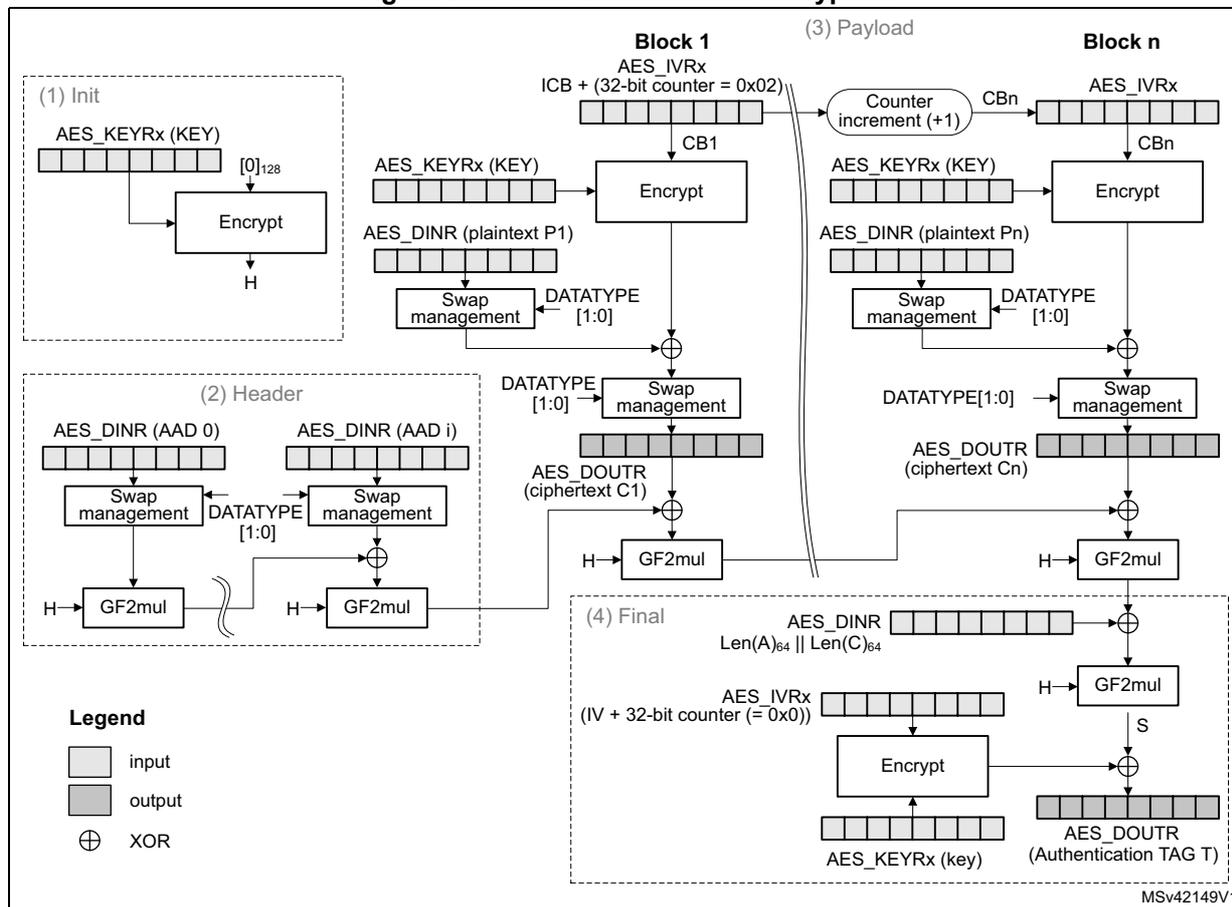

Figure 245 describes the GCM implementation in the AES peripheral. The GCM is selected by writing 011 to the CHMOD[2:0] bitfield of the AES_CR register.

Figure 245. GCM authenticated encryption

The mechanism for the confidentiality of the plaintext in GCM mode is similar to that in the Counter mode, with a particular increment function (denoted 32-bit increment) that generates the sequence of input counter blocks.

AES_IVRx registers keeping the counter block of data are used for processing each data block. The AES peripheral automatically increments the Counter[31:0] bitfield. The first counter block (CB1) is derived from the initial counter block ICB by the application software (see Table 128).

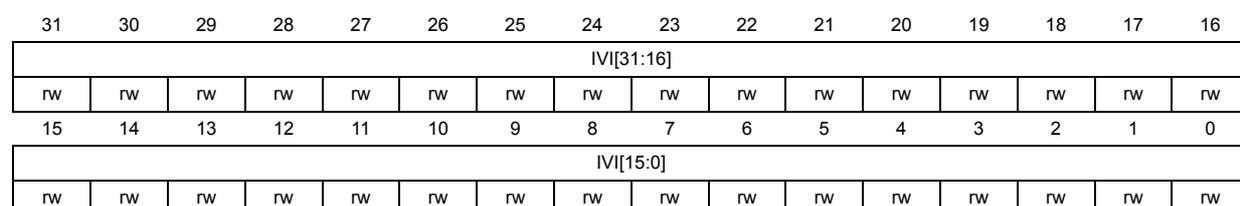

Table 128. GCM mode IVI bitfield initialization

| Register | AES_IVR3[31:0] | AES_IVR2[31:0] | AES_IVR1[31:0] | AES_IVR0[31:0] |

|---|---|---|---|---|

| Input data | ICB[31:0] | ICB[63:32] | ICB[95:64] | Counter[31:0] = 0x2 |

Note: In GCM mode, the settings 01 and 11 of the MODE[1:0] bitfield are forbidden.

The authentication mechanism in GCM mode is based on a hash function called GF2mul that performs multiplication by a fixed parameter, called hash subkey (H), within a binary Galois field.

A GCM message is processed through the following phases, further described in next subsections:

- • Init phase: AES prepares the GCM hash subkey (H).

- • Header phase: AES processes the additional authenticated data (AAD), with hash computation only.

- • Payload phase: AES processes the plaintext (P) with hash computation, counter block encryption and data XOR-ing. It operates in a similar way for ciphertext (C).

- • Final phase: AES generates the authenticated tag (T) using the last block of the message.

GCM init phase

During this first step, the GCM hash subkey (H) is calculated and saved internally, to be used for processing all the blocks. The recommended sequence is:

- 1. Ensure that AES is disabled (the EN bit of the AES_CR must be 0).

- 2. Select GCM chaining mode, by setting to 011 the CHMOD[2:0] bitfield of the AES_CR register, and set to 00 (no data swapping) the DATATYPE[1:0] bitfield.

- 3. Indicate the Init phase, by setting to 00 the GCMPH[1:0] bitfield of the AES_CR register.

- 4. Set the MODE[1:0] bitfield of the AES_CR register to 00 or 10.

- 5. Initialize the AES_KEYRx registers with a key, and initialize AES_IVRx registers with the information as defined in Table 128 .

- 6. Start the calculation of the hash key, by setting to 1 the EN bit of the AES_CR register (EN is automatically reset when the calculation finishes).

- 7. Wait until the end of computation, indicated by the CCF flag of the AES_SR transiting to 1. Alternatively, use the corresponding interrupt.

- 8. Clear the CCF flag of the AES_SR register, by setting to 1 the CCFC bit of the AES_CR register, and optionally set the data type (1-, 8- or 16-bit) using the DATATYPE[1:0] bitfield.

GCM header phase

This phase coming after the GCM Init phase must be completed before the payload phase. The sequence to execute, identical for encryption and decryption, is:

- 1. Indicate the header phase, by setting to 01 the GCMPH[1:0] bitfield of the AES_CR register. Do not modify the MODE[1:0] bitfield as set in the Init phase.

- 2. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 3. If it is the last block and the AAD size in the block is inferior to 128 bits, pad the remainder of the block with zeros. Then append the data block into AES in one of ways described in Section 24.4.4: AES procedure to perform a cipher operation on page 695 .

- 4. Repeat the step 3 until the last additional authenticated data block is processed.

Note: The header phase can be skipped if there is no AAD, that is, Len(A) = 0.

GCM payload phase

This phase, identical for encryption and decryption, is executed after the GCM header phase. During this phase, the encrypted/decrypted payload is stored in the AES_DOUTR register. The sequence to execute is:

- 1. If the header phase was skipped, enable the AES peripheral by setting the EN bit of the AES_CR register.

- 2. Indicate the payload phase, by setting to 10 the GCMPH[1:0] bitfield of the AES_CR register. Do not modify the MODE[1:0] bitfield as set in the Init phase.

- 3. If it is the last block and the plaintext (encryption) or ciphertext (decryption) size in the block is inferior to 128 bits, pad the remainder of the block with zeros.

- 4. Append the data block into AES in one of ways described in Section 24.4.4: AES procedure to perform a cipher operation on page 695 , and read the result.

- 5. Repeat the previous step till the second-last plaintext block is encrypted or till the last block of ciphertext is decrypted. For the last block of plaintext (encryption only), execute the two previous steps. For the last block, discard the bits that are not part of the payload when the last block size is less than 16 bytes.

Note: The payload phase can be skipped if there is no payload data, that is, Len(C) = 0 (see GMAC mode).

GCM final phase

In this last phase, the AES peripheral generates the GCM authentication tag and stores it in the AES_DOUTR register. The sequence to execute is:

- 1. Indicate the final phase, by setting to 11 the GCMPH[1:0] bitfield of the AES_CR register. Select encrypt mode by setting to 00 the MODE[1:0] bitfield of the AES_CR register.

- 2. Compose the data of the block, by concatenating the AAD bit length and the payload bit length, as shown in Table 127 . Write the block into the AES_DINR register.

- 3. Wait until the end of computation, indicated by the CCF flag of the AES_SR transiting to 1.

- 4. Get the GCM authentication tag, by reading the AES_DOUTR register four times.

- 5. Clear the CCF flag in the AES_SR register, by setting to 1 the CCFC bit of the AES_CR register.

- 6. Disable the AES peripheral, by clearing the bit EN of the AES_CR register. If it is an authenticated decryption, compare the generated tag with the expected tag passed with the message.

Note: In the final phase, data must be swapped according to the data type set in the DATATYPE[1:0] bitfield of the AES_CR register.

When transiting from the header or the payload phase to the final phase, the AES peripheral must not be disabled, otherwise the result is wrong.

Suspend/resume operations in GCM mode

To suspend the processing of a message, proceed as follows:

- 1. If DMA is used, stop the AES DMA transfers to the IN FIFO by clearing the DMAINEN bit of the AES_CR register. If DMA is not used, make sure that the current computation is completed, which is indicated by the CCF flag of the AES_SR register set to 1.

- 2. In the payload phase, if DMA is not used, read four times the AES_DOUTR register to save the last-processed block. If DMA is used, wait until the CCF flag is set in the AES_SR register then stop the DMA transfers from the OUT FIFO by clearing the DMAOUTEN bit of the AES_CR register.

- 3. Clear the CCF flag of the AES_SR register, by setting to 1 the CCFC bit of the AES_CR register. In the payload phase (encryption mode only), verify that the BUSY flag of the AES_SR register is cleared, to ensure that GF2mul hash function is completed.

- 4. Save the AES_SUSPxR registers in the memory, where x is from 0 to 7.

- 5. In the payload phase, save the AES_IVRx registers as, during the data processing, they changed from their initial values. In the header phase, this step is not required.

- 6. Disable the AES peripheral, by clearing the EN bit of the AES_CR register.

- 7. Save the current AES configuration in the memory, excluding the initialization vector registers AES_IVRx. Key registers do not need to be saved as the original key value is known by the application.

- 8. If DMA is used, save the DMA controller status (pointers for IN data transfers, number of remaining bytes, and so on). In the payload phase, pointers for OUT data transfers must also be saved.

To resume the processing of a message, proceed as follows:

- 1. If DMA is used, configure the DMA controller in order to complete the rest of the FIFO IN transfers. In the payload phase, the rest of the FIFO OUT transfers must also be configured in the DMA controller.

- 2. Ensure that the AES peripheral is disabled (the EN bit of the AES_CR register must be 0).

- 3. Write the suspend register values, previously saved in the memory, back into their corresponding AES_SUSPxR registers, where x is from 0 to 7.

- 4. In the payload phase, write the initialization vector register values, previously saved in the memory, back into their corresponding AES_IVRx registers. In the header phase, write initial setting values back into the AES_IVRx registers.

- 5. Restore the initial setting values in the AES_CR and AES_KEYRx registers.

- 6. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 7. If DMA is used, enable AES DMA requests by setting the DMAINEN bit (and DMAOUTEN bit if in payload phase) of the AES_CR register.

24.4.11 AES Galois message authentication code (GMAC)

Overview

The Galois message authentication code (GMAC) allows the authentication of a plaintext, generating the corresponding tag information (also known as message authentication code). It is based on GCM algorithm, as defined in NIST Special Publication 800-38D, Recommendation for Block Cipher Modes of Operation - Galois/Counter Mode (GCM) and GMAC .

A typical message construction for GMAC is given in Figure 246.

Figure 246. Message construction in GMAC mode

![Figure 246: Message construction in GMAC mode. The diagram shows a message structure with 16-byte boundaries. It starts with an ICB (Initialization Counter Block) which is split into an Initialization vector (IV) and a Counter, each with 4-byte boundaries. This is followed by 'Authenticated data' of length Len(A). The last block contains zero padding (indicated by a grey box and '0') and a 'Last block' indicator. Above the last block, there are two fields: [Len(A)]64 and [0]64. An arrow labeled 'auth.' points from the authenticated data to an 'Authentication tag (T)'.](/RM0430-STM32F413-423/cfb3ce1876741e50ca2c1df335a17bfc_img.jpg)

AES GMAC processing

Figure 247 describes the GMAC mode implementation in the AES peripheral. This mode is selected by writing 011 to the CHMOD[2:0] bitfield of the AES_CR register.

Figure 247. GMAC authentication mode

![Figure 247: GMAC authentication mode. The diagram is divided into four phases: (1) Init, (2) Header, (3) Payload (omitted), and (4) Final. Phase (1) shows the initialization where AES_KEYRx (KEY) and [0]128 are input to an Encrypt block, producing H. Phase (2) shows the header processing where AES_DINR (message block 1 to n) are processed through Swap management (controlled by DATATYPE [1:0]) and GF2mul blocks, XORed with H, and then XORed together. Phase (4) shows the final step where AES_KEYRx (KEY) and IV + 32-bit counter (= 0x0) are input to an Encrypt block, producing S. The final authentication tag T is obtained by XORing S with the output of a GF2mul block that takes len(A)64 || len(C)64 and H as inputs. A legend indicates that white boxes are input, grey boxes are output, and circles with plus signs are XOR operations.](/RM0430-STM32F413-423/009bd9eab25edaa72970a496fba6c755_img.jpg)

The GMAC algorithm corresponds to the GCM algorithm applied on a message only containing a header. As a consequence, all steps and settings are the same as with the GCM, except that the payload phase is omitted.

Suspend/resume operations in GMAC

In GMAC mode, the sequence described for the GCM applies except that only the header phase can be interrupted.

24.4.12 AES counter with CBC-MAC (CCM)

Overview

The AES counter with cipher block chaining-message authentication code (CCM) algorithm allows encryption and authentication of plaintext, generating the corresponding ciphertext and tag (also known as message authentication code). To ensure confidentiality, the CCM algorithm is based on AES in counter mode. It uses cipher block chaining technique to generate the message authentication code. This is commonly called CBC-MAC.

Note: NIST does not approve this CBC-MAC as an authentication mode outside the context of the CCM specification.

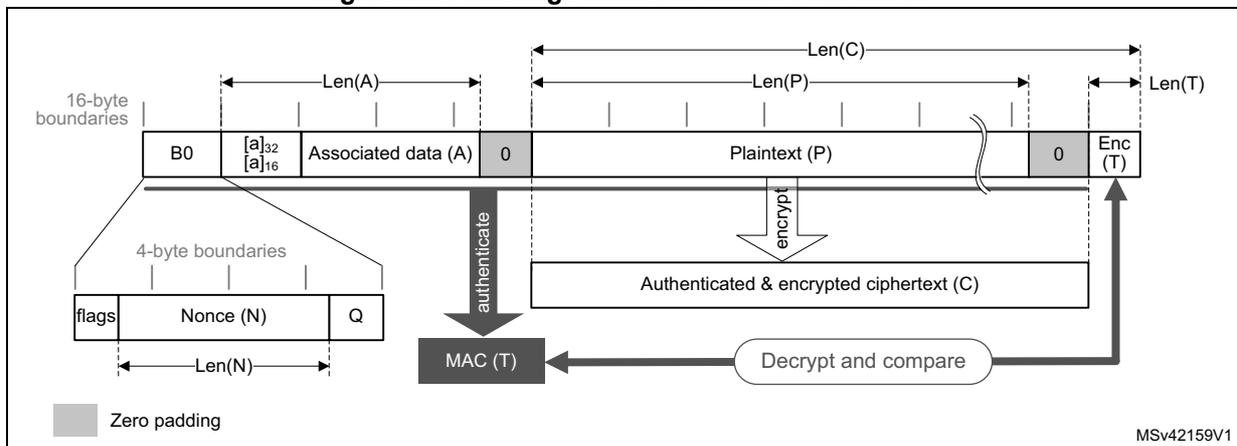

CCM chaining is specified in NIST Special Publication 800-38C, Recommendation for Block Cipher Modes of Operation - The CCM Mode for Authentication and Confidentiality . A typical message construction for CCM is given in Figure 248 .

Figure 248. Message construction in CCM mode

The diagram illustrates the message construction in CCM mode. It shows a sequence of blocks aligned to 16-byte boundaries. The sequence starts with

B0

, followed by

Associated data (A)

of length Len(A), and then

Plaintext (P)

of length Len(P).

-

B0

is detailed as having 4-byte boundaries containing

flags

,

Nonce (N)

of length Len(N), and

Q

.

-

Associated data (A)

is preceded by length encoding [a]

32

or [a]

16

and followed by zero padding to a 16-byte boundary.

-

Plaintext (P)

is followed by zero padding to a 16-byte boundary.

- The

authenticate

process takes B0 and A to produce

MAC (T)

of length Len(T).

- The

encrypt

process transforms P into

Authenticated & encrypted ciphertext (C)

of length Len(C).

- The final output is the concatenation of C and the encrypted MAC (Enc(T)).

- A

Decrypt and compare

path is shown returning from the final output to verify the MAC (T).

The structure of the message is:

- •

16-byte first authentication block (B0)

, composed of three distinct fields:

- – Q : a bit string representation of the octet length of P (Len(P))

- – Nonce (N) : a single-use value (that is, a new nonce should be assigned to each new communication) of Len(N) size. The sum Len(N) + Len(P) must be equal to 15 bytes.

- – Flags : most significant octet containing four flags for control information, as specified by the standard. It contains two 3-bit strings to encode the values t (MAC length expressed in bytes) and Q (plaintext length such that \( \text{Len}(P) < 2^{8Q} \) bytes). The counter blocks range associated to Q is equal to \( 2^{8Q-4} \) , that is, if the maximum value of Q is 8, the counter blocks used in cipher shall be on 60 bits.

- • 16-byte blocks (B) associated to the Associated Data (A). This part of the message is only authenticated, not encrypted. This section has a known length Len(A) that can be a non-multiple of 16 bytes (see Figure 248 ). The

standard also states that, on MSB bits of the first message block (B1), the associated data length expressed in bytes (a) must be encoded as follows:

- – If \( 0 < a < 2^{16} - 2^8 \) , then it is encoded as \( [a]_{16} \) , that is, on two bytes.

- – If \( 2^{16} - 2^8 < a < 2^{32} \) , then it is encoded as \( 0xff \parallel 0xfe \parallel [a]_{32} \) , that is, on six bytes.

- – If \( 2^{32} < a < 2^{64} \) , then it is encoded as \( 0xff \parallel 0xff \parallel [a]_{64} \) , that is, on ten bytes.

- • 16-byte blocks (B) associated to the plaintext message P, which is both authenticated and encrypted as ciphertext C, with a known length Len(P). This length can be a non-multiple of 16 bytes (see Figure 248 ).

- • Encrypted MAC (T) of length Len(T) appended to the ciphertext C of overall length Len(C).

When a part of the message (A or P) has a length that is a non-multiple of 16-bytes, a special padding scheme is required.

Note: CCM chaining mode can also be used with associated data only (that is, no payload).

As an example, the C.1 section in NIST Special Publication 800-38C gives the following values (hexadecimal numbers):

N: 10111213 141516 (Len(N)= 56 bits or 7 bytes)

A: 00010203 04050607 (Len(A)= 64 bits or 8 bytes)

P:

20212223

(Len(P)= 32 bits or 4 bytes)

T: 6084341B (Len(T)= 32 bits or t = 4)

B0: 4F101112 13141516 00000000 00000004

B1:

00080001 02030405 06070000 00000000

B2:

20212223

00000000 00000000 00000000

CTR0: 0710111213 141516 00000000 00000000

CTR1: 0710111213 141516 00000000 00000001

Generation of formatted input data blocks B x (especially B0 and B1) must be managed by the application.

CCM processing

Figure 249 describes the CCM implementation within the AES peripheral (decryption example).

Figure 249. CCM mode authenticated decryption

The data input to the generation-encryption process are a valid nonce, a valid payload string, and a valid associated data string, all properly formatted. The CBC chaining mechanism is applied to the formatted plaintext data to generate a MAC, with a known length. Counter mode encryption that requires a sufficiently long sequence of counter blocks as input, is applied to the payload string and separately to the MAC. The resulting ciphertext C is the output of the generation-encryption process on plaintext P.

AES_IVRx registers are used for processing each data block, AES automatically incrementing the CTR counter with a bit length defined by the first block B0. Table 129 shows how the application must load the B0 data.

Table 129. Initialization of AES_IVRx registers in CCM mode

| Register | AES_IVR3[31:0] | AES_IVR2[31:0] | AES_IVR1[31:0] | AES_IVR0[31:0] |

|---|---|---|---|---|

| Input data | B0[31:0] | B0[63:32] | B0[95:64] | B0[127:96] |

A CCM message is processed through two distinct processes - first, payload encryption or decryption , in which the AES peripheral is configured in CTR mode, then associated data and payload authentication , in which the AES peripheral first executes the CCM header phase, then the CCM final phase.

Payload encryption/decryption

This step is performed independently of the tag computation. It uses standard CTR chaining mode. Refer to Section 24.4.9: AES counter (CTR) mode for details. The construction of the CTR1 initialization vector (see Figure 249 ) to load into AES_IVRx registers is defined in NIST Special Publication 800-38C.

Note: This phase can be skipped if there is no payload data, that is, when \( Len(P) = 0 \) or \( Len(C) = Len(T) \) .

Remove \( LSB_{Len(T)}(C) \) encrypted tag information when decrypting ciphertext C.

Associated data and payload authentication

In order to compute the CCM authentication tag associated with the plaintext message, it is recommended to execute the following header phase sequence:

- 1. Ensure that the AES peripheral is disabled (the EN bit of the AES_CR must be 0).

- 2. Select CCM chaining mode, by setting to 100 the CHMOD[2:0] bitfield of the AES_CR register, and optionally, set the DATATYPE[1:0] bitfield.

- 3. Indicate the header phase, by setting to 01 the GCMPH[1:0] bitfield of the AES_CR register. Select encrypt mode by setting to 00 the MODE[1:0] bitfield of the AES_CR register.

- 4. Initialize the AES_KEYRx registers with a key, and initialize AES_IVRx registers with zero values.

- 5. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 6. Write the AES_DINR register with B0, as shown in Table 129 . B0 data must be swapped according to the DATATYPE[1:0] bitfield of the AES_CR register.

- 7. Wait until the end-of-computation flag CCF of the AES_SR register is set to 1.

- 8. Clear the CCF flag of the AES_SR register by setting the CCFC bit of the AES_CR register.

- 9. Process data block. If it is the last block of associated data or plaintext and data size in the block is inferior to 128 bits, pad the remainder of the block with zeros. Then append the data block into AES in one of ways described in Section 24.4.4: AES procedure to perform a cipher operation on page 695 .

- 10. Repeat the previous step to process all data blocks, starting from the first block of associated data and ending with the last block of plaintext payload data.

In final phase, the AES peripheral generates the CCM authentication tag and stores it in the AES_DOUTR register:

- 11. Indicate the final phase, by setting to 11 the GCMPH[1:0] bitfield of the AES_CR register. Keep as-is the encryption mode in the MODE[1:0] bitfield.

- 12. Write four times the last data input into the AES_DIN register. This input must be the 128-bit value CTR0, formatted from the original B0 packet (that is, 5 flag bits set to 0, and Q length bits set to 0).

- 13. Wait until the end-of-computation flag CCF of the AES_SR register is set.

- 14. Read four times the AES_DOUTR register: the output corresponds to the encrypted CCM authentication tag.

- 15. Clear the CCF flag of the AES_SR register by setting the CCFC bit of the AES_CR register.

- 16. Disable the AES peripheral, by clearing the EN bit of the AES_CR register.

- 17. For authenticated decryption, compare the generated encrypted tag with the encrypted tag padded in the ciphertext.

Note: In this final phase, data must be swapped according to the DATATYPE[1:0] bitfield of the AES_CR register.

When transiting from the header phase to the final phase, the AES peripheral must not be disabled, otherwise the result is wrong.

Application must mask the authentication tag output with tag length to obtain a valid tag.

Suspend/resume operations in CCM mode

To suspend the authentication of the associated data and payload (GCMPH[1:0]= 01), proceed as follows. Suspending the message during the encryption/decryption phase is described in Section 24.4.9: AES counter (CTR) mode on page 707 .

- 1. If DMA is used, stop the AES DMA transfers to the IN FIFO by clearing the DMAINEN bit of the AES_CR register. If DMA is not used, make sure that the current computation is completed, which is indicated by the CCF flag of the AES_SR register set to 1.

- 2. Clear the CCF flag of the AES_SR register, by setting to 1 the CCFC bit of the AES_CR register.

- 3. Save the AES_SUSPxR registers (where x is from 0 to 7) in the memory.

- 4. Save the AES_IVRx registers, as during the data processing they changed from their initial values.

- 5. Disable the AES peripheral, by clearing the bit EN of the AES_CR register.

- 6. Save the current AES configuration in the memory, excluding the initialization vector registers AES_IVRx. Key registers do not need to be saved as the original key value is known by the application.

- 7. If DMA is used, save the DMA controller status (pointers for IN data transfers, number of remaining bytes, and so on).

To resume the authentication of the associated data and payload (GCM PH [1:0]= 01 or 11), proceed as follows:

- 1. If DMA is used, configure the DMA controller in order to complete the rest of the FIFO IN transfers.

- 2. Ensure that AES processor is disabled (the EN bit of the AES_CR register must be 0).

- 3. Write the suspend register values, previously saved in the memory, back into their corresponding AES_SUSPxR registers (where x is from 0 to 7).

- 4. Write the initialization vector register values, previously saved in the memory, back into their corresponding AES_IVRx registers.

- 5. Restore the initial setting values in the AES_CR and AES_KEYRx registers.

- 6. Enable the AES peripheral by setting the EN bit of the AES_CR register.

- 7. If DMA is used, enable AES DMA requests by setting the DMAINEN bit of the AES_CR register.

Note: In CCM mode the MODE[1:0] bitfield settings 01 and 11 (key derivation) are forbidden.

24.4.13 .AES data registers and data swapping

Data input and output

A 128-bit data block is entered into the AES peripheral with four successive 32-bit word writes into the AES_DINR register (bitfield DIN[127:0]), the most significant word (bits [127:96]) first, the least significant word (bits [31:0]) last.

A 128-bit data block is retrieved from the AES peripheral with four successive 32-bit word reads from the AES_DOUTR register (bitfield DOUT[127:0]), the most significant word (bits [127:96]) first, the least significant word (bits [31:0]) last.

The 32-bit data word for AES_DINR register or from AES_DOUTR register is organized in big endian order, that is:

- • the most significant byte of a word to write into AES_DINR must be put on the lowest address out of the four adjacent memory locations keeping the word to write, or

- • the most significant byte of a word read from AES_DOUTR goes to the lowest address out of the four adjacent memory locations receiving the word

For using DMA for input data block write into AES, the four words of the input block must be stored in the memory consecutively and in big-endian order, that is, the most significant word on the lowest address. See Section 24.4.16: AES DMA interface .

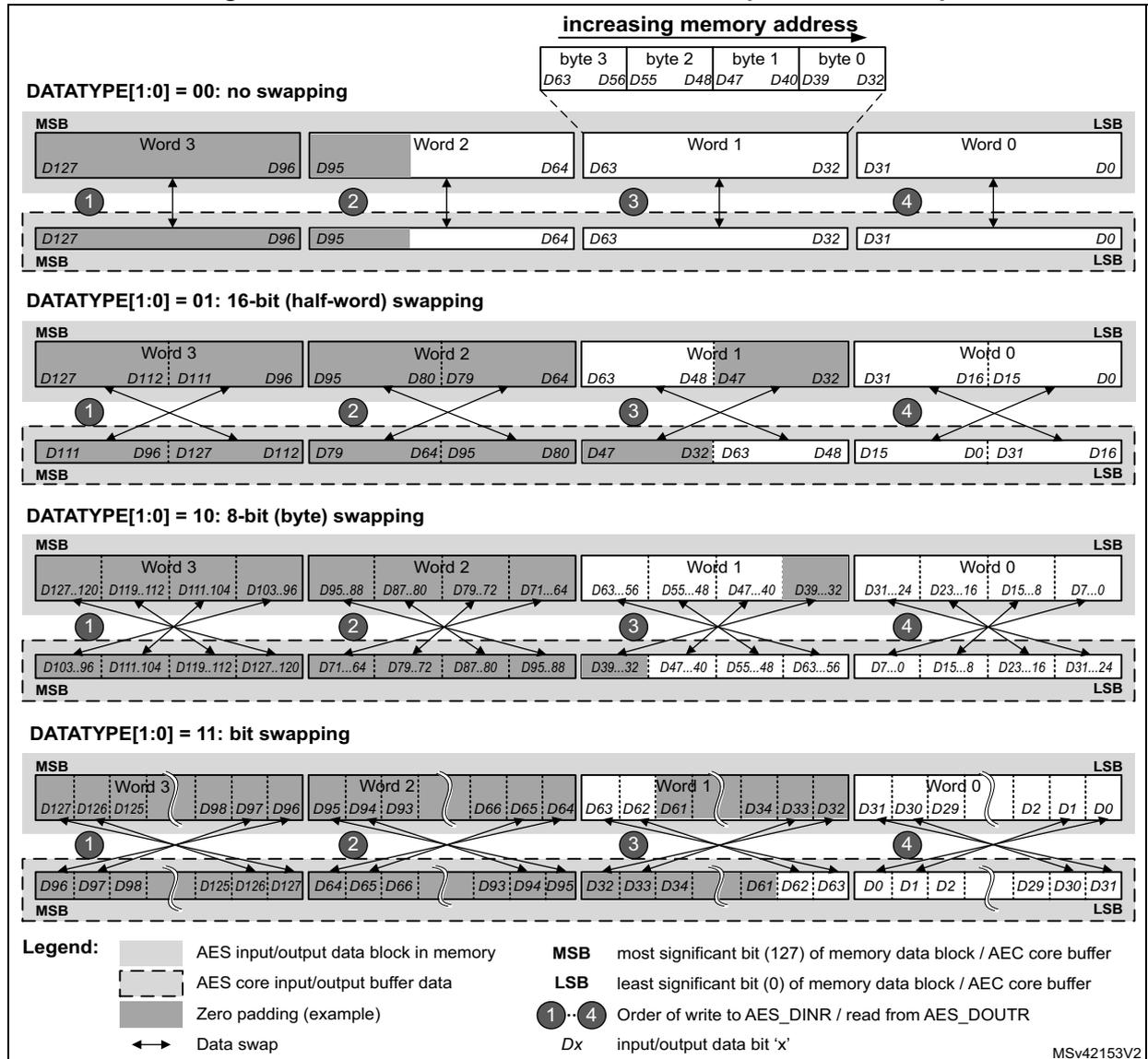

Data swapping

The AES peripheral can be configured to perform a bit-, a byte-, a half-word-, or no swapping on the input data word in the AES_DINR register, before loading it to the AES processing core, and on the data output from the AES processing core, before sending it to the AES_DOUTR register. The choice depends on the type of data. For example, a byte swapping is used for an ASCII text stream.

The data swap type is selected through the DATATYPE[1:0] bitfield of the AES_CR register. The selection applies both to the input and the output of the AES core.