45. Device electronic signature

The electronic signature is stored in the Flash memory area. It can be read using the JTAG/SWD or the CPU. It contains factory-programmed identification data that allow the user firmware or other external devices to automatically match its interface to the characteristics of the STM32F76xxx and STM32F77xxx microcontrollers.

45.1 Unique device ID register (96 bits)

The unique device identifier is ideally suited:

- • for use as serial numbers (for example USB string serial numbers or other end applications)

- • for use as security keys in order to increase the security of code in Flash memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal Flash memory

- • to activate secure boot processes, etc.

The 96-bit unique device identifier provides a reference number which is unique for any device and in any context. These bits can never be altered by the user.

The 96-bit unique device identifier can also be read in single bytes/half-words/words in different ways and then be concatenated using a custom algorithm.

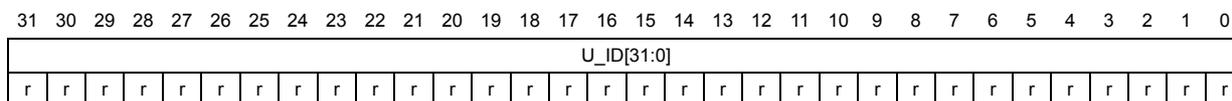

Base address: 0x1FF0 F420

Address offset: 0x00

Read only = 0xXXXX XXXX where X is factory-programmed

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| U_ID[31:0] | ||||||||||||||||||||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 U_ID[31:0] : 31:0 unique ID bits

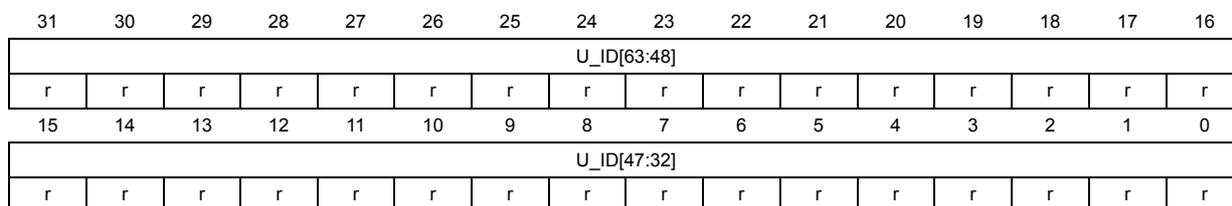

Address offset: 0x04

Read only = 0xXXXX XXXX where X is factory-programmed

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| U_ID[63:48] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| U_ID[47:32] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 U_ID[63:32] : 63:32 unique ID bits

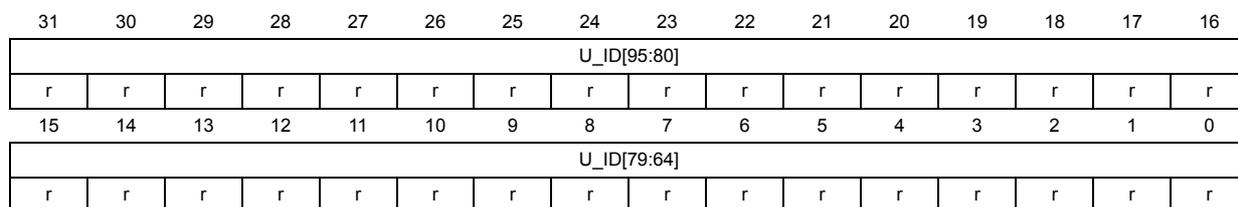

Address offset: 0x08

Read only = 0xXXXX XXXX where X is factory-programmed

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| U_ID[95:80] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| U_ID[79:64] | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 31:0 U_ID[95:64] : 95:64 Unique ID bits.

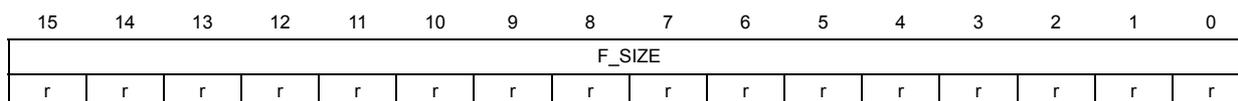

45.2 Flash size

Base address: 0x1FF0 F442

Address offset: 0x00

Read only = 0xXXXX where X is factory-programmed

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| F_SIZE | |||||||||||||||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Bits 15:0 F_ID[15:0] : Flash memory size

This bitfield indicates the size of the device Flash memory expressed in Kbytes.

As an example, 0x0800 corresponds to 2048 Kbytes.

45.3 Package data register

Base address: 0x1FF0 F7E0

Address offset: 0x00

Read only = 0xXXXX where X is factory-programmed

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | PKG[2:0] | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ||

| rw | rw | rw | |||||||||||||

Bits 15:11 Reserved, must be kept at reset value.

Bits 10:8 PKG[2:0] : Package type

- 0x111: STM32F767 and STM32F777 LQFP208 and TFBGA216 package

- 0x110: STM32F769 and STM32F779 LQFP208 and TFBGA216 package

- 0x101: STM32F767 and STM32F777 LQFP176 package

- 0x100: STM32F769 and STM32F779 LQFP176 package

- 0x011: WLCSP180 package

- 0x010: LQFP144 package

- 0x001: LQFP100 package

- 0x000: Reserved

Bits 7:0 Reserved, must be kept at reset value.