34. DSI Host (DSI)

34.1 Introduction

Portions Copyright (c) Synopsys, Inc. All rights reserved. Used with permission.

The display serial interface (DSI) is part of a group of communication protocols defined by the MIPI® Alliance.

The MIPI® DSI Host controller is a digital core that implements all protocol functions defined in the MIPI® DSI specification. It provides an interface between the system and the MIPI® D-PHY, allowing the user to communicate with a DSI-compliant display.

34.2 Standard and references

- • MIPI® Alliance Specification for Display Serial interface (DSI)

v1.1 - 22 November 2011 - • MIPI® Alliance Specification for Display Bus interface (DBI-2)

v2.00 - 16 November 2005 - • MIPI® Alliance Specification for Display Command set (DCS)

v1.1 - 22 November 2011 - • MIPI® Alliance Specification for Display Pixel interface (DPI-2)

v2.00 - 15 September 2005 - • MIPI® Alliance Specification for Stereoscopic Display Formats (SDF)

v1.0 - 22 November 2011 - • MIPI® Alliance Specification for D-PHY

v1.1 - 7 November 2011

34.3 DSI Host main features

- • Compliant with MIPI ® Alliance standards (see Section 34.2: Standard and references )

- • Interface with MIPI ® D-PHY

- • Supports all commands defined in the MIPI

®

Alliance specification for DCS:

- – Transmission of all command mode packets through the APB interface

- – Transmission of commands in low-power and high-speed during video mode

- • Supports up to two D-PHY data lanes

- • Bidirectional communication and escape mode support through data lane 0

- • Supports non continuous clock in D-PHY clock lane for additional power saving

- • Supports ultra low-power mode with PLL disabled

- • ECC and checksum capabilities

- • Support for end of transmission packet (EoTp)

- • Fault recovery schemes

- • Configurable selection of system interfaces:

- – AMBA APB for control and optional support for generic and DCS commands

- – Video mode interface through LTDC

- – Adapted command mode interface through LTDC

- – Independently programmable virtual channel ID in video mode, adapted command mode, and APB slave

- • Video mode interfaces features:

- – LTDC interface color coding mappings into 24-bit interface:

- • 16-bit RGB, configurations 1, 2, and 3

- • 18-bit RGB, configurations 1 and 2

- • 24-bit RGB

- – Programmable polarity of all LTDC interface signals

- – Extended resolutions beyond the DPI standard maximum resolution of 800x480 pixels

- – Maximum resolution is limited by available DSI physical link bandwidth:

- • Number of lanes: 2

- • Maximum speed per lane: 1 Gbit/s

- • See examples in Section 34.4.3: Supported resolutions and frame rates

- – LTDC interface color coding mappings into 24-bit interface:

- • Adapted interface features:

- – Support for sending large amounts of data through the memory_write_start (WMS) and memory_write_continue (WMC) DCS commands

- – LTDC interface color coding mappings into 24-bit interface:

- • 16-bit RGB, configurations 1, 2, and 3

- • 18-bit RGB, configurations 1 and 2

- • 24-bit RGB

- • Video mode pattern generator:

- – Vertical and horizontal color bar generation without LTDC stimuli

- – BER pattern without LTDC stimuli

34.4 DSI Host functional description

34.4.1 General description

The MIPI® DSI Host includes dedicated video interfaces internally connected to the LTDC and a generic APB interface that can be used to transmit information to the display. More in detail:

- • LTDC interface:

- – Used to transmit information in video mode, in which the transfers from the host processor to the peripheral take the form of a real-time pixel stream (DPI).

- – Through a customized mode, this interface can be used to transmit information in full bandwidth in the adapted command mode (DBI).

- • APB slave interface: allows the transmission of generic information in command mode, and follows a proprietary register interface. This interface can operate concurrently with either LTDC interface in either video mode or adapted command mode.

- • Video mode pattern generator: allows the transmission of horizontal/vertical color bar and D-PHY BER testing pattern without any kind of stimuli.

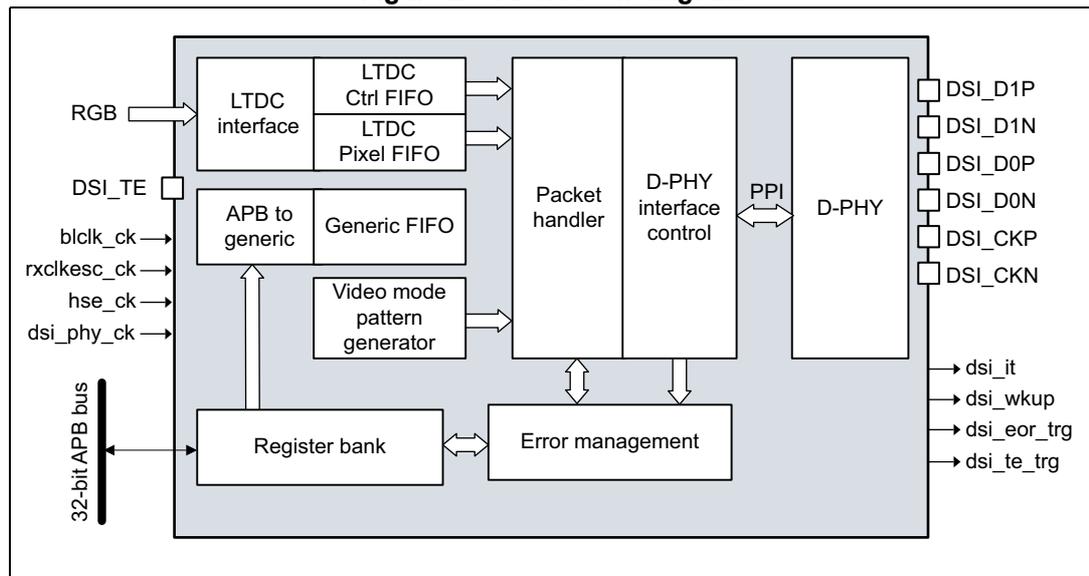

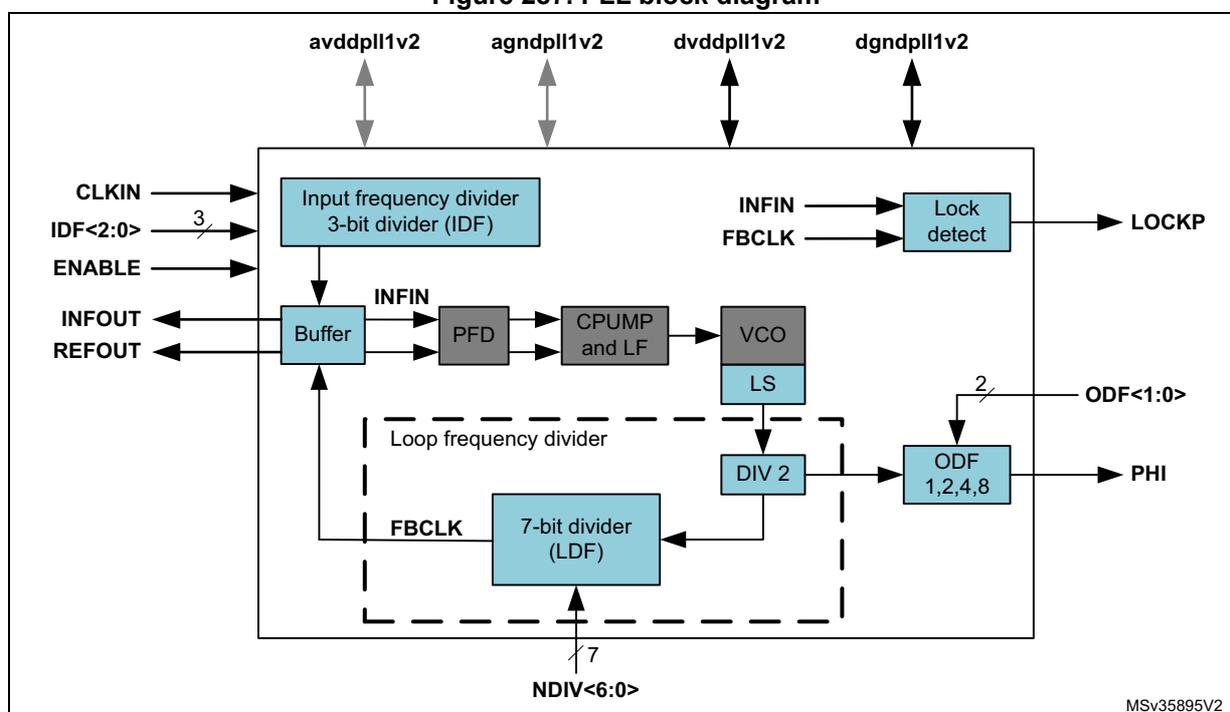

The block diagram is shown in Figure 255 .

Figure 255. DSI block diagram

34.4.2 DSI Host pins and internal signals

Table 279 and Table 280 list, respectively, the DSI pins (alternate functions) and the internal input/output signals.

Table 279. DSI pins

| Signal name | Signal type | Description |

|---|---|---|

| DSI_D0P/D0N | Input/Output | Differential Data lane 0 |

| DSI_D1P/D1N | Output | Differential Data lane 1 |

Table 279. DSI pins (continued)

| Signal name | Signal type | Description |

|---|---|---|

| DSI_CKP DSI_CKN | Output | Differential clock |

| DSI_TE | Input | DSI tearing effect pin |

Table 280. DSI internal input/output signals

| Signal name | Signal type | Description |

|---|---|---|

| dsi_it | Output | DSI global interrupt |

| dsi_wkup | Output | DSI wakeup event |

| dsi_te_trg | Output | DSI tearing effect for MDMA |

| dsi_eor_trg | Output | DSI end-of-refresh for MDMA |

| bclk_ck | Input | Byte lane clock |

| rxclkesck_ck | Input | Escape clock |

| hse_ck | Input | HSE clock used for DSI PLL |

| dsi_phy_ck | Input | D-PHY clock |

34.4.3 Supported resolutions and frame rates

The DSI specification does not define supported standard resolutions or frame rates. Display resolution, blanking periods, synchronization events duration, frame rates, and pixel color depth play a fundamental role in the required bandwidth. In addition, other link related attributes can influence the ability of the link to support a DSI-specific device, namely display input buffering capabilities, video transmission mode (burst or non-burst), bus turn-around (BTA) time, concurrent command mode traffic in a video mode transmission, or display device specifics. All these variables make it difficult to define a standard procedure to estimate the minimum lane rate and the minimum number of lanes that support a specific display device.

The basic assumptions for estimates are:

- • clock lane frequency is 500 MHz, resulting in a bandwidth of 1 Gbit/s for each data lane

- • the display must be capable of buffering the pixel data at the speed at which it is delivered in the DSI link

- • no significant control traffic is present on the link when the pixel data is being transmitted.

34.4.4 System level architecture

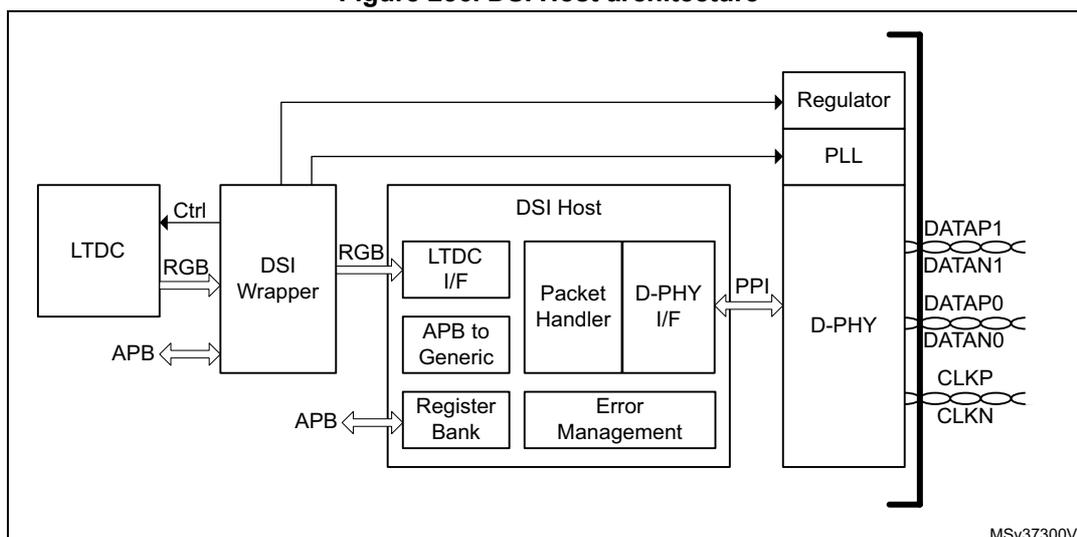

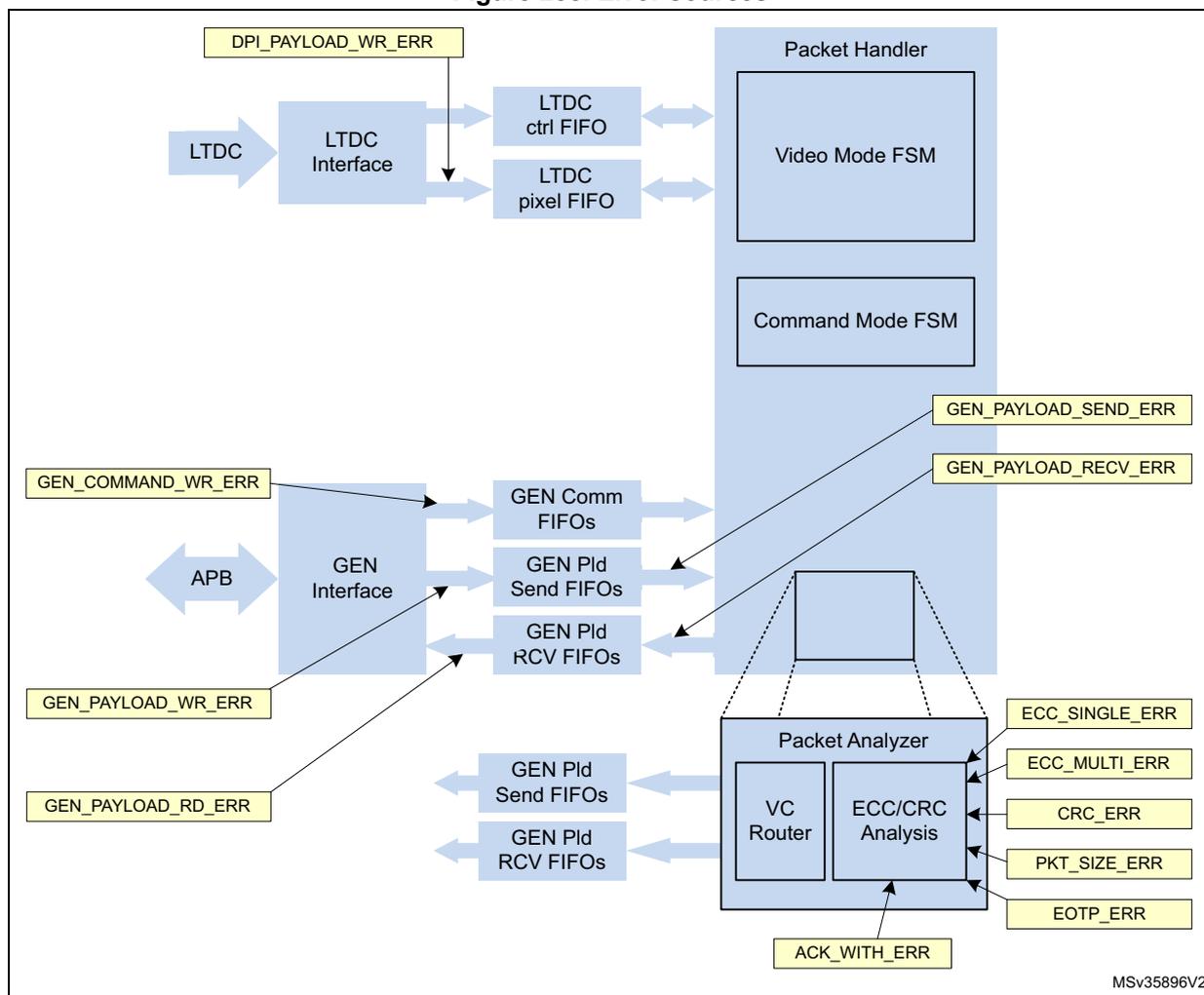

Figure 256 shows the architecture of the DSI Host

Figure 256. DSI Host architecture

The different parts have the following functions:

- • The DSI Wrapper ensures the interfacing between the LTDC and the DSI Host kernel. It can adapt the color mode, the signal polarity and manages the tearing effect (TE) management for automatic frame buffer update in adapted command mode. The DSI Wrapper also controls the DSI regulator, the DSI PLL and specific functions of the MIPI® D-PHY.

- • The LTDC interface captures the data and control signals from the LTDC and conveys them to a FIFO for video control signals and another one for the pixel data. This data is then used to build one of the following:

- – Video packets, when in video mode (see Section 34.5 )

- – The memory_write_start and memory_write_continue DCS commands, when in adapted command mode (see Section 34.6 )

- • The register bank is accessible through a standard AMBA-APB slave interface, providing access to the DSI Host registers for configuration and control. There is also a fully programmable interrupt generator to inform the system about certain events.

- • The PHY interface control is responsible for managing the D-PHY interface. It acknowledges the current operation and enables low-power transmission/reception or a high-speed transmission. It also performs data splitting between available D-PHY lanes for high-speed transmission.

- • The packet handler schedules the activities inside the link. It performs several functions based on the interfaces that are currently operational and the video transmission mode that is used (burst mode or non-burst mode with sync pulses or sync events). It builds

long or short packet generating correspondent ECC and CRC codes. This block also performs the following functions:

- – packet reception

- – validation of packet header by checking the ECC

- – header correction and notification for single-bit errors

- – termination of reception

- – multiple header error notification

- – depending on the virtual channel of the incoming packet, the handler routes the output data to the respective port.

- • The APB-to-generic block bridges the APB operations into FIFOs holding the generic commands. The block interfaces with the following FIFOs:

- – Command FIFO

- – Write payload FIFO

- – Read payload FIFO

- • The error management notifies and monitors the error conditions on the DSI link. It controls the timers used to determine if a timeout condition occurred, performing an internal soft reset and triggering an interruption notification.

34.5 Functional description: video mode on LTDC interface

The LTDC interface captures the data and control signals and conveys them to the FIFO interfaces that transmit them to the DSI link.

Two different streams of data are present at the interface, namely video control signals and pixel data. Depending on the interface color coding, the pixel data is disposed differently throughout the LTDC bus.

Interface pixel color coding is summarized in Table 281 .

Table 281. Location of color components in the LTDC interface

| Location | 16-bit | 18-bit | 24-bit | |||

|---|---|---|---|---|---|---|

| Config 1 | Config 2 | Config 3 | Config 1 | Config 2 | ||

| D23 | - | - | - | - | - | R[7] |

| D22 | - | - | - | - | - | R[6] |

| D21 | - | - | R[4] | - | R[5] | R[5] |

| D20 | - | R[4] | R[3] | - | R[4] | R[4] |

| D19 | - | R[3] | R[2] | - | R[3] | R[3] |

| D18 | - | R[2] | R[1] | - | R[2] | R[2] |

| D17 | - | R[1] | R[0] | R[5] | R[1] | R[1] |

| D16 | - | R[0] | - | R[4] | R[0] | R[0] |

| D15 | R[4] | - | - | R[3] | - | G[7] |

| D14 | R[3] | - | - | R[2] | - | G[6] |

| D13 | R[2] | G[5] | G[5] | R[1] | G[5] | G[5] |

| D12 | R[1] | G[4] | G[4] | R[0] | G[4] | G[4] |

| D11 | R[0] | G[3] | G[3] | G[5] | G[3] | G[3] |

| D10 | G[5] | G[2] | G[2] | G[4] | G[2] | G[2] |

| D9 | G[4] | G[1] | G[1] | G[3] | G[1] | G[1] |

| D8 | G[3] | G[0] | G[0] | G[2] | G[0] | G[0] |

| D7 | G[2] | - | - | G[1] | - | B[7] |

| D6 | G[1] | - | - | G[0] | - | B[6] |

| D5 | G[0] | - | B[4] | B[5] | B[5] | B[5] |

| D4 | B[4] | B[4] | B[3] | B[4] | B[4] | B[4] |

| D3 | B[3] | B[3] | B[2] | B[3] | B[3] | B[3] |

| D2 | B[2] | B[2] | B[1] | B[2] | B[2] | B[2] |

| D1 | B[1] | B[1] | B[0] | B[1] | B[1] | B[1] |

| D0 | B[0] | B[0] | - | B[0] | B[0] | B[0] |

The LTDC interface can be configured to increase flexibility and promote correct use of this interface for several systems. The following configuration options are available:

- • Polarity control: all the control signals are programmable to change the polarity depending on the LTDC configuration.

- • After the core reset, DSI Host waits for the first VSYNC active transition to start signal sampling, including pixel data, thus avoiding starting the transmission of the image data in the middle of a frame.

- • If interface pixel color coding is 18 bits and the 18-bit loosely packed stream is disabled, the number of pixels programmed in the VPSIZE field must be a multiple of four. This means that in this mode, the two LSBs in the configuration are always inferred as zero. The specification states that in this mode, the pixel line size must be a multiple of four.

- • To avoid FIFO underflows and overflows, the configured number of pixels is assumed to be received from the LTDC at all times.

- • To keep the memory organized with respect to the packet scheduling, the number of pixels per packet parameter is used to separate the memory space of different video packets.

For SHTDN and COLM sampling and transmission, the video streaming from the LTDC must be active. This means that if the LTDC is not actively generating the video signals like VSYNC and HSYNC, these signals are not transmitted through the DSI link. Because of such constraints and for commands to be correctly transmitted, the first VSYNC active pulse must occur for the command sampling and transmission. When shutting down the display, it is necessary for the LTDC to be kept active for one frame after the command being issued. This ensures that the commands are correctly transmitted before actually disabling the video generation at the LTDC interface.

The SHTDN and COLM values can be programmed in the DSI Wrapper control register (DSI_WCR).

For all of the data types, one entire pixel is received per each clock cycle. The number of pixels of payload is restricted to a multiple of a value, as shown in Table 282 .

Table 282. Multiplicity of the payload size in pixels for each data type

| Value | Data types |

|---|---|

| 1 | 16-bit 18-bit loosely packed 24-bit |

| 2 | Loosely packed pixel stream |

| 4 | 18-bit non-loosely packed |

34.5.1 Video transmission mode

There are different video transmission modes, namely:

- • Burst mode

- • Non-burst mode

- – Non-burst mode with sync pulse

- – Non-burst mode with sync event

Burst mode

In this mode, the entire active pixel line is buffered into a FIFO and transmitted in a single packet with no interruptions. This transmission mode requires that the DPI pixel FIFO has the capacity to store a full line of active pixel data inside it. This mode is optimally used when the difference between the pixel required bandwidth and DSI link bandwidth is significant, it enables the DSI Host to quickly dispatch the entire active video line in a single burst of data and then return to low-power mode.

Non-burst mode

In this mode, the processor uses the partitioning properties of the DSI Host to divide the video line transmission into several DSI packets. This is done to match the pixel required bandwidth with the DSI link bandwidth. With this mode, the controller configuration does not require a full line of pixel data to be stored inside the LTDC interface pixel FIFO. It requires only the content of one video packet.

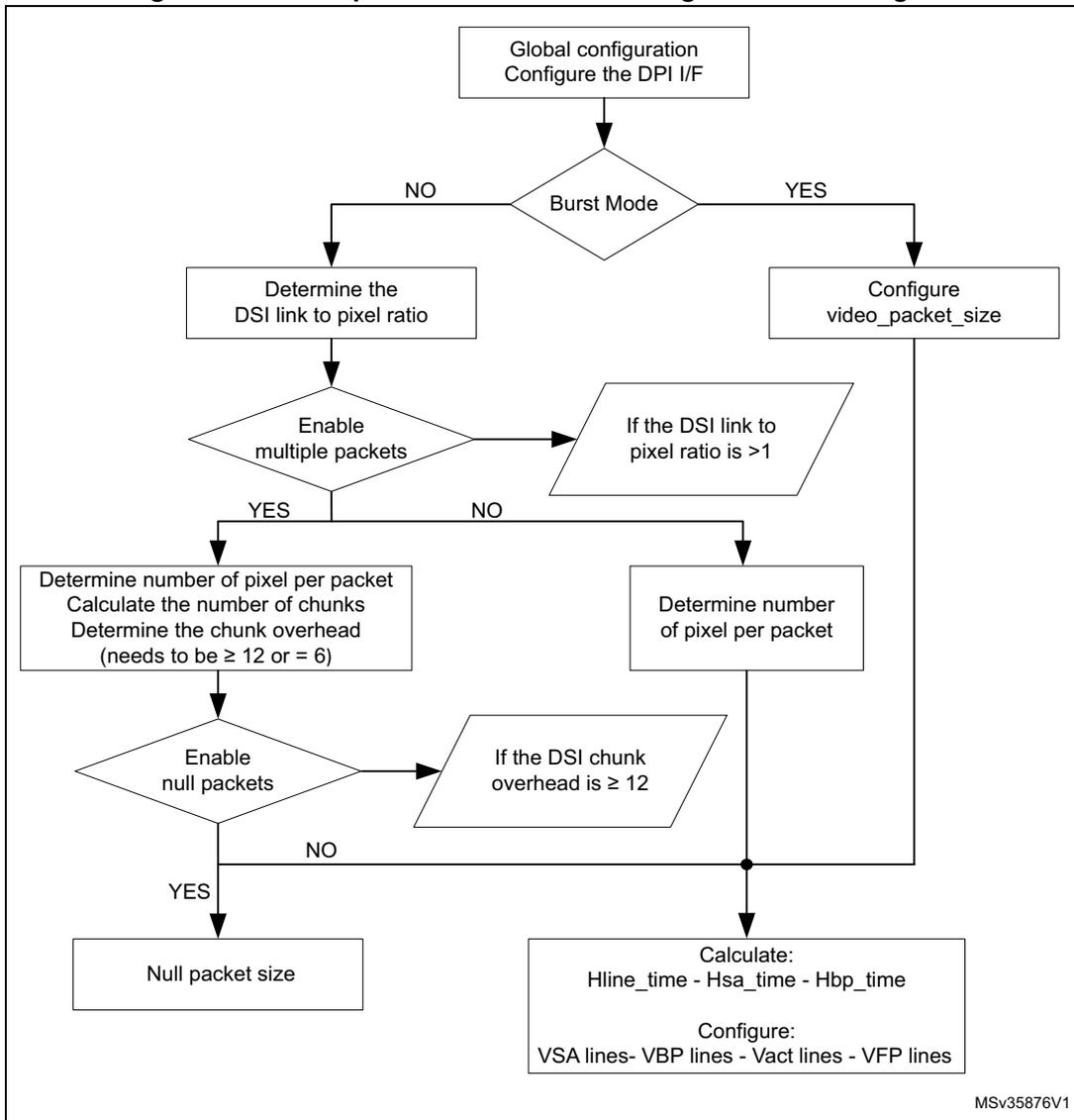

Guidelines for selecting the burst or non-burst mode

Selecting the burst and non-burst mode is mainly dependent on the system configuration and the device requirements. Choose the video transmission mode that suits the application scenario. The burst mode is more beneficial because it increases the probability of the link spending more time in the low-power mode, decreasing power consumption. The following conditions must be met to get the maximum benefits from the burst mode of operation:

- • The DSI Host core must have sufficient pixel memory to store an entire pixel line to avoid the overflow of the internal FIFOs.

- • The display device must support receiving a full pixel line in a single packet burst to avoid the overflow on the reception buffer.

- • The DSI output bandwidth must be higher than the LTDC interface input bandwidth in a relation that enables the link to go to low-power once per line.

If the system cannot meet these requirements, it is likely that the pixel data is lost causing the malfunctioning of the display device while using the burst mode. These errors are related to the capabilities of the system to store the temporary pixel data.

If all the conditions for using the burst mode cannot be met, use the non-burst mode to avoid errors. The non-burst mode provides a better matching of rates for pixel transmission, enabling:

- • only a certain number of pixels to be stored in the memory, and not requiring a full pixel line (lesser LTDC interface RAM requirements in the DSI Host)

- • operation with devices that support only a small amount of pixel buffering (less than a full pixel line).

The DSI non-burst mode must be configured so that the DSI output pixel ratio matches with the LTDC interface input pixel ratio, reducing the memory requirements on both host and/or device side. This is achieved by dividing a pixel line into several chunks of pixels and optionally interleaving them with null packets.

The following equations show how the DSI Host core transmission parameters must be programmed in non-burst mode to match the DSI link pixel output ratio (left hand side of the “=” sign) and LTDC interface pixel input (right hand side of the “=” sign).

When the null packets are enabled:

When the null packets are disabled:

34.5.2 Updating the LTDC interface configuration in video mode

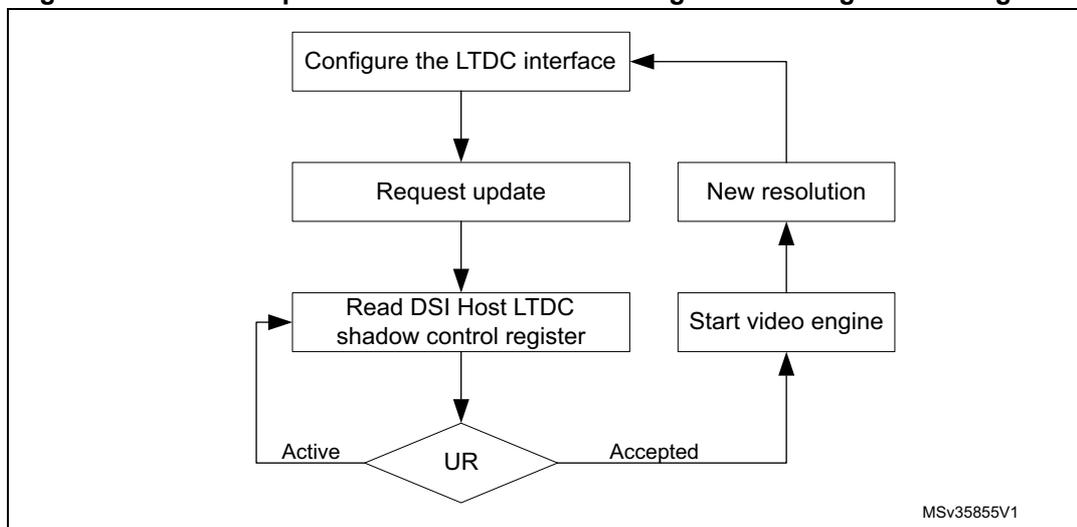

It is possible to update the LTDC interface configuration on the fly without impacting the current frame. It is done with the help of shadow registers. This feature is controlled by the DSI Host video shadow control register (DSI_VSCR).

The new configuration is only used when the system requests for it. To update the video configuration during the transmission of a video frame, the configuration of that frame needs to be stored in the auxiliary registers. This way, the new frame configurations can be set through the APB interface without corrupting the current frame.

By default, this feature is disabled. To enable this feature, set the enable (EN) bit of the DSI Host video shadow control register (DSI_VSCR) to 1.

When this feature is enabled, the system supplies the configuration stored in the auxiliary registers.

Figure 257 shows the necessary steps to update the LTDC interface configuration.

Figure 257. Flow to update the LTDC interface configuration using shadow registers

graph TD

A[Configure the LTDC interface] --> B[Request update]

B --> C[Read DSI Host LTDC shadow control register]

C --> D{UR}

D -- Active --> C

D -- Accepted --> E[Start video engine]

E --> F[New resolution]

F --> A

MSv35855V1

Immediate update

When the shadow register feature is active, the auxiliary registers require the LTDC configuration before the video engine starts. This means that, after a reset, update register (UR) bit is immediately granted.

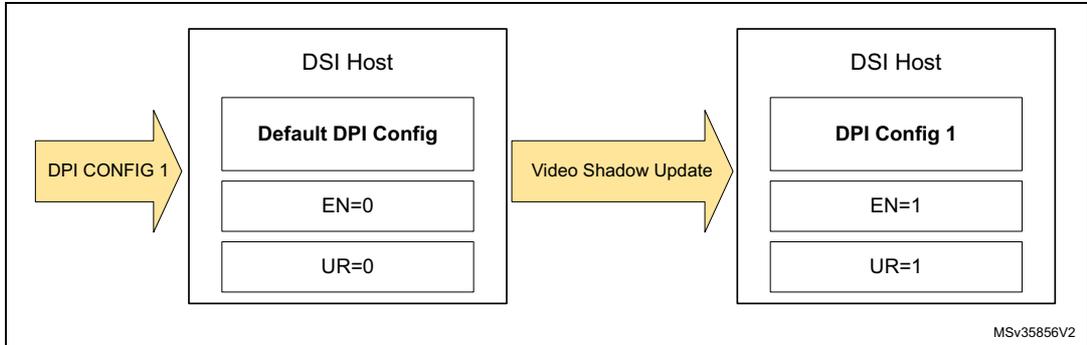

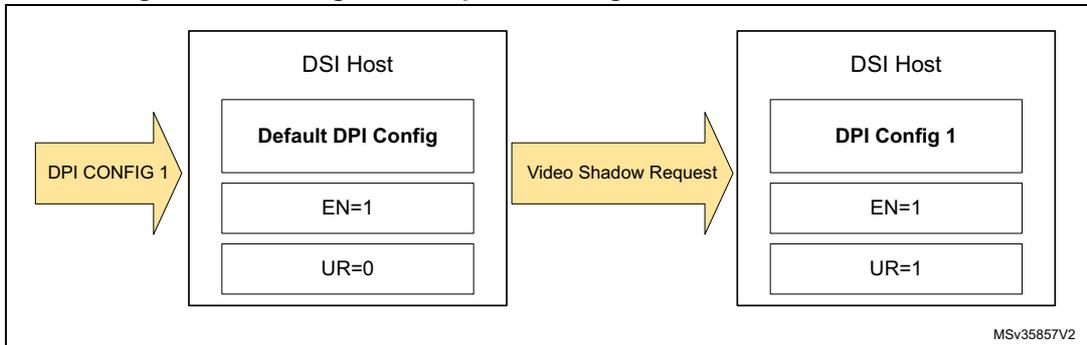

When it is required to immediately update the active registers without the reset (as in Figure 258 ), ensure that the enable (EN) and update register (UR) bits of the DSI Host video shadow control register (DSI_VSCR) are set to 0.

Figure 258. Immediate update procedure

The diagram illustrates the immediate update procedure. It shows two states of the DSI Host registers. The initial state, reached via 'DPI CONFIG 1', contains 'Default DPI Config', 'EN=0', and 'UR=0'. A 'Video Shadow Update' action transitions the system to a new state containing 'DPI Config 1', 'EN=1', and 'UR=1'. A small code 'MSv35856V2' is visible in the bottom right corner.

Updating the configuration during the transmission of a frame using APB

To update the LTDC interface configuration, follow the steps shown in Figure 259 :

- 1. Ensure that the enable (EN) bit of the DSI Host video shadow control register (DSI_VSCR) register is set to 1.

- 2. Set the update register (UR) bit of DSI Host video shadow control register (DSI_VSCR) to 1.

- 3. Monitor the update register (UR) bit. This bit is set to 0 when the update is complete.

Figure 259. Configuration update during the transmission of a frame

The diagram illustrates the configuration update during the transmission of a frame. It shows two states of the DSI Host registers. The initial state, reached via 'DPI CONFIG 1', contains 'Default DPI Config', 'EN=1', and 'UR=0'. A 'Video Shadow Request' action transitions the system to a new state containing 'DPI Config 1', 'EN=1', and 'UR=1'. A small code 'MSv35857V2' is visible in the bottom right corner.

Requesting a configuration update

It is possible to request for the LTDC interface configuration update at any part of the frame. DSI Host waits until the end of the frame to change the configuration. However, avoid sending the update request during the first line of the frame because the data must propagate between clock domains.

34.6 Functional description: adapted command mode on LTDC interface

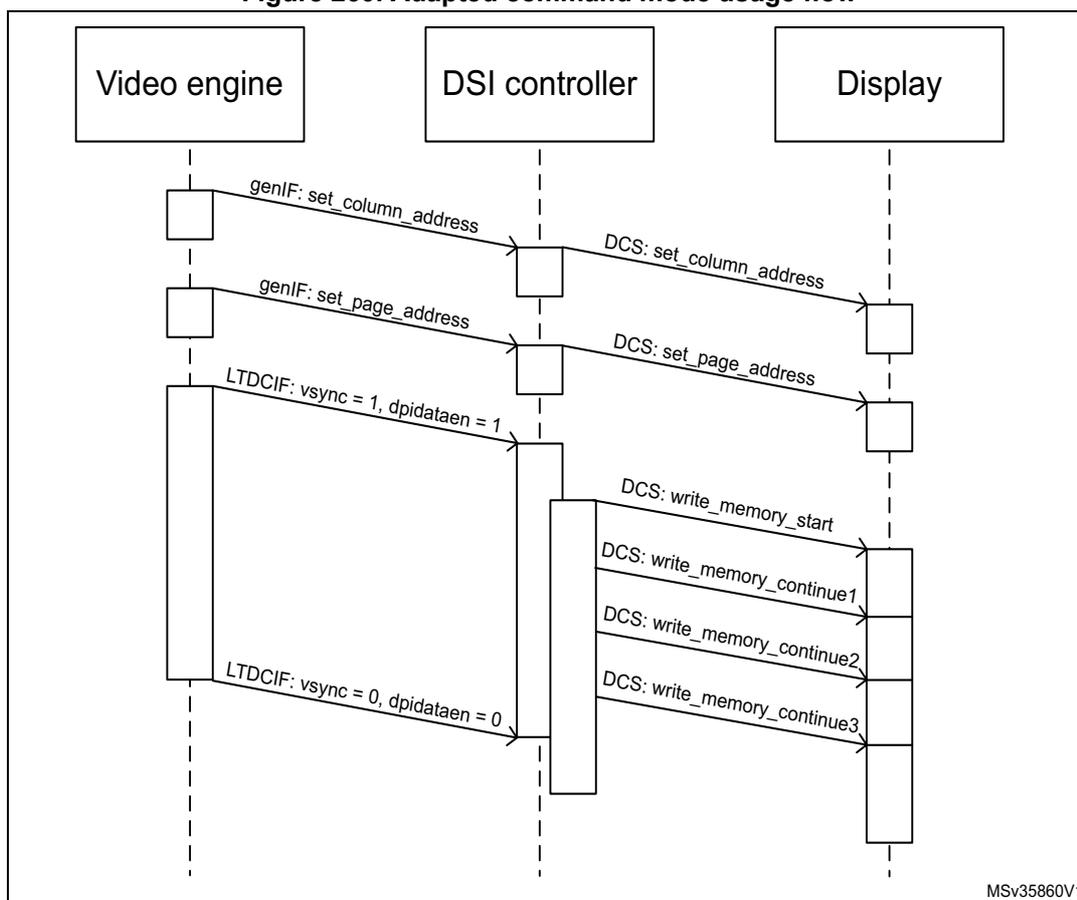

The adapted command mode, enables the system to input a stream of pixel from the LTDC that is conveyed by DSI Host using the command mode transmission (using the DCS packets). The adapted command mode also supports pixel input control rate signaling and tearing effect report mechanism.

The adapted command mode makes it possible to send large amounts of data through the memory_write_start (WMS) and memory_write_continue (WMC) DCS commands. It helps in delivering a wider data bandwidth for the memory write operations sent in command mode to MIPI® displays and to refresh large areas of pixels in high resolution displays. If additional commands such as display configuration commands, read back commands, and tearing effect initialization are to be transferred, then the APB slave generic interface must be used to complement the adapted command mode functionality.

Adapted command mode of operation supports 16 bpp, 18 bpp, and 24 bpp RGB.

To transmit the image data in adapted command mode:

- • Set command mode (CMDM) bit of the DSI Host mode configuration register (DSI_MCR) to 1.

- • Set DSI mode (DSIM) bit in the DSI Wrapper configuration register (DSI_WCFGR) to 1.

To transmit the image data, follow these steps:

- • Define the image area to be refreshed, by using the set_column_address and set_page_address DCS commands. The image area needs to be defined only once and remains effective until different values are defined.

- • Define the pixel color coding to be used by using the color coding (COLC) field in the DSI Host LTDC color coding register (DSI_LCOLCR).

- • Define the virtual channel ID of the LTDC interface generated packets using the virtual channel ID (VCID) field in the DSI Host LTDC VCID register (DSI_LVCIDR). These also need to be defined only once.

- • Start transmitting the data from the LTDC setting the LTDC enable (LTDCEN) bit of the DSI_WCR register.

Figure 260 shows the adapted command mode usage flow.

Figure 260. Adapted command mode usage flow

sequenceDiagram

participant VE as Video engine

participant DC as DSI controller

participant D as Display

Note right of D: MSv35860V1

VE->>DC: genIF: set_column_address

DC->>D: DCS: set_column_address

VE->>DC: genIF: set_page_address

DC->>D: DCS: set_page_address

VE->>DC: LTDCIF: vsync = 1, dpidataen = 1

DC->>D: DCS: write_memory_start

DC->>D: DCS: write_memory_continue1

DC->>D: DCS: write_memory_continue2

DC->>D: DCS: write_memory_continue3

VE->>DC: LTDCIF: vsync = 0, dpidataen = 0

When the command mode (CMDM) bit of the DSI Host mode configuration register (DSI_CFGR) is set to 1, the LTDC interface assumes the behavior corresponding to the adapted command mode.

In this mode, the host processor can use the LTDC interface to transmit a continuous stream of pixels to be written in the local frame buffer of the peripheral. It uses a pixel input bus to receive the pixels and controls the flow automatically to limit the stream of continuous pixels. When the first pixel is received, the current value of the command size (CMDSIZE) field of the DSI Host LTDC command configuration register (DSI_LCCR), is shadowed to the internal interface function. The interface increments a counter on every valid pixel that is input through the interface. When this pixel counter reaches command size (CMDSIZE), a command is written into the command FIFO, and the packet can be transmitted through the DSI link.

If the last pixel arrives before the counter reaches the value of shadowed command size (CMDSIZE), a WMS command is issued to the command FIFO with word count (WC) set to the number of bytes corresponding to the counter value. If more than CMDSIZE pixels are received (shadowed value), a WMS command is sent to the command FIFO with WC set to the number of bytes corresponding to the command size (CMDSIZE) and the counter is restarted.

After the first WMS command has been written to the FIFO, the circuit behaves in a similar way, but issues WMC commands instead of WMS commands. The process is repeated until the last pixel of the image is received. The core automatically starts sending a new packet

when the last pixel of the image is received, falls, or command size (CMDSIZE) limit is reached.

Synchronization with the LTDC

The DSI Wrapper performs the synchronization of the transfer process by:

- • controlling the start/halt of the LTDC

- • making the data flow control between LTDC and DSI Host.

The transfer to refresh the display frame buffer can be triggered

- • manually, setting the LTDC enable (LTDCEN) bit of the DSI Wrapper control register (DSI_WCR)

- • automatically when a tearing effect (TEIF) event occurs, and automatic refresh (AR) is enabled.

The selection between manual and automatic mode is done through the automatic refresh (AR) bit of the DSI Wrapper configuration register (DSI_WCFGR).

Once the transfer of one frame is done whatever in manual or automatic refresh mode, the DSI Wrapper halts the TFT display controller (LTDC), resetting the LTDC enable (LTDCEN) bit of the DSI Wrapper control register (DSI_WCR), and setting the end of refresh interrupt flag (ERIF) flag of the DSI Wrapper status register (DSI_WSR). If the end of refresh interrupt enable (ERIE) bit of the DSI Wrapper configuration register (DSI_WCFGR) is set, an interrupt is generated.

The end of refresh interrupt flag (ERIF) flag of the DSI Wrapper status register (DSI_WSR) can be reset setting the clear end of refresh interrupt flag (CERIF) bit of the DSI Wrapper clear interrupt flag register (DSI_WCIFR).

The halting of the TFT display controller (LTDC) by the DSI Wrapper is done synchronously on a rising edge or a falling edge of VSync according to the VSync polarity (VSPOL) bit of the DSI Wrapper configuration register (DSI_WCFGR).

Support of tearing effect

The DSI specification supports tearing effect function in command mode displays. It enables the Host processor to receive timing accurate information about where the display peripheral is in the process of reading the content of its frame buffer.

The tearing effect can be managed through:

- • a separate pin, which is not covered in the DSI specification

- • the DSI tearing effect functionality: a set_tear_on DCS command must be issued through the APB interface using the generic interface registers.

Tearing effect through a GPIO

When the tearing effect source (TESRC) bit of the DSI Wrapper configuration register (DSI_WCFGR) is set, the tearing effect is signaled through a GPIO.

The polarity of the input signal can be configured by the tearing effect polarity (TEPOL) bit of the DSI Wrapper configuration register (DSI_WCFGR).

When the programmed edge is detected, the tearing effect interrupt flag (TEIF) bit of the DSI Wrapper interrupt and status register (DSI_WISR) is set.

If the tearing effect interrupt enable (TEIE) bit of the DSI Wrapper interrupt enable register (DSI_WIER) is set, an interrupt is generated.

Tearing effect through DSI link

When the TESRC bit of the DSI Wrapper configuration register (DSI_WCFGR) is reset, the tearing effect is managed through the DSI link:

The DSI Host performs a double bus turn-around (BTA) after sending the set_tear_on command granting the ownership of the link to the DSI display. The display holds the ownership of the bus until the tear event occurs, which is indicated to the DSI Host by a D-PHY trigger event. The DSI Host then decodes the trigger and reports the event setting the tearing effect interrupt flag (TEIF) bit of the DSI Wrapper interrupt and status register (DSI_WISR).

If the tearing effect interrupt enable (TEIE) bit of the DSI Wrapper interrupt enable register (DSI_WIER) is set, an interrupt is generated.

To use this function, it is necessary to issue a set_tear_on command after the update of the display using the WMS and WMC DCS commands. This procedure halts the DSI link until the display is ready to receive a new frame update.

The DSI Host does not automatically generate the tearing effect request (double BTA) after a WMS/WMC sequence for flexibility purposes, so several regions of the display can be updated improving DSI bandwidth usage. Tearing effect request must always be triggered by a set_tear_on command in the DSI Host implementation.

Configure the following registers to activate the tearing effect:

- • DSI Host command mode configuration register (DSI_CMCR): TEARE

- • DSI Host protocol configuration register (DSI_PCR): BTAE.

34.7 Functional description: APB slave generic interface

The APB slave interface allows the transmission of generic information in command mode, and follows a proprietary register interface. Commands sent through this interface are not constrained to comply with the DCS specification, and can include generic commands described in the DSI specification as manufacturer-specific.

The DSI Host supports the transmission of write and read command mode packets as described in the DSI specification. These packets are built using the APB register access. The DSI Host generic payload data register (DSI_GPDR) has two distinct functions based on the operation. Writing to this register sends the data as payload when sending a command mode packet. Reading this register returns the payload of a read back operation. The DSI Host generic header configuration register (DSI_GHCR) contains the command mode packet header type and header data. Writing to this register triggers the transmission of the packet implying that for a long command mode packet, the packet payload needs to be written in advance in the DSI Host generic payload data register (DSI_GPDR).

The valid packets that can be transmitted through the generic interface are the following:

- • Generic write short packet 0 parameters

- • Generic write short packet 1 parameters

- • Generic write short packet 2 parameters

- • Generic read short packet 0 parameters

- • Generic read short packet 1 parameters

- • Generic read short packet 2 parameters

- • Maximum read packet configuration

- • Generic long write packet

- • DCS write short packet 0 parameters

- • DCS write short packet 1 parameters

- • DCS read short packet 0 parameters

- • DCS write long packet.

A set of bits in the DSI Host generic packet status register (DSI_GPSR) reports the status of the FIFO associated with APB interface support.

Generic interface packets are always transported using one of the DSI transmission modes, that is, video mode or command mode. If neither of these modes is selected, the packets are not transmitted through the link, and the related FIFO eventually becomes overflowed.

34.7.1 Packet transmission using the generic interface

The transfer of packets through the APB bus is based on the following conditions:

- • The APB protocol defines that the write and read procedure takes two clock cycles each to be executed. This means that the maximum input data rate through the APB interface is always half the speed of the APB clock.

- • The data input bus has a maximum width of 32 bits. This allows for a relation to be defined between the input APB clock frequency and the maximum bit rate achievable by the APB interface.

- • The DSI link pixel bit rate when using solely APB is \( (\text{APB clock frequency}) * 16 \) Mbit/s.

- • When using only the APB interface, the theoretical DSI link maximum bit rate can be expressed as \( \text{DSI link maximum bit rate} = \text{APB clock frequency (in MHz)} * 32 / 2 \) Mbit/s.

In this formula, the number 32 represents the APB data bus width, and the division by two is present because each APB write procedure takes two clock cycles to be executed.

- • The bandwidth is dependent on the APB clock frequency; the available bandwidth increases with the clock frequency.

To drive the APB interface to achieve high bandwidth command mode traffic transported by the DSI link, the DSI Host must operate only in the command mode, and the APB interface must be the only data source in use. Thus, the APB interface has the entire bandwidth of the DSI link and does not share it with any another input interface source.

The memory write commands require maximum throughput from the APB interface, because they contain the most amount of data conveyed by the DSI link. While writing the packet information, first write the payload of a given packet into the payload FIFO using the DSI Host generic payload data register (DSI_GPCR). When the payload data is for the command parameters, place the first byte to be transmitted in the least significant byte position of the APB data bus.

After writing the payload, write the packet header into the command FIFO. For more information about the packet header organization on the 32-bit APB data bus, so that it is correctly stored inside the command FIFO.

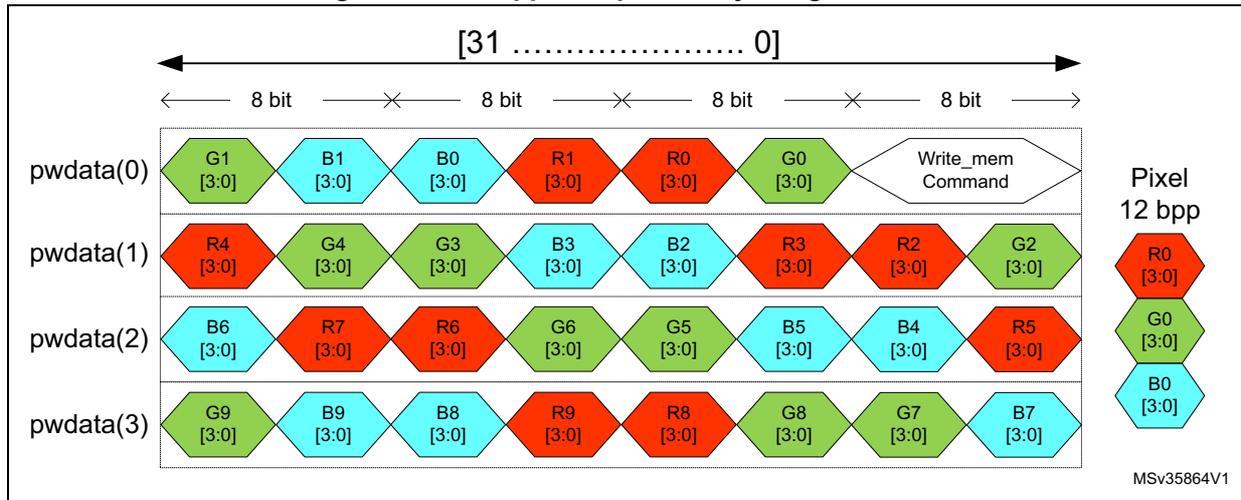

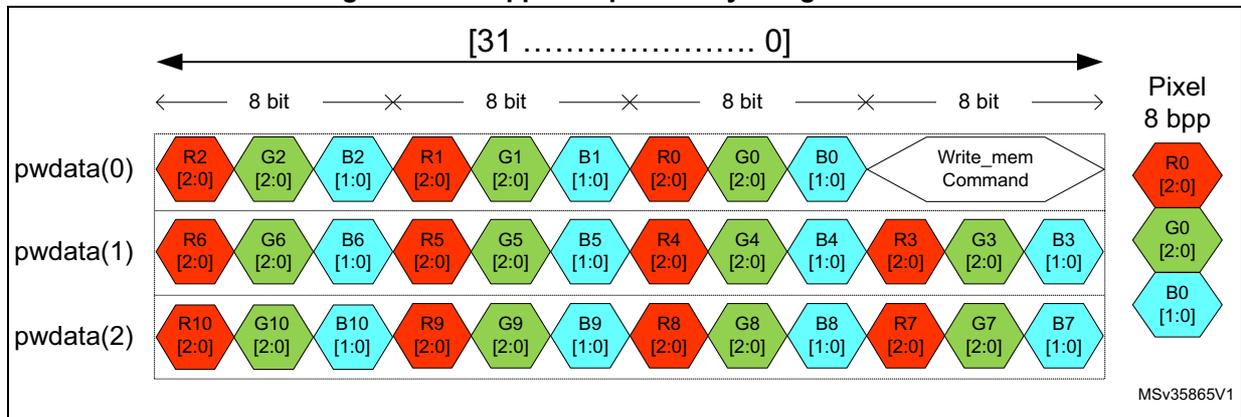

When the payload data is for a memory write command, it contains pixel information and it must follow the pixel to byte conversion organization referred in the Annex A of the DCS specification.

Figures 261 to 265 show how the pixel data must be organized in the APB data write bus.

The memory write commands are conveyed in DCS long packets, encapsulated in a DSI packet. The DSI specifies that the DCS command must be present in the first payload byte of the packet. This is also included in the diagrams. In figures 261 to 265, the write memory command can be replaced by the DCS command write memory Start and write memory Continue .

Figure 261. 24 bpp APB pixel to byte organization

![Diagram showing the 24 bpp APB pixel to byte organization. It illustrates five rows of pixel data (pwdata(0) to pwdata(4)) across a 32-bit bus. Each row contains four 8-bit segments. pwdata(0) contains B0[7:0], G0[7:0], R0[7:0], and a Write_mem Command. Subsequent rows contain interleaved Red, Green, and Blue components. A legend on the right shows the pixel structure for 24 bpp: R0[7:0], G0[7:0], B0[7:0].](/RM0399-STM32H745-755-747-757/80274cb853c70bebba02d0fb4498627e_img.jpg)

The diagram illustrates the organization of pixel data on a 32-bit APB bus for 24-bit per pixel (bpp) format. The bus is divided into four 8-bit segments. The data is organized into five rows (pwdata(0) to pwdata(4)).

- pwdata(0): B0[7:0] (Blue), G0[7:0] (Green), R0[7:0] (Red), Write_mem Command

- pwdata(1): R2[7:0] (Red), B1[7:0] (Blue), G1[7:0] (Green), R1[7:0] (Red)

- pwdata(2): G3[7:0] (Green), R3[7:0] (Red), B2[7:0] (Blue), G2[7:0] (Green)

- pwdata(3): B4[7:0] (Blue), G4[7:0] (Green), R4[7:0] (Red), B3[7:0] (Blue)

- pwdata(4): R6[7:0] (Red), B5[7:0] (Blue), G5[7:0] (Green), R5[7:0] (Red)

Pixel 24 bpp structure:

- R0 [7:0] (Red)

- G0 [7:0] (Green)

- B0 [7:0] (Blue)

MSv35861V1

Figure 262. 18 bpp APB pixel to byte organization

![Diagram of 18 bpp APB pixel to byte organization showing five rows of pixel data (pwdata(0) to pwdata(4)) packed into 32-bit words. Each row contains color components (R, G, B) and padding (2'd0) or a write command. A legend on the right shows the pixel format: R0[5:0], G0[5:0], B0[5:0].](/RM0399-STM32H745-755-747-757/53bb57cefbafac201b870f9fef8f2659_img.jpg)

Figure 262 illustrates the 18 bpp APB pixel to byte organization. The diagram shows five rows of pixel data (pwdata(0) to pwdata(4)) packed into 32-bit words. Each row contains color components (R, G, B) and padding (2'd0) or a write command. The data is organized into four 8-bit segments per 32-bit word.

The pixel format is 18 bpp, with the following color components:

- R0[5:0]

- G0[5:0]

- B0[5:0]

The diagram shows the following data for each row:

- pwdata(0): B0[5:0], 2'd0, G0[5:0], 2'd0, R0[5:0], 2'd0, Write_mem Command

- pwdata(1): R2[5:0], 2'd0, B1[5:0], 2'd0, G1[5:0], 2'd0, R1[5:0], 2'd0

- pwdata(2): G3[5:0], 2'd0, R3[5:0], 2'd0, B2[5:0], 2'd0, G2[5:0], 2'd0

- pwdata(3): B4[5:0], 2'd0, G4[5:0], 2'd0, R4[5:0], 2'd0, B3[5:0], 2'd0

- pwdata(4): R6[5:0], 2'd0, B5[5:0], 2'd0, G5[5:0], 2'd0, R5[5:0], 2'd0

MSv35862V1

Figure 263. 16 bpp APB pixel to byte organization

![Diagram of 16 bpp APB pixel to byte organization showing four rows of pixel data (pwdata(0) to pwdata(3)) packed into 32-bit words. Each row contains color components (R, G, B) and padding (2'd0) or a write command. A legend on the right shows the pixel format: R0[4:0], G0[5:0], B0[4:0].](/RM0399-STM32H745-755-747-757/cdbfb62017dac2ff3de4f021598ede91_img.jpg)

Figure 263 illustrates the 16 bpp APB pixel to byte organization. The diagram shows four rows of pixel data (pwdata(0) to pwdata(3)) packed into 32-bit words. Each row contains color components (R, G, B) and padding (2'd0) or a write command. The data is organized into four 8-bit segments per 32-bit word.

The pixel format is 16 bpp, with the following color components:

- R0[4:0]

- G0[5:0]

- B0[4:0]

The diagram shows the following data for each row:

- pwdata(0): R1[4:0], G1[5:3], G0[2:0], B0[4:0], R0[4:0], G0[5:3], Write_mem Command

- pwdata(1): R3[4:0], G3[5:3], G2[2:0], B2[4:0], R2[4:0], G2[5:3], G1[2:0], B1[4:0]

- pwdata(2): R5[4:0], G5[5:3], G4[2:0], B4[4:0], R4[4:0], G4[5:3], G3[2:0], B3[4:0]

- pwdata(3): R7[4:0], G7[5:3], G6[2:0], B6[4:0], R6[4:0], G6[5:3], G5[2:0], B5[4:0]

MSv35863V1

Figure 264. 12 bpp APB pixel to byte organization

The diagram illustrates the 12 bpp APB pixel to byte organization. It shows four data lines, pwdata(0) through pwdata(3), each containing a sequence of 8-bit bytes. The bytes are color-coded: red for Red (R), green for Green (G), and cyan for Blue (B). The bit ranges for each component are [3:0].

- pwdata(0): G1 [3:0], B1 [3:0], B0 [3:0], R1 [3:0], R0 [3:0], G0 [3:0], Write_mem Command. This line corresponds to Pixel 12 bpp components R0 [3:0], G0 [3:0], and B0 [3:0].

- pwdata(1): R4 [3:0], G4 [3:0], G3 [3:0], B3 [3:0], B2 [3:0], R3 [3:0], R2 [3:0], G2 [3:0].

- pwdata(2): B6 [3:0], R7 [3:0], R6 [3:0], G6 [3:0], G5 [3:0], B5 [3:0], B4 [3:0], R5 [3:0].

- pwdata(3): G9 [3:0], B9 [3:0], B8 [3:0], R9 [3:0], R8 [3:0], G8 [3:0], G7 [3:0], B7 [3:0].

The overall bit range is [31 ..... 0]. The diagram is labeled MSv35864V1.

Figure 265. 8 bpp APB pixel to byte organization

The diagram illustrates the 8 bpp APB pixel to byte organization. It shows three data lines, pwdata(0) through pwdata(2), each containing a sequence of 8-bit bytes. The bytes are color-coded: red for Red (R), green for Green (G), and cyan for Blue (B). The bit ranges for each component are [2:0] for R and G, and [1:0] for B.

- pwdata(0): R2 [2:0], G2 [2:0], B2 [1:0], R1 [2:0], G1 [2:0], B1 [1:0], R0 [2:0], G0 [2:0], B0 [1:0], Write_mem Command. This line corresponds to Pixel 8 bpp components R0 [2:0], G0 [2:0], and B0 [1:0].

- pwdata(1): R6 [2:0], G6 [2:0], B6 [1:0], R5 [2:0], G5 [2:0], B5 [1:0], R4 [2:0], G4 [2:0], B4 [1:0], R3 [2:0], G3 [2:0], B3 [1:0].

- pwdata(2): R10 [2:0], G10 [2:0], B10 [1:0], R9 [2:0], G9 [2:0], B9 [1:0], R8 [2:0], G8 [2:0], B8 [1:0], R7 [2:0], G7 [2:0], B7 [1:0].

The overall bit range is [31 ..... 0]. The diagram is labeled MSv35865V1.

34.8 Functional description: timeout counters

The DSI Host includes counters to manage timeout during the various communication phases. The duration of each timeout can be configured by the six timeout counter configuration registers (DSI_TCCR0...5).

There are two types of counters:

- • contention error detection timeout counters ( Section 34.8.1 )

- • peripheral response timeout counters ( Section 34.8.2 ).

34.8.1 Contention error detection timeout counters

The DSI Host implements a set of counters and conditions to notify the errors. It features a set of registers to control the timers used to determine if a timeout has occurred, and also contains a set of interruption status registers that are cleared upon a read operation (detailed in Table 283 ). Optionally, these registers also trigger an interrupt signal that can be used by the system to be activated when an error occurs within the DSI connection.

Table 283. Contention detection timeout counters configuration

| Timeout counter | Value register | Value field | Flag register | Flag field |

|---|---|---|---|---|

| High-speed transmission | DSI_TCCR0 | TOHSTX | DSI_ISR1 | TOHSTX |

| Low-power reception | DSI_TCCR0 | TOLPRX | DSI_ISR1 | TOLPRX |

Time units for these 16-bit counters are configured in cycles defined in the timeout clock division (TOCKDIV) field in the DSI Host clock control register (DSI_CCR).

The value written to the timeout clock division (TOCKDIV) field in the DSI Host clock control register (DSI_CCR) defines the time unit for the timeout limits using the lane byte clock as input.

This mechanism increases the range to define these limits.

High-speed transmission contention detection

The timeout duration is configured in the high-speed transmission timeout count (HSTX_TOCNT) field of the DSI Host timeout counter configuration register 1 (DSI_TCCR0). A 16-bit counter measures the time during which the high-speed mode is active.

If that counter reaches the value defined by the high-speed transmission timeout count (HSTX_TOCNT) field of the DSI Host timeout counter configuration register 1 (DSI_TCCR0), the timeout high-speed transmission (TOHSTX) bit in the DSI Host interrupt and status register 1 (DSI_ISR1) is asserted and an internal soft reset is generated to the DSI Host.

If the timeout high-speed transmission interrupt enable (TOHSTXIE) bit of the DSI Host interrupt enable register 1 (DSI_IER1) is set, an interrupt is generated.

Low-power reception contention detection

The timeout is configured in the low-power reception timeout counter (LPRX_TOCNT) field of the DSI Host timeout counter configuration register 1 (DSI_TCCR1). A 16-bit counter measures the time during which the low-power reception is active.

If that counter reaches the value defined by the low-power reception timeout counter (LPRX_TOCNT) field of the DSI Host timeout counter configuration register 1 (DSI_TCCR0), the timeout low-power reception (TOLPRX) bit in the DSI Host interrupt and status register 1 (DSI_ISR1) is asserted and an internal soft reset is generated to the DSI Host.

If the timeout low-power reception interrupt enable (TOLPRXIE) bit of the DSI Host interrupt enable register 1 (DSI_IER1) is set, an interrupt is generated. Once the software gets notified by the interrupt, it must reset the D-PHY by deasserting and asserting the digital enable (DEN) bit of the DSI Host PHY control register (DSI_PCTLR).

34.8.2 Peripheral response timeout counters

A peripheral may not immediately respond correctly to some received packets. For example, a peripheral receives a read request, but due to its architecture cannot access the RAM for a while (for example, the panel is being refreshed and takes some time to respond). In this case, set a timeout to ensure that the host waits long enough so that the device is able to process the previous data before receiving the new data or responding correctly to new requests.

Table 284 lists the events belonging to various categories having an associated timeout for peripheral response.

Table 284. List of events of different categories of the PRESP_TO counter

| Category | Event |

|---|---|

| Items implying a BTA PRESP_TO | Bus-turn-around |

| READ requests indicating a PRESP_TO (replicated for HS and LP) | (0x04) Generic read, no parameters short (0x14) Generic read, 1 parameter short (0x24) Generic read, 2 parameters short (0x06) DCS read, no parameters short |

| WRITE requests indicating a PRESP_TO (replicated for HS and LP) | (0x03) Generic short write, no parameters short (0x13) Generic short write, 1 parameter short (0x23) Generic short write, 2 parameters short (0x29) Generic long write long (0x05) DCS short write, no parameters short (0x15) DCS short write, 1 parameter short (0x39) DCS long write/write_LUT, command packet long (0x37) Set maximum return packet size |

The DSI Host ensures that, on sending an event that triggers a timeout, the D-PHY switches to the Stop state and a counter starts running until it reaches the value of that timeout. The link remains in the LP-11 state and unused until the timeout ends, even if there are other events ready to be transmitted.

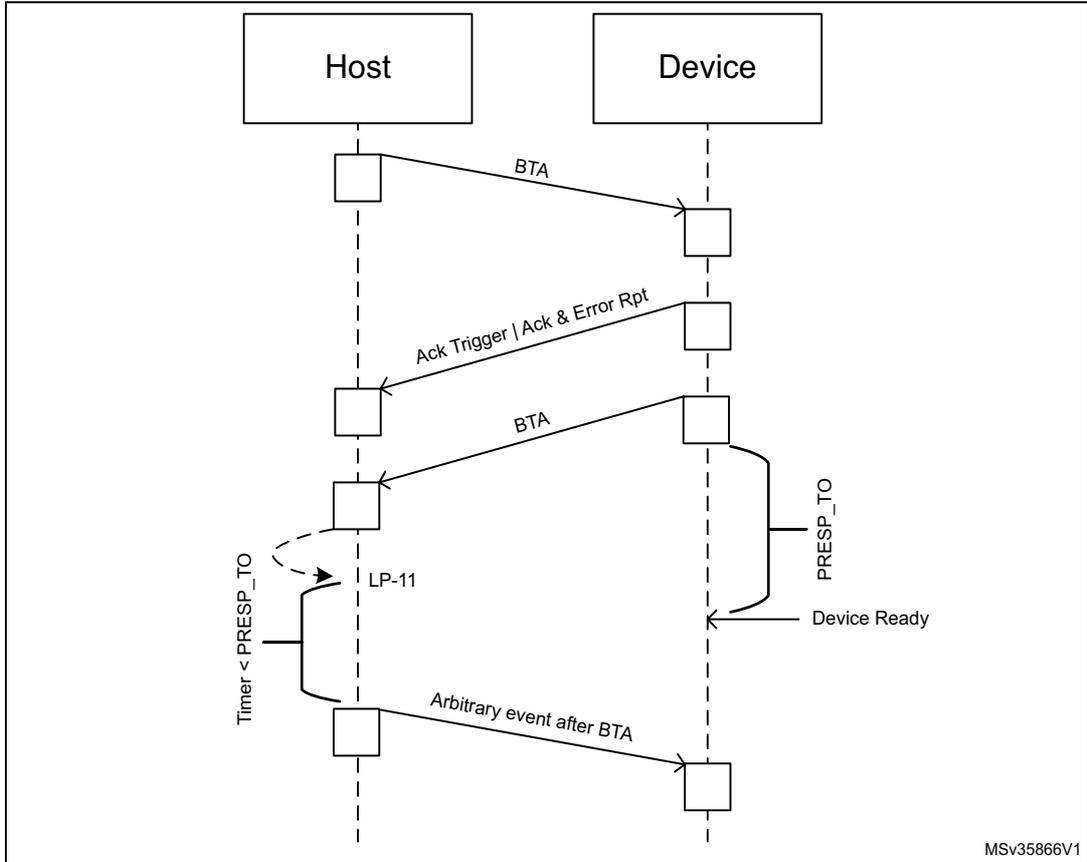

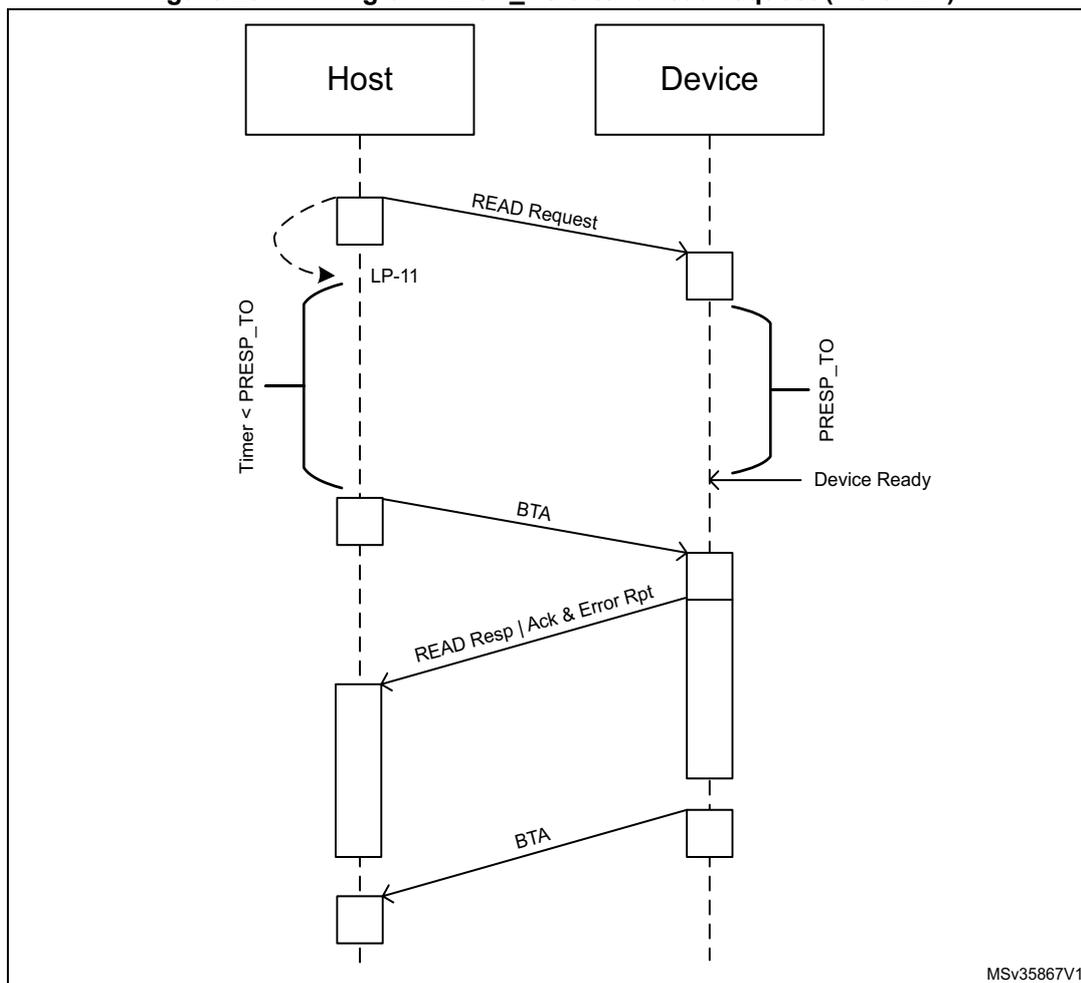

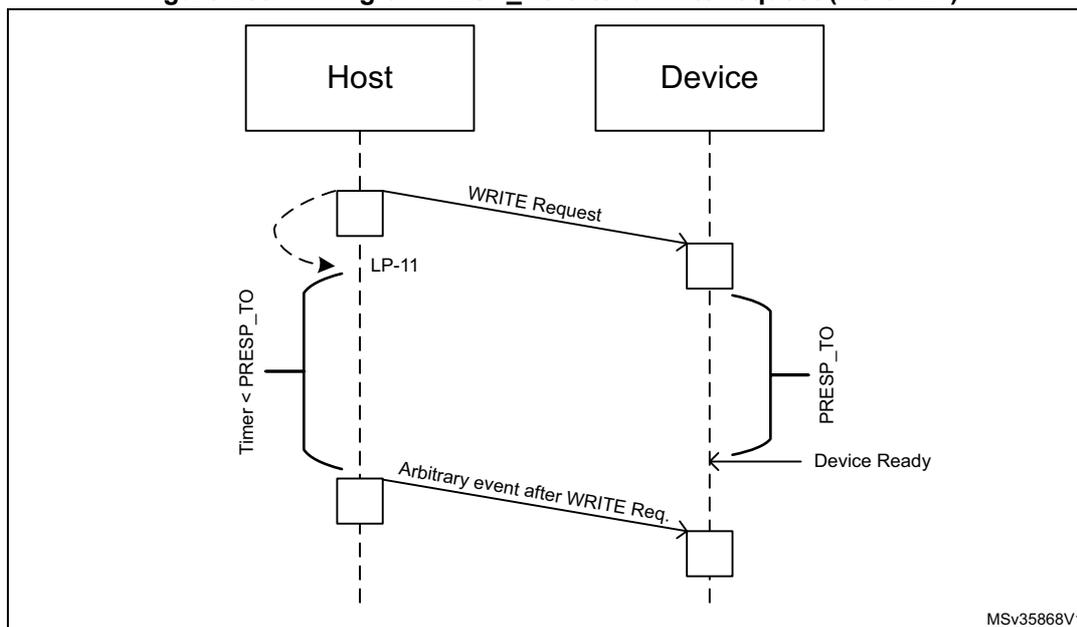

Figures 266 to 268 illustrate the flow of counting in the PRESP_TO counter for the three categories listed in Table 284 .

Figure 266. Timing of PRESP_TO after a bus-turn-around

The diagram illustrates the timing of a PRESP_TO (Pre-Response Timeout) timer after a bus-turn-around (BTA) in a DSI Host-Device interaction. The sequence of events is as follows:

- The Host sends a BTA (Bus Turn-Around) signal to the Device .

- The Device responds with an Ack Trigger | Ack & Error Rpt (Acknowledge Trigger | Acknowledge & Error Report) signal back to the Host .

- Upon receiving the response, the Host sends another BTA signal to the Device .

- Simultaneously, the Host starts a Timer < PRESP_TO (Pre-Response Timeout timer).

- The Device enters a low-power state ( LP-11 ).

- An Arbitrary event after BTA occurs on the Device side.

- When the Device becomes Device Ready , it sends a PRESP_TO (Pre-Response Timeout) signal to the Host .

The diagram uses dashed vertical lines for lifelines and solid arrows for message exchanges. Small squares mark the start and end of messages and events. A bracket on the Host lifeline indicates the active period for the PRESP_TO timer, starting from the second BTA transmission and ending when the Device Ready signal is received.

MSV35866V1

Figure 267. Timing of PRESP_TO after a read request (HS or LP)

The diagram illustrates the timing of PRESP_TO after a read request between a Host and a Device. The sequence of events is as follows:

- The Host sends a READ Request to the Device.

- The Host transitions to the LP-11 state.

- A timer starts on the Host side, labeled Timer < PRESP_TO .

- On the Device side, a timer labeled PRESP_TO is active until the Device Ready state is reached.

- The Device initiates a BTA (Bus Turnaround) to the Host.

- The Device then sends a READ Resp | Ack & Error Rpt .

- Another BTA occurs to return control to the Host.

MSV35867V1

Figure 268. Timing of PRESP_TO after a write request (HS or LP)

The diagram illustrates the timing of the PRESP_TO counter after a write request. A Host sends a WRITE Request to a Device. A timer labeled 'Timer < PRESP_TO' starts at the Host. The Device responds with 'Device Ready'. An 'Arbitrary event after WRITE Req.' occurs on the Host side. The diagram also shows 'LP-11' and 'PRESP_TO' states. The code MSV35868V1 is noted in the bottom right corner.

Table 285 describes the fields used for the configuration of the PRESP_TO counter.

Table 285. PRESP_TO counter configuration

| Description | Register | Field | |

|---|---|---|---|

| Period for which the DSI Host keeps the link still | After sending a High-speed read operation | DSI_TCCR1 | HSRD_TOCNT |

| After sending a Low-power read operation | DSI_TCCR2 | LPRD_TOCNT | |

| After completing a Bus-turn-around (BTA) | DSI_TCCR5 | BTA_TOCNT | |

| Period for which the DSI Host keeps the link inactive | After sending a High-speed write operation | DSI_TCCR3 | HSWR_TOCNT |

| After sending a Low-power write operation | DSI_TCCR4 | LPWR_TOCNT | |

The values in these registers are measured in number of cycles of the lane byte clock. These registers are only used in command mode because in video mode, there is a rigid timing schedule to be met to keep the display properly refreshed and it must not be broken by these or any other timeouts. Setting a given timeout to 0 disables going into LP-11 state and timeout for events of that category.

The read and the write requests in high-speed mode are distinct from those in low-power mode. For example, if HSRD_TOCNT is set to 0 and LPRD_TOCNT is set to a non-0 value, a generic read with no parameters does not activate the PRESP_TO counter in high-speed, but activates the PRESP_TO in low-power.

The DSI Host timeout counter configuration register 4 (DSI_TCCR3) includes a special Presp mode (PM) bit to change the normal behavior of PRESP_TO in Adaptive command

mode for high-speed write operation timeout. When set to 1, this bit allows the RESP_TO from HSWR_TOCNT to be used only once, when both of the following conditions are met:

- • the LTDC VSYNC signal rises and falls

- • the packets originated from the LTDC interface in adapted command mode are transmitted and its FIFO is empty again.

In this scenario, non-adapted command mode requests are not sent to the D-PHY, even if there is traffic from the generic interface ready to be sent, returning them to the Stop state. When it happens, the RESP_TO counter is activated and only when it is completed, the DSI Host sends any other traffic that is ready, as illustrated in Figure 269.

Figure 269. Effect of prep mode at 1

![Timing diagram showing various signals over time: dpivsync_edpiwms, dpidataen, dpidata[29:0], edpi_fifo_empty, gen_wr_en, gen_data[31:0], link_state[1:0], link_data[31:0], and RESP_TO_active. The diagram illustrates the effect of prep mode at 1 on data transmission.](/RM0399-STM32H745-755-747-757/1344ab8943c7f8c34e99477d43714313_img.jpg)

The timing diagram illustrates the relationship between several signals during a DSI Host operation. The signals are as follows:

- dpivsync_edpiwms : A signal that goes high at the start and remains high until after the PRESP_TO_active signal goes high.

- dpidataen : A signal that pulses high three times during the initial phase, corresponding to the transmission of data packets A10, A20, and A30.

- dpidata[29:0] : A bus showing data packets A10, A20, and A30 being transmitted, separated by idle periods (indicated by 'x').

- edpi_fifo_empty : A signal that goes low when the FIFO is empty and returns high when it is no longer empty.

- gen_wr_en : A signal that pulses high twice, corresponding to the transmission of data packet B3.

- gen_data[31:0] : A bus showing data packet B3 being transmitted, with other periods of inactivity (indicated by 'x').

- link_state[1:0] : A signal indicating the link state, alternating between LP (Low Power) and HS (High Speed) states.

- link_data[31:0] : A bus showing multiple data packets being transmitted, with idle periods (indicated by 'x').

- RESP_TO_active : A signal that goes high when the PRESP_TO counter is active and returns low when it completes.

The diagram shows that when PRESP_TO is active, the transmission of non-adapted command mode requests (like those on the gen_data bus) is suspended until the counter completes. The identifier MSv35880V1 is present in the bottom right corner.

34.9 Functional description: transmission of commands

34.9.1 Transmission of commands in video mode

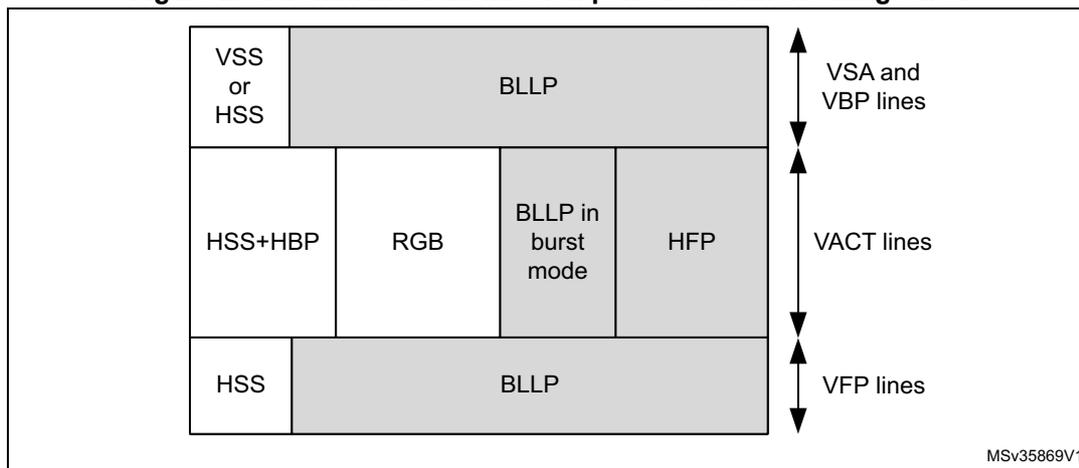

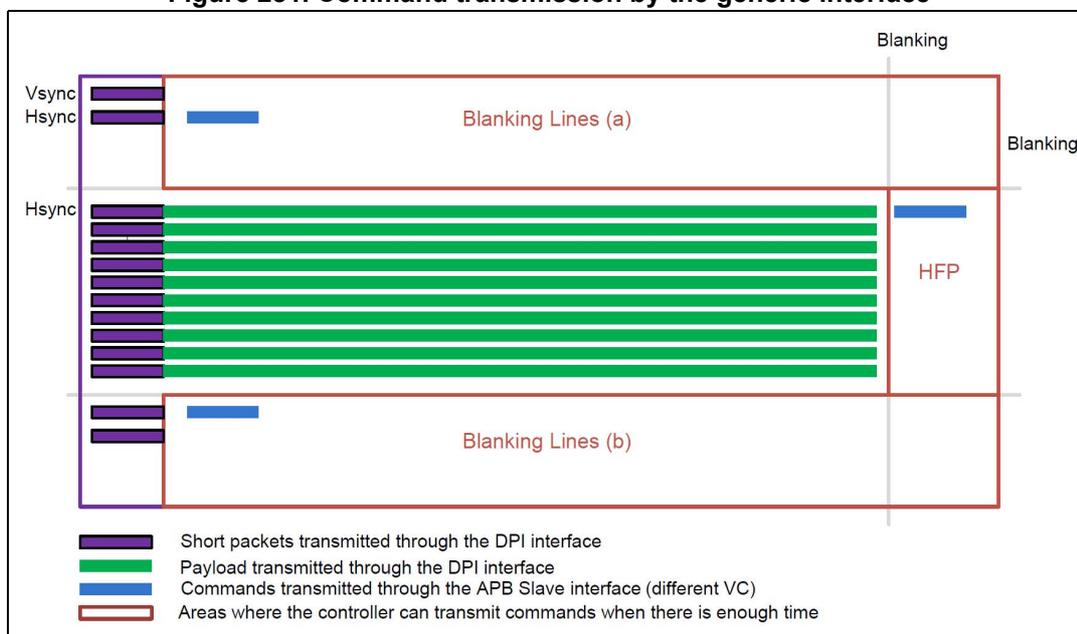

The DSI Host supports the transmission of commands, both in high-speed and low-power, while in video mode. The DSI Host uses blanking or low-power (BLLP) periods to transmit commands inserted through the APB generic interface. Those periods correspond to the gray areas of Figure 270 .

Figure 270. Command transmission periods within the image area

Commands are transmitted in the blanking periods after the following packets/states:

- • Vertical Sync Start (VSS) packets, if the video sync pulses are not enabled

- • Horizontal sync end (HSE) packets, in the VSA, VBP, and VFP regions

- • Horizontal sync Start (HSS) packets, if the video sync pulses are not enabled in the VSA, VBP, and VFP regions

- • Horizontal active (HACT) state

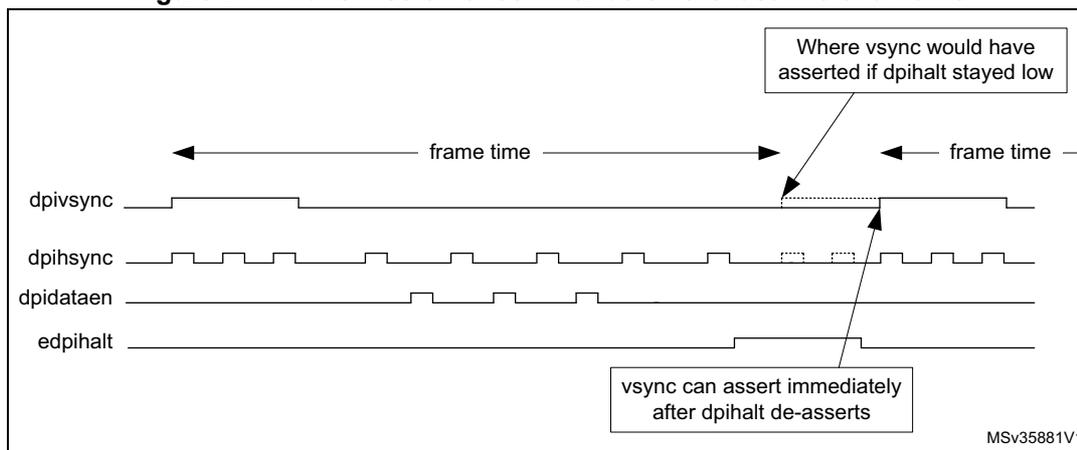

Besides the areas corresponding to BLLP, large commands can also be sent during the last line of a frame. In that case, the line time for the video mode is violated and the edpihalt signal is set to request the DPI video timing signals to remain inactive. Only if a command does not fit into any BLLP area, it is postponed to the last line, causing the violation of the line time for the video mode, as illustrated in Figure 271 .

Figure 271. Transmission of commands on the last line of a frame

Only one command is transmitted per line, even in the case of the last line of a frame but one command is possible for each line.

There can be only one command sent in low-power per line. However, one low-power command is possible for each line. In high-speed, the DSI Host can send more than one command, as many as it determines to fit in the available time.

The DSI Host avoids sending commands in the last line because it is possible that the last line is shorter than the other ones. For instance, the line time ( \( t_L \) ) can be half a cycle longer than the \( t_L \) on the LTDC interface, that is, each line in the frame taking half a cycle from time for the last line. This results in the last line being \( (\frac{1}{2} \text{ cycle}) \times (\text{number of lines} - 1) \) shorter than \( t_L \) .

The COLM and SHTDN bits of the DSI Wrapper control register (DSI_WCR) are also able to trigger the sending of command packets. The commands are:

- • Color mode ON

- • Color mode OFF

- • Shut down peripheral

- • Turn on peripheral

These commands are not sent in the VACT region. If the low-power command enable (LPCE) bit of the DSI Host video mode configuration register (DSI_VMCR) is set, these commands are sent in low-power mode.

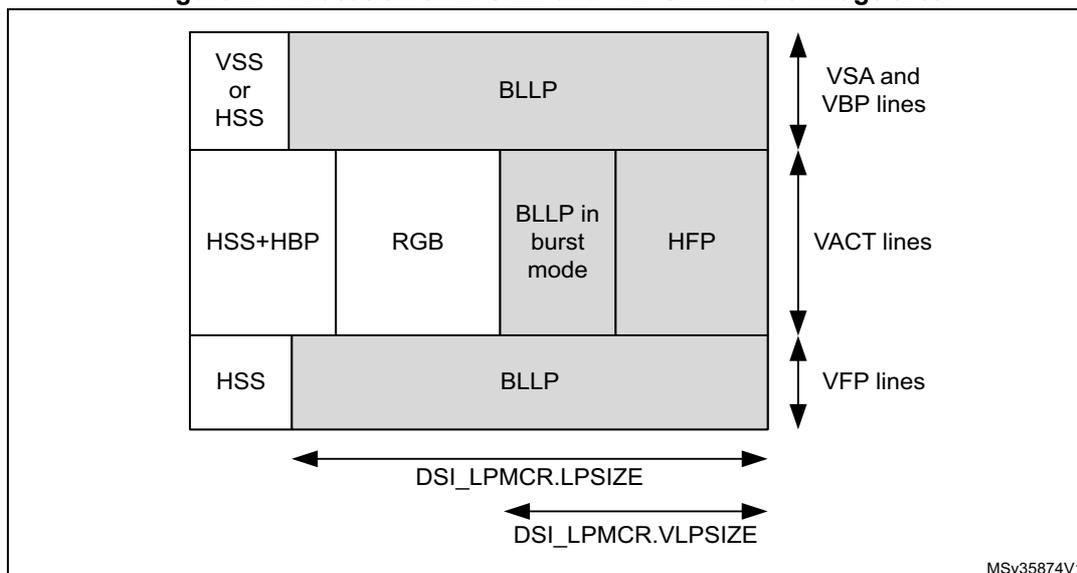

In low-power mode, the largest packet size (LPSIZE) field of the DSI Host low-power mode configuration register (DSI_LPMCR) is used to determine if these commands can be transmitted. It is assumed that largest packet size (LPSIZE) is greater than or equal to four bytes (number of bytes in a short packet), because the DSI Host does not transmit these commands on the last line.

If the frame bus-turn-around acknowledge enable (FBTAEE) bit is set in the DSI Host low-power mode configuration register (DSI_LPMCR), a BTA is generated by DSI Host after the last line of a frame. This may coincide with a write command or a read command. In either case, the LTDC interface is halted until an acknowledge is received (control of the DSI bus is returned to the host).

34.9.2 Transmission of commands in low-power mode

DSI Host can be configured to send the low-power commands during the high-speed video mode transmission.

To enable this feature, set the Low Power command enable (LPCE) bit of the DSI Host video mode configuration register (DSI_VMCR) to 1. In this case, it is necessary to calculate the time available, in bytes, to transmit a command in low-power mode to horizontal front-porch (HFP), vertical sync active (VSA), vertical back-porch (VBP), and vertical front-porch (VFP) regions.

Bits 8 to 13 of the video mode configuration register (DSI_VMCR) indicate if DSI Host can go to LP when idle. If the low-power command enable (LPCE) bit is set and non-video packets are in queue, DSI Host ignores the low-power configuration and transmits low-power commands, even if it is not allowed to enter low-power mode in a specific region. After the low-power commands transmission, DSI Host remains in low-power until a sync event occurs.

For example, consider that the VFP is selected as high-speed region (LPVFPE = 1'b0) with LPCE set as a command to transmit in low-power in the VPF region. This command is transmitted in low-power, and the line stays in low-power mode until a new HSS arrives.

Calculating the time to transmit commands in LP mode in the VSA, VBP, and VFP regions

The largest packet size (LPSIZE) field of the DSI Host low-power mode configuration register (DSI_LPMCR) indicates the time available (in bytes) to transmit a command in low-power mode (based on the escape clock) on a line during the VSA, VBP, and the VFP regions.

Calculation of largest packet size (LPSIZE) depends on the used video mode.

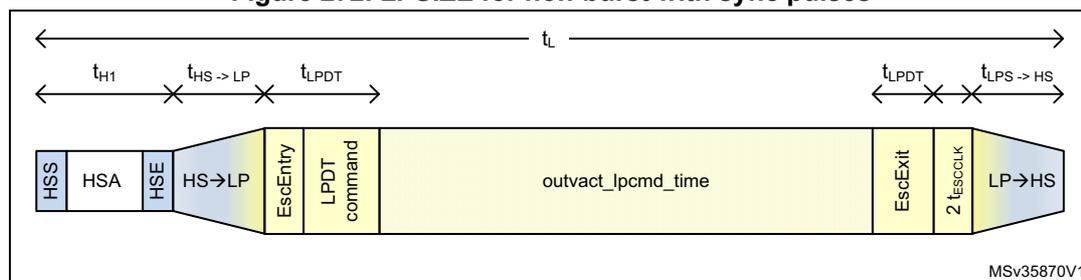

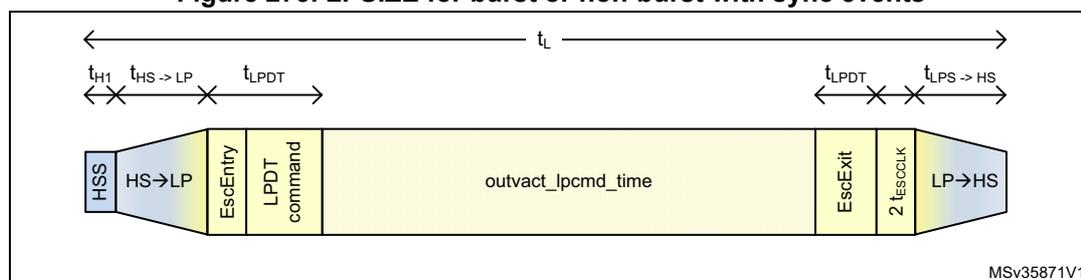

Figure 272 illustrates the timing intervals for the video mode in non-burst with sync pulses, while Figure 273 refers to video mode in burst and non-burst with sync events.

Figure 272. LPSIZE for non-burst with sync pulses

The diagram shows the timing for non-burst mode with sync pulses. The sequence starts with HSS, HSA, and HSE packets. This is followed by a transition block HS→LP. The low-power phase consists of an EscEntry block, an LPDT command block, a large outvact_lpcmd_time block, an EscExit block, and a 2 t ESCCLK block. The sequence ends with a transition block LP→HS. Timing intervals are defined as: \( t_{H1} \) (HSS to HSA), \( t_{HS \rightarrow LP} \) (HSA to start of LP), \( t_{LPDT} \) (duration of EscEntry and LPDT command), \( t_{LPDT} \) (duration of EscExit and 2 t ESCCLK ), and \( t_{LPS \rightarrow HS} \) (LP to HS transition). The total line time is \( t_L \) . Label: MSV35870V1.

Figure 273. LPSIZE for burst or non-burst with sync events

The diagram shows the timing for burst or non-burst mode with sync events. The sequence starts with an HSS packet, followed immediately by a transition block HS→LP. The low-power phase consists of an EscEntry block, an LPDT command block, a large outvact_lpcmd_time block, an EscExit block, and a 2 t ESCCLK block. The sequence ends with a transition block LP→HS. Timing intervals are defined as: \( t_{H1} \) (HSS duration), \( t_{HS \rightarrow LP} \) (HSS to start of LP), \( t_{LPDT} \) (duration of EscEntry and LPDT command), \( t_{LPDT} \) (duration of EscExit and 2 t ESCCLK ), and \( t_{LPS \rightarrow HS} \) (LP to HS transition). The total line time is \( t_L \) . Label: MSV35871V1.

This time is calculated as follows:

- • \( t_L \) = line time

- • \( t_{H1} \) = time of the HSA pulse for sync pulses mode ( Figure 272 ) or time to send the HSS packet, including EoTp ( Figure 273 )

- • \( t_{\text{HS}\rightarrow\text{LP}} \) = time to enter the low-power mode

- • \( t_{\text{LP}\rightarrow\text{HS}} \) = time to leave the low-power mode

- • \( t_{\text{LPDT}} \) = D-PHY timing related with escape mode entry, LPDT command, and escape exit. According to the D-PHY specification, this value is always 11 bits in LP (or 22 TX escape clock cycles)

- • \( t_{\text{ESCCCLK}} \) = escape clock period as programmed in the TXECKDIV field of the DSI_CCR register

- • \( t_{\text{ESCCCLK}} \) = delay imposed by the DSI Host implementation.

In the above equation, division by eight is done to convert the available time to bytes. Division by two is done because one bit is transmitted every two escape clock cycles. The largest packet size (LPSIZE) field can be compared directly with the size of the command to be transmitted to determine if there is enough time to transmit the command. The maximum size of a command that can be transmitted in low-power mode is limited to 255 bytes by this field. Program this register to a value greater than or equal to 4 bytes for the transmission of the DCTRL commands, such as shutdown and color in low-power mode.

Consider an example of a frame with 12.4 \( \mu\text{s} \) per line and assume an escape clock frequency of 20 MHz and a lane bit rate of 800 Mbit/s. In this case, it is possible to send 124 bits in escape mode (that is, 124 bit = 12.4 \( \mu\text{s} \) * 20 MHz / 2). Still, you need to consider the D-PHY protocol and PHY timings.

The following assumptions are made:

- • lane byte clock period is 10 ns (800 Mbit/s per lane)

- • escape clock period is 50 ns (DSI_CCR.TXECKDIV = 5)

- • video is transmitted in non-burst mode with sync pulses bounded by HSS and HSE packets

- • DSI is configured for two lanes

- • D-PHY takes 180 ns to transit from low-power to high-speed mode (DSI_DLTCCR.LS2HS_TIME = 18)

- • D-PHY takes 200 ns to transit from high-speed to low-power mode (DSI_DLTCCR.HS2LP_TIME = 20)

- • \( t_{\text{HSA}} = 420 \text{ ns} \) .

In this example, a 13-byte command can be transmitted as follows:

Calculating the time to transmit commands in low-power mode in HFP region

The VACT largest packet size (VLPSIZE) field of the DSI Host low-power mode configuration register (DSI_LPMCR) indicates the time available (in bytes) to transmit a command in low-power mode (based on the escape clock) in the vertical active (VACT) region.

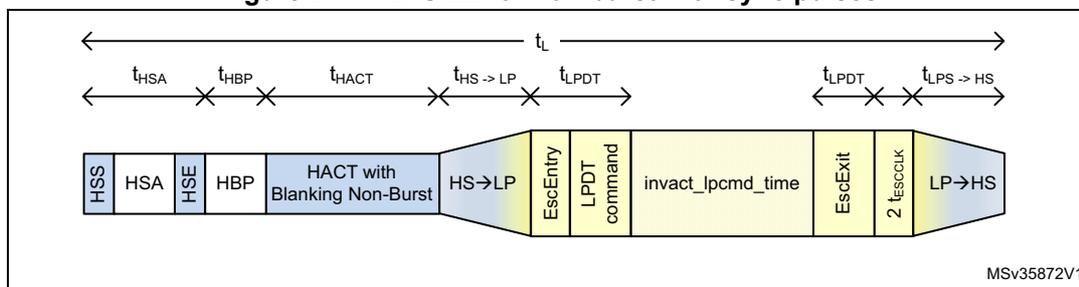

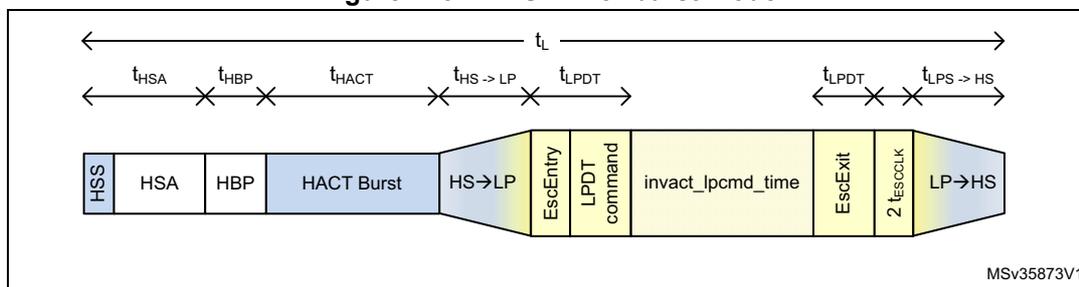

To calculate the value of VACT largest packet size (VLPSIZE), consider the video mode being used. Figure 274 shows the timing intervals for video mode in non-burst with sync pulses, Figure 275 those for video mode in non-burst with sync events, and Figure 276 refers to the burst video mode.

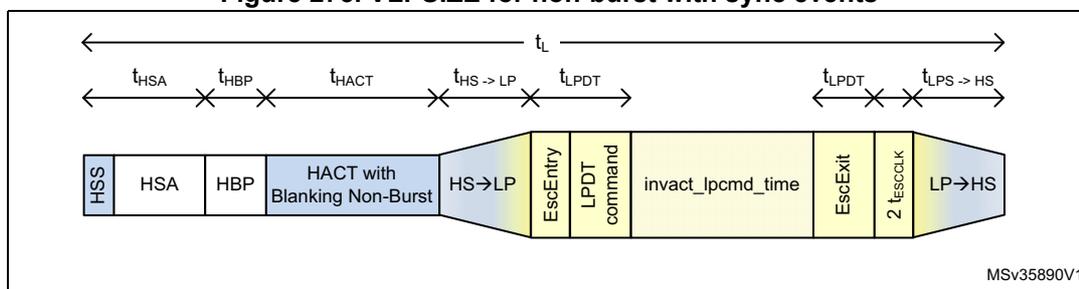

Figure 274. VLPSIZE for non-burst with sync pulses

Timing diagram for non-burst with sync pulses. The diagram shows a sequence of signal states and timing intervals. The signal starts in HSS (High Speed Sync) state, followed by HSA (Horizontal Sync Active), HBP (Horizontal Back Porch), and HACT with Blanking Non-Burst. It then transitions to HS→LP (High Speed to Low Power) state, followed by EscEntry, LPDT command, invact_lpcmd_time, EscExit, 2 t ESCCLK , and LP→HS (Low Power to High Speed) state. The total line time is t L . The timing intervals are defined as follows: t HSA (time of the HSA pulse), t HBP (time of horizontal back-porch), t HACT (time of video active), t HS→LP (time of HS→LP transition), t LPDT (time of LPDT command), and t LP→HS (time of LP→HS transition).

Figure 275. VLPSIZE for non-burst with sync events

Timing diagram for non-burst with sync events. The diagram shows a sequence of signal states and timing intervals. The signal starts in HSS (High Speed Sync) state, followed by HSA (Horizontal Sync Active), HBP (Horizontal Back Porch), and HACT with Blanking Non-Burst. It then transitions to HS→LP (High Speed to Low Power) state, followed by EscEntry, LPDT command, invact_lpcmd_time, EscExit, 2 t ESCCLK , and LP→HS (Low Power to High Speed) state. The total line time is t L . The timing intervals are defined as follows: t HSA (time of the HSA pulse), t HBP (time of horizontal back-porch), t HACT (time of video active), t HS→LP (time of HS→LP transition), t LPDT (time of LPDT command), and t LP→HS (time of LP→HS transition).

Figure 276. VLPSIZE for burst mode

Timing diagram for burst mode. The diagram shows a sequence of signal states and timing intervals. The signal starts in HSS (High Speed Sync) state, followed by HSA (Horizontal Sync Active), HBP (Horizontal Back Porch), and HACT Burst. It then transitions to HS→LP (High Speed to Low Power) state, followed by EscEntry, LPDT command, invact_lpcmd_time, EscExit, 2 t ESCCLK , and LP→HS (Low Power to High Speed) state. The total line time is t L . The timing intervals are defined as follows: t HSA (time of the HSA pulse), t HBP (time of horizontal back-porch), t HACT (time of video active), t HS→LP (time of HS→LP transition), t LPDT (time of LPDT command), and t LP→HS (time of LP→HS transition).

This time is calculated as follows:

where

- • \( t_L \) = line time

- • \( t_{\text{HSA}} \) = time of the HSA pulse (DSI_VHSACR.HSA)

- • \( t_{\text{HBP}} \) = time of horizontal back-porch (DSI_VHBPCR.HBP)

- • \( t_{\text{HACT}} \) = time of video active. For burst mode, the video active is time compressed and is calculated as \( t_{\text{HACT}} = \text{VPSIZE} \times \text{Bytes\_per\_Pixel} / \text{Number\_Lanes} \times t_{\text{Lane\_byte\_clk}} \)

- • \( t_{\text{ESCCLK}} \) = escape clock period as programmed in TXECKDIV field of the DSI_CCR register.

The VLPSIZE field can be compared directly with the size of the command to be transmitted to determine if there is time to transmit the command.

Consider an example of a frame with 16.4 \( \mu\text{s} \) per line and assume an escape clock frequency of 20 MHz and a lane bit rate of 800 Mbits/s. In this case, it is possible to send 420 bits in escape mode (that is, \( 164 \text{ bits} = 16.4 \mu\text{s} \times 20 \text{ MHz} / 2 \) ). Still, since it is the vertical active region of the frame, consider the HSA, HBP, and HACT timings apart from the D-PHY protocol and PHY timings. The following assumptions are made:

- • number of active lanes is four

- • Lane byte clock period (lanebyteclkperiod) is 10 ns (800 Mbit/s per lane)

- • escape clock period is 50 ns (DSI_CCR.TXECKDIV = 5)

- • D-PHY takes 180 ns to pass from low-power to high-speed mode (DSI_DLTCCR.LP2HS_TIME = 18)

- • D-PHY takes 200 ns to pass from high-speed to low-power mode (DSI_DLTCCR.HS2LP_TIME = 20)

- • \( t_{\text{HSA}} = 420 \text{ ns} \)

- • \( t_{\text{HBP}} = 800 \text{ ns} \)

- • \( t_{\text{HACT}} = 12800 \text{ ns} \) to send 1280 pixel at 24 bpp

- • video is transmitted in non-burst mode

- • DSI is configured for four lanes.

In this example, consider that video is sent in non-burst mode. The VLPSIZE is calculated as follows:

Only one byte can be transmitted in this period. A short packet (for example, generic short write) requires a minimum of four bytes. Therefore, in this example, commands are not sent in the VACT region.

If burst mode is enabled, more time is available to transmit the commands in the VACT region, because HACT is time compressed.

For burst mode, the VLPSIZE is 5 bytes and then a 4-byte short packet can be sent.

Transmission of commands in different periods

The LPSIZE and VLPSIZE fields allow a simple comparison to determine if a command can be transmitted in any of the BLLP periods.

Figure 277 illustrates the meaning of VLPSIZE and LPSIZE, matching them with the shaded areas and the VACT region.

Figure 277. Location of LPSIZE and VLPSIZE in the image area

34.9.3 Transmission of commands in high-speed

If the LPCE bit of the DSI_VMCR register is 0, the commands are sent in high-speed video mode. In this case, the DSI Host automatically determines the area where each command can be sent and no programming or calculation is required.

34.9.4 Read command transmission

The MRD_TIME field of the DSI_DLTCR register configures the maximum amount of time required to perform a read command in lane byte clock cycles, it is calculated as:

MRD_TIME = time to transmit the read command in low-power mode + time to enter and leave low-power mode + time to return the read data packet from the peripheral device.

The time to return the read data packet from the peripheral depends on the number of bytes read and the escape clock frequency of the peripheral, not the escape clock of the host. The MRD_TIME field is used in both high-speed and low-power mode to determine if there is time to complete a read command in a BLLP period.

In high-speed mode (LPCE = 0), MRD_TIME is calculated as follows:

In low-power mode (LPCE = 1), MRD_TIME is calculated as follows:

- • \( t_{\text{HS}\rightarrow\text{LP}} \) = time to enter the low-power mode

- • \( t_{\text{LP}\rightarrow\text{HS}} \) = time to leave the low-power mode

- • \( t_{\text{LPDT}} \) = D-PHY timing related to escape mode entry, LPDT command, and escape mode exit (according to the D-PHY specification, this value is always 11 bits in LP, or 22 TX escape clock cycles)

- • \( t_{\text{lprd}} \) = read command time in low-power mode ( \( 64 \times \text{TX esc clock} \) )

- • \( t_{\text{read}} \) = time to return the read data packet from the peripheral

- • \( t_{\text{BTA}} \) = time to perform a bus-turn-around (D-PHY dependent).

Keep the maximum number of bytes read from the peripheral to a minimum, to issue the read commands in a line time. Ensure that \( MRD\_TIME \times \text{lane byte clock period} \) is less than \( LPSIZE \times 16 \times \text{escape clock period of the host} \) , otherwise, the read commands are dispatched on the last line of a frame. If it is necessary to read a large number of parameters ( \( > 16 \) ), increase the \( MRD\_TIME \) while the read command is executed. When the read has completed, decrease the \( MRD\_TIME \) to a lower value.

If a read command is issued on the last line of a frame, the LTDC interface is halted and stays halted until the read command is in progress. The video transmission must be stopped during this period.

34.9.5 Clock lane in low-power mode

To reduce the power consumption of the D-PHY, the DSI Host, when not transmitting in the high-speed mode, allows the clock lane to enter into the low-power mode. The controller automatically handles the transition of the clock lane from HS (clock lane active sending clock) to LP state without direct intervention by the software. This feature can be enabled by configuring the DPCC and the ACR bits of the DSI_CLCR register.

In the command mode, the DSI Host can place the clock lane in the low-power mode when it does not have any HS packets to transmit.

In the video mode (LTDC interface), the DSI Host controller uses its internal video and PHY timing configurations to determine if there is time available for the clock line to enter the low-power mode and not compromise the video data transmission of pixel data and sync events.

Along with a correct configuration of the video mode (see Section 34.5: Functional description: video mode on LTDC interface ), the DSI Host needs to know the time required by the clock lane to go from high-speed to low-power mode and vice-versa. The values required can be obtained from the D-PHY specification: program the DSI_CLTCR register with the following values:

- • \( HS2LP\_TIME \) = time from HS to LP in clock lane / byte clock period in HS (lanebyteclk)

- • \( LP2HS\_TIME \) = time from LP to HS in clock lane / byte clock period in HS (lanebyteclk)

Based on the programmed values, the DSI Host calculates if there is enough time for the clock lane to enter the low-power mode during inactive regions of the video frame.

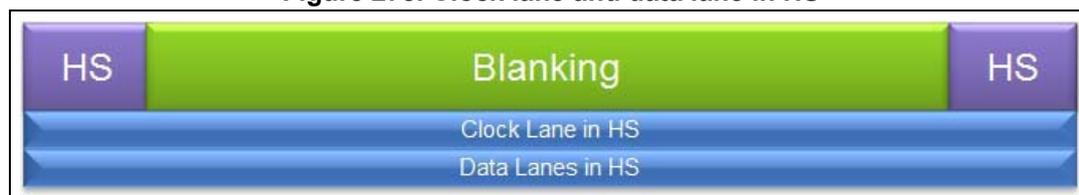

The DSI Host decides the best approach to follow regarding power saving out of the three possible scenarios:

- • there is no enough time to go to the low-power mode. Therefore, blanking period is added as shown in Figure 278

- • there is enough time for the data lanes to go to the low-power mode but not enough time for the clock lane to enter the low-power mode, see Figure 279 .

- • there is enough time for both data lanes and clock lane to go to the low-power mode, as in Figure 280 .

Figure 278. Clock lane and data lane in HS

The diagram illustrates the timing for the Clock Lane and Data Lanes in High-Speed (HS) mode. It is divided into three horizontal segments: a purple segment labeled 'HS' on the left, a green segment labeled 'Blanking' in the center, and another purple segment labeled 'HS' on the right. Below the green 'Blanking' segment, there are two blue horizontal bars. The top blue bar is labeled 'Clock Lane in HS' and the bottom blue bar is labeled 'Data Lanes in HS'. This indicates that both the clock lane and data lanes remain in high-speed mode throughout the entire frame, including the blanking period.

Figure 279. Clock lane in HS and data lanes in LP

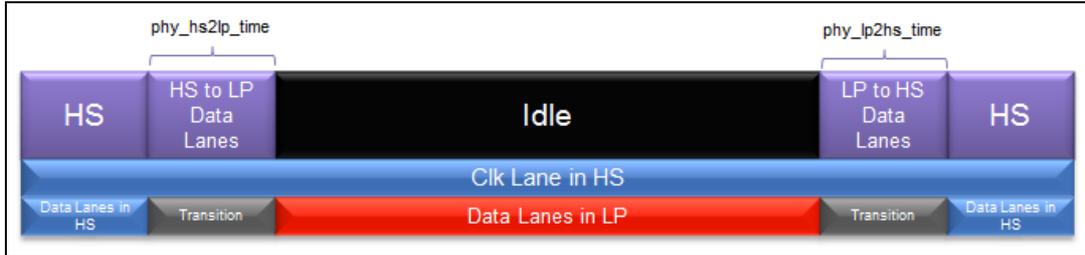

This diagram illustrates the timing sequence for a DSI interface where the clock lane remains in High-Speed (HS) mode while data lanes switch to Low-Power (LP) mode. The top row shows the state of the lanes: starting with 'HS', followed by 'HS to LP Data Lanes' (duration \( phy\_hs2lp\_time \) ), an 'Idle' state, 'LP to HS Data Lanes' (duration \( phy\_lp2hs\_time \) ), and returning to 'HS'. The middle row shows the 'Clk Lane in HS' as a continuous blue signal. The bottom row shows the 'Data Lanes' transitioning from 'Data Lanes in HS' (blue) through a 'Transition' (grey) to 'Data Lanes in LP' (red), then back through a 'Transition' (grey) to 'Data Lanes in HS' (blue).

Figure 280. Clock lane and data lane in LP

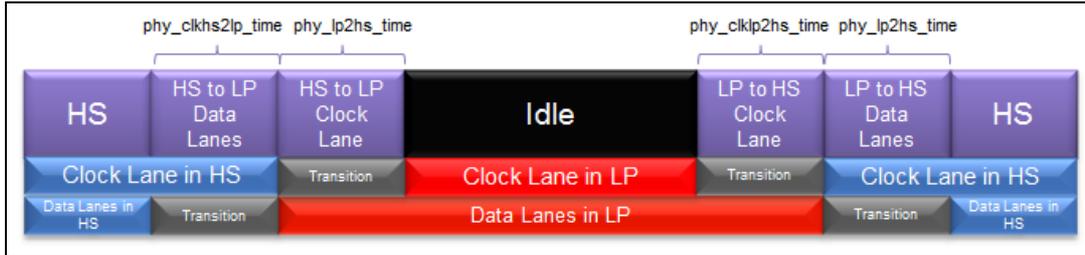

This diagram illustrates the timing sequence for a DSI interface where both the clock and data lanes switch to Low-Power (LP) mode. The top row shows the state: 'HS', 'HS to LP Data Lanes' ( \( phy\_clkhs2lp\_time \) ), 'HS to LP Clock Lane' ( \( phy\_lp2hs\_time \) ), 'Idle', 'LP to HS Clock Lane' ( \( phy\_clklp2hs\_time \) ), 'LP to HS Data Lanes' ( \( phy\_lp2hs\_time \) ), and 'HS'. The middle row shows the 'Clock Lane' transitioning from 'Clock Lane in HS' (blue) to 'Clock Lane in LP' (red) during the 'HS to LP Clock Lane' phase, and returning to 'Clock Lane in HS' (blue) during the 'LP to HS Clock Lane' phase. The bottom row shows the 'Data Lanes' transitioning from 'Data Lanes in HS' (blue) to 'Data Lanes in LP' (red) during the 'HS to LP Data Lanes' phase, and returning to 'Data Lanes in HS' (blue) during the 'LP to HS Data Lanes' phase. Both transitions include 'Transition' (grey) periods.

34.10 Functional description: virtual channels

The DSI Host supports choosing the virtual channel (VC) for use for each interface. Using multiple virtual channels, the system can address multiple displays at the same time, when each display has a different virtual channel identifier.

When the LTDC interface is configured for a particular virtual channel, it is possible to use the APB slave generic interface to issue the commands while the video stream is being transmitted. With this, it is possible to send the commands through the ongoing video stream, addressing different virtual channels and thus enable the interface with multiple displays. During the video mode, the video stream transmission has the maximum priority. Therefore, the transmission of sideband packets such as the ones from the generic interface are only transported when there is time available within the video stream transmission. The DSI Host identifies the available time periods and uses them to transport the generic interface packets. Figure 281 illustrates where the DSI Host inserts the packets from the APB generic interface within the video stream transmitted by the LTDC interface.

Figure 281. Command transmission by the generic interface

The diagram illustrates the timing of data transmission over a video interface. The vertical axis represents the sequence of lines in a video frame, with labels for Vsync, Hsync, and Hsync. The horizontal axis represents time.

Key elements include:

- Blanking Lines (a) and (b): Red rectangular regions indicating the time intervals for horizontal blanking.

- Blanking: Labels on the right side of the diagram pointing to the blanking intervals.

- HFP: Horizontal Front Porch, indicated by a label in the active video area.

- Legend:

- Short packets transmitted through the DPI interface

- Payload transmitted through the DPI interface

- Commands transmitted through the APB Slave interface (different VC)

- Areas where the controller can transmit commands when there is enough time

It is also possible to address the multiple displays with only the generic interface using different virtual channels. Because the generic interface is not restricted to any particular virtual channel through configuration, it is possible to issue the packets with different virtual channels. This enables the interface to time multiplex the packets to be provided to the displays with different virtual channels.

You can use the following configuration registers to select the virtual channel ID associated with transmissions over the LTDC and APB slave generic interfaces:

- • DSI_LVCIIDR.VCID field configures the virtual channel ID that is indexed to the video mode packets using the LTDC interface.

- • DSI_GHCR register configures the packet header (which includes the virtual channel ID to be used) for transmissions using APB slave generic interface.

- • DSI_GVCIDR register configures the virtual channel ID of the read responses to store and return to the generic interface.

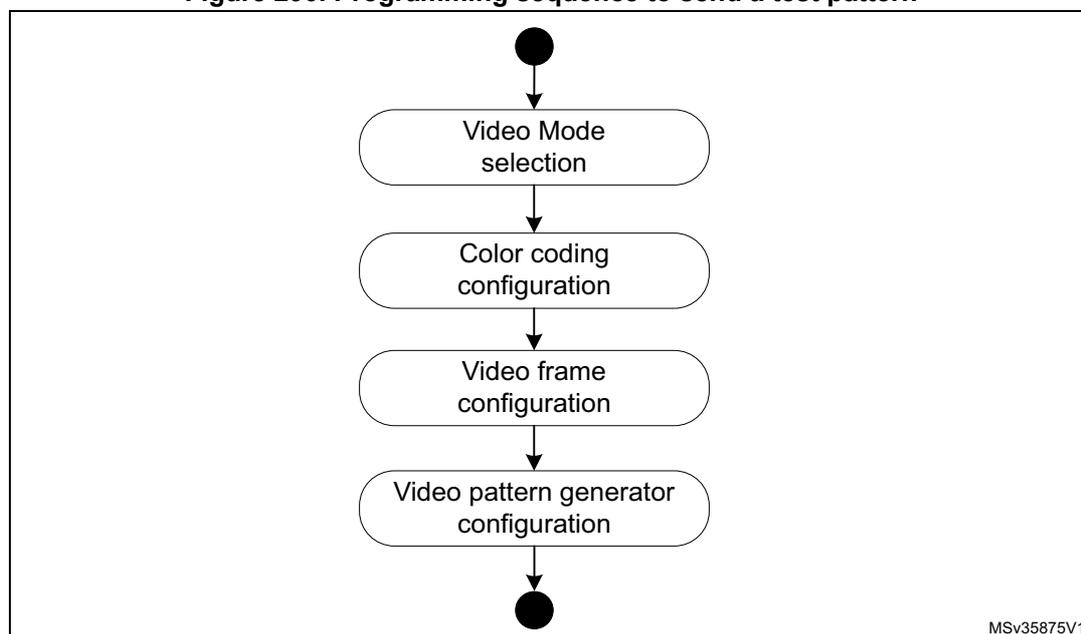

34.11 Functional description: video mode pattern generator

The video mode pattern generator allows the transmission of horizontal/vertical color bar and D-PHY BER testing pattern without any stimuli.

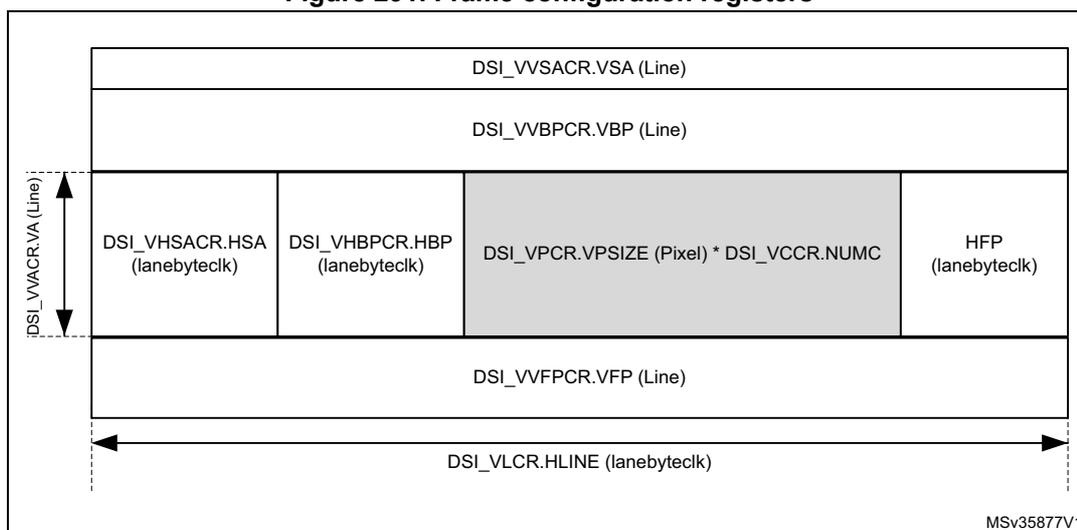

The frame requirements must be defined in video registers that are listed in Table 286 .

Table 286. Frame requirement configuration registers

| Register name | Description |

|---|---|

| DSI Host video mode configuration | Video mode configuration |

| DSI Host video packet configuration | Video packet size |

| DSI Host video chunks configuration | Number of chunks |

| DSI Host video null packet configuration | Null packet size |

| DSI Host video HSA configuration | Horizontal sync active time |

| DSI Host video HBP configuration | Horizontal back-porch time |

| DSI Host video line configuration | Line time |

| DSI Host video VSA configuration | Vertical sync active period |

| DSI Host video VBP configuration | Vertical back-porch period |

| DSI Host video VFP configuration | Vertical front-porch period |

| DSI Host video VA configuration | Vertical resolution |

34.11.1 Color bar pattern

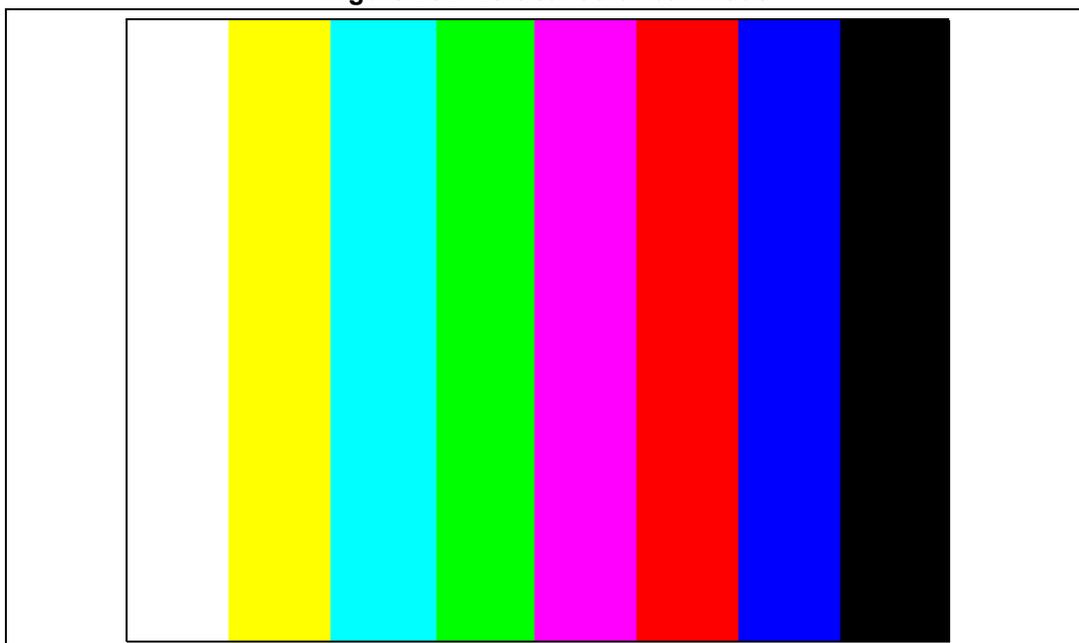

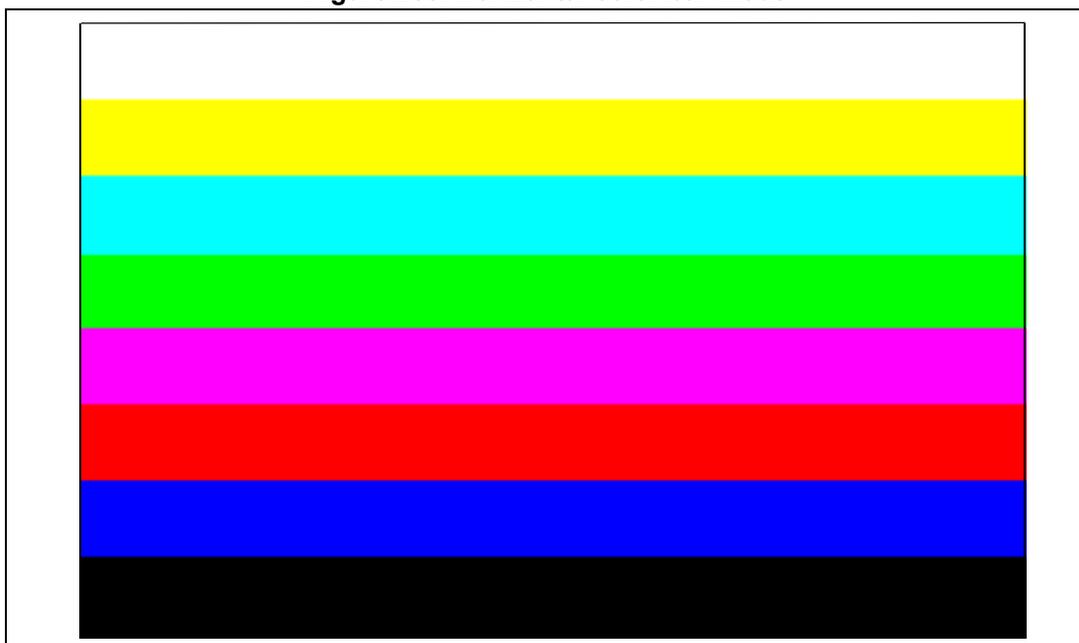

The color bar pattern comprises eight bars for white, yellow, cyan, green, magenta, red, blue, and black colors.

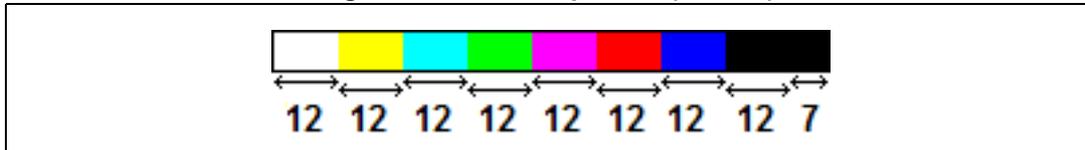

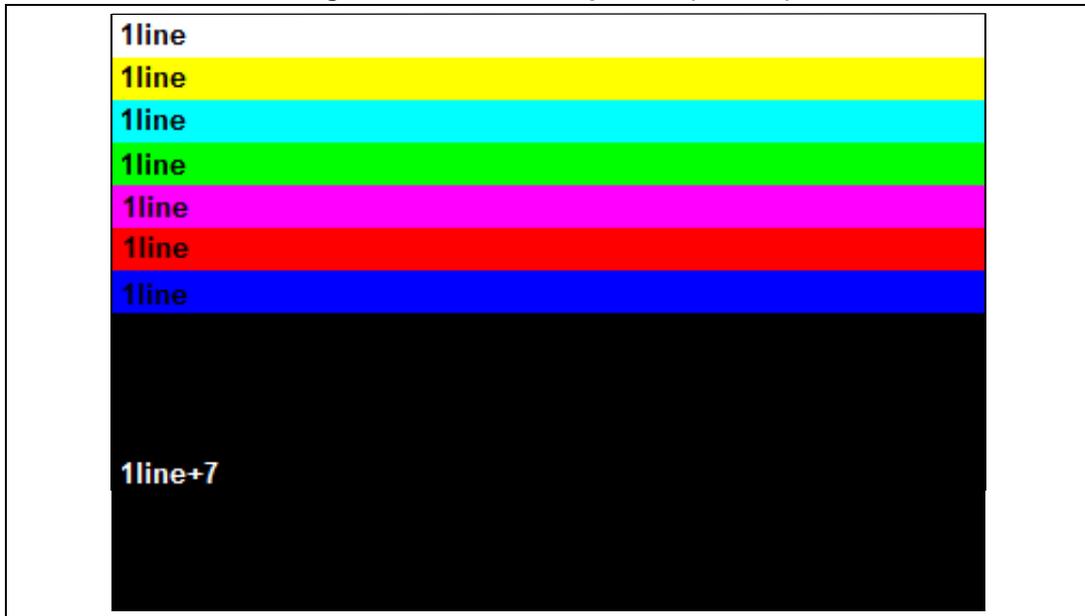

Each color width is calculated by dividing the line pixel size (vertical pattern) or the number of lines (horizontal pattern) by eight. In the vertical color bar mode ( Figure 282 ), each single color bar has a width of the number of pixels in a line divided by eight. In case the number of pixels in a line is not divisible by eight, the last color (black) contains the remaining.