19. Basic timers (TIM6&TIM7)

19.1 TIM6&TIM7 introduction

The basic timers TIM6 and TIM7 consist of a 16-bit auto-reload counter driven by a programmable prescaler.

They may be used as generic timers for time-base generation but they are also specifically used to drive the digital-to-analog converter (DAC). In fact, the timers are internally connected to the DAC and are able to drive it through their trigger output.

The timers are completely independent, and do not share any resources.

19.2 TIM6&TIM7 main features

Basic timer (TIM6&TIM7) features include:

- • 16-bit auto-reload upcounter

- • 16-bit programmable prescaler used to divide (also “on the fly”) the counter clock frequency by any factor between 1 and 65536

- • Synchronization circuit to trigger the DAC

- • Interrupt/DMA generation on the update event: counter overflow

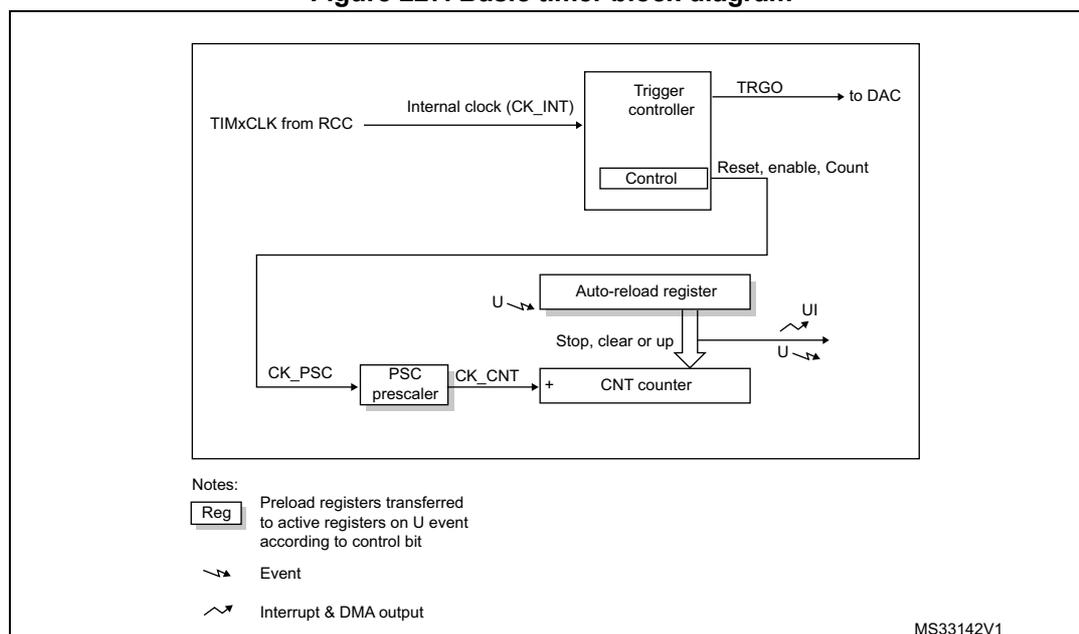

Figure 227. Basic timer block diagram

The block diagram illustrates the internal architecture of a basic timer (TIM6 or TIM7). At the top, a 'Trigger controller' block receives an 'Internal clock (CK_INT)' from the 'TIMxCLK from RCC' input. It has a 'Control' sub-block and outputs a 'TRGO' signal 'to DAC'. Below the trigger controller, a 'CNT counter' (labeled with a '+') receives a 'CK_CNT' signal from a 'PSC prescaler' block. The 'PSC prescaler' is driven by 'CK_PSC'. The 'CNT counter' is connected to an 'Auto-reload register' (labeled 'Reg'). The 'Auto-reload register' receives 'U' (Update) events and sends 'UI' (Update Interrupt) signals. It also provides 'Stop, clear or up' control signals to the counter. The 'Trigger controller' also provides 'Reset, enable, Count' signals to the counter. A legend at the bottom left explains the symbols: 'Reg' for preload registers, a single arrow for 'Event', and a wavy arrow for 'Interrupt & DMA output'. The diagram is labeled 'MS33142V1' in the bottom right corner.

Notes:

Reg

Preload registers transferred to active registers on U event according to control bit

➤ Event

⇝ Interrupt & DMA output

MS33142V1

19.3 TIM6&TIM7 functional description

19.3.1 Time-base unit

The main block of the programmable timer is a 16-bit upcounter with its related auto-reload register. The counter clock can be divided by a prescaler.

The counter, the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running.

The time-base unit includes:

- • Counter Register (TIMx_CNT)

- • Prescaler Register (TIMx_PSC)

- • Auto-Reload Register (TIMx_ARR)

The auto-reload register is preloaded. The preload register is accessed each time an attempt is made to write or read the auto-reload register. The contents of the preload register are transferred into the shadow register permanently or at each update event UEV, depending on the auto-reload preload enable bit (ARPE) in the TIMx_CR1 register. The update event is sent when the counter reaches the overflow value and if the UDIS bit equals 0 in the TIMx_CR1 register. It can also be generated by software. The generation of the update event is described in detail for each configuration.

The counter is clocked by the prescaler output CK_CNT, which is enabled only when the counter enable bit (CEN) in the TIMx_CR1 register is set.

Note that the actual counter enable signal CNT_EN is set 1 clock cycle after CEN.

Prescaler description

The prescaler can divide the counter clock frequency by any factor between 1 and 65536. It is based on a 16-bit counter controlled through a 16-bit register (in the TIMx_PSC register). It can be changed on the fly as the TIMx_PSC control register is buffered. The new prescaler ratio is taken into account at the next update event.

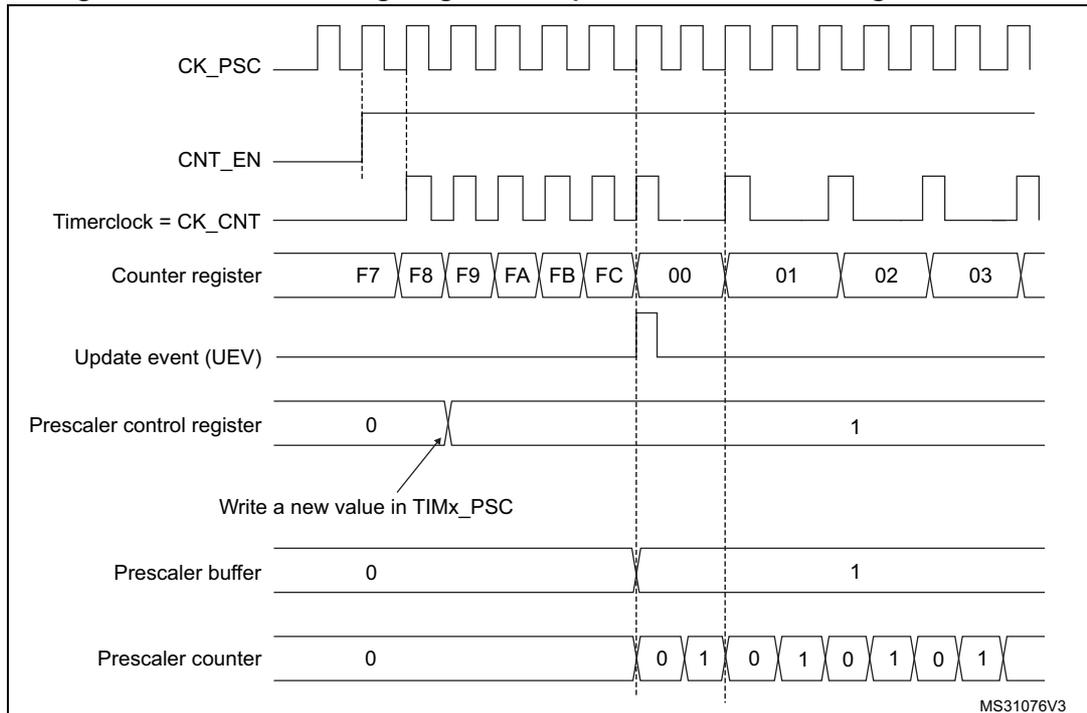

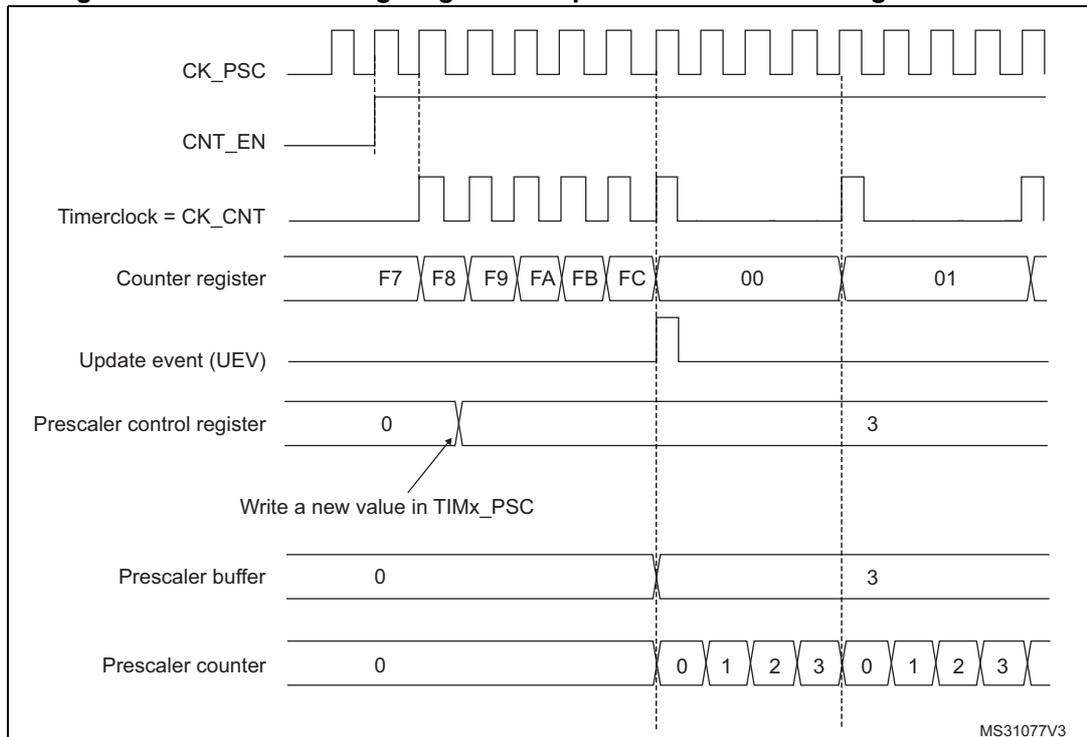

Figure 228 and Figure 229 give some examples of the counter behavior when the prescaler ratio is changed on the fly.

Figure 228. Counter timing diagram with prescaler division change from 1 to 2

Timing diagram for prescaler division change from 1 to 2. The diagram shows the relationship between the prescaler and the counter. The CK_PSC signal is a square wave. The CNT_EN signal is active-low. The Timerclock = CK_CNT signal is derived from CK_PSC. The Counter register shows values F7, F8, F9, FA, FB, FC, 00, 01, 02, 03. The Update event (UEV) is generated when the counter overflows. The Prescaler control register is initially 0 and is changed to 1. The Prescaler buffer is initially 0 and is updated to 1. The Prescaler counter counts 0, 1, 0, 1, 0, 1, 0, 1. The diagram is labeled MS31076V3.

Figure 229. Counter timing diagram with prescaler division change from 1 to 4

Timing diagram for prescaler division change from 1 to 4. The diagram shows the relationship between the prescaler and the counter. The CK_PSC signal is a square wave. The CNT_EN signal is active-low. The Timerclock = CK_CNT signal is derived from CK_PSC. The Counter register shows values F7, F8, F9, FA, FB, FC, 00, 01. The Update event (UEV) is generated when the counter overflows. The Prescaler control register is initially 0 and is changed to 3. The Prescaler buffer is initially 0 and is updated to 3. The Prescaler counter counts 0, 1, 2, 3, 0, 1, 2, 3. The diagram is labeled MS31077V3.

19.3.2 Counting mode

The counter counts from 0 to the auto-reload value (contents of the TIMx_ARR register), then restarts from 0 and generates a counter overflow event.

An update event can be generated at each counter overflow or by setting the UG bit in the TIMx_EGR register (by software or by using the slave mode controller).

The UEV event can be disabled by software by setting the UDIS bit in the TIMx_CR1 register. This avoids updating the shadow registers while writing new values into the preload registers. In this way, no update event occurs until the UDIS bit has been written to 0, however, the counter and the prescaler counter both restart from 0 (but the prescale rate does not change). In addition, if the URS (update request selection) bit in the TIMx_CR1 register is set, setting the UG bit generates an update event UEV, but the UIF flag is not set (so no interrupt or DMA request is sent).

When an update event occurs, all the registers are updated and the update flag (UIF bit in the TIMx_SR register) is set (depending on the URS bit):

- • The buffer of the prescaler is reloaded with the preload value (contents of the TIMx_PSC register)

- • The auto-reload shadow register is updated with the preload value (TIMx_ARR)

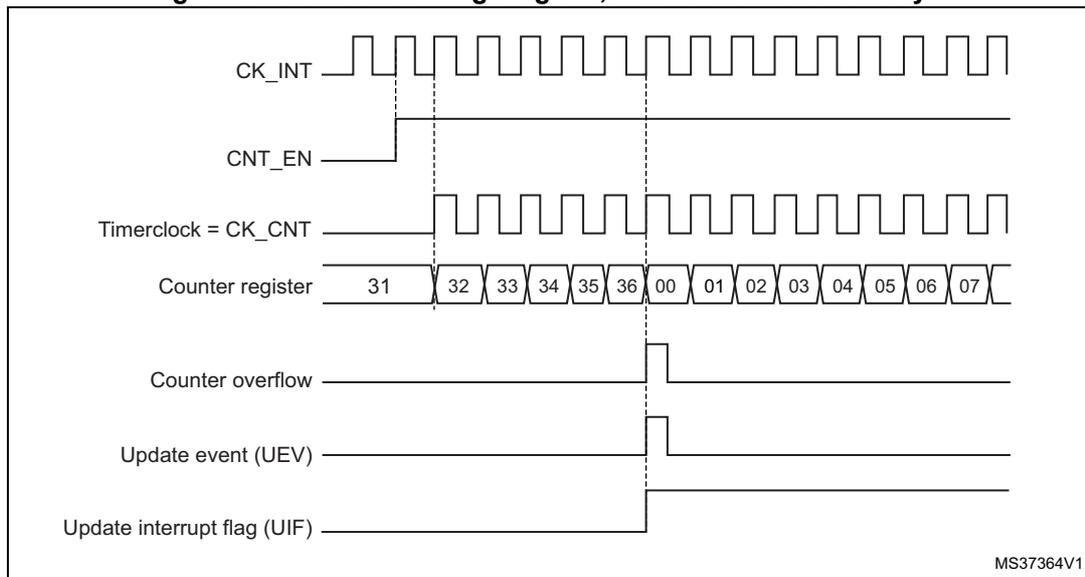

The following figures show some examples of the counter behavior for different clock frequencies when TIMx_ARR = 0x36.

Figure 230. Counter timing diagram, internal clock divided by 1

The timing diagram illustrates the counter's behavior over time. The top signal, CK_INT, is a continuous square wave representing the internal clock. Below it, CNT_EN is a signal that goes high to enable the counter. The third signal, Timerclock = CK_CNT, is a square wave that starts when CNT_EN goes high. The fourth signal, Counter register, shows a sequence of values: 31, 32, 33, 34, 35, 36, 00, 01, 02, 03, 04, 05, 06, 07. The counter increments by 1 at each rising edge of the timer clock. When the counter reaches 36 (0x36), it overflows to 00. The fifth signal, Counter overflow, is a pulse that goes high when the counter reaches 36 and returns low when it reaches 00. The sixth signal, Update event (UEV), is a pulse that goes high at the same time as the counter overflow. The seventh signal, Update interrupt flag (UIF), is a pulse that goes high at the same time as the counter overflow and returns low when the counter reaches 00. The diagram is labeled MS37364V1 in the bottom right corner.

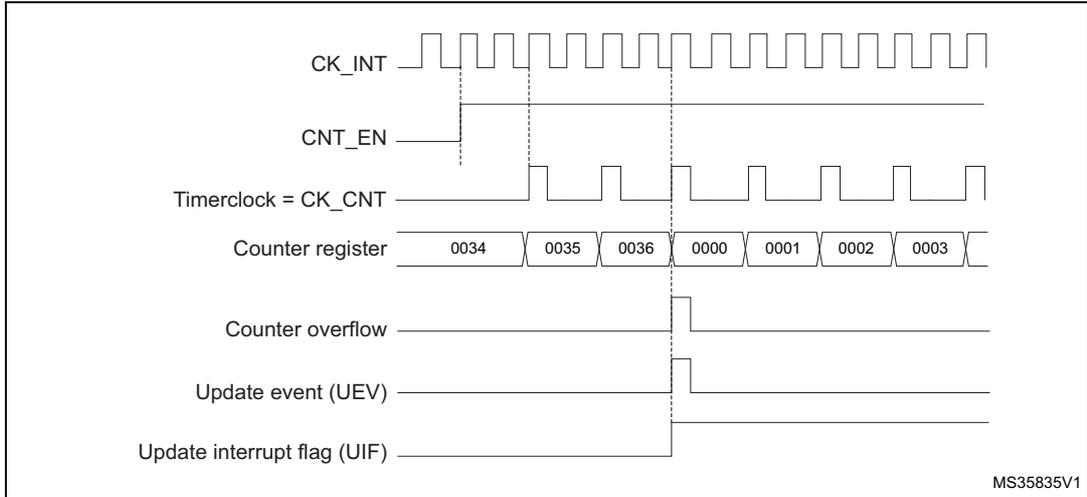

Figure 231. Counter timing diagram, internal clock divided by 2

This timing diagram illustrates the operation of a counter when the internal clock is divided by 2. The top signal, CK_INT, is a high-frequency square wave. Below it, CNT_EN is a horizontal line indicating the counter is enabled. The Timerclock = CK_CNT signal is a square wave with a period twice that of CK_INT. The Counter register shows a sequence of values: 0034, 0035, 0036, 0000, 0001, 0002, 0003. A 'Counter overflow' pulse occurs when the counter transitions from 0036 to 0000. The 'Update event (UEV)' and 'Update interrupt flag (UIF)' are shown as pulses that coincide with the overflow event. The diagram is labeled MS35835V1 in the bottom right corner.

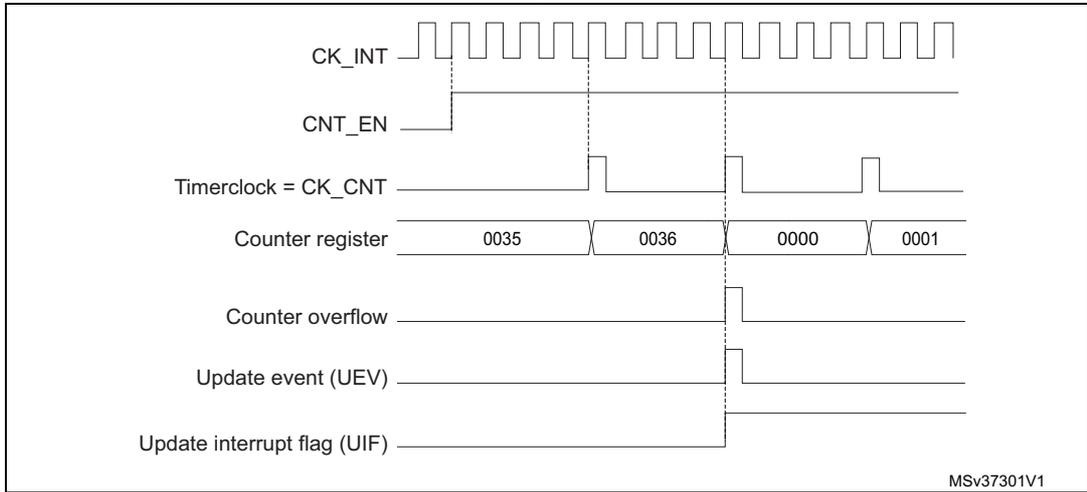

Figure 232. Counter timing diagram, internal clock divided by 4

This timing diagram illustrates the operation of a counter when the internal clock is divided by 4. The top signal, CK_INT, is a high-frequency square wave. Below it, CNT_EN is a horizontal line indicating the counter is enabled. The Timerclock = CK_CNT signal is a square wave with a period four times that of CK_INT. The Counter register shows a sequence of values: 0035, 0036, 0000, 0001. A 'Counter overflow' pulse occurs when the counter transitions from 0036 to 0000. The 'Update event (UEV)' and 'Update interrupt flag (UIF)' are shown as pulses that coincide with the overflow event. The diagram is labeled MSv37301V1 in the bottom right corner.

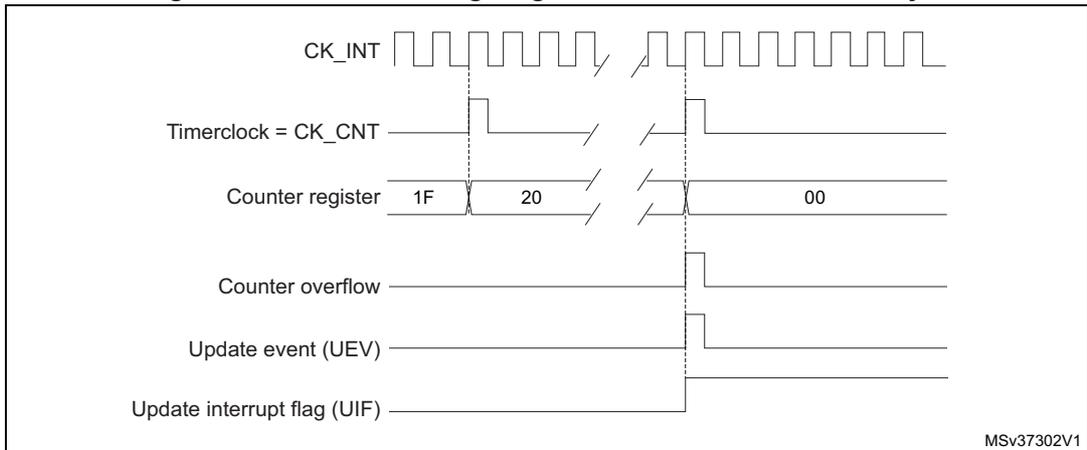

Figure 233. Counter timing diagram, internal clock divided by N

This timing diagram illustrates the operation of a counter when the internal clock is divided by an arbitrary value N. The top signal, CK_INT, is a high-frequency square wave. Below it, the Timerclock = CK_CNT signal is a square wave with a period N times that of CK_INT. The Counter register shows a sequence of values: 1F, 20, 00. A 'Counter overflow' pulse occurs when the counter transitions from 20 to 00. The 'Update event (UEV)' and 'Update interrupt flag (UIF)' are shown as pulses that coincide with the overflow event. The diagram is labeled MSv37302V1 in the bottom right corner.

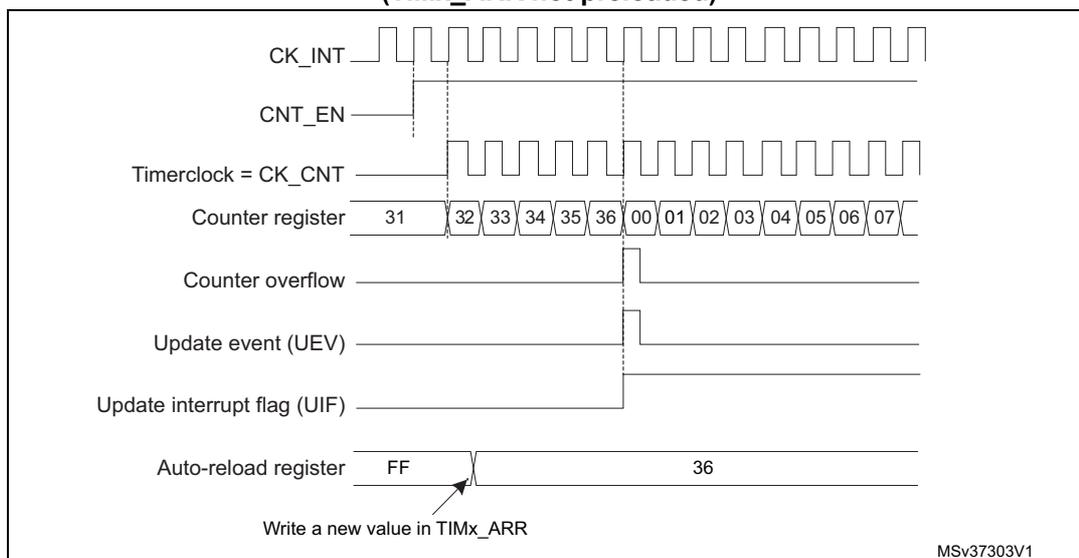

Figure 234. Counter timing diagram, update event when ARPE = 0

(TIMx_ARR not preloaded)

The diagram shows the following signals and their timing:

- CK_INT : Internal clock signal, a continuous square wave.

- CNT_EN : Counter enable signal, goes high to start counting.

- Timerclock = CK_CNT : Counter clock signal, derived from CK_INT.

- Counter register : Shows values 31, 32, 33, 34, 35, 36, 00, 01, 02, 03, 04, 05, 06, 07. It overflows from 36 to 00.

- Counter overflow : Pulse when the counter reaches 36 and overflows to 00.

- Update event (UEV) : Pulse when the counter overflows.

- Update interrupt flag (UIF) : Set when an update event occurs.

- Auto-reload register : Contains the value FF. An arrow indicates a write to TIMx_ARR.

MSv37303V1

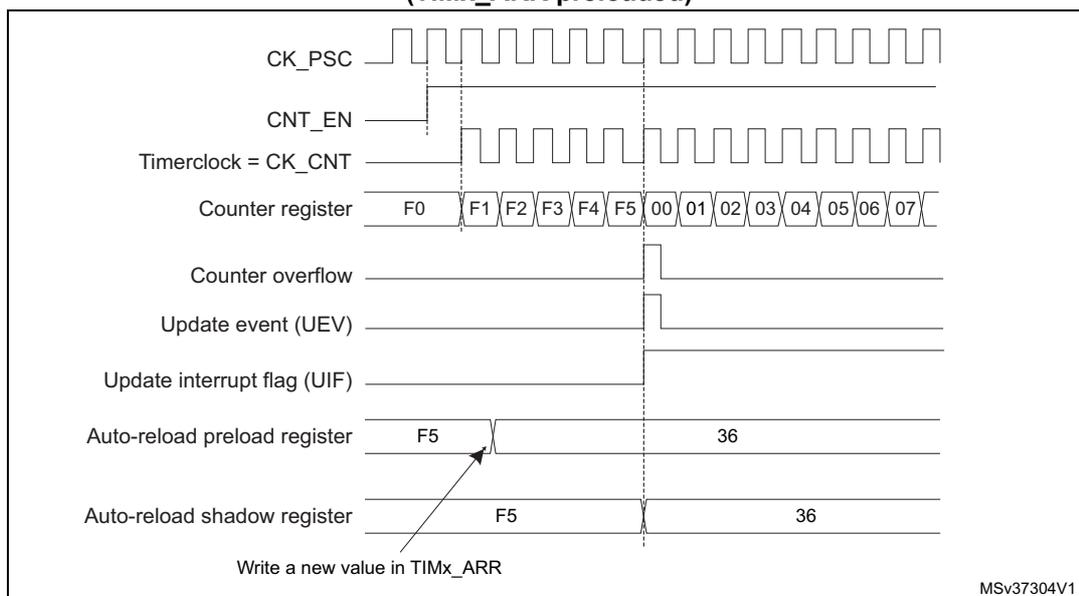

Figure 235. Counter timing diagram, update event when ARPE=1

(TIMx_ARR preloaded)

The diagram shows the following signals and their timing:

- CK_PSC : Prescaler clock signal, a continuous square wave.

- CNT_EN : Counter enable signal, goes high to start counting.

- Timerclock = CK_CNT : Counter clock signal, derived from CK_PSC.

- Counter register : Shows values F0, F1, F2, F3, F4, F5, 00, 01, 02, 03, 04, 05, 06, 07. It overflows from F5 to 00.

- Counter overflow : Pulse when the counter reaches F5 and overflows to 00.

- Update event (UEV) : Pulse when the counter overflows.

- Update interrupt flag (UIF) : Set when an update event occurs.

- Auto-reload preload register : Contains the value F5. An arrow indicates a write to TIMx_ARR.

- Auto-reload shadow register : Contains the value F5. An arrow indicates the value is loaded into the shadow register.

MSv37304V1

19.3.3 Clock source

The counter clock is provided by the Internal clock (CK_INT) source.

The CEN (in the TIMx_CR1 register) and UG bits (in the TIMx_EGR register) are actual control bits and can be changed only by software (except for UG that remains cleared automatically). As soon as the CEN bit is written to 1, the prescaler is clocked by the internal clock CK_INT.

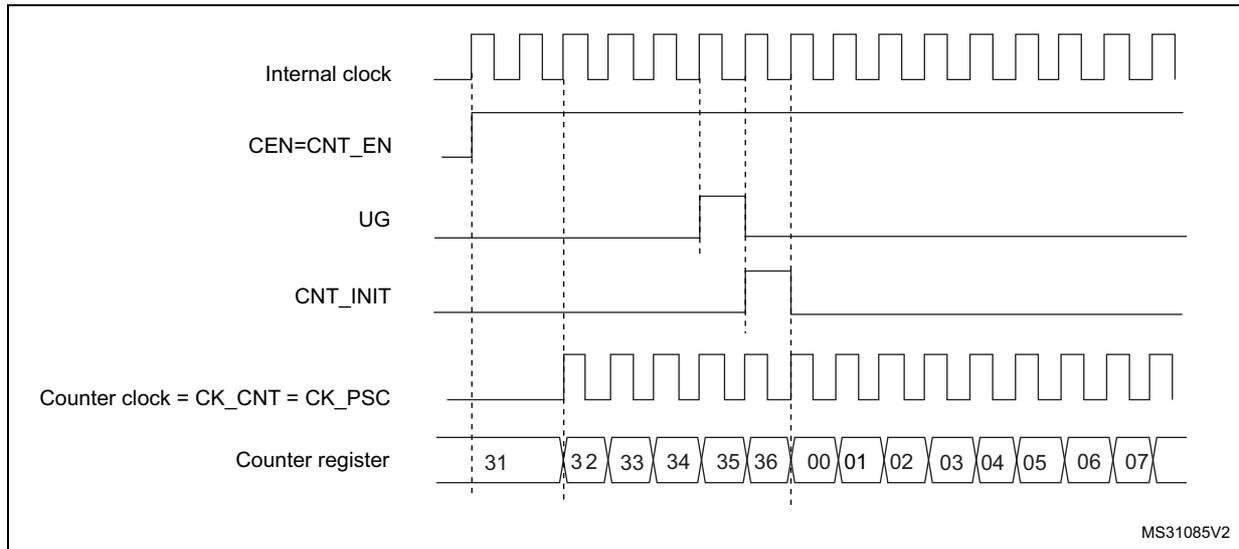

Figure 236 shows the behavior of the control circuit and the upcounter in normal mode, without prescaler.

Figure 236. Control circuit in normal mode, internal clock divided by 1

MS31085V2

19.3.4 Debug mode

When the microcontroller enters the debug mode (Cortex ® -M4 with FPU core - halted), the TIMx counter either continues to work normally or stops, depending on the DBG_TIMx_STOP configuration bit in the DBG module. For more details, refer to Section 33.16.2: Debug support for timers, watchdog, bxCAN and I 2 C .

19.4 TIM6&TIM7 registers

Refer to Section 1.2 on page 51 for a list of abbreviations used in register descriptions.

The peripheral registers have to be written by half-words (16 bits) or words (32 bits). Read accesses can be done by bytes (8 bits), half-words (16 bits) or words (32 bits).

19.4.1 TIM6&TIM7 control register 1 (TIMx_CR1)

Address offset: 0x00

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ARPE | Res. | Res. | Res. | OPM | URS | UDIS | CEN |

| rw | rw | rw | rw | rw |

Bits 15:8 Reserved, must be kept at reset value.

Bit 7 ARPE : Auto-reload preload enable

0: TIMx_ARR register is not buffered.

1: TIMx_ARR register is buffered.

Bits 6:4 Reserved, must be kept at reset value.

Bit 3 OPM : One-pulse mode

0: Counter is not stopped at update event

1: Counter stops counting at the next update event (clearing the CEN bit).

Bit 2 URS: Update request sourceThis bit is set and cleared by software to select the UEV event sources.

0: Any of the following events generates an update interrupt or DMA request if enabled.

These events can be:

- – Counter overflow/underflow

- – Setting the UG bit

- – Update generation through the slave mode controller

1: Only counter overflow/underflow generates an update interrupt or DMA request if enabled.

Bit 1 UDIS: Update disableThis bit is set and cleared by software to enable/disable UEV event generation.

0: UEV enabled. The Update (UEV) event is generated by one of the following events:

- – Counter overflow/underflow

- – Setting the UG bit

- – Update generation through the slave mode controller

Buffered registers are then loaded with their preload values.

1: UEV disabled. The Update event is not generated, shadow registers keep their value (ARR, PSC). However the counter and the prescaler are reinitialized if the UG bit is set or if a hardware reset is received from the slave mode controller.

Bit 0 CEN: Counter enable0: Counter disabled

1: Counter enabled

Note: Gated mode can work only if the CEN bit has been previously set by software. However trigger mode can set the CEN bit automatically by hardware.

CEN is cleared automatically in one-pulse mode, when an update event occurs.

19.4.2 TIM6&TIM7 control register 2 (TIMx_CR2)

Address offset: 0x04

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | MMS[2:0] | Res. | Res. | Res. | |||

| rw | rw | rw | |||||||||||||

Bits 15:7 Reserved, must be kept at reset value.

Bits 6:4 MMS[2:0] : Master mode selection

These bits are used to select the information to be sent in master mode to slave timers for synchronization (TRGO). The combination is as follows:

000: Reset - the UG bit from the TIMx_EGR register is used as a trigger output (TRGO). If reset is generated by the trigger input (slave mode controller configured in reset mode) then the signal on TRGO is delayed compared to the actual reset.

001: Enable - the Counter enable signal, CNT_EN, is used as a trigger output (TRGO). It is useful to start several timers at the same time or to control a window in which a slave timer is enabled. The Counter Enable signal is generated by a logic OR between CEN control bit and the trigger input when configured in gated mode.

When the Counter Enable signal is controlled by the trigger input, there is a delay on TRGO, except if the master/slave mode is selected (see the MSM bit description in the TIMx_SMCR register).

010: Update - The update event is selected as a trigger output (TRGO). For instance a master timer can then be used as a prescaler for a slave timer.

Bits 3:0 Reserved, must be kept at reset value.

19.4.3 TIM6&TIM7 DMA/Interrupt enable register (TIMx_DIER)

Address offset: 0x0C

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | UDE | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UIE |

| rw | rw |

Bits 15:9 Reserved, must be kept at reset value.

Bit 8 UDE : Update DMA request enable

0: Update DMA request disabled.

1: Update DMA request enabled.

Bits 7:1 Reserved, must be kept at reset value.

Bit 0 UIE : Update interrupt enable

0: Update interrupt disabled.

1: Update interrupt enabled.

19.4.4 TIM6&TIM7 status register (TIMx_SR)

Address offset: 0x10

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UIF |

| rc_w0 |

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 UIF : Update interrupt flag

This bit is set by hardware on an update event. It is cleared by software.

0: No update occurred.

1: Update interrupt pending. This bit is set by hardware when the registers are updated:

- – At overflow or underflow and if UDIS = 0 in the TIMx_CR1 register.

- – When CNT is reinitialized by software using the UG bit in the TIMx_EGR register, if URS = 0 and UDIS = 0 in the TIMx_CR1 register.

19.4.5 TIM6&TIM7 event generation register (TIMx_EGR)

Address offset: 0x14

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UG |

| w |

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 UG : Update generation

This bit can be set by software, it is automatically cleared by hardware.

0: No action.

1: Re-initializes the timer counter and generates an update of the registers. Note that the prescaler counter is cleared too (but the prescaler ratio is not affected).

19.4.6 TIM6&TIM7 counter (TIMx_CNT)

Address offset: 0x24

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CNT[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 CNT[15:0] : Counter value

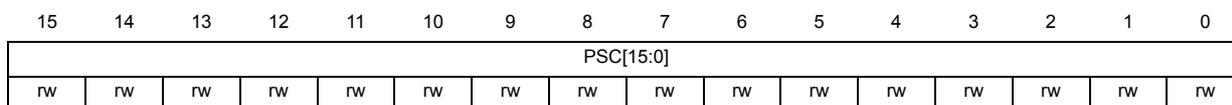

19.4.7 TIM6&TIM7 prescaler (TIMx_PSC)

Address offset: 0x28

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PSC[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 PSC[15:0] : Prescaler value

The counter clock frequency \( f_{CK\_CNT} \) is equal to \( f_{CK\_PSC} / (PSC[15:0] + 1) \) .

PSC contains the value to be loaded into the active prescaler register at each update event.

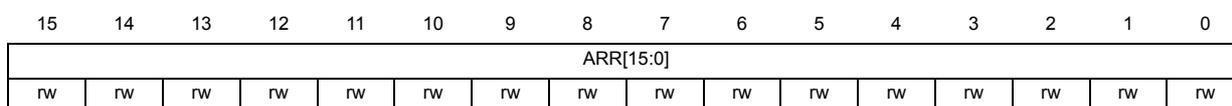

19.4.8 TIM6&TIM7 auto-reload register (TIMx_ARR)

Address offset: 0x2C

Reset value: 0x0000

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ARR[15:0] | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Bits 15:0 ARR[15:0] : Auto-reload value

ARR is the value to be loaded into the actual auto-reload register.

Refer to Section 19.3.1: Time-base unit on page 619 for more details about ARR update and behavior.

The counter is blocked while the auto-reload value is null.

19.4.9 TIM6&TIM7 register map

TIMx registers are mapped as 16-bit addressable registers as described in the table below:

Table 120. TIM6&TIM7 register map and reset values

| Offset | Register | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0x00 | TIMx_CR1 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ARPE | Res. | Res. | Res. | Res. | OPM | URS | UDIS | CEN |

| Reset value | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||||

| 0x04 | TIMx_CR2 | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | MMS[2:0] | Res. | Res. | Res. | Res. | Res. | |||

| Reset value | 0 | 0 | 0 | |||||||||||||||||||||||||||||||

| 0x08 | Reserved | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |

| 0x0C | TIMx_DIER | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UDE | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UIE | |

| Reset value | 0 | 0 | ||||||||||||||||||||||||||||||||

| 0x10 | TIMx_SR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UIF | |

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x14 | TIMx_EGR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | UG | |

| Reset value | 0 | |||||||||||||||||||||||||||||||||

| 0x18 | Reserved | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |

| 0x1C | Reserved | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |

| 0x20 | Reserved | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | |

| 0x24 | TIMx_CNT | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | CNT[15:0] | ||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||

| 0x28 | TIMx_PSC | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | PSC[15:0] | ||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||

| 0x2C | TIMx_ARR | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | ARR[15:0] | ||||||||||||||||

| Reset value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||

Refer to Section 2.2 on page 56 for the register boundary addresses.