14. Analog-to-digital converter (ADC)

14.1 Introduction

The 12-bit ADC is a successive approximation analog-to-digital converter. It has up to 19 multiplexed channels allowing it to measure signals from 16 external and 3 internal sources. A/D conversion of the various channels can be performed in single, continuous, scan or discontinuous mode. The result of the ADC is stored in a left-aligned or right-aligned 16-bit data register.

The analog watchdog feature allows the application to detect if the input voltage goes outside the user-defined higher or lower thresholds.

An efficient low-power mode is implemented to allow very low consumption at low frequency.

A built-in hardware oversampler allows analog performances to be improved while off-loading the related computational burden from the CPU.

14.2 ADC main features

- • High performance

- – 12-bit, 10-bit, 8-bit or 6-bit configurable resolution

- – ADC conversion time: 0.87 µs for 12-bit resolution (1.14 MHz), 0.81 µs conversion time for 10-bit resolution, faster conversion times can be obtained by lowering resolution.

- – Self-calibration

- – Programmable sampling time

- – Data alignment with built-in data coherency

- – DMA support

- • Low-power

- – The application can reduce PCLK frequency for low-power operation while still keeping optimum ADC performance. For example, 0.87 µs conversion time is kept, whatever the PCLK frequency

- – Wait mode: prevents ADC overrun in applications with low PCLK frequency

- – Auto off mode: ADC is automatically powered off except during the active conversion phase. This dramatically reduces the power consumption of the ADC.

- • Analog input channels

- – 16 external analog inputs

- – 1 channel for internal temperature sensor ( \( V_{\text{SENSE}} \) )

- – 1 channel for internal reference voltage ( \( V_{\text{REFINT}} \) )

- – 1 channel for monitoring \( V_{\text{LCD}} \) derived voltage (LCD_VLCD1 signal)

- • Start-of-conversion can be initiated:

- – By software

- – By hardware triggers with configurable polarity (timer events or GPIO input events)

- • Conversion modes

- – Can convert a single channel or can scan a sequence of channels.

- – Single mode converts selected inputs once per trigger

- – Continuous mode converts selected inputs continuously

- – Discontinuous mode

- • Interrupt generation at the end of sampling, end of conversion, end of sequence conversion, and in case of analog watchdog or overrun events

- • Analog watchdog

- • Oversampler

- – 16-bit data register

- – Oversampling ratio adjustable from 2 to 256x

- – Programmable data shift up to 8-bits

- • ADC input range: \( V_{\text{SSA}} \leq V_{\text{IN}} \leq V_{\text{DDA}} \)

14.3 ADC functional description

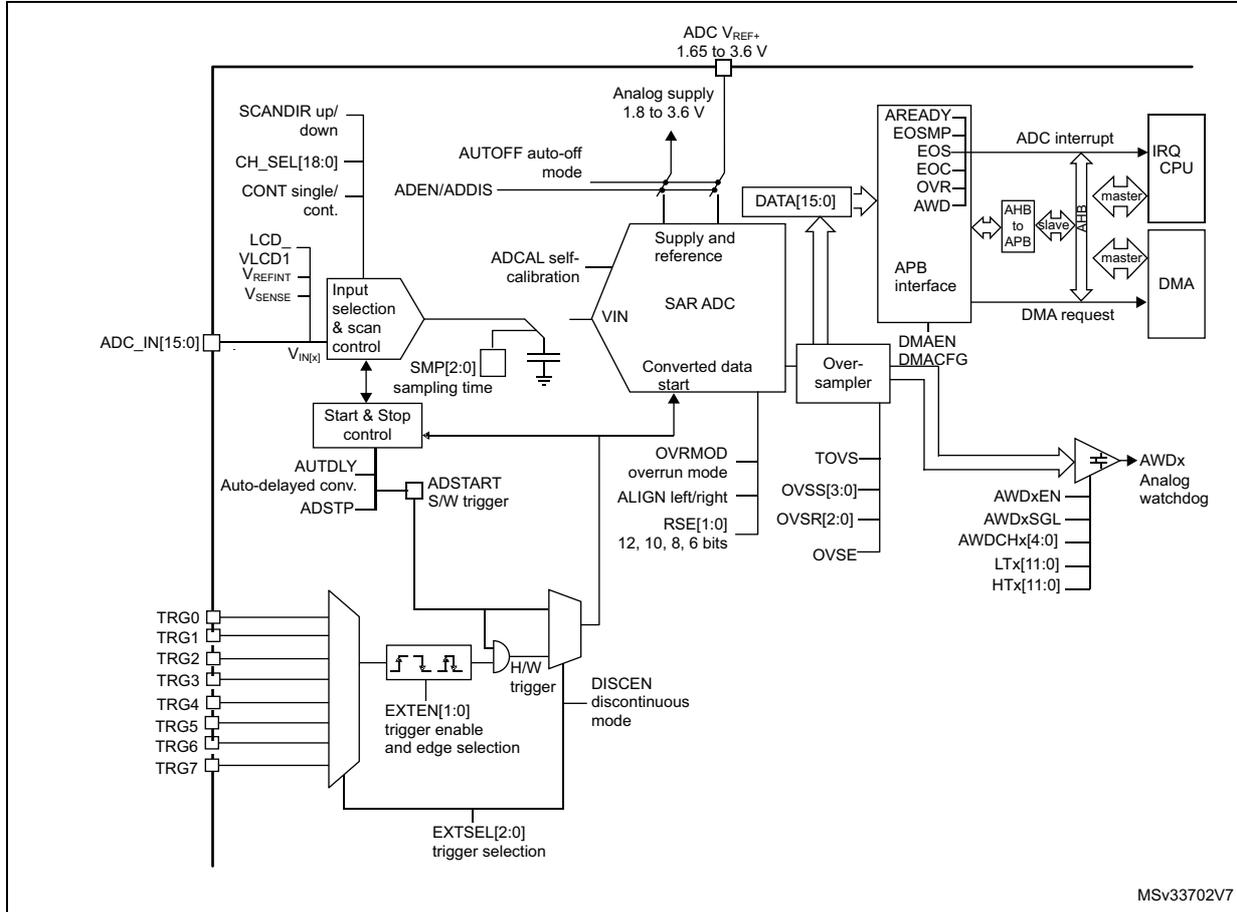

Figure 31 shows the ADC block diagram and Table 58 gives the ADC pin description.

Figure 31. ADC block diagram

The block diagram illustrates the internal architecture of the ADC. On the left, external pins include ADC_IN[15:0] (labeled V_IN[15:0]), TRG0 through TRG7, VDDA (ADC VREF+, 1.65 to 3.6 V), and VSSA. Internal blocks include 'Input selection & scan control' which takes SCANDIR, CH_SEL[18:0], and CONT signals; 'Start & Stop control' with ADSTART and ADSTP; 'SAR ADC' with VIN, DATA[15:0], and various control signals (AUTOFF, ADEN/ADDIS, ADCAL); 'Over-sampler' with TOVS, OVSSS[3:0], OVSR[2:0], and OVSE; 'APB interface' with AREADY, EOSMP, EOS, EOC, OVR, and AWD; and 'ADC interrupt' and 'DMA request' logic. An 'Analog watchdog' (AWDx) is shown on the right with inputs from the over-sampler and configuration registers (AWDxEN, AWDxSGL, AWDCHx[4:0], LTx[11:0], HTx[11:0]). A 'Supply and reference' block provides V_IN to the SAR ADC. A 'Converted data start' block connects the SAR ADC to the Over-sampler. A 'H/W trigger' block combines TRG signals with EXTEN[1:0] and EXTSEL[2:0] to provide triggers to the SAR ADC. The APB interface connects to an AHB to APB bridge, which is then connected to a CPU (IRQ) and a DMA.

1. TRGi are mapped at product level. Refer to Table External triggers in Section 14.3.1: ADC pins and internal signals .

14.3.1 ADC pins and internal signals

Table 58. ADC input/output pins

| Name | Signal type | Remarks |

|---|---|---|

| VDDA | Input, analog power supply | Analog power supply and positive reference voltage for the ADC |

| VSSA | Input, analog supply ground | Ground for analog power supply |

| ADC_INx | Analog input signals | 16 external analog input channels |

Table 59. ADC internal input/output signals

| Internal signal name | Signal type | Description |

|---|---|---|

| V IN [x] | Analog Input channels | Connected either to internal channels or to ADC_INi external channels |

| TRGx | Input | ADC conversion triggers |

| V SENSE | Input | Internal temperature sensor output voltage |

| V REFINT | Input | Internal voltage reference output voltage |

| LCD_VLCD1 | Input | 1/3 V

LCD

when the LCD is configured to 1/3Bias 1/4 V LCD when the LCD is configured to 1/4Bias or 1/2Bias |

| ADC_AWDx_OUT | Output | Internal analog watchdog output signal connected to on-chip timers (x = Analog watchdog number = 1) |

Table 60. External triggers

| Name | Source | EXTSEL[2:0] |

|---|---|---|

| TRG0 | TIM6_TRGO | 000 |

| TRG1 | TIM21_CH2 | 001 |

| TRG2 | TIM2_TRGO | 010 |

| TRG3 | TIM2_CH4 | 011 |

| TRG4 | TIM22_TRGO | 100 |

| TRG5 (1) | TIM2_CH3 | 101 |

| TRG6 | TIM3_TRGO | 110 |

| TRG7 | EXTI11 | 111 |

1. Available on all categories except category 3.

14.3.2 ADC voltage regulator (ADVREGEN)

The ADC has a specific internal voltage regulator which must be enabled and stable before using the ADC.

The ADC voltage regulator stabilization time is entirely managed by the hardware and software does not need to care about it.

After ADC operations are complete, the ADC can be disabled (ADEN = 0). To keep power consumption low, it is important to disable the ADC voltage regulator before entering low-power mode (LPRun, LPSleep or Stop mode). Refer to Section : ADVREG disable sequence .

Note: When the internal voltage regulator is disabled, the internal analog calibration is kept.

Analog reference for the ADC internal voltage regulator

The internal ADC voltage regulator uses a buffered copy of the internal voltage reference. This buffer is always enabled when the main voltage regulator is in normal Run mode (MR mode, with the device operating either in Run or Sleep mode). When the main voltage

regulator is in low-power mode (with the device operating in LPRun, LPSleep or Stop mode), the voltage reference is disabled and the ADC cannot be used anymore.

The software must follow the procedure described below to manage the ADC in low-power mode:

- 1. Make sure that the ADC is disabled (ADEN = 0).

- 2. Write ADVREGEN = 0.

- 3. Enter low-power mode.

- 4. Resume from low-power mode.

- 5. Check that REGLPF = 0.

- 6. Enable the ADC voltage regulator by using the sequence described in Section : ADVREG enable sequence (ADVREGEN = 1 in ADC_CR).

- 7. Write ADC_CR ADEN = 1 and wait until ADC_CR ADRDY = 1.

- 8. Write ADRDY = 1 to clear it.

ADVREG enable sequence

There are three ways to enable the voltage regulator:

- • by writing ADVREGEN = 1.

- • by launching the calibration by writing by ADCAL = 1 (the ADVREGEN bit is automatically set).

- • by enabling the ADC by writing ADEN = 1.

ADVREG disable sequence

To disable the ADC voltage regulator, perform the sequence below:

- 1. Ensure that the ADC is disabled (ADEN = 0).

- 2. Write ADVREGEN = 0.

14.3.3 Calibration (ADCAL)

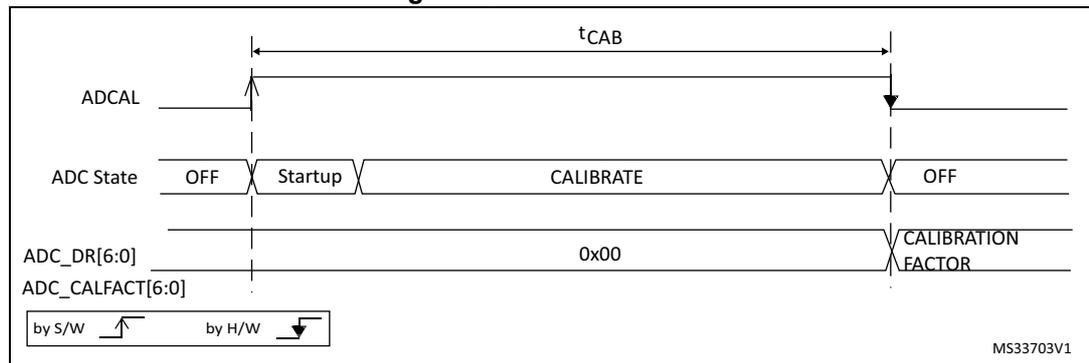

The ADC has a calibration feature. During the procedure, the ADC calculates a calibration factor which is internally applied to the ADC until the next ADC power-off. The application must not use the ADC during calibration and must wait until it is complete.

Calibration should be performed before starting A/D conversion. It removes the offset error which may vary from chip to chip due to process variation.

The calibration is initiated by software by setting bit ADCAL = 1. Calibration can only be initiated when the ADC is disabled (when ADEN = 0). ADCAL bit stays at 1 during all the calibration sequence. It is then cleared by hardware as soon the calibration completes. After this, the calibration factor can be read from the ADC_DR register (from bits 6 to 0).

The internal analog calibration is kept if the ADC is disabled (ADEN = 0) or if the ADC voltage reference is disabled (ADVREGEN = 0). When the ADC operating conditions change ( \( V_{DDA} \) changes are the main contributor to ADC offset variations and temperature change to a lesser extend), it is recommended to re-run a calibration cycle.

The calibration factor is lost in the following cases:

- • The product is in Standby mode (power supply removed from the ADC)

- • The ADC peripheral is reset.

The calibration factor is maintained in the following low-power modes: LPRun, LPSleep and Stop.

It is still possible to save and restore the calibration factor by software to save time when re-starting the ADC (as long as temperature and voltage are stable during the ADC power down).

The calibration factor can be written if the ADC is enabled but not converting (ADEN = 1 and ADSTART = 0). Then, at the next start of conversion, the calibration factor is automatically injected into the analog ADC. This loading is transparent and does not add any cycle latency to the start of the conversion.

Software calibration procedure

- 1. Ensure that ADEN = 0 and DMAEN = 0.

- 2. Set ADCAL = 1.

- 3. Wait until ADCAL = 0 (or until EOCAL = 1). This can be handled by interrupt if the interrupt is enabled by setting the EOCALIE bit in the ADC_IER register. The ADCAL bit can remain set for some time even after EOCAL has been set. As a result, the software must wait for ADCAL = 0 after EOCAL = 1 to be able to set ADEN = 1 for next ADC conversions.

- 4. The calibration factor can be read from bits 6:0 of ADC_DR or ADC_CALFACT registers.

For code example, refer to A.8.1: Calibration code example .

Figure 32. ADC calibration

The diagram illustrates the timing of ADC calibration. The top signal, ADCAL, is set by software (upward arrow) and cleared by hardware (downward arrow). The ADC State transitions from OFF to Startup, then to CALIBRATE, and back to OFF. During the CALIBRATE state, the ADC_DR[6:0] register is set to 0x00 by software, and the ADC_CALFACT[6:0] register is updated with the CALIBRATION FACTOR by hardware. The time interval between the rising and falling edges of the ADCAL signal is labeled tCAB. A legend at the bottom left indicates that upward arrows represent software (S/W) writes and downward arrows represent hardware (H/W) writes. The diagram is labeled MS33703V1 in the bottom right corner.

If the ADC voltage regulator was not previously set, it is automatically enabled when setting ADCAL = 1 (bit ADVREGEN is automatically set by hardware). In this case, the ADC calibration time is longer to take into account the stabilization time of the ADC voltage regulator.

At the end of the calibration, the ADC voltage regulator remains enabled.

Calibration factor forcing software procedure

- 1. Ensure that ADEN= 1 and ADSTART = 0 (ADC started with no conversion ongoing)

- 2. Write ADC_CALFACT with the saved calibration factor

- 3. The calibration factor is used as soon as a new conversion is launched.

Figure 33. Calibration factor forcing

![Timing diagram for calibration factor forcing. The diagram shows four signal lines over time: ADC state, Internal calibration factor[6:0], Start conversion (hardware or software), and WRITE ADC_CALFACT. The ADC state transitions from 'Ready (not converting)' to 'Converting channel (Single ended)' when 'Start conversion' is asserted. During the conversion, the 'Internal calibration factor[6:0]' is updated from F1 to F2. The 'WRITE ADC_CALFACT' signal is used to write the new calibration factor F2. The diagram also shows a second conversion cycle. A legend indicates that rising edges are 'by S/W' (software) and falling edges are 'by H/W' (hardware). The identifier MS31925V1 is present in the bottom right corner.](/RM0367-STM32L0x3/edcc90a24f49ab7de0920aa221fb1867_img.jpg)

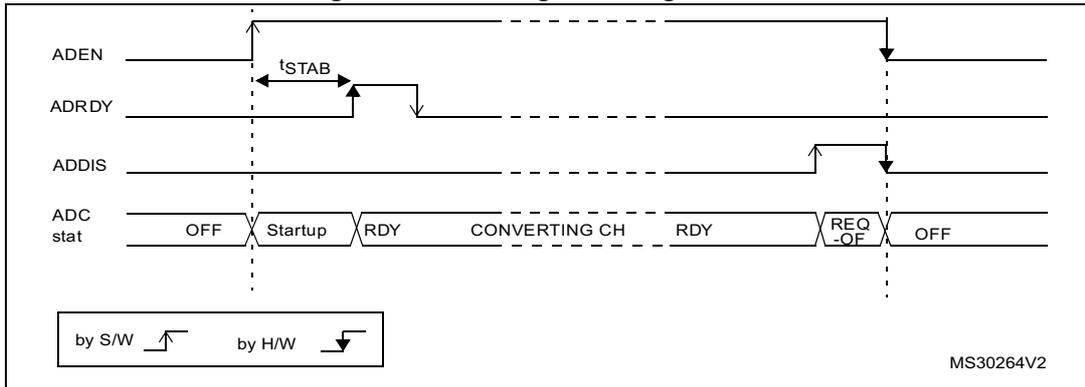

14.3.4 ADC on-off control (ADEN, ADDIS, ADRDY)

At power-up, the ADC is disabled and put in power-down mode (ADEN = 0).

As shown in Figure 34 , the ADC needs a stabilization time of \( t_{\text{STAB}} \) before it starts converting accurately.

Two control bits are used to enable or disable the ADC:

- • Set ADEN = 1 to enable the ADC. The ADRDY flag is set as soon as the ADC is ready for operation.

- • Set ADDIS = 1 to disable the ADC and put the ADC in power down mode. The ADEN and ADDIS bits are then automatically cleared by hardware as soon as the ADC is fully disabled.

If the ADC voltage regulator was not previously set, it is automatically enabled when setting ADEN=1 (bit ADVREGEN is automatically set by hardware). In this case, the ADC stabilization time \( t_{\text{STAB}} \) is longer to take into account the stabilization time of the ADC voltage regulator.

Conversion can then start either by setting ADSTART to 1 (refer to Section 14.4: Conversion on external trigger and trigger polarity (EXTSEL, EXTEN) on page 315 ) or when an external trigger event occurs if triggers are enabled.

Follow this procedure to enable the ADC:

- 1. Clear the ADRDY bit in ADC_ISR register by programming this bit to 1.

- 2. Set ADEN = 1 in the ADC_CR register.

- 3. Wait until ADRDY = 1 in the ADC_ISR register (ADRDY is set after the ADC startup time). This can be handled by interrupt if the interrupt is enabled by setting the ADRDYIE bit in the ADC_IER register.

For code example, refer to A.8.2: ADC enable sequence code example .

Follow this procedure to disable the ADC:

- 1. Check that ADSTART = 0 in the ADC_CR register to ensure that no conversion is ongoing. If required, stop any ongoing conversion by writing 1 to the ADSTP bit in the ADC_CR register and waiting until this bit is read at 0.

- 2. Set ADDIS = 1 in the ADC_CR register.

- 3. If required by the application, wait until ADEN = 0 in the ADC_CR register, indicating that the ADC is fully disabled (ADDIS is automatically reset once ADEN = 0).

- 4. Clear the ADRDY bit in ADC_ISR register by programming this bit to 1 (optional).

For code example, refer to A.8.3: ADC disable sequence code example .

Figure 34. Enabling/disabling the ADC

Note: In Auto-off mode (AUTOFF = 1) the power-on/off phases are performed automatically, by hardware and the ADRDY flag is not set.

14.3.5 ADC clock (CKMODE, PRESC[3:0], LFMEN)

The ADC has a dual clock-domain architecture, so that the ADC can be fed with a clock (ADC asynchronous clock) independent from the APB clock (PCLK).

Figure 35. ADC clock scheme

![Block diagram of the ADC clock scheme. It shows the RCC (Reset & Clock Controller) providing PCLK and an ADC asynchronous clock. The ADITF block contains an APB interface, a prescaler (1 or 2 or 4) controlled by CKMODE[1:0] of ADC_CFGR2, and a list of prescaler values (1,2,4,6,8,10,12,16,32,64,128,256) controlled by PRESC[3:0] of ADC_CCR. These are combined through a multiplexer (Others, 00) controlled by CKMODE[1:0] of ADC_CFGR2 to produce the Analog ADC_CK signal for the Analog ADC.](/RM0367-STM32L0x3/7f4322f907601d633f4da43a83be79a1_img.jpg)

- 1. Refer to Section Reset and clock control (RCC) for how the PCLK clock and ADC asynchronous clock are enabled.

The input clock of the analog ADC can be selected between two different clock sources (see Figure 35: ADC clock scheme to see how the PCLK clock and the ADC asynchronous clock are enabled):

- The ADC clock can be a specific clock source, named “ADC asynchronous clock” which is independent and asynchronous with the APB clock.

Refer to RCC Section for more information on generating this clock source.

To select this scheme, bits CKMODE[1:0] of the ADC_CFGR2 register must be reset.

- The ADC clock can be derived from the APB clock of the ADC bus interface, divided by a programmable factor (1, 2 or 4) according to bits CKMODE[1:0].

To select this scheme, bits CKMODE[1:0] of the ADC_CFGR2 register must be different from “00”.

For code example, refer to A.8.4: ADC clock selection code example .

In option a), the generated ADC clock can eventually be divided by a prescaler (1, 2, 4, 6, 8, 10, 12, 16, 32, 64, 128, 256) when programming the bits PRESC[3:0] in the ADC_CCR register).

Option a) has the advantage of reaching the maximum ADC clock frequency whatever the APB clock scheme selected.

Option b) has the advantage of bypassing the clock domain resynchronizations. This can be useful when the ADC is triggered by a timer and if the application requires that the ADC is precisely triggered without any uncertainty (otherwise, an uncertainty of the trigger instant is added by the resynchronizations between the two clock domains).

Table 61. Latency between trigger and start of conversion (1)

| ADC clock source | CKMODE[1:0] | Latency between the trigger event and the start of conversion |

|---|---|---|

| HSI16 MHz clock | 00 | Latency is not deterministic (jitter) |

| PCLK divided by 2 | 01 | Latency is deterministic (no jitter) and equal to 4.25 ADC clock cycles |

| PCLK divided by 4 | 10 | Latency is deterministic (no jitter) and equal to 4.125 ADC clock cycles |

| PCLK divided by 1 | 11 | Latency is deterministic (no jitter) and equal to 4.5 ADC clock cycles |

1. Refer to the device datasheet for the maximum ADC_CLK frequency.

Caution: When selecting CKMODE[1:0] = 11 (PCLK divided by 1), the user must ensure that the PCLK has a 50% duty cycle. This is done by selecting a system clock with a 50% duty cycle and configuring the APB prescaler in bypass modes in the RCC (refer to there Reset and clock controller section). If an internal source clock is selected, the AHB and APB prescalers do not divide the clock.

Low frequency

When selecting an analog ADC clock frequency lower than 3.5 MHz, it is mandatory to first enable the Low Frequency Mode by setting bit LFMEN = 1 into the ADC_CCR register

14.3.6 ADC connectivity

ADC inputs are connected to the external channels as well as internal sources as described in Figure 36.

Figure 36. ADC connectivity

![Schematic diagram of ADC connectivity for STM32L0x3 showing 19 channels (VIN[0] to VIN[18]) connected to a SAR ADC1 block. Channels include external pins (ADC_IN0 to ADC_IN15), LCD_VLCD1, VREFINT, and VSENSE. Some channels are marked as 'Fast channel'.](/RM0367-STM32L0x3/a8e9f749343a414e17a319694c4fd18c_img.jpg)

The diagram illustrates the internal architecture of the ADC for the STM32L0x3 microcontroller. On the left, the STM32L0x3 chip is shown with 16 external pins labeled ADC_IN0 through ADC_IN15. These pins are connected to internal signal lines labeled VIN[0] through VIN[15]. The internal lines for VIN[0], VIN[4], and VIN[5] are specifically marked as 'Fast channel'. Below these, three additional internal sources are connected to the ADC: LCD_VLCD1 to VIN[16], VREFINT to VIN[17], and VSENSE to VIN[18]. All 19 internal signal lines (VIN[0] to VIN[18]) are connected to a common vertical bus. This bus is connected to a SAR ADC1 block on the right. The SAR ADC1 block has a V_IN input connected to the bus, a V_REF+ input at the top, and a V_REF- input at the bottom. A 'Channel selection' switch mechanism is shown between the internal lines and the bus, indicating that each channel can be individually selected for conversion.

14.3.7 Configuring the ADC

The software must write the ADCAL and ADEN bits in the ADC_CR register and configure the ADC_CFGR1 and ADC_CFGR2 registers only when the ADC is disabled (ADEN must be cleared).

The software must only write to the ADSTART and ADDIS bits in the ADC_CR register only if the ADC is enabled and there is no pending request to disable the ADC (ADEN = 1 and ADDIS = 0).

For all the other control bits in the ADC_IER, ADC_SMPR, ADC_TR, ADC_CHSELR and ADC_CCR registers, refer to the description of the corresponding control bit in Section 14.12: ADC registers .

The software must only write to the ADSTP bit in the ADC_CR register if the ADC is enabled (and possibly converting) and there is no pending request to disable the ADC (ADSTART = 1 and ADDIS = 0).

Note: There is no hardware protection preventing software from making write operations forbidden by the above rules. If such a forbidden write access occurs, the ADC may enter an undefined state. To recover correct operation in this case, the ADC must be disabled (clear ADEN = 0 and all the bits in the ADC_CR register).

14.3.8 Channel selection (CHSEL, SCANDIR)

There are up to 19 multiplexed channels:

- • 16 analog inputs from GPIO pins (ADC_INx)

- • 3 internal analog inputs (Temperature Sensor, Internal Reference Voltage, LCD_VLCD1 channel)

It is possible to convert a single channel or a sequence of channels.

The sequence of the channels to be converted can be programmed in the ADC_CHSELR channel selection register: each analog input channel has a dedicated selection bit (CHSELx).

The order in which the channels is scanned can be configured by programming the bit SCANDIR bit in the ADC_CFGR1 register:

- • SCANDIR = 0: forward scan Channel 0 to Channel 18

- • SCANDIR = 1: backward scan Channel 18 to Channel 0

Temperature sensor, V REFINT and LCD_VLCD1 internal channels

The temperature sensor is connected to channel ADC V IN [18].

The internal voltage reference V REFINT is connected to channel ADC V IN [17].

LCD_VLCD1 channel is connected to ADC V IN [16] channel.

14.3.9 Programmable sampling time (SMP)

Before starting a conversion, the ADC needs to establish a direct connection between the voltage source to be measured and the embedded sampling capacitor of the ADC. This sampling time must be enough for the input voltage source to charge the sample and hold capacitor to the input voltage level.

Having a programmable sampling time allows the conversion speed to be trimmed according to the input resistance of the input voltage source.

The ADC samples the input voltage for a number of ADC clock cycles that can be modified using the SMP[2:0] bits in the ADC_SMPR register.

This programmable sampling time is common to all channels. If required by the application, the software can change and adapt this sampling time between each conversions.

The total conversion time is calculated as follows:

Example:

With ADC_CLK = 16 MHz and a sampling time of 1.5 ADC clock cycles:

The ADC indicates the end of the sampling phase by setting the EOSMP flag.

14.3.10 Single conversion mode (CONT = 0)

In Single conversion mode, the ADC performs a single sequence of conversions, converting all the channels once. This mode is selected when CONT = 0 in the ADC_CFGR1 register. Conversion is started by either:

- • Setting the ADSTART bit in the ADC_CR register

- • Hardware trigger event

Inside the sequence, after each conversion is complete:

- • The converted data are stored in the 16-bit ADC_DR register

- • The EOC (end of conversion) flag is set

- • An interrupt is generated if the EOCIE bit is set

After the sequence of conversions is complete:

- • The EOS (end of sequence) flag is set

- • An interrupt is generated if the EOSIE bit is set

Then the ADC stops until a new external trigger event occurs or the ADSTART bit is set again.

Note: To convert a single channel, program a sequence with a length of 1.

14.3.11 Continuous conversion mode (CONT = 1)

In continuous conversion mode, when a software or hardware trigger event occurs, the ADC performs a sequence of conversions, converting all the channels once and then automatically re-starts and continuously performs the same sequence of conversions. This mode is selected when CONT = 1 in the ADC_CFGR1 register. Conversion is started by either:

- • Setting the ADSTART bit in the ADC_CR register

- • Hardware trigger event

Inside the sequence, after each conversion is complete:

- • The converted data are stored in the 16-bit ADC_DR register

- • The EOC (end of conversion) flag is set

- • An interrupt is generated if the EOCIE bit is set

After the sequence of conversions is complete:

- • The EOS (end of sequence) flag is set

- • An interrupt is generated if the EOSIE bit is set

Then, a new sequence restarts immediately and the ADC continuously repeats the conversion sequence.

Note: To convert a single channel, program a sequence with a length of 1.

It is not possible to have both discontinuous mode and continuous mode enabled: it is forbidden to set both bits DISCEN = 1 and CONT = 1.

14.3.12 Starting conversions (ADSTART)

Software starts ADC conversions by setting ADSTART = 1.

When ADSTART is set, the conversion:

- • Starts immediately if EXTEN = 00 (software trigger)

- • At the next active edge of the selected hardware trigger if EXTEN ≠ 00

The ADSTART bit is also used to indicate whether an ADC operation is currently ongoing. It is possible to re-configure the ADC while ADSTART = 0, indicating that the ADC is idle.

The ADSTART bit is cleared by hardware:

- • In single mode with software trigger (CONT = 0, EXTEN = 00)

- – At any end of conversion sequence (EOS = 1)

- • In discontinuous mode with software trigger (CONT = 0, DISCEN = 1, EXTEN = 00)

- – At end of conversion (EOC = 1)

- • In all cases (CONT = x, EXTEN = XX)

- – After execution of the ADSTP procedure invoked by software (see Section 14.3.14: Stopping an ongoing conversion (ADSTP) on page 315 )

Note: In continuous mode (CONT = 1), the ADSTART bit is not cleared by hardware when the EOS flag is set because the sequence is automatically relaunched.

When hardware trigger is selected in single mode (CONT = 0 and EXTEN = 01), ADSTART is not cleared by hardware when the EOS flag is set (except if DMAEN = 1 and DMACFG = 0 in which case ADSTART is cleared at end of the DMA transfer). This avoids

the need for software having to set the ADSTART bit again and ensures the next trigger event is not missed.

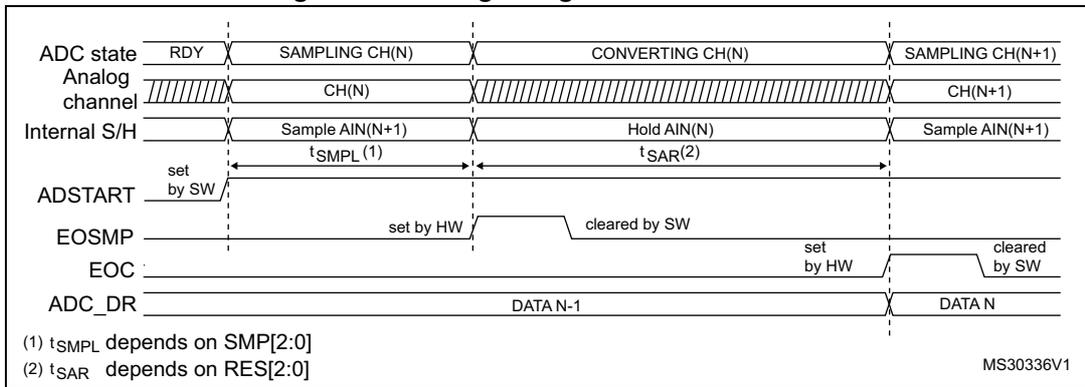

14.3.13 Timings

The elapsed time between the start of a conversion and the end of conversion is the sum of the configured sampling time plus the successive approximation time depending on data resolution:

Figure 37. Analog to digital conversion time

The diagram shows the timing of an ADC conversion. The ADC state transitions from RDY to SAMPLING CH(N), then to CONVERTING CH(N), and finally to SAMPLING CH(N+1). The Analog channel shows CH(N) being sampled and then CH(N+1) being sampled. The Internal S/H signal shows Sample AIN(N+1) during the sampling phase and Hold AIN(N) during the converting phase. The ADSTART signal is set by software. The EOSMP signal is set by hardware and cleared by software. The EOC signal is set by hardware and cleared by software. The ADC_DR signal shows DATA N-1 and DATA N. The sampling time is labeled t SMPL (1) and the conversion time is labeled t SAR (2).

(1)

\(

t_{SMPL}

\)

depends on SMP[2:0]

(2)

\(

t_{SAR}

\)

depends on RES[2:0]

MS30336V1

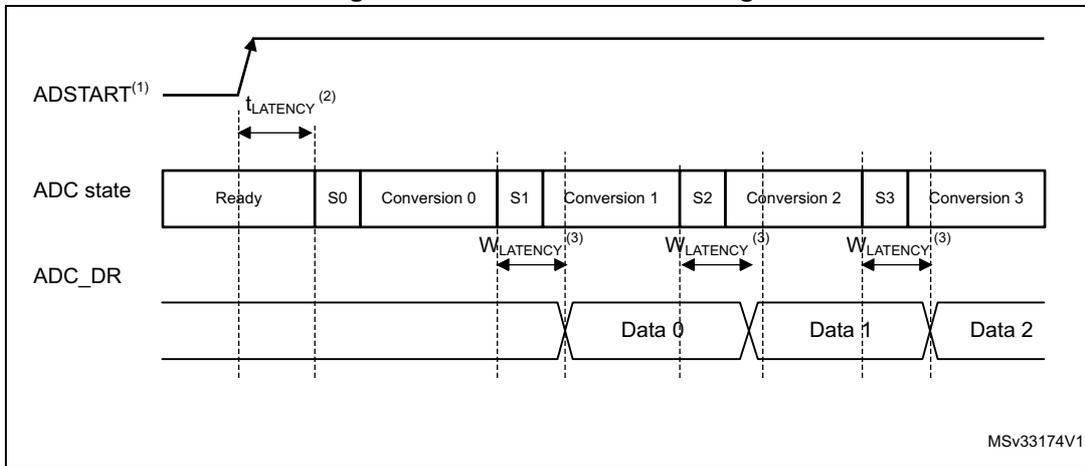

Figure 38. ADC conversion timings

The diagram shows the timing of multiple ADC conversions. The ADSTART signal is shown with a rising edge. The ADC state transitions through Ready, S0, Conversion 0, S1, Conversion 1, S2, Conversion 2, S3, and Conversion 3. The ADC_DR signal shows Data 0, Data 1, and Data 2. The latency between the start of a conversion and the data becoming available is labeled t LATENCY (2). The write latency for the ADC_DR register is labeled W LATENCY (3).

- 1. EXTEN = 00 or EXTEN ≠ 00

- 2. Trigger latency (refer to datasheet for more details)

- 3. ADC_DR register write latency (refer to datasheet for more details)

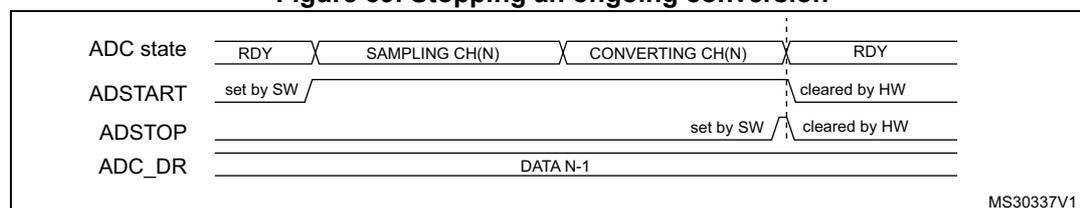

14.3.14 Stopping an ongoing conversion (ADSTP)

The software can decide to stop any ongoing conversions by setting ADSTP = 1 in the ADC_CR register.

This resets the ADC operation and the ADC is idle, ready for a new operation.

When the ADSTP bit is set by software, any ongoing conversion is aborted and the result is discarded (ADC_DR register is not updated with the current conversion).

The scan sequence is also aborted and reset (meaning that restarting the ADC would restart a new sequence).

Once this procedure is complete, the ADSTP and ADSTART bits are both cleared by hardware and the software must wait until ADSTART=0 before starting new conversions.

Figure 39. Stopping an ongoing conversion

The diagram illustrates the timing for stopping an ongoing conversion. It shows four horizontal timelines:

- ADC state: Starts at RDY, transitions to SAMPLING CH(N), then to CONVERTING CH(N), and finally back to RDY.

- ADSTART: Set by software at the beginning of the conversion. It is cleared by hardware when the ADC state returns to RDY.

- ADSTOP: Set by software while the ADC is in the CONVERTING CH(N) state. It is also cleared by hardware when the ADC state returns to RDY.

- ADC_DR: Contains the data from the previous conversion (DATA N-1) while the current conversion is ongoing.

MS30337V1

14.4 Conversion on external trigger and trigger polarity (EXTSEL, EXTEN)

A conversion or a sequence of conversion can be triggered either by software or by an external event (for example timer capture). If the EXTEN[1:0] control bits are not equal to “0b00”, then external events are able to trigger a conversion with the selected polarity. The trigger selection is effective once software has set bit ADSTART = 1.

Any hardware triggers which occur while a conversion is ongoing are ignored.

If bit ADSTART = 0, any hardware triggers which occur are ignored.

Table 62 provides the correspondence between the EXTEN[1:0] values and the trigger polarity.

Table 62. Configuring the trigger polarity

| Source | EXTEN[1:0] |

|---|---|

| Trigger detection disabled | 00 |

| Detection on rising edge | 01 |

| Detection on falling edge | 10 |

| Detection on both rising and falling edges | 11 |

Note: The polarity of the external trigger can be changed only when the ADC is not converting (ADSTART = 0).

The EXTSEL[2:0] control bits are used to select which of 8 possible events can trigger conversions.

Refer to Table 60: External triggers in Section 14.3.1: ADC pins and internal signals for the list of all the external triggers that can be used for regular conversion.

The software source trigger events can be generated by setting the ADSTART bit in the ADC_CR register.

Note: The trigger selection can be changed only when the ADC is not converting (ADSTART = 0).

14.4.1 Discontinuous mode (DISCEN)

This mode is enabled by setting the DISCEN bit in the ADC_CFGR1 register.

In this mode (DISCEN = 1), a hardware or software trigger event is required to start each conversion defined in the sequence. On the contrary, if DISCEN = 0, a single hardware or software trigger event successively starts all the conversions defined in the sequence.

Example:

- • DISCEN = 1, channels to be converted = 0, 3, 7, 10

- – 1st trigger: channel 0 is converted and an EOC event is generated

- – 2nd trigger: channel 3 is converted and an EOC event is generated

- – 3rd trigger: channel 7 is converted and an EOC event is generated

- – 4th trigger: channel 10 is converted and both EOC and EOS events are generated.

- – 5th trigger: channel 0 is converted an EOC event is generated

- – 6th trigger: channel 3 is converted and an EOC event is generated

- – ...

- • DISCEN = 0, channels to be converted = 0, 3, 7, 10

- – 1st trigger: the complete sequence is converted: channel 0, then 3, 7 and 10. Each conversion generates an EOC event and the last one also generates an EOS event.

- – Any subsequent trigger events restarts the complete sequence.

Note: It is not possible to have both discontinuous mode and continuous mode enabled: it is forbidden to set both bits DISCEN = 1 and CONT = 1.

14.4.2 Programmable resolution (RES) - Fast conversion mode

It is possible to obtain faster conversion times ( \( t_{SAR} \) ) by reducing the ADC resolution.

The resolution can be configured to be either 12, 10, 8, or 6 bits by programming the RES[1:0] bits in the ADC_CFGR1 register. Lower resolution allows faster conversion times for applications where high data precision is not required.

Note: The RES[1:0] bit must only be changed when the ADEN bit is reset.

The result of the conversion is always 12 bits wide and any unused LSB bits are read as zeros.

Lower resolution reduces the conversion time needed for the successive approximation steps as shown in Table 63 .

Table 63.\( t_{SAR} \) timings depending on resolution| RES[1:0] bits | \( t_{SAR} \) (ADC clock cycles) | \( t_{SAR} \) (ns) at \( f_{ADC} = 16 \) MHz | \( t_{SMPL} \) (min) (ADC clock cycles) | \( t_{CONV} \) (ADC clock cycles) (with min. \( t_{SMPL} \) ) | \( t_{CONV} \) (ns) at \( f_{ADC} = 16 \) MHz |

|---|---|---|---|---|---|

| 12 | 12.5 | 781 ns | 1.5 | 14 | 875 ns |

| 10 | 11.5 | 719 ns | 1.5 | 13 | 812 ns |

| 8 | 9.5 | 594 ns | 1.5 | 11 | 688 ns |

| 6 | 7.5 | 469 ns | 1.5 | 9 | 562 ns |

14.4.3 End of conversion, end of sampling phase (EOC, EOSMP flags)

The ADC indicates each end of conversion (EOC) event.

The ADC sets the EOC flag in the ADC_ISR register as soon as a new conversion data result is available in the ADC_DR register. An interrupt can be generated if the EOCIE bit is set in the ADC_IER register. The EOC flag is cleared by software either by writing 1 to it, or by reading the ADC_DR register.

The ADC also indicates the end of sampling phase by setting the EOSMP flag in the ADC_ISR register. The EOSMP flag is cleared by software by writing 1 to it. An interrupt can be generated if the EOSMPIE bit is set in the ADC_IER register.

The aim of this interrupt is to allow the processing to be synchronized with the conversions. Typically, an analog multiplexer can be accessed in hidden time during the conversion phase, so that the multiplexer is positioned when the next sampling starts.

Note: As there is only a very short time left between the end of the sampling and the end of the conversion, it is recommenced to use polling or a WFE instruction rather than an interrupt and a WFI instruction.

14.4.4 End of conversion sequence (EOS flag)

The ADC notifies the application of each end of sequence (EOS) event.

The ADC sets the EOS flag in the ADC_ISR register as soon as the last data result of a conversion sequence is available in the ADC_DR register. An interrupt can be generated if the EOSIE bit is set in the ADC_IER register. The EOS flag is cleared by software by writing 1 to it.

14.4.5 Example timing diagrams (single/continuous modes hardware/software triggers)

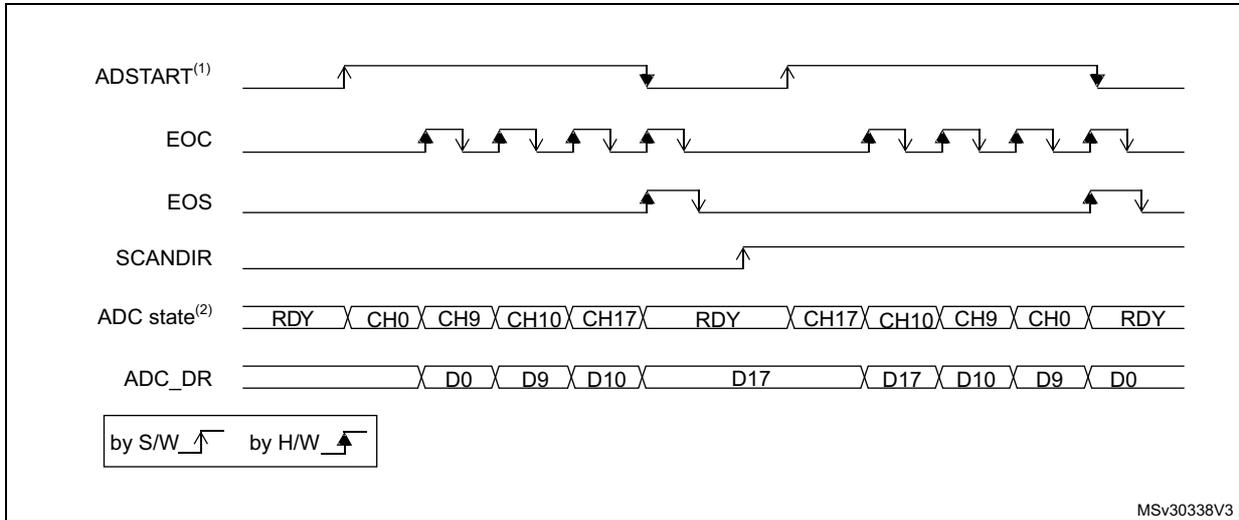

Figure 40. Single conversions of a sequence, software trigger

Timing diagram for single conversions of a sequence, software trigger. The diagram shows the following signals and states over time:

- ADSTART (1) : Software (S/W) and Hardware (H/W) triggers.

- EOC : End of Conversion pulses for each channel.

- EOS : End of Sequence, goes high after the last conversion.

- SCANDIR : Scan direction indicator, goes high after the last conversion.

- ADC state (2) : RDY, CH0, CH9, CH10, CH17, RDY, CH17, CH10, CH9, CH0, RDY.

- ADC_DR : Data Register, showing values D0, D9, D10, D17, D17, D10, D9, D0.

Legend: by S/W (Software trigger), by H/W (Hardware trigger).

MSv30338V3

- 1. EXTEN = 00, CONT = 0

- 2. CHSEL = 0x20601, WAIT = 0, AUTOFF = 0

For code example, refer to A.8.5: Single conversion sequence code example - Software trigger .

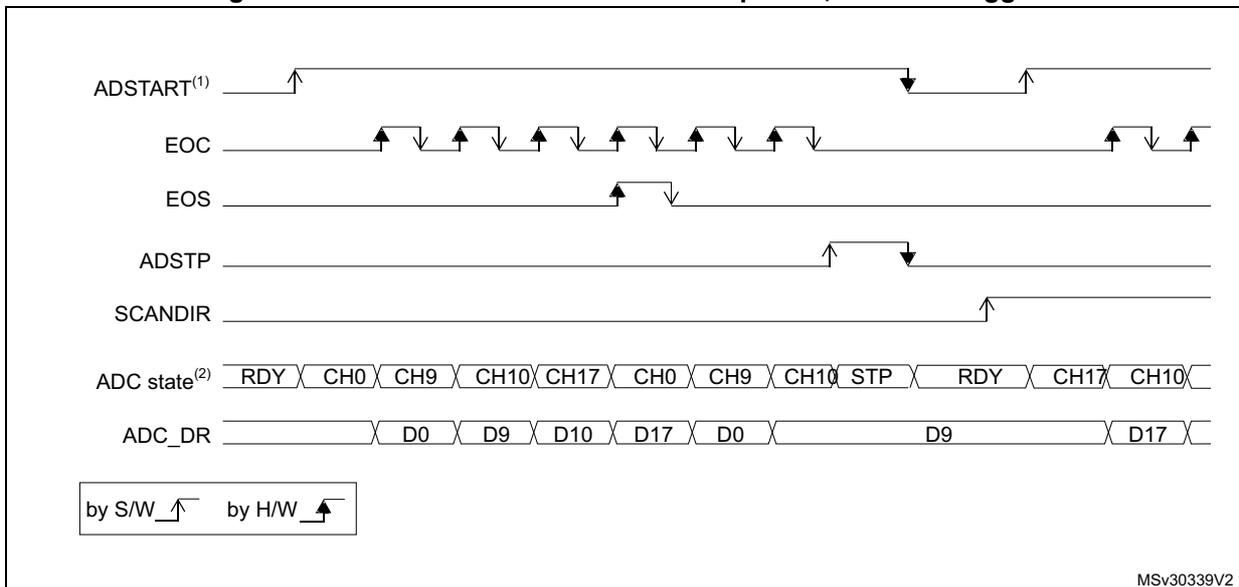

Figure 41. Continuous conversion of a sequence, software trigger

Timing diagram for continuous conversion of a sequence, software trigger. The diagram shows the following signals and states over time:

- ADSTART (1) : Software (S/W) and Hardware (H/W) triggers.

- EOC : End of Conversion pulses for each channel.

- EOS : End of Sequence, goes high after the first sequence.

- ADSTP : Start of Sequence, goes high to start a new sequence.

- SCANDIR : Scan direction indicator, goes high after the last conversion.

- ADC state (2) : RDY, CH0, CH9, CH10, CH17, CH0, CH9, CH10, STP, RDY, CH17, CH10.

- ADC_DR : Data Register, showing values D0, D9, D10, D17, D0, D9, D17.

Legend: by S/W (Software trigger), by H/W (Hardware trigger).

MSv30339V2

- 1. EXTEN = 00, CONT = 1,

- 2. CHSEL = 0x20601, WAIT = 0, AUTOFF = 0

For code example, refer to A.8.6: Continuous conversion sequence code example - Software trigger .

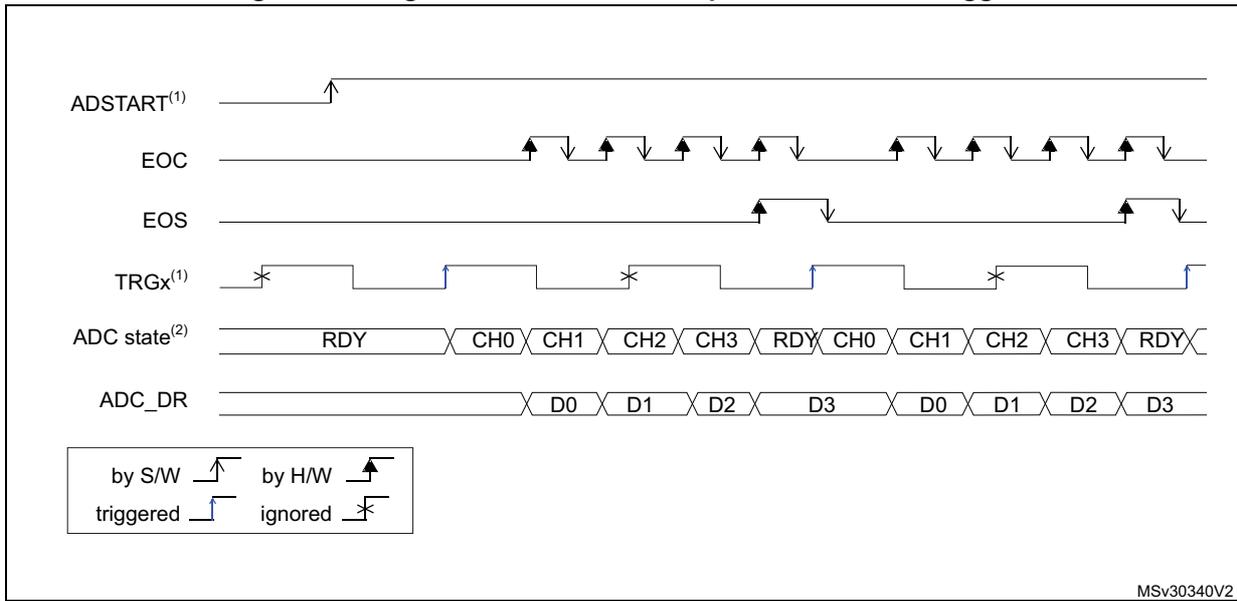

Figure 42. Single conversions of a sequence, hardware trigger

Timing diagram for single conversions of a sequence, hardware trigger. The diagram shows the relationship between several signals over time:

- ADSTART (1) : A software trigger signal that goes high to start the conversion sequence.

- EOC : End of Conversion signal, which pulses high when each conversion in the sequence is complete.

- EOS : End of Sequence signal, which goes high after the last conversion (CH3) and returns low after the next conversion starts.

- TRGx (1) : Hardware trigger signal. It is shown as a series of rising edges. The first edge is ignored (marked with an asterisk), and subsequent edges are triggered (marked with a vertical line).

- ADC state (2) : Shows the state of the ADC during conversions: RDY (Ready) → CH0 → CH1 → CH2 → CH3 → RDY → CH0 → CH1 → CH2 → CH3 → RDY.

- ADC_DR : Data Register, which outputs the conversion results: D0 → D1 → D2 → D3 → D0 → D1 → D2 → D3.

Legend:

- by S/W (Software): Rising edge

- by H/W (Hardware): Rising edge

- triggered: Rising edge

- ignored: Rising edge with an asterisk

MSv30340V2

- 1. EXTSEL = TRGx (over-frequency), EXTEN = 01 (rising edge), CONT = 0

- 2. CHSEL = 0xF, SCANDIR = 0, WAIT = 0, AUTOFF = 0

For code example, refer to A.8.7: Single conversion sequence code example - Hardware trigger .

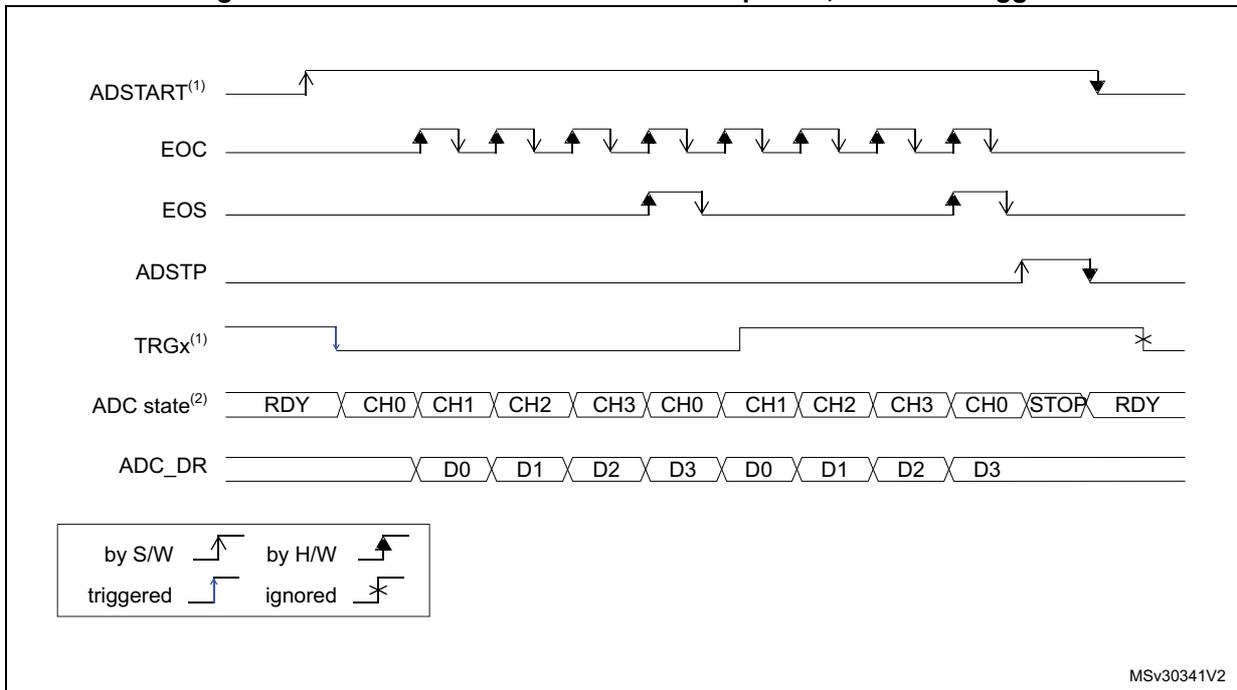

Figure 43. Continuous conversions of a sequence, hardware trigger

Timing diagram for continuous conversions of a sequence, hardware trigger. The diagram shows the relationship between several signals over time:

- ADSTART (1) : A software trigger signal that goes high to start the conversion sequence and low to stop it.

- EOC : End of Conversion signal, which pulses high when each conversion in the sequence is complete.

- EOS : End of Sequence signal, which goes high after the last conversion (CH3) and returns low after the next conversion starts.

- ADSTP : Stop Conversion signal, which goes high to stop the continuous conversion sequence.

- TRGx (1) : Hardware trigger signal. It is shown as a falling edge that starts the conversions and another falling edge that stops them (marked with an asterisk).

- ADC state (2) : Shows the state of the ADC during conversions: RDY → CH0 → CH1 → CH2 → CH3 → CH0 → CH1 → CH2 → CH3 → CH0 → STOP → RDY.

- ADC_DR : Data Register, which outputs the conversion results: D0 → D1 → D2 → D3 → D0 → D1 → D2 → D3.

Legend:

- by S/W (Software): Rising edge

- by H/W (Hardware): Falling edge

- triggered: Rising edge

- ignored: Rising edge with an asterisk

MSv30341V2

- 1. EXTSEL = TRGx, EXTEN = 10 (falling edge), CONT = 1

- 2. CHSEL = 0xF, SCANDIR = 0, WAIT = 0, AUTOFF = 0

For code example, refer to A.8.8: Continuous conversion sequence code example - Hardware trigger .

14.5 Data management

14.5.1 Data register and data alignment (ADC_DR, ALIGN)

At the end of each conversion (when an EOC event occurs), the result of the converted data is stored in the ADC_DR data register which is 16-bit wide.

The format of the ADC_DR depends on the configured data alignment and resolution.

The ALIGN bit in the ADC_CFGR1 register selects the alignment of the data stored after conversion. Data can be right-aligned (ALIGN = 0) or left-aligned (ALIGN = 1) as shown in Figure 44.

Figure 44. Data alignment and resolution (oversampling disabled: OVSE = 0)

| ALIGN | RES | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0x0 | 0x0 | DR[11:0] | ||||||||||||||

| 0x1 | 0x00 | DR[9:0] | |||||||||||||||

| 0x2 | 0x00 | DR[7:0] | |||||||||||||||

| 0x3 | 0x00 | DR[5:0] | |||||||||||||||

| 1 | 0x0 | DR[11:0] | 0x0 | ||||||||||||||

| 0x1 | DR[9:0] | 0x00 | |||||||||||||||

| 0x2 | DR[7:0] | 0x00 | |||||||||||||||

| 0x3 | 0x00 | DR[5:0] | 0x0 | ||||||||||||||

MS30342V1

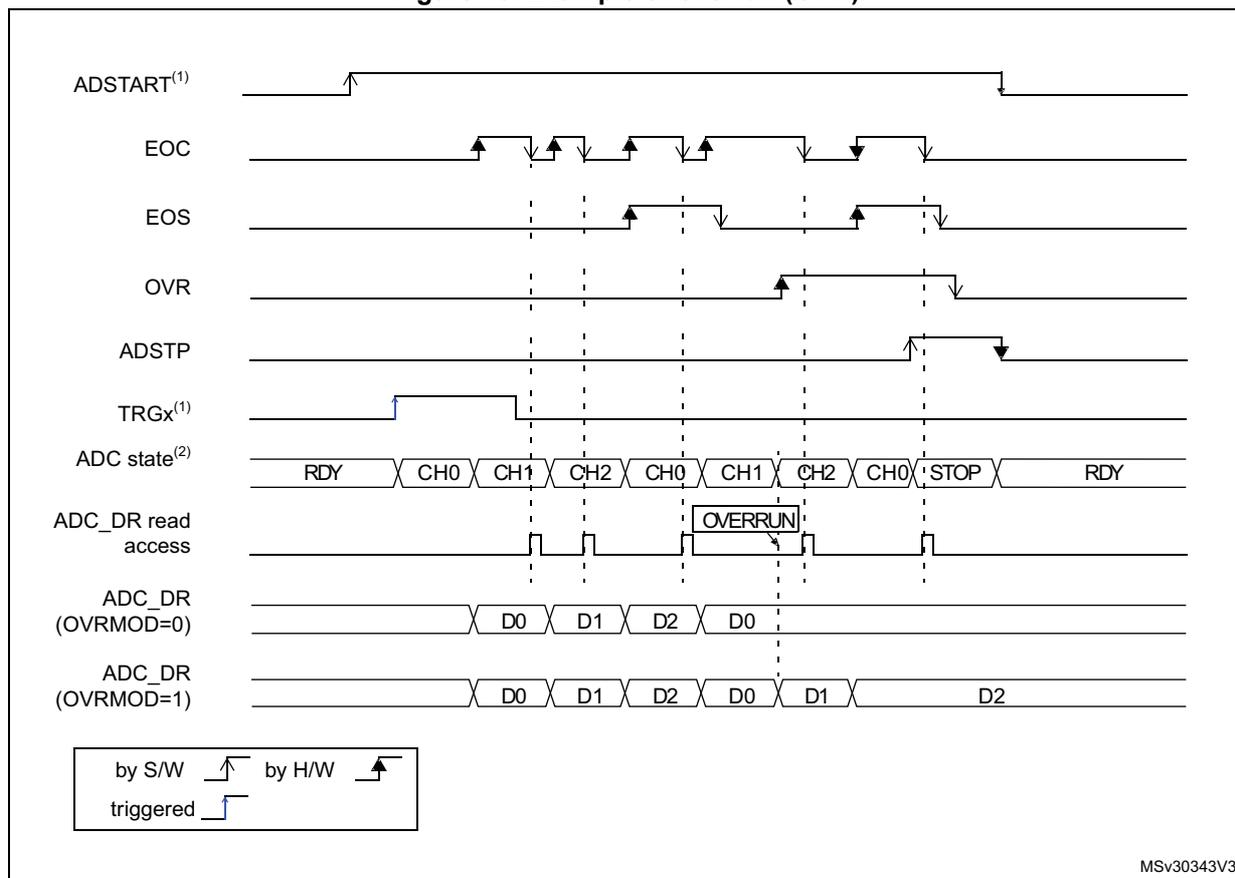

14.5.2 ADC overrun (OVR, OVRMOD)

The overrun flag (OVR) indicates a data overrun event, when the converted data was not read in time by the CPU or the DMA, before the data from a new conversion is available.

The OVR flag is set in the ADC_ISR register if the EOC flag is still at '1' at the time when a new conversion completes. An interrupt can be generated if the OVRRIE bit is set in the ADC_IER register.

When an overrun condition occurs, the ADC keeps operating and can continue to convert unless the software decides to stop and reset the sequence by setting the ADSTP bit in the ADC_CR register.

The OVR flag is cleared by software by writing 1 to it.

It is possible to configure if the data is preserved or overwritten when an overrun event occurs by programming the OVRMOD bit in the ADC_CFGR1 register:

- • OVRMOD = 0

- – An overrun event preserves the data register from being overwritten: the old data is maintained and the new conversion is discarded. If OVR remains at 1, further conversions can be performed but the resulting data is discarded.

- • OVRMOD = 1

- – The data register is overwritten with the last conversion result and the previous unread data is lost. If OVR remains at 1, further conversions can be performed and the ADC_DR register always contains the data from the latest conversion.

Figure 45. Example of overrun (OVR)

The diagram illustrates the timing of an ADC overrun (OVR) event. The signals shown are:

- ADSTART (1) : Start of conversion signal, set by software (S/W).

- EOC : End of Conversion flag, set by hardware (H/W) when a conversion is complete.

- EOS : End of Sequence flag, set by hardware (H/W) when the last conversion in a sequence is complete.

- OVR : Overrun flag, set by hardware (H/W) when a new conversion starts before the previous one is read.

- ADSTP : Stop conversion signal, set by software (S/W).

- TRGx (1) : Trigger signal, set by hardware (H/W).

- ADC state (2) : Sequence of states: RDY, CH0, CH1, CH2, CH0, CH1, CH2, CH0, STOP, RDY.

- ADC_DR read access : Software read access to the data register. An overrun occurs when a read is not performed before the next conversion completes.

- ADC_DR (OVRMOD=0) : Data register values: D0, D1, D2, D0. The value D0 is overwritten by D1 before it is read.

- ADC_DR (OVRMOD=1) : Data register values: D0, D1, D2, D0, D1, D2. The value D0 is overwritten by D1, but the previous value D2 is still present.

Legend:

- by S/W: Software triggered (upward arrow).

- by H/W: Hardware triggered (downward arrow).

MSV30343V3

14.5.3 Managing a sequence of data converted without using the DMA

If the conversions are slow enough, the conversion sequence can be handled by software. In this case the software must use the EOC flag and its associated interrupt to handle each data result. Each time a conversion is complete, the EOC bit is set in the ADC_ISR register and the ADC_DR register can be read. The OVRMOD bit in the ADC_CFGR1 register should be configured to 0 to manage overrun events as an error.

14.5.4 Managing converted data without using the DMA without overrun

It may be useful to let the ADC convert one or more channels without reading the data after each conversion. In this case, the OVRMOD bit must be configured at 1 and the OVR flag should be ignored by the software. When OVRMOD = 1, an overrun event does not prevent the ADC from continuing to convert and the ADC_DR register always contains the latest conversion data.

14.5.5 Managing converted data using the DMA

Since all converted channel values are stored in a single data register, it is efficient to use DMA when converting more than one channel. This avoids losing the conversion data results stored in the ADC_DR register.

When DMA mode is enabled (DMAEN bit set in the ADC_CFGR1 register), a DMA request is generated after the conversion of each channel. This allows the transfer of the converted data from the ADC_DR register to the destination location selected by the software.

Note: The DMAEN bit in the ADC_CFGR1 register must be set after the ADC calibration phase.

Despite this, if an overrun occurs (OVR = 1) because the DMA could not serve the DMA transfer request in time, the ADC stops generating DMA requests and the data corresponding to the new conversion is not transferred by the DMA. Which means that all the data transferred to the RAM can be considered as valid.

Depending on the configuration of OVRMOD bit, the data is either preserved or overwritten (refer to Section 14.5.2: ADC overrun (OVR, OVRMOD) on page 320 ).

The DMA transfer requests are blocked until the software clears the OVR bit.

Two different DMA modes are proposed depending on the application use and are configured with bit DMACFG in the ADC_CFGR1 register:

- • DMA one shot mode (DMACFG = 0).

This mode should be selected when the DMA is programmed to transfer a fixed number of data words. - • DMA circular mode (DMACFG = 1)

This mode should be selected when programming the DMA in circular mode.

DMA one shot mode (DMACFG = 0)

In this mode, the ADC generates a DMA transfer request each time a new conversion data word is available and stops generating DMA requests once the DMA has reached the last DMA transfer (when a DMA_EOT interrupt occurs, see Section 11: Direct memory access controller (DMA) on page 264 ) even if a conversion has been started again.

For code example, refer to A.8.9: DMA one shot mode sequence code example .

When the DMA transfer is complete (all the transfers configured in the DMA controller have been done):

- • The content of the ADC data register is frozen.

- • Any ongoing conversion is aborted and its partial result discarded

- • No new DMA request is issued to the DMA controller. This avoids generating an overrun error if there are still conversions which are started.

- • The scan sequence is stopped and reset

- • The DMA is stopped

DMA circular mode (DMACFG = 1)

In this mode, the ADC generates a DMA transfer request each time a new conversion data word is available in the data register, even if the DMA has reached the last DMA transfer. This allows the DMA to be configured in circular mode to handle a continuous analog input data stream.

For code example, refer to A.8.10: DMA circular mode sequence code example .

14.6 Low-power features

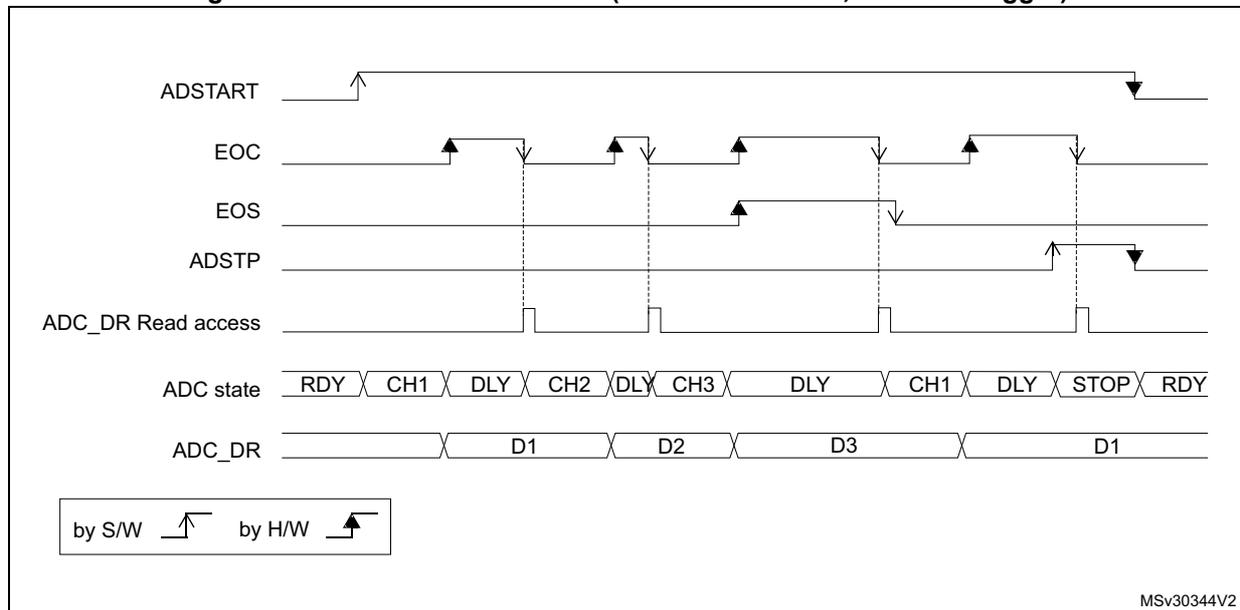

14.6.1 Wait mode conversion

Wait mode conversion can be used to simplify the software as well as optimizing the performance of applications clocked at low frequency where there might be a risk of ADC overrun occurring.

When the WAIT bit is set in the ADC_CFGR1 register, a new conversion can start only if the previous data has been treated, once the ADC_DR register has been read or if the EOC bit has been cleared.

This is a way to automatically adapt the speed of the ADC to the speed of the system that reads the data.

Note: Any hardware triggers which occur while a conversion is ongoing or during the wait time preceding the read access are ignored.

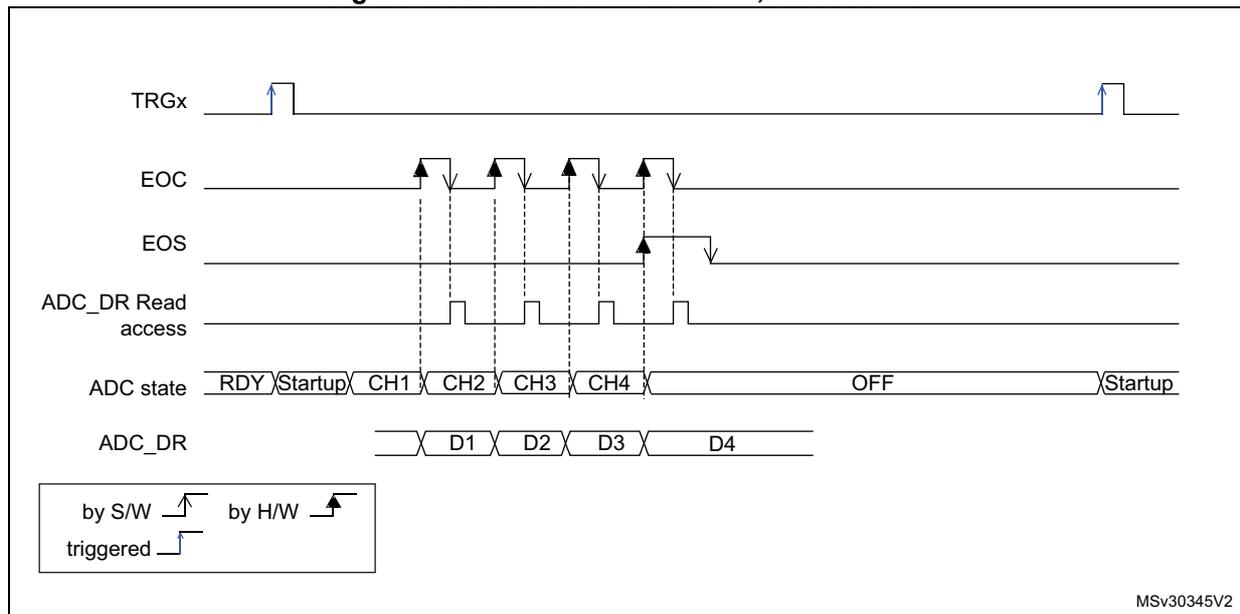

Figure 46. Wait mode conversion (continuous mode, software trigger)

- 1. EXTEN = 00, CONT = 1

- 2. CHSEL = 0x3, SCANDIR = 0, WAIT = 1, AUTOFF = 0

For code example, refer to A.8.11: Wait mode sequence code example .

14.6.2 Auto-off mode (AUTOFF)

The ADC has an automatic power management feature which is called auto-off mode, and is enabled by setting AUTOFF = 1 in the ADC_CFGR1 register.

When AUTOFF = 1, the ADC is always powered off when not converting and automatically wakes-up when a conversion is started (by software or hardware trigger). A startup-time is automatically inserted between the trigger event which starts the conversion and the sampling time of the ADC. The ADC is then automatically disabled once the sequence of conversions is complete.

Auto-off mode can cause a dramatic reduction in the power consumption of applications which need relatively few conversions or when conversion requests are timed far enough apart (for example with a low frequency hardware trigger) to justify the extra power and extra time used for switching the ADC on and off.

Auto-off mode can be combined with the wait mode conversion (WAIT = 1) for applications clocked at low frequency. This combination can provide significant power savings if the ADC is automatically powered-off during the wait phase and restarted as soon as the ADC_DR register is read by the application (see Figure 48: Behavior with WAIT = 1, AUTOFF = 1 ).

Note: Refer to the Section Reset and clock control (RCC) for the description of how to manage the dedicated 14 MHz internal oscillator. The ADC interface can automatically switch ON/OFF the 14 MHz internal oscillator to save power.

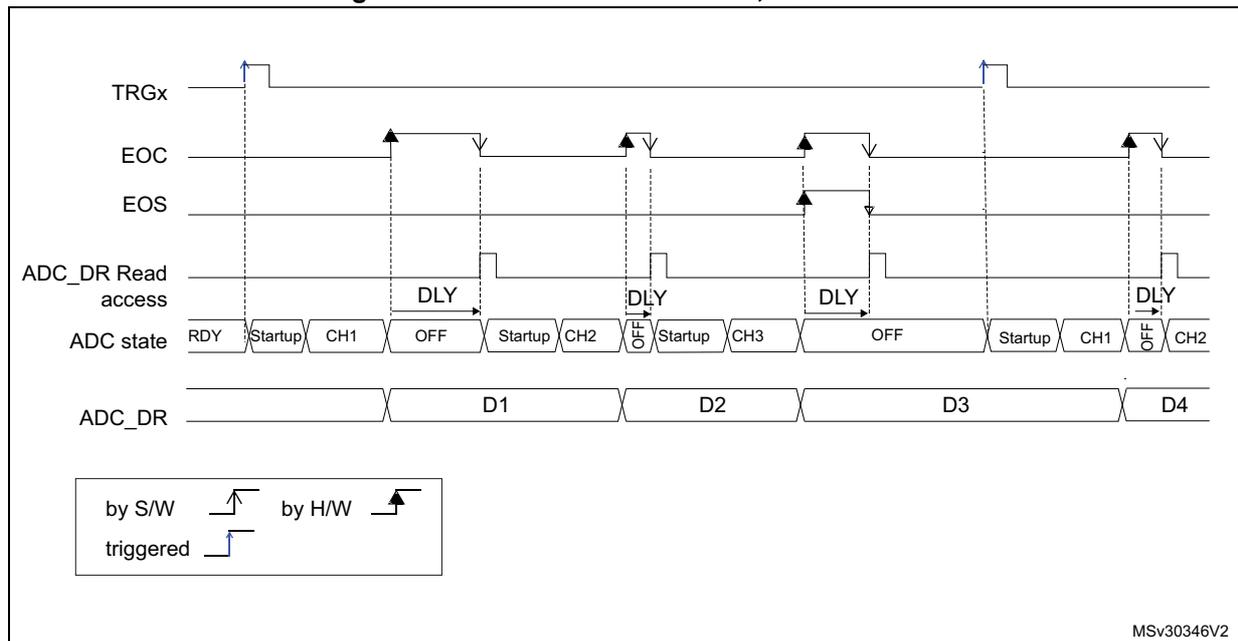

Figure 47. Behavior with WAIT = 0, AUTOFF = 1

The timing diagram shows the following signals and states over time:

- TRGx: Trigger signal. It shows two rising edges. The first rising edge is labeled 'by S/W triggered' (software trigger). The second rising edge is labeled 'by H/W' (hardware trigger).

- EOC (End of Conversion): A signal that pulses high for each conversion. It is shown as a series of four pulses corresponding to CH1, CH2, CH3, and CH4.

- EOS (End of Sequence): A signal that goes high after the last conversion (CH4) and returns low when the ADC_DR register is read.

- ADC_DR Read access: A signal showing the application reading the data register. It has four pulses corresponding to the data outputs D1, D2, D3, and D4.

- ADC state: Shows the state of the ADC. It starts at 'RDY', then goes to 'Startup' upon the first trigger. It then cycles through 'CH1', 'CH2', 'CH3', and 'CH4'. After the last conversion, it goes to 'OFF'. Upon the second trigger, it returns to 'Startup'.

- ADC_DR: The data register output. It shows four data values: D1, D2, D3, and D4, each appearing after its corresponding EOC pulse.

A legend at the bottom left indicates:

- by S/W triggered: Represented by a rising edge with a square wave symbol.

- by H/W: Represented by a rising edge with a triangle symbol.

MSv30345V2

- EXTSEL = TRGx, EXTEN = 01 (rising edge), CONT = x, ADSTART = 1, CHSEL = 0xF, SCANDIR = 0, WAIT = 0, AUTOFF = 1

For code example, refer to A.8.12: Auto off and no wait mode sequence code example .

Figure 48. Behavior with WAIT = 1, AUTOFF = 1

Legend:

- by S/W:

- by H/W:

- triggered:

MSv30346V2

- 1. EXTSEL = TRGx, EXTEN = 01 (rising edge), CONT = x, ADSTART = 1, CHSEL = 0xF, SCANDIR = 0, WAIT = 1, AUTOFF = 1

For code example, refer to A.8.13: Auto off and wait mode sequence code example .

14.7 Analog window watchdog (AWDEN, AWDSGL, AWDCH, ADC_TR)

14.7.1 Description of the analog watchdog

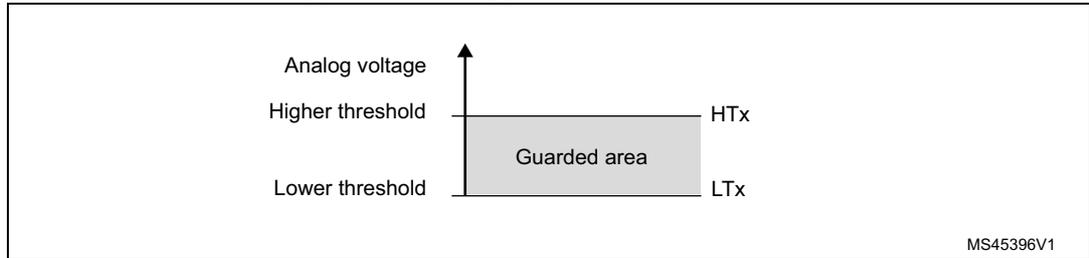

The AWD analog watchdog is enabled by setting the AWDEN bit in the ADC_CFGR1 register. It is used to monitor that either one selected channel or all enabled channels (see Table 65: Analog watchdog channel selection ) remain within a configured voltage range (window) as shown in Figure 49 .

The AWD analog watchdog status bit is set if the analog voltage converted by the ADC is below a lower threshold or above a higher threshold. These thresholds are programmed in HT[11:0] and LT[11:0] bit of ADC_TR register. An interrupt can be enabled by setting the AWDIE bit in the ADC_IER register.

The AWD flag is cleared by software by programming it to it.

When converting data with a resolution of less than 12-bit (according to bits RES[1:0]), the LSB of the programmed thresholds must be kept cleared because the internal comparison is always performed on the full 12-bit raw converted data (left aligned).

For code example, refer to A.8.14: Analog watchdog code example .

Table 64 describes how the comparison is performed for all the possible resolutions.

Table 64. Analog watchdog comparison

| Resolution bits RES[1:0] | Analog Watchdog comparison between: | Comments | |

|---|---|---|---|

| Raw converted data, left aligned (1) | Thresholds | ||

| 00: 12-bit | DATA[11:0] | LT[11:0] and HT[11:0] | - |

| 01: 10-bit | DATA[11:2],00 | LT[11:0] and HT[11:0] | The user must configure LT1[1:0] and HT1[1:0] to “00” |

| 10: 8-bit | DATA[11:4],0000 | LT[11:0] and HT[11:0] | The user must configure LT1[3:0] and HT1[3:0] to “0000” |

| 11: 6-bit | DATA[11:6],000000 | LT[11:0] and HT[11:0] | The user must configure LT1[5:0] and HT1[5:0] to “000000” |

1. The watchdog comparison is performed on the raw converted data before any alignment calculation.

Table 65 shows how to configure the AWDSGL and AWDEN bits in the ADC_CFGR1 register to enable the analog watchdog on one or more channels.

Figure 49. Analog watchdog guarded area

Table 65. Analog watchdog channel selection

| Channels guarded by the analog watchdog | AWDSGL bit | AWDEN bit |

|---|---|---|

| None | x | 0 |

| All channels | 0 | 1 |

| Single (1) channel | 1 | 1 |

1. Selected by the AWDCH[4:0] bits

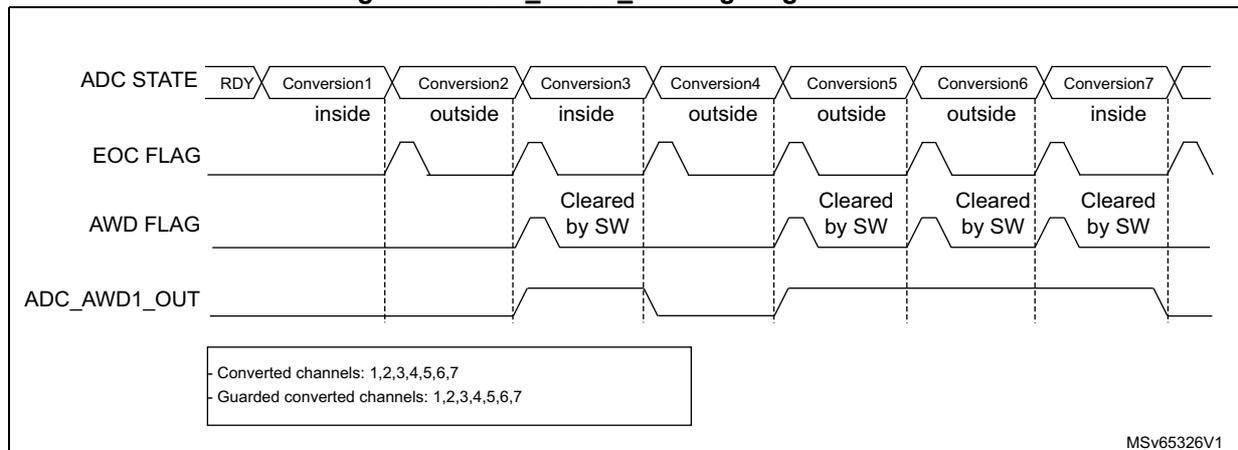

14.7.2 ADC_AWD1_OUT output signal generation

The analog watchdog is associated to an internal hardware signal, ADC_AWD1_OUT that is directly connected to the ETR input (external trigger) of some on-chip timers (refer to the timers section for details on how to select the ADC_AWD1_OUT signal as ETR).

ADC_AWD1_OUT is activated when the analog watchdog is enabled:

- • ADC_AWD1_OUT is set when a guarded conversion is outside the programmed thresholds.

- • ADC_AWD1_OUT is reset after the end of the next guarded conversion which is inside the programmed thresholds. It remains at 1 if the next guarded conversions are still outside the programmed thresholds.

- • ADC_AWD1_OUT is also reset when disabling the ADC (when setting ADDIS to 1). Note that stopping conversions (ADSTP set), might clear the ADC_AWD1_OUT state.

- • ADC_AWD1_OUT state does not change when the ADC converts the none-guarded channel (see Figure 50 )

AWD flag is set by hardware and reset by software: AWD flag has no influence on the generation of ADC_AWD1_OUT (as an example, ADC_AWD1_OUT can toggle while AWD flag remains at 1 if the software has not cleared the flag).

The ADC_AWD1_OUT signal is generated by the ADC_CLK domain. This signal can be generated even the APB clock is stopped.

The AWD comparison is performed at the end of each ADC conversion. The ADC_AWD1_OUT rising edge and falling edge occurs two ADC_CLK clock cycles after the comparison.

As ADC_AWD1_OUT is generated by the ADC_CLK domain and AWD flag is generated by the APB clock domain, the rising edges of these signals are not synchronized.

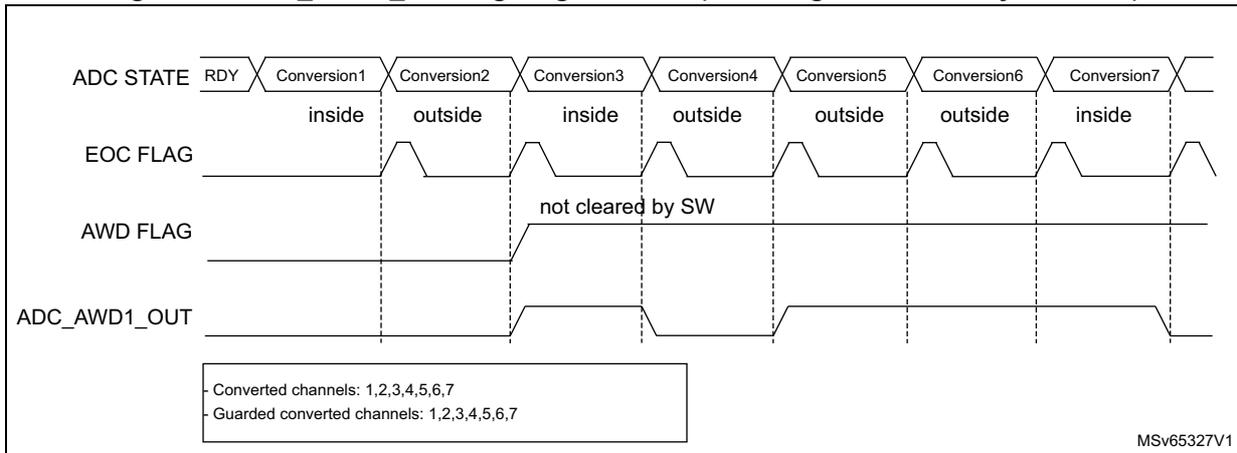

Figure 50. ADC_AWD1_OUT signal generation

The timing diagram shows the relationship between ADC STATE, EOC FLAG, AWD FLAG, and ADC_AWD1_OUT over seven conversions. The ADC STATE transitions through RDY, then seven conversions labeled as inside or outside. The EOC FLAG pulses at the end of every conversion. The AWD FLAG is set high when a conversion is 'outside' and is marked 'Cleared by SW'. ADC_AWD1_OUT goes high after an 'outside' conversion and returns low after an 'inside' conversion.

| Signal | RDY | Conv 1 (inside) | Conv 2 (outside) | Conv 3 (inside) | Conv 4 (outside) | Conv 5 (outside) | Conv 6 (outside) | Conv 7 (inside) |

|---|---|---|---|---|---|---|---|---|

| ADC STATE | RDY | inside | outside | inside | outside | outside | outside | inside |

| EOC FLAG | Low | Pulse | Pulse | Pulse | Pulse | Pulse | Pulse | Pulse |

| AWD FLAG | Low | Low | High (Cleared by SW) | Low | High (Cleared by SW) | High (Cleared by SW) | High (Cleared by SW) | Low |

| ADC_AWD1_OUT | Low | Low | High | Low | High | High | High | Low |

- Converted channels: 1,2,3,4,5,6,7

- Guarded converted channels: 1,2,3,4,5,6,7

MSv65326V1

Figure 51. ADC_AWD1_OUT signal generation (AWD flag not cleared by software)

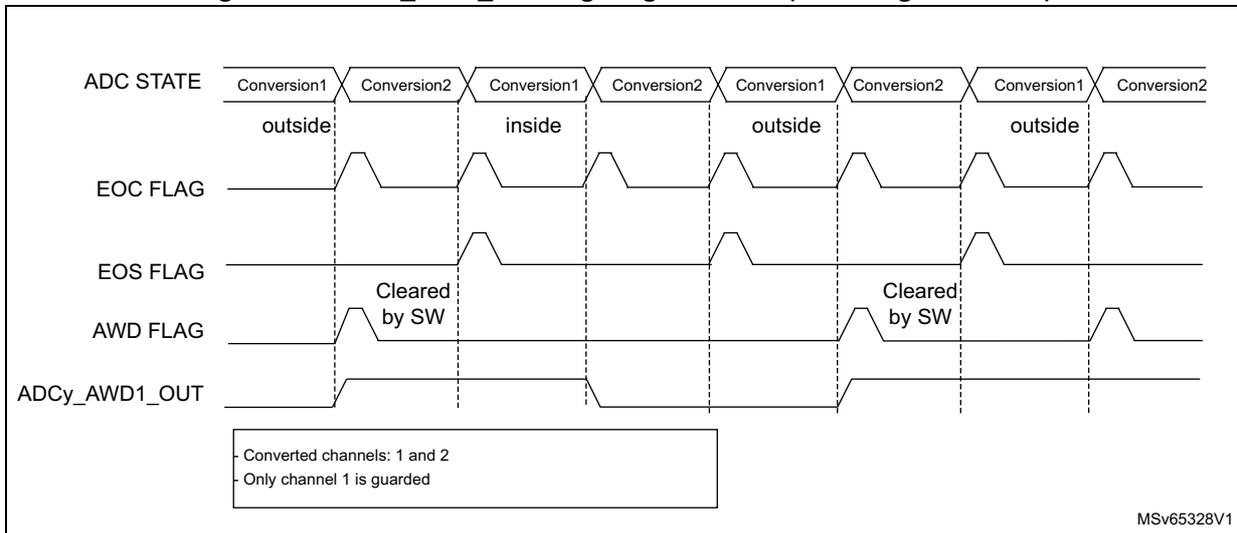

Figure 52. ADC1_AWD_OUT signal generation (on a single channel)

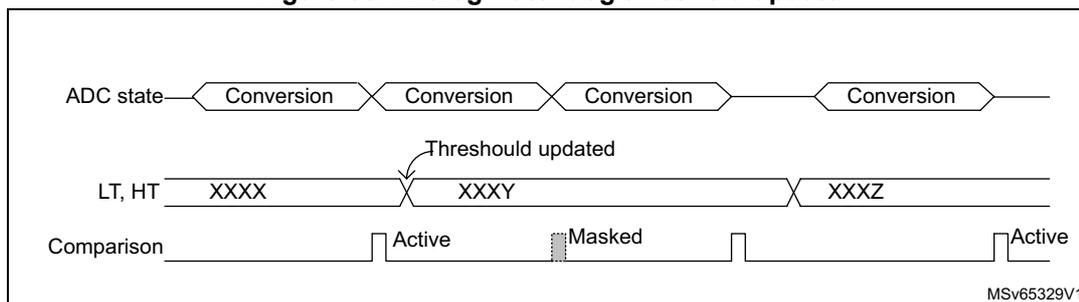

14.7.3 Analog watchdog threshold control

LT[11:0] and HT[11:0] can be changed during an analog-to-digital conversion (that is between the start of the conversion and the end of conversion of the ADC internal state). If LT and HT bits are programmed during the ADC guarded channel conversion, the watchdog function is masked for this conversion. This mask is cleared when starting a new conversion, and the resulting new AWD threshold is applied starting the next ADC conversion result. AWD comparison is performed at each end of conversion. If the current ADC data are out of the new threshold interval, this does not generate any interrupt or an ADC_AWD1_OUT signal. The Interrupt and the ADC_AWD1_OUT generation only occurs at the end of the ADC conversion that started after the threshold update. If ADC_AWD1_OUT is already asserted, programming the new threshold does not deassert the ADC_AWD1_OUT signal.

Figure 53. Analog watchdog threshold update

14.8 Oversampler

The oversampling unit performs data preprocessing to offload the CPU. It can handle multiple conversions and average them into a single data with increased data width, up to 16-bit.

It provides a result with the following form, where N and M can be adjusted:

It allows the following functions to be performed by hardware: averaging, data rate reduction, SNR improvement, basic filtering.

The oversampling ratio N is defined using the OVFS[2:0] bits in the ADC_CFGR2 register. It can range from 2x to 256x. The division coefficient M consists of a right bit shift up to 8 bits. It is configured through the OVSS[3:0] bits in the ADC_CFGR2 register.

For code example, refer to A.8.15: Oversampling code example .

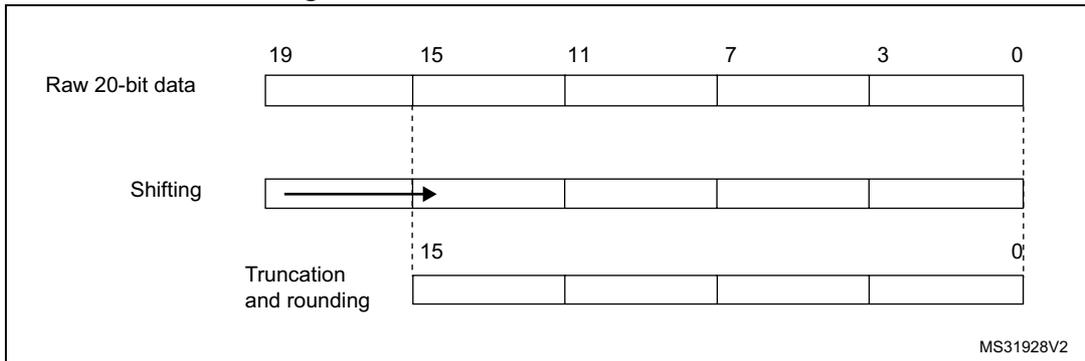

The summation unit can yield a result up to 20 bits (256 x 12-bit), which is first shifted right. The upper bits of the result are then truncated, keeping only the 16 least significant bits rounded to the nearest value using the least significant bits left apart by the shifting, before being finally transferred into the ADC_DR data register.

Note: If the intermediate result after the shifting exceeds 16 bits, the upper bits of the result are simply truncated.

Figure 54. 20-bit to 16-bit result truncation

The diagram illustrates the process of truncating a 20-bit raw data value to a 16-bit result. The raw data is shown in a 20-bit format with bit positions 19, 15, 11, 7, 3, and 0 marked. A 'Shifting' arrow indicates a right shift of 4 bits. The 'Truncation and rounding' step results in a 16-bit value, with bit positions 15 and 0 marked. The source identifier MS31928V2 is in the bottom right.

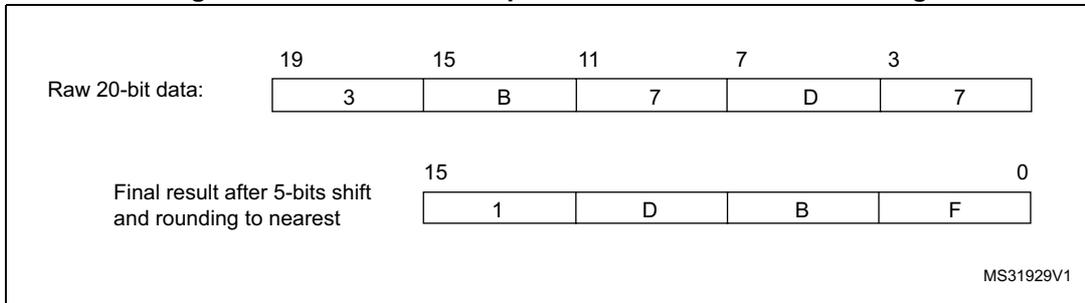

The Figure 55 gives a numerical example of the processing, from a raw 20-bit accumulated data to the final 16-bit result.

Figure 55. Numerical example with 5-bits shift and rounding

This diagram provides a numerical example of the conversion process. The raw 20-bit data is represented by the hex digits 3, B, 7, D, and 7, corresponding to bit groups 19-15, 11-7, and 3-0. After a 5-bit shift and rounding to the nearest, the final 16-bit result is 1, D, B, and F, corresponding to bit groups 15-11, 7-4, and 3-0. The source identifier MS31929V1 is in the bottom right.

The Table 66 below gives the data format for the various N and M combination, for a raw conversion data equal to 0xFFF.

Table 66. Maximum output results vs N and M. Grayed values indicates truncation

| Oversampling ratio | Max Raw data | No-shift OVSS = 0000 | 1-bit shift OVSS = 0001 | 2-bit shift OVSS = 0010 | 3-bit shift OVSS = 0011 | 4-bit shift OVSS = 0100 | 5-bit shift OVSS = 0101 | 6-bit shift OVSS = 0110 | 7-bit shift OVSS = 0111 | 8-bit shift OVSS = 1000 |

|---|---|---|---|---|---|---|---|---|---|---|

| 2x | 0x1FFE | 0x1FFE | 0x0FFF | 0x0800 | 0x0400 | 0x0200 | 0x0100 | 0x0080 | 0x0040 | 0x0020 |

| 4x | 0x3FFC | 0x3FFC | 0x1FFE | 0x0FFF | 0x0800 | 0x0400 | 0x0200 | 0x0100 | 0x0080 | 0x0040 |

| 8x | 0x7FF8 | 0x7FF8 | 0x3FFC | 0x1FFE | 0x0FFF | 0x0800 | 0x0400 | 0x0200 | 0x0100 | 0x0080 |

| 16x | 0xFFF0 | 0xFFF0 | 0x7FF8 | 0x3FFC | 0x1FFE | 0x0FFF | 0x0800 | 0x0400 | 0x0200 | 0x0100 |

| 32x | 0x1FFE0 | 0xFFE0 | 0xFFF0 | 0x7FF8 | 0x3FFC | 0x1FFE | 0x0FFF | 0x0800 | 0x0400 | 0x0200 |

| 64x | 0x3FFC0 | 0xFFC0 | 0xFFE0 | 0xFFF0 | 0x7FF8 | 0x3FFC | 0x1FFE | 0x0FFF | 0x0800 | 0x0400 |

| 128x | 0x7FF80 | 0xFF80 | 0xFFC0 | 0xFFE0 | 0xFFF0 | 0x7FF8 | 0x3FFC | 0x1FFE | 0x0FFF | 0x0800 |

| 256x | 0xFFF00 | 0xFF00 | 0xFF80 | 0xFFC0 | 0xFFE0 | 0xFFF0 | 0x7FF8 | 0x3FFC | 0x1FFE | 0x0FFF |

The conversion timings in oversampled mode do not change compared to standard conversion mode: the sample time is maintained equal during the whole oversampling

sequence. New data are provided every N conversion, with an equivalent delay equal to \( N \times t_{\text{CONV}} = N \times (t_{\text{SMP}} + t_{\text{SAR}}) \) . The flags features are raised as following:

- • the end of the sampling phase (EOSMP) is set after each sampling phase

- • the end of conversion (EOC) occurs once every N conversions, when the oversampled result is available

- • the end of sequence (EOCSEQ) occurs once the sequence of oversampled data is completed (i.e. after N x sequence length conversions total)

14.8.1 ADC operating modes supported when oversampling

In oversampling mode, most of the ADC operating modes are available:

- • Single or continuous mode conversions, forward or backward scanned sequences

- • ADC conversions start either by software or with triggers

- • ADC stop during a conversion (abort)

- • Data read via CPU or DMA with overrun detection

- • Low-power modes (WAIT, AUTOFF)

- • Programmable resolution: in this case, the reduced conversion values (as per RES[1:0] bits in ADC_CFGR1 register) are accumulated, truncated, rounded and shifted in the same way as 12-bit conversions are

Note: The alignment mode is not available when working with oversampled data. The ALIGN bit in ADC_CFGR1 is ignored and the data are always provided right-aligned.

14.8.2 Analog watchdog

The analog watchdog functionality is available (AWDSGL, AWDEN bits), with the following differences:

- • the RES[1:0] bits are ignored, comparison is always done on using the full 12-bits values HT[11:0] and LT[11:0]

- • the comparison is performed on the most significant 12 bits of the 16 bits oversampled results ADC_DR[15:4]

Note: Care must be taken when using high shifting values. This reduces the comparison range. For instance, if the oversampled result is shifted by 4 bits thus yielding a 12-bit data right-aligned, the affective analog watchdog comparison can only be performed on 8 bits. The comparison is done between ADC_DR[11:4] and HT[7:0] / LT[[7:0], and HT[11:8] / LT[11:8] must be kept reset.

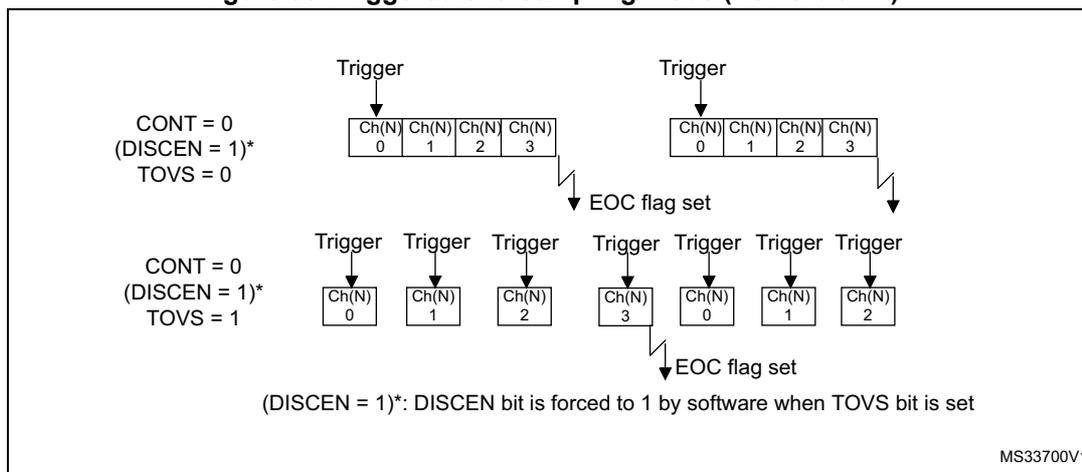

14.8.3 Triggered mode

The averager can also be used for basic filtering purposes. Although not a very efficient filter (slow roll-off and limited stop band attenuation), it can be used as a notch filter to reject constant parasitic frequencies (typically coming from the mains or from a switched mode power supply). For this purpose, a specific discontinuous mode can be enabled with TOVS bit in ADC_CFGR2, to be able to have an oversampling frequency defined by a user and independent from the conversion time itself.

Figure 56 below shows how conversions are started in response to triggers in discontinuous mode.

If the TOVS bit is set, the content of the DISCEN bit is ignored and considered as 1.

Figure 56. Triggered oversampling mode (TOVS bit = 1)

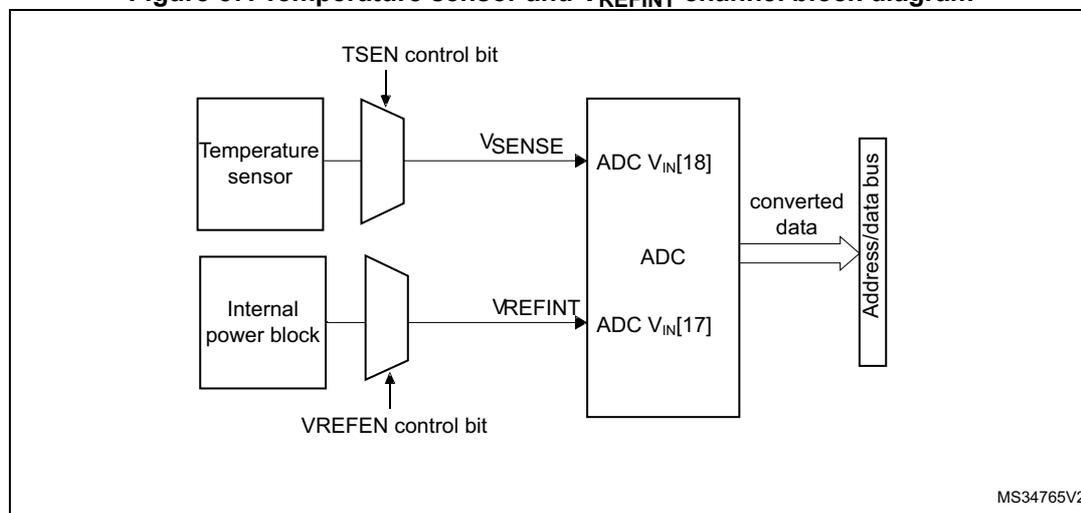

14.9 Temperature sensor and internal reference voltage

The temperature sensor can be used to measure the junction temperature ( T J ) of the device. The temperature sensor is internally connected to the ADC V IN [18] input channel which is used to convert the sensor's output voltage to a digital value. The sampling time for the temperature sensor analog pin must be greater than the minimum T S_temp value specified in the datasheet. When not in use, the sensor can be put in power down mode.

The internal voltage reference (V REFINT ) provides a stable (bandgap) voltage output for the ADC and comparators. V REFINT is internally connected to the ADC V IN [17] input channel. The precise voltage of V REFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

Figure 57 shows the block diagram of connections between the temperature sensor, the internal voltage reference and the ADC.

The TSEN bit must be set to enable the conversion of ADC V IN [18] (temperature sensor) and the VREFEN bit must be set to enable the conversion of ADC V IN [17] (V REFINT ).

The temperature sensor output voltage changes linearly with temperature. The offset of this line varies from chip to chip due to process variation (up to 45 °C from one chip to another).

The uncalibrated internal temperature sensor is more suited for applications that detect temperature variations instead of absolute temperatures. To improve the accuracy of the temperature sensor measurement, calibration values are stored in system memory for each device by ST during production.

During the manufacturing process, the calibration data of the temperature sensor and the internal voltage reference are stored in the system memory area. The user application can then read them and use them to improve the accuracy of the temperature sensor or the internal reference. Refer to the datasheet for additional information.

Main features

- Linearity: ±2 °C max., precision depending on calibration

Figure 57. Temperature sensor and V REFINT channel block diagram

The diagram illustrates the signal path for temperature and reference voltage measurement. It shows two main blocks on the left: "Temperature sensor" and "Internal power block". The Temperature sensor output goes through a multiplexer controlled by the "TSEN control bit" to become V SENSE , which enters the ADC at V IN [18]. The Internal power block output goes through a multiplexer controlled by the "VREFEN control bit" to become V REFINT , which enters the ADC at V IN [17]. The ADC block processes these inputs and outputs "converted data" to an "Address/data bus". The diagram is identified by the code MS34765V2.

Reading the temperature

- Select the ADC V IN [18] input channel.

- Select an appropriate sampling time specified in the device datasheet (T S_temp ).

- Set the TSEN bit in the ADC_CCR register to wake up the temperature sensor from power down mode and wait for its stabilization time (t

START

).

For code example, refer to A.8.16: Temperature configuration code example . - Start the ADC conversion by setting the ADSTART bit in the ADC_CR register (or by external trigger).

- Read the resulting V SENSE data in the ADC_DR register.

- Calculate the temperature using the following formula

Where:

- TS_CAL2 is the temperature sensor calibration value acquired at TS_CAL2_TEMP (refer to the datasheet for TS_CAL2 value)

- TS_CAL1 is the temperature sensor calibration value acquired at TS_CAL1_TEMP (refer to the datasheet for TS_CAL1 value)

- TS_DATA is the actual temperature sensor output value converted by ADC

Refer to the specific device datasheet for more information about TS_CAL1 and TS_CAL2 calibration points.

For code example, refer to A.8.17: Temperature computation code example .

Note: The sensor has a startup time after waking from power down mode before it can output V SENSE at the correct level. The ADC also has a startup time after power-on, so to minimize the delay, the ADEN and TSEN bits should be set at the same time.

Calculating the actual \( V_{DDA} \) voltage using the internal reference voltage

The \( V_{DDA} \) power supply voltage applied to the device may be subject to variation or not precisely known. The embedded internal voltage reference ( \( V_{REFINT} \) ) and its calibration data, acquired by the ADC during the manufacturing process at \( V_{DDA\_Charac} \) , can be used to evaluate the actual \( V_{DDA} \) voltage level.

The following formula gives the actual \( V_{DDA} \) voltage supplying the device:

Where:

- • \( V_{DDA\_Charac} \) is the value of \( V_{DDA} \) voltage characterized at \( V_{REFINT} \) during the manufacturing process. It is specified in the device datasheet.

- • \( VREFINT\_CAL \) is the \( VREFINT \) calibration value

- • \( VREFINT\_DATA \) is the actual \( VREFINT \) output value converted by ADC

Converting a supply-relative ADC measurement to an absolute voltage value

The ADC is designed to deliver a digital value corresponding to the ratio between the analog power supply and the voltage applied on the converted channel. For most application use cases, it is necessary to convert this ratio into a voltage independent of \( V_{DDA} \) . For applications where \( V_{DDA} \) is known and ADC converted values are right-aligned you can use the following formula to get this absolute value:

For applications where \( V_{DDA} \) value is not known, you must use the internal voltage reference and \( V_{DDA} \) can be replaced by the expression provided in Section : Calculating the actual \( V_{DDA} \) voltage using the internal reference voltage , resulting in the following formula:

Where:

- • \( V_{DDA\_Charac} \) is the value of \( V_{DDA} \) voltage characterized at \( V_{REFINT} \) during the manufacturing process. It is specified in the device datasheet.

- • \( VREFINT\_CAL \) is the \( VREFINT \) calibration value

- • \( ADC\_DATA_x \) is the value measured by the ADC on channelx (right-aligned)

- • \( VREFINT\_DATA \) is the actual \( VREFINT \) output value converted by the ADC

- • \( full\_SCALE \) is the maximum digital value of the ADC output. For example with 12-bit resolution, it is \( 2^{12} - 1 = 4095 \) or with 8-bit resolution, \( 2^8 - 1 = 255 \) .

Note: If ADC measurements are done using an output format other than 12 bit right-aligned, all the parameters must first be converted to a compatible format before the calculation is done.

14.10 \( V_{LCD} \) voltage monitoring

The VLCDEN bit in the ADC_CCR register allows to measure the LCD supply voltage on the VLCD pin. As the \( V_{LCD} \) voltage can be higher than \( V_{DDA} \) , to ensure the correct operation of the ADC, the VLCD pin is internally connected to a bridge divider. This bridge is automatically enabled when VLCDEN bit is set, to connect LCD_VLCD1 to the ADC1_IN16 input channel. As a consequence, the converted digital value is either one third of \( V_{LCD} \)

voltage when the LCD is configured to 1/3Bias or a quarter of \( V_{LCD} \) voltage when the LCD is configured to 1/4Bias or 1/2Bias. To prevent any unwanted consumption on the battery, it is recommended to enable the bridge divider only when needed, that is to perform ADC conversions.

14.11 ADC interrupts

An interrupt can be generated by any of the following events:

- • End Of Calibration (EOCAL flag)

- • ADC power-up, when the ADC is ready (ADRDY flag)

- • End of any conversion (EOC flag)

- • End of a sequence of conversions (EOS flag)

- • When an analog watchdog detection occurs (AWD flag)

- • When the end of sampling phase occurs (EOSMP flag)

- • when a data overrun occurs (OVR flag)

Separate interrupt enable bits are available for flexibility.

Table 67. ADC interrupts

| Interrupt event | Event flag | Enable control bit |

|---|---|---|

| End Of Calibration | EOCAL | EOCALIE |

| ADC ready | ADRDY | ADRDYIE |

| End of conversion | EOC | EOCIE |

| End of sequence of conversions | EOS | EOSIE |

| Analog watchdog status bit is set | AWD | AWDIE |

| End of sampling phase | EOSMP | EOSMPIE |

| Overrun | OVR | OVRIE |

14.12 ADC registers

Refer to Section 1.2 for a list of abbreviations used in register descriptions.

14.12.1 ADC interrupt and status register (ADC_ISR)

Address offset: 0x00

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | EOCAL | Res. | Res. | Res. | AWD | Res. | Res. | OVR | EOS | EOC | EOSMP | ADRDY |

| rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | rc_w1 | |||||||||

Bits 31:13 Reserved, must be kept at reset value.

Bit 12 Reserved, must be kept at reset value.

Bit 11 EOCAL : End Of Calibration flag

This bit is set by hardware when calibration is complete. It is cleared by software writing 1 to it.

0: Calibration is not complete

1: Calibration is complete

Bit 10 Reserved, must be kept at reset value.

Bits 9:8 Reserved, must be kept at reset value.

Bit 7 AWD : Analog watchdog flag

This bit is set by hardware when the converted voltage crosses the values programmed in ADC_TR register. It is cleared by software by programming it to 1.

0: No analog watchdog event occurred (or the flag event was already acknowledged and cleared by software)

1: Analog watchdog event occurred

Bits 6:5 Reserved, must be kept at reset value.

Bit 4 OVR : ADC overrun

This bit is set by hardware when an overrun occurs, meaning that a new conversion has complete while the EOC flag was already set. It is cleared by software writing 1 to it.

0: No overrun occurred (or the flag event was already acknowledged and cleared by software)

1: Overrun has occurred

Bit 3 EOS : End of sequence flag

This bit is set by hardware at the end of the conversion of a sequence of channels selected by the CHSEL bits. It is cleared by software writing 1 to it.

0: Conversion sequence not complete (or the flag event was already acknowledged and cleared by software)

1: Conversion sequence complete

Bit 2 EOC : End of conversion flag

This bit is set by hardware at the end of each conversion of a channel when a new data result is available in the ADC_DR register. It is cleared by software writing 1 to it or by reading the ADC_DR register.

0: Channel conversion not complete (or the flag event was already acknowledged and cleared by software)

1: Channel conversion complete

Bit 1 EOSMP : End of sampling flag

This bit is set by hardware during the conversion, at the end of the sampling phase. It is cleared by software by programming it to '1'.

0: Not at the end of the sampling phase (or the flag event was already acknowledged and cleared by software)

1: End of sampling phase reached

Bit 0 ADRDY : ADC ready

This bit is set by hardware after the ADC has been enabled (ADEN = 1) and when the ADC reaches a state where it is ready to accept conversion requests.

It is cleared by software writing 1 to it.

0: ADC not yet ready to start conversion (or the flag event was already acknowledged and cleared by software)

1: ADC is ready to start conversion

14.12.2 ADC interrupt enable register (ADC_IER)

Address offset: 0x04

Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | Res. | Res. | Res. | EOCAL IE | Res. | Res. | Res. | AWDIE | Res. | Res. | OVRIE | EOSIE | EOCIE | EOSMP IE | ADRDY IE |

| rw | rw | rw | rw | rw | rw | rw | |||||||||

Bits 31:13 Reserved, must be kept at reset value.

Bit 12 Reserved, must be kept at reset value.

Bit 11 EOCALIE : End of calibration interrupt enable

This bit is set and cleared by software to enable/disable the end of calibration interrupt.

0: End of calibration interrupt disabled

1: End of calibration interrupt enabled

Note: The software is allowed to write this bit only when ADSTART bit is cleared (this ensures that no conversion is ongoing).

Bit 10 Reserved, must be kept at reset value.

Bits 9:8 Reserved, must be kept at reset value.

Bit 7 AWDIE: Analog watchdog interrupt enableThis bit is set and cleared by software to enable/disable the analog watchdog interrupt.

0: Analog watchdog interrupt disabled

1: Analog watchdog interrupt enabled

Note: The Software is allowed to write this bit only when ADSTART bit is cleared (this ensures that no conversion is ongoing).

Bits 6:5 Reserved, must be kept at reset value.