17. Advanced-control timer (TIM1)

In this section, “TIMx” should be understood as “TIM1” since there is only one instance of this type of timer for the products to which this reference manual applies.

17.1 TIM1 introduction

The advanced-control timer (TIM1) consists of a 16-bit auto-reload counter driven by a programmable prescaler.

It may be used for a variety of purposes, including measuring the pulse lengths of input signals (input capture) or generating output waveforms (output compare, PWM, complementary PWM with dead-time insertion).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the RCC clock controller prescalers.

The advanced-control (TIM1) and general-purpose (TIMy) timers are completely independent, and do not share any resources. They can be synchronized together as described in Section 17.3.25: Timer synchronization .

17.2 TIM1 main features

TIM1 timer features include:

- • 16-bit up, down, up/down auto-reload counter.

- • 16-bit programmable prescaler allowing dividing (also “on the fly”) the counter clock frequency either by any factor between 1 and 65536.

- • Up to 6 independent channels for:

- – Input Capture (but channels 5 and 6)

- – Output Compare

- – PWM generation (Edge and Center-aligned Mode)

- – One-pulse mode output

- • Complementary outputs with programmable dead-time

- • Synchronization circuit to control the timer with external signals and to interconnect several timers together.

- • Repetition counter to update the timer registers only after a given number of cycles of the counter.

- • 2 break inputs to put the timer’s output signals in a safe user selectable configuration.

- • Interrupt/DMA generation on the following events:

- – Update: counter overflow/underflow, counter initialization (by software or internal/external trigger)

- – Trigger event (counter start, stop, initialization or count by internal/external trigger)

- – Input capture

- – Output compare

- • Supports incremental (quadrature) encoder and Hall-sensor circuitry for positioning purposes

- • Trigger input for external clock or cycle-by-cycle current management

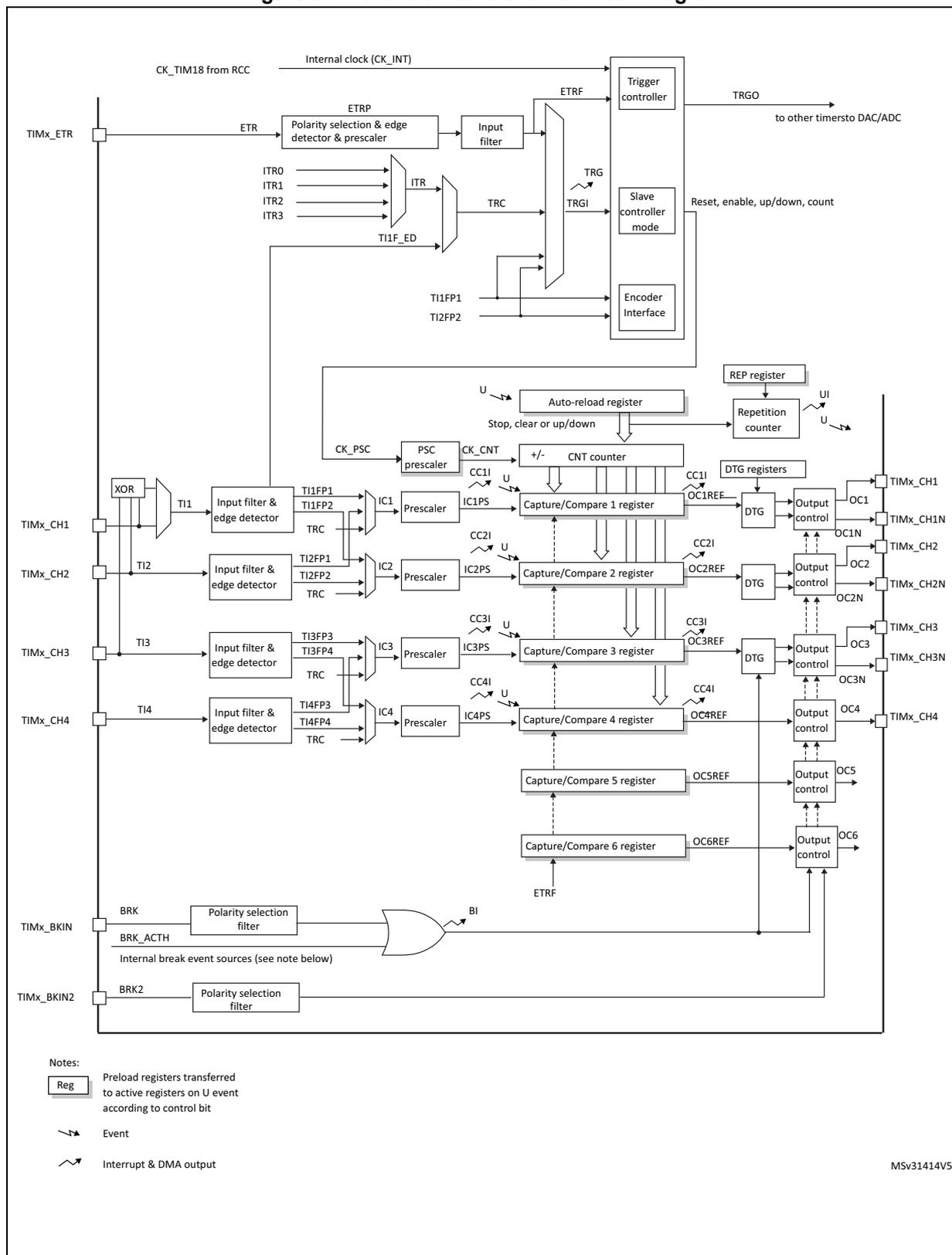

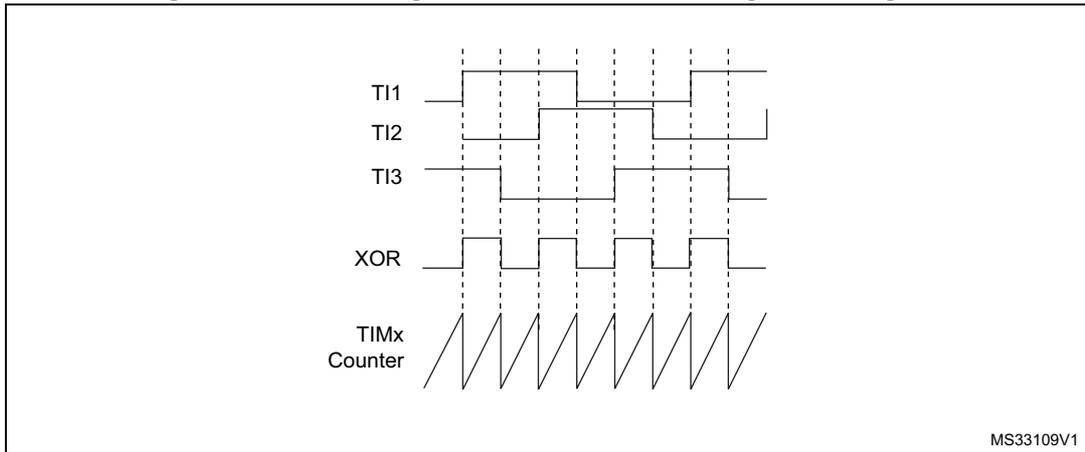

Figure 92. Advanced-control timer block diagram

The block diagram illustrates the internal architecture of the Advanced-control timer (TIM1). At the top, the internal clock (CK_INT) from RCC is connected to the Trigger controller, Slave controller mode, and Encoder Interface. The ETR input is processed through a polarity selection & edge detector & prescaler, resulting in ETRF, which is then filtered and sent to the Trigger controller. ITR0, ITR1, ITR2, and ITR3 inputs are combined via an ITR block, resulting in TRC, which is also filtered and sent to the Trigger controller. TI1F_ED, TI1FP1, and TI2FP2 inputs are connected to the Encoder Interface. The Trigger controller outputs TRGO to other timers/DAC/ADC and provides reset, enable, up/down, and count signals to the Slave controller mode. The Slave controller mode is connected to the Auto-reload register, REP register, and CNT counter. The CNT counter is a +/- counter that receives CK_CNT from the PSC prescaler. The PSC prescaler receives CK_PSC. The Auto-reload register and REP register are connected to the Repetition counter. The Repetition counter outputs UI. The CNT counter is connected to Capture/Compare 1 register, Capture/Compare 2 register, Capture/Compare 3 register, Capture/Compare 4 register, Capture/Compare 5 register, and Capture/Compare 6 register. Each Capture/Compare register is connected to a Prescaler and a DTG register. The Prescalers receive IC1, IC2, IC3, and IC4 from the Input filter & edge detector blocks. The Input filter & edge detector blocks receive TI1, TI2, TI3, and TI4 inputs. The DTG registers are connected to Output control blocks for OC1, OC2, OC3, OC4, OC5, and OC6. The Output control blocks also receive signals from the Capture/Compare registers and the ETRF input. The OC1, OC2, OC3, and OC4 outputs are TIMx_CH1, TIMx_CH2, TIMx_CH3, and TIMx_CH4 respectively. The OC1N, OC2N, OC3N, and OC4N outputs are TIMx_CH1N, TIMx_CH2N, TIMx_CH3N, and TIMx_CH4N respectively. The OC5 and OC6 outputs are TIMx_CH5 and TIMx_CH6 respectively. The BRK input is processed through a polarity selection filter, resulting in BI, which is then combined with internal break event sources via an OR gate. The BRK2 input is processed through a polarity selection filter, resulting in BRK2. The BRK and BRK2 inputs are connected to the Output control blocks for OC1, OC2, OC3, OC4, OC5, and OC6.

Notes:

Reg

Preload registers transferred to active registers on U event according to control bit

Event

Interrupt & DMA output

MSv31414V5

- 1. The internal break event source can be:

- - A clock failure event generated by CSS. For further information on the CSS, refer to Section 7.2.7: Clock security system (CSS)

- - A PVD output

- - SRAM parity error signal

- - Cortex®-M4F LOCKUP (Hardfault) output.

- - COMP Output.

17.3 TIM1 functional description

17.3.1 Time-base unit

The main block of the programmable advanced-control timer is a 16-bit counter with its related auto-reload register. The counter can count up, down or both up and down. The counter clock can be divided by a prescaler.

The counter, the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running.

The time-base unit includes:

- • Counter register (TIMx_CNT)

- • Prescaler register (TIMx_PSC)

- • Auto-reload register (TIMx_ARR)

- • Repetition counter register (TIMx_RCR)

The auto-reload register is preloaded. Writing to or reading from the auto-reload register accesses the preload register. The content of the preload register are transferred into the shadow register permanently or at each update event (UEV), depending on the auto-reload preload enable bit (ARPE) in TIMx_CR1 register. The update event is sent when the counter reaches the overflow (or underflow when downcounting) and if the UDIS bit equals 0 in the TIMx_CR1 register. It can also be generated by software. The generation of the update event is described in detailed for each configuration.

The counter is clocked by the prescaler output CK_CNT, which is enabled only when the counter enable bit (CEN) in TIMx_CR1 register is set (refer also to the slave mode controller description to get more details on counter enabling).

Note that the counter starts counting 1 clock cycle after setting the CEN bit in the TIMx_CR1 register.

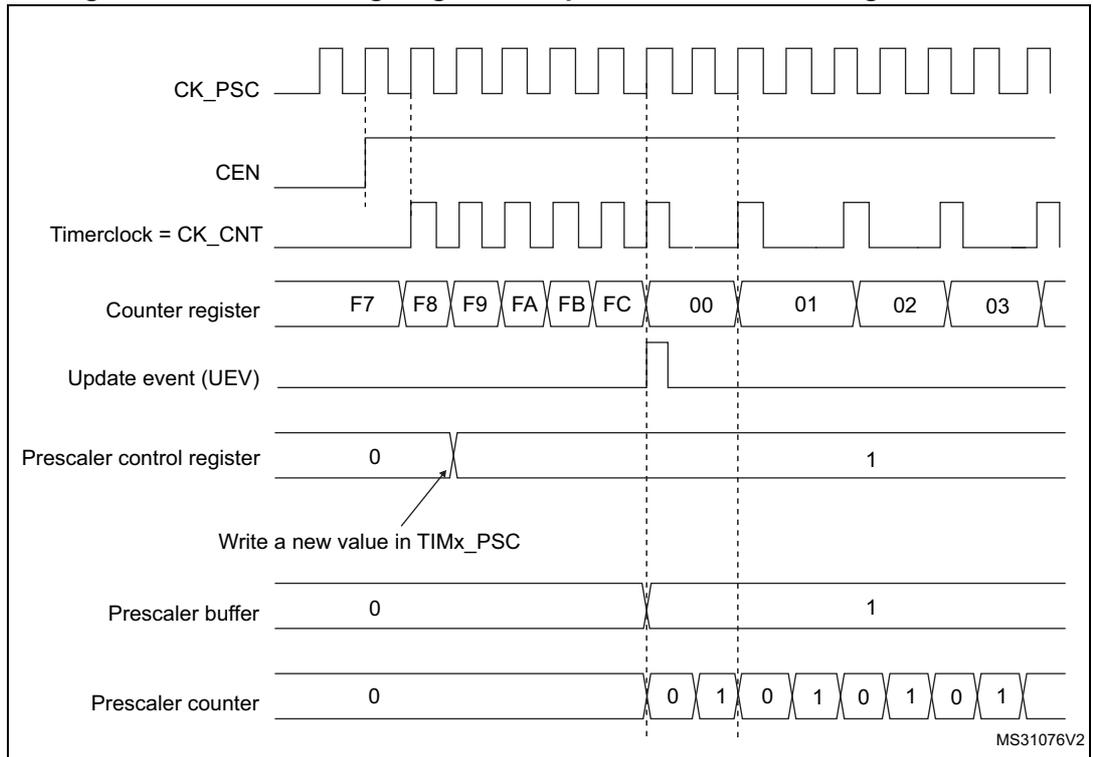

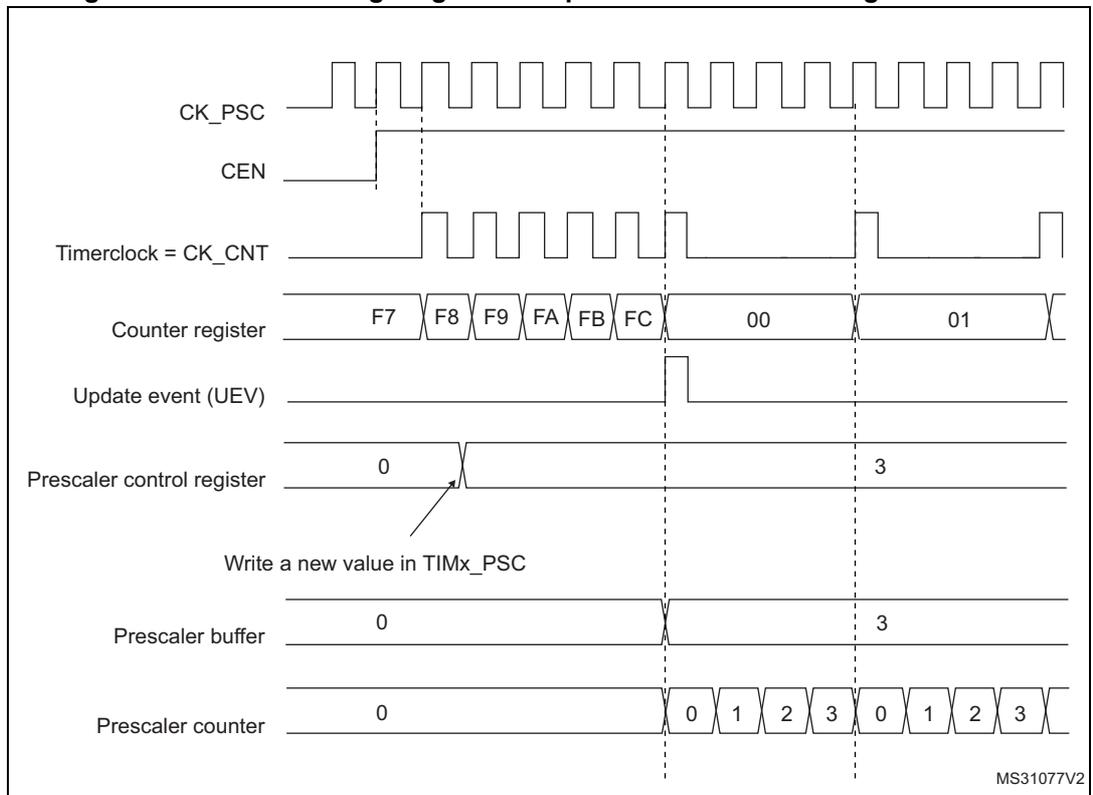

Prescaler description

The prescaler can divide the counter clock frequency by any factor between 1 and 65536. It is based on a 16-bit counter controlled through a 16-bit register (in the TIMx_PSC register). It can be changed on the fly as this control register is buffered. The new prescaler ratio is taken into account at the next update event.

Figure 93 and Figure 94 give some examples of the counter behavior when the prescaler ratio is changed on the fly:

Figure 93. Counter timing diagram with prescaler division change from 1 to 2

The diagram illustrates the timing of an advanced-control timer (TIM1) when the prescaler division is changed from 1 to 2. The top signal, CK_PSC, is a periodic clock. Below it, CEN (Counter Enable) is shown as a high-level signal. The Timerclock = CK_CNT signal is derived from CK_PSC. The Counter register shows a sequence of values: F7, F8, F9, FA, FB, FC, followed by 00, 01, 02, and 03. An Update event (UEV) is indicated by a pulse. The Prescaler control register is initially set to 0. A note indicates that a new value (1) is written in TIMx_PSC. This value is then reflected in the Prescaler buffer and the Prescaler counter. The Prescaler counter is shown as a sequence of 0, 1, 0, 1, 0, 1, 0, 1, indicating a division of 2. The diagram is labeled MS31076V2.

Figure 94. Counter timing diagram with prescaler division change from 1 to 4

The diagram illustrates the timing of an advanced-control timer (TIM1) when the prescaler division is changed from 1 to 4. The top signal, CK_PSC, is a periodic clock. Below it, CEN (Counter Enable) is shown as a high-level signal. The Timerclock = CK_CNT signal is derived from CK_PSC. The Counter register shows a sequence of values: F7, F8, F9, FA, FB, FC, followed by 00, 01. An Update event (UEV) is indicated by a pulse. The Prescaler control register is initially set to 0. A note indicates that a new value (3) is written in TIMx_PSC. This value is then reflected in the Prescaler buffer and the Prescaler counter. The Prescaler counter is shown as a sequence of 0, 1, 2, 3, 0, 1, 2, 3, indicating a division of 4. The diagram is labeled MS31077V2.

17.3.2 Counter modes

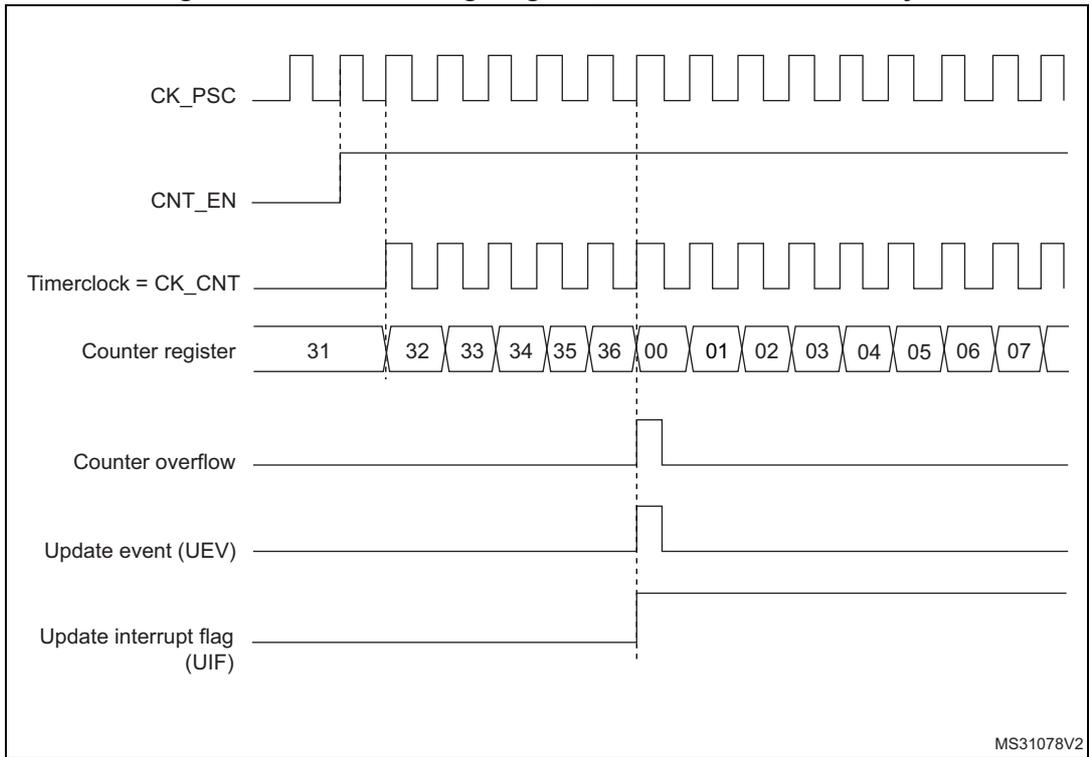

Upcounting mode

In upcounting mode, the counter counts from 0 to the auto-reload value (content of the TIMx_ARR register), then restarts from 0 and generates a counter overflow event.

If the repetition counter is used, the update event (UEV) is generated after upcounting is repeated for the number of times programmed in the repetition counter register (TIMx_RCR) + 1. Else the update event is generated at each counter overflow.

Setting the UG bit in the TIMx_EGR register (by software or by using the slave mode controller) also generates an update event.

The UEV event can be disabled by software by setting the UDIS bit in the TIMx_CR1 register. This is to avoid updating the shadow registers while writing new values in the preload registers. Then no update event occurs until the UDIS bit has been written to 0. However, the counter restarts from 0, as well as the counter of the prescaler (but the prescale rate does not change). In addition, if the URS bit (update request selection) in TIMx_CR1 register is set, setting the UG bit generates an update event UEV but without setting the UIF flag (thus no interrupt or DMA request is sent). This is to avoid generating both update and capture interrupts when clearing the counter on the capture event.

When an update event occurs, all the registers are updated and the update flag (UIF bit in TIMx_SR register) is set (depending on the URS bit):

- • The repetition counter is reloaded with the content of TIMx_RCR register,

- • The auto-reload shadow register is updated with the preload value (TIMx_ARR),

- • The buffer of the prescaler is reloaded with the preload value (content of the TIMx_PSC register).

The following figures show some examples of the counter behavior for different clock frequencies when TIMx_ARR=0x36.

Figure 95. Counter timing diagram, internal clock divided by 1

This timing diagram illustrates the operation of the TIM1 counter when the internal clock is divided by 1. The diagram consists of seven horizontal signal lines. The first line, CK_PSC, shows a periodic square wave. The second line, CNT_EN, is a signal that goes high to enable the counter. The third line, Timerclock = CK_CNT, shows the clock signal for the counter, which is a square wave with a frequency twice that of CK_PSC. The fourth line, Counter register, shows the sequence of values: 31, 32, 33, 34, 35, 36, 00, 01, 02, 03, 04, 05, 06, 07. The fifth line, Counter overflow, is a pulse that goes high when the counter reaches 36 and returns low at 00. The sixth line, Update event (UEV), is a pulse that goes high when the counter reaches 36 and returns low at 00. The seventh line, Update interrupt flag (UIF), is a signal that goes high when the counter reaches 36 and returns low at 00. Vertical dashed lines indicate the timing relationships between the signals.

MS31078V2

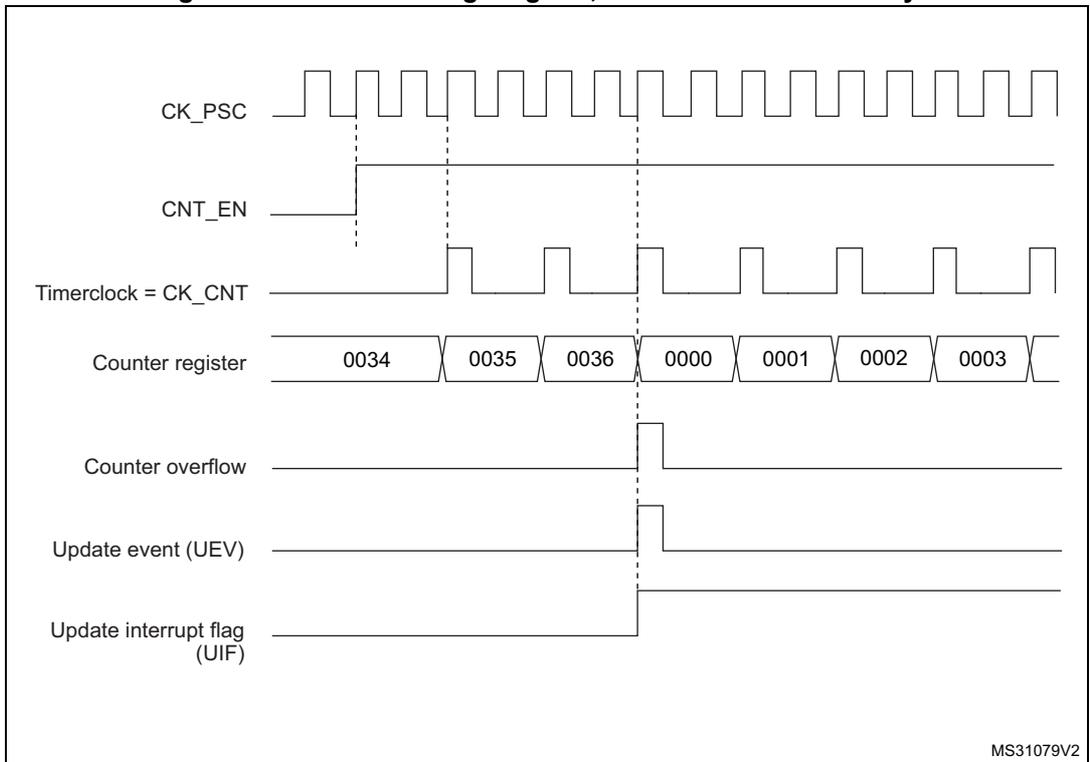

Figure 96. Counter timing diagram, internal clock divided by 2

This timing diagram illustrates the operation of the TIM1 counter when the internal clock is divided by 2. The diagram consists of seven horizontal signal lines. The first line, CK_PSC, shows a periodic square wave. The second line, CNT_EN, is a signal that goes high to enable the counter. The third line, Timerclock = CK_CNT, shows the clock signal for the counter, which is a square wave with a frequency half that of CK_PSC. The fourth line, Counter register, shows the sequence of values: 0034, 0035, 0036, 0000, 0001, 0002, 0003. The fifth line, Counter overflow, is a pulse that goes high when the counter reaches 0036 and returns low at 0000. The sixth line, Update event (UEV), is a pulse that goes high when the counter reaches 0036 and returns low at 0000. The seventh line, Update interrupt flag (UIF), is a signal that goes high when the counter reaches 0036 and returns low at 0000. Vertical dashed lines indicate the timing relationships between the signals.

MS31079V2

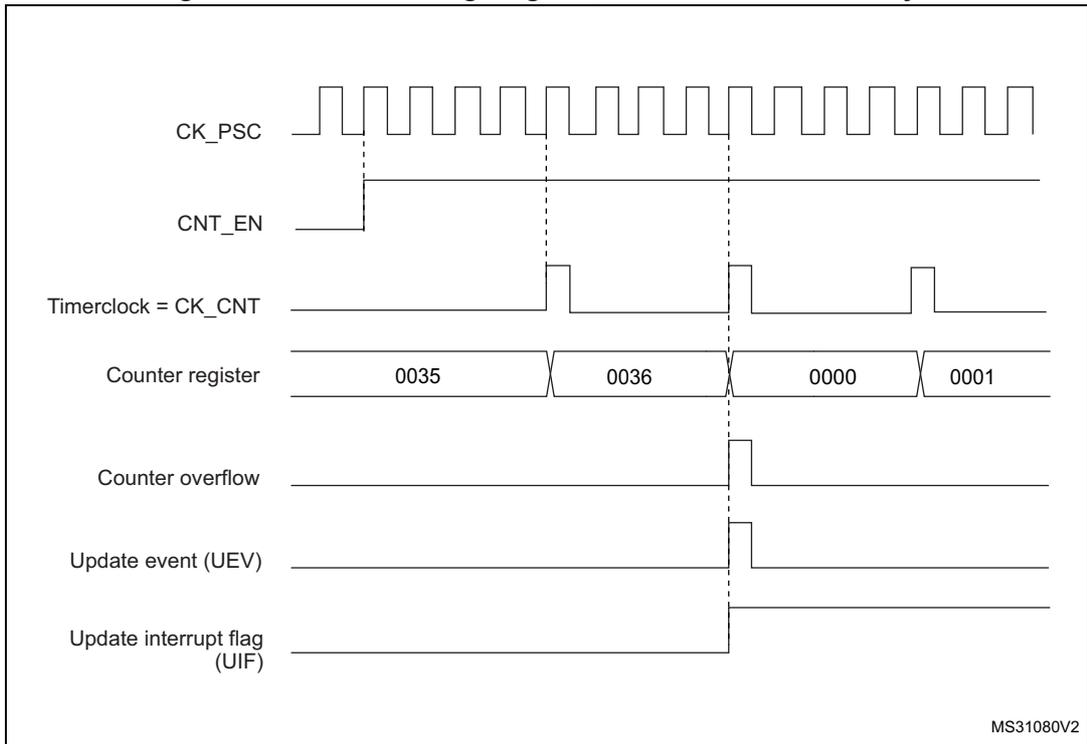

Figure 97. Counter timing diagram, internal clock divided by 4

This timing diagram illustrates the operation of a counter when the internal clock is divided by 4. The top signal, CK_PSC, is a periodic square wave. Below it, CNT_EN is shown as a high-level signal. The Timerclock = CK_CNT signal is a series of pulses. The Counter register shows a sequence of values: 0035, 0036, 0000, and 0001. A Counter overflow pulse occurs when the counter transitions from 0036 to 0000. The Update event (UEV) is a pulse that coincides with the counter overflow. The Update interrupt flag (UIF) is shown as a high-level signal that goes high at the time of the overflow and remains high until it is cleared.

MS31080V2

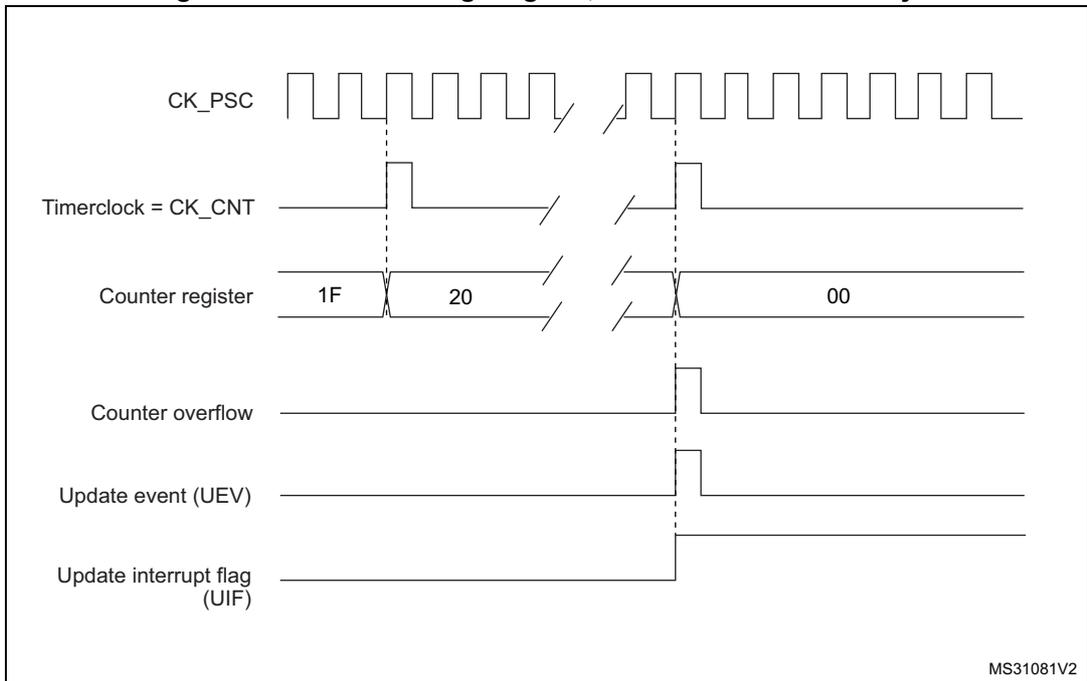

Figure 98. Counter timing diagram, internal clock divided by N

This timing diagram illustrates the operation of a counter when the internal clock is divided by N. The top signal, CK_PSC, is a periodic square wave. Below it, the Timerclock = CK_CNT signal is shown as a series of pulses. The Counter register shows a sequence of values: 1F, 20, and 00. A Counter overflow pulse occurs when the counter transitions from 20 to 00. The Update event (UEV) is a pulse that coincides with the counter overflow. The Update interrupt flag (UIF) is shown as a high-level signal that goes high at the time of the overflow and remains high until it is cleared.

MS31081V2

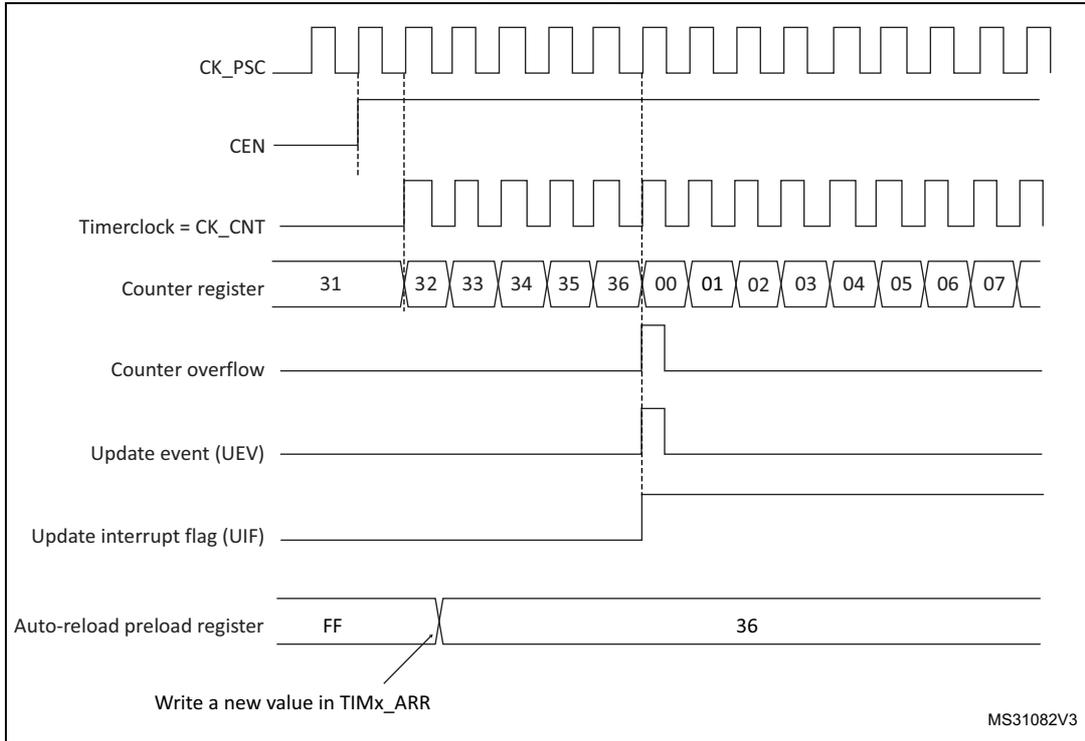

Figure 99. Counter timing diagram, update event when ARPE=0 (TIMx_ARR not preloaded)

This timing diagram illustrates the operation of an advanced-control timer when the ARPE bit is 0. The diagram shows the following signals over time:

- CK_PSC: A periodic clock signal.

- CEN: Counter Enable signal, which is active low. It is shown going high (disabling the counter).

- Timerclock = CK_CNT: The counter clock, which is a divided version of CK_PSC.

- Counter register: Shows the count values. It starts at 31, increments through 32, 33, 34, 35, and 36. Upon reaching 36, it overflows to 00 and continues incrementing through 01, 02, 03, 04, 05, 06, and 07.

- Counter overflow: A signal that pulses high when the counter reaches its maximum value (36) and resets to 00.

- Update event (UEV): A signal that pulses high when the counter overflows.

- Update interrupt flag (UIF): A signal that goes high in response to the Update event (UEV).

- Auto-reload preload register: Shows the register value starting at FF. An arrow labeled "Write a new value in TIMx_ARR" points to a change in the register value to 36. This value is then loaded into the counter at the next overflow event.

Reference: MS31082V3

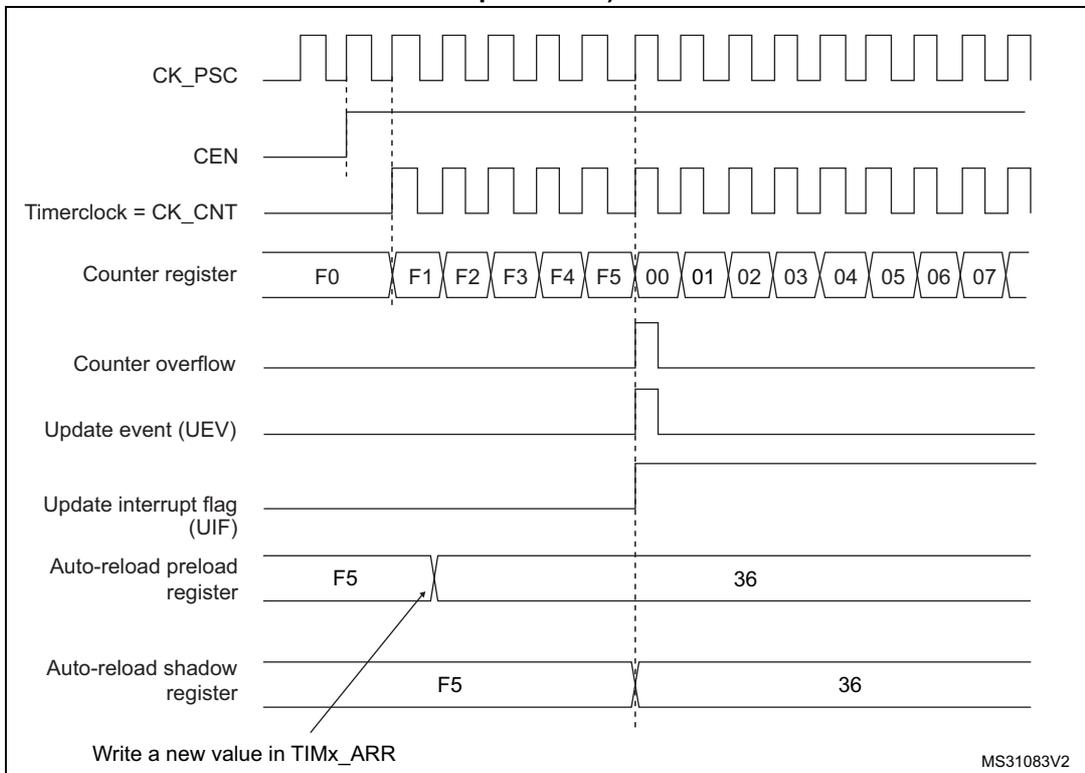

Figure 100. Counter timing diagram, update event when ARPE=1 (TIMx_ARR preloaded)

This timing diagram illustrates the operation of an advanced-control timer when the ARPE bit is 1. The diagram shows the following signals over time:

- CK_PSC: A periodic clock signal.

- CEN: Counter Enable signal, which is active low. It is shown going high (disabling the counter).

- Timerclock = CK_CNT: The counter clock, which is a divided version of CK_PSC.

- Counter register: Shows the count values. It starts at F0, increments through F1, F2, F3, F4, and F5. Upon reaching F5, it overflows to 00 and continues incrementing through 01, 02, 03, 04, 05, 06, and 07.

- Counter overflow: A signal that pulses high when the counter reaches its maximum value (F5) and resets to 00.

- Update event (UEV): A signal that pulses high when the counter overflows.

- Update interrupt flag (UIF): A signal that goes high in response to the Update event (UEV).

- Auto-reload preload register: Shows the register value starting at F5. An arrow labeled "Write a new value in TIMx_ARR" points to a change in the register value to 36. This value is then loaded into the counter at the next overflow event.

- Auto-reload shadow register: This register holds the current reload value. It initially contains F5. At the overflow event, it is updated to the new value 36 from the preload register.

Reference: MS31083V2

Downcounting mode

In downcounting mode, the counter counts from the auto-reload value (content of the TIMx_ARR register) down to 0, then restarts from the auto-reload value and generates a counter underflow event.

If the repetition counter is used, the update event (UEV) is generated after downcounting is repeated for the number of times programmed in the repetition counter register (TIMx_RCR) + 1. Else the update event is generated at each counter underflow.

Setting the UG bit in the TIMx_EGR register (by software or by using the slave mode controller) also generates an update event.

The UEV update event can be disabled by software by setting the UDIS bit in TIMx_CR1 register. This is to avoid updating the shadow registers while writing new values in the preload registers. Then no update event occurs until UDIS bit has been written to 0. However, the counter restarts from the current auto-reload value, whereas the counter of the prescaler restarts from 0 (but the prescale rate doesn't change).

In addition, if the URS bit (update request selection) in TIMx_CR1 register is set, setting the UG bit generates an update event UEV but without setting the UIF flag (thus no interrupt or DMA request is sent). This is to avoid generating both update and capture interrupts when clearing the counter on the capture event.

When an update event occurs, all the registers are updated and the update flag (UIF bit in TIMx_SR register) is set (depending on the URS bit):

- • The repetition counter is reloaded with the content of TIMx_RCR register.

- • The buffer of the prescaler is reloaded with the preload value (content of the TIMx_PSC register).

- • The auto-reload active register is updated with the preload value (content of the TIMx_ARR register). Note that the auto-reload is updated before the counter is reloaded, so that the next period is the expected one.

The following figures show some examples of the counter behavior for different clock frequencies when TIMx_ARR=0x36.

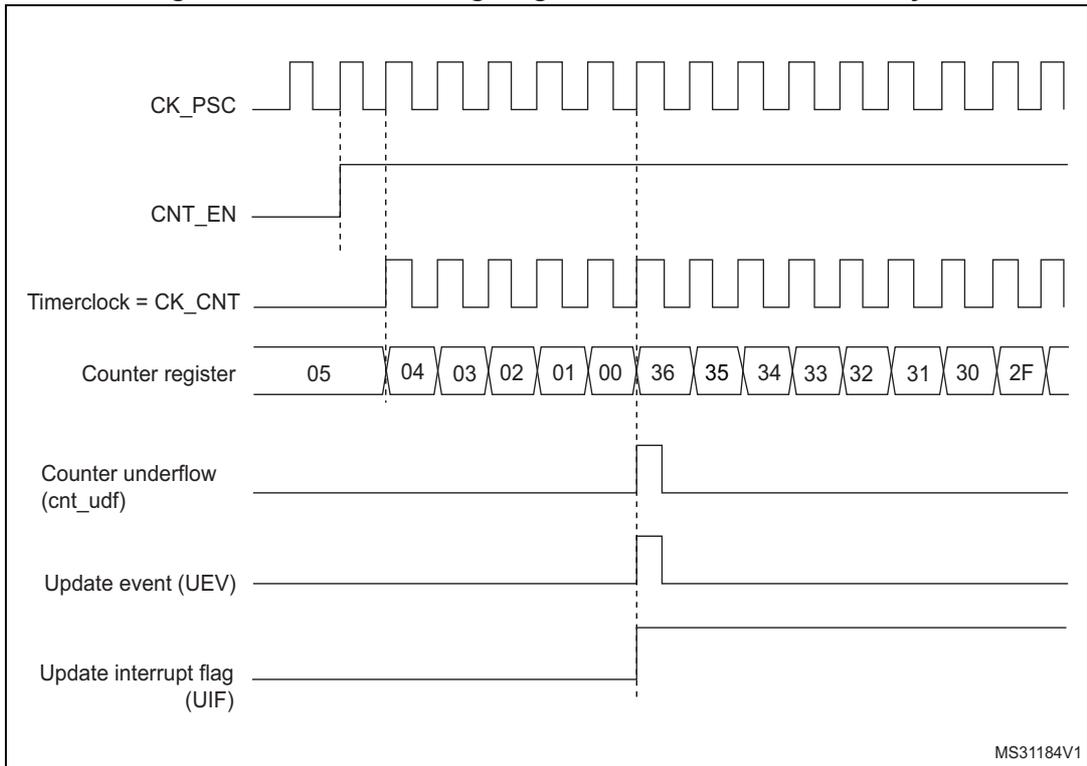

Figure 101. Counter timing diagram, internal clock divided by 1

This timing diagram illustrates the operation of the TIM1 counter when the internal clock is divided by 1. The diagram consists of seven horizontal signal lines. The top line, CK_PSC, shows a periodic square wave. The second line, CNT_EN, is a signal that goes high to enable the counter. The third line, Timerclock = CK_CNT, shows the clock signal for the counter, which is a square wave with a frequency twice that of CK_PSC. The fourth line, Counter register, displays a sequence of hexadecimal values: 05, 04, 03, 02, 01, 00, 36, 35, 34, 33, 32, 31, 30, 2F. The fifth line, Counter underflow (cnt_udf), is a signal that goes high when the counter register reaches 00 and then returns low. The sixth line, Update event (UEV), is a signal that goes high when the counter register reaches 00 and then returns low. The bottom line, Update interrupt flag (UIF), is a signal that goes high when the counter register reaches 00 and remains high until it is manually cleared. Vertical dashed lines indicate the timing relationships between the signals. The identifier MS31184V1 is located in the bottom right corner.

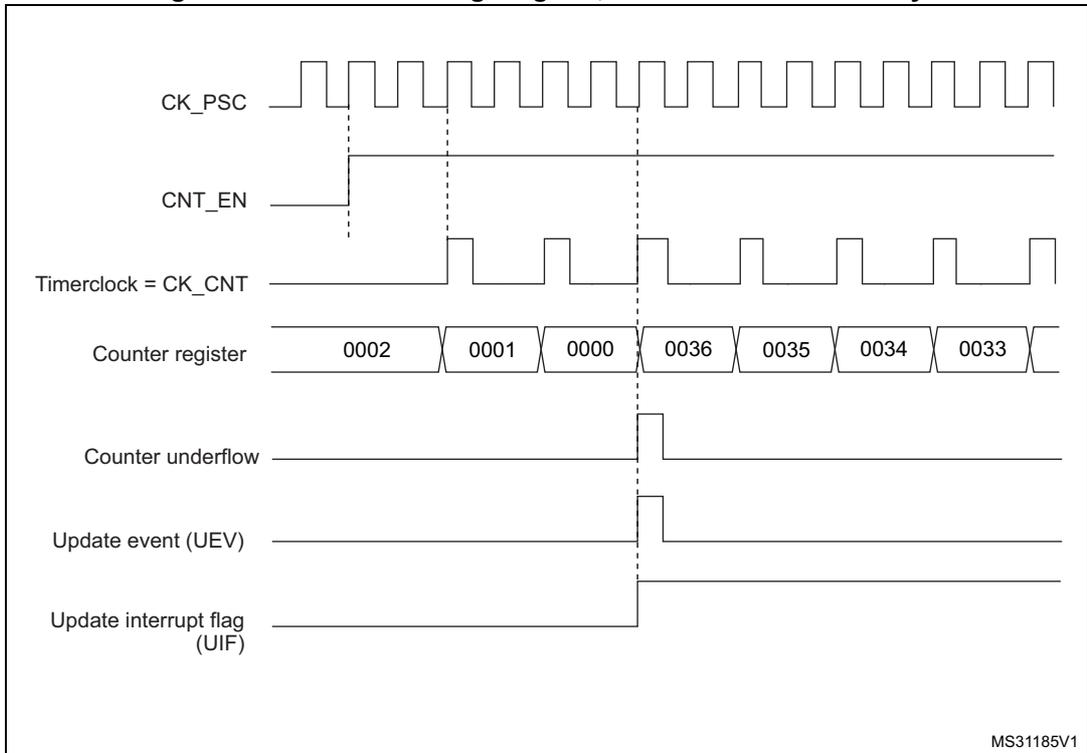

Figure 102. Counter timing diagram, internal clock divided by 2

This timing diagram illustrates the operation of the TIM1 counter when the internal clock is divided by 2. The diagram consists of seven horizontal signal lines. The top line, CK_PSC, shows a periodic square wave. The second line, CNT_EN, is a signal that goes high to enable the counter. The third line, Timerclock = CK_CNT, shows the clock signal for the counter, which is a square wave with a frequency half that of CK_PSC. The fourth line, Counter register, displays a sequence of hexadecimal values: 0002, 0001, 0000, 0036, 0035, 0034, 0033. The fifth line, Counter underflow, is a signal that goes high when the counter register reaches 0000 and then returns low. The sixth line, Update event (UEV), is a signal that goes high when the counter register reaches 0000 and then returns low. The bottom line, Update interrupt flag (UIF), is a signal that goes high when the counter register reaches 0000 and remains high until it is manually cleared. Vertical dashed lines indicate the timing relationships between the signals. The identifier MS31185V1 is located in the bottom right corner.

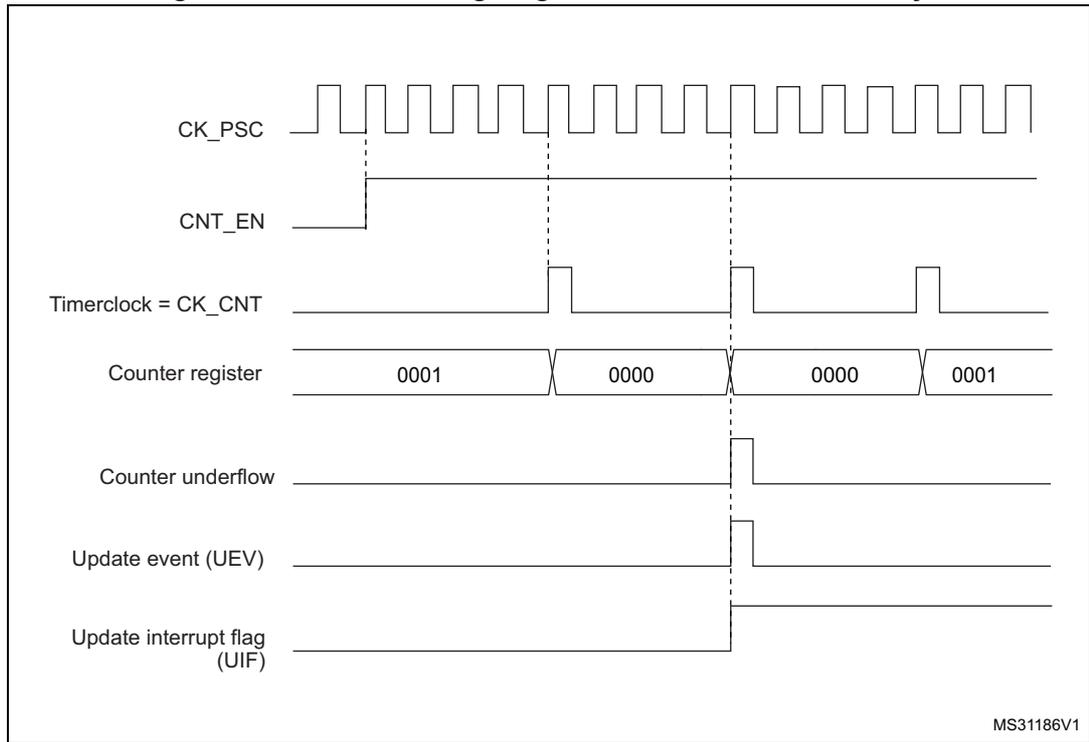

Figure 103. Counter timing diagram, internal clock divided by 4

The diagram shows the following signals over time:

- CK_PSC : A periodic square wave clock signal.

- CNT_EN : Counter Enable signal, held high throughout the diagram.

- Timerclock = CK_CNT : The internal counter clock, which is CK_PSC divided by 4. It is a square wave with a frequency one-quarter that of CK_PSC.

- Counter register : Shows the count values. It starts at 0001, then becomes 0000 (underflow), stays at 0000 for one clock cycle, and then becomes 0001.

- Counter underflow : A short pulse that goes high when the counter register reaches 0000.

- Update event (UEV) : A short pulse that goes high when the counter register reaches 0000, coinciding with the underflow.

- Update interrupt flag (UIF) : A signal that goes high when the counter register reaches 0000 and remains high until it is manually cleared.

MS31186V1

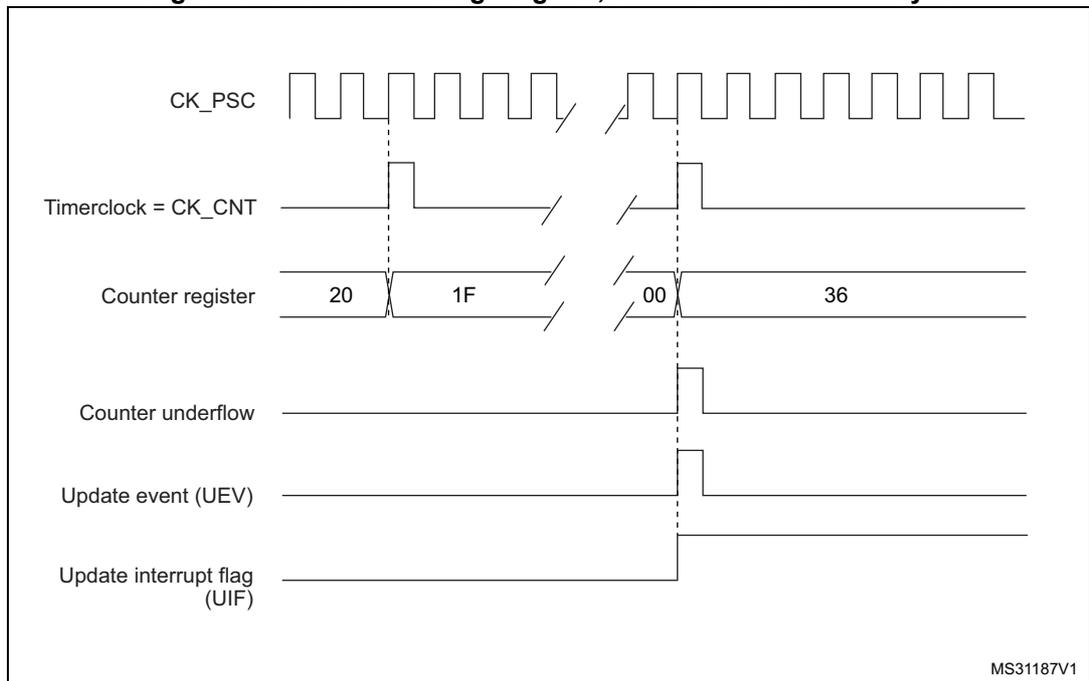

Figure 104. Counter timing diagram, internal clock divided by N

The diagram shows the following signals over time:

- CK_PSC : A periodic square wave clock signal.

- Timerclock = CK_CNT : The internal counter clock, which is CK_PSC divided by N. The diagram shows a break in the signal.

- Counter register : Shows the count values. It starts at 20 (hex), then becomes 1F (hex), then 00 (hex) (underflow), and then becomes 36 (hex).

- Counter underflow : A short pulse that goes high when the counter register reaches 00.

- Update event (UEV) : A short pulse that goes high when the counter register reaches 00, coinciding with the underflow.

- Update interrupt flag (UIF) : A signal that goes high when the counter register reaches 00 and remains high until it is manually cleared.

MS31187V1

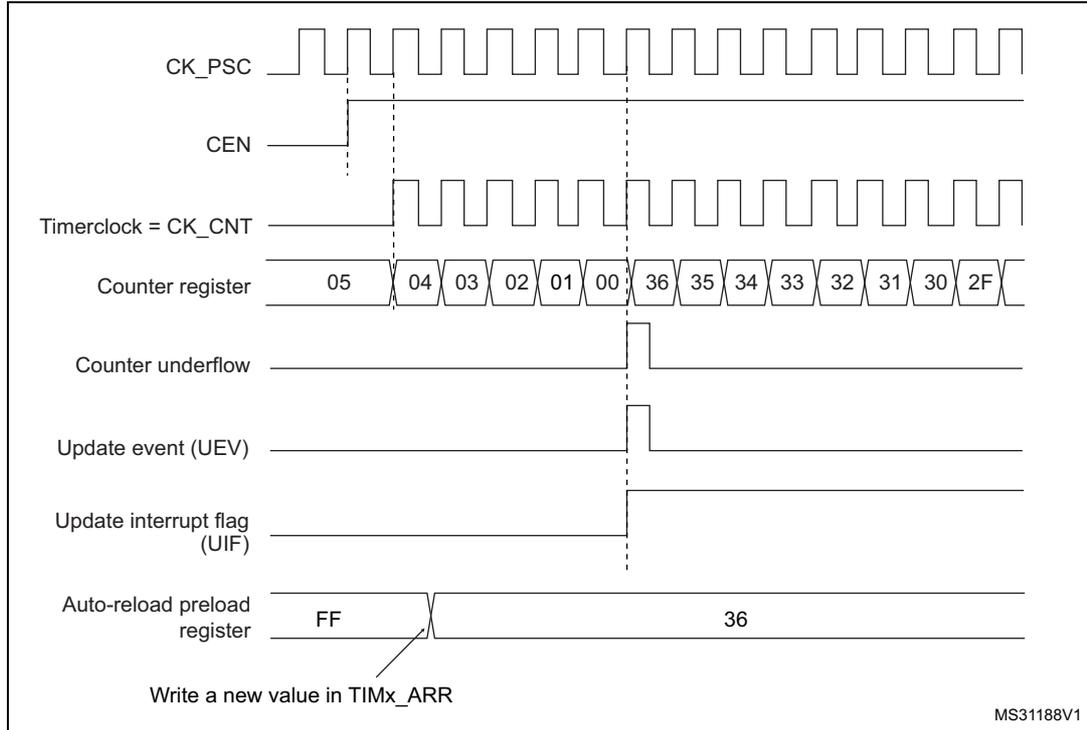

The diagram illustrates the timing of an update event (UEV) for a counter. The top signal, CK_PSC, is a periodic clock. The CEN signal is a horizontal line indicating the counter is enabled. The Timerclock = CK_CNT signal is a periodic clock derived from CK_PSC. The Counter register shows a sequence of values: 05, 04, 03, 02, 01, 00, 36, 35, 34, 33, 32, 31, 30, 2F. The Counter underflow signal is a horizontal line that goes high when the counter reaches 00. The Update event (UEV) signal is a horizontal line that goes high when the counter reaches 00. The Update interrupt flag (UIF) signal is a horizontal line that goes high when the counter reaches 00. The Auto-reload preload register shows a value of FF, which is then updated to 36. An arrow points to the register with the text 'Write a new value in TIMx_ARR'. The diagram is labeled MS31188V1 in the bottom right corner.

Center-aligned mode (up/down counting)

In center-aligned mode, the counter counts from 0 to the auto-reload value (content of the TIMx_ARR register) – 1, generates a counter overflow event, then counts from the auto-reload value down to 1 and generates a counter underflow event. Then it restarts counting from 0.

Center-aligned mode is active when the CMS bits in TIMx_CR1 register are not equal to '00'. The Output compare interrupt flag of channels configured in output is set when: the counter counts down (Center aligned mode 1, CMS = "01"), the counter counts up (Center aligned mode 2, CMS = "10") the counter counts up and down (Center aligned mode 3, CMS = "11").

In this mode, the DIR direction bit in the TIMx_CR1 register cannot be written. It is updated by hardware and gives the current direction of the counter.

The update event can be generated at each counter overflow and at each counter underflow or by setting the UG bit in the TIMx_EGR register (by software or by using the slave mode controller) also generates an update event. In this case, the counter restarts counting from 0, as well as the counter of the prescaler.

The UEV update event can be disabled by software by setting the UDIS bit in the TIMx_CR1 register. This is to avoid updating the shadow registers while writing new values in the preload registers. Then no update event occurs until UDIS bit has been written to 0. However, the counter continues counting up and down, based on the current auto-reload value.

In addition, if the URS bit (update request selection) in TIMx_CR1 register is set, setting the UG bit generates an UEV update event but without setting the UIF flag (thus no interrupt or

DMA request is sent). This is to avoid generating both update and capture interrupts when clearing the counter on the capture event.

When an update event occurs, all the registers are updated and the update flag (UIF bit in TIMx_SR register) is set (depending on the URS bit):

- • The repetition counter is reloaded with the content of TIMx_RCR register

- • The buffer of the prescaler is reloaded with the preload value (content of the TIMx_PSC register)

- • The auto-reload active register is updated with the preload value (content of the TIMx_ARR register). Note that if the update source is a counter overflow, the auto-reload is updated before the counter is reloaded, so that the next period is the expected one (the counter is loaded with the new value).

The following figures show some examples of the counter behavior for different clock frequencies.

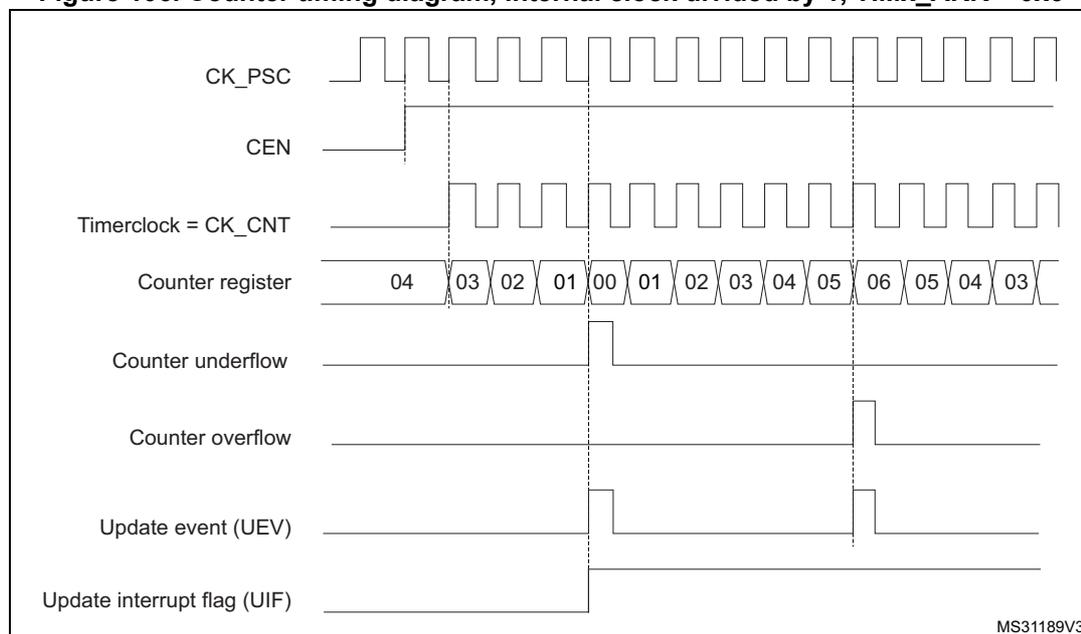

Figure 106. Counter timing diagram, internal clock divided by 1, TIMx_ARR = 0x6

The timing diagram illustrates the relationship between several signals over time. The top signal, CK_PSC, is a periodic square wave. Below it, the CEN (Counter Enable) signal is shown as a horizontal line that goes high at the start. The third signal, Timerclock = CK_CNT, is a square wave that is active only when CEN is high. The fourth signal, Counter register, shows a sequence of hexadecimal values: 04, 03, 02, 01, 00, 01, 02, 03, 04, 05, 06, 05, 04, 03. This sequence indicates a center-aligned mode where the counter counts down from 04 to 00, then up to 06, and then back down. The fifth signal, Counter underflow, is a pulse that goes high when the counter reaches 00. The sixth signal, Counter overflow, is a pulse that goes high when the counter reaches 06. The seventh signal, Update event (UEV), is a pulse that goes high when the counter reaches 00. The bottom signal, Update interrupt flag (UIF), is a pulse that goes high when the counter reaches 00. The diagram is labeled MS31189V3 in the bottom right corner.

- 1. Here, center-aligned mode 1 is used (for more details refer to Section 17.4: TIM1 registers ).

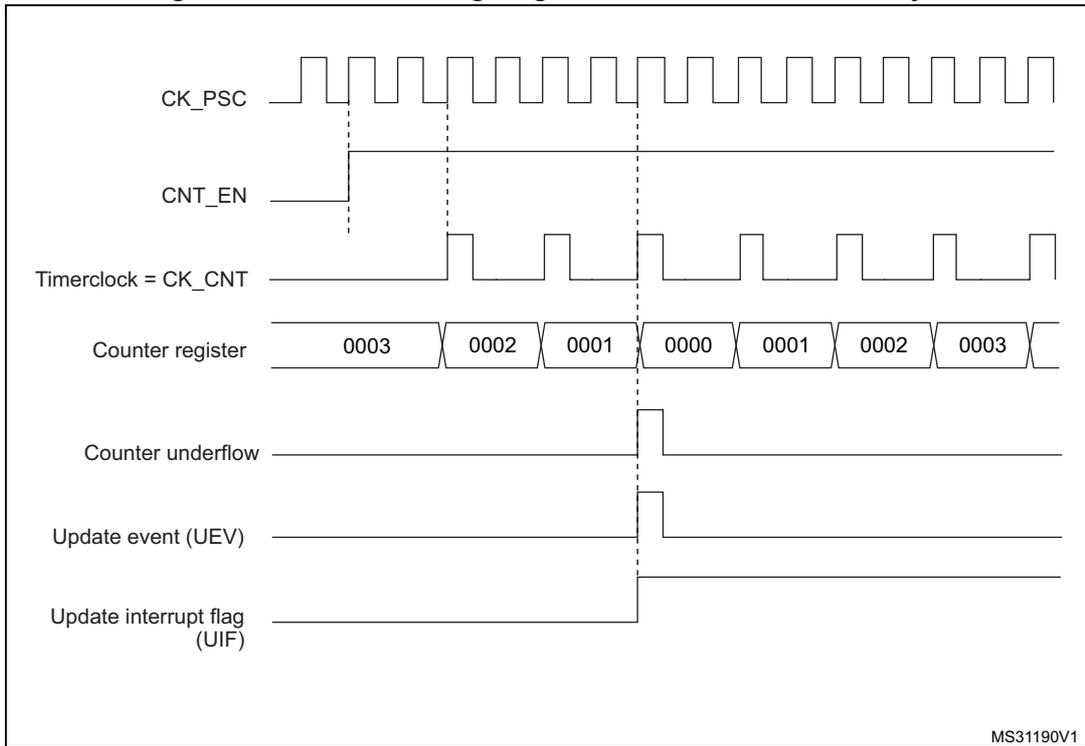

Figure 107. Counter timing diagram, internal clock divided by 2

This timing diagram illustrates the operation of an advanced-control timer (TIM1) with the internal clock divided by 2. The diagram shows the following signals and states over time:

- CK_PSC : Prescaler clock signal, shown as a continuous square wave.

- CNT_EN : Counter enable signal, which goes high to start the counter.

- Timerclock = CK_CNT : The clock signal for the counter, which is the CK_PSC signal divided by 2.

- Counter register : Shows the counter values decreasing from 0003 to 0002, 0001, and 0000, then rolling over back to 0001, 0002, and 0003.

- Counter underflow : A pulse that occurs when the counter reaches 0000 and rolls over to 0001.

- Update event (UEV) : A pulse that occurs at the same time as the counter underflow.

- Update interrupt flag (UIF) : A signal that goes high when an update event occurs.

MS31190V1

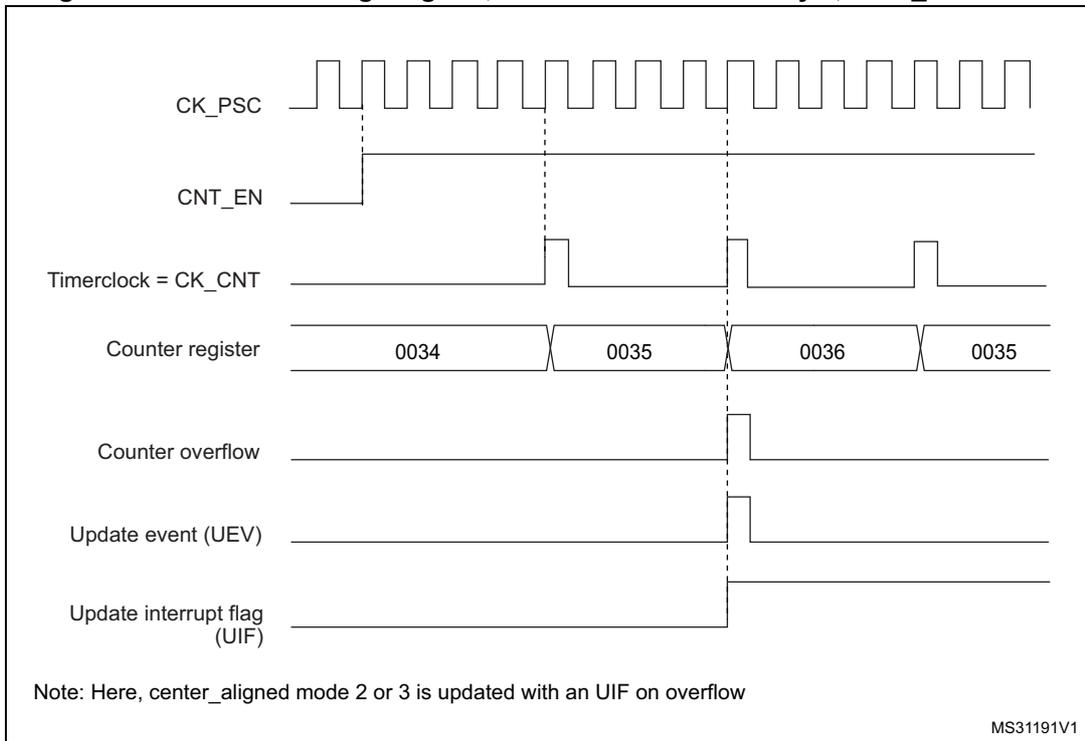

Figure 108. Counter timing diagram, internal clock divided by 4, TIMx_ARR=0x36

This timing diagram illustrates the operation of an advanced-control timer (TIM1) with the internal clock divided by 4 and the auto-reload register (TIMx_ARR) set to 0x36. The diagram shows the following signals and states over time:

- CK_PSC : Prescaler clock signal, shown as a continuous square wave.

- CNT_EN : Counter enable signal, which goes high to start the counter.

- Timerclock = CK_CNT : The clock signal for the counter, which is the CK_PSC signal divided by 4.

- Counter register : Shows the counter values increasing from 0034 to 0035, 0036, and then rolling over back to 0035.

- Counter overflow : A pulse that occurs when the counter reaches 0036 and rolls over to 0035.

- Update event (UEV) : A pulse that occurs at the same time as the counter overflow.

- Update interrupt flag (UIF) : A signal that goes high when an update event occurs.

Note: Here, center_aligned mode 2 or 3 is updated with an UIF on overflow

MS31191V1

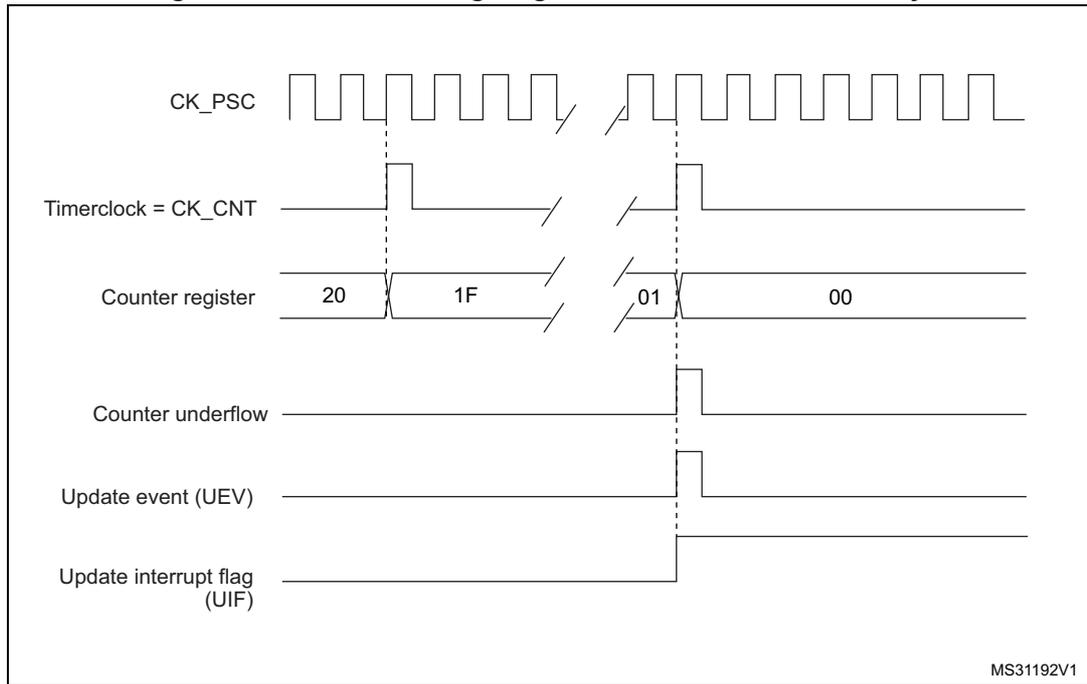

Figure 109. Counter timing diagram, internal clock divided by N

This timing diagram illustrates the operation of a counter with an internal clock divided by N. The top signal, CK_PSC, is a periodic square wave. Below it, the Timerclock = CK_CNT is shown as a series of pulses, with a break in the middle. The Counter register is shown with values 20, 1F, 01, and 00. The Counter underflow signal is a pulse that goes high when the counter reaches 00. The Update event (UEV) and Update interrupt flag (UIF) are also shown as pulses that go high at the counter underflow. The diagram is labeled MS31192V1 in the bottom right corner.

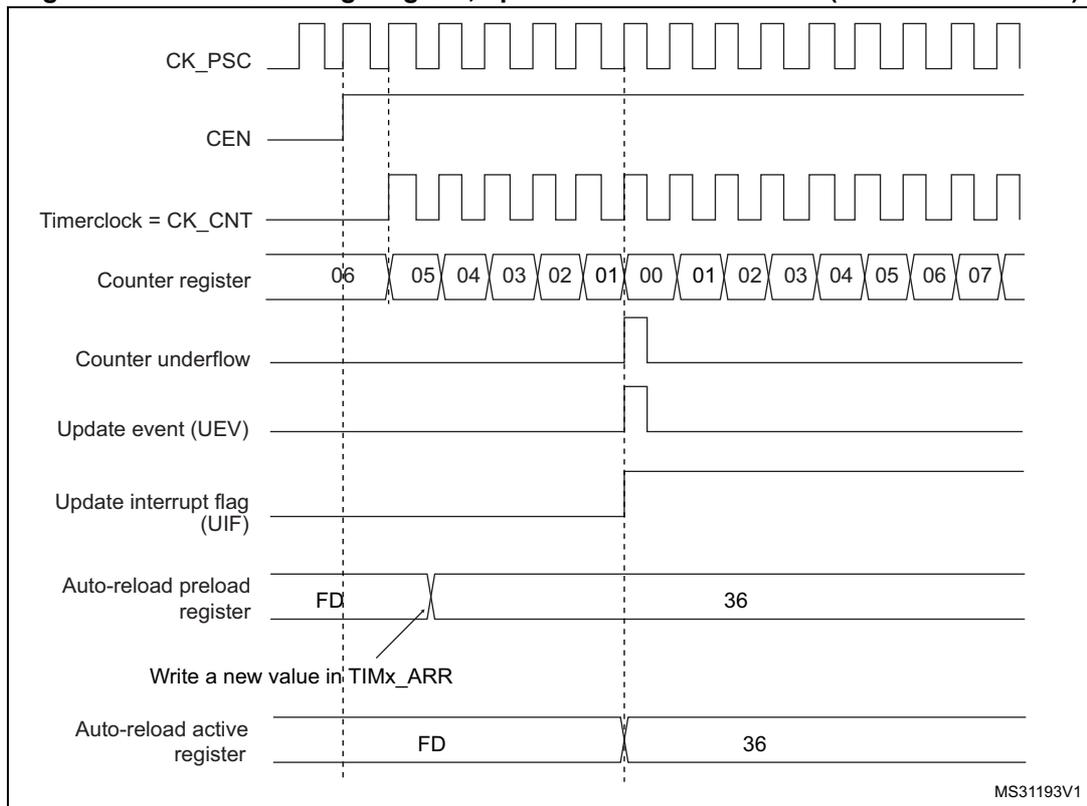

Figure 110. Counter timing diagram, update event with ARPE=1 (counter underflow)

This timing diagram shows the counter operation with ARPE=1. The signals include CK_PSC, CEN (Counter Enable), Timerclock = CK_CNT, Counter register (counting from 06 down to 00, then 01 up to 07), Counter underflow, Update event (UEV), Update interrupt flag (UIF), Auto-reload preload register (values FD and 36), Write a new value in TIMx_ARR, and Auto-reload active register (values FD and 36). The diagram is labeled MS31193V1 in the bottom right corner.

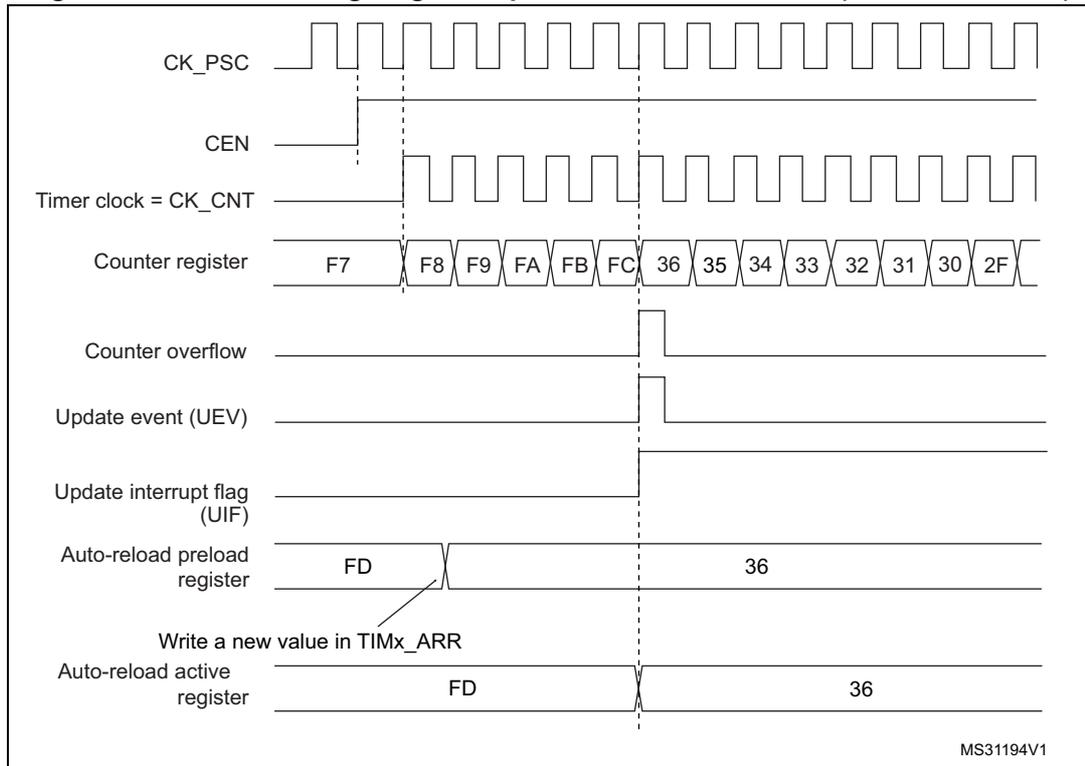

Figure 111. Counter timing diagram, Update event with ARPE=1 (counter overflow)

The timing diagram illustrates the operation of an advanced-control timer (TIM1) in counter mode with ARPE=1. The signals shown are:

- CK_PSC : Prescaler clock signal, a periodic square wave.

- CEN : Counter enable signal, which is high when the counter is active.

- Timer clock = CK_CNT : The clock signal for the counter, derived from CK_PSC.

- Counter register : A sequence of values: F7, F8, F9, FA, FB, FC, 36, 35, 34, 33, 32, 31, 30, 2F. The counter is counting down from F7 to 2F.

- Counter overflow : A signal that goes high when the counter overflows from FC to 36.

- Update event (UEV) : A signal that goes high when the counter overflows from FC to 36.

- Update interrupt flag (UIF) : A signal that goes high when the counter overflows from FC to 36.

- Auto-reload preload register : A register that contains the value FD. An arrow indicates that a new value (FD) is being written to this register.

- Auto-reload active register : A register that contains the value 36. An arrow indicates that the value 36 is being updated to this register.

MS31194V1

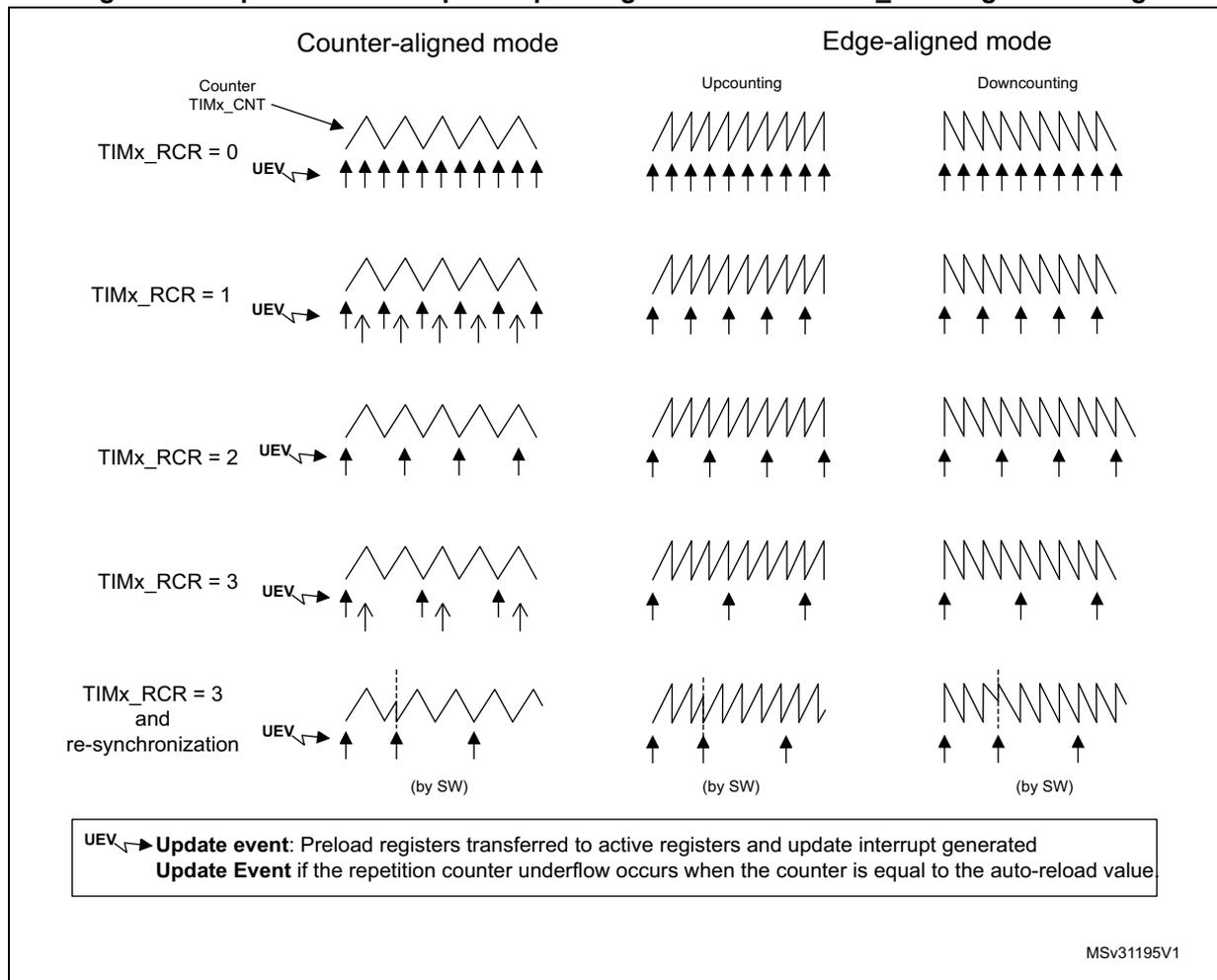

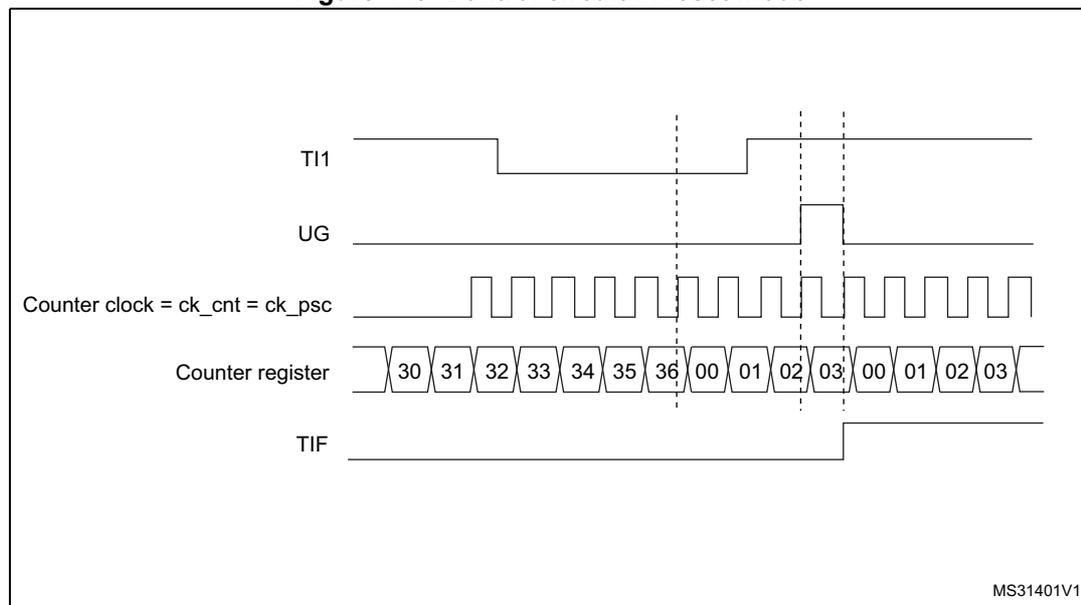

17.3.3 Repetition counter

Section 17.3.1: Time-base unit describes how the update event (UEV) is generated with respect to the counter overflows/underflows. It is actually generated only when the repetition counter has reached zero. This can be useful when generating PWM signals.

This means that data are transferred from the preload registers to the shadow registers (TIMx_ARR auto-reload register, TIMx_PSC prescaler register, but also TIMx_CCRx capture/compare registers in compare mode) every N+1 counter overflows or underflows, where N is the value in the TIMx_RCR repetition counter register.

The repetition counter is decremented:

- • At each counter overflow in upcounting mode,

- • At each counter underflow in downcounting mode,

- • At each counter overflow and at each counter underflow in center-aligned mode.

- Although this limits the maximum number of repetition to 32768 PWM cycles, it makes it possible to update the duty cycle twice per PWM period. When refreshing compare registers only once per PWM period in center-aligned mode, maximum resolution is \( 2 \times T_{ck} \) , due to the symmetry of the pattern.

The repetition counter is an auto-reload type; the repetition rate is maintained as defined by the TIMx_RCR register value (refer to Figure 112 ). When the update event is generated by software (by setting the UG bit in TIMx_EGR register) or by hardware through the slave mode controller, it occurs immediately whatever the value of the repetition counter is and the repetition counter is reloaded with the content of the TIMx_RCR register.

In Center aligned mode, for odd values of RCR, the update event occurs either on the overflow or on the underflow depending on when the RCR register was written and when the counter was launched: if the RCR was written before launching the counter, the UEV occurs on the underflow. If the RCR was written after launching the counter, the UEV occurs on the overflow.

For example, for RCR = 3, the UEV is generated each 4th overflow or underflow event depending on when the RCR was written.

Figure 112. Update rate examples depending on mode and TIMx_RCR register settings

| Counter-aligned mode | Edge-aligned mode | ||

|---|---|---|---|

| Upcounting | Downcounting | ||

| Counter TIMx_CNT | |||

| TIMx_RCR = 0 | UEV at every overflow | UEV at every overflow | UEV at every underflow |

| TIMx_RCR = 1 | UEV every 2nd overflow | UEV every 2nd overflow | UEV every 2nd underflow |

| TIMx_RCR = 2 | UEV every 3rd overflow | UEV every 3rd overflow | UEV every 3rd underflow |

| TIMx_RCR = 3 | UEV every 4th overflow (first at underflow) | UEV every 4th overflow | UEV every 4th underflow |

| TIMx_RCR = 3 and re-synchronization | UEV every 4th overflow after (by SW) | UEV every 4th overflow after (by SW) | UEV every 4th underflow after (by SW) |

UEV →

Update event:

Preload registers transferred to active registers and update interrupt generated

Update Event

if the repetition counter underflow occurs when the counter is equal to the auto-reload value.

MSv31195V1

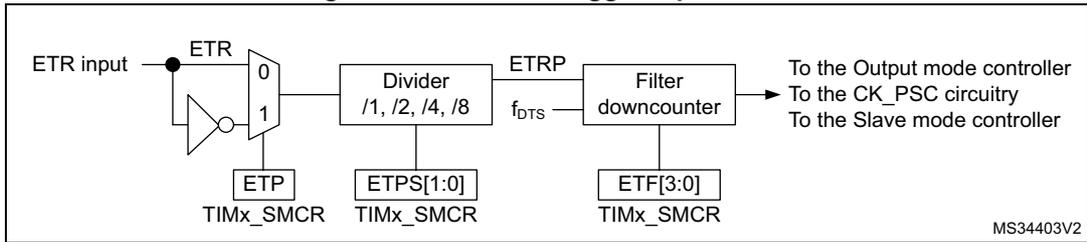

17.3.4 External trigger input

The timer features an external trigger input ETR. It can be used as:

- • external clock (external clock mode 2, see Section 17.3.5 )

- • trigger for the slave mode (see Section 17.3.25 )

- • PWM reset input for cycle-by-cycle current regulation (see Section 17.3.7 )

Figure 113 below describes the ETR input conditioning. The input polarity is defined with the ETP bit in TIMxSMCR register. The trigger can be prescaled with the divider programmed by the ETPS[1:0] bitfield and digitally filtered with the ETF[3:0] bitfield.

Figure 113. External trigger input block

The diagram illustrates the signal path for the External Trigger (ETR) input. It begins with the 'ETR input' entering a polarity selector (represented by a switch with '0' and '1' positions and an inverter). This selector is controlled by the 'ETP' bit in the 'TIMx_SMCR' register. The output of the selector passes through a 'Divider' block with options '/1, /2, /4, /8', which is controlled by the 'ETPS[1:0]' bitfield in the 'TIMx_SMCR' register. The output of the divider is labeled 'ETRP'. This signal then enters a 'Filter downcounter' block, which is controlled by the 'ETF[3:0]' bitfield in the 'TIMx_SMCR' register. A 'f_bts' input is also shown for the filter. The final output of the filter downcounter is directed to three destinations: 'To the Output mode controller', 'To the CK_PSC circuitry', and 'To the Slave mode controller'. The diagram is labeled 'MS34403V2' in the bottom right corner.

17.3.5 Clock selection

The counter clock can be provided by the following clock sources:

- • Internal clock (CK_INT)

- • External clock mode1: external input pin

- • External clock mode2: external trigger input ETR

- • Encoder mode

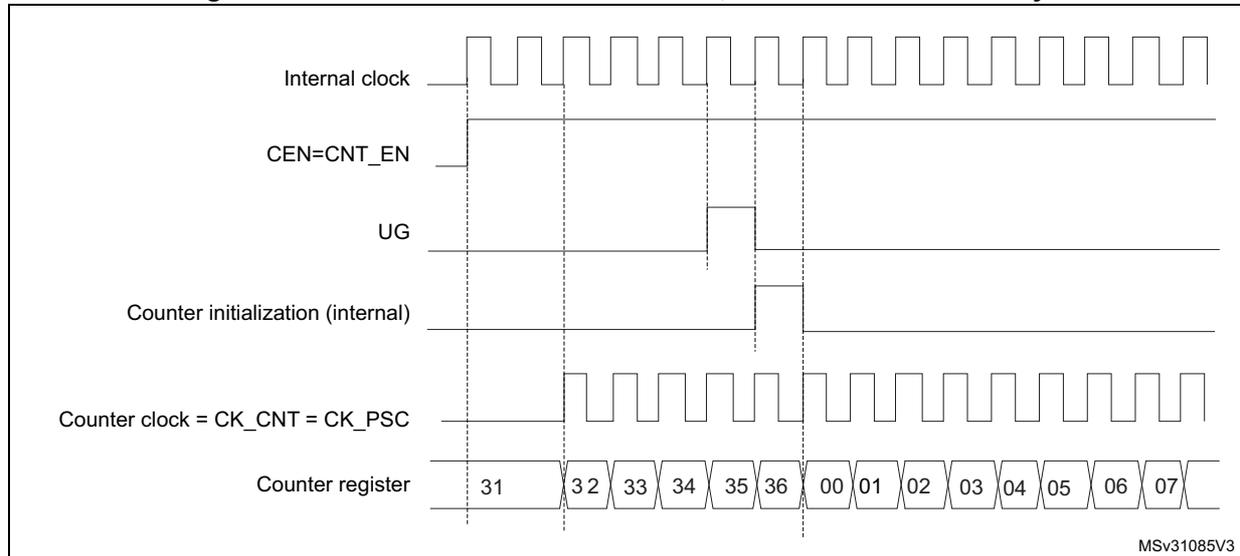

Internal clock source (CK_INT)

If the slave mode controller is disabled (SMS=000), then the CEN, DIR (in the TIMx_CR1 register) and UG bits (in the TIMx_EGR register) are actual control bits and can be changed only by software (except UG which remains cleared automatically). As soon as the CEN bit is written to 1, the prescaler is clocked by the internal clock CK_INT.

Figure 114 shows the behavior of the control circuit and the upcounter in normal mode, without prescaler.

Figure 114. Control circuit in normal mode, internal clock divided by 1

The timing diagram illustrates the relationship between several signals over time. The top signal, 'Internal clock', is a continuous square wave. Below it, 'CEN=CNT_EN' is a horizontal line that transitions from low to high at a certain point. Following this transition, the 'UG' signal shows a short pulse. Below 'UG', the 'Counter initialization (internal)' signal also shows a pulse. The 'Counter clock = CK_CNT = CK_PSC' signal is initially low and then becomes a square wave starting at the same time as the CEN signal goes high. The bottom signal, 'Counter register', shows a sequence of values: 31, 32, 33, 34, 35, 36, 00, 01, 02, 03, 04, 05, 06, 07. These values change at the rising edges of the counter clock. Vertical dashed lines indicate the timing relationships between the signals.

MSv31085V3

External clock source mode 1

This mode is selected when SMS=111 in the TIMx_SMCR register. The counter can count at each rising or falling edge on a selected input.

Figure 115. TI2 external clock connection example

![Figure 115. TI2 external clock connection example. This block diagram shows the internal logic for using the TI2 input as an external clock source. The TI2 pin is connected to a 'Filter' block, which is controlled by the ICF[3:0] bits in the TIMx_CCMR1 register. The output of the filter goes to an 'Edge detector' block. The edge detector produces two signals: 'TI2F_Rising' and 'TI2F_Falling'. These signals are inputs to a multiplexer controlled by the CC2P bit in the TIMx_CCER register. The output of this multiplexer is connected to another multiplexer that selects the trigger source (TRGI). This second multiplexer has inputs for ITRx (0xx), TI1_ED (100), TI1FP1 (101), TI2FP2 (110), and ETRF (111). The TRGI signal is then connected to a third multiplexer that selects the clock mode: 'Encoder mode', 'External clock mode 1', 'External clock mode 2', or 'Internal clock mode (internal clock)'. This third multiplexer is controlled by the ECE and SMS[2:0] bits in the TIMx_SMCR register. The final output is the CK_PSC signal. The TIMx_SMCR register also contains the TS[2:0] bits, which are used to select the trigger source for the counter.](/RM0366-STM32F301x6-8-318x8/aa2a48fc9f812c57f953d4510e732212_img.jpg)

For example, to configure the upcounter to count in response to a rising edge on the TI2 input, use the following procedure:

- 1. Configure channel 2 to detect rising edges on the TI2 input by writing CC2S = '01' in the TIMx_CCMR1 register.

- 2. Configure the input filter duration by writing the IC2F[3:0] bits in the TIMx_CCMR1 register (if no filter is needed, keep IC2F=0000).

- 3. Select rising edge polarity by writing CC2P=0 and CC2NP=0 in the TIMx_CCER register.

- 4. Configure the timer in external clock mode 1 by writing SMS=111 in the TIMx_SMCR register.

- 5. Select TI2 as the trigger input source by writing TS=110 in the TIMx_SMCR register.

- 6. Enable the counter by writing CEN=1 in the TIMx_CR1 register.

Note: The capture prescaler is not used for triggering, so the user does not need to configure it.

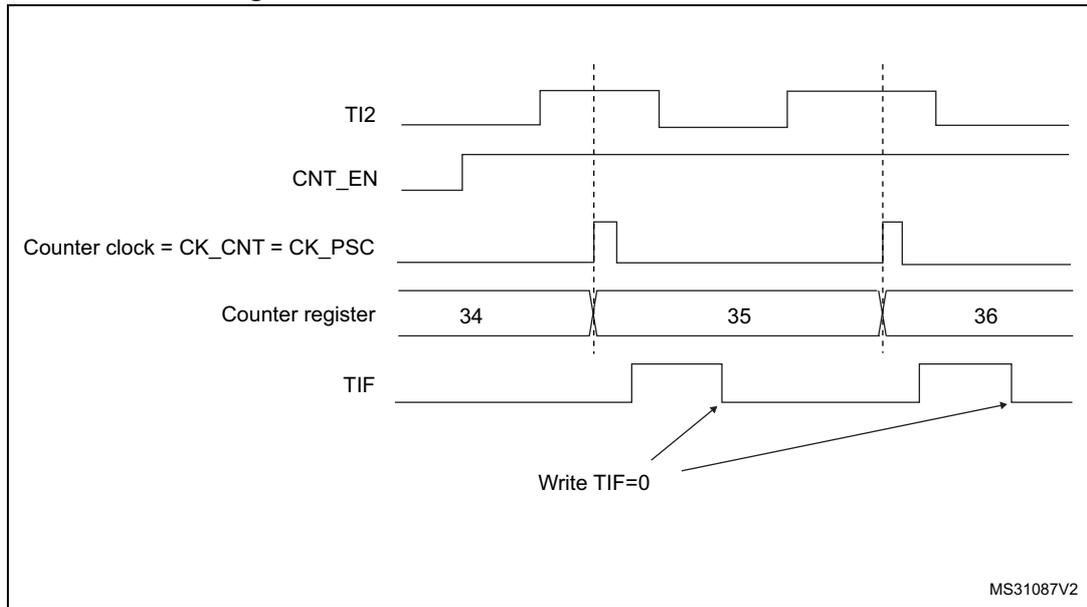

When a rising edge occurs on TI2, the counter counts once and the TIF flag is set.

The delay between the rising edge on TI2 and the actual clock of the counter is due to the resynchronization circuit on TI2 input.

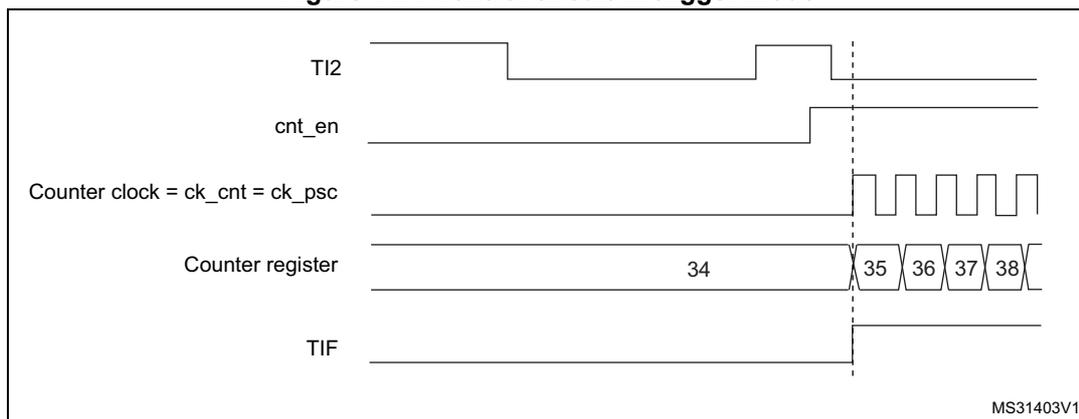

Figure 116. Control circuit in external clock mode 1

The diagram shows the relationship between several signals in external clock mode 1. The TI2 signal is a periodic square wave. The CNT_EN signal is a horizontal line indicating the counter is enabled. The Counter clock (CK_CNT = CK_PSC) is a square wave that toggles on the rising edges of TI2. The Counter register shows values 34, 35, and 36, with increments occurring at the rising edges of the counter clock. The TIF signal is a horizontal line that goes high when the counter overflows (from 36 back to 34) and is cleared by writing TIF=0.

External clock source mode 2

This mode is selected by writing ECE=1 in the TIMx_SMCR register.

The counter can count at each rising or falling edge on the external trigger input ETR.

The Figure 117 gives an overview of the external trigger input block.

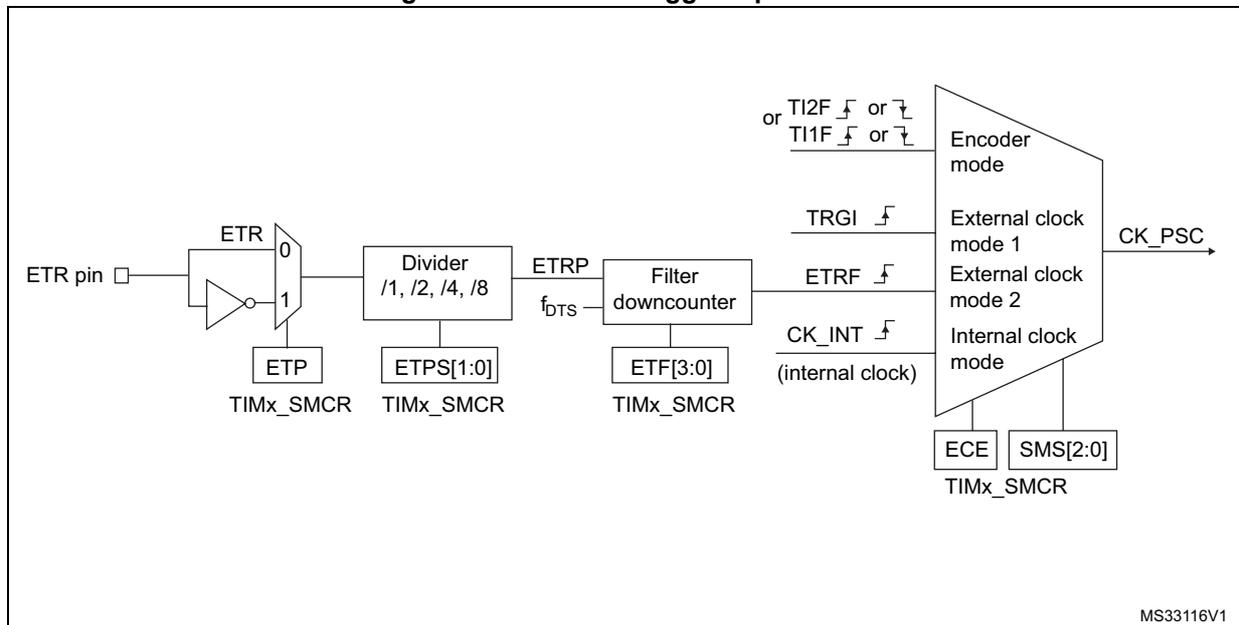

Figure 117. External trigger input block

The diagram illustrates the external trigger input block. The ETR pin is connected to a multiplexer (ETR) with two inputs: 0 (direct) and 1 (inverted). The output of the multiplexer is connected to a divider (/1, /2, /4, /8). The divider's output is ETRP, which is then passed through a filter downcounter. The filter downcounter has a configuration register ETF[3:0]. The output of the filter is ETRF. The ETRF signal is then passed to a clock selection logic block. This block also receives inputs from TI2F, TI1F, TRGI, and CK_INT (internal clock). The output of the selection logic is CK_PSC. The selection logic is controlled by registers ECE and SMS[2:0] in the TIMx_SMCR register. Other control registers shown include ETP, ETPS[1:0], and f_bts.

For example, to configure the upcounter to count each 2 rising edges on ETR, use the following procedure:

- 1. As no filter is needed in this example, write ETF[3:0]=0000 in the TIMx_SMCR register.

- 2. Set the prescaler by writing ETPS[1:0]=01 in the TIMx_SMCR register

- 3. Select rising edge detection on the ETR pin by writing ETP=0 in the TIMx_SMCR register

- 4. Enable external clock mode 2 by writing ECE=1 in the TIMx_SMCR register.

- 5. Enable the counter by writing CEN=1 in the TIMx_CR1 register.

The counter counts once each 2 ETR rising edges.

The delay between the rising edge on ETR and the actual clock of the counter is due to the resynchronization circuit on the ETRP signal. As a consequence, the maximum frequency which can be correctly captured by the counter is at most 1/4 of TIMxCLK frequency. When the ETRP signal is faster, the user should apply a division of the external signal by proper ETPS prescaler setting.

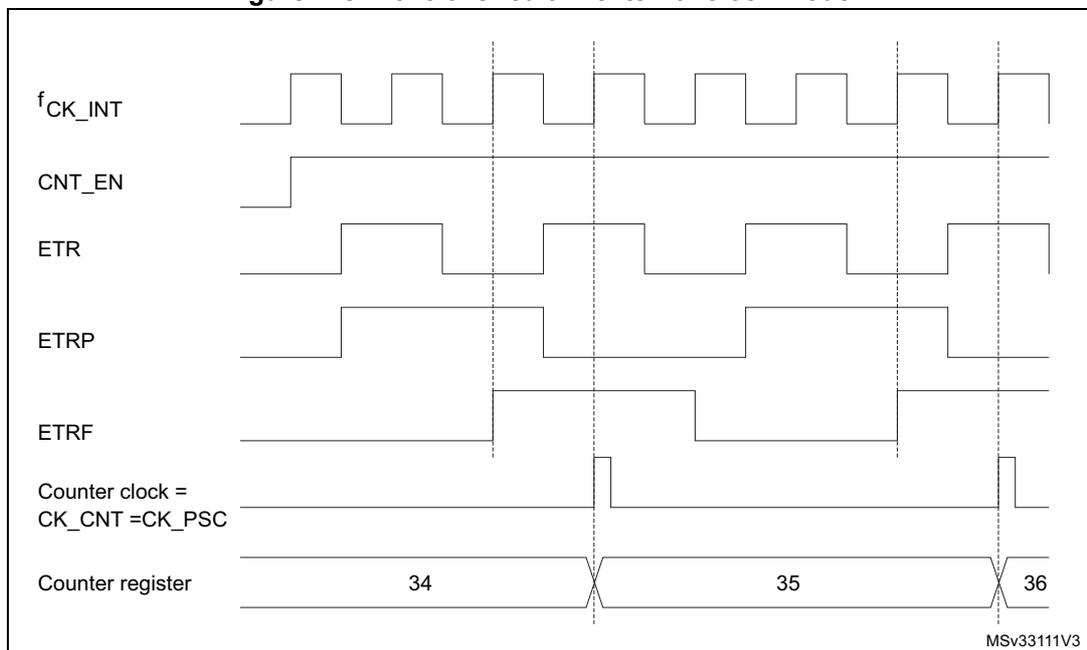

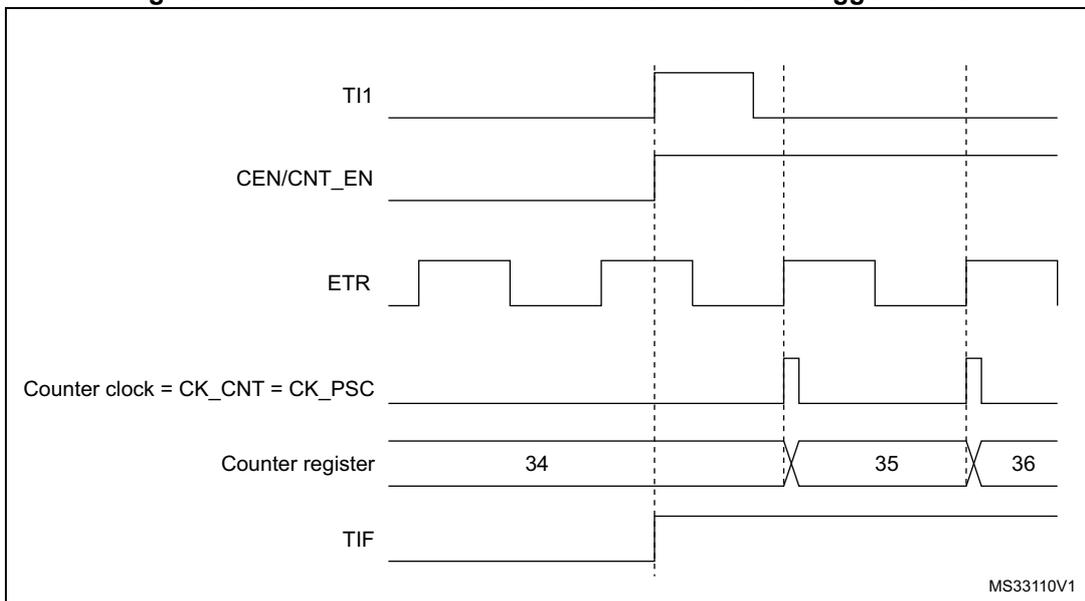

Figure 118. Control circuit in external clock mode 2

The timing diagram illustrates the relationship between several signals in external clock mode 2. The signals shown are:

- f CK _INT : Internal clock signal, shown as a periodic square wave.

- CNT_EN : Counter enable signal, which goes high to start counting.

- ETR : External trigger signal, shown as a square wave.

- ETRP : Resynchronized ETR signal, which follows ETR with some delay and jitter.

- ETRF : ETR filter output signal.

- Counter clock = CK_CNT = CK_PSC : The clock signal for the counter, which toggles (high-to-low and low-to-high) on every second rising edge of the ETR signal.

- Counter register : Shows the count values 34, 35, and 36. The count increments by one for each rising edge of the counter clock signal.

Vertical dashed lines indicate the timing relationships between the ETR rising edges and the subsequent counter clock transitions and count updates. The counter register values 34, 35, and 36 are shown at the bottom, with 34 and 36 marked by 'X' symbols indicating they are captured at specific ETR rising edges.

MSV3311V3

17.3.6 Capture/compare channels

Each Capture/Compare channel is built around a capture/compare register (including a shadow register), an input stage for capture (with digital filter, multiplexing, and prescaler, except for channels 5 and 6) and an output stage (with comparator and output control).

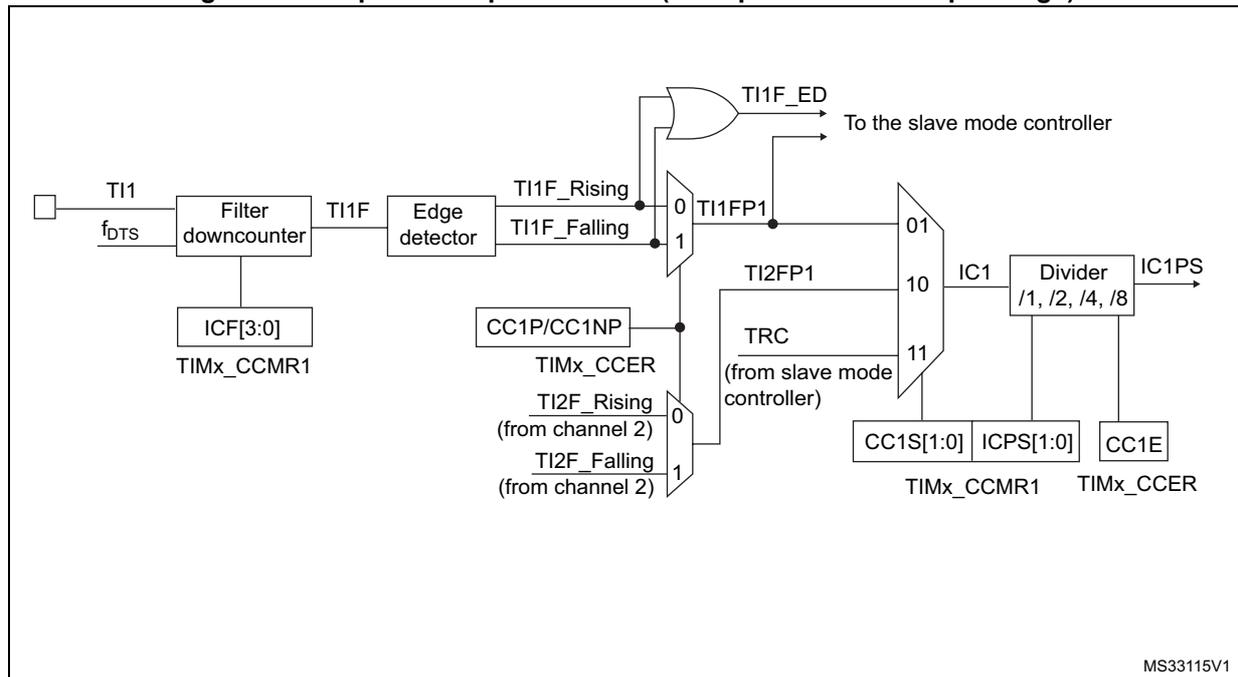

Figure 119 to Figure 122 give an overview of one Capture/Compare channel.

The input stage samples the corresponding TIx input to generate a filtered signal TIxF. Then, an edge detector with polarity selection generates a signal (TIxFPx) which can be used as trigger input by the slave mode controller or as the capture command. It is prescaled before the capture register (ICxPS).

Figure 119. Capture/compare channel (example: channel 1 input stage)

The diagram illustrates the input stage of a Capture/Compare channel. The input signal TI1 is processed through a 'Filter downcounter' block, which is controlled by ICF[3:0] from TIMx_CCMR1. The output of the filter is TI1F. This signal is then processed by an 'Edge detector' block, which generates two signals: TI1F_Rising and TI1F_Falling. These signals are multiplexed by a 2-to-1 multiplexer (inputs 0 and 1) controlled by CC1P/CC1NP from TIMx_CCER. The output of this multiplexer is TI1FP1. TI1FP1 is then processed by an OR gate along with TRC (from slave mode controller) to generate TI1F_ED, which is sent to the slave mode controller. TI1FP1 is also multiplexed by a 4-to-1 multiplexer (inputs 01, 10, 11) controlled by CC1S[1:0] from TIMx_CCMR1. The output of this multiplexer is IC1. IC1 is then processed by a 'Divider' block (/1, /2, /4, /8) controlled by ICPS[1:0] from TIMx_CCMR1 and CC1E from TIMx_CCER. The output of the divider is IC1PS. The diagram also shows various control signals and registers: ICF[3:0] from TIMx_CCMR1, CC1P/CC1NP from TIMx_CCER, TRC from slave mode controller, CC1S[1:0] from TIMx_CCMR1, ICPS[1:0] from TIMx_CCMR1, and CC1E from TIMx_CCER. The diagram is labeled MS33115V1.

The output stage generates an intermediate waveform which is then used for reference: OCxRef (active high). The polarity acts at the end of the chain.

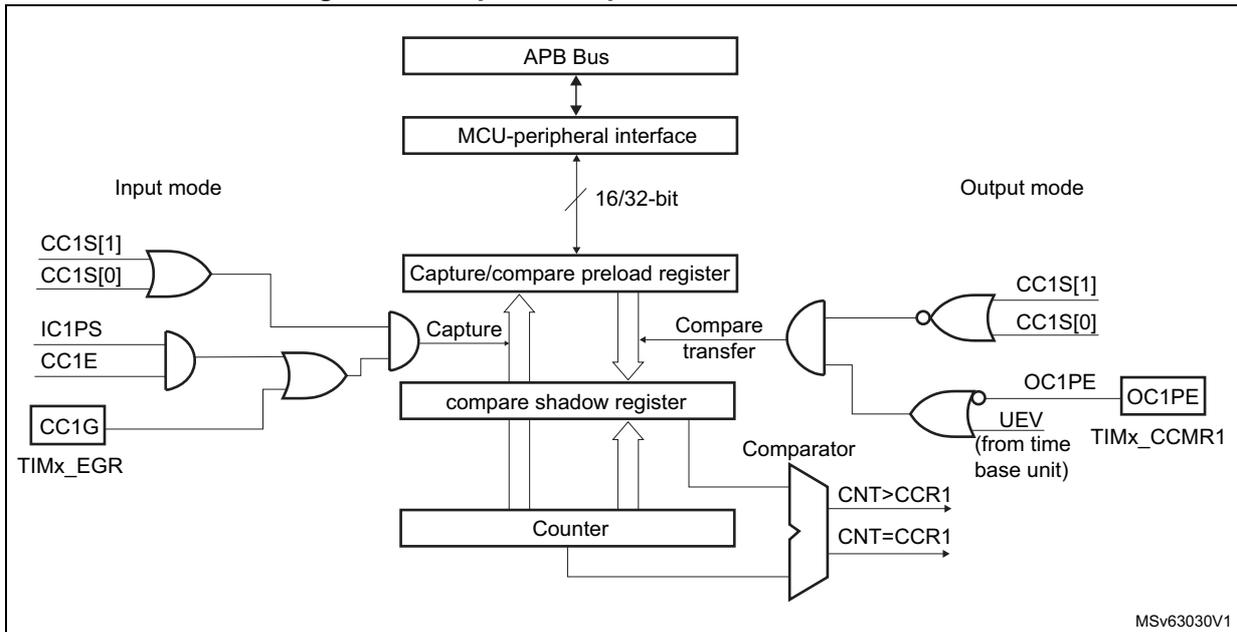

Figure 120. Capture/compare channel 1 main circuit

This diagram illustrates the internal logic of capture/compare channel 1. At the top, an APB Bus connects to an MCU-peripheral interface, which in turn connects to a 16/32-bit Capture/compare preload register and a compare shadow register. A Counter is also connected to these registers. In 'Input mode' on the left, signals CC1S[1], CC1S[0], IC1PS, CC1E, CC1G, and TIMx_EGR are processed through a series of OR gates to control the 'Capture' function into the preload register. In 'Output mode' on the right, the preload register feeds into the 'Compare transfer' logic, which includes a Comparator that checks CNT > CCR1 and CNT = CCR1. This logic, along with CC1S[1], CC1S[0], OC1PE, and a UEV signal from the time base unit, controls the output stage. The diagram is labeled MSv63030V1.

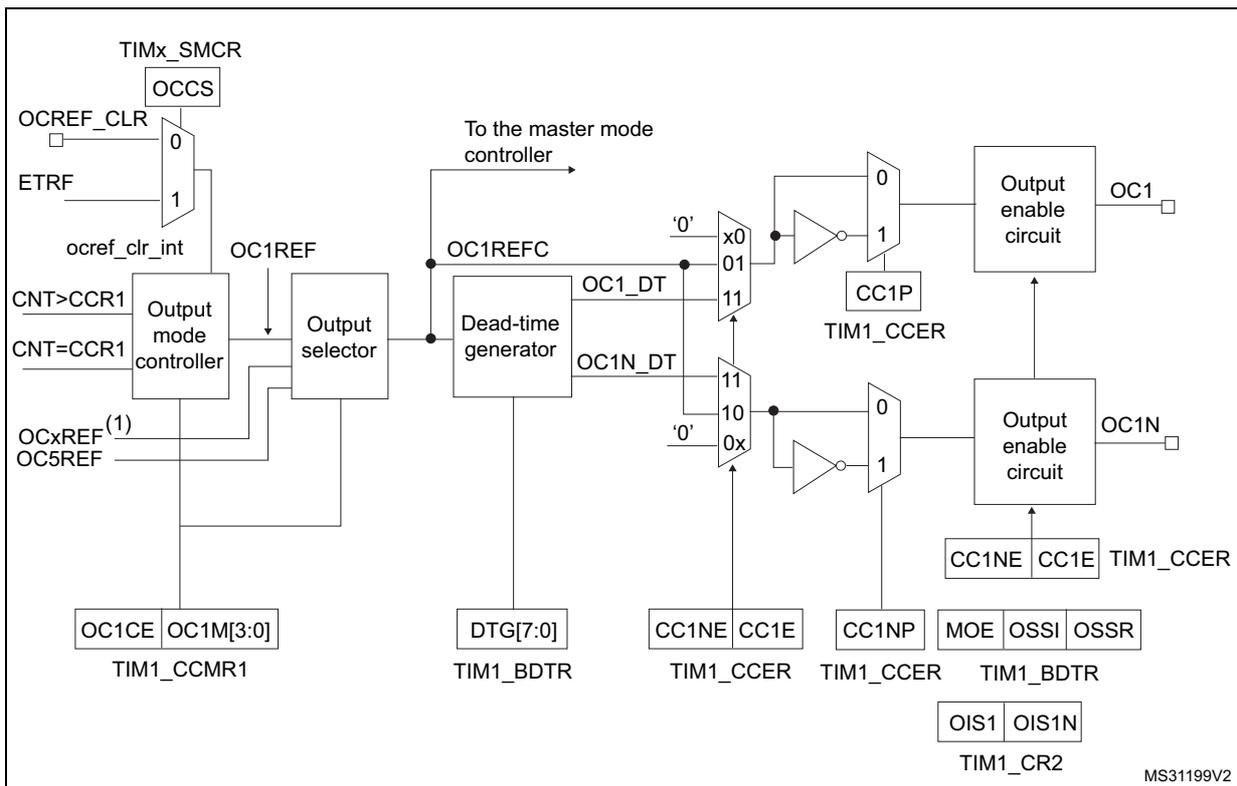

Figure 121. Output stage of capture/compare channel (channel 1, idem ch. 2 and 3)

This diagram shows the output stage logic for channel 1. It starts with TIMx_SMCR registers (OCCS, OCREF_CLR, ETRF) and an OCREF_CLR signal that feeds into a multiplexer. The output of this mux, labeled ocref_clr_int, is connected to an OC1REF signal. This signal, along with CNT > CCR1, CNT = CCR1, and OCxREF (where x is the complementary channel), feeds into an Output mode controller. The controller's output goes to an Output selector, which also receives inputs from OC1CE and OC1M[3:0] from the TIM1_CCMR1 register. The Output selector feeds into a Dead-time generator, which also receives DTG[7:0] from the TIM1_BDTR register. The Dead-time generator produces OC1REFC, OC1_DT, and OC1N_DT signals. OC1REFC is sent to the master mode controller. OC1_DT and OC1N_DT are processed through multiplexers and inverters to produce OC1 and OC1N signals. These signals are then passed through Output enable circuits. The enable circuits are controlled by CC1P and CC1NE/CC1E from the TIM1_CCER register, as well as MOE, OSSI, and OSSR from the TIM1_BDTR register. The diagram is labeled MS31199V2.

1. OCxREF, where x is the rank of the complementary channel

Figure 122. Output stage of capture/compare channel (channel 4)

![Schematic diagram of the output stage for capture/compare channel 4. It shows the flow from TIMx_SMCR (OCCS) and OCREF_CLR (0/1) through an output mode controller (inputs: CNT > CCR4, CNT = CCR4) to an output selector. The output mode controller also generates OC3REF and OC4REF signals. The output selector produces OC4REFC, which is connected to the master mode controller. The signal then passes through a series of multiplexers and an inverter to the output enable circuit, which generates the final OC4 output. Control signals include TIM1_CCMR2 (OC4CE, OC4M[3:0]), TIM1_CCER (CC4E, CC4P), TIM1_BDTR (MOE, OSSI), and TIM1_CR2 (OIS4).](/RM0366-STM32F301x6-8-318x8/35fc617eda17b1412dee0b52e3b28f59_img.jpg)

Figure 123. Output stage of capture/compare channel (channel 5, idem ch. 6)

![Schematic diagram of the output stage for capture/compare channel 5, which is identical in structure to channel 4. It shows the flow from TIMx_SMCR (OCCS) and OCREF_CLR (0/1) through an output mode controller (inputs: CNT > CCR5, CNT = CCR5) to an output selector. The output mode controller generates OC5REF and OC5REFC signals. The output selector produces OC5REFC, which is connected to the master mode controller. The signal then passes through a series of multiplexers and an inverter to the output enable circuit, which generates the final OC5 output (labeled OC5(1)). Control signals include TIM1_CCMR2 (OC5CE, OC5M[3:0]), TIM1_CCER (CC5E, CC5P), TIM1_BDTR (MOE, OSSI), and TIM1_CR2 (OIS5).](/RM0366-STM32F301x6-8-318x8/34340d1a45e15a8faee7d715966220d1_img.jpg)

1. Not available externally.

The capture/compare block is made of one preload register and one shadow register. Write and read always access the preload register.

In capture mode, captures are actually done in the shadow register, which is copied into the preload register.

In compare mode, the content of the preload register is copied into the shadow register which is compared to the counter.

17.3.7 Input capture mode

In Input capture mode, the Capture/Compare Registers (TIMx_CCRx) are used to latch the value of the counter after a transition detected by the corresponding ICx signal. When a capture occurs, the corresponding CCxIF flag (TIMx_SR register) is set and an interrupt or a DMA request can be sent if they are enabled. If a capture occurs while the CCxIF flag was already high, then the over-capture flag CCxOF (TIMx_SR register) is set. CCxIF can be cleared by software by writing it to '0' or by reading the captured data stored in the TIMx_CCRx register. CCxOF is cleared when written with '0'.

The following example shows how to capture the counter value in TIMx_CCR1 when TI1 input rises. To do this, use the following procedure:

- 1. Select the active input: TIMx_CCR1 must be linked to the TI1 input, so write the CC1S bits to 01 in the TIMx_CCMR1 register. As soon as CC1S becomes different from 00, the channel is configured in input and the TIMx_CCR1 register becomes read-only.

- 2. Program the appropriate input filter duration in relation with the signal connected to the timer (when the input is one of the TIx (ICxF bits in the TIMx_CCMRx register). Let's imagine that, when toggling, the input signal is not stable during at most 5 internal clock cycles. We must program a filter duration longer than these 5 clock cycles. We can validate a transition on TI1 when 8 consecutive samples with the new level have been detected (sampled at \( f_{DTS} \) frequency). Then write IC1F bits to 0011 in the TIMx_CCMR1 register.

- 3. Select the edge of the active transition on the TI1 channel by writing CC1P and CC1NP bits to 0 in the TIMx_CCER register (rising edge in this case).

- 4. Program the input prescaler. In our example, we wish the capture to be performed at each valid transition, so the prescaler is disabled (write IC1PS bits to '00' in the TIMx_CCMR1 register).

- 5. Enable capture from the counter into the capture register by setting the CC1E bit in the TIMx_CCER register.

- 6. If needed, enable the related interrupt request by setting the CC1IE bit in the TIMx_DIER register, and/or the DMA request by setting the CC1DE bit in the TIMx_DIER register.

When an input capture occurs:

- • The TIMx_CCR1 register gets the value of the counter on the active transition.

- • CC1IF flag is set (interrupt flag). CC1OF is also set if at least two consecutive captures occurred whereas the flag was not cleared.

- • An interrupt is generated depending on the CC1IE bit.

- • A DMA request is generated depending on the CC1DE bit.

In order to handle the overcapture, it is recommended to read the data before the overcapture flag. This is to avoid missing an overcapture which could happen after reading the flag and before reading the data.

Note: IC interrupt and/or DMA requests can be generated by software by setting the corresponding CCxG bit in the TIMx_EGR register.

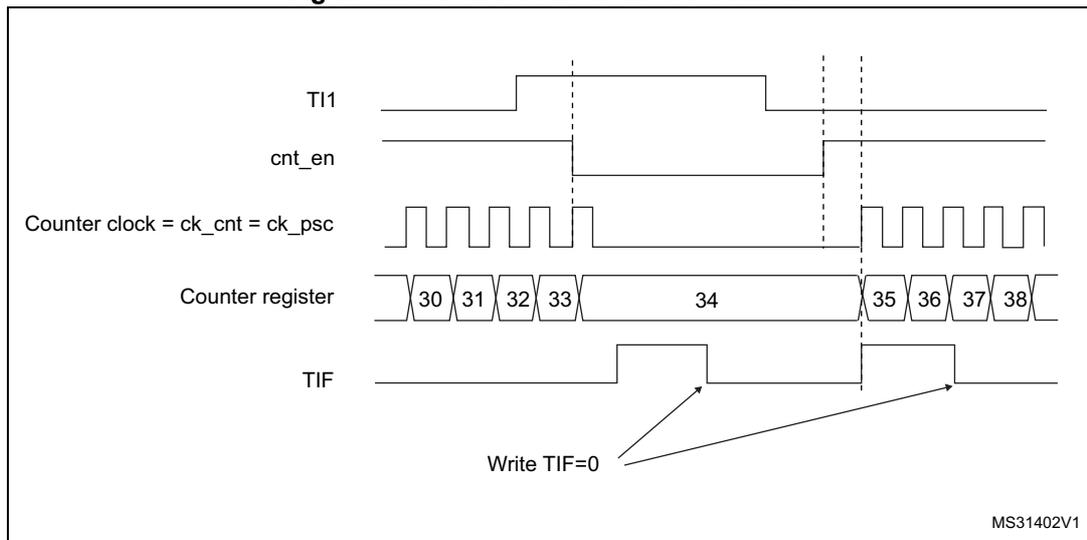

17.3.8 PWM input mode

This mode is a particular case of input capture mode. The procedure is the same except:

- • Two ICx signals are mapped on the same TIx input.

- • These 2 ICx signals are active on edges with opposite polarity.

- • One of the two TIxFP signals is selected as trigger input and the slave mode controller is configured in reset mode.

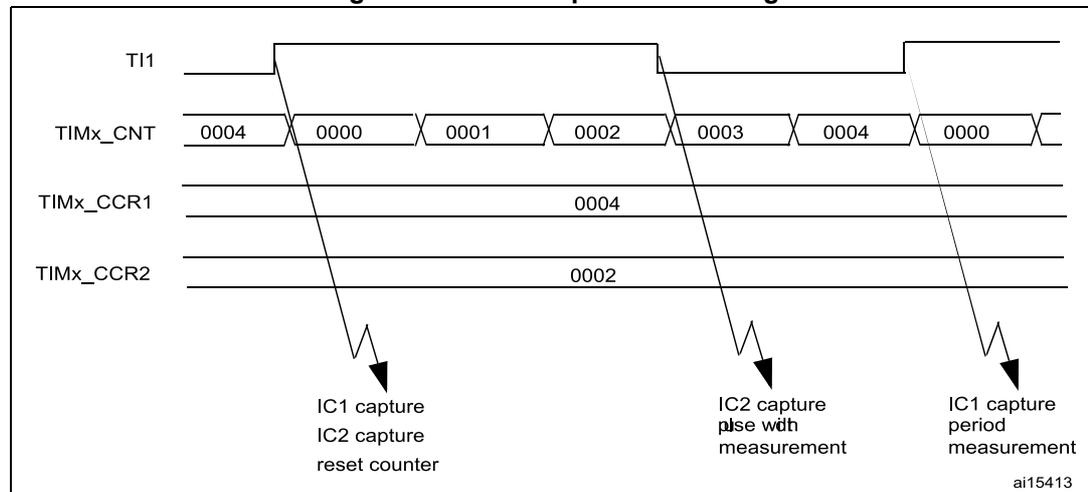

For example, the user can measure the period (in TIMx_CCR1 register) and the duty cycle (in TIMx_CCR2 register) of the PWM applied on TI1 using the following procedure (depending on CK_INT frequency and prescaler value):

- 1. Select the active input for TIMx_CCR1: write the CC1S bits to 01 in the TIMx_CCMR1 register (TI1 selected).

- 2. Select the active polarity for TI1FP1 (used both for capture in TIMx_CCR1 and counter clear): write the CC1P and CC1NP bits to '0' (active on rising edge).

- 3. Select the active input for TIMx_CCR2: write the CC2S bits to 10 in the TIMx_CCMR1 register (TI1 selected).

- 4. Select the active polarity for TI1FP2 (used for capture in TIMx_CCR2): write the CC2P and CC2NP bits to CC2P/CC2NP='10' (active on falling edge).

- 5. Select the valid trigger input: write the TS bits to 101 in the TIMx_SMCR register (TI1FP1 selected).

- 6. Configure the slave mode controller in reset mode: write the SMS bits to 0100 in the TIMx_SMCR register.

- 7. Enable the captures: write the CC1E and CC2E bits to '1' in the TIMx_CCER register.

Figure 124. PWM input mode timing

17.3.9 Forced output mode

In output mode (CCxS bits = 00 in the TIMx_CCMRx register), each output compare signal (OCxREF and then OCx/OCxN) can be forced to active or inactive level directly by software, independently of any comparison between the output compare register and the counter.

To force an output compare signal (OCXREF/OCx) to its active level, user just needs to write 0101 in the OCxM bits in the corresponding TIMx_CCMRx register. Thus OCXREF is

forced high (OCxREF is always active high) and OCx get opposite value to CCxP polarity bit.

For example: CCxP=0 (OCx active high) => OCx is forced to high level.

The OCxREF signal can be forced low by writing the OCxM bits to 0100 in the TIMx_CCMRx register.

Anyway, the comparison between the TIMx_CCRx shadow register and the counter is still performed and allows the flag to be set. Interrupt and DMA requests can be sent accordingly. This is described in the output compare mode section below.

17.3.10 Output compare mode

This function is used to control an output waveform or indicate when a period of time has elapsed. Channels 1 to 4 can be output, while Channel 5 and 6 are only available inside the device (for instance, for compound waveform generation or for ADC triggering).

When a match is found between the capture/compare register and the counter, the output compare function:

- • Assigns the corresponding output pin to a programmable value defined by the output compare mode (OCxM bits in the TIMx_CCMRx register) and the output polarity (CCxP bit in the TIMx_CCER register). The output pin can keep its level (OCxM=0000), be set active (OCxM=0001), be set inactive (OCxM=0010) or can toggle (OCxM=0011) on match.

- • Sets a flag in the interrupt status register (CCxIF bit in the TIMx_SR register).

- • Generates an interrupt if the corresponding interrupt mask is set (CCxIE bit in the TIMx_DIER register).

- • Sends a DMA request if the corresponding enable bit is set (CCxDE bit in the TIMx_DIER register, CCDS bit in the TIMx_CR2 register for the DMA request selection).

The TIMx_CCRx registers can be programmed with or without preload registers using the OCxPE bit in the TIMx_CCMRx register.

In output compare mode, the update event UEV has no effect on OCxREF and OCx output. The timing resolution is one count of the counter. Output compare mode can also be used to output a single pulse (in One Pulse mode).

Procedure

- 1. Select the counter clock (internal, external, prescaler).

- 2. Write the desired data in the TIMx_ARR and TIMx_CCRx registers.

- 3. Set the CCxIE bit if an interrupt request is to be generated.

- 4. Select the output mode. For example:

- – Write OCxM = 0011 to toggle OCx output pin when CNT matches CCRx

- – Write OCxPE = 0 to disable preload register

- – Write CCxP = 0 to select active high polarity

- – Write CCxE = 1 to enable the output

- 5. Enable the counter by setting the CEN bit in the TIMx_CR1 register.

The TIMx_CCRx register can be updated at any time by software to control the output waveform, provided that the preload register is not enabled (OCxPE='0', else TIMx_CCRx

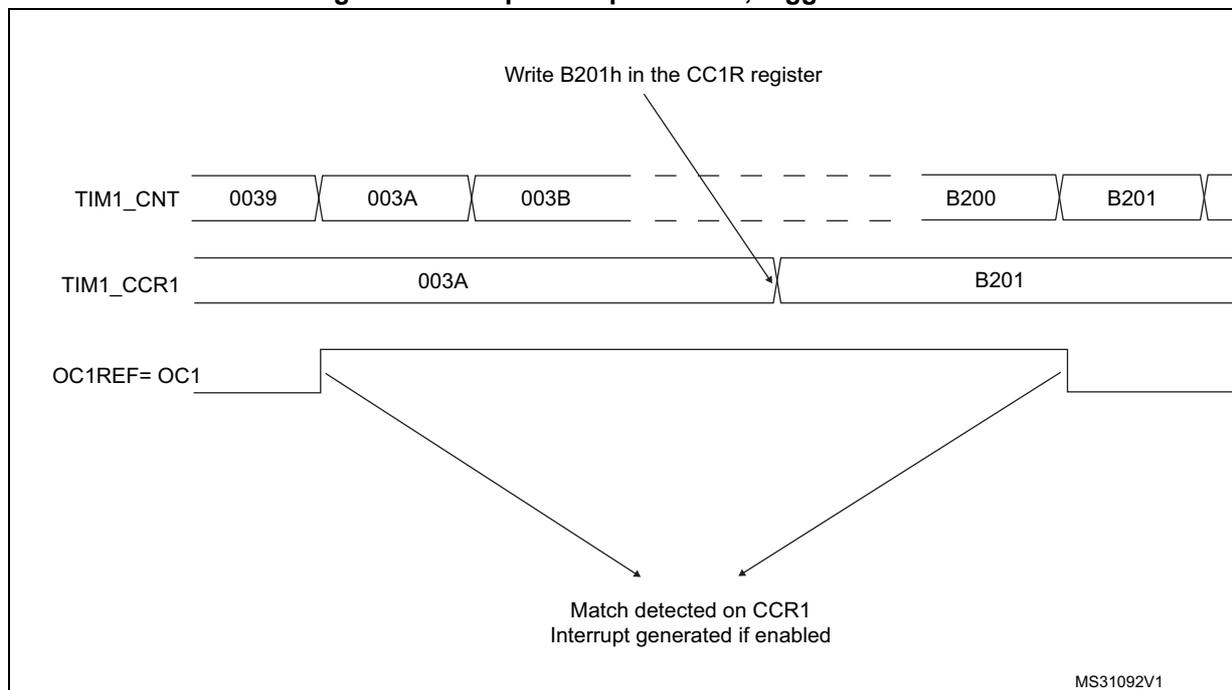

shadow register is updated only at the next update event UEV). An example is given in Figure 125 .

Figure 125. Output compare mode, toggle on OC1

Write B201h in the CC1R register

TIM1_CNT: 0039 | 003A | 003B | - - - - - | B200 | B201

TIM1_CCR1: 003A | B201

OC1REF= OC1: [High] --- [Low] --- [High]

Match detected on CCR1

Interrupt generated if enabled

MS31092V1

17.3.11 PWM mode

Pulse Width Modulation mode allows a signal to be generated with a frequency determined by the value of the TIMx_ARR register and a duty cycle determined by the value of the TIMx_CCRx register.

The PWM mode can be selected independently on each channel (one PWM per OCx output) by writing '0110' (PWM mode 1) or '0111' (PWM mode 2) in the OCxM bits in the TIMx_CCMRx register. The corresponding preload register must be enabled by setting the OCxPE bit in the TIMx_CCMRx register, and eventually the auto-reload preload register (in upcounting or center-aligned modes) by setting the ARPE bit in the TIMx_CR1 register.

As the preload registers are transferred to the shadow registers only when an update event occurs, before starting the counter, all registers must be initialized by setting the UG bit in the TIMx_EGR register.

OCx polarity is software programmable using the CCxP bit in the TIMx_CCER register. It can be programmed as active high or active low. OCx output is enabled by a combination of the CCxE, CCxNE, MOE, OSSI and OSSR bits (TIMx_CCER and TIMx_BDTR registers). Refer to the TIMx_CCER register description for more details.

In PWM mode (1 or 2), TIMx_CNT and TIMx_CCRx are always compared to determine whether \( TIMx\_CCRx \leq TIMx\_CNT \) or \( TIMx\_CNT \leq TIMx\_CCRx \) (depending on the direction of the counter).

The timer is able to generate PWM in edge-aligned mode or center-aligned mode depending on the CMS bits in the TIMx_CR1 register.

PWM edge-aligned mode

- • Upcounting configuration

Upcounting is active when the DIR bit in the TIMx_CR1 register is low. Refer to the Upcounting mode on page 337 .

In the following example, we consider PWM mode 1. The reference PWM signal OCxREF is high as long as TIMx_CNT < TIMx_CCRx else it becomes low. If the compare value in TIMx_CCRx is greater than the auto-reload value (in TIMx_ARR) then OCxREF is held at '1'. If the compare value is 0 then OCxRef is held at '0'.

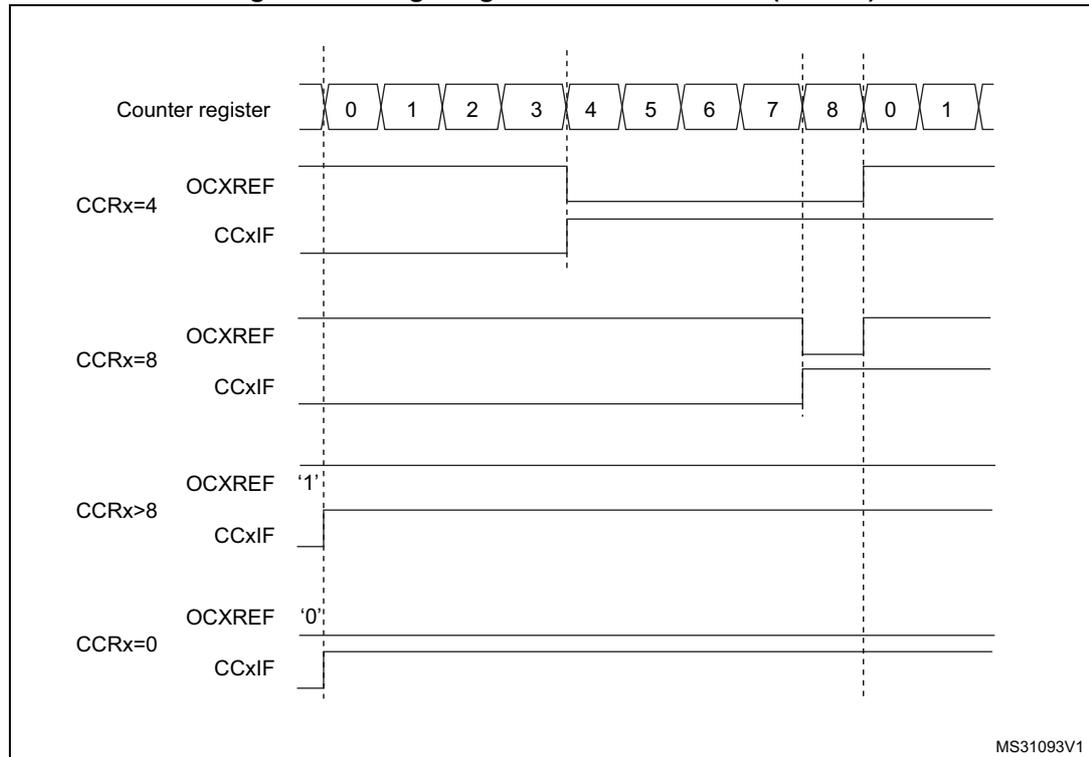

Figure 126 shows some edge-aligned PWM waveforms in an example where TIMx_ARR=8.

Figure 126. Edge-aligned PWM waveforms (ARR=8)

The figure is a timing diagram illustrating edge-aligned PWM waveforms for an advanced-control timer (TIM1) in upcounting mode with an auto-reload register (ARR) value of 8. The counter register (TIMx_CNT) is shown at the top, with values 0, 1, 2, 3, 4, 5, 6, 7, 8, 0, 1. Vertical dashed lines indicate the counter's state at each integer value. Below the counter, four sets of waveforms are shown for different compare register (CCR) values:

- CCRx=4: The OCxREF signal is high from counter 0 to 3 and becomes low at counter 4. The CCxIF flag is shown as a pulse at counter 4.

- CCRx=8: The OCxREF signal is high from counter 0 to 7 and becomes low at counter 8. The CCxIF flag is shown as a pulse at counter 8.

- CCRx>8: The OCxREF signal is permanently high ('1') because the counter never reaches the compare value. The CCxIF flag is shown as a low signal.

- CCRx=0: The OCxREF signal is permanently low ('0') because the counter is always greater than or equal to the compare value. The CCxIF flag is shown as a low signal.

- • Downcounting configuration

Downcounting is active when DIR bit in TIMx_CR1 register is high. Refer to the Downcounting mode on page 341

In PWM mode 1, the reference signal OCxRef is low as long as TIMx_CNT > TIMx_CCRx else it becomes high. If the compare value in TIMx_CCRx is greater than the auto-reload value in TIMx_ARR, then OCxREF is held at '1'. 0% PWM is not possible in this mode.

PWM center-aligned mode

Center-aligned mode is active when the CMS bits in TIMx_CR1 register are different from '00' (all the remaining configurations having the same effect on the OCxRef/OCx signals). The compare flag is set when the counter counts up, when it counts down or both when it counts up and down depending on the CMS bits configuration. The direction bit (DIR) in the

TIMx_CR1 register is updated by hardware and must not be changed by software. Refer to the Center-aligned mode (up/down counting) on page 344 .

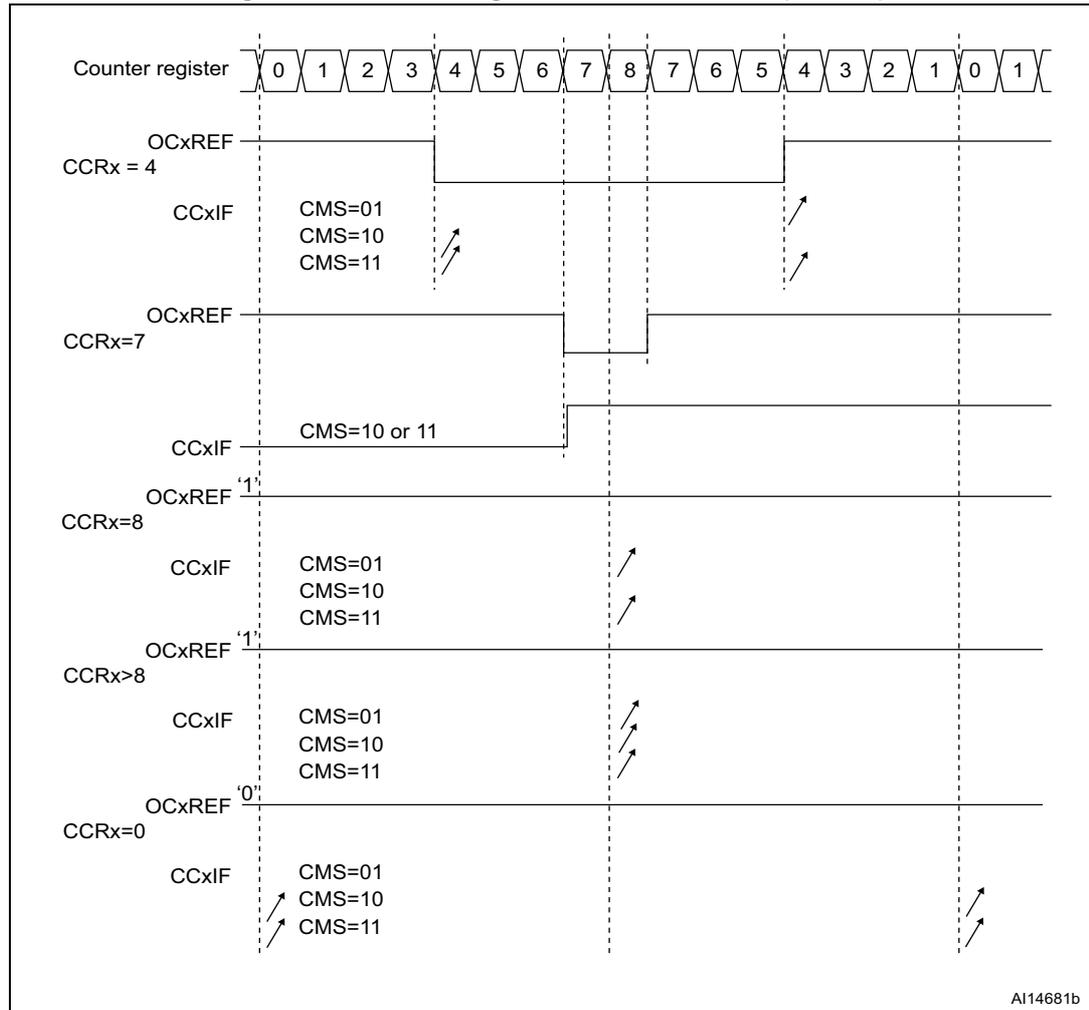

Figure 127 shows some center-aligned PWM waveforms in an example where:

- • TIMx_ARR=8,

- • PWM mode is the PWM mode 1,

- • The flag is set when the counter counts down corresponding to the center-aligned mode 1 selected for CMS=01 in TIMx_CR1 register.

Figure 127. Center-aligned PWM waveforms (ARR=8)

The figure illustrates the relationship between the counter register values and the resulting PWM waveforms for different CCRx values in center-aligned mode. The counter register values are shown at the top: 0, 1, 2, 3, 4, 5, 6, 7, 8, 7, 6, 5, 4, 3, 2, 1, 0, 1. Vertical dashed lines mark the counter values 0, 4, 7, 8, and 0 again. The OCxREF signal is shown for CCRx = 4, 7, 8, >8, and 0. The CCxIF flag is shown for each CCRx value, with arrows indicating the specific counter values that trigger the flag (e.g., for CCRx=4, the flag is set when the counter counts down from 5 to 4). The diagram also shows the initial state of the OCxREF signal for CCRx=8 and CCRx>8.

A14681b

Hints on using center-aligned mode

- • When starting in center-aligned mode, the current up-down configuration is used. It means that the counter counts up or down depending on the value written in the DIR bit

in the TIMx_CR1 register. Moreover, the DIR and CMS bits must not be changed at the same time by the software.

- • Writing to the counter while running in center-aligned mode is not recommended as it can lead to unexpected results. In particular:

- – The direction is not updated if a value greater than the auto-reload value is written in the counter (TIMx_CNT > TIMx_ARR). For example, if the counter was counting up, it continues to count up.

- – The direction is updated if 0 or the TIMx_ARR value is written in the counter but no Update Event UEV is generated.

- • The safest way to use center-aligned mode is to generate an update by software (setting the UG bit in the TIMx_EGR register) just before starting the counter and not to write the counter while it is running.

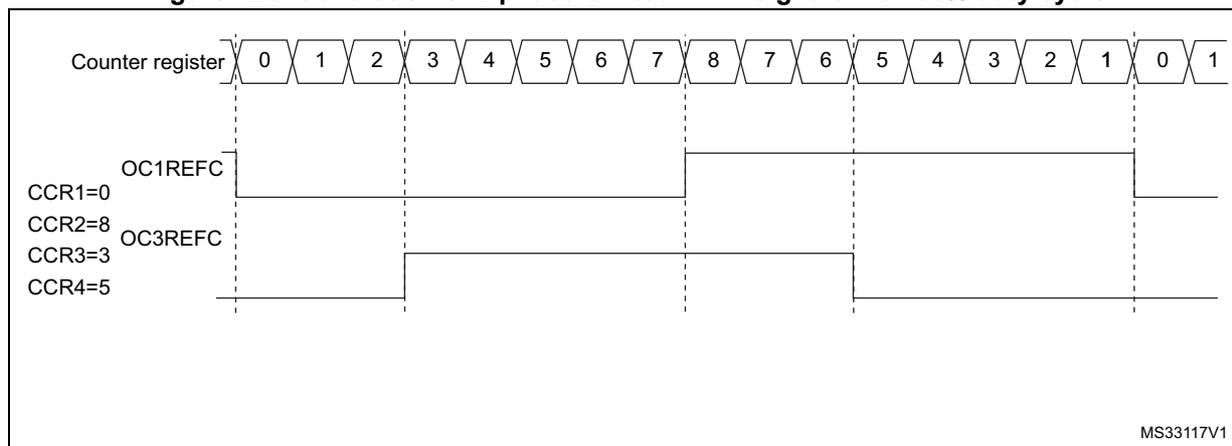

17.3.12 Asymmetric PWM mode

Asymmetric mode allows two center-aligned PWM signals to be generated with a programmable phase shift. While the frequency is determined by the value of the TIMx_ARR register, the duty cycle and the phase-shift are determined by a pair of TIMx_CCRx register. One register controls the PWM during up-counting, the second during down counting, so that PWM is adjusted every half PWM cycle:

- – OC1REFC (or OC2REFC) is controlled by TIMx_CCR1 and TIMx_CCR2

- – OC3REFC (or OC4REFC) is controlled by TIMx_CCR3 and TIMx_CCR4

Asymmetric PWM mode can be selected independently on two channel (one OCx output per pair of CCR registers) by writing '1110' (Asymmetric PWM mode 1) or '1111' (Asymmetric PWM mode 2) in the OCxM bits in the TIMx_CCMRx register.

Note: The OCxM[3:0] bit field is split into two parts for compatibility reasons, the most significant bit is not contiguous with the 3 least significant ones.

When a given channel is used as asymmetric PWM channel, its complementary channel can also be used. For instance, if an OC1REFC signal is generated on channel 1 (Asymmetric PWM mode 1), it is possible to output either the OC2REF signal on channel 2, or an OC2REFC signal resulting from asymmetric PWM mode 1.

Figure 128 represents an example of signals that can be generated using Asymmetric PWM mode (channels 1 to 4 are configured in Asymmetric PWM mode 1). Together with the deadtime generator, this allows a full-bridge phase-shifted DC to DC converter to be controlled.

Figure 128. Generation of 2 phase-shifted PWM signals with 50% duty cycle

Counter register: 0 1 2 3 4 5 6 7 8 7 6 5 4 3 2 1 0 1

OC1REFC (CCR1=0)

OC3REFC (CCR3=3)

MS33117V1

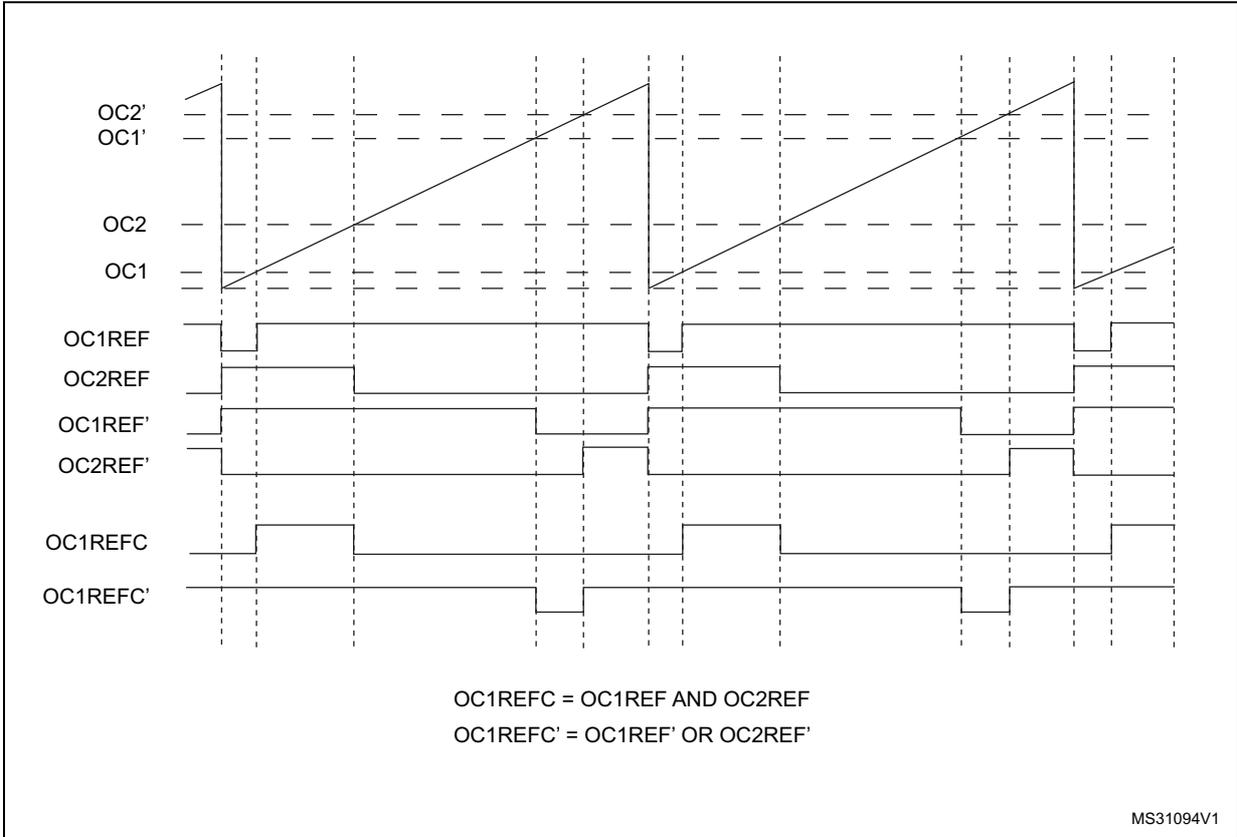

17.3.13 Combined PWM mode

Combined PWM mode allows two edge or center-aligned PWM signals to be generated with programmable delay and phase shift between respective pulses. While the frequency is determined by the value of the TIMx_ARR register, the duty cycle and delay are determined by the two TIMx_CCRx registers. The resulting signals, OCxREFC, are made of an OR or AND logical combination of two reference PWMs:

- – OC1REFC (or OC2REFC) is controlled by TIMx_CCR1 and TIMx_CCR2

- – OC3REFC (or OC4REFC) is controlled by TIMx_CCR3 and TIMx_CCR4

Combined PWM mode can be selected independently on two channels (one OCx output per pair of CCR registers) by writing '1100' (Combined PWM mode 1) or '1101' (Combined PWM mode 2) in the OCxM bits in the TIMx_CCMRx register.

When a given channel is used as combined PWM channel, its complementary channel must be configured in the opposite PWM mode (for instance, one in Combined PWM mode 1 and the other in Combined PWM mode 2).

Note: The OCxM[3:0] bit field is split into two parts for compatibility reasons, the most significant bit is not contiguous with the 3 least significant ones.

Figure 129 represents an example of signals that can be generated using Asymmetric PWM mode, obtained with the following configuration:

- – Channel 1 is configured in Combined PWM mode 2,

- – Channel 2 is configured in PWM mode 1,

- – Channel 3 is configured in Combined PWM mode 2,

- – Channel 4 is configured in PWM mode 1.

Figure 129. Combined PWM mode on channel 1 and 3

OC1REFC = OC1REF AND OC2REF

OC1REFC' = OC1REF' OR OC2REF'

MS31094V1

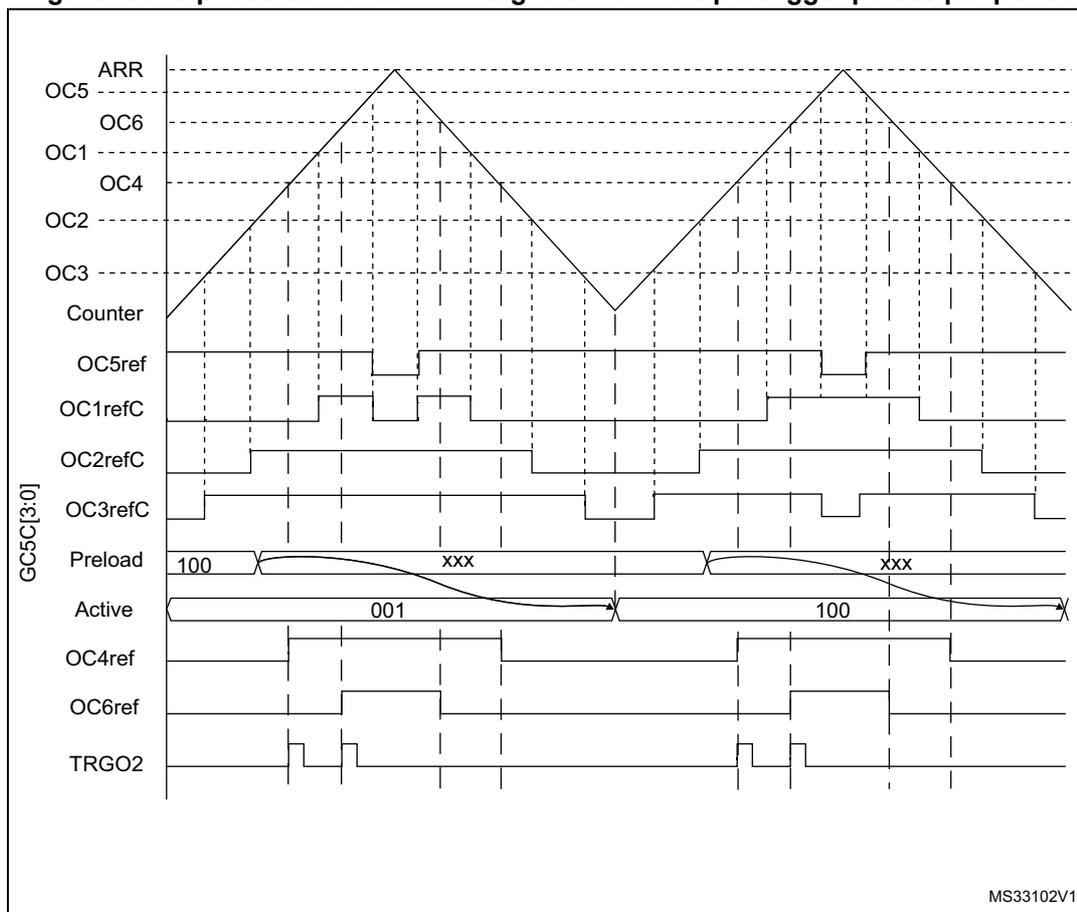

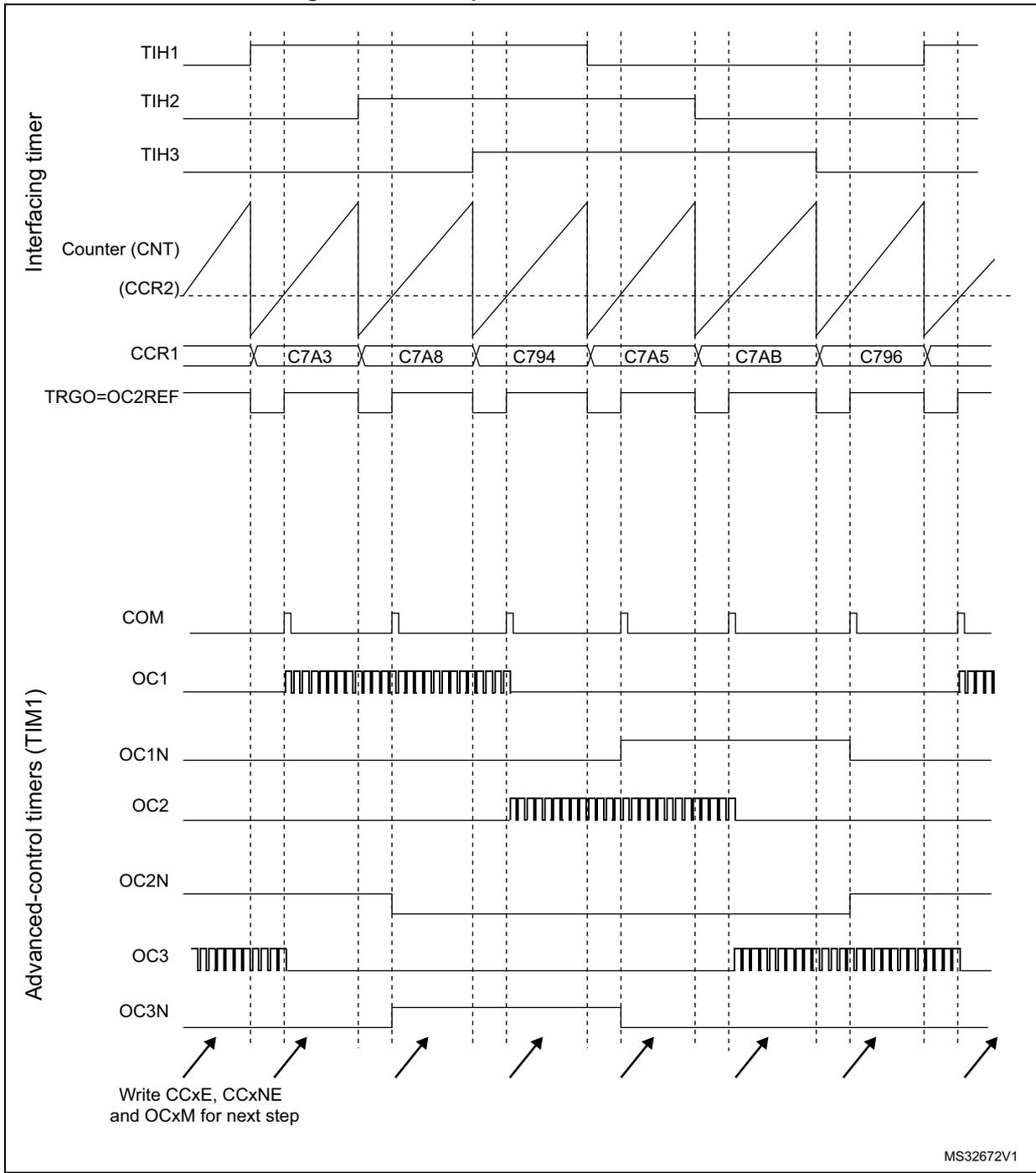

17.3.14 Combined 3-phase PWM mode

Combined 3-phase PWM mode allows one to three center-aligned PWM signals to be generated with a single programmable signal ANDed in the middle of the pulses. The OC5REF signal is used to define the resulting combined signal. The 3-bits GC5C[3:1] in the TIMx_CCR5 allow selection on which reference signal the OC5REF is combined. The resulting signals, OCxREFC, are made of an AND logical combination of two reference PWMs:

- - If GC5C1 is set, OC1REFC is controlled by TIMx_CCR1 and TIMx_CCR5

- - If GC5C2 is set, OC2REFC is controlled by TIMx_CCR2 and TIMx_CCR5

- - If GC5C3 is set, OC3REFC is controlled by TIMx_CCR3 and TIMx_CCR5

Combined 3-phase PWM mode can be selected independently on channels 1 to 3 by setting at least one of the 3-bits GC5C[3:1].

Figure 130. 3-phase combined PWM signals with multiple trigger pulses per period

The TRGO2 waveform shows how the ADC can be synchronized on given 3-phase PWM signals. Refer to Section 17.3.26: ADC synchronization for more details.

17.3.15 Complementary outputs and dead-time insertion

The advanced-control timers (TIM1) can output two complementary signals and manage the switching-off and the switching-on instants of the outputs.

This time is generally known as dead-time and it has to be adjusted depending on the devices that are connected to the outputs and their characteristics (intrinsic delays of level-shifters, delays due to power switches...)

The polarity of the outputs (main output OCx or complementary OCxN) can be selected independently for each output. This is done by writing to the CCxP and CCxNP bits in the TIMx_CCER register.

The complementary signals OCx and OCxN are activated by a combination of several control bits: the CCxE and CCxNE bits in the TIMx_CCER register and the MOE, OISx, OISxN, OSSI and OSSR bits in the TIMx_BDTR and TIMx_CR2 registers. Refer to Table 61: Output control bits for complementary OCx and OCxN channels with break feature on page 411 for more details. In particular, the dead-time is activated when switching to the idle state (MOE falling down to 0).

Dead-time insertion is enabled by setting both CCxE and CCxNE bits, and the MOE bit if the break circuit is present. There is one 10-bit dead-time generator for each channel. From a reference waveform OCxREF, it generates 2 outputs OCx and OCxN. If OCx and OCxN are active high:

- • The OCx output signal is the same as the reference signal except for the rising edge, which is delayed relative to the reference rising edge.

- • The OCxN output signal is the opposite of the reference signal except for the rising edge, which is delayed relative to the reference falling edge.

If the delay is greater than the width of the active output (OCx or OCxN) then the corresponding pulse is not generated.

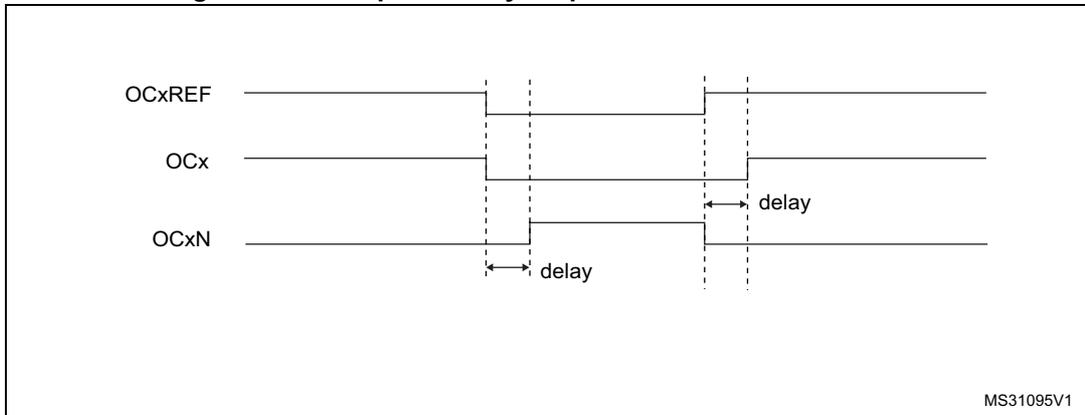

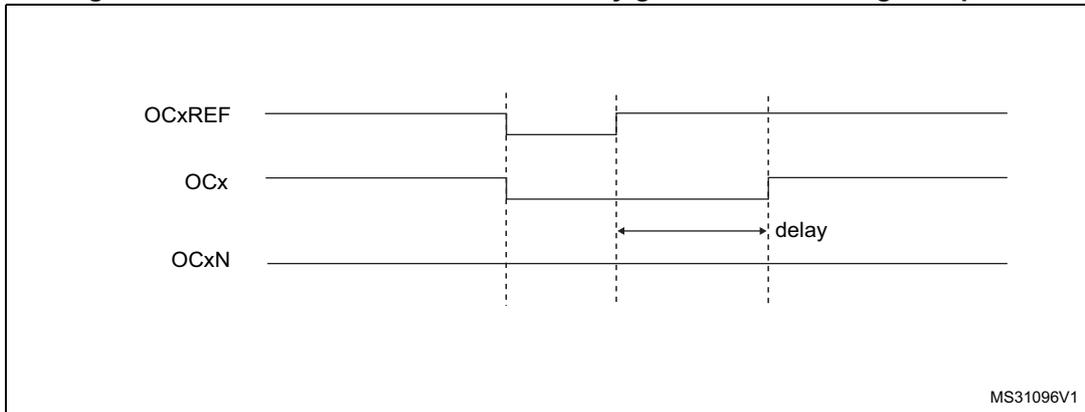

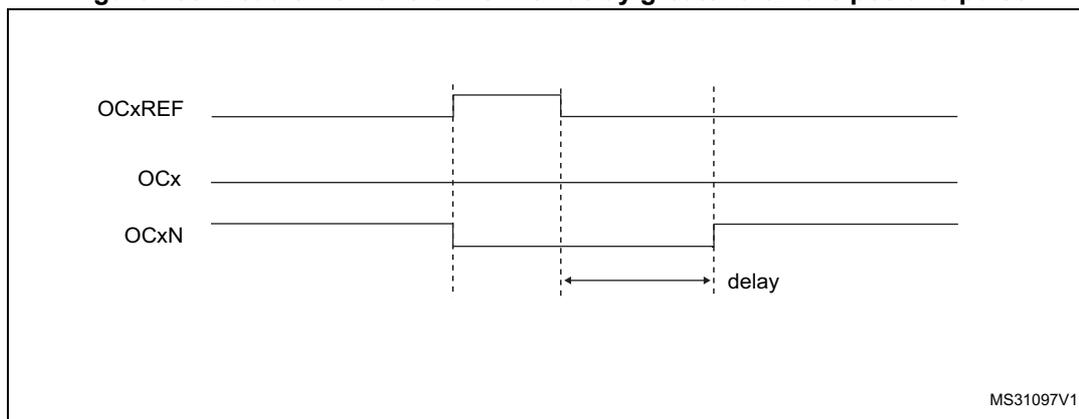

The following figures show the relationships between the output signals of the dead-time generator and the reference signal OCxREF. (we suppose CCxP=0, CCxNP=0, MOE=1, CCxE=1 and CCxNE=1 in these examples)

Figure 131. Complementary output with dead-time insertion

This timing diagram illustrates the relationship between a reference signal (OCxREF) and two complementary output signals (OCx and OCxN) with dead-time insertion. The OCxREF signal is a square wave. The OCx signal follows the OCxREF signal but has a delayed rising edge. The OCxN signal is the inverse of the OCx signal but also has a delayed rising edge. The 'delay' is indicated by double-headed arrows between the rising edges of the reference signal and the output signals. The diagram is labeled MS31095V1 in the bottom right corner.

Figure 132. Dead-time waveforms with delay greater than the negative pulse

This timing diagram shows the output signals when the dead-time delay is greater than the width of the negative pulse of the reference signal. The OCxREF signal is a square wave. The OCx signal follows the OCxREF signal but has a delayed rising edge. The OCxN signal is the inverse of the OCx signal but also has a delayed rising edge. The 'delay' is indicated by a double-headed arrow between the rising edges of the reference signal and the output signals. The diagram is labeled MS31096V1 in the bottom right corner.

Figure 133. Dead-time waveforms with delay greater than the positive pulse

The diagram shows three digital signals over time. OCxREF is a reference signal that pulses high. OCx is the primary output that is initially high and becomes low when OCxREF is high. OCxN is the complementary output that is initially low and becomes high when OCxREF is high. A horizontal double-headed arrow labeled 'delay' indicates the time interval between the falling edge of OCxREF and the rising edge of OCxN. The text 'MS31097V1' is in the bottom right corner.

The dead-time delay is the same for each of the channels and is programmable with the DTG bits in the TIMx_BDTR register. Refer to Section 17.4.20: TIM1 break and dead-time register (TIM1_BDTR) for delay calculation.

Re-directing OCxREF to OCx or OCxN

In output mode (forced, output compare or PWM), OCxREF can be re-directed to the OCx output or to OCxN output by configuring the CCxE and CCxNE bits in the TIMx_CCER register.

This allows a specific waveform to be sent (such as PWM or static active level) on one output while the complementary remains at its inactive level. Other alternative possibilities are to have both outputs at inactive level or both outputs active and complementary with dead-time.

Note: When only OCxN is enabled (CCxE=0, CCxNE=1), it is not complemented and becomes active as soon as OCxREF is high. For example, if CCxNP=0 then OCxN=OCxRef. On the other hand, when both OCx and OCxN are enabled (CCxE=CCxNE=1) OCx becomes active when OCxREF is high whereas OCxN is complemented and becomes active when OCxREF is low.

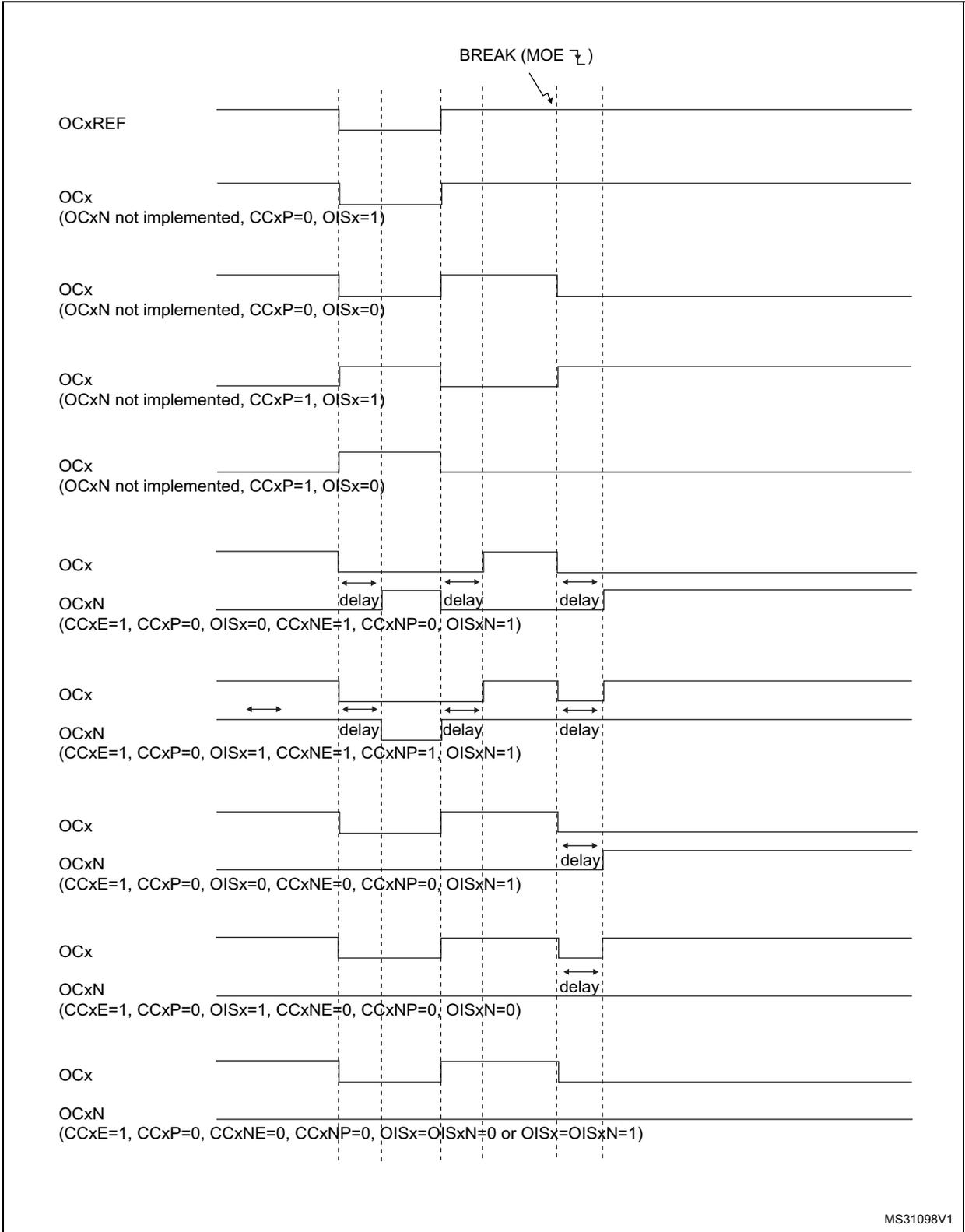

17.3.16 Using the break function

The purpose of the break function is to protect power switches driven by PWM signals generated with the TIM1 timer. The two break inputs are usually connected to fault outputs of power stages and 3-phase inverters. When activated, the break circuitry shuts down the PWM outputs and forces them to a predefined safe state.

When using the break functions, the output enable signals and inactive levels are modified according to additional control bits (MOE, OSSI and OSSR bits in the TIMx_BDTR register, OISx and OISxN bits in the TIMx_CR2 register). In any case, the OCx and OCxN outputs cannot be set both to active level at a given time. Refer to Table 61: Output control bits for complementary OCx and OCxN channels with break feature on page 411 for more details.

The source for BRK can be:

- • An external source connected to the BKIN pin

- • An internal source: COMP4 output

The source for BRK_ACTH can be internal only:

- – A clock failure event generated by the CSS. For further information on the CSS, refer to Section 7.2.7: Clock security system (CSS)

- – A PVD output

- – Cortex®-M4F LOCKUP (Hardfault) output

- – COMPx output, x = (2, 6)

Caution: The internal sources protection is not available when the timer is in automatic output enable mode (AOE bit set in the TIMx_BDTR). The MOE bit is set again on the next update event, regardless of any pending error on the BRK_ACTH input.

The source for BRK2 can be:

- • An external source connected to the BKIN2 pin

- • An internal source coming from COMPx output, x = , 2, 4 or 6

If there are several break sources, the resulting break signal will be an OR between all the input signals.

When exiting from reset, the break circuit is disabled and the MOE bit is low. The break functions can be enabled by setting the BKE and BK2E bits in the TIMx_BDTR register. The break input polarities can be selected by configuring the BKP and BK2P bits in the same register. BKE/BK2E and BKP/BK2P can be modified at the same time. When the BKE/BK2E and BKP/BK2P bits are written, a delay of 1 APB clock cycle is applied before the writing is effective. Consequently, it is necessary to wait 1 APB clock period to correctly read back the bit after the write operation.

Because MOE falling edge can be asynchronous, a resynchronization circuit has been inserted between the actual signal (acting on the outputs) and the synchronous control bit (accessed in the TIMx_BDTR register). It results in some delays between the asynchronous and the synchronous signals. In particular, if MOE is set to 1 whereas it was low, a delay must be inserted (dummy instruction) before reading it correctly. This is because the write acts on the asynchronous signal whereas the read reflects the synchronous signal.

The break can be generated by any of the two break inputs (BRK, BRK2) and which has a:

- – Programmable polarity (BKP/BK2P bit in the TIMx_BDTR register)

- – Programmable enable bit (BKE/BK2E in the TIMx_BDTR register)

- – Programmable filter (BKxF[3:0] bits in the TIMx_BDTR register) to avoid spurious events.

The digital filter feature is available on BRK and BRK2. It is not available on BRK_ACTH.

That means that the digital filter is:

- • Available when the break source is external and comes from the external inputs BKIN/BKIN2.

- • Available when the break source is internal and connected to BRK (COMP4 output) or BRK2 (all comparators' outputs)

- • Not available when the break source is internal and connected to BRK_ACTH. (i.e. PVD output, Cortex®-M4F LOCKUP (Hardfault) output or COMPx output, x = 2, 6).

Break events can also be generated by software using BG and B2G bits in the TIMx_EGR register. The software break generation using BG and B2G is active whatever the BKE and BK2E enable bits values.

Note: An asynchronous (clockless) operation is only guaranteed when the programmable filter is disabled. If it is enabled, a fail safe clock mode (for example by using the internal PLL and/or the CSS) must be used to guarantee that break events are handled.

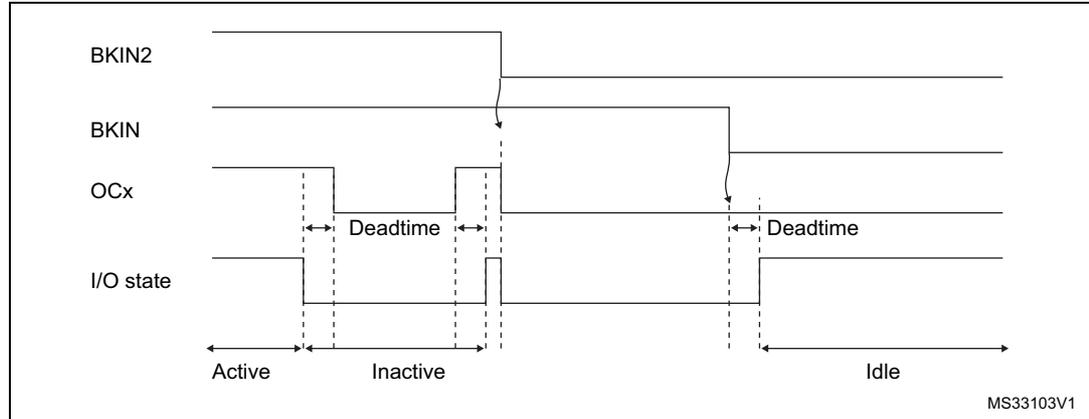

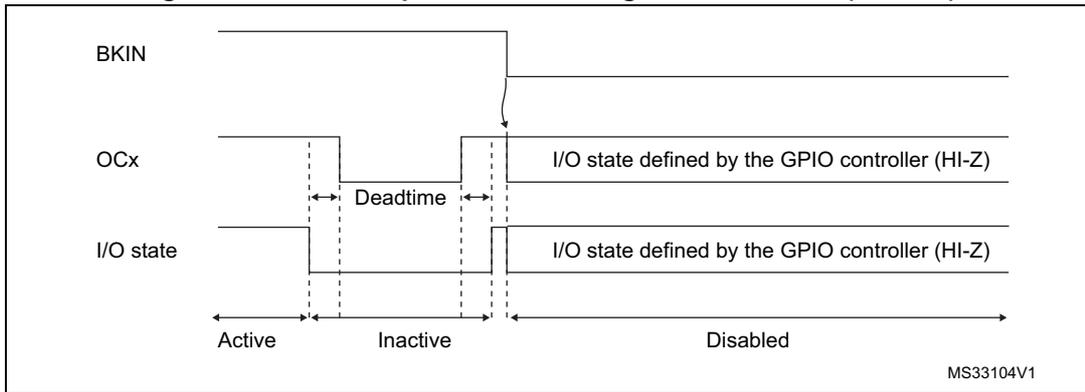

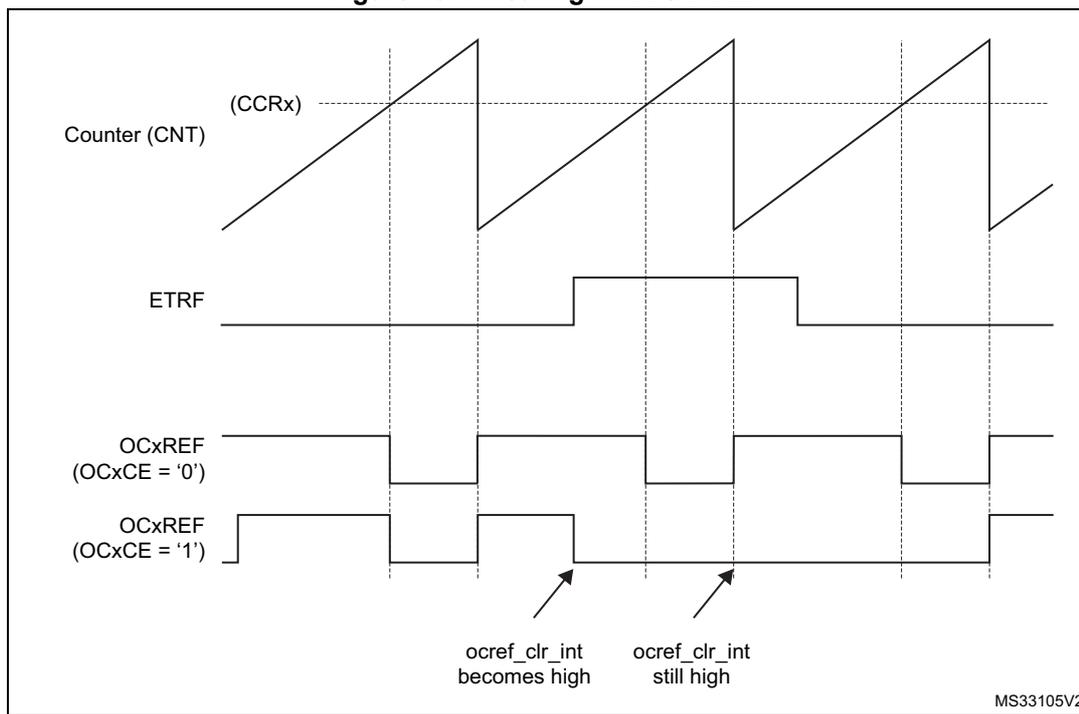

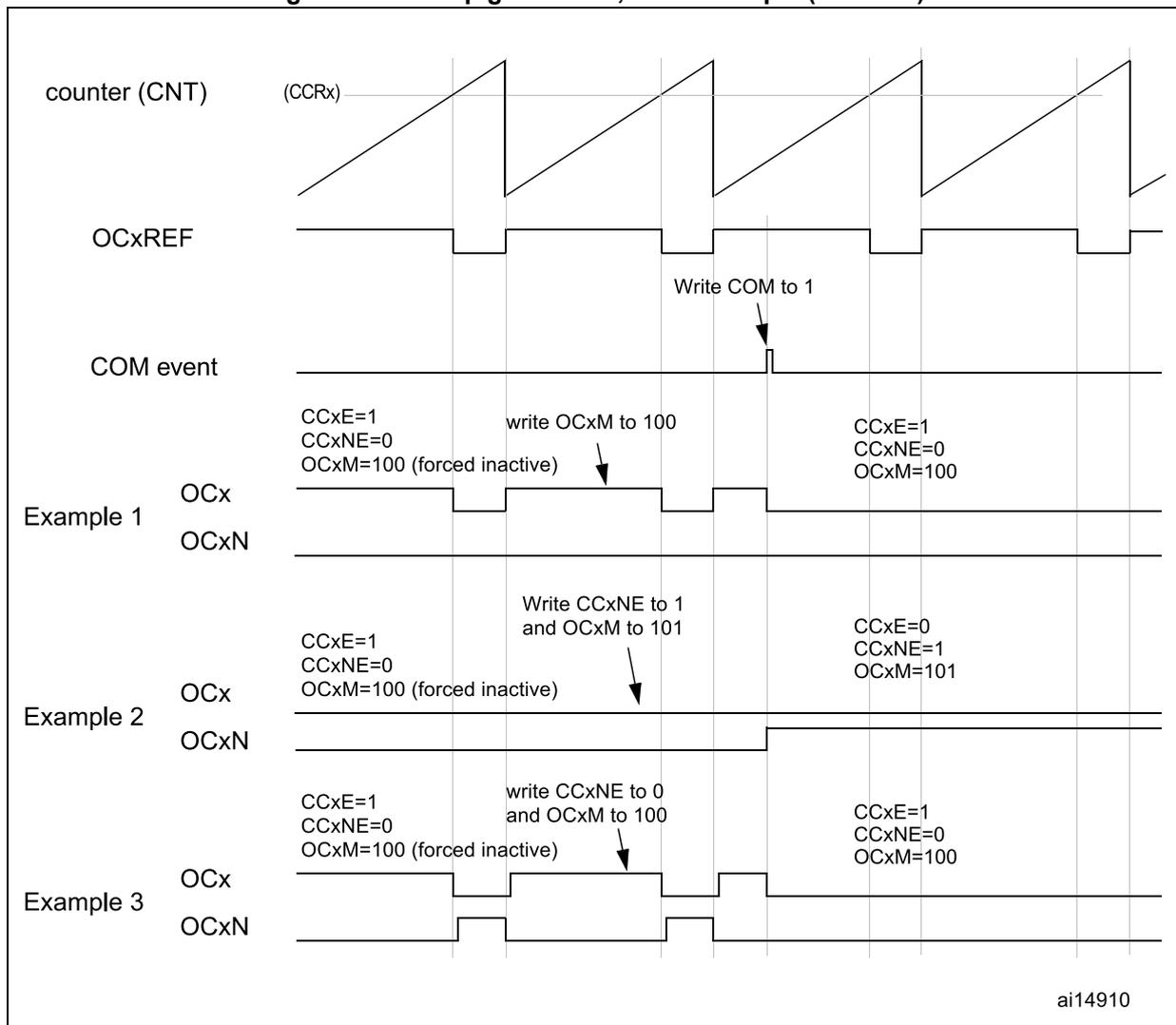

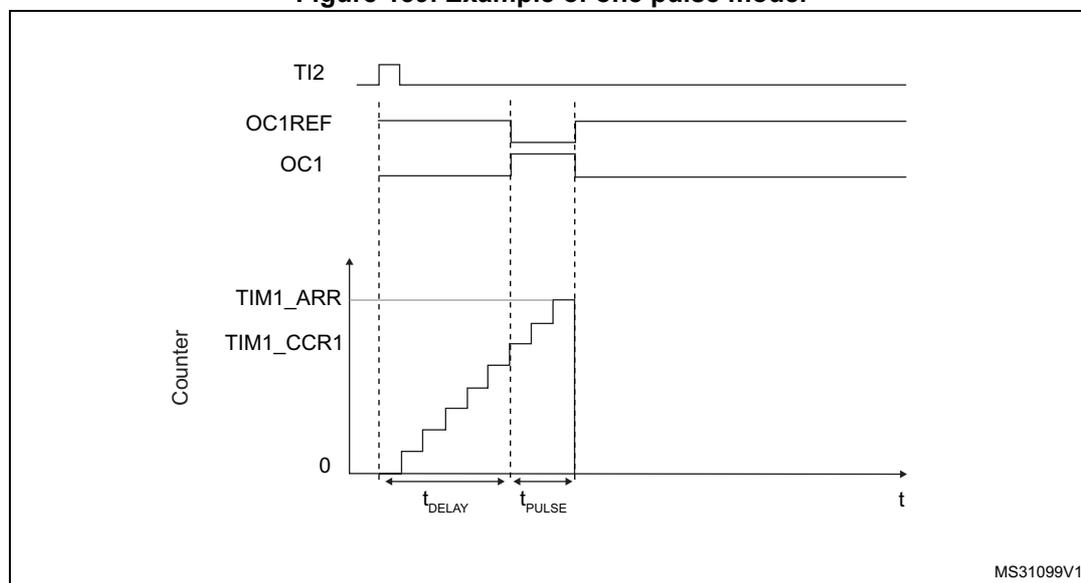

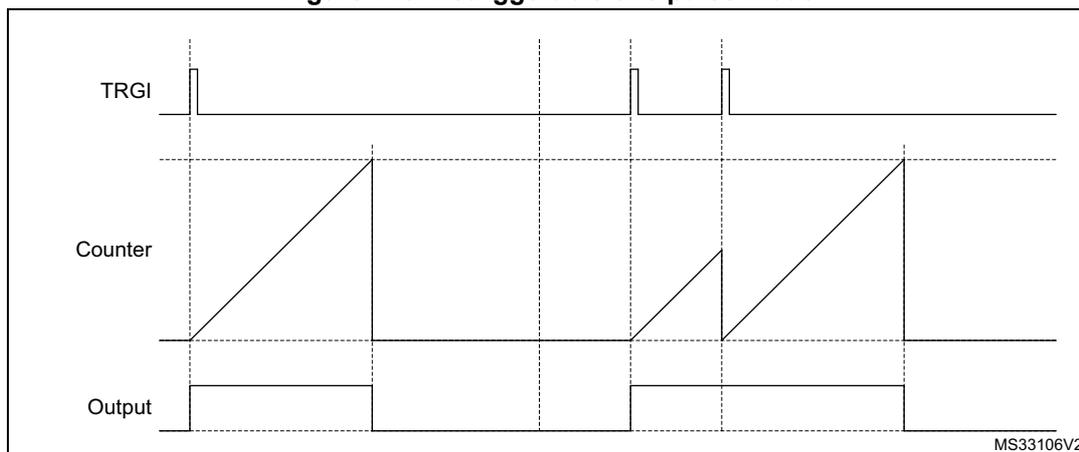

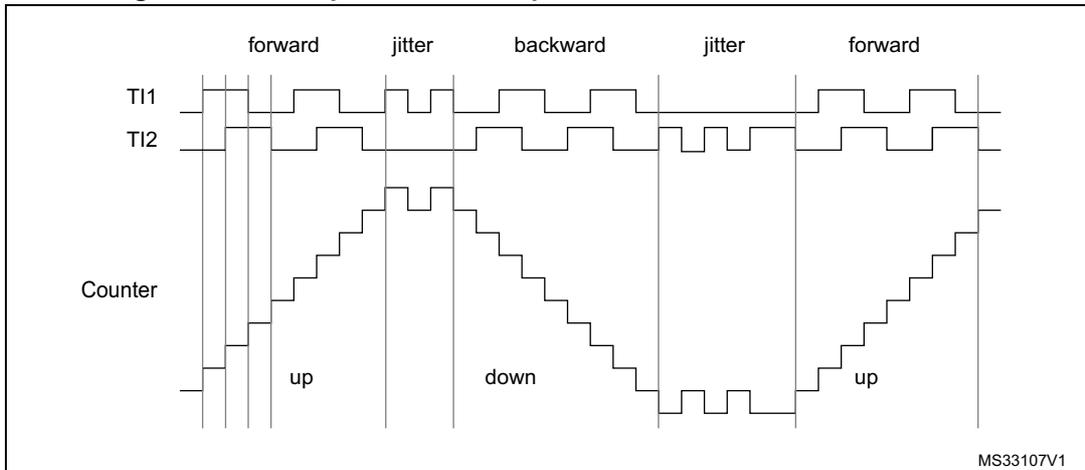

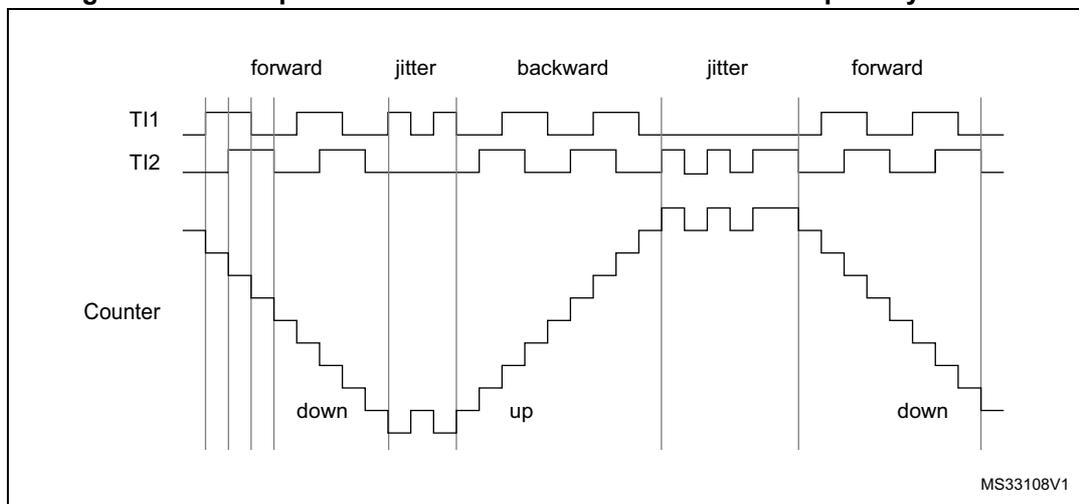

When one of the breaks occurs (selected level on one of the break inputs):