28. Inter-integrated circuit interface (I2C)

28.1 Introduction

The I2C peripheral handles the interface between the device and the serial I 2 C (inter-integrated circuit) bus. It provides multimaster capability, and controls all I 2 C-bus-specific sequencing, protocol, arbitration and timing. It supports Standard-mode (Sm), Fast-mode (Fm) and Fast-mode Plus (Fm+).

The I2C peripheral is also SMBus (system management bus) and PMBus ® (power management bus) compatible.

It can use DMA to reduce the CPU load.

28.2 I2C main features

- • I

2

C-bus specification rev03 compatibility:

- – Slave and master modes

- – Multimaster capability

- – Standard-mode (up to 100 kHz)

- – Fast-mode (up to 400 kHz)

- – Fast-mode Plus (up to 1 MHz)

- – 7-bit and 10-bit addressing mode

- – Multiple 7-bit slave addresses (2 addresses, 1 with configurable mask)

- – All 7-bit-addresses acknowledge mode

- – General call

- – Programmable setup and hold times

- – Easy-to-use event management

- – Clock stretching (optional)

- • 1-byte buffer with DMA capability

- • Programmable analog and digital noise filters

- • SMBus specification rev 3.0 compatibility:

- – Hardware PEC (packet error checking) generation and verification with ACK control

- – Command and data acknowledge control

- – Address resolution protocol (ARP) support

- – Host and device support

- – SMBus alert

- – Timeouts and idle condition detection

- • PMBus rev 1.3 standard compatibility

- • Independent clock

- • Wake-up from Stop mode on address match

For information on I2C instantiation, refer to Section 28.3: I2C implementation .

28.3 I2C implementation

This section provides an implementation overview with respect to the I2C instantiation.

Table 142. I2C implementation

| I2C features (1) | I2C1 | I2C2 (2) | I2C3 (3) |

|---|---|---|---|

| 7-bit addressing mode | X | X | X |

| 10-bit addressing mode | X | X | X |

| Standard-mode (up to 100 kbit/s) | X | X | X |

| Fast-mode (up to 400 kbit/s) | X | X | X |

| Fast-mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | X | X | X |

| Independent clock | X | X | X |

| Wake-up from Stop mode | X | X | X |

| SMBus/PMBus | X | X | X |

1. X = supported.

2. I2C2 is not available on STM32F303x6/x8 and STM32F328x8.

3. I2C3 is available on STM32F303xD/xE and STM32F398xE only.

28.4 I2C functional description

In addition to receiving and transmitting data, the peripheral converts them from serial to parallel format and vice versa. The interrupts are enabled or disabled by software. The peripheral is connected to the I 2 C-bus through a data pin (SDA) and a clock pin (SCL). It supports Standard-mode (up to 100 kHz), Fast-mode (up to 400 kHz), and Fast-mode Plus (up to 1 MHz) I 2 C-bus.

The peripheral can also be connected to an SMBus, through the data pin (SDA), the clock pin (SCL), and an optional SMBus alert pin (SMBA).

The independent clock function allows the I2C communication speed to be independent of the PCLK1 frequency.

For I2C I/Os supporting 20 mA output current drive for Fast-mode Plus operation, the driving capability is enabled through control bits in the system configuration controller (SYSCFG).

28.4.1 I2C block diagram

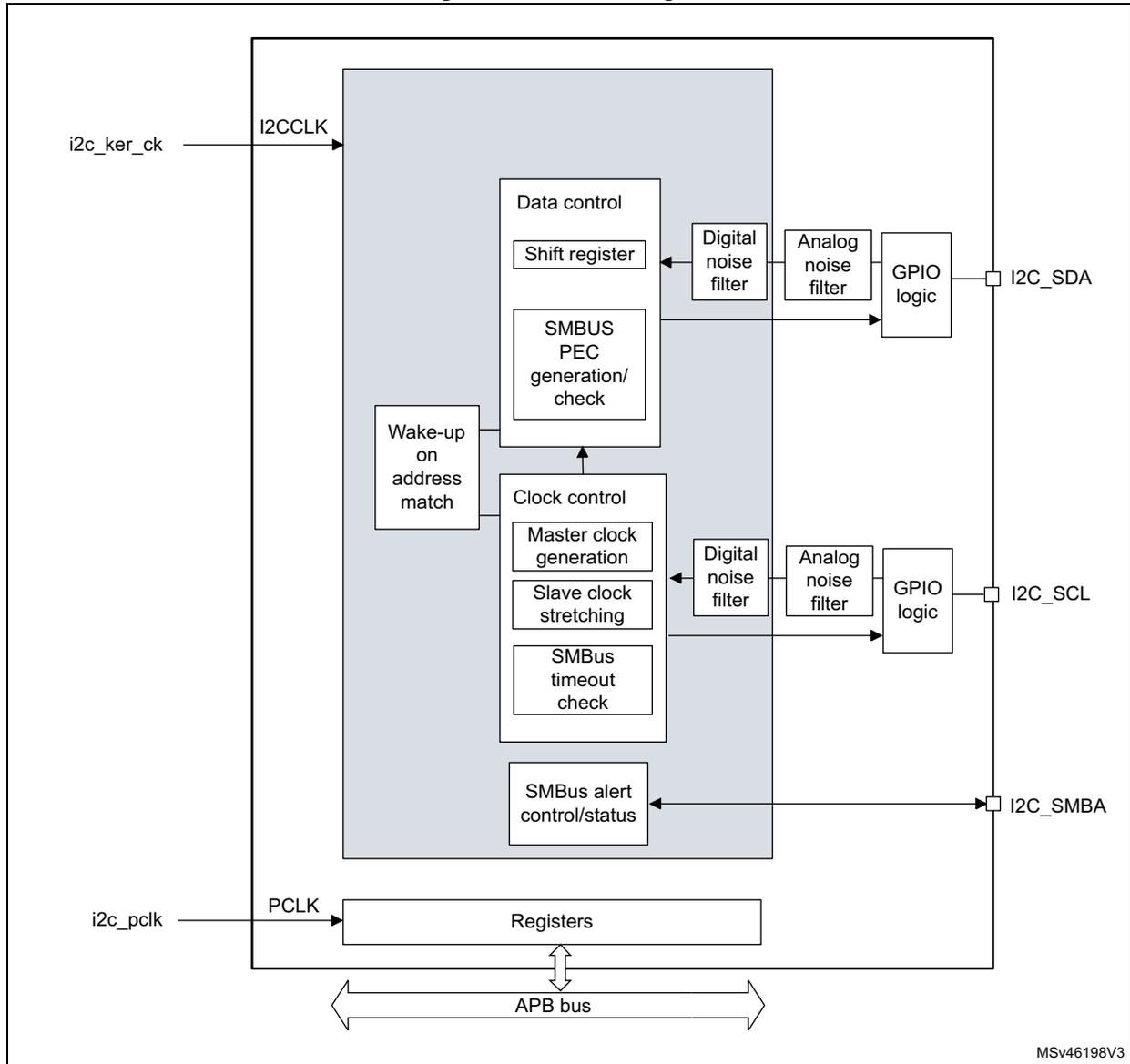

Figure 295. Block diagram

The block diagram illustrates the internal architecture of the I2C interface. On the left, external signals i2c_ker_ck and PCLK are inputs. i2c_ker_ck connects to the I2CCLK pin and feeds into the Data control and Clock control blocks. PCLK connects to the PCLK pin and feeds into the Registers block. The Registers block is connected to an APB bus . The Data control block contains a Shift register and SMBUS PEC generation/check . The Clock control block contains Master clock generation , Slave clock stretching , and SMBus timeout check . A Wake-up on address match block is also present. The SMBus alert control/status block is connected to the I2C_SMBA pin. The I2C_SDA and I2C_SCL pins are connected to GPIO logic blocks, which are preceded by Analog noise filter and Digital noise filter blocks. The Digital noise filter for SDA is connected to the Shift register , and for SCL to the Slave clock stretching block. The diagram is labeled MSV46198V3 in the bottom right corner.

28.4.2 I2C pins and internal signals

Table 143. I2C input/output pins

| Pin name | Signal type | Description |

|---|---|---|

| I2C_SDA | Bidirectional | I 2 C-bus data |

| I2C_SCL | Bidirectional | I 2 C-bus clock |

| I2C_SMBA | Bidirectional | SMBus alert |

Table 144. I2C internal input/output signals

| Internal signal name | Signal type | Description |

|---|---|---|

| i2c_ker_ck | Input | I2C kernel clock, also named I2CCLK in this document |

| i2c_pclk | Input | I2C APB clock |

| i2c_it | Output | I2C interrupts, refer to Table 158 for the list of interrupt sources |

| i2c_rx_dma | Output | I2C receive data DMA request (I2C_RX) |

| i2c_tx_dma | Output | I2C transmit data DMA request (I2C_TX) |

28.4.3 I2C clock requirements

The I2C kernel is clocked by I2CCLK.

The I2CCLK period \( t_{I2CCLK} \) must respect the following conditions:

where \( t_{LOW} \) is the SCL low time, \( t_{HIGH} \) is the SCL high time, and \( t_{filters} \) is the sum of the analog and digital filter delays (when enabled).

The digital filter delay is \( DNF[3:0] \times t_{I2CCLK} \) .

The PCLK1 clock period \( t_{PCLK} \) must respect the condition \( t_{PCLK} < 4/3 t_{SCL} \) , where \( t_{SCL} \) is the SCL period.

Caution: When the I2C kernel is clocked by PCLK1, this clock must respect the conditions for \( t_{I2CCLK} \) .

28.4.4 Mode selection

The peripheral can operate as:

- • slave transmitter

- • slave receiver

- • master transmitter

- • master receiver

By default, the peripheral operates in slave mode. It automatically switches from slave to master mode upon generating START condition, and from master to slave mode upon arbitration loss or upon generating STOP condition. This allows the use of the I2C peripheral in a multimaster I 2 C-bus environment.

Communication flow

In master mode, the I2C peripheral initiates a data transfer and generates the clock signal. Serial data transfers always begin with a START condition and end with a STOP condition. Both START and STOP conditions are generated in master mode by software.

In slave mode, the peripheral recognizes its own 7-bit or 10-bit address, and the general call address. The general call address detection can be enabled or disabled by software. The reserved SMBus addresses can also be enabled by software.

Data and addresses are transferred as 8-bit bytes, MSB first. The first one (7-bit addressing) or two (10-bit addressing) bytes following the START condition contain the address. The address is always transmitted in master mode.

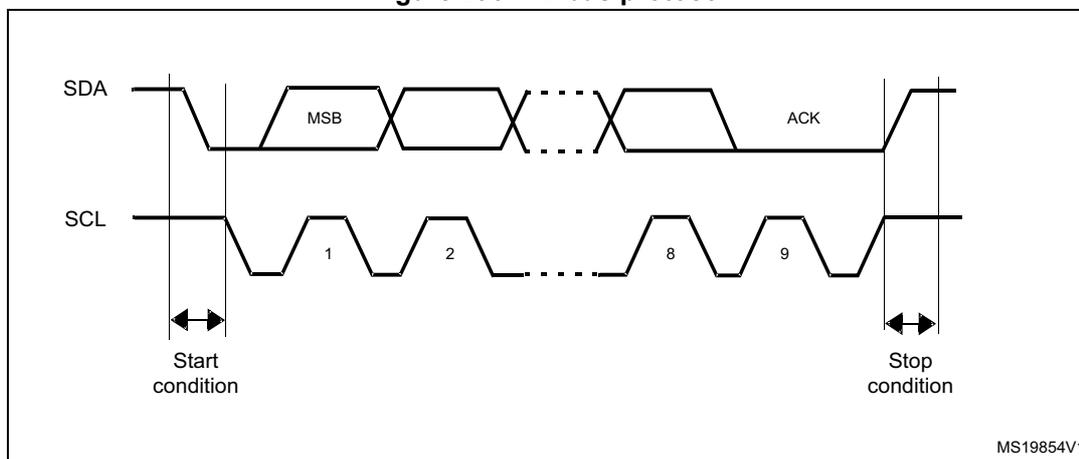

The following figure shows the transmission of a single byte. The master generates nine SCL pulses. The transmitter sends the eight data bits to the receiver with the SCL pulses 1 to 8. Then the receiver sends the acknowledge bit to the transmitter with the ninth SCL pulse.

Figure 296. I 2 C-bus protocol

The acknowledge can be enabled or disabled by software. The own addresses of the I2C peripheral can be selected by software.

28.4.5 I2C initialization

Enabling and disabling the peripheral

Before enabling the I2C peripheral, configure and enable its clock through the clock controller, and initialize its control registers.

The I2C peripheral can then be enabled by setting the PE bit of the I2C_CR1 register.

Disabling the I2C peripheral by clearing the PE bit resets the I2C peripheral. Refer to Section 28.4.6 for more details.

Noise filters

Before enabling the I2C peripheral by setting the PE bit of the I2C_CR1 register, the user must configure the analog and/or digital noise filters, as required.

The analog noise filter on the SDA and SCL inputs complies with the I 2 C-bus specification which requires, in Fast-mode and Fast-mode Plus, the suppression of spikes shorter than 50 ns. Enabled by default, it can be disabled by setting the ANFOFF bit.

The digital filter is controlled through the DNF[3:0] bitfield of the I2C_CR1 register. When it is enabled, the internal SCL and SDA signals only take the level of their corresponding I 2 C-bus line when remaining stable for more than DNF[3:0] periods of I2CCLK. This allows suppressing spikes shorter than the filtering capacity period programmable from one to fifteen I2CCLK periods.

The following table compares the two filters.

Table 145. Comparison of analog and digital filters| Item | Analog filter | Digital filter |

|---|---|---|

| Filtering capacity (1) | ≥ 50 ns | One to fifteen I2CCLK periods |

| Benefits | Available in Stop mode |

|

| Drawbacks | Filtering capacity variation with temperature, voltage, and silicon process | Wake-up from Stop mode on address match not supported when the digital filter is enabled |

1. Maximum duration of spikes that the filter can suppress

Caution: The filter configuration cannot be changed when the I2C peripheral is enabled.

I2C timings

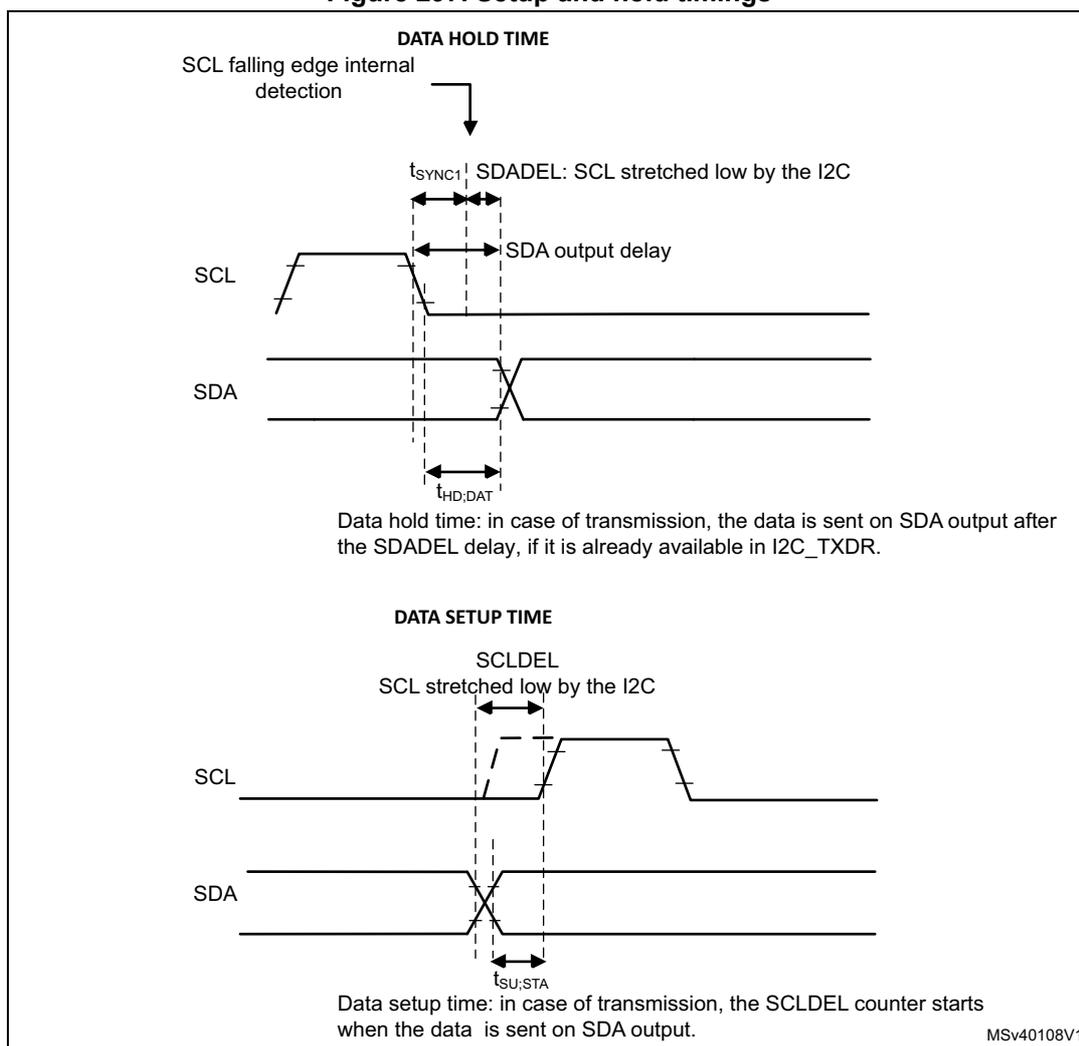

To ensure correct data hold and setup times, the corresponding timings must be configured through the PRESC[3:0], SCLDEL[3:0], and SDADEL[3:0] bitfields of the I2C_TIMINGR register.

The STM32CubeMX tool calculates and provides the I2C_TIMINGR content in the I2C configuration window.

Figure 297. Setup and hold timings

When the SCL falling edge is internally detected, the delay \( t_{SDADEL} \) (impacting the hold time \( t_{HD;DAT} \) ) is inserted before sending SDA output:

The total SDA output delay is:

The \( t_{SYNC1} \) duration depends upon:

- • SCL falling slope

- • input delay \( t_{AF(min)} < t_{AF} < t_{AF(max)} \) introduced by the analog filter (if enabled)

- • input delay \( t_{DNF} = DNF \times t_{I2CCLK} \) introduced by the digital filter (if enabled)

- • delay due to SCL synchronization to I2CCLK clock (two to three I2CCLK periods)

To bridge the undefined region of the SCL falling edge, the user must set SDADEL[3:0] so as to fulfill the following condition:

Note: \( t_{AF(min)} \) and \( t_{AF(max)} \) are only part of the condition when the analog filter is enabled. Refer to the device datasheet for \( t_{AF} \) values.

The \( t_{HD;DAT} \) time can at maximum be 3.45 µs for Standard-mode, 0.9 µs for Fast-mode, and 0.45 µs for Fast-mode Plus. It must be lower than the maximum of \( t_{VD;DAT} \) by a transition time. This maximum must only be met if the device does not stretch the LOW period ( \( t_{LOW} \) ) of the SCL signal. When it stretches SCL, the data must be valid by the set-up time before it releases the clock.

The SDA rising edge is usually the worst case. The previous condition then becomes:

Note: This condition can be violated when \( NOSTRETCH = 0 \) , because the device stretches SCL low to guarantee the set-up time, according to the \( SCLDEL[3:0] \) value.

After \( t_{SDADEL} \) , or after sending SDA output when the slave had to stretch the clock because the data was not yet written in \( I2C\_TXDR \) register, the SCL line is kept at low level during the setup time. This setup time is \( t_{SCLDEL} = (SCLDEL + 1) \times t_{PRESC} \) , where \( t_{PRESC} = (PRESC + 1) \times t_{I2CCLK} \) . \( t_{SCLDEL} \) impacts the setup time \( t_{SU;DAT} \) .

To bridge the undefined region of the SDA transition (rising edge usually worst case), the user must program \( SCLDEL[3:0] \) so as to fulfill the following condition:

Refer to the following table for \( t_f \) , \( t_r \) , \( t_{HD;DAT} \) , \( t_{VD;DAT} \) , and \( t_{SU;DAT} \) standard values.

Use the SDA and SCL real transition time values measured in the application to widen the scope of allowed \( SDADEL[3:0] \) and \( SCLDEL[3:0] \) values. Use the maximum SDA and SCL transition time values defined in the standard to make the device work reliably regardless of the application.

Note: At every clock pulse, after SCL falling edge detection, I2C operating as master or slave stretches SCL low during at least \( [(SDADEL + SCLDEL + 1) \times (PRESC + 1) + 1] \times t_{I2CCLK} \) , in both transmission and reception modes. In transmission mode, if the data is not yet written in \( I2C\_TXDR \) when SDA delay elapses, the I2C peripheral keeps stretching SCL low until the next data is written. Then new data MSB is sent on SDA output, and \( SCLDEL \) counter starts, continuing stretching SCL low to guarantee the data setup time.

When the \( NOSTRETCH \) bit is set in slave mode, the SCL is not stretched. The \( SDADEL[3:0] \) must then be programmed so that it ensures a sufficient setup time.

Table 146. I 2 C-bus and SMBus specification data setup and hold times

| Symbol | Parameter | Standard-mode (Sm) | Fast-mode (Fm) | Fast-mode Plus (Fm+) | SMBus | Unit | ||||

|---|---|---|---|---|---|---|---|---|---|---|

| Min | Max | Min | Max | Min | Max | Min | Max | |||

| \( t_{HD;DAT} \) | Data hold time | 0 | - | 0 | - | 0 | - | 0.3 | - | µs |

| \( t_{VD;DAT} \) | Data valid time | - | 3.45 | - | 0.9 | - | 0.45 | - | - | |

| \( t_{SU;DAT} \) | Data setup time | 250 | - | 100 | - | 50 | - | 250 | - | ns |

| \( t_r \) | Rise time of both SDA and SCL signals | - | 1000 | - | 300 | - | 120 | - | 1000 | |

| \( t_f \) | Fall time of both SDA and SCL signals | - | 300 | - | 300 | - | 120 | - | 300 | |

Additionally, in master mode, the SCL clock high and low levels must be configured by programming the PRESC[3:0], SCLH[7:0], and SCLL[7:0] bitfields of the I2C_TIMINGR register.

When the SCL falling edge is internally detected, the I2C peripheral releasing the SCL output after the delay \( t_{SCLL} = (SCLL + 1) \times t_{PRESCL} \) , where \( t_{PRESCL} = (PRESC + 1) \times t_{I2CCLK} \) . The \( t_{SCLL} \) delay impacts the SCL low time \( t_{LOW} \) .

When the SCL rising edge is internally detected, the I2C peripheral forces the SCL output to low level after the delay \( t_{SCLH} = (SCLH + 1) \times t_{PRESCL} \) , where \( t_{PRESCL} = (PRESC + 1) \times t_{I2CCLK} \) . The \( t_{SCLH} \) impacts the SCL high time \( t_{HIGH} \) .

Refer to I2C master initialization for more details.

Caution: Changing the timing configuration and the NOSTRETCH configuration is not allowed when the I2C peripheral is enabled. Like the timing settings, the slave NOSTRETCH settings must also be done before enabling the peripheral. Refer to I2C slave initialization for more details.

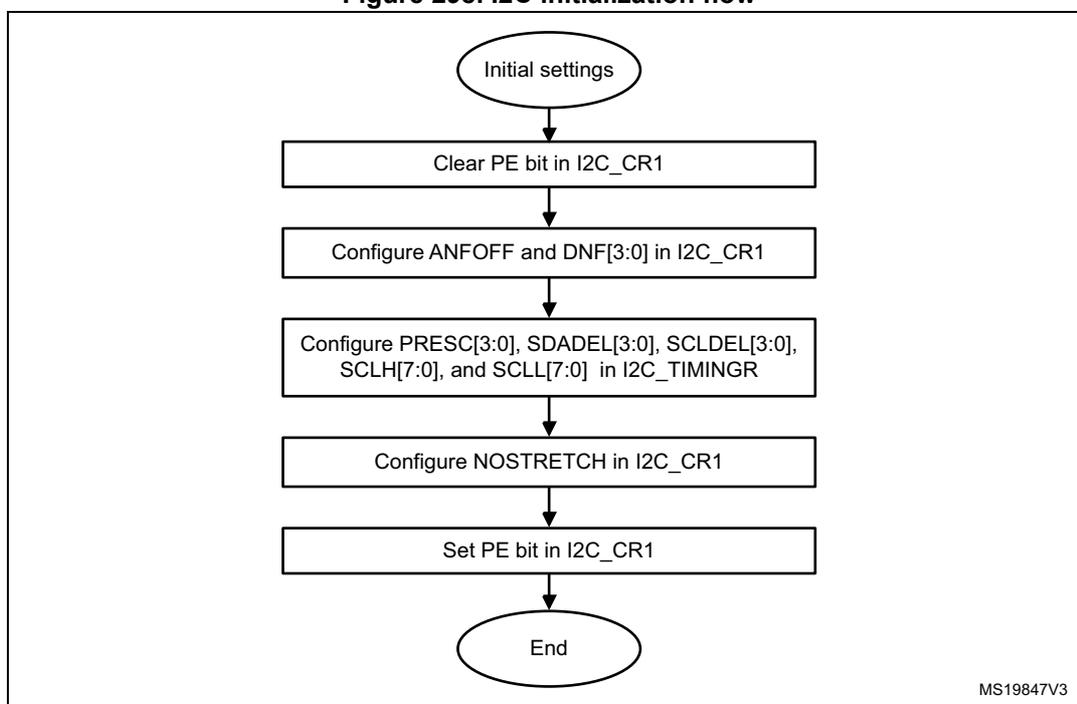

Figure 298. I2C initialization flow

graph TD; A([Initial settings]) --> B[Clear PE bit in I2C_CR1]; B --> C[Configure ANFOFF and DNF[3:0] in I2C_CR1]; C --> D["Configure PRESC[3:0], SDADEL[3:0], SCLDEL[3:0], SCLH[7:0], and SCLL[7:0] in I2C_TIMINGR"]; D --> E[Configure NOSTRETCH in I2C_CR1]; E --> F[Set PE bit in I2C_CR1]; F --> G([End]);

The flowchart illustrates the I2C initialization process. It begins with 'Initial settings' (oval), followed by 'Clear PE bit in I2C_CR1' (rectangle), 'Configure ANFOFF and DNF[3:0] in I2C_CR1' (rectangle), 'Configure PRESC[3:0], SDADEL[3:0], SCLDEL[3:0], SCLH[7:0], and SCLL[7:0] in I2C_TIMINGR' (rectangle), 'Configure NOSTRETCH in I2C_CR1' (rectangle), and 'Set PE bit in I2C_CR1' (rectangle), ending with 'End' (oval). The steps are connected by downward arrows. The identifier MS19847V3 is located in the bottom right corner of the diagram area.

28.4.6 I2C reset

The reset of the I2C peripheral is performed by clearing the PE bit of the I2C_CR1 register. It has the effect of releasing the SCL and SDA lines. Internal state machines are reset and the communication control bits and the status bits revert to their reset values. This reset does not impact the configuration registers.

The impacted register bits are:

- 1. I2C_CR2 register: START, STOP, PECBYTE, and NACK

- 2. I2C_ISR register: BUSY, TXE, TXIS, RXNE, ADDR, NACKF, TCR, TC, STOPF, BERR, ARLO, PECERR, TIMEOUT, ALERT, and OVR

PE must be kept low during at least three APB clock cycles to perform the I2C reset. To ensure this, perform the following software sequence:

- 1. Write PE = 0

- 2. Check PE = 0

- 3. Write PE = 1

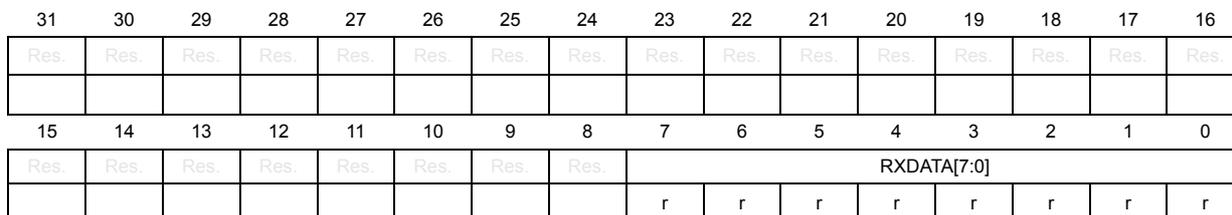

28.4.7 Data transfer

The data transfer is managed through transmit and receive data registers and a shift register.

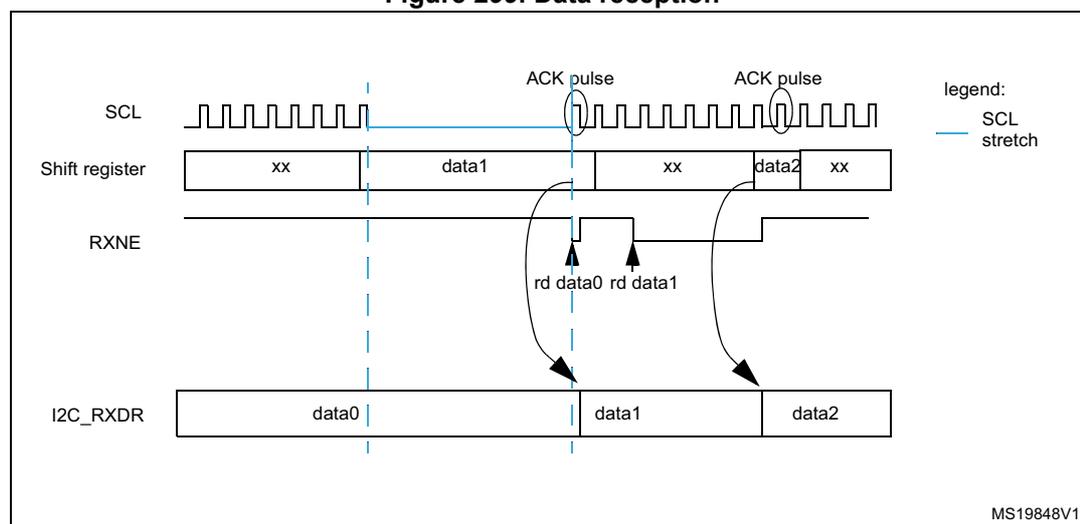

Reception

The SDA input fills the shift register. After the eighth SCL pulse (when the complete data byte is received), the shift register is copied into the I2C_RXDR register if it is empty (RXNE = 0). If RXNE = 1, which means that the previous received data byte has not yet been read, the SCL line is stretched low until I2C_RXDR is read. The stretch occurs between the eighth and ninth SCL pulse (before the acknowledge pulse).

Figure 299. Data reception

The diagram illustrates the timing for data reception in an I2C interface. It shows four horizontal timelines: SCL (Serial Clock Line), Shift register, RXNE (Receive Not Empty flag), and I2C_RXDR (Receive Data Register).

- SCL: Shows a series of clock pulses. Two "ACK pulse" labels with circles are placed after the eighth and ninth pulses. A blue horizontal line indicates an "SCL stretch" (SCL held low) between the eighth and ninth pulses.

- Shift register: A horizontal bar divided into five cells. The first cell contains "xx". The second cell contains "data1". The third cell contains "xx". The fourth cell contains "data2". The fifth cell contains "xx". Vertical dashed lines align the boundaries of these cells with the SCL pulses.

- RXNE: A signal line that goes high after the eighth SCL pulse and returns low when the data is read from I2C_RXDR. Two arrows labeled "rd data0" and "rd data1" point from the RXNE high state to the I2C_RXDR register.

- I2C_RXDR: A horizontal bar divided into three cells containing "data0", "data1", and "data2".

Arrows indicate the flow of data: from the Shift register to the I2C_RXDR register, and from the I2C_RXDR register to the RXNE signal. A legend on the right shows a blue line segment labeled "SCL stretch". The diagram is identified by the code MS19848V1 in the bottom right corner.

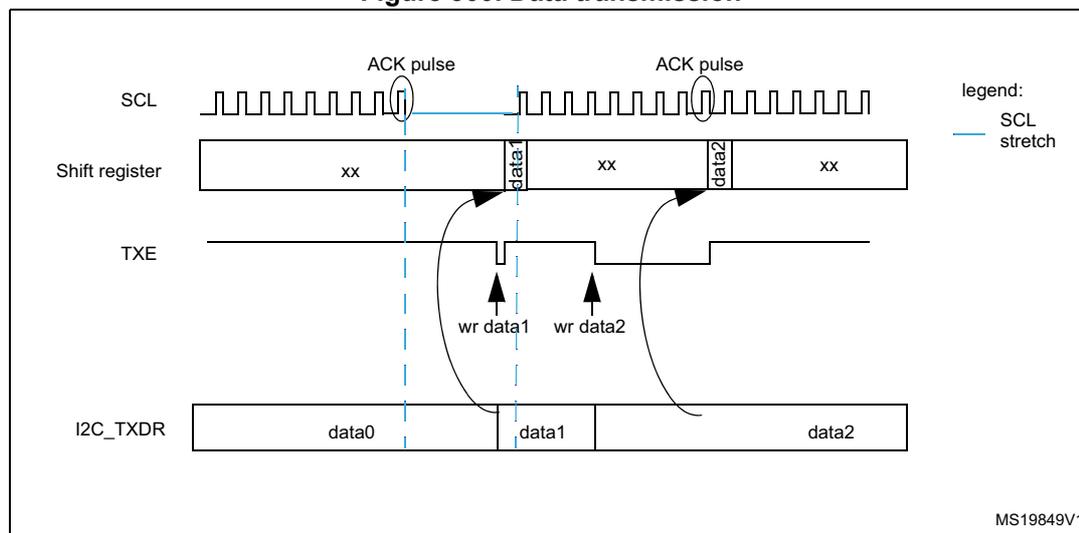

Transmission

If the I2C_TXDR register is not empty (TXE = 0), its content is copied into the shift register after the ninth SCL pulse (the acknowledge pulse). Then the shift register content is shifted out on the SDA line. If TXE = 1, which means that no data is written yet in I2C_TXDR, the SCL line is stretched low until I2C_TXDR is written. The stretch starts after the ninth SCL pulse.

Figure 300. Data transmission

The diagram illustrates the I2C transmission sequence:

- SCL: Shows clock pulses. A blue horizontal line indicates an SCL stretch occurring during the ACK pulse when TXE=1.

- Shift register: Shows data being shifted. It transitions from 'xx' to 'data1' (loaded from I2C_TXDR) and then to 'data2'.

- TXE (Transmit data register empty): This flag goes high (1) when the I2C_TXDR content is transferred to the shift register. It is cleared (0) when new data is written to I2C_TXDR.

- I2C_TXDR: Shows the buffer containing 'data0', then 'data1' after 'wr data1', and 'data2' after 'wr data2'.

- Arrows: Indicate the transfer of data from I2C_TXDR to the Shift register and the timing of write operations ('wr data1', 'wr data2') relative to the TXE flag.

legend:

—

SCL stretch

MS19849V1

Hardware transfer management

The I2C features an embedded byte counter to manage byte transfer and to close the communication in various modes, such as:

- – NACK, STOP and ReSTART generation in master mode

- – ACK control in slave receiver mode

- – PEC generation/checking

In master mode, the byte counter is always used. By default, it is disabled in slave mode. It can be enabled by software, by setting the SBC (slave byte control) bit of the I2C_CR1 register.

The number of bytes to transfer is programmed in the NBYTES[7:0] bitfield of the I2C_CR2 register. If this number is greater than 255, or if a receiver wants to control the acknowledge value of a received data byte, the reload mode must be selected, by setting the RELOAD bit of the I2C_CR2 register. In this mode, the TCR flag is set when the number of bytes programmed in NBYTES[7:0] is transferred (when the associated counter reaches zero), and an interrupt is generated if TCIE is set. SCL is stretched as long as the TCR flag is set. TCR is cleared by software when NBYTES[7:0] is written to a non-zero value.

When NBYTES[7:0] is reloaded with the last number of bytes to transfer, the RELOAD bit must be cleared.

When RELOAD = 0 in master mode, the counter can be used in two modes:

- • Automatic end (AUTOEND = 1 in the I2C_CR2 register). In this mode, the master automatically sends a STOP condition once the number of bytes programmed in the NBBYTES[7:0] bitfield is transferred.

- • Software end (AUTOEND = 0 in the I2C_CR2 register). In this mode, software action is expected once the number of bytes programmed in the NBBYTES[7:0] bitfield is transferred; the TC flag is set and an interrupt is generated if the TCIE bit is set. The SCL signal is stretched as long as the TC flag is set. The TC flag is cleared by software when the START or STOP bit of the I2C_CR2 register is set. This mode must be used when the master wants to send a RESTART condition.

Caution: The AUTOEND bit has no effect when the RELOAD bit is set.

Table 147. I2C configuration

| Function | SBC bit | RELOAD bit | AUTOEND bit |

|---|---|---|---|

| Master Tx/Rx NBBYTES + STOP | X | 0 | 1 |

| Master Tx/Rx + NBBYTES + RESTART | X | 0 | 0 |

| Slave Tx/Rx, all received bytes ACKed | 0 | X | X |

| Slave Rx with ACK control | 1 | 1 | X |

28.4.8 I2C slave mode

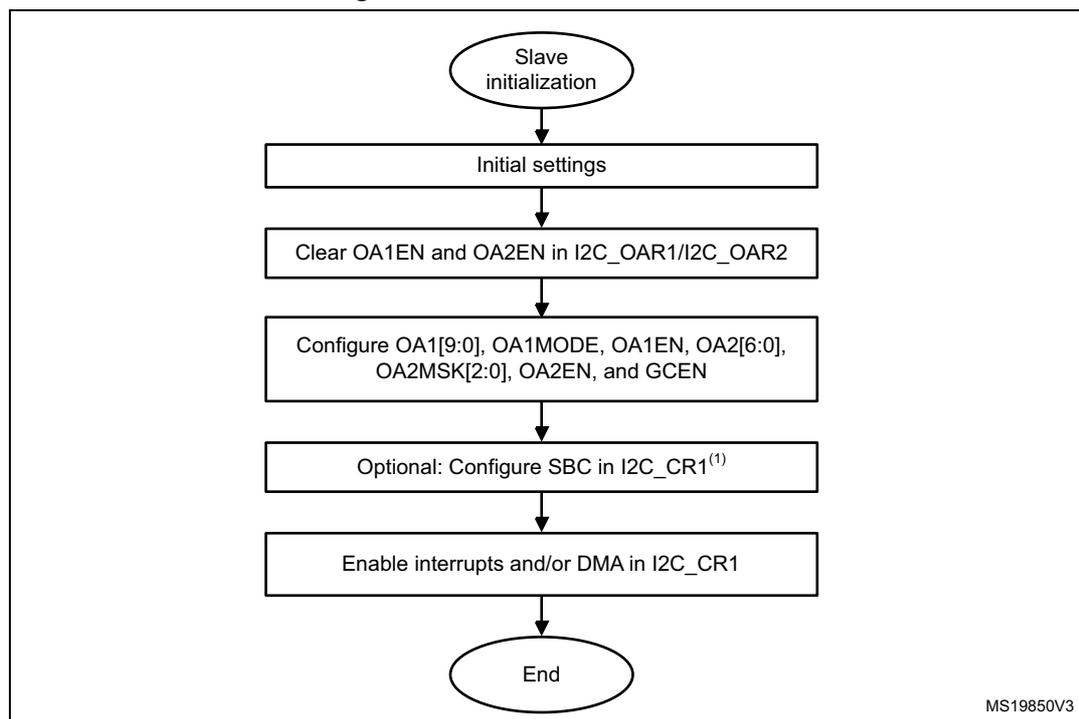

I2C slave initialization

To work in slave mode, the user must enable at least one slave address. The I2C_OAR1 and I2C_OAR2 registers are available to program the slave own addresses OA1 and OA2, respectively.

OA1 can be configured either in 7-bit (default) or in 10-bit addressing mode, by setting the OA1MODE bit of the I2C_OAR1 register.

OA1 is enabled by setting the OA1EN bit of the I2C_OAR1 register.

If an additional slave addresses are required, the second slave address OA2 can be configured. Up to seven OA2 LSBs can be masked, by configuring the OA2MSK[2:0] bitfield of the I2C_OAR2 register. Therefore, for OA2MSK[2:0] configured from 1 to 6, only OA2[7:2], OA2[7:3], OA2[7:4], OA2[7:5], OA2[7:6], or OA2[7] are compared with the received address. When OA2MSK[2:0] is other than 0, the address comparator for OA2 excludes the I2C reserved addresses (0000 XXX and 1111 XXX) and they are not acknowledged. If OA2MSK[2:0] = 7, all received 7-bit addresses are acknowledged (except reserved addresses). OA2 is always a 7-bit address.

When enabled through the specific bit, the reserved addresses can be acknowledged if they are programmed in the I2C_OAR1 or I2C_OAR2 register with OA2MSK[2:0] = 0.

OA2 is enabled by setting the OA2EN bit of the I2C_OAR2 register.

The general call address is enabled by setting the GCEN bit of the I2C_CR1 register.

When the I2C peripheral is selected by one of its enabled addresses, the ADDR interrupt status flag is set, and an interrupt is generated if the ADDRIE bit is set.

By default, the slave uses its clock stretching capability, which means that it stretches the SCL signal at low level when required, to perform software actions. If the master does not

support clock stretching, I2C must be configured with NOSTRETCH = 1 in the I2C_CR1 register.

After receiving an ADDR interrupt, if several addresses are enabled, the user must read the ADDCODE[6:0] bitfield of the I2C_ISR register to check which address matched. The DIR flag must also be checked to know the transfer direction.

Slave with clock stretching

As long as the NOSTRETCH bit of the I2C_CR1 register is zero (default), the I2C peripheral operating as an I 2 C-bus slave stretches the SCL signal in the following situations:

- • The ADDR flag is set and the received address matches with one of the enabled slave addresses.

The stretch is released when the software clears the ADDR flag by setting the ADDRCF bit. - • In transmission, the previous data transmission is completed and no new data is written in I2C_TXDR register, or the first data byte is not written when the ADDR flag is cleared (TXE = 1).

The stretch is released when the data is written to the I2C_TXDR register. - • In reception, the I2C_RXDR register is not read yet and a new data reception is completed.

The stretch is released when I2C_RXDR is read. - • In slave byte control mode (SBC bit set) with reload (RELOAD bit set), the last data byte transfer is finished (TCR bit set).

The stretch is released when the TCR is cleared by writing a non-zero value in the NBBYTES[7:0] bitfield. - • After SCL falling edge detection.

The stretch is released after \( [(SDADEL + SCLDEL + 1) \times (PRESC + 1) + 1] \times t_{I2CCLK} \) period.

Slave without clock stretching

As long as the NOSTRETCH bit of the I2C_CR1 register is set, the I2C peripheral operating as an I 2 C-bus slave does not stretch the SCL signal.

The SCL clock is not stretched while the ADDR flag is set.

In transmission, the data must be written in the I2C_TXDR register before the first SCL pulse corresponding to its transfer occurs. If not, an underrun occurs, the OVR flag is set in the I2C_ISR register and an interrupt is generated if the ERRIE bit of the I2C_CR1 register is set. The OVR flag is also set when the first data transmission starts and the STOPF bit is still set (has not been cleared). Therefore, if the user clears the STOPF flag of the previous transfer only after writing the first data to be transmitted in the next transfer, it ensures that the OVR status is provided, even for the first data to be transmitted.

In reception, the data must be read from the I2C_RXDR register before the ninth SCL pulse (ACK pulse) of the next data byte occurs. If not, an overrun occurs, the OVR flag is set in the I2C_ISR register, and an interrupt is generated if the ERRIE bit of the I2C_CR1 register is set.

Slave byte control mode

To allow byte ACK control in slave reception mode, the slave byte control mode must be enabled, by setting the SBC bit of the I2C_CR1 register. This is required to comply with SMBus standards.

The reload mode must be selected to allow byte ACK control in slave reception mode (RELOAD = 1). To get control of each byte, NBBYTES[7:0] must be initialized to 0x1 in the ADDR interrupt subroutine, and reloaded to 0x1 after each received byte. When the byte is received, the TCR bit is set, stretching the SCL signal low between the eighth and ninth SCL pulses. The user can read the data from the I2C_RXDR register, and then decide to acknowledge it or not by configuring the ACK bit of the I2C_CR2 register. The SCL stretch is released by programming NBBYTES to a non-zero value: the acknowledge or not-acknowledge is sent, and the next byte can be received.

NBYTES[7:0] can be loaded with a value greater than 0x1. Receiving then continues until the corresponding number of bytes are received.

Note: The SBC bit must be configured when the I2C peripheral is disabled, when the slave is not addressed, or when ADDR = 1.

The RELOAD bit value can be changed when ADDR = 1, or when TCR = 1.

Caution: The slave byte control mode is not compatible with NOSTRETCH mode. Setting SBC when NOSTRETCH = 1 is not allowed.

Figure 301. Slave initialization flow

graph TD; A([Slave initialization]) --> B[Initial settings]; B --> C[Clear OA1EN and OA2EN in I2C_OAR1/I2C_OAR2]; C --> D["Configure OA1[9:0], OA1MODE, OA1EN, OA2[6:0], OA2MSK[2:0], OA2EN, and GCEN"]; D --> E["Optional: Configure SBC in I2C_CR1<sup>1</sup>"]; E --> F[Enable interrupts and/or DMA in I2C_CR1]; F --> G([End]);

The flowchart illustrates the slave initialization process. It begins with an oval labeled 'Slave initialization', which points down to a rectangle 'Initial settings'. This is followed by a sequence of rectangles: 'Clear OA1EN and OA2EN in I2C_OAR1/I2C_OAR2', 'Configure OA1[9:0], OA1MODE, OA1EN, OA2[6:0], OA2MSK[2:0], OA2EN, and GCEN', 'Optional: Configure SBC in I2C_CR1 1 ', and 'Enable interrupts and/or DMA in I2C_CR1'. The process concludes with an oval labeled 'End'. A small note 'MS19850V3' is visible in the bottom right corner of the diagram area.

- 1. SBC must be set to support SMBus features.

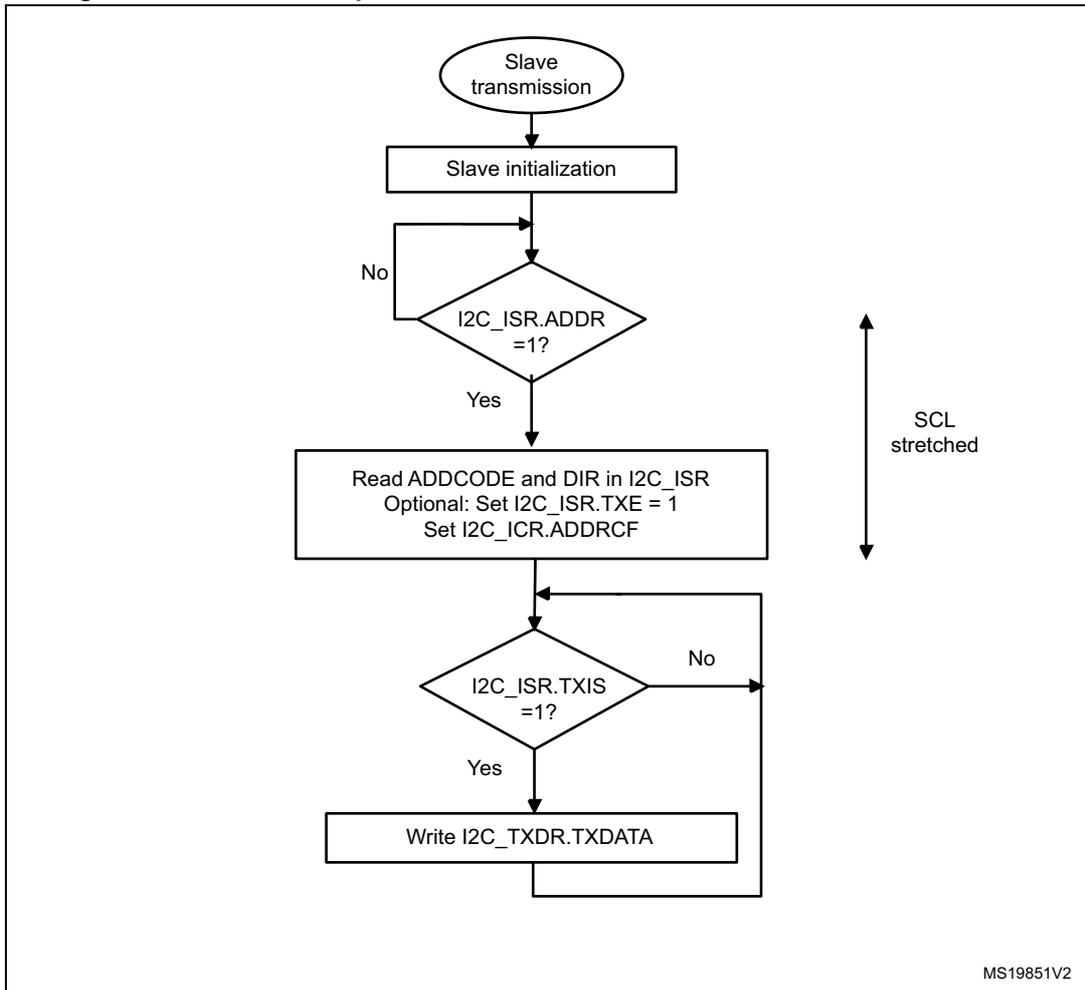

Slave transmitter

A transmit interrupt status (TXIS) flag is generated when the I2C_TXDR register becomes empty. An interrupt is generated if the TXIE bit of the I2C_CR1 register is set.

The TXIS flag is cleared when the I2C_TXDR register is written with the next data byte to transmit.

When NACK is received, the NACKF flag is set in the I2C_ISR register and an interrupt is generated if the NACKIE bit of the I2C_CR1 register is set. The slave automatically releases the SCL and SDA lines to let the master perform a STOP or a RESTART condition. The TXIS bit is not set when a NACK is received.

When STOP is received and the STOPIE bit of the I2C_CR1 register is set, the STOPF flag of the I2C_ISR register is set and an interrupt is generated. In most applications, the SBC bit is usually programmed to 0. In this case, if TXE = 0 when the slave address is received (ADDR = 1), the user can choose either to send the content of the I2C_TXDR register as the first data byte, or to flush the I2C_TXDR register, by setting the TXE bit in order to program a new data byte.

In slave byte control mode (SBC = 1), the number of bytes to transmit must be programmed in NBBYTES[7:0] in the address match interrupt subroutine (ADDR = 1). In this case, the number of TXIS events during the transfer corresponds to the value programmed in NBBYTES[7:0].

Caution: When NOSTRETCH = 1, the SCL clock is not stretched while the ADDR flag is set, so the user cannot flush the I2C_TXDR register content in the ADDR subroutine to program the first data byte. The first data byte to send must be previously programmed in the I2C_TXDR register:

- • This data can be the one written in the last TXIS event of the previous transmission message.

- • If this data byte is not the one to send, the I2C_TXDR register can be flushed, by setting the TXE bit, to program a new data byte. The STOPF bit must be cleared only after these actions. This guarantees that they are executed before the first data transmission starts, following the address acknowledge.

If STOPF is still set when the first data transmission starts, an underrun error is generated (the OVR flag is set).

If a TXIS event (transmit interrupt or transmit DMA request) is required, the user must set the TXIS bit in addition to the TXE bit, to generate the event.

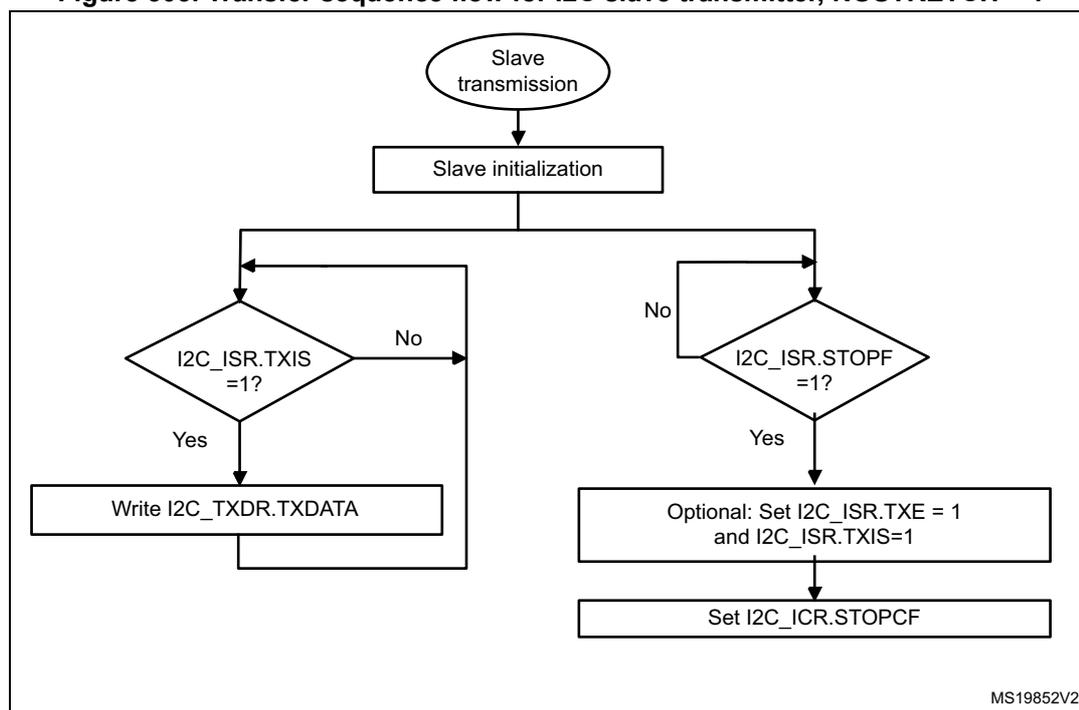

Figure 302. Transfer sequence flow for I2C slave transmitter, NOSTRETCH = 0

graph TD; Start([Slave transmission]) --> Init[Slave initialization]; Init --> ADDR{I2C_ISR.ADDR = 1?}; ADDR -- No --> Init; ADDR -- Yes --> Read[Read ADDCODE and DIR in I2C_ISR<br/>Optional: Set I2C_ISR.TXE = 1<br/>Set I2C_ICR.ADDRCF]; Read --> TXIS{I2C_ISR.TXIS = 1?}; TXIS -- No --> ADDR; TXIS -- Yes --> Write[Write I2C_TXDR.TXDATA]; Write --> TXIS; style ADDR fill:none,stroke:none; style TXIS fill:none,stroke:none;MS19851V2

Figure 303. Transfer sequence flow for I2C slave transmitter, NOSTRETCH = 1

graph TD; Start([Slave transmission]) --> Init[Slave initialization]; Init --> LoopStart(( )); LoopStart --> TXIS{I2C_ISR.TXIS = 1?}; TXIS -- No --> LoopStart; TXIS -- Yes --> Write[Write I2C_TXDR.TXDATA]; Write --> LoopStart; LoopStart --> STOPF{I2C_ISR.STOPF = 1?}; STOPF -- No --> LoopStart; STOPF -- Yes --> Optional[Optional: Set I2C_ISR.TXE = 1 and I2C_ISR.TXIS=1]; Optional --> StopPCF[Set I2C_ICR.STOPCF]; StopPCF --> End(( ));The flowchart illustrates the transfer sequence flow for an I2C slave transmitter with NOSTRETCH = 1. It begins with an oval labeled "Slave transmission", which points to a rectangle labeled "Slave initialization". From "Slave initialization", the flow proceeds to a decision diamond labeled "I2C_ISR.TXIS = 1?". If the answer is "No", the flow loops back to the entry point before the decision. If the answer is "Yes", the flow proceeds to a rectangle labeled "Write I2C_TXDR.TXDATA", which then loops back to the entry point. After the "I2C_ISR.TXIS = 1?" decision, the flow proceeds to another decision diamond labeled "I2C_ISR.STOPF = 1?". If the answer is "No", the flow loops back to the entry point. If the answer is "Yes", the flow proceeds to a rectangle labeled "Optional: Set I2C_ISR.TXE = 1 and I2C_ISR.TXIS=1", which then proceeds to a rectangle labeled "Set I2C_ICR.STOPCF". Finally, the flow proceeds to an oval labeled "End". The identifier "MS19852V2" is located in the bottom right corner of the diagram.

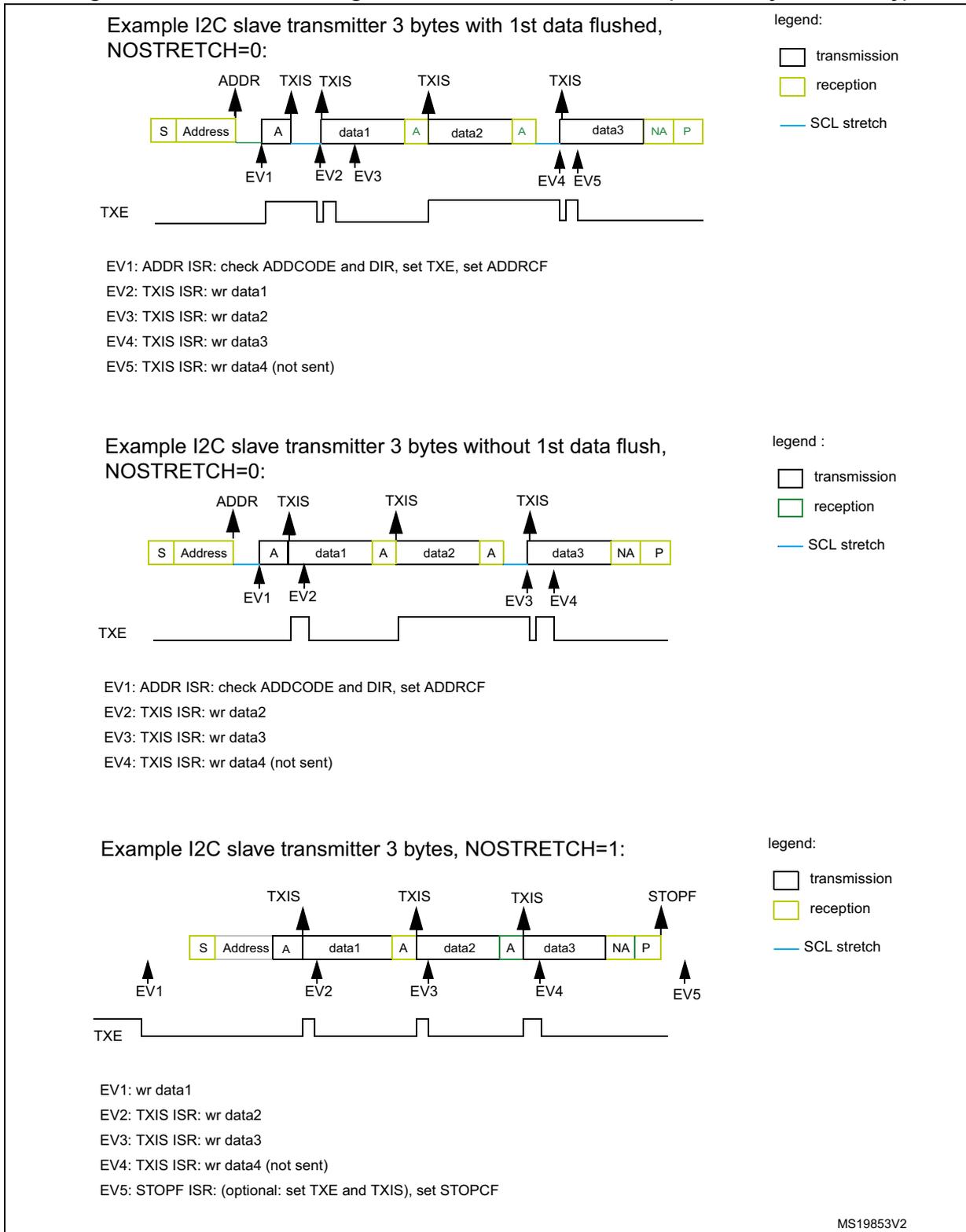

Figure 304. Transfer bus diagrams for I2C slave transmitter (mandatory events only)

Example I2C slave transmitter 3 bytes with 1st data flushed, NOSTRETCH=0:

EV1: ADDR ISR: check ADDCODE and DIR, set TXE, set ADDRCF

EV2: TXIS ISR: wr data1

EV3: TXIS ISR: wr data2

EV4: TXIS ISR: wr data3

EV5: TXIS ISR: wr data4 (not sent)

Example I2C slave transmitter 3 bytes without 1st data flush, NOSTRETCH=0:

EV1: ADDR ISR: check ADDCODE and DIR, set ADDRCF

EV2: TXIS ISR: wr data2

EV3: TXIS ISR: wr data3

EV4: TXIS ISR: wr data4 (not sent)

Example I2C slave transmitter 3 bytes, NOSTRETCH=1:

EV1: wr data1

EV2: TXIS ISR: wr data2

EV3: TXIS ISR: wr data3

EV4: TXIS ISR: wr data4 (not sent)

EV5: STOPF ISR: (optional: set TXE and TXIS), set STOPCF

MS19853V2

Slave receiver

The RXNE bit of the I2C_ISR register is set when the I2C_RXDR is full, which generates an interrupt if the RXIE bit of the I2C_CR1 register is set. RXNE is cleared when I2C_RXDR is read.

When a STOP is received and STOPIE is set in I2C_CR1, STOPF is set in I2C_ISR and an interrupt is generated.

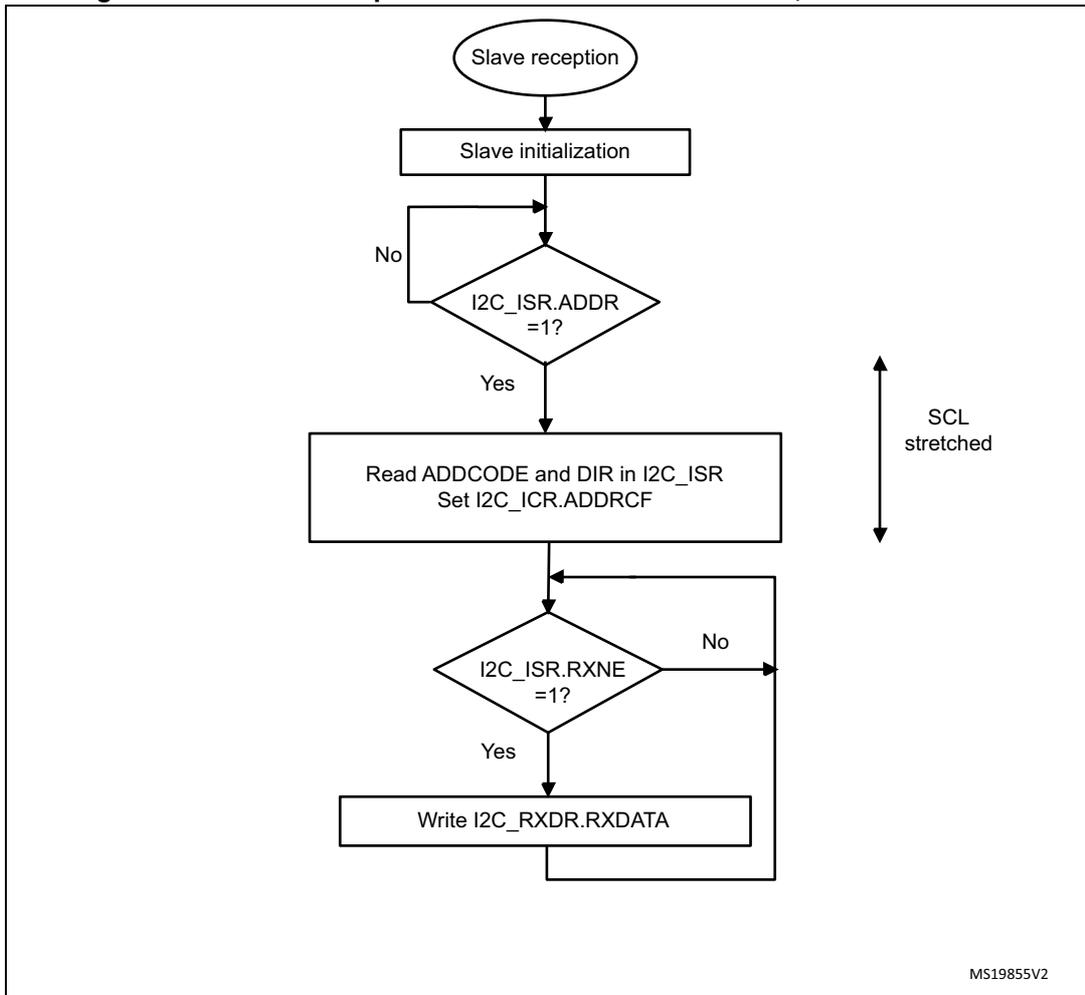

Figure 305. Transfer sequence flow for I2C slave receiver, NOSTRETCH = 0

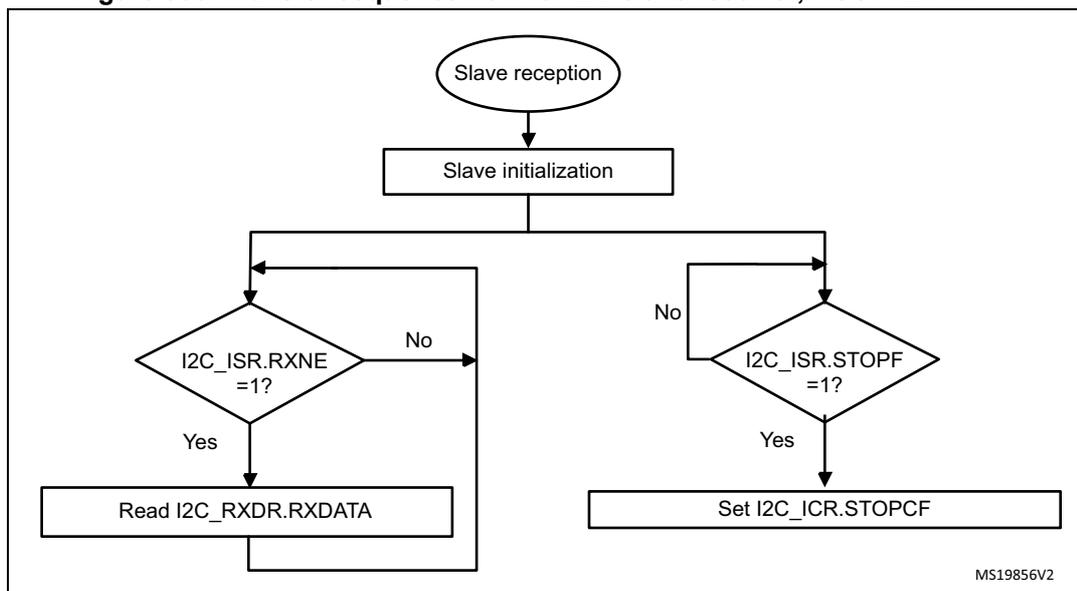

graph TD; Start([Slave reception]) --> Init[Slave initialization]; Init --> ADDR{I2C_ISR.ADDR = 1?}; ADDR -- No --> ADDR; ADDR -- Yes --> Read[Read ADDCODE and DIR in I2C_ISR<br/>Set I2C_ICR.ADDRCF]; Read --> RXNE{I2C_ISR.RXNE = 1?}; RXNE -- No --> RXNE; RXNE -- Yes --> Write[Write I2C_RXDR.RXDATA]; Write --> RXNE;Figure 306. Transfer sequence flow for I2C slave receiver, NOSTRETCH = 1

graph TD

Start([Slave reception]) --> Init[Slave initialization]

Init --> RXNE{I2C_ISR.RXNE = 1?}

RXNE -- Yes --> Read[Read I2C_RXDR.RXDATA]

Read --> RXNE

RXNE -- No --> STOPF{I2C_ISR.STOPF = 1?}

STOPF -- Yes --> StopCF[Set I2C_ICR.STOPCF]

StopCF --> RXNE

STOPF -- No --> RXNE

MS19856V2

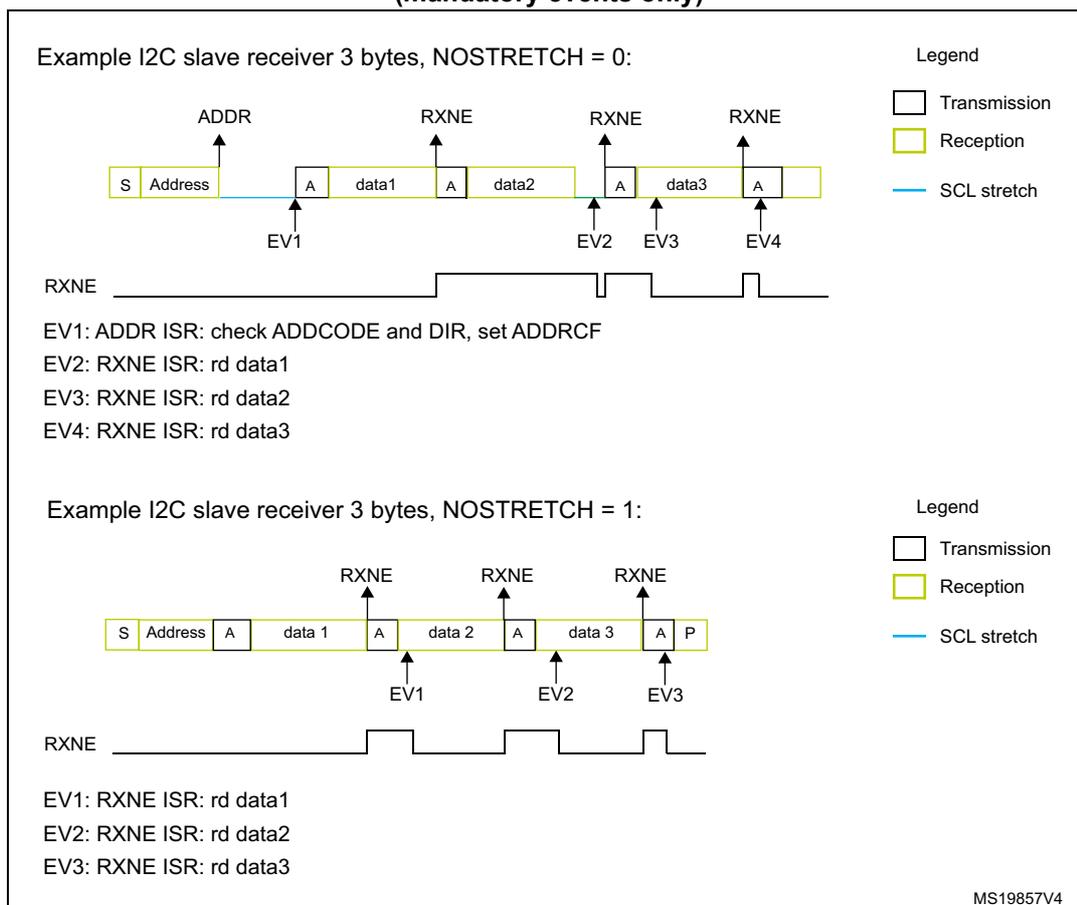

Figure 307. Transfer bus diagrams for I2C slave receiver (mandatory events only)

Example I2C slave receiver 3 bytes, NOSTRETCH = 0:

RXNE

EV1: ADDR ISR: check ADDCODE and DIR, set ADDRCF

EV2: RXNE ISR: rd data1

EV3: RXNE ISR: rd data2

EV4: RXNE ISR: rd data3

Example I2C slave receiver 3 bytes, NOSTRETCH = 1:

RXNE

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: rd data2

EV3: RXNE ISR: rd data3

MS19857V4

28.4.9 I2C master mode

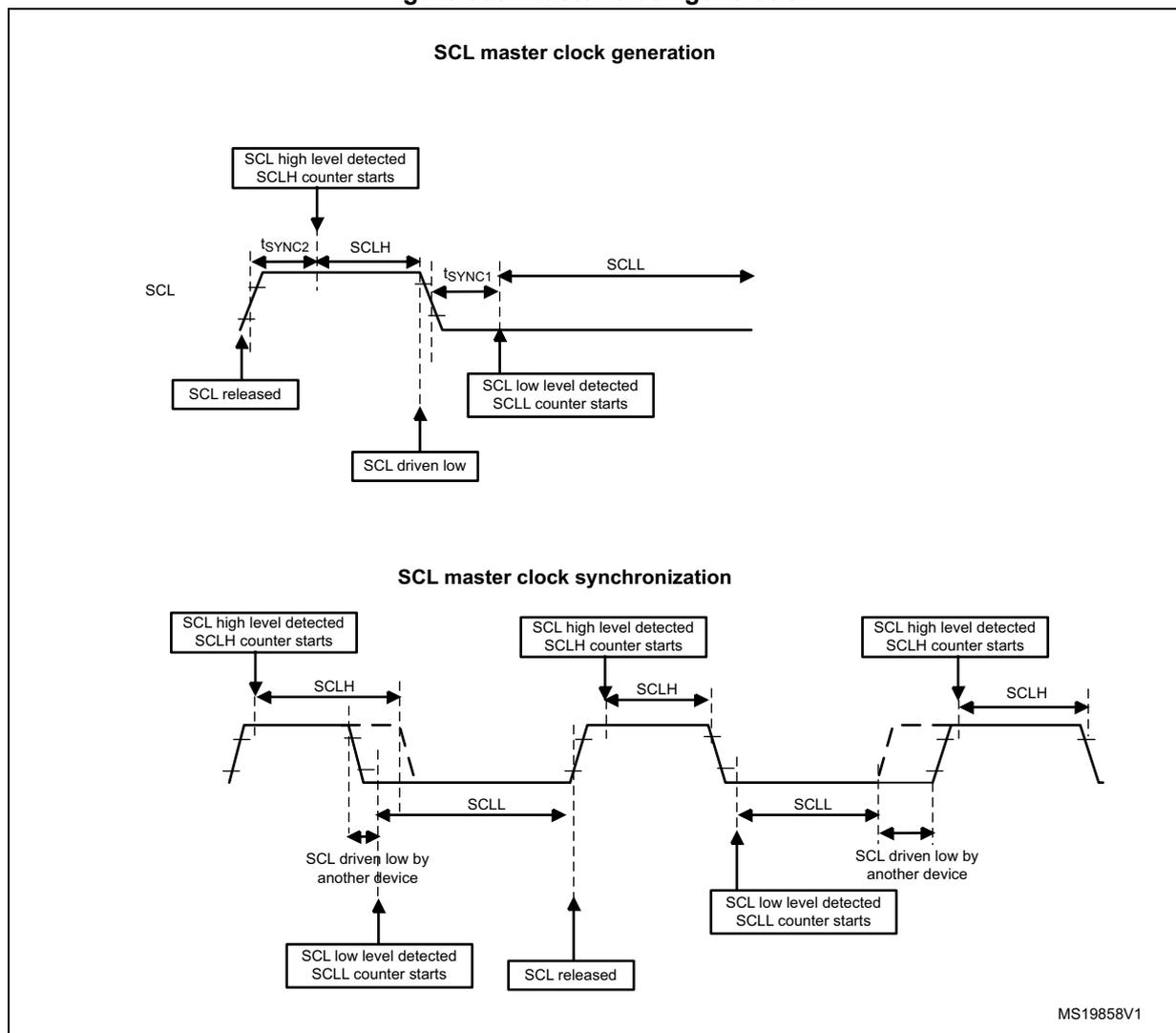

I2C master initialization

Before enabling the peripheral, the I2C master clock must be configured, by setting the SCLH and SCLL bits in the I2C_TIMINGR register.

The STM32CubeMX tool calculates and provides the I2C_TIMINGR content in the I2C Configuration window.

A clock synchronization mechanism is implemented in order to support multi-master environment and slave clock stretching.

In order to allow clock synchronization:

- • The low level of the clock is counted using the SCLL counter, starting from the SCL low level internal detection.

- • The high level of the clock is counted using the SCLH counter, starting from the SCL high level internal detection.

I2C detects its own SCL low level after a \( t_{\text{SYNC1}} \) delay depending on the SCL falling edge, SCL input noise filters (analog and digital), and SCL synchronization to the I2CxCLK clock. I2C releases SCL to high level once the SCLL counter reaches the value programmed in the SCLL[7:0] bitfield of the I2C_TIMINGR register.

I2C detects its own SCL high level after a \( t_{\text{SYNC2}} \) delay depending on the SCL rising edge, SCL input noise filters (analog and digital), and SCL synchronization to the I2CxCLK clock. I2C ties SCL to low level once the SCLH counter reaches the value programmed in the SCLH[7:0] bitfield of the I2C_TIMINGR register.

Consequently the master clock period is:

The duration of \( t_{\text{SYNC1}} \) depends upon:

- • SCL falling slope

- • input delay induced by the analog filter (when enabled)

- • input delay induced by the digital filter (when enabled): \( \text{DNF}[3:0] \times t_{\text{I2CCLK}} \)

- • delay due to SCL synchronization with the I2CCLK clock (two to three I2CCLK periods)

The duration of \( t_{\text{SYNC2}} \) depends upon:

- • SCL rising slope

- • input delay induced by the analog filter (when enabled)

- • input delay induced by the digital filter (when enabled): \( \text{DNF}[3:0] \times t_{\text{I2CCLK}} \)

- • delay due to SCL synchronization with the I2CCLK clock (two to three I2CCLK periods)

Figure 308. Master clock generation

SCL master clock generation

The diagram illustrates the timing for SCL master clock generation. The SCL signal transitions from a released state to a high level, then is driven low. The time from SCL released to high level detection is \( t_{SYNC2} \) . The SCLH counter starts when the high level is detected. The time from SCL driven low to low level detection is \( t_{SYNC1} \) . The SCLL counter starts when the low level is detected.

SCL master clock synchronization

The diagram illustrates SCL master clock synchronization. It shows how the SCLH and SCLL counters are triggered by level detection. It specifically highlights cases where the SCL line is driven low by another device, extending the low period, and how the master waits for the SCL line to be released before starting its high level counter.

MS19858V1

Caution: For compliance with the I 2 C-bus or SMBus specification, the master clock must respect the timings in the following table.

Table 148. I 2 C-bus and SMBus specification clock timings

| Symbol | Parameter | Standard-mode (Sm) | Fast-mode (Fm) | Fast-mode Plus (Fm+) | SMBus | Unit | ||||

|---|---|---|---|---|---|---|---|---|---|---|

| Min | Max | Min | Max | Min | Max | Min | Max | |||

| f SCL | SCL clock frequency | - | 100 | - | 400 | - | 1000 | - | 100 | kHz |

| t HD:STA | Hold time (repeated) START condition | 4.0 | - | 0.6 | - | 0.26 | - | 4.0 | - | µs |

| t SU:STA | Set-up time for a repeated START condition | 4.7 | - | 0.6 | - | 0.26 | - | 4.7 | - | |

| t SU:STO | Set-up time for STOP condition | 4.0 | - | 0.6 | - | 0.26 | - | 4.0 | - | |

| t BUF | Bus free time between a STOP and START condition | 4.7 | - | 1.3 | - | 0.5 | - | 4.7 | - | |

| t LOW | Low period of the SCL clock | 4.7 | - | 1.3 | - | 0.5 | - | 4.7 | - | |

| t HIGH | High period of the SCL clock | 4.0 | - | 0.6 | - | 0.26 | - | 4.0 | 50 | |

| t r | Rise time of both SDA and SCL signals | - | 1000 | - | 300 | - | 120 | - | 1000 | ns |

| t f | Fall time of both SDA and SCL signals | - | 300 | - | 300 | - | 120 | - | 300 | |

Note: The SCLL[7:0] bitfield also determines the t BUF and t SU:STA timings and SCLH[7:0] the t HD:STA and t SU:STO timings.

Refer to Section 28.4.10 for examples of I2C_TIMINGR settings versus the I2CCLK frequency.

Master communication initialization (address phase)

To initiate the communication with a slave to address, set the following bitfields of the I2C_CR2 register:

- • ADD10: addressing mode (7-bit or 10-bit)

- • SADD[9:0]: slave address to send

- • RD_WRN: transfer direction

- • HEAD10R: in case of 10-bit address read, this bit determines whether the header only (for direction change) or the complete address sequence is sent.

- • NBYTES[7:0]: the number of bytes to transfer; if equal to or greater than 255 bytes, the bitfield must initially be set to 0xFF.

Note: Changing these bitfields is not allowed as long as the START bit is set.

Before launching the communication, make sure that the I 2 C-bus is idle. This can be checked using the bus idle detection function or by verifying that the IDR bits of the GPIOs selected as SDA and SCL are set. Any low-level incident on the I 2 C-bus lines that coincides with the START condition asserted by the I2C peripheral may cause its deadlock if not filtered out by the input filters. If such incidents cannot be prevented, design the software so that it restores the normal operation of the I2C peripheral in case of a deadlock, by toggling the PE bit of the I2C_CR1 register.

To launch the communication, set the START bit of the I2C_CR2 register. The master then automatically sends a START condition followed by the slave address as soon as it detects that the bus is free (BUSY = 0) and after the \( t_{\text{BUF}} \) delay from a previous STOP condition expires.

In case of an arbitration loss, the master automatically switches back to slave mode and can acknowledge its own address if it is addressed as a slave.

Note: The START bit is reset by hardware when the slave address is sent on the bus, whatever the received acknowledge value. The START bit is also reset by hardware upon arbitration loss.

In 10-bit addressing mode, the master automatically keeps resending the slave address in a loop until the first address byte (first seven address bits) is acknowledged by the slave.

Setting the ADDRCF bit makes I2C quit that loop.

If the I2C peripheral is addressed as a slave (ADDR = 1) while the START bit is set, the I2C peripheral switches to slave mode and the START bit is cleared when the ADDRCF bit is set.

Note: The same procedure is applied for a repeated start condition. In this case, BUSY = 1.

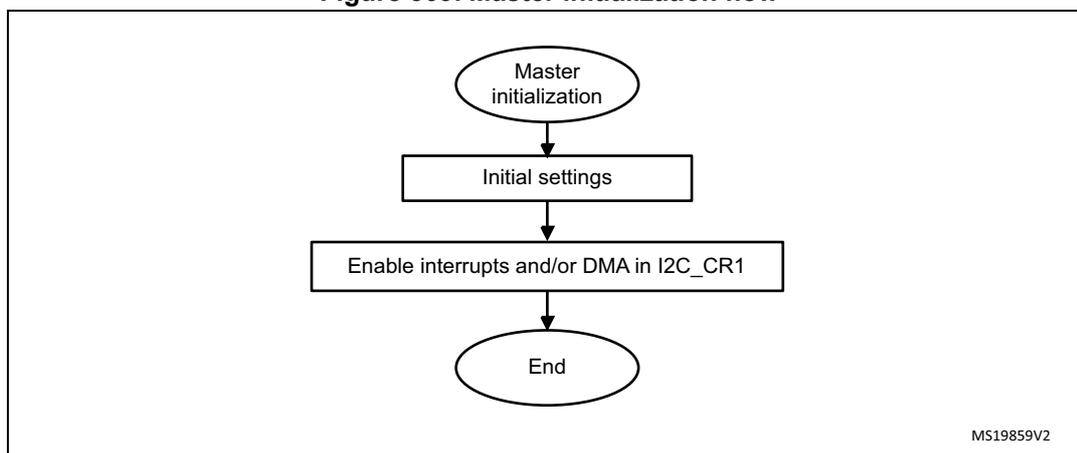

Figure 309. Master initialization flow

graph TD

A([Master initialization]) --> B[Initial settings]

B --> C[Enable interrupts and/or DMA in I2C_CR1]

C --> D([End])

MS19859V2

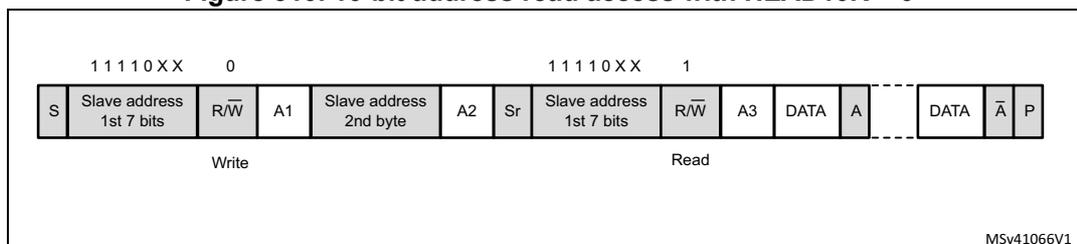

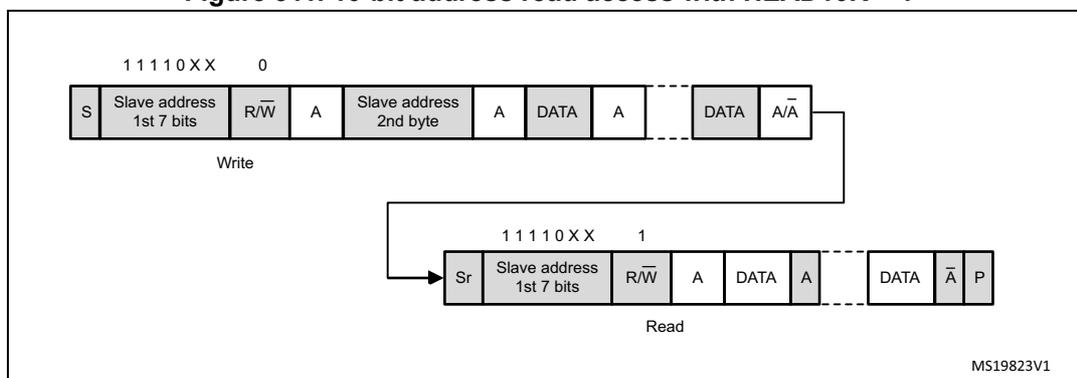

Initialization of a master receiver addressing a 10-bit address slave

If the slave address is in 10-bit format, the user can choose to send the complete read sequence, by clearing the HEAD10R bit of the I2C_CR2 register. In this case, the master automatically sends the following complete sequence after the START bit is set:

(RE)START + Slave address 10-bit header Write + Slave address second byte + (RE)START + Slave address 10-bit header Read.

Figure 310. 10-bit address read access with HEAD10R = 0

| 1 1 1 1 0 X X 0 | 1 1 1 1 0 X X 1 | |||||||||||||

| S | Slave address 1st 7 bits | R/W | A1 | Slave address 2nd byte | A2 | Sr | Slave address 1st 7 bits | R/W | A3 | DATA | A | DATA | Ā | P |

| Write | Read | |||||||||||||

MSV41066V1

If the master addresses a 10-bit address slave, transmits data to this slave and then reads data from the same slave, a master transmission flow must be done first. Then a repeated START is set with the 10-bit slave address configured with HEAD10R = 1. In this case, the master sends this sequence:

RESTART + Slave address 10-bit header Read.

Figure 311. 10-bit address read access with HEAD10R = 1

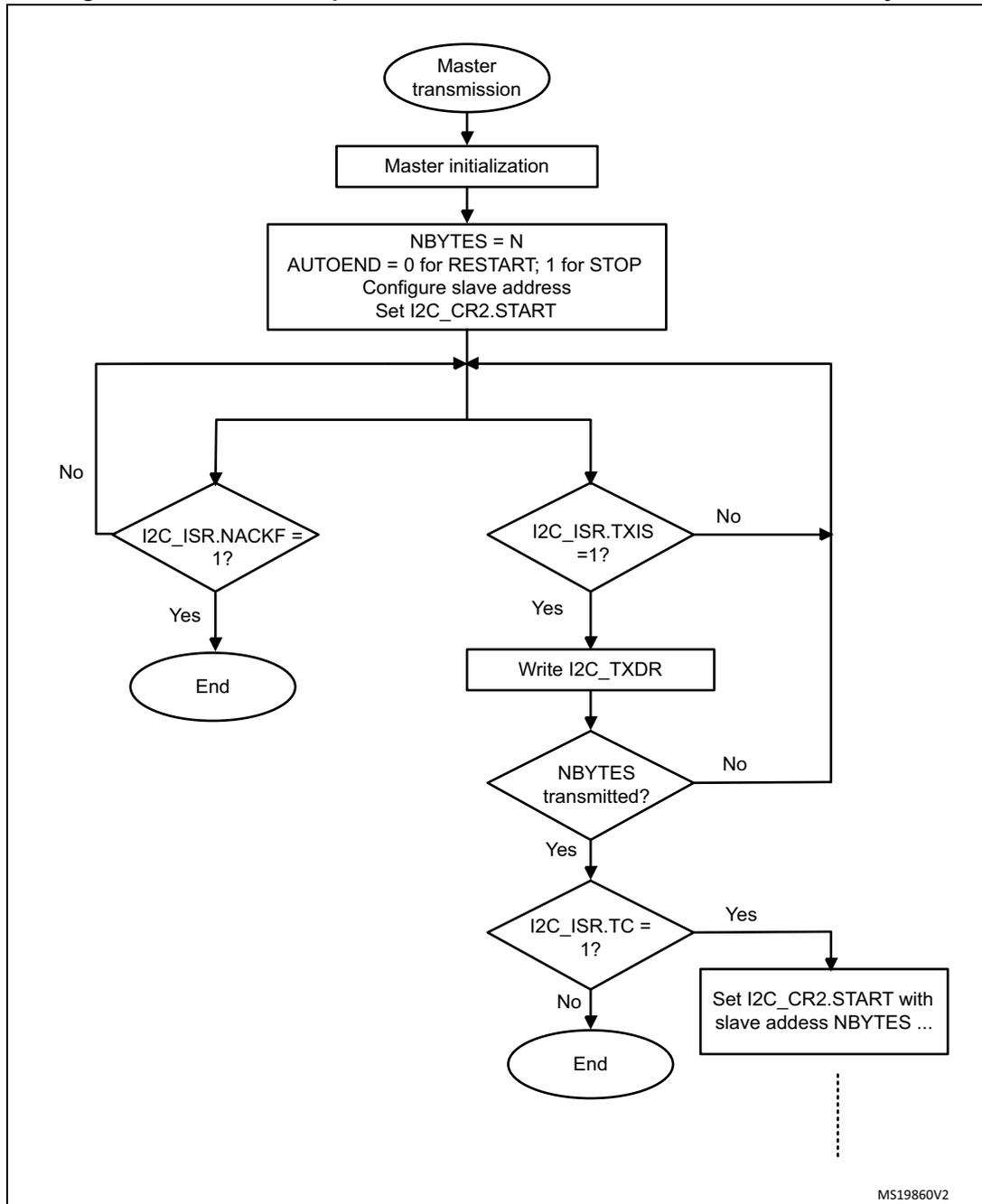

Master transmitter

In the case of a write transfer, the TXIS flag is set after each byte transmission, after the ninth SCL pulse when an ACK is received.

A TXIS event generates an interrupt if the TXIE bit of the I2C_CR1 register is set. The flag is cleared when the I2C_TXDR register is written with the next data byte to transmit.

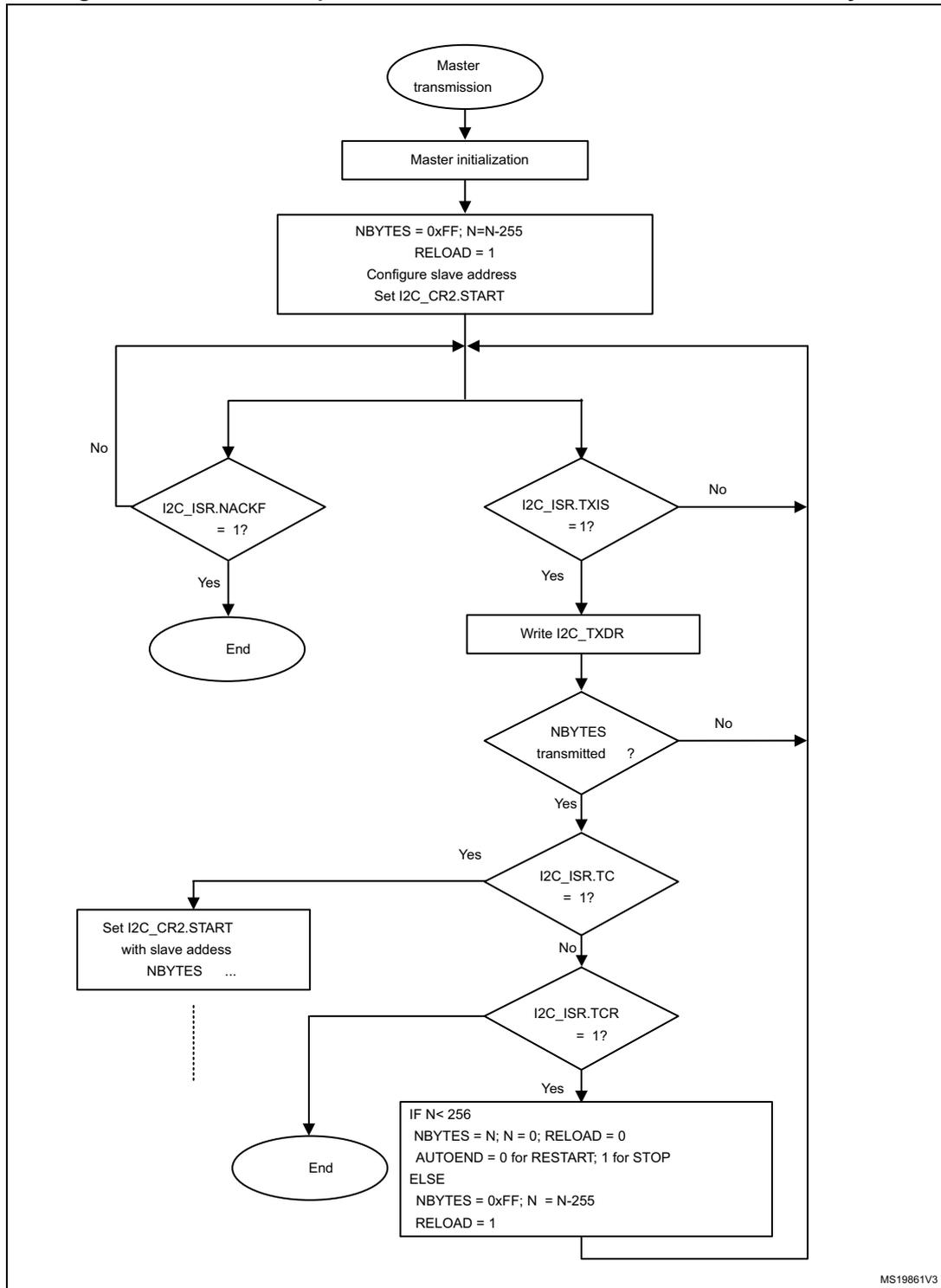

The number of TXIS events during the transfer corresponds to the value programmed in NBBYTES[7:0]. If the total number of data bytes to transmit is greater than 255, the reload mode must be selected by setting the RELOAD bit in the I2C_CR2 register. In this case, when the NBBYTES[7:0] number of data bytes is transferred, the TCR flag is set and the SCL line is stretched low until NBBYTES[7:0] is written with a non-zero value.

When RELOAD = 0 and the number of data bytes defined in NBBYTES[7:0] is transferred:

- • In automatic end mode (AUTOEND = 1), a STOP condition is automatically sent.

- • In software end mode (AUTOEND = 0), the TC flag is set and the SCL line is stretched low, to perform software actions:

- – A RESTART condition can be requested by setting the START bit of the I2C_CR2 register with the proper slave address configuration and the number of bytes to transfer. Setting the START bit clears the TC flag and sends the START condition on the bus.

- – A STOP condition can be requested by setting the STOP bit of the I2C_CR2 register. This clears the TC flag and sends a STOP condition on the bus.

When a NACK is received, the TXIS flag is not set and a STOP condition is automatically sent. the NACKF flag of the I2C_ISR register is set. An interrupt is generated if the NACKIE bit is set.

Figure 312. Transfer sequence flow for I2C master transmitter, N ≤ 255 bytes

graph TD; A([Master transmission]) --> B[Master initialization]; B --> C["NBYTES = N<br/>AUTOEND = 0 for RESTART; 1 for STOP<br/>Configure slave address<br/>Set I2C_CR2.START"]; C --> D{"I2C_ISR.NACKF = 1?"}; D -- Yes --> E([End]); D -- No --> F{"I2C_ISR.TXIS = 1?"}; F -- Yes --> G[Write I2C_TXDR]; F -- No --> D; G --> H{"NBYTES transmitted?"}; H -- Yes --> I{"I2C_ISR.TC = 1?"}; H -- No --> D; I -- Yes --> J["Set I2C_CR2.START with<br/>slave address NBYTES ..."]; I -- No --> K([End]); J --> K;MS19860V2

Figure 313. Transfer sequence flow for I2C master transmitter, N > 255 bytes

graph TD; Start([Master transmission]) --> Init[Master initialization]; Init --> Config["NBYTES = 0xFF; N=N-255<br/>RELOAD = 1<br/>Configure slave address<br/>Set I2C_CR2.START"]; Config --> LoopStart(( )); LoopStart --> NACKF{I2C_ISR.NACKF = 1?}; NACKF -- Yes --> End1([End]); NACKF -- No --> TXIS{I2C_ISR.TXIS = 1?}; TXIS -- No --> LoopStart; TXIS -- Yes --> Write[Write I2C_TXDR]; Write --> Transmitted{NBYTES transmitted ?}; Transmitted -- No --> LoopStart; Transmitted -- Yes --> TC{I2C_ISR.TC = 1?}; TC -- Yes --> SetStart["Set I2C_CR2.START<br/>with slave address<br/>NBYTES ..."]; SetStart -.-> Dots[...]; Dots --> TCR{I2C_ISR.TCR = 1?}; TC -- No --> TCR; TCR -- Yes --> End2([End]); TCR -- No --> Reconfig["IF N < 256<br/>NBYTES = N; N = 0; RELOAD = 0<br/>AUTOEND = 0 for RESTART; 1 for STOP<br/>ELSE<br/>NBYTES = 0xFF; N = N-255<br/>RELOAD = 1"]; Reconfig --> LoopStart;The flowchart illustrates the transfer sequence for an I2C master transmitter when the number of bytes to transmit (N) is greater than 255. It begins with 'Master transmission' leading to 'Master initialization'. The initialization block sets NBYTES to 0xFF, N to N-255, RELOAD to 1, configures the slave address, and sets the I2C_CR2.START bit. The main loop starts with a decision 'I2C_ISR.NACKF = 1?'. If 'Yes', the process ends. If 'No', it proceeds to 'I2C_ISR.TXIS = 1?'. If 'No', it loops back to the start of the loop. If 'Yes', it proceeds to 'Write I2C_TXDR'. After writing, it checks 'NBYTES transmitted ?'. If 'No', it loops back. If 'Yes', it checks 'I2C_ISR.TC = 1?'. If 'Yes', it proceeds to 'Set I2C_CR2.START with slave address NBYTES ...', followed by a vertical ellipsis. If 'No', it checks 'I2C_ISR.TCR = 1?'. If 'Yes', it ends. If 'No', it proceeds to a configuration block: 'IF N < 256, NBYTES = N; N = 0; RELOAD = 0; AUTOEND = 0 for RESTART; 1 for STOP ELSE NBYTES = 0xFF; N = N-255; RELOAD = 1', which then loops back to the start of the loop.

MS19861V3

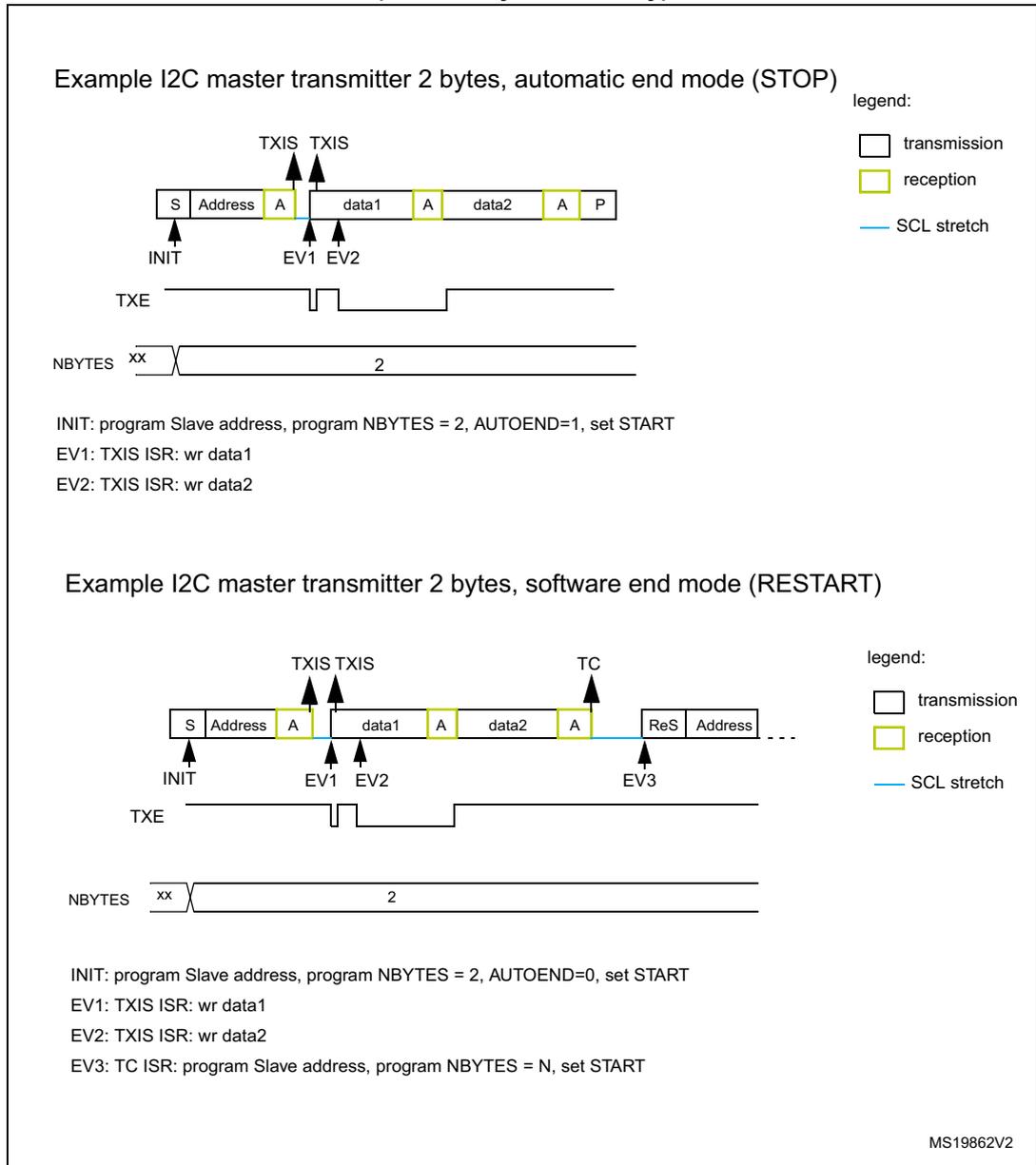

Figure 314. Transfer bus diagrams for I2C master transmitter (mandatory events only)

Example I2C master transmitter 2 bytes, automatic end mode (STOP)

legend:

transmission

reception

—

SCL stretch

INIT: program Slave address, program NBYTES = 2, AUTOEND=1, set START

EV1: TXIS ISR: wr data1

EV2: TXIS ISR: wr data2

Example I2C master transmitter 2 bytes, software end mode (RESTART)

legend:

transmission

reception

—

SCL stretch

INIT: program Slave address, program NBYTES = 2, AUTOEND=0, set START

EV1: TXIS ISR: wr data1

EV2: TXIS ISR: wr data2

EV3: TC ISR: program Slave address, program NBYTES = N, set START

MS19862V2

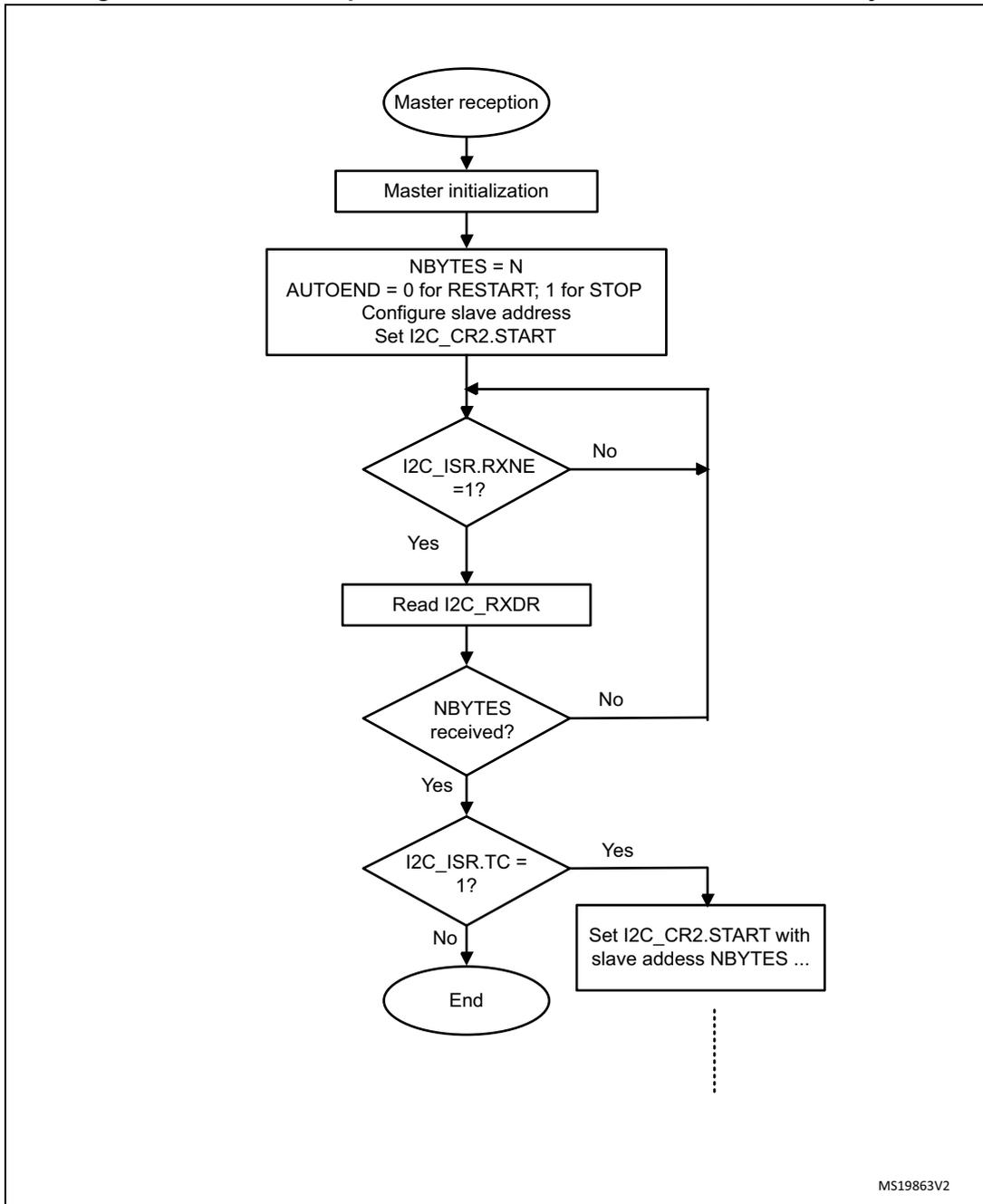

Master receiver

In the case of a read transfer, the RXNE flag is set after each byte reception, after the eighth SCL pulse. An RXNE event generates an interrupt if the RXIE bit of the I2C_CR1 register is set. The flag is cleared when I2C_RXDR is read.

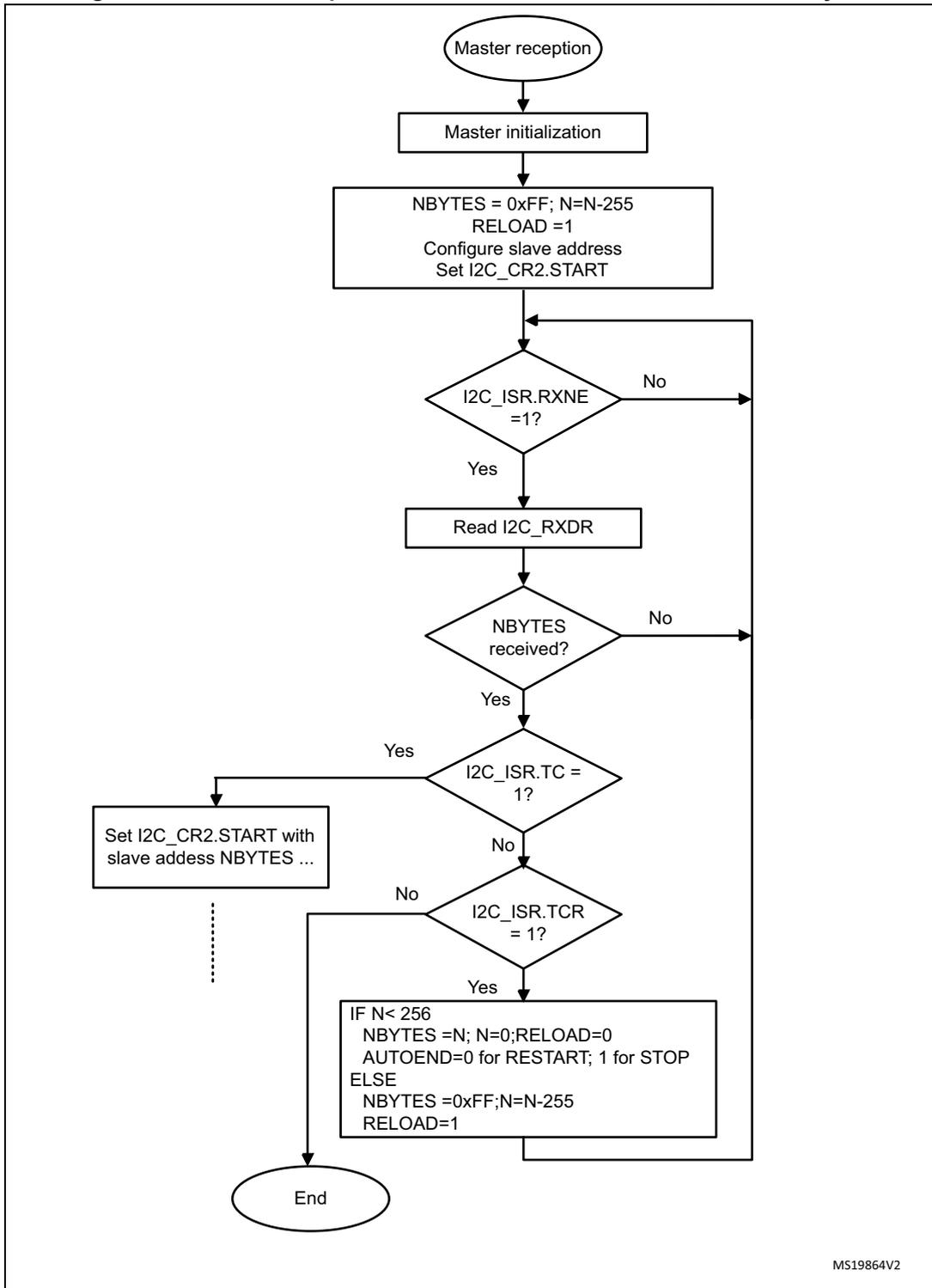

If the total number of data bytes to receive is greater than 255, select the reload mode, by setting the RELOAD bit of the I2C_CR2 register. In this case, when the NBBYTES[7:0] number of data bytes is transferred, the TCR flag is set and the SCL line is stretched low until NBBYTES[7:0] is written with a non-zero value.

When RELOAD = 0 and the number of data bytes defined in NBBYTES[7:0] is transferred:

- • In automatic end mode (AUTOEND = 1), a NACK and a STOP are automatically sent after the last received byte.

- • In software end mode (AUTOEND = 0), a NACK is automatically sent after the last received byte. The TC flag is set and the SCL line is stretched low in order to allow software actions:

- – A RESTART condition can be requested by setting the START bit of the I2C_CR2 register, with the proper slave address configuration and the number of bytes to transfer. Setting the START bit clears the TC flag and the START condition, followed by slave address, are sent on the bus.

- – A STOP condition can be requested by setting the STOP bit of the I2C_CR2 register. This clears the TC flag and sends a STOP condition on the bus.

Figure 315. Transfer sequence flow for I2C master receiver, N ≤ 255 bytes

graph TD; Start([Master reception]) --> Init[Master initialization]; Init --> Config["NBYTES = N<br/>AUTOEND = 0 for RESTART; 1 for STOP<br/>Configure slave address<br/>Set I2C_CR2.START"]; Config --> RXNE{"I2C_ISR.RXNE<br/>= 1?"}; RXNE -- No --> RXNE; RXNE -- Yes --> Read[Read I2C_RXDR]; Read --> NBYTES{"NBYTES<br/>received?"}; NBYTES -- No --> RXNE; NBYTES -- Yes --> TC{"I2C_ISR.TC<br/>= 1?"}; TC -- Yes --> SetStart["Set I2C_CR2.START with<br/>slave address NBYTES ..."]; TC -- No --> End([End]); SetStart -.-> Dots[...];MS19863V2

Figure 316. Transfer sequence flow for I2C master receiver, N > 255 bytes

graph TD; Start([Master reception]) --> Init[Master initialization]; Init --> Config["NBYTES = 0xFF; N=N-255<br>RELOAD =1<br>Configure slave address<br>Set I2C_CR2.START"]; Config --> RXNE{I2C_ISR.RXNE =1?}; RXNE -- No --> End([End]); RXNE -- Yes --> Read[Read I2C_RXDR]; Read --> Received{NBYTES received?}; Received -- No --> End; Received -- Yes --> TC{I2C_ISR.TC = 1?}; TC -- Yes --> SetStart["Set I2C_CR2.START with<br>slave address NBYTES ..."]; SetStart --> Dots[...]; Dots --> TCR{I2C_ISR.TCR = 1?}; TC -- No --> TCR; TCR -- Yes --> IFN["IF N< 256<br>NBYTES =N; N=0;RELOAD=0<br>AUTOEND=0 for RESTART; 1 for STOP<br>ELSE<br>NBYTES =0xFF;N=N-255<br>RELOAD=1"]; TCR -- No --> End; IFN --> End; IFN --> Config;The flowchart illustrates the transfer sequence for an I2C master receiver when the number of bytes to receive (N) is greater than 255. It begins with 'Master reception', followed by 'Master initialization'. The initialization block sets NBYTES to 0xFF, N to N-255, RELOAD to 1, configures the slave address, and sets the I2C_CR2.START bit. A loop begins with a decision 'I2C_ISR.RXNE =1?'. If 'No', the process ends. If 'Yes', it proceeds to 'Read I2C_RXDR'. Next is a decision 'NBYTES received?'. If 'No', the process ends. If 'Yes', it proceeds to 'I2C_ISR.TC = 1?'. If 'Yes', it goes to 'Set I2C_CR2.START with slave address NBYTES ...', followed by a vertical ellipsis. If 'No', it proceeds to 'I2C_ISR.TCR = 1?'. If 'Yes', it enters a block: 'IF N < 256, NBYTES =N; N=0;RELOAD=0, AUTOEND=0 for RESTART; 1 for STOP, ELSE, NBYTES =0xFF;N=N-255, RELOAD=1'. Both the ellipsis and this block lead to the 'End' state. The 'IF N < 256' block also loops back to the initialization configuration block.

MS19864V2

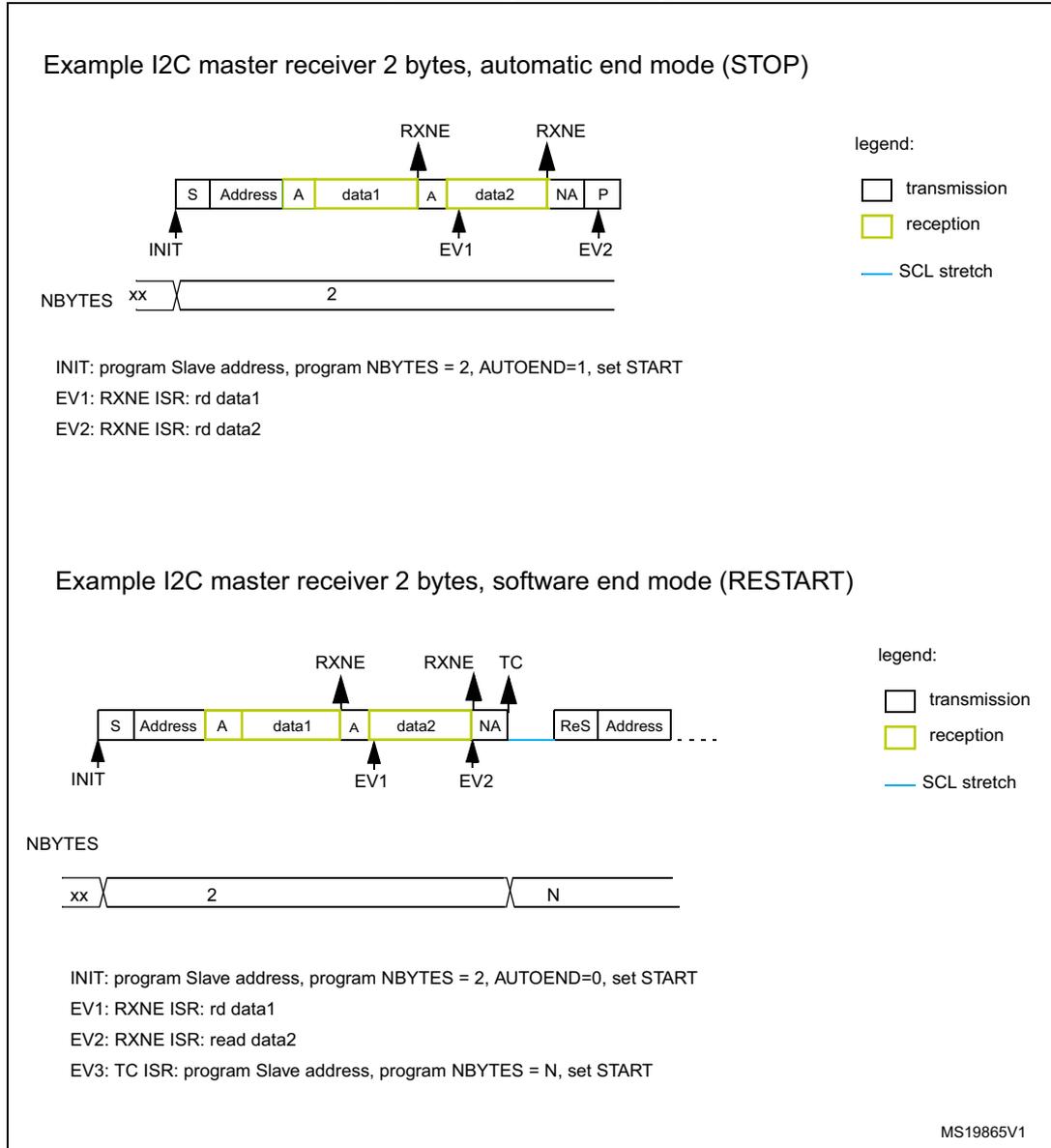

Figure 317. Transfer bus diagrams for I2C master receiver (mandatory events only)

Example I2C master receiver 2 bytes, automatic end mode (STOP)

INIT: program Slave address, program NBBYTES = 2, AUTOEND=1, set START

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: rd data2

Example I2C master receiver 2 bytes, software end mode (RESTART)

INIT: program Slave address, program NBBYTES = 2, AUTOEND=0, set START

EV1: RXNE ISR: rd data1

EV2: RXNE ISR: read data2

EV3: TC ISR: program Slave address, program NBBYTES = N, set START

MS19865V1

28.4.10 I2C_TIMINGR register configuration examples

The following tables provide examples of how to program the I2C_TIMINGR to obtain timings compliant with the I 2 C-bus specification. To get more accurate configuration values, use the STM32CubeMX tool ( I2C Configuration window).

Table 149. Timing settings for\( f_{I2CCLK} \) of 8 MHz| Parameter | Standard-mode (Sm) | Fast-mode (Fm) | Fast-mode Plus (Fm+) | |

|---|---|---|---|---|

| 10 kHz | 100 kHz | 400 kHz | 500 kHz | |

| PRESC[3:0] | 0x1 | 0x1 | 0x0 | 0x0 |

| SCLL[7:0] | 0xC7 | 0x13 | 0x9 | 0x6 |

| \( t_{SCLL} \) | 200 x 250 ns = 50 µs | 20 x 250 ns = 5.0 µs | 10 x 125 ns = 1250 ns | 7 x 125 ns = 875 ns |

| SCLH[7:0] | 0xC3 | 0xF | 0x3 | 0x3 |

| \( t_{SCLH} \) | 196 x 250 ns = 49 µs | 16 x 250 ns = 4.0 µs | 4 x 125 ns = 500 ns | 4 x 125 ns = 500 ns |

| \( t_{SCL}^{(1)} \) | ~100 µs (2) | ~10 µs (2) | ~2.5 µs (3) | ~2.0 µs (4) |

| SDADEL[3:0] | 0x2 | 0x2 | 0x1 | 0x0 |

| \( t_{SDADEL} \) | 2 x 250 ns = 500 ns | 2 x 250 ns = 500 ns | 1 x 125 ns = 125 ns | 0 ns |

| SCLDEL[3:0] | 0x4 | 0x4 | 0x3 | 0x1 |

| \( t_{SCLDEL} \) | 5 x 250 ns = 1250 ns | 5 x 250 ns = 1250 ns | 4 x 125 ns = 500 ns | 2 x 125 ns = 250 ns |

- 1. \( t_{SCL} \) is greater than \( t_{SCLL} + t_{SCLH} \) due to SCL internal detection delay. Values provided for \( t_{SCL} \) are examples only.

- 2. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times f_{I2CCLK} = 500 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 1000 \) ns.

- 3. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times f_{I2CCLK} = 500 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 750 \) ns.

- 4. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times f_{I2CCLK} = 500 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 655 \) ns.

| Parameter | Standard-mode (Sm) | Fast-mode (Fm) | Fast-mode Plus (Fm+) | |

|---|---|---|---|---|

| 10 kHz | 100 kHz | 400 kHz | 1000 kHz | |

| PRESC[3:0] | 0x3 | 0x3 | 0x1 | 0x0 |

| SCLL[7:0] | 0xC7 | 0x13 | 0x9 | 0x4 |

| \( t_{SCLL} \) | 200 x 250 ns = 50 µs | 20 x 250 ns = 5.0 µs | 10 x 125 ns = 1250 ns | 5 x 62.5 ns = 312.5 ns |

| SCLH[7:0] | 0xC3 | 0xF | 0x3 | 0x2 |

| \( t_{SCLH} \) | 196 x 250 ns = 49 µs | 16 x 250 ns = 4.0 µs | 4 x 125 ns = 500 ns | 3 x 62.5 ns = 187.5 ns |

| \( t_{SCL}^{(1)} \) | ~100 µs (2) | ~10 µs (2) | ~2.5 µs (3) | ~1.0 µs (4) |

| SDADEL[3:0] | 0x2 | 0x2 | 0x2 | 0x0 |

| \( t_{SDADEL} \) | 2 x 250 ns = 500 ns | 2 x 250 ns = 500 ns | 2 x 125 ns = 250 ns | 0 ns |

| SCLDEL[3:0] | 0x4 | 0x4 | 0x3 | 0x2 |

| \( t_{SCLDEL} \) | 5 x 250 ns = 1250 ns | 5 x 250 ns = 1250 ns | 4 x 125 ns = 500 ns | 3 x 62.5 ns = 187.5 ns |

- 1. \( t_{SCL} \) is greater than \( t_{SCLL} + t_{SCLH} \) due to SCL internal detection delay. Values provided for \( t_{SCL} \) are examples only.

- 2. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times f_{I2CCLK} = 250 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 1000 \) ns.

- 3. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times f_{I2CCLK} = 250 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 750 \) ns.

- 4. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times f_{I2CCLK} = 250 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 500 \) ns.

| Parameter | Standard-mode (Sm) | Fast-mode (Fm) | Fast-mode Plus (Fm+) | |

|---|---|---|---|---|

| 10 kHz | 100 kHz | 400 kHz | 1000 kHz | |

| PRESC[3:0] | 0xB | 0xB | 0x5 | 0x5 |

| SCLL[7:0] | 0xC7 | 0x13 | 0x9 | 0x3 |

| \( t_{SCLL} \) | 200 x 250 ns = 50 µs | 20 x 250 ns = 5.0 µs | 10 x 125 ns = 1250 ns | 4 x 125 ns = 500 ns |

| SCLH[7:0] | 0xC3 | 0xF | 0x3 | 0x1 |

| \( t_{SCLH} \) | 196 x 250 ns = 49 µs | 16 x 250 ns = 4.0 µs | 4 x 125 ns = 500 ns | 2 x 125 ns = 250 ns |

| \( t_{SCL}^{(1)} \) | ~100 µs (2) | ~10 µs (2) | ~2.5 µs (3) | ~875 ns (4) |

| SDADEL[3:0] | 0x2 | 0x2 | 0x3 | 0x0 |

| \( t_{SDADEL} \) | 2 x 250 ns = 500 ns | 2 x 250 ns = 500 ns | 3 x 125 ns = 375 ns | 0 ns |

| SCLDEL[3:0] | 0x4 | 0x4 | 0x3 | 0x1 |

| \( t_{SCLDEL} \) | 5 x 250 ns = 1250 ns | 5 x 250 ns = 1250 ns | 4 x 125 ns = 500 ns | 2 x 125 ns = 250 ns |

1. \( t_{SCL} \) is greater than \( t_{SCLL} + t_{SCLH} \) due to the SCL internal detection delay. Values provided for \( t_{SCL} \) are only examples.

2. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times t_{I2CCLK} = 83.3 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 1000 \) ns

3. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times t_{I2CCLK} = 83.3 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 750 \) ns

4. \( t_{SYNC1} + t_{SYNC2} \) minimum value is \( 4 \times t_{I2CCLK} = 83.3 \) ns. Example with \( t_{SYNC1} + t_{SYNC2} = 250 \) ns

28.4.11 SMBus specific features

Introduction

The system management bus (SMBus) is a two-wire interface through which various devices can communicate with each other and with the rest of the system. It is based on operation principles of the I 2 C-bus. The SMBus provides a control bus for system and power management related tasks.

The I2C peripheral is compatible with the SMBus specification ( http://smbus.org ).

The system management bus specification refers to three types of devices:

- • Slave is a device that receives or responds to a command.

- • Master is a device that issues commands, generates clocks, and terminates the transfer.

- • Host is a specialized master that provides the main interface to the system CPU. A host must be a master-slave and must support the SMBus host notify protocol. Only one host is allowed in a system.

The I2C peripheral can be configured as a master or a slave device, and also as a host.

Bus protocols

There are eleven possible command protocols for any given device. A device can use any or all of them to communicate. The protocols are: Quick Command , Send Byte , Receive Byte , Write Byte , Write Word , Read Byte , Read Word , Process Call , Block Read , Block Write , and Block Write-Block Read Process Call . The protocols must be implemented by the user software.

For more details on these protocols, refer to the SMBus specification ( http://smbus.org ). STM32CubeMX implements an SMBus stack thanks to X-CUBE-SMBUS, a downloadable software pack that allows basic SMBus configuration per I2C instance.

Address resolution protocol (ARP)

SMBus slave address conflicts can be resolved by dynamically assigning a new unique address to each slave device. To provide a mechanism to isolate each device for the purpose of address assignment, each device must implement a unique 128-bit device identifier (UDID). In the I2C peripheral, is implemented by software.

The I2C peripheral supports the Address resolution protocol (ARP). The SMBus device default address (0b1100 001) is enabled by setting the SMBDEN bit of the I2C_CR1 register. The ARP commands must be implemented by the user software.

Arbitration is also performed in slave mode for ARP support.

For more details on the SMBus address resolution protocol, refer to the SMBus specification ( http://smbus.org ).

Received command and data acknowledge control

A SMBus receiver must be able to NACK each received command or data. In order to allow the ACK control in slave mode, the slave byte control mode must be enabled, by setting the SBC bit of the I2C_CR1 register. Refer to Slave byte control mode for more details.

Host notify protocol

To enable the host notify protocol, set the SMBHEN bit of the I2C_CR1 register. The I2C peripheral then acknowledges the SMBus host address (0b0001 000).

When this protocol is used, the device acts as a master and the host as a slave.

SMBus alert

The I2C peripheral supports the SMBALERT# optional signal through the SMBA pin. With the SMBALERT# signal, an SMBus slave device can signal to the SMBus host that it wants to talk. The host processes the interrupt and simultaneously accesses all SMBALERT# devices through the alert response address (0b0001 100). Only the device/devices which pulled SMBALERT# low acknowledges/acknowledge the alert response address.

When the I2C peripheral is configured as an SMBus slave device (SMBHEN = 0), the SMBA pin is pulled low by setting the ALERTEN bit of the I2C_CR1 register. The alert response address is enabled at the same time.

When the I2C peripheral is configured as an SMBus host (SMBHEN = 1), the ALERT flag of the I2C_ISR register is set when a falling edge is detected on the SMBA pin and ALERTEN = 1. An interrupt is generated if the ERRIE bit of the I2C_CR1 register is set. When ALERTEN = 0, the alert line is considered high even if the external SMBA pin is low.

Note: If the SMBus alert pin is not required, keep the ALERTEN bit cleared. The SMBA pin can then be used as a standard GPIO.

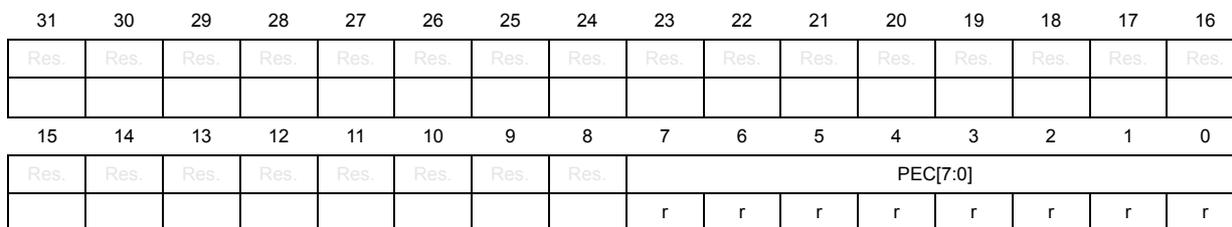

Packet error checking

A packet error checking mechanism introduced in the SMBus specification improves reliability and communication robustness. The packet error checking is implemented by appending a packet error code (PEC) at the end of each message transfer. The PEC is

calculated by using the \( C(x) = x^8 + x^2 + x + 1 \) CRC-8 polynomial on all the message bytes (including addresses and read/write bits).

The I2C peripheral embeds a hardware PEC calculator and allows a not acknowledge to be sent automatically when the received byte does not match the hardware calculated PEC.

Timeouts

To comply with the SMBus timeout specifications, the I2C peripheral embeds hardware timers.

Table 152. SMBus timeout specifications

| Symbol | Parameter | Limits | Unit | |

|---|---|---|---|---|

| Min | Max | |||

| \( t_{\text{TIMEOUT}} \) | Detect clock low timeout | 25 | 35 | ms |

| \( t_{\text{LOW:SEXT}}^{(1)} \) | Cumulative clock low extend time (slave device) | - | 25 | |

| \( t_{\text{LOW:MEXT}}^{(2)} \) | Cumulative clock low extend time (master device) | - | 10 | |

- \( t_{\text{LOW:SEXT}} \) is the cumulative time a given slave device is allowed to extend the clock cycles in one message from the initial START to the STOP. It is possible that another slave device or the master also extends the clock causing the combined clock low extend time to be greater than \( t_{\text{LOW:SEXT}} \) . Therefore, this parameter is measured with the slave device as the sole target of a full-speed master.

- \( t_{\text{LOW:MEXT}} \) is the cumulative time a master device is allowed to extend its clock cycles within each byte of a message as defined from START-to-ACK, ACK-to-ACK, or ACK-to-STOP. It is possible that a slave device or another master also extends the clock, causing the combined clock low time to be greater than \( t_{\text{LOW:MEXT}} \) on a given byte. Therefore, this parameter is measured with a full speed slave device as the sole target of the master.

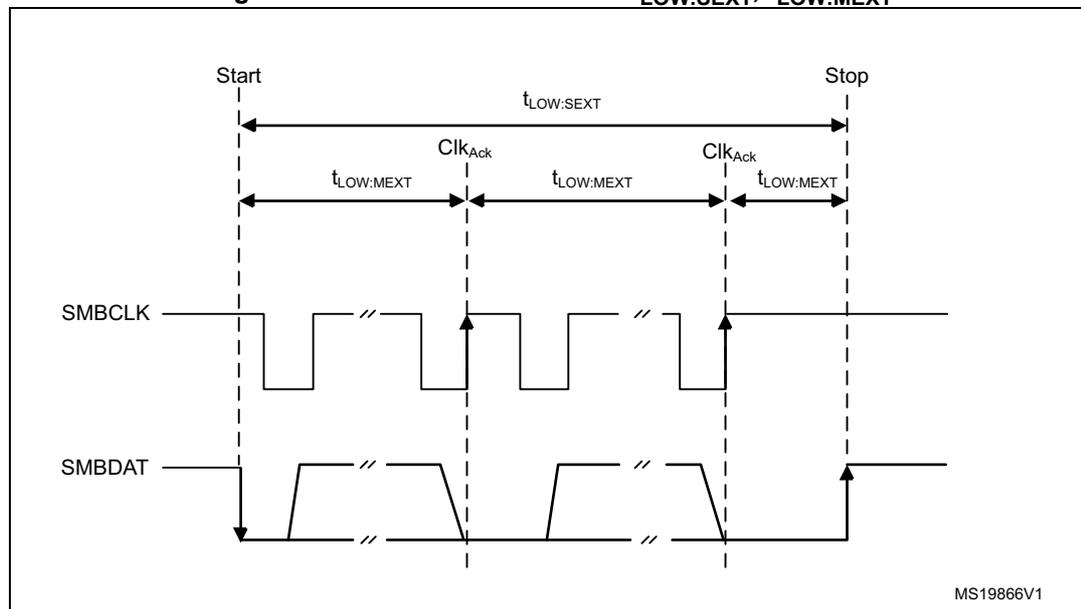

Figure 318. Timeout intervals for \( t_{\text{LOW:SEXT}} \) , \( t_{\text{LOW:MEXT}} \)

The diagram shows two signal lines: SMBCLK (top) and SMBDAT (bottom). The sequence starts with a 'Start' condition and ends with a 'Stop' condition. The SMBCLK signal is shown as a square wave. The SMBDAT signal is shown as a series of pulses. The diagram includes several vertical dashed lines representing key events: 'Start', 'ClkAck' (acknowledge), and 'Stop'. The interval between the 'Start' and the first 'ClkAck' is labeled \( t_{\text{LOW:MEXT}} \) . The interval between the first 'ClkAck' and the second 'ClkAck' is also labeled \( t_{\text{LOW:MEXT}} \) . The interval between the second 'ClkAck' and the 'Stop' condition is labeled \( t_{\text{LOW:MEXT}} \) . The total interval from 'Start' to 'Stop' is labeled \( t_{\text{LOW:SEXT}} \) .

MS19866V1

Bus idle detection

A master can assume that the bus is free if it detects that the clock and data signals have been high for \( t_{\text{IDLE}} > t_{\text{HIGH,MAX}} \) (refer to I2C timings ).

This timing parameter covers the condition where a master is dynamically added to the bus, and may not have detected a state transition on the SMBCLK or SMBDAT lines. In this case, the master must wait long enough to ensure that a transfer is not currently in progress. The I2C peripheral supports a hardware bus idle detection.

28.4.12 SMBus initialization

In addition to the I2C initialization for the I 2 C-bus, the use of the peripheral for the SMBus communication requires some extra initialization steps.

Received command and data acknowledge control (slave mode)

An SMBus receiver must be able to NACK each received command or data. To allow ACK control in slave mode, the slave byte control mode must be enabled, by setting the SBC bit of the I2C_CR1 register. Refer to Slave byte control mode for more details.

Specific addresses (slave mode)

The specific SMBus addresses must be enabled if required. Refer to Bus idle detection for more details.

The SMBus device default address (0b1100 001) is enabled by setting the SMBDEN bit of the I2C_CR1 register.

The SMBus host address (0b0001 000) is enabled by setting the SMBHEN bit of the I2C_CR1 register.

The alert response address (0b0001100) is enabled by setting the ALERTEN bit of the I2C_CR1 register.

Packet error checking

PEC calculation is enabled by setting the PECEN bit of the I2C_CR1 register. Then the PEC transfer is managed with the help of the hardware byte counter associated with the NBBYTES[7:0] bitfield of the I2C_CR2 register. The PECEN bit must be configured before enabling the I2C.

The PEC transfer is managed with the hardware byte counter, so the SBC bit must be set when interfacing the SMBus in slave mode. The PEC is transferred after transferring NBBYTES[7:0] - 1 data bytes, if the PECBYTE bit is set and the RELOAD bit is cleared. If RELOAD is set, PECBYTE has no effect.

Caution: Changing the PECEN configuration is not allowed when the I2C peripheral is enabled.

Table 153. SMBus with PEC configuration

| Mode | SBC bit | RELOAD bit | AUTOEND bit | PECBYTE bit |

|---|---|---|---|---|

| Master Tx/Rx NBBYTES + PEC+ STOP | X | 0 | 1 | 1 |

| Master Tx/Rx NBBYTES + PEC + ReSTART | X | 0 | 0 | 1 |

| Slave Tx/Rx with PEC | 1 | 0 | X | 1 |

Timeout detection

The timeout detection is enabled by setting the TIMOUTEN and TEXTEN bits of the I2C_TIMEOUTR register. The timers must be programmed in such a way that they detect a timeout before the maximum time given in the SMBus specification.

\( t_{\text{TIMEOUT}} \) check

To check the \( t_{\text{TIMEOUT}} \) parameter, load the 12-bit TIMEOUTA[11:0] bitfield with the timer reload value. Keep the TIDLE bit at 0 to detect the SCL low level timeout.

Then set the TIMOUTEN bit of the I2C_TIMEOUTR register, to enable the timer.

If SCL is tied low for longer than the \( (\text{TIMEOUTA} + 1) \times 2048 \times t_{\text{I2CCLK}} \) period, the TIMEOUT flag of the I2C_ISR register is set.

Refer to Table 154 .

Caution: Changing the TIMEOUTA[11:0] bitfield and the TIDLE bit values is not allowed when the TIMOUTEN bit is set.

\( t_{\text{LOW:SEXT}} \) and \( t_{\text{LOW:MEXT}} \) check

A 12-bit timer associated with the TIMEOUTB[11:0] bitfield allows checking \( t_{\text{LOW:SEXT}} \) for the I2C peripheral operating as a slave, or \( t_{\text{LOW:MEXT}} \) when it operates as a master. As the standard only specifies a maximum, the user can choose the same value for both. The timer is then enabled by setting the TEXTEN bit in the I2C_TIMEOUTR register.

If the SMBus peripheral performs a cumulative SCL stretch for longer than the \( (\text{TIMEOUTB} + 1) \times 2048 \times t_{\text{I2CCLK}} \) period, and within the timeout interval described in Bus idle detection section, the TIMEOUT flag of the I2C_ISR register is set.

Refer to Table 155 .

Caution: Changing the TIMEOUTB[11:0] bitfield value is not allowed when the TEXTEN bit is set.

Bus idle detection

To check the \( t_{\text{IDLE}} \) period, the TIMEOUTA[11:0] bitfield associated with 12-bit timer must be loaded with the timer reload value. Keep the TIDLE bit at 1 to detect both SCL and SDA high level timeout. Then set the TIMOUTEN bit of the I2C_TIMEOUTR register to enable the timer.

If both the SCL and SDA lines remain high for longer than the \( (\text{TIMEOUTA} + 1) \times 4 \times t_{\text{I2CCLK}} \) period, the TIMEOUT flag of the I2C_ISR register is set.

Refer to Table 156 .

Caution: Changing the TIMEOUTA[11:0] bitfield and the TIDLE bit values is not allowed when the TIMOUTEN bit is set.

28.4.13 SMBus I2C_TIMEOUTR register configuration examples

The following tables provide examples of settings to reach target \( t_{\text{TIMEOUT}} \) , \( t_{\text{LOW:SEXT}} \) , \( t_{\text{LOW:MEXT}} \) , and \( t_{\text{TIDLE}} \) timings at different \( f_{\text{I2CCLK}} \) frequencies.

Table 154. TIMEOUTA[11:0] for maximum \( t_{\text{TIMEOUT}} \) of 25 ms

| \( f_{\text{I2CCLK}} \) | TIMEOUTA[11:0] | TIDLE | TIMEOUTEN | \( t_{\text{TIMEOUT}} \) |

|---|---|---|---|---|

| 8 MHz | 0x61 | 0 | 1 | \( 98 \times 2048 \times 125 \text{ ns} = 25 \text{ ms} \) |

| 16 MHz | 0xC3 | 0 | 1 | \( 196 \times 2048 \times 62.5 \text{ ns} = 25 \text{ ms} \) |

| 48 MHz | 0x249 | 0 | 1 | \( 586 \times 2048 \times 20.08 \text{ ns} = 25 \text{ ms} \) |

Table 155. TIMEOUTB[11:0] for maximum \( t_{\text{LOW:SEXT}} \) and \( t_{\text{LOW:MEXT}} \) of 8 ms

| \( f_{\text{I2CCLK}} \) | TIMEOUTB[11:0] | TEXTEN | \(

t_{\text{LOW:SEXT}}

\) \( t_{\text{LOW:MEXT}} \) |

|---|---|---|---|

| 8 MHz | 0x1F | 1 | \( 32 \times 2048 \times 125 \text{ ns} = 8 \text{ ms} \) |

| 16 MHz | 0x3F | 1 | \( 64 \times 2048 \times 62.5 \text{ ns} = 8 \text{ ms} \) |

| 48 MHz | 0xBB | 1 | \( 188 \times 2048 \times 20.08 \text{ ns} = 8 \text{ ms} \) |

Table 156. TIMEOUTA[11:0] for maximum \( t_{\text{TIDLE}} \) of 50 \( \mu\text{s} \)

| \( f_{\text{I2CCLK}} \) | TIMEOUTA[11:0] | TIDLE | TIMEOUTEN | \( t_{\text{TIDLE}} \) |

|---|---|---|---|---|

| 8 MHz | 0x63 | 1 | 1 | \( 100 \times 4 \times 125 \text{ ns} = 50 \mu\text{s} \) |

| 16 MHz | 0xC7 | 1 | 1 | \( 200 \times 4 \times 62.5 \text{ ns} = 50 \mu\text{s} \) |

| 48 MHz | 0x257 | 1 | 1 | \( 600 \times 4 \times 20.08 \text{ ns} = 50 \mu\text{s} \) |

28.4.14 SMBus slave mode

In addition to I2C slave transfer management (refer to Section 28.4.8: I2C slave mode ), this section provides extra software flowcharts to support SMBus.

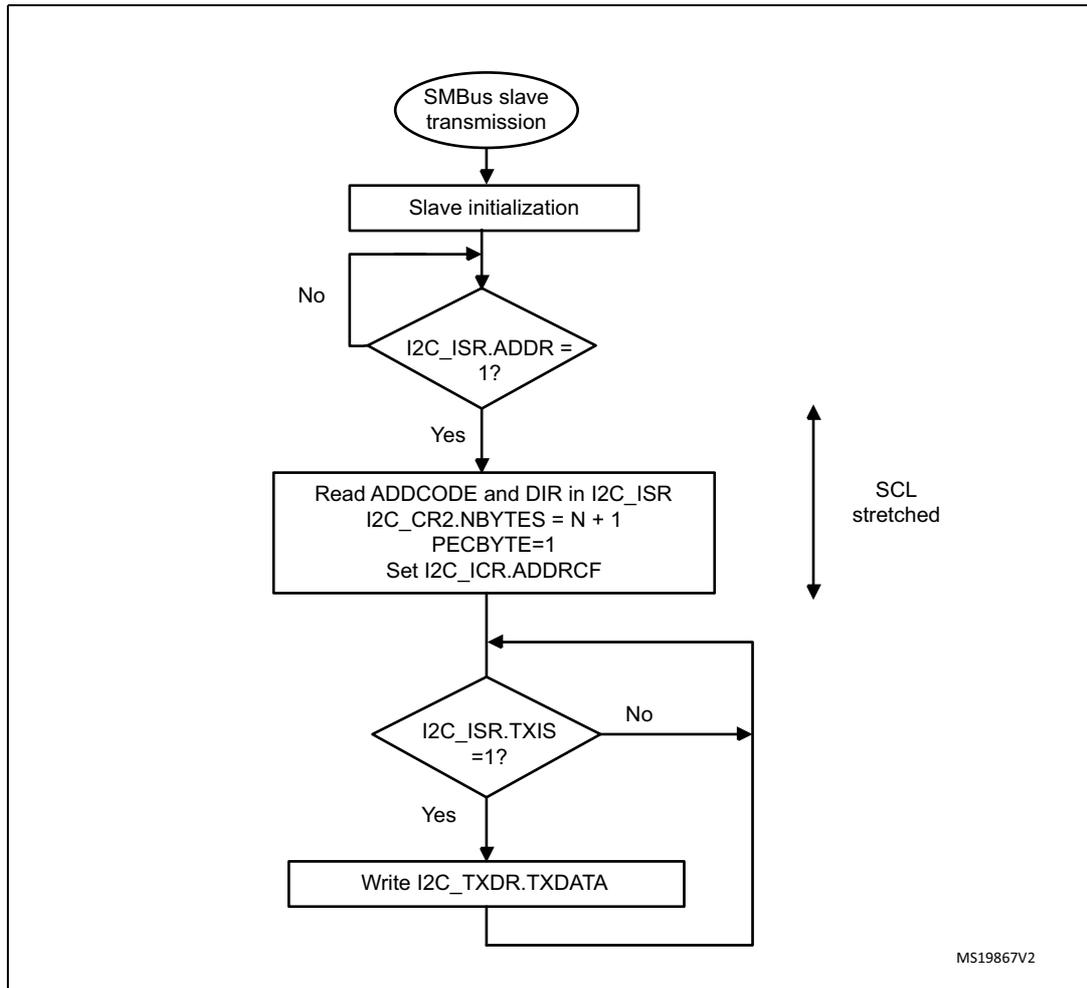

SMBus slave transmitter

When using the I2C peripheral in SMBus mode, set the SBC bit to enable the PEC transmission at the end of the programmed number of data bytes. When the PECBYTE bit is set, the number of bytes programmed in NBBYTES[7:0] includes the PEC transmission. In that case, the total number of TXIS interrupts is NBBYTES[7:0] - 1, and the content of the I2C_PECR register is automatically transmitted if the master requests an extra byte after the transfer of the NBBYTES[7:0] - 1 data bytes.

Caution: The PECBYTE bit has no effect when the RELOAD bit is set.

Figure 319. Transfer sequence flow for SMBus slave transmitter N bytes + PEC

graph TD

Start([SMBus slave transmission]) --> Init[Slave initialization]

Init --> ADDR{I2C_ISR.ADDR = 1?}

ADDR -- No --> Stretched[SCL stretched]

Stretched --> ADDR

ADDR -- Yes --> Config[Read ADDCODE and DIR in I2C_ISR

I2C_CR2.NBYTES = N + 1

PECBYTE=1

Set I2C_ICR.ADDRCF]

Config --> TXIS{I2C_ISR.TXIS = 1?}

TXIS -- No --> TXIS

TXIS -- Yes --> Write[Write I2C_TXDR.TXDATA]

Write --> TXIS

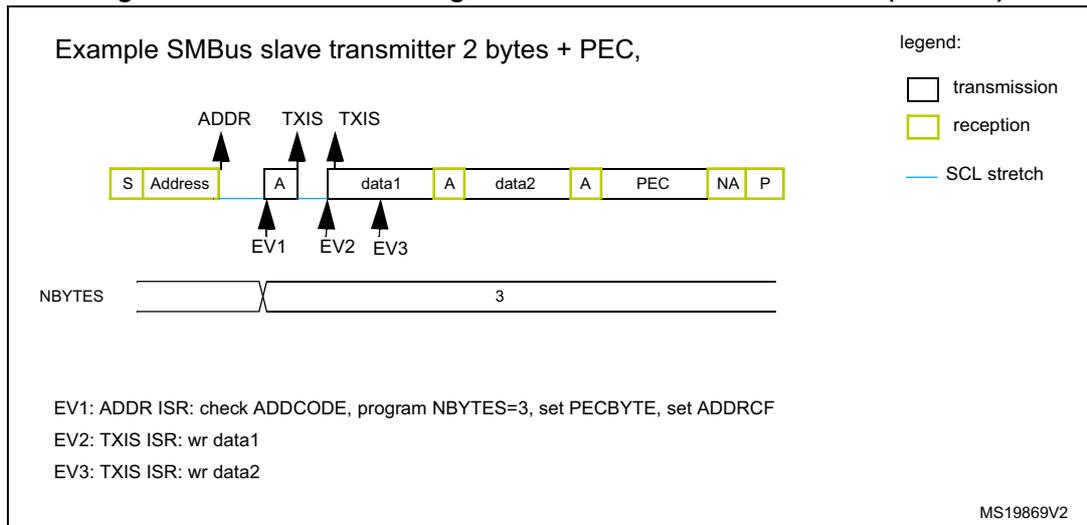

Figure 320. Transfer bus diagram for SMBus slave transmitter (SBC = 1)

Example SMBus slave transmitter 2 bytes + PEC,

legend:

transmission (white box)

reception (yellow box)

SCL stretch (blue line)

Sequence: S Address A data1 A data2 A PEC NA P

Events: EV1 (ADDR ISR), EV2 (TXIS ISR), EV3 (TXIS ISR)

NBYTES: 3

EV1: ADDR ISR: check ADDCODE, program NBYTES=3, set PECBYTE, set ADDRCF

EV2: TXIS ISR: wr data1

EV3: TXIS ISR: wr data2

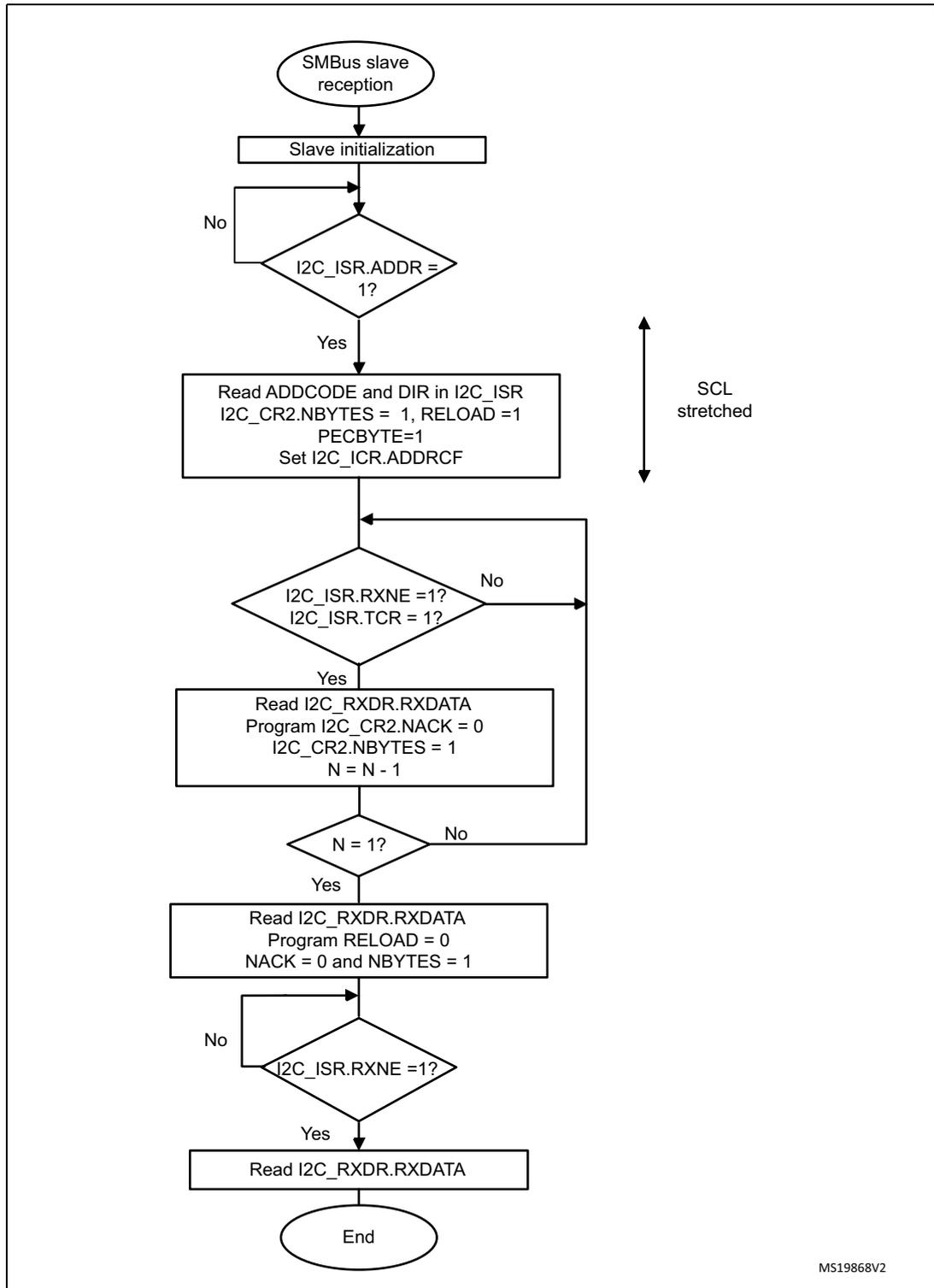

SMBus slave receiver

When using the I2C peripheral in SMBus mode, set the SBC bit to enable the PEC checking at the end of the programmed number of data bytes. To allow the ACK control of each byte, the reload mode must be selected (RELOAD = 1). Refer to Slave byte control mode for more details.

To check the PEC byte, the RELOAD bit must be cleared and the PECBYTE bit must be set. In this case, after the receipt of NBBYTES[7:0] - 1 data bytes, the next received byte is compared with the internal I2C_PECR register content. A NACK is automatically generated if the comparison does not match, and an ACK is automatically generated if the comparison matches, whatever the ACK bit value. Once the PEC byte is received, it is copied into the I2C_RXDR register like any other data, and the RXNE flag is set.

Upon a PEC mismatch, the PECERR flag is set and an interrupt is generated if the ERRIE bit of the I2C_CR1 register is set.

If no ACK software control is required, the user can set the PECBYTE bit and, in the same write operation, load NBBYTES[7:0] with the number of bytes to receive in a continuous flow. After the receipt of NBBYTES[7:0] - 1 bytes, the next received byte is checked as being the PEC.

Caution: The PECBYTE bit has no effect when the RELOAD bit is set.

Figure 321. Transfer sequence flow for SMBus slave receiver N bytes + PEC

graph TD

Start([SMBus slave reception]) --> Init[Slave initialization]

Init --> AddrMatch{I2C_ISR.ADDR = 1?}

AddrMatch -- No --> Init

AddrMatch -- Yes --> InitParams["Read ADDCODE and DIR in I2C_ISR

I2C_CR2.NBYTES = 1, RELOAD = 1

PECBYTE = 1

Set I2C_ICR.ADDRCF"]

InitParams --> RXNE_TCR{I2C_ISR.RXNE = 1?

I2C_ISR.TCR = 1?}

RXNE_TCR -- No --> AddrMatch

RXNE_TCR -- Yes --> ReadData1["Read I2C_RXDR.RXDATA

Program I2C_CR2.NACK = 0

I2C_CR2.NBYTES = 1

N = N - 1"]

ReadData1 --> NEquals1{N = 1?}

NEquals1 -- No --> RXNE_TCR

NEquals1 -- Yes --> ReadData2["Read I2C_RXDR.RXDATA

Program RELOAD = 0

NACK = 0 and NBYTES = 1"]

ReadData2 --> RXNE{I2C_ISR.RXNE = 1?}

RXNE -- No --> RXNE_TCR

RXNE -- Yes --> ReadData3[Read I2C_RXDR.RXDATA]

ReadData3 --> End([End])

SCL stretched

MS19868V2

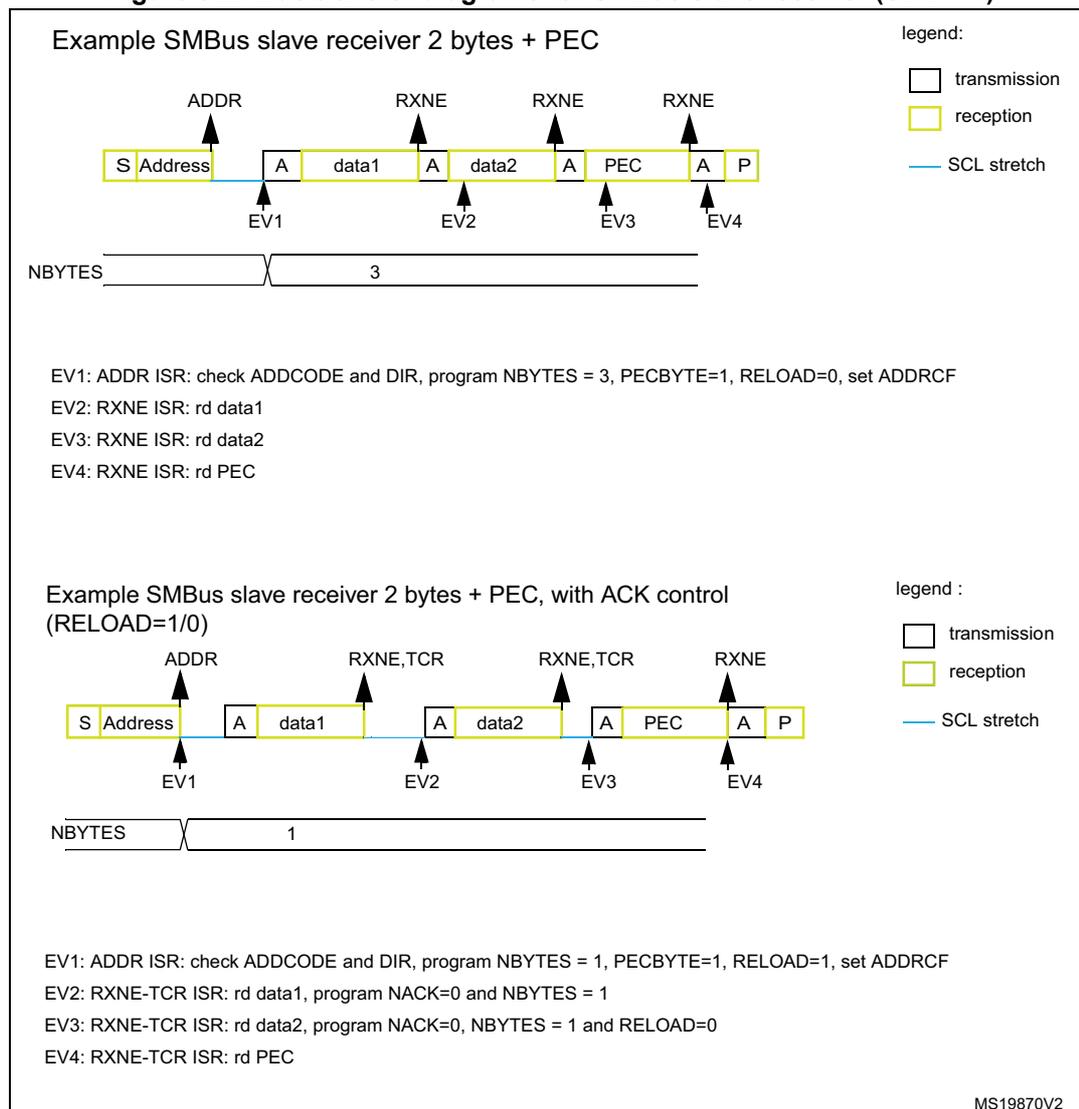

Figure 322. Bus transfer diagrams for SMBus slave receiver (SBC = 1)

Example SMBus slave receiver 2 bytes + PEC

legend:

- transmission

- reception

- SCL stretch

NBYTES 3

EV1: ADDR ISR: check ADDCODE and DIR, program NBYTES = 3, PECBYTE=1, RELOAD=0, set ADDRCF

EV2: RXNE ISR: rd data1

EV3: RXNE ISR: rd data2

EV4: RXNE ISR: rd PEC

Example SMBus slave receiver 2 bytes + PEC, with ACK control (RELOAD=1/0)

legend :

- transmission

- reception

- SCL stretch

NBYTES 1

EV1: ADDR ISR: check ADDCODE and DIR, program NBYTES = 1, PECBYTE=1, RELOAD=1, set ADDRCF

EV2: RXNE-TCR ISR: rd data1, program NACK=0 and NBYTES = 1

EV3: RXNE-TCR ISR: rd data2, program NACK=0, NBYTES = 1 and RELOAD=0

EV4: RXNE-TCR ISR: rd PEC

MS19870V2

28.4.15 SMBus master mode

In addition to I2C master transfer management (refer to Section 28.4.9: I2C master mode ), this section provides extra software flowcharts to support SMBus.

SMBus master transmitter

When the SMBus master wants to transmit the PEC, the PECBYTE bit must be set and the number of bytes must be loaded in the NBYTES[7:0] bitfield, before setting the START bit. In this case, the total number of TXIS interrupts is NBYTES[7:0] - 1. So if the PECBYTE bit is set when NBYTES[7:0] = 0x1, the content of the I2C_PECR register is automatically transmitted.

If the SMBus master wants to send a STOP condition after the PEC, the automatic end mode must be selected (AUTOEND = 1). In this case, the STOP condition automatically follows the PEC transmission.

When the SMBus master wants to send a RESTART condition after the PEC, the software mode must be selected (AUTOEND = 0). In this case, once NBBYTES[7:0] - 1 are transmitted, the I2C_PECR register content is transmitted. The TC flag is set after the PEC transmission, stretching the SCL line low. The RESTART condition must be programmed in the TC interrupt subroutine.

Caution: The PECBYTE bit has no effect when the RELOAD bit is set.

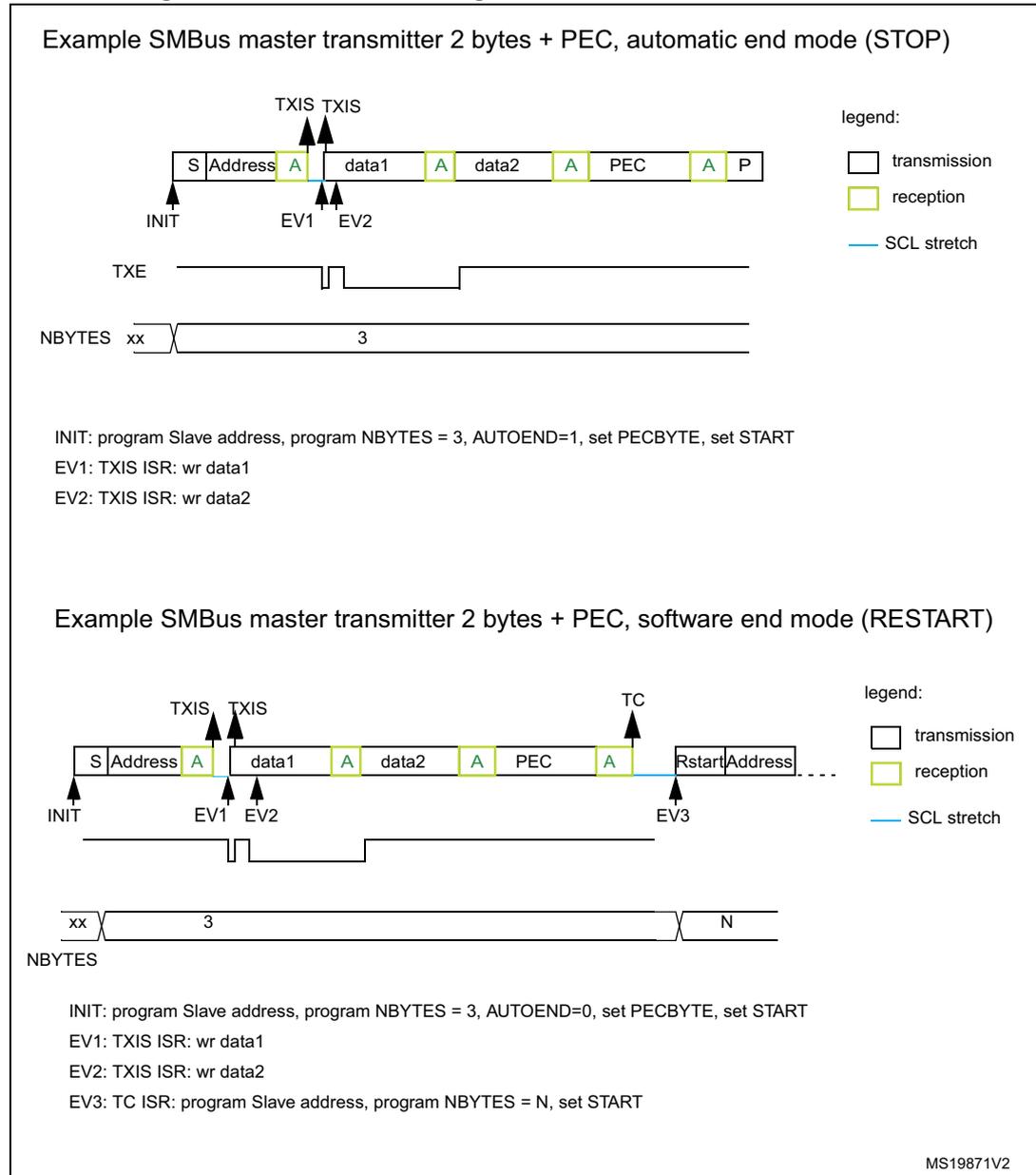

Figure 323. Bus transfer diagrams for SMBus master transmitter

Example SMBus master transmitter 2 bytes + PEC, automatic end mode (STOP)

INIT: program Slave address, program NBBYTES = 3, AUTOEND=1, set PECBYTE, set START

EV1: TXIS ISR: wr data1

EV2: TXIS ISR: wr data2

Example SMBus master transmitter 2 bytes + PEC, software end mode (RESTART)

INIT: program Slave address, program NBBYTES = 3, AUTOEND=0, set PECBYTE, set START

EV1: TXIS ISR: wr data1

EV2: TXIS ISR: wr data2

EV3: TC ISR: program Slave address, program NBBYTES = N, set START

MS19871V2

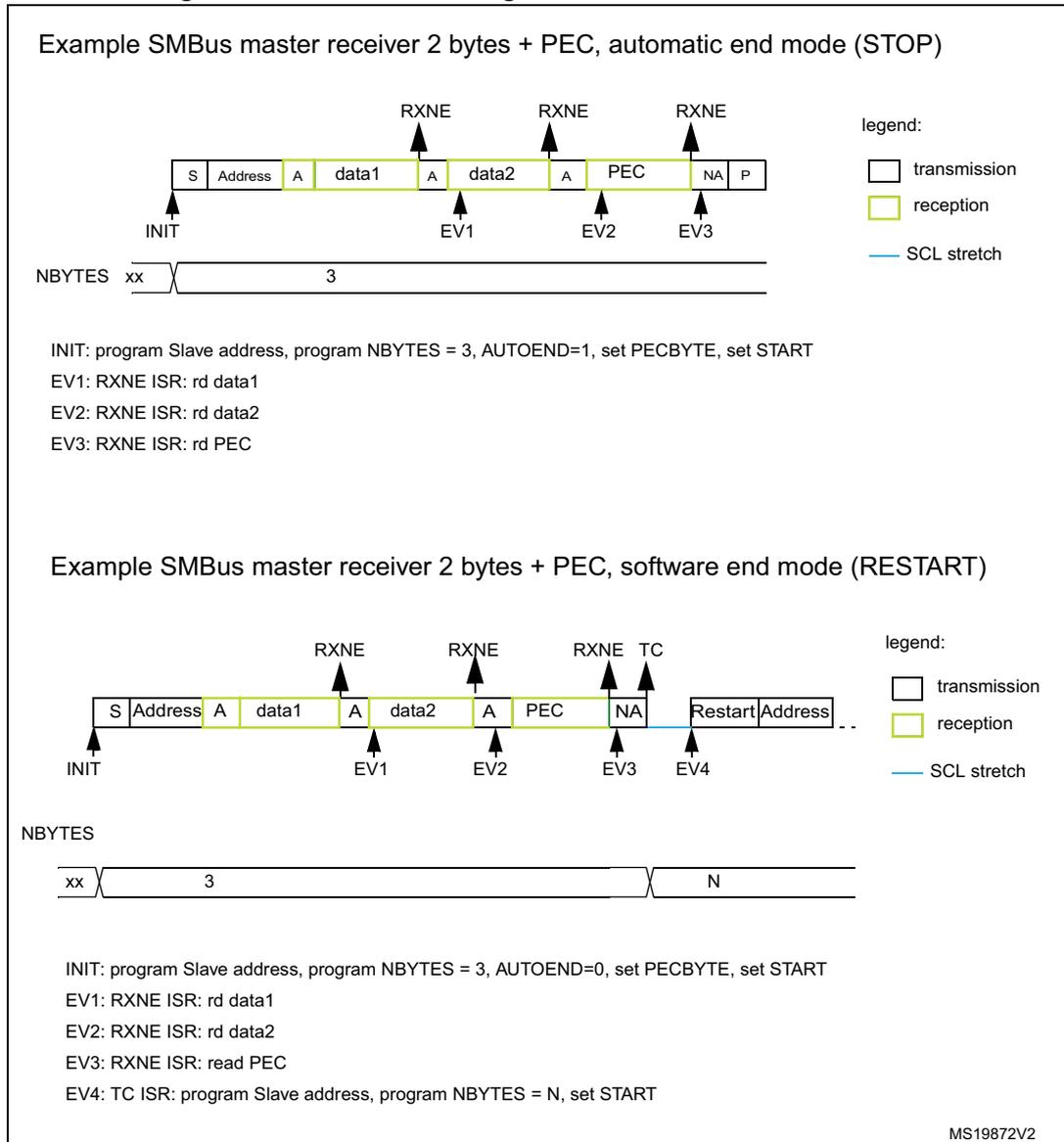

SMBus master receiver